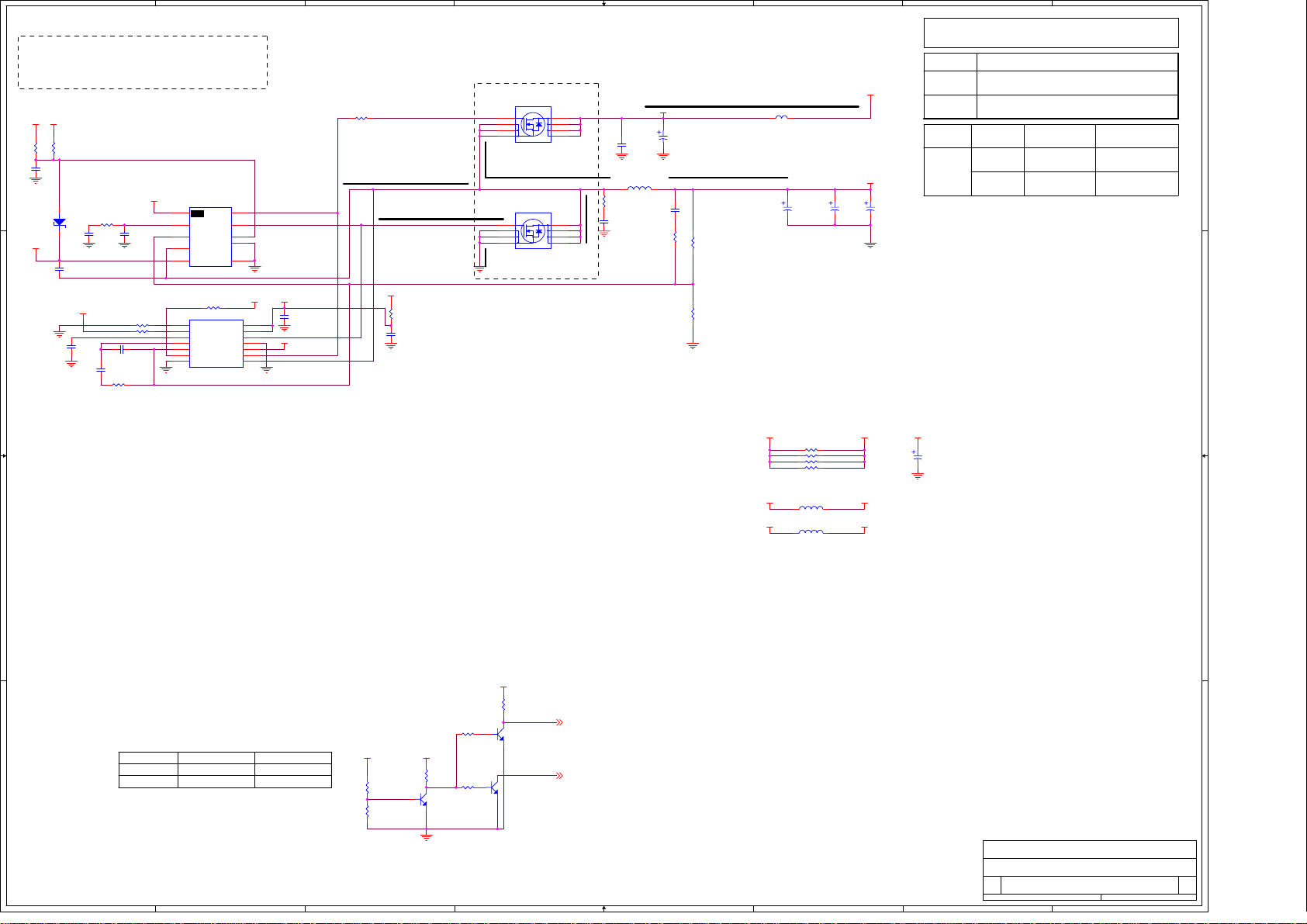

Gigabyte gv-rx30s128d_hynix1220 Schematics

8

7

6

5

4

3

2

1

+12V_BUS

C5

100uF_16V

DNI DNI DNI

D D

A_HSYNC_DAC1(2,11)

PETp0_GFXRp0(2)

PETn0_GFXRn0(2)

PETp1_GFXRp1(2)

C C

B B

PETn1_GFXRn1(2)

PETp2_GFXRp2(2)

PETn2_GFXRn2(2)

PETp3_GFXRp3(2)

PETn3_GFXRn3(2)

PETp4_GFXRp4(2)

PETn4_GFXRn4(2)

PETp5_GFXRp5(2)

PETn5_GFXRn5(2)

PETp6_GFXRp6(2)

PETn6_GFXRn6(2)

PETp7_GFXRp7(2)

PETn7_GFXRn7(2)

PETp8_GFXRp8(2)

PETn8_GFXRn8(2)

PETp9_GFXRp9(2)

PETn9_GFXRn9(2)

PETp10_GFXRp10(2)

PETn10_GFXRn10(2)

PETp11_GFXRp11(2)

PETn11_GFXRn11(2)

PETp12_GFXRp12(2)

PETn12_GFXRn12(2)

PETp13_GFXRp13(2)

PETn13_GFXRn13(2)

PETp14_GFXRp14(2)

PETn14_GFXRn14(2)

PETp15_GFXRp15(2)

PETn15_GFXRn15(2)

C8

100uF_16V

+3.3V_BUS+3.3V_BUS

USE 47uF TANTALUM

C2

CAPACITOR OR HIGHER

47uF_16V/X

>=6.3V>=6.3V

R1008 0R/X

TP28

TP30

TP29

TP32

TP31

TP34

TP33

TP36

TP35

TP38

TP37

TP40

TP39

TP42

TP41

TP44

TP43

TP46

TP45

TP48

TP47

TP50

TP49

TP52

TP51

TP54

TP53

TP56

TP55

TP58

TP57

PRESENCE

TP59

402

JTAG_TRST#

DNI

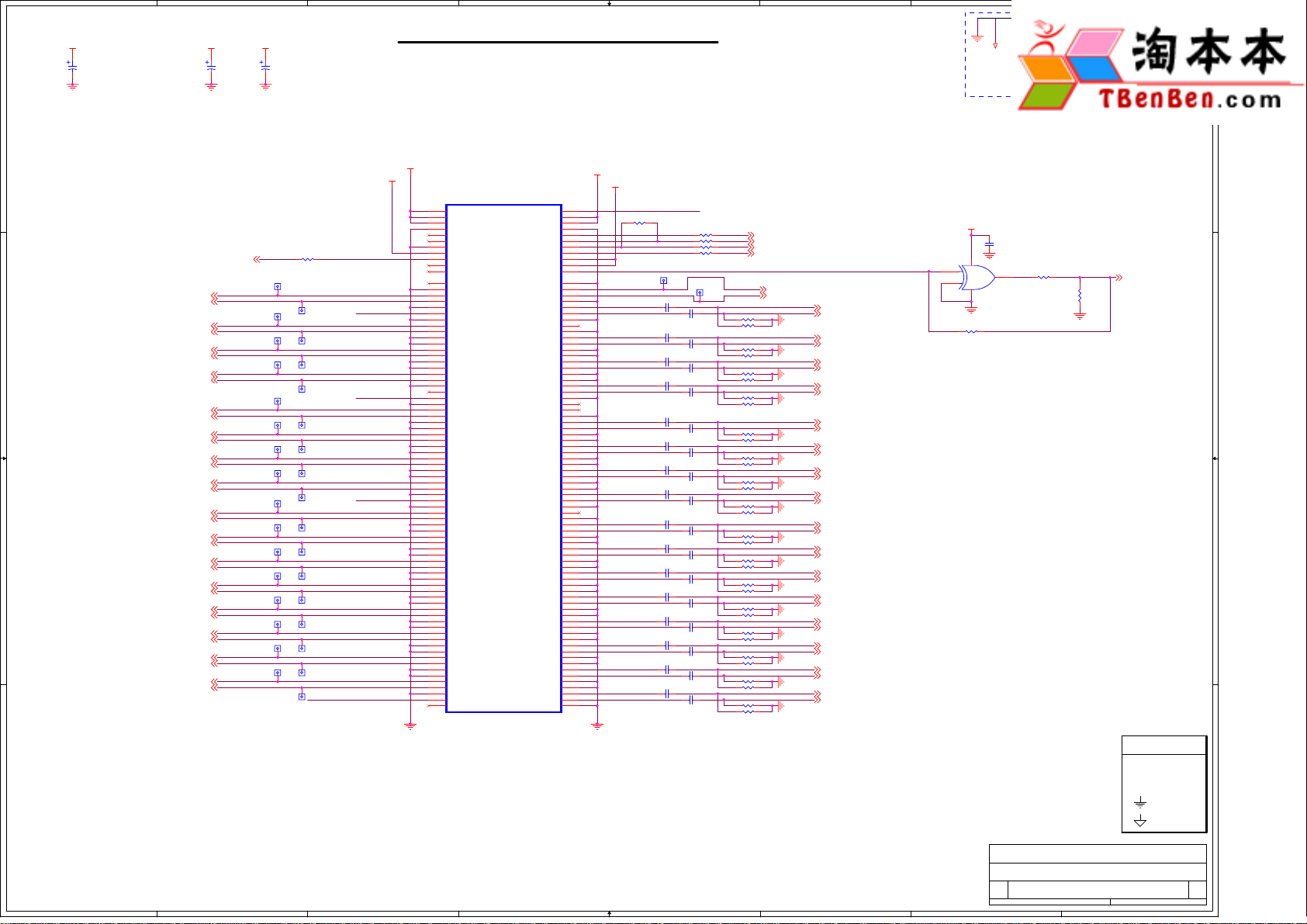

PCI-EXPRESS EDGE CONNECTOR

+3.3V_BUS

PRESENT_NULL

PRESENT_NULL

PRESENT_NULL

+12V_BUS

B1

B2

B3

B4

B5

B6

B7

B8

B9

B10

B11

B12

B13

B14

B15

B16

B17

B18

B19

B20

B21

B22

B23

B24

B25

B26

B27

B28

B29

B30

B31

B32

B33

B34

B35

B36

B37

B38

B39

B40

B41

B42

B43

B44

B45

B46

B47

B48

B49

B50

B51

B52

B53

B54

B55

B56

B57

B58

B59

B60

B61

B62

B63

B64

B65

B66

B67

B68

B69

B70

B71

B72

B73

B74

B75

B76

B77

B78

B79

B80

B81

B82

MPCIE1

+12V#B1

+12V#B2

RSVD#B3

GND#B4

SMCLK

SMDAT

GND#B7

+3.3V#B8

JTAG1

3.3Vaux

WAKE#

RSVD#B12

GND#B13

PETp0

PETn0

GND#B16

PRSNT2#B17

GND#B18

PETp1

PETn1

GND#B21

GND#B22

PETp2

PETn2

GND#B25

GND#B26

PETp3

PETn3

GND#B29

RSVD#B30

PRSNT2#B31

GND#B32

PETp4

PETn4

GND#B35

GND#B36

PETp5

PETn5

GND#B39

GND#B40

PETp6

PETn6

GND#B43

GND#B44

PETp7

PETn7

GND#B47

PRSNT2#B48

GND#B49

PETp8

PETn8

GND#B52

GND#B53

PETp9

PETn9

GND#B56

GND#B57

PETp10

PETn10

GND#B60

GND#B61

PETp11

PETn11

GND#B64

GND#B65

PETp12

PETn12

GND#B68

GND#B69

PETp13

PETn13

GND#B72

GND#B73

PETp14

PETn14

GND#B76

GND#B77

PETp15

PETn15

GND#B80

PRSNT2#B81

RSVD#B82

x16 PCIe

Mechanical Key

PRSNT1#A1

+12V#A2

+12V#A3

GND#A4

+3.3V#A9

+3.3V#A10

PERST#

GND#A12

REFCLK+

REFCLK-

GND#A15

GND#A18

RSVD#A19

GND#A20

GND#A23

GND#A24

GND#A27

GND#A28

GND#A31

RSVD#A32

RSVD#A33

GND#A34

GND#A37

GND#A38

GND#A41

GND#A42

GND#A45

GND#A46

GND#A49

RSVD#A50

GND#A51

GND#A54

GND#A55

GND#A58

GND#A59

PERp10

PERn10

GND#A62

GND#A63

PERp11

PERn11

GND#A66

GND#A67

PERp12

PERn12

GND#A70

GND#A71

PERp13

PERn13

GND#A74

GND#A75

PERp14

PERn14

GND#A78

GND#A79

PERp15

PERn15

GND#A82

JTAG2

JTAG3

JTAG4

JTAG5

PERp0

PERn0

PERp1

PERn1

PERp2

PERn2

PERp3

PERn3

PERp4

PERn4

PERp5

PERn5

PERp6

PERn6

PERp7

PERn7

PERp8

PERn8

PERp9

PERn9

+12V_BUS

+3.3V_BUS

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

A16

A17

A18

A19

A20

A21

A22

A23

A24

A25

A26

A27

A28

A29

A30

A31

A32

A33

A34

A35

A36

A37

A38

A39

A40

A41

A42

A43

A44

A45

A46

A47

A48

A49

A50

A51

A52

A53

A54

A55

A56

A57

A58

A59

A60

A61

A62

A63

A64

A65

A66

A67

A68

A69

A70

A71

A72

A73

A74

A75

A76

A77

A78

A79

A80

A81

A82

PERp0

PERn0

PERp1

PERn1

PERp2

PERn2

PERp3

PERn3

PERp4

PERn4

PERp5

PERn5

PERp6

PERn6

PERp7

PERn7

PERp8

PERn8

PERp9

PERn9

PERp10

PERn10

PERp11

PERn11

PERp12

PERn12

PERp13

PERn13

PERp14

PERn14

PERp15

PERn15

JTAG_TCK

JTAG_TDI

JTAG_TDO

JTAG_TMS

PRESENCE

R12440R

DNI

402

RP194A 0R/X

8 1

RP194B 0R/X

7 2

RP194C 0R/X

6 3

RP194D 0R/X

5 4

TP26

TP27

C607

C608

100nF

100nF

C617

C618

100nF

100nF

C626

C627

100nF

100nF

C631

100nF

C632

100nF

C611

C612

100nF

100nF

C622

100nF

C623

100nF

C621

C630

100nF

100nF

C605

C606

100nF

100nF

C615

C616

100nF

100nF

C624

C625

100nF

100nF

C633

C634

100nF

100nF

C609

100nF

C610

100nF

C619

C620

100nF

100nF

C628

C629

100nF

100nF

C603

C604

100nF

100nF

C613

C614

100nF

100nF

DNI

A_VSYNC_DAC1 (2,11)

DNI

CRT1DDCDATA (2,11)

DNI

SCL (2)

DNI

CRT1DDCCLK (2,11)

R701 2.21K/X

R702 2.21K/X

R703 2.21K/X

R704 2.21K/X

R705 2.21K/X

R706 2.21K/X

R707 2.21K/X

R708 2.21K/X

R709 2.21K/X

R710 2.21K/X

R711 2.21K/X

R712 2.21K/X

R713 2.21K/X

R714 2.21K/X

R715 2.21K/X

R716 2.21K/X

R717 2.21K/X

R718 2.21K/X

R719 2.21K/X

R720 2.21K/X

R721 2.21K/X

R722 2.21K/X

R723 2.21K/X

R724 2.21K/X

R725 2.21K/X

R726 2.21K/X

R727 2.21K/X

R728 2.21K/X

R729 2.21K/X

R730 2.21K/X

R731 2.21K/X

R732 2.21K/X

PCIE_REFCLKP (2)

PCIE_REFCLKN (2)

GFXTp0_PERp0 (2)

GFXTn0_PERn0 (2)

GFXTp1_PERp1 (2)

GFXTn1_PERn1 (2)

GFXTp2_PERp2 (2)

GFXTn2_PERn2 (2)

GFXTp3_PERp3 (2)

GFXTn3_PERn3 (2)

GFXTp4_PERp4 (2)

GFXTn4_PERn4 (2)

GFXTp5_PERp5 (2)

GFXTn5_PERn5 (2)

GFXTp6_PERp6 (2)

GFXTn6_PERn6 (2)

GFXTp7_PERp7 (2)

GFXTn7_PERn7 (2)

GFXTp8_PERp8 (2)

GFXTn8_PERn8 (2)

GFXTp9_PERp9 (2)

GFXTn9_PERn9 (2)

GFXTp10_PERp10 (2)

GFXTn10_PERn10 (2)

GFXTp11_PERp11 (2)

GFXTn11_PERn11 (2)

GFXTp12_PERp12 (2)

GFXTn12_PERn12 (2)

GFXTp13_PERp13 (2)

GFXTn13_PERn13 (2)

GFXTp14_PERp14 (2)

GFXTn14_PERn14 (2)

GFXTp15_PERp15 (2)

GFXTn15_PERn15 (2)

PERST#

NOTE: THIS IS A DRAWING. THESE

GROUNDS MUST BE MANUALLY

CONNECTED TO THE GROUND PLANE

+5V

147

1

2

R64 0R/X

DNI

GND_PVSS GND_TXVSSR

C972

100nF

402

SN74ACT86D

U6A

R3 100R

3

402

GND_TPVSSGND_MPVSS

GND_A2VSSN

GND_AVSSQ GND_RSET

GND_R2SETGND_AVSSN

PERST#_buf (2)

R4

180R

402

GND_A2VSSQ

SYMBOL LEGEND

DO NOT

DNI

INSTALL

ACTIVE

#

LOW

A A

Title

Size Docum e n t N u mb er Re v

C

8

7

6

5

4

3

Date: Sheet

2

GIGABYTE

PCI-E Edge Connector

GV-RX30S128D-RH-HT

DIGITAL

GROUND

ANALOG

GROUND

01 16Tuesday, De ce m ber 27, 2005

1

1.1

of

5

4

3

2

1

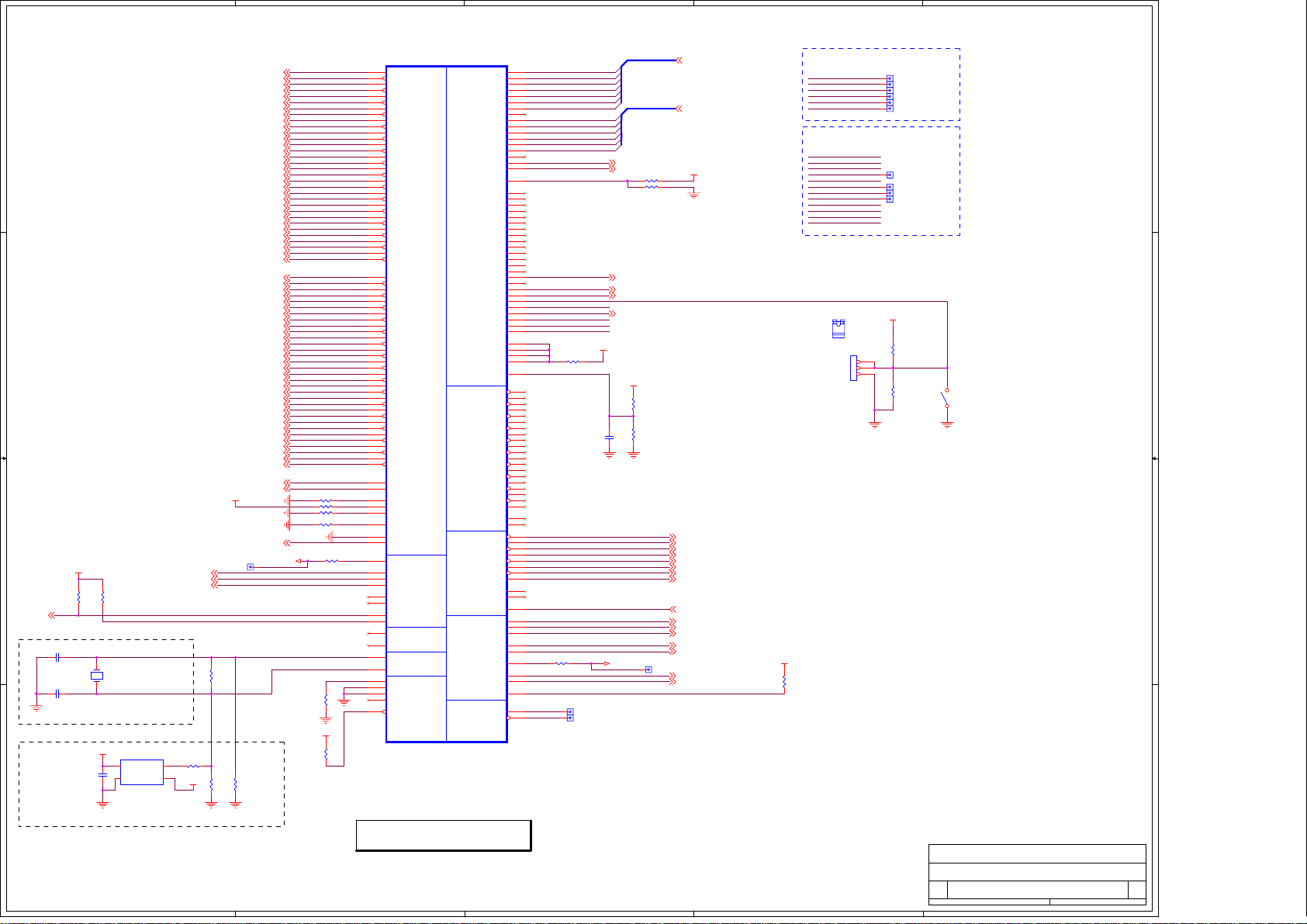

+3.3V_BUS

Mem_Strap1 (10)

Mem_Strap0 (10)

SVHS/YPrPbb (13)

LCDDATA16 (10)

LCDDATA17 (10)

VHAD0 (10)

+3.3V_BUS

C16

100nF

402

A_HSYNC_DAC1

GND_RSET

GPIO[6..0]

GPIO[13..8]

R22 10K/X

R23 10K

Pull-up to 1.8V

12bit-DVO mode for SDR

Ext. TMDS 1.8V DVO I/O

U1A

PETp0_GFXRp0(1)

PETn0_GFXRn0(1)

PETp1_GFXRp1(1)

PETn1_GFXRn1(1)

PETp2_GFXRp2(1)

PETn2_GFXRn2(1)

PETp3_GFXRp3(1)

D D

C C

SCL(1)

C71 15PF

C72 15PF

+3.3V_BUS

R45

R46

4.7K

4.7K

402 402

402

Y1

27_MHZ

2 1

402

OPTION 1: Crystal Circuit

+3.3V_BUS

4

C18

2

100nF/X

402

5015270000

B B

A A

MY1

VCC

GND

27.000MHz/X

A_R/C_DAC2(13)

A_G/Y_DAC2(13)

A_B/COMP_DAC2(13)

R27

220R/X

3

OUT

1

E/D

+3.3V_BUS

PETn3_GFXRn3(1)

PETp4_GFXRp4(1)

PETn4_GFXRn4(1)

PETp5_GFXRp5(1)

PETn5_GFXRn5(1)

PETp6_GFXRp6(1)

PETn6_GFXRn6(1)

PETp7_GFXRp7(1)

PETn7_GFXRn7(1)

PETp8_GFXRp8(1)

PETn8_GFXRn8(1)

PETp9_GFXRp9(1)

PETn9_GFXRn9(1)

PETp10_GFXRp10(1)

PETn10_GFXRn10(1)

PETp11_GFXRp11(1)

PETn11_GFXRn11(1)

PETp12_GFXRp12(1)

PETn12_GFXRn12(1)

PETp13_GFXRp13(1)

PETn13_GFXRn13(1)

PETp14_GFXRp14(1)

PETn14_GFXRn14(1)

PETp15_GFXRp15(1)

PETn15_GFXRn15(1)

GFXTp0_PERp0(1)

GFXTn0_PERn0(1)

GFXTp1_PERp1(1)

GFXTn1_PERn1(1)

GFXTp2_PERp2(1)

GFXTn2_PERn2(1)

GFXTp3_PERp3(1)

GFXTn3_PERn3(1)

GFXTp4_PERp4(1)

GFXTn4_PERn4(1)

GFXTp5_PERp5(1)

GFXTn5_PERn5(1)

GFXTp6_PERp6(1)

GFXTn6_PERn6(1)

GFXTp7_PERp7(1)

GFXTn7_PERn7(1)

GFXTp8_PERp8(1)

GFXTn8_PERn8(1)

GFXTp9_PERp9(1)

GFXTn9_PERn9(1)

GFXTp10_PERp10(1)

GFXTn10_PERn10(1)

GFXTp11_PERp11(1)

GFXTn11_PERn11(1)

GFXTp12_PERp12(1)

GFXTn12_PERn12(1)

GFXTp13_PERp13(1)

GFXTn13_PERn13(1)

GFXTp14_PERp14(1)

GFXTn14_PERn14(1)

GFXTp15_PERp15(1)

GFXTn15_PERn15(1)

PCIE_REFCLKP(1)

PCIE_REFCLKN(1)

+PCIE_VDDR

TP6

R32

1.0M

402

R28

130R/X

R1009 150R

R1010 100R

R1011 10K

R1089 10K

PERST#_buf(1)

R29

0R/X

402

GND_R2SET

R40 715R

R33

1K

402

+3.3V_BUS

R44

10K

402

OPTION 2: Oscillator Circuit

5

AH30

PCIE_RX0P

AG30

PCIE_RX0N

AG29

PCIE_RX1P

AF29

PCIE_RX1N

AE29

PCIE_RX2P

AE30

PCIE_RX2N

AD30

PCIE_RX3P

AD29

PCIE_RX3N

AC29

PCIE_RX4P

AB29

PCIE_RX4N

AB30

PCIE_RX5P

AA30

PCIE_RX5N

AA29

PCIE_RX6P

Y29

PCIE_RX6N

W29

PCIE_RX7P

W30

PCIE_RX7N

V30

PCIE_RX8P

V29

PCIE_RX8N

U29

PCIE_RX9P

T29

PCIE_RX9N

T30

PCIE_RX10P

R30

PCIE_RX10N

R29

PCIE_RX11P

P29

PCIE_RX11N

N29

PCIE_RX12P

N30

PCIE_RX12N

M30

PCIE_RX13P

M29

PCIE_RX13N

L29

PCIE_RX14P

K29

PCIE_RX14N

K30

PCIE_RX15P

J30

PCIE_RX15N

AF26

PCIE_TX0P

AE26

PCIE_TX0N

AC25

PCIE_TX1P

AB25

PCIE_TX1N

AC27

PCIE_TX2P

AB27

PCIE_TX2N

AC26

PCIE_TX3P

AB26

PCIE_TX3N

Y25

PCIE_TX4P

W25

PCIE_TX4N

Y27

PCIE_TX5P

W27

PCIE_TX5N

Y26

PCIE_TX6P

W26

PCIE_TX6N

U25

PCIE_TX7P

T25

PCIE_TX7N

U27

PCIE_TX8P

T27

PCIE_TX8N

U26

PCIE_TX9P

T26

PCIE_TX9N

P25

PCIE_TX10P

N25

PCIE_TX10N

P27

PCIE_TX11P

N27

PCIE_TX11N

P26

PCIE_TX12P

N26

PCIE_TX12N

L25

PCIE_TX13P

K25

PCIE_TX13N

L27

PCIE_TX14P

K27

PCIE_TX14N

L26

PCIE_TX15P

K26

PCIE_TX15N

AF27

PCIE_REFCLKP

AE27

PCIE_REFCLKN

402

AC23

PCIE_CALRP

402

AB24

PCIE_CALRN

402

AB23

PCIE_CALI

402

AE25

PCIE_TEST

AD24

PWRGD_MASK

AD25

PWRGD

AH21

R2SET

402

AJ22

C_R_PR

AK21

Y_G

AK22

COMP_B_PB

AJ24

H2SYNC

AK24

V2SYNC

AG22

DDC3CLK

AG23

DDC3DATA

AJ23

NC#AJ23

AH24

NC#AH24

AH28

XTALIN

AJ29

XTALOUT

TESTEN

AH27

TESTEN

E8

TEST_YCLK

B6

TEST_MCLK

AF25

PLLTEST

AH25

STEREOSYNC

RV370SE

IT IS RECOMMENDED TO ALLOW SERIES RESISTOR

FOOT PRINTS ON THE INDICATED AGP CONTROL SIGNALS

TO ADDRESS ANY LAYOUT NOISE RELATED

SIGNAL DAMPING REQUIREMENTS

4

PCI Express

DAC2CLK

Part 1 of 6

GPIO_PWRCNTL

GPIO_MEMSSIN

DVOVMODE

DVPDATA_0

DVPDATA_1

DVPDATA_2

DVPDATA_3

DVPDATA_4

DVPDATA_5

DVPDATA_6

DVPDATA_7

DVPDATA_8

DVPDATA_9

DVPDATA_10

DVPDATA_11

DVPDATA_12

DVPDATA_13

DVPDATA_14

DVPDATA_15

DVPDATA_16

DVPDATA_17

DVPDATA_18

DVPDATA_19

DVPDATA_20

DVPDATA_21

DVO / EXT TMDS / GPIOTMDSDAC1

DVPDATA_22

DVPDATA_23

DVPCNTL_0

DVPCNTL_1

DVPCNTL_2

DVPCNTL_3

GPIO__AUXWIN

THERM

GPIO_0

GPIO_1

GPIO_2

GPIO_3

GPIO_4

GPIO_5

GPIO_6

GPIO_7

GPIO_8

GPIO_9

GPIO_10

GPIO_11

GPIO_12

GPIO_13

GPIO_14

VREFG

NC#AH15

NC#AH16

NC#AJ16

NC#AJ17

NC#AJ18

NC#AK18

NC#AJ20

NC#AJ21

NC#AK19

NC#AJ19

NC#AG16

NC#AG17

NC#AF16

NC#AF17

NC#AE18

NC#AE19

NC#AF19

NC#AF20

NC#AG19

NC#AG20

NC#AE12

NC#AG12

TX0M

TX0P

TX1M

TX1P

TX2M

TX2P

TXCM

TXCP

DDC2CLK

DDC2DATA

HPD1

HSYNC

VSYNC

RSET

DDC1DATA

DDC1CLK

DPLUS

DMINUS

R

G

B

AJ5

AH5

AJ4

AK4

AH4

AF4

AJ3

AK3

AH3

AJ2

AH2

AH1

AG3

AG1

AG2

AF3

AF2

AE10

AH6

AJ6

AK6

AH7

AK7

AJ7

AH8

AJ8

AH9

AJ9

AK9

AH10

AE6

AG6

AF6

AE7

AF7

AE8

AG8

AF8

AE9

AF9

AG10

AF10

AJ10

AK10

AJ11

AH11

AG4

AH15

AH16

AJ16

AJ17

AJ18

AK18

AJ20

AJ21

AK19

AJ19

AG16

AG17

AF16

AF17

AE18

AE19

AF19

AF20

AG19

AG20

AE12

AG12

AK13

AJ13

AJ14

AJ15

AK15

AK16

AJ12

AK12

AE13

AE14

AF12

AK27

AJ27

AJ26

AJ25

AK25

AH26

AG25

AF24

AG24

AF11

AE11

GPIO0

GPIO1

GPIO2

GPIO3

GPIO4

GPIO5

GPIO6

GPIO8

GPIO9

GPIO10

GPIO11

GPIO12

GPIO13

DVOMODE

VID/DVO14

VID/DVO16

VID/DVO17

VID/DVO18

VID/DVO19

VID/DVO20

VID/DVO21

VID/DVO22

VID/DVO23

R43 10K

R39 499R

AUXWIN

402

402

TP11

TP12

3

GPIO[6..0] (10)

GPIO[13..8] (10)

+VDDR4

402

402

R35

1K

402

Both resistors and

capacitor close to ASIC

R34

1K

402

TMDS_TX0N (12)

TMDS_TX0P (12)

TMDS_TX1N (12)

TMDS_TX1P (12)

TMDS_TX2N (12)

TMDS_TX2P (12)

TMDS_TXCN (12)

TMDS_TXCP (12)

HPD (12)

A_R_D AC1 (11)

A_G_DAC1 (11)

A_B_DAC 1 (11)

A_HSYNC_DAC1 (1,11)

A_VSYNC_DAC1 (1,11)

TP7

CRT1DDCDATA (1,11)

CRT1DDCCLK (1,11)

BOUNDARY SCAN TEST ACCESS

A_HSYNC_DAC1

SCL

CRT1DDCDATA

CRT1DDCCLK

A_VSYNC_DAC1

TESTEN

DEBUG BUS ACCESS

VID/DVO16

VID/DVO17

VID/DVO18

VID/DVO19

VID/DVO20

VID/DVO21

VID/DVO22

VID/DVO23

GPIO10

GPIO11

GPIO12

GPIO13

ALT

JU2

Header_3_Pin_1X3/X

+3.3V_BUS

R65

4.7K

402

2

P1

PLUG

TRST/

TP1

TP2

TDO

TDI

TP3

TMS

TP4

TCK

TP5

TP8

TESTOUT(0)

TESTOUT(1)

TESTOUT(2)

TP17

TESTOUT(3)

TESTOUT(4)

TESTOUT(5)

TP19

TP20

TESTOUT(6)

TP21

TESTOUT(7)

TESTOUT(8)

TESTOUT(9)

TESTOUT(10)

TESTOUT(11)

+VDDR4

R584

10K

402

1

2

3

R585

10K/X

ALT

402

41

SW1A

DIP_SWX2/X

Title

Size Docum e n t N u mb er Re v

Custom

Date: Sheet

GIGABYTE

RV370 main

GV-RX30S128D-RH-HT

02 16Tuesday, De ce m ber 27, 2005

1

of

1.1

1

2

3

4

5

6

7

8

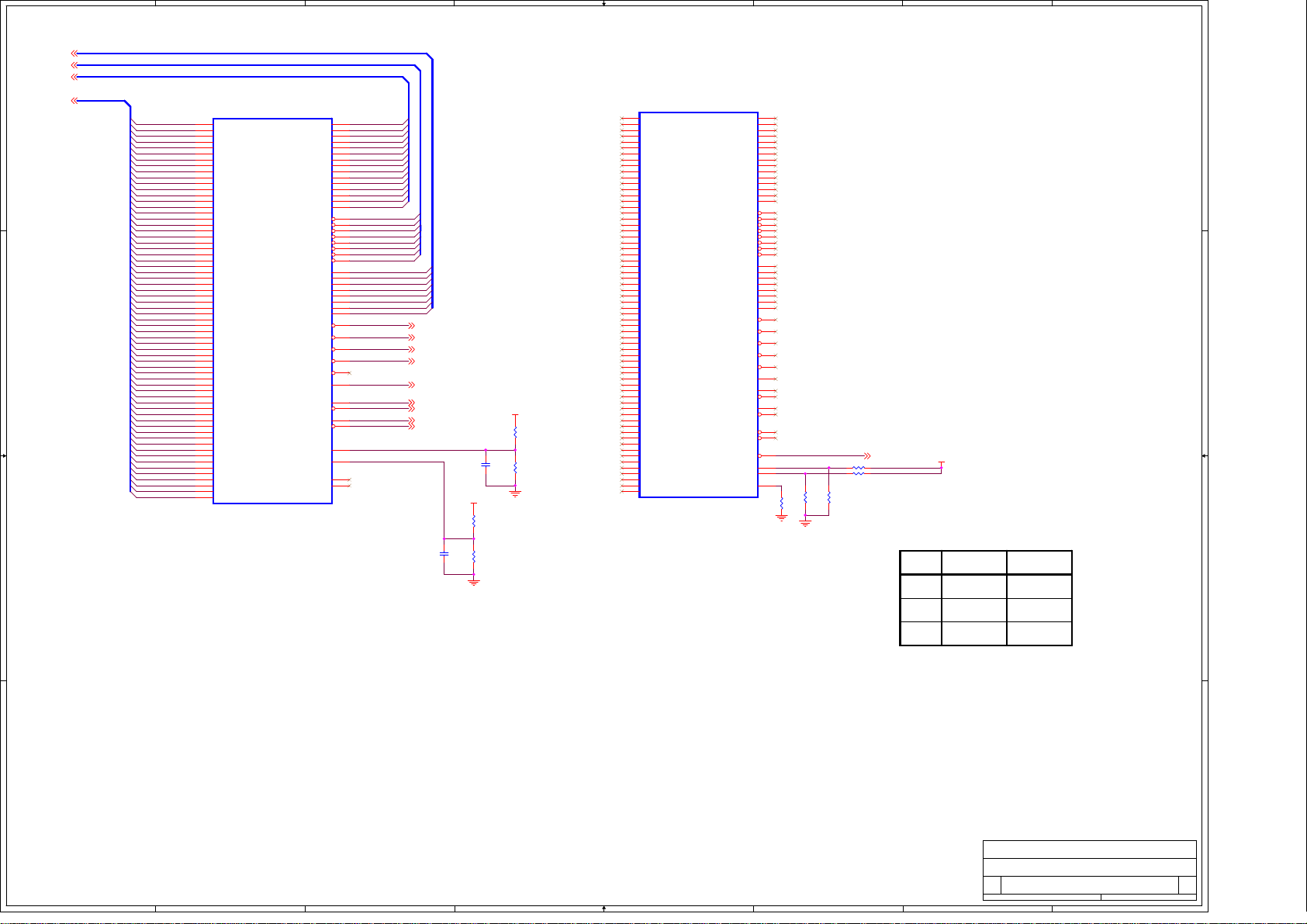

QSA[7..0](8)

DQMA#[7..0](8)

MAA[14..0](9)

MDA[63..0](8)

A A

B B

C C

QSA[7..0]

DQMA#[7..0]

MAA[14..0]

MDA[63..0]

MDA0

MDA1

MDA2

MDA3

MDA4

MDA5

MDA6

MDA7

MDA8

MDA9

MDA10

MDA11

MDA12

MDA13

MDA14

MDA15

MDA16

MDA17

MDA18

MDA19

MDA20

MDA21

MDA22

MDA23

MDA24

MDA25

MDA26

MDA27

MDA28

MDA29

MDA30

MDA31

MDA32

MDA33

MDA34

MDA35

MDA36

MDA37

MDA38

MDA39

MDA40

MDA41

MDA42

MDA43

MDA44

MDA45

MDA46

MDA47

MDA48

MDA49

MDA50

MDA51

MDA52

MDA53

MDA54

MDA55

MDA56

MDA57

MDA58

MDA59

MDA60

MDA61

MDA62

MDA63

U1B

H28

DQA_0

DQA_1

DQA_2

DQA_3

DQA_4

DQA_5

DQA_6

DQA_7

DQA_8

DQA_9

DQA_10

DQA_11

DQA_12

DQA_13

DQA_14

DQA_15

DQA_16

DQA_17

DQA_18

DQA_19

DQA_20

DQA_21

DQA_22

DQA_23

DQA_24

DQA_25

DQA_26

DQA_27

DQA_28

DQA_29

DQA_30

DQA_31

DQA_32

DQA_33

DQA_34

DQA_35

DQA_36

DQA_37

DQA_38

DQA_39

DQA_40

DQA_41

DQA_42

DQA_43

DQA_44

DQA_45

DQA_46

DQA_47

DQA_48

DQA_49

DQA_50

DQA_51

DQA_52

DQA_53

DQA_54

DQA_55

DQA_56

DQA_57

DQA_58

DQA_59

DQA_60

DQA_61

DQA_62

DQA_63

Part 2 of 6

MEMORY INTERFACE

A

H29

J28

J29

J26

H25

H26

G26

G30

D29

D28

E28

E29

G29

G28

F28

G25

F26

E26

F25

E24

F23

E23

D22

B29

C29

C25

C27

B28

B25

C26

B26

F17

E17

D16

F16

E15

F14

E14

F13

C17

B18

B17

B15

C13

B14

C14

C16

A13

A12

C12

B12

C10

C9

B9

B10

E13

E12

E10

F12

F11

E9

F9

F8

RV370SE

MEMORY CHANNEL A

MAA_0

MAA_1

MAA_2

MAA_3

MAA_4

MAA_5

MAA_6

MAA_7

MAA_8

MAA_9

MAA_10

MAA_11

MAA_12

MAA_13

MAA_14

DQMAb_0

DQMAb_1

DQMAb_2

DQMAb_3

DQMAb_4

DQMAb_5

DQMAb_6

DQMAb_7

QSA_0

QSA_1

QSA_2

QSA_3

QSA_4

QSA_5

QSA_6

QSA_7

RASAb

CASAb

WEAb

CSAb_0

CSAb_1

CKEA

CLKA0

CLKA0b

CLKA1

CLKA1b

MVREFD

MVREFS

DIMA_0

DIMA_1

U1C

D7

MAA0

E22

MAA1

B22

MAA2

B23

MAA3

B24

MAA4

C23

MAA5

C22

MAA6

F22

MAA7

F21

MAA8

C21

MAA9

A24

MAA10

C24

MAA11

A25

MAA12

E21

MAA13

B20

MAA14

C19

DQMA#0

J25

DQMA#1

F29

DQMA#2

E25

DQMA#3

A27

DQMA#4

F15

DQMA#5

C15

DQMA#6

C11

DQMA#7

E11

QSA0

J27

QSA1

F30

QSA2

F24

QSA3

B27

QSA4

E16

QSA5

B16

QSA6

B11

QSA7

F10

RASA#

A19

CASA#

E18

WEA#

E19

CSA#0

E20

F20

CKEA

B19

CLKA0

B21

CLKA#0

C20

CLKA1

C18

CLKA#1

A18

B7

B8

D30

B13

RASA# (9)

CASA# (9)

WEA# (9)

CSA#0 (9)

CKEA (9)

CLKA0 (8,9)

CLKA#0 (8,9)

CLKA1 (8,9)

CLKA#1 (8,9)

C153

100nF

402

+MVDDQ

R58

100R

402

C154

R59

100nF

100R

402

402

PLACE C351/152 VERY CLOSE TO ASIC

R56/57/58/59 CLOSE TO ASIC AS WELL

+MVDDQ

R56

100R

402

R57

100R

402

DQB_0

DQB_1

DQB_2

DQB_3

DQB_4

DQB_5

DQB_6

DQB_7

DQB_8

DQB_9

DQB_10

DQB_11

DQB_12

DQB_13

DQB_14

DQB_15

DQB_16

DQB_17

DQB_18

DQB_19

DQB_20

DQB_21

DQB_22

DQB_23

DQB_24

DQB_25

DQB_26

DQB_27

DQB_28

DQB_29

DQB_30

DQB_31

DQB_32

DQB_33

DQB_34

DQB_35

DQB_36

DQB_37

DQB_38

DQB_39

DQB_40

DQB_41

DQB_42

DQB_43

DQB_44

DQB_45

DQB_46

DQB_47

DQB_48

DQB_49

DQB_50

DQB_51

DQB_52

DQB_53

DQB_54

DQB_55

DQB_56

DQB_57

DQB_58

DQB_59

DQB_60

DQB_61

DQB_62

DQB_63

Part 3 of 6

MEMORY INTERFACE

B

F7

E7

G6

G5

F5

E5

C4

B5

C5

A4

B4

C2

D3

D1

D2

G4

H6

H5

J6

K5

K4

L6

L5

G2

F3

H2

E2

F2

J3

F1

H3

U6

U5

U3

V6

W5

W4

Y6

Y5

U2

V2

V1

V3

W3

Y2

Y3

AA2

AA6

AA5

AB6

AB5

AD6

AD5

AE5

AE4

AB2

AB3

AC2

AC3

AD3

AE1

AE2

AE3

RV370SE

MEMORY CHANNEL B

MAB_0

MAB_1

MAB_2

MAB_3

MAB_4

MAB_5

MAB_6

MAB_7

MAB_8

MAB_9

MAB_10

MAB_11

MAB_12

MAB_13

MAB_14

DQMBb_0

DQMBb_1

DQMBb_2

DQMBb_3

DQMBb_4

DQMBb_5

DQMBb_6

DQMBb_7

QSB_0

QSB_1

QSB_2

QSB_3

QSB_4

QSB_5

QSB_6

QSB_7

RASBb

CASBb

WEBb

CSBb_0

CSBb_1

CKEB

CLKB0

CLKB0b

CLKB1

CLKB1b

DIMB_0

DIMB_1

ROMCSb

MEMVMODE_0

MEMVMODE_1

MEMTEST

N5

M1

M3

L3

L2

M2

M5

P6

N3

K2

K3

J2

P5

P3

P2

E6

B2

J5

G3

W6

W2

AC6

AD2

F6

B3

K6

G1

V5

W1

AC5

AD1

R2

T5

T6

R5

R6

R3

N1

N2

T2

T3

E3

AA3

AF5

C6

C7

C8

R53

4.7K

R55

402 402

47R

402

LAYOUT NOTE: SOME OF THE RESISTORS R51-54 MAY BE

REMOVED IF SPACE IS AN ISSUE, ASK BEFORE REMOVING

R51 4.7K

R52 4.7K/X

R54

4.7K/X

DNI

ROMCS# (10)

402

402

DNI

+VDDC_CT

VDDR1 MEMVMODE_0 MEMVMODE_1

1.8V

2.5V

2.8V

GND

+VDDC_CT

+VDDC_CT GND

+VDDC_CT +VDDC_CT

D D

Title

Size Document Number Rev

Custom

1

2

3

4

5

6

Date: Sheet

7

GIGABYTE

RV370 memory interface

GV-RX30S128D-RH-HT

of

03 16Tuesday, December 27, 2005

8

1.1

5

+MVDDQ

D D

+MVDDQ

C38

10uf

+MVDDQ

C32

100nF

100nF

402 402 402

C C

+1.8V

B11

200R/200mA

ALT: 0R

+1.8V

B14

0R/8

ALT: 0R

B B

A A

+1.8V

B13

0R/8

ALT: 0R

C31

100nF

100nF

402 402402

+TPVDD

C50

10uf

OPT

GND_TPVSS

+TXVDDR_PINS

C59

4.7uF

GND_TXVSSR

+A2VDDQ

C63

4.7uF

GND_A2VSSQ

AVDD/A2VDDQ (1st & 2nd

DAC Band Gap) - 200mA

+AVDD

C67

4.7uF

GND_AVSSN

C35

C33

C75

C74

100nF

100nF

C43

C58

2.2uF

2.2uF

ALT:

ALT:

100nF

100nF

C60

C81

100nF

100nF

402

402

C64

100nF

402

C68

100nF

402

5

C73

100nF

402

C94

100nF

+1.8V

B12

0R/8

ALT: 0R

C95

100nF

402402 402402

C96

100nF

GND_A2VSSN

+VDDOI_PINS

C66

4.7uF

+PVDD

GND_PVSS

+MPVDD

GND_MPVSS

C97

100nF

+A2VDD

C65

100nF

402

C54

4.7uF

C52

4.7uF

C62

100nF

402

C53

100nF

402

C51

100nF

402

+MVDDQ

AE15

AE16

AE17

AF15

AH19

AH13

AF13

AF14

AE20

AF21

AF23

AH23

AE23

AE22

AK28

K23

K24

L23

H10

H13

H15

H17

AA1

AA4

AA7

AA8

A15

A21

A28

B30

D26

D23

D20

D17

D14

D11

E27

G10

G13

G15

G19

G22

G27

H22

H19

AD4

F18

T7

R4

R1

N8

N7

M4

L8

J8

J7

J4

J1

T8

V4

V7

V8

A3

A9

B1

D8

D5

F4

G7

N4

N6

A7

4

U1D

VDDR1#T7

VDDR1#R4

VDDR1#R1

VDDR1#N8

VDDR1#N7

VDDR1#M4

VDDR1#L8

VDDR1#K23

VDDR1#K24

VDDR1#L23

VDDR1#J8

VDDR1#J7

VDDR1#J4

VDDR1#J1

VDDR1#H10

VDDR1#H13

VDDR1#H15

VDDR1#H17

VDDR1#T8

VDDR1#V4

VDDR1#V7

VDDR1#V8

VDDR1#AA1

VDDR1#AA4

VDDR1#AA7

VDDR1#AA8

VDDR1#A3

VDDR1#A9

VDDR1#A15

VDDR1#A21

VDDR1#A28

VDDR1#B1

VDDR1#B30

VDDR1#D26

VDDR1#D23

VDDR1#D20

VDDR1#D17

VDDR1#D14

VDDR1#D11

VDDR1#D8

VDDR1#D5

VDDR1#E27

VDDR1#F4

VDDR1#G7

VDDR1#G10

VDDR1#G13

VDDR1#G15

VDDR1#G19

VDDR1#G22

VDDR1#G27

VDDR1#H22

VDDR1#H19

VDDR1#AD4

VDDR1#N4

NC#AE15

NC#AE16

NC#AE17

NC#AF15

NC#AH19

TPVDD

TXVDDR#AF13

TXVDDR#AF14

VDDRH0

VDDRH1

A2VDD#AE20

A2VDD#AF21

A2VDDQ

AVDD

VDD1DI

VDD2DI

PVDD

MPVDD

RV370SE

4

Part 4 of 6

PCIE_VDDR_12#AG26

PCIE_VDDR_12#AG27

PCIE_VDDR_12#AG28

PCIE_VDDR_12#AJ30

PCIE_VDDR_12#AK29

PCIE_PVDD_12#N23

PCIE_PVDD_12#N24

PCIE_PVDD_12#P23

PCIE_PVDD_18#T23

PCIE_PVDD_18#U23

PCIE_PVDD_18#V23

PCIE_PVDD_18#W23

I/O POWER

VDDC#AC13

VDDC#AC15

VDDC#AC17

VDDC#AD13

VDDC#AD15

VDD15#H11

VDD15#H20

VDD15#M23

VDD15#P8

VDD15#Y23

VDD15#Y8

VDD15#AC11

VDD15#AC20

VDDR3#AC8

VDDR3#AC19

VDDR3#AC21

VDDR3#AC22

VDDR3#AD7

VDDR3#AD19

VDDR3#AD21

VDDR4#AC9

VDDR4#AC10

VDDR4#AD9

VDDR4#AD10

VDDR4#AG7

NC#D9

NC#D13

NC#D19

NC#D25

NC#E4

NC#T4

NC#AB4

NC#AF18

NC#AG15

NC#AG18

NC#AH17

NC#AH18

TPVSS

TXVSSR#AH14

TXVSSR#AG13

TXVSSR#AG14

VSSRH0

VSSRH1

A2VSSN#AH20

A2VSSN#AG21

A2VSSQ

AVSSN

AVSSQ

VSS1DI

VSS2DI

PVSS

MPVSS

AC13

AC15

AC17

AD13

AD15

H11

H20

M23

P8

Y23

Y8

AC11

AC20

AC8

AC19

AC21

AC22

AD7

AD19

AD21

AC9

AC10

AD9

AD10

AG7

D9

D13

D19

D25

E4

T4

AB4

AG26

AG27

AG28

AJ30

AK29

N23

N24

P23

T23

U23

V23

W23

AF18

AG15

AG18

AH17

AH18

AH12

AH14

AG13

AG14

F19

M6

AH20

AG21

AF22

AH22

AD22

AE24

AE21

AJ28

A6

+VDDC

+VDDC_CT

+3.3V_BUS

GND_TPVSS

GND_TXVSSR

GND_A2VSSN

GND_A2VSSQ

GND_AVSSN

GND_PVSS

GND_MPVSS

+VDDC

+VDDR4

C69

C70

100nF

4.7uF

402

+PCIE_VDDR

+PCIE_PVDD_12

+PCIE_PVDD_18

GND_AVSSQ

C20

100nF

3

C21

C22

100nF

100nF

402 402402

+3.3V_BUS

B15

0R/8

ALT: 0R

C99

C98

1.0uF

1.0uF

TP9

3

C82

C23

100nF

100nF

402 402 402 402 402 402 402 402402 402 402 402 402

C37

1.0uF

C968

C969

1.0uF

1.0uF

C970

C971

1.0uF

1.0uF

C83

100nF

C44

100nF

+3.3V_BUS

+MVDDQ

C84

100nF

+3.3V_BUS

C39

100nF

402 402

C41

100nF

402 402

C55

100nF

402 402

C983

100nF/X

C984

100nF/X

C985

100nF/X

C46

100nF

C979

100nF/X

C980

100nF/X

C981

100nF/X

C982

100nF/X

C85

100nF

+VDDC_CT

C40

100nF

C42

100nF

C56

100nF

+VDDC

+Vout_Switcher

+MVDDQ

+12V_BUS_F1

+VDDC

+MVDDC

C86

100nF

C45

100nF

402 402 402 402402 402

C76

100nF

402 402

C78

100nF

402 402

C57

100nF

402 402

CAPS C979..C985 are

accross Plane Splits

They are no t r e q uired

They should be populated

only if EMI issues are

found.

C87

100nF

C47

100nF

+VDDC

+VDDC

C77

100nF

C79

100nF

C61

100nF

C26

100nF

C88

100nF

C48

100nF

2

C24

10uf

C28

100nF

C90

100nF

C29

100nF

C91

100nF

C27

100nF

402 402 402 402402

C89

100nF

C49

100nF

2

C30

100nF

C92

100nF

+VDDC

U1F

P17

VDDC#P17

P18

VDDC#P18

P19

VDDC#P19

U12

VDDC#U12

U13

VDDC#U13

U14

VDDC#U14

U17

VDDC#U17

U18

VDDC#U18

U19

VDDC#U19

V19

VDDC#V19

V18

VDDC#V18

V17

VDDC#V17

V14

VDDC#V14

V13

VDDC#V13

V12

VDDC#V12

N18

C93

100nF

VDDC#N18

N17

VDDC#N17

N14

VDDC#N14

W17

VDDC#W17

W18

VDDC#W18

W12

VDDC#W12

W13

VDDC#W13

W14

VDDC#W14

N13

VDDC#N13

N19

VDDC#N19

M19

VDDC#M19

M18

VDDC#M18

M12

VDDC#M12

N12

VDDC#N12

M13

VDDC#M13

M14

VDDC#M14

P12

VDDC#P12

P13

VDDC#P13

RV370SE

U1E

A2

VSS#A2

A10

VSS#A10

A16

VSS#A16

A22

VSS#A22

A29

VSS#A29

C1

VSS#C1

C3

VSS#C3

C28

VSS#C28

C30

VSS#C30

D27

VSS#D27

D24

VSS#D24

D21

VSS#D21

D18

VSS#D18

D15

VSS#D15

D12

VSS#D12

D6

VSS#D6

D4

VSS#D4

D10

VSS#D10

F27

VSS#F27

G9

VSS#G9

G12

VSS#G12

G16

VSS#G16

G18

VSS#G18

G21

VSS#G21

G24

VSS#G24

H27

VSS#H27

H23

VSS#H23

H21

VSS#H21

H18

VSS#H18

H16

VSS#H16

H14

VSS#H14

H12

VSS#H12

H9

VSS#H9

H8

VSS#H8

H4

VSS#H4

J23

VSS#J23

J24

VSS#J24

AD12

VSS#AD12

AG5

VSS#AG5

AG9

VSS#AG9

AG11

VSS#AG11

R7

VSS#R7

P4

VSS#P4

M7

VSS#M7

M8

VSS#M8

L4

VSS#L4

K1

VSS#K1

K7

VSS#K7

K8

VSS#K8

R8

VSS#R8

T1

VSS#T1

W8

VSS#W8

W7

VSS#W7

U8

VSS#U8

U4

VSS#U4

Y4

VSS#Y4

RV370SE

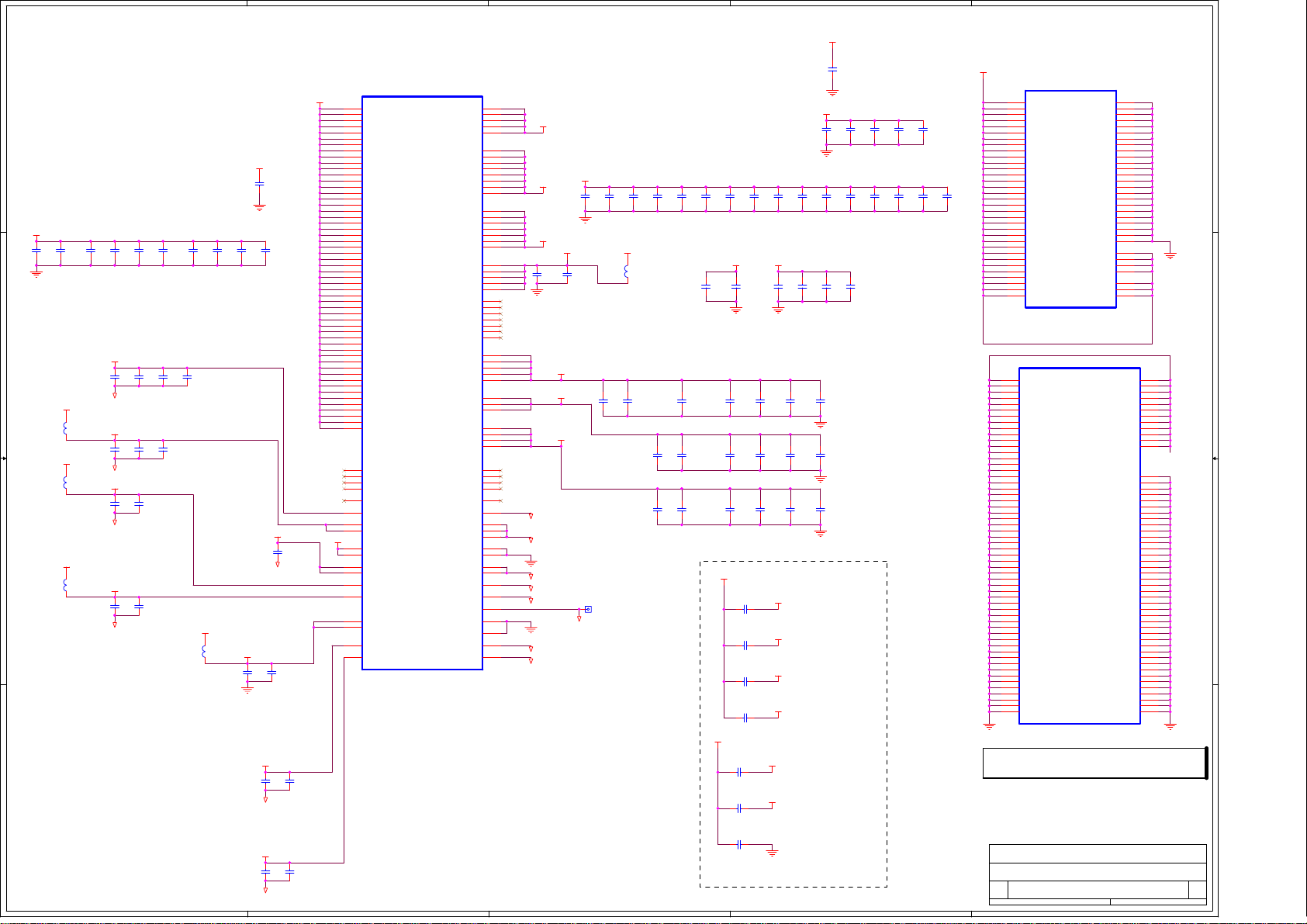

ADD ASIC DECOUPLING FOR ALL POWER AS REQUIRED

PLACED CLOSE TO THE POWER/GND PINS

WITH AS MANY AS POSSIBLE PLACED UNDER THE ASIC

Title

Size Docum e n t N u mb er Re v

C

Date: Sheet

1

Part 6 of 6

Part 5 of 6

CORE GND

VSS#M16

VSS#N16

VSS#N15

VSS#P15

VSS#P16

VSS#R18

VSS#R17

VSS#R16

VSS#R15

VSS#R14

VSS#R13

VSS#R12

VSS#T13

VSS#T14

VSS#T15

VSS#W15

VSS#V16

VSS#V15

VSS#U15

VSS#U16

VSS#T19

VSS#T18

VSS#T17

VSS#T16

CENTER ARRAY

VDDCI#W16

VDDCI#M15

VDDCI#R19

VDDCI#T12

VDDC#W19

VDDC#M17

VDDC#P14

M16

N16

N15

P15

P16

R18

R17

R16

R15

R14

R13

R12

T13

T14

T15

W15

V16

V15

U15

U16

T19

T18

T17

T16

W16

M15

R19

T12

W19

M17

P14

VSS#AB8

VSS#AB7

VSS#AB1

VSS#AC4

VSS#AC12

VSS#AC14

VSS#AD16

VSS#AC16

VSS#AC18

VSS#AD18

VSS#AK2

VSS#AJ1

PCIE_VSS#K28

PCIE_VSS#L28

PCIE_VSS#M24

PCIE_VSS#M25

PCIE_VSS#M26

PCIE_VSS#M27

PCIE_VSS#M28

PCIE_VSS#N28

PCIE_VSS#P28

PCIE_VSS#R23

PCIE_VSS#R24

PCIE_VSS#R25

PCIE_VSS#R26

PCIE_VSS#R27

PCIE_VSS#R28

PCIE_VSS#T24

PCIE_VSS#T28

PCIE_VSS#U28

PCIE_VSS#V24

PCIE_VSS#V25

PCIE_VSS#V26

PCIE_VSS#V27

PCIE_VSS#V28

PCIE_VSS#W24

PCIE_VSS#W28

PCIE_VSS#Y28

PCIE_VSS#AA23

PCIE_VSS#AA24

PCIE_VSS#AA25

PCIE_VSS#AA26

PCIE_VSS#AA27

PCIE_VSS#AA28

PCIE_VSS#AB28

PCIE_VSS#AC28

PCIE_VSS#AD26

PCIE_VSS#AD27

PCIE_VSS#AD28

PCIE_VSS#AE28

PCIE_VSS#AF28

PCIE_VSS#AH29

GIGABYTE

RV370 power

GV-RX30S128D-RH-HT

1

AB8

AB7

AB1

AC4

AC12

AC14

AD16

AC16

AC18

AD18

AK2

AJ1

K28

L28

M24

M25

M26

M27

M28

N28

P28

R23

R24

R25

R26

R27

R28

T24

T28

U28

V24

V25

V26

V27

V28

W24

W28

Y28

AA23

AA24

AA25

AA26

AA27

AA28

AB28

AC28

AD26

AD27

AD28

AE28

AF28

AH29

04 16Tuesday, De ce m ber 27, 2005

1.1

of

8

7

6

5

4

3

2

***

Indicate num be r of power via required for the connection

1

Regulator for VDDC (ASIC Core)

Vout = 1.2V ~ 1.3V

81

72

63

54

+12V_BUS

+Vout_Switcher

C323

22uF_16V

******

OPT OPT

**

C324

22uF_16V

ALT. 1: MAXIM REGULATOR

D D

+5V +12V_BUS

R315

R316

0R/X

0R

C151

1.0uF/X

+VDDC_S

21

R314

D1

BAT254

+VDDC_B

C147

100nF

603

X7R

5%

C C

510K/X

C148

C149

470pF/X

27pF/X

402

ALT. 2: INTERSIL REGULATOR

+VDDC_S

C104

22nf

C312

10nF

402

R358 51K

R359 3K

C111

33pF

R368

15K_1%

402

U41

1

2

3

9

10

1

2

3

4

5

6

7

HSD

ILIM

COMP

FB

LX

BST

PGND

MAX1954EUB/X

R357 10K

MU31

RT

OCSET

SS

COMP

FB

EN

GND

ISL6522CB

GND

DH

DL

IN

PVCC

LGATE

PGND

BOOT

UGATE

PHASE

8

6

5

4

7

+3.3V_BUS

VCC

14

13

12

11

10

9

8

ISL6522CB : SOIC

+PW_VDDC_HGD

+PW_VDDC_LGD

+12V_BUS_F1

C143

0.22uF

+VDDC_B

R351 0R

402

must be low imp e dance

must be low imp e dance

VDDC_FB

+12V_BUS

R99

2.2R

C115

100nF

603

X7R

5%

Alt. 1: Separate MOSFETs

Q24

4 5

3

2

1

+PW_VDDC_M

4 5

3

2

1

IRF7413A

Q22

IRF7413A

6

7

8

6

7

8

L21 2. 2uH

R15

1R/X

C152

2.2nF/X

C150

10uF

+VDDC_S

***

***

C325

10nF/X

Cc1

R254

1.5K/X

Rc1

C301

470UF

0.019R @ 100kHz

3.5mm LS

High current path

R1

R353

1.00K

1%

0.8V Ref

R2

R356

2K

1%

B17

60R/6A

***

***

***

C321

470uF_10V

***

+Vout_Switcher +VDDC +VDDC

RP1A 0R

RP1B 0R

RP1C 0R

RP1D 0R

Part NOTES

MAX1954

ISL6522

Do not install Cc1, Rc1

Install Cc1, Rc1

Part Vo ut R1 R2

MAX1954

ISL6522

0.8V Ref

***

C322

470uF_10V

***

1.2V

1.3V

1.00K 1%

ATI P/N 3240100100 ATI P/N 3240200100

1.00K 1%

ATI P/N 3240100100

2.00K 1%

1.6K 1%

ATI P/N 3240162100

+Vout_Switcher

L6 0R/8

+Vout_Switcher

L7 0R/8

B B

ALT: 0R

ALT: 0R

+PCIE_VDDR

+PCIE_PVDD_12

Circuit to hold PCI-E voltage low and w ait for +VDDC for proper power sequence

+3.3V_BUS

R153

100K/X

402

1

R396

2 3

100R/X

CMPT3904/X

Rq3

Rq4

+VDDC

R393

1.50K/X

R394

3.01K/X

+VDDC

+1.3V

A A

+1.2V 1.5K 3K

8

Rq3

1.5K

Rq4

2.4K

7

6

CMPT3904/X

Q28

1

+12V_BUS

2 3

R395

20K/X

402

402

1

R397

100R/X

402

2 3

Q29

CMPT3904/X

Q27

5

VDDC_G OOD_PU (7)

VDDC_G OOD (7)

Title

Size Document Number Rev

Custom

4

3

Date: Sheet

2

GIGABYTE

REG (VDDC)

GV-RX30S128D-RH-HT

of

05 16Tuesday, December 27, 2005

1

1.1

Loading...

Loading...