5

4

3

2

1

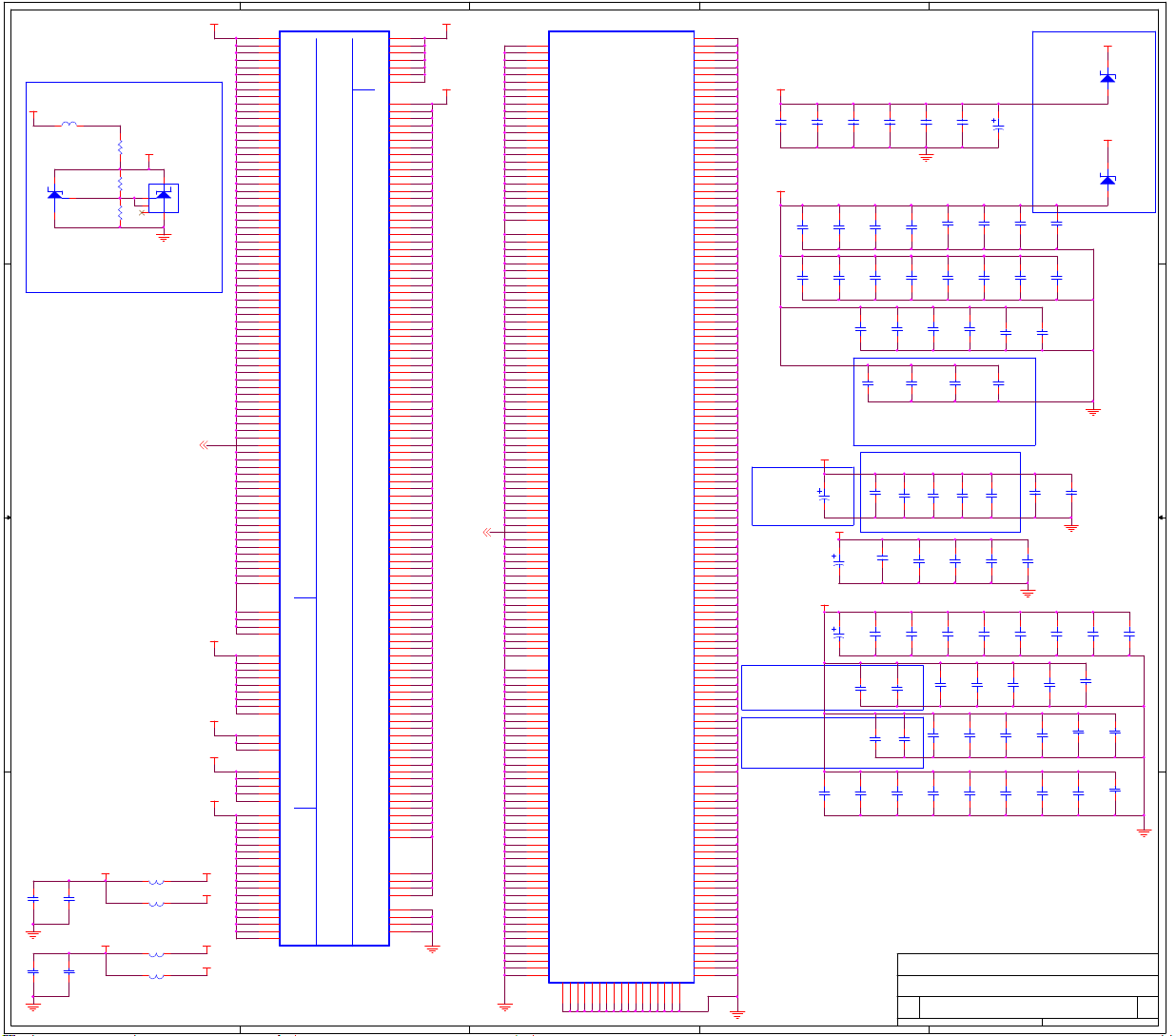

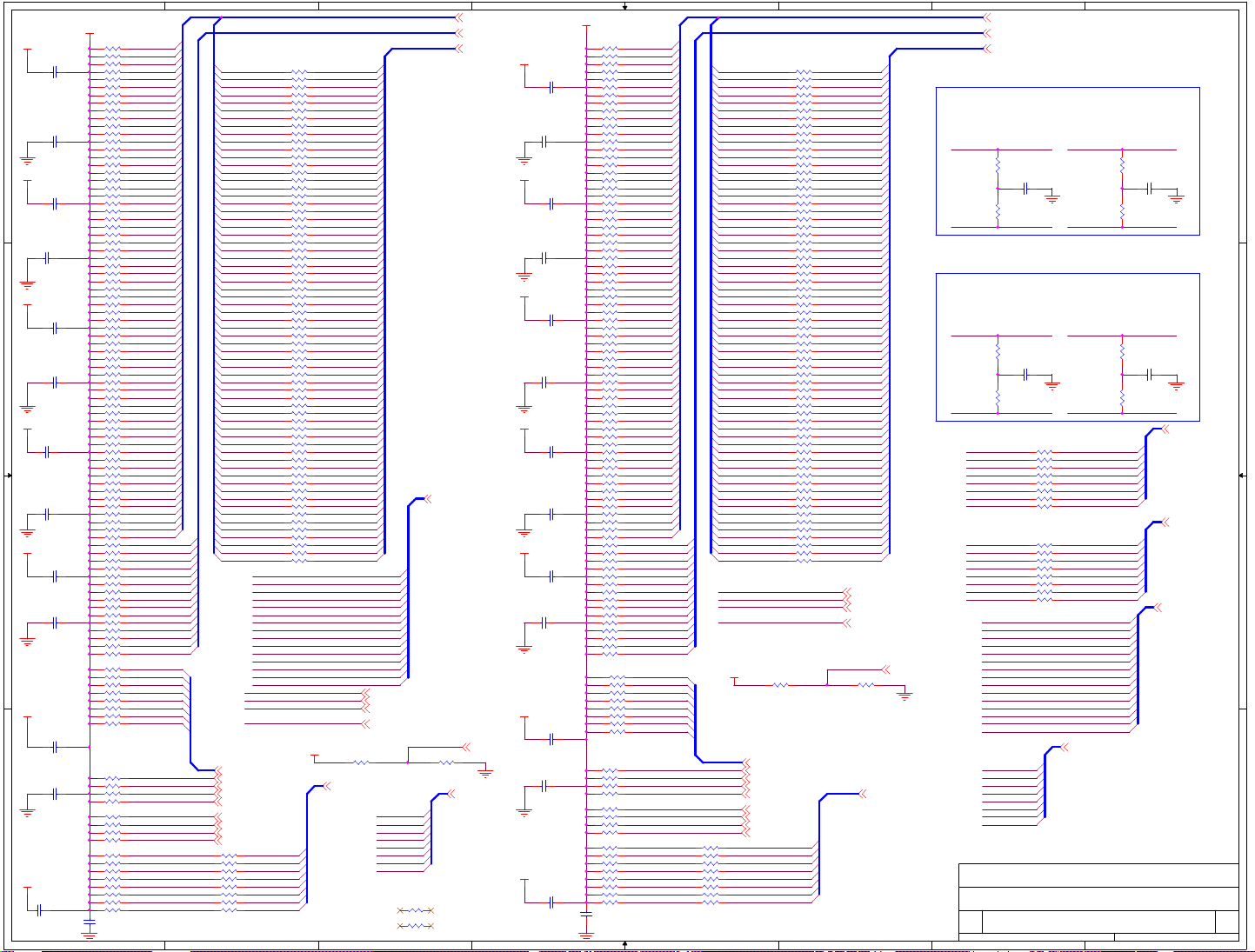

MEMORY CHANNEL A B

D D

DDR 4M X 32 (BGA)

MEMORY TERMINATIONS A B

SHT 13

SHT 11

MEMORY CHANNEL C D

DDR 4M X 32 (BGA)

MEMORY TERMINATIONS C D

SHT 14

SHT 12

VGA1

PRIMARY CRT

LOGIC

SHEET 19

INTEG TMDS

LOGIC

HDH

SHT 23

TVout

CONN

RASA/B#

WEA/B#

ROMCS#

QSA/B[7..0]

CS0A/B#MDA/B[63..0]

DQMA/B[0..7]

CLKA/B01CKEA/B

CLKA/B01#

MEM A B

MEM C D

DAC1

TMDS

MDC/D[63..0] QSC/D[7..0] CS0C/D#

MC/D[14..0]

CASC/D#

WEA/B#RASC/D#

CKEC/D CLKC/D01

R G B HSY VSY DDC1DATA DDC1CLK

TMDS_TX[C,2..0]N TMDS_TX[C,2..0]P HPD, DDC2CLK DDC2DATA

DQMC/D[0..7]

CLKC/D01#

ROM

R300

SHEET 3, 4, 5, 09, 10

AGP

TVO

DVO

VIP

DAC2

DVO, VIP Host, VIP Data

Y/R C/G COMP/B H2SYNC

GPIO

CRT2DDCDATA CRT2DDCCLK V2SYNC

D

E

M

U

SEL

X

SHT 22

TVOUT

LOGIC

SHT 22

SECONDARY

CRT LOGIC

SHT 19

MA/B[14..0]

CASA/B#

C C

STRAPS

SHT 15

BIOS

SHT 17

External

power

B B

POWER

REGULATION

SHT 6,7,8

FAN

SHT 16

VDDC VDDC18 VDD VTT VDDQ

PVDD TPVDD MPVDD

A2VDD Vref

DB15

CONN

SHT 19

DVI-I1

CONN

SHT 18

CBE3..0

GNT#

CLK

SBA[7..0]

AD_STB1#

CPUCLK

TRDY#

INTR

ST2..0

SUSPEND#

AD_STB0

DEVSEL#

SB_STB

AD_STB0#

RESET#

SERR#

SB_STB#

RBF#

Title

Size Document Number Rev

B

3

2

Date: Sheet of

GIGABYTE

R300 128M DVII VGA2 VO

GV-R9700

1 27Tuesday, March 11, 2003

1

1.1

AD31..0

IRDY#

FRAME#

AGPREF

+5V

+3.3V

A A

5

+12V

AD_STB1

AGP BUS

2X/4X/8X

SHT 2

4

REQ#

PAR

STOP#

8

7

6

5

4

3

2

1

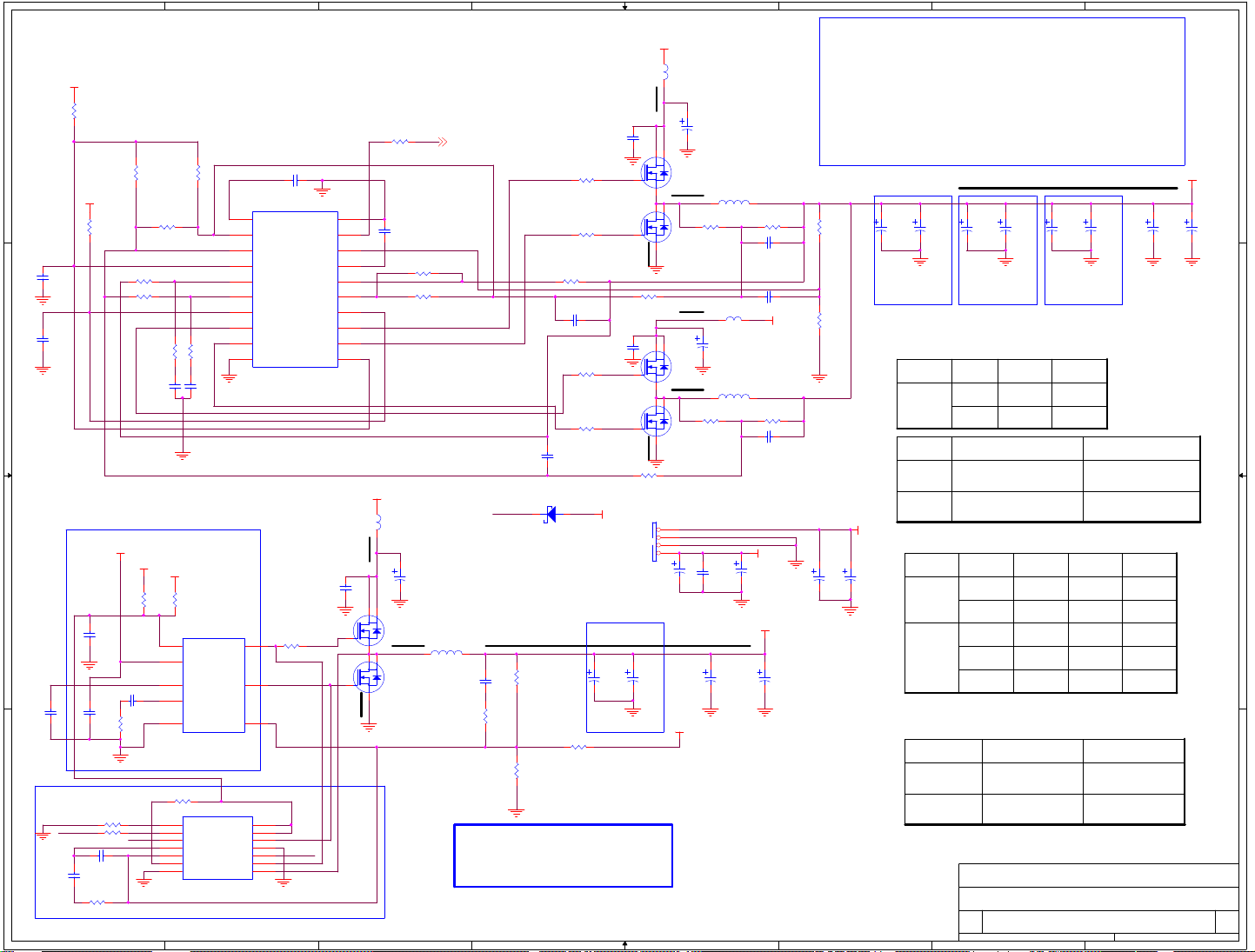

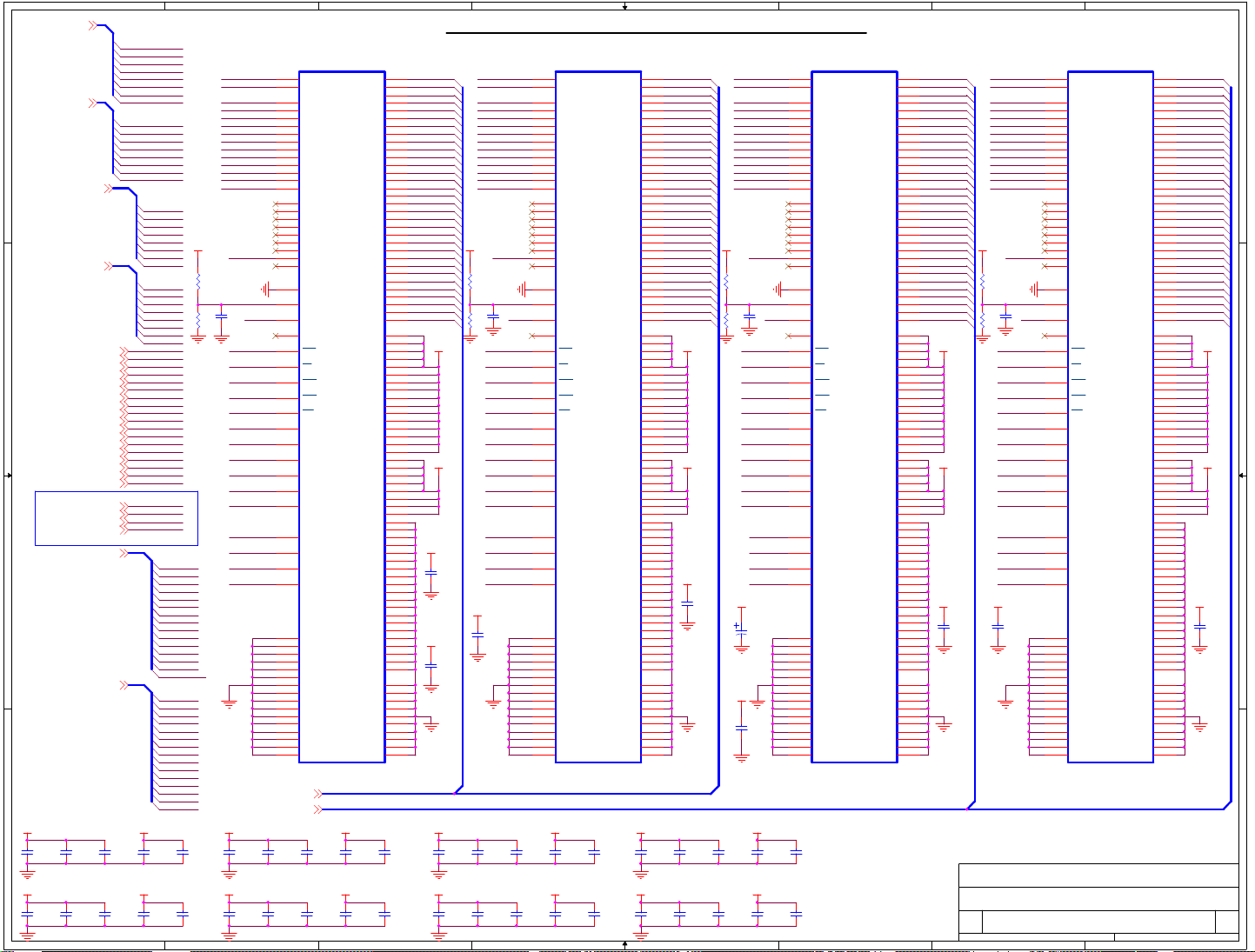

2X/4X/8X AGP BUS

GND_TPVSSGND_MPVSS

GND_PVSS GND_TXVSSR

NOTE: THIS IS A DRAWING. THESE

GROUNDS MUST BE MANUALLY

D D

CONNECTED TO THE GROUND PLANE

AGP_MB_8X_DET#(3)

C C

B B

A A

8

GND_A2VSSN

AGP_GNT#(3)

AGP_DBI_HI(3)

AGP_WBF#(3)

AGP_SBSTB#(3)

AGP_ADSTB1#(3)

AGP_FRAME#(3)

AGP_TRDY#_R(24)

AGP_TRDY#(3,24)

AGP_STOP#(3,24)

AGP_STOP#_R(24)

AGP_PAR(3)

AGP_ADSTB0#(3) AGP_ADSTB0 (3)

AGP_VREFGC(3,24)

AGP_RESET#(3,9,10,23,24)

GND_A2VSSQ

+VDDQ_BUS

+VDDQ_BUS

+VDDQ_BUS

DNI

R854

180R

GND_AVSSQ GND_RSET

GND_R2SETGND_AVSSN

AGP_INTR#(3)

AGP_GC_8X_DET#

R2 0R

AGP_RST#

R4 0R

R5 0R

R7 8K2

R9 8K2

DNI

R13 0R

DNI

R15 0R

R16 8K2

AGP_VREFGC

R22 100R

74ACT08MTC

R25

180R

7

GND_TVVSSN

U2A

3

+5V_BUS

147

+12V_BUS

+3.3V_BUS +3.3V_BUS

A1

TYDET

A2

A3

A4

GND_TY

A5

A6

A7

A8

AGP_ST1

AGP_DBI_HI_R

AGP_SBA1 AGP_SBA0

AGP_SBA3

AGP_SBSTB#_R

AGP_SBA5

AGP_SBA7

AGP_AD30

AGP_AD28

AGP_AD26

AGP_AD24

AGP_ADSTB1#_R

AGP_C/BE#3

AGP_AD22

AGP_AD20

AGP_AD18

AGP_AD16

AGP_TRDY#_R

AGP_STOP#_R

AGP_PAR_R

AGP_AD15

AGP_AD13

AGP_AD11

AGP_AD9

AGP_C/BE#0

AGP_ADSTB0#_R

AGP_AD6

AGP_AD4

AGP_AD2

C5

R19

100nF

10K

1

2

AGP_RST#

DNI

C731

100nF

6

A9

A10

A11

A12

A13

A14

A15

A16

A17

A18

A19

A20

A21

A22

A23

A24

A25

A26

A27

A28

A29

A30

A31

A32

A33

A34

A35

A36

A37

A38

A39

A40

A41

A42

A43

A44

A45

A46

A47

A48

A49

A50

A51

A52

A53

A54

A55

A56

A57

A58

A59

A60

A61

A62

A63

A64

A65

A66

PWGOOD_VDDC (6)

5

R1 0R

MAGP1

12V

TYPEDET#

GC_DET#/RESEVED

USBGND

INTA#

RST#

GNT#

VCC3.3

ST1

MB_DET#/RESERVED

DBI_HI/PIPE#

GND

WBF#

SBA1

VCC3.3

SBA3

SB_STB#

GND

SBA5

SBA7

KEY

KEY

KEY

KEY

AD30

AD28

VCC3.3

AD26

AD24

GND

AD_STB1#

C/BE3#

VDDQ

AD22

AD20

GND

AD18

AD16

VDDQ

FRAME#

KEY

KEY

KEY

KEY

TRDY#

STOP#

PME#

GND

PAR

AD15

VDDQ

AD13

AD11

GND

AD9

C/BE0#

VDDQ

AD_STB0#

AD6

GND

AD4

AD2

VDDQ

AD0

VREFGC

UNIVERSAL AGP BUS

GND_TYTYDET

OVRCNT#

5.0V

5.0V

USB+

GND

INTB#

CLK

REQ#

VCC3.3

ST0

ST2

RBF#

GND

DBI_LO/RESERVED

SBA0

VCC3.3

SBA2

SB_STB

GND

SBA4

SBA6

KEY

KEY

KEY

KEY

AD31

AD29

VCC3.3

AD27

AD25

GND

AD_STB1

AD23

VDDQ

AD21

AD19

GND

AD17

C/BE2#

VDDQ

IRDY#

KEY

KEY

KEY

KEY

DEVSEL#

VDDQ

PERR#

GND

SERR#

C/BE1#

VDDQ

AD14

AD12

GND

AD10

AD8

VDDQ

AD_STB0

AD7

GND

AD5

AD3

VDDQ

AD1

VREFCG

SYMBOL LEGEND

DNI

4

AGP_C/BE#[3..0]

AGP_AD[31..0]

AGP_SBA[7..0]

AGP_ST[2..0]

+5V_BUS+VDDQ_BUS

+VDDQ_BUS

B1

B2

B3

B4

B5

B6

B7

B8

B9

B10

B11

B12

B13

B14

B15

B16

B17

B18

B19

B20

B21

B22

B23

B24

B25

B26

B27

B28

B29

B30

B31

B32

B33

B34

B35

B36

B37

B38

B39

B40

B41

B42

B43

B44

B45

B46

B47

B48

B49

B50

B51

B52

B53

B54

B55

B56

B57

B58

B59

B60

B61

B62

B63

B64

B65

B66

#

DO NOT

INSTALL

ACTIVE

LOW

DIGITAL

GROUND

ANALOG

GROUND

AGP_ST0

AGP_ST2

AGP_DBI_LO_R

AGP_SBA2

AGP_SBA4

AGP_SBA6

AGP_AD31

AGP_AD29

AGP_AD27

AGP_AD25

AGP_AD23

AGP_AD21

AGP_AD19

AGP_AD17

AGP_C/BE#2

AGP_C/BE#1

AGP_AD14

AGP_AD12

AGP_AD10

AGP_AD8

AGP_AD7

AGP_AD5

AGP_AD3

AGP_AD1AGP_AD0

AGP_AGPCLK_R

R6 0R

AGP_SBSTB_R

AGP_ADSTB1_R

AGP_DEVSEL#_R

AGP_ADSTB0_R

3

+12V_BUS

AGP_C/BE#[3..0] (3)

AGP_AD[31..0] (3)

AGP_SBA[7..0] (3)

AGP_ST[2..0] (3)

R3 0R

AGP_REQ# (3)

AGP_RBF# (3)

AGP_DBI_LO (3)

R8 0R

R10 0R

R17 0R

C1127

1.0uF

Title

Size Document Number Rev

B

Date: Sheet of

+5V_BUS

C1

100uF 16V

ALU

C2

100uF 16V

AGP_SBSTB (3)

AGP_ADSTB1 (3)

AGP_IRDY# (3)

AGP_DEVSEL#_R (3,24)

AGP_AGPREF (3)

GIGABYTE

R300 128M DVII VGA2 VO

GV-R9700

2

+3.3V_BUS

AGP_AGPCLK (3,24)

C4

10pF

DNI

C3

100uF 16V

2 27Tuesday, March 11, 2003

1

1.1

8

7

6

5

4

3

2

1

D D

PLACE

CLOSE TO

THE ASIC

1

PIN

C14

100nF

DNI

R895 0R

32

Q19

NDS335N

AGP_C/BE#[3..0](2)

AGP_ST[2..0](2)

AGP_SBA[7..0](2)

AGPREFCG

AGP_C/BE#[3..0]

AGP_ST[2..0]

AGP_SBA[7..0]

AGP_SBSTB(2)

AGP_SBSTB#(2)

AGP_ADSTB0(2)

AGP_ADSTB0#(2)

AGP_ADSTB1(2)

AGP_ADSTB1#(2)

TEST

AGPREFCG

C C

AGP_AGPREF(2)

AGP_RESET#(2,9,10,23,24)

B B

AGP_DEVSEL#_R(2,24)

2N7002E

AGP_AGPCLK(2,24)

AGP_GNT#(2)

AGP_REQ#(2)

AGP_RBF#(2)

AGP_INTR#(2)

AGP_RESET#(2,9,10,23,24)

AGP_WBF#(2)

AGP_FRAME#(2)

AGP_TRDY#(2,24)

AGP_IRDY#(2)

AGP_STOP#(2,24)

AGP_PAR(2)

AGP_SBA0

AGP_SBA1

AGP_SBA2

AGP_SBA3

AGP_SBA4

AGP_SBA5

AGP_SBA6

AGP_SBA7

+VDDQ_BUS

1

Q2

AGP_C/BE#0

AGP_C/BE#1

AGP_C/BE#2

AGP_C/BE#3

AGP_ST0

AGP_ST1

AGP_ST2

AGP_SBSTB

AGP_SBSTB#

AGP_ADSTB0

AGP_ADSTB0#

AGP_ADSTB1

AGP_ADSTB1#

32

R39 169R

R40 71.5R

AV39

AP38

AU39

AM39

AU37

AP35

AM36

AG35

AE35

AH35

AD35

AB35

AA35

AG34

AL36

AF36

AL37

AA39

AD38

AP39

AN39

AN38

AT37

AT38

AT39

AR39

AP36

AP37

AN36

AN37

AR38

AR37

AE37

AD36

AF39

AE38

U42A

PCICLK

GNT#

REQ#

RBF#

INTA#

RST#

WBF#

FRAME#

TRDY#

IRDY#

DEVSEL#

STOP#

PAR

AGPREF

AGPTEST

CBE#0

CBE#1

CBE#2

CBE#3

ST0

ST1

ST2

SBA0

SBA1

SBA2

SBA3

SBA4

SBA5

SBA6

SBA7

SB_STBF

SB_STBS

AD_STBF0

AD_STBS0

AD_STBF1

AD_STBS1

R300

PART 1 OF 8

A

G

P

/

P

C

I

I

N

T

E

R

F

A

C

E

AGP 8X

TEST_AGPCLK

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

AD8

AD9

AD10

AD11

AD12

AD13

AD14

AD15

AD16

AD17

AD18

AD19

AD20

AD21

AD22

AD23

AD24

AD25

AD26

AD27

AD28

AD29

AD30

AD31

DBI_HI

DBI_LO

AGP8X_DET#

Y36

Y37

AA36

AA37

AB36

AB37

AC36

AD37

AF37

AG36

AG37

AH36

AH37

AJ36

AK37

AK36

Y39

AB39

AA38

AC39

AB38

AD39

AC38

AE39

AG39

AG38

AH39

AH38

AJ39

AJ38

AK39

AK38

AL38

AL39

AL35

AP33

AGP_AD0

AGP_AD1

AGP_AD2

AGP_AD3

AGP_AD4

AGP_AD5

AGP_AD6

AGP_AD7

AGP_AD8

AGP_AD9

AGP_AD10

AGP_AD11

AGP_AD12

AGP_AD13

AGP_AD14

AGP_AD15

AGP_AD16

AGP_AD17

AGP_AD18

AGP_AD19

AGP_AD20

AGP_AD21

AGP_AD22

AGP_AD23

AGP_AD24

AGP_AD25

AGP_AD26

AGP_AD27

AGP_AD28

AGP_AD29

AGP_AD30

AGP_AD31

AGP_DBI_HI

AGP_DBI_LO

AGP_MB_8X_DET#

TEST_AGPCLK

AGP_AD[31..0]

AGP_DBI_HI (2)

AGP_DBI_LO (2)

AGP_MB_8X_DET# (2)

TP1

AGP_AD[31..0] (2)

2N7002E

R23

1K

1

Q1

5

+VDDQ_BUS+3.3V_BUS

32

R21 1.47K

R20

3.32K

R24

1.02K

*

AGP_VREFGC

C6

10nF

4

AGP_VREFGC (2,24)

3

Title

Size Document Number Rev

B

Date: Sheet of

GIGABYTE

R300 128M DVII VGA2 VO

GV-R9700

2

3 27Tuesday, March 11, 2003

1

1.1

8X_DET#(24)

R18

47K

AGP_MB_8X_DET#(2)

AGP_MB_8X_DET#

+5V_BUS

4

5

U2B

6

74ACT08MTC

TEST

UNIVERSAL VREFGC CIRCUIT (2X, 4X, 8X)

A A

8

7

6

8

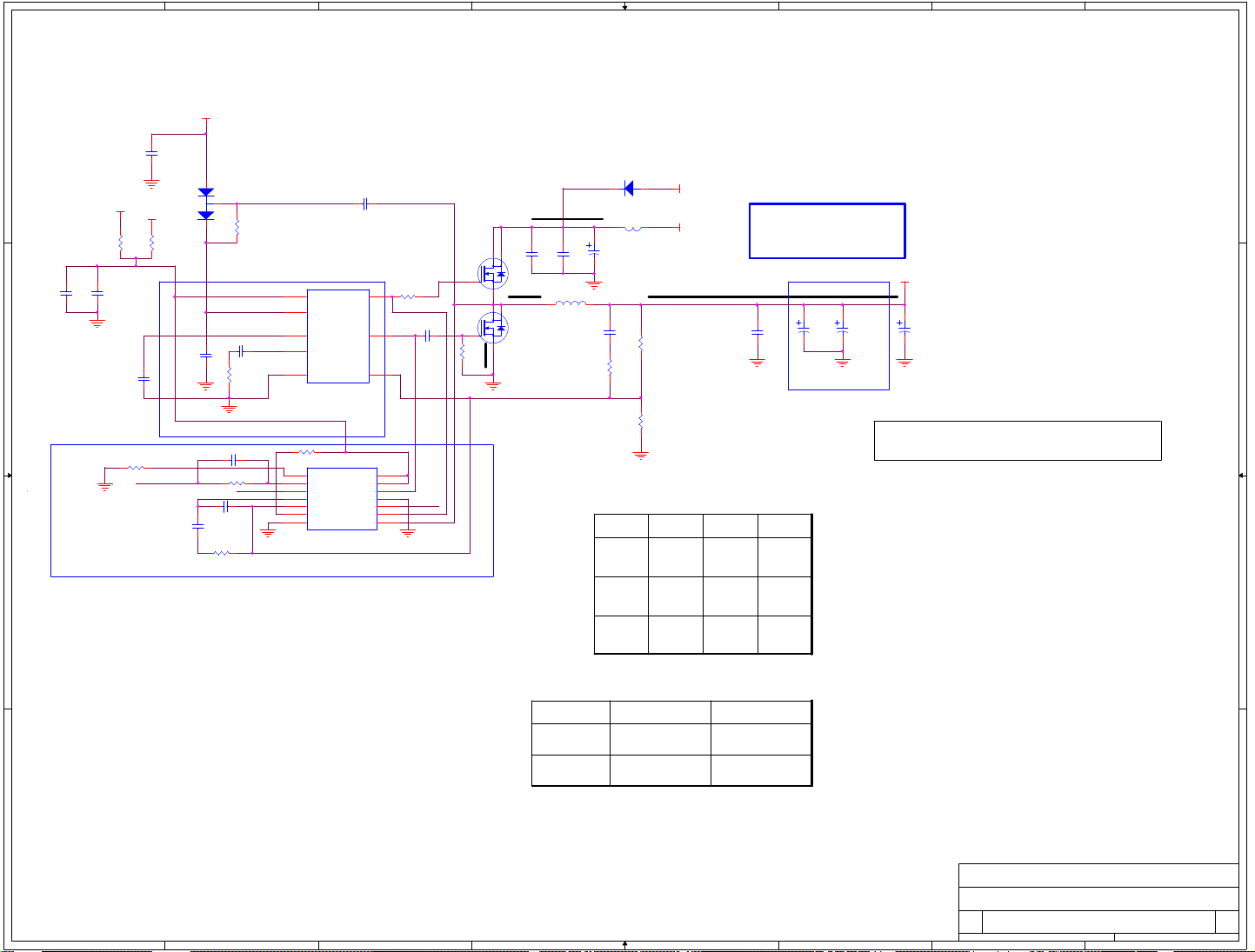

APPLICATION

D D

TVout w/ Rage Theatre

ext 24b DDR TMDS

ext 12b DDR TMDS&TVout

24b SDR TMDS

Note1 : PVSS, and MPVSS go to ground plane directly through their own

dedicated via. No connection with other VSS..

Note2 : Separate vias for AVSSQ (A2VSSQ), and AVSSN (A2VSSN) to

C C

ground plane.

Note3 : AVDD/AVSSN power need to use a pair of short traces (20mil at

least) and direct to link to AVDD & AVSSN balls, the ground return point

should be near the ground trace start point.

Note4: Rset resistor ground point should link to AVSSQ trace, or have via

at resistor directly to ground plane.

Note5 : Populate Ra9 and Ra10 only if they are not populated on page

24 or 25 or 31 or 32.

B B

TVOVMODE DVOVMODE

0V

VDDC18 VDDC18

0V

0V 0V

1uF

C29

1uF

C35

CLOCK SOURCE SELECTION

XTAL/OSC.

R300 alone

A A

CRYSTAL

OSC (OPTION 1)

OSC (OPTION 2)

DEFAULT

X

VDDC18

+VDDC_CT

DNI

DNI

+VDDDI

C30

100nF

+VDD2DI

C36

100nF

INSTALL

Ra1,Ra4

Crystal Circuit(27M)

Ra1 = 0R

Oscillator circuit(27M)

Ra4,Ra8

Oscillator circuit(27M)

7

R45 0R

R46 0R

R47 0R

R48 0R

DVO[11..0](23)

C28

22uF 16V

C34

22uF 16V

+VDDDI

+VDD2DI

VID[7..0](15,23)

DVO[11..0]

Ra4,Ra8

Crystal Circuit

Ra1

Crystal Circuit

VID[7..0]

CLK_VIDCLK(23)

DVALID(15,23)

PSYNC(15)

TVO0(22,23)

TVO1(23)

TVO2(22,23)

TVO3(23)

TVO4(23)

TVO5(23)

TVO6(15)

TVO7(15)

TVO8(15)

ROMSCK(15,17)

ROMSO(15,17)

ROMSI(15,17)

ROMCS#(15,17)

TP3

TP4

+VDDC_CT

B7

Bead

+VDDC_CT

B8

Bead

NOT INSTALL

Ra8

Oscillator circuit

CLK_DVOCLK0(23)

CLK_DVOCLK1(23)

6

VID0

VID1

VID2

VID3

VID4

VID5

VID6

VID7

R43 1K

TVO0

TVO1

TVO2

TVO3

TVO4

TVO5

TVO6

TVO7

TVO8

DVOCNTL0(23)

DVOCNTL1(23)

DVOCNTL2(23)

TEST_MCLK

TEST_YCLK

TESTEN

TP7

TP27

TP28

DVO0

DVO1

DVO2

DVO3

DVO4

DVO5

DVO6

DVO7

DVO8

DVO9

DVO10

DVO11

ROMCS#

+VDDDI

+VDD2DI

Crystal Circuit

U42B

AW35

VID0

AV35

VID1

AU35

VID2

AT35

VID3

AW34

VID4

AV34

VID5

AU34

VID6

AT34

VID7

AW36

VPCLK0

AU36

DVALID

AV36

PSYNC

AT36

TESTEN

AW21

TVOCLKO

AV21

TVOCLKI

AW19

TVODATA0

AV19

TVODATA1

AU19

TVODATA2

AT19

TVODATA3

AW20

TVODATA4

AV20

TVODATA5

AU20

TVODATA6

AT20

TVODATA7

AU21

TVODATA8

AT21

TVODATA9

AR19

TVOVMODE

AT18

DVOVMODE

AW17

DVOCLK0

AV17

DVOCLK1

AU15

DVOCNTL0

AV15

DVOCNTL1

AW15

DVOCNTL2

AT15

DVODATA0

AR15

DVODATA1

AW16

DVODATA2

AV16

DVODATA3

AU16

DVODATA4

AT16

DVODATA5

AU17

DVODATA6

AT17

DVODATA7

AR17

DVODATA8

AW18

DVODATA9

AV18

DVODATA10

AU18

DVODATA11

AP30

ROMSCK

AP29

ROMSO

AR29

ROMSI

AR30

ROMCS#

F9

TEST_MCLK

G6

TEST_YCLK

AU23

VDD1DI

AU27

VDD2DI

AU24

VSS1DI

AT26

VSS2DI

R300

DNI

C40

10pF

C41

10pF

DNI

Oscillator Circuit

+3.3V_BUS

8

C47

4

100nF

2 1

Y1

VDD

GND

27.000MHz

5

PART 2 OF 8

V

Video Capture & Test

I

D

E

O

&

TMDS / Flat PanelDAC / VGAXTAL

M

U

L

T

I

M

E

D

I

STEREOSYNC

A

TVOut, DVOut & ROM

VIP HostI2C

DNI

R56 0R

DNI

MY1

27 MHZ

DNI

R58 0R

5

OUT

1

E/D

TXCM

TXCP

TX0M

TX0P

TX1M

TX1P

TX2M

TX2P

TPVDD

TPVSS

TXVDDR

TXVDDR

TXVSSR

TXVSSR

TXVSSR

HPD1

HPD2

DDC1DATA

DDC1CLK

AUXWIN

VSYNC

HSYNC

G

B

AVDD

AVDD

AVSSN

AVSSN

AVSSQ

RSET

VIPCLK

VPHCTL

VHAD0

VHAD1

SCL

SDA

XTALOUT

XTALIN

PVDD

PVSS

MPVDD

MPVSS

R2SET

C-R

Y-G

COMP_B

H2SYNC

V2SYNC

DDC2CLK

DAC2 PLL

DDC2DATA

A2VDD

A2VDD

A2VSSN

A2VSSN

A2VDDQ

A2VSSQ

R63 107R

+3.3V_BUS

4

AV29

AW29

AV30

AW30

AV31

AW31

AV32

AW32

AW28

AV28

AT29

AT28

AU28

AU29

AU30

AR31

HPD1 (18)

AR33

HPD2 (23)

AU32

CRT1DDCDATA (20)

AU31

CRT1DDCCLK (20)

TP2

AP31

AT30

VSYNC_DAC1 (20)

AT31

HSYNC_DAC1 (20)

AP32

STEREOSYNC (22)

AW24

R

AW23

AW22

AV23

AV24

AR24

AT24

AU22

R52 499R

AV22

AV33

CLK_VIPCLK (23)

AW33

VPHCTL (23)

AU33

VHAD0 (15,23)

AT33

VHAD1 (23)

AR27

AR28

R300_XOUT

AW38

R300_XIN

AV38

AW37

AV37

+MPVDD

C7

GND_MPVSS

C6

AV25

AW27

AW26

AW25

AR32

AT32

AR34

AR35

AV26

AV27

AT25

AU26

AU25

AT27

DNI

Ra1

R66

150R

TXCM (18)

TXCP (18)

TX0M (18)

TX0P (18)

TX1M (18)

TX1P (18)

TX2M (18)

TX2P (18)

R55 715R

R/C_DAC2 (22)

G/Y_DAC2 (22)

B/COMP_DAC2 (22)

HSYNC_DAC2 (21)

VSYNC_DAC2 (21)

CRT2DDCCLK (21)

CRT2DDCDATA (21)

R57

1M

Ra4

R59 0R

TP34

GND_RSET

C738

SCL

SDA

R300_XOUT

1uF

1uF

C15

C19

22uF 16V

R53

4.7K

GND_R2SET

3

C17

100pF

TXVDDR

+3.3V_BUS+3.3V_BUS

TP35

C20

100pF

R54

4.7K

Ra10Ra9

R300_XIN

R65

0R

Ra8

C16

C18

22uF 16V

100nF

GND_TPVSS

C21

100nF

GND_TXVSSR

GND_AVSSQ

SCL (23)

SDA (23)

1uF

C25

DNI

1uF

C37

+MPVDD

GND_MPVSS

Rk

TP33

+A2VDDQ

C38

100nF

C26

100nF

Ba1

B3

Bead

R44

0R

DNI

Ba2

B4

Bead

C27

22uF 16V

C39

22uF 16V

GND_A2VSSQ

1uF

C42

DNI DNI DNI

2

+VDDC_CT+TPVDD

DNI

+VDDC_CT

Ba4

GND_PVSS

1uF

C31

DNI

Ba5

1uF

C43

B6

200R

B9

Bead

1uF

C44

R_DAC1 (20)

G_DAC1 (20)

B_DAC1 (20)

1uF

C22

DNI

+VDDC_CT+PVDD

DNI

C33

100nF

GND_A2VSSN

+AVDD

C23

C24

100nF

GND_AVSSN

+A2VDD

C32

22uF 16V

+VDDC_CT

+MPVDD +VDDC_CT

C45

C46

100nF

22uF 16V

GND_MPVSS

22uF 16V

Ba6

B10

200R

1

B5

Bead

Ba3

DNI

+VDDC_CT

Title

Size Document Number Rev

B

8

7

6

5

4

3

Date: Sheet of

GIGABYTE

R300 128M DVII VGA2 VO

GV-R9700

2

4 27Tuesday, March 11, 2003

1

1.1

5

U42G

M34

VDDR1

F33

VDDR1

H33

VDDR1

R6

VDDR1

U34

VDDR1

L34

VDDR1

N34

VDDR1

T33

REGULATOR

+5V_BUS

DNI

B11 200R

D D

DNI

3 2

AS432S

MREG1

R68

47R

R69

681R

1%

1

R70

1.50K

1%

FOR

DVO/TVO(+1.8V)

DNI

+VTVO/DVO

SC431LC5SK-1

DNI

4

NC

1

NC

2

5 3

DNI DNI

REG1

USE ONLY IF TVO OR DVO MODES ARE 1.8V

C C

VTERM2(16)

B B

+VDDTVO

B12 200R

B13 200R

C709

C74

A A

1uF

100nF

+VDDDVO

B14 200R

C75

1uF

C710

100nF

B15 200R

5

+3.3V_BUS

+VDDTVO

+VDDDVO

+VDDQ_BUS

+3.3V_BUS

+VTVO/DVO

DNI

+3.3V_BUS

+VTVO/DVO

DNI

W33

W34

AP12

AN12

AP11

AN13

AP10

AN14

AR25

AN29

AP26

AN28

AN25

AR22

AR23

AP24

AP27

AP19

AN21

AP20

AN17

AN18

AP15

AR16

AP16

AN34

AM34

AN33

AK33

AJ33

AC33

AB33

AA33

AL33

AJ34

AF34

AB34

AH33

AG33

AF33

AE33

AD33

VDDR1

V33

VDDR1

VDDR1

VDDR1

F11

VDDR1

F28

VDDR1

G13

VDDR1

F14

VDDR1

F16

VDDR1

F17

VDDR1

G23

VDDR1

F25

VDDR1

F27

VDDR1

T34

VDDR1

F31

VDDR1

G8

VDDR1

G26

VDDR1

G10

VDDR1

G11

VDDR1

G17

VDDR1

G18

VDDR1

F19

VDDR1

F20

VDDR1

F21

VDDR1

F22

VDDR1

G25

VDDR1

G29

VDDR1

G30

VDDR1

R33

VDDR1

G32

VDDR1

H7

VDDR1

K6

VDDR1

J7

VDDR1

L6

VDDR1

T7

VDDR1

V6

VDDR1

V7

VDDR1

W6

VDDR1

AF7

VDDR1

D6

VDDR1

AA6

VDDR1

AA7

VDDR1

AB7

VDDR1

AB6

VDDR1

AE6

VDDR1

AD6

VDDR1

AG7

VDDR1

AJ6

VDDR1

AP8

VDDR1

AH6

VDDR1

VDDR1

AN6

VDDR1

AL6

VDDR1

AN8

VDDR1

VDDR1

VDDR1

VDDR1

AN9

VDDR1

VDDR1

G14

VDDR1

F12

VDDR1

VDDR1

F32

VDDR1

H34

VDDR1

M5

VDDR1

G33

VDDR1

U7

VDDR1

AM6

VDDR1

AP7

VDDR1

L33

VDDRH

G22

VDDRH

L7

VDDRH

AL7

VDDRH

VDDR3

VDDR3

VDDR3

VDDR3

VDDR3

VDDR3

VDDR3

VDDR3

VDDR3

VDDR2

VDDR2

VDDR2

VDDR4

VDDR4

VDDR4

VDDR4

VDDR4

VDDP

VDDP

VDDP

VDDP

VDDP

VDDP

VDDP

VDDP

Y33

VDDP

VDDP

VDDP

VDDP

VDDP

VDDP

VDDP

VDDP

VDDP

VDDP

R300

PART 7 OF 8

P

O

W

E

R

DISPLAY I/O PWR

4

VDDC18

VDDC18

VDDC18

VDDC18

VDDC18

VDDC18

VDDC18

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

MEMORY I/O

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

CORE

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

AGP / PCI I/O

VDDCI

VDDCI

VDDCI

VDDCI

VSSRH

VSSRH

VSSRH

VSSRH

4

J33

N7

AK7

G20

AN22

AN27

AN32

AV2

AU3

AT4

AR5

AP6

AN7

N13

P13

R13

T13

U13

N14

P14

R14

T14

U14

P15

R15

T15

U15

N16

P16

R16

T16

U16

N17

P17

R17

T17

U17

AC23

AD23

AE23

AF23

AC24

AD24

AE24

AF24

AG24

AC25

AD25

AE25

AF25

AG25

AC26

AD26

AE26

AF26

AG26

AD27

AE27

AF27

AG27

N24

N25

N26

N27

P23

P24

P25

P26

P27

R23

R24

R25

R26

R27

T23

T24

T25

T26

T27

U23

U24

U25

U26

U27

AC14

AC15

AC16

AC17

AD13

AD14

AD15

AD16

AD17

AE13

AE14

AE15

AE16

AE17

AF13

AF14

AF15

AF16

AF17

AG13

AG14

AG15

AG16

AG17

N15

AC27

AG23

AC13

N23

M33

G21

M7

AM7

+VDDC_CT+MVDDQ

+VDDC

3

U42H

AM38

AF38

Y38

AM37

AJ37

AC37

AR36

AE36

AU38

AM35

AJ35

AF35

Y35

AM33

AL34

AN35

AK34

AH34

AE34

AD34

AC34

AA34

Y34

AC35

AK35

AA26

Y26

U37

U33

F29

P35

V35

V13

AU6

N37

T3

B20

AR2

K35

U6

W13

C35

C31

E32

E28

C27

Y13

AA13

E24

G7

E20

AB13

V14

C16

C37

C23

E18

E14

D4

C13

E5

C9

E10

C3

F3

N6

AU13

AR12

AA14

AB14

AA15

AB15

AA16

AB16

AA17

AB17

AA18

AB18

AA19

AB19

AA20

AB20

AA21

AB21

AA22

AG5

AD3

AP5

AH3

N3

W5

Y3

AU9

AM3

K5

AC5

W14

AL5

B2

F35

H38

Y14

F6

V15

W15

Y15

V16

W16

Y16

V17

W17

Y17

V18

W18

Y18

V19

W19

Y19

V20

W20

Y20

V21

W21

Y21

V22

W22

Y22

R300

VTERM1(16)

VSSP

VSSP

VSSP

VSSP

VSSP

VSSP

VSSP

VSSP

VSSP

VSSP

VSSP

VSSP

VSSP

VSSP

VSSP

VSSP

VSSP

VSSP

VSSP

VSSP

VSSP

VSSP

VSSP

VSSP

VSSP

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AB22

Part 8 of 8

CORE GND

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

N18

P18

VSS

R18

T18

U18

N19

P19

R19

T19

U19

N20

3

P21

VSS

R21

VSS

T21

VSS

U21

VSS

N22

VSS

P22

VSS

R22

VSS

T22

VSS

U22

VSS

V23

VSS

W23

VSS

Y23

VSS

AA23

VSS

AB23

VSS

V24

VSS

W24

VSS

Y24

VSS

AA24

VSS

AB24

VSS

V25

VSS

W25

VSS

Y25

VSS

AA25

VSS

AB25

VSS

V26

VSS

W26

VSS

AB26

VSS

V27

VSS

W27

VSS

Y27

VSS

AA27

VSS

AB27

VSS

AP28

VSS

AR26

VSS

AG22

VSS

AT22

VSS

AP34

VSS

AR20

VSS

AT23

VSS

AR21

VSS

AN31

VSS

AF22

VSS

AN23

VSS

AP25

VSS

AE22

VSS

AN30

VSS

AD22

VSS

AP22

VSS

AP17

VSS

AR18

VSS

AN19

VSS

AP21

VSS

AC22

VSS

AC21

VSS

AN24

VSS

AN16

VSS

AK6

VSS

AN10

VSS

AN15

VSS

AN20

VSS

AP13

VSS

AP14

VSS

AP18

VSS

AP9

VSS

AN11

VSS

AH7

VSS

AJ7

VSS

AP23

VSS

AF6

VSS

AG6

VSS

AD7

VSS

AE7

VSS

Y6

VSS

W7

VSS

M6

VSS

Y7

VSS

R7

VSS

P7

VSS

T6

VSS

K7

VSS

G12

VSS

F10

VSS

G9

VSS

F13

VSS

F15

VSS

G19

VSS

G15

VSS

G16

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

P20

R20

T20

U20

N21

F18

F23

AN26

AC7

F26

G27

G28

F30

G31

J34

K34

K33

J6

N33

P34

V34

R34

P33

AC18

AD18

AE18

AF18

AG18

AG19

AF19

AE19

AD19

AC19

AC20

AD20

AE20

AF20

AG20

AG21

AF21

AE21

AD21

F8

H6

D7

K2

PLACE DIRECTLY

UNDERNEATH

CHANNELS A

AND B

PLACE DIRECTLY

UNDERNEATH

CHANNELS C

AND D

+VDDC_CT

C48

100nF

+VDDC

USE 47uF

TANTALUM

CAPACITOR OR

HIGHER

2

CP1A

10nF

8 1

CP2A

10nF

8 1

+VDDQ_BUS

+3.3V_BUS

+MVDDQ

2

C49

100nF

8 1

7 2

7 2

C64

47uF 16V

CP12A

10nF

CP1B

10nF

CP2B

10nF

C67

22uF 16V

C68

47uF 6.3V

1

C53

5 4

5 4

CP5A

10nF

7 2

C73

10uf

C54

C52

10uf

1uF

C55

CP1D

1uF

10nF

CP3A

CP2D

10nF

10nF

8 1

7 2

CP4C

CP4D

10nF

10nF

6 3

5 4

C61

C62

10uf

10uf

CP5B

CP5C

10nF

10nF

7 2

6 3

CP11A

CP11B

10nF

10nF

8 1

7 2

CP6B

CP6C

10nF

10nF

5 4

6 3

CP8A

CP8B

10nF

10nF

8 1

7 2

CP9B

CP9A

10nF

10nF

7 2

8 1

CP12D

CP13A

10nF

10nF

5 4

8 1

R300 128M DVII VGA2 VO

Diodes Da1

and Da2 are

22uF 16V

needed to

protect ASIC

during power

ramping.

C57

C56

1uF

1uF

CP3B

CP3C

10nF

10nF

6 3

C59

C58

10uf

10uf

C63

10uf

C674

CP5D

10nF

CP11C

10nF

100nF

CP11D

10nF

5 4

CP7A

10nF

8 1

CP8C

10nF

5 4

6 3

CP9C

CP9D

10nF

10nF

6 3

5 4

CP13B

CP13C

10nF

10nF

7 2

6 3

5 4

6 3

CP6D

10nF

GIGABYTE

GV-R9700

1

C50

C51

100nF

100nF

CP1C

10nF

6 3

CP2C

10nF

6 3

CP4B

CP4A

10nF

10nF

7 2

8 1

C60

10uf

PLACE DIRECTLY

UNDERNEATH ASIC

AT THE OPPOSITE

CORNER OF THE

VDDC FEED.

PLACE DIRECTLY UNDERNEATH

VDDP SECTION OF ASIC.

C65

10uf

8 1

C66

1uF

CP6A

10nF

8 1

C70

C71

10uf

10uf

C72

10uf

CP12B

CP12C

10nF

10nF

7 2

6 3

Title

Size Document Number Rev

Custom

Date: Sheet of

5 4

7 2

CP8D

10nF

C673

1uF

CP3D

10nF

CP7B

10nF

C675

5 4

5 27Tuesday, March 11, 2003

+3.3V_BUS

+3.3V_BUS

100nF

6 3

C69

1uF

C707

100nF

CP13D

10nF

CP7C

10nF

Da1

D2

1.8V

2 1

Da2

D3

2.4V

2 1

CP7D

10nF

5 4

C708

100nF

C676

100nF

1.1

8

+5V_BUS

R72

D D

C C

2.2R

R910

100K

+12V_BUS

DNI DNI

R73

2.2R

1uF

C90

1uF

R81 0RC87

R83 0R

R911

100K

R1552 56R

Rb9

Rb10

Rb7 Rb8

DNI

R74

33K

Cb1

DNI

C78

2.2nF

Regulator for VTT Termination

+12V_BUS

+12V_BUS

+5V_BUS

SS_VTT

C102 2.2nF

DNI

DNIDNI

R96

27K

SS_VTT

DNI

R938

0R

BOOT

COMP_VTT

R99 10K

R939

0R

U44

2

Vcc

6

Vc

7

Comp

4

GND

IRU3037ACS

Alternate part

IRU3037CS

DNI

U45

2

OCSET

3

SS

4

COMP

5

FB

6

EN

7

GND

ISL6522CB

B B

C95

100nF

C103

150nF

A A

+PW_VTT

DNI

COMP_VTT

C104 33pF

C105

10nF

R102 15K

C762

100nF

R100 51K

R101 3K

DNI

8

7

CORE REGULATOR VDDC

C77 1nf

U43

DNI

R75

100K

Cb2

DNI

C79

150pF

Alternative 1

HDrv

LDrvSS

Fb

DNI

VCCRT

PVCC

LGATE

PGND

BOOT

UGATE

PHASE

1

VREF

2

+IN2

3

-IN2

4

VCC

5

CL2-

6

CL2+

7

BST2

8

DH2

9

DL2

10 11

PGND BSTC

SC1175CSW

Alternate part IRU3047

R93 10R

5

38

1

141

13

12

11

BOOT

10

9

8

7

20

GND

19

PWRGD

18

-IN1

17

SS/ENA

16

CL1-

15

CL1+

14

BST1

13

DH1

12

DL1

C742

1.0uF

2

4

Alternative 2

6

R873 0R

DNI

C85

1nF

R80 0R

R84 0R

+5V_BUS

B19

***

60R

+PW_VTT

71

8

Q5A

STS8DNF3LL

53

6

Q5B

STS8DNF3LL

6

Rb5

Rb6

C94

470uF 6.3V

L3 3.3uH

1 2

5

PWGOOD_VDDC (2)

DNI

DNI

C100

Cb5

10nF

DNI

R95

Rb14

1.5K

PW1

R82 0R

1 2

MBRS340T3

R94

825R

1%

Rb11

R98

1.10K

1%

C89 10nF

C93

10nF

D25

R97 1.40K

Rb12

*

C10, C11, C12, and C7 are the alternate surface

mount components for C80, C81, C82, C97

respectively.

5

R71 5.1R

FDS6898A

R79 5.1R

FDS6898A

Rb4

C741

R88 5.1R

R91 5.1R

FDS6898A

DNI

+3.3V_BUS

C7

470uF

DUAL FOOTPRINT

DNI

Rb13

C740

1.0uF

2

Q3B

4

R85 100R

1.0uF

2

FDS6898A

Q4B

4

R92 100R

JUb2

JU2

***

+3.3V_BUS

***

71

53

PW1

71

53

C1128

22uF 16V

C97

470uF 10V

B16

60R

PW

8

Q3A

6

R76 51.1R

8

Q4A

6

R89 51.1R

HEADER 1X4 RA

1

2

3

4

+MPVDD

4

C76

470uF 6.3V

L1 1.5uH

1 2

B18

C91

470uF

L2 1.5uH

1 2

C1129

2.2uF

** *****

**

4

60R

Bb1

C98

22uF 16V

R77 150R

C86 2.2uF

Cb4

C88 0.22uF

+5VEXT

R90 150R

C92 2.2uF

+5VEXT

C101

22uF 16V

6.8uF 25V

+VTT

C99

22uF 16V

**

3

2

Layout Guide Lines for switching regulators

1) Feedback trace from the voltage divider resistors to the controller as short as possible.

2) Trace from VIN to Qb1 should be in the same layer, with no via, width no less than 2MM

3) VIN_SOURCE should be a 2-3" snaked trace (with at least 6 bends.) The trace width

should be 2 MM.

4) Components with " ** " should have two vias on each pad

5) Components with " *** " should have three vias on each pad.

6) Connections indicated by bold thick line are high current path. Short, thick traces (at

least 30 mil) should be used.

R78

511R

1%

Rb1

R87

2.43K

***

DNI DNI DNI

C80

* * *

C10

470uF 10V

470uF

***

DUAL FOOTPRINT DUAL FOOTPRINT DUAL FOOTPRINT

1%

C11

470uF

***

C81

470uF 10V

***

C12

470uF

***

C82

470uF 10V

***

Rb2

Rb1

110R 1% DNI

511R 1%

2.43k 1%

INSTALL

Db1, Db2

VTT

Rb11

0.9V

1.25V DNI

0.9V

1.25V

0R

1.07K 1%

576R 1%

8.45K 1%

1.02K 1%

DO NOT INSTALL

Rb7, Rb8, Rb5, Cb1,

Cb2, Db2, Db1

Rb4, Rb6, Rb9, Rb10,

Rb12 Rb13

DNI47.5K 1%

75K 1%

C739

+12VEXT

C737

6.8uF 25V

Part

SC1175

IRU3047

Part

SC1175

IRU3047

Part

IRU3037

IRU3037A

ISL6522CB

VDDC Rb2

1.2V

1.5V

Rb4, Rb6, Rb9, Rb10, Cb4

Rb7, Rb8, Rb5, Cb1, Cb2

1.40V 825R 1% 1.0K 1% DNI

Part

IRU3037

IRU3037A

ISL6522CB

3

INSTALL

Alternative1

Alternative2

Title

Size Document Number Rev

B

Date: Sheet of

R300 128M DVII VGA2 VO

2

DO NOT INSTALL

Cb5, Rb14,

Alternative2

Alternative1

GIGABYTE

GV-R9700

1

+VDDC

**

***

***

C732

470uF

C84

22uF 16V

**

Cb4

DNI

DNI

DNI

6 27Tuesday, March 11, 2003

1

1.1

8

7

6

5

4

3

2

1

MVDDC Switching Regulator for

Memory Core for 128M

configuration

C121 100nF

+PW_VDD

71

8

Q8A

R954

10K

2

53

6

Q8B

4

DNI

R113 10R

5

HDrv

38

LDrvSS

1

Fb

141

VCCRT

13

PVCC

12

LGATE

11

PGND

10

BOOT

9

UGATE

8

PHASE

Alternative 2

C764 10nF

BOOT1

C744

220nF

STS8DNF3LL

STS8DNF3LL

C745

220nF

L5 2.2uH

1 2

Cd1

Rd4

D24

S3AB

B21

60R

C120

180uF 16V

C125

10nF

R115

1.5K

Part

IRU3037

IRU3037A

ISL6522CB

IRU3037A

ISL6522CB

21

+12V_BUS

***

+12VEXT

R114

1%

1.33K

Rd1

R117

499R

1%

Rd2

MVDDC

2.5V

2.5V

2.9V

Rd1

1.21K

1%

2.55K

1%

1.33K1%499R

C8 is an alternate surface

*

mount component for C122.

C746

10uF

DNI

C8

DNI

*

470uF

DUAL FOOTPRINT

**

**

**

** ***

Rd2

1.21K

1%

1.21K

1%

1%

+MVDDC

***

C122

470uF 10V

***

C736

470uF

***

Layout Guide Lines for VDD switching regulator

The same rules apply as for VDDC regulator.

C763

220nF

R937

0R

+12V_BUS

1

2

C734

1uF

DNI

DNI

C747 1nf

COMP_VDD

C128 33pF

C129

10nF

R122 15K

D6

BAT54SLT1

3

R112

0R

BOOT1

C126

2.2nF

R116

27K

DNI

R121 3K

SS_VDD

SS_VDD

COMP_VDD

DNI

U48

2

Vcc

6

Vc

7

Comp

4

GND

IRU3037ACS

Alternate part IRU3037CS

Alternative 1

R118 10K

U49

2

OCSET

3

SS

4

COMP

5

FB

6

EN

7

GND

ISL6522CB

D D

+12V_BUS

+5V_BUS

DNI

R936

0R

C743

220nF

C C

B B

C119

220nF

C127

22nf

R120 51K

+PW_VDD

Part

IRU3037

IRU3037A

INSTALL

Alternative1

ISL6522CB

A A

8

7

6

5

DO NOT INSTALL

Cd1, Rd4, Alternative2

Alternative1Alternative2

4

Title

Size Document Number Rev

B

3

Date: Sheet of

GIGABYTE

R300 128M DVII VGA2 VO

GV-R9700

2

7 27Tuesday, March 11, 2003

1

1.1

8

7

Regulator for MVDDQ (Memory I/O)

6

+5V_BUS

B22

***

60R

5

4

3

2

1

+1.8V Regulator for VDDC_CT (Core Transform)

D D

+12V_BUS

C133

100nF

C765

C142

150nF

C C

B B

A A

100nF

+PW_VDDQ

DNI

+5V_BUS

8

BOOT2

C141

2.2nF

R128

27K

DNI

R133 51K

R134 3K

DNI

SS_VDDQ

COMP_VDDQ

C143 33pF

DNI

C144

10nF

R135 15K

Part

IRU3037

IRU3037A

ISL6522CB

B26 200R

AS432S

MREG5

3 2

+12V_BUS

+5V_BUS

DNI

R935

R934

0R

0R

Alternative 1

U50

SS_VDDQ

COMP_VDDQ

DNI

R132 10K

2

Vcc

6

Vc

7

Comp

4

GND

IRU3037ACS

Alternate part IRU3037CS

U51

2

OCSET

3

SS

4

COMP

5

FB

6

EN

7

GND

ISL6522CB

HDrv

LDrvSS

Alternative 2

DNI

LGATE

PGND

BOOT

UGATE

PHASE

Fb

VCCRT

PVCC

5

38

1

Alternative1 Ce1, Re8, Alternative2

REGULATOR

FOR

MVDD(+1.8V)

REG5

SC431LC5SK-1

5 3

Alternative1

Alternative2

R142

47R

+MPVDD +TPVDD

R144

681R

1%

1

R146

1.50K

1%

4

NC

1

NC

2

GND_MPVSS GND_TPVSS

7

+PW_VDDQ

71

8

53

6

C130

470uF 6.3V

Q9A

STS8DNF3LL

Q9B

STS8DNF3LL

L6 3.3uH

1 2

Ce1

Re8

C13 is an alternate surface

*

mount component for C136.

R124

4.99K

C140

10nF

1%

Re4

R127

1.5K

DUAL FOOTPRINT

*

C13

DNI

470uF

+MVDDQ

***

***

C136

470uF 10V

C137

C138

**

22uF 16V

**

**

22uF 16V

**

C748

1.0uF

2

4

Re5

R131

2K

1%

141

13

12

11

BOOT2

10

9

8

Part

IRU3037

IRU3037A

ISL6522CB

IRU3037A

ISL6522CB

MVDDQ

2.5V

2.5V

2.8V

DO NOT INSTALLINSTALL

IRU3037

IRU3037A

ISL6522CB

+3.3V_BUS

B27 200R

R143

R145

681R

AS432S

1%

1

R147

MREG6

1.50K

1%

3 2

6

1.8V

1.8V

18R

4

NC

1

NC

2

5

REGULATOR

FOR TPVDD

(+1.8V)

REG6

SC431LC5SK-1

5 3

Re4

1.21K

1%

2.55K

1%

4.99K1%2.0K

681R

1%

1.87K

1%

Re5

1.21K

1%

1.21K

1%

1%

1.5K

1%

1.5K

1%

4

+3.3V_BUS

B23

REG2

60R

LT1117CST

3 2

IN OUT

C135

C134

22uF 16VR123 10R

100nF

1

+3.3V_BUS

CASE

ADJ

USE ONLY IF VDD IS +3.3V

B24

200R

1uF

C145

GND_A2VSSN GND_A2VSSN

+3.3V_BUS

B25 200R

AS432S

MREG4

3 2

Title

Size Document Number Rev

B

3

Date: Sheet of

+VDDC_CT

GND

2

R130

1.33K

1%

R126

562R

1%

+PVDD

VOUT

BYPASS

REGULATOR

FOR PVDD

(+1.8V)

4

NC

1

NC

2

GND_PVSS

C131

100nF

5 3

4

REG3

1

VIN

3

SHDN

2.5V

R139

18R

R140

681R

1%

1

R141

1.50K

1%

GIGABYTE

R300 128M DVII VGA2 VO

GV-R9700

2

C132

100uF 16V

REGULATOR

FOR

A2VDD(+2.5V)

5

4

C147

470pF

DNI

REG4

SC431LC5SK-1

+A2VDD

1uF

C146

8 27Tuesday, March 11, 2003

1

1.1

5

4

3

2

1

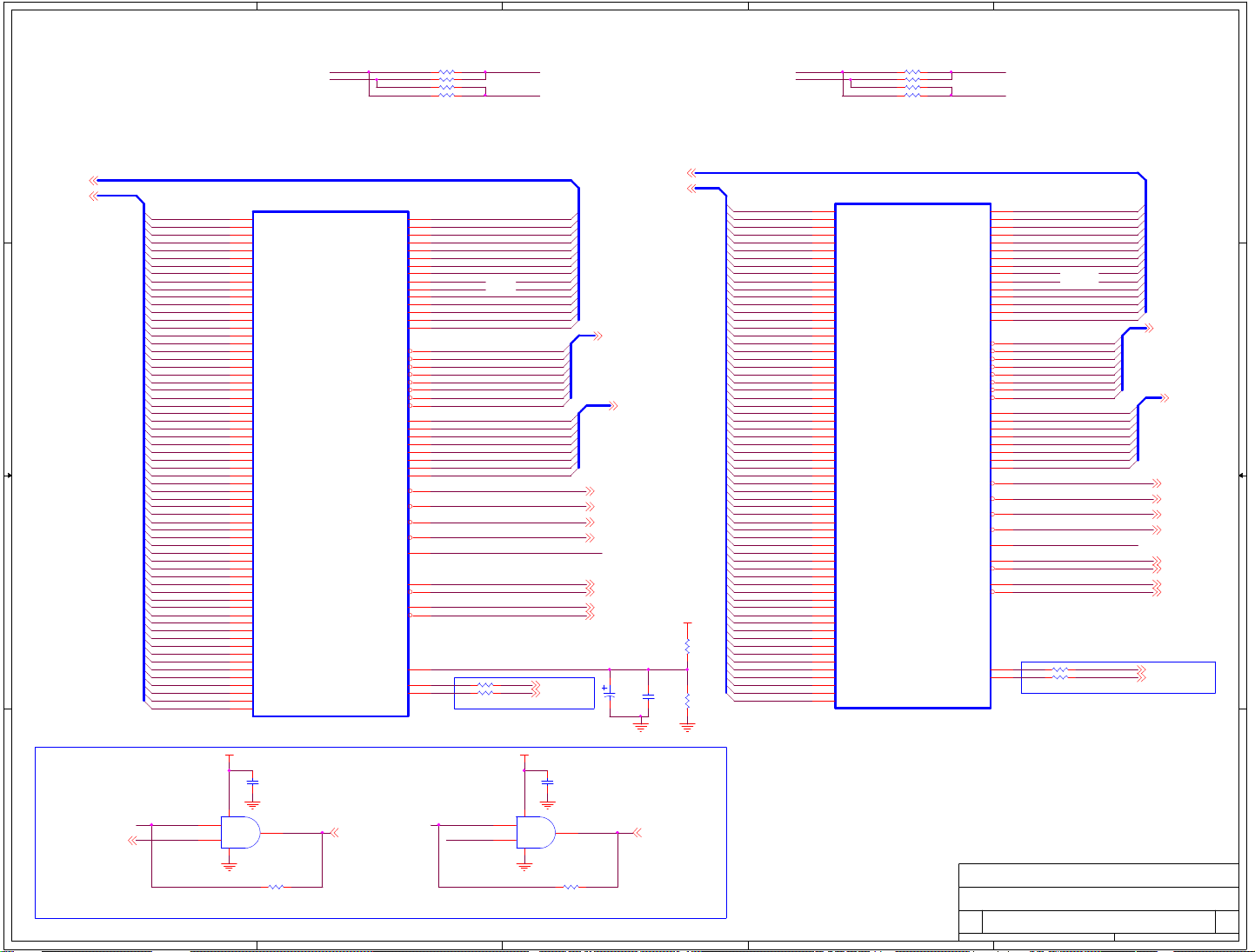

R-300

MEMORY CHANNELS A and B

MAA8X

MAA9X

D D

R883 0R

R884 0R

R880 0R

R879 0R

MAA8

MAA9 MAB9

MAB8X

MAB9X

R885 0R

R886 0R

R882 0R

R881 0R

MAB8

+MVDDQ

R137

75.0R

R138

75.0R

MAB[14..0]

MDB0

MDB1

MDB2

MDB3

MDB4

MDB5

MDB7

MDB8

MDB9

MDB10

MDB11

MDB12

MDB13

MDB14

MDB15

MDB16

MDB17

MDB18

MDB19

MDB20

MDB21

MDB22

MDB23

MDB24

MDB25

MDB26

MDB27

MDB28

MDB29

MDB30

MDB31

MDB32

MDB33

MDB34

MDB35

MDB36

MDB37

MDB38

MDB39

MDB40

MDB41

MDB42

MDB43

MDB44

MDB45

MDB46

MDB47

MDB48

MDB49

MDB50

MDB51

MDB52

MDB53

MDB54

MDB55

MDB56

MDB57

MDB58

MDB59

MDB60

MDB61

MDB62

MDB63

U42D

E25

DQB0

D25

DQB1

C25

DQB2

D24

DQB3

D23

DQB4

E22

DQB5

D22

DQB6

C22

DQB7

B26

DQB8

A26

DQB9

B25

DQB10

A25

DQB11

B23

DQB12

A23

DQB13

B22

DQB14

A22

DQB15

E29

DQB16

D29

DQB17

C29

DQB18

D28

DQB19

D27

DQB20

E26

DQB21

D26

DQB22

C26

DQB23

B31

DQB24

A31

DQB25

B30

DQB26

A30

DQB27

B28

DQB28

A28

DQB29

B27

DQB30

A27

DQB31

B15

DQB32

A15

DQB33

B14

DQB34

A14

DQB35

B12

DQB36

A12

DQB37

B11

DQB38

A11

DQB39

E15

DQB40

D15

DQB41

C15

DQB42

D14

DQB43

D13

DQB44

E12

DQB45

D12

DQB46

C12

DQB47

B10

DQB48

A10

DQB49

B9

DQB50

A9

DQB51

B7

DQB52

A7

DQB53

B6

DQB54

A6

DQB55

E11

DQB56

D11

DQB57

C11

DQB58

D10

DQB59

D9

DQB60

E8

DQB61

D8

DQB62

C8

DQB63

R300

Part 4 of 8

DQMB#0

DQMB#1

DQMB#2

DQMB#3

DQMB#4

DQMB#5

DQMB#6

DQMB#7

MEMORY INTERFACE

B

MAB0

MAB1

MAB2

MAB3

MAB4

MAB5

MAB6

MAB7

MAB8

MAB9

MAB10

MAB11

MAB12

MAB13

MAB14

QSB0

QSB1

QSB2

QSB3

QSB4

QSB5

QSB6

QSB7

RASB#

CASB#

WEB#

CSB#

CKEB

CLKB0

CLKB0#

CLKB1

CLKB1#

DIMB0

DIMB1

MAB0

C18

MAB1

C19

MAB2

E19

MAB3

D20

MAB4

C20

MAB5

D19

MAB6MDB6

D18

MAB7

B18

MAB8X

D17

MAB9X

C21

MAB10

D21

MAB11

E21

MAB12

A18

MAB13

C17

MAB14

E17

DQMB#0

C24

DQMB#1

B24

C28

DQMB#3

B29

DQMB#4

B13

DQMB#5

C14

DQMB#6

B8

DQMB#7DQMA#6

C10

QSB0

E23

QSB1

A24

QSB2

E27

QSB3

A29

QSB4

A13

QSB5

E13

QSB6

A8

QSB7

E9

RASB#

D16

CASB#

A16

WEB#

B16

CSB#

B17

CKEB

A17

A20

B21

B19

A19

R710 0R

A21

R711 0R

E16

MAB8

MAB9

DQMB#[7..0] (11)

DIMB0 (13)

DIMB1 (13)

Only for BGA Elpida memory

QSB[7..0] (11)

RASB# (11,13)

CASB# (11,13)

WEB# (11,13)

CSB# (11,13)

M_CLKB0 (11,13)

M_CLKB#0 (11,13)

M_CLKB1 (11,13)

M_CLKB#1 (11,13)

MAA[14..0](11,13)

MDA[63..0](11)

C C

B B

MAA[14..0]

MDA[63..0]

MDA0

MDA1

MDA2

MDA3

MDA4

MDA5

MDA6

MDA7

MDA8

MDA9

MDA10

MDA11

MDA12

MDA13

MDA14

MDA15

MDA16

MDA17

MDA18

MDA19

MDA20

MDA21

MDA22

MDA23

MDA24

MDA25

MDA26

MDA27

MDA28

MDA29

MDA30

MDA31

MDA32

MDA33

MDA34

MDA35

MDA36

MDA37

MDA38

MDA39

MDA40

MDA41

MDA42

MDA43

MDA44

MDA45

MDA46

MDA47

MDA48

MDA49

MDA50

MDA51

MDA52

MDA53

MDA54

MDA55

MDA56

MDA57

MDA58

MDA59

MDA60

MDA61

MDA62

MDA63

W35

W36

W37

W38

W39

U42C

R35

DQA0

R36

DQA1

R37

DQA2

P36

DQA3

N36

DQA4

M35

DQA5

M36

DQA6

M37

DQA7

P38

DQA8

P39

DQA9

N38

DQA10

N39

DQA11

L38

DQA12

L39

DQA13

K38

DQA14

K39

DQA15

DQA16

DQA17

DQA18

V36

DQA19

U36

DQA20

T35

DQA21

T36

DQA22

T37

DQA23

DQA24

DQA25

V38

DQA26

V39

DQA27

T38

DQA28

T39

DQA29

R38

DQA30

R39

DQA31

E38

DQA32

D39

DQA33

D38

DQA34

C39

DQA35

B38

DQA36

A38

DQA37

B37

DQA38

A37

DQA39

E37

DQA40

D37

DQA41

E36

DQA42

D36

DQA43

D35

DQA44

E34

DQA45

D34

DQA46

C34

DQA47

B36

DQA48

A36

DQA49

B35

DQA50

A35

DQA51

B33

DQA52

A33

DQA53

B32

DQA54

A32

DQA55

E33

DQA56

D33

DQA57

C33

DQA58

D32

DQA59

D31

DQA60

E30

DQA61

D30

DQA62

C30

DQA63

R300

Part 3 of 8

DQMA#0

DQMA#1

DQMA#2

DQMA#3

DQMA#4

DQMA#5

DQMA#6

DQMA#7

MEMORY INTERFACE

A

MAA10

MAA11

MAA12

MAA13

MAA14

RASA#

CASA#

WEA#

CLKA0

CLKA0#

CLKA1

CLKA1#

VREF2

DIMA0

DIMA1

MAA0

H36

MAA0

MAA1

J37

MAA1

MAA2

J35

MAA2

MAA3

K36

MAA3

MAA4

K37

MAA4

MAA5

J36

MAA5

MAA6

H35

MAA6

MAA7

H37

MAA7

MAA8

MAA9

QSA0

QSA1

QSA2

QSA3

QSA4

QSA5

QSA6

QSA7

CSA#

CKEA

MAA8X

G36

MAA9X

L37

MAA10

L36

MAA11

L35

MAA12

G35

MAA13

G37

MAA14

G34

DQMA#0

P37

DQMA#1 DQMB#2

M38

DQMA#2

V37

DQMA#3

U38

DQMA#4

C38

DQMA#5

C36

B34

DQMA#7

C32

QSA0

N35

QSA1

M39

QSA2

U35

QSA3

U39

QSA4

B39

QSA5

E35

QSA6

A34

QSA7

E31

RASA#

F39

CASA#

E39

WEA#

F36

CSA#

F37

CKEA

F38

H39

J38

G38

G39

G24

R708 0R

J39

R709 0R

F34

MAA8

MAA9

DIMA0 (13)

DIMA1 (13)

Only for BGA Elpida memory

+MVDDQ+MVDDQ

MAB[14..0](11,13)

MDB[63..0](11)

DQMA#[7..0] (11)

QSA[7..0] (11)

RASA# (11,13)

CASA# (11,13)

WEA# (11,13)

CSA# (11,13)

M_CLKA0 (11,13)

M_CLKA#0 (11,13)

M_CLKA1 (11,13)

M_CLKA#1 (11,13)

C148

10uF 16V

B - size

C149

100nF

C727

100nF

53

A A

AGP_RESET#(2,3,10,23,24)

CKEA

AGP_RESET#

5

TC7SZ08FU

1

2

M_CKEA M_CKEB

4

U89

DNI DNI

R855 0R R856 0R

M_CKEA (11,13) M_CKEB (11,13)

4

CKEB

AGP_RESET#

C728

100nF

53

TC7SZ08FU

1

2

4

U90

Title

Size Document Number Rev

B

3

2

Date: Sheet of

GIGABYTE

R300 128M DVII VGA2 VO

GV-R9700

9 27Tuesday, March 11, 2003

1

1.1

5

(2,3,9,23,24)

4

3

2

1

R-300

MEMORY CHANNELS C and D

MAC8X

MAC9X

D D

R905 0R

R907 0R

R889 0R

R887 0R

MAC8

MAC9

MAD8X MAD8

MAD9X

R906 0R

R908 0R

R890 0R

R888 0R

MAD9

MAC[14..0](12,14)

MDC[63..0](12)

C C

B B

A A

AGP_RESET#

MAC[14..0]

MDC0

MDC1

MDC2

MDC3

MDC4

MDC5

MDC6

MDC7

MDC8 MAC8X

MDC9

MDC10

MDC11

MDC12

MDC13

MDC14

MDC15

MDC16

MDC17

MDC18

MDC19

MDC20

MDC21

MDC22

MDC23

MDC24

MDC25

MDC26

MDC27

MDC28

MDC29

MDC30

MDC31

MDC32

MDC33

MDC34

MDC35

MDC36

MDC37

MDC38

MDC39

MDC40

MDC41

MDC42

MDC43

MDC44

MDC45

MDC46

MDC47

MDC48

MDC49

MDC50

MDC51

MDC52

MDC53

MDC54

MDC55

MDC56

MDC57

MDC58

MDC59

MDC60

MDC61

MDC62

MDC63

CKEC

U42E

G4

DQC0

G3

DQC1

H5

DQC2

H4

DQC3

J4

DQC4

J3

DQC5

K4

DQC6

K3

DQC7

D2

DQC8

D1

DQC9

E2

DQC10

E1

DQC11

G2

DQC12

G1

DQC13

H2

DQC14

H1

DQC15

C5

DQC16

C4

DQC17

D5

DQC18

D3

DQC19

E6

DQC20

F5

DQC21

F4

DQC22

G5

DQC23

B5

DQC24

A5

DQC25

B4

DQC26

A4

DQC27

A2

DQC28

B1

DQC29

C2

DQC30

C1

DQC31

P2

DQC32

P1

DQC33

R2

DQC34

R1

DQC35

U2

DQC36

U1

DQC37

V2

DQC38

V1

DQC39

U4

DQC40

U3

DQC41

V5

DQC42

V4

DQC43

W3

DQC44

Y5

DQC45

Y4

DQC46

AA5

DQC47

W2

DQC48

W1

DQC49

Y2

DQC50

Y1

DQC51

AB2

DQC52

AB1

DQC53

AC2

DQC54

AC1

DQC55

AA4

DQC56

AA3

DQC57

AB5

DQC58

AB4

DQC59

AC3

DQC60

AD5

DQC61

AD4

DQC62

AE5

DQC63

R300

53

1

2

C729

100nF

TC7SZ08FU

M_CKEC

4

U91

Part 5 of 8

MEMORY

M_CKEC (12,14) M_CKED (12,14)

INTERFACE C

MAC0

MAC1

MAC2

MAC3

MAC4

MAC5

MAC6

MAC7

MAC8

MAC9

MAC10

MAC11

MAC12

MAC13

MAC14

DQMC#0

DQMC#1

DQMC#2

DQMC#3

DQMC#4

DQMC#5

DQMC#6

DQMC#7

QSC0

QSC1

QSC2

QSC3

QSC4

QSC5

QSC6

QSC7

RASC#

CASC#

WEC#

CSC#

CKEC

CLKC0

CLKC0#

CLKC1

CLKC1#

DIMC0

DIMC1

MAC0

N2

MAC1

N5

MAC2

M2

MAC3

M4

MAC4

M3

MAC5

M1

MAC6

N4

MAC7

N1

P4

MAC9X

L3

MAC10

L4

MAC11

L5

MAC12

P5

MAC13

P3

MAC14

P6

DQMC#0

H3

F2

DQMC#2

E4

DQMC#3

B3

DQMC#4

T2

DQMC#5

V3

DQMC#6

AA2

DQMC#7

AB3

QSC0

J5

QSC1

F1

QSC2

E3

QSC3

A3

QSC4

T1

QSC5

W4

QSC6

AA1

QSC7

AC4

RASC#

R4

CASC#

T4

WEC#

T5

CSC#

R3

CKEC

R5

K1

J2

L2

L1

R712 0R

J1

R713 0R

U5

CKED

AGP_RESET#AGP_RESET#

MAC8

MAC9

DIMC0 (14)

C730

100nF

TC7SZ08FU

M_CKED

4

U92

DIMC1 (14)

Only for Elpida

memory

53

1

2

MAD[14..0](12,14)

MDD[63..0](12)

DQMC#[7..0] (12)

QSC[7..0] (12)

RASC# (12,14)

CASC# (12,14)

WEC# (12,14)

CSC# (12,14)

M_CLKC0 (12,14)

M_CLKC#0 (12,14)

M_CLKC1 (12,14)

M_CLKC#1 (12,14)

MAD[14..0]

MDD0

MDD1

MDD2

MDD3

MDD4

MDD5

MDD7

MDD8

MDD9

MDD10

MDD11

MDD12

MDD13

MDD14

MDD15

MDD16

MDD17

MDD18

MDD19

MDD20

MDD21

MDD22

MDD23

MDD24

MDD25

MDD26

MDD27

MDD28

MDD29

MDD30

MDD31

MDD32

MDD33

MDD34

MDD35

MDD36

MDD37

MDD38

MDD39

MDD40

MDD41

MDD42

MDD43

MDD44

MDD45

MDD46

MDD47

MDD48

MDD49

MDD50

MDD51

MDD52

MDD53

MDD54

MDD55

MDD56

MDD57

MDD58

MDD59

MDD60

MDD61

MDD62

MDD63

MEMVMODE[1:0]

MEMORY IO VOLTAGE

0 1

1 0 1.8V (DDR)

1 1

2.5V (DDR)

3.3V (SDR)

AK5

AK4

AL3

AM5

AM4

AN5

AK2

AK1

AM2

AM1

AN2

AN1

AE4

AE3

AF5

AF4

AG3

AH5

AH4

AD2

AD1

AE2

AE1

AG2

AG1

AH2

AH1

AV5

AW5

AV6

AW6

AV8

AW8

AV9

AW9

AT7

AU7

AR8

AT8

AT9

AR10

AT10

AU10

AV10

AW10

AV11

AW11

AV13

AW13

AV14

AW14

AR11

AT11

AU11

AT12

AT13

AR14

AT14

AU14

U42F

AJ4

DQD0

AJ3

DQD1

DQD2

DQD3

DQD4

DQD5

DQD6

DQD7

AJ2

DQD8

AJ1

DQD9

DQD10

DQD11

DQD12

DQD13

DQD14

DQD15

DQD16

DQD17

DQD18

DQD19

DQD20

DQD21

DQD22

AJ5

DQD23

DQD24

DQD25

DQD26

DQD27

DQD28

DQD29

DQD30

DQD31

DQD32

DQD33

DQD34

DQD35

DQD36

DQD37

DQD38

DQD39

DQD40

DQD41

DQD42

DQD43

DQD44

DQD45

DQD46

DQD47

DQD48

DQD49

DQD50

DQD51

DQD52

DQD53

DQD54

DQD55

DQD56

DQD57

DQD58

DQD59

DQD60

DQD61

DQD62

DQD63

R300

MEMMODE0

MEMMODE1

R167

4.7K

Part 6 of 8

MAD0

MAD1

MAD2

MAD3

MAD4

MAD5

MAD6

MAD7

MAD8

MAD9

MAD10

MAD11

MAD12

MAD13

MAD14

DQMD#0

DQMD#1

DQMD#2

DQMD#3

DQMD#4

DQMD#5

DQMD#6

DQMD#7

QSD0

QSD1

QSD2

QSD3

QSD4

QSD5

QSD6

QSD7

RASD#

CASD#

WED#

CSD#

MEMORY

INTERFACE D

CKED

CLKD0

CLKD0#

CLKD1

CLKD1#

VREF1

DIMD0

DIMD1

MEMVMODE0

MEMVMODE1

MEMTEST

R164 4.7K

R165 4.7K

R168

4.7K

AT3

AT6

AR4

AP3

AR6

AR3

AT5

AU5

AU2

AP4

AN3

AN4

AU4

AU1

AV4

AK3

AL2

AF3

AF2

AV7

AU8

AV12

AU12

AL4

AL1

AG4

AF1

AW7

AR9

AW12

AR13

AW4

AW2

AW3

AV3

AV1

AR1

AP2

AT2

AT1

AC6

AP1

AR7

E7

F7

F24

MAD0

MAD1

MAD2

MAD3

MAD4

MAD5

MAD6MDD6

MAD7

MAD8X

MAD9X

MAD10

MAD11

MAD12

MAD13

MAD14

DQMD#0

DQMD#1

DQMD#2

DQMD#3DQMC#1

DQMD#4

DQMD#5

DQMD#6

DQMD#7

QSD0

QSD1

QSD2

QSD3

QSD4

QSD5

QSD6

QSD7

RASD#

CASD#

WED#

CSD#

CKED

R166

47R

+VDDC_CT+MVDDQ +MVDDQ

MAD8

MAD9

MEMMODE0

MEMMODE1

R714 0R

R715 0R

DQMD#[7..0] (12)

QSD[7..0] (12)

RASD# (12,14)

CASD# (12,14)

WED# (12,14)

CSD# (12,14)

M_CLKD0 (12,14)

M_CLKD#0 (12,14)

M_CLKD1 (12,14)

M_CLKD#1 (12,14)

C150

10uF 16V

Only for Elpida

memory

DIMD0 (14)

DIMD1 (14)

C151

100nF

+MVDDQ

R773

75.0R

R774

75.0R

DNI DNI

R857 0R

5

4

R858 0R

Title

Size Document Number Rev

B

3

2

Date: Sheet of

GIGABYTE

R300 128M DVII VGA2 VO

GV-R9700

10 27Tuesday, March 11, 2003

1

1.1

8

+MVDDQ

100nF

D D

100nF

+MVDDQ

100nF

C158

100nF

+MVDDQ

100nF

C C

100nF

+MVDDQ

C164

100nF

C166

100nF

+MVDDQ

100nF

B B

100nF

+MVDDQ

100nF

100nF

A A

+MVDDQ

C177

100nF

+VTT

RP1A 56R

RP1B 56R

RP1C 56R

C152

RP1D 56R

RP2A 56R

RP2B 56R

RP2C 56R

RP2D 56R

RP3A 56R

RP3B 56R

RP3C 56R

RP3D 56R

RP4A 56R

C154

RP4B 56R

RP4C 56R

RP4D 56R

RP5A 56R

RP5B 56R

RP5C 56R

RP5D 56R

RP6A 56R

C156

RP6B 56R

RP6C 56R

RP6D 56R

RP7A 56R

RP7B 56R

RP7C 56R

RP7D 56R

RP8A 56R

RP8B 56R

RP8C 56R

RP8D 56R

RP9A 56R

8 1

RP9B 56R

7 2

RP9C 56R

6 3

RP9D 56R

5 4

RP10A 56R

C161

C162

C168

C170

C173

C175

Rf Rff

8 1

RP10B 56R

7 2

RP10C 56R

6 3

RP10D 56R

5 4

RP11A 56R

8 1

RP11B 56R

7 2

RP11C 56R

6 3

RP11D 56R

5 4

RP12A 56R

8 1

RP12B 56R

7 2

RP12C 56R

6 3

RP12D 56R

5 4

RP13A 56R

8 1

RP13B 56R

7 2

RP13C 56R

6 3

RP13D 56R

5 4

RP14A 56R

8 1

RP14B 56R

7 2

RP14C 56R

6 3

RP14D 56R

5 4

RP15A 56R

RP15B 56R

RP15C 56R

RP15D 56R

RP16A 56R

8 1

RP16B 56R

7 2

RP16C 56R

6 3

RP16D 56R

5 4

RP18D 56R

RP19A 56R

8 1

RP18C 56R

RP17C 56R

6 3

RP17B 56R

7 2

RP18B 56R

RP19B 56R

7 2

RP20B 56R

RP20A 56R

RP18A 56R

RP17D 56R

5 4

RP17A 56R

8 1

RP19C 56R

6 3

RP19D 56R

5 4

RP20D 56R

R189 56R

R190 56R

R192 56R

R194 56R

R196 56R

R198 56R

R200 56R

R202 56R

RP23B 56R

7 2

RP23C 56R

6 3

RP20C 56R

RP23A 56R

8 1

R776 56R

R778 56R

R780 56R

R782 56R

R718 56R

R719 56R

R720 56R

R721 56R

R722 56R

R723 56R

R724 56R

R725 56R

8

C179

22uF

MDA0

81

MDA1

72

MDA2

63

MDA3

54

MDA4

81

MDA5

72

MDA6

63

MDA7

54

MDA8

81

MDA9

72

MDA10

63

MDA11

54

MDA12

81

MDA13

72

MDA14

63

MDA15

54

MDA16

81

MDA17

72

MDA18

63

MDA19

54

MDA20

81

MDA21

72

MDA22

63

MDA23

54

MDA24

81

MDA25

72

MDA26

63

MDA27

54

MDA28

81

MDA29

72

MDA30

63

MDA31

54

MDA32

MDA33

MDA34

MDA35

MDA36

MDA37

MDA38

MDA39

MDA40

MDA41

MDA42

MDA43

MDA44

MDA45

MDA46

MDA47

MDA48

MDA49

MDA50

MDA51

MDA52

MDA53

MDA54

MDA55

MDA56

81

MDA57

72

MDA58

63

MDA59

54

MDA60

MDA61

MDA62

MDA63

MAA0

54

MAA1

MAA2

63

MAA3

MAA4

MAA5

72

MAA6

MAA7

72

MAA8

81

MAA9

81

MAA10

MAA11

MAA12

MAA13

54

DQMA#0

DQMA#1

DQMA#2

DQMA#3

DQMA#4

DQMA#5

DQMA#6

DQMA#7

WEA#

CASA#

RASA#

63

CSA#

M_CLK0

M_CLK#0

M_CLK1

M_CLK#1

QSA0

QSA1

QSA2

QSA3

QSA4

QSA5

QSA6

QSA7

7

MDA0

MDA1

MDA2

MDA3

MDA4

MDA5

MDA6

MDA7

MDA8

MDA9

MDA10

MDA11

MDA12

MDA13

MDA14

MDA15

MDA16

MDA17

MDA18

MDA19

MDA20

MDA21

MDA22

MDA23

MDA24

MDA25

MDA26

MDA27

MDA28

MDA29

MDA30

MDA31

MDA32

MDA33

MDA34

MDA35

MDA36

MDA37

MDA38

MDA39

MDA40

MDA41

MDA42

MDA43

MDA44

MDA45

MDA46

MDA47

MDA48

MDA49

MDA50

MDA51

MDA52

MDA53

MDA54

MDA55

MDA56

MDA57

MDA58

MDA59

MDA60

MDA61

MDA62

MDA63

DQMA#[7..0] (9)

WEA# (9,13)

CASA# (9,13)

RASA# (9,13)

CSA# (9,13)

M_CLKA0 (9,13)

M_CLKA#0 (9,13)

M_CLKA1 (9,13)

M_CLKA#1 (9,13)

R208 47R

R210 47R

R212 47R

R214 47R

R216 47R

R218 47R

R220 47R

R222 47R

7

RP25A 47R

8 1

RP25B 47R

7 2

RP25C 47R

6 3

RP25D 47R

5 4

RP26A 47R

8 1

RP26B 47R

7 2

RP26C 47R

6 3

RP26D 47R

5 4

RP27A 47R

8 1

RP27B 47R

7 2

RP27C 47R

6 3

RP27D 47R

5 4

RP28A 47R

8 1

RP28B 47R

7 2

RP28C 47R

6 3

RP28D 47R

5 4

RP29A 47R

8 1

RP29B 47R

7 2

RP29C 47R

6 3

RP29D 47R

5 4

RP30A 47R

8 1

RP30B 47R

7 2

RP30C 47R

6 3

RP30D 47R

5 4

RP31A 47R

8 1

RP31B 47R

7 2

RP31C 47R

6 3

RP31D 47R

5 4

RP32A 47R

8 1

RP32B 47R

7 2

RP32C 47R

6 3

RP32D 47R

5 4

RP33A 47R

RP33B 47R

RP33C 47R

RP33D 47R

RP34A 47R

RP34B 47R

RP34C 47R

RP34D 47R

RP35A 47R

RP35B 47R

RP35C 47R

RP35D 47R

RP36A 47R

RP36B 47R

RP36C 47R

RP36D 47R

RP37A 47R

RP37B 47R

RP37C 47R

RP37D 47R

RP38A 47R

RP38B 47R

RP38C 47R

RP38D 47R

RP39A 47R

RP39B 47R

RP39C 47R

RP39D 47R

RP40A 47R

RP40B 47R

RP40C 47R

RP40D 47R

MAA0

MAA1

MAA2

MAA3

MAA4

MAA5

MAA6

MAA7

MAA8

MAA9

MAA10

MAA11

MAA12

MAA13

MAA14

WEA#

RASA#

CASA#

CSA#

M_QSA0

M_QSA1

M_QSA2

M_QSA3

M_QSA4

M_QSA5

M_QSA6

M_QSA7

6

MDA[63..0]

MAA[14..0]

M_MDA[63..0]

M_MDA0

M_MDA1

M_MDA2

M_MDA3

M_MDA4

M_MDA5

M_MDA6

M_MDA7

M_MDA8

M_MDA9

M_MDA10

M_MDA11

M_MDA12

M_MDA13

M_MDA14

M_MDA15

M_MDA16

M_MDA17

M_MDA18

M_MDA19

M_MDA20

M_MDA21

M_MDA22

M_MDA23

M_MDA24

M_MDA25

M_MDA26

M_MDA27

M_MDA28

M_MDA29

M_MDA30

M_MDA31

M_MDA32

81

M_MDA33

72

M_MDA34

63

M_MDA35

54

M_MDA36

81

M_MDA37

72

M_MDA38

63

M_MDA39

54

M_MDA40

81

M_MDA41

72

M_MDA42

63

M_MDA43

54

M_MDA44

81

M_MDA45

72

M_MDA46

63

M_MDA47

54

M_MDA48

81

M_MDA49

72

M_MDA50

63

M_MDA51

54

M_MDA52

81

M_MDA53

72

M_MDA54

63

M_MDA55

54

M_MDA56

81

M_MDA57

72