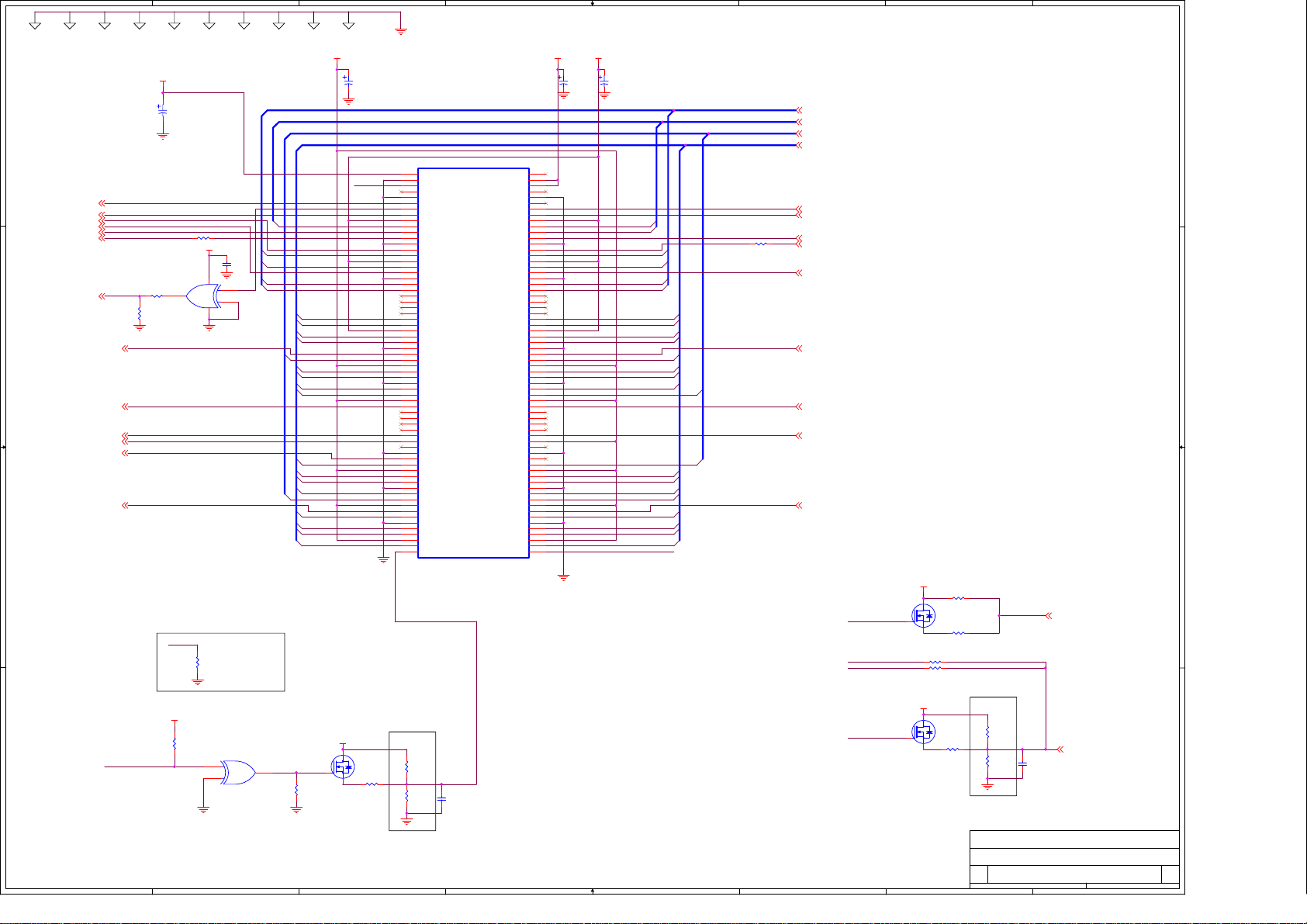

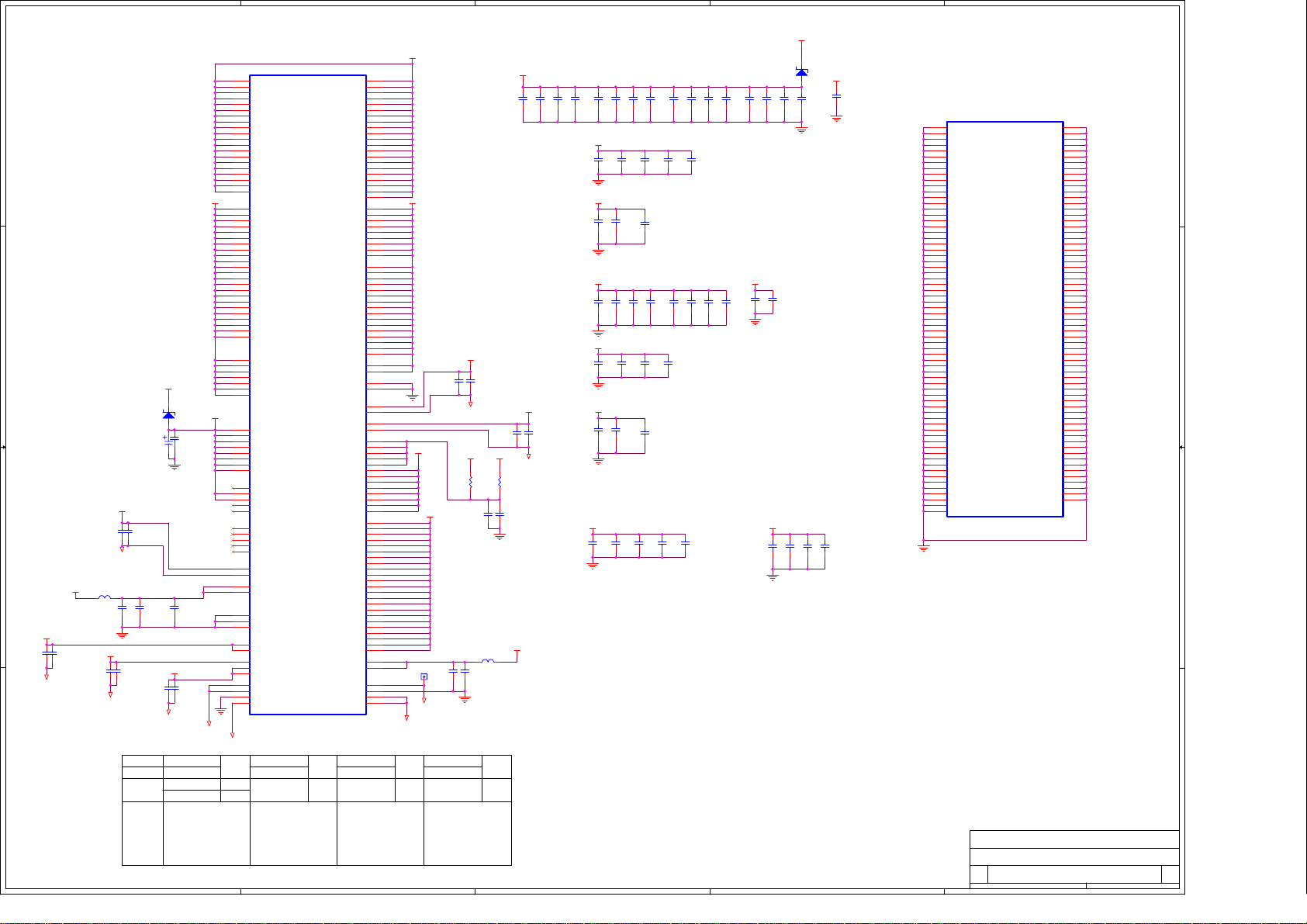

Gigabyte GV-R9200C3-HT REV.1.0 Schematic

5

<Variant Name>

Title

4

3

Schematic No.

2

1

Date:

RV280 AGP8x 32/64/128MB 4/8x16 DDR

GV-R9200C3-HT

REVISION HISTORY

D D

Sch

Rev

0 09/21/02 PRELIMINARY based on RV250 REFERENCE REF109 Schematic and RV250 BGA 958 Schematic

0.1 09/23/02 PRELIMINARY based on the RV280 REFERENCE REF 105-REF112-00A

C C

B B

Date

09/24/02 Copied from 09/24/02 version 0 of 105-ref112-00a RV280 Reference Design

09/25/02 Ready for design review. open issues listed below.

9/27/02 MVDD circuit changed to linear, based on 988 brd.

10/01/02 QSMA4/5 corrected.

10/04/02

- pg1 Add AGP8X cold boot pull-ups

- pg9,10 Move DQM Memory Termination Resistor close to ASIC

John Digweed updated the ASIC to 215R78ANA11H09/25/02

- (pg 1) Rearrange XOR gates, eliminate single AND gate

- (pg 1) Rename AGP_AD_STB1# to AGP_AGPREF (cold boot fix)

- (pg 6) Remove A2VDD option from +MVDDQ

- (pg 7) Add resistor to disable microswitch

Branch from filename 105-A06200-00A netlisted_1002, renamed part refs to match 105-988000-00A10/03/02

- (pg 1) Add TXVSSR ground symbol connected to digital GND

- (pg 1) Change VDDQ_BUS cap to 47uF tant

- (pg 1) Remove VREFGC fixed resistor/capacitor circuit, change R91 to 1K

- (pg 1) Change value of C76 capacitor (AGP_AGPREF)

- (pg 4) Replace 1uF cap on TXVDDR to 100pF and 100nF X7R caps

- (pg 4) Replace 10uF cap on A2VDD to 22uF electrolitic or 10uF tantalum cap

- (pg 4) Add 10nF capacitor arrray on +VDDQ_BUS

- (pg 5) Update VDDC Alt1 regulator circuits

- (pg 14) Change 0R for chassis and digital ground to 805 resistors

- (pg 1) Removed AGP 8x Cool Boot Fix

- (pg 1) Removed Q8, R87 for AGP_REFCG

REVISION DESCRIPTION

10/18/02 - (pg.1) added R84, R85 to comply with AGP 3.0 Spec Rev 1.0, AGPVref provision

11/15/02 - (pg. 1) Remove AGP series resistors

1

- (pg.11) added C6, C7, C9 on MVDDQ and MVDDC

- (pg. 1) Add AGPVREFCG circuit isolated from AGPVREFGC

- Change all 1.0uF Y5V caps to 100nF X7R caps

- Remove R34, C74, C75

- Change C20 footprint to 805

- Change C2, C5, C8, C52, C54, C55, C57, C59,

C61, C63, C66, C67, C126, C130, C1035 footprint

- Layout: Move R265 and R268 close to the ASIC ball

星期一, 七月

26, 2004

Rev

1.0

10/07/02 - (pg 1) C2, C5, C8 changed to 100 uF Alu Elec for cost savings. (p/n 4260110700)

10/08/02

10/08/02 - (pg.4) Added C83 to +VDDC_CT

10/09/02 - (pg.9/10) Rearranged Resistor Packs to facilitate layout

10/10/02 - (pg.1) U4 added to replace U6D gate. Facilitates layout.

A A

- (pg 11) C281-286 changed to 22uF Alu Elec for cost savings. (p/n 4260022600)

- (pg.6) MPVDD regulator removed. Derived from VDD_CT through B24. (moved to pg.4)

- (pg.11) Reduced decoupling capacitors C221..C280 to C221..236 and changed value to 100 nF. (Layout cannot fit all)

- (pg.4) Updated caps (add/remove) according to layout efforts on A058

- (pg. 6) MPVDD regulator added back. Should be DNI

- (pg.9/10) Rpacks changed from 22R to 56R

- (pg.12) Slim VGA changed to regular. DVI-i circuit removed.

- (pg.10) RPacks 167 to 174 flipped L-R (pin 1-8, 2-7, 3-6, 4-5)10/11/02

- (pg.11) Bytes swapped on Channel B data bus and M_QSB, M_DQMB. M_MDB[0:7] <=> M_MDB_[8:15], M_MDB[16:23] <=> M_MDB[24:31]

- (pg.1) Fixed short between 5VBus and AGP_MB_8X_DET#

- (pg.9,10) RPacks 126, 188, 189 pins moved for layout.10/15/02

- (pg. 13) J8 RCA connector added for footprint, to overlap with Svideo

- (pg.11) added C237-C244 on MVDDQ10/16/02

5

4

3

Layout Begins

EASY BOM created

2

1

8

GND_TXVSSR

+12V_BUS

C10 place at the AGP connector

C10

180/6

10U/12/Y/16V/S/X

4239010600

DNI

R3

100/6

3

U6A

R4

SN74ACT86D

COMMON

AGP_GC_8X_DET#

+3.3V_BUS

D D

AGP_INTR#2

AGP_GNT#2

AGP_WBF#2

AGP_SB_STB#2

AGP_MB_8X_DET#2

AGP_DBI_HI2

AGP_AD_STB1#2

AGP_FRAME#2

AGP_TRDY#2

AGP_AD_STB0#2

AGP_STOP#2

AGP_PAR2

AGP_RESET#

AGP_MB_8X_DET#

AGP_RESET#2,19

C C

B B

A A

R83 0/6

+5V_BUS

147

R81

0/6/S

R90

47K/6

13

12

7

C11

0.1U/6/Y/25V

X7R

1

2

U6D

SN74ACT86D

6

The following grounds should be routed back to their respective regulators and then t ied directly to the ground plane wit h one

GND_RSET

GND_R2SETGND_PVSSGND_MPVSSGND_AVSSQGND_AVSSNGND_A2VSSN GND_A2VSSQGND_TPVSS

C2

100U/D/10V/57

4261010700

Biggest footprint

AGP_GC_8X_DET#

AGP_ST1

AGP_SBA1

AGP_SBA3

AGP_SBA5

AGP_SBA7

AGP_AD30

AGP_AD28

AGP_AD26

AGP_AD24

AGP_C/BE#3

AGP_AD22

AGP_AD20

AGP_AD18

AGP_AD16

AGP_AD15

AGP_AD13

AGP_AD11

AGP_AD9

AGP_C/BE#0

AGP_AD6

AGP_AD4

AGP_AD2

AGP_AD0

+VDDQ_BUS

32

2N7002/SOT23

TEST

11

R91

1K/6/S

1

Q10

R92 147/6/1

via: GND_PVSS, GND_MPVSS, GND_TPVSS, and GND_A2VSSN. The other ground pins (GND_AVSSN, GND_A2VSSQ,

GND_RSET, GND_R2SET) should be tied to the ground plane directly through one via as close to the pins as possible

without connecting to anything else. If space is an issue it is possible to use one via for two adjacent pins.

Use 47uF Tant. 16V 20% D size (P/N 4230047600),

800mR Max. ESR and Max. ripple 430mA @ 100kHz

or

100uF, Alum. 6.3V 20% 6.3mm dia (P/N 4261010700),

440mR Max. ESR and Max. ripple 230mA @ 100kHz

or

47uF, Alum. 6.3V 20% 5mm dia (P/N 4262047600),

760mR Max. ESR and Max. ripple 150mA @ 100kHz

MAGP1

A1

12V

A2

TYPEDET#

A3

GC_DET#/RESEVED

A4

USB-

A5

GND

A6

INTA#

A7

RST#

A8

GNT#

A9

VCC3.3

A10

ST1

A11

MB_DET#/RESERVED

A12

DBI_HI/PIPE#

A13

GND

A14

WBF#

A15

SBA1

A16

VCC3.3

A17

SBA3

A18

SB_STB#

A19

GND

A20

SBA5

A21

SBA7

A22

KEY

A23

KEY

A24

KEY

A25

KEY

A26

AD30

A27

AD28

A28

VCC3.3

A29

AD26

A30

AD24

A31

GND

A32

AD_STB1#

A33

C/BE3#

A34

VDDQ

A35

AD22

A36

AD20

A37

GND

A38

AD18

A39

AD16

A40

VDDQ

A41

FRAME#

A42

KEY

A43

KEY

A44

KEY

A45

KEY

A46

TRDY#

A47

STOP#

A48

PME#

A49

GND

A50

PAR

A51

AD15

A52

VDDQ

A53

AD13

A54

AD11

A55

GND

A56

AD9

A57

C/BE0#

A58

VDDQ

A59

AD_STB0#

A60

AD6

A61

GND

A62

AD4

A63

AD2

A64

VDDQ

A65

AD0

A66

VREFGC

UNIVERSAL AGP BUS

AGP_VREFGC

R_AGP8X must be 1%

resistor to provide

350mV +/- 5% on Vref

R_AGP8X

R93

332/6/1

C19

R94

0.01U/6/X/25V

100/6/1

OVRCNT#

USB+

INTB#

REQ#

VCC3.3

RBF#

DBI_LO/RESERVED

SBA0

VCC3.3

SBA2

SB_STB

SBA4

SBA6

AD31

AD29

VCC3.3

AD27

AD25

AD_STB1

AD23

VDDQ

AD21

AD19

AD17

C/BE2#

VDDQ

IRDY#

DEVSEL#

VDDQ

PERR#

SERR#

C/BE1#

VDDQ

AD14

AD12

AD10

VDDQ

AD_STB0

VDDQ

VREFCG

5

+3.3V_BUS+5V_BUS+VDDQ_BUS

C8

C5

100U/D/10V/57

100U/D/10V/57

>=6.3V

>=6.3V

DNIDNI

B1

B2

5.0V

B3

5.0V

B4

B5

GND

B6

B7

CLK

B8

B9

B10

ST0

B11

ST2

B12

B13

GND

B14

B15

B16

B17

B18

B19

GND

B20

B21

B22

KEY

B23

KEY

B24

KEY

B25

KEY

B26

B27

B28

B29

B30

B31

GND

B32

B33

B34

B35

B36

B37

GND

B38

B39

B40

B41

B42

KEY

B43

KEY

B44

KEY

B45

KEY

B46

B47

B48

B49

GND

B50

B51

B52

B53

B54

B55

GND

B56

B57

AD8

B58

B59

B60

AD7

B61

GND

B62

AD5

B63

AD3

B64

B65

AD1

B66

AGP_ST0

AGP_ST2

AGP_SBA0

AGP_SBA2

AGP_SBA4

AGP_SBA6

AGP_AD31

AGP_AD29

AGP_AD27

AGP_AD25

AGP_AD23

AGP_AD21

AGP_AD19

AGP_AD17

AGP_C/BE#2

AGP_C/BE#1

AGP_AD14

AGP_AD12

AGP_AD10

AGP_AD8

AGP_AD7

AGP_AD5

AGP_AD3

AGP_AD1

AGP_AGPREF

4

AGP_SBA[7..0]

AGP_ST[2..0]

AGP_C/BE#[3..0]

AGP_AD[31..0]

R86 0/6

3

AGP_SBA[7..0] 2

AGP_ST[2..0] 2

AGP_C/BE#[3..0] 2

AGP_AD[31..0] 2

AGP_AGP/PCICLK 2

AGP_REQ# 2

AGP_RBF# 2

AGP_DBI_LO 2

AGP_SB_STB 2

AGP_AD_STB1 2

AGP_IRDY# 2

AGP_DEVSEL# 2

AGP_AD_STB0 2

TEST

AGP_AGPREF

AGP_VREFGC

TEST

+VDDQ_BUS

1

R84 0/6/X

R85 0/6/X

+VDDQ_BUS

1

R88 137/6/1

32

Q9

2N7002/SOT23

R89 71.5/6/1

32

2N7002/SOT23

Q11

R95 147/6/1

2

R_AGP8X must be 1%

resistor to provide

350mV +/- 5% on Vref

R_AGP8X

R96

332/6/1

R97

100/6/1

AGP_AGPTEST

Keep stubs short

C21

0.01U/6/X/25V

1

AGP_AGPTEST 2

AGP_AGPREFCG 2

26, 2004

GIGABYTE

AGP Bus 8X

GV-R9200C3-HT

119

1

1.0

UNIVERSAL VREFGC CIRCUIT (2X, 4X, 8X)

8

7

6

5

4

3

Title

Size Document Number Rev

Custom

星期一, 七月

Date: Sheet of

2

5

4

3

2

1

Model Name :

GV-R9200C3-HT

Revision 1.0

D D

Component value change history

1.0A

MODE

03/15 Initial Version

Change Item ReasonBOM Rev Date

Modify From

9VR92B3-HT-10C

Change Memory 64M=>128M

05/141.0A For PVT BOM

1.0B 05/27 For F ab12 ASIC

1.0B 06/01

C C

改為蜂巢包裝

Circuit or PCB layout change for

next version history

PCB Rev

Date Change Item Reason

B B

A A

GIGABYTE

Title

BOM & PCB Modify History

Size Document Number Rev

C

星期一, 七月

5

4

3

2

Date: Sheet of

GV-R9200C3-HT

26, 2004

1

11

1.0

8

AGP_RESET#1,19

AGP_DEVSEL#1

AGP_IRDY#1

AGP_FRAME#1

AGP_AD_STB01

AGP_AD_STB11

AGP_SB_STB1

AGP_SBA[7..0]1

AGP_REQ#1

AGP_GNT#1

AGP_PAR1

AGP_STOP#1

AGP_TRDY#1

AGP_INTR#1

AGP_WBF#1

AGP_RBF#1

8

AGP_AD[31..0]

AGP_C/BE#[3..0]

R36 0/6

AGP_ST[2..0]

C20

0.1U/6/Y/25V

A_R/C_DAC217

A_G/Y_DAC217

A_B/COMP_DAC217

A_HSYNC_DAC217

Y2

27 MHz/D/20PF/20PPM

2 1

C73

22P/6/N/50V/X

DNI

AGP_SBA[7..0]

OSC_IN

AGP_AD[31..0]1

D D

AGP_C/BE#[3..0]1

AGP_AGP/PCICLK1

C C

AGP_ST[2..0]1

AGP_AGPREFCG1

B B

AGP_AGPTEST1

To update:

XTAL to 10 ppm

A A

AGP_SB_STB#1

AGP_AD_STB0#1

AGP_AD_STB1#1

AGP_MB_8X_DET#1

AGP_DBI_HI1

AGP_DBI_LO1

TP8

C1205 22P/6/N/50V

R1115

1M/6

C1206 22P/6/N/50V

7

AGP_ST0

AGP_ST1

AGP_ST2

GND_R2SET

7

AGP_AD0

AGP_AD1

AGP_AD2

AGP_AD3

AGP_AD4

AGP_AD5

AGP_AD6

AGP_AD7

AGP_AD8

AGP_AD9

AGP_AD10

AGP_AD11

AGP_AD12

AGP_AD13

AGP_AD14

AGP_AD15

AGP_AD16

AGP_AD17

AGP_AD18

AGP_AD19

AGP_AD20

AGP_AD21

AGP_AD22

AGP_AD23

AGP_AD24

AGP_AD25

AGP_AD26

AGP_AD27

AGP_AD28

AGP_AD29

AGP_AD30

AGP_AD31

AGP_C/BE#0

AGP_C/BE#1

AGP_C/BE#2

AGP_C/BE#3

AGP_SBA0

AGP_SBA1

AGP_SBA2

AGP_SBA3

AGP_SBA4

AGP_SBA5

AGP_SBA6

AGP_SBA7

R40 715/6/1

A_VSYNC_DAC217

CRT2DDCCLK15

CRT2DDCDAT15

R33

1K/6/S

TESTEN

W29

W28

AA29

AA28

AF29

AG30

AE29

AG28

AF28

AF27

AJ26

AH25

AC29

AB26

AE27

AD26

AC25

AC26

AA25

AA26

AD28

AD29

AC28

AB25

AG27

AB28

AB29

AJ21

AJ22

AK22

AK21

AG25

AF25

AF23

AG24

AG29

AH29

AJ28

AJ29

AH26

AJ27

K27

L26

L25

L27

M25

M26

N26

N25

R26

R25

T26

T25

U26

U25

U27

V26

M28

N29

N28

P29

P28

R29

R28

T28

V29

V28

Y29

Y28

P27

V25

M29

T29

K29

K28

L29

L28

P25

U29

Y25

Y26

P26

U28

H29

H28

J29

J28

6

U1A

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

AD8

AD9

AD10

AD11

AD12

AD13

AD14

AD15

AD16

AD17

AD18

AD19

AD20

AD21

AD22

AD23

AD24

AD25

AD26

AD27

AD28

AD29

AD30

AD31

C/BEb0

C/BEb1

C/BEb2

C/BEb3

PCICLK

RSTb

REQb

GNTb

PAR

STOPb

DEVSELb

TRDYb

IRDYb

FRAMEb

INTAb

WBFb

NC19

NC18

RBFb

AD_STBF0

AD_STBF1

SB_STBF

SBA0

SBA1

SBA2

SBA3

SBA4

SBA5

SBA6

SBA7/IDSEL

ST0

ST1

ST2

SB_STBS

AD_STBS0

AD_STBS1

AGPREF

AGPTEST

AGP8X_DETb

DBI_HI

DBI_LO

R2SET

C_R

Y_G

COMP_B

H2SYNC

V2SYNC

CRT2DDCCLK

CRT2DDCDAT

NC34

NC33

XTALIN

XTALOUT

TESTEN

STEREOSYNC

RV280

STEREOSYNC

6

Part 1 of 5

PCI/AGPAGP2XCLK

AGP4X/8X

SSC DAC2

GPIO0

GPIO1

GPIO2

GPIO3

GPIO4

GPIO5

GPIO6

GPIO7

GPIO8

GPIO9

GPIO10

GPIO11

GPIO12

GPIO13

GPIO14

GPIO15

GPIO16

ROMCSb

DVOMODE

ZV_LCDDATA0

ZV_LCDDATA1

ZV_LCDDATA2

ZV_LCDDATA3

ZV_LCDDATA4

ZV_LCDDATA5

ZV_LCDDATA6

ZV_LCDDATA7

ZV_LCDDATA8

ZV_LCDDATA9

ZV_LCDDATA10

ZV_LCDDATA11

EXT TMDS / GPIO /

ROM

ZV_LCDDATA12

ZV_LCDDATA13

ZV_LCDDATA14

ZV_LCDDATA15

ZV_LCDDATA16

ZV_LCDDATA17

ZV_LCDDATA18

ZV_LCDDATA19

ZV_LCDDATA20

ZV_LCDDATA21

ZV_LCDDATA22

ZV_LCDDATA23

ZV_LCDCNTL0

ZV_LCDCNTL1

ZV_LCDCNTL2

ZV_LCDCNTL3

NC35

NC27

NC36

NC28

NC37

NC29

NC39

NC31

NC38

NC30

NC22

NC13

NC23

NC14

NC24

NC15

NC26

NC17

NC25

NCSTMDSDAC1

NC16

NC7

NC8

DPLUS

DMINUS

TX0M

TX0P

TX1M

TX1P

TX2M

TX2P

TXCM

TXCP

DVIDDCCLK

DVIDDCDATA

HPD

HSYNC

VSYNC

RSET

VGADDCDATA

VGADDCCLK

AUXWIN

STEREOSYNC 7

R

G

B

5

AJ5

AK4

AJ4

AF4

AG4

AH4

AK3

AJ3

AH3

AG3

AF3

AJ2

AH2

AG2

AF2

AH1

AG1

AH5

AE10

AF5

AE6

AF6

AE7

AG6

AF7

AG8

AF8

AE8

AE9

AF9

AG9

AK7

AJ7

AH8

AJ8

AH9

AJ9

AK9

AH10

AK10

AJ10

AH11

AJ11

AK6

AJ6

AH6

AH7

AE15

AF15

AE16

AF16

AG15

AH15

AH16

AH17

AF17

AG17

AJ17

AH18

AK18

AJ18

AG19

AH19

AJ16

AK16

AH20

AJ20

AF11

AE12

AF10

AE11

AJ13

AH13

AJ14

AH14

AJ15

AK15

AK12

AK13

AF13

AE13

AF12

AK25

AJ25

AK24

AH28

AH27

AJ23

AG26

AF26

AE25

5

VID0

VID1

VID2

VID3

VID4

VID5

VID6

VID7

VID/DVO12

VID/DVO13

VID/DVO14

VID/DVO15

R39 499/6/1

GND_RSET

TP10

GPIO0

GPIO1

GPIO2

GPIO3

GPIO4

GPIO5

GPIO6

GPIO7

GPIO8

GPIO9

GPIO10

GPIO11

GPIO12

GPIO13

GPIO14

GPIO15

GPIO16

ROMCS#

DVOMODE

VID[7..0]

VID/DVO16

VID/DVO17

VID/DVO18

VID/DVO19

VID/DVO20

TMDS_TX0N 16

TMDS_TX0P 16

TMDS_TX1N 16

TMDS_TX1P 16

TMDS_TX2N 16

TMDS_TX2P 16

TMDS_TXCN 16

TMDS_TXCP 16

DVIDDCCLK 15

DVIDDCDATA 15

CHARGE_POW 15

TP7

4

VID[7..0] 19

VSYNC

VGADDCDATA

VGADDCCLK

4

GPIO[13..0]

R1280 10K/6/S/X

R986

10K/6/S

24bit-SDR-DVO

DC_Strap1 8

DC_Strap2 8

DC_Strap3 8

DC_Strap4 8

GPIO[13..0] 7,8

Mem_Strap2 7

Mem_Strap1 7

Mem_Strap0 7

ROMCS# 8

+VDDC_CT

A_R_DAC1 12

A_G_DAC1 12

A_B_DAC1 12

A_HSYNC_DAC1 12

A_VSYNC_DAC1 12

CRT1DDCDATA 12

CRT1DDCCLK 12

RSET

R2SET

3

THE VALUES OF RSET AND R2SET SHOWN IN THE TABLE MAY BE

APPROXIMATE VALUES ONLY (SUITABLE FOR PROTOTYPING)

BEFORE GOING INTO PRODUCTION,CONTACT YOUR ATI

499R

REPRESENTATIVE FOR THE RSET/R2SET VALUES QUALIFIED FOR

715R

MASS PRODUCTION

LCDDATA16 7

LCDDATA17 7

PAL/NTSC 8

DC_Strap5 8

LCDDATA20 7,19

VHAD1 19

VPHCTL 19

VIPCLK 19

VPCLK 19

STEREOSYNC

VGADDCDATA

VGADDCCLK

VSYNC

TESTEN

TDO

TDI

TMS

TCK

TRST

2

TP1

TP2

OPTION BOUNDARY

TP3

SCAN WITH TESTEN

TP4

TP5

1

Some Part Ref's updated to 988 brd

Title

Size Document Number Rev

Custom

星期一, 七月

3

Date: Sheet

2

GIGABYTE

RV280 Core

26, 2004

GV-R9200C3-HT

1.0

of

219

1

5

D D

4

3

2

1

MEMORY CHANNEL A

QSA[7..0]9

DQMA#[7..0]9

MAA[13..0]9

MDA[63..0]9

C C

B B

A A

QSA[7..0]

DQMA#[7..0]

MAA[13..0]

MDA[63..0]

MDA0

MDA1

MDA2

MDA3

MDA4

MDA5

MDA6

MDA7

MDA8

MDA9

MDA10

MDA11

MDA12

MDA13

MDA14

MDA15

MDA16

MDA17

MDA18

MDA19

MDA20

MDA21

MDA22

MDA23

MDA24

MDA25

MDA26

MDA27

MDA28

MDA29

MDA30

MDA31

MDA32

MDA33

MDA34

MDA35

MDA36

MDA37

MDA38

MDA39

MDA40

MDA41

MDA42

MDA43

MDA44

MDA45

MDA46

MDA47

MDA48

MDA49

MDA50

MDA51

MDA52

MDA53

MDA54

MDA55

MDA56

MDA57

MDA58

MDA59

MDA60

MDA61

MDA62

MDA63

QSB[7..0]10

DQMB#[7..0]10

MAB[13..0]10

R265

499/6/1

sterm

R268

499/6/1

sterm

MDB[63..0]10

+VREF

U1B

RV280

DQA1

DQA2

DQA3

DQA4

DQA5

DQA6

DQA7

DQA8

DQA9

DQA10

DQA11

DQA12

DQA13

DQA14

DQA15

DQA16

DQA17

DQA18

DQA19

DQA20

DQA21

DQA22

DQA23

DQA24

DQA25

DQA26

DQA27

DQA28

DQA29

DQA30

DQA31

DQA32

DQA33

DQA34

DQA35

DQA36

DQA37

DQA38

DQA39

DQA40

DQA41

DQA42

DQA43

DQA44

DQA45

DQA46

DQA47

DQA48

DQA49

DQA50

DQA51

DQA52

DQA53

DQA54

DQA55

DQA56

DQA57

DQA58

DQA59

DQA60

DQA61

DQA62

DQA63

Part 2 of 5

ELPIDA

DQMAb0

DQMAb1

DQMAb2

DQMAb3

DQMAb4

DQMAb5

DQMAb6

DQMAb7

MEMORY

INTERFACE A

G30

F28

F30

E29

D28

D29

D30

K25

K26

J25

J26

G28

G25

G26

G27

C29

B29

B28

C27

C26

B26

C25

B25

E26

F25

E25

F24

E23

D22

F22

E22

C17

B17

C16

B16

C14

B14

C13

B13

E18

F17

E17

D16

F15

E15

F14

E14

A13

C12

A12

B12

C10

B10

C9

B9

E13

F12

E12

F11

E10

F9

E9

F8

AA10

AA11

AA12

AA13

QSA0

QSA1

QSA2

QSA3

QSA4

QSA5

QSA6

QSA7

RASAb

CASAb

WEAb

CSAb0

CSAb1

CKEA

CLKA0

CLKA0b

CLKA1

CLKA1b

CLKAFB

VREF

DIMA0

DIMA1

MAA0

B24G29

AA0DQA0

MAA1

A24

AA1

MAA2

B23

AA2

MAA3

C23

AA3

MAA4

B21

AA4

MAA5

F21

AA5

MAA6

E21

AA6

MAA7

F20

AA7

MAA8

E20

AA8

MAA9

C21

AA9

MAA10

B22

MAA11

C22

MAA12

A25

MAA13

C24

DQMA#0

E28

DQMA#1

H26

DQMA#2

A27

DQMA#3

E24

DQMA#4

B15

DQMA#5

E16

DQMA#6

C11

DQMA#7

E11

QSA0

F29

QSA1

H25

QSA2

B27

QSA3

F23

QSA4

C15

QSA5

F16

QSA6

B11

QSA7

F10

RASA#

A19

CASA#

C18

WEA#

F18

CSA#0

E19

CSA#1

F19

CKEA

B19

CLKA0

C20

CLKA#0

B20

CLKA1

B18

CLKA#1

A18

C19

TP11

+VREF

B8

F26

F13

RASA# 9

CASA# 9

WEA# 9

CSA#0 9

CSA#1 9

CKEA 9

CLKA0 9,11

CLKA#0 9,11

CLKA1 9,11

CLKA#1 9,11

Vref Voltage

+MVDDQ

Re6

Re7

Place close to ASIC ball

Use localized Vref on the memory page

QSB[7..0]

DQMB#[7..0]

MAB[13..0]

MDB[63..0]

MEMORY CHANNEL B

MDB0

MDB1

MDB2

MDB3

MDB4

MDB5

MDB6

MDB7

MDB8

MDB9

MDB10

MDB11

MDB12

MDB13

MDB14

MDB15

MDB16

MDB17

MDB18

MDB19

MDB20

MDB21

MDB22

MDB23

MDB24

MDB25

MDB26

MDB27

MDB28

MDB29

MDB30

MDB31

MDB32

MDB33

MDB34

MDB35

MDB36

MDB37

MDB38

MDB39

MDB40

MDB41

MDB42

MDB43

MDB44

MDB45

MDB46

MDB47

MDB48

MDB49

MDB50

MDB51

MDB52

MDB53

MDB54

MDB55

MDB56

MDB57

MDB58

MDB59

MDB60

MDB61

MDB62

MDB63

B6

C6

B5

C5

B2

C3

C2

D2

E8

E7

D4

D3

F6

F3

F5

G6

D1

E2

F2

F1

G2

H3

H2

J3

G4

H6

H5

J6

K5

K4

L6

L5

U2

V2

V1

V3

W3

Y2

Y3

AA2

AA3

AB2

AB3

AC2

AD1

AD3

AE1

AE2

U6

U5

U3

V6

W5

W4

Y6

Y5

AA6

AA5

AB6

AB5

AD6

AD5

AE5

AE4

U1C

DQB0

DQB1

DQB2

DQB3

DQB4

DQB5

DQB6

DQB7

DQB8

DQB9

DQB10

DQB11

DQB12

DQB13

DQB14

DQB15

DQB16

DQB17

DQB18

DQB19

DQB20

DQB21

DQB22

DQB23

DQB24

DQB25

DQB26

DQB27

DQB28

DQB29

DQB30

DQB31

DQB32

DQB33

DQB34

DQB35

DQB36

DQB37

DQB38

DQB39

DQB40

DQB41

DQB42

DQB43

DQB44

DQB45

DQB46

DQB47

DQB48

DQB49

DQB50

DQB51

DQB52

DQB53

DQB54

DQB55

DQB56

DQB57

DQB58

DQB59

DQB60

DQB61

DQB62

DQB63

RV280

Part 3 of 5

ELPIDA

DQMBb0

DQMBb1

DQMBb2

DQMBb3

DQMBb4

DQMBb5

DQMBb6

DQMBb7

MEMORY

INTERFACE B

CLKB0b

CLKB1b

CLKBFB

MEMVMODE

MEMVMODE1

MEMTEST

AB10

AB11

AB12

AB13

QSB0

QSB1

QSB2

QSB3

QSB4

QSB5

QSB6

QSB7

RASBb

CASBb

WEBb

CSBb0

CSBb1

CKEB

CLKB0

CLKB1

DIMB0

DIMB1

MAB0

J2

AB0

MAB1

K3

AB1

MAB2

K2

AB2

MAB3

L3

AB3

MAB4

L2

AB4

MAB5

M3

AB5

MAB6

M2

AB6

MAB7

N5

AB7

MAB8

M1

AB8

MAB9

M5

AB9

MAB10

N3

MAB11

P2

MAB12

P6

MAB13

P5

DQMB#0

A4

DQMB#1

E3

DQMB#2

G3

DQMB#3

J5

DQMB#4

W2

DQMB#5

AC3

DQMB#6

W6

DQMB#7

AC6

QSB0

B4

QSB1

E5

QSB2

G1

QSB3

K6

QSB4

W1

QSB5

AD2

QSB6

V5

QSB7

AC5

RASB#

R2

CASB#

T5

WEB#

T6

CSB#0

R5

CSB#1

R6

CKEB

R3

CLKB0

N1

CLKB#0

N2

CLKB1

T2

CLKB#1

T3

P3

B7

C7

G5

AE3

C8

R55

47/6

RASB# 10

CASB# 10

WEB# 10

CSB#0 10

CSB#1 10

CKEB 10

CLKB0 10,11

CLKB#0 10,11

CLKB1 10,11

CLKB#1 10,11

TP12

MEMVMODE[1:0] MEMORY IO VOLTAGE

0 1

1 0

1 1

2.5V (DDR)

1.8V (DDR)

3.3V (SDR)

R53

4.7K/6

R51 4.7K/6

R52 4.7K/6/X

DNI

R54

4.7K/6/X

DNI

Default

+VDDC_CT

Title

Size Document Number Rev

Custom

星期一, 七月

5

4

3

2

Date: Sheet of

GIGABYTE

RV280 Mem Interface

GV-R9200C3-HT

26, 2004

1

319

1.0

5

U1D

P18

VDDC

P19

U12

U13

U14

U17

+MVDDQ

+VDDC_CT

GND_A2VSSN

(80mA)

U18

U19

V12

V13

V14

V17

V18

V19

W12

W13

W14

W17

W18

W19

H10

H13

H15

H17

H19

H22

J1

J23

J24

J27

J4

J7

J8

L8

M4

N4

N7

N8

R1

R4

T4

T7

T8

E27

F4

G10

G13

G15

G22

G7

L23

H20

H11

P8

Y8

AC11

AC20

AK19

AE19

AE20

AF20

AG20

AJ19

AF18

AF19

AE18

AE17

AJ12

AH12

AF14

AE14

AG14

AG13

AG12

AF21

AF22

AH21

AF24

AE23

AE21

AE22

AG22

AH22

GND_A2VSSQ

Matching

Ground

AVSSN

(Noisy)

AVSSQ

D D

C C

+3.3V_BUS

D31

MMSZ5521B/2.4V/SOD123/S

2 1

C55

100U/D/10V/57

0.1U/6/Y/25V/S

>=6.3V

X7R

+TPVDD

C58

C57

DNI

4.7U/12/Y/16V/S

>=6.3V

+VDDC_CT

C62

0.1U/6/Y/25V/S

X7R

>=6.3V

Ceramic

Ceramic

B16 200/8/0.2A/S

C59

4.7U/12/Y/16V/S

>=6.3V

Ceramic

+A2VDDQ

C63

4.7U/12/Y/16V

GND_A2VSSQ

B B

+A2VDD

C61

4.7U/12/Y/16V/S

>=6.3V

Ceramic

GND_A2VSSN

A A

0.1U/6/Y/25V/S

X7R

GND_TPVSS

C64

0.1U/6/Y/25V/S

X7R

>=6.3V

Ceramic

Pin Names

Voltage

Usage

Board power

and ground

option(s)

5

DNI

C77

C60

0.1U/6/Y/25V/S

100P/6/N/50V/S/X

X7R

X7R

DNI

+AVDD

C68

C67

0.1U/6/Y/25V/S

4.7U/12/Y/16V

X7R

GND_AVSSN

+AVDD

DAC1 VDD A2VSSQ

DAC1 Band Gap Ref.

AVDD sourced from VDDC_CT

thru bead at least 15 mil trace

and not longer than 1.5 inch.

AVSSN and AVSSQ with single

via to GND close to the pin.

Part 4 of 5

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDR1

Memory I/O Power

VDDR1

(1.8V/2.5V/3.3V)

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

I/O level shift power

(1.8V)

VDDC18

VDDC18

VDDC18

VDDC18

VDDC18

VDDC18

VDDC18

NC

VDDC18

VDDC18

NC

NC

NC

NC

NC

NC

NC

(1.8V)

TMDS PLL TMDS I/O

TPVDD

TPVSS

TXVDDR

TXVDDR

(1.8V)

TXVSSR

TXVSSR

TXVSSR

Analog Display Power,

A2VDD

see table below

A2VDD

A2VDDQ

AVDD

AVDD

A2VSSN

A2VSSN

A2VSSDI

A2VSSQ

RV280

+A2VDD

2.5V1.8V

(120mA)

DAC2 VDD

(1) A2VDD regulated source

and A2VSSN return path routed

with at least 15 mil trace and

not longer than 1.5 inch.

AVSSN with single via to GND

at the regulator.

(2) Sourced from VDD thru bead

instead of the regulator

I/O

POWER

VDDRH0

VDDRH1

VSSRH0

VSSRH1

VDDRH0 - CH A Clock Power

VDDRH1 - CH B Clock PowerAGP Bus I/O Power

(VDDR1)

PLL MPLL

Ext. TMDS/

DVO Power

(1.8V/3.3V)

(3.3V)

GPIO & Ext.

TMDS I/O

Power

(1.5V/3.3V) (1.8V) (1.8V)

AVDDDI

A2VDDDI

+A2VDDQ

Matching

Ground

1.8V

A2VSSN

(Noisy)

DAC2 Band Gap Ref.

Source from AVDD thru bead.

A2VSSQ with sigle via to GND

close to the pin.

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDC

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

VDDR1

MPVDD

MPVSS

PVDD

PVSSVDDC18

VDDR4

VDDR4

VDDR4

VDDR4

VDDR4

VDDR3

VDDR3

VDDR3

VDDR3

VDDR3

VDDR3

VDDR3

VDDR3

VDDP

VDDP

VDDP

VDDP

VDDP

VDDP

VDDP

VDDP

VDDP

VDDP

VDDP

VDDP

VDDP

VDDP

VDDP

VDDP

VDDP

VDDP

VDDP

VDDP

VDDP

VDDP

VDDP

AVSSQ

AVSSDI

AVSSN

AVSSN

4

+VDDC

C52

4.7U/12/Y/16V

>=6.3V

Ceramic

C53

0.1U/6/Y/25V/S

X7R

+3.3V_BUS +VDDC_CT

R1282

R1281

0/8/S/X

0/8/S

C1210

C1209

4.7U/8/Y/10V/S

0.1U/6/Y/25V/S

B17 200/8/0.2A/S

C66

4.7U/12/Y/16V

>=6.3V

Ceramic

Matching

Ground

AVSSDI

A2VSSDI

(Digital)(Quiet)

+VDDC

CP9A

8 1

0.01U/8P4C/X/25V/S

+PVDD

C54

4.7U/12/Y/16V

>=6.3V

Ceramic

GND_PVSS

+VDDC_CT

CP9B

7 2

0.01U/8P4C/X/25V/S

AC13

AC15

AC17

AD13

AD15

M12

M13

M14

M17

M18

M19

N12

N13

N14

N17

N18

N19

P12

P13

P14

P17

+MVDDQ

A15

A21

AA7

AA8

D11

D14

D17

D8

V4

A28

A3

A9

AA1

AA4

AD4

B1

B30

D10

D19

D20

D23

D26

D6

V7

V8

G19

N6

G18

M6

A7

A6

AK27

AK28Y23

AC10

AC9

+3.3V_BUS

AD10

AD9

AG10

AD22

AC22

AC21

AD21

AC19

AD19

AD7

AC8

AA23

AA24

AB27

AB30

AC23

AD27

AE30

AH30

J30

M23

M24

N27

N30

P23

T23

T24

T27

T30

V23

V24

W27

W30

Y27

AH24

AH23

AJ24

AG23

AD24

AE24

GND_AVSSQ

GND_AVSSN

Matching

Ground

(Quiet)

4

C51

0.1U/6/Y/25V

X7R

+VDDQ_BUS

TP9

C65

0.1U/6/Y/25V/S

X7R

+AVDDDI

+A2VDDDI

1.8V

Digital Power for

DAC1 and DAC2

Source from VDDC_CT

thru bead

+MPVDD

GND_MPVSS

3

CP9D

CP3A

CP3C

CP9C

6 3

0.01U/8P4C/X/25V/S

CP3B

5 4

8 1

6 3

7 2

0.01U/8P4C/X/25V/S

+MVDDQ +MVDDQ

+MVDDQ

0.01U/8P4C/X/25V/S

0.01U/8P4C/X/25V/S

0.01U/8P4C/X/25V/S

+VDDC

C27

C26

0.1U/6/Y/25V/S

X7R X7R X7R X7R X7R

0.1U/6/Y/25V/S

+3.3V_BUS

CP1B

CP1A

7 2

8 1

0.01U/8P4C/X/25V/S

0.01U/8P4C/X/25V/S

CP5C

CP5B

CP5A

6 3

7 2

8 1

0.01U/8P4C/X/25V/S

0.01U/8P4C/X/25V/S

0.01U/8P4C/X/25V/S

C32

C33

0.1U/6/Y/25V/S

X7R X7R X7R X7R

0.1U/6/Y/25V/S

+VDDC_CT

CP1C

CP1D

6 3

5 4

0.01U/8P4C/X/25V/S

0.01U/8P4C/X/25V/S

+VDDQ_BUS

C45

C46

0.1U/6/Y/25V

X7R

Distributed around

+VDDQ_BUS plane

3

C47

0.1U/6/Y/25V/S

X7R X7R X7R X7R

0.1U/6/Y/25V/S

CP4A

CP3D

8 1

5 4

0.01U/8P4C/X/25V/S

0.01U/8P4C/X/25V/S

C28

C29

0.1U/6/Y/25V/S

0.1U/6/Y/25V/S

C44

0.1U/6/Y/25V/S

CP5D

CP6A

5 4

8 1

0.01U/8P4C/X/25V/S

0.01U/8P4C/X/25V/S

C34

C35

0.1U/6/Y/25V/S

0.1U/6/Y/25V/S

C83

0.1U/6/Y/25V/SC56

X7R

C48

0.1U/6/Y/25V

CP4B

7 2

0.01U/8P4C/X/25V/S

C30

0.1U/6/Y/25V/S

CP6B

7 2

0.01U/8P4C/X/25V/S

C49

0.1U/6/Y/25V

CP4C

CP4D

6 3

5 4

0.01U/8P4C/X/25V/S

0.01U/8P4C/X/25V/S

CP6C

CP6D

6 3

5 4

0.01U/8P4C/X/25V/S

0.01U/8P4C/X/25V/S

+3.3V_BUS

CP2A

CP2B

CP2C

8 1

7 2

6 3

0.01U/8P4C/X/25V/S

0.01U/8P4C/X/25V/S

0.01U/8P4C/X/25V/S

C38

C39

10U/12/Y/10V/S

10U/12/Y/10V/S

PLACE DIRECTLY

UNDERNEATH CHANNEL

A & B SECTION OF ASIC.

+VDDQ_BUS

CP8A

CP8B

8 1

7 2

0.01U/8P4C/X/25V/S

0.01U/8P4C/X/25V/S

2

D30

MMSZ5521B/2.4V/SOD123/S

+VDDC

2 1

C23

10U/12/Y/10V/S

CP2D

5 4

0.01U/8P4C/X/25V/S

At the corner of VDDC plane

CP8C

CP8D

6 3

5 4

0.01U/8P4C/X/25V/S

0.01U/8P4C/X/25V/S

2

1

U1E

F27

VSS

F7

G12

G16

G21

G24

G9

H12

H14

H16

H18

H21

H23

H27

H4

H8

H9

K1

K23

K24

K30

K7

K8

L4

M15

M16

M27

M30

M7

M8

N15

N16

N23

N24

P15

P16

P4

R12

R13

R14

R15

R16

R17

R18

R19

R23

R24

R27

R30

R7

R8

T1

T12

T13

T14

T15

T16

T17

T18

T19

W23

W24

W25

W26

W7

W8

Y4

RV280

Part 5 of 5

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

CORE

GND

Title

Size Document Number Rev

Custom

星期一, 七月

Date: Sheet of

26, 2004

U15

VSS

U16

VSS

U23

VSS

U4

VSS

U8

VSS

V15

VSS

A10

VSS

A16

VSS

A2

VSS

A22

VSS

A29

VSS

AA27

VSS

AA30

VSS

AB1

VSS

AB23

VSS

AB24

VSS

AB4

VSS

AB7

VSS

AB8

VSS

AC12

VSS

AC14

VSS

AC16

VSS

AC18

VSS

AC27

VSS

AC4

VSS

AD12

VSS

AD16

VSS

AD18

VSS

AD25

VSS

AD30

VSS

AE26

VSS

AE28

VSS

AG11

VSS

AG16

VSS

AG18

VSS

AG21

VSS

AG5

VSS

AG7

VSS

AJ1

VSS

AJ30

VSS

AK2

VSS

AK29

VSS

B3

VSS

C1

VSS

C28

VSS

C30

VSS

C4

VSS

D12

VSS

D13

VSS

D15

VSS

D18

VSS

D21

VSS

D24

VSS

D25

VSS

D27

VSS

D5

VSS

D7

VSS

D9

VSS

E4

VSS

E6

VSS

V16

VSS

V27

VSS

V30

VSS

W15

VSS

W16

VSS

GIGABYTE

RV280 Power

GV-R9200C3-HT

1

419

1.0

Loading...

Loading...