Page 1

5

4

3

2

1

E

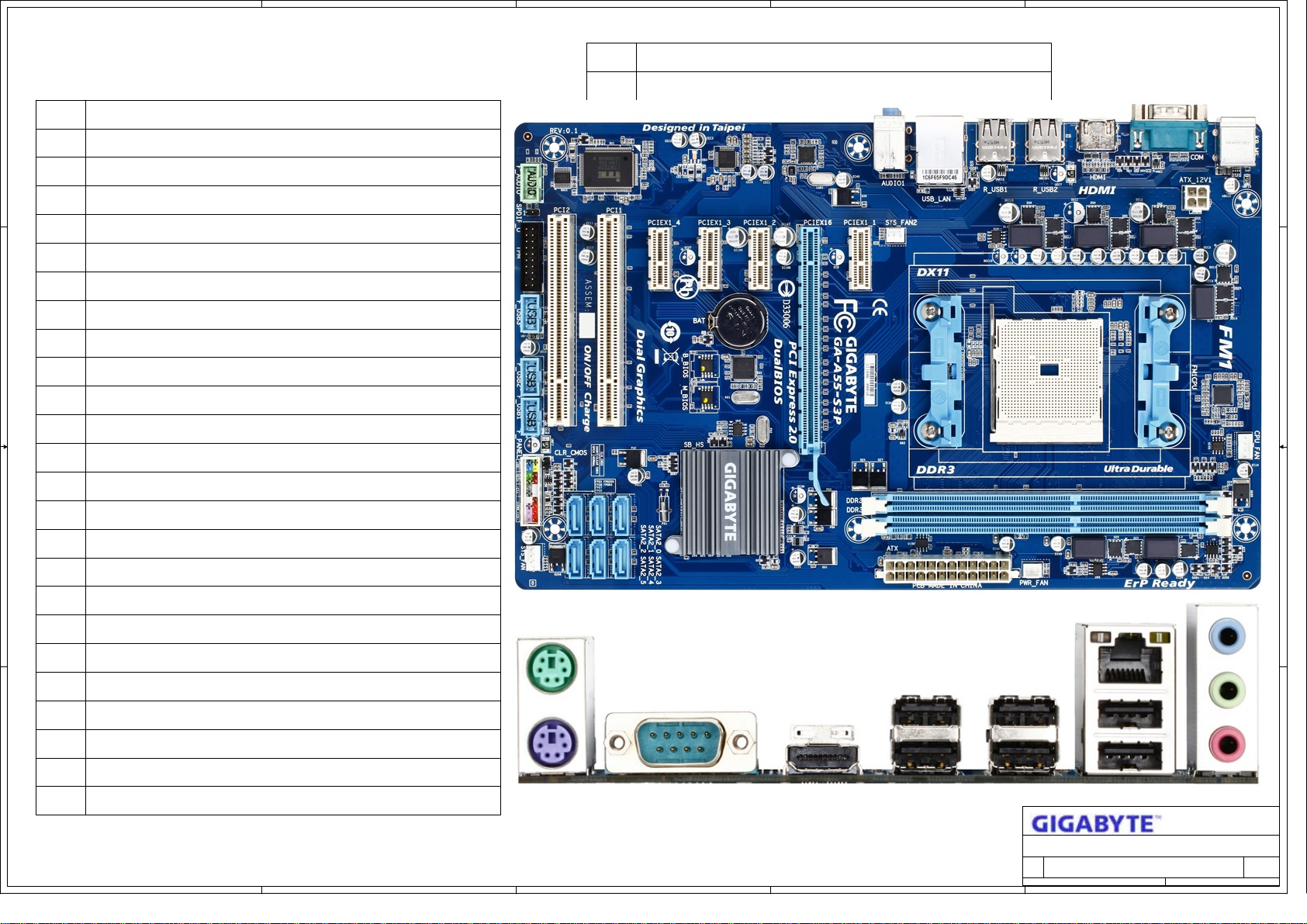

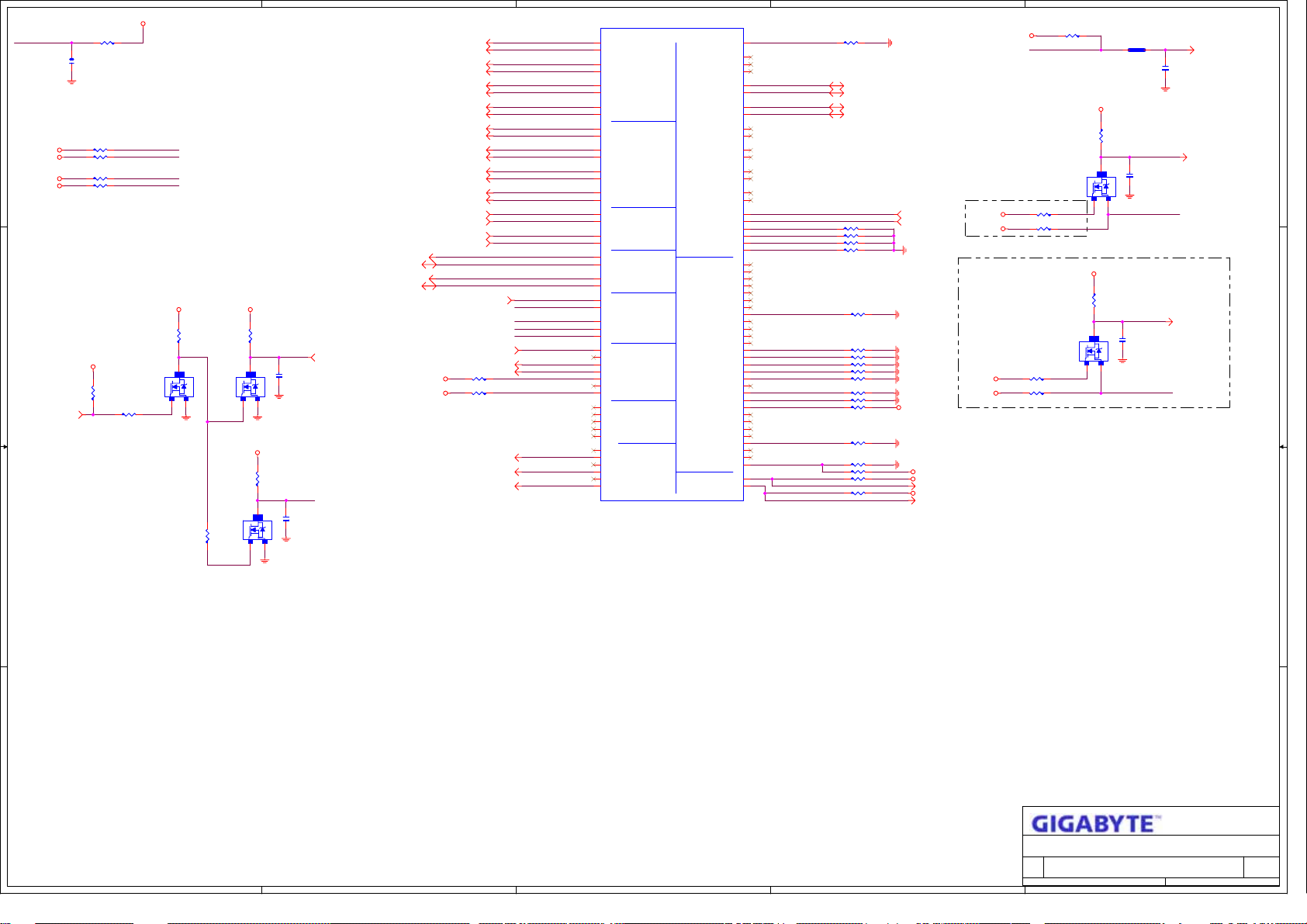

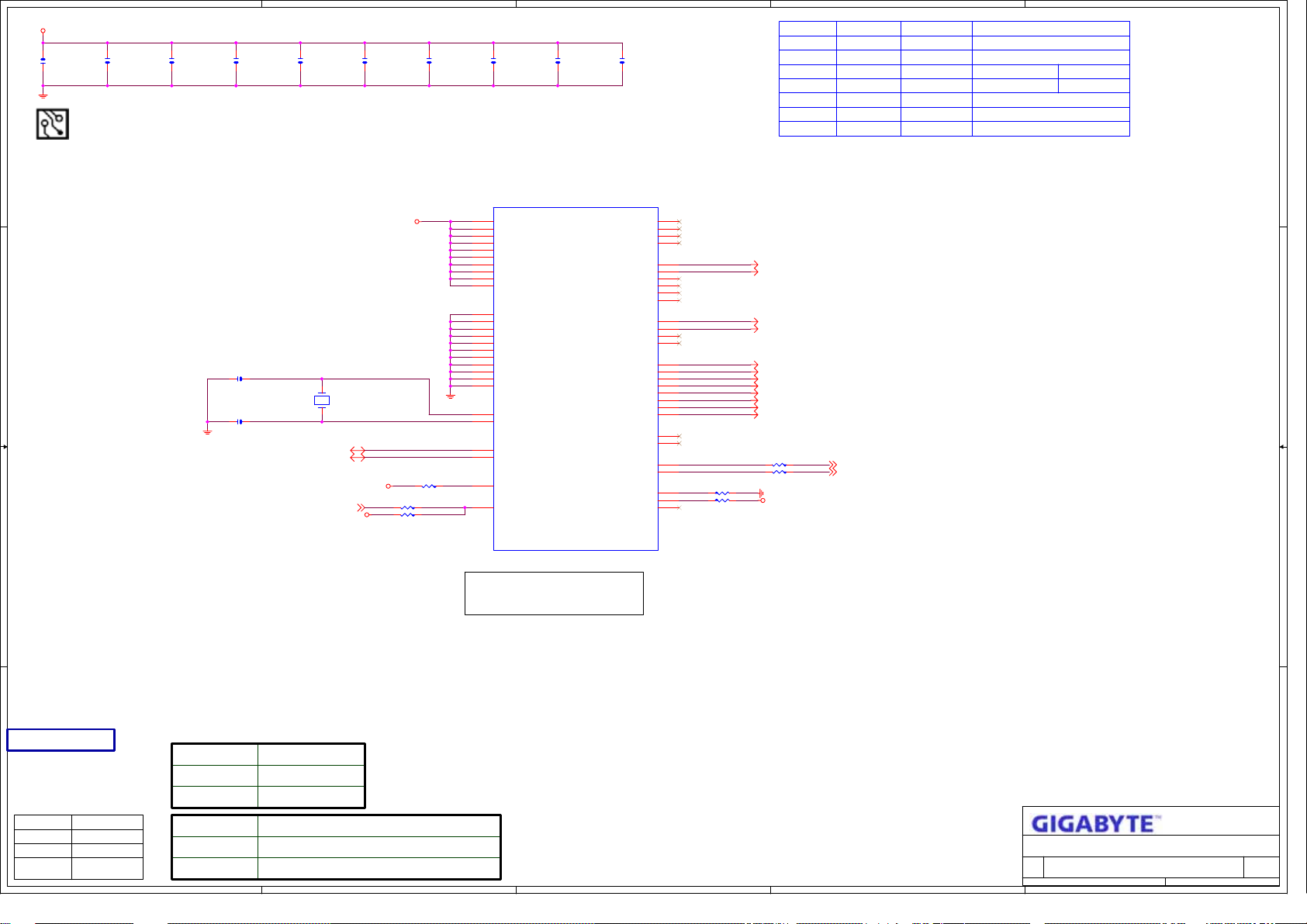

GA-A55M-DS2

PAGE

D D

01 COVER SHEET

02

03

04

05

06

07

08

C C

09

10

11

12

13

TITLE

BOM & PCB MODIFY HISTORY

BLOCK DIAGRAM

APU DDRIII MEMORY

APU CONTROL

APU UMI, GFX, GPP

APU POWER & GND

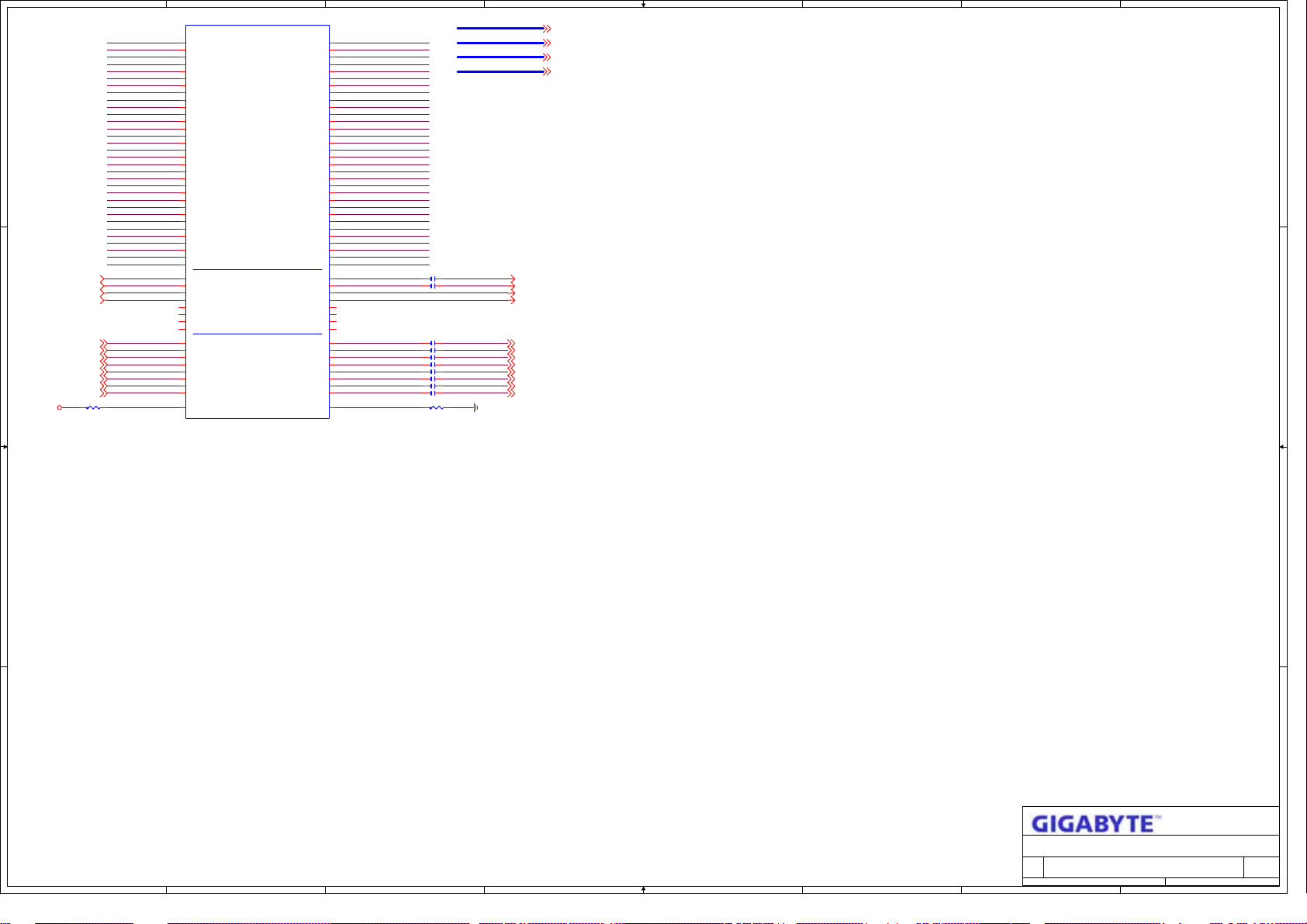

DDRIII CHANNEL A

RTM880T-792

HUDSON UMI, PCIE, PCI, CPU, LPC

HUDSON ACPI, GPIO, USB, AUDIO

HUDSON SATA,SPI,HWM

HUDSON POWER & GND

Revision : 1.01

26

TITLEPAG

ARTHEROS AR8161/AR8151

DVI27

14

15

B B

16

17

18

19

20

21

22

23

A A

24

25

APU_VDDIO_SUS=DDR15V

APU_VTT_SUS=DDRVTT

APU_VDDP_RUN=APU_VDDR_RUN=APU_VDDP

PCIE x16 , x1

PCI SLOT

ITE 8728 , Dual-BIOS , KB/MS

COM , F_USB ,RGB

FAN , HWMO , R_USB

VT1708S CODEC

AUDIO JACK

ATX, FRONT PANEL

POWER S

EQUENCE

VCORE (PWMISL6324A+6609A)

VCC_SB , APU_VDDPA , VCC11_DUAL , VDDA25

DDR POWER, VCC18 , EUP

+1.1V_RUN=FCH_VDD_11_RUN=VCC_SB

+3.3V_RUN=VCC3

+3.3V_ALW=3VDUAL

5

4

Title

COVER SHEET

Size Document Number Rev

Custom

3

2

Date: Sheet

GA-A55M-DS2 1.01

1

127Tuesday, August 23, 2011

of

Page 2

5

4

3

2

1

Model Name:GA-A55M-DS2

Component value change history

D D

Change ItemDate

2011.07.04 0.1 New BOM release PCB:0.1 Modify from GA-A55M-S2V Rev1.0

Change ARTHEROS AR8151 ,Codec VT1708S2011.08.03 1.0A BOM release PCB:1.0

2011.08.08 1.0B BOM release PCB:1.01 ARTHEROS AR8151 All Ref GND plane

2011.08.23 1.0C BOM release PCB:1.01 Codec for Anti4 ,

C C

轉

P-BOM

Reason

Version: 1.01

P-Code: U98126-0

Circuit or PCB layout change for next version

ReasonDate Change Item

2011.07.01 Modify from GA-A55M-S2V Rev1.0Rev 0.1 Gerber-out

2011.08.02 Rev 1.0 Gerber-out Change ARTHEROS AR8151 ,Codec VT1708S

2011.08.05 Rev 1.01 Gerber-out ARTHEROS AR8151 All Ref GND plane

B B

A A

Title

BOM & PCB HISTORY

Size Document Number Rev

Custom

5

4

3

2

Date: Sheet

GA-A55M-DS2 1.01

227Tuesday, August 23, 2011

1

of

Page 3

5

4

3

2

1

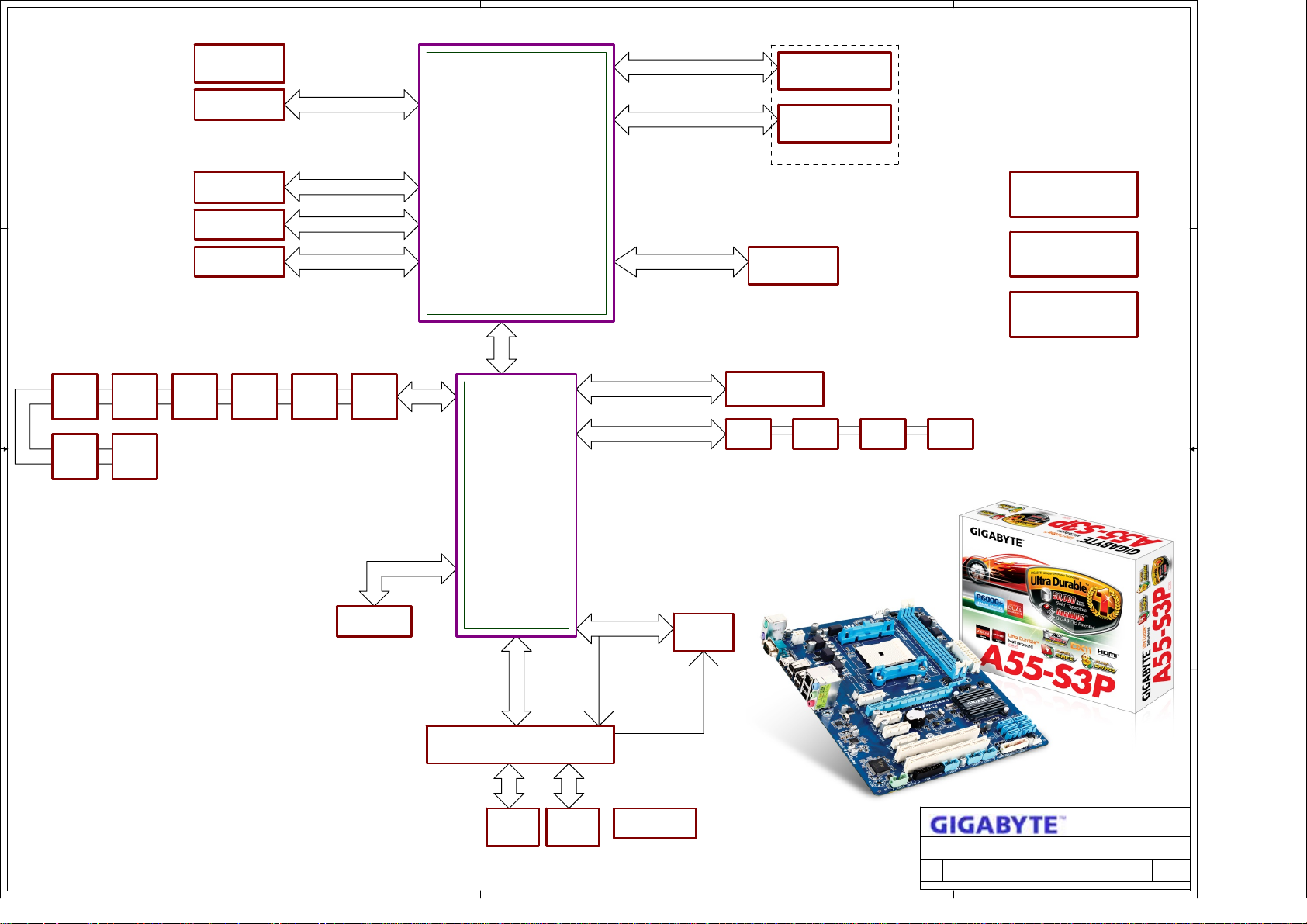

AMD Fusion Hudson CUSTOMER DESKTOP REFERENCE DESIGN

Clock

Generator

RTM880T-792

DVI(DP0)

D D

9

27

AMD APU

1 X16 PCIE VIDEO I/F

1 X4 PCIE I/F WITH

DX11 IGP

DDRIII 1066,1333, 1600, 1866

128bit

DDRIII 1066,1333, 1600, 1866

UNBUFFERED

DDRIII DIMM1

UNBUFFERED

DDRIII DIMM2

DDRIII FIRST LOGICAL DIMM

8

8

RGB (DP1) to

VGA CON

PCIE SLOT

16X

PCIE SLOT

1X

12,17

14

14

PCIE X16

PCIE X1

4,5,6,7

PCIE X1

GIGABIT

AR8151

26

Fusion D2 CORE &

PCIE POWER

DDR3 MEMORY

POWER

FCH CORE & PCIE

POWER

23,24

25

24

C C

USB-7 USB-4USB-5

USB-6

17 26 2617

USB-3

USB-2

18

USB 2.0

18

USB2.0

USB-8

USB-9

17

17

AZALIA

SATA II

AMD

FCH D2

4X

PCIE

HD AUDIO I/F

SATA II I/F

VT1708S

HD AUDIO CODEC

19,20

12

SATA#1

12

SATA#2

12

SATA#3SATA#0

12

LPC I/F

INT RTC

HW MONITOR

ACPI

4 1X PCIE I/F

B B

PCI BUS

PCI SLOT #1

15

VGA Translator I/F

10,11,12,13

SPI I/F

SPI

Dual-BIOS

12

LPC BUS

ITE LPC SIO

IT8728

A A

COM

5

4

KBD

MOUSE

17

SB_SPI_CS ITE_SPI_CS1/2

16

HW

MONITOR

16

3

18

Title

BLOCK DIAGRAM

Size Document Number Rev

Custom

2

Date: Sheet

GA-A55M-DS2 1.01

327Tuesday, August 23, 2011

1

of

Page 4

5

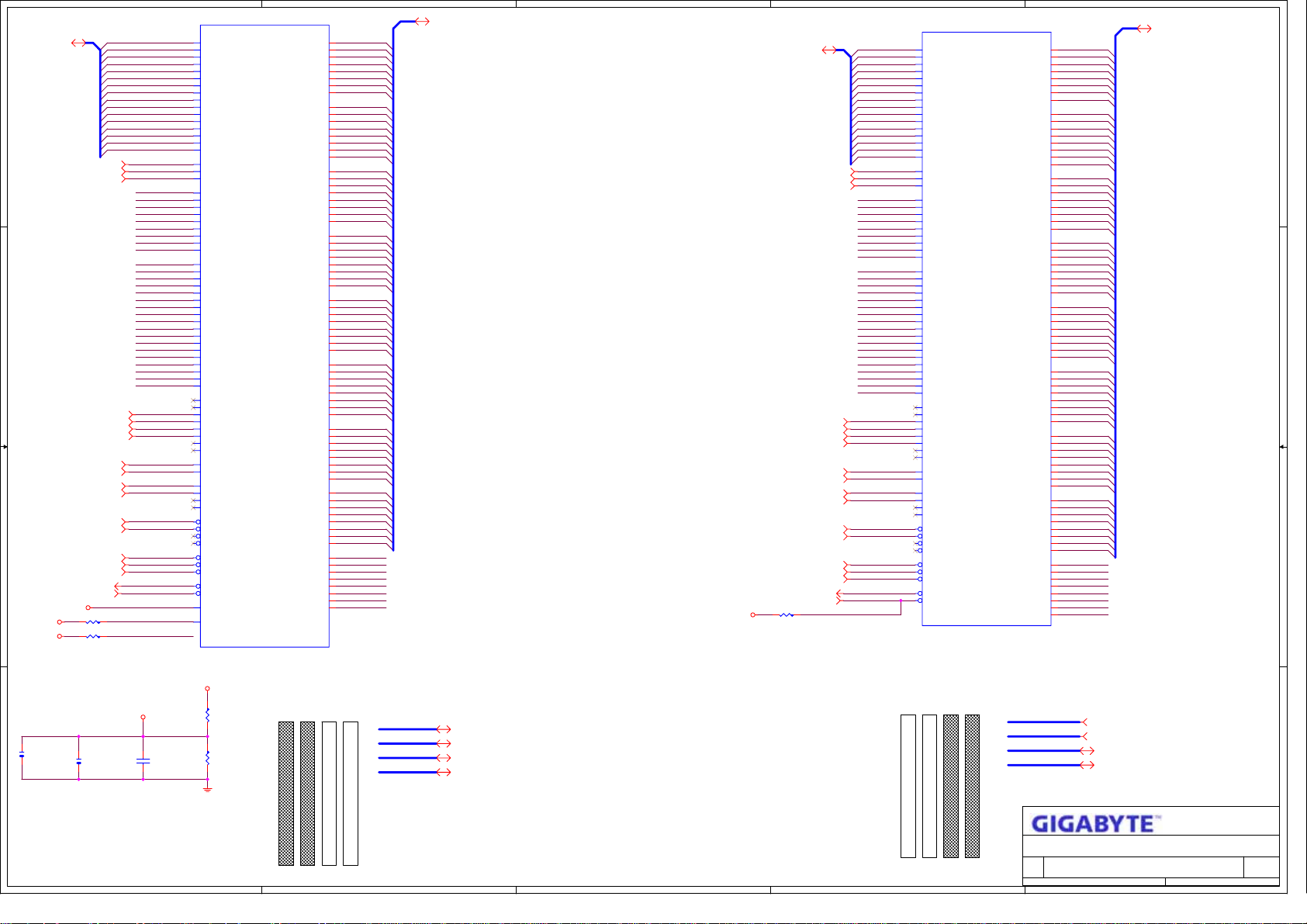

MAAA[0..15]8

D D

C C

MODT_A08

MODT_A18

B B

MEM_MA_RST-8

MEM_MA_HOT-8 MEM_MB_RST-8

APU_M_VREF

AR23 39.2/4/1

DDR15V

AR48 1K/4/1

DDR15V

MAAA0

MAAA1

MAAA2

MAAA3

MAAA4

MAAA5

MAAA6

MAAA7

MAAA8

MAAA9

MAAA10

MAAA11

MAAA12

MAAA13

MAAA14

MAAA15

SBAA0

SBAA08

SBAA1

SBAA18

SBAA2

SBAA28

DMA0

DMA1

DMA2

DMA3

DMA4

DMA5

DMA6

DMA7

DMA8

DQSA0

-DQSA0

DQSA1

-DQSA1

DQSA2

-DQSA2

DQSA3

-DQSA3

DQSA4

-DQSA4

DQSA5

-DQSA5

DQSA6

-DQSA6

DQSA7

-DQSA7

DQSA8

-DQSA8

DCLKA1

DCLKA18

-DCLKA1

-DCLKA18

DCLKA2

DCLKA28

-DCLKA28

CKEA0

CKEA08

CKEA1

CKEA18

MODT_A0

MODT_A1

-CSA0

-CSA08

-CSA1

-CSA18

-SRASA

-SRASA8

-SCASA

-SCASA8

-SWEA

-SWEA8 -SCASB8

MEM_MA_RSTMEM_MA_HOT-

M_ZVDD

MEM_MA_HOT-

M25

M24

W26

AF29

AE25

AG21

AF17

G29

G13

G17

G26

G25

AE28

AE29

AG24

AG25

AF20

AF21

AE16

AD16

AA24

AC27

AA25

AC26

AB26

W23

AB25

W25

FM1CPUA

MEMORY CHANNEL A

MA_ADD0

V27

MA_ADD1

P27

MA_ADD2

R25

MA_ADD3

P26

MA_ADD4

R24

MA_ADD5

P24

MA_ADD6

P23

MA_ADD7

N26

MA_ADD8

N23

MA_ADD9

MA_ADD10

V24

MA_ADD11

N25

MA_ADD12

MA_ADD13

Y23

MA_ADD14

L27

MA_ADD15

L24

MA_BANK0

MA_BANK1

V25

MA_BANK2

L26

MA_DM0

H12

MA_DM1

E17

MA_DM2

H21

MA_DM3

F25

MA_DM4

MA_DM5

MA_DM6

MA_DM7

MA_DM8

MA_DQS_H0

MA_DQS_L0

F13

MA_DQS_H1

H17

MA_DQS_L1

MA_DQS_H2

F21

MA_DQS_L2

E21

MA_DQS_H3

MA_DQS_L3

MA_DQS_H4

MA_DQS_L4

MA_DQS_H5

MA_DQS_L5

MA_DQS_H6

MA_DQS_L6

MA_DQS_H7

MA_DQS_L7

MA_DQS_H8

F30

MA_DQS_L8

E30

MA_CLK_H0

U27

MA_CLK_L0

U26

MA_CLK_H1

T23

MA_CLK_L1

U23

MA_CLK_H2

T25

MA_CLK_L2

T26

MA_CLK_H3

R27

MA_CLK_L3

R28

MA_CKE0

L23

MA_CKE1

K26

MA0_ODT0

MA0_ODT1

MA1_ODT0

MA1_ODT1

MA0_CS_L0

Y27

MA0_CS_L1

MA1_CS_L0

MA1_CS_L1

MA_RAS_L

MA_CAS_L

Y24

MA_WE_L

Y26

MA_RESET_L

J25

MA_EVENT_L

U24

M_VREF

K22

M_ZVDDIO

J24

MA_DATA0

MA_DATA1

MA_DATA2

MA_DATA3

MA_DATA4

MA_DATA5

MA_DATA6

MA_DATA7

MA_DATA8

MA_DATA9

MA_DATA10

MA_DATA11

MA_DATA12

MA_DATA13

MA_DATA14

MA_DATA15

MA_DATA16

MA_DATA17

MA_DATA18

MA_DATA19

MA_DATA20

MA_DATA21

MA_DATA22

MA_DATA23

MA_DATA24

MA_DATA25

MA_DATA26

MA_DATA27

MA_DATA28

MA_DATA29

MA_DATA30

MA_DATA31

MA_DATA32

MA_DATA33

MA_DATA34

MA_DATA35

MA_DATA36

MA_DATA37

MA_DATA38

MA_DATA39

MA_DATA40

MA_DATA41

MA_DATA42

MA_DATA43

MA_DATA44

MA_DATA45

MA_DATA46

MA_DATA47

MA_DATA48

MA_DATA49

MA_DATA50

MA_DATA51

MA_DATA52

MA_DATA53

MA_DATA54

MA_DATA55

MA_DATA56

MA_DATA57

MA_DATA58

MA_DATA59

MA_DATA60

MA_DATA61

MA_DATA62

MA_DATA63

MA_CHECK0

MA_CHECK1

MA_CHECK2

MA_CHECK3

MA_CHECK4

MA_CHECK5

MA_CHECK6

MA_CHECK7

E12

F12

H14

E15

G11

H11

E14

G14

F16

G16

H18

F19

F15

H15

E18

F18

G20

H20

E23

G23

G19

E20

F22

G22

F24

H24

E27

F27

H23

E24

E26

H26

AD30

AF30

AG27

AF27

AD31

AE31

AG28

AD28

AF26

AD25

AF23

AE23

AD27

AE26

AF24

AD24

AG22

AD21

AE19

AG19

AD22

AE22

AE20

AD19

AG18

AE17

AF15

AG15

AD18

AF18

AG16

AD15

F28

E29

G31

H30

H27

G28

F31

H29

MDA0

MDA1

MDA2

MDA3

MDA4

MDA5

MDA6

MDA7

MDA8

MDA9

MDA10

MDA11

MDA12

MDA13

MDA14

MDA15

MDA16

MDA17

MDA18

MDA19

MDA20

MDA21

MDA22

MDA23

MDA24

MDA25

MDA26

MDA27

MDA28

MDA29

MDA30

MDA31

MDA32

MDA33

MDA34

MDA35

MDA36

MDA37

MDA38

MDA39

MDA40

MDA41

MDA42

MDA43

MDA44

MDA45

MDA46

MDA47

MDA48

MDA49

MDA50

MDA51

MDA52

MDA53

MDA54

MDA55

MDA56

MDA57

MDA58

MDA59

MDA60

MDA61

MDA62

MDA63

MA_CK0

MA_CK1

MA_CK2

MA_CK3

MA_CK4

MA_CK5

MA_CK6

MA_CK7

4

MDA[0..63] 8

3

MAAB[0..15]8

SBAB08

SBAB18

SBAB28

DCLKB18

-DCLKB18

DCLKB28

-DCLKB28

CKEB08

CKEB18

MODT_B0

MODT_B08

MODT_B1

MODT_B18

-CSB08

-CSB18

-SRASB8

-SWEB8

MEM_MB_RST-

MEM_MB_HOT-

MEM_MB_HOT-

DDR15V

MEM_MB_HOT-8

AR49 1K/4/1

MAAB0

MAAB1

MAAB2

MAAB3

MAAB4

MAAB5

MAAB6

MAAB7

MAAB8

MAAB9

MAAB10

MAAB11

MAAB12

MAAB13

MAAB14

MAAB15

SBAB0

SBAB1

SBAB2

DMB0

DMB1

DMB2

DMB3

DMB4

DMB5

DMB6

DMB7

DMB8

DQSB0

-DQSB0

DQSB1

-DQSB1

DQSB2

-DQSB2

DQSB3

-DQSB3

DQSB4

-DQSB4

DQSB5

-DQSB5

DQSB6

-DQSB6

DQSB7

-DQSB7

DQSB8

-DQSB8

DCLKB1

-DCLKB1

DCLKB2-DCLKA2

-DCLKB2

CKEB0

CKEB1

-CSB0

-CSB1

-SRASB

-SCASB

-SWEB

M30

M31

M28

M27

W31

AB28

W29

AL29

AH25

AK21

AJ17

AJ29

AH29

AK25

AL25

AJ20

AJ21

AL16

AL17

AA30

AC30

AA31

AC29

AB29

AB31

W28

AA27

AA28

2

FM1CPUB

MEMORY CHANNEL B

MB_ADD0

V31

MB_ADD1

N28

MB_ADD2

P29

MB_ADD3

N29

MB_ADD4

N31

MB_ADD5

MB_ADD6

MB_ADD7

MB_ADD8

MB_ADD9

L30

MB_ADD10

MB_ADD11

L29

MB_ADD12

K28

MB_ADD13

MB_ADD14

K31

MB_ADD15

J31

MB_BANK0

MB_BANK1

V30

MB_BANK2

K29

MB_DM0

B12

MB_DM1

D16

MB_DM2

B20

MB_DM3

A25

MB_DM4

MB_DM5

MB_DM6

MB_DM7

MB_DM8

D29

MB_DQS_H0

D13

MB_DQS_L0

C13

MB_DQS_H1

A17

MB_DQS_L1

B17

MB_DQS_H2

B21

MB_DQS_L2

C21

MB_DQS_H3

D25

MB_DQS_L3

C25

MB_DQS_H4

MB_DQS_L4

MB_DQS_H5

MB_DQS_L5

MB_DQS_H6

MB_DQS_L6

MB_DQS_H7

MB_DQS_L7

MB_DQS_H8

B29

MB_DQS_L8

A29

MB_CLK_H0

U30

MB_CLK_L0

U29

MB_CLK_H1

T29

MB_CLK_L1

T28

MB_CLK_H2

R31

MB_CLK_L2

T31

MB_CLK_H3

P30

MB_CLK_L3

R30

MB_CKE0

J30

MB_CKE1

J28

MB0_ODT0

MB0_ODT1

MB1_ODT0

MB1_ODT1

MB0_CS_L0

Y29

MB0_CS_L1

MB1_CS_L0

Y30

MB1_CS_L1

MB_RAS_L

MB_CAS_L

MB_WE_L

MB_RESET_L

J27

MB_EVENT_L

V28

MB_DATA0

MB_DATA1

MB_DATA2

MB_DATA3

MB_DATA4

MB_DATA5

MB_DATA6

MB_DATA7

MB_DATA8

MB_DATA9

MB_DATA10

MB_DATA11

MB_DATA12

MB_DATA13

MB_DATA14

MB_DATA15

MB_DATA16

MB_DATA17

MB_DATA18

MB_DATA19

MB_DATA20

MB_DATA21

MB_DATA22

MB_DATA23

MB_DATA24

MB_DATA25

MB_DATA26

MB_DATA27

MB_DATA28

MB_DATA29

MB_DATA30

MB_DATA31

MB_DATA32

MB_DATA33

MB_DATA34

MB_DATA35

MB_DATA36

MB_DATA37

MB_DATA38

MB_DATA39

MB_DATA40

MB_DATA41

MB_DATA42

MB_DATA43

MB_DATA44

MB_DATA45

MB_DATA46

MB_DATA47

MB_DATA48

MB_DATA49

MB_DATA50

MB_DATA51

MB_DATA52

MB_DATA53

MB_DATA54

MB_DATA55

MB_DATA56

MB_DATA57

MB_DATA58

MB_DATA59

MB_DATA60

MB_DATA61

MB_DATA62

MB_DATA63

MB_CHECK0

MB_CHECK1

MB_CHECK2

MB_CHECK3

MB_CHECK4

MB_CHECK5

MB_CHECK6

MB_CHECK7

D11

C12

A14

B14

B11

A11

A13

D14

A16

C16

B18

A19

C15

B15

D17

C18

D20

A20

D22

D23

C19

D19

A22

C22

C24

B24

B26

C27

A23

B23

D26

A26

AJ30

AK30

AH28

AJ27

AG30

AH31

AK28

AL28

AJ26

AH26

AH23

AJ23

AK27

AL26

AJ24

AK24

AK22

AH22

AL19

AK19

AL23

AL22

AH20

AL20

AJ18

AH17

AJ15

AK15

AH19

AK18

AK16

AH16

A28

D28

C30

D31

B27

C28

B30

C31

MDB0

MDB1

MDB2

MDB3

MDB4

MDB5

MDB6

MDB7

MDB8

MDB9

MDB10

MDB11

MDB12

MDB13

MDB14

MDB15

MDB16

MDB17

MDB18

MDB19

MDB20

MDB21

MDB22

MDB23

MDB24

MDB25

MDB26

MDB27

MDB28

MDB29

MDB30

MDB31

MDB32

MDB33

MDB34

MDB35

MDB36

MDB37

MDB38

MDB39

MDB40

MDB41

MDB42

MDB43

MDB44

MDB45

MDB46

MDB47

MDB48

MDB49

MDB50

MDB51

MDB52

MDB53

MDB54

MDB55

MDB56

MDB57

MDB58

MDB59

MDB60

MDB61

MDB62

MDB63

MB_CK0

MB_CK1

MB_CK2

MB_CK3

MB_CK4

MB_CK5

MB_CK6

MB_CK7

1

MDB[0..63] 8

FM1_APU/[10SC1-A01905-01R_10SC1-A01905-02R]

FM1_APU/[10SC1-A01905-01R_10SC1-A01905-02R]

CPUVREF

40 MILS WIDTH

SABC1

1N/4/X7R/50V/K

A A

APU_M_VREF

SABC2

0.1U/4/X7R/16V/K

12

SABC3

1U/6/X7R/16V/K

DDR15V

SAR1

1K/4/1

SAR2

1K/4/1

MEM CHA

-DQSA[0..8]

DQSA[0..8]

MA_CK[0..7]

DMA[0:8]

-DQSA[0..8] 8

DQSA[0..8] 8

MA_CK[0..7] 8

DMA[0..8] 8

MEM CHB

-DQSB[0..8]

DQSB[0..8]

MB_CK[0..7]

DMB[0..8]

-DQSB[0..8] 8

DQSB[0..8] 8

MB_CK[0..7] 8

DMB[0..8] 8

Layout: Place within

500mils of the CPU socket.

Title

Size Document Number Rev

5

A0 A1

4

3

B0 B1

2

Custom

Date: Sheet

APU DDRIII MEMORY

GA-A55M-DS2 1.01

1

of

427Tuesday, August 23, 2011

Page 5

5

DDR15V

-CPURST

100P/4/NPO/50V/J

D D

DDR15V

DDR15V

DDR15V

DDR15V

AC25

AR47 300/4

AR50 1K/4/1

AR51 1K/4/1

AR39 1K/4/1

AR40 1K/4/1

APU_SVC

APU_SVD

APU_SIC

APU_SID

APU Spread 100Mhz clock

DP Non-Spread 100Mhz clock

3VDUAL VCC3

AR41

8.2K/4/1

3

AQ4

D

GS

2

1

2N7002/SOT23/25pF/5

DDR15V

AR44

300/4

CPU_PWRGD

3

AQ5

D

GS

2

1

2N7002/SOT23/25pF/5

PWM_PWRGD 23

AC23

0.1u/4/Y5V/16V/Z/X

AMD comment for validation.

AC24

0.1u/4/Y5V/16V/Z/X

AQ3

GS

AR42

8.2K/4/1

3

D

2

1

AR46

1K/4/1

C C

DDR15V

AR43

300/4

CPU_PG_SB10

B B

AR45 1K/4/1

MMBT2222A/SOT23/600mA/40

4

DP0_TXP027

DP0_TXN027

DP0_TXP127

DP0_TXN127

DP0_TXP227

DP0_TXN227

DP0_TXP327

DP0_TXN327

DP1_TXP012

DP1_TXN012

DP1_TXP112

DP1_TXN112

DP1_TXP212

DP1_TXN212

DP1_TXP312

DP1_TXN312

APUCLKP9

APUCLKN9

DISP_CLKP9

DDR15V

DDR15V

DISP_CLKN9

AR54 1K/4/1

AR38 300/4

APU_SVC23

APU_SVD23

APU_SIC16

APU_SID16

DP0_TXP0

DP0_TXN0

DP0_TXP1

DP0_TXN1

DP0_TXP2

DP0_TXN2

DP0_TXP3

DP0_TXN3

DP1_TXP0

DP1_TXN0

DP1_TXP1

DP1_TXN1

DP1_TXP2

DP1_TXN2

DP1_TXP3

DP1_TXN3

APUCLKP

APUCLKN

DISP_CLKP

DISP_CLKN

APU_SVC

APU_SVD

APU_SIC

APU_SID

-CPURST

-CPURST10

CPU_PWRGD

-PROCHOT

THERMTRIP_L

APU_ALERT-

CPU_TDI

CPU_TDI11

CPU_TCK

CPU_TCK11

CPU_TMS

CPU_TMS11

CPU_TRST

CPU_DBREQ

VNB_FB+23

COREFB+23

COREFB-23

AL12

AK12

AH12

AG12

AF10

AG10

AJ13

AG11

AL14

AK14

AD10

AF13

M2

M3

L2

L1

L4

L5

K2

K3

R4

R5

P2

P3

N2

N1

N4

N5

A8

B8

E9

G10

E8

D8

F10

D7

F8

E11

H9

K23

K25

B5

A6

B6

C7

A5

C6

3

FM1CPUC

ANALOG/DISPLAY/MISC

DP0_TXP0

DP0_TXN0

DP0_TXP1

DP0_TXN1

DP0_TXP2

DP0_TXN2

DP0_TXP3

DP0_TXN3

DP1_TXP0

DP1_TXN0

DP1_TXP1

DP1_TXN1

DP1_TXP2

DP1_TXN2

DP1_TXP3

DP1_TXN3

CLKIN_H

CLKIN_L

DISP_CLKIN_H

DISP_CLKIN_L

SVC

SVD

SIC

SID

RESET_L

PWROK

PROCHOT_L

THERMTRIP_L

ALERT_L

TDI

TDO

TCK

TMS

TRST_L

DBRDY

DBREQ_L

RSVD_1

RSVD_2

RSVD_3

RSVD_4

RSVD_5

VDDP_SENSE

VDDNB_SENSE

VDDIO_SENSE

VDD_SENSE

VDDR_SENSE

VSS_SENSE

DISPLAY

DISPLAY

CLK

CTRL SER.

JTAG

SENSE RSVD

PORT 0

PORT 1

DISPLAY PORT

MISC.

TEST

DP_AUX_ZVSS

DP_BLON

DP_DIGON

DP_VARY_BL

DP0_AUXP

DP0_AUXN

DP1_AUXP

DP1_AUXN

DP2_AUXP

DP2_AUXN

DP3_AUXP

DP3_AUXN

DP4_AUXP

DP4_AUXN

DP5_AUXP

DP5_AUXN

DP0_HPD

DP1_HPD

DP2_HPD

DP3_HPD

DP4_HPD

DP5_HPD

THERMDA

THERMDC

TEST2

TEST3

TEST6

TEST9

TEST10

TEST12

TEST14

TEST15

TEST16

TEST17

TEST18

TEST19

TEST20

TEST21

TEST22

TEST23

TEST24

TEST25_H

TEST25_L

TEST28_H

TEST28_L

TEST30_H

TEST30_L

TEST31

TEST32_H

TEST32_L

TEST35

FM1R1

DMAACTIVE_L

FM1_APU/[10SC1-A01905-01R_10SC1-A01905-02R]

J9

G9

G7

H8

K6

K8

L7

L8

R7

R8

P8

P9

N7

N8

M8

M9

K9

K5

P5

P6

M5

M6

AH14

AG14

AB23

AC24

AG13

D10

C10

F6

D9

C9

B9

A9

E4

F5

D4

D5

E5

F7

E6

AE11

AD11

G5

G6

AD14

AE14

AG31

AE13

AD13

A7

AC12

AF11

DP_A_ZVSS

DP0_AUXP

DP0_AUXN

DP1_AUXP

DP1_AUXN

DP0_HPD

DP1_HPD

DP2_HPD

DP3_HPD

DP4_HPD

DP5_HPD

APU_TEST12

APU_TEST18

APU_TEST19

APU_TEST20

APU_TEST21

APU_TEST22

APU_TEST24

APU_TEST25H

APU_TEST25L

APU_TEST31

APU_TEST35

FM1R1

FM1R1

-DMA_ACTIVE

AR26 150/4/1

DP0_AUXP 27

DP0_AUXN 27

DP1_AUXP 12

DP1_AUXN 12

AR27 100K/4/1

AR1 100K/4/1

AR2 100K/4/1

AR3 100K/4/1

AR5 1K/4/1

AR6 1K/4/1

AR7 1K/4/1

AR8 1K/4/1

AR9 1K/4/1

AR10 1K/4/1

AR11 1K/4/1

AR12 510/4/1

AR13 510/4/1

AR20 39.2/4/1

AR21 300/4/1/X

AR22 300/4

AR31 10K/4/1

AR30 1K/4/1

2

DP0_HPD 27

DP1_HPD 12

APU_VDDPA

TEST35: high=>HDMI enable,

DDR15V

low=>HDMI disable.

3VDUAL

FM1R1 22

DDR15V

-DMA_ACTIVE 10

DDR15V

DDR15V

DDR15V

DDR15V

AR35 1K/4/1

DDR15V

-PROCHOT

AR32 1K/4/1

AR33 300/4

AR36 1K/4/1

AR52 1K/4/1

AQ6

AQ7

GS

3VDUAL

D

GS

2

3VDUAL

3

D

2

1

AR37 0/4/SHT/X

AR34

8.2K/4

THERMTRIP_CPU_L

3

AC13

0.1u/4/Y5V/16V/Z/X

1

THERMTRIP_L

MMBT2222A/SOT23/600mA/40

AR53

8.2K/4

SB_ALERT-

AC35

0.1u/4/Y5V/16V/Z/X

1

MMBT2222A/SOT23/600mA/40

APU_ALERT-

-PROCHOT_CPU 10

AC14

0.1u/4/Y5V/16V/Z/X

THERMTRIP_CPU_L 11

SB_ALERT- 12

A A

Title

Size Document Number Rev

Custom

5

4

3

2

Date: Sheet

APU CONTROL

GA-A55M-DS2 1.01

1

of

527Tuesday, August 23, 2011

Page 6

8

FM1CPUH

EXP_A_RXP0

EXP_A_RXN0

EXP_A_RXP1

EXP_A_RXN1

EXP_A_RXP2

EXP_A_RXN2

EXP_A_RXP3

EXP_A_RXN3

EXP_A_RXP4

EXP_A_RXN4

EXP_A_RXP5

D D

PCIE1_IP14

PCIE1_IN14

C C

APU_VDDPB

A_RX0P10

A_RX0N10

A_RX1P10

A_RX1N10

A_RX2P10

A_RX2N10

A_RX3P10

A_RX3N10

AR25 196/4/1

EXP_A_RXN5

EXP_A_RXP6

EXP_A_RXN6

EXP_A_RXP7

EXP_A_RXN7

EXP_A_RXP8

EXP_A_RXN8

EXP_A_RXP9

EXP_A_RXN9

EXP_A_RXP10

EXP_A_RXN10

EXP_A_RXP11

EXP_A_RXN11

EXP_A_RXP12

EXP_A_RXN12

EXP_A_RXP13

EXP_A_RXN13

EXP_A_RXP14

EXP_A_RXN14

EXP_A_RXP15

EXP_A_RXN15

ML_IP26

ML_IN26

Within 1500mil from APU Within 1500mil from APU

P_GFX_RXP0

AF8

P_GFX_RXN0

AF9

P_GFX_RXP1

AE7

P_GFX_RXN1

AE8

P_GFX_RXP2

AD5

P_GFX_RXN2

AD6

P_GFX_RXP3

AD8

P_GFX_RXN3

AD9

P_GFX_RXP4

AC7

P_GFX_RXN4

AC8

P_GFX_RXP5

AB5

P_GFX_RXN5

AB6

P_GFX_RXP6

AB8

P_GFX_RXN6

AB9

P_GFX_RXP7

AA7

P_GFX_RXN7

AA8

P_GFX_RXP8

Y5

P_GFX_RXN8

Y6

P_GFX_RXP9

Y8

P_GFX_RXN9

Y9

P_GFX_RXP10

W7

P_GFX_RXN10

W8

P_GFX_RXP11

V5

P_GFX_RXN11

V6

P_GFX_RXP12

V8

P_GFX_RXN12

V9

P_GFX_RXP13

U7

P_GFX_RXN13

U8

P_GFX_RXP14

T5

P_GFX_RXN14

T6

P_GFX_RXP15

T8

P_GFX_RXN15

T9

P_GPP_RXP0

AH5

P_GPP_RXN0

AH6

P_GPP_RXP1

AH8

P_GPP_RXN1

AH9

P_GPP_RXP2

AG7

P_GPP_RXN2

AG8

P_GPP_RXP3

AF5

P_GPP_RXN3

AF6

P_UMI_RXP0

AL5

P_UMI_RXN0

AL4

P_UMI_RXP1

AK3

P_UMI_RXN1

AK2

P_UMI_RXP2

AJ2

P_UMI_RXN2

AJ1

P_UMI_RXP3

AJ4

P_UMI_RXN3

AJ5

P_ZVDDP

J7

FM1_APU/[10SC1-A01905-01R_10SC1-A01905-02R]

PCI EXPRESS

7

P_ZVSS

AE2

AE1

AE4

AE5

AD2

AD3

AC2

AC1

AC4

AC5

AB2

AB3

AA2

AA1

AA4

AA5

Y2

Y3

W2

W1

W4

W5

V2

V3

U2

U1

U4

U5

T2

T3

R2

R1

AH2

AH3

AG2

AG1

AG4

AG5

AF2

AF3

AK8

AK9

AL7

AL8

AK5

AK6

AJ7

AJ8

J6

EXP_A_TXP0

EXP_A_TXN0

EXP_A_TXP1

EXP_A_TXN1

EXP_A_TXP2

EXP_A_TXN2

EXP_A_TXP3

EXP_A_TXN3

EXP_A_TXP4

EXP_A_TXN4

EXP_A_TXP5

EXP_A_TXN5

EXP_A_TXP6

EXP_A_TXN6

EXP_A_TXP7

EXP_A_TXN7

EXP_A_TXP8

EXP_A_TXN8

EXP_A_TXP9

EXP_A_TXN9

EXP_A_TXP10

EXP_A_TXN10

EXP_A_TXP11

EXP_A_TXN11

EXP_A_TXP12

EXP_A_TXN12

EXP_A_TXP13

EXP_A_TXN13

EXP_A_TXP14

EXP_A_TXN14

EXP_A_TXP15

EXP_A_TXN15

GPP_TXP0

GPP_TXN0

PCIE1_OP

PCIE1_ON

A_TX0P_C

A_TX0N_C

A_TX1P_C

A_TX1N_C

A_TX2P_C

A_TX2N_C

A_TX3P_C

A_TX3N_C

P_ZVSSP_ZDD

P_GFX_TXP0

P_GFX_TXN0

P_GFX_TXP1

P_GFX_TXN1

P_GFX_TXP2

P_GFX_TXN2

P_GFX_TXP3

P_GFX_TXN3

P_GFX_TXP4

P_GFX_TXN4

P_GFX_TXP5

P_GFX_TXN5

P_GFX_TXP6

P_GFX_TXN6

P_GFX_TXP7

P_GFX_TXN7

P_GFX_TXP8

P_GFX_TXN8

P_GFX_TXP9

P_GFX_TXN9

P_GFX_TXP10

P_GFX_TXN10

P_GFX_TXP11

P_GFX_TXN11

P_GFX_TXP12

P_GFX_TXN12

P_GFX_TXP13

P_GFX_TXN13

P_GFX_TXP14

P_GFX_TXN14

P_GFX_TXP15

P_GFX_TXN15

P_GPP_TXP0

P_GPP_TXN0

P_GPP_TXP1

GPP GRAPHICS

UMI_LINK

P_GPP_TXN1

P_GPP_TXP2

P_GPP_TXN2

P_GPP_TXP3

P_GPP_TXN3

P_UMI_TXP0

P_UMI_TXN0

P_UMI_TXP1

P_UMI_TXN1

P_UMI_TXP2

P_UMI_TXN2

P_UMI_TXP3

P_UMI_TXN3

6

EXP_A_RXP[0..15]

EXP_A_RXN[0..15]

EXP_A_TXP[0..15]

EXP_A_TXN[0..15]

TX CAP close to CPU side

AC33 0.1u/4/X7R/16V/K

AC34 0.1u/4/X7R/16V/K

PLACE THESE CAP CLOSE TO APU.

AC1 0.1u/4/X7R/16V/K

AC2 0.1u/4/X7R/16V/K

AC3 0.1u/4/X7R/16V/K

AC4 0.1u/4/X7R/16V/K

AC5 0.1u/4/X7R/16V/K

AC6 0.1u/4/X7R/16V/K

AC7 0.1u/4/X7R/16V/K

AC8 0.1u/4/X7R/16V/K

AR24 196/4/1

ML_OP 26

ML_ON 26

PCIE1_OP 14

PCIE1_ON 14

A_TX0P 10

A_TX0N 10

A_TX1P 10

A_TX1N 10

A_TX2P 10

A_TX2N 10

A_TX3P 10

A_TX3N 10

5

EXP_A_RXP[0..15] 14

EXP_A_RXN[0..15] 14

EXP_A_TXP[0..15] 14

EXP_A_TXN[0..15] 14

4

3

2

1

B B

A A

Title

Size Document Number Rev

Custom

8

7

6

5

4

3

Date: Sheet

2

APU GFX , GPP , UMI

GA-A55M-DS2 1.01

627Tuesday, August 23, 2011

of

1

Page 7

DDR15V=1.25V/1.35V/1.5V(DDR3)

VCORE VCORE DDR15V

FM1CPUD

VDD

VDD

M12

VDD

P12

VDD

H10

VDD

H6

VDD

U19

VDD

J11

VDD

J13

VDD

J15

VDD

J17

VDD

J19

VDD

J21

VDD

J5

VDD

K10

VDD

K12

VDD

K14

VDD

K16

VDD

K18

VDD

K20

VDD

K4

VDD

L11

VDD

W19

VDD

L15

VDD

L17

VDD

N19

VDD

L21

VDD

L3

VDD

L6

VDD

M1

VDD

M10

VDD

W13

VDD

M16

VDD

M18

VDD

M20

VDD

U21

VDD

M4

VDD

M7

VDD

N11

VDD

N21

VDD

P1

VDD

P10

VDD

P20

VDD

R11

VDD

R21

VDD

R3

VDD

R6

VDD

T1

VDD

T10

VDD

T12

VDD

T20

VDD

T4

VDD

T7

FM1_APU/[10SC1-A01905-01R_10SC1-A01905-02R]

VCORE_NB

ABC4

22u/8/X5R/6.3V/M

VCORE_NB

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

ABC8

22u/8/X5R/6.3V/M

U11

U13

V1

V10

V12

V20

W11

W21

W3

W6

Y1

Y10

Y12

Y14

Y16

Y18

Y20

Y4

Y7

AA11

AA13

AA15

AA17

AA19

AA21

AB1

AB10

R13

AB14

AB16

AB18

R19

AC11

AC13

AC15

AC17

AC19

AC21

AC3

AC6

AD1

AD4

AD7

AF1

AG3

AG6

AH1

AH4

AH7

AK4

AK7

ABC9

22u/8/X5R/6.3V/M

FM1CPUE

POWER

VDDIO

J26

VDDIO

J29

VDDIO

K24

K27

K30

M23

M26

M29

N24

N27

N30

P22

P25

P28

P31

R23

R26

R29

U25

U28

U31

V22

V23

V26

V29

W24

W27

W30

Y22

Y25

Y28

Y31

AA23

AA26

AA29

AB22

AB24

AB27

AB30

AC23

AC25

AC28

AC31

M22

VDDIO

VDDIO

VDDIO

L25

VDDIO

L28

VDDIO

L31

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

T22

VDDIO

T24

VDDIO

T27

VDDIO

T30

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB_CAP_1

VDDNB_CAP_2

VDDP_A_1

VDDP_A_2

VDDP_A_3

VDDP_A_4

VDDP_B_1

VDDP_B_2

VDDP_B_3

VDDP_B_4

FM1_APU/[10SC1-A01905-01R_10SC1-A01905-02R]

ABC5

22u/8/X5R/6.3V/M

FM1CPUF

VSS

VSS_1

A10

VSS_2

A12

VSS_3

A15

VSS_4

A18

VSS_5

A21

VSS_6

A24

VSS_7

A27

VSS_8

AL9

VSS_9

B10

VSS_10

B13

VSS_11

B16

VSS_12

B19

VSS_13

B22

VSS_14

B25

VSS_15

B28

VSS_16

B7

VSS_17

C11

VSS_18

C14

VSS_19

C17

VSS_20

C20

VSS_21

C23

VSS_22

C26

VSS_23

C29

VSS_24

C8

VSS_25

D12

VSS_26

D15

VSS_27

D18

VSS_28

D21

VSS_29

D24

VSS_30

D27

VSS_31

D30

VSS_32

D6

VSS_33

E10

VSS_34

E13

VSS_35

E16

VSS_36

E19

VSS_37

E22

VSS_38

E25

VSS_39

E28

VSS_40

E31

VSS_41

E7

VSS_42

F11

VSS_43

F14

VSS_44

F17

VSS_45

F20

VSS_46

F23

VSS_47

F26

VSS_48

F29

VSS_49

F9

VSS_50

G1

VSS_51

G12

VSS_52

G15

VSS_53

G18

VSS_54

G2

VSS_55

G21

VSS_56

G24

VSS_57

G27

VSS_58

G3

FM1_APU/[10SC1-A01905-01R_10SC1-A01905-02R]

SAC8

22u/8/X5R/6.3V/M

VCORE_NB

APU_VDDPA

APU_VDDPA

APU_VDDPB

APU_VDDPB

VDDA25

ABC16

4.7u/6/X5R/6.3V/K

Place close N13, M14 pin inside

the backplate cavity opeining.

ABC1

0.22u/6/X7R/16V/K

ABC2

3.3N/4/X7R/50V/K

VDDA25

VDDA

AD12

VDDA

AE12

A3

A4

B3

B4

C1

C2

C3

C4

C5

D1

D2

D3

E1

E2

E3

F1

F2

F3

F4

SAC1 22u/8/X5R/6.3V/M

M14

SAC2 22u/8/X5R/6.3V/M

N13

AH10

AJ10

AK10

AL10

VDDR

AH11

VDDR

AJ11

VDDR

AK11

VDDR

AL11

J1

J2

J3

Check Power from AMD

J4

VDDR

H1

VDDR

H2

VDDR

H3

VDDR

H4

FM1CPU

VCORE

BUTTOM SIDE

SAC6

22u/8/X5R/6.3V/M/X

SAC7

22u/8/X5R/6.3V/M

VSS_59

VSS_60

VSS_61

VSS_62

VSS_63

VSS_64

VSS_65

VSS_66

VSS_67

VSS_68

VSS_69

VSS_70

VSS_71

VSS_72

VSS_73

VSS_74

VSS_75

VSS_76

VSS_77

VSS_78

VSS_79

VSS_80

VSS_81

VSS_82

VSS_83

VSS_84

VSS_85

VSS_86

VSS_87

VSS_88

VSS_89

VSS_90

VSS_91

VSS_92

VSS_93

VSS_94

VSS_95

VSS_96

VSS_97

VSS_98

VSS_99

VSS_100

VSS_101

VSS_102

VSS_103

VSS_104

VSS_105

VSS_106

VSS_107

VSS_108

VSS_109

VSS_110

VSS_111

VSS_112

VSS_113

VSS_114

VSS_115

VSS_116

SAC9

22u/8/X5R/6.3V/M

G30

G4

G8

H13

H16

H19

H22

H25

H28

H31

H5

H7

J10

J12

J14

J16

J18

J20

J22

J23

J8

K1

K11

V13

K15

K17

V19

K21

K7

L10

L12

L14

L16

L18

L20

L22

L9

M11

M13

M15

M17

M21

N10

N12

N20

N22

N3

N6

N9

P11

P21

P4

P7

R10

R12

R20

R22

R9

SAC10

22u/8/X5R/6.3V/M

FM1CPUG

VSS

W10

W12

W20

W22

AA10

AA14

AA16

AA18

AA22

AB11

AB13

AB15

AB17

AB19

AB21

AC10

AC14

AC16

AC18

AC20

AC22

AD17

AD20

AD23

AD26

AD29

AE10

AE15

AE18

AE21

AE24

AE27

T11

T21

U10

U12

U20

U22

V11

V21

Y11

Y13

Y15

Y17

Y19

Y21

AA3

AA6

AA9

AB4

AB7

AC9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

U3

VSS

U6

VSS

U9

VSS

VSS

VSS

V4

VSS

V7

VSS

VSS

VSS

VSS

VSS

W9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AE3

VSS

AE30

VSS

AE6

VSS

AE9

VSS

AF12

VSS

AF14

VSS

AF16

VSS

AF19

VSS

AF22

VSS

AF25

VSS

AF28

VSS

AF31

VSS

AF4

VSS

AF7

VSS

AG17

VSS

AG20

VSS

AG23

VSS

AG26

VSS

AG29

VSS

AG9

VSS

AH13

VSS

AH15

VSS

AH18

VSS

AH21

VSS

AH24

VSS

AH27

VSS

AH30

VSS

AJ12

VSS

AJ14

VSS

AJ16

VSS

AJ19

VSS

AJ22

VSS

AJ25

VSS

AJ28

VSS

AJ3

VSS

AJ31

VSS

AJ6

VSS

AJ9

VSS

AK13

VSS

AK17

VSS

AK20

VSS

AK23

VSS

AK26

VSS

AK29

VSS

AL13

VSS

AL15

VSS

AL18

VSS

AL21

VSS

AL24

VSS

AL27

VSS

AL3

VSS

AL6

VSS

M19

VSS

P13

VSS

P19

VSS

T13

VSS

T19

FM1_APU/[10SC1-A01905-01R_10SC1-A01905-02R]

SAC11

22u/8/X5R/6.3V/M/X

SAC12

22u/8/X5R/6.3V/M

SAC13

22u/8/X5R/6.3V/M

AC15

0.22U/6/X7R/16V/K

DDR15V

SAC27

22u/8/X5R/6.3V/M

APU_VDDPB

AC21

22u/8/X5R/6.3V/M

APU_VDDPB

AC12

22u/8/X5R/6.3V/M/X

AC16

0.22U/6/X7R/16V/K

SAC28

22u/8/X5R/6.3V/M

ABC10

4.7u/6/X5R/6.3V/K

ABC3

4.7u/6/X5R/6.3V/K

ABC6

4.7u/6/X5R/6.3V/K

SAC29

22u/8/X5R/6.3V/M/X

AC20

0.22U/6/X7R/16V/K/X

AC10

0.22U/6/X7R/16V/K

ABC7

4.7u/6/X5R/6.3V/K

SAC15

180P/4/NPO/50V/J

AC19

0.22U/6/X7R/16V/K

AC11

0.22U/6/X7R/16V/K/X

SAC30

0.22U/6/X7R/16V/K/X

AC18

1N/4/X7R/50V/K/X

AC9

180P/4/NPO/50V/J

SAC31

0.22U/6/X7R/16V/K/X

AC17

1N/4/X7R/50V/K

SAC32

4.7u/6/X5R/6.3V/K/X

AMD RM/BLUE/[12KRC-04K812-41R_12KRC-04K812-42R]

SAC54

4.7u/6/X5R/6.3V/K

SAC55

0.22U/6/X7R/16V/K

SAC53

22u/8/X5R/6.3V/M

APU_VDDPA

AC27

22u/8/X5R/6.3V/M/X

APU_VDDPA

AC31

22u/8/X5R/6.3V/M

VCORE

SAC18

22u/8/X5R/6.3V/M

VCORE

SAC16

0.22U/6/X7R/16V/K

AC26

4.7u/6/X5R/6.3V/K/X

AC30

4.7u/6/X5R/6.3V/K/X

AC22

4.7u/6/X5R/6.3V/K

AC29

4.7u/6/X5R/6.3V/K

SAC14

22u/8/X5R/6.3V/M

SAC24

0.22U/6/X7R/16V/K

AC32

0.22U/6/X7R/16V/K

AC28

0.22U/6/X7R/16V/K

SAC17

22u/8/X5R/6.3V/M

SABC9

4.7u/6/X5R/6.3V/K

SAC47

180P/4/NPO/50V/J

SAC43

180P/4/NPO/50V/J/X

SAC19

22u/8/X5R/6.3V/M

SABC10

4.7u/6/X5R/6.3V/K

SAC52

1N/4/X7R/50V/K

SAC20

22u/8/X5R/6.3V/M/X

SAC3

180P/4/NPO/50V/J

Title

APU POWER & GND

Size Document Number Rev

Custom

Date: Sheet

SAC21

22u/8/X5R/6.3V/M

SAC5

180P/4/NPO/50V/J

GA-A55M-DS2 1.01

SAC23

22u/8/X5R/6.3V/M

SAC4

180P/4/NPO/50V/J/X

727Tuesday, August 23, 2011

SAC22

22u/8/X5R/6.3V/M

of

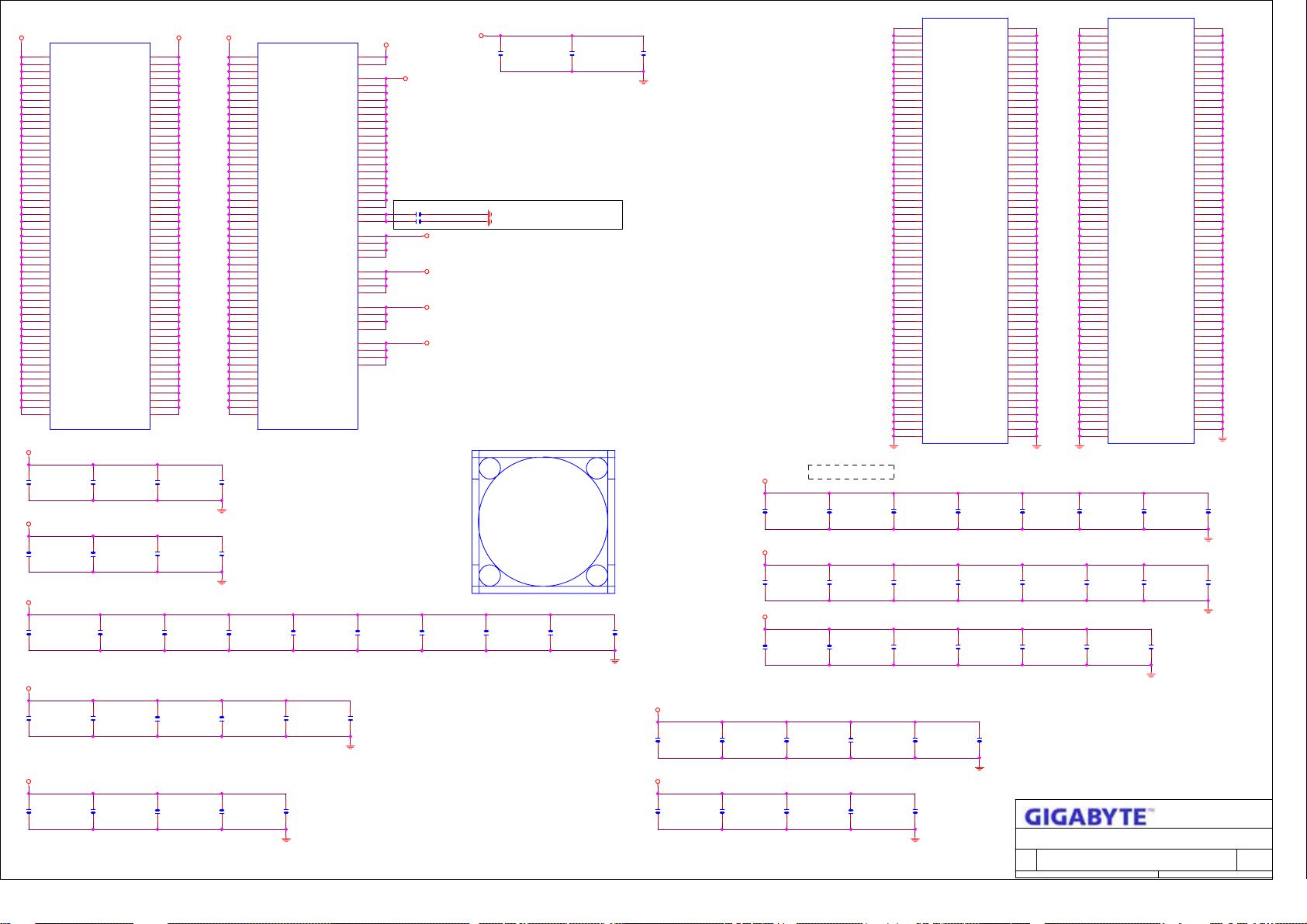

Page 8

8

D D

SMBDATA

SMBCLK

C205

100p/4/NPO/50V/J/X

C C

C275 0.1u/4/Y5V/16V/Z

VCC3

C277 0.1u/4/X7R/16V/K

C279 0.1u/4/X7R/16V/K

B B

A A

DDR15V Decouple

DDR15V

SMBDATA9,11,23

MAAA[0..15]4

MEM_MA_RST-4

8

C206

100p/4/NPO/50V/J/X

DDR15V

VREFCA_A

VREFDQ_A

SMBCLK9,11,23

SBAA24

SBAA14

SBAA04

CKEA14

CKEA04

-CSA14

-CSA04

-DCLKA24

DCLKA24

-DCLKA14

DCLKA14

MEM_MA_RST-

-SCASA4

-SRASA4

-SWEA4

BC2

0.1u/4/Y5V/16V/Z

BC3

0.1u/4/Y5V/16V/Z

BC6

0.1u/4/Y5V/16V/Z

DDRVTT

SMBCLK

SMBDATA

SBAA2

SBAA1

SBAA0

CKEA1

CKEA0

-CSA1

-CSA0

-DCLKA2

DCLKA2

-DCLKA1

DCLKA1

MAAA0

MAAA1

MAAA2

MAAA3

MAAA4

MAAA5

MAAA6

MAAA7

MAAA8

MAAA9

MAAA10

MAAA11

MAAA12

MAAA13

MAAA14

MAAA15

-SCASA

-SRASA

-SWEA

DDRVTT

7

DDR3_2

120

VTT

2

VSS

5

VSS

8

VSS

11

VSS

14

VSS

17

VSS

20

VSS

23

VSS

26

VSS

29

VSS

32

VSS

35

VSS

38

VSS

41

VSS

44

VSS

47

VSS

80

VSS

83

VSS

86

VSS

89

VSS

92

VSS

95

VSS

98

VSS

101

VSS

104

VSS

107

VSS

110

VSS

113

VSS

116

VSS

119

VSS

121

VSS

124

VSS

127

VSS

130

VSS

133

VSS

136

VSS

139

VSS

142

VSS

145

VSS

148

VSS

151

VSS

154

VSS

157

VSS

160

VSS

163

VSS

166

VSS

199

VSS

202

VSS

205

VSS

208

VSS

211

VSS

214

VSS

217

VSS

220

VSS

223

VSS

226

VSS

229

VSS

232

VSS

235

VSS

239

VSS

51

VDD

54

VDD

57

VDD

60

VDD

62

VDD

65

VDD

66

VDD

69

VDD

72

VDD

75

VDD

78

VDD

170

VDD

173

VDD

176

VDD

179

VDD

182

VDD

183

VDD

186

VDD

189

VDD

191

VDD

194

VDD

197

VDD

236

VDDSPD

67

VREFCA

1

VREFDQ

118

SCL

238

SDA

237

SA1

117

SA0

52

BA2

190

BA1

71

BA0

169

CKE1

50

CKE0

76

S1*

193

S0*

64

CK1/NU*

63

CK1/NU

185

CK0*

184

CK0

188

A0

181

A1

61

A2

180

A3

59

A4

58

A5

178

A6

56

A7

177

A8

175

A9

70

A10/AP

55

A11

174

A12

196

A13

172

A14

171

A15

168

RESET*

74

CAS*

192

RAS*

73

WE*

DDRVTT Decouple

BC7

0.1u/4/Y5V/16V/Z

BC8

0.1u/4/Y5V/16V/Z

BC9

0.1u/4/Y5V/16V/Z

7

6

FREE

FREEVTT

FREE

FREE

RSVD

ODT1

ODT0

NC/PAR_IN

NC/ERR_OUT

NC/TEST4

DQS0

DQS0*

DQS1

DQS1*

DQS2

DQS2*

DQS3

DQS3*

DQS4

DQS4*

DQS5

DQS5*

DQS6

DQS6*

DQS7

DQS7*

DQS8

DQS8*

DM0/DQS9

NC/DQS9*

DM1/DQS10

NC/DQS10*

DM2/DQS11

NC/DQS11*

DM3/DQS12

NC/DQS12*

DM4/DQS13

NC/DQS13*

DM5/DQS14

NC/DQS14*

DM6/DQS15

NC/DQS15*

DM7/DQS16

NC/DQS16*

DM8/DQS17

NC/DQS17*

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

DDR3/240/BU/VA/D

6

5

48

49240

MEM_MA_HOT-

187

198

79

77

195

68

53

167

39

CB0

40

CB1

45

CB2

46

CB3

158

CB4

159

CB5

164

CB6

165

CB7

7

6

16

15

25

24

34

33

85

84

94

93

103

102

112

111

43

42

125

126

134

135

143

144

152

153

203

204

212

213

221

222

230

231

161

162

3

DQ0

4

DQ1

9

DQ2

10

DQ3

122

DQ4

123

DQ5

128

DQ6

129

DQ7

12

DQ8

13

DQ9

18

19

131

132

137

138

21

22

27

28

140

141

146

147

30

31

36

37

149

150

155

156

81

82

87

88

200

201

206

207

90

91

96

97

209

210

215

216

99

100

105

106

218

219

224

225

108

109

114

115

227

228

233

234

MODT_A1

MODT_A0

MA_CK0

MA_CK1

MA_CK2

MA_CK3

MA_CK4

MA_CK5

MA_CK6

MA_CK7

DQSA0

-DQSA0

DQSA1

-DQSA1

DQSA2

-DQSA2

DQSA3

-DQSA3

DQSA4

-DQSA4

DQSA5

-DQSA5

DQSA6

-DQSA6

DQSA7

-DQSA7

DQSA8

-DQSA8

DMA0

DMA1

DMA2

DMA3

DMA4

DMA5

DMA6

DMA7

DMA8

MDA0

MDA1

MDA2

MDA3

MDA4

MDA5

MDA6

MDA7

MDA8

MDA9

MDA10

MDA11

MDA12

MDA13

MDA14

MDA15

MDA16

MDA17

MDA18

MDA19

MDA20

MDA21

MDA22

MDA23

MDA24

MDA25

MDA26

MDA27

MDA28

MDA29

MDA30

MDA31

MDA32

MDA33

MDA34

MDA35

MDA36

MDA37

MDA38

MDA39

MDA40

MDA41

MDA42

MDA43

MDA44

MDA45

MDA46

MDA47

MDA48

MDA49

MDA50

MDA51

MDA52

MDA53

MDA54

MDA55

MDA56

MDA57

MDA58

MDA59

MDA60

MDA61

MDA62

MDA63

MEM_MA_HOT- 4

MODT_A1 4

MODT_A0 4

-DQSA[0..8]

DQSA[0..8]

DMA[0..8]

MA_CK[0..7]

-DQSB[0..8]

DQSB[0..8]

DMB[0..8]

MB_CK[0..7]

DDR15V

R101

1K/4/1

R23

1K/4/1

DDR15V

R24

1K/4/1

R2

1K/4/1

MDA[0..63] 4

DDR15V Decouple

DDR15V

DDR15V

DDRVTT Decouple

DDRVTT

Device

DIMMA0

DIMMA1

DIMMB0

DIMMB1

DDRVTT

BC152

4.7u/6/X5R/6.3V/K

5

Trace min 10/10

VREFDQ_A

Trace min 10/10

VREFCA_A

BC10

22U/8/X5R/6.3V/M

SMBus 0

8-bit Address (hex)

A0

A4

A2

A6

-DQSA[0..8] 4

DQSA[0..8] 4

DMA[0..8] 4

MA_CK[0..7] 4

-DQSB[0..8] 4

DQSB[0..8] 4

DMB[0..8] 4

MB_CK[0..7] 4

VREFDQ_A

BC131

0.1u/4/Y5V/16V/Z

BC129

0.1u/4/Y5V/16V/Z

BC125

0.1u/4/Y5V/16V/Z

BC11

22U/8/X5R/6.3V/M

BC148

0.1u/4/Y5V/16V/Z

VREFCA_A

4

DDRVTT

VCC3

C283 0.1u/4/X7R/16V/K

C285 0.1u/4/X7R/16V/K

SMBCLK9,11,23

SMBDATA9,11,23

VCC3

SBAB24

SBAB14

SBAB04

CKEB14

CKEB04

-CSB14

-CSB04

-DCLKB24

DCLKB24

-DCLKB14

DCLKB14

MAAB[0..15]4

MEM_MB_RST-4

-SCASB4

-SRASB4

-SWEB4

4

DDR15V

VREFCA_A

VREFDQ_A

MEM_MB_RST-

SMBCLK

SMBDATA

SBAB2

SBAB1

SBAB0

CKEB1

CKEB0

-CSB1

-CSB0

-DCLKB2

DCLKB2

-DCLKB1

DCLKB1

MAAB0

MAAB1

MAAB2

MAAB3

MAAB4

MAAB5

MAAB6

MAAB7

MAAB8

MAAB9

MAAB10

MAAB11

MAAB12

MAAB13

MAAB14

MAAB15

-SCASB

-SRASB

-SWEB

3

DDR3_1

120

VTT

2

VSS

5

VSS

8

VSS

11

VSS

14

VSS

17

VSS

20

VSS

23

VSS

26

VSS

29

VSS

32

VSS

35

VSS

38

VSS

41

VSS

44

VSS

47

VSS

80

VSS

83

VSS

86

VSS

89

VSS

92

VSS

95

VSS

98

VSS

101

VSS

104

VSS

107

VSS

110

VSS

113

VSS

116

VSS

119

VSS

121

VSS

124

VSS

127

VSS

130

VSS

133

VSS

136

VSS

139

VSS

142

VSS

145

VSS

148

VSS

151

VSS

154

VSS

157

VSS

160

VSS

163

VSS

166

VSS

199

VSS

202

VSS

205

VSS

208

VSS

211

VSS

214

VSS

217

VSS

220

VSS

223

VSS

226

VSS

229

VSS

232

VSS

235

VSS

239

VSS

51

VDD

54

VDD

57

VDD

60

VDD

62

VDD

65

VDD

66

VDD

69

VDD

72

VDD

75

VDD

78

VDD

170

VDD

173

VDD

176

VDD

179

VDD

182

VDD

183

VDD

186

VDD

189

VDD

191

VDD

194

VDD

197

VDD

236

VDDSPD

67

VREFCA

1

VREFDQ

118

SCL

238

SDA

237

SA1

117

SA0

52

BA2

190

BA1

71

BA0

169

CKE1

50

CKE0

76

S1*

193

S0*

64

CK1/NU*

63

CK1/NU

185

CK0*

184

CK0

188

A0

181

A1

61

A2

180

A3

59

A4

58

A5

178

A6

56

A7

177

A8

175

A9

70

A10/AP

55

A11

174

A12

196

A13

172

A14

171

A15

168

RESET*

74

CAS*

192

RAS*

73

WE*

3

2

48

FREE

49240

FREEVTT

MEM_MB_HOT-

187

FREE

198

FREE

79

RSVD

MODT_B1

77

ODT1

MODT_B0

195

ODT0

68

NC/PAR_IN

53

NC/ERR_OUT

167

NC/TEST4

DM0/DQS9

NC/DQS9*

DM1/DQS10

NC/DQS10*

DM2/DQS11

NC/DQS11*

DM3/DQS12

NC/DQS12*

DM4/DQS13

NC/DQS13*

DM5/DQS14

NC/DQS14*

DM6/DQS15

NC/DQS15*

DM7/DQS16

NC/DQS16*

DM8/DQS17

NC/DQS17*

DDR3/240/BU/VA/D

Title

Size Document Number Rev

Custom

Date: Sheet

2

MB_CK0

39

CB0

MB_CK1

40

CB1

MB_CK2

45

CB2

MB_CK3

46

CB3

MB_CK4

158

CB4

MB_CK5

159

CB5

MB_CK6

164

CB6

MB_CK7

165

CB7

DQSB0

7

DQS0

-DQSB0

6

DQS0*

DQSB1

16

DQS1

-DQSB1

15

DQS1*

DQSB2

25

DQS2

-DQSB2

24

DQS2*

DQSB3

34

DQS3

-DQSB3

33

DQS3*

DQSB4

85

DQS4

-DQSB4

84

DQS4*

DQSB5

94

DQS5

-DQSB5

93

DQS5*

DQSB6

103

DQS6

-DQSB6

102

DQS6*

DQSB7

112

DQS7

-DQSB7

111

DQS7*

DQSB8

43

DQS8

-DQSB8

42

DQS8*

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

DMB0

125

126

DMB1

134

135

DMB2

143

144

DMB3

152

153

DMB4

203

204

DMB5

212

213

DMB6

221

222

DMB7

230

231

DMB8

161

162

MDB0

3

DQ0

MDB1

4

DQ1

MDB2

9

DQ2

MDB3

10

DQ3

MDB4

122

DQ4

MDB5

123

DQ5

MDB6

128

DQ6

MDB7

129

DQ7

MDB8

12

DQ8

MDB9

13

DQ9

MDB10

18

MDB11

19

MDB12

131

MDB13

132

MDB14

137

MDB15

138

MDB16

21

MDB17

22

MDB18

27

MDB19

28

MDB20

140

MDB21

141

MDB22

146

MDB23

147

MDB24

30

MDB25

31

MDB26

36

MDB27

37

MDB28

149

MDB29

150

MDB30

155

MDB31

156

MDB32

81

MDB33

82

MDB34

87

MDB35

88

MDB36

200

MDB37

201

MDB38

206

MDB39

207

MDB40

90

MDB41

91

MDB42

96

MDB43

97

MDB44

209

MDB45

210

MDB46

215

MDB47

216

MDB48

99

MDB49

100

MDB50

105

MDB51

106

MDB52

218

MDB53

219

MDB54

224

MDB55

225

MDB56

108

MDB57

109

MDB58

114

MDB59

115

MDB60

227

MDB61

228

MDB62

233

MDB63

234

DDR III CHANNEL A

GA-A55M-DS2 1.01

1

MEM_MB_HOT- 4

MODT_B1 4

MODT_B0 4

827Tuesday, August 23, 2011

1

MDB[0..63] 4

of

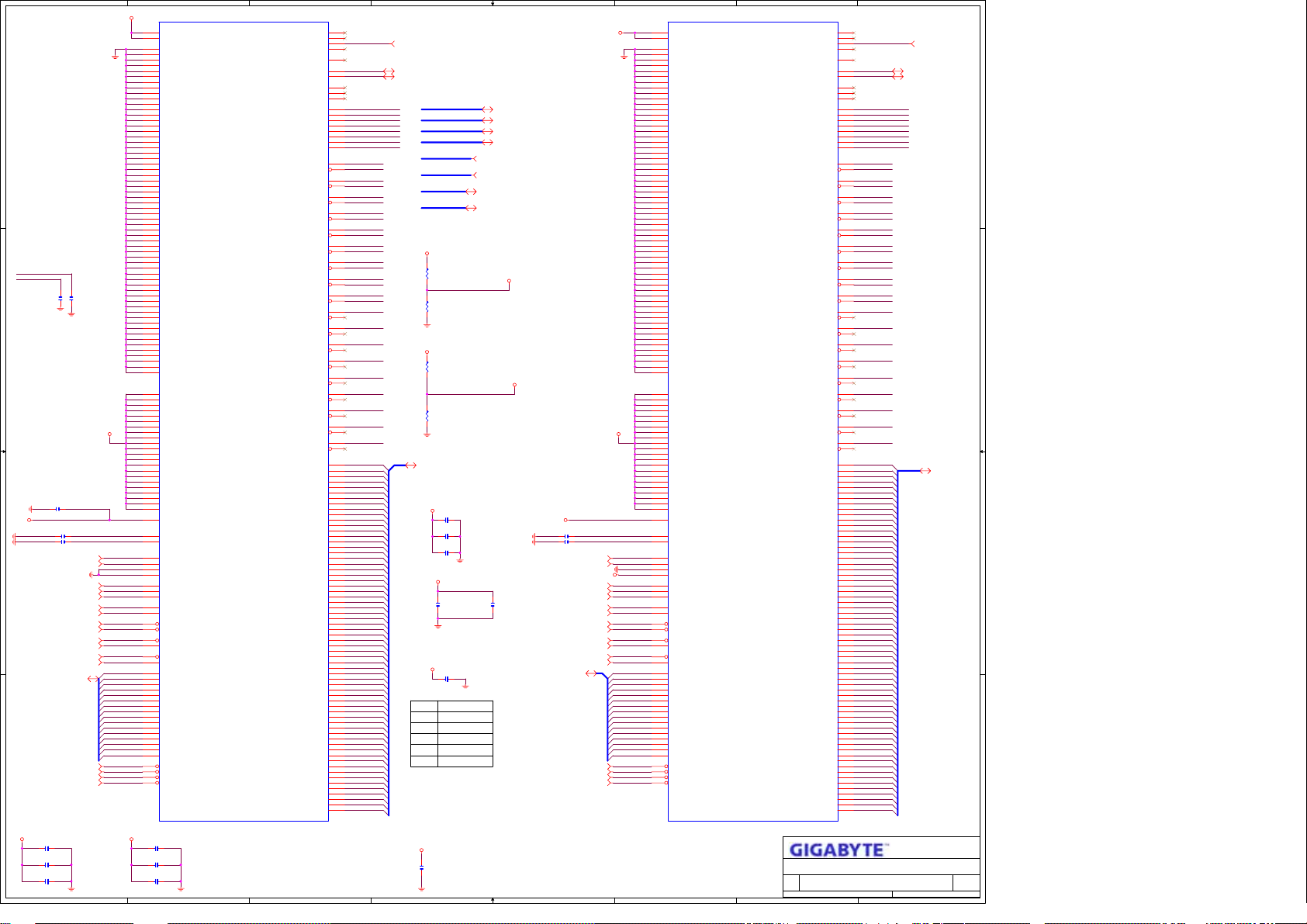

Page 9

5

VCC3

KBC9

1u/4/X5R/6.3V/K

D D

C C

KBC1

0.1u/4/X7R/16V/K

1- PLACE ALL THE SERIES TERMINATION

RESISTORS AS CLOSE TO U800 AS

POSSIBLE

2- ROUTE ALL SRCCLKTx AND SRCCLKCx

AS DIFFERENT PAIR RULE

3- PUT DECOUPLING CAPS CLOSE TO U800

POWER PIN

KBC2

0.1u/4/X7R/16V/K

KBC3

0.1u/4/X7R/16V/K

KC2 22P/4/NPO/50V/J

KC1 22P/4/NPO/50V/J

KBC4

0.1u/4/X7R/16V/K

KX1

14.318M/16p/20ppm/49US/40/D

SMBCLK8,11,23

SMBDATA8,11,23

RESET21,22

VCC3

4

KBC5

0.1u/4/X7R/16V/K

VCC3

KR5 1K/4/1

VCC3

KR0 22/4

KR9 1K/4/1/X

KBC6

0.1u/4/X7R/16V/K

KBC7

0.1u/4/X7R/16V/K

U4

1

VDDHTT

5

VDDREF

20

VDDSRC

21

VDDSRC

30

VDDSB

37

VDDATIG

42

VDD

45

VDDA

49

VDDCPU

9

VDD48

6

GNDREF

12

GND48

19

GNDSRC

22

GNDSRC

29

GNDSB

33

GNDATIG

36

GNDATIG

43

GND

44

GNDA

48

GNDCPU

54

GNDHTT

9LPRS482 / RTM880T-792

7

X1

8

X2

13

SMBCLK

14

SMBDAT

52

*PD#

53

*RESTORE#

KBC10

22u/8/X5R/6.3V/M

**SEL_HTT66/REF0

3

KBC8

0.1u/4/X7R/16V/K

CPUK8_0T

CPUK8_0C

CPUK8_1T

CPUK8_1C

ATIG0T

ATIG0C

ATIG1T

ATIG1C

ATIG2T

ATIG2C

SB_SRC0T

SB_SRC0C

SB_SRC1T

SB_SRC1C

SRC0T

SRC0C

SRC1T

SRC1C

SRC2T

SRC2C

SRC3T

SRC3C

HTT0T/66M

HTT0C/66M

48Mz_0

48Mz_1

REF1

REF2

51

50

47

46

41

40

39

38

35

34

32

31

28

27

26

25

24

23

18

17

16

15

56

55

11

10

4

3

2

SIO_CLOCK_R

48M_USB_R

KR6 1K/4/1

KR7 1K/4/1/X

NB CLOCK INPUT TABLE

NB CLOCKS

HT_REFCLKP

HT_REFCLKN

REFCLK_P

REFCLK_N

GFX_REFCLK*

GPP_REFCLK

GPPSB_REFCLK 100M DIFF 100M DIFF

DISP_CLKP 5

DISP_CLKN 5

APUCLKP 5

APUCLKN 5

SRCCLK_1XP 14

SRCCLK_1XN 14

SRCCLK_LAN 26

-SRCCLK_LAN 26

SBSRC_CLKP 10

SBSRC_CLKN 10

SRCCLK_16XP 14

SRCCLK_16XN 14

KR3 22/4

KR4 22/4

VCC3

RS740 RX780 RS780

66M SE(SE)

NC

14M SE (3.3V) 14M SE (1.8V) 14M SE (1.1V)

NC NC vref

100M DIFF

NC

100M DIFF

* the GFX_REFCLK input is required for all cases

LPC48 16

USB48M 11

2

100M DIFF

100M DIFF

100M DIFF

100M DIFF

100M DIFF

100M DIFF

100M DIFF

100M DIFF(OUT)

1

100M DIFF

100M DIFF

B B

Clock chip has internal serial terminations

for differencial pairs, external resistors are

reserved for debug purpose.

watch dog --

接

RESTORE#

A A

RS740

RX780

RS780

(Single-ended)

RESET

OSC_14M_NB

3.3V 33R serial

1.8V 82.5R/130R

1.1V 158R/90.9R

REF0/SEL_HTT66 HTT CLOCK

0

1

REF1/SEL_SATA

0

1

5

100.00 DIFFERENTIAL

66.66 SINGLE END

SRC6/SATA

100.00 DIFFERENTIAL SPREADING SRC CLOCK

100.00 NON-SPREADING DIFFERENTIAL SATA CLOCK

4

RTM880T-792_TSSOP56/[10HL6-1A0880-30R]

3

Title

Size Document Number Rev

Custom

2

Date: Sheet

RTM880T-792

GA-A55M-DS2 1.01

1

of

927Tuesday, August 23, 2011

Page 10

5

PLACE THESE PCIE AC COUPLING

CAPS CLOSE TO SB850

D D

APUPCIE_RST-14,26

A_RX0P6

A_RX0N6

A_RX1P6

A_RX1N6

A_RX2P6

A_RX2N6

A_RX3P6

A_RX3N6

S.B HEATSINK

1

1

SB_HS

VCC_SB

For APU PCI_E devices.

PR2 33/4

PR3 33/4

-A_RST16

PC3 0.1U/4/X7R/16V/K

PC4 0.1U/4/X7R/16V/K

PC5 0.1U/4/X7R/16V/K

PC6 0.1U/4/X7R/16V/K

PC7 0.1U/4/X7R/16V/K

PC8 0.1U/4/X7R/16V/K

PC9 0.1U/4/X7R/16V/K

PC10 0.1U/4/X7R/16V/K

A_TX0P6

A_TX0N6

A_TX1P6

A_TX1N6

A_TX2P6

A_TX2N6

A_TX3P6

A_TX3N6

PR5 590/4/1

PR4 2K/4/1

2

2

SB_HS/[12SP2-SA0301-01R_12SP2-SA0301-02R_12SP2-SA0301-03R]

C C

B B

VCC_SB

PR45 2K/4/1

SBSRC_CLKP9

SBSRC_CLKN9

RTC_XI

PR6 20M/4

1 2

3 4

PC13

A A

18P/4/NPO/50V/J

PX1

SHW/D0.64*5.08*6.74

RTC_XO

PX1

32.768K/12.5p/20ppm/TF38/35K/D

PC14

18P/4/NPO/50V/J

5

PR7 1M/4

PX2

1 2

25M/20p/30ppm/49US/20/D

PC15

22P/4/NPO/50V/J

4

UMI_TXP0

UMI_TXN0

UMI_TXP1

UMI_TXN1

UMI_TXP2

UMI_TXN2

UMI_TXP3

UMI_TXN3

25MHZ_X1

25MHZ_X2

PC16

22P/4/NPO/50V/J

4

AD5

AE30

AE32

AD33

AD31

AD28

AD29

AC30

AC32

AB33

AB31

AB28

AB29

AF29

AF31

W30

W32

AB26

AB27

AA24

AA23

AA27

AA26

W27

W26

W24

W23

AE2

Y33

Y31

Y28

Y29

V33

V31

V27

V26

F27

G30

G28

R26

T26

H33

H31

T24

T23

K29

H27

H28

K26

F33

F31

E33

E31

M23

M24

M27

M26

N25

N26

R23

R24

N27

R27

C31

C33

J30

J27

J26

U1E

PCIE_RST#

A_RST#

UMI_TX0P

UMI_TX0N

UMI_TX1P

UMI_TX1N

UMI_TX2P

UMI_TX2N

UMI_TX3P

UMI_TX3N

UMI_RX0P

UMI_RX0N

UMI_RX1P

UMI_RX1N

UMI_RX2P

UMI_RX2N

UMI_RX3P

UMI_RX3N

PCIE_CALRP

PCIE_CALRN

GPP_TX0P

GPP_TX0N

GPP_TX1P

GPP_TX1N

GPP_TX2P

GPP_TX2N

GPP_TX3P

GPP_TX3N

GPP_RX0P

GPP_RX0N

GPP_RX1P

GPP_RX1N

GPP_RX2P

GPP_RX2N

GPP_RX3P

GPP_RX3N

CLK_CALRN

PCIE_RCLKP

PCIE_RCLKN

DISP_CLKP

DISP_CLKN

DISP2_CLKP

DISP2_CLKN

APU_CLKP

APU_CLKN

SLT_GFX_CLKP

SLT_GFX_CLKN

GPP_CLK0P

GPP_CLK0N

GPP_CLK1P

GPP_CLK1N

GPP_CLK2P

GPP_CLK2N

GPP_CLK3P

GPP_CLK3N

GPP_CLK4P

GPP_CLK4N

GPP_CLK5P

GPP_CLK5N

GPP_CLK6P

GPP_CLK6N

GPP_CLK7P

GPP_CLK7N

GPP_CLK8P

GPP_CLK8N

14M_25M_48M_OSC

25M_X1

25M_X2

HUDSON-2

Part 1 of 5

PCI

CLKS

PCI EXPRESS

INTERFACES

PCI

CLOCK

GENERATOR

APU

S5

HUDSON-D2/[10HB1-0600D2-10R]

PCICLK4/14M_OSC/GPO39

INTERFACE

REQ2#/CLK_REQ8#/GPIO41

REQ3#/CLK_REQ5#/GPIO42

GNT2#/SD_LED/GPO45

GNT3#/CLK_REQ7#/GPIO46

LPC

LDRQ1#/CLK_REQ6#/GP IO4 9

PLUS

INTRUDER_ALERT#

PCICLK0

PCICLK1/GPO36

PCICLK2/GPO37

PCICLK3/GPO38

PCIRST#

AD0/GPIO0

AD1/GPIO1

AD2/GPIO2

AD3/GPIO3

AD4/GPIO4

AD5/GPIO5

AD6/GPIO6

AD7/GPIO7

AD8/GPIO8

AD9/GPIO9

AD10/GPIO10

AD11/GPIO11

AD12/GPIO12

AD13/GPIO13

AD14/GPIO14

AD15/GPIO15

AD16/GPIO16

AD17/GPIO17

AD18/GPIO18

AD19/GPIO19

AD20/GPIO20

AD21/GPIO21

AD22/GPIO22

AD23/GPIO23

AD24/GPIO24

AD25/GPIO25

AD26/GPIO26

AD27/GPIO27

AD28/GPIO28

AD29/GPIO29

AD30/GPIO30

AD31/GPIO31

FRAME#

DEVSEL#

REQ1#/GPIO40

GNT1#/GPO44

CLKRUN#

INTE#/GPIO32

INTF#/GPIO33

INTG#/GPIO34

INTH#/GPIO35

LPCCLK0

LPCCLK1

LFRAME#

LDRQ0#

SERIRQ/GPIO48

DMA_ACTIVE#

PROCHOT#

APU_PG

LDT_STP#

APU_RST#

32K_X1

32K_X2

S5_CORE_EN

RTCCLK

VDDBT_RTC_G

3

CBE0#

CBE1#

CBE2#

CBE3#

IRDY#

TRDY#

STOP#

PERR#

SERR#

REQ0#

GNT0#

LOCK#

3

2

1

VCC3

PCLK0

PCLK3

PCLK4

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

AD8

AD9

AD10

AD11

AD12

AD13

AD14

AD15

AD16

AD17

AD18

AD19

AD20

AD21

AD22

AD23

AD24

AD25

AD26

AD27

AD28

AD29

AD30

AD31

-C_BE0

-C_BE1

-C_BE2

-C_BE3

-FRAME

-DEVSEL

-IRDY

-TRDY

PAR

-STOP

-PERR

-SERR

-REQ0

-GNT0

-PLOCK

-INTA

-INTB

-INTC

-INTD

LPC_CLK0

LPC_CLK1

LAD0

LAD1

LAD2

LAD3

-LFRAME

-LDRQ0

SERIRQ

-DMA_ACTIVE

-PROCHOT_CPU

-CPURST

RTC_XI

RTC_XO

RTC_CLK

-INTR_ALERT

PR8 33/4

PR9 33/4

PR13 33/4

-FRAME 15

-STOP 15

-PERR 15

-SERR 15

-REQ0 15

-GNT0 15

-PLOCK 15

-INTA 15

-INTB 15

-INTC 15

-INTD 15

PR0 8.2K/4

-DMA_ACTIVE 5

Note: LDT_STP# leave NC--DG1.0

PR27 100K/4/1

RTCVDD

PBC2

0.1U/6/X7R/25V/K

AF3

AF1

AF5

AG2

AF6

AB5

AJ3

AL5

AG4

AL6

AH3

AJ5

AL1

AN5

AN6

AJ1

AL8

AL3

AM7

AJ6

AK7

AN8

AG9

AM11

AJ10

AL12

AK11

AN12

AG12

AE12

AC12

AE13

AF13

AH13

AH14

AD15

AC15

AE16

AN3

AJ8

AN10

AD12

AG10

AK9

AL10

AF10

PAR

AE10

AH1

AM9

AH8

AG15

AG13

AF15

AM17

AD16

AD13

AD21

AK17

AD19

AH9

AF18

AE18

AC16

AD18

B25

D25

LAD0

D27

LAD1

C28

LAD2

A26

LAD3

A29

A31

B27

AE27

AE19

G25

E28

E26

G26

F26

G2

G4

H7

F1

F3

E6

LPC33

PCICLK1PCLK1

-PPCIRST

-C_BE0 15

-C_BE1 15

-C_BE2 15

-C_BE3 15

-DEVSEL 15

-IRDY 15

-TRDY 15

PAR 15

-PROCHOT_CPU 5

CPU_PG_SB 5

-CPURST 5

AD[0..31] 15

LAD0 16

LAD1 16

LAD2 16

LAD3 16

-LFRAME 16

-LDRQ0 16

VCC3

SERIRQ 16

S5_CORE_EN 24

RTCVDD

LPC33 16

PCICLK1 15

-PPCIRST 15

VBAT16

VBAT_2

RB 1K/4/1

12

BAT

BAT-SK/BK/P/S/D/SN

CR2032

+

3VDUAL_SB

20mil

BAT

CR2032

PCLK1

Low: Force PCIE GEN1, Up: Allow PCIE GEN2

PCLK3

PCLK4

CLKGEN Mode: Only for integrated clock mode.

LPC_CLK0

LPC_CLK1

PULL

HIGH

PULL

LOW

PQ1

BAT54C/SOT23/200mA

CLR_CMOS

SHORT

NOT ADD ICT FOR RTCVDD PIN

PR14 8.2K/4

PR92 8.2K/4

PCLK3

USE

PULL

DEBUG

HIGH

STRAPS

IGNORE

PULL

DEBUG

LOW

STRAPS

DEFAULT

LPC_CLK0

IMC

ENABLED

AOD Extreme

IMC

DISABLED

DEFAULT

20mil20mil

PR28 1K/4/1

PBC24

0.1U/6/X7R/25V/K

CLR_CMOS

RTCVDD

PH/1*2/BK/2.54/VA/D

CLEAR CMOS

NORMALOPEN

PR17 8.2K/4

PR20 8.2K/4

PR22 8.2K/4

LPC_CLK1

CLKGEN

ENABLED

CLKGEN

DISABLED

DEFAULT

RTCVDD

PBC25

1U/6/Y5V/10V/Z

VCC3

3VDUAL_SB

RTC_CLK

PR90 8.2K/4/X

PR97 2.2K/4/1

Pull down for S5+ Mode

2

Title

Hudson D3 PCIE/PCI/CPU/LPC

Size Document Number Rev

Custom

Date: Sheet

GA-A55M-DS2 1.01

1

of

10 27Tuesday, August 23, 2011

Page 11

5

VCC3

PBC4

PBC5

PR55 1K/4/1

PR56 1K/4/1

PR34 8.2K/4/X

PR57 2.2K/4/1

PR58 2.2K/4/1

PR60 2.2K/4/1/X

PBC6

100P/4/NPO/50V/J/X

3VDUAL_SB

22P/4/N/50V/XPC17

-SYS_RST21

PR68 22/4PR59 8.2K/4/1

-PCIE_WAKE14,26

THERMTRIP_CPU_L5

3VDUAL_SB

SMBCLK8,9,23

SMBDATA8,9,23

SMBCLK114

SMBDATA114

SMBCLK

SMBDATA

D D

-RI

SMBCLK1

SMBDATA1

-PCIE_WAKE

Pull up for S5+ Mode.

-PCIPME

SB_PWROK

100p/4/NPO/50V/J

SMBCLK

SMBDATA

100P/4/NPO/50V/J/X

AZ_BIT_CLK

C C

PBC7

100P/4/NPO/50V/J/X

AZ_SDATA_OUT19

AZ_SDATA_IN019

-RSMRST

5VSB

3

D

PQ6

GS

2

1

2N7002/SOT23/25pF/5

B B

PR33

8.2K/4

PQ9

MMBT2222A/SOT23/600mA/40

SOT23

VCC11_DUAL

A A

PR18 1K/4/1

132

PBC21

100P/4/NPO/50V/J/X

VCC3

-RI17

-SLP_S316,22

SLP_S5-22

-PSOUT16

SB_PWROK22

VCC3

PR91 20K/4/1

SPKR21

AZ_BIT_CLK19

AZ_SYNC19

-AZ_RST19

4

For FCH PCI_E devices.

PR46 8.2K/4/1

SLP_S5-

PR69 0/4/SHT/X

A20GATE16

-KBRST16

-PCIPME15,16

GP5316

THERMTRIP_CPU_L

PR67 300/4

DG. 1.20

AC_PRES16

-USBOC_R126

-USBOC_F117

-RI

-PWRBTN

A20GATE

-KBRST

-PCIPME

-PCIE_WAKE

WD_PWRGD

-RSMRST

PBC3

2.2u/6/X5R/6.3V/K

SPKR

SMBCLK

SMBDATA

SMBCLK1

SMBDATA1

PR63 22/4

PR64 22/4

PR65 22/4

PR66 22/4

IMC_TDO

IMC_TMS

IMC_TCK

U1A

PCIE_RST2#/GEVENT4#

AB6

RI#/GEVENT22#

R2

SPI_CS3#/GBE_STAT1/GEVENT21#

W7

SLP_S3#

T3

SLP_S5#

W2

PWR_BTN#

J4

PWR_GOOD

N7

TEST0

T9

TEST1/TMS

T10

TEST2

V9

GA20IN/GEVENT0#

AE22

KBRST#/GEVENT1#

AG19

PME#/GEVENT3#

R9

LPC_SMI#/GEVENT23#

C26

LPC_PD#/GEVENT5#

T5

SYS_RESET#/GEVENT19#

U4

WAKE#/GEVENT8#

K1

IR_RX1/GEVENT20#

V7

THRMTRIP#/SMBALERT#/GEVENT2#

R10

WD_PWRGD

AF19

RSMRST#

U2

CLK_REQ4#/SATA_IS0#/GPIO64

AG24

CLK_REQ3#/SATA_IS1#/GPIO63

AE24

SMARTVOLT1/SATA_IS2#/GPIO50

AE26

CLK_REQ0#/SATA_IS3#/GPIO60

AF22

SATA_IS4#/FANOUT3/GPIO5 5

AH17

SATA_IS5#/FANIN3/GPIO59

AG18

SPKR/GPIO66

AF24

SCL0/GPIO43

AD26

SDA0/GPIO47

AD25

SCL1/GPIO227

T7

SDA1/GPIO228

R7

CLK_REQ2#/FANIN4/GPIO62

AG25

CLK_REQ1#/FANOUT4/GPIO61

AG22

IR_LED#/LLB#/GPIO184

J2

SMARTVOLT2/SHUTDOWN#/GPIO51

AG26

DDR3_RST#/GEVENT7#/VGA_PD

V8

GBE_LED0/GPIO183

W8

SPI_HOLD#/GBE_ LED1/GEVENT9#

Y6

GBE_LED2/GEVENT10#

V10

GBE_STAT0/GEVENT11#

AA8

CLK_REQG#/GPIO65/OSCIN/IDLEEXIT#

AF25

BLINK/USB_OC7#/GEVENT18#

M7

USB_OC6#/IR_TX 1/GEVENT6#

R8

USB_OC5#/IR_TX 0/GEVENT17#

T1

USB_OC4#/IR_RX0/GEVENT16#

P6

USB_OC3#/AC_PR ES/TDO/GEVENT15#

F5

USB_OC2#/TCK/GEVENT14#

P5

USB_OC1#/TDI/GEVENT13#

J7

USB_OC0#/SPI_T PM_CS#/TRST#/GEVENT12#

T8

AZ_BITCLK

AB3

AZ_SDOUT

AB1

AZ_SDIN0/GPIO167

AA2

AZ_SDIN1/GPIO168

Y5

AZ_SDIN2/GPIO169

Y3

AZ_SDIN3/GPIO170

Y1

AZ_SYNC

AD6

AZ_RST#

AE4

PS2_DAT/SDA4/GPIO187

K19

PS2_CLK/CEC/SCL4/GPIO188

J19

SPI_CS2#/GBE_STAT2/GPIO166

J21

PS2KB_DAT/GPIO189

D21

PS2KB_CLK/GPIO190

C20

PS2M_DAT/GPIO191

D23

PS2M_CLK/GPIO192

C22

KSO_0/GPIO209

F21

KSO_1/GPIO210

E20

KSO_2/GPIO211

F20

KSO_3/GPIO212

A22

KSO_4/GPIO213

E18

KSO_5/GPIO214

A20

KSO_6/GPIO215

J18

KSO_7/GPIO216

H18

KSO_8/GPIO217

G18

KSO_9/GPIO218

B21

KSO_10/GPIO219

K18

KSO_11/GPIO220

D19

KSO_12/GPIO221

A18

KSO_13/GPIO222

C18

KSO_14/XDB0/GPIO223

B19

KSO_15/XDB1/GPIO224

B17

KSO_16/XDB2/GPIO225

A24

KSO_17/XDB3/GPIO226

D17

HUDSON-D2/[10HB1-0600D2-10R]

HUDSON-2

Part 4 of 5

EMBEDDED CTRL

?

3

USBCLK/14M_25M_48M_OSC

USB

USB

ACPI / WAKE UP

EVENTS

GPIO

USB

OC

HD

AUDIO

USB_FSD1P/GPIO186

MISC

USB_FSD0P/GPIO185

1.1

USB

2.0

USB

3.0

EC_PWM0/EC_TIMER0/GPIO197

EC_PWM1/EC_TIMER1/GPIO198

EC_PWM2/EC_TIMER2/WOL_EN/GPIO199

EC_PWM3/EC_TIMER3/GPIO200

USB_RCOMP

USB_FSD1N

USB_FSD0N

USB_HSD13P

USB_HSD13N

USB_HSD12P

USB_HSD12N

USB_HSD11P

USB_HSD11N

USB_HSD10P

USB_HSD10N

USB_HSD9P

USB_HSD9N

USB_HSD8P

USB_HSD8N

USB_HSD7P

USB_HSD7N

USB_HSD6P

USB_HSD6N

USB_HSD5P

USB_HSD5N

USB_HSD4P

USB_HSD4N

USB_HSD3P

USB_HSD3N

USB_HSD2P

USB_HSD2N

USB_HSD1P

USB_HSD1N

USB_HSD0P

USB_HSD0N

USBSS_CALRP

USBSS_CALRN

USB_SS_TX3P

USB_SS_TX3N

USB_SS_RX3P

USB_SS_RX3N

USB_SS_TX2P

USB_SS_TX2N