Gigabyte Ga-9ivdpc_11 Schematics

第 1 頁,共 1 頁Technical Information Release Notice

Technical Information Release Notice

Doc Type Schematic Date 2005/6/17 下午 06:15:58

Project Code S93058-0 Customer

Project Name GS-SR195 Revision Old NA New 1.1

Model Name GA-9IVDPC IT Doc No DR056214

P/N RD Doc No

PCB Rev. 1.1 Check Sum

R N M

P/N Description

Description

Remark

Approved By daniel.hou 2005/6/17 下午 08:13:43 Applicant leopard.hsieh

Research

Management

Mimosa.Kao

2005/6/20 上午

10:25:30

Validation Manager Project Manager

Effected Class

gfedc gfedcb gfedc

A B C D E F

gfedc

gfedcb

A B

gfedc gfedcb

gfedc gfedc

gfedc gfedc

I

I

T

T

R

R

e

e

s

s

e

e

a

a

r

r

c

c

2

2

h

h

0

0

M

M

0

0

5

5

a

a

/

/

n

n

6

6

/

/

a

a

2

2

g

g

0

0

e

e

m

m

e

e

n

n

t

t

FinePrint - www.fineprint.com 用 列印 可在 訂購

2005/6/20http://10.1.1.15/ef2kweb/CHT/Forms/RTC009/RTC009_P.asp

Mimosa.Kao

5

4

3

2

1

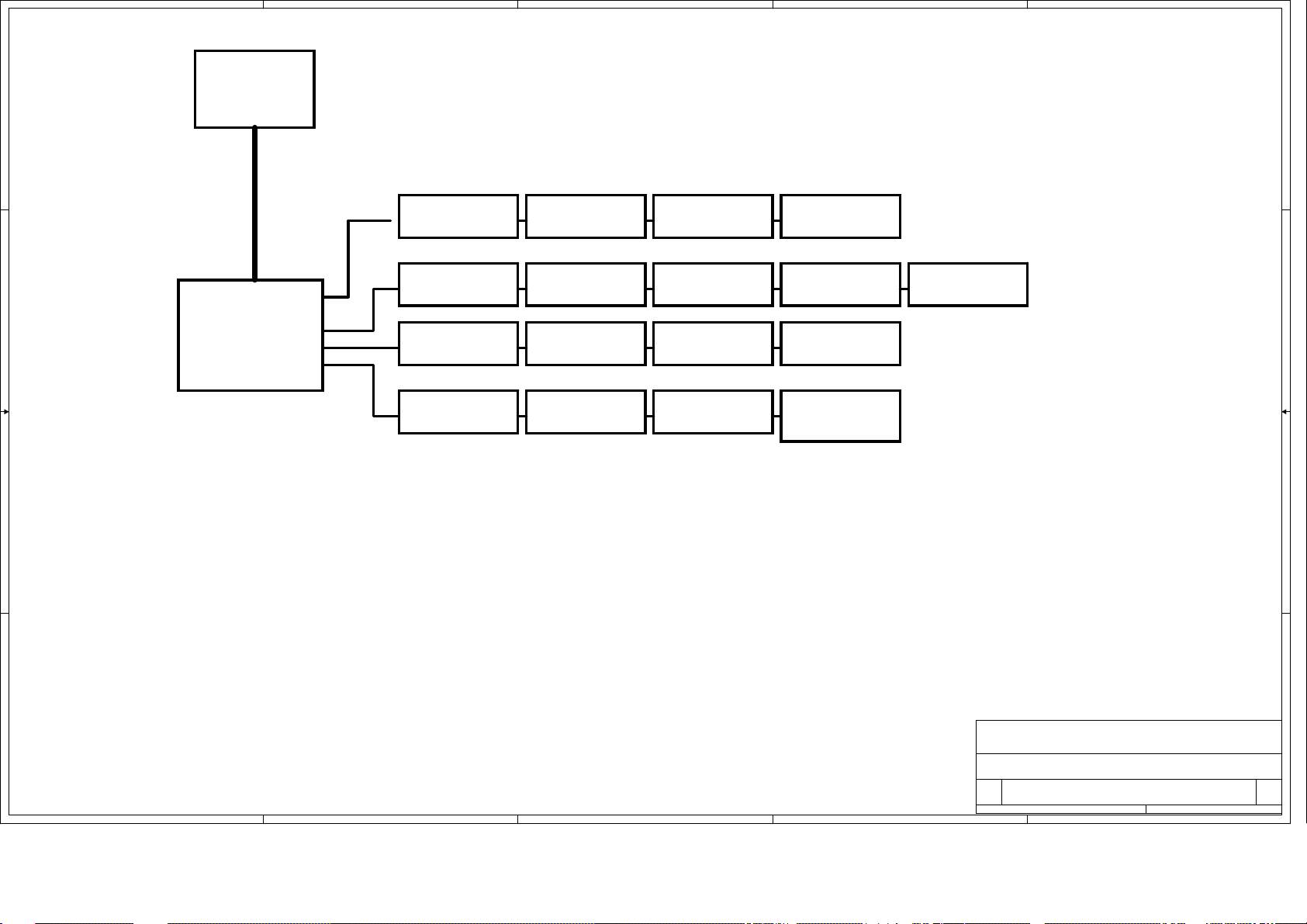

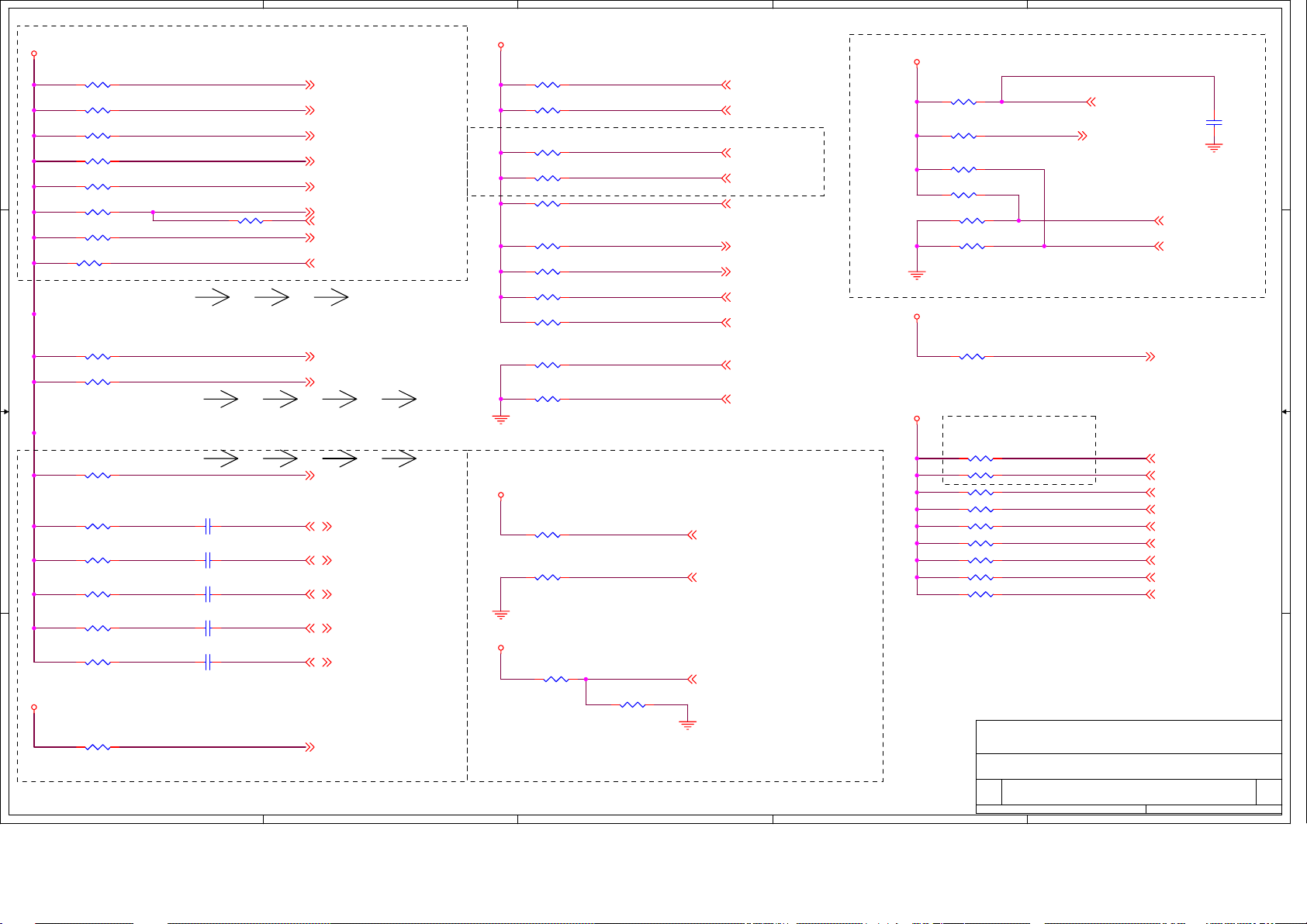

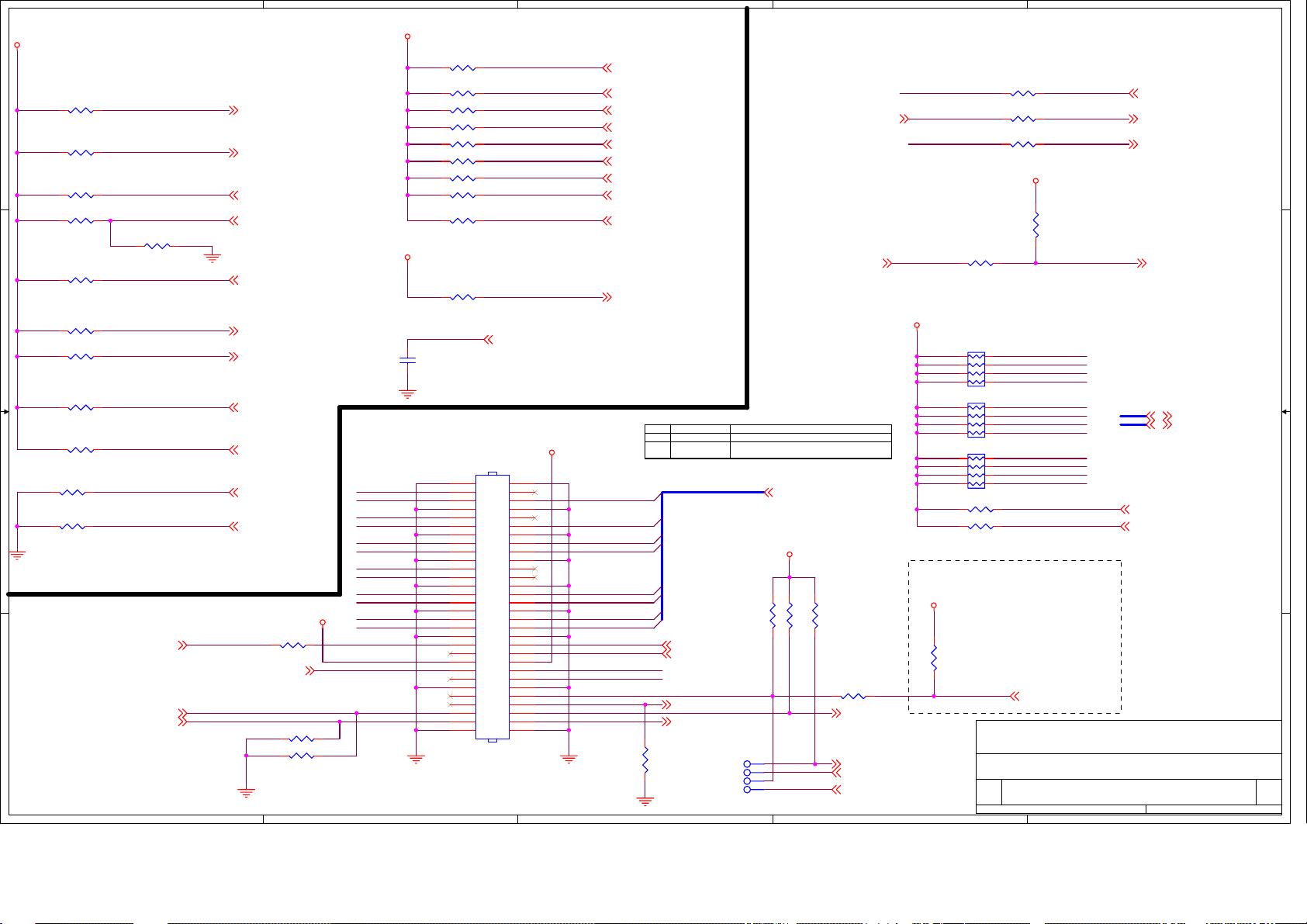

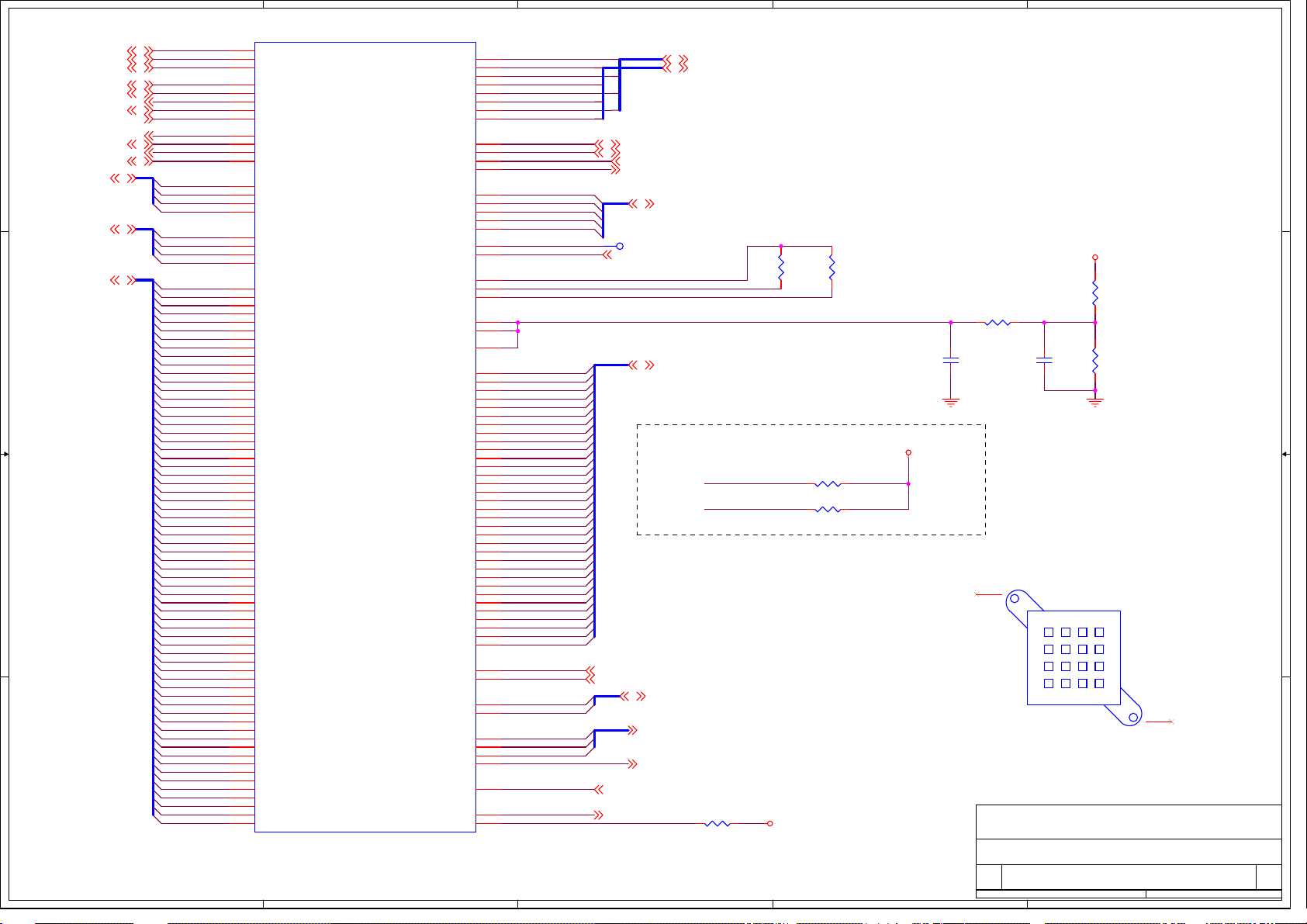

LV-NOCONA800/ LINDENHURST

GA-9IVDPC V1.1

D D

01_TITLE

02_SYS BLOCK

03_SYS RESET

04_CLOCK BLOCK

05_SMBUS

06_POWER FLOW

07_PCI ROUTING_GPIO

08_CPU1 SYSTEM INTERFACE

C C

09_CPU1 TERMINATION

10_CPU1 POWER/GND

11_CPU2 SYSTEM INTERFACE

12_CPU1 POWER/GND

13_CPU1 TERMINATION/ITP

14_LEVEL SHIFT&CPU REDUCTION

15_MCH DDR266 CHANNEL A

16_MCH DDR266 CHANNEL B

17_MCH HI1.5&MISC

B B

18_MCH SYSTEM BUS

19_MCH PCI EXPRESS

20_MCH PWR/GND

21_MCH DECOUPLING

22_DDR266 CHANNEL A DIMMA1

23_DDR266 CHANNEL A DIMMA2

24_DDR266 CHANNEL A DIMMA3

25_DDR266 CHANNEL A DIMMA4

26_DDR266 CHANNEL A TERM/DECOUP

27_DDR266 CHANNEL A DIMMB1

A A

28_DDR266 CHANNEL A DIMMB2

29_DDR266 CHANNEL A DIMMB3

30_DDR266 CHANNEL A DIMMB4

5

31_DDR266 CHANNEL B TERM/DECOUP 61_P2V5 & P1V25_VTT

32_CK409B CLOCK GENERATOR

33_CK409B CLOCK TERMINATION

34_DB400 100NHZ BUFFER

35_PCIE X8 SLOT

36_HR PCI/HI/IDE/LPC/GPIO

37_HR SATA/GPIO/CPU/PCI-X

38_HR PWR/GND

39_HR IDE CONNECTOR

40_AIC-8130 PCIX/SATA

62_CPU1 VOLTERRA VRD

63_CPU2 VOLTERRA VRD

64_BROADCOM PCIE BCM5721

65_BROADCOM PCI BCM5705

66_IPMI & ID SWITCH

67_SMBUS MULTIPLEXER

68_COUPON

69_HISTORY

70_HISTORY

41_AIC-8130 POWER 1.2V/2.5V

42_AIC-8130 GPIO

43_AIC7901 PCIX INTERFACE

44_AIC-7901 SCSI CHANNEL

45_AIC-7901 TERMINATORS

46_AIC-7901 POWER & ZCR

47_ATI RAGE XL

48_ATI BUFFER & SDRAM

49_VGA CONNECTOR

50_SO-DIMM ZCR

51_PCIX SLOT_66MHZ

52_GLUE LOGIC CIRCUIT

53_IT8712F-IX SIO

54_FAN CONTROL

55_COM1 & KB/MOUSE

56_FRONT PANEL

57_ATX POWER CONNECTOR

3.70 mil

3.70 mil

11.1 mil

10.0 mil

11.1 mil

3.70 mil

3.70 mil

58_BIOS

59_USB

60_P1V5 & P_VTT

4

3

BOARD STACK-UP

PP 2116

CORE

PP 2116+7628

CORE

PP 2116+7628

CORE

PP 2116

2

COMPONENT SIDE

GND

INT 1

(PWR)

INT 2

SOLDER SIDE

Title

Size Document Number Rev

Date: Sheet

GIGA-BYTE TECHNOLOGY CO., LTD.

COVER SHEET

GA-9IVDPC

1

1.5 OZ

1 OZ

1 OZ

2 OZ

2 OZ(PWR)

1 OZ

1 OZGND

1.5 OZ

170Tuesday, June 14, 2005

2.0 mil

1.35 mil

1.35 mil

2.7 mil

2.7 mil

1.35 mil

1.35 mil

2.0 mil

of

1.1

5

4

3

2

1

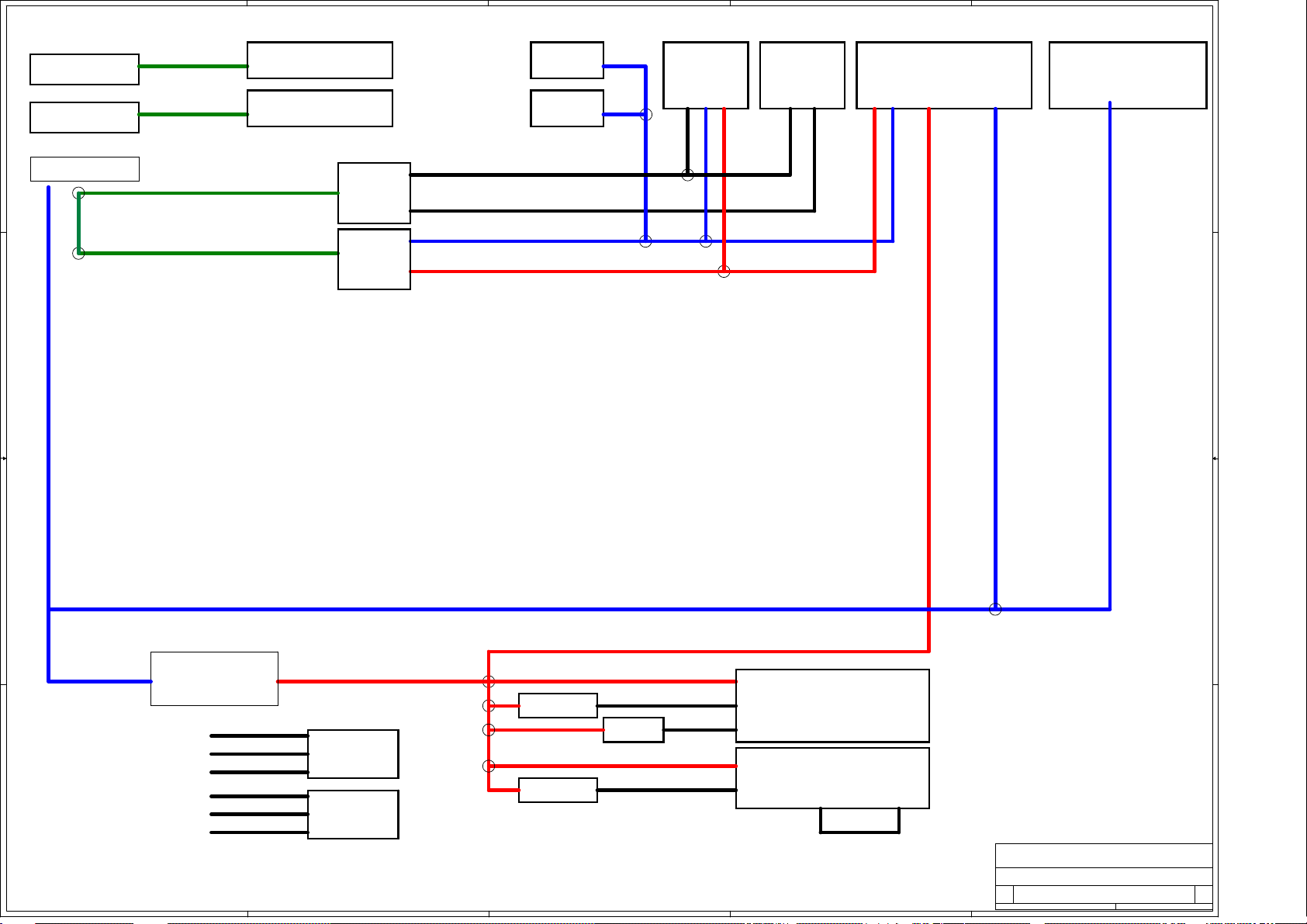

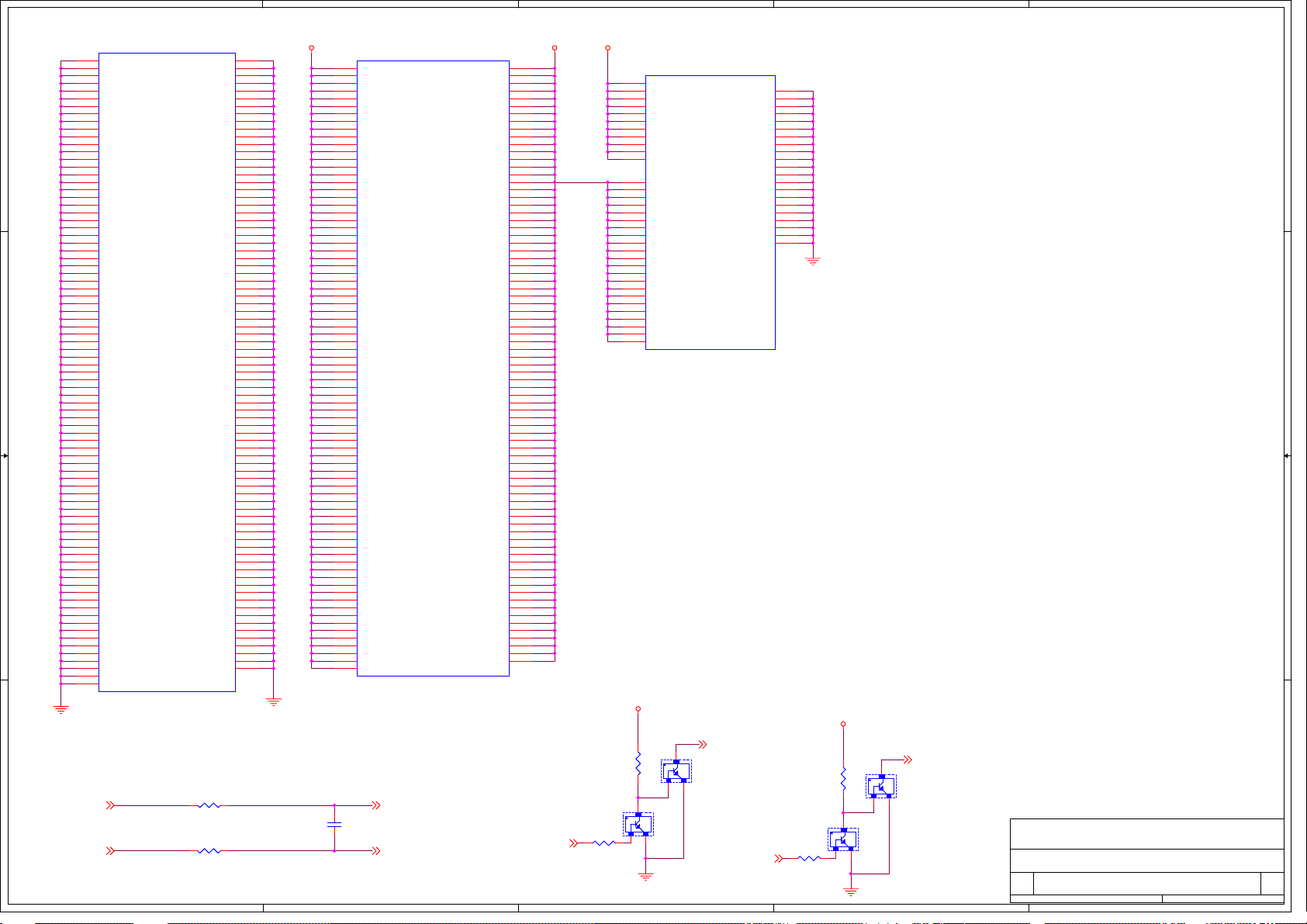

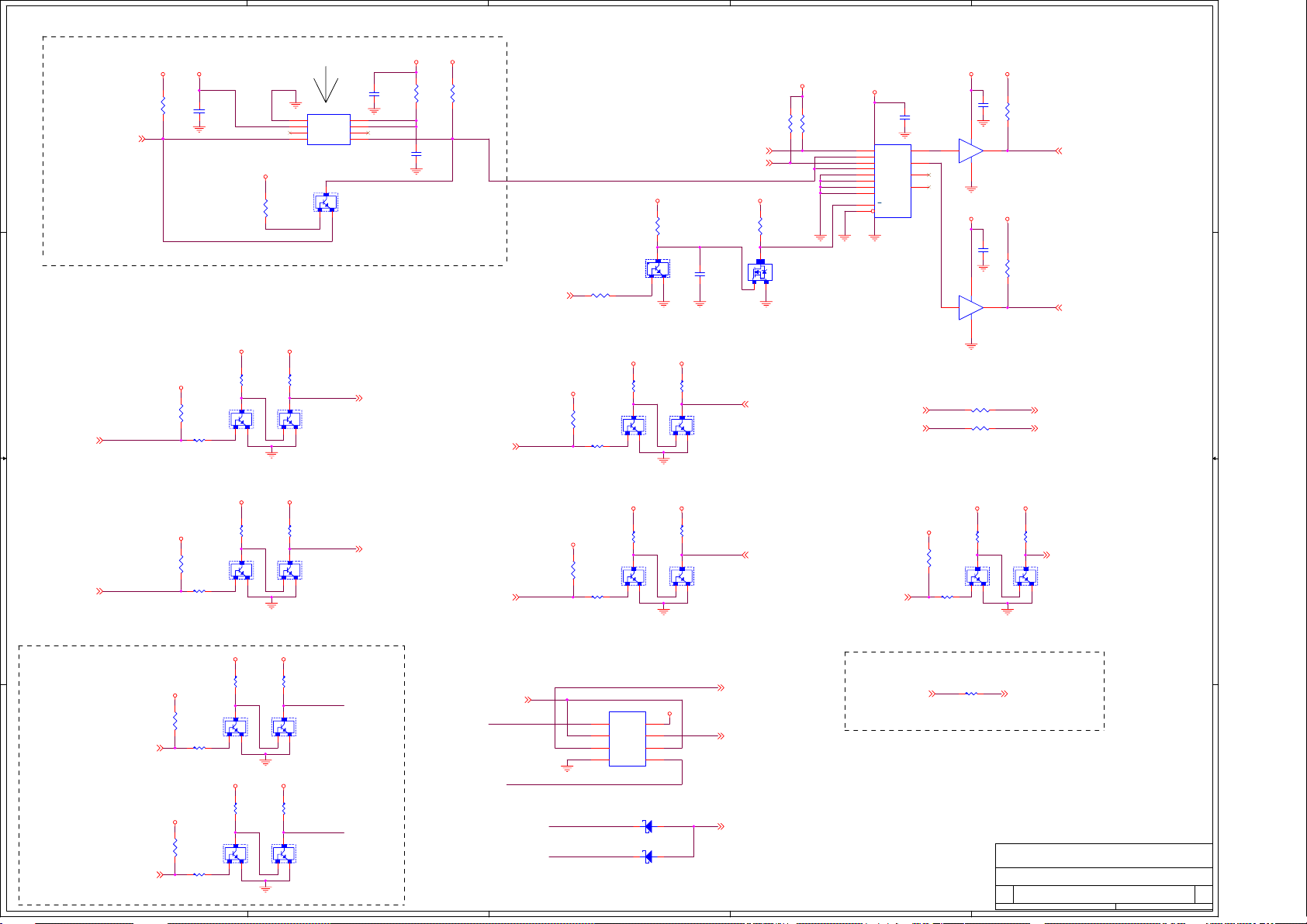

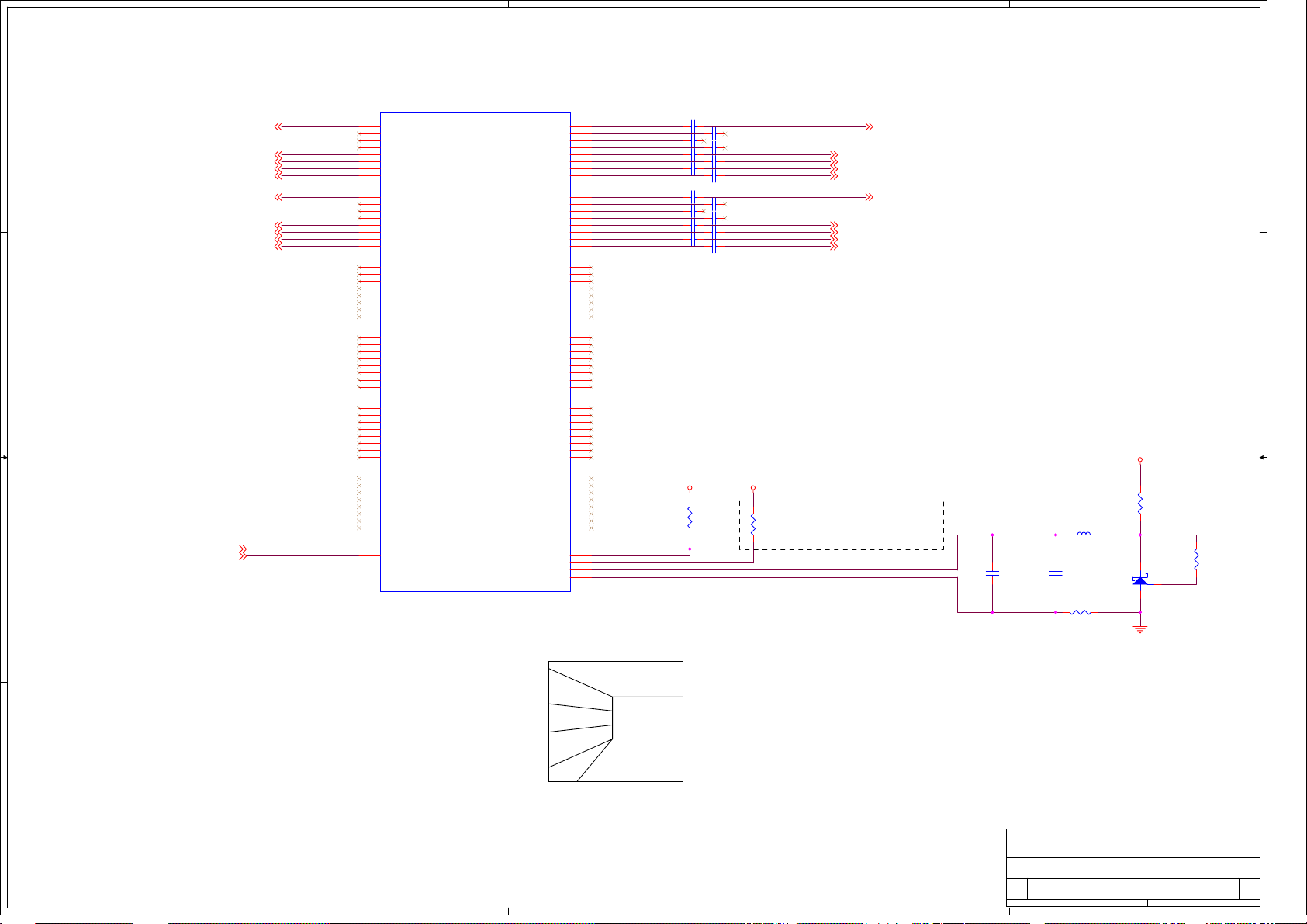

EVRD 10.1

Intel Xeon

D D

RJ45

LAN

BROADCOM

BCM5751

PCI-E SLOT(X4)

X4

PCI EXPRESS X8 ( 16GB/S)

GbE MAC/PHY

X1

Processor

CPU 0

6.4GB/s

System Bus(800MT/S)

Intel

Lindenhurst

EVRD 10.1

Intel Xeon

Processor

CPU 1

2.1GB/s up to 2.7GB/s

Channel A

DDR266(X4)/333(X3)DIMMModuleX4

Channel B

VS

C C

ZCR SO-DIMM

PCI-X 66MHZ SLOT

RJ45

LAN

68PIN SCSI CON

SATAx4

AIC8130

AIC7901

HUB INTERFACE 1.5

266MB/s

PCI-X (64/66)

Hance

2.1GB/s up to 2.7GB/s

150MB/s

SATAx2

USB

DDR266(X4)/333(X3)DIMMModuleX4

Rear Panel USB 2.0X2

Rapids

B B

BCM5705

PCI 32 Bit BUS 133MB/s

ESB6300

IDE Connector * 1IDE BusATA-100

8MB

SDRAM

ATI Rage XL

VGA

Intel

FWH

LPC

IPMI

Front USB

SST49LF004B

VGA CON

IT8712IX

LPC Super I/O

128 PQFP

A A

COM1 LPT/GPIO

5

4

COM2 for

LCD Module

3

GIGA-BYTE TECHNOLOGY CO., LTD.

Title

Size Do c um e n t N u mb er Re v

2

Date: Sheet

BLOCK DIAGRAM

GA-9IVDPC

1

270Tuesday, Ju ne 14, 2005

1.1

of

5

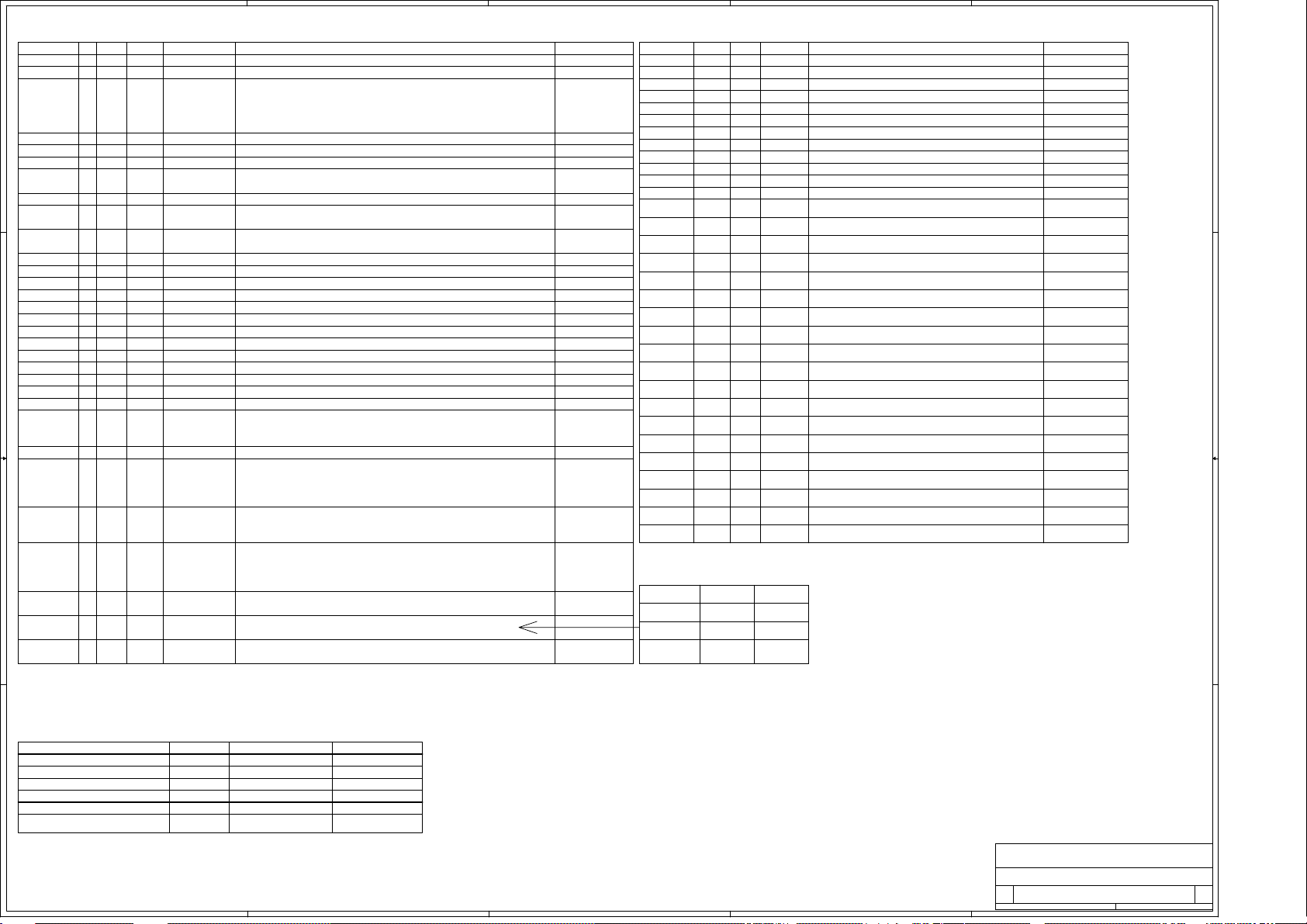

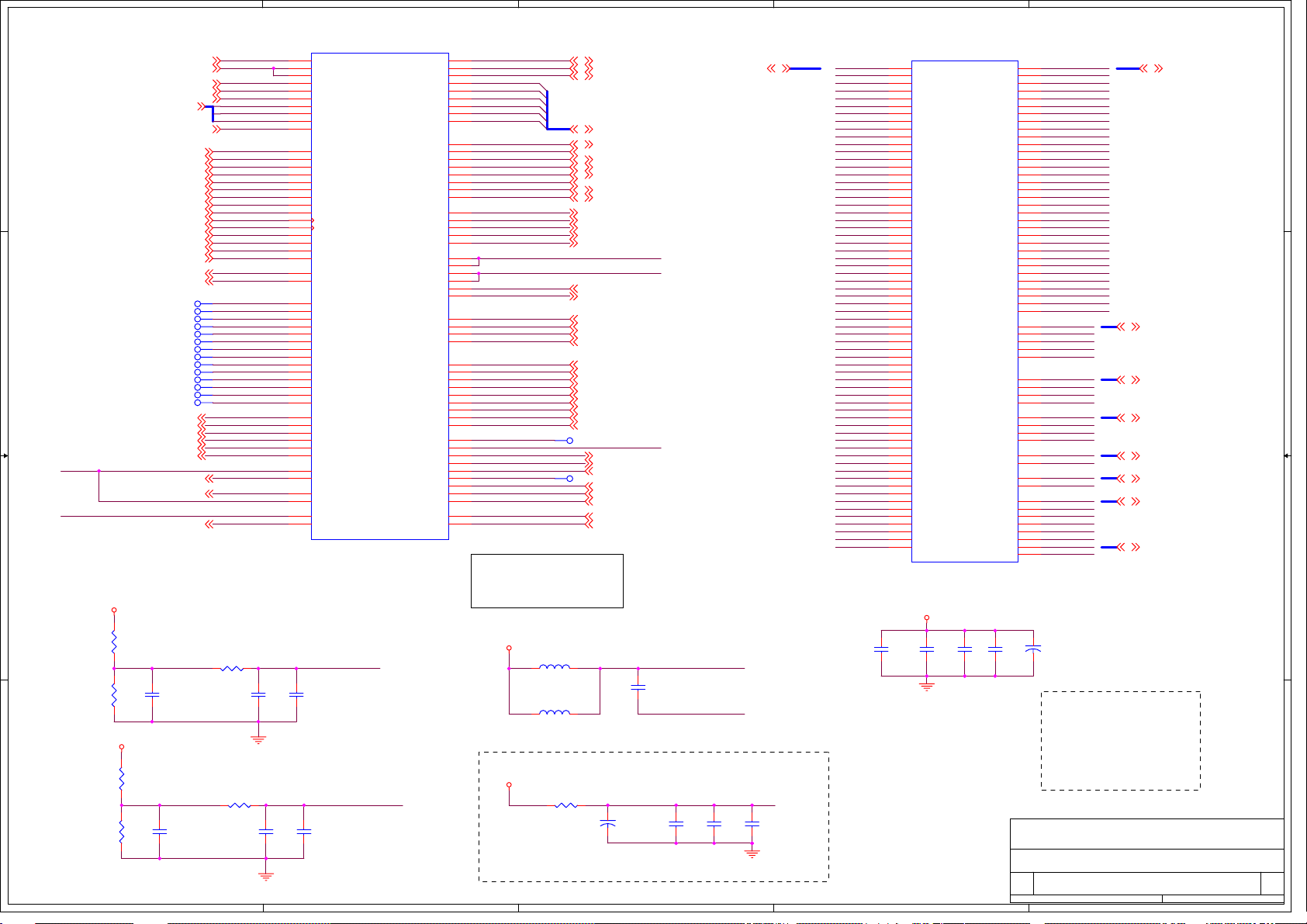

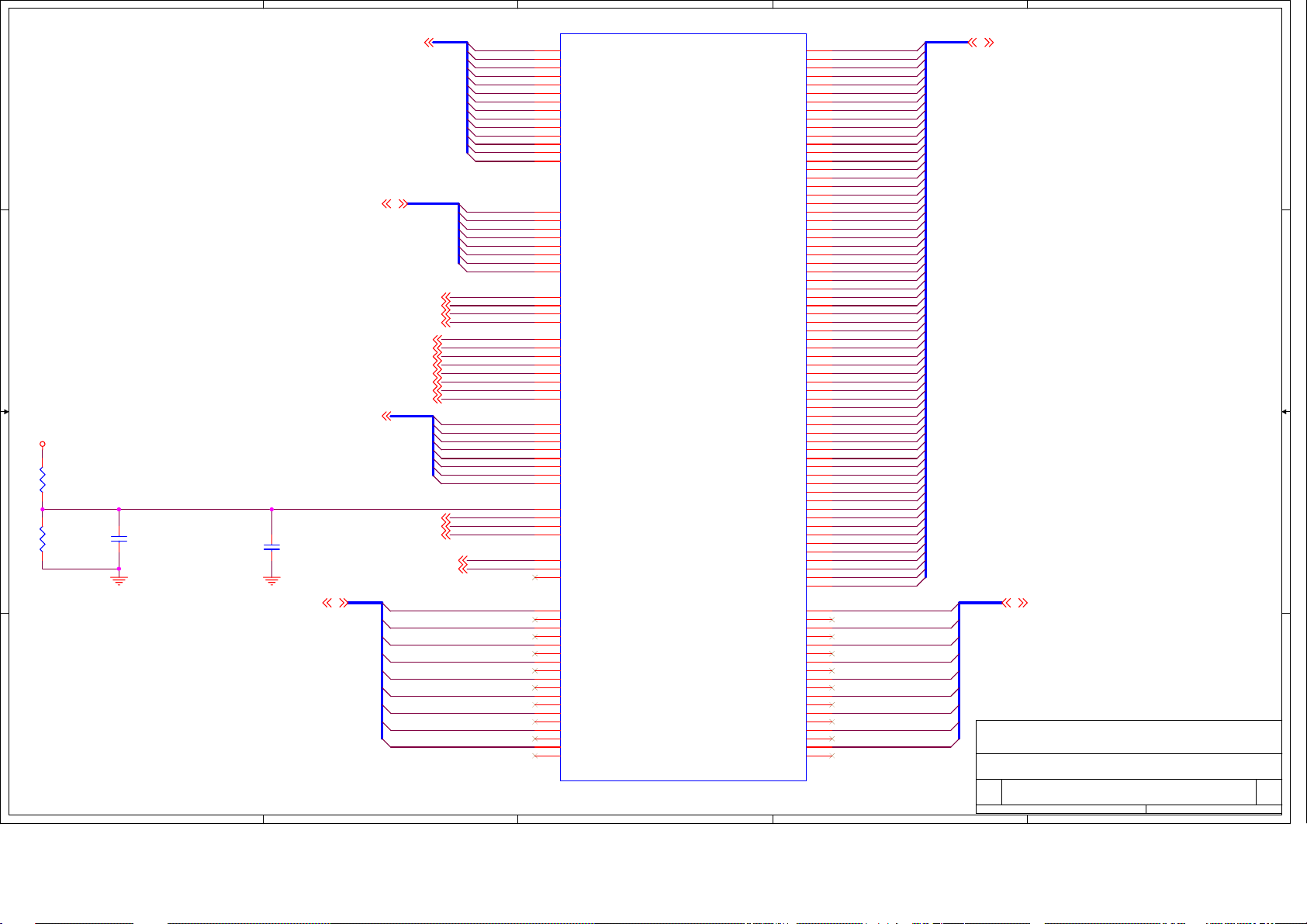

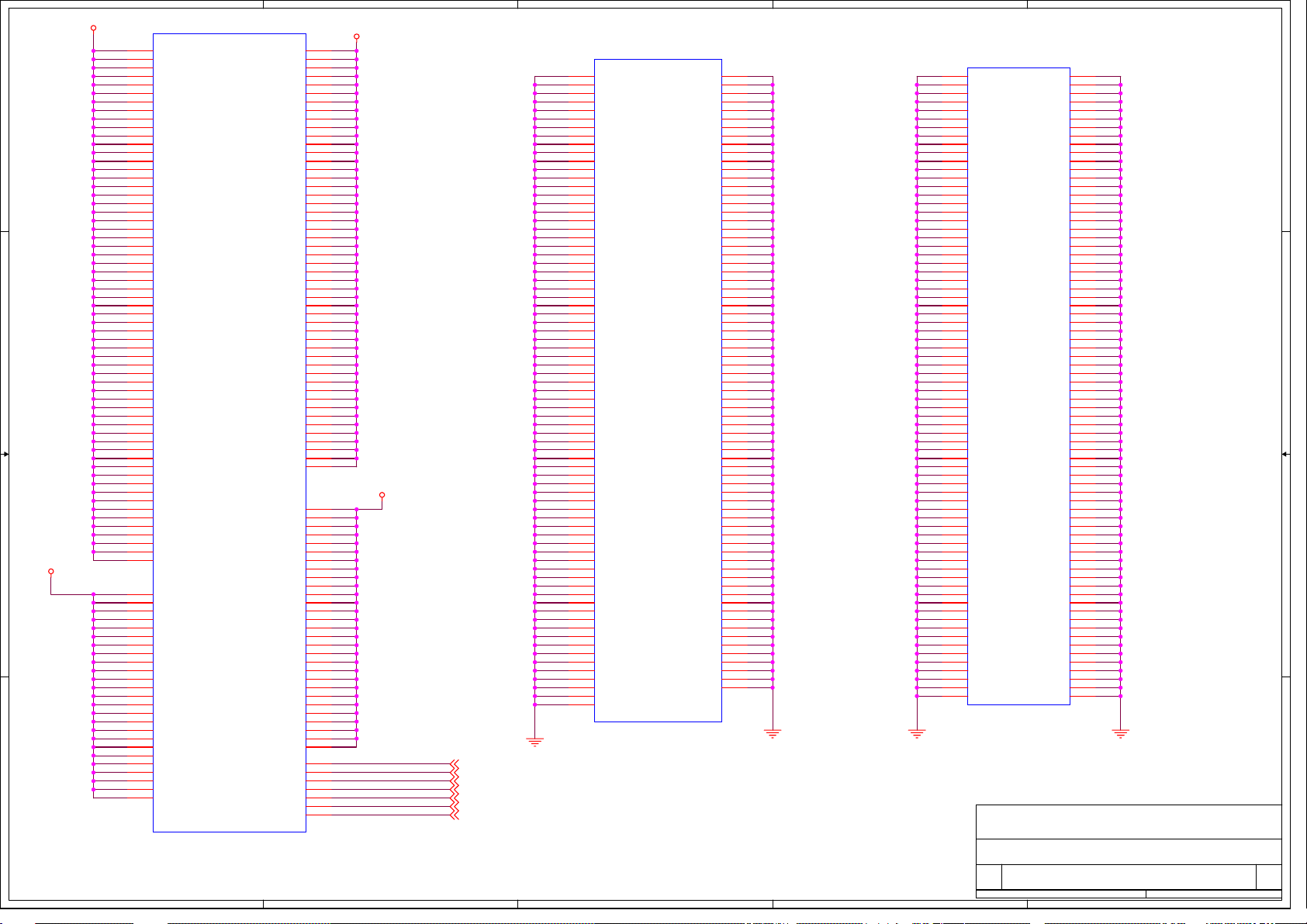

SYS RESET & PWR SET

4

3

2

1

BTN

LEVEL

D D

LOGIC

DB400

CK409B

CK409B_PWR_GD#

VID_PWRGD

C C

B B

FP

PWRDWN#

PWRDWN#

CPU0_THRMTRIP#

VIP_PWRGD

CPU_PWR_GD

CPU_RST#

CPU0_BSEL[0/1]

CPU1_BSEL[0/1]

VIP_PWRGD

CPU_PWR_GD

CPU_RST#

CPU1_THRMTRIP#

PWB+

R

CPU_VRD_PWR_GD

VTT

LEVEL

P0

VTTEN

VTTEN

P1

FET

LINDENHUST

CPU_RST#

A A

BTN

PCI_RST#

5

MCH

FP

PWROK

RST_SW

P1_SKT0CC#

CPU_PWR_GD

PWRBTN

75

SB_VTT_PWRGD

VTTEN

P3V3

LEVEL

71

SIO

1.2V

ISL6227

VTT_PWRGD

BSEL

COMPARE

LOGIC

H-R

SYS RST#

76

72

ATX_PG

DDR DIMM DDR DIMM

DDR DIMM

DDR DIMM

AB

DDR DIMM

VTT_ENABLE

DDRA_PCIRST#

CPU_VRD_PWR_GD

DDR DIMM

DDR DIMM

DDR DIMM

DDRB_PCIRST#

2.5V

ISL6563

1.25V

6420A

PLD

PWRGD_1_5VPWRGD_2_5V

1.5V

ISL6539

LOGIC

100ms

CPU_VRD_PWR_GD

SYS_PWR_GD_3_3V

PWROK

PCI_RST#

4

PCI_RST#

RESET buffer

SYS_PWR_GD#

PLD

PCI_RST_BUFF1#

BUFF

IDE_RSTDRV#

ATI VGA

SII3114

PCI-64/66 CONN

ATP867

PCI- 32/33 CONN

3

RESET buffer

IDE_RSTDRV#

PWRBTN

SLP_S#3

PS_PWR_GD

PS_PWR_GD#

VR0_SYS_ENABLE

VR1_SYS_ENABLE

CPU1_VRD_PWR_GD

SYS_PWR_GD_BUFF

IDE CONN

IDE CONN

PCI-E 5751

PCI-X 82541PI

SIO

SE-LINK

FWH

IDE CONN

2

ATX CONN

H-R

SLP_S#3

ATX_PG

PCI-E X4 SLOT1

GIGA-BYTE TECHNOLOGY CO., LTD.

Title

Size Do c um e n t N u mb er Re v

Date: Sheet

SYS RESET

5VSB

3VSB

ISL6227

5V

ISL6227

3V

ISL6227

P0 VCORE

ISL6563CPU0_VRD_PWR_GD

P1 VCORE

ISL6563

GA-9IVDPC

1

370Tuesday, Ju ne 14, 2005

of

1.1

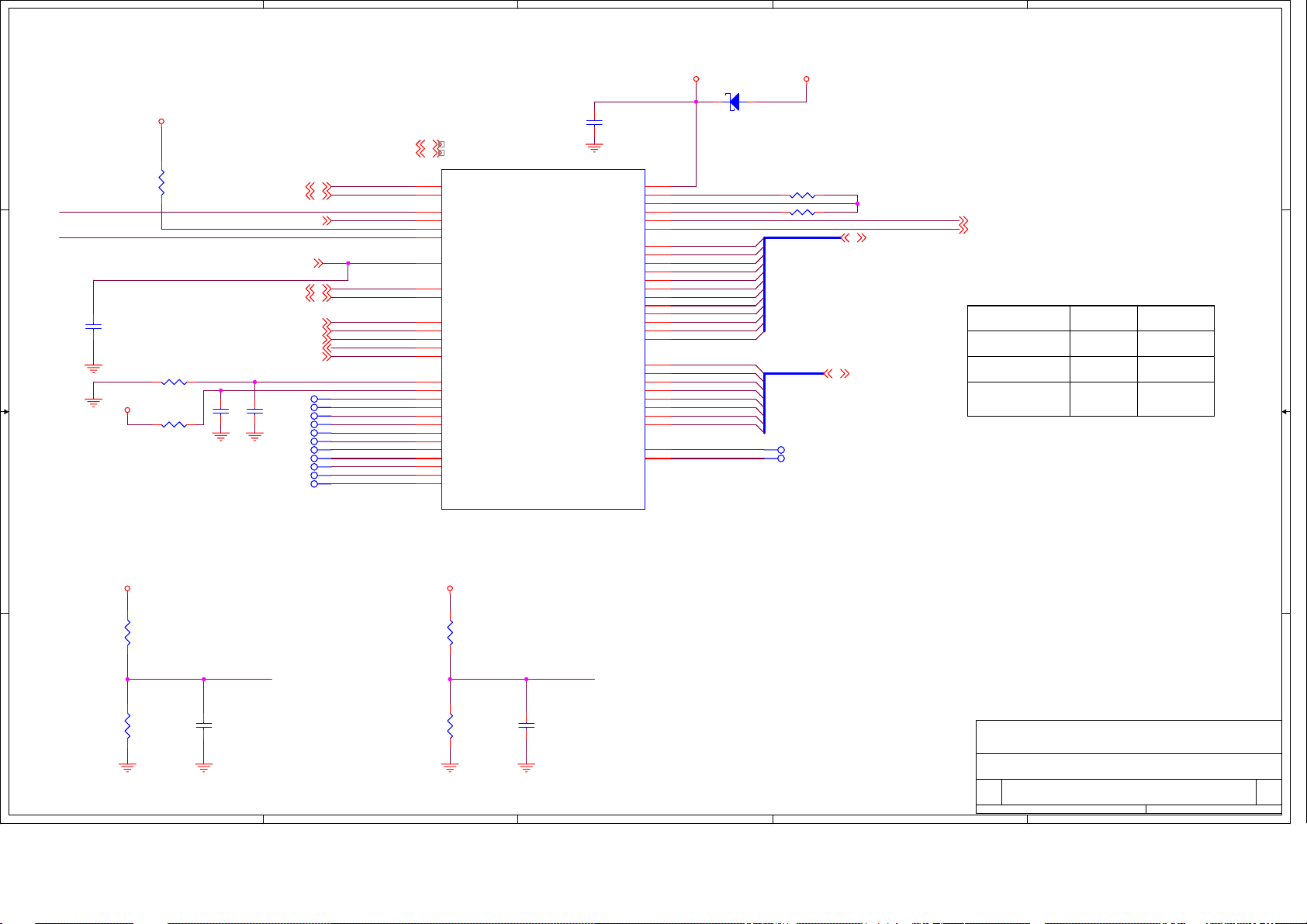

5

4

3

2

1

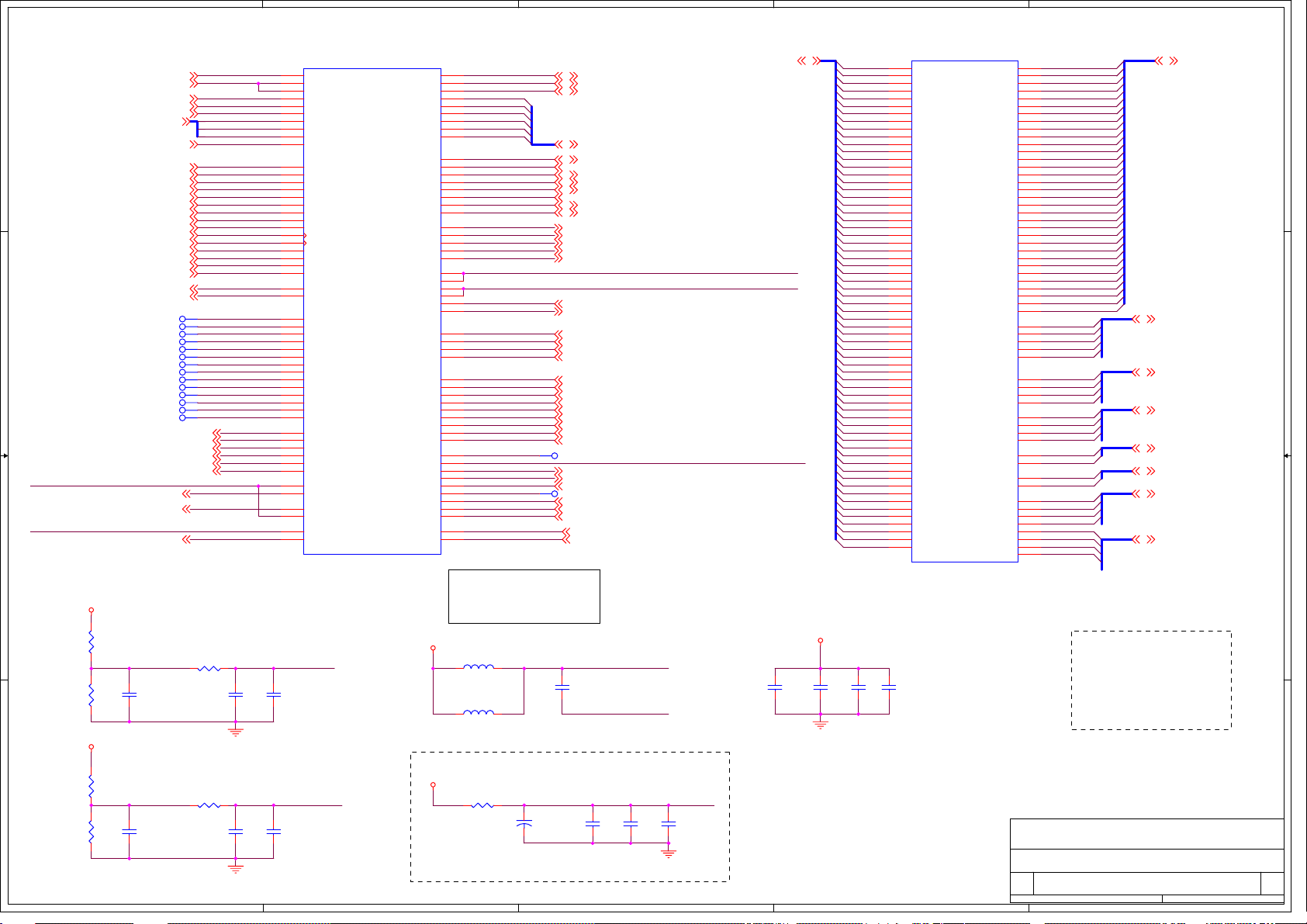

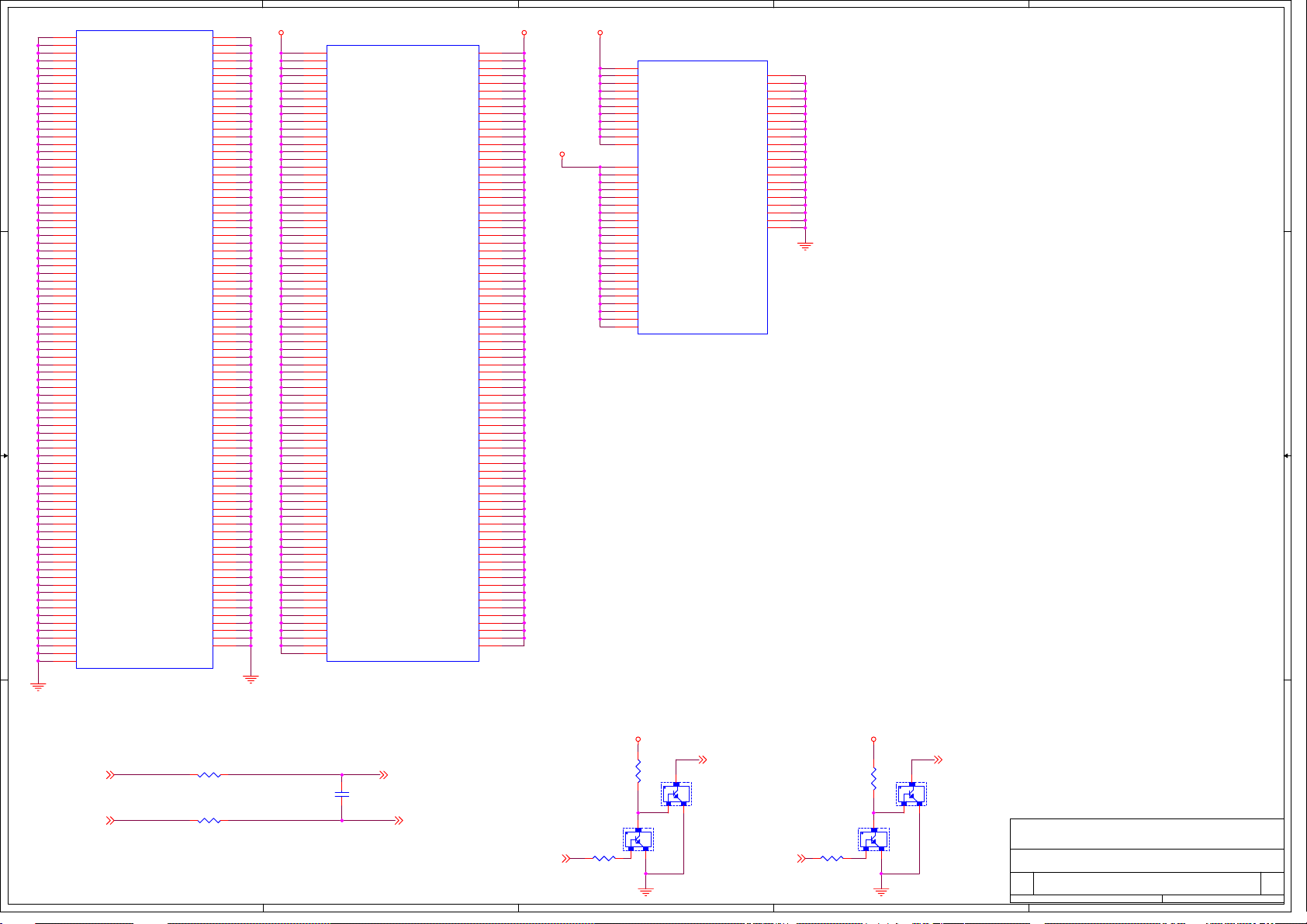

14.318

CRYSTAL

CPU3

D D

CPU2

3V66_1

CPU1

CPU0

SMA CONNECTOR

ITP_BCLK_P/ N ( 1 6 7MHZ)

2

MCH_BCLK_P/ N ( 1 6 7MHZ)

2

MCH_66MHZ_CLK

P1_BCLK_P/N(167MHZ)

2

P0_BCLK_P/N(167MHZ)

2

CK 409B

CLOCK SYNTHESIZER

DRIVER

C C

3V66_2

USB_48

PCIF0

REF0

DOT_48

PCI_4

ICH_HI66MHZ_CLK

ICH_USB_48MHZ_CLK

ICH_33MHZ_CLK

ICH_14MHZ_CLK

SIO_48MHZ_CLK

SIO_33MHZ_CLK

CLOCK BLOCK DIAGRAM

ITP_XDP

DDRA_CMDCLK_A0_P/N

DDRA_CMDCLK_A1_P/N

DDRA_CMDCLK_A2_P/N

BCLK(P/N-1/0)

BCLK(P/N-1/0)

32.768KHZ

CRYSTAL

Hance

Rapids

SIO

CUP1

CUP0

MCH_SRC_100MHZ_CLK_P/N

ICH_SRC_100MHZ_CLK_P/N

SUS_CLK

DDRA_CMDCLK_A3_P/N

DDRB_CMDCLK_B0_P/N

DDRB_CMDCLK_B1_P/N

LINDENHURST

DDRB_CMDCLK_B2_P/N

DDRB_CMDCLK_B3_P/N

SRC

2

DDR266 DIMM #A1

DDR266 DIMM #B1

2

DDR266 DIMM #A2

DDR266 DIMM #B2

DDR266 DIMM #A3

2

2

2

2

2

2

PCI EXPRESS SLOT1

EXP_SLOT1_100MHZ_CLK_P/N

2

DIFF0 DIFF1

2

DB400 (SRC -DIFFERENTIAL BUFFER)

2

DIFF3

DIFF2

DDR266 DIMM #B3

DDR266 DIMM #B4

DDR266 DIMM #A4

DB400_SRC_100MHZ_CLK_P/N

SRC

B B

PCIF1

PCI 0

PCI_SLOT3_33MHZ_CLK

VIDEO_33MHZ_CLK

PCI 1

PCI 2

REF 1

PLD_33MHZ_CLK

VIDEO_14MHZ_CLK

FWH_33MHZ_CLK

PCI 3

A A

2

PCI 32/33 (SLOT )

PLD

VIDEO

(RAGE XL)

FWH

25MHZ

CRYSTAL

SUS_CLK

PCIXSLOT

82541PI

ATP867B

SIL3114

25MHZ

CRYSTAL

Title

2

BCM5751

25MHZ

CRYSTAL

GIGA-BYTE TECHNOLOGY CO., LTD.

CLOCK BLOCK

Size Document Number Re v

GA-9IVDPC

5

4

3

Date: Sheet

2

470Tuesday, June 14, 2005

of

1

1.1

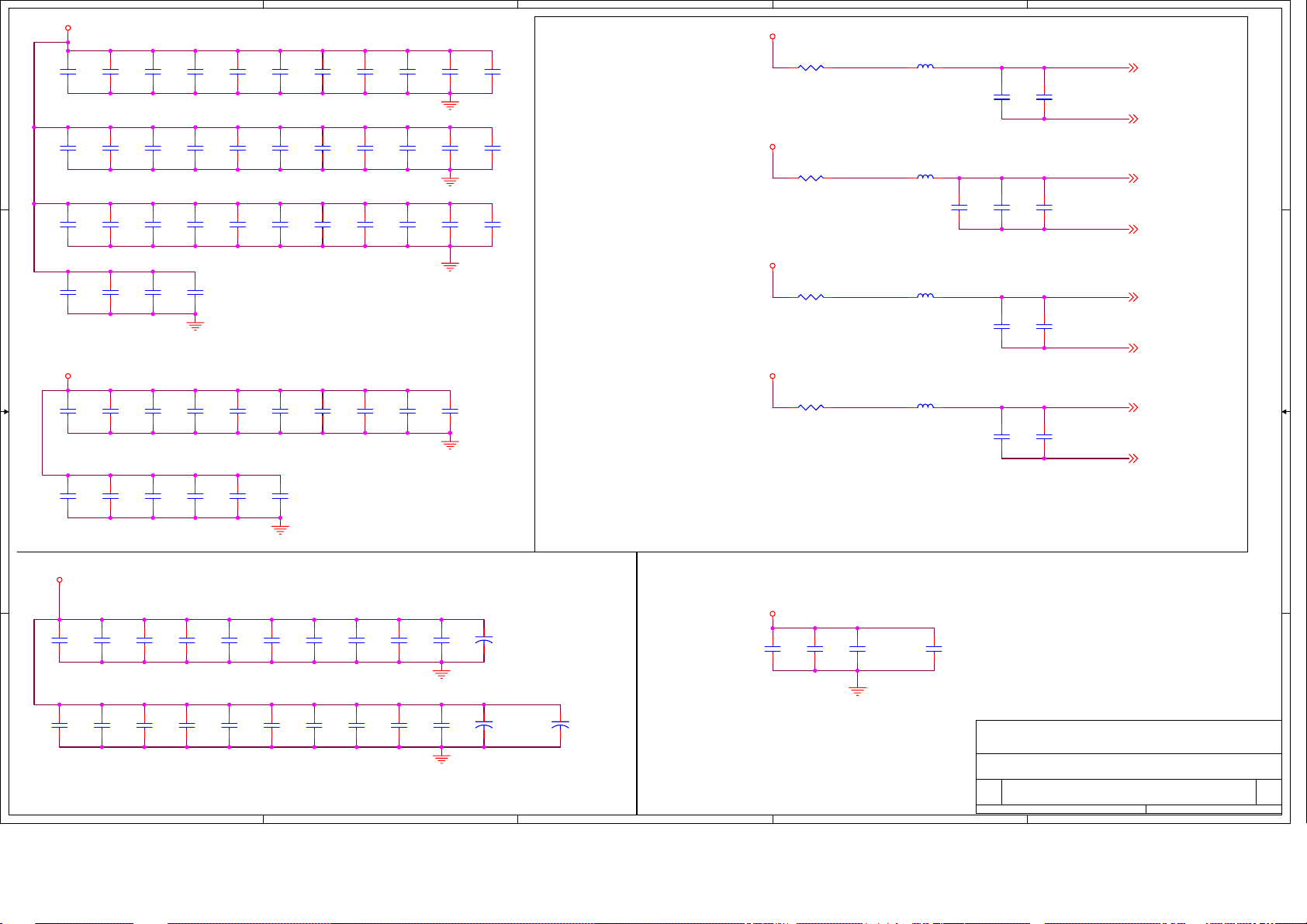

5

4

3

2

1

Hance

D D

Rapids

SMB Address = 44h

HR SMB PU 3.3VSB

HR/ LAN1/LAN2/SMBUS_HEADER

BUS0

ICH_SDA

C C

ICH_SCL

SMB Address = E0h

PCA9545/SO8

BUS1

BUS1

I2C_SDA

ITE-8712F-IX BACK-PLANE

SMB Address = 5Ah

DIMM B-1

SMB Address = A8h

DIMM A-1

SMB Address = A0h

HW W83792D

DIMM B-2 DIMM B-3 CK-409B

SMB Address = AAh

DIMM A-2

IPMI MODULE POWER MODULE

DIMM B-4

SMB Address = ACh

DIMM A-3

SMB Address = A4hSMB Address = A2h

SMB Address = AEh

DIMM A-3

SMB Address = A6h

P3V3

SMB Address = D2h

P3V3

I2C_SCL

BUS2

B B

PCI-X Slot1

PCI-E Slot#166MHZ

DB400

SMB Address = DCh

MCH

LINDENHURST-VS

SMB Address = 60h

P3V3

A A

Title

Size Document Number Rev

5

4

3

2

Date: Sheet

GIGA-BYTE TECHNOLOGY CO., LTD.

SMBUS

GA-9IVDPC

570Friday, June 17, 2005

1

of

1.1

5

4

3

2

1

ERP12V

VT1105M,VT1105S

P12V_CPU_0

120A

VT1105M,VT1105S

P12V_CPU_1

D D

120A

P_VCCP0

P_VCCP1

CPU0

1.0/CORE

CPU1

1.0/CORE

MCH

1.2/1.5/2.5

DDR266 Hance

1.25/2.5

Rapid

1.2/1.5

3.3/P3V3_STBY/P5V_STBY

IT8712F

300mW max

P5V

P5V_STBY VBAT

ATX CONN

P12V

P12V

ISL6563

39A/8A

ISL6539

8A/15A

C C

B B

P2V5

P1V25_VTT

P_VTT

P1V5

38.8A

6.5A

6.5A

13A

4.8A

8.8A

3.2A

5.5A

30.0A

6.5A

732 mA

2.5 mA

142 mA

60 mA

30 mA

P5V_STBY

P3V3_STBYP5V_STBY

2000mA

P3V3_STBY

P5V

PCI-X CONN

P3V3

A A

P3V3_STBY

P3V3

PCI-E CONN

RC1117

320 mA

FAN1112

400 mA

26mA(3.3V) + 206mA(2.5V)

MMJT9435

563mA

P12V

5

4

3

40 mA

320mA

400mA

563mA

3.3V

1.8V

1.2V

3.3V

1.2V

BCM5705

BCM5721 1.5W

206mA

2

2.5V3.3V

GIGA-BYTE TECHNOLOGY CO., LTD.

Title

Size Do c um e n t N u mb er Re v

Date: Sheet

PWR DELIVERY

GA-9IVDPC

1

670Friday, J une 17, 2005

1.1

of

5

4

3

2

1

Hance Rapids

GPIO R PWR WELL FUNCTION

GPI 0

GPI 1

GPI 2

GPI 3

GPI 4

D D

GPI 5

GPI 6

GPI 7

GPI 8

GPI 9

GPI 10

GPI 11

GPI 12

GPI 13

GPI 14

GPI 15

GPO 16

GPO 17

GPO 18

GPO 19

GPO 20

GPO 21

GPIO 22

GPO 23

C C

GPIO 24

GPIO 25

GPIO 26

GPIO 27

GPIO 28

GPIO 29

GPIO 30

GPIO 31

GPIO 32

GPIO 33

GPIO 34

GPIO 35

GPIO 36

GPIO 37

GPIO 38

GPIO 39

GPIO 40

GPIO 41

GPIO 42

B B

GPIO 43

GPIO 44

GPIO 55

GPIO 56

GPIO 57

GPIO 58

GPIO 63

NOTE

PUPU8.2K

I

I

I

PU

I

PU

I

PU

I

I

PU 4.7K P3V3

I

PU IN P3V3_STBY

I

I

I

PU

PU

I

O

PU IN

O

PU IN

O

O

O

O

OD

O

I

PU 8.2K

I/O

PU 8.2K

O

PU 8.2K

O

PU 8.2K

O

O

O

O

PU 8.2K P3V3

/O

I

/O

PU

I

PU

/O

I

PU

/O

I

O

O

I

O

I/O

I

I

PD

PU

OD

PU

OD

P3V3

8.2K

P3V3

8.2K

P3V3

8.2K

P3V3

8.2K

P3V3

8.2K

P3V3

4.7K

P3V3PU

8.2KPU ICH_SMBALERT# ALERT EVENT FROM SMBUS

P3V3_STBY

8.2K

P3V3_STBY

8.2K

P3V3_STBY

P3V3

P3V3

P3V3

P3V3

P3V3

P3V3

P3V38.2K

P3V3

P3V3_STBY

P3V3_STBY

P3V3_STBY

P3V3_STBY

P3V3

P3V3

8.2K

P3V3

8.2K

P3V3

8.2K

P3V3

P3V3

P3V3

10K

10K ERROR SIGNAL FROM IPMIP3V3

P3V3_STBY

10K

P3V3_STBY

10K

ONLY GPIO[0:15] ALLOW AN INPUT TO BE ROUTED TO SMI# OR SCI

SIGNAL NAME

PX_REQ2PX_REQ3-

P_ IRQE-PU

P_ IRQFP_ IRQGP_ IRQH-

RESERVED

RESERVED

MCH_PME#

RESERVED

RESERVED

PX_GNT2PX_GNT3-

HW_CPU1_SMI# CPU1 SMI OUT

SATALED# HR SATALED

HW_CPU0_SMI#

PANEL_ALERT# H/L

RESERVED

RESERVED

RESERVED

RESERVED

PX_IRQ0PX_IRQ1PX_IRQ2PX_IRQ3WP#

TBL#

NMI#/SMI#

SCSI_DIS

P66DETPD

ALL_ERROR

RESERVED

RESERVED

PLL0

PLL1

RESERVED

RESERVED

PX_REQ2PX_REQ3-

NO USE

NO USE

CPU0_PROCHOT#

CPU1_PROCHOT#

CPU0 THERMALTRIP INPUT

CPU1 THERMALTRIP INPUT

SIO_SMI#

NO USE

PME EVENT FROM MCH

PX_GNT2PX_GNT3-

NO USE

NO USE

NO USE

CPU0 SMI OUT

ALERT FROM FRONT PANEL

NO USE

POWER LED CONTROL

POWER LED CONTROL

WDT_TOUTPCI-X CONN

PCI-X CONN

PCI-X CONN

PCI-X CONN

BIOS WP#

BIOS TOP BLOCK

LOCK#

NMI OR SMI INPUT

DISABLE OBBOARD SCSI

NO USE

DETECT PRIMERY IDE CABLEP3V3

PLLSEL0

PLLSEL1

NOMAL/ACT

H/L

H/L

H/L

H/L

H/L

H/L

H/L

H/L

H/L

H/L

H/L

H/L

H/L

H/L

H/H

H/L

H/L

H/L

H/L

L/H

H/L

H/L

L/H

H/L

H/L

H/L

GPIO PWR

GPIO 17

GPIO 22

GPIO 23

GPIO 42

GPIO 43 STBY

GPIO 44

GPIO 45 STBY

GPIO 46

GPIO 47

GPIO 53

GPIO 54

GP40

GP41

P5V

P5V

P5V

STBY

STBY

STBY O

STBY

STBY

STBY

STBY

STBY

I

I

O

OD

I/OD

PU_8.2K

PU_8.2K

GP30

GP31

GP32

GP33

GP34

GP35

GP37

GP52

GP24

GP25

GPIO(10/40/41/42/43/44/45/46/53/54/55) POWER BY STBY

NOTE

PLL[1:0]

133/533

167/667

200/800 1100

A Inverter between S.B and MCH , so below table difference MCH spec. table

DDR266

DDR333

01

00

SB_CPU_FORCEPR#

strap to 0.

strap to 0.

SIO_PSON# PWR ON FROM SIO(NO USE)O

PWBTIN

HR_PWRBNIN#

SLP_S#3

DIS_BCM5705

SIO_SMI

DIS_BCM5721

ICH PME

SIO_SCL

SIO_SDA

CPU1 VID0

CPU1 VID1

CPU1 VID2

CPU1 VID3

CPU1 VID4

CPU1 VID5

FAN TAC1

FAN TAC2

FAN TAC3

FAN TAC4

11

01

SIO

FUNCTION NOMAL/ACT

PWR BTIN FROM FP(NO USE)

HR_PWRBNIN#(NO USE)

H/L(PWR ON)

H/L

H/L

H/L

H/L

H/L

H/LO

H/L

H/L

H/L

H/L

PCI DEVICE

PCI-X 66 SLOT

PCI-X 64/66 AIC7902

PCI-X 64/66 ADAPTEC SATA2

SODIMM ZCR SLOT

A A

BCM5705 PCI LAN

IDSEL

PX_AD18

PX_AD20

PX_AD21

PX_AD22

AD20

REQ / GNT

PX_REQ0 / PX_GNT0

PX_REQ1 / PX_GNT1

PX_REQ2 / PX_GNT2

PX_REQ3 / PX_GNT3

REQ2/GNT2 IRQB

IRQ ROUTING

3 0 1 2

0

1

2

IRQCATI RAGE XL VGA AD30 REQ0/GNT0

GIGA-BYTE TECHNOLOGY CO., LTD.

Title

Size Do c um e n t N u mb er Re v

5

4

3

2

Date: Sheet

PCI ROUTING

GA-9IVDPC

1

770Tuesday, Ju ne 14, 2005

1.1

of

5

4

3

2

1

END PROCESSOR 0

SB_BPRI#[11,18]

SB_CPU0_BREQ#23[9]

SB_BREQ#1[9,11,14]

SB_BREQ#0[9,11,14]

SB_CPURST#[9,11,13,14,18]

D D

C C

P_VCCP_A_CPU0

AGND_CPU0

B B

P_VTT

SB_RS#[2..0][11,18]

SB_RSP#[11,18]

SB_CPU_A20M#[9,11,37]

SB_CPU_IGNNE#[9,11,37]

SB_CPU_INIT#[9,11,37,58]

SB_CPU_NMI[9,11,14]

SB_CPU_INTR[9,11,37]

CPU_PWR_GD[9,11,13,52]

SB_CPU0_SMI#[14]

SB_CPU_SLP#[9,11,37]

SB_CPU_STPCLK#[9,11]

P0_BCLK#[32]

P0_BCLK[32]

ITP_TCK0[11,13]

ITP_TDI_MAIN[13]

ITP_TMS_MAIN[11,13]

ITP_TRST#[11,13,17]

SB_CPU0_BSEL1[9,10]

SB_CPU0_BSEL0[9,10]

TP1

TP2

TP3

TP4

TP5

TP6

TP7

TP8

TP9

TP10

TP11

TP12

TP13

TP14

VID_CPU0_R5[53,62]

VID_CPU0_R4[53,62]

VID_CPU0_R3[53,62]

VID_CPU0_R2[53,62]

VID_CPU0_R1[53,62]

VID_CPU0_R0[53,62]

VR0_VCCSENSE[62]

VTTEN[9,11,52]

VR0_VSSSENSE[62]

SB_BPRI#

SB_CPU0_BREQ#23

SB_BREQ#1

SB_BREQ#0

SB_CPURST#

SB_RS#2

SB_RS#1

SB_RS#0

SB_RSP#

SB_CPU_A20M#

SB_CPU_IGNNE#

SB_CPU_INIT#

SB_CPU_NMI

SB_CPU_INTR

CPU_PWR_GD

SB_CPU_SLP#

SB_CPU_STPCLK#

P0_BCLK#

P0_BCLK

ITP_TCK0

ITP_TDI_MAIN

ITP_TMS_MAIN

ITP_TRST#

SB_CPU0_BSEL1

SB_CPU0_BSEL0

VID_CPU0_R5

VID_CPU0_R4

VID_CPU0_R3

VID_CPU0_R2

VID_CPU0_R1

VID_CPU0_R0

VR0_VCCSENSE

VTTEN

VR0_VSSSENSE

D23

D10

E11

F12

D20

F21

D22

E21

F27

C26

G23

B24

AB7

C27

AE6

E24

C24

A25

F24

AB3

AA3

AE29

AE28

AE30

AD29

AD28

AC29

AB29

AB28

AA29

AA28

AE15

AC1

AE16

AD4

B27

AB4

AA5

D26

Y8

C6

D6

D4

W5

Y4

Y3

A1

B3

C3

D3

E3

F3

E1

U36A

BPRI#

NOCONA 667

BR3#

BR2#

BR1#

BR0#

RESET#

RS2#

RS1#

RS0#

RSP#

A20M#

IGNNE#

INIT#

LINT1_NMI

LINT0_INTR

PWRGOOD

SMI#

SLP#

STPCLK#

BCLK1

BCLK0

TCK

TDI

TMS

TRST#

BSEL1

BSEL0

RESERVED1

RESERVED0

RSVD16

RSVD15

RSVD14

RSVD13

RSVD12

RSVD10

RSVD9

RSVD8

RSVD7

RSVD3

RSVD2

RSVD1

VID5

VID4

VID3

VID2

VID1

VID0

VCCIOPLL

VCC_SENSE

VTTEN

VCCA

VSSA

VSS_SENSE

NOCONA 667_7

ADS#

BINIT#

BNR#

BPM5#

BPM4#

BPM3#

BPM2#

BPM1#

BPM0#

DBSY#

DEFER#

DRDY#

HIT#

HITM#

TRDY#

LOCK#

MCERR#

IERR#

FERR#

THERMTRIP#

PROCHOT#

TDO

GTLREF3

GTLREF2

GTLREF1

GTLREF0

ODTEN

SKTOCC#

COMP3

COMP2

COMP1

COMP0

TESTHI8

TESTHI7

TESTHI6

TESTHI5

TESTHI4

TESTHI3

TESTHI2

TESTHI1

TESTHI0

SMB_PRT

VCCPLL

THERMDC

THERMDA

BOOT_SELECT

RSVD

VIDPWRGD

TEST_BUS

FORCEPR#

SLEW_CTRL

OPTIMIZED_COMPAT#

SB_ADS#

D19

SB_BINIT#

F11

SB_BNR#

F20

CPU0_BPM#5

E4

CPU0_BPM#4

E8

CPU0_BPM#3

F5

CPU0_BPM#2

E7

CPU0_BPM#1

F8

CPU0_BPM#0

F6

SB_DBSY#

F18

SB_DEFER#

C23

SB_DRDY#

E18

SB_HIT#

E22

SB_HITM#

A23

SB_TRDY#

E19

SB_LOCK#

A17

SB_MCERR#

D7

SB_CPU0_IERR#

E5

SB_CPU_FERR#

E27

CPU0_THERMALTRIP#

F26

SB_CPU0_PROCHOT#

B25

ITP_TDO_P0

E25

F9

F23

W9

W23

PD_ODTEN_CPU0

B5

SMC_CPU0_SKTOCC#

A3

PD_COMP3_CPU0

AC28

PD_COMP2_CPU0

D25

PD_COMP1_CPU0

E16

PD_COMP0_CPU0

AD16

PU_CPU0_8

Y29

PU_CPU0_7

A26

PU_CPU0_6

AE5

PU_CPU0_5

AD5

PU_CPU0_4

AA7

PU_CPU0_3

Y6

PU_CPU0_2

W8

PU_CPU0_1

W7

PU_CPU0_0

W6

AE4

AD1

CPU0_THERMDC

Y28

CPU0_THERMDA

Y27

PU_BOOT_SELECT_CPU0

G7

W3

VID_PWRGD

B1

SB_CPU0_CPU1_TESTBUS

A16

CPU_FORCEPR#

A15

SLEW_CTRL_CPU0

AC30

CPU0_OPTIM_COMPAT_CTRL

C1

COMP3 =SB_CPU0_ADDR_ERC

COMP2 =SB_CPU0_DATA_ERC

PU_CPU0_8=SB_CPU0_EDRDY

PU_CPU0_0=SB_CPU0_SNPD#

TP15

TP16

SB_ADS# [11,18]

SB_BINIT# [9,11,18]

SB_BNR# [9,11,18]

CPU0_BPM#[5..0] [13]

SB_DBSY# [11,18]

SB_DEFER# [11,18]

SB_DRDY# [11,18]

SB_HIT# [9,11,18]

SB_HITM# [9,11,18]

SB_TRDY# [11,18]

SB_LOCK# [11,18]

SB_MCERR# [ 9 ,11 ,1 8]

SB_CPU0_IERR# [9,14]

SB_CPU_FERR# [9,11,37]

CPU0_THERMALTRIP# [14]

SB_CPU0_PROCHOT# [9,14]

ITP_TDO_P0 [13]

PD_ODTEN_CPU0 [9]

SMC_CPU0_SKTOCC# [9,66]

PD_COMP3_CPU0 [9]

PD_COMP2_CPU0 [9]

PD_COMP1_CPU0 [9]

PD_COMP0_CPU0 [9]

PU_CPU0_8 [9]

PU_CPU0_7 [9]

PU_CPU0_6 [9]

PU_CPU0_5 [9]

PU_CPU0_4 [9]

PU_CPU0_3 [9]

PU_CPU0_2 [9]

PU_CPU0_1 [9]

PU_CPU0_0 [9]

CPU0_THERMDC [10]

CPU0_THERMDA [10]

PU_BOOT_SELECT_CPU0 [9]

VID_PWRGD [11,52]

SB_CPU0_CPU1_TESTBUS [9,11]

CPU_FORCEPR# [9,11,14]

SLEW_CTRL_CPU0 [9]

CPU0_OPTIM_COMPAT_CTRL [9]

SB_D#[63..0][11,18]

VREF_P_VTT_CPU0_3

VREF_P_VTT_CPU0_0

PU_VCCPLL_CPU0

SB_D#63

SB_D#62

SB_D#61

SB_D#60

SB_D#59

SB_D#58

SB_D#57

SB_D#56

SB_D#55

SB_D#54

SB_D#53

SB_D#52

SB_D#51

SB_D#50

SB_D#49

SB_D#48

SB_D#47

SB_D#46

SB_D#45

SB_D#44

SB_D#43

SB_D#42

SB_D#41

SB_D#40

SB_D#39

SB_D#38

SB_D#37

SB_D#36

SB_D#35

SB_D#34

SB_D#33

SB_D#32

SB_D#31

SB_D#30

SB_D#29

SB_D#28

SB_D#27

SB_D#26

SB_D#25

SB_D#24

SB_D#23

SB_D#22

SB_D#21

SB_D#20

SB_D#19

SB_D#18

SB_D#17

SB_D#16

SB_D#15

SB_D#14

SB_D#13

SB_D#12

SB_D#11

SB_D#10

SB_D#9

SB_D#8

SB_D#7

SB_D#6

SB_D#5

SB_D#4

SB_D#3

SB_D#2

SB_D#1

SB_D#0

AB6

AA8

AC5

AC6

AE7

AD7

AC8

AB10

AA10

AA11

AB13

AB12

AC14

AA14

AA13

AC9

AD8

AD10

AE9

AC11

AE10

AC12

AD11

AD14

AD13

AB15

AD18

AE13

AC17

AA16

AB16

AB17

AD19

AD21

AE20

AE22

AC21

AC20

AA18

AC23

AE23

AD24

AC24

AE25

AD25

AC26

AE26

AA19

AB19

AB22

AB20

AA21

AA22

AB23

AB25

AB26

AA24

Y23

AD27

AA25

Y24

AA27

Y26

Y9

U36B

D63

NOCONA 667

D62

D61

D60

D59

D58

D57

D56

D55

D54

D53

D52

D51

D50

D49

D48

D47

D46

D45

D44

D43

D42

D41

D40

D39

D38

D37

D36

D35

D34

D33

D32

D31

D30

D29

D28

D27

D26

D25

D24

D23

D22

D21

D20

D19

D18

D17

D16

D15

D14

D13

D12

D11

D10

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

NOCONA 667_7

A35

A34

A33

A32

A31

A30

A29

A28

A27

A26

A25

A24

A23

A22

A21

A20

A19

A18

A17

A16

A15

A14

A13

A12

A11

A10

BREQ4#

BREQ3#

BREQ2#

BREQ1#

BREQ0#

DBI3#

DBI2#

DBI1#

DBI0#

DP3#

DP2#

DP1#

DP0#

AP1#

AP0#

ADSTB1#

ADSTB0#

DSTBP3#

DSTBP2#

DSTBP1#

DSTBP0#

DSTBN3#

DSTBN2#

DSTBN1#

DSTBN0#

SB_HA#35

C8

SB_HA#34

C9

SB_HA#33

A7

SB_HA#32

A6

SB_HA#31

B7

SB_HA#30

C11

SB_HA#29

D12

SB_HA#28

E13

SB_HA#27

B8

SB_HA#26

A9

SB_HA#25

D13

SB_HA#24

E14

SB_HA#23

C12

SB_HA#22

B11

SB_HA#21

B10

SB_HA#20

A10

SB_HA#19

F15

SB_HA#18

D15

SB_HA#17

D16

SB_HA#16

C14

SB_HA#15

C15

SB_HA#14

A12

SB_HA#13

B13

SB_HA#12

B14

SB_HA#11

B16

SB_HA#10

A13

SB_HA#9

D17

A9

A8

A7

A6

A5

A4

A3

C17

A19

C18

B18

A20

A22

B22

C20

C21

B21

B19

AB9

AE12

AD22

AC27

AE17

AC15

AE19

AC18

D9

E10

F14

F17

Y11

Y14

Y17

Y20

Y12

Y15

Y18

Y21

SB_HA#8

SB_HA#7

SB_HA#6

SB_HA#5

SB_HA#4

SB_HA#3

SB_REQ#4

SB_REQ#3

SB_REQ#2

SB_REQ#1

SB_REQ#0

SB_DBI#3

SB_DBI#2

SB_DBI#1

SB_DBI#0

SB_DP#3

SB_DP#2

SB_DP#1

SB_DP#0

SB_AP#1

SB_AP#0

SB_ADSTB#1

SB_ADSTB#0

SB_DSTBP#3

SB_DSTBP#2

SB_DSTBP#1

SB_DSTBP#0

SB_DSTBN#3

SB_DSTBN#2

SB_DSTBN#1

SB_DSTBN#0

SB_HA#[35..3] [11,18]

SB_REQ#[4..0] [11,18]

SB_DBI#[3..0] [11,18]

SB_DP#[3..0] [11,18]

SB_AP#[1..0] [11,18]

SB_ADSTB#[1..0] [11,18]

SB_DSTBP#[3..0] [11,18]

SB_DSTBN#[3..0] [11,18]

12

SC369

22U/12/Y/10V

P_VTT

12

SC473

22U/12/Y/10V

SC393

1U/6/Y/10V

SC470

0.1U/6/X/16V

2

Trace Width:12 Mils

VREF_P_VTT_CPU0_0

VREF_P_VTT_CPU0_3

VCCIOPLL_CPU0

AGND_CPU0

PU_VCCPLL_CPU0

Title

Size Document Number Rev

Date: Sheet

GIGA-BYTE TECHNOLOGY CO., LTD.

NOCONA 800 MICS P0

GA-9IVDPC

870Tuesday, June 14, 2005

1

of

1.1

P_VTT

P1V5

100mA

L14

10UH/1206

L13

10UH/1206

SR59

0/6/X

12

+

SEC2

470U/4V/7343/X

WIDE 10-12 MILS

P_VCCP_A_CPU0

12

C406

22U/12/Y/10V

AGND_CPU0

WIDE 10-12 MILS

12

SC392

4.7U/1206/X

PU_VCCPLL_CPU0

SC396

0.1U/6/X

3

SC398

0.1U/6/X

NO USE

754mV

SR86

49.9/6/1

VREF_P_VTT_CPU0_3_R

SR87

90.9/6/1

P_VTT

SC493

1U/6/Y/10V

SR82

0/6

WIDE 10-12 MILS

VREF_P_VTT_CPU0_3

SC472

SC464

220P/6

220P/6

WIDE 10-12 MILS

R637

A A

754mV

49.9/6/1

VREF_P_VTT_CPU0_0_R

R636

C395

90.9/6/1

1U/6/Y/10V

5

R673

0/6

VREF_P_VTT_CPU0_0

C414

C413

220P/6

220P/6

4

5

4

3

2

1

P_VTT

R788 220/6

D D

R789 220/6 R804 51/6/X

R799 220/6

R814 220/6

R677 220/6

R803 220/6

R808 220/6

R797 51/6

SB_CPU_A20M#

SB_CPU_IGNNE#

SB_CPU_INIT#

SB_CPU_INTR

SB_CPU_SLP#

SB_CPU_STPCLK#

SB_CPU_NMI

CPU_FORCEPR#

R554 0/6

SB_CPU_A20M# [8,11,37]

SB_CPU_IGNNE# [8,11,37]

SB_CPU_INIT# [8,11,37,58]

SB_CPU_INTR [8,11,37]

SB_CPU_SLP# [8,11,37]

SB_CPU_STPCLK# [8,11]

ICH_CPU_STPCLK# [37]

SB_CPU_NMI [8,11,14]

CPU_FORCEPR# [8,11,14]

together

To CPU

From HR

CPU1HRRouting topology CPU0 PU_R

C C

R800 51/6 R802 4.7K/6

R817 51/6

SB_CPU0_IERR#

SB_CPU0_PROCHOT#

SB_CPU0_IERR# [8 ,14]

SB_CPU0_PROCHOT# [8,14]

CPU0 HRRouting topology PU_RCPU1PU_R

P_VTT

R798 51/6/X

SR81 51/6

SR79 51/6

SR80 51/6

R638 510/6

R678 510/6

R813 100/6/1

R635 100/6/1

SR78 49.9/6/1

R672 49.9/6/1

PU_BOOT_SELECT_CPU0

CPU0_OPTIM_COMPAT_CTRL

SB_BREQ#0

SB_BREQ#1

SB_CPU0_BREQ#23

SB_CPU0_BSEL1

SB_CPU0_BSEL0

PD_COMP2_CPU0

PD_COMP3_CPU0

PD_COMP1_CPU0

PD_COMP0_CPU0

X

PU_BOOT_SELECT_CPU0 [8]

X

CPU0_OPTIM_COMPAT_CTRL [8]

SB_BREQ#0 [8,11,14]

SB_BREQ#1 [8,11,14]

SB_CPU0_BREQ#23 [8]

SB_CPU0_BSEL1 [8,10]

SB_CPU0_BSEL0 [8,10]

PD_COMP2_CPU0 [8]

PD_COMP3_CPU0 [8]

PD_COMP1_CPU0 [8]

PD_COMP0_CPU0 [8]

together

P_VTT

R676 300/6

R675 51/6

R659 51/6/X

R634 51/6/X

R665 51/6/X

R660 0/6

P3V3_STBY

P_VTT

CLOSE TO CPU0

SB_CPURST#

SLEW_CTRL_CPU0

SLEW_CTRL_CPU1

SMC_CPU0_SKTOCC#

CPU_PWR_GD

CPU_PWR_GD [8,11,13,52]

SB_CPURST# [8,11,13,14,18]

X

SLEW_CTRL_CPU0 [8]

SLEW_CTRL_CPU1 [11]

SMC_CPU0_SKTOCC# [8,66]

C397

100P/6/X

END CPU NOT USE

X

X

GA-9IVDPC

PU_CPU0_8 [8]

PU_CPU0_7 [8]

PU_CPU0_6 [8]

PU_CPU0_5 [8]

PU_CPU0_4 [8]

PU_CPU0_3 [8]

PU_CPU0_2 [8]

PU_CPU0_1 [8]

PU_CPU0_0 [8]

970Tuesday, June 14, 2005

1

of

1.1

2

R666 51/6/X

R794 51/6/X

R606 51/6

R603 51/6

R625 51/6

R622 51/6

R619 51/6

R610 51/6

R615 51/6

Title

Size Document Number Rev

Date: Sheet

Routing topology PU_RHRPU_R CPU0 CPU1

R776 51/6

B B

A A

SR74 39/6

SR85 39/6

SR83 39/6

SR84 39/6

SR73 39/6

P3V3

R805 4.7K/6

SB_CPU_FERR#

SB_BININ#_R SB_BINIT#

SB_BNR#_R

SB_HIT#_R

SB_HITM#_R

SB_MCERR#_R S B_MCERR#

VTTEN

5

SC457

47P/6/N/50V

SC465

47P/6/N/50V

SC467

47P/6/N/50V

SC466

47P/6/N/50V

SC452

47P/6/N/50V

SB_BNR#

SB_HIT#

SB_HITM#

SB_CPU_FERR# [8,11,37]

SB_BINIT# [8,11,18]

SB_BNR# [8,11,18]

SB_HIT# [8,11,18]

SB_HITM# [8,11,18]

SB_MCERR# [8,11,18]

O.D.

VTTEN [8,11,52]

4

P_VTT

R801 51/6

R778 51/6

P_VTT

R796

PD_ODTEN_CPU0

PD_ODTEN_CPU1

SB_CPU0_CPU1_TESTBUS

51/6

R795 0/6/X

End-CPU ENABLE ODT

PD_ODTEN_CPU0 [8]

PD_ODTEN_CPU1 [1 1 ]

Mid-CPU DISABLE ODT

SB_CPU0_CPU1_TESTBUS [8,11]

3

PU_CPU0_8

PU_CPU0_7

PU_CPU0_6

PU_CPU0_5

PU_CPU0_4

PU_CPU0_3

PU_CPU0_2

PU_CPU0_1

PU_CPU0_0

GIGA-BYTE TECHNOLOGY CO., LTD.

NOCONA 800 P0 TERMINATION

5

4

3

2

1

AA31

AA26

AA20

AA6

AA4

AA1

Y30

Y22

Y16

Y2

W31

W29

W27

W25

W1

V30

V28

V26

V24

V8

V6

V4

V2

U31

U29

U27

U25

U23

U9

U7

U5

U3

U1

T30

T28

T26

T24

T8

T6

T4

T2

R31

R29

R27

R25

R23

R9

R7

R5

R3

R1

P30

P28

P26

P24

P8

P6

P4

P2

N31

N29

N27

N25

N23

N9

N7

N5

N3

N1

M31

M29

M27

M25

M23

M9

M7

M5

M3

M1

P_VCCP0P_VCCP0 P_VTT

AD12

AC10

AA12

Y10

F10

E12

C10

B12

AE24

AE18

AE14

AE8

AE3

AD30

AD26

AD20

AD6

AD2

AC31

AC22

AC16

AC4

AC3

AB30

AB24

AB18

AB14

AB8

AB2

C5

L28

P3V3

B4

A4

U36E

VCC_VTT1

VCC_VTT2

VCC_VTT3

VCC_VTT4

VCC_VTT5

VCC_VTT6

VCC_VTT7

VCC_VTT8

VCC_VTT9

VCC_VTT10

VCC_VTT11

VCC_CORE160

VCC_CORE161

VCC_CORE162

VCC_CORE163

VCC_CORE164

VCC_CORE165

VCC_CORE166

VCC_CORE167

VCC_CORE168

VCC_CORE169

VCC_CORE170

VCC_CORE171

VCC_CORE172

VCC_CORE173

VCC_CORE174

VCC_CORE175

VCC_CORE176

VCC_CORE177

VCC_CORE178

VCC_CORE179

VCC_CORE180

VCC_CORE181

NOCONA 667_7

NOCONA 667

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

AE2

AD3

AE27

AE21

AE11

AD31

AD23

AD17

AD15

AD9

AC25

AC19

AC13

AC7

AC2

AB31

AB27

AB21

AB11

AB5

AB1

P3V3

U36C

L31

VSS9

L29

L27

L25

L23

D D

C C

B B

H30

H28

H26

H24

G31

G29

G27

G25

F30

F28

F25

F19

F13

E31

E29

E23

E17

E15

D30

D28

D27

D21

D11

C31

C29

C25

C19

C13

B30

B28

B23

B17

B15

A31

A29

A27

A21

A11

K30

K28

K26

K24

J31

J29

J27

J25

J23

VSS10

VSS11

VSS12

VSS13

L9

VSS14

L7

VSS15

L5

VSS16

L3

VSS17

L1

VSS18

VSS19

VSS20

VSS21

VSS22

K8

VSS23

K6

VSS24

K4

VSS25

K2

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

J9

VSS32

J7

VSS33

J5

VSS34

J3

VSS35

J1

VSS36

VSS37

VSS38

VSS39

VSS40

H8

VSS41

H6

VSS42

H4

VSS43

H2

VSS44

VSS45

VSS46

VSS47

VSS48

G9

VSS49

G5

VSS51

G3

VSS52

G1

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

F7

VSS59

F2

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

E9

VSS66

VSS68

VSS69

VSS70

VSS71

VSS72

D5

VSS73

D2

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

C7

VSS80

VSS82

VSS83

VSS84

VSS85

VSS86

B9

VSS87

B2

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

A5

VSS94

NOCONA 667_7

NOCONA 667

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

VSS161

VSS162

VSS163

VSS164

VSS165

VSS166

VSS167

VSS168

VSS169

VSS170

VSS171

VSS172

VSS173

VSS174

VSS175

VSS176

VSS177

VSS178

VSS179

VSS180

VSS181

VSS182

VSS183

VSS184

VSS185

VSS186

VSS187

VSS188

VSS189

VSS8

VSS7

VSS6

VSS5

VSS4

VSS3

VSS2

VSS1

AA30

AA23

AA17

AA15

AA9

AA2

Y31

Y25

Y19

Y13

Y7

Y5

Y1

W30

W28

W26

W24

W4

W2

V31

V29

V27

V25

V23

V9

V7

V5

V3

V1

U30

U28

U26

U24

U8

U6

U4

U2

T31

T29

T27

T25

T23

T9

T7

T5

T3

T1

R30

R28

R26

R24

R8

R6

R4

R2

P31

P29

P27

P25

P23

P9

P7

P5

P3

P1

N30

N28

N26

N24

N8

N6

N4

N2

M2

M4

M6

M8

M24

M26

M28

M30

K31

K29

K27

K25

K23

H31

H29

H27

H25

H23

G30

G28

G26

G24

E30

E28

E26

E20

D31

D29

D24

D18

D14

C30

C28

C22

C16

B31

B29

B26

B20

A30

A28

A24

A18

A14

L30

L26

L24

L8

L6

L4

L2

K9

K7

K5

K3

K1

J30

J28

J26

J24

J8

J6

J4

J2

H9

H7

H5

H3

H1

G8

G6

G4

G2

F31

F29

F22

F16

F4

F1

E6

E2

D8

D1

C4

C2

B6

A8

A2

U36D

VCC_CORE1

VCC_CORE2

VCC_CORE3

VCC_CORE4

VCC_CORE5

VCC_CORE6

VCC_CORE7

VCC_CORE8

VCC_CORE9

VCC_CORE10

VCC_CORE11

VCC_CORE12

VCC_CORE13

VCC_CORE14

VCC_CORE15

VCC_CORE16

VCC_CORE17

VCC_CORE18

VCC_CORE19

VCC_CORE20

VCC_CORE21

VCC_CORE22

VCC_CORE23

VCC_CORE24

VCC_CORE25

VCC_CORE26

VCC_CORE27

VCC_CORE28

VCC_CORE29

VCC_CORE30

VCC_CORE31

VCC_CORE32

VCC_CORE33

VCC_CORE34

VCC_CORE35

VCC_CORE36

VCC_CORE37

VCC_CORE38

VCC_CORE39

VCC_CORE40

VCC_CORE41

VCC_CORE42

VCC_CORE43

VCC_CORE44

VCC_CORE45

VCC_CORE46

VCC_CORE47

VCC_CORE48

VCC_CORE49

VCC_CORE50

VCC_CORE51

VCC_CORE52

VCC_CORE53

VCC_CORE54

VCC_CORE55

VCC_CORE56

VCC_CORE57

VCC_CORE58

VCC_CORE59

VCC_CORE60

VCC_CORE61

VCC_CORE62

VCC_CORE63

VCC_CORE64

VCC_CORE65

VCC_CORE66

VCC_CORE67

VCC_CORE68

VCC_CORE69

VCC_CORE70

VCC_CORE71

VCC_CORE72

VCC_CORE73

VCC_CORE74

VCC_CORE75

VCC_CORE76

VCC_CORE77

VCC_CORE78

VCC_CORE79

VCC_CORE80

NOCONA 667_7

NOCONA 667

VCC_CORE81

VCC_CORE82

VCC_CORE83

VCC_CORE84

VCC_CORE85

VCC_CORE86

VCC_CORE87

VCC_CORE88

VCC_CORE89

VCC_CORE90

VCC_CORE91

VCC_CORE92

VCC_CORE93

VCC_CORE94

VCC_CORE95

VCC_CORE96

VCC_CORE97

VCC_CORE98

VCC_CORE99

VCC_CORE100

VCC_CORE101

VCC_CORE102

VCC_CORE103

VCC_CORE104

VCC_CORE105

VCC_CORE106

VCC_CORE107

VCC_CORE108

VCC_CORE109

VCC_CORE110

VCC_CORE111

VCC_CORE112

VCC_CORE113

VCC_CORE114

VCC_CORE115

VCC_CORE116

VCC_CORE117

VCC_CORE118

VCC_CORE119

VCC_CORE120

VCC_CORE121

VCC_CORE122

VCC_CORE123

VCC_CORE124

VCC_CORE125

VCC_CORE126

VCC_CORE127

VCC_CORE128

VCC_CORE129

VCC_CORE130

VCC_CORE131

VCC_CORE132

VCC_CORE133

VCC_CORE134

VCC_CORE135

VCC_CORE136

VCC_CORE137

VCC_CORE138

VCC_CORE139

VCC_CORE140

VCC_CORE141

VCC_CORE142

VCC_CORE143

VCC_CORE144

VCC_CORE145

VCC_CORE146

VCC_CORE147

VCC_CORE148

VCC_CORE149

VCC_CORE150

VCC_CORE151

VCC_CORE152

VCC_CORE153

VCC_CORE154

VCC_CORE155

VCC_CORE156

VCC_CORE157

VCC_CORE158

VCC_CORE159

R640

470/6

A A

CPU0_THERMDA[8]

CPU0_THERMDC[8]

CPU0_THERMDC

5

R668

0/6

R667

0/6

CPU0_THERMDA_H7

GNDSIOA

TD1PCPU0_THERMDA

C410

100P/6

GNDSIOA

TD1P [53]

GNDSIOA [12,53]

4

MMBT3904

SB_CPU0_BSEL1[8,9]

R680

470/6

Q82

SOT23

ECB

3

CPU0_BSEL1 [32,52]

Q78

MMBT3904

SOT23

ECB

R639

470/6

MMBT3904

SB_CPU0_BSEL0[8,9]

R679

470/6

Q81

SOT23

ECB

CPU0_BSEL0 [32,52]

Q77

MMBT3904

SOT23

ECB

2

Title

Size Document Number Rev

Date: Sheet

GIGA-BYTE TECHNOLOGY CO., LTD.

NOCONA 800 P0 PWR/GND

GA-9IVDPC

10 70Tuesday, June 14, 2005

1

of

1.1

5

4

3

2

1

PROCESSOR 1

SB_BPRI#[8,18]

SB_CPU1_BREQ#23[13]

SB_BREQ#0[8,9,14]

SB_BREQ#1[8,9,14]

SB_CPURST#[8,9,13,14,18]

SB_RS#[2..0][8,18]

D D

C C

AGND_CPU1

B B

P_VTT

R669

49.9/6/1

754mV

VREF_P_VCCP_CPU1_0_R

R671

84.5/6/1

P_VTT

SB_CPU_A20M#[8, 9,37]

SB_CPU_IGNNE#[8,9,37]

SB_CPU_INIT#[8,9,37,58]

SB_CPU_NMI[8,9,14]

SB_CPU_INTR[8, 9,37]

CPU_PWR_GD[8,9,13,52]

SB_CPU1_SMI#[14]

SB_CPU_SLP#[8,9,37]

SB_CPU_STPCLK#[8,9]

ITP_TMS_MAIN[8,13]

SB_CPU1_BSEL1[12,13]

SB_CPU1_BSEL0[12,13]

VID_CPU1_R5[63]

VID_CPU1_R4[63]

VID_CPU1_R3[63]

VID_CPU1_R2[63]

VID_CPU1_R1[63]

VID_CPU1_R0[63]

VR1_VCCSENSE[63]

VR1_VSSSENSE[63]

P1 VREF

SB_RSP#[8,18]

P1_BCLK#[32]

P1_BCLK[32]

ITP_TCK0[8,13]

ITP_TDI_P1[13]

ITP_TRST#[8,13,17]

TP17

TP18

TP19

TP20

TP21

TP22

TP23

TP24

TP25

TP26

TP27

TP28

TP29

TP30

VTTEN[8,9,52]

C415

1U/6/Y/10V

SB_BPRI#

SB_CPU1_BREQ#23

SB_BREQ#0

SB_BREQ#1

SB_CPURST#

SB_RS#2

SB_RS#1

SB_RS#0

SB_RSP#

SB_CPU_A20M#

SB_CPU_IGNNE#

SB_CPU_INIT#

SB_CPU_NMI

SB_CPU_INTR

CPU_PWR_GD

SB_CPU_SLP#

SB_CPU_STPCLK#

P1_BCLK#

P1_BCLK

ITP_TCK0

ITP_TDI_P1

ITP_TMS_MAIN

ITP_TRST#

SB_CPU1_BSEL1

SB_CPU1_BSEL0

VID_CPU1_R5

VID_CPU1_R4

VID_CPU1_R3

VID_CPU1_R2

VID_CPU1_R1

VID_CPU1_R0

P_VCCP_A_CPU1

VR1_VCCSENSE

VTTEN

P_VCCP_A_CPU1

VR1_VSSSENSE

MCH A0 CPU B0 800 64.9ohm 0.678V

MCH B0 CPU C1 800 49.9ohm 0.756V

R670

0/6

C411

220P/6

U35A

D23

BPRI#

AE29

AE28

AE30

AD29

AD28

AC29

AB29

AB28

AA29

AA28

AE15

AE16

D10

E11

F12

D20

F21

D22

E21

F27

C26

G23

B24

AB7

C27

AE6

E24

C24

A25

F24

AB3

AA3

AC1

AD4

B27

AB4

AA5

D26

Y8

C6

D6

D4

W5

Y4

Y3

A1

B3

C3

D3

E3

F3

E1

NOCONA 667

BR3#

BR2#

BR1#

BR0#

RESET#

RS2#

RS1#

RS0#

RSP#

A20M#

IGNNE#

INIT#

LINT1_NMI

LINT0_INTR

PWRGOOD

SMI#

SLP#

STPCLK#

BCLK1

BCLK0

TCK

TDI

TMS

TRST#

BSEL1

BSEL0

RESERVED1

RESERVED0

RSVD16

RSVD15

RSVD14

RSVD13

RSVD12

RSVD10

RSVD9

RSVD8

RSVD7

RSVD3

RSVD2

RSVD1

VID5

VID4

VID3

VID2

VID1

VID0

VCCIOPLL

VCC_SENSE

VTTEN

VCCA

VSSA

VSS_SENSE

NOCONA 667_7

WIDE 10-12 MILS

VREF_P_VTT_CPU1_0

C412

220P/6

ADS#

BINIT#

BNR#

BPM5#

BPM4#

BPM3#

BPM2#

BPM1#

BPM0#

DBSY#

DEFER#

DRDY#

HITM#

TRDY#

LOCK#

MCERR#

IERR#

FERR#

THERMTRIP#

PROCHOT#

GTLREF3

GTLREF2

GTLREF1

GTLREF0

ODTEN

SKTOCC#

COMP3

COMP2

COMP1

COMP0

TESTHI8

TESTHI7

TESTHI6

TESTHI5

TESTHI4

TESTHI3

TESTHI2

TESTHI1

TESTHI0

SMB_PRT

VCCPLL

THERMDC

THERMDA

BOOT_SELECT

RSVD

VIDPWRGD

TEST_BUS

FORCEPR#

SLEW_CTRL

OPTIMIZED_COMPAT#

HIT#

TDO

SB_ADS#

D19

SB_BINIT#

F11

SB_BNR#

F20

CPU1_BPM#5

E4

CPU1_BPM#4

E8

CPU1_BPM#3

F5

CPU1_BPM#2

E7

CPU1_BPM#1

F8

CPU1_BPM#0

F6

SB_DBSY#

F18

SB_DEFER#

C23

SB_DRDY#

E18

SB_HIT#

E22

SB_HITM#

A23

SB_TRDY#

E19

SB_LOCK#

A17

SB_MCERR#

D7

SB_CPU1_IERR#

E5

SB_CPU_FERR#

E27

CPU1_THERMALTRIP#

F26

SB_CPU1_PROCHOT#

B25

ITP_TDO_MAIN

E25

F9

F23

W9

W23

PD_ODTEN_CPU1

B5

SMC_CPU1_SKTOCC#

A3

PD_COMP3_CPU1

AC28

PD_COMP2_CPU1

D25

PD_COMP1_CPU1

E16

PD_COMP0_CPU1

AD16

PU_CPU1_8

Y29

PU_CPU1_7

A26

PU_CPU0_6

AE5

PU_CPU1_5

AD5

PU_CPU1_4

AA7

PU_CPU1_3

Y6

PU_CPU1_2

W8

PU_CPU1_1

W7

PU_CPU1_0

W6

AE4

AD1

CPU1_THERMDC

Y28

CPU1_THERMDA

Y27

PU_BOOT_SELECT_CPU1

G7

W3

VID_PWRGD

B1

SB_CPU0_CPU1_TESTBUS

A16

CPU_FORCEPR#

A15

SLEW_CTRL_CPU1

AC30

CPU1_OPTIM_COMPAT_CTRL

C1

COMP3 =SB_CPU1_ADDR_ERC

COMP2 =SB_CPU1_DATA_ERC

PU_CPU1_8=SB_CPU1_EDRDY

PU_CPU1_0=SB_CPU1_SNPD#

P_VTT

SL1

10UH/1206

SL2

10UH/1206

SB_ADS# [8,18]

SB_BINIT# [8 , 9 ,18 ]

SB_BNR# [ 8 ,9,18]

CPU1_BPM#[5..0] [13]

SB_DBSY# [8,18]

SB_DEFER# [8,18]

SB_DRDY# [8,18]

SB_HIT# [8,9,18]

SB_HITM# [8,9,18]

SB_TRDY# [8,18]

SB_LOCK# [8,18]

SB_MCERR# [8 , 9,18]

SB_CPU1_IERR# [13,14 ]

SB_CPU_FERR# [8,9,37]

CPU1_THERMALTRIP# [14]

SB_CPU1_PROCHOT# [13,14]

ITP_TDO_P1 [13]

VREF_P_VTT_CPU1_3

VREF_P_VTT_CPU1_0

PD_ODTEN_CPU1 [9]

SMC_CPU1_SKTOCC# [13,52,66]

PD_COMP3_CPU1 [13]

PD_COMP2_CPU1 [13]

PD_COMP1_CPU1 [13]

PD_COMP0_CPU1 [13]

PU_CPU1_8 [13]

PU_CPU1_7 [13]

PU_CPU1_6 [13]

PU_CPU1_5 [13]

PU_CPU1_4 [13]

PU_CPU1_3 [13]

PU_CPU1_2 [13]

PU_CPU1_1 [13]

PU_CPU1_0 [13]

TP31

PU_VCCPLL_CPU1

CPU1_THERMDC [12]

CPU1_THERMDA [12]

PU_BOOT_SELECT_CPU1 [13]

TP32

VID_PWRGD [8,52]

SB_CPU0_CPU1_TESTBUS [8,9]

CPU_FORCEPR# [8 ,9,14]

SLEW_CTRL_CPU1 [9]

CPU1_OPTIM_COMPAT_CTRL [13]

WIDE 10-12 MILS

P_VCCP_A_CPU1

12

SC399

22U/12/Y/10V

AGND_CPU1

SB_D#[63..0][8, 18]

SB_D#63

SB_D#62

SB_D#61

SB_D#60

SB_D#59

SB_D#58

SB_D#57

SB_D#56

SB_D#55

SB_D#54

SB_D#53

SB_D#52

SB_D#51

SB_D#50

SB_D#49

SB_D#48

SB_D#47

SB_D#46

SB_D#45

SB_D#44

SB_D#43

SB_D#42

SB_D#41

SB_D#40

SB_D#39

SB_D#38

SB_D#37

SB_D#36

SB_D#35

SB_D#34

SB_D#33

SB_D#32

SB_D#31

SB_D#30

SB_D#29

SB_D#28

SB_D#27

SB_D#26

SB_D#25

SB_D#24

SB_D#23

SB_D#22

SB_D#21

SB_D#20

SB_D#19

SB_D#18

SB_D#17

SB_D#16

SB_D#15

SB_D#14

SB_D#13

SB_D#12

SB_D#11

SB_D#10

SB_D#9

SB_D#8

SB_D#7

SB_D#6

SB_D#5

SB_D#4

SB_D#3

SB_D#2

SB_D#1

SB_D#0

WIDE 10-12 MILS

SR48

A A

754mV

49.9/6/1

VREF_P_VCCP_CPU1_3_R

SC368

SR49

1U/6/Y/10V

84.5/6/1

5

SR50

0/6

WIDE 10-12 MILS

VREF_P_VTT_CPU1_3

SC370

SC371

220P/6

220P/6

4

P1V5

SR60

0/6/X

12

+

SEC1

470U/4V/7343/X

NO USE

PU_VCCPLL_CPU1

12

3

SC394

4.7U/1206/X

SC379

0.1U/6/X

SC378

0.1U/6/X

AB6

Y9

AA8

AC5

AC6

AE7

AD7

AC8

AB10

AA10

AA11

AB13

AB12

AC14

AA14

AA13

AC9

AD8

AD10

AE9

AC11

AE10

AC12

AD11

AD14

AD13

AB15

AD18

AE13

AC17

AA16

AB16

AB17

AD19

AD21

AE20

AE22

AC21

AC20

AA18

AC23

AE23

AD24

AC24

AE25

AD25

AC26

AE26

AA19

AB19

AB22

AB20

AA21

AA22

AB23

AB25

AB26

AA24

Y23

AD27

AA25

Y24

AA27

Y26

12

SC383

22U/12/Y/10V

2

U35B

D63

NOCONA 667

D62

D61

D60

D59

D58

D57

D56

D55

D54

D53

D52

D51

D50

D49

D48

D47

D46

D45

D44

D43

D42

D41

D40

D39

D38

D37

D36

D35

D34

D33

D32

D31

D30

D29

D28

D27

D26

D25

D24

D23

D22

D21

D20

D19

D18

D17

D16

D15

D14

D13

D12

D11

D10

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

NOCONA 667_7

P_VTT

12

SC480

22U/12/Y/10V

SB_HA#35

BREQ4#

BREQ3#

BREQ2#

BREQ1#

BREQ0#

DBI3#

DBI2#

DBI1#

DBI0#

DP3#

DP2#

DP1#

DP0#

AP1#

AP0#

ADSTB1#

ADSTB0#

DSTBP3#

DSTBP2#

DSTBP1#

DSTBP0#

DSTBN3#

DSTBN2#

DSTBN1#

DSTBN0#

SC469

1U/6/Y/10V

C8

A35

C9

A34

A7

A33

A6

A32

B7

A31

C11

A30

D12

A29

E13

A28

B8

A27

A9

A26

D13

A25

E14

A24

C12

A23

B11

A22

B10

A21

A10

A20

F15

A19

D15

A18

D16

A17

C14

A16

C15

A15

A12

A14

B13

A13

B14

A12

B16

A11

A13

A10

D17

A9

C17

A8

A19

A7

C18

A6

B18

A5

A20

A4

A22

A3

B22

C20

C21

B21

B19

AB9

AE12

AD22

AC27

AE17

AC15

AE19

AC18

D9

E10

F14

F17

Y11

Y14

Y17

Y20

Y12

Y15

Y18

Y21

SC391

0.1U/6/X/16V

SB_HA#34

SB_HA#33

SB_HA#32

SB_HA#31

SB_HA#30

SB_HA#29

SB_HA#28

SB_HA#27

SB_HA#26

SB_HA#25

SB_HA#24

SB_HA#23

SB_HA#22

SB_HA#21

SB_HA#20

SB_HA#19

SB_HA#18

SB_HA#17

SB_HA#16

SB_HA#15

SB_HA#14

SB_HA#13

SB_HA#12

SB_HA#11

SB_HA#10

SB_HA#9

SB_HA#8

SB_HA#7

SB_HA#6

SB_HA#5

SB_HA#4

SB_HA#3

SB_REQ#4

SB_REQ#3

SB_REQ#2

SB_REQ#1

SB_REQ#0

SB_DBI#3

SB_DBI#2

SB_DBI#1

SB_DBI#0

SB_DP#3

SB_DP#2

SB_DP#1

SB_DP#0

SB_AP#1

SB_AP#0

SB_ADSTB#1

SB_ADSTB#0

SB_DSTBP#3

SB_DSTBP#2

SB_DSTBP#1

SB_DSTBP#0

SB_DSTBN#3

SB_DSTBN#2

SB_DSTBN#1

SB_DSTBN#0

EC27

PSA2.5VB680MH11/8X11.5/X

Trace Width:12 Mils

VREF_P_VTT_CPU1_0

SB_HA#[35..3] [8,18]

SB_REQ#[4..0] [8,18]

SB_DBI#[3..0] [8,18]

SB_DP#[3..0] [8,18]

SB_AP#[1..0] [8,18]

SB_ADSTB#[1..0] [ 8 ,1 8 ]

SB_DSTBP#[3..0 ] [ 8,18]

SB_DSTBN#[3..0] [8,18]

VREF_P_VTT_CPU1_3

VCCIOPLL_CPU1

AGND_CPU1

PU_VCCPLL_CPU1

Title

Size Document Number Rev

Date: Sheet

GIGA-BYTE TECHNOLOGY CO., LTD.

NOCONA 800 MICS P1

GA-9IVDPC

1

11 70Tuesday, June 14, 2005

1.1

of

5

U35C

L31

VSS9

L29

L27

L25

L23

K30

H30

H28

H26

H24

G31

G29

G27

G25

F30

F28

F25

F19

F13

E31

E29

E23

E17

E15

D30

D28

D27

D21

D11

C31

C29

C25

C19

C13

B30

B28

B23

B17

B15

A31

A29

A27

A21

A11

K28

K26

K24

J31

J29

J27

J25

J23

G9

G5

G3

G1

D D

C C

B B

VSS10

VSS11

VSS12

VSS13

L9

VSS14

L7

VSS15

L5

VSS16

L3

VSS17

L1

VSS18

VSS19

VSS20

VSS21

VSS22

K8

VSS23

K6

VSS24

K4

VSS25

K2

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

J9

VSS32

J7

VSS33

J5

VSS34

J3

VSS35

J1

VSS36

VSS37

VSS38

VSS39

VSS40

H8

VSS41

H6

VSS42

H4

VSS43

H2

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

F7

VSS59

F2

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

E9

VSS66

VSS68

VSS69

VSS70

VSS71

VSS72

D5

VSS73

D2

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

C7

VSS80

VSS82

VSS83

VSS84

VSS85

VSS86

B9

VSS87

B2

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

A5

VSS94

NOCONA 667_7

NOCONA 667

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

VSS161

VSS162

VSS163

VSS164

VSS165

VSS166

VSS167

VSS168

VSS169

VSS170

VSS171

VSS172

VSS173

VSS174

VSS175

VSS176

VSS177

VSS178

VSS179

VSS180

VSS181

VSS182

VSS183

VSS184

VSS185

VSS186

VSS187

VSS188

VSS189

VSS8

VSS7

VSS6

VSS5

VSS4

VSS3

VSS2

VSS1

AA30

AA23

AA17

AA15

AA9

AA2

Y31

Y25

Y19

Y13

Y7

Y5

Y1

W30

W28

W26

W24

W4

W2

V31

V29

V27

V25

V23

V9

V7

V5

V3

V1

U30

U28

U26

U24

U8

U6

U4

U2

T31

T29

T27

T25

T23

T9

T7

T5

T3

T1

R30

R28

R26

R24

R8

R6

R4

R2

P31

P29

P27

P25

P23

P9

P7

P5

P3

P1

N30

N28

N26

N24

N8

N6

N4

N2

M2

M4

M6

M8

M24

M26

M28

M30

P_VCCP1 P_VCCP1

H31

H29

H27

H25

H23

G30

G28

G26

G24

D31

D29

D24

D18

D14

C30

C28

C22

C16

L30

L26

L24

L8

L6

L4

L2

K31

K29

K27

K25

K23

K9

K7

K5

K3

K1

J30

J28

J26

J24

J8

J6

J4

J2

H9

H7

H5

H3

H1

G8

G6

G4

G2

F31

F29

F22

F16

F4

F1

E30

E28

E26

E20

E6

E2

D8

D1

C4

C2

B31

B29

B26

B20

B6

A30

A28

A24

A18

A14

A8

A2

U35D

VCC_CORE1

VCC_CORE2

VCC_CORE3

VCC_CORE4

VCC_CORE5

VCC_CORE6

VCC_CORE7

VCC_CORE8

VCC_CORE9

VCC_CORE10

VCC_CORE11

VCC_CORE12

VCC_CORE13

VCC_CORE14

VCC_CORE15

VCC_CORE16

VCC_CORE17

VCC_CORE18

VCC_CORE19

VCC_CORE20

VCC_CORE21

VCC_CORE22

VCC_CORE23

VCC_CORE24

VCC_CORE25

VCC_CORE26

VCC_CORE27

VCC_CORE28

VCC_CORE29

VCC_CORE30

VCC_CORE31

VCC_CORE32

VCC_CORE33

VCC_CORE34

VCC_CORE35

VCC_CORE36

VCC_CORE37

VCC_CORE38

VCC_CORE39

VCC_CORE40

VCC_CORE41

VCC_CORE42

VCC_CORE43

VCC_CORE44

VCC_CORE45

VCC_CORE46

VCC_CORE47

VCC_CORE48

VCC_CORE49

VCC_CORE50

VCC_CORE51

VCC_CORE52

VCC_CORE53

VCC_CORE54

VCC_CORE55

VCC_CORE56

VCC_CORE57

VCC_CORE58

VCC_CORE59

VCC_CORE60

VCC_CORE61

VCC_CORE62

VCC_CORE63

VCC_CORE64

VCC_CORE65

VCC_CORE66

VCC_CORE67

VCC_CORE68

VCC_CORE69

VCC_CORE70

VCC_CORE71

VCC_CORE72

VCC_CORE73

VCC_CORE74

VCC_CORE75

VCC_CORE76

VCC_CORE77

VCC_CORE78

VCC_CORE79

VCC_CORE80

NOCONA 667_7

4

NOCONA 667

VCC_CORE81

VCC_CORE82

VCC_CORE83

VCC_CORE84

VCC_CORE85

VCC_CORE86

VCC_CORE87

VCC_CORE88

VCC_CORE89

VCC_CORE90

VCC_CORE91

VCC_CORE92

VCC_CORE93

VCC_CORE94

VCC_CORE95

VCC_CORE96

VCC_CORE97

VCC_CORE98

VCC_CORE99

VCC_CORE100

VCC_CORE101

VCC_CORE102

VCC_CORE103

VCC_CORE104

VCC_CORE105

VCC_CORE106

VCC_CORE107

VCC_CORE108

VCC_CORE109

VCC_CORE110

VCC_CORE111

VCC_CORE112

VCC_CORE113

VCC_CORE114

VCC_CORE115

VCC_CORE116

VCC_CORE117

VCC_CORE118

VCC_CORE119

VCC_CORE120

VCC_CORE121

VCC_CORE122

VCC_CORE123

VCC_CORE124

VCC_CORE125

VCC_CORE126

VCC_CORE127

VCC_CORE128

VCC_CORE129

VCC_CORE130

VCC_CORE131

VCC_CORE132

VCC_CORE133

VCC_CORE134

VCC_CORE135

VCC_CORE136

VCC_CORE137

VCC_CORE138

VCC_CORE139

VCC_CORE140

VCC_CORE141

VCC_CORE142

VCC_CORE143

VCC_CORE144

VCC_CORE145

VCC_CORE146

VCC_CORE147

VCC_CORE148

VCC_CORE149

VCC_CORE150

VCC_CORE151

VCC_CORE152

VCC_CORE153

VCC_CORE154

VCC_CORE155

VCC_CORE156

VCC_CORE157

VCC_CORE158

VCC_CORE159

AA31

AA26

AA20

AA6

AA4

AA1

Y30

Y22

Y16

Y2

W31

W29

W27

W25

W1

V30

V28

V26

V24

V8

V6

V4

V2

U31

U29

U27

U25

U23

U9

U7

U5

U3

U1

T30

T28

T26

T24

T8

T6

T4

T2

R31

R29

R27

R25

R23

R9

R7

R5

R3

R1

P30

P28

P26

P24

P8

P6

P4

P2

N31

N29

N27

N25

N23

N9

N7

N5

N3

N1

M31

M29

M27

M25

M23

M9

M7

M5

M3

M1

P_VCCP1

P_VTT

AD12

AC10

AA12

AE24

AE18

AE14

AD30

AD26

AD20

AD6

AD2

AC31

AC22

AC16

AC4

AC3

AB30

AB24

AB18

AB14

AB8

AB2

Y10

F10

E12

C10

B12

AE8

AE3

L28

B4

C5

A4

3

U35E

VCC_VTT1

VCC_VTT2

VCC_VTT3

VCC_VTT4

VCC_VTT5

VCC_VTT6

VCC_VTT7

VCC_VTT8

VCC_VTT9

VCC_VTT10

VCC_VTT11

VCC_CORE160

VCC_CORE161

VCC_CORE162

VCC_CORE163

VCC_CORE164

VCC_CORE165

VCC_CORE166

VCC_CORE167

VCC_CORE168

VCC_CORE169

VCC_CORE170

VCC_CORE171

VCC_CORE172

VCC_CORE173

VCC_CORE174

VCC_CORE175

VCC_CORE176

VCC_CORE177

VCC_CORE178

VCC_CORE179

VCC_CORE180

VCC_CORE181

NOCONA 667_7

NOCONA 667

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

AE2

AD3

AE27

AE21

AE11

AD31

AD23

AD17

AD15

AD9

AC25

AC19

AC13

AC7

AC2

AB31

AB27

AB21

AB11

AB5

AB1

2

1

P3V3 P3V3

ECB

SQ2

MMBT3904

SOT23

CPU1_BSEL1 [5 2 ]

SB_CPU1_BSEL0[11,13]

MMBT3904

SR68

470/6

SR52

470/6

SQ3

SOT23

ECB

CPU1_THERMDA[11]

A A

CPU1_THERMDC[11]

CPU1_THERMDA

CPU1_THERMDC

5

R663

0/6

R662

0/6

CPU1_THERMDA_H7

GNDSIOA

TD2P

C409

100P/6

GNDSIOA

TD2P [53]

GNDSIOA [10,53]

4

MMBT3904

SB_CPU1_BSEL1[11,13]

SR66

470/6

SR51

470/6

SQ1

SOT23

ECB

3

2

ECB

SQ4

MMBT3904

SOT23

CPU1_BSEL0 [5 2]

Title

Size Document Number Rev

Date: Sheet

GIGA-BYTE TECHNOLOGY CO., LTD.

NOCONA 800 P1 PWR/GND

GA-9IVDPC

12 70Tuesday, June 14, 2005

1

of

1.1

P_VTT

5

4

P_VTT

3

2

1

R661 51/6

R780 51/6

R787 51/6

D D

R811 51/6

R786 51/6/X

R784 51/6/X

R785 51/6

C C

SR65 510/6

SR67 510/6

R664 100/6/1

R810 100/6/1

SR77 49.9/6/1

B B

R681 49.9/6/1

A A

SB_CPU1_IERR#

SB_CPU1_PROCHOT#

PU_BOOT_SELECT_CPU1

CPU1_OPTIM_COMPAT_CTRL

R783 51/6/X

SB_CPU1_BREQ#23

SB_CPU1_BSEL1

SB_CPU1_BSEL0

PD_COMP3_CPU1

PD_COMP2_CPU1

PD_COMP1_CPU1

PD_COMP0_CPU1

CPU_PWR_GD[8,9,11,52]

ITP_TCK1[17]

ITP_TCK0[8,11]

5

CPU_PWR_GD

SB_CPU1_IERR# [11,14]

SB_CPU1_PROCHOT# [11,14]

X

PU_BOOT_SELECT_CPU1 [11]

X

CPU1_OPTIM_COMPAT_CTRL [11]

SB_CPU1_BREQ#23 [11]

SB_CPU1_BSEL1 [11,12]

SB_CPU1_BSEL0 [11,12]

PD_COMP3_CPU1 [11]

PD_COMP2_CPU1 [11]

PD_COMP1_CPU1 [11]

PD_COMP0_CPU1 [11]

P_VTT

R792 0/6

MCH_PME#[18,37]

R835 51/6

R828 51/6

ITP_CPU_PWRGOOD

R657 51/6

R658 51/6

R653 51/6

R655 51/6

R652 51/6

R654 51/6

R656 51/6

P3V3_STBY

R779 4.7K/6

CPU_PWR_GD

C396

100P/6/X

CPU0_BPM#5

CPU0_BPM#4

CPU0_BPM#3

CPU0_BPM#2

CPU0_BPM#1

CPU0_BPM#0

CPU1_BPM#5

CPU1_BPM#4

CPU1_BPM#3

CPU1_BPM#2

CPU1_BPM#1

CPU1_BPM#0

MCH_PME# SB_CPURST#_R

ITP_TCK1

ITP_TCK0

4

11

13

15

17

19

21

23

25

27

29

31

33

35

37

39

41

43

45

47

49

51

53

55

57

59

PU_CPU1_8

PU_CPU1_7

PU_CPU1_6

PU_CPU1_5

PU_CPU1_4

PU_CPU1_3

PU_CPU1_2

PU_CPU1_1

PU_CPU1_0

SMC_CPU1_SKTOCC#

CPU_PWR_GD [8,9,11,52]

ITP

1

3

5

7

9

ITP/X

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

54

56

58

60

P1V5

PU_CPU1_8 [ 11]

PU_CPU1_7 [ 11]

PU_CPU1_6 [ 11]

PU_CPU1_5 [ 11]

PU_CPU1_4 [ 11]

PU_CPU1_3 [ 11]

PU_CPU1_2 [ 11]

PU_CPU1_1 [ 11]

PU_CPU1_0 [ 11]

SMC_CPU1_SKTOCC# [11,52,66]

MODE TEST PROCESSOR CONFIGURATION

UP 2-3 P0 INSTALLED;P1 REMOVED

DP 1-2 & 3-4 P0 & P1 INSTALLED

ITP_MCH_DEBUG0

ITP_MCH_DEBUG1

ITP_MCH_DEBUG2

ITP_MCH_DEBUG3

ITP_MCH_DEBUG4

ITP_MCH_DEBUG5

ITP_MCH_DEBUG6

ITP_MCH_DEBUG7

ITP_BCLK

ITP_BCLK#

DBR_RESET#

ITP_TDO_MAIN

ITP_TRST#

ITP_TDI_MAIN

ITP_TMS_MAIN

R895

3

ITP_MCH_DEBUG[7..0]

ITP_BCLK [32]

ITP_BCLK# [32]

ITP_TRST# [8,11,17]

ITP_TMS_MAIN [8,11]

1K/6

TP133

TP250

TP251

TP296

ITP_TMS_MAIN[8,11] ITP_TMS_MCH [17]

ITP_TDI_MAIN[8]

ITP_MCH_DEBUG[7..0] [17]

PLACE WITHIN 1" OF CPU

P_VTT

R882

51/6

ITP_TDI_P1

ITP_TDO_P0

ITP_TDO_P1

R762

51/6

R897 0/6

ITP_TDI_MAIN [8]

ITP_TDI_P1 [11]

ITP_TDO_P0 [8]

ITP_TDO_P1 [11]

R896

51/6/X

SB_CPURST#_R

ITP_TMS_MAIN

DBR_RESET#

ITP_TDI_MAIN

P_VTT

R870

0/6

RN93 51/8P4R

1 2

3 4

5 6

7 8

RN94 51/8P4R

1 2

3 4

5 6

7 8

RN95 51/8P4R

1 2

3 4

5 6

7 8

R841 51/6

R850 51/6

P_VTT

R903

51/6

PLACE WITHIN 1" OF MCH

ITP_TDO_MCH

Title

Size Document Number Rev

2

Date: Sheet

R674 0/6

R847 0/6

R898 0/6

P_VTT

R861

51/6

CPU1_BPM#5

CPU1_BPM#4

CPU1_BPM#3

CPU1_BPM#2

CPU0_BPM#4

CPU1_BPM#1

CPU1_BPM#0

CPU0_BPM#5

CPU0_BPM#0

CPU0_BPM#1

CPU0_BPM#2

CPU0_BPM#3

ITP_TDO_MCH [17]

SB_CPURST#

ITP_TMS_MCH

ITP_RESET#

SB_CPURST# [8,9,11,14,18]

SYS_RESET# [37,53,56]

PLACE WITHIN 1" OF MCH

ITP_TDI_MCH

ITP_TMS_MCH

ITP_TMS_MAIN

ITP_TDI_MCH [17]

CPU1_BPM#[5..0] [11]

CPU0_BPM#[5..0] [8]

ITP_TMS_MCH [17]

ITP_TMS_MAIN [8,11]

GIGA-BYTE TECHNOLOGY CO., LTD.

NOCONA 800 P1 TERMINATION/ITP

GA-9IVDPC

13 70Tuesday, June 14, 2005

1

of

1.1

5

4

3

2

1

check

P_VTT

12

R1864

200/6

package

U184

1

GND

GREF

2

SREF

DREF

3

S1

S24D2

GTL2002/TSSOP8/X

ECB

D1

Q232

MMBT3904

SOT23

8

7

6

5

C1259

0.1U/6/X/16V

1 2

C1474

0.1U/6/Y/10V/X

P_VTT

P_VTT

12

R1872

12

C908

200/6

D D

ICH_CPU_SMI#[37]

0.01U/6/X/50V

ICH_CPU_SMI# GTL_SMI#

Trace Length Limitation

V1.0

ECB

ECB

R856

470/6

R868

470/6

SOT23

SOT23

P3V3

P3V3P5V

R887

300/6

CPU0_PROCHOT#

Q99

MMBT3904

SOT23

ECB

R869

300/6

CPU1_PROCHOT#

Q96

MMBT3904

SOT23

ECB

CPU0_PROCHOT# [36]

CPU1_PROCHOT# [36]

R825

51/6

R867

51/6

P5V

Q93

MMBT3904

Q95

MMBT3904

C C

P_VTT

SB_CPU0_PROCHOT#[8,9]

B B

SB_CPU1_PROCHOT#[11, 13]

SB_CPU0_PROCHOT#

SB_CPU1_PROCHOT#

R833 470/6

P_VTT

R866 470/6

P3V3

P3V3

12

12

R1627

10K/6

1 2

R1632

1K/6

SB_CPURST#[8 , 9 , 1 1, 13,18]

Trace Length Limitation

SB_CPU0_IERR#[8,9]

SB_CPU0_IERR#

Trace Length Limitation

SB_CPU1_IERR#[11,13]

SB_CPU1_IERR#

P_VTT

P_VTT

R826

51/6

R881

51/6

Q194

MMBT2222A/SOT23

R1643 10K/ 6

1 2

Q92

MMBT3904

R832 470/6

Q101

MMBT3904

R880 470/6

53

2 4

P3V3 P_VTT

C1262

53

2 4

R528 0/6

R530 0/6

P5V

Q91

MMBT3904

P_VTTP3V3

12

12

U181

74LVC07/SOT23-5

12

12

U183

74LVC07/SOT23-5

SB_BREQ#0MCH_BREQ#0

SB_BREQ#1

R854

470/6

SOT23

ECB

R1636

51/6/1

SB_CPU0_SMI#

R1642

51/6/1

SB_CPU1_SMI#

SB_BREQ#0 [8,9,11]

SB_BREQ#1 [8,9,11]

P_VTT

R886

51/6/X

ECB

SB_CPU0_SMI# [8]

SB_CPU1_SMI# [11]

CPU_FORCEPR# [8,9,11]

Q97

MMBT3904

SOT23

CPU0/1MCH

P3V3

12

12

R1638

R1637

1K/6

1K/6

BMC_BSP_TRI#[66]

BMC_AP_TRI#[ 66]

P3V3

12

R1641

1K/6

12

C1263

SOT23

0.1U/6/Y/25V

ECB

P5V

R855

470/6

ECB

R879

470/6

ECB

SOT23

SOT23

P3V3

P3V3P5V

R846

4.7K/6

-PROC_IERR0

Q98

MMBT3904

SOT23

ECB

R860

4.7K/6

-PROC_IERR1

Q100

MMBT3904

SOT23

ECB

GTL_SMI#

P3V3

12

R1640

1K/6

D

D

Q193

2N7002

GS

S

G

CPU0_IERR# [66]

CPU1_IERR# [66]

P3V3

16

11

10

14

13

15

SB_CPU_FORCEPR#[53]

12

U182

VCC

2

1A

1Y

3

1B

5

2A

2Y

6

2B

3A

3Y

3B

4A

4Y

4B

1

A/B

G

8

GND

74LCX157/TSSOP16

MCH_BREQ#0[18]

MCH_BREQ#1[18]

C1261

0.1U/6/Y/25V

4

7

9

12

MCH_BREQ#1

P5V

C1260

0.1U/6/Y/25V

0.1U/6/Y/25V

R824

4.7K/6

R831

4.7K/6

R1865

470/6

ECB

R1869

470/6

ECB

SOT23