Gigabyte GA-9ITDW-FJ rev.1.3 Schematic

第1頁,共1頁

Technical Information Release Notice

Technical Information Release Notice

Doc Type Schematic Date 2004/11/2 下午 02:56:37

Project Code S93011-0 Customer FJ JPN

Project Name GS-ST591-FJ Revision Old 1.2 New 1.3

Model Name GA-9ITDW IT Doc No DR04B021

P/N 9M9ITDW00-FJ-13B RD Doc No

PCB Rev. 1.3 Check Sum

M/B GA-9ITDW 1.3B

P/N Description

FINISHED GOOD FUJITSU

Description

Remark

Approved By daniel.hou 2004/11/2 下午 08:55:27 Applicant Vincent.Weng

Research

Management

emily.chin

2004/11/3 下午

03:57:27

R

R

IT

IT

Validation Manager Project Manager

h

h

c

c

r

r

ea

ea

s

e

e

s

2

2

00

00

Effected Class

a

a

M

M

/1

/1

4

4

n

n

1/

1/

a

a

g

g

3

3

e

e

R N M

A B C D E F

A B

t

t

n

n

e

e

m

m

2004/11/3http://gwfap/ef2kweb/CHT/Forms/RTC009/RTC009_P.asp

emily.chin

5

4

3

2

1

GA - 9ITDW-FJ REV 1.3

D D

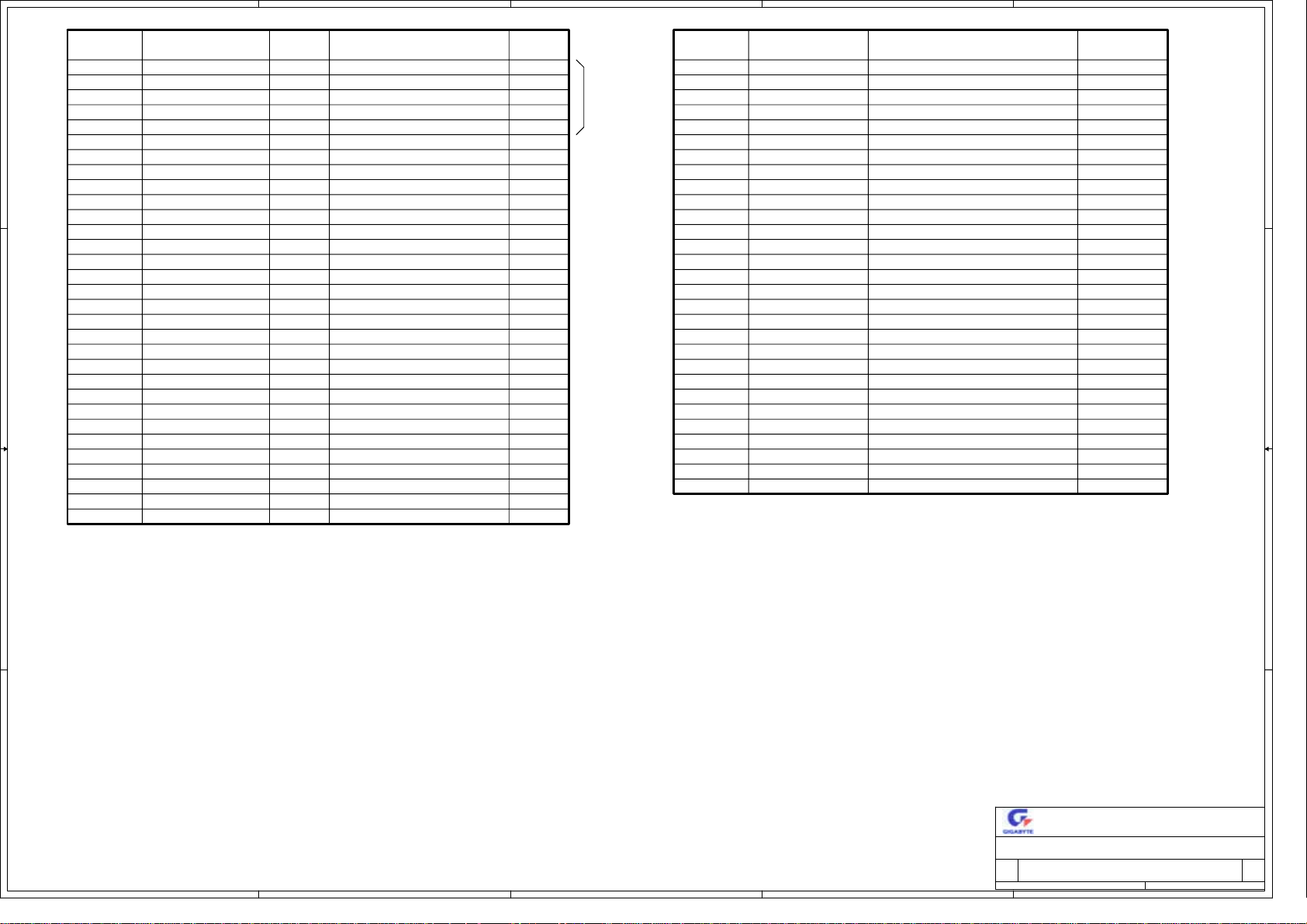

1 TITLE

2 PCB STACK UP

3 SYSTEM BLOCK DIAGRAM

4 GPIO LIST

5 SYSTEM RESET / POWER GOOD DIAGRAM

6 CLOCK BLOCK DIAGRAM

7 SMBUS DIAGRAM

8 POWER DELIVERY DIAGRAM

C C

9-12 NOCONA P0

11-14 NOCONA P1

15 THERMAL SENSORS

16 ITP - EXTENDED DEBUG PORT

17-23 MCH-TUMWATER

24-26 DDRII CHANNEL A

27-29 DDRII CHANNEL B

30 DDRII TERMINATION / DECOUPLING

31-32 CK409B CLOCK GENERATOR

33 DB800 - CLOCK SRC BUFFER

B B

34 X16 PCI EXPRESS SLOT 6

35 PCI EXPRESS SERIES CAPS

36-40 PXH-D/PXH

41-44 U320 SCSI - ADAPTEC AIC7902W

TABLE OF CONTENTS

56 1394a - TSB43AB23

57 SATA / IDE CONNECTOR

58 LPC SUPER I/O - IT8712F

59 FWH

60-61 AUDIO - ALC655 / AUDIO CONNECTOR

62 USB2.0 / USB+RJ-45 CONNECTOR

63 SSI 3.5 POWER / USB+1394 CONNECTOR

64 COM / PS2 / FLOPPY / LPT

65 FRONT PANEL

66 FAN CONTROL

67 VTT / AUX / PCI-X VIO VOLTAGE REGULATORS

68 1.5V / 1.8V / LAN VOLTAGE REGULATOR

69 EVRD 10.1 - PROCESSOR 0 VOLTAGE REGULATORS

70 EVRD 10.1 - PROCESSOR 1 VOLTAGE REGULATORS

71 VID CIRCUITS

72 SMBUS REPEATER / SYSTEM MOUNTING HOLS

73 H/W MONITOR - LM93

74-77 BLANK

78 PCI ROUTING TABLE

79 REVISION HISTORY 0.2

80 REVISION HISTORY 1.0 & 1.1

81 REVISION HISTORY 1.2 & 1.3

45-46 PCI-X 1.0 (100MHz) SLOT 3-4

47 PCI-X 1.0 (133MHz) SLOT 5

48 GbE -Broadcom BCM5751

49 S3/S4 POWER CONTROL & OVP CIRCUIT

50-53 ICH5

54 PCI 32-BIT/33MHz SLOT 1-2

A A

55 GLUE LOGIC (PLD)

Title

Size Document Number Rev

5

4

3

2

Date: Sheet

GIGA-BYTE TECHNOLOGY CO., LTD.

TITLE / TABLE OF CONTENTS

GA-9ITDW-FJ

1

of

181Wednesday, October 13, 2004

1.3

5

D D

4

3

2

1

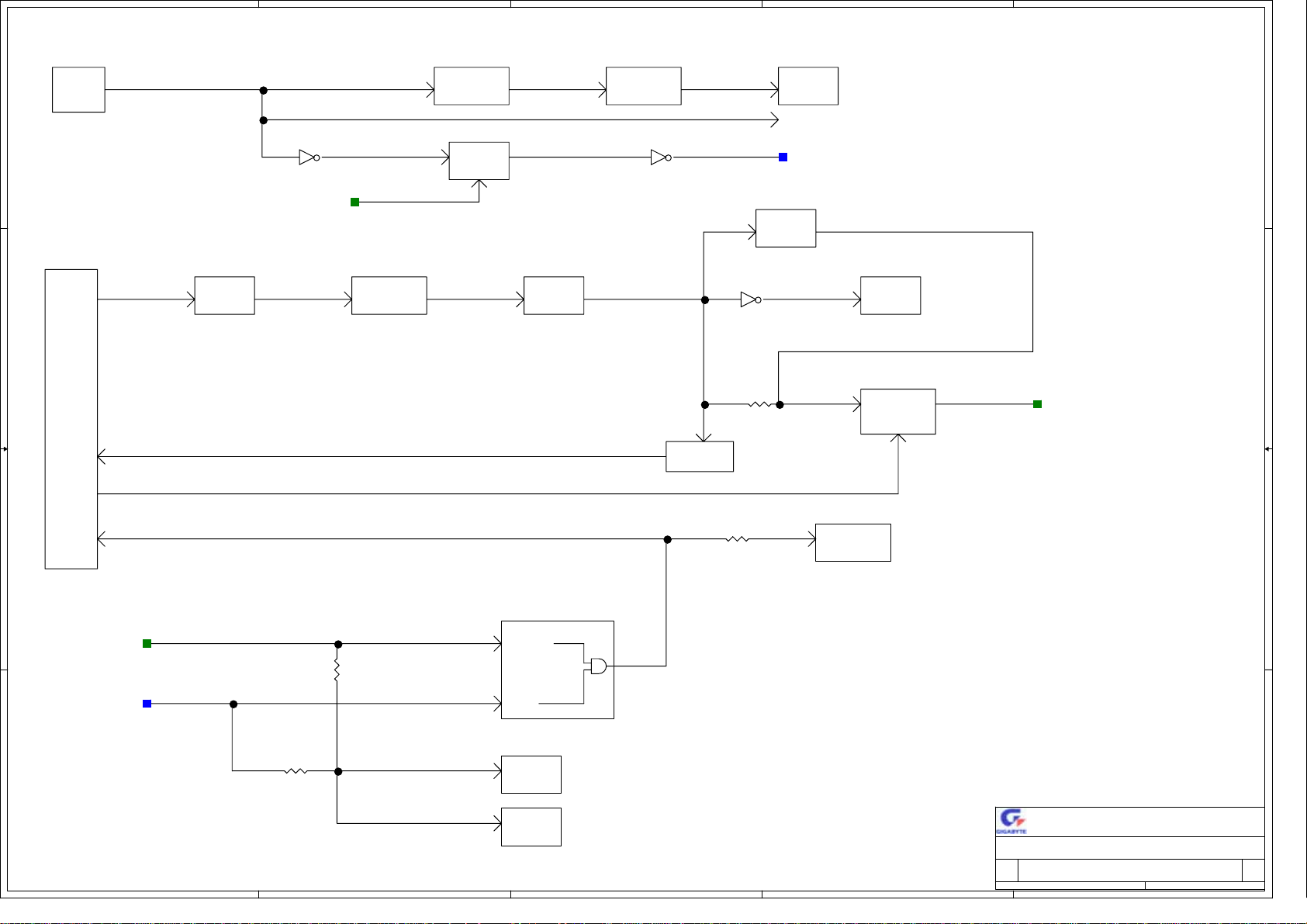

PCB STACK UP

SIGNAL

(3.7-mil)

PREPREG

GND

(3.7-mil)

CORE

SIGNAL

(11.10-mil)

PREPREG

POWER

C C

(10-mil)

CORE

POWER

(11.10-mil)

PREPREG

SIGNAL

(3.7-mil)

CORE

GND

(3.7-mil)

PREPREG

SIGNAL

(2.0-mil/1.5oz Cu Plating)

(1.35-mil / 1.0oz Cu)

(1.35-mil / 1.0oz Cu)

(2.7-mil / 2.0oz Cu)

(2.7-mil / 2.0oz Cu)

(1.35-mil / 1.0oz Cu)

(1.35-mil / 1.0oz Cu)

(2.0-mil/1.5oz Cu Plating)

B B

A A

Title

GIGA-BYTE TECHNOLOGY CO., LTD.

PCB STACK UP

Size Document Number Rev

GA-9ITDW-FJ

5

4

3

Date: Sheet

2

of

281Wednesday, October 13, 2004

1

1.3

5

4

3

2

1

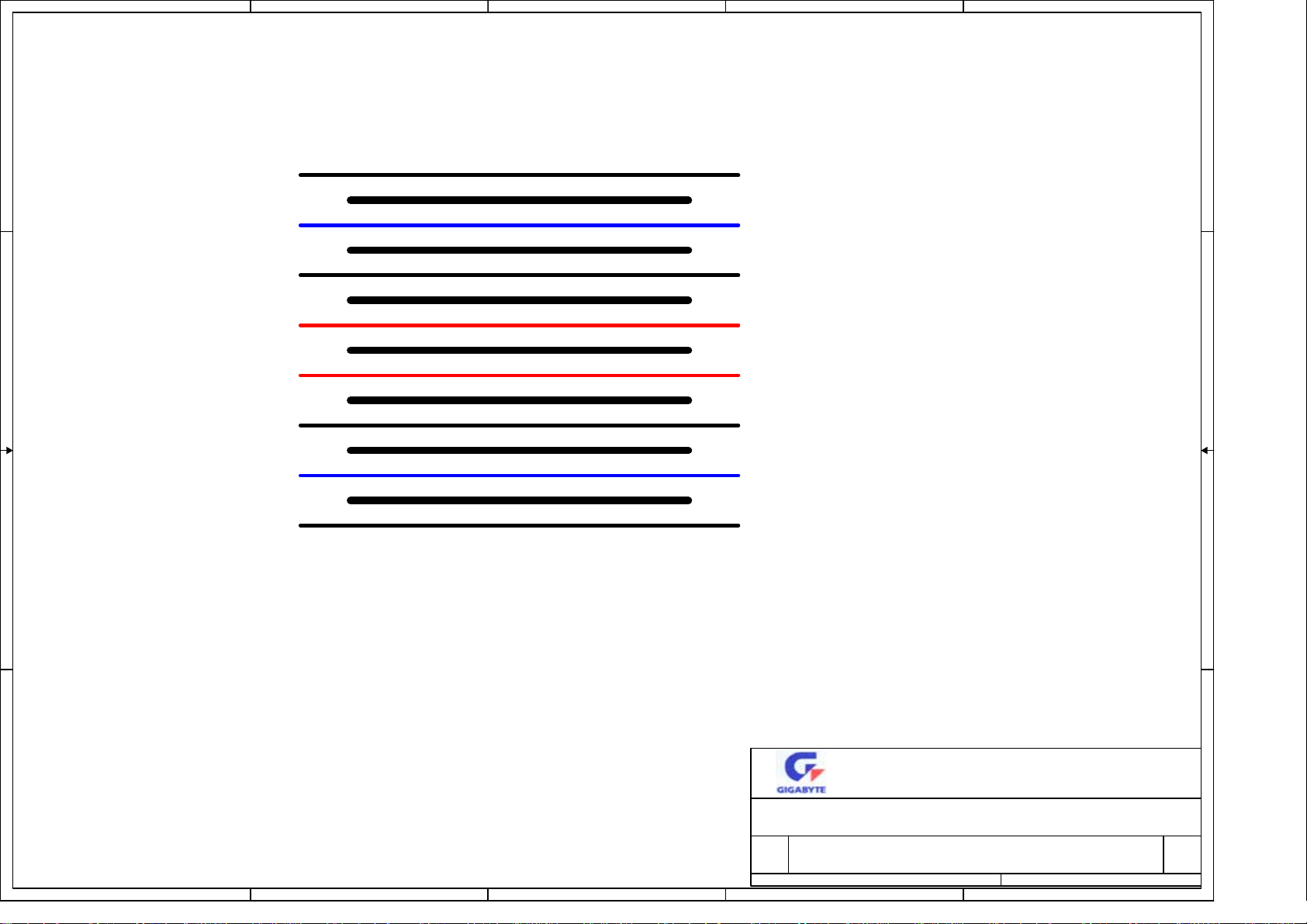

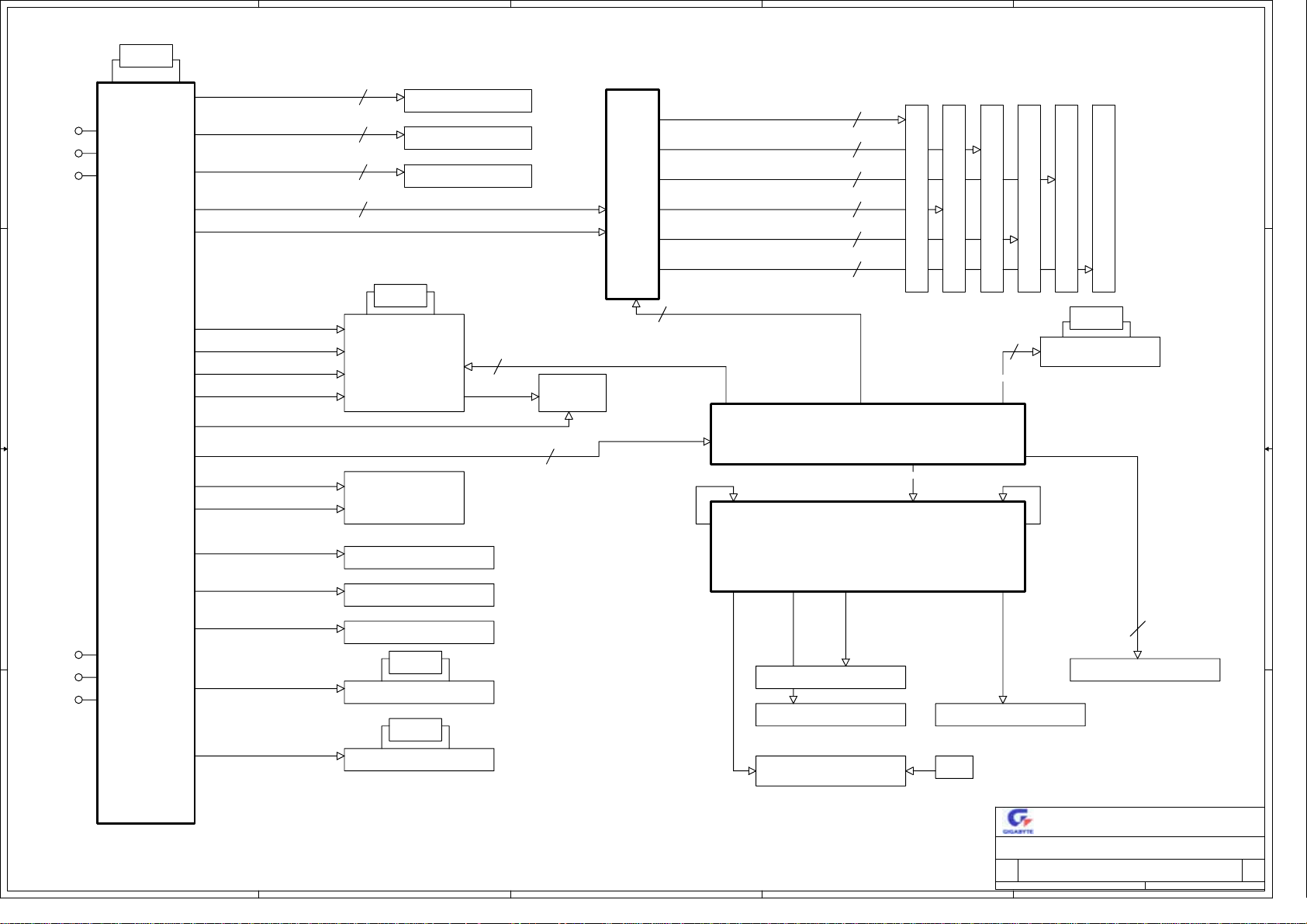

GA - 9ITDW SYSTEM BLOCK DIAGRAM

SCSI 68-pin

CONNECTOR

SCSI 68-pin

CONNECTOR

D D

SLOT #5

PCI-X 133MHz

C C

SLOT #4

PCI-X 100MHz

SLOT #3

SUPPORT ZCR

PCI-X 100MHz

SCSI 0

Dual U320

SCSI

(AIC7902W)

PCI-X (100MT/S - 800MB/S)

PCI-X (133MT/S - 1GB/S)

PCI-X (266MT/S - 2GB/S) if PXH-D

SCSI 1

PXH /

PXH-D

PCI EXPRESS X4 (2 GB/S)

PCI EXPRESS X16 ( 8 GB/S)

BCM5721

PCI EXPRESS X16 SLOT #6

RJ-45

or 5751

PCI EXPRESS X1 (0.5 GB/S)

For TPM interface( BCM 5751 only)

LPC

NOCONA /

JAYHAWK

NOCONA /

JAYHAWK

CPU0 CPU1

System Bus(800MT/S - 6.4GB/S)

Tumwater

MCH

HUB INTERFACE 1.5

DDR II (400MT/S - 3.2GB/S)

DDR II (400MT/S - 3.2GB/S)

USB 2.0 (480 Mb/S)

Channel A

DDRII 400 DIMM Module X 3

Channel B

DDRII 400 DIMM Module X 3

ITP

DEBUG PORT

FRONT PANEL

USB 2.0 X 4

REAR PANEL USB

2.0 X 4

EVRD

10.1

CK409B

CLOCK

DB800

SRC buffer

PCI 32-Bit 33MT/S - 133MB/S

PCI 33MHz

SLOT #1

PCI 33MHz

SLOT #2

B B

400 Mb/s

REAR PANEL

1394 X 1

A A

5

IEEE 1394

TSB43AB23

400 Mb/s

FRONT PANEL

1394 X 2

400 Mb/s

SATA 0

SATA 1

SYSTEM BIOS

COM 1

COM 2

4

Intel

FWH

COM 2

KB / MS

150 MB/s

150 MB/s

LPC

Floppy Connector

ICH5 /

ICH5R

IT 8712F

LPC Super I/O

AC LINK

AC-97 2.3 COMPATIBLE

LPT PORT

3

ATA-100

ATA-100

ALC 658

6CH AC97

CODEC

SYS

FAN1

SYS

FAN2

SYS

FAN3

IDE

Connector X2

AUDIO PHONE

JACK

2

CPU0

FAN

CPU1

FAN

LM93

H/W

MONITOR

GIGA-BYTE TECHNOLOGY CO., LTD.

Title

Size Document Number Rev

Date: Sheet

BLOCK DIAGRAM

GA-9ITDW-FJ

1

381Wednesday, October 13, 2004

of

1.3

5

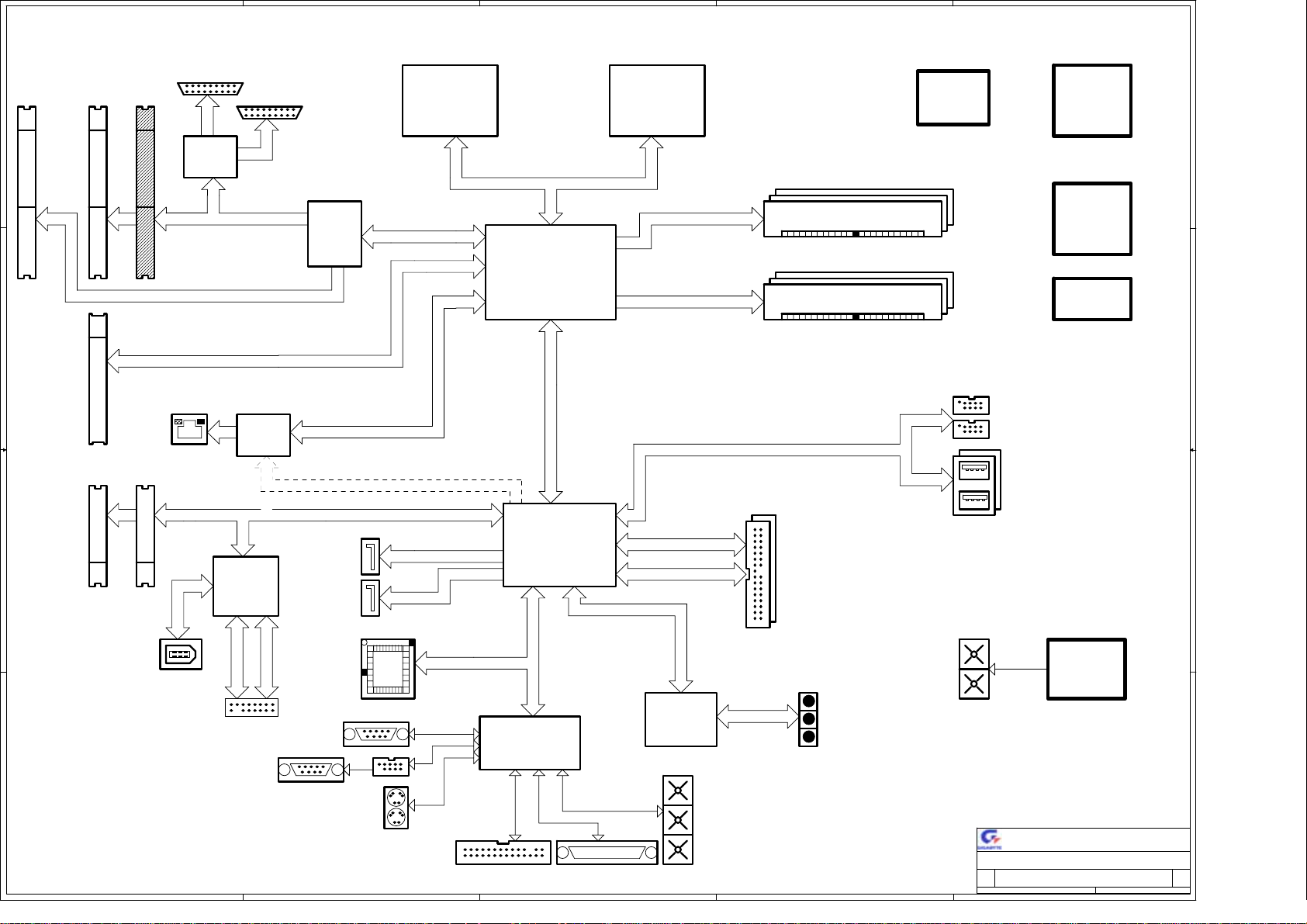

ICH5/R GPIO LIST

ITEM FUNCTION DEFAULT POWER

GPI 0

GPI 1

ICH_SL E E P _BTN# Front Panel sleep button P3V3

GPI [5..2] PCI_PIRQ#H / G / F / E

D D

GPI 6

GPI 7 MCHPME#

GPI 8

GPI 9

MCHGPE# P3V3

WAKE# P3V3_DUAL

CISW_PRESENT#

USB_ICH_OC#5 Not UsedGPI 10 P3V3_DUAL

GPI 11 ICH_SMBALERT#

GPI 12

GPI 13

FP_NMI#

SIO_PME#

GPI [15..14] USB_ICH_OC#7 / 6

TER_SCSIA_EN#

GPO 17

GPO 18

TER_SCSIB_EN#

ICH_GPO18

GPO 19 P3V3SLEEP_S1-5#

CPU0_FORCEPR#GPO 20 P3V3High

C C

GPIO 24

GPIO 25

GPIO 27

GPIO 28

FWH_TBL#GPO 23 P3V3

ICH_PWRLED_G

ICH_PWRLED_O

ICH_MESSAGE

ICH_SCSIDIS#

SKIP_PWD#GPIO 32 P3V3

SATA_LED# P3V3GPIO 33

IDE_PRI_CBLSNS P3V3GPIO 34 Primary IDE cable sense

GPI 40 FREQ_SEL0 P3V3

FREQ_SEL1GPI 41 FSB frequency select 1 P3V3

Low

Secondary IDE cable sense LAN_DISABLE# (OD)P U L L-UPGPIO 10

High

PCI slot interrupts

High

Not Used

High

MCH PME

High

PCI Express Devices Wake Event

High

Chasis Instrusion Switch present detect

High

High

SMBus Alert

High

Front Panel NMI

High

Super I/O PME

High

Not Used

High

SCSI Channel A terminator disable

High

SCSI Channel B terminator disable

High

Not Used

High

Low

F_USB2 S1 ~ S5 wake up enable

FWH write protect

High

High

Front Panel Power-On L ED

LOW

Front Panel Standby LED

High

Front Panel Message LED

High

Onboard SCSI disable

High

Skip Password

High

High

SATA access LED

Low

FSB frequency select 0

High

High

4

DESCRIPTION

P3V3IDE_SEC_CBLSNS

P5V

P3V3

P3V3_DUAL

P3V3_DUAL

P3V3_DUAL

P3V3_DUAL

P3V3_DUAL

P3V3GPO 16

P3V3

P3V3

P3V3GPO 2 1 CPU1_ F O R C E P R # High

P3V3GPO 22(OD) FWH_WP#

P3V3_DUAL

P3V3_DUAL

P3V3_DUAL

P3V3_DUAL

3

5V TOLERANT

GPIO

2

1

IT8712F GPIO LIST

POWER RAILITEM DEFAULT CONDITIONFUNCTION

GPIO 11

GPIO 12

GPIO 13

GPIO 14

GPIO 15

GPIO[16..17]

GPIO 20

GPIO 21

GPIO 22

SCRCLK

SCRIO

SCRFETSCRRST

CIRTX

N.C

SIO_BEEP

N.C

SIO_S1LED#

(OD)PULL-UP

(OD)PULL-UP

(OD)PULL-UP

(OD)PULL-UP

N.C

GPIO 2 5 SIO_SYS_FAN_TACH4 (OD)PULL - UP MAIN(5V)

GPIO [27..23]

GPIO [35..30]

GPIO 36

GPIO 37

GPIO 40

GPIO 41

GPIO 42

GPIO 43

GPIO 44

GPIO 45

GPIO 46

GPIO 47

N.C

N.C

SIO_SYS_FAN_PWM3

SIO_SYS_FAN_TACH3

S5_FUSB_DIS#

S5_RUSB_DIS#

PS_ON#

SIO_PWRBTN#

SIO_PWRON#

SIO_PSIN

IRRX

IRTX

GPIO 50

GPIO 51

GPIO 52

GPIO 53

GPIO 54 RESUME(3V3)

GPIO 55

SIO_SYS_FAN_PWM2

SIO_SYS_FAN_TACH2

SIO_RING#

SIO_PME#

CIRRX

N.C

N.C

(OD)PULL-UP

(OD)PULL-UP

(OD)PULL-UP

(OD)PULL-UP

(OD)ICH5 INTERNAL PULL-UP

(OD)NO PULL-UP, CONTROL BY SLP_S#3

N.C

N.C

(OD)PULL-UP

(OD)PULL-UP

(OD)PULL-UP

N.C

RESUME(3V3)

MAIN(5V)

MAIN(5V)

MAIN(5V)

MAIN(5V)

MAIN(3V3)

MAIN(3V3)(OD)PULL-UP

MAIN(3V3)

MAIN(3V3)

RESUME(3V3)

RESUME(3V3)

RESUME(5V)

RESUME(5V)

RESUME(3V3)

RESUME(3V3)

RESUME

MAIN(5V)

MAIN(3V3)

MAIN(3V3)

RESUME(5V)

RESUME

P3V3GPO 48 TP_OEM_GPIO1 NOT USED,TEST POINT

GPO 4 9 CPU_PWR _GD P_VTT

High

CPU Power Good

IT8712F GPIOs HAVE INTEGRATED OPEN DRAIN INPUT/OUTPUT BUFFER

B B

A A

Title

Size Document Number Rev

5

4

3

2

Date: Sheet

GIGA-BYTE TECHNOLOGY CO., LTD.

POWER TABLE / GPIO LIST

GA-9ITDW-FJ

1

of

481Wednesday, October 13, 2004

1.3

5

4

3

2

1

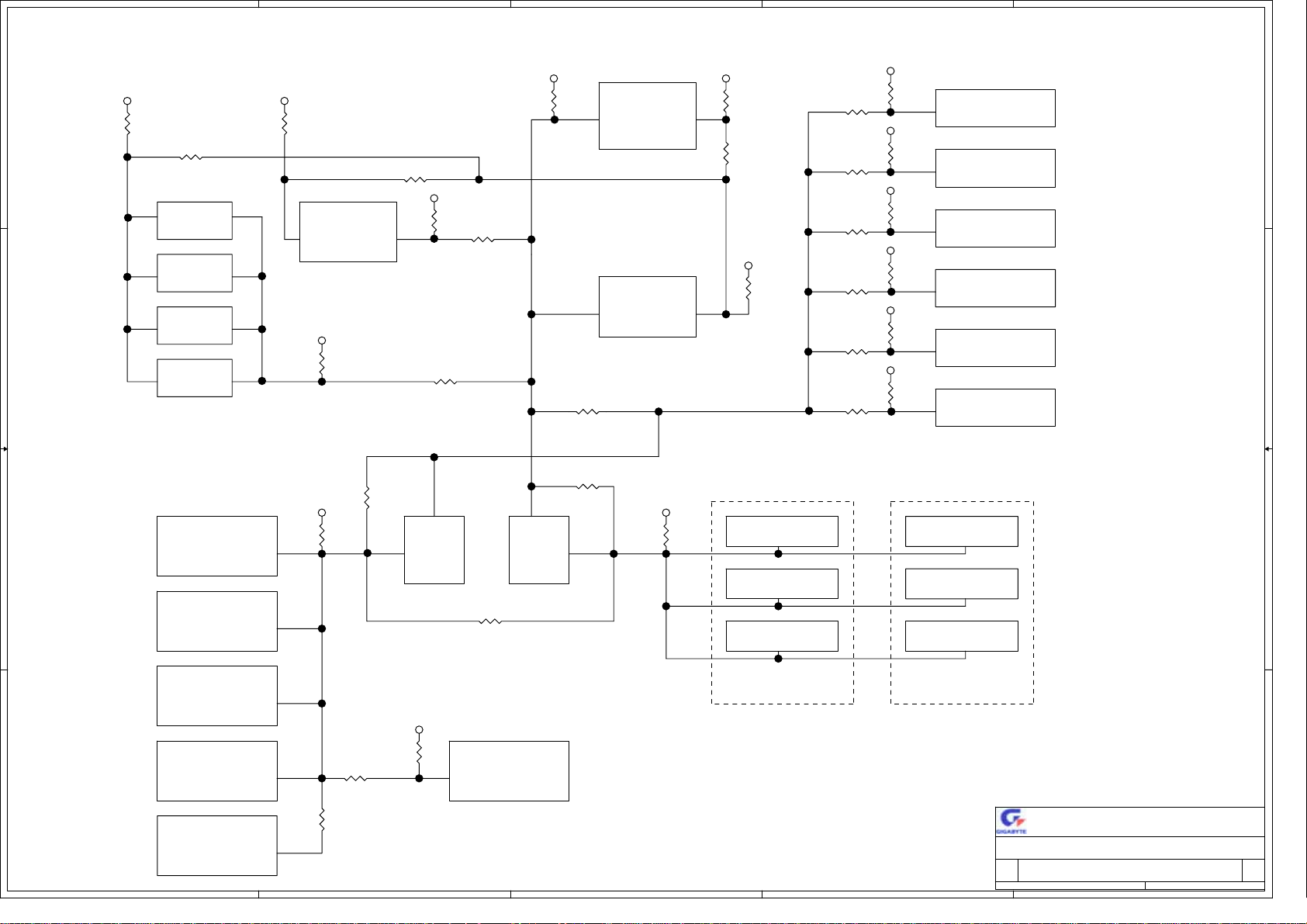

(P5V)

PS_PWR_GD

D D

VR 1.5V soft-start control signal

(P3V3)

PS_PWR_GD#

VR_P1V5PSU

PWRGD_1_5V

SYS_PWR_GD#

VR_P1V8

CPLD

CPU_VRD_PWR_GD

delay 110 ms

(P3V3)

PWRGD_1_8V

CPLD

P3V3_DUAL/P5VDUAL control signal

SYS_PWR_GD_3_3V

CPLD

delay 1 ms

(P3V3) (P3V3)

VTTEN

C C

CPLD

(P3V3)

VTT_ENABLE

VR_VTT

(P3V3)

VTT_PWRGD SB_VTT_PWRGD

CPLD

delay 1 ms

(P3V3)

CK409B_PWR_GD#

CK409B will latch FS[1..0] input after

CK409B_PWR_GD# signal asserted.

CK 409B

CPU

(P3V3)

0/X

(P_VTT)

VID_PWRGD

(P_VTT)

VID[5..0]

(P_VTT)

CPU_PWR_GD

VOLTAGE

TRANSLATOR

(P3V3 to P_VTT)

VR_SYS_ENABLE

VR_CPU

0

CPU_VRD_PWR_GD

ITP

B B

CPU_VRD_PWR_GD

0

SYS_PWR_GD_3_3V

0/X

A A

5

(P3V3)

CK409B_PWRDWN#

4

VRMPWRGD

ICH5

PWROK

CK 409B

DB800

Title

Size Document Number Rev

3

2

Date: Sheet

GIGA-BYTE TECHNOLOGY CO., LTD.

SYSTEM PWRGD DIAGRAM

GA-9ITDW-FJ

1

of

581Wednesday, October 13, 2004

1.3

5

4

3

2

1

14.318MHz

CRYSTAL

P0_BCLK/P0_BCLK# (200MHZ)

CPU0

D D

3V66_0

3V66_3

3V66_4

P1_BCLK/P1_BCLK# (200MHZ)

CPU1

ITP_BCLK/ITP_BCLK# (200MHZ)

CPU3

MCH_BCLK/MCH_BCLK# (200MHZ)

CPU2

MCH_66MHZ_CLK

3V66_1

2

2

2

2

CK 409B

CLOCK

SYNTHESIZER

ICH5_HI66MHZ_CLK

C C

B B

PCIF2

PCI6

PCI 5

A A

3V66_2

USB_48

PCIF0

REF0

PCI 3

SRC

DOT_48

PCI_F1

PCI 0

PCI 1

PCI 2

PCI 4

REF 1

ICH5_USB_48MHZ_CLK

ICH5_33MHZ_CLK

PLD_33MHZ_CLK

DB800_SRC_100MHZ_CLK_P/DB800_SRC_100MHZ_CLK_N

SIO_48MHZ_CLK

SIO_33MHZ_CLK

PCI_SLOT1_33MHZ_CLK

PCI_SLOT2_33MHZ_CLK

FWH_33MHZ_CLK

1394_33MHZ_CLK

AUDIO_14MHZ_CLK

32.768KHZ

CRYSTAL

ICH5

SUS_CLK

SIO

PCI 33MHz SLOT #1

PCI 33MHz SLOT #2

FWH

24.576MHZ

CRYSTAL

TSB43AB23 IEEE-1394

24.576MHZ

CRYSTAL

ALC655 AUDIO CODEC

CLOCK BLOCK DIAGRAM

CPU0

CUP1

ITP PORT

TUMWATER

2

ICH_SRC_100MHZ_CLK_P/ICH_SRC_100MHZ_CLK_N

2

SUS_CLKICH5_14MHZ_CLK

CPLD

2

PXH_PAPCLK_FB PXH_PBPCLK_FB

DDRA_CMDCLK0_P/DDRA_CMDCLK0_N

DDRA_CMDCLK1_P/DDRA_CMDCLK1_N

DDRA_CMDCLK2_P/DDRA_CMDCLK2_N

DDRB_CMDCLK0_P/DDRB_CMDCLK0_N

DDRB_CMDCLK1_P/DDRB_CMDCLK1_N

DDRB_CMDCLK2_P/DDRB_CMDCLK2_N

MCH_SRC_100MHZ_CLK_P/MCH_SRC_100MHZ_CLK_N

DIFF3

DB800 (SRC -DIFFERENTIAL BUFFER)

SRC

PAPCLKI

PAPCLK0(6)

PXH/PXH-D

PAPCLK0(2)

PXH_PAPCLKO2

PXH_PAPCLKO1

PCI-X 100MHz SLOT #4

PCI-X 100MHz SLOT #3V(ZCR) PCI-X 133/266MHz SLOT #5

U320 SCSI

2

2

2

2

DDR II DIMM #A1

2

DDR II DIMM #B1

2

LAN_SRC_100MHZ_CLK_P/LAN_SRC_100MHZ_CLK_N

DIFF6

DIFF2

PXH_SRC_100MHZ_CLK_P/PXH_SRC_100MHZ_CLK_N

PXH_PAPCLKO0

80MHZ

OSC

DIFF7

DIFF0DIFF1 DIFF4 DIFF5

PBPCLKI

PBPCLK0(6)

PBPCLK0(0)PAPCLK0(1) PAPCLK0(0)

DDR II DIMM #A2

2

PXH_PBPCLKO0

DDR II DIMM #B2

DDR II DIMM #B3

DDR II DIMM #A3

25MHZ

CRYSTAL

BCM5751

EXP_SLOT6_100MHZ_CLK_P/EXP_SLOT6_100MHZ_CLK_N

2

PCI EXPRESS X16 SLOT #6

Title

Size Document Number Rev

5

4

3

2

Date: Sheet

GIGA-BYTE TECHNOLOGY CO., LTD.

CLOCK BLOCK DIAGRAM

GA-9ITDW-FJ

1

of

681Wednesday, October 13, 2004

1.3

5

4

3

2

1

GA-9ITDW SMBUS BLOCK DIAGRAM

0/X

0/X

0/X

0/X

0/X

P3V_STBY

P3V_STBY

P3V_STBY

P3V_STBY

P3V_STBY

P3V_STBY

5.1K

5.1K

5.1K

5.1K

5.1K

PCI-EXPRESS X16 Slot

Slot # 1

PCI-X 133MHz Slot

Slot # 2

PCI 33MHz Slot

Slot # 3

PCI 33MHz Slot

Slot # 4

PCI-X 100MHz Slot

Slot # 5

DYNAMIC BUS ADDRESSING FOR I/O SLOTS

P3V_STBY

P3V3_DUAL

D D

1K/X 8.2K

0

LM75

Addr 0X90

CPU0 socket

LM75_SMBALERT#

LM75

Addr 0X92

P3V_STBY

8.2K

ICH_SMB

NIC_SMBALERT# LM93_SMBALERT#

NORTHWAY

82570EI

Addr TBD

0

P3V_STBY

NIC_SMB

8.2K/X

0

DDRII slots

LM75

C C

Addr 0X94

PCI slots

LM75

P3V3_DUAL

1K/X

LM75_SMB

0

ICH5/R

SLAVE ADDR 0X44

( SMBUS DEFAULT )

SLAVE ADDR 0X80

( SMLINK )

LM93

Addr 0X5C

P3V_STBY

8.2K/X

0

P3V_STBY

10K/X

Addr 0X96

SCSI controller

P3V3

0/X

0

0/X

PCI_SMB

P3V3

DIMM A1

MCH TUMWATER

B B

Addr 0X60

5.1K

PCA9515PCA9515

DIMM_SMB

5.1K

Addr 0XA2

DIMM A2

Addr 0XA4

PXH/PXH-D

Addr 0XC0

MCH_SMB

0/X

DIMM A3

Addr 0XA6

5.1K

0/X

PCI-X 100MHz Slot

Slot # 6

DIMM B1

Addr 0XAA

DIMM B2

Addr 0XAC

DIMM B3

Addr 0XAE

2

DDR II CH B

Title

Size Document Number Rev

Date: Sheet

GIGA-BYTE TECHNOLOGY CO., LTD.

SMBUS DIAGRAM

GA-9ITDW-FJ

1

of

781Wednesday, October 13, 2004

1.3

CK409B

DDR II CH A

Addr 0XD2

A A

DB800

Addr 0XDC

0/X

0/X

ITP PORT

MASTER ONLY

5

1394_SMB

4

P3V3

2.7K

IEEE1394 TI

TSB43AB23

DYNAMIC BUS ADDRESSING

3

5

ATX CONN 2X2

4

3

2

1

D D

P12V_CPU_0

EVRD 10.1 PWM

4 PHASE

ISL6556B

+

HIP6601B

MOSFET DRIVER

X4

ATX CONN 2X4

P_VCCP0

105A Typical

120A Maximun

CPU0

0.8375V ~ 1.6V/ CORE

P_VTT

P_VTT

Voltage

Regulator

P12V_CPU_0

4 PHASE

P12V_CPU_1

C C

ATX CONN 2X12

EVRD 10.1 PWM

2 PHASE

ISL6556B

+

HIP6601B

MOSFET DRIVER

HIP6302 HIP6602

P12V

P5V

B B

1.8V PWM MOSFET DRIVER

ISL6525

1.5V PWM

APL1084

APL1084

P3V3

APL1084

P5V_STBY

A A

P5V

P-MOSFET +

N-MOSFET

+

P3V3_DUAL

P2V5_SCSIA

P2V5_SCSIB

P1V8_SCSI

P5V_DUAL P3V3_DUAL

X4

APL1084

P_VCCP1

105A Typical

120A Maximun

P1V8

40A Maximun

APL1084

P1V5

18A Maximun

U320 SCSI

3.3V : 0.36A Typical

2.5V_B : 0.35A Typical

2.5V_A : 0.35A Typical

1.8V : 0.78A Typical

P1V8_STBY

CPU1

0.8375V ~ 1.6V/ CORE

S3/S4

Control

Circuit

PXH

1.5V (Core+PCI-X

MODE2+PCI EXPRESS):

3.1A Max

3.3V (PCI/PCI-X MODE1):

1.8A Max

P3V3

P1V8_AUX

NPN

BJT

P3V3

P1V2_AUX

DDRII

400

MODULE

1.8V : 27.5A Max

TUMWATER

1.5V (Core+HI+PCI

EXPRESS): 5.11A Max

1.8V (DDRII 400): 6.7A Max

1.25V (VTT, FSB): TBD

ICH5/R

1.5V : 1A Max

1.2V (VTT) : 2.5mA Max

3.3V : 0.48A Max

3.3V STBY : 0.58A Max

BCM5751

3.3V : 230mA Typ

2.5V : 210mA Typ

1.2V : 570mA Typ

3.5A Typical

6A Maximun

P0V9_DDR

1.98A Typical

2.1A Maximun

P2V5_AUX

RT9173A

DDR2

TERMINATOR

N12V

Title

Size Document Number Rev

5

4

3

2

Date: Sheet

GIGA-BYTE TECHNOLOGY CO., LTD.

PWR DELIVERY

GA-9ITDW-FJ

1

of

881Wednesday, October 13, 2004

1.3

5

4

3

2

1

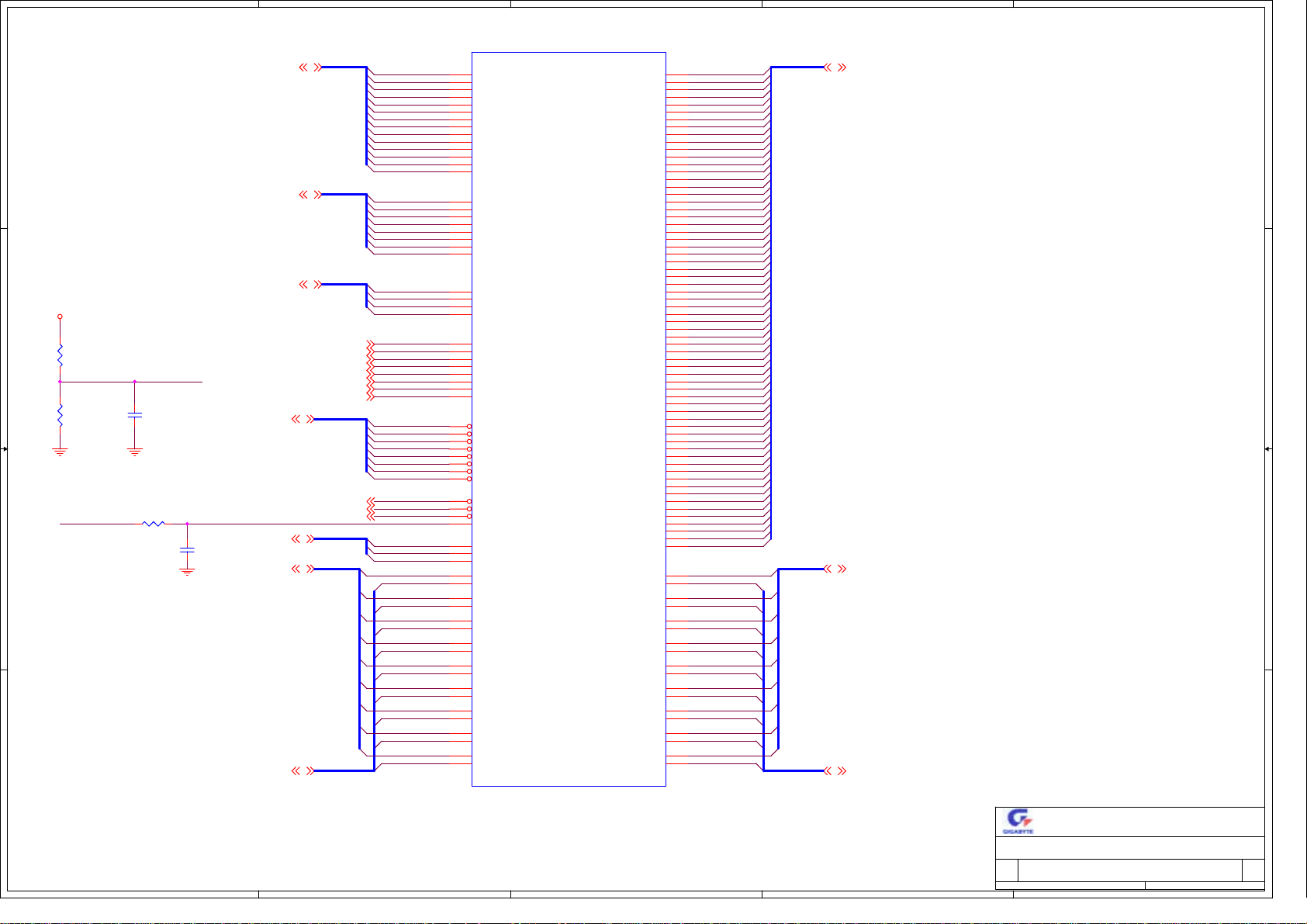

PROCESSOR 0

AB10

AA10

AA11

AB13

AB12

AC14

AA14

AA13

AD10

AC11

AE10

AC12

AD11

AD14

AD13

AB15

AD18

AE13

AC17

AA16

AB16

AB17

AD19

AD21

AE20

AE22

AC21

AC20

AA18

AC23

AE23

AD24

AC24

AE25

AD25

AC26

AE26

AA19

AB19

AB22

AB20

AA21

AA22

AB23

AB25

AB26

AA24

AD27

AA25

AA27

AB6

AA8

AC5

AC6

AE7

AD7

AC8

AC9

AD8

AE9

Y23

Y24

Y26

Y9

U1B

D63#

NOCONA 800

D62#

D61#

D60#

D59#

D58#

D57#

D56#

D55#

D54#

D53#

D52#

D51#

D50#

D49#

D48#

D47#

D46#

D45#

D44#

D43#

D42#

D41#

D40#

D39#

D38#

D37#

D36#

D35#

D34#

D33#

D32#

D31#

D30#

D29#

D28#

D27#

D26#

D25#

D24#

D23#

D22#

D21#

D20#

D19#

D18#

D17#

D16#

D15#

D14#

D13#

D12#

D11#

D10#

D9#

D8#

D7#

D6#

D5#

D4#

D3#

D2#

D1#

D0#

NOCONA 667

A35#

A34#

A33#

A32#

A31#

A30#

A29#

A28#

A27#

A26#

A25#

A24#

A23#

A22#

A21#

A20#

A19#

A18#

A17#

A16#

A15#

A14#

A13#

A12#

A11#

A10#

REQ4#

REQ3#

REQ2#

REQ1#

REQ0#

DBI3#

DBI2#

DBI1#

DBI0#

DP3#

DP2#

DP1#

DP0#

AP1#

AP0#

ADSTB1#

ADSTB0#

DSTBP3#

DSTBP2#

DSTBP1#

DSTBP0#

DSTBN3#

DSTBN2#

DSTBN1#

DSTBN0#

SB_HA#35

C8

SB_HA#34

C9

SB_HA#33

A7

SB_HA#32

A6

SB_HA#31

B7

SB_HA#30

C11

SB_HA#29

D12

SB_HA#28

E13

SB_HA#27

B8

SB_HA#26

A9

SB_HA#25

D13

SB_HA#24

E14

SB_HA#23

C12

SB_HA#22

B11

SB_HA#21

B10

SB_HA#20

A10

SB_HA#19

F15

SB_HA#18

D15

SB_HA#17

D16

SB_HA#16

C14

SB_HA#15

C15

SB_HA#14

A12

SB_HA#13

B13

SB_HA#12

B14

SB_HA#11

B16

SB_HA#10

A13

SB_HA#9

D17

A9#

A8#

A7#

A6#

A5#

A4#

A3#

C17

A19

C18

B18

A20

A22

B22

C20

C21

B21

B19

AB9

AE12

AD22

AC27

AE17

AC15

AE19

AC18

D9

E10

F14

F17

Y11

Y14

Y17

Y20

Y12

Y15

Y18

Y21

SB_HA#8

SB_HA#7

SB_HA#6

SB_HA#5

SB_HA#4

SB_HA#3

SB_REQ#4

SB_REQ#3

SB_REQ#2

SB_REQ#1

SB_REQ#0

SB_DBI#3

SB_DBI#2

SB_DBI#1

SB_DBI#0

SB_DP#3

SB_DP#2

SB_DP#1

SB_DP#0

SB_AP#1

SB_AP#0

SB_ADSTB#1

SB_ADSTB#0

SB_DSTBP#3

SB_DSTBP#2

SB_DSTBP#1

SB_DSTBP#0

SB_DSTBN#3

SB_DSTBN#2

SB_DSTBN#1

SB_DSTBN#0

SB_BPRI#13,19

SB_CPU0_BREQ#2311

SB_BREQ#111,12,13

SB_BREQ#011,12,13

D D

C C

B B

SB_RS#[0..2]13,19

VID_CPU0_R[5..0]71

P_VCCP_A_CPU0

AGND_CPU0

P_VTT

754mV

P_VTT

SB_CPURST#11,13,16,19

SB_RSP#13,19

SB_CPU_A20M#11,13,51

SB_CPU_IGNNE#11,13,51

SB_CPU_INIT#11,13,51,59

SB_CPU_NMI11,12,13

SB_CPU_INTR11,13,51

CPU_PWR_GD11,13,16,51

SB_CPU0_SMI#11,12

SB_CPU_SLP#11,13,51

SB_CPU_STPCLK#11,13

P0_BCLK#31

P0_BCLK31

ITP_TCK013,16

ITP_TDI_MAIN16

ITP_TMS_MAIN13,16

ITP_TRST#13,16,21

SB_CPU0_BSEL111,12

SB_CPU0_BSEL011,12

VR0_VCCSENSE69

VTTEN11,13,55

VR0_VSSSENSE69

PLACE COMPONENTS: GROUP ASSOCIATE COMPONENTS

TOGETHER AND AS PHYISCALLY CLOSE TO ASSOCIATED PIN AS

POSSIBBLE WITH THE 220PF CAP CL OSEST TO THE PIN

MIN TRACE WIDTH >=10 - 12 MILS

SR164

49.9/1%

VREF_P_VTT_CPU0_0_R

SC767

SR165

1U/6/X/10V

90.9/1%

SB_BPRI#

SB_CPU0_BREQ#23

SB_BREQ#1

SB_BREQ#0

SB_CPURST#

SB_RS#2

SB_RS#1

SB_RS#0

SB_RSP#

SB_CPU_A20M#

SB_CPU_IGNNE#

SB_CPU_INIT#

SB_CPU_NMI

SB_CPU_INTR

CPU_PWR_GD

SB_CPU0_SMI#

SB_CPU_SLP#

SB_CPU_STPCLK#

P0_BCLK#

P0_BCLK

ITP_TCK0

ITP_TDI_MAIN

ITP_TMS_MAIN

ITP_TRST#

SB_CPU0_BSEL1

SB_CPU0_BSEL0

TP1

TP2

TP3

TP4

TP5

TP6

TP7

TP8

TP9

TP10

TP11

TP12

TP13

TP14

P0_RSVD13

P0_RSVD12

P0_RSVD11

P0_RSVD10

P0_RSVD9

P0_RSVD8

P0_RSVD7

P0_RSVD6

P0_RSVD5

P0_RSVD4

P0_RSVD3

P0_RSVD2

P0_RSVD1

P0_RSVD0

VID_CPU0_R5

VID_CPU0_R4

VID_CPU0_R3

VID_CPU0_R2

VID_CPU0_R1

VID_CPU0_R0

VR0_VCCSENSE

VTTEN

VR0_VSSSENSE

PLACE 0 OHM RESISTOR ON BACK SIDE

SR160

0

VREF_P_VTT_CPU0_0

SC763

220P/6/X/50V

U1A

D23

BPRI#

D10

E11

F12

D20

F21

D22

E21

F27

C26

G23

B24

AB7

C27

AE6

E24

C24

A25

F24

AB3

AA3

AE29

AE28

AE30

AD29

AD28

AC29

AB29

AB28

AA29

AA28

AE15

AC1

AE16

AD4

B27

AB4

AA5

D26 C1

NOCONA 800

BR3#

BR2#

BR1#

BR0#

Y8

RESET#

RS2#

RS1#

RS0#

C6

RSP#

A20M#

IGNNE#

D6

INIT#

LINT1_NMI

LINT0_INTR

PWRGOOD

SMI#

SLP#

D4

STPCLK#

W5

BCLK1

Y4

BCLK0

TCK

TDI

TMS

TRST#

BSEL1

BSEL0

RESERVED1

RESERVED0

NC

Y3

RSVD15

RSVD14

RSVD13

RSVD12

RSVD10

RSVD9

RSVD8

RSVD7

RSVD3

RSVD2

RSVD1

A1

VID5

B3

VID4

C3

VID3

D3

VID2

E3

VID1

F3

VID0

VCCIOPLL

VCC_SENSE

E1

VTTEN

VCCA

VSSA

VSSSENSE OPTIMIZED_COMPAT#

NOCONA 667

SC764

220P/6/X/50V

ADS#

BINIT#

BNR#

BPM5#

BPM4#

BPM3#

BPM2#

BPM1#

BPM0#

DBSY#

DEFER#

DRDY#

HIT#

HITM#

TRDY#

LOCK#

MCERR#

IERR#

FERR#

THERMTRIP#

PROCHOT#

TDO

GTLREF3

GTLREF2

GTLREF1

GTLREF0

ODTEN

SKTOCC#

RSVD11/COMP3

RSVD5/COMP2

COMP1

COMP0

TESTHI8

TESTHI7

TESTHI6

TESTHI5

TESTHI4

TESTHI3

TESTHI2

TESTHI1

TESTHI0

SMB_PRT

VCCPLL

THERMDC

THERMDA

BOOT_SELECT

RSVD

VIDPWRGD

TEST_BUS

FORCEPR#

SLEW_CTRL

P_VTT

PLACE COMP ONENTS: ROUTE TRACE FROM L1 TO P IN AD4 , ROUTE

TRACE FROM L2 TO PIN AB4 .PLACE CAP BETWEEN AB4 AND

AGND_CPU0 . MI N TR AC E WI DTH >=10 - 12 MILS

SB_ADS#

D19

SB_BINIT#

F11

SB_BNR#

F20

CPU0_BPM#5

E4

CPU0_BPM#4

E8

CPU0_BPM#3

F5

CPU0_BPM#2

E7

CPU0_BPM#1

F8

CPU0_BPM#0

F6

SB_DBSY#

F18

SB_DEFER#

C23

SB_DRDY#

E18

SB_HIT#

E22

SB_HITM#

A23

SB_TRDY#

E19

SB_LOCK#

A17

SB_MCERR#

D7

SB_CPU0_IERR#

E5

SB_CPU_FERR#

E27

SB_CPU_THERMTRIP#

F26

SB_CPU0_PROCHOT#

B25

ITP_TDO_P0

E25

F9

F23

W9

W23

PU_ODTEN_CPU0

B5

SMC_CPU0_SKTOCC#

A3

PU_COMP3_CPU0

D25

PU_COMP2_CPU0

AC28

PD_COMP1_CPU0

E16

PD_COMP0_CPU0

AD16

PU_CPU0_8

Y29

PU_CPU0_0

A26

PU_CPU0_5

AE5

PU_CPU0_6

AD5

PU_CPU0_1

AA7

PU_CPU0_7

Y6

PU_CPU0_3

W8

PU_CPU0_2

W7

PU_CPU0_4

W6

P0_RSVD16

AE4

AD1

CPU0_THERMDC

Y28

CPU0_THERMDA

Y27

PU_BOOT_SELECT_CPU0

G7

P0_RSVD15

W3

VID_PWRGD

B1

SB_CPU0_CPU1_TESTBUS

A16

SB_CPU0_FORCEPR#

A15

SLEW_CTRL_CPU0

AC30

CPU0_OPTIM_COMPAT_CTRL

SB_ADS# 13,19

SB_BINIT# 11,13,19

SB_BNR# 11,13,19

SB_DBSY# 13,19

SB_DEFER# 13,19

SB_DRDY# 13,19

SB_HIT# 11,13,19

SB_HITM# 11,13,19

SB_TRDY# 13,19

SB_LOCK# 13,19

SB_MCERR# 11,13,19

SB_CPU0_IERR# 11,12

SB_CPU_FERR# 11,13,51,53

SB_CPU_THERMTRIP# 11,12,13,51,53

SB_CPU0_PROCHOT# 11,12

ITP_TDO_P0 16

PU_ODTEN_CPU0 11

SMC_CPU0_SKTOCC# 11,15

PU_COMP3_CPU0 11

PU_COMP2_CPU0 11

PD_COMP1_CPU0 11

PD_COMP0_CPU0 11

PU_CPU0_8 11

PU_CPU0_0 11

PU_CPU0_5 11

PU_CPU0_6 11

PU_CPU0_1 11

PU_CPU0_7 11

PU_CPU0_3 11

PU_CPU0_2 11

PU_CPU0_4 11

TP15

CPU0_THERMDC 15

CPU0_THERMDA 15

PU_BOOT_SELECT_CPU0 11

TP16

VID_PWRGD 13,55

SB_CPU0_CPU1_TESTBUS 11,13

SB_CPU0_FORCEPR# 11,12

CPU0_SLEW_CTRL 11

CPU0_OPTIM_COMPAT_CTRL 11

WW35 eMOW: Icc of VCCIOPLL pins : 100 mA

WW35 eMOW: Icc for VCCA pins : 120mA

L1

10UH/8

L2

10UH/8

P_VCCP_A_CPU0

12

C1

22U/1210/X/6.3V

AGND_CPU0

CPU0_BPM#[5..0] 16

SB_D#[63..0]13,19

VREF_P_VTT_CPU0_3

VREF_P_VTT_CPU0_0

PU_VCCPLL_CPU0

SB_D#63

SB_D#62

SB_D#61

SB_D#60

SB_D#59

SB_D#58

SB_D#57

SB_D#56

SB_D#55

SB_D#54

SB_D#53

SB_D#52

SB_D#51

SB_D#50

SB_D#49

SB_D#48

SB_D#47

SB_D#46

SB_D#45

SB_D#44

SB_D#43

SB_D#42

SB_D#41

SB_D#40

SB_D#39

SB_D#38

SB_D#37

SB_D#36

SB_D#35

SB_D#34

SB_D#33

SB_D#32

SB_D#31

SB_D#30

SB_D#29

SB_D#28

SB_D#27

SB_D#26

SB_D#25

SB_D#24

SB_D#23

SB_D#22

SB_D#21

SB_D#20

SB_D#19

SB_D#18

SB_D#17

SB_D#16

SB_D#15

SB_D#14

SB_D#13

SB_D#12

SB_D#11

SB_D#10

SB_D#9

SB_D#8

SB_D#7

SB_D#6

SB_D#5

SB_D#4

SB_D#3

SB_D#2

SB_D#1

SB_D#0

COMP3 =SB_CPU0_ADDR_ERC

COMP2 =SB_CPU0_DATA_ERC

PU_CPU0_8=SB_CPU0_EDRDY

PU_CPU0_0=SB_CPU0_SNPD#

SB_HA#[35..3] 13,19

SB_REQ#[4..0] 13,19

SB_DBI#[3..0] 13,19

SB_DP#[3..0] 13,19

SB_AP#[1..0] 13,19

SB_ADSTB#[1..0] 13,19

SB_DSTBP#[3..0] 13,19

SB_DSTBN#[3..0] 13,19

C1105

P_VTT

12

SC192

22U/1206/X/6.3V

SC2

1U/6/X/10V

2

C1103

0.1U/6/X/16V

Title

Size Document Number Rev

Date: Sheet

GIGA-BYTE TECHNOLOGY CO., LTD.

P0 SYSTEM BUS INTERFACE

GA-9ITDW-FJ

1

1.3

of

981Wednesday, October 13, 2004

SR166

A A

754mV

49.9/1%

SR167

SC768

90.9/1%

1U/6/X/10V

R3, R7: change from 84.5 to 90.9

ohm/ 1% (2004 WW12 eMOW)

PLACE 0 OHM RESISTOR ON BACK SIDE

SR161

0

5

SC766

220P/6/X/50V

VREF_P_VTT_CPU0_3VREF_P_VTT_CPU0_3_R

SC765

220P/6/X/50V

P1V5

R6

0/X

PLACE COMPONENTS: GROUP ASSOCIATE COMPONENTS

TOGETHER AND AS PHYISCALLY CLOSE TO ASSOCIATED PIN AS

POSSIBBLE M IN TRACE W IDTH >=10 - 12 MILS

4

WW35 eMOW: Icc for VCCPLL pin is 220 mA

12

TC1

+

470U/4V/7343/X

12

C4

4.7U/1206/X/10V/X

PU_VCCPLL_CPU0

C5

0.1U/6/X/16V/X

3

C6

0.1U/6/X/16V/X

12

22U/1206/X/6.3V

5

4

3

2

1

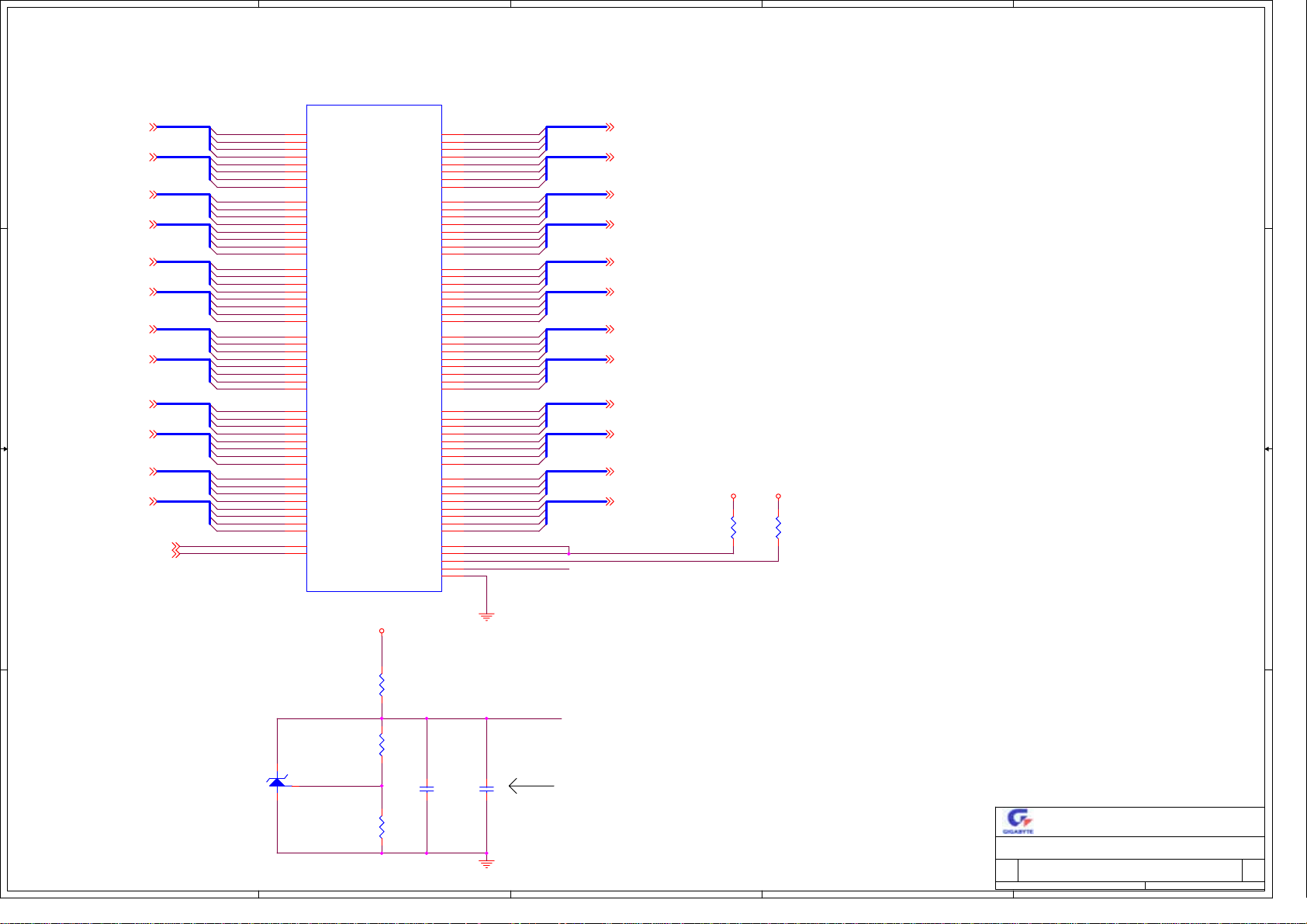

U1C

L31

GND

H30

H28

H26

H24

G31

G29

G27

G25

F30

F28

F25

F19

F13

E31

E29

E23

E17

E15

D30

D28

D27

D21

D11

C31

C29

C25

C19

C13

B30

B28

B23

B17

B15

A31

A29

A27

A21

A11

L29

L27

L25

L23

L9

L7

L5

L3

L1

K30

K28

K26

K24

K8

K6

K4

K2

J31

J29

J27

J25

J23

J9

J7

J5

J3

J1

H8

H6

H4

H2

G9

G5

G3

G1

F7

F2

E9

D5

D2

C7

B9

B2

A5

D D

C C

B B

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

NOCONA 800

NOCONA 667

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

AA30

AA23

AA17

AA15

AA9

AA2

Y31

Y25

Y19

Y13

Y7

Y5

Y1

W30

W28

W26

W24

W4

W2

V31

V29

V27

V25

V23

V9

V7

V5

V3

V1

U30

U28

U26

U24

U8

U6

U4

U2

T31

T29

T27

T25

T23

T9

T7

T5

T3

T1

R30

R28

R26

R24

R8

R6

R4

R2

P31

P29

P27

P25

P23

P9

P7

P5

P3

P1

N30

N28

N26

N24

N8

N6

N4

N2

M2

M4

M6

M8

M24

M26

M28

M30

P_VCCP0 P_VCCP0

H31

H29

H27

H25

H23

G30

G28

G26

G24

F31

F29

F22

F16

E30

E28

E26

E20

D31

D29

D24

D18

D14

C30

C28

C22

C16

B31

B29

B26

B20

A30

A28

A24

A18

A14

U1D

L30

L26

L24

L8

L6

L4

L2

K31

K29

K27

K25

K23

K9

K7

K5

K3

K1

J30

J28

J26

J24

J8

J6

J4

J2

H9

H7

H5

H3

H1

G8

G6

G4

G2

F4

F1

E6

E2

D8

D1

C4

C2

B6

A8

A2

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

NOCONA 800

NOCONA 667

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

L28

AA31

AA26

AA20

AA6

AA4

AA1

Y30

Y22

Y16

Y2

W31

W29

W27

W25

W1

V30

V28

V26

V24

V8

V6

V4

V2

U31

U29

U27

U25

U23

U9

U7

U5

U3

U1

T30

T28

T26

T24

T8

T6

T4

T2

R31

R29

R27

R25

R23

R9

R7

R5

R3

R1

P30

P28

P26

P24

P8

P6

P4

P2

N31

N29

N27

N25

N23

N9

N7

N5

N3

N1

M31

M29

M27

M25

M23

M9

M7

M5

M3

M1

PLACE IN ACCESSIBLE LOCATION

SECONDARY SIDE IS

PREFERABLE

P_VTT

SR1

SR2

0

0

CPU0_TEST0

CPU0_TEST1

P_VCCP0

P_VTT

U1E

B4

C5

A4

NOCONA 800

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

CPU0_TEST0

NOCONA 667

AD12

AC10

AA12

Y10

F10

E12

C10

B12

AE24

AE18

AE14

AE8

AE3

AD30

AD26

AD20

AD6

AD2

AC31

AC22

AC16

AC4

AC3

AB30

AB24

AB18

AB14

AB8

AB2

PIN SIGNAL C-SPEC SIGNAL

C5B4CPU0_TEST1

VCCVIDPRG

VCCFUSEPRG

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

AE2

AD3

AE27

AE21

AE11

AD31

AD23

AD17

AD15

AD9

AC25

AC19

AC13

AC7

AC2

AB31

AB27

AB21

AB11

AB5

AB1

A A

Title

Size Document Number Rev

5

4

3

2

Date: Sheet

GIGA-BYTE TECHNOLOGY CO., LTD.

P0 POWER/GROUND

GA-9ITDW-FJ

1

of

10 81Wednesday, October 13, 2004

1.3

5

4

3

2

1

P_VTT

ROUTE PD_COMP0_CPU0,PD_COMP1_CPU0 AS SHORT AS POSSIBLE, 10-mil WIDE

R10 220

R13 220

D D

C C

B B

A A

SR3 220

R18 220

R20 220

SR5 220

R25 220

R27 220

R30 51/X

SR6 51

R34 51

R36 51

R39 51

SR7 51/X

SR8 51/X

SR10 51

SR11 51

SR12 51

R55 510

R59 510

R62 100/1%

R67 100/1%

P3V3

R74 4.7K

P_VTT

SR13 39

SR14 39

SR15 39

SR16 39

SR17 39

SB_CPU_IGNNE#

SB_CPU_INIT#

SB_CPU_INTR

SB_CPU_SLP#

SB_CPU_STPCLK#

SB_CPU_NMI

SB_CPU0_SMI#

SB_CPU0_FORCEPR#

SB_CPU0_IERR#

SB_CPU0_PROCHOT#

SB_CPU_THERMTRIP#

SB_CPU_FERR#

PU_BOOT_SELECT_CPU0

CPU0_OPTIM_COMPAT_CTRL

SR9 51/X

SB_BREQ#0

SB_BREQ#1

SB_CPU0_BREQ#23

SB_CPU0_BSEL1

SB_CPU0_BSEL0

PU_COMP2_CPU0

PU_COMP3_CPU0

VTTEN

SC6

SB_BINIT#_R

SB_BNR#_R

SB_HIT#_R

SB_HITM#_R SB_HITM#

SB_MCERR#_R

5

47P/6/N/50V

SC7

47P/6/N/50V

SC9

47P/6/N/50V

SC10

47P/6/N/50V

SC11

47P/6/N/50V

SB_BINIT#

SB_BNR#

SB_HIT#

SB_MCERR#

SB_CPU_A20M# 9,13,51

SB_CPU_IGNNE# 9,13,51

SB_CPU_INIT# 9,13,51,59

SB_CPU_INTR 9,13,51

SB_CPU_SLP# 9,13,51

SB_CPU_STPCLK# 9,13

SB_CPU_NMI 9,12,13

SB_CPU0_SMI# 9,12

SB_CPU0_FORCEPR# 9,12

SB_CPU0_IERR# 9,12

SB_CPU0_PROCHOT# 9,12

SB_CPU_THERMTRIP# 9,12,13,51,53

SB_CPU_FERR# 9,13,51,53

PU_BOOT_SELECT_CPU0 9

CPU0_OPTIM_COMPAT_CTRL 9

SB_BREQ#0 9,12,13

SB_BREQ#1 9,12,13

SB_CPU0_BREQ#23 9

SB_CPU0_BSEL1 9,12

SB_CPU0_BSEL0 9,12

PU_COMP2_CPU0 9

PU_COMP3_CPU0 9

VTTEN 9,13,55

SB_BINIT# 9,13,19

SB_BNR# 9,13,19

SB_HIT# 9,13,19

SB_HITM# 9,13,19

SB_MCERR# 9,13,19

4

R11 49.9/1%

SR22 49.9/1%

P_VTT

SR4 51

P_VTT

R29 300

R37 51

R41 51/X

P3V3_DUAL

R49 4.7K

P_VTT

P_VTT

R54 51/X

RN81

1 2

3 4

5 6

7 8

51/8P4R

RN82

1 2

3 4

5 6

7 8

51/8P4R

R72 51/X

Place near CPU1(Middle Agent)

R77 51

PD_COMP1_CPU0SB_CPU_A20M#

PD_COMP0_CPU0

PU_ODTEN_CPU0

CPU_PWR_GD

SC5

100P/6/N/50V/X

PLACE CLOSE TO CPU0

SB_CPURST#

CPU0_SLEW_CTRL

R44 0/X

SMC_CPU0_SKTOCC#

PU_CPU0_8

PU_CPU0_7

PU_CPU0_6

PU_CPU0_5

PU_CPU0_4

PU_CPU0_3

PU_CPU0_2

PU_CPU0_1

PU_CPU0_0

SB_CPU0_CPU1_TESTBUS

R80 100/X

R84 0

PD_COMP1_CPU0 9

PD_COMP0_CPU0 9

PU_ODTEN_CPU0 9

CPU_PWR_GD 9,13,16,51

SB_CPURST# 9,13,16,19

CPU0_SLEW_CTRL 9

SMC_CPU0_SKTOCC# 9,15

PU_CPU0_8 9

PU_CPU0_7 9

PU_CPU0_6 9

PU_CPU0_5 9

PU_CPU0_4 9

PU_CPU0_3 9

PU_CPU0_2 9

PU_CPU0_1 9

PU_CPU0_0 9

SB_CPU0_CPU1_TESTBUS 9,13

ICH_CPU_STPCLK# 51SB_CPU_STPCLK#9,13

3

P_VTT

R12 220

R15 51

R17 51

R19 51

R21 51/X

R24 51/X

R28 51

R31 51/X

R35 510

R38 510

R40 100/1%

R43 100/1%

ROUTE PD_COMP0_CPU1,PD_COMP1_CPU1 AS SHORT AS POSSIBLE, 10-mil WIDE

R46 49.9/1%

R48 49.9/1%

R51 51

P_VTT

R57 51

RN83

1 2

3 4

5 6

7 8

51/8P4R

RN84

1 2

3 4

5 6

7 8

51/8P4R

R76 51

P3V3_DUAL

R79 4.7K

PLACE CLOSE TO CPU1 PIN

2

SB_CPU1_SMI#

SB_CPU1_FORCEPR#

SB_CPU1_IERR#

SB_CPU1_PROCHOT#

PU_BOOT_SELECT_CPU1

CPU1_OPTIM_COMPAT_CTRL

R26 51/X

SB_CPU1_BREQ#23

CPU1_SLEW_CTRL

R33 0

SB_CPU1_BSEL1

SB_CPU1_BSEL0

PU_COMP3_CPU1

PU_COMP2_CPU1

PD_COMP1_CPU1

PD_COMP0_CPU1

PD_ODTEN_CPU1

PU_CPU1_8

PU_CPU1_7

PU_CPU1_6

PU_CPU1_5

PU_CPU1_4

PU_CPU1_3

PU_CPU1_2

PU_CPU1_1

PU_CPU1_0

SMC_CPU1_SKTOCC#

SC8

CPU_PWR_GD

100P/6/N/50V/X

Title

Size Document Number Rev

Date: Sheet

GIGA-BYTE TECHNOLOGY CO., LTD.

NOCONA P0 TERMINATION

SB_CPU1_SMI# 12,13

SB_CPU1_FORCEPR# 12,13

SB_CPU1_IERR# 12,13

SB_CPU1_PROCHOT# 12,13

PU_BOOT_SELECT_CPU1 13

CPU1_OPTIM_COMPAT_CTRL 13

SB_CPU1_BREQ#23 13

CPU1_SLEW_CTRL 13

SB_CPU1_BSEL1 12,13

SB_CPU1_BSEL0 12,13

PU_COMP3_CPU1 13

PU_COMP2_CPU1 13

PD_COMP1_CPU1 13

PD_COMP0_CPU1 13

PD_ODTEN_CPU1 13

PU_CPU1_8 13

PU_CPU1_7 13

PU_CPU1_6 13

PU_CPU1_5 13

PU_CPU1_4 13

PU_CPU1_3 13

PU_CPU1_2 13

PU_CPU1_1 13

PU_CPU1_0 13

SMC_CPU1_SKTOCC# 13,55

CPU_PWR_GD 9,13,16,51

GA-9ITDW-FJ

1

1.3

of

11 81Wednesday, October 13, 2004

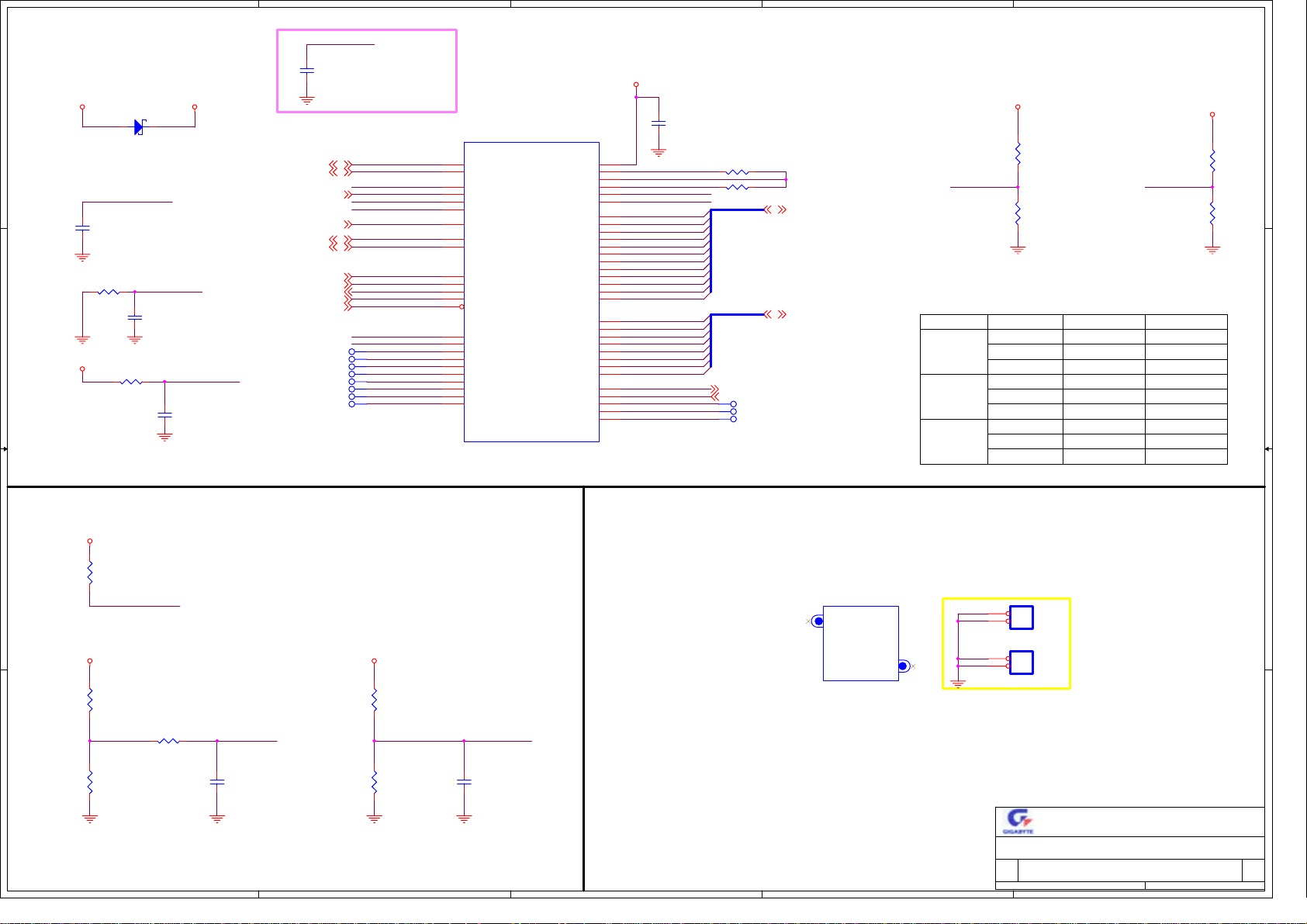

PROCESSOR 0 TERMINATION PROCESSOR 1 TERMINATION

5

D D

SB_CPU1_BSEL011,13

SB_CPU1_BSEL111,13

C C

R88

SB_CPU1_BSEL0_R SB_CPU0_BSEL0_R

100

R92

SB_CPU1_BSEL1_R

100

P3V3

ECB

R86

3.3K

CPU1_BSEL0_N

Q3

MMBT2222A

SOT23

R90

3.3K

CPU1_BSEL1_N

Q7

MMBT2222A

SOT23

ECB

4

ECB

ECB

Q1

MMBT2222A

SOT23

Q5

MMBT2222A

SOT23

3

CPU1_BSEL0 55 CPU0_BSEL0 31,55

SB_CPU0_BSEL09,11

CPU1_BSEL1 55

SB_CPU0_BSEL19,11

R89

100

R93

100

2

SB_CPU0_BSEL1_R

P3V3

CPU0_BSEL0_N

ECB

P3V3P3V3

R91

3.3K

CPU0_BSEL1_N

ECB

R87

3.3K

Q4

MMBT2222A

SOT23

Q8

MMBT2222A

SOT23

ECB

ECB

Q2

MMBT2222A

SOT23

Q6

MMBT2222A

SOT23

1

CPU0_BSEL1 31,55

SC14

0.01U/6/X/50V

R116 4.7K

R117 4.7K

5

R94 0/X

R98 0

R99 0/X

R100 0

R94, R99 UNSTUFF ED

R98, R100 UNSTUFFED

R107

200

R108

200

R109

220

GTL_B01

CPU1_FORCEPR#51,53

VR1_FORCEPR#70,73

CPU0_FORCEPR#51,53

VR0_FORCEPR#69,73

(* DEFAULT)

STUFFING OPTIONS FOR FORCEPR:

* THERMAL CIRCUIT SUPPORT: R98, R100 STUFFED

GPIO SUPPORT: R94, R99 STUFF ED

B B

P_VTT

SC13

1U/6/X/10V

SB_CPU1_IERR#11,13

SB_CPU0_IERR#9,11

SB_CPU0_PROCHOT#9,11

SB_CPU1_PROCHOT#11,13

A A

SB_CPU_THERMTRIP#9,11,13,51,53

SB_CPU0_FORCEPR#9,11

SB_CPU1_FORCEPR#11,13

ICH_CPU_SMI#51

SB_ICH_NMI51

P3V3

CPU1_FORCEPR#_R

CPU0_FORCEPR#_R

R110

51

PU_DIS_CPU0#

PU_DIS_CPU1#

R111

51

R112

51/X

R113

51

BSP SEL

MCH_BREQ#0

MCH_BREQ#119

P_VTT

R103

P_VTT

R114

R115

51

220

4

49.9/1%

GTL2006_VREF

R106

100/1%

U8

1

VREF

27

1BI

26

2BI

19

3BI

18

4BI

21

5BI

25

7BO1

20

6BI

24

7BO2

23

8BO

9

9BI

12

10AI1

13

10AI2

7

11BI

SC15

1U/6/X/10V

VCC

1AO

2AO

3AO

4AO

8AI

9AO

10BO1

10BO2

11BO

11AGND

GTL2006/TSSOP28

5A

6A

P3V3

28

2

3

10

11

4

5

6

15

17

16

22

814

TP_SMC_SMI#_R

PU_SMC_CPU_NMI

SC16

1U/6/X/10V

P3V3

3

R104

220

R105

1K

CPU0_FORCEPR#_RGTL_BI

CPU1_FORCEPR#_R

R1134

TP17

1K/X

R1135

1K/X

CPU1_IERR# 73

CPU0_IERR# 73

CPU0_PROCHOT# 73

CPU1_PROCHOT# 73

CPU_THERMTRIP# 73

SB_CPU0_SMI# 9,11

SB_CPU1_SMI# 11,13

SB_CPU_NMI 9,11,13

MCH_BREQ#1

2

R95 0

R96 0

Title

Size Document Number Rev

Date: Sheet

SB_BREQ#0

SB_BREQ#1

SB_BREQ#0 9,11,13MCH_BREQ#019

SB_BREQ#1 9,11,13

GIGA-BYTE TECHNOLOGY CO., LTD.

NOCONA FREQ. SELECT LOGIC

GA-9ITDW-FJ

1

of

12 81Wednesday, October 13, 2004

1.3

5

4

3

2

1

PROCESSOR 1

SB_BPRI#9,19

SB_CPU1_BREQ#2311

SB_BREQ#09,11,12

SB_BREQ#19,11,12

D D

SB_RS#[0..2]9,19

C C

VID_CPU1_R[5..0]71

B B

P_VTT

754mV

P_VTT

SB_CPURST#9,11,16,19

SB_RSP#9,19

SB_CPU_A20M#9,11,51

SB_CPU_IGNNE#9,11,51

SB_CPU_INIT#9,11,51,59

SB_CPU_NMI9,11,12

SB_CPU_INTR9,11,51

CPU_PWR_GD9,11,16,51

SB_CPU1_SMI#11,12

SB_CPU_SLP#9,11,51

SB_CPU_STPCLK#9,11

P1_BCLK#31

P1_BCLK31

ITP_TCK09,16

ITP_TDI_P116

ITP_TMS_MAIN9,16

ITP_TRST#9,16,21

SB_CPU1_BSEL111,12

SB_CPU1_BSEL011,12

P_VCCP_A_CPU1

VR1_VCCSENSE70

VTTEN9,11,55

AGND_CPU1

VR1_VSSSENSE70

PLACE COMPONENTS: GROUP ASSOCIATE COMPONENTS

TOGETHER AND AS PHYISCALLY CLOSE TO ASSOCIATED PIN AS

POSSIBBLE WITH THE 220PF CAP CL OSEST TO THE PIN

MIN TRACE WIDTH >=10 - 12 MILS

R118

49.9/1%

VREF_P_VTT_CPU1_0_R

C8

R120

1U/6/X/10V

84.5/1%

SB_BPRI#

SB_CPU1_BREQ#23

SB_BREQ#0

SB_BREQ#1

SB_CPURST#

SB_RS#2

SB_RS#1

SB_RS#0

SB_RSP#

SB_CPU_A20M#

SB_CPU_IGNNE#

SB_CPU_INIT#

SB_CPU_NMI

SB_CPU_INTR

CPU_PWR_GD

SB_CPU1_SMI#

SB_CPU_SLP#

SB_CPU_STPCLK#

P1_BCLK#

P1_BCLK

ITP_TCK0

ITP_TDI_P1

ITP_TMS_MAIN

ITP_TRST#

SB_CPU1_BSEL1

SB_CPU1_BSEL0

TP18

TP19

TP20

TP21

TP22

TP23

TP24

TP25

TP26

TP27

TP28

TP29

TP30

TP31

P1_RSVD13

P1_RSVD12

P1_RSVD11

P1_RSVD10

P1_RSVD9

P1_RSVD8

P1_RSVD7

P1_RSVD6

P1_RSVD5

P1_RSVD4

P1_RSVD3

P1_RSVD2

P1_RSVD1

P1_RSVD0

VID_CPU1_R5

VID_CPU1_R4

VID_CPU1_R3

VID_CPU1_R2

VID_CPU1_R1

VID_CPU1_R0

VR1_VCCSENSE

VTTEN

VR1_VSSSENSE

PLACE 0 OHM RESISTOR ON BACK SIDE

SR162

0

VREF_P_VTT_CPU1_0

C12

220P/6/X/50V

U2A

D23

BPRI#

D10

E11

F12

D20

F21

D22

E21

F27

C26

G23

B24

AB7

C27

AE6

E24

C24

A25

F24

AB3

AA3

AE29

AE28

AE30

AD29

AD28

AC29

AB29

AB28

AA29

AA28

AE15

AC1

AE16

AD4

B27

AB4

AA5

D26 C1

C13

220P/6/X/50V

NOCONA 800

BR3#

BR2#

BR1#

BR0#

Y8

RESET#

RS2#

RS1#

RS0#

C6

RSP#

A20M#

IGNNE#

D6

INIT#

LINT1_NMI

LINT0_INTR

PWRGOOD

SMI#

SLP#

D4

STPCLK#

W5

BCLK1

Y4

BCLK0

TCK

TDI

TMS

TRST#

BSEL1

BSEL0

RESERVED1

RESERVED0

NC

Y3

RSVD15

RSVD14

RSVD13

RSVD12

RSVD10

RSVD9

RSVD8

RSVD7

RSVD3

RSVD2

RSVD1

A1

VID5

B3

VID4

C3

VID3

D3

VID2

E3

VID1

F3

VID0

VCCIOPLL

VCC_SENSE

E1

VTTEN

VCCA

VSSA

VSSSENSE OPTIMIZED_COMPAT#

NOCONA 667

ADS#

BINIT#

BNR#

BPM5#

BPM4#

BPM3#

BPM2#

BPM1#

BPM0#

DBSY#

DEFER#

DRDY#

HIT#

HITM#

TRDY#

LOCK#

MCERR#

IERR#

FERR#

THERMTRIP#

PROCHOT#

TDO

GTLREF3

GTLREF2

GTLREF1

GTLREF0

ODTEN

SKTOCC#

RSVD11/COMP3

RSVD5/COMP2

COMP1

COMP0

TESTHI8

TESTHI7

TESTHI6

TESTHI5

TESTHI4

TESTHI3

TESTHI2

TESTHI1

TESTHI0

SMB_PRT

VCCPLL

THERMDC

THERMDA

BOOT_SELECT

RSVD

VIDPWRGD

TEST_BUS

FORCEPR#

SLEW_CTRL

P_VTT

10UH/8

10UH/8

PLACE COMP ONENTS: ROUTE TRACE FROM L1 TO P IN AD4 , ROUTE

TRACE FROM L2 TO PIN AB4 .PLACE CAP BETWEEN AB4 AND

AGND_CPU0 . MI N TR AC E WI DTH >=10 - 12 MILS

D19

F11

F20

E4

E8

F5

E7

F8

F6

F18

C23

E18

E22

A23

E19

A17

D7

E5

E27

F26

B25

E25

F9

F23

W9

W23

B5

SMC_CPU1_SKTOCC#

A3

PU_COMP3_CPU1

D25

PU_COMP2_CPU1

AC28

PD_COMP1_CPU1

E16

PD_COMP0_CPU1

AD16

PU_CPU1_8

Y29

PU_CPU1_0

A26

PU_CPU0_5

AE5

PU_CPU1_6

AD5

PU_CPU1_1

AA7

PU_CPU1_7

Y6

PU_CPU1_3

W8

PU_CPU1_2

W7

PU_CPU1_4

W6

P1_RSVD16

AE4

AD1

CPU1_THERMDC

Y28

CPU1_THERMDA

Y27

PU_BOOT_SELECT_CPU1

G7

P1_RSVD15

W3

VID_PWRGD

B1

SB_CPU0_CPU1_TESTBUS

A16

SB_CPU1_FORCEPR#

A15

CPU1_SLEW_CTRL

AC30

CPU1_OPTIM_COMPAT_CTRL

L3

L4

SB_ADS#

SB_BINIT#

SB_BNR#

CPU1_BPM#5

CPU1_BPM#4

CPU1_BPM#3

CPU1_BPM#2

CPU1_BPM#1

CPU1_BPM#0

SB_DBSY#

SB_DEFER#

SB_DRDY#

SB_HIT#

SB_HITM#

SB_TRDY#

SB_LOCK#

SB_MCERR#

SB_CPU1_IERR#

SB_CPU_FERR#

SB_CPU_THERMTRIP#

SB_CPU1_PROCHOT#

ITP_TDO_P1

PD_ODTEN_CPU1

12

C11

22U/1210/X/6.3V

SB_ADS# 9,19

SB_BINIT# 9,11,19

SB_BNR# 9,11,19

SB_DBSY# 9,19

SB_DEFER# 9,19

SB_DRDY# 9,19

SB_HIT# 9,11,19

SB_HITM# 9,11,19

SB_TRDY# 9,19

SB_LOCK# 9,19

SB_MCERR# 9,11,19

SB_CPU1_IERR# 11,12

SB_CPU_FERR# 9,11,51,53

SB_CPU_THERMTRIP# 9,11,12,51,53

SB_CPU1_PROCHOT# 11,12

ITP_TDO_P1 16

PD_ODTEN_CPU1 11

SMC_CPU1_SKTOCC# 11,55

PU_COMP3_CPU1 11

PU_COMP2_CPU1 11

PD_COMP1_CPU1 11

PD_COMP0_CPU1 11

PU_CPU1_8 11

PU_CPU1_0 11

PU_CPU1_5 11

PU_CPU1_6 11

PU_CPU1_1 11

PU_CPU1_7 11

PU_CPU1_3 11

PU_CPU1_2 11

PU_CPU1_4 11

TP32

CPU1_THERMDC 15

CPU1_THERMDA 15

PU_BOOT_SELECT_CPU1 11

TP33

VID_PWRGD 9,55

SB_CPU0_CPU1_TESTBUS 9,11

SB_CPU1_FORCEPR# 11,12

CPU1_SLEW_CTRL 11

CPU1_OPTIM_COMPAT_CTRL 11

P_VCCP_A_CPU1

AGND_CPU1

CPU1_BPM#[5..0] 16

SB_D#[63..0]9,19

VREF_P_VTT_CPU1_3

VREF_P_VTT_CPU1_0

PU_VCCPLL_CPU1

SB_D#63

SB_D#62

SB_D#61

SB_D#60

SB_D#59

SB_D#58

SB_D#57

SB_D#56

SB_D#55

SB_D#54

SB_D#53

SB_D#52

SB_D#51

SB_D#50

SB_D#49

SB_D#48

SB_D#47

SB_D#46

SB_D#45

SB_D#44

SB_D#43

SB_D#42

SB_D#41

SB_D#40

SB_D#39

SB_D#38

SB_D#37

SB_D#36

SB_D#35

SB_D#34

SB_D#33

SB_D#32

SB_D#31

SB_D#30

SB_D#29

SB_D#28

SB_D#27

SB_D#26

SB_D#25

SB_D#24

SB_D#23

SB_D#22

SB_D#21

SB_D#20

SB_D#19

SB_D#18

SB_D#17

SB_D#16

SB_D#15

SB_D#14

SB_D#13

SB_D#12

SB_D#11

SB_D#10

SB_D#9

SB_D#8

SB_D#7

SB_D#6

SB_D#5

SB_D#4

SB_D#3

SB_D#2

SB_D#1

SB_D#0

COMP3 =SB_CPU1_ADDR_ERC

COMP2 =SB_CPU1_DATA_ERC

PU_CPU1_8=SB_CPU1_EDRDY

PU_CPU1_0=SB_CPU1_SNPD#

AB6

AA8

AC5

AC6

AE7

AD7

AC8

AB10

AA10

AA11

AB13

AB12

AC14

AA14

AA13

AC9

AD8

AD10

AE9

AC11

AE10

AC12

AD11

AD14

AD13

AB15

AD18

AE13

AC17

AA16

AB16

AB17

AD19

AD21

AE20

AE22

AC21

AC20

AA18

AC23

AE23

AD24

AC24

AE25

AD25

AC26

AE26

AA19

AB19

AB22

AB20

AA21

AA22

AB23

AB25

AB26

AA24

Y23

AD27

AA25

Y24

AA27

Y26

Y9

U2B

D63#

NOCONA 800

D62#

D61#

D60#

D59#

D58#

D57#

D56#

D55#

D54#

D53#

D52#

D51#

D50#

D49#

D48#

D47#

D46#

D45#

D44#

D43#

D42#

D41#

D40#

D39#

D38#

D37#

D36#

D35#

D34#

D33#

D32#

D31#

D30#

D29#

D28#

D27#

D26#

D25#

D24#

D23#

D22#

D21#

D20#

D19#

D18#

D17#

D16#

D15#

D14#

D13#

D12#

D11#

D10#

D9#

D8#

D7#

D6#

D5#

D4#

D3#

D2#

D1#

D0#

NOCONA 667

A35#

A34#

A33#

A32#

A31#

A30#

A29#

A28#

A27#

A26#

A25#

A24#

A23#

A22#

A21#

A20#

A19#

A18#

A17#

A16#

A15#

A14#

A13#

A12#

A11#

A10#

A9#

A8#

A7#

A6#

A5#

A4#

A3#

REQ4#

REQ3#

REQ2#

REQ1#

REQ0#

DBI3#

DBI2#

DBI1#

DBI0#

DP3#

DP2#

DP1#

DP0#

AP1#

AP0#

ADSTB1#

ADSTB0#

DSTBP3#

DSTBP2#

DSTBP1#

DSTBP0#

DSTBN3#

DSTBN2#

DSTBN1#

DSTBN0#

SB_HA#35

C8

SB_HA#34

C9

SB_HA#33

A7

SB_HA#32

A6

SB_HA#31

B7

SB_HA#30

C11

SB_HA#29

D12

SB_HA#28

E13

SB_HA#27

B8

SB_HA#26

A9

SB_HA#25

D13

SB_HA#24

E14

SB_HA#23

C12

SB_HA#22

B11

SB_HA#21

B10

SB_HA#20

A10

SB_HA#19

F15

SB_HA#18

D15

SB_HA#17

D16

SB_HA#16

C14

SB_HA#15

C15

SB_HA#14

A12

SB_HA#13

B13

SB_HA#12

B14

SB_HA#11

B16

SB_HA#10

A13

SB_HA#9

D17

SB_HA#8

C17

SB_HA#7

A19

SB_HA#6

C18

SB_HA#5

B18

SB_HA#4

A20

SB_HA#3

A22

SB_REQ#4

B22

SB_REQ#3

C20

SB_REQ#2

C21

SB_REQ#1

B21

SB_REQ#0

B19

SB_DBI#3

AB9

SB_DBI#2

AE12

SB_DBI#1

AD22

SB_DBI#0

AC27

SB_DP#3

AE17

SB_DP#2

AC15

SB_DP#1

AE19

SB_DP#0

AC18

SB_AP#1

D9

SB_AP#0

E10

SB_ADSTB#1

F14

SB_ADSTB#0

F17

SB_DSTBP#3

Y11

SB_DSTBP#2

Y14

SB_DSTBP#1

Y17

SB_DSTBP#0

Y20

SB_DSTBN#3

Y12

SB_DSTBN#2

Y15

SB_DSTBN#1

Y18

SB_DSTBN#0

Y21

Trace Width:12 Mils

VREF_P_VTT_CPU1_0

VREF_P_VTT_CPU1_3

VCCIOPLL_CPU1

AGND_CPU1

PU_VCCPLL_CPU1

SB_HA#[35..3] 9,19

SB_REQ#[4..0] 9,19

SB_DBI#[3..0] 9,19

SB_DP#[3..0] 9,19

SB_AP#[1..0] 9,19

SB_ADSTB#[1..0] 9,19

SB_DSTBP#[3..0] 9,19

SB_DSTBN#[3..0] 9,19

12

C1106

22U/1206/X/6.3V

P_VTT

12

SC193

22U/1206/X/6.3V

SC18

1U/6/X/10V

2

SC19

0.1U/6/X/16V

Title

Size Document Number Rev

Date: Sheet

GIGA-BYTE TECHNOLOGY CO., LTD.

NOCONA 667 MICS P1

GA-9ITDW-FJ

1

of

13 81Wednesday, October 13, 2004

1.3

R121

A A

754mV

49.9/1%

R124

84.5/1%

C18

1U/6/X/10V

PLACE 0 OHM RESISTOR ON BACK SIDE

SR163

0

5

C20

220P/6/X/50V

VREF_P_VTT_CPU1_3VREF_P_VTT_CPU1_3_R

C19

220P/6/X/50V

P1V5

R123

12

0/X

PLACE COMPONENTS: GROUP ASSOCIATE COMPONENTS

TOGETHER AND AS PHYISCALLY CLOSE TO ASSOCIATED PIN AS

POSSIBBLE M IN TRACE W IDTH >=10 - 12 MILS

4

TC2

+

470U/4V/7343/X

12

C14

4.7U/1206/X/10V/X

PU_VCCPLL_CPU1

C15

0.1U/6/X/16V/X

3

C16

0.1U/6/X/16V/X

5

4

3

2

1

P_VCCP1 P_VCCP1

H31

H29

H27

H25

H23

G30

G28

G26

G24

F31

F29

F22

F16

E30

E28

E26

E20

D31

D29

D24

D18

D14

C30

C28

C22

C16

B31

B29

B26

B20

A30

A28

A24

A18

A14

U2D

L30

L26

L24

L8

L6

L4

L2

K31

K29

K27

K25

K23

K9

K7

K5

K3

K1

J30

J28

J26

J24

J8

J6

J4

J2

H9

H7

H5

H3

H1

G8

G6

G4

G2

F4

F1

E6

E2

D8

D1

C4

C2

B6

A8

A2

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

NOCONA 800

NOCONA 667

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

L28

AA31

AA26

AA20

AA6

AA4

AA1

Y30

Y22

Y16

Y2

W31

W29

W27

W25

W1

V30

V28

V26

V24

V8

V6

V4

V2

U31

U29

U27

U25

U23

U9

U7

U5

U3

U1

T30

T28

T26

T24

T8

T6

T4

T2

R31

R29

R27

R25

R23

R9

R7

R5

R3

R1

P30

P28

P26

P24

P8

P6

P4

P2

N31

N29

N27

N25

N23

N9

N7

N5

N3

N1

M31

M29

M27

M25

M23

M9

M7

M5

M3

M1

P_VCCP1

P_VTT

AD12

AC10

AA12

AE24

AE18

AE14

AE8

AE3

AD30

AD26

AD20

AD6

AD2

AC31

AC22

AC16

AC4

AC3

AB30

AB24

AB18

AB14

AB8

AB2

U2E

NOCONA 800

VTT

VTT

VTT

Y10

VTT

F10

VTT

E12

VTT

C10

VTT

B12

VTT

B4

VTT

C5

VTT

A4

VTT

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

NOCONA 667

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

AE2

AD3

AE27

AE21

AE11

AD31

AD23

AD17

AD15

AD9

AC25

AC19

AC13

AC7

AC2

AB31

AB27

AB21

AB11

AB5

AB1

H30

H28

H26

H24

G31

G29

G27

G25

F30

F28

F25

F19

F13

E31

E29

E23

E17

E15

D30

D28

D27

D21

D11

C31

C29

C25

C19

C13

B30

B28

B23

B17

B15

A31

A29

A27

A21

A11

U2C

L31

GND

L29

L27

L25

L23

L9

L7

L5

L3

L1

K30

K28

K26

K24

K8

K6

K4

K2

J31

J29

J27

J25

J23

J9

J7

J5

J3

J1

H8

H6

H4

H2

G9

G5

G3

G1

F7

F2

E9

D5

D2

C7

B9

B2

A5

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

NOCONA 800

NOCONA 667

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

AA30

AA23

AA17

AA15

AA9

AA2

Y31

Y25

Y19

Y13

Y7

Y5

Y1

W30

W28

W26

W24

W4

W2

V31

V29

V27

V25

V23

V9

V7

V5

V3

V1

U30

U28

U26

U24

U8

U6

U4

U2

T31

T29

T27

T25

T23

T9

T7

T5

T3

T1

R30

R28

R26

R24

R8

R6

R4

R2

P31

P29

P27

P25

P23

P9

P7

P5

P3

P1

N30

N28

N26

N24

N8

N6

N4

N2

M2

M4

M6

M8

M24

M26

M28

M30

D D

C C

B B

A A

Title

Size Document Number Rev

5

4

3

2

Date: Sheet

GIGA-BYTE TECHNOLOGY CO., LTD.

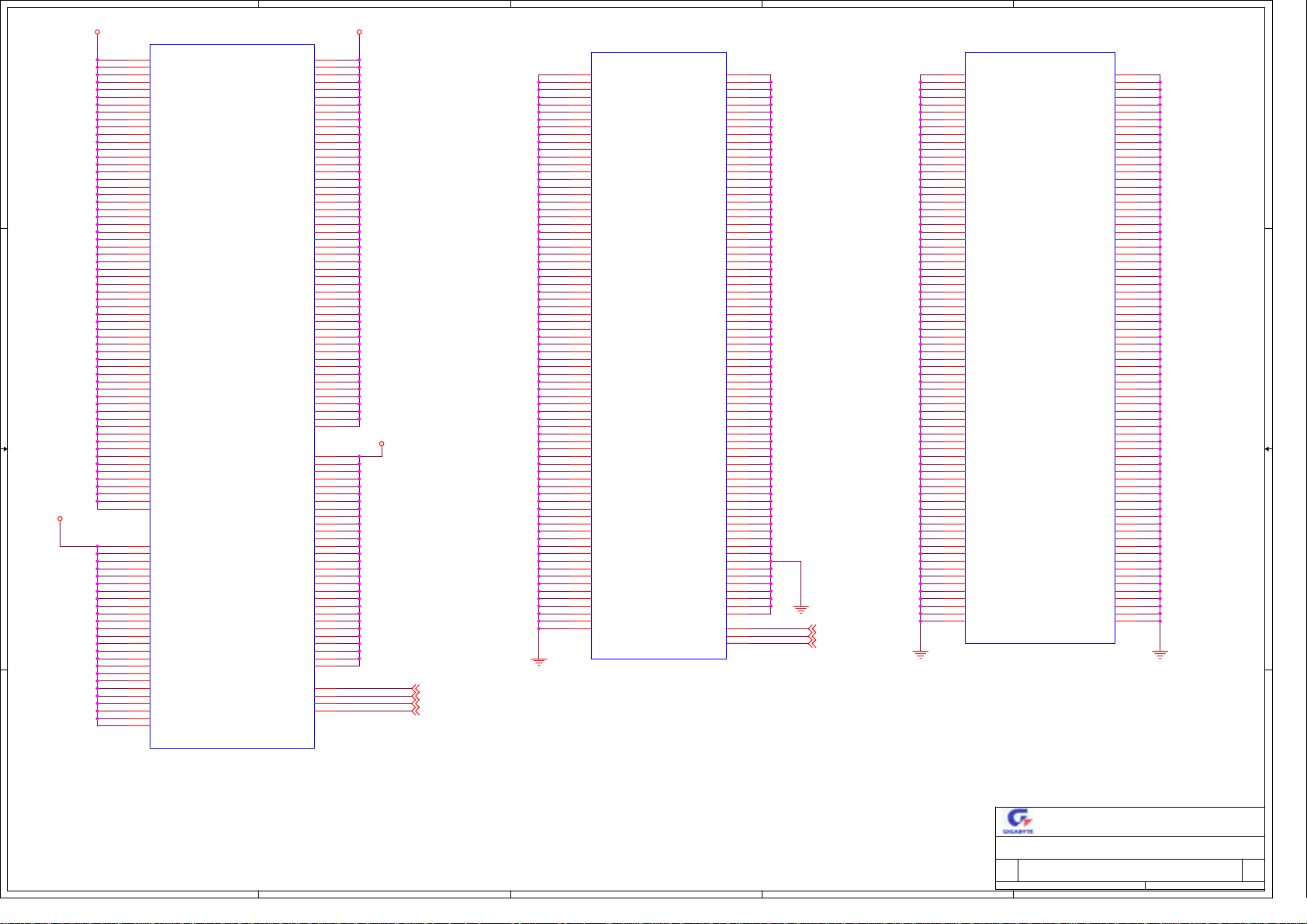

NOCONA 667 P1 PWR/GND

GA-9ITDW-FJ

1

of

14 81Wednesday, October 13, 2004

1.3

5

D D

SLP_S#449,51

P3V3_DUAL

4.7K

D

D

GS

NEAR CPU0

R125

0

R127

0

NEAR MCH

R129

0/X

R131

0/X

NEAR CPU1

R126

0

R128

0

NEAR PXH

R130

0/X

R132

0/X

SMC_CPU0_SKTOCC#

CPU0_THERMDC_H7

MCH_TDA_H7

MEM_TDA

MEM_TDC

CPU1_THERMDA_H7

CPU1_THERMDC_H7

PXH_TDA_H7

PXH_TDC_H7

CPU0_SKT_TDA

CPU0_SKT_TDC

SMC_CPU0_SKTOCC#9,11 SLP_S#349,51,58,63

C C

CPU0_THERMDA9 TD1P 73

MCH_TDA21

MCH_TDC21

B B

CPU1_THERMDA13 TD2P 73

CPU1_THERMDC13

PXH_TDA36

PXH_TDC36

A A

CPU0_THERMDA CPU0_THERMDA_H7

CPU0_THERMDC

MCH_TDA

MCH_TDC MCH_TDC_H7

Q9

B

C

E

MMBT2222A/X

MMBT2222A/X

CPU1_THERMDA

CPU1_THERMDC

PXH_TDA

PXH_TDC

Q10

B

C

E

5

SOT23

SOT23

G

S

R260

R261

R263

R264

R266

R267

4

R1184

SMC_CPU0_SKTOCC

Q115

2N7002

0

0

0/X

0/X

0/X

0/X

R269

R270

R272

R273

R275

R276

0

0

0/X

0/X

0/X

0/X

TD1P

C21

100P/6/N/50V

TD1N

PLACE CLOSE TOGETHER AND NEAR LM93

PLACE CLOSE TOGETHER AND NEAR LM93

TD2P

C22

100P/6/N/50V

TD2N

4

P3V3_DUAL

53

1

2

SN74LVC1G08

TD1N 73CPU0_THERMDC9

TD2N 73

3

Q113

2N7002

S

R1364

10K/1%

RT2

10K/8/1%/TR

R1182 0

t

D

D

GS

G

P5V_STBY

R1183

10K

CPU_S3_PS_ON#

Q114

U74

4

CPU0_SKTOCC_S3

VREF58

TEMPIN158

TEMPIN258

TEMPIN358

10RH1-001002-20

R1185

1K

R1366

10K/1%

RT1

t

10K/8/1%/TR

3

ECB

MMBT2222A

SOT23

t

2

P5V_STBY

R1181

4.7K

PS_ON#_R 49,63

1

SMC_CPU0_SKTOCC# SLP_S#3 SLP_S#4 PS_ON#

1

11 1

110

0

1

TOUT

VDD

TOUT

VDD

TOUT

VDD

TOUT

VDD

3

8

3

8

3

8

3

8

P3V3_DUAL

R1111

1K/X

UNDER

CPU

SOCKET

NEAR DDRII

SLOT

NEAR PCI

SLOT

NEAR SCSI

CONTROLLER

LM75_SMBALERT#

U66

SDA

SCL

A2

A1

A0 GND

LM75/3.3V/X

U67

SDA

SCL

A2

A1

A0 GND

LM75/3.3V/X

U68

SDA

SCL

A2

A1

A0 GND

LM75/3.3V/X

U69

SDA

SCL

A2

A1

A0 GND

LM75/3.3V/X

GIGA-BYTE TECHNOLOGY CO., LTD.

THERMAL SENSER

GA-9ITDW-FJ

1

LM93_SMBALERT#72,73

removable, duplicated.

LM75_SMBDAT72

LM75_SMBCLK72

R1365

10K/1%

RT3

10K/8/1%/TR

0

0

00

R1110

P3V3_DUAL

R1109

R1108

1K/X

1K/X

2

R1112 47/X

R1113

47/X

R1122

47/X

R1123

47/X

0/X

1

2

5

6

7 4

1

P3V3_DUAL

2

5

6

7 4

1

2

5

6

7 4

1

2

5

6

7 4

Title

Size Document Number Rev

Date: Sheet

0

1

1

1.3

of

15 81Wednesday, October 13, 2004

5

2

2

4

3

2

1

ITP1

CPU0_BPM#5

CPU0_BPM#4

CPU0_BPM#3

CPU0_BPM#2

D D

CPU_PWR_GD9,11,13,51

MCHPME#19,53

MCH_SMBDAT

,56,7

MCH_SMBCLK

,56,7

C C

B B

ITP_TCK121

ITP_TCK09,13

CPU_PWR_GD

MCHPME#

MCH_SMBDAT

MCH_SMBCLK MCH_SMBCLK_R

P_VTT

SR23 51

SR24 51

SR25 51

SR26 51

SR27 51

SR28 51

SR29 51

SR30 51

SR31 51

SR32 51

SR33 51

SR34 51

PLACE RESISTORS AT END OF NET

R160 51

R162 51

R136 0/X

R137 0/X

R138 0/X

R139 51

R140 51

PLACE RESISTORS AT END OF NET

CPU1_BPM#5

CPU1_BPM#4

CPU1_BPM#3

CPU1_BPM#2

CPU1_BPM#1

CPU1_BPM#0

CPU0_BPM#5

CPU0_BPM#4

CPU0_BPM#3

CPU0_BPM#2

CPU0_BPM#1

CPU0_BPM#0

P_VTT

ITP_TMS_MCH

ITP_TMS_MAIN

TP34

TP35

CPU0_BPM#1

CPU0_BPM#0

CPU1_BPM#5

CPU1_BPM#4

CPU1_BPM#3

CPU1_BPM#2

CPU1_BPM#1

CPU1_BPM#0

ITP_CPU_PWRGOOD

ITP_TP_41

ITP_TP_47

MCH_SMBDAT_R

ITP_TCK1

ITP_TCK0

CPU1_BPM#[5..0] 13

CPU0_BPM#[5..0] 9

ITP_TMS_MCH 21

ITP_TMS_MAIN 9,13

1

3

5

7

9

11

13

15

17

19

21

23

25

27

29

31

33

35

37

39

41

43

45

47

49

51

53

55

57

59

ITP CONN/X

P1V5

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

54

56

58

60

ITP_TP_4

ITP_MCH_DEBUG0

ITP_TP_10

ITP_MCH_DEBUG1

ITP_MCH_DEBUG2

ITP_MCH_DEBUG3

ITP_TP_22

ITP_TP_24

ITP_MCH_DEBUG4

ITP_MCH_DEBUG5

ITP_MCH_DEBUG6

ITP_MCH_DEBUG7

ITP_BCLK

ITP_BCLK#

SB_CPURST#_R

DBR_RESET#

ITP_TDO_MAIN

ITP_TRST#

ITP_TDI_MAIN

ITP_TMS_MAIN

ITP_TMS_MAIN9,13 ITP_TMS_MCH 21