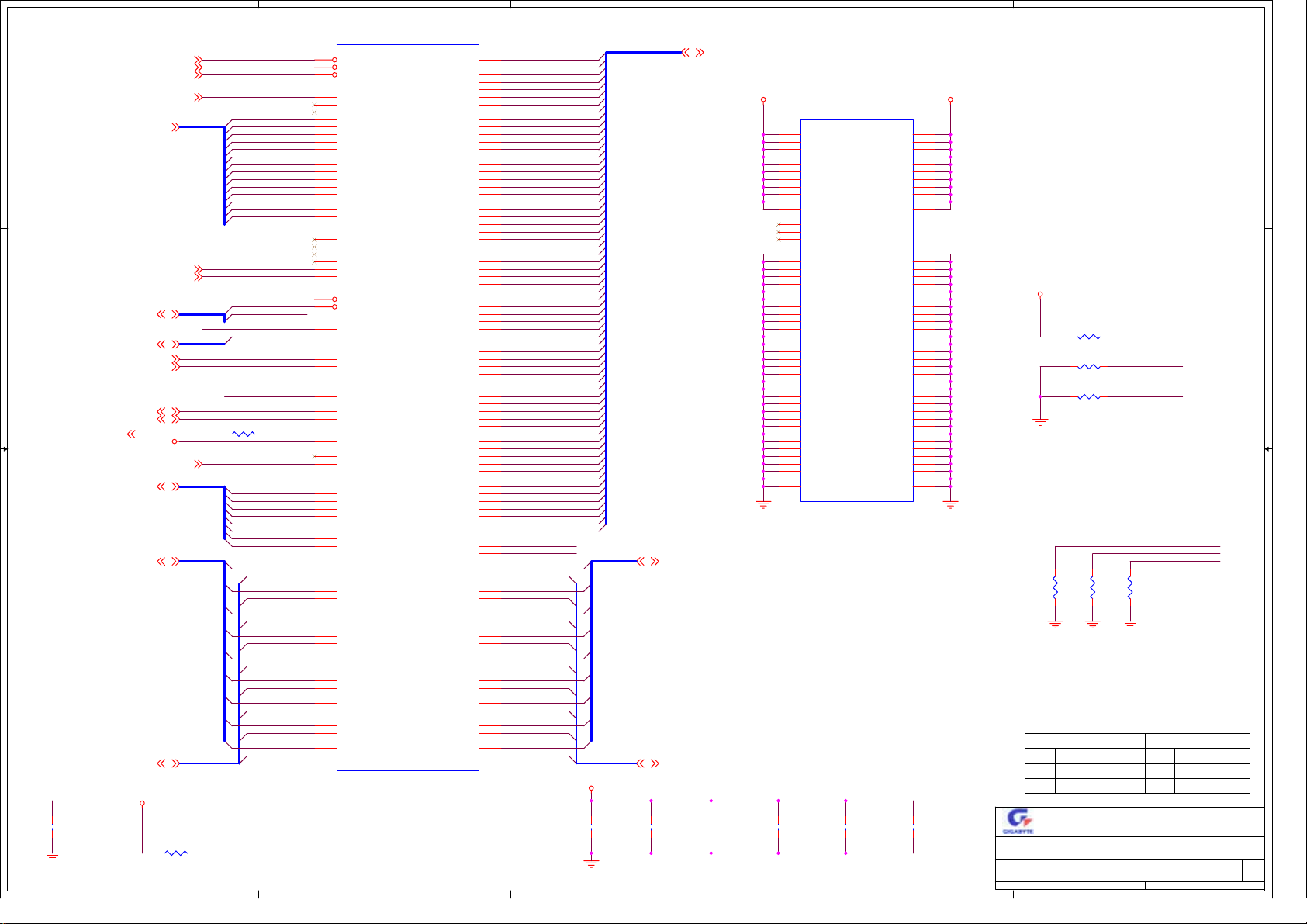

Gigabyte GA-9ILDTH REV1.1 Schematic

第 1 頁,共 1 頁Technical Information Release Notice

Technical Information Release Notice

Doc Type Schematic Date 2005/6/22 下午 01:44:57

Project Code S93048-0 Customer LC

Project Name GA-9ILDTH Revision Old N/A New 1.1

Model Name GA-9ILDTH IT Doc No DR056254

P/N RD Doc No

PCB Rev. 1.1 Check Sum

R N M

M/B GA-9ILDTH 1.1A

P/N Description

FINISHED GOOD LC

Description GA-9ILDTH-LC schamtic v1.1 release

Remark

Approved By daniel.hou 2005/6/22 下午 02:24:20 Applicant Victor.Tien

Research

Management

Mimosa.Kao

2005/6/22 下午

03:12:46

Validation Manager Project Manager

Effected Class

gfedc gfedcb gfedc

A B C D E F

gfedcb gfedc gfedc

A B

gfedc gfedcb

gfedc

gfedc gfedc

I

I

T

T

R

R

e

e

s

s

e

e

a

a

r

r

c

c

2

2

h

h

0

0

M

M

0

0

5

5

a

a

/

/

n

n

6

6

/

/

a

a

2

2

g

g

2

2

e

e

m

m

e

e

n

n

t

t

FinePrint - www.fineprint.com 用 列印 可在 訂購

2005/6/22http://10.1.1.15/ef2kweb/CHT/Forms/RTC009/RTC009_P.asp

Mimosa.Kao

5

4

3

2

1

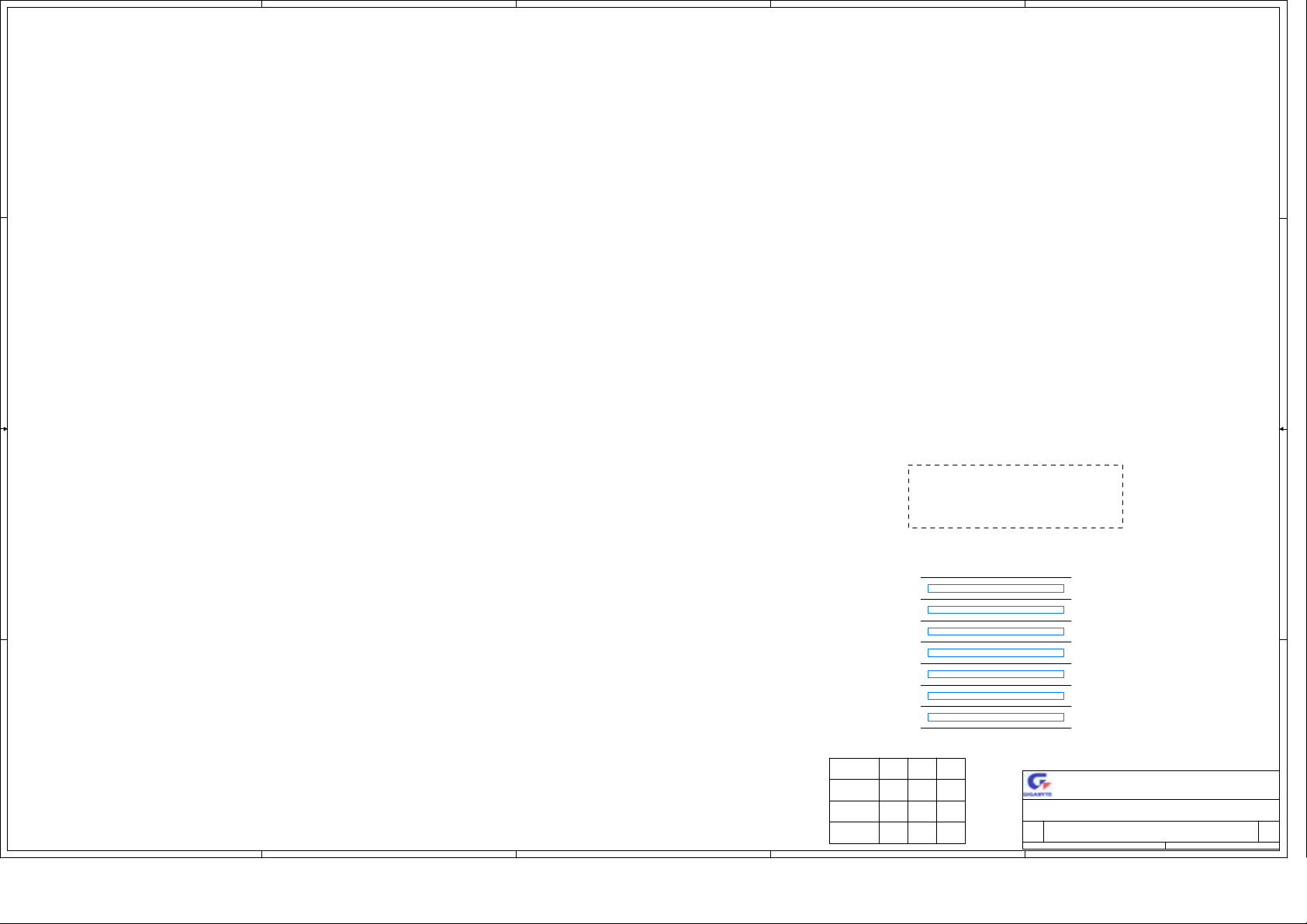

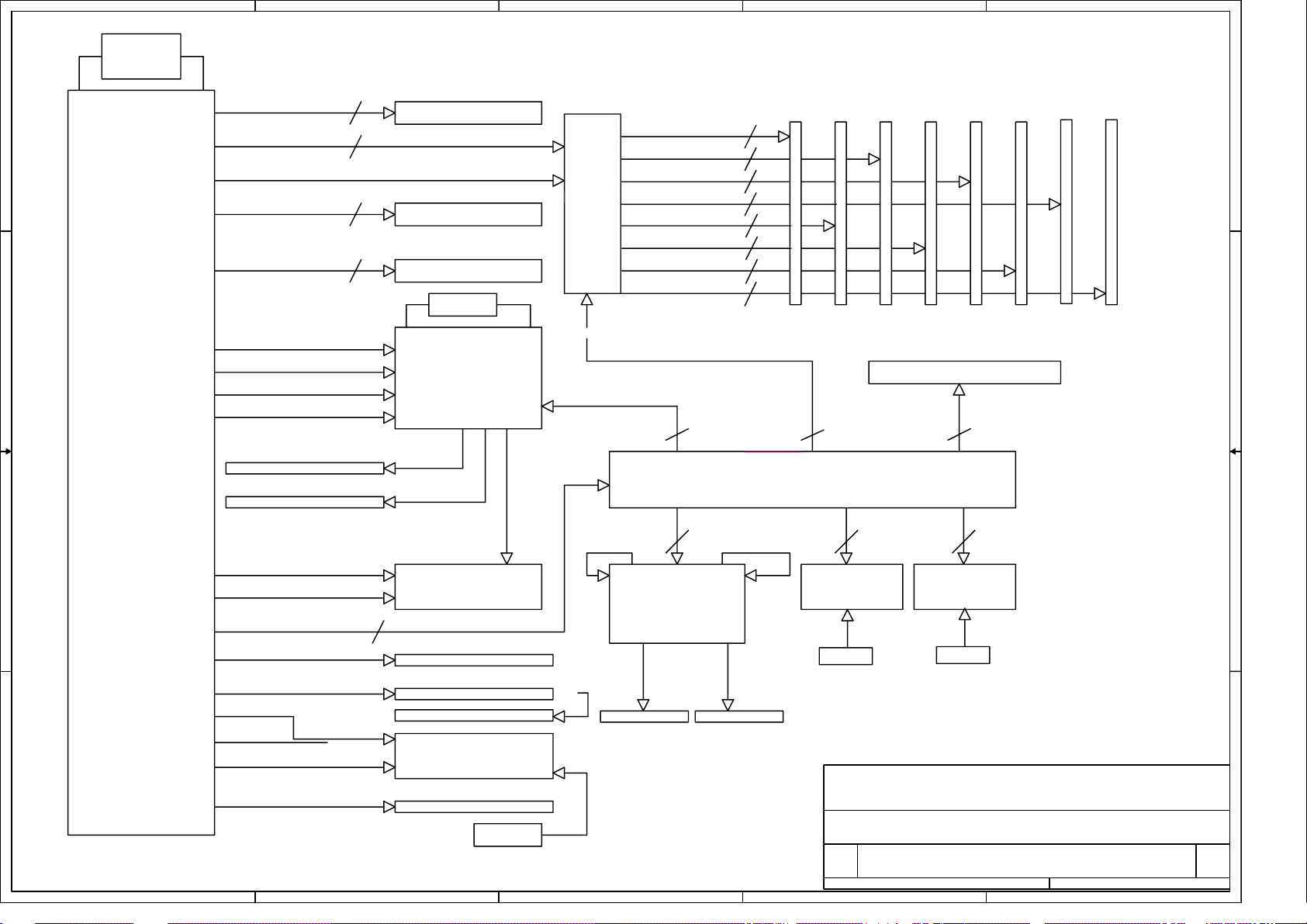

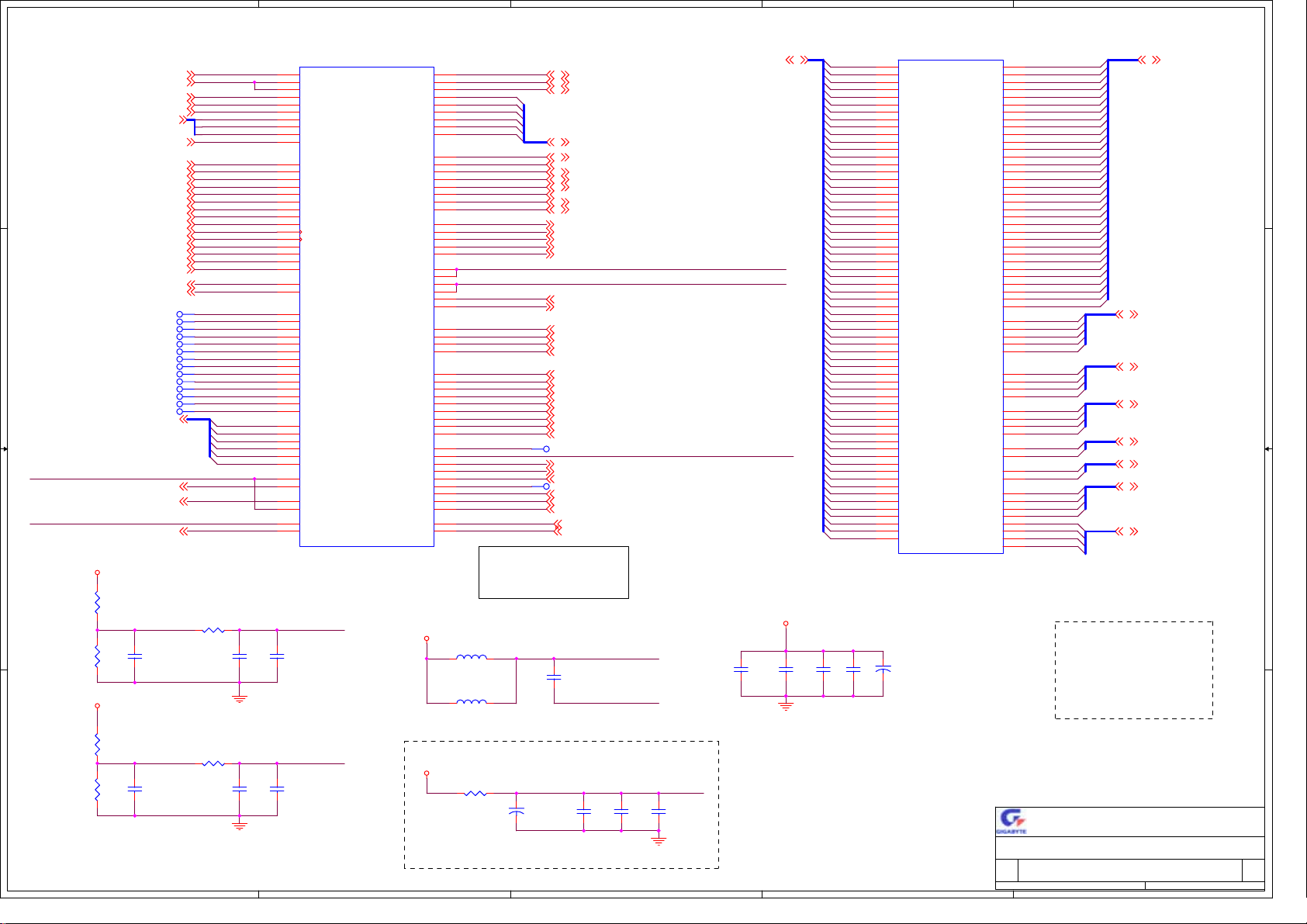

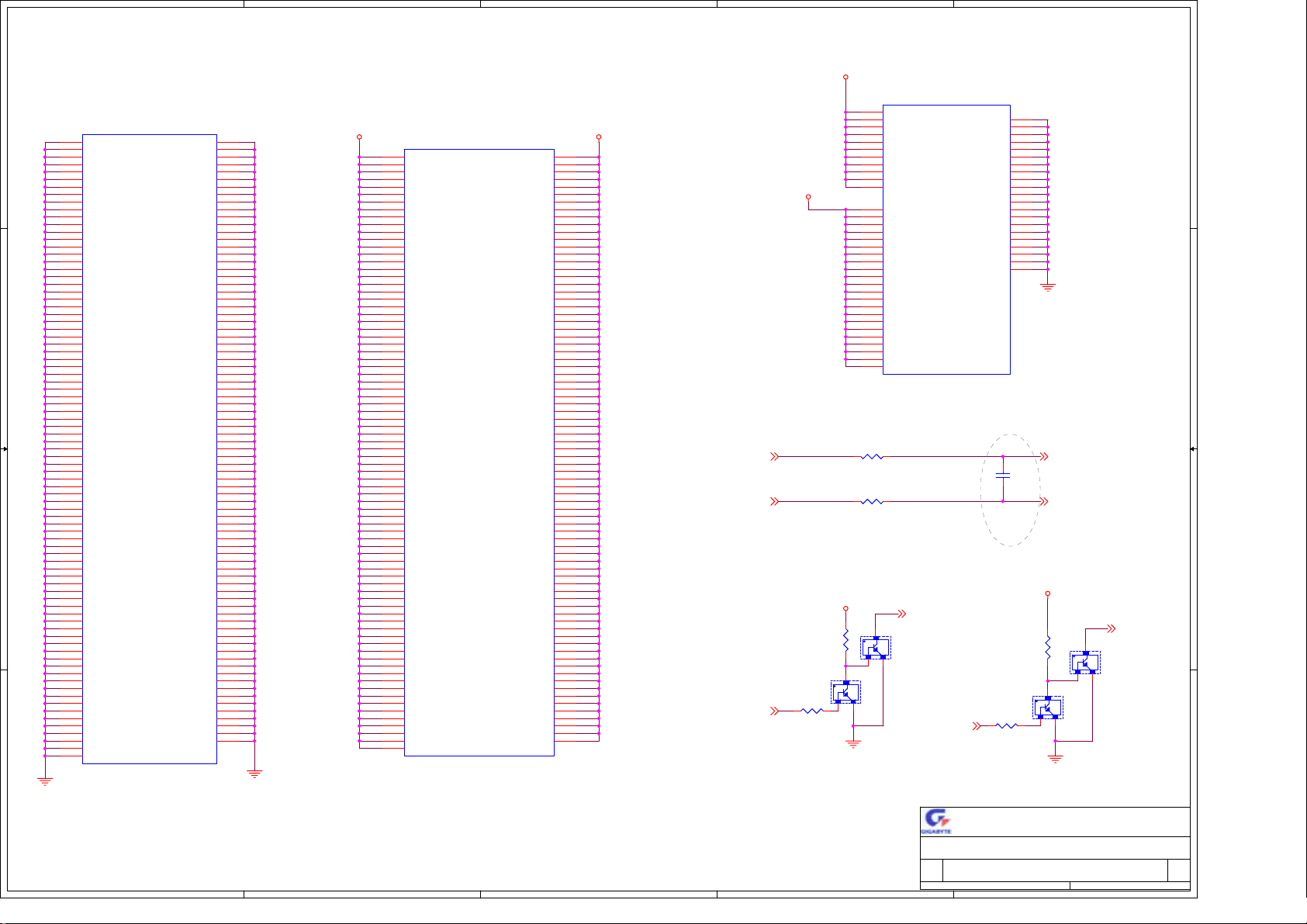

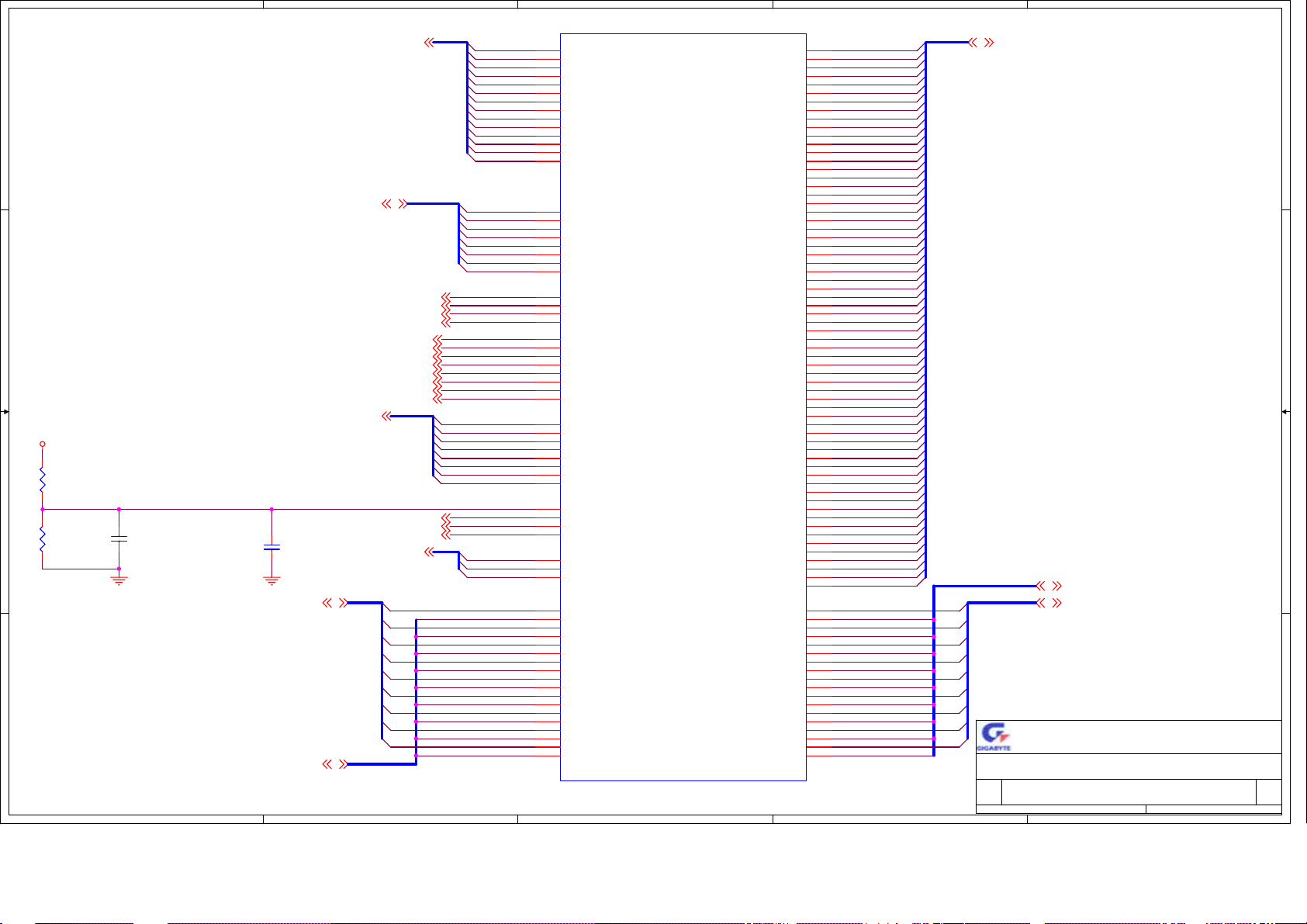

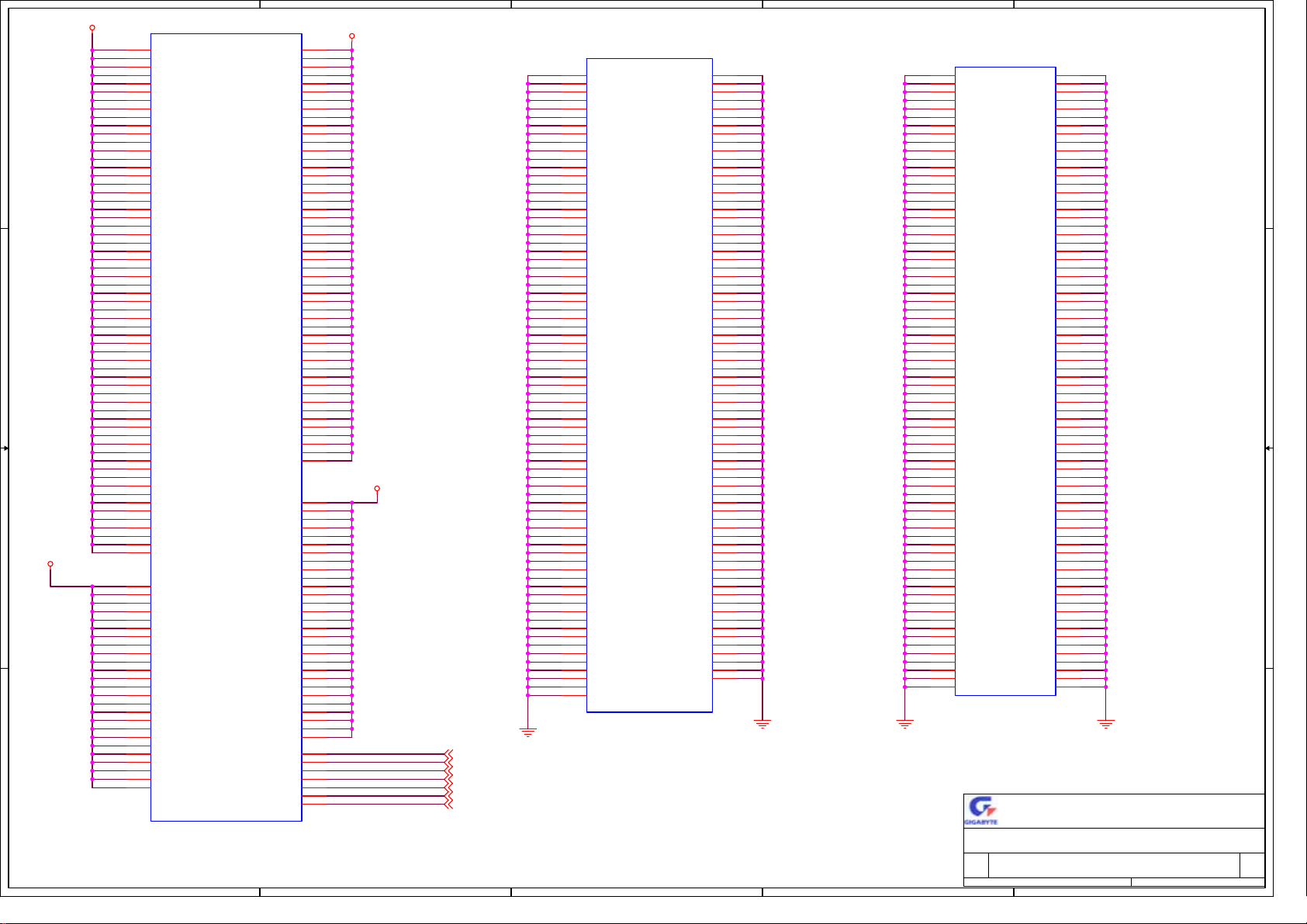

NOCONA800/LINDENHURST

D D

1 TITLE

2 SYS BLOCK

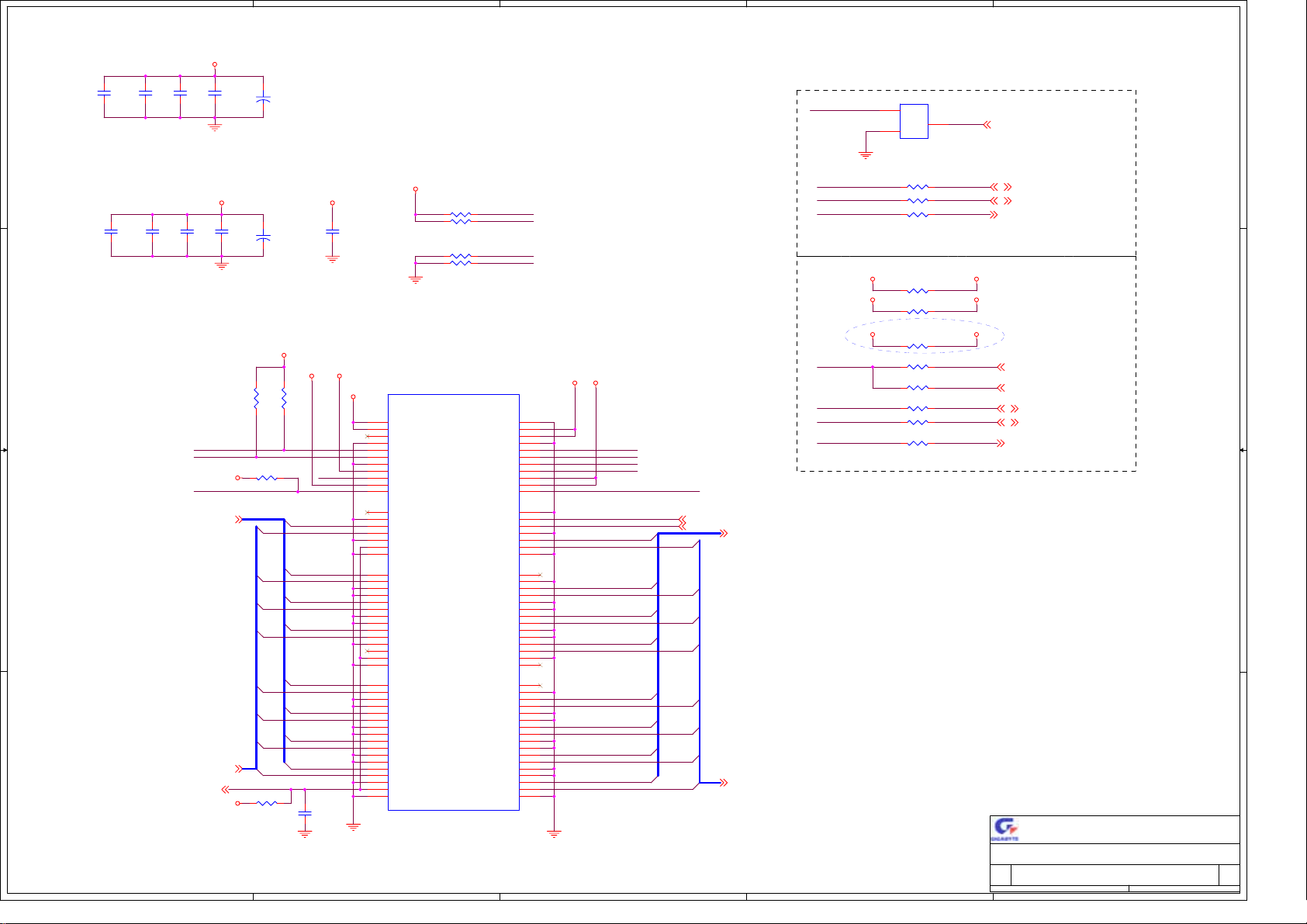

3 SYS RESET

4 CLOCK

5 SMBUS

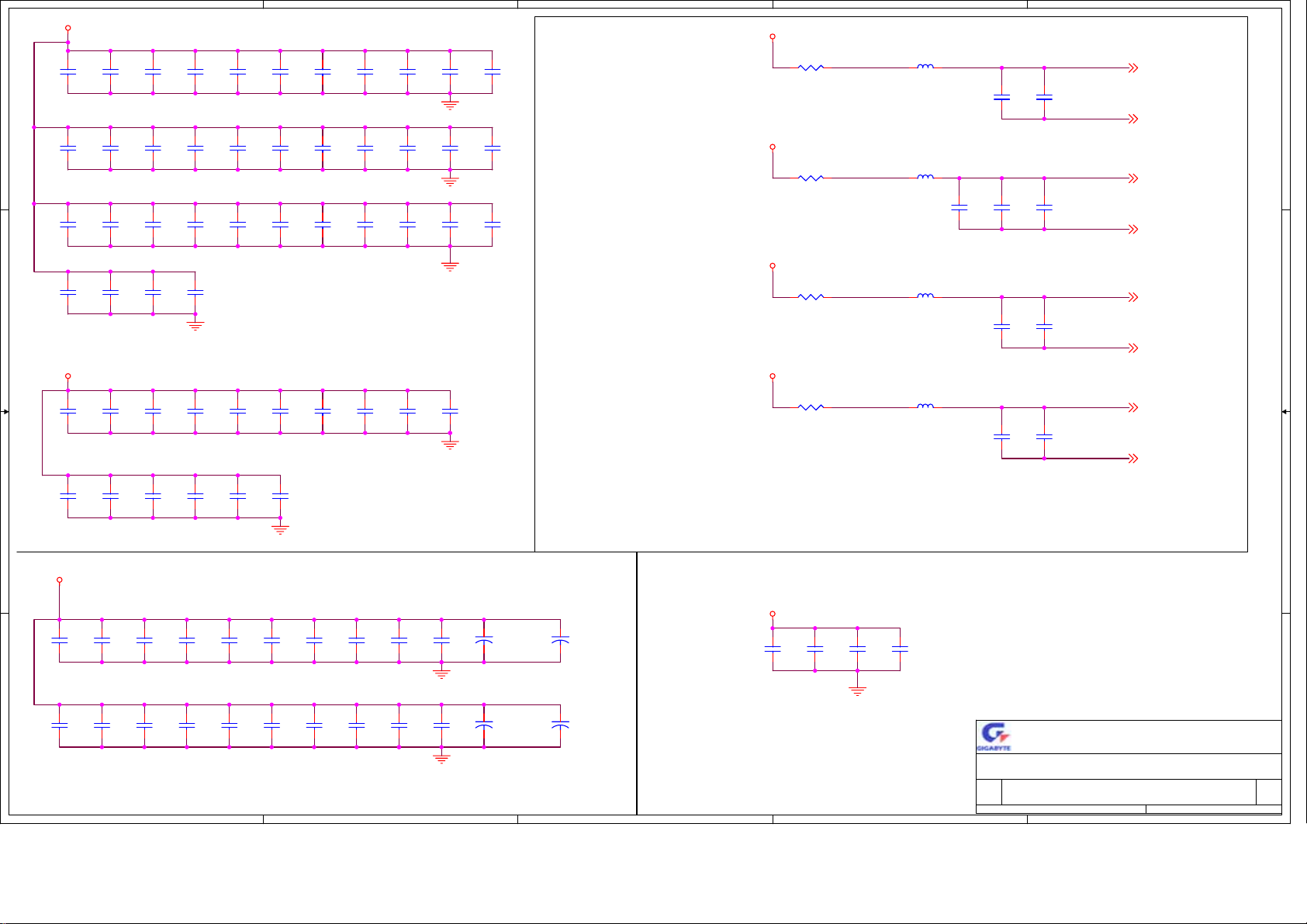

6 POWER DELIVERY

7 PCI / GPIO

8-10 P0 NOCONA

C C

11-12 P1 NOCONA

13 ITP

14 BSP_SEL/BREQ/LEVEL

15 MCH/DDRII CH A

16 MCH/DDRII CH B

17 MCH/HI1.5/MISC

18 MCH/SYSBUS

19 MCH/PCIEXPRESS

20 MCH/PWR/GND

21 DECOUPING

B B

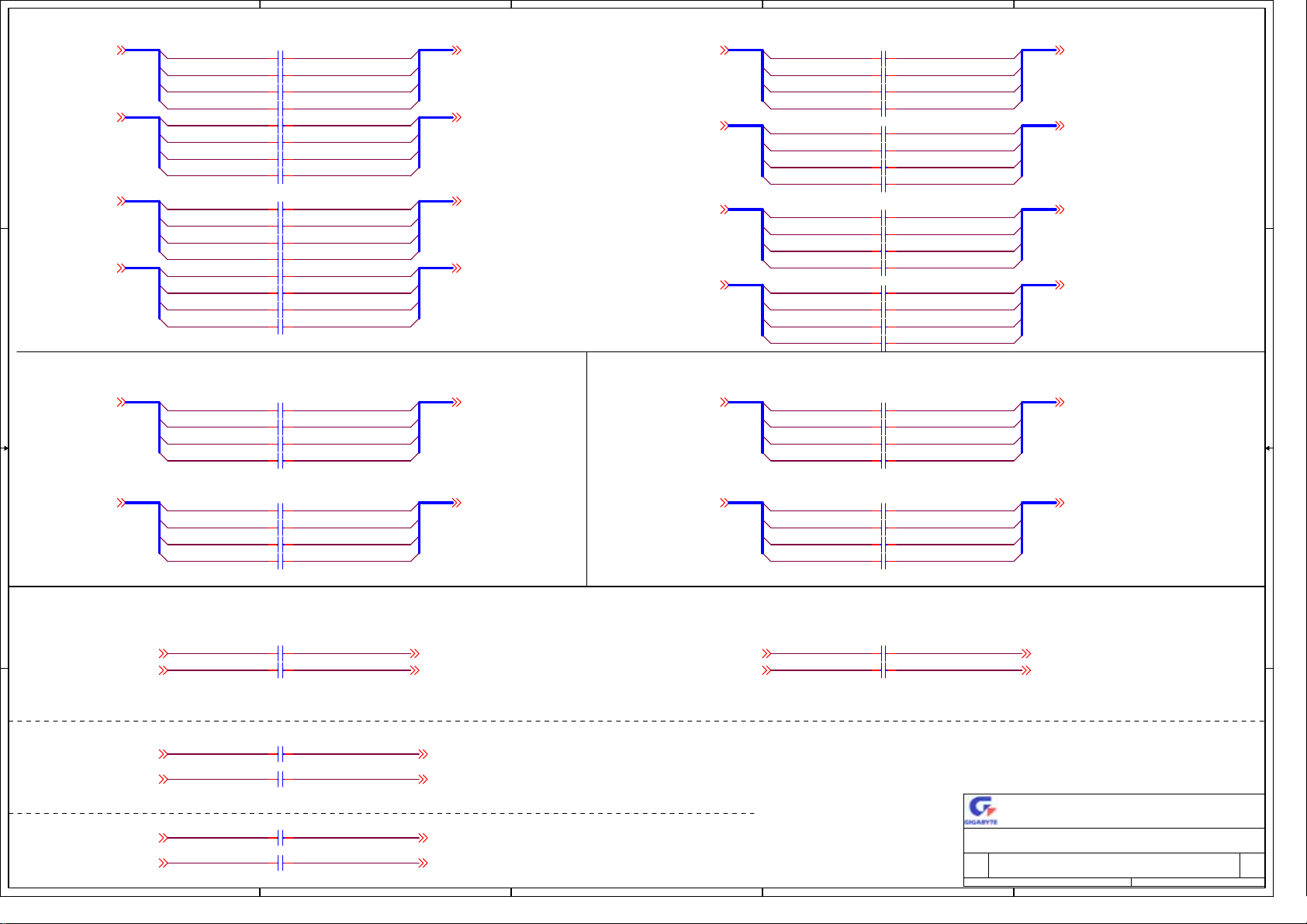

22 MCH PCIEXPRESS SERIES CAPS

23 PCI-E X8 (HOT-PLUG)

24-27 MCH/DDRII A DIMMX4

28-31 MCH/DDRII B DIMMX4

32 DDRII TERMINATION/DECOUPING

33-34 CK409B

35 DB800

36 H-R/IDE/PCI/USB/HI1.5

37 H-R/SATA/GPIO/LPC/RTC/HOST/PCI-X

38 H-R/PWR/GND

A A

39 H-R/USB/IDE CONN

40 PXH/PCI-E

41 PXH/PWR/GND

42 PXH/PCI-X CH A(133MHZ)

5

GA-9ILDTH

43 PXH/PCI-X CH B(133MHZ)

44 PCI-X SLOT 2 133MHZ

45 PCI-X SLOT 3 133MHZ

46 PCI-X SLOT 4 66MHZ

47 PCI-X SLOT 5 66MHZ/ZCR

48 PCI SLOT 6 33MHZ

49 PCI-E HOT-PLUG PWR CTRL

50 PCI-X HOT-PLUG PWR CTRL

51 HOT-PLUG ATTN.SW & LED

52-53 Broadcom BCM5721 GbE Lan

54 OVP

55-57 ATI VGA/CONN/SDRAM

58-61 AIC-7902 SCSI/ZCR

62 G-LOGIC/PSON/VIDGOOD

63 SIO-IT8712/FWH

64 PS2/COM/PRT/FLOPPY

65 POWER CONN

66 1.2 VTT R/ PCI VIO

67 1.5V

68 1.8V

69 P0 VR

70 P1 VR

71 FAN CONTROL

72 MB HOLE/FAN/LAN LED

73 SMBUS

74 FP/RIN/WOL/MRN

75 ID/RST/SPKR/HDLED

76 LM93/LM75/83791

77 IPMI

78-79 BLANK

80 CHANGE LIST

81 COUPON AND IMPEDANCE LIST

4

3

PCB VENDOR LIST

HTC/GBT : CADAC/TEAN/ALLED CIRCUIT

BOARD STACK-UP

3.70 mil

PP 2113

4.0 mil

11.1 mil

10.0 mil

11.1 mil

4.0 mil

3.70 mil

CORE

PP 2116+7628

CORE

PP 2116+7628

CORE

PP 2113

GA-9ILDTH FEATURE

MODEL

HOT-PLUG

FAN

CTRL

0

X

0

-CH-LC

X

XIPMI

0

2

COMPONENT SIDE

GND

INT 1

(PWR)

INT 2

SOLDER SIDE

Title

Size Document Number Rev

Date: Sheet

GIGA-BYTE TECHNOLOGY CO., LTD.

COVER SHEET

GA-9ILDTH

1

1.5 OZ

1OZ

1OZ

2 OZ

2 OZ(PWR)

1OZ

1OZGND

1.5 OZ

1.90 mil

1.30 mil

1.30 mil

2.70 mil

2.70 mil

1.30 mil

1.3 mil

1.9 mil

181Tuesday, June 21, 2005

of

1.1

5

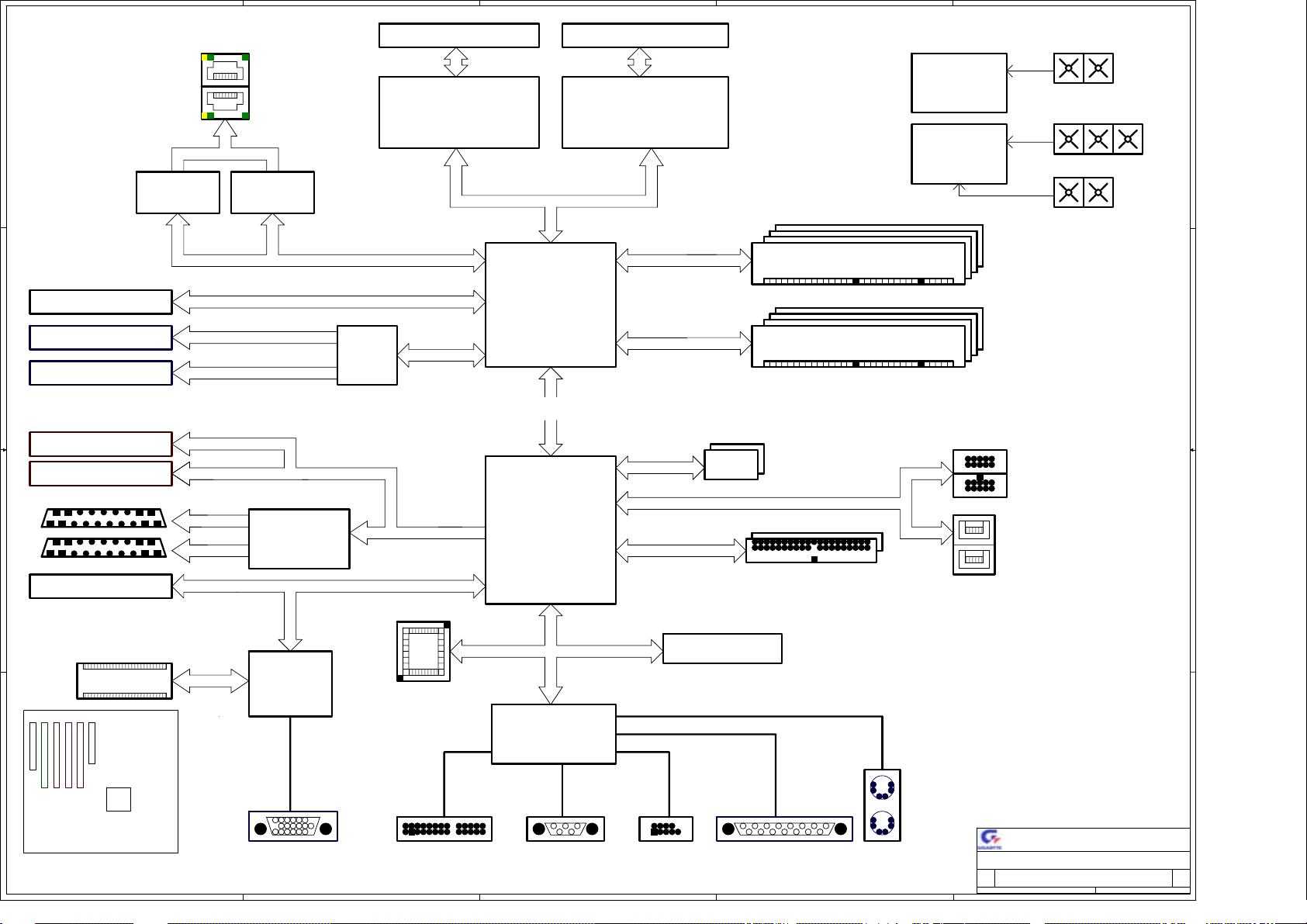

RJ45X2

DUAL-LAN

4

EVRD 10.1

3

EVRD 10.1

2

CPU0

FAN

1

CPU1

FAN

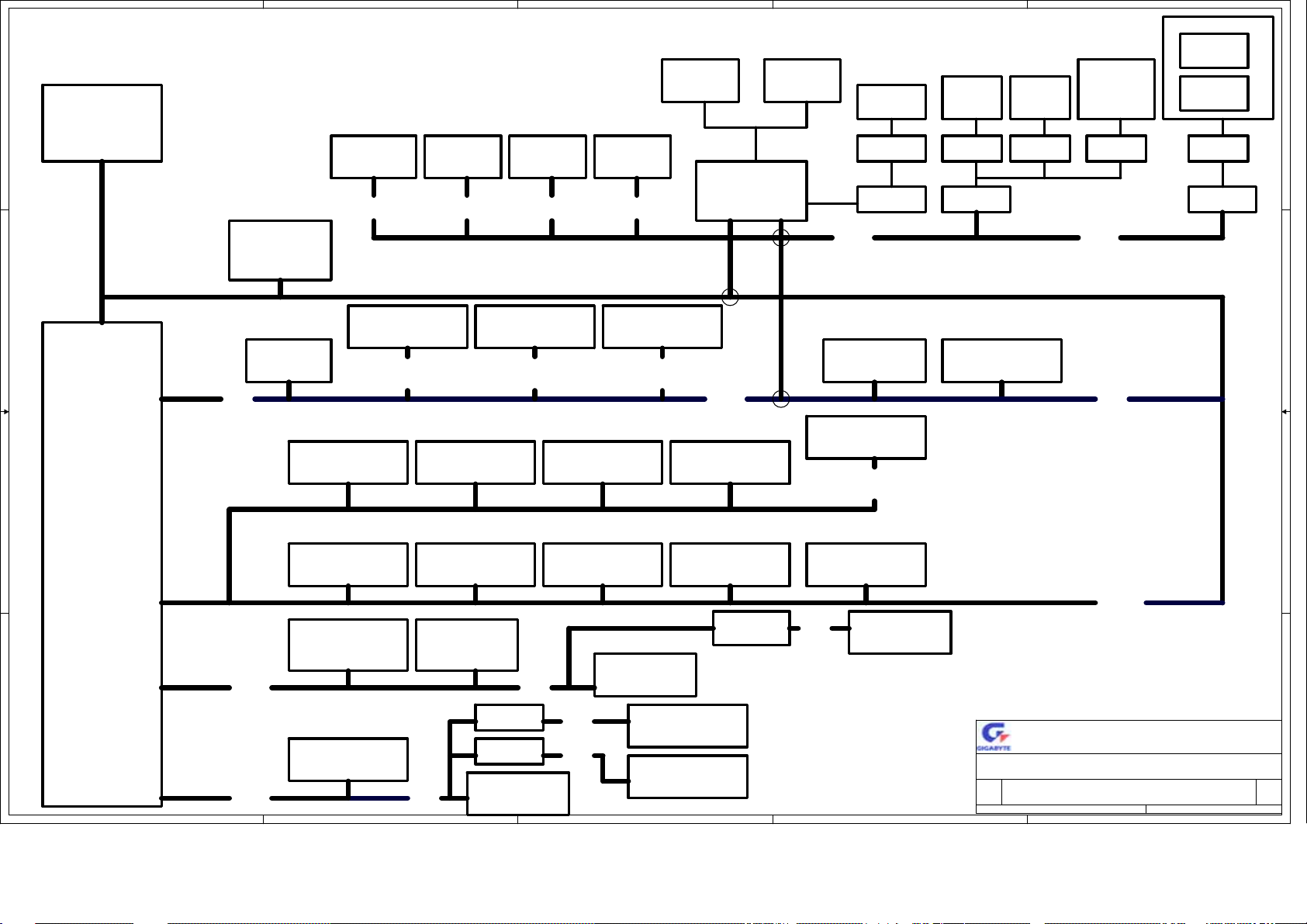

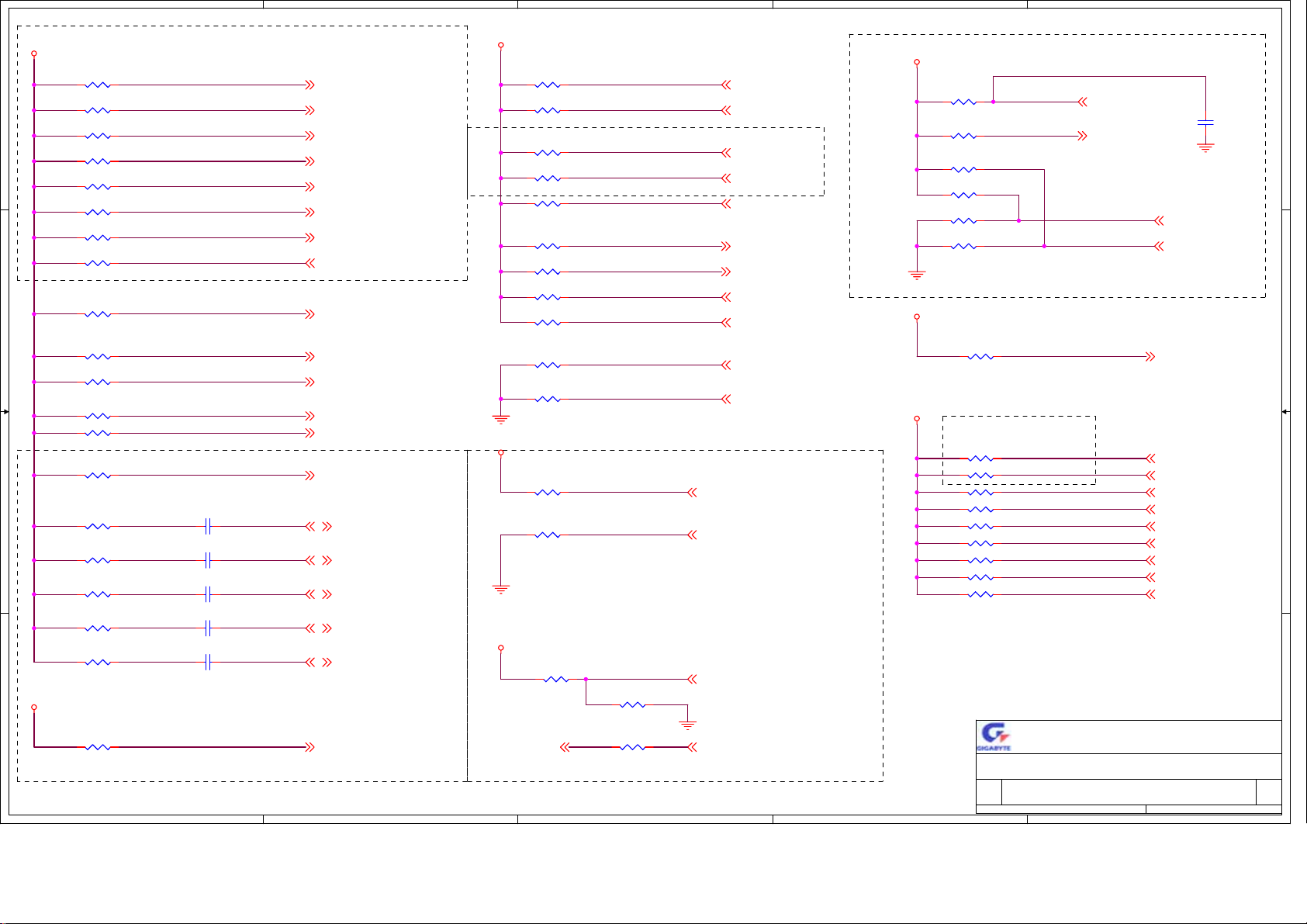

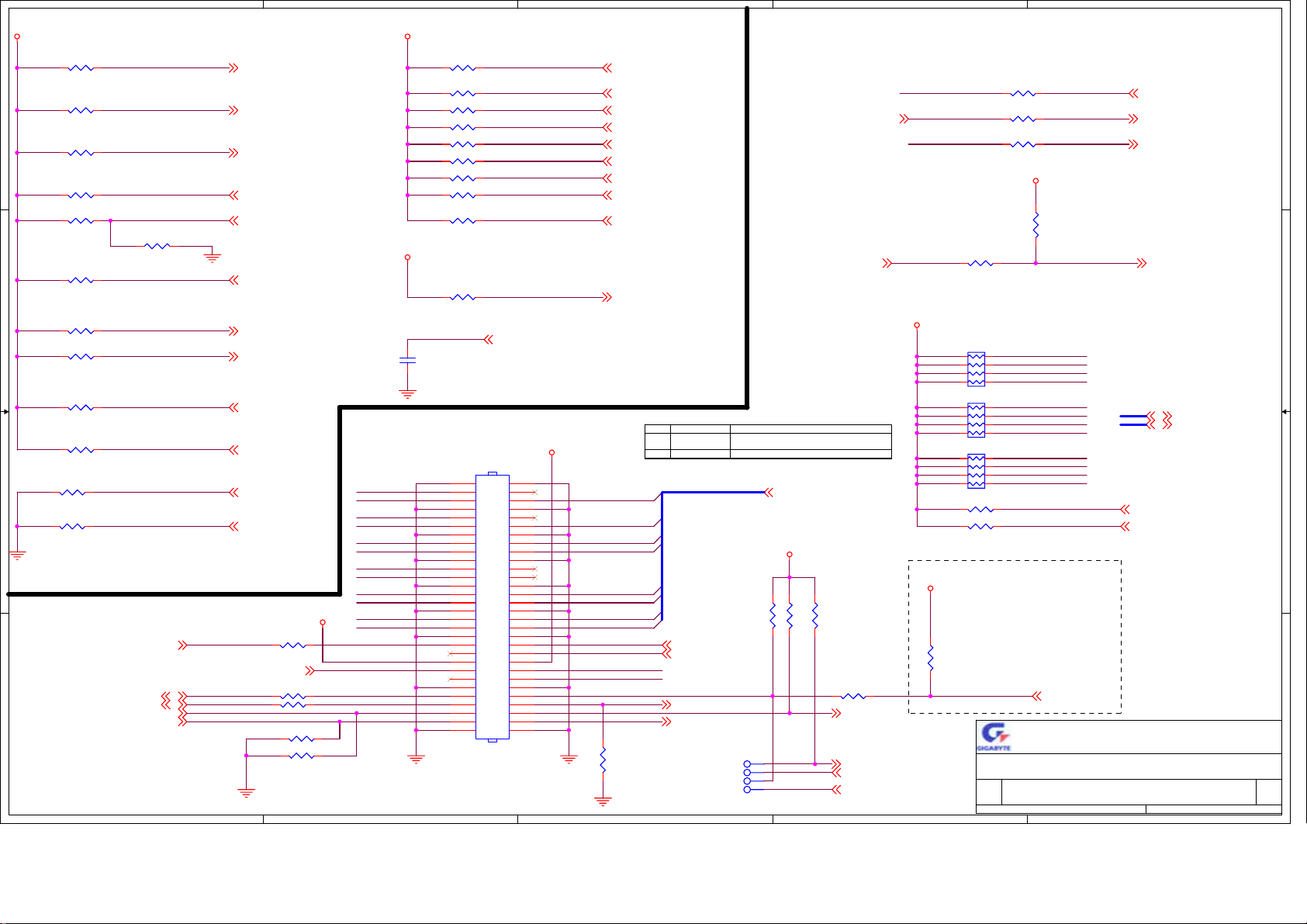

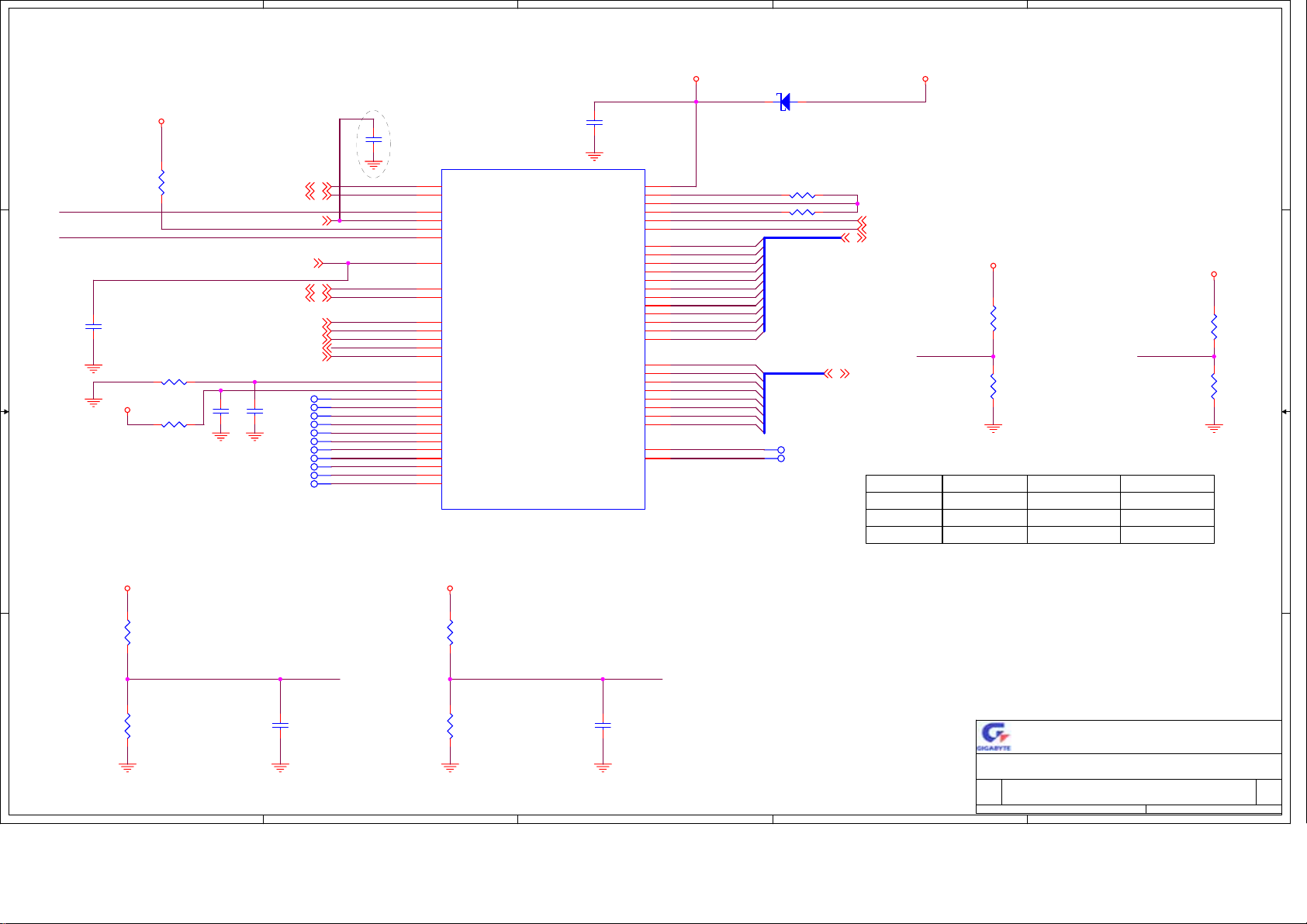

Intel

D D

NOCONA/Irwindale

Processor

CPU 0

Intel

NOCONA/Irwindale

Processor

CPU 1

LM93

H/M

SYS1

FAN

SYS2

FAN

SYS3

FAN

83791

H/M

Broadcom 5721 Broadcom 5721

GbE MAC/PHY GbE MAC/PHY

PCI EXPRESS X1 ( 2GB/S)

PCI-E X8 (SLOT1)

PCI-X 133MHZ (SLOT2)

C C

PCI-X 133MHZ (SLOT3)

PCI-X 66MHZ (SLOT4)

PCI-X 66MHZ[ZCR](SLOT5)

SCSI 68Pin

SCSI 68Pin

B B

PCI 33MHZ (SLOT6)

HOT-PLUG

HOT-PLUG

HOT-PLUG

SCSI CHA

SCSI CHB

PCI EXPRESS X8 ( 16GB/S)

PCI-X (133MT/S)

PXH

PCI-X (133MT/S)

Dual U320

SCSI

(AIC

7902W)

PCI 32 Bit BUS 133MB/s

PCI EXPRESS X8

( 16GB/S)

PCI-X (66MT/S)

6.4GB/s

System Bus(800MT/S)

Intel

Lindenhurst

HUB INTERFACE 1.5

266MB/s

Hance

Rapids

2.1GB/s up to 2.7GB/s

2.1GB/s up to 2.7GB/s

150MB/s

USB

IDE BusATA-100

SATAx2

Channel A

DDRII-400 DIMM Module X4

Channel B

DDRII-400 DIMM Module X4

IDE Connector * 2

1U

COOL

FAN

Front Side

USB 2.0x2

Back Panel USB

2.0X2

PWR4

FAN

IPMI

GSMI

8MB

SDRAM

ATI Rage XL

VGA

Intel

FWH

LPC

Interface

LPC

IT8712F

LPC Super I/O

PCI

PCI-X 66M

A A

PCI-X 66M

PCI-X 133M

PCI-EX X8

PCI-X 133M

MCH

VGA Connector

5

Floppy Connector

4

128 PQFP

COM1

COM2 KB & MS

3

Printer Port

2

GIGA-BYTE TECHNOLOGY CO., LTD.

Title

Size Document Number Rev

Date: Sheet

BLOCK DIAGRAM

GA-9ILDTH

1

281Tuesday, June 21, 2005

of

1.1

5

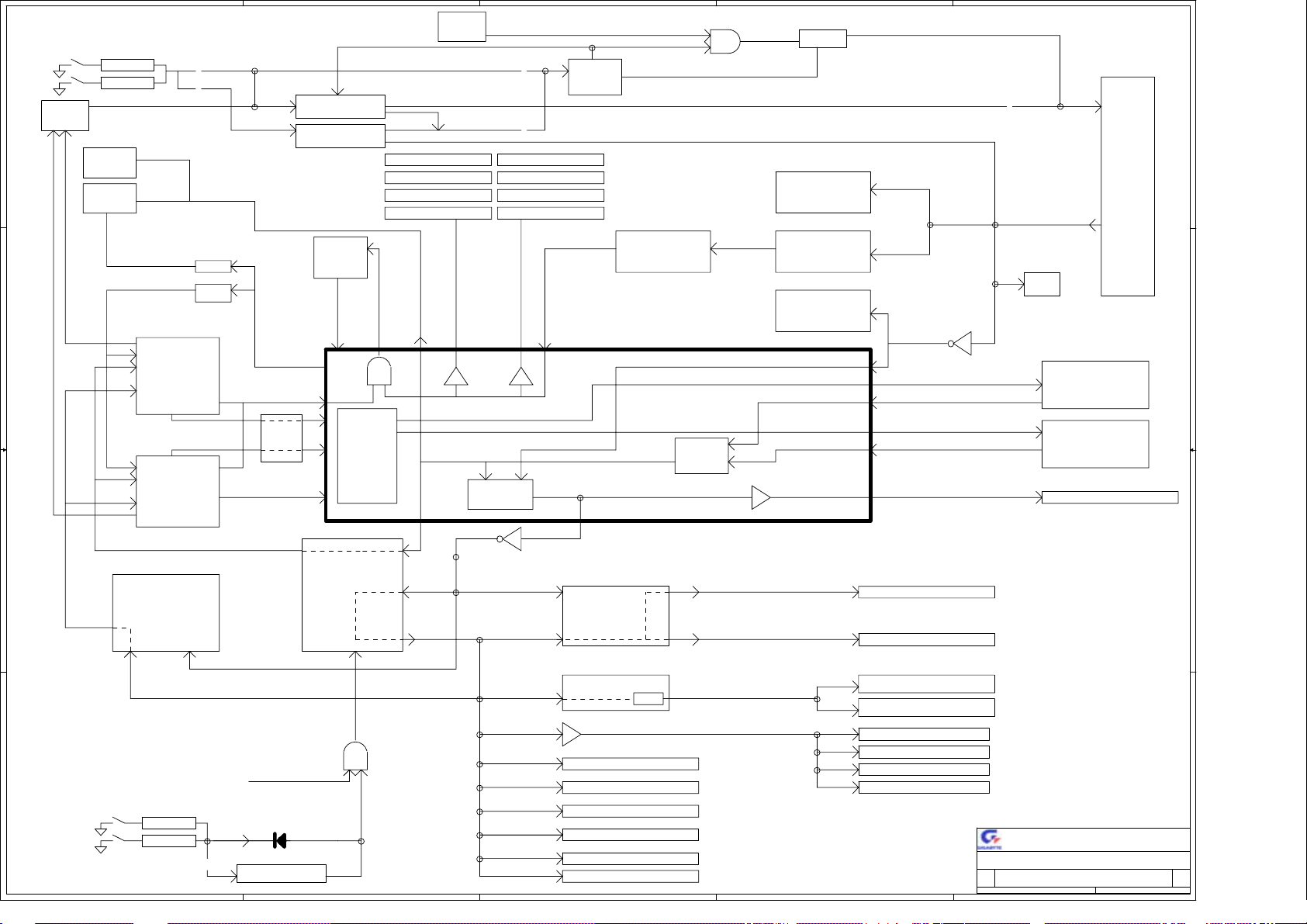

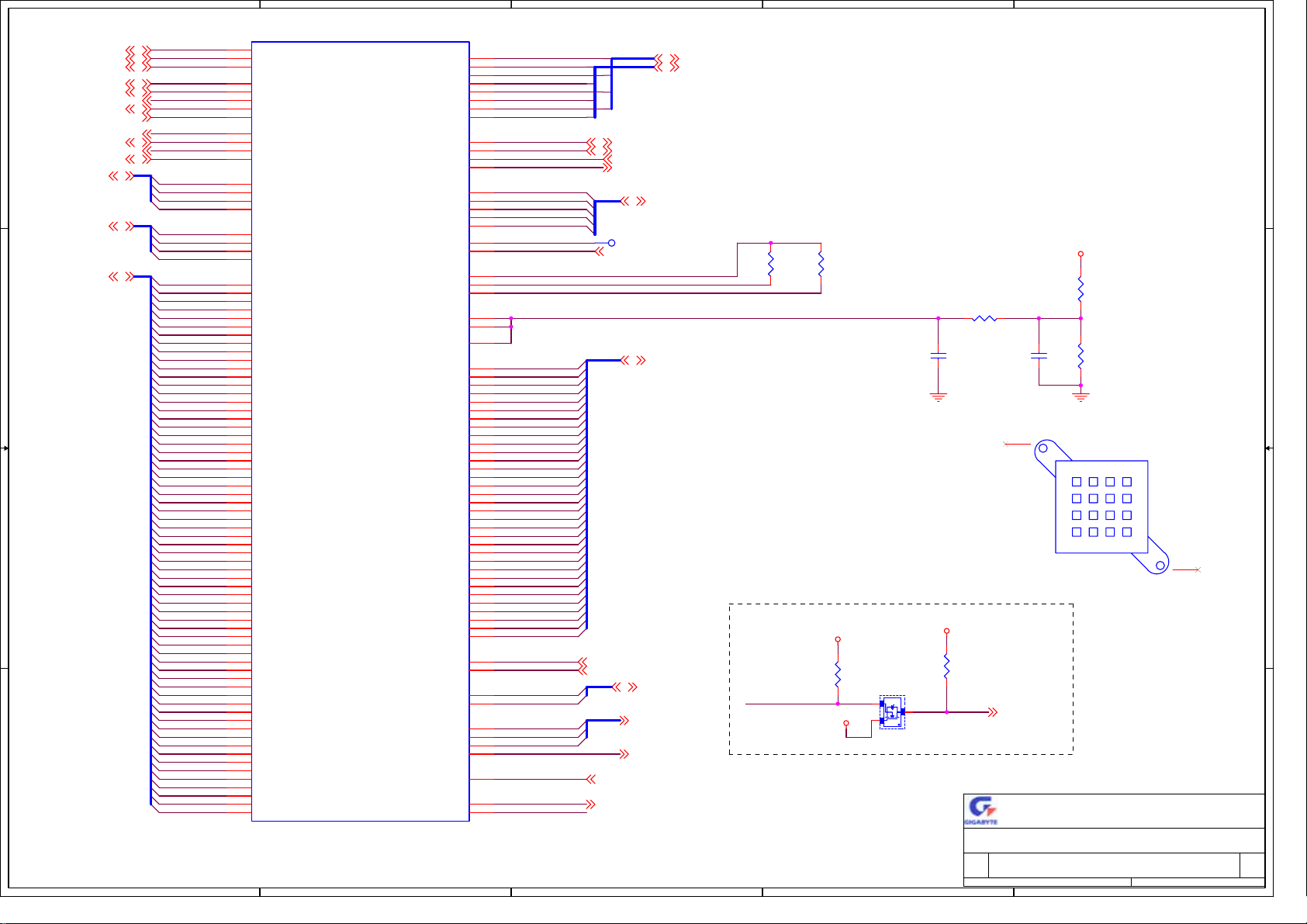

SYS RESET & PWR SET

BTN

LEVEL

D D

LOGIC

FP

FFC3

DB800

CK409B

CK409B_PWR_GD#

VID_PWRGD

C C

B B

PWB+

PWRDWN#

PWRDWN#

CPU0_THRMTRIP#

VIP_PWRGD

CPU_PWR_GD

CPU_RST#

CPU0_BSEL[0/1]

CPU1_BSEL[0/1]

VIP_PWRGD

CPU_PWR_GD

CPU_RST#

CPU1_THRMTRIP#

R

R

CPU_VRD_PWR_GD

FET

VTT

LEVEL

P0

VTTEN

VTTEN

P1

LINDENHUST

CPU_RST#

A A

BTN

PCI_RST#

5

MCH

FP

FFC3

PWROK

RST_SW

R

PWRBTN

IPMI_PWRBT_IN

SB_VTT_PWRGD

VTTEN

P3V3

LEVEL

P1_SKT0CC#

CPU_PWR_GD

PS_PWR_GD

40 35

IPMI CONN

75

37

IPMI CONN

71

SIO

1.2V

ISL6520

VTT_PWRGD

BSEL

COMPARE

LOGIC

H-R

SYS RST#

IPMI_RST_OUT#RST_IPMI#

4

75--72--71--76

76

72

36

PWRBTN

HR_PWRBNIN#

P0_SKT0CC#

R

R

CPU 0

7

H-R

3

SLP_S#3

LOGIC

SLP_S#4

DDRII DIMM DDRII DIMM

DDRII DIMM

AB

DDRII DIMM

DDRII DIMM

CPU_VRD_PWR_GD

DDRA_PCIRST#

VTT_ENABLE

DDRII DIMM

DDRII DIMM

DDRII DIMM

PWRGD_1_8V

DDRB_PCIRST#

1.8V

HIP6302CB

PLD

PWRGD_1_5V

5VSB

HUF76107

1.5V

ISL6525

P3V3 AUX

APL1084

LOGIC

100ms

CPU_VRD_PWR_GD

PWROK

SYS_PWR_GD_3_3V

SYS_PWR_GD#

PWROK

PXH_HAPRST#

PXH

PCI_RST#

4

PCI_RST#

PLD

BUFF

PCI_RST_BUFF1#

ATI VGA

AIC-7902

IPMI CONN

PCI- 66 CONN

PCI- 66 CONN

PCI- 32 CONN

3

PXH_HBPRST#

IDE_RSTDRV#

2

CPU1_VRD_PWR_GD

SYS_PWR_GD_BUFF

PCI-X 133 CONN

PCI-X 133 CONN

PCI-E X8 SLOT1

2

PS_PWR_GD#

IDE CONN

IDE CONN

SIO

SE-LINK

FWH

1

R

VR0_SYS_ENABLE

VR1_SYS_ENABLE

PS_ON#

PS_PWR_GD

VGA_HV

P0 VCORE

ATX CONN

ISL6556BCPU0_VRD_PWR_GD

P1 VCORE

ISL6556B

PCI-E X8 SLOT1

GIGA-BYTE TECHNOLOGY CO., LTD.

Title

Size Document Number Rev

Date: Sheet

SYS RESET

GA-9ILDTH

1

381Tuesday, June 21, 2005

1.1

of

5

4

3

2

1

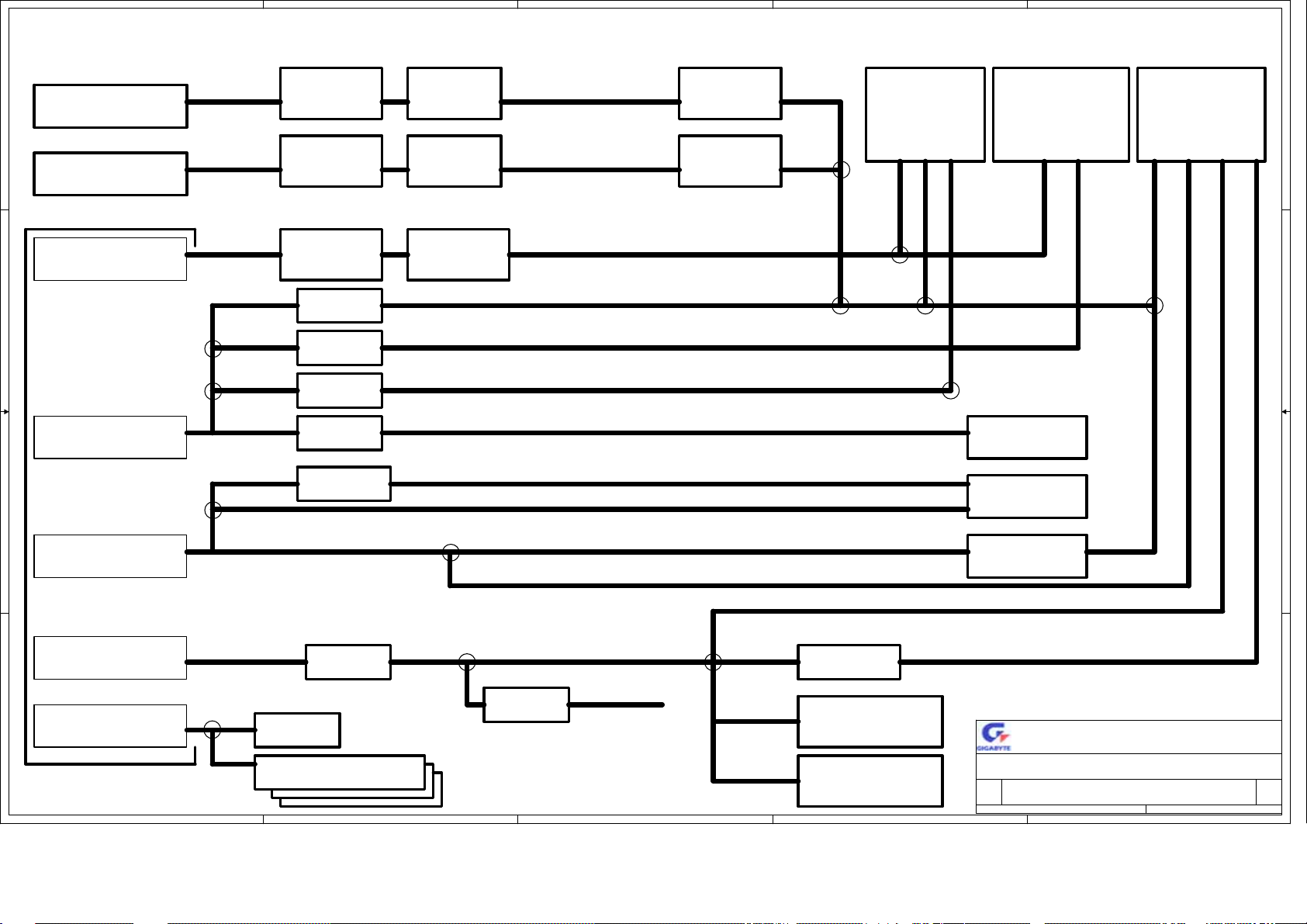

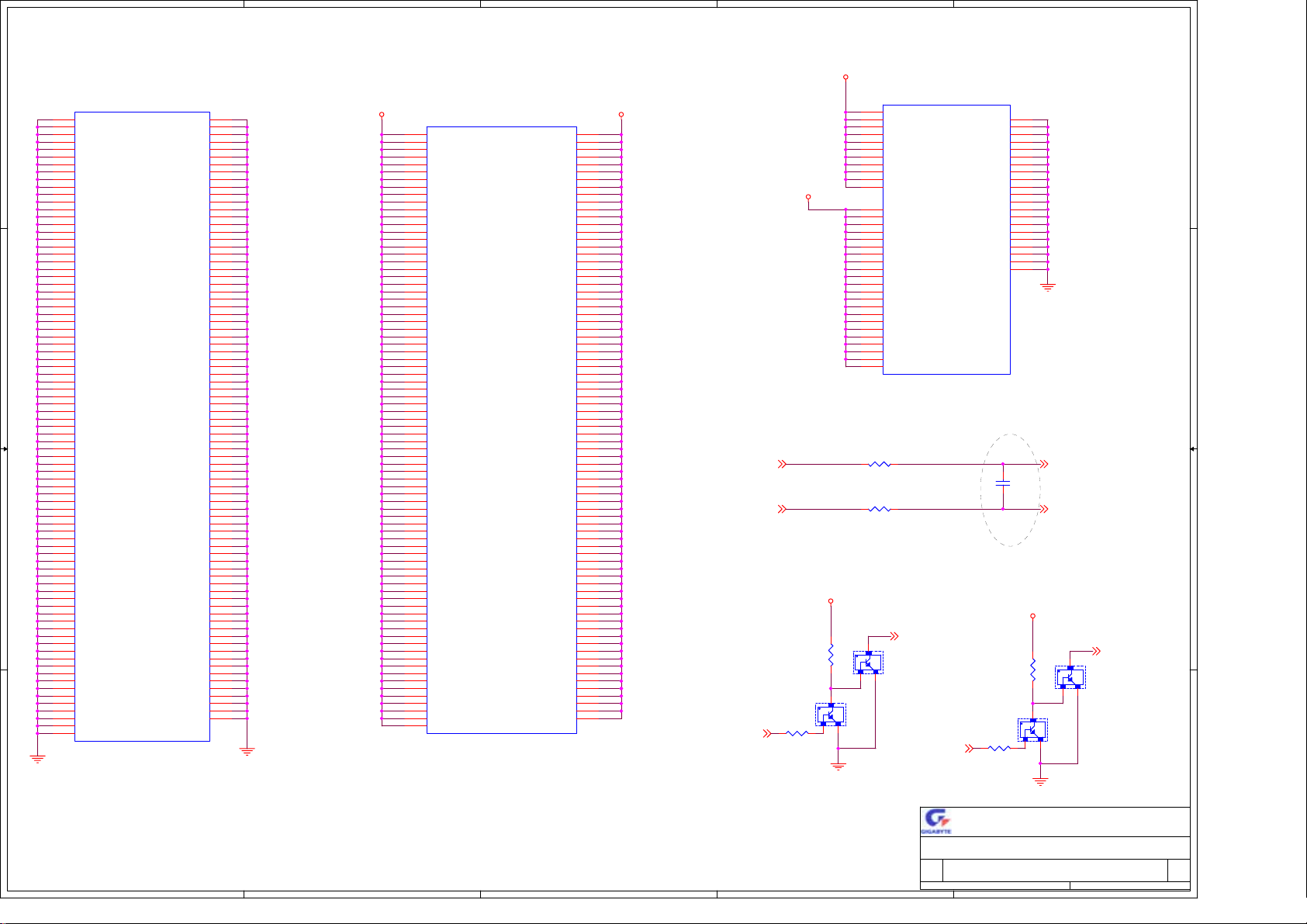

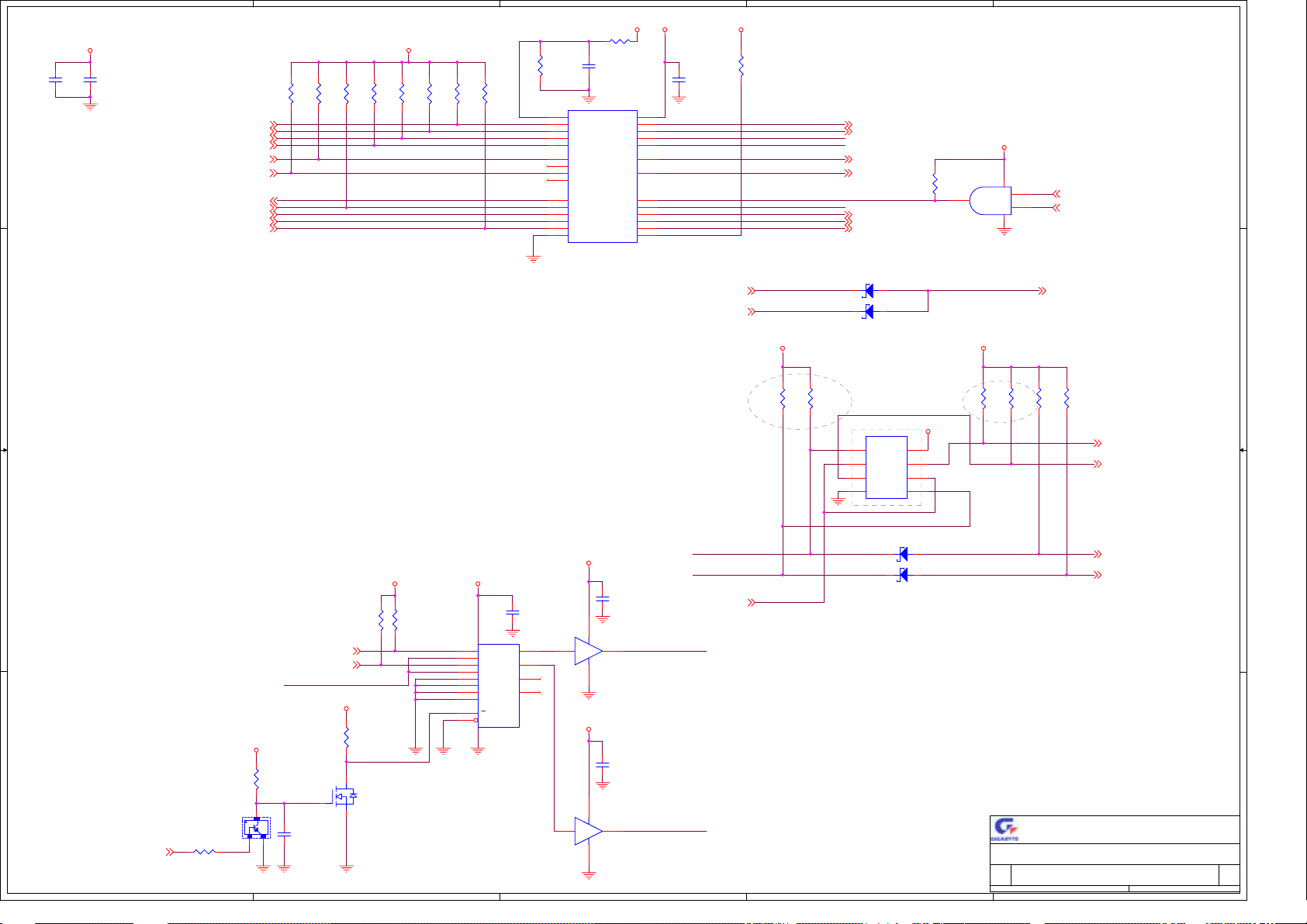

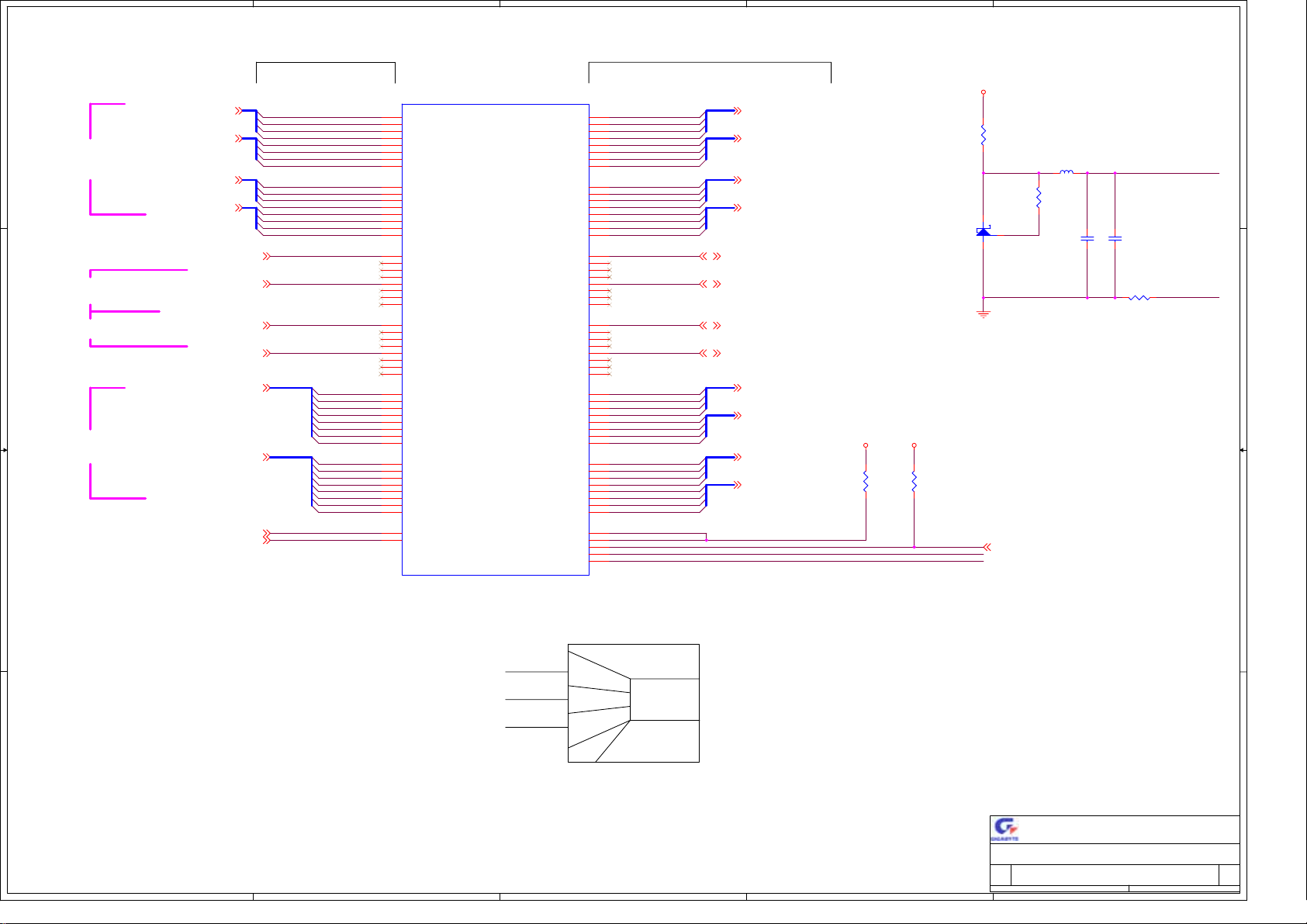

14.318

SMA CONNECTOR

CLOCK BLOCK DIAGRAM

CRYSTAL

D D

CPU2

3V66_1

CPU1 CUP1

CPU0

CPU3

CK 409B

CLOCK SYNTHESIZER

C C

DRIVER

3V66_2

USB_48

PCIF0

REF0

B B

DOT_48

PCI_4

ITP_BCLK_P/N (200MHZ)

2

MCH_BCLK_P/N (200MHZ)

2

MCH_66MHZ_CLK

P1_BCLK_P/N(200MHZ)

2

P0_BCLK_P/N(200MHZ)

2

ICH_HI66MHZ_CLK

ICH_USB_48MHZ_CLK

ICH_33MHZ_CLK

ICH_14MHZ_CLK

PCI 64/66 (SLOT #4)

PCI 64/66 (SLOT #5)

SIO_48MHZ_CLK

SIO_33MHZ_CLK

ITP_XDP

BCLK(P/N-1/0)

BCLK(P/N-1/0)

32.768KHZ

CRYSTAL

Hance

Rapids

PX_PCLKO3

PX_PCLKO0

SIO

CUP0

LINDENHURST

MCH_SRC_100MHZ_CLK_P/N

ICH_SRC_100MHZ_CLK_P/N

SUS_CLK

PXH_PAPCLK_FB PXH_PBPCLK_FB

DDRA_CMDCLK_A0_P/N

DDRA_CMDCLK_A1_P/N

DDRA_CMDCLK_A2_P/N

DDRA_CMDCLK_A3_P/N

DDRB_CMDCLK_B0_P/N

DDRB_CMDCLK_B1_P/N

DDRB_CMDCLK_B2_P/N

DDRB_CMDCLK_B3_P/N

2

DDRII DIMM #A1

2

2

2

2

2

2

2

2

DIFF3 DIFF5 DIFF0

DB800 (SRC -DIFFERENTIAL BUFFER)

SRC

DIFF2

PXH_SRC_100MHZ_CLK_P/N

2

LANB_SRC_100MHZ_CLK_P/N

2

PAPCLK0(6)

PAPCLKI

PXH

PBPCLK0(6)

PB_PCLKI

BCM5721 BCM5721

DDRII DIMM #B1

DDRII DIMM #A2

DDRII DIMM #B2

PCI EXPRESS SLOT1

EXP_SLOT1_100MHZ_CLK_P/N

2

DIFF6 DIFF7

LANA_SRC_100MHZ_CLK_P/N

2

DDRII DIMM #A3

DDRII DIMM #B3

DDRII DIMM #B4

DDRII DIMM #A4

2

SRC

PCIF1

PCI 0

PCI 1

PCI 2

REF 1

A A

PCI 3

5

DB800_SRC_100MHZ_CLK_P/N

IPMI33_LPC_CLK

PCI_SLOT3_33MHZ_CLK

VIDEO_33MHZ_CLK

PLD_33MHZ_CLK

VIDEO_14MHZ_CLK

FWH_33MHZ_CLK

2

IPMI CON

PCI 32/33 (SLOT #6)

PLD

VIDEO

(RAGE

XL)

FWH

25MHZ

CRYSTAL

4

SUS_CLK

PAPCLK0(0)

PXH_PAPCLK0<0>

PCI_X SLOT #2

3

PBPCLK0(0)

PXH_PBPCLK0<0>

PCI_X SLOT #3

25MHZ

CRYSTAL

Title

25MHZ

CRYSTAL

GIGA-BYTE TECHNOLOGY CO., LTD.

CLOCK BLOCK

Size Document Number Rev

GA-9ILDTH

of

Date: Sheet

2

481Tuesday, June 21, 2005

1

1.1

5

4

3

2

1

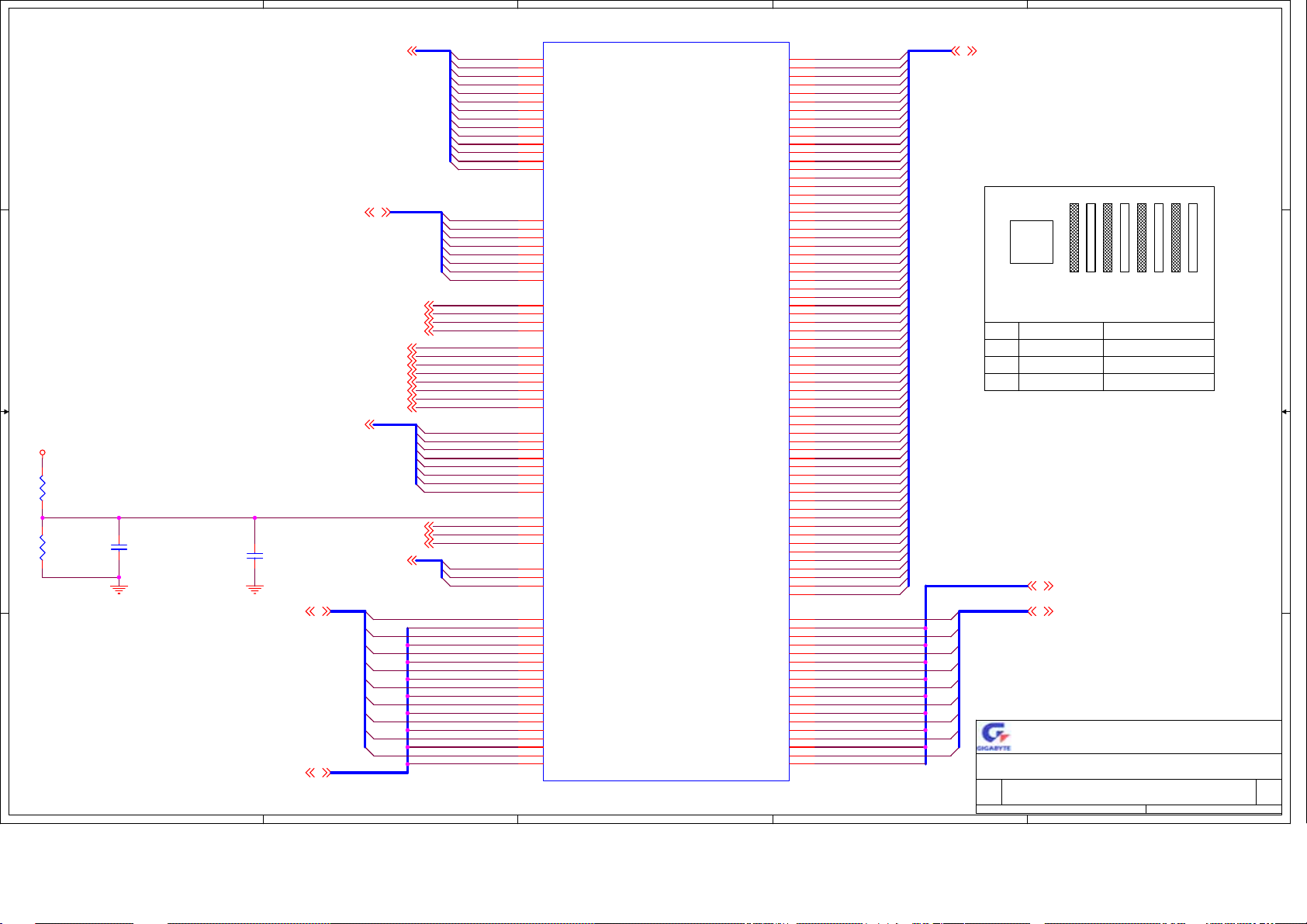

PS-PL

W83791D

SMB = 5Ah

IPMI

GSMI

70P

GbE

BCM5721

IPMB_SDA

IPMB_SCL

I2C_BUS0_SDA2

I2C_BUS0_SCL2

SVP

SMB = 30h

IPMB1

PCA9515

IPMB_SDA2

SR79,

SR80

IPMB_SCL2

W83791

SMB Address = 5Eh

HDD-PL

SMB =

94h,E0h

FFC1

FFC_SDA

FFC_SCL

LM93

SMB = 58h

HDD-PL

SMB =

90h,E2h

FFC2

GbE

BCM5721

D D

Hance

Rapids

SMB Address = 44h

LM75

CPU

SMB = 9Ah

R601 R415 R599 R879

LM75

PCI

SMB = 98h

LM75

DDR

SMB = 92h

LM75

SCSI

SMB = 96h

LAN_EMP_SDA

LAN_EMP_SCL

SE-LINK

P3V3_STBY

ICH_SDA

ICH_SCL

C C

PCA9545

Mutiplexer

SMB = E0h

I2C_BUS0_SDA

I2C_BUS0_SCL

P3V3

IDEEPROM

R851,

R853

IPMB

SMB = A8h

PCI-X Slot#4

66MHZ

R289/X,

R295/X

PCI-X Slot#5

R288/X,

R294/X

PCI Slot#6

33MHZ66MHZ

R272/X,

R276/X

R498/X

R499/X

PS-UNIT

SMB =

A0h,B0h,A2h,B2h,

A4h,B4h,ACh,BCh

PWRDET

R329,

R330

R817,

R819

W83791D

SMB = 5Ch

IPMB2

IPMB2_SDA

IPMB2_SCL

PCA9515PCA9515

IPMB_SDA3

IPMB_SCL3

CK-409B

DIMM B-1

SMB Address = A8h SMB Address = ACh

B B

DIMM B-2

SMB Address = AAh

DIMM B-4DIMM B-3

SMB Address = AEh

SMB Address = D2h

R937,

R949

30

DIMM A-1

SMB Address = A0h

I2C_BUS1_SDA

I2C_BUS1_SCL

P3V3

MCH

LINDENHURST

I2C_BUS2_SDA

I2C_BUS2_SCL

A A

P3V3

R800,

R822

SMB Address = 60h

PXH

SMB Address = C2h

4

I2C_BUS3_SDA

I2C_BUS3_SCL

5

P3V3

R796,

R797

DIMM A-2

SMB Address = A2h

PCA9554A

SMB Address = 70h

SR154,

SR155

SMB Address = 8Eh

Q-Switch

Q-Switch

MIC2593

DIMM A-3

SMB Address = A4h SMB Address = DCh

MIC2592B

SR29,

SR30

SMB Address = 8Ch

R282,

R285

R281,

R284

PCI-X Slot#2

133MHZ

PCI-X Slot#3

133MHZ

3

DIMM A-4

SMB Address = A6h

Q-Switch

SR42,

SR54

DB800

PCI-E Slot#1

R818/X,

R820/X

Title

Size Document Number Rev

2

Date: Sheet

GIGA-BYTE TECHNOLOGY CO., LTD.

SMBUS

GA-9ILDTH

581Tuesday, June 21, 2005

1

of

1.1

5

4

3

2

1

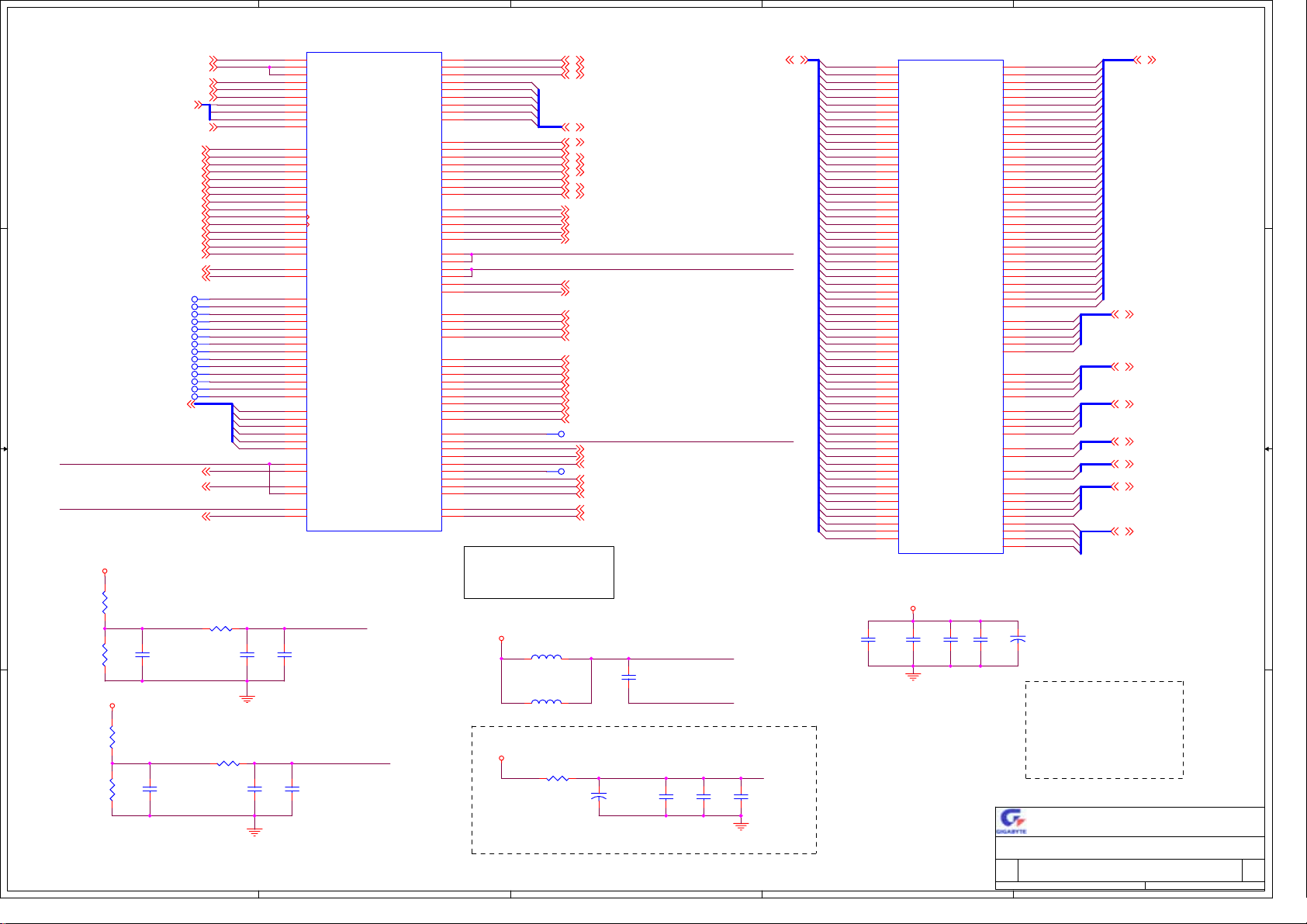

ERP12V

ISL6556B

D D

P12V_CPU_0

120A

ISL6556B HIP6601B

P12V_CPU_1

120A

ATX CONN

HIP6302

P12V

C C

P5V

39A

ISL6520

6A

RT9173A

1.98A

ISL6525

13A

APL1084

1.5A

HIP6601B

X4

X4

HIP6602

X2

P_VCCP0

P_VCCP1

CPU0

1.2/CORE

CPU1

1.2/CORE

P1V8

P_VTT

P0V9_DDR

P1V5

P2V5_VIDEO

MCH

1.2/1.5/2.5

DDRII-400

0.9/1.8

VIDEO

HR

1.2/1.5

3.3/3.3SBY

LT1963EQ

1.7A

B B

P3V3

P1V8_SCSI

SCSI

3.3/1.8

PXH

3.3/2.5

P5V_STBY

A A

N12V

5

APL1084

3A

GD75232

PCI/PCI-X CONN

4

APL1084

3A

P1V8_STBY

3

P3V3_STBY

265mA

RC1117ST

BROADCOM

BCM5721 GBE

BROADCOM

BCM5721 GBE

2

P1V5_HR_STBY

Title

Size Document Number Rev

Date: Sheet

GIGA-BYTE TECHNOLOGY CO., LTD.

PWR DELIVERY

GA-9ILDTH

681Tuesday, June 21, 2005

1

of

1.1

5

4

3

2

1

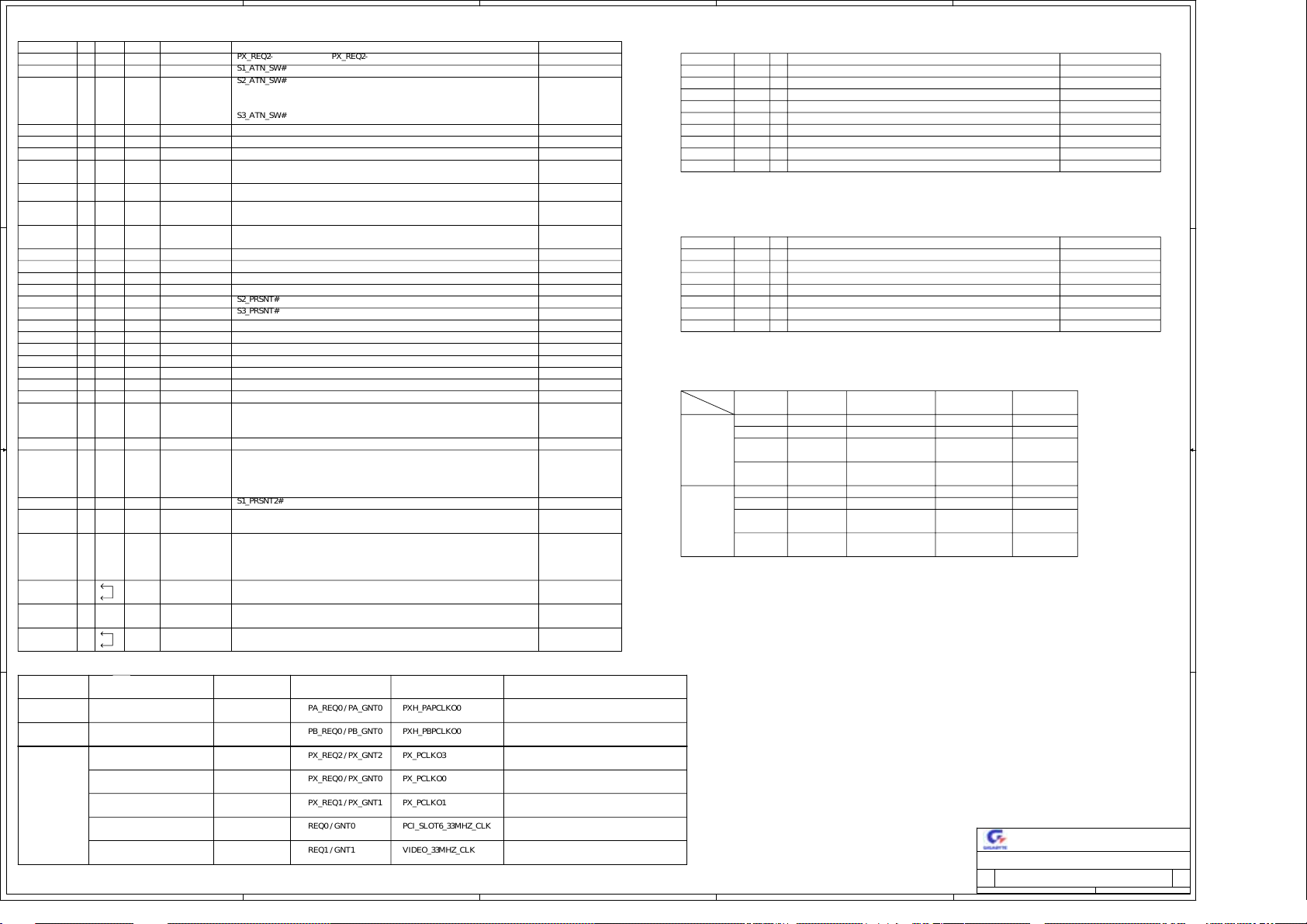

Hance Rapids

GPIO R PWR WELL FUNCTION

GPIO 0

GPIO 1

GPIO 2

GPIO 3

GPIO 4

GPIO 5

D D

GPIO 6

GPIO 7

GPIO 8

GPIO 9

GPIO 10

GPIO 11

GPIO 12

GPIO 13

GPIO 14

GPIO 15

GPIO 16

GPIO 17

GPIO 18

GPIO 19

GPIO 20

GPIO 21

GPIO 22

GPIO 23

C C

GPIO 24

GPIO 25

GPIO 26

GPIO 27

GPIO 28

GPIO 29

GPIO 30

GPIO 31

GPIO 32

GPIO 33

GPIO 34

GPIO 35

GPIO 36

GPIO 37

GPIO 38

GPIO 39

GPIO 40

GPIO 41

GPIO 42

B B

GPIO 43

GPIO 44

GPIO 55

GPIO 56

GPIO 57

GPIO 58

GPIO 63

NOTE

CONTROLLER

PXH A

PXH B

I

PUPU8.2K

I

I

PU

PU

I

PU

I

PU

I

I

PU 4.7K P3V3 MCH_PME# PME EVENT FROM MCH PCI -E PORT

I

I

P3V3

8.2K

P3V3

P3V3

8.2K

P3V3

8.2K

P3V3

8.2K

P3V3

8.2K

P3V3PU

4.7K IPMI_FP_SMI#

RESERVED

I

I

I

O

O

O

O

I

I

O

O

I/O

I/

I/

I/

N/A

N/A

N/A

I/O PU P3V3

/O

I

/O

I

/O

I

/O

I

I/O PU P3V3

I

I

I

I

I

O

O

O

8.2KPU

P3V3_STBY

PU 8.2K

PU IN

PU IN

PD IN

PD IN

PU

PU

PU

O

PD

O

O

PU 8.2K

P3V3_STBY

P3V3_STBY

RESERVED

P3V3

P3V3

8.2K

P3V3

8.2K

P3V3

8.2K

P3V3

8.2K

P3V3

P3V3

P3V3_STBY

8.2K

P3V3_STBY

8.2K

R E S E R V E D

P3V3_STBY

8.2KPU

P3V3_STBY

RESERVED

PU 8.2K P3V3

PU

8.2K

PU

PU

PDPD8.2K

PD

PD

PD

PU

PU

P3V3

8.2K

P3V3

8.2K

P3V3

P3V3

8.2K

P3V3

P3V3

8.2K

P3V3

8.2K DP MB ID SETTING

8.2K

P3V3

P3V3 PERR_SMI_RST#

RESERVED

P3V3_STBY

10K

P3V3_STBY

10K

RESERVED

ONLY GPIO[0:15] ALLOW AN INPUT TO BE ROUTED TO SMI# OR SCI

PCI DEVICE

PCI-X 133 SLOT2

PCI-X 133 SLOT3

PCI-X 66 SLOT4 PX_AD17

A A

PCI-X 66 SLOT5(ZCR)

PCI-X 66 SCSI

Hance

Rapids

PCI-33 SLOT6

PCI-33 ATI

5

PX_REQ2

-

S1_ATN_SW

S2_ATN_SW

GPI3_SMI#

P_ IRQG-

S3_ATN_SW

#

#

#

PX_REQ2

-

PCI-E SLOT1 Hot-plug event.

PCI-X SLOT2 Hot-plug event.

SMI EVENT FROM WINBOND/SIO

TM_ALERT#

PCI-X SLOT3 Hot-plug event.

SMI EVENT FROM IPMI or NMI EVENT from FP.

WAKE#PU IN P3V3_STBY PXHPME# FROM PCIE-X CONN AND LAN

PCI_PERR_SMI#

ICH_SMBALERT#

MCH_GPE#PU 8.2K

SIO_PME#

PX_GNT2PX_GNT3HR_S2_DISABLE

HR_S3_DISABLE

S2_PRSNT#

S3_PRSNT#

SATALED# SATALED#

I2C_MUX_RST# RST 9545 I2C BUS

DIS_LANA#

DIS_LANB# DISABLE BCM5721 LAN B

PX_IRQ0PX_IRQ1PX_IRQ2PX_IRQ3-

S1_PRSNT2

#

S66DET

P66DET

DPMB_SET0#

DPMB_SET1#

DPMB_SET2# DP MB ID SETTING

MEM FREQ_SEL0

MEM FREQ_SEL1

IDSEL

PA_AD17

PB_AD17

PX_AD18

PX_AD21

A_D17

A_D18

SMI EVENT FROM EXT-PERR / LM93

MCH GENERAL PURPOSE EVENT for Hot-plug

PME FROM SIO

PX_GNT2-

NO USE

DISABLE PCI-X SLOT2 POWER(HOT-PLUG)

DISABLE PCI-X SLOT3 POWER(HOT-PLUG)

PCI-X SLOT2 CARD PRSENT STATUS.

PCI-E SLOT3 CARD PRSENT STATUS.

NO USE

NO USE

DISABLE BCM5721 LAN A

NO USEWDT_TOUT#

PCI-X CONN

PCI-X CONN

PCI-X CONN

PCI-X CONN

PCI-E SLOT1 CARD PRSENT STATUS.

DETECT PRIMERY IDE CABLE

DETECT SECANDERY IDE CABLE

DP MB ID SETTING

ISSUE RESET WHEN PERR SMI EVENT OCCURS.

AUTO MEM DET 400

AUTO MEM DET 400

REQ / GNT

PA_REQ0 / PA_GNT0

PB_REQ0 / PB_GNT0

PX_REQ2 / PX_GNT2

PX_REQ0 / PX_GNT0

PX_REQ1 / PX_GNT1

REQ0 / GNT0

REQ1 / GNT1

4

CLOCK

PXH_PAPCLKO

PXH_PBPCLKO

PX_PCLKO3

PX_PCLKO0

PX_PCLKO1

PCI_SLOT6_33MHZ_CLK

VIDEO_33MHZ_CLK

0

0

NOMAL/ACT

H/L

H/L

H/L

H/L

H/L

H/L

H/L

H/L

H/L

H/L

H/L

H/L

H/L

L/H

L/H

H/L

H/L

H/L

H/L

H/L

H/L

H/L

L/H

IRQ ROUTING

D

CINT A

B

0 1 2 3

0 1 2 3

1 0 2 3

0 1 2(SCSIA) 3(SCSIB)

2(SCSIA) 3( SCSIB)

A B C D

D

3

GPIO PWR

GPIO 16

GPIO 17

GPIO 53

GPIO 42

GPIO 43 STBY

GPIO 44

GPIO 45 STBY

NOTE

GPIO 0

GPIO 1

GPIO 2

GPIO 3

GPIO 4

GPIO 5

GPIO 6

GPIO 7

P3V3

P3V3OO

STBY

STBY

STBY

STBYGPIO 54

SIO_S1_PWR_LED

SIO_S1_ATN_LED

PWRLED

O

SIO_PSON# PWR ON FROM SIOO

PWBTN

HR_PWRBTN#

O

SLP_S#3I

O

SIO_PME#

GPIO(10/40/41/42/43/44/45/46/53/54/55) POWER BY STBY

P3V3

I

P3V3

P3V3

P3V3

P3V3

P3V3

P3V3

P3V3

CPU0_FAN_TACH DETECT CPU0 FAN SPEED

CPU1_FAN_TACH

OIHW_CPU0_SMI#

HW_CPU1_SMI#O

I

CPU0_THERMTRIP#

I

CPU1_THERMTRIP#

I

CPU0_IERR#

I

CPU1_IERR#

DDRII-400 Memory Mapping Table

SMB Addr.Location CMDCLK Mapping CS# Mapping CKE

CH.A

CH.B

DDR8

DDR6

DDR4

DDR2

DDR7

DDR5

DDR3

DDR1

0XA0

0XA2

0XA4

0XA6

0XA8

0XAA

0XAC

0XAE

SIO

FUNCTION NOMAL/ACT

PWR LED for Hot-plug PCI-E Slot1

ATN LED for Hot-plug PCI-E Slot1

ACT PWR ON

PWR BTN FROM FP & IPMI

PWR BTN TO H-R

INDECATE S3 MODE FROM H-R

RST IPMI FROM SIOGPIO 46 STBY O SIO_BMC_RST# H/L

WAKE UP FROM ICH5

LM93

DETECT CPU1 FAN SPEED

SMI EVENT FROM LM93HW

SMI EVENT FROM LM93HW

MONITOR CPU0_THERMTRIP#

MONITOR CPU1_THERMTRIP#

DETECT CPU0_IERR#

DETECT CPU1_IERR# H/L

DDRA_CMDCLK0

DDRA_CMDCLK3

DDRA_CMDCLK2

DDRA_CMDCLK1

DDRA_CMDCLK3

DDRA_CMDCLK1

DDRA_CMDCLK2

DDRA_CMDCLK0

2

CS#0,CS#1

CS#2,CS#3

CS#4,CS#5

(CS#2,CS#3)

CS#6,CS#7

(CS#0,CS#1)

CS#0,CS#1

CS#2,CS#3

CS#4,CS#5

(CS#2,CS#3)

CS#6,CS#7

(CS#0,CS#1)

MEM_CKE0

MEM_CKE2

MEM_CKE4/2

MEM_CKE6/0

MEM_CKE1

MEM_CKE3

MEM_CKE5/3

MEM_CKE7/1

GIGA-BYTE TECHNOLOGY CO., LTD.

Title

Size Document Number Rev

Date: Sheet

PCI ROUTING

GA-9ILDTH

L/H/Blinking

L/H/Blinking

H/L(PWR ON)

H/L

H/LI

H/L

H/L

H/L

NON

NON

H/L

H/L

H/L

H/L

H/L

1

781Tuesday, June 21, 2005

1.1

of

5

4

3

2

1

END PROCESSOR 0

SB_BPRI#{11,18}

SB_CPU0_BREQ#23{9}

SB_BREQ#1{9,11,18}

SB_BREQ#0{9,11,18}

SB_CPURST#{9,11,13,14,18}

D D

C C

P_VCCP_A_CPU0

AGND_CPU0

B B

P_VTT

774mV

P_VTT

SB_RS#[0..2]{11,18}

SB_RSP#{11,18}

SB_CPU_A20M#{9,11,37}

SB_CPU_IGNNE#{9,11,37}

SB_CPU_INIT#{9,11,37,63}

SB_CPU_NMI{9,11,14}

SB_CPU_INTR{9,11,37}

CPU_PWR_GD{9,11,13,37}

SB_CPU0_SMI#{9,14}

SB_CPU_SLP#{9,11,37}

SB_CPU_STPCLK#{9,11}

P0_BCLK#{33}

P0_BCLK{33}

ITP_TCK0{11,13}

ITP_TDI_MAIN{13}

ITP_TMS_MAIN{11,13}

ITP_TRST#{11,13,17}

SB_CPU0_BSEL1{9,10}

SB_CPU0_BSEL0{9,10}

TP97

TP98

TP99

TP116

TP94

TP93

TP112

TP105

TP115

TP107

TP106

TP95

TP108

TP20

VID_CPU0_R[5..0]{69,76}

VR0_VCCSENSE{69}

VTTEN{9,11,62}

VR0_VSSSENSE{69}

SR194

49.9/6/1

VREF_P_VTT_CPU0_3_R VREF_P_VTT_CPU0_3

SC589

SR195

1U/6/Y/10V

90.9/6/1

SB_BPRI#

SB_CPU0_BREQ#23

SB_BREQ#1

SB_BREQ#0

SB_CPURST#

SB_RS#2

SB_RS#1

SB_RS#0

SB_RSP#

SB_CPU_A20M#

SB_CPU_IGNNE#

SB_CPU_INIT#

SB_CPU_NMI

SB_CPU_INTR

CPU_PWR_GD

SB_CPU0_SMI#

SB_CPU_SLP#

SB_CPU_STPCLK#

P0_BCLK#

P0_BCLK

ITP_TCK0

ITP_TDI_MAIN

ITP_TMS_MAIN

ITP_TRST#

SB_CPU0_BSEL1

SB_CPU0_BSEL0

VID_CPU0_R5

VID_CPU0_R4

VID_CPU0_R3

VID_CPU0_R2

VID_CPU0_R1

VID_CPU0_R0

VR0_VCCSENSE

VTTEN

VR0_VSSSENSE

SR190

0/6

SC581

220P/6/X/50V

U86A

D23

BPRI#

D10

E11

F12

D20

F21

D22

E21

F27

C26

G23

B24

AB7

C27

AE6

E24

C24

A25

F24

AB3

AA3

AE29

AE28

AE30

AD29

AD28

AC29

AB29

AB28

AA29

AA28

AE15

AC1

AE16

AD4

B27

AB4

AA5

D26 C1

NOCONA 667

BR3#

BR2#

BR1#

BR0#

Y8

RESET#

RS2#

RS1#

RS0#

C6

RSP#

A20M#

IGNNE#

D6

INIT#

LINT1_NMI

LINT0_INTR

PWRGOOD

SMI#

SLP#

D4

STPCLK#

W5

BCLK1

Y4

BCLK0

TCK

TDI

TMS

TRST#

BSEL1

BSEL0

RESERVED1

RESERVED0

RSVD16

Y3

RSVD15

RSVD14

RSVD13

RSVD12

RSVD10

RSVD9

RSVD8

RSVD7

RSVD3

RSVD2

RSVD1

A1

VID5

B3

VID4

C3

VID3

D3

VID2

E3

VID1

F3

VID0

VCCIOPLL

VCC_SENSE

E1

VTTEN

VCCA

VSSA

VSS_SENSE OPTIMIZED_COMPAT#

NOCONA 800

ADS#

BINIT#

BNR#

BPM5#

BPM4#

BPM3#

BPM2#

BPM1#

BPM0#

DBSY#

DEFER#

DRDY#

HIT#

HITM#

TRDY#

LOCK#

MCERR#

IERR#

FERR#

THERMTRIP#

PROCHOT#

TDO

GTLREF3

GTLREF2

GTLREF1

GTLREF0

ODTEN

SKTOCC#

COMP3

COMP2

COMP1

COMP0

TESTHI8

TESTHI7

TESTHI6

TESTHI5

TESTHI4

TESTHI3

TESTHI2

TESTHI1

TESTHI0

SMB_PRT

VCCPLL

THERMDC

THERMDA

BOOT_SELECT

RSVD

VIDPWRGD

TEST_BUS

FORCEPR#

SLEW_CTRL

WIDE 10-12 MILS

P_VTT

SC561

220P/6/X/50V

SB_ADS#

D19

SB_BINIT#

F11

SB_BNR#

F20

CPU0_BPM#5

E4

CPU0_BPM#4

E8

CPU0_BPM#3

F5

CPU0_BPM#2

E7

CPU0_BPM#1

F8

CPU0_BPM#0

F6

SB_DBSY#

F18

SB_DEFER#

C23

SB_DRDY#

E18

SB_HIT#

E22

SB_HITM#

A23

SB_TRDY#

E19

SB_LOCK#

A17

SB_MCERR#

D7

SB_CPU0_IERR#

E5

SB_CPU_FERR#

E27

SB_CPU_THERMTRIP#

F26

SB_CPU0_PROCHOT#

B25

ITP_TDO_P0

E25

F9

F23

W9

W23

PD_ODTEN_CPU0

B5

SMC_CPU0_SKTOCC#

A3

PD_COMP3_CPU0

AC28

PD_COMP2_CPU0

D25

PD_COMP1_CPU0

E16

PD_COMP0_CPU0

AD16

PU_CPU0_8

Y29

PU_CPU0_0

A26

PU_CPU0_5

AE5

PU_CPU0_6

AD5

PU_CPU0_1

AA7

PU_CPU0_7

Y6

PU_CPU0_3

W8

PU_CPU0_2

W7

PU_CPU0_4

W6

AE4

AD1

CPU0_THERMDC

Y28

CPU0_THERMDA

Y27

PU_BOOT_SELECT_CPU0

G7

W3

VID_PWRGD

B1

SB_CPU0_CPU1_TESTBUS

A16

SB_CPU_FORCEPR#

A15

SLEW_CTRL_CPU0

AC30

CPU0_OPTIM_COMPAT_CTRL

COMP3 =SB_CPU0_ADDR_ERC

COMP2 =SB_CPU0_DATA_ERC

PU_CPU0_8=SB_CPU0_EDRDY

PU_CPU0_0=SB_CPU0_SNPD#

WW35 eMOW: Icc of VCCIOPLL pins : 100 mA

WW35 eMOW: Icc for VCCA pins : 120mA

120mA

L13

10UH/8

L12

10UH/8

TP104

TP120

12

SB_ADS# {11,18}

SB_BINIT# {9,11,18}

SB_BNR# {9,11,18}

CPU0_BPM#[5..0] {13}

SB_DBSY# {11,18}

SB_DEFER# {11,18}

SB_DRDY# {11,18}

SB_HIT# {9,11,18}

SB_HITM# {9,11,18}

SB_TRDY# {11,18}

SB_LOCK# {11,18}

SB_MCERR# {9,11,18}

SB_CPU0_IERR# {9,14}

SB_CPU_FERR# {9,11,37}

SB_CPU0_THERMTRIP# {9,14}

SB_CPU0_PROCHOT# {9,14}

ITP_TDO_P0 {13}

PD_ODTEN_CPU0 {9}

SMC_CPU0_SKTOCC# {9,62,76,77}

PD_COMP3_CPU0 {9}

PD_COMP2_CPU0 {9}

PD_COMP1_CPU0 {9}

PD_COMP0_CPU0 {9}

PU_CPU0_8 {9}

PU_CPU0_0 {9}

PU_CPU0_5 {9}

PU_CPU0_6 {9}

PU_CPU0_1 {9}

PU_CPU0_7 {9}

PU_CPU0_3 {9}

PU_CPU0_2 {9}

PU_CPU0_4 {9}

CPU0_THERMDC {10}

CPU0_THERMDA {10}

PU_BOOT_SELECT_CPU0 {9}

VID_PWRGD {11,62}

SB_CPU0_CPU1_TESTBUS {9,11}

SB_CPU_FORCEPR# {9,11,14}

SLEW_CTRL_CPU0 {9}

CPU0_OPTIM_COMPAT_CTRL {9}

WIDE 10-12 MILS

P_VCCP_A_CPU0

C483

22U/12/Y/10V

AGND_CPU0

SB_D#[63..0]{11,18}

VREF_P_VTT_CPU0_3

VREF_P_VTT_CPU0_0

PU_VCCPLL_CPU0

12

SC328

22U/12/Y/10V

P_VTT

12

SC580

22U/12/Y/10V

SB_D#63

SB_D#62

SB_D#61

SB_D#60

SB_D#59

SB_D#58

SB_D#57

SB_D#56

SB_D#55

SB_D#54

SB_D#53

SB_D#52

SB_D#51

SB_D#50

SB_D#49

SB_D#48

SB_D#47

SB_D#46

SB_D#45

SB_D#44

SB_D#43

SB_D#42

SB_D#41

SB_D#40

SB_D#39

SB_D#38

SB_D#37

SB_D#36

SB_D#35

SB_D#34

SB_D#33

SB_D#32

SB_D#31

SB_D#30

SB_D#29

SB_D#28

SB_D#27

SB_D#26

SB_D#25

SB_D#24

SB_D#23

SB_D#22

SB_D#21

SB_D#20

SB_D#19

SB_D#18

SB_D#17

SB_D#16

SB_D#15

SB_D#14

SB_D#13

SB_D#12

SB_D#11

SB_D#10

SB_D#9

SB_D#8

SB_D#7

SB_D#6

SB_D#5

SB_D#4

SB_D#3

SB_D#2

SB_D#1

SB_D#0

SC443

1U/6/Y/10V

AB6

Y9

AA8

AC5

AC6

AE7

AD7

AC8

AB10

AA10

AA11

AB13

AB12

AC14

AA14

AA13

AC9

AD8

AD10

AE9

AC11

AE10

AC12

AD11

AD14

AD13

AB15

AD18

AE13

AC17

AA16

AB16

AB17

AD19

AD21

AE20

AE22

AC21

AC20

AA18

AC23

AE23

AD24

AC24

AE25

AD25

AC26

AE26

AA19

AB19

AB22

AB20

AA21

AA22

AB23

AB25

AB26

AA24

Y23

AD27

AA25

Y24

AA27

Y26

SC569

0.1U/6/X/16V

U86B

D63

NOCONA 667

D62

D61

D60

D59

D58

D57

D56

D55

D54

D53

D52

D51

D50

D49

D48

D47

D46

D45

D44

D43

D42

D41

D40

D39

D38

D37

D36

D35

D34

D33

D32

D31

D30

D29

D28

D27

D26

D25

D24

D23

D22

D21

D20

D19

D18

D17

D16

D15

D14

D13

D12

D11

D10

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

NOCONA 800

EC28

PSA2.5VB820MH11/8X11.5

ADSTB1#

ADSTB0#

DSTBP3#

DSTBP2#

DSTBP1#

DSTBP0#

DSTBN3#

DSTBN2#

DSTBN1#

DSTBN0#

BREQ4#

BREQ3#

BREQ2#

BREQ1#

BREQ0#

DBI3#

DBI2#

DBI1#

DBI0#

DP3#

DP2#

DP1#

DP0#

AP1#

AP0#

A35

A34

A33

A32

A31

A30

A29

A28

A27

A26

A25

A24

A23

A22

A21

A20

A19

A18

A17

A16

A15

A14

A13

A12

A11

A10

A9

A8

A7

A6

A5

A4

A3

C9

A7

A6

B7

C11

D12

E13

B8

A9

D13

E14

C12

B11

B10

A10

F15

D15

D16

C14

C15

A12

B13

B14

B16

A13

D17

C17

A19

C18

B18

A20

A22

B22

C20

C21

B21

B19

AB9

AE12

AD22

AC27

AE17

AC15

AE19

AC18

D9

E10

F14

F17

Y11

Y14

Y17

Y20

Y12

Y15

Y18

Y21

SB_HA#34

SB_HA#33

SB_HA#32

SB_HA#31

SB_HA#30

SB_HA#29

SB_HA#28

SB_HA#27

SB_HA#26

SB_HA#25

SB_HA#24

SB_HA#23

SB_HA#22

SB_HA#21

SB_HA#20

SB_HA#19

SB_HA#18

SB_HA#17

SB_HA#16

SB_HA#15

SB_HA#14

SB_HA#13

SB_HA#12

SB_HA#11

SB_HA#10

SB_HA#9

SB_HA#8

SB_HA#7

SB_HA#6

SB_HA#5

SB_HA#4

SB_HA#3

SB_REQ#4

SB_REQ#3

SB_REQ#2

SB_REQ#1

SB_REQ#0

SB_DBI#3

SB_DBI#2

SB_DBI#1

SB_DBI#0

SB_DP#3

SB_DP#2

SB_DP#1

SB_DP#0

SB_AP#1

SB_AP#0

SB_ADSTB#1

SB_ADSTB#0

SB_DSTBP#3

SB_DSTBP#2

SB_DSTBP#1

SB_DSTBP#0

SB_DSTBN#3

SB_DSTBN#2

SB_DSTBN#1

SB_DSTBN#0

Trace Width:12 Mils

VREF_P_VTT_CPU0_0

SB_HA#35

C8

VREF_P_VTT_CPU0_3

VCCIOPLL_CPU0

AGND_CPU0

PU_VCCPLL_CPU0

WIDE 10-12 MILS

R722

49.9/6/1

A A

774mV

VREF_P_VTT_CPU0_0_R

C479

R721

1U/6/Y/10V

90.9/6/1

5

R762

0/6

VREF_P_VTT_CPU0_0

C490

C489

220P/6/X/50V

220P/6/X/50V

SC465

0.1U/6/X

3

NO USE

SC472

0.1U/6/X

Title

Size Document Number Rev

2

Date: Sheet

GIGA-BYTE TECHNOLOGY CO., LTD.

NOCONA 800 MICS P0

GA-9ILDTH

P1V5

WIDE 10-12 MILS

SR168

0/6/X

4

12

+

SEC1

470U/4V/7343/X

12

SC444

4.7U/1206/X

PU_VCCPLL_CPU0

SB_HA#[35..3] {11,18}

SB_REQ#[4..0] {11,18}

SB_DBI#[3..0] {11,18}

SB_DP#[3..0] {11,18}

SB_AP#[1..0] {11,18}

SB_ADSTB#[1..0] {11,18}

SB_DSTBP#[3..0] {11,18}

SB_DSTBN#[3..0] {11,18}

of

881Tuesday, June 21, 2005

1

1.1

5

4

3

2

1

P_VTT

R920 220/6

D D

R945 220/6

R965 220/6

R719 220/6

R758 220/6

R933 220/6

R951 220/6

R988 51/6

C C

R926 220/6

R966 51/6

R973 51/6

R927 51/6

R935 51/6

SB_CPU_A20M#

SB_CPU_IGNNE#

SB_CPU_INIT#

SB_CPU_INTR

SB_CPU_SLP#

SB_CPU_STPCLK#

SB_CPU_NMI

SB_CPU_FORCEPR#

SB_CPU0_SMI#

SB_CPU0_IERR#

SB_CPU0_PROCHOT#

SB_CPU1_THERMTRIP#

SB_CPU0_THERMTRIP#

SB_CPU_A20M# {8,11,37}

SB_CPU_IGNNE# {8,11,37}

SB_CPU_INIT# {8,11,37,63}

SB_CPU_INTR {8,11,37}

SB_CPU_SLP# {8,11,37}

SB_CPU_STPCLK# {8,11}

SB_CPU_NMI {8,11,14}

SB_CPU_FORCEPR# {8,11,14}

SB_CPU0_SMI# {8,14}

SB_CPU0_IERR# {8,14}

SB_CPU0_PROCHOT# {8,14}

SB_CPU1_THERMTRIP# {11,14}

SB_CPU0_THERMTRIP# {8,14}

together

together

R913 51/6

B B

SR183 39/6

SR193 39/6

SR191 39/6

SR192 39/6

SR182 39/6

SB_CPU_FERR#

SB_BININ#_R SB_BINIT#

SB_BNR#_R

SB_HIT#_R

SB_HITM#_R

SB_MCERR#_R SB_MCERR#

SC556

47P/6/N/50V

SC565

47P/6/N/50V

SC563

47P/6/N/50V

SC564

47P/6/N/50V

SC551

47P/6/N/50V

SB_BNR#

SB_HIT#

SB_HITM#

SB_CPU_FERR# {8,11,37}

SB_BINIT# {8,11,18}

SB_BNR# {8,11,18}

SB_HIT# {8,11,18}

SB_HITM# {8,11,18}

SB_MCERR# {8,11,18}

P3V3

A A

5

VTTEN

VTTEN {8,11,62}

4

R903 4.7K/6

P_VTT

R989 51/6/X

R914 51/6/X

SR189 51/6

SR187 51/6

SR188 51/6

R724 510/6

R759 510/6

R972 100/6/1

R745 100/6/1

SR186 49.9/6/1

R761 49.9/6/1

P_VTT

R967 51/6

R958 51/6

P_VTT

R987

SB_CPU_STPCLK#{8,11}

PU_BOOT_SELECT_CPU0

CPU0_OPTIM_COMPAT_CTRL

SB_BREQ#0

SB_BREQ#1

SB_CPU0_BREQ#23

SB_CPU0_BSEL1

SB_CPU0_BSEL0

PD_COMP2_CPU0

PD_COMP3_CPU0

PD_COMP1_CPU0

PD_COMP0_CPU0

PD_ODTEN_CPU0

PD_ODTEN_CPU1

SB_CPU0_CPU1_TESTBUS

51/6

R986 0/6/X

R712 0/6

together

P_VTT

CPU_PWR_GD

PU_BOOT_SELECT_CPU0 {8}

CPU0_OPTIM_COMPAT_CTRL {8}

R765 300/6

R764 51/6

CPU_PWR_GD

SB_CPURST#

CPU_PWR_GD {8,11,13,37}

CLOSE TO CPU0

SB_CPURST# {8,11,13,14,18}

C481

100P/6/X

SB_BREQ#0 {8,11,18}

R736 51/6/X

SB_BREQ#1 {8,11,18}

R742 51/6/X

SB_CPU0_BREQ#23 {8}

SLEW_CTRL_CPU0

SLEW_CTRL_CPU1

SLEW_CTRL_CPU0 {8}

SLEW_CTRL_CPU1 {11}

SB_CPU0_BSEL1 {8,10}

R743 51/6/X

R737 0/6

SB_CPU0_BSEL0 {8,10}

PD_COMP2_CPU0 {8}

P3V3_STBY

PD_COMP3_CPU0 {8}

PD_COMP1_CPU0 {8}

R968 4.7K/6

SMC_CPU0_SKTOCC#

SMC_CPU0_SKTOCC# {8,62,76,77}

PD_COMP0_CPU0 {8}

P_VTT

END CPU NOT USE

R744 51/6/X

R690 51/6/X

PD_ODTEN_CPU0 {8}

R680 51/6

R668 51/6

R710 51/6

PD_ODTEN_CPU1 {11}

R703 51/6

R696 51/6

R685 51/6

R955 51/6

SB_CPU0_CPU1_TESTBUS {8,11}

ICH_CPU_STPCLK# {37}

Title

Size Document Number Rev

3

2

Date: Sheet

PU_CPU0_8

PU_CPU0_7

PU_CPU0_6

PU_CPU0_5

PU_CPU0_4

PU_CPU0_3

PU_CPU0_2

PU_CPU0_1

PU_CPU0_0

PU_CPU0_8 {8}

PU_CPU0_7 {8}

PU_CPU0_6 {8}

PU_CPU0_5 {8}

PU_CPU0_4 {8}

PU_CPU0_3 {8}

PU_CPU0_2 {8}

PU_CPU0_1 {8}

PU_CPU0_0 {8}

GIGA-BYTE TECHNOLOGY CO., LTD.

NOCONA 800 P0 TERMINATION

GA-9ILDTH

981Tuesday, June 21, 2005

1

of

1.1

5

4

3

2

P_VTT

1

Q76

SOT23

AD12

AC10

AA12

AE24

AE18

AE14

AD30

AD26

AD20

AC31

AC22

AC16

AB30

AB24

AB18

AB14

U86E

VCC_VTT1

VCC_VTT2

VCC_VTT3

Y10

VCC_VTT4

F10

VCC_VTT5

E12

VCC_VTT6

C10

VCC_VTT7

B12

VCC_VTT8

B4

VCC_VTT9

C5

VCC_VTT10

A4

VCC_VTT11

VCC_CORE160

VCC_CORE161

VCC_CORE162

AE8

VCC_CORE163

AE3

VCC_CORE164

VCC_CORE165

VCC_CORE166

VCC_CORE167

AD6

VCC_CORE168

AD2

VCC_CORE169

VCC_CORE170

VCC_CORE171

VCC_CORE172

AC4

VCC_CORE173

AC3

VCC_CORE174

VCC_CORE175

VCC_CORE176

VCC_CORE177

VCC_CORE178

AB8

VCC_CORE179

AB2

VCC_CORE180

L28

VCC_CORE181

NOCONA 667_7

R747

0/6

R746

0/6

Q77

MMBT2222A/SOT23

ECB

SOT23

NOCONA 667

CPU0_THERMDC_H7

CPU0_BSEL1 {33,62}

MMBT2222A/SOT23

SB_CPU0_BSEL0{8,9}

AE2

VSS95

AD3

VSS96

AE27

VSS97

AE21

VSS98

AE11

VSS99

AD31

VSS100

AD23

VSS101

AD17

VSS102

AD15

VSS103

AD9

VSS104

AC25

VSS106

AC19

VSS107

AC13

VSS108

AC7

VSS109

AC2

VSS110

AB31

VSS111

AB27

VSS112

AB21

VSS113

AB11

VSS114

AB5

VSS115

AB1

VSS116

TD1P

SC339

100P/6

TD1NCPU0_THERMDC

CLOSED TO LM93

R725

470/6

R760

470/6

TD1P {76}

TD1N {76}

P3V3

ECB

Q75

SOT23

CPU0_BSEL0 {33,62}

Q72

MMBT2222A/SOT23

SOT23

ECB

U86C

K30

K28

K26

K24

H30

H28

H26

H24

G31

G29

G27

G25

F30

F28

F25

F19

F13

E31

E29

E23

E17

E15

D30

D28

D27

D21

D11

C31

C29

C25

C19

C13

B30

B28

B23

B17

B15

A31

A29

A27

A21

A11

L31

L29

L27

L25

L23

L9

L7

L5

L3

L1

K8

K6

K4

K2

J31

J29

J27

J25

J23

J9

J7

J5

J3

J1

H8

H6

H4

H2

G9

G5

G3

G1

F7

F2

E9

D5

D2

C7

B9

B2

A5

VSS9

NOCONA 667

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

NOCONA 800

D D

C C

B B

A A

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

VSS161

VSS162

VSS163

VSS164

VSS165

VSS166

VSS167

VSS168

VSS169

VSS170

VSS171

VSS172

VSS173

VSS174

VSS175

VSS176

VSS177

VSS178

VSS179

VSS180

VSS181

VSS182

VSS183

VSS184

VSS185

VSS186

VSS187

VSS188

VSS189

VSS8

VSS7

VSS6

VSS5

VSS4

VSS3

VSS2

VSS1

AA30

AA23

AA17

AA15

AA9

AA2

Y31

Y25

Y19

Y13

Y7

Y5

Y1

W30

W28

W26

W24

W4

W2

V31

V29

V27

V25

V23

V9

V7

V5

V3

V1

U30

U28

U26

U24

U8

U6

U4

U2

T31

T29

T27

T25

T23

T9

T7

T5

T3

T1

R30

R28

R26

R24

R8

R6

R4

R2

P31

P29

P27

P25

P23

P9

P7

P5

P3

P1

N30

N28

N26

N24

N8

N6

N4

N2

M2

M4

M6

M8

M24

M26

M28

M30

K31

K29

K27

K25

K23

H31

H29

H27

H25

H23

G30

G28

G26

G24

F31

F29

F22

F16

E30

E28

E26

E20

D31

D29

D24

D18

D14

C30

C28

C22

C16

B31

B29

B26

B20

A30

A28

A24

A18

A14

L30

L26

L24

L8

L6

L4

L2

K9

K7

K5

K3

K1

J30

J28

J26

J24

J8

J6

J4

J2

H9

H7

H5

H3

H1

G8

G6

G4

G2

F4

F1

E6

E2

D8

D1

C4

C2

B6

A8

A2

U86D

VCC_CORE1

VCC_CORE2

VCC_CORE3

VCC_CORE4

VCC_CORE5

VCC_CORE6

VCC_CORE7

VCC_CORE8

VCC_CORE9

VCC_CORE10

VCC_CORE11

VCC_CORE12

VCC_CORE13

VCC_CORE14

VCC_CORE15

VCC_CORE16

VCC_CORE17

VCC_CORE18

VCC_CORE19

VCC_CORE20

VCC_CORE21

VCC_CORE22

VCC_CORE23

VCC_CORE24

VCC_CORE25

VCC_CORE26

VCC_CORE27

VCC_CORE28

VCC_CORE29

VCC_CORE30

VCC_CORE31

VCC_CORE32

VCC_CORE33

VCC_CORE34

VCC_CORE35

VCC_CORE36

VCC_CORE37

VCC_CORE38

VCC_CORE39

VCC_CORE40

VCC_CORE41

VCC_CORE42

VCC_CORE43

VCC_CORE44

VCC_CORE45

VCC_CORE46

VCC_CORE47

VCC_CORE48

VCC_CORE49

VCC_CORE50

VCC_CORE51

VCC_CORE52

VCC_CORE53

VCC_CORE54

VCC_CORE55

VCC_CORE56

VCC_CORE57

VCC_CORE58

VCC_CORE59

VCC_CORE60

VCC_CORE61

VCC_CORE62

VCC_CORE63

VCC_CORE64

VCC_CORE65

VCC_CORE66

VCC_CORE67

VCC_CORE68

VCC_CORE69

VCC_CORE70

VCC_CORE71

VCC_CORE72

VCC_CORE73

VCC_CORE74

VCC_CORE75

VCC_CORE76

VCC_CORE77

VCC_CORE78

VCC_CORE79

VCC_CORE80

NOCONA 800

NOCONA 667

VCC_CORE81

VCC_CORE82

VCC_CORE83

VCC_CORE84

VCC_CORE85

VCC_CORE86

VCC_CORE87

VCC_CORE88

VCC_CORE89

VCC_CORE90

VCC_CORE91

VCC_CORE92

VCC_CORE93

VCC_CORE94

VCC_CORE95

VCC_CORE96

VCC_CORE97

VCC_CORE98

VCC_CORE99

VCC_CORE100

VCC_CORE101

VCC_CORE102

VCC_CORE103

VCC_CORE104

VCC_CORE105

VCC_CORE106

VCC_CORE107

VCC_CORE108

VCC_CORE109

VCC_CORE110

VCC_CORE111

VCC_CORE112

VCC_CORE113

VCC_CORE114

VCC_CORE115

VCC_CORE116

VCC_CORE117

VCC_CORE118

VCC_CORE119

VCC_CORE120

VCC_CORE121

VCC_CORE122

VCC_CORE123

VCC_CORE124

VCC_CORE125

VCC_CORE126

VCC_CORE127

VCC_CORE128

VCC_CORE129

VCC_CORE130

VCC_CORE131

VCC_CORE132

VCC_CORE133

VCC_CORE134

VCC_CORE135

VCC_CORE136

VCC_CORE137

VCC_CORE138

VCC_CORE139

VCC_CORE140

VCC_CORE141

VCC_CORE142

VCC_CORE143

VCC_CORE144

VCC_CORE145

VCC_CORE146

VCC_CORE147

VCC_CORE148

VCC_CORE149

VCC_CORE150

VCC_CORE151

VCC_CORE152

VCC_CORE153

VCC_CORE154

VCC_CORE155

VCC_CORE156

VCC_CORE157

VCC_CORE158

VCC_CORE159

AA31

AA26

AA20

AA6

AA4

AA1

Y30

Y22

Y16

Y2

W31

W29

W27

W25

W1

V30

V28

V26

V24

V8

V6

V4

V2

U31

U29

U27

U25

U23

U9

U7

U5

U3

U1

T30

T28

T26

T24

T8

T6

T4

T2

R31

R29

R27

R25

R23

R9

R7

R5

R3

R1

P30

P28

P26

P24

P8

P6

P4

P2

N31

N29

N27

N25

N23

N9

N7

N5

N3

N1

M31

M29

M27

M25

M23

M9

M7

M5

M3

M1

P_VCCP0P_VCCP0

P_VCCP0

CPU0_THERMDA{8}

CPU0_THERMDC{8}

SB_CPU0_BSEL1{8,9}

CPU0_THERMDA CPU0_THERMDA_H7

P3V3

R726

470/6

MMBT2222A/SOT23

R766

470/6

ECB

Title

Size Document Number Rev

5

4

3

2

Date: Sheet

GIGA-BYTE TECHNOLOGY CO., LTD.

NOCONA 800 P0 PWR/GND

GA-9ILDTH

1

of

10 81Tuesday, June 21, 2005

1.1

5

4

3

2

1

PROCESSOR 1

SB_BPRI#{8,18}

SB_CPU1_BREQ#23{13}

SB_BREQ#0{8,9,18}

SB_BREQ#1{8,9,18}

SB_CPURST#{8,9,13,14,18}

D D

C C

B B

P_VTT

754mV

P_VTT

SB_RS#[0..2]{8,18}

SB_RSP#{8,18}

SB_CPU_A20M#{8,9,37}

SB_CPU_IGNNE#{8,9,37}

SB_CPU_INIT#{8,9,37,63}

SB_CPU_NMI{8,9,14}

SB_CPU_INTR{8,9,37}

CPU_PWR_GD{8,9,13,37}

SB_CPU1_SMI#{13,14}

SB_CPU_SLP#{8,9,37}

SB_CPU_STPCLK#{8,9}

P1_BCLK#{33}

P1_BCLK{33}

ITP_TCK0{8,13}

ITP_TDI_P1{13}

ITP_TMS_MAIN{8,13}

ITP_TRST#{8,13,17}

SB_CPU1_BSEL1{12,13}

SB_CPU1_BSEL0{12,13}

TP22

TP101

TP100

TP117

TP23

TP103

TP102

TP111

TP110

TP118

TP114

TP24

TP113

TP96

VID_CPU1_R[5..0]{70,76}

P_VCCP_A_CPU1

VR1_VCCSENSE{70}

VTTEN{8,9,62}

AGND_CPU1

VR1_VSSSENSE{70}

R748

49.9/6/1

VREF_P_VCCP_CPU1_0_R

R749

C486

84.5/6/1

1U/6/Y/10V

SR144

49.9/6/1

754mV

A A

P1 VREF

SR145

SC327

84.5/6/1

1U/6/Y/10V

MCH A0 CPU B0 800 64.9ohm 0.678V

MCH B0 CPU C1 800 49.9ohm 0.756V

5

SB_BPRI#

SB_CPU1_BREQ#23

SB_BREQ#0

SB_BREQ#1

SB_CPURST#

SB_RS#2

SB_RS#1

SB_RS#0

SB_RSP#

SB_CPU_A20M#

SB_CPU_IGNNE#

SB_CPU_INIT#

SB_CPU_NMI

SB_CPU_INTR

CPU_PWR_GD

SB_CPU1_SMI#

SB_CPU_SLP#

SB_CPU_STPCLK#

P1_BCLK#

P1_BCLK

ITP_TCK0

ITP_TDI_P1

ITP_TMS_MAIN

ITP_TRST#

SB_CPU1_BSEL1

SB_CPU1_BSEL0

VR1_VCCSENSE

VTTEN

VR1_VSSSENSE

R750

0/6

SR152

0/6

VID_CPU1_R5

VID_CPU1_R4

VID_CPU1_R3

VID_CPU1_R2

VID_CPU1_R1

VID_CPU1_R0

C487

220P/6/X/50V

SC331

220P/6/X/50V

U85A

D23

BPRI#

D10

E11

F12

D20

F21

D22

E21

F27

C26

G23

B24

AB7

C27

AE6

E24

C24

A25

F24

AB3

AA3

AE29

AE28

AE30

AD29

AD28

AC29

AB29

AB28

AA29

AA28

AE15

AC1

AE16

AD4

B27

AB4

AA5

D26 C1

NOCONA 667

BR3#

BR2#

BR1#

BR0#

Y8

RESET#

RS2#

RS1#

RS0#

C6

RSP#

A20M#

IGNNE#

D6

INIT#

LINT1_NMI

LINT0_INTR

PWRGOOD

SMI#

SLP#

D4

STPCLK#

W5

BCLK1

Y4

BCLK0

TCK

TDI

TMS

TRST#

BSEL1

BSEL0

RESERVED1

RESERVED0

RSVD16

Y3

RSVD15

RSVD14

RSVD13

RSVD12

RSVD10

RSVD9

RSVD8

RSVD7

RSVD3

RSVD2

RSVD1

A1

VID5

B3

VID4

C3

VID3

D3

VID2

E3

VID1

F3

VID0

VCCIOPLL

VCC_SENSE

E1

VTTEN

VCCA

VSSA

VSS_SENSE OPTIMIZED_COMPAT#

NOCONA 800

THERMTRIP#

PROCHOT#

BOOT_SELECT

VIDPWRGD

TEST_BUS

FORCEPR#

SLEW_CTRL

WIDE 10-12 MILS

VREF_P_VTT_CPU1_0

C488

220P/6/X/50V

WIDE 10-12 MILS

VREF_P_VTT_CPU1_3VREF_P_VCCP_CPU1_3_R

SC332

220P/6/X/50V

4

ADS#

BINIT#

BNR#

BPM5#

BPM4#

BPM3#

BPM2#

BPM1#

BPM0#

DBSY#

DEFER#

DRDY#

HIT#

HITM#

TRDY#

LOCK#

MCERR#

IERR#

FERR#

TDO

GTLREF3

GTLREF2

GTLREF1

GTLREF0

ODTEN

SKTOCC#

COMP3

COMP2

COMP1

COMP0

TESTHI8

TESTHI7

TESTHI6

TESTHI5

TESTHI4

TESTHI3

TESTHI2

TESTHI1

TESTHI0

SMB_PRT

VCCPLL

THERMDC

THERMDA

RSVD

SB_ADS#

D19

SB_BINIT#

F11

SB_BNR#

F20

CPU1_BPM#5

E4

CPU1_BPM#4

E8

CPU1_BPM#3

F5

CPU1_BPM#2

E7

CPU1_BPM#1

F8

CPU1_BPM#0

F6

SB_DBSY#

F18

SB_DEFER#

C23

SB_DRDY#

E18

SB_HIT#

E22

SB_HITM#

A23

SB_TRDY#

E19

SB_LOCK#

A17

SB_MCERR#

D7

SB_CPU1_IERR#

E5

SB_CPU_FERR#

E27

SB_CPU_THERMTRIP#

F26

SB_CPU1_PROCHOT#

B25

ITP_TDO_MAIN

E25

F9

F23

W9

W23

PD_ODTEN_CPU1

B5

SMC_CPU1_SKTOCC#

A3

PD_COMP3_CPU1

AC28

PD_COMP2_CPU1

D25

PD_COMP1_CPU1

E16

PD_COMP0_CPU1

AD16

PU_CPU1_8

Y29

PU_CPU1_0

A26

PU_CPU0_5

AE5

PU_CPU1_6

AD5

PU_CPU1_1

AA7

PU_CPU1_7

Y6

PU_CPU1_3

W8

PU_CPU1_2

W7

PU_CPU1_4

W6

AE4

AD1

CPU1_THERMDC

Y28

CPU1_THERMDA

Y27

PU_BOOT_SELECT_CPU1

G7

W3

VID_PWRGD

B1

SB_CPU0_CPU1_TESTBUS

A16

SB_CPU_FORCEPR#

A15

SLEW_CTRL_CPU1

AC30

CPU1_OPTIM_COMPAT_CTRL

COMP3 =SB_CPU1_ADDR_ERC

COMP2 =SB_CPU1_DATA_ERC

PU_CPU1_8=SB_CPU1_EDRDY

PU_CPU1_0=SB_CPU1_SNPD#

WW35 eMOW: Icc of VCCIOPLL pins : 100 mA

WW35 eMOW: Icc for VCCA pins : 120mA

P_VTT

SL1

10UH/8

SL2

10UH/8

P1V5

SB_ADS# {8,18}

SB_BINIT# {8,9,18}

SB_BNR# {8,9,18}

CPU1_BPM#[5..0] {13}

SB_DBSY# {8,18}

SB_DEFER# {8,18}

SB_DRDY# {8,18}

SB_HIT# {8,9,18}

SB_HITM# {8,9,18}

SB_TRDY# {8,18}

SB_LOCK# {8,18}

SB_MCERR# {8,9,18}

SB_CPU1_IERR# {13,14}

SB_CPU_FERR# {8,9,37}

SB_CPU1_THERMTRIP# {9,14}

SB_CPU1_PROCHOT# {13,14}

ITP_TDO_P1 {13}

PD_ODTEN_CPU1 {9}

SMC_CPU1_SKTOCC# {13,62,77}

PD_COMP3_CPU1 {13}

PD_COMP2_CPU1 {13}

PD_COMP1_CPU1 {13}

PD_COMP0_CPU1 {13}

PU_CPU1_8 {13}

PU_CPU1_0 {13}

PU_CPU1_5 {13}

PU_CPU1_6 {13}

PU_CPU1_1 {13}

PU_CPU1_7 {13}

PU_CPU1_3 {13}

PU_CPU1_2 {13}

PU_CPU1_4 {13}

TP86

CPU1_THERMDC {12}

CPU1_THERMDA {12}

PU_BOOT_SELECT_CPU1 {13}

TP124

VID_PWRGD {8,62}

SB_CPU0_CPU1_TESTBUS {8,9}

SB_CPU_FORCEPR# {8,9,14}

SLEW_CTRL_CPU1 {9}

CPU1_OPTIM_COMPAT_CTRL {13}

SR167

0/6/X

12

+

SEC2

470U/4V/7343/X

WIDE 10-12 MILS

P_VCCP_A_CPU1

12

SC473

22U/12/Y/10V

AGND_CPU1

WIDE 10-12 MILS

PU_VCCPLL_CPU1

12

SC438

4.7U/1206/X

3

SB_D#[63..0]{8,18}

VREF_P_VTT_CPU1_3

VREF_P_VTT_CPU1_0

PU_VCCPLL_CPU1

NO USE

SC446

SC439

0.1U/6/X

0.1U/6/X

SB_D#63

SB_D#62

SB_D#61

SB_D#60

SB_D#59

SB_D#58

SB_D#57

SB_D#56

SB_D#55

SB_D#54

SB_D#53

SB_D#52

SB_D#51

SB_D#50

SB_D#49

SB_D#48

SB_D#47

SB_D#46

SB_D#45

SB_D#44

SB_D#43

SB_D#42

SB_D#41

SB_D#40

SB_D#39

SB_D#38

SB_D#37

SB_D#36

SB_D#35

SB_D#34

SB_D#33

SB_D#32

SB_D#31

SB_D#30

SB_D#29

SB_D#28

SB_D#27

SB_D#26

SB_D#25

SB_D#24

SB_D#23

SB_D#22

SB_D#21

SB_D#20

SB_D#19

SB_D#18

SB_D#17

SB_D#16

SB_D#15

SB_D#14

SB_D#13

SB_D#12

SB_D#11

SB_D#10

SB_D#9

SB_D#8

SB_D#7

SB_D#6

SB_D#5

SB_D#4

SB_D#3

SB_D#2

SB_D#1

SB_D#0

AB6

Y9

AA8

AC5

AC6

AE7

AD7

AC8

AB10

AA10

AA11

AB13

AB12

AC14

AA14

AA13

AC9

AD8

AD10

AE9

AC11

AE10

AC12

AD11

AD14

AD13

AB15

AD18

AE13

AC17

AA16

AB16

AB17

AD19

AD21

AE20

AE22

AC21

AC20

AA18

AC23

AE23

AD24

AC24

AE25

AD25

AC26

AE26

AA19

AB19

AB22

AB20

AA21

AA22

AB23

AB25

AB26

AA24

Y23

AD27

AA25

Y24

AA27

Y26

12

SC449

22U/12/Y/10V

2

U85B

D63

NOCONA 667

D62

D61

D60

D59

D58

D57

D56

D55

D54

D53

D52

D51

D50

D49

D48

D47

D46

D45

D44

D43

D42

D41

D40

D39

D38

D37

D36

D35

D34

D33

D32

D31

D30

D29

D28

D27

D26

D25

D24

D23

D22

D21

D20

D19

D18

D17

D16

D15

D14

D13

D12

D11

D10

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

NOCONA 800

P_VTT

12

SC570

22U/12/Y/10V

SB_HA#[35..3] {8,18}

SB_REQ#[4..0] {8,18}

SB_DBI#[3..0] {8,18}

SB_DP#[3..0] {8,18}

SB_AP#[1..0] {8,18}

SB_ADSTB#[1..0] {8,18}

SB_DSTBP#[3..0] {8,18}

SB_DSTBN#[3..0] {8,18}

BREQ4#

BREQ3#

BREQ2#

BREQ1#

BREQ0#

ADSTB1#

ADSTB0#

DSTBP3#

DSTBP2#

DSTBP1#

DSTBP0#

DSTBN3#

DSTBN2#

DSTBN1#

DSTBN0#

SC568

1U/6/Y/10V

A35

A34

A33

A32

A31

A30

A29

A28

A27

A26

A25

A24

A23

A22

A21

A20

A19

A18

A17

A16

A15

A14

A13

A12

A11

A10

A9

A8

A7

A6

A5

A4

A3

DBI3#

DBI2#

DBI1#

DBI0#

DP3#

DP2#

DP1#

DP0#

AP1#

AP0#

SC445

0.1U/6/X/16V

SB_HA#35

C8

SB_HA#34

C9

SB_HA#33

A7

SB_HA#32

A6

SB_HA#31

B7

SB_HA#30

C11

SB_HA#29

D12

SB_HA#28

E13

SB_HA#27

B8

SB_HA#26

A9

SB_HA#25

D13

SB_HA#24

E14

SB_HA#23

C12

SB_HA#22

B11

SB_HA#21

B10

SB_HA#20

A10

SB_HA#19

F15

SB_HA#18

D15

SB_HA#17

D16

SB_HA#16

C14

SB_HA#15

C15

SB_HA#14

A12

SB_HA#13

B13

SB_HA#12

B14

SB_HA#11

B16

SB_HA#10

A13

SB_HA#9

D17

SB_HA#8

C17

SB_HA#7

A19

SB_HA#6

C18

SB_HA#5

B18

SB_HA#4

A20

SB_HA#3

A22

SB_REQ#4

B22

SB_REQ#3

C20

SB_REQ#2

C21

SB_REQ#1

B21

SB_REQ#0

B19

SB_DBI#3

AB9

SB_DBI#2

AE12

SB_DBI#1

AD22

SB_DBI#0

AC27

SB_DP#3

AE17

SB_DP#2

AC15

SB_DP#1

AE19

SB_DP#0

AC18

SB_AP#1

D9

SB_AP#0

E10

SB_ADSTB#1

F14

SB_ADSTB#0

F17

SB_DSTBP#3

Y11

SB_DSTBP#2

Y14

SB_DSTBP#1

Y17

SB_DSTBP#0

Y20

SB_DSTBN#3

Y12

SB_DSTBN#2

Y15

SB_DSTBN#1

Y18

SB_DSTBN#0

Y21

EC27

PSA2.5VB820MH11/8X11.5

Trace Width:12 Mils

VREF_P_VTT_CPU1_0

VREF_P_VTT_CPU1_3

VCCIOPLL_CPU1

AGND_CPU1

PU_VCCPLL_CPU1

Title

Size Document Number Rev

Date: Sheet

GIGA-BYTE TECHNOLOGY CO., LTD.

NOCONA 800 MICS P1

GA-9ILDTH

1

1.1

of

11 81Tuesday, June 21, 2005

5

D D

C C

B B

A A

H30

H28

H26

H24

G31

G29

G27

G25

F30

F28

F25

F19

F13

E31

E29

E23

E17

E15

D30

D28

D27

D21

D11

C31

C29

C25

C19

C13

B30

B28

B23

B17

B15

A31

A29

A27

A21

A11

L31

L29

L27

L25

L23

L9

L7

L5

L3

L1

K30

K28

K26

K24

K8

K6

K4

K2

J31

J29

J27

J25

J23

J9

J7

J5

J3

J1

H8

H6

H4

H2

G9

G5

G3

G1

F7

F2

E9

D5

D2

C7

B9

B2

A5

U85C

VSS9

NOCONA 667

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

NOCONA 800

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

VSS161

VSS162

VSS163

VSS164

VSS165

VSS166

VSS167

VSS168

VSS169

VSS170

VSS171

VSS172

VSS173

VSS174

VSS175

VSS176

VSS177

VSS178

VSS179

VSS180

VSS181

VSS182

VSS183

VSS184

VSS185

VSS186

VSS187

VSS188

VSS189

VSS8

VSS7

VSS6

VSS5

VSS4

VSS3

VSS2

VSS1

AA30

AA23

AA17

AA15

AA9

AA2

Y31

Y25

Y19

Y13

Y7

Y5

Y1

W30

W28

W26

W24

W4

W2

V31

V29

V27

V25

V23

V9

V7

V5

V3

V1

U30

U28

U26

U24

U8

U6

U4

U2

T31

T29

T27

T25

T23

T9

T7

T5

T3

T1

R30

R28

R26

R24

R8

R6

R4

R2

P31

P29

P27

P25

P23

P9

P7

P5

P3

P1

N30

N28

N26

N24

N8

N6

N4

N2

M2

M4

M6

M8

M24

M26

M28

M30

4

P_VCCP1

G30

G28

G26

G24

E30

E28

E26

E20

D31

D29

D24

D18

D14

C30

C28

C22

C16

B31

B29

B26

B20

A30

A28

A24

A18

A14

L30

L26

L24

L8

L6

L4

L2

K31

K29

K27

K25

K23

K9

K7

K5

K3

K1

J30

J28

J26

J24

J8

J6

J4

J2

H31

H29

H27

H25

H23

H9

H7

H5

H3

H1

G8

G6

G4

G2

F31

F29

F22

F16

F4

F1

E6

E2

D8

D1

C4

C2

B6

A8

A2

U85D

VCC_CORE1

VCC_CORE2

VCC_CORE3

VCC_CORE4

VCC_CORE5

VCC_CORE6

VCC_CORE7

VCC_CORE8

VCC_CORE9

VCC_CORE10

VCC_CORE11

VCC_CORE12

VCC_CORE13

VCC_CORE14

VCC_CORE15

VCC_CORE16

VCC_CORE17

VCC_CORE18

VCC_CORE19

VCC_CORE20

VCC_CORE21

VCC_CORE22

VCC_CORE23

VCC_CORE24

VCC_CORE25

VCC_CORE26

VCC_CORE27

VCC_CORE28

VCC_CORE29

VCC_CORE30

VCC_CORE31

VCC_CORE32

VCC_CORE33

VCC_CORE34

VCC_CORE35

VCC_CORE36

VCC_CORE37

VCC_CORE38

VCC_CORE39

VCC_CORE40

VCC_CORE41

VCC_CORE42

VCC_CORE43

VCC_CORE44

VCC_CORE45

VCC_CORE46

VCC_CORE47

VCC_CORE48

VCC_CORE49

VCC_CORE50

VCC_CORE51

VCC_CORE52

VCC_CORE53

VCC_CORE54

VCC_CORE55

VCC_CORE56

VCC_CORE57

VCC_CORE58

VCC_CORE59

VCC_CORE60

VCC_CORE61

VCC_CORE62

VCC_CORE63

VCC_CORE64

VCC_CORE65

VCC_CORE66

VCC_CORE67

VCC_CORE68

VCC_CORE69

VCC_CORE70

VCC_CORE71

VCC_CORE72

VCC_CORE73

VCC_CORE74

VCC_CORE75

VCC_CORE76

VCC_CORE77

VCC_CORE78

VCC_CORE79

VCC_CORE80

NOCONA 800

NOCONA 667

VCC_CORE81

VCC_CORE82

VCC_CORE83

VCC_CORE84

VCC_CORE85

VCC_CORE86

VCC_CORE87

VCC_CORE88

VCC_CORE89

VCC_CORE90

VCC_CORE91

VCC_CORE92

VCC_CORE93

VCC_CORE94

VCC_CORE95

VCC_CORE96

VCC_CORE97

VCC_CORE98

VCC_CORE99

VCC_CORE100

VCC_CORE101

VCC_CORE102

VCC_CORE103

VCC_CORE104

VCC_CORE105

VCC_CORE106

VCC_CORE107

VCC_CORE108

VCC_CORE109

VCC_CORE110

VCC_CORE111

VCC_CORE112

VCC_CORE113

VCC_CORE114

VCC_CORE115

VCC_CORE116

VCC_CORE117

VCC_CORE118

VCC_CORE119

VCC_CORE120

VCC_CORE121

VCC_CORE122

VCC_CORE123

VCC_CORE124

VCC_CORE125

VCC_CORE126

VCC_CORE127

VCC_CORE128

VCC_CORE129

VCC_CORE130

VCC_CORE131

VCC_CORE132

VCC_CORE133

VCC_CORE134

VCC_CORE135

VCC_CORE136

VCC_CORE137

VCC_CORE138

VCC_CORE139

VCC_CORE140

VCC_CORE141

VCC_CORE142

VCC_CORE143

VCC_CORE144

VCC_CORE145

VCC_CORE146

VCC_CORE147

VCC_CORE148

VCC_CORE149

VCC_CORE150

VCC_CORE151

VCC_CORE152

VCC_CORE153

VCC_CORE154

VCC_CORE155

VCC_CORE156

VCC_CORE157

VCC_CORE158

VCC_CORE159

AA31

AA26

AA20

AA6

AA4

AA1

Y30

Y22

Y16

Y2

W31

W29

W27

W25

W1

V30

V28

V26

V24

V8

V6

V4

V2

U31

U29

U27

U25

U23

U9

U7

U5

U3

U1

T30

T28

T26

T24

T8

T6

T4

T2

R31

R29

R27

R25

R23

R9

R7

R5

R3

R1

P30

P28

P26

P24

P8

P6

P4

P2

N31

N29

N27

N25

N23

N9

N7

N5

N3

N1

M31

M29

M27

M25

M23

M9

M7

M5

M3

M1

3

P_VCCP1

2

P_VTT

U85E

AD12

VCC_VTT1

AC10

AA12

Y10

F10

E12

C10

B12

B4

C5

SR157

470/6

P3V3

A4

AE24

AE18

AE14

AE8

AE3

AD30

AD26

AD20

AD6

AD2

AC31

AC22

AC16

AC4

AC3

AB30

AB24

AB18

AB14

AB8

AB2

L28

R740

0/6

R739

0/6

SQ28

SOT23

ECB

P_VCCP1

CPU1_THERMDA{11}

SB_CPU1_BSEL1{11,13}

CPU1_THERMDA

CPU1_THERMDC TD2N

MMBT2222A/SOT23

SR176

470/6

NOCONA 667

VCC_VTT2

VCC_VTT3

VCC_VTT4

VCC_VTT5

VCC_VTT6

VCC_VTT7

VCC_VTT8

VCC_VTT9

VCC_VTT10

VCC_VTT11

VCC_CORE160

VCC_CORE161

VCC_CORE162

VCC_CORE163

VCC_CORE164

VCC_CORE165

VCC_CORE166

VCC_CORE167

VCC_CORE168

VCC_CORE169

VCC_CORE170

VCC_CORE171

VCC_CORE172

VCC_CORE173

VCC_CORE174

VCC_CORE175

VCC_CORE176

VCC_CORE177

VCC_CORE178

VCC_CORE179

VCC_CORE180

VCC_CORE181

NOCONA 667_7

CPU1_THERMDA_H7 TD2P

CPU1_THERMDC_H7

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

CLOSED TO LM93

CPU1_BSEL1 {62}

SQ29

MMBT2222A/SOT23

SOT23

ECB

SB_CPU1_BSEL0{11,13}

MMBT2222A/SOT23

SR179

470/6

AE2

AD3

AE27

AE21

AE11

AD31

AD23

AD17

AD15

AD9

AC25

AC19

AC13

AC7

AC2

AB31

AB27

AB21

AB11

AB5

AB1

SC345

100P/6

SR162

470/6

1

TD2P {76}

TD2N {76}CPU1_THERMDC{11}

P3V3

SQ30

SOT23

ECB

CPU1_BSEL0 {62}

SQ31

MMBT2222A/SOT23

SOT23

ECB

Title

Size Document Number Rev

5

4

3

2

Date: Sheet

GIGA-BYTE TECHNOLOGY CO., LTD.

NOCONA 800 P1 PWR/GND

GA-9ILDTH

1

of

12 81Tuesday, June 21, 2005

1.1

P_VTT

5

4

P_VTT

3

2

1

R936 220/6

R925 51/6

D D

R963 51/6

R961 51/6/X

R948 51/6/X

R964 51/6

C C

SR175 510/6

SR178 510/6

R741 100/6/1

R962 100/6/1

SR185 49.9/6/1

B B

R767 49.9/6/1

A A

SB_CPU1_SMI#

SB_CPU1_IERR#

SB_CPU1_PROCHOT#

PU_BOOT_SELECT_CPU1

CPU1_OPTIM_COMPAT_CTRL

R960 51/6/X

SB_CPU1_BREQ#23

SB_CPU1_BSEL1

SB_CPU1_BSEL0

PD_COMP3_CPU1

PD_COMP2_CPU1

PD_COMP1_CPU1

PD_COMP0_CPU1

CPU_PWR_GD{8,9,11,37}

I2C_BUS2_SDA{17,23,49,73}

I2C_BUS2_SCL{17,23,49,73}

ITP_TCK1{17}

ITP_TCK0{8,11}

5

SB_CPU1_SMI# {11,14}

SB_CPU1_IERR# {11,14}

SB_CPU1_PROCHOT# {11,14}

PU_BOOT_SELECT_CPU1 {11}

CPU1_OPTIM_COMPAT_CTRL {11}

SB_CPU1_BREQ#23 {11}

SB_CPU1_BSEL1 {11,12}

SB_CPU1_BSEL0 {11,12}

PD_COMP3_CPU1 {11}

PD_COMP2_CPU1 {11}

PD_COMP1_CPU1 {11}

PD_COMP0_CPU1 {11}

CPU_PWR_GD

R938 0/6

MCH_PME#{18,36}

R950 0/6/X R1026 0/6

R971 0/6/X

R984 51/6

R982 51/6

P_VTT

R738 51/6

R754 51/6

R757 51/6

R756 51/6

R755 51/6

R751 51/6

R753 51/6

R752 51/6

R947 51/6

P3V3_STBY

R959 4.7K/6

CPU_PWR_GD

C480

100P/6/X

CPU0_BPM#5

CPU0_BPM#4

CPU0_BPM#3

CPU0_BPM#2

CPU0_BPM#1

CPU0_BPM#0

CPU1_BPM#5

CPU1_BPM#4

CPU1_BPM#3

CPU1_BPM#2

CPU1_BPM#1

CPU1_BPM#0

ITP_CPU_PWRGOOD

MCH_PME# SB_CPURST#_R

ITP_SMBDAT

ITP_SMBCLK

ITP_TCK1

ITP_TCK0

4

11

13

15

17

19

21

23

25

27

29

31

33

35

37

39

41

43

45

47

49

51

53

55

57

59

PU_CPU1_8

PU_CPU1_7

PU_CPU1_6

PU_CPU1_5

PU_CPU1_4

PU_CPU1_3

PU_CPU1_2

PU_CPU1_1

PU_CPU1_0

SMC_CPU1_SKTOCC#

CPU_PWR_GD {8,9,11,37}

ITP

1

3

5

7

9

ITP/X

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

54

56

58

60

P1V5

PU_CPU1_8 {11}

PU_CPU1_7 {11}

PU_CPU1_6 {11}

PU_CPU1_5 {11}

PU_CPU1_4 {11}

PU_CPU1_3 {11}

PU_CPU1_2 {11}

PU_CPU1_1 {11}

PU_CPU1_0 {11}

SMC_CPU1_SKTOCC# {11,62,77}

ITP_MCH_DEBUG0

ITP_MCH_DEBUG1

ITP_MCH_DEBUG2

ITP_MCH_DEBUG3

ITP_MCH_DEBUG4

ITP_MCH_DEBUG5

ITP_MCH_DEBUG6

ITP_MCH_DEBUG7

ITP_BCLK

ITP_BCLK#

DBR_RESET#

ITP_TDO_MAIN

ITP_TRST#

ITP_TDI_MAIN

ITP_TMS_MAIN

R1024

1K/6

ITP_TMS_MAIN{8,11} ITP_TMS_MCH {17}

ITP_TDI_MAIN{8}

MODE TEST PROCESSOR CONFIGURATION

UP 2-3 P0 INSTALLED;P1 REMOVED

DP 1-2 & 3-4 P0 & P1 INSTALLED

ITP_MCH_DEBUG[7..0]

ITP_MCH_DEBUG[7..0] {17}

PLACE WITHIN 1" OF CPU

P_VTT

R1012

51/6

ITP_TDI_P1

ITP_TDO_P0

ITP_TDO_P1

R908

51/6

ITP_TDI_MAIN {8}

ITP_TDI_P1 {11}

ITP_TDO_P0 {8}

ITP_TDO_P1 {11}

ITP_BCLK {33}

ITP_BCLK# {33}

ITP_TRST# {8,11,17}

ITP_TMS_MAIN {8,11}

3

TP31

TP135

TP137

TP136

R1025