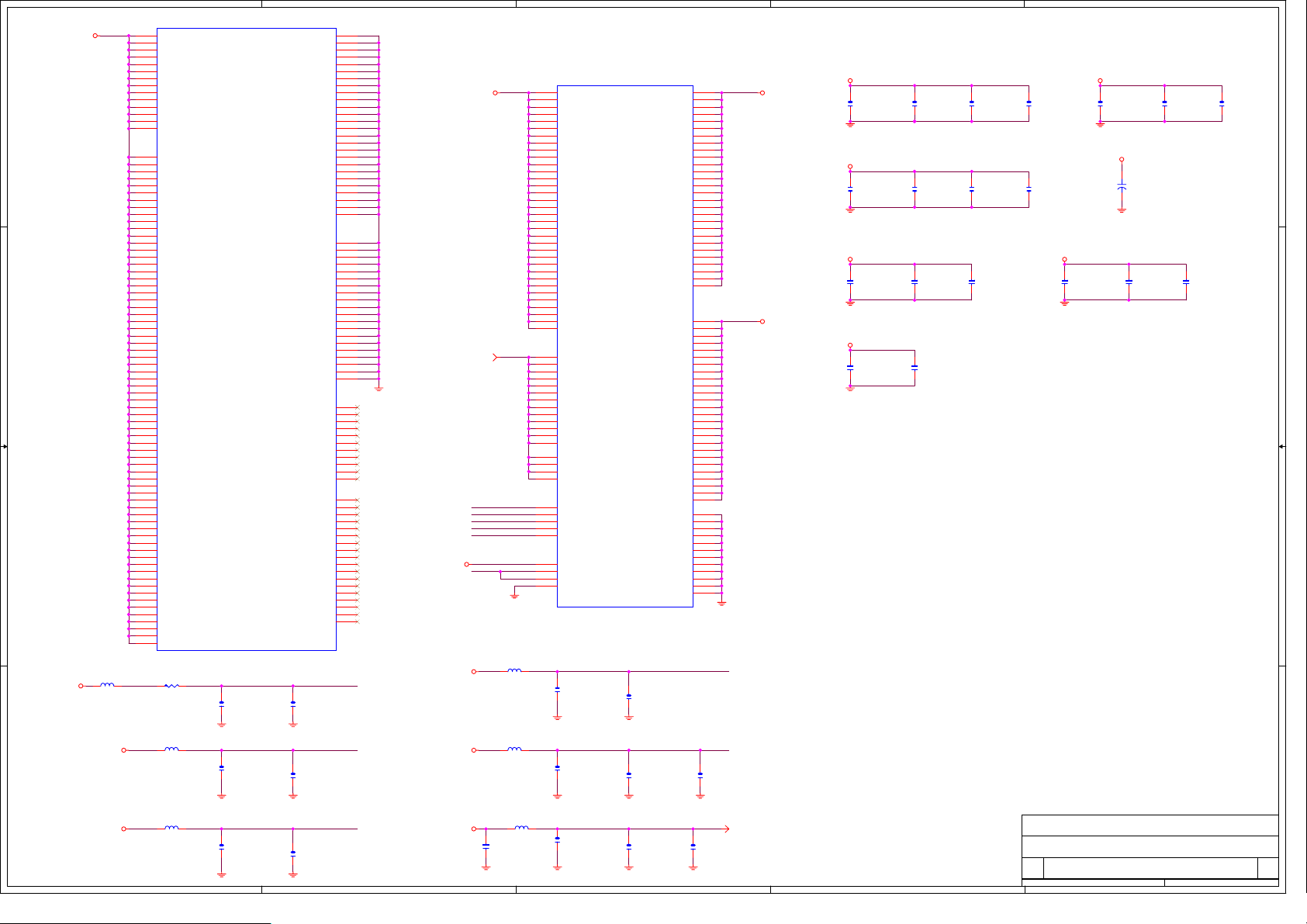

Gigabyte GA-8i915g-yfd REV.1.0 Schematics

5

Model Name: 8I915G-YFD

4

3

2

1

D D

SHEET TITLE

01

02

03

04

05

06

C C

07

08

09

10

11

12

13

COVER SHEET

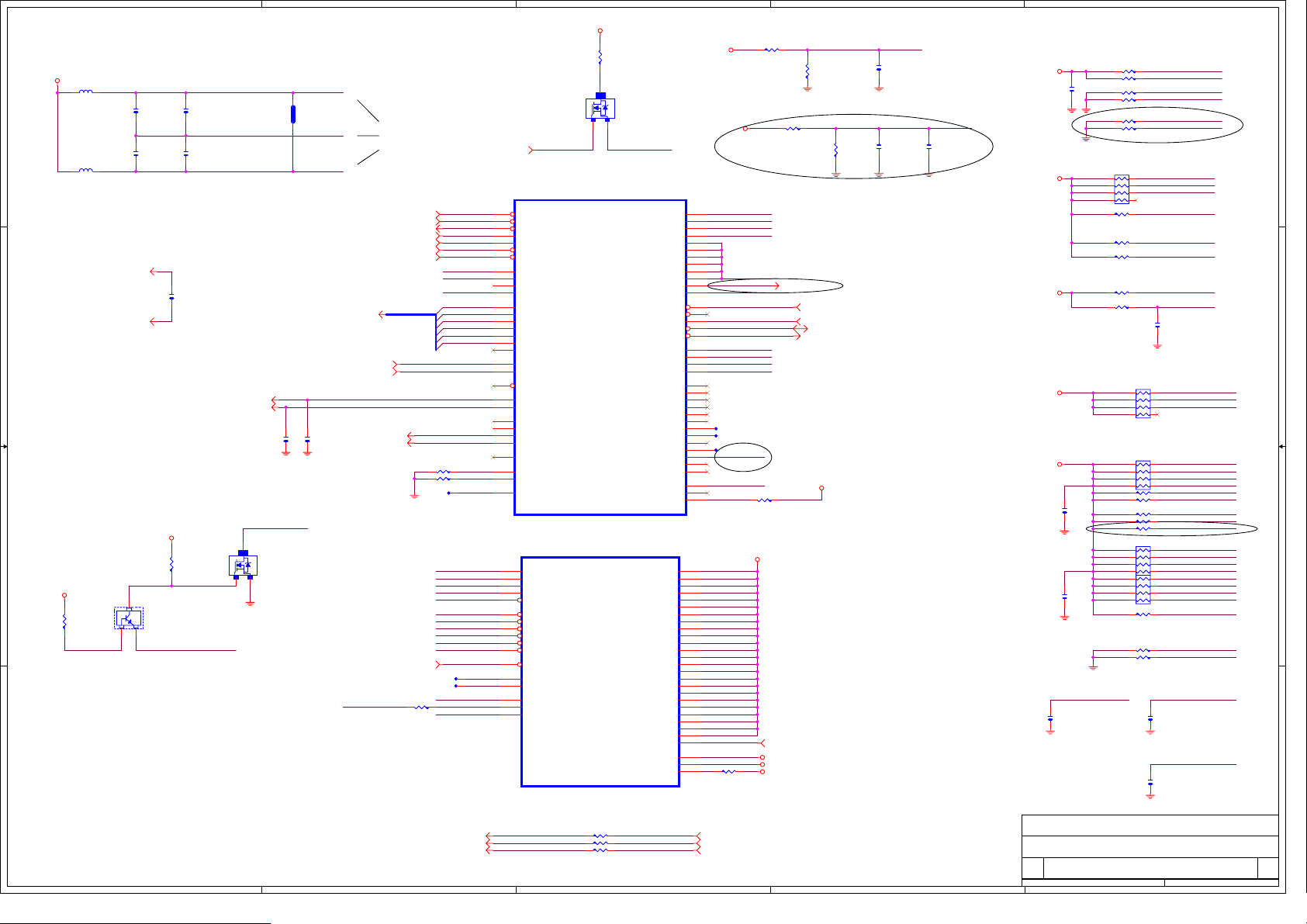

BLOCK DIAGRAM

BOM & PCB MODIFY HISTORY

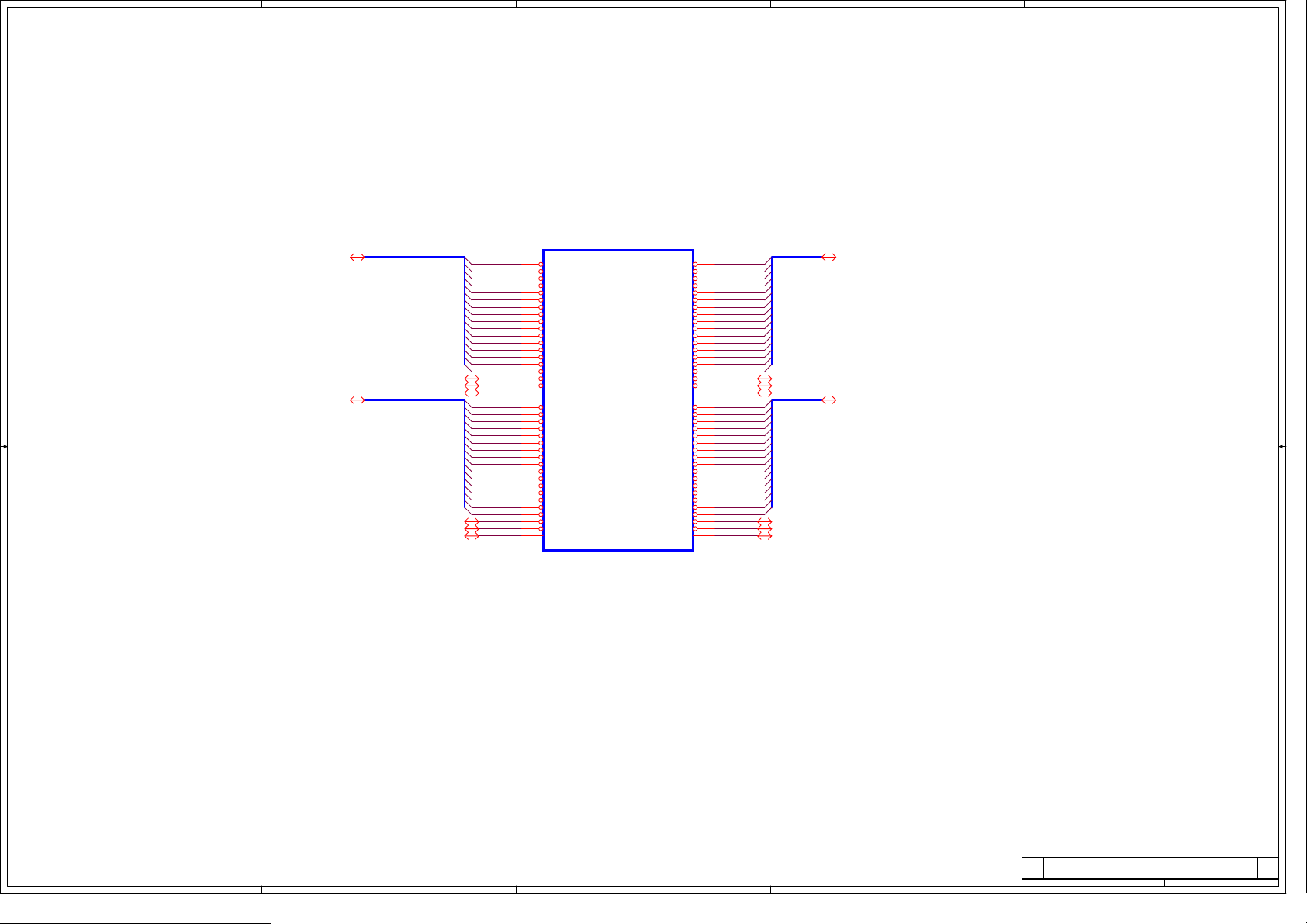

P4_LGA775_A

P4_LGA775_B

P4_LGA775_C

P4_LGA775_D

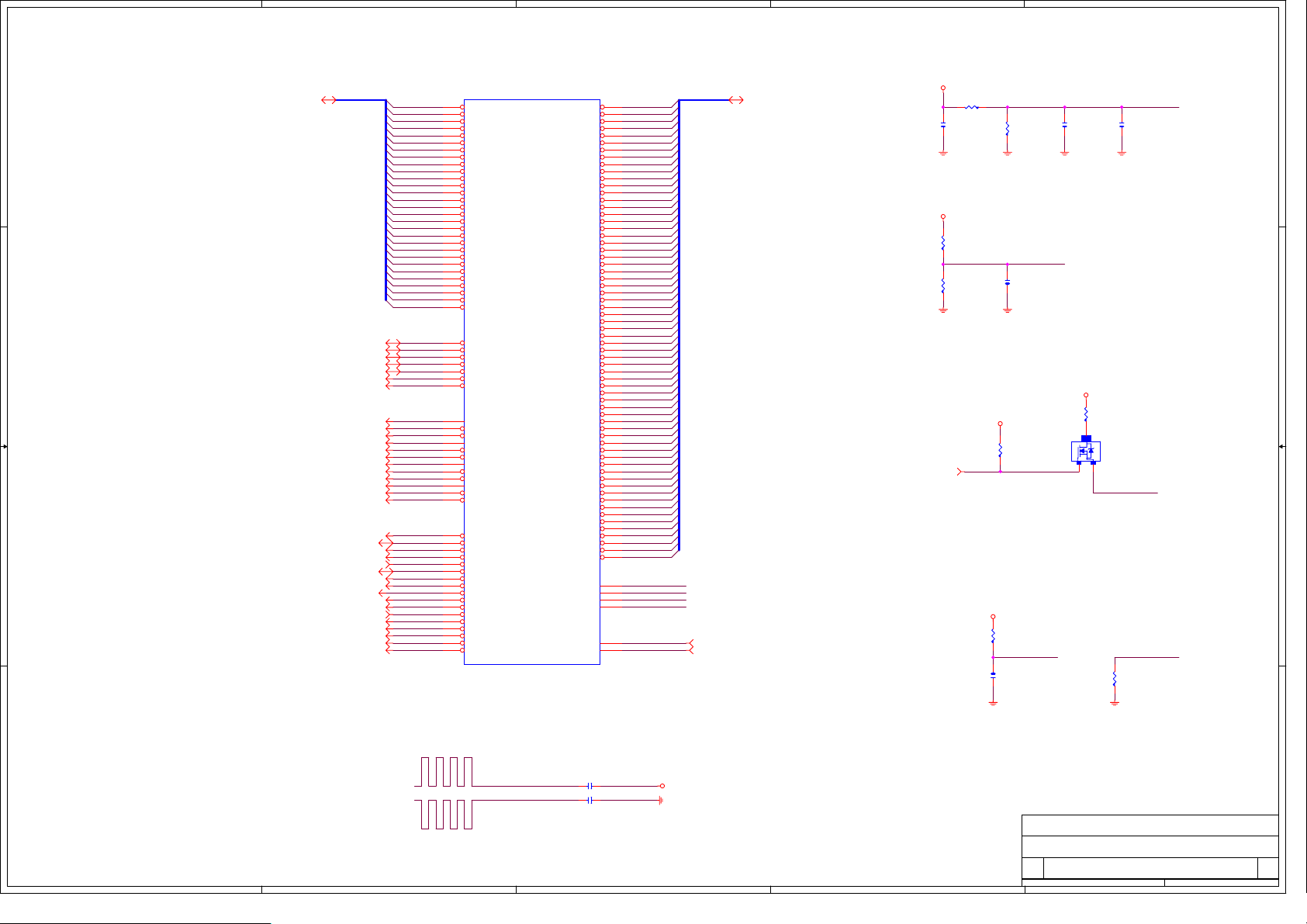

GMCH-GRANTSDALE_HOST

GMCH-GARNTSDALE_DDR

GMCH-GRANTSDALE_PCI E, DMI

GMCH-GRANTSDALE_INT VGA

GMCH-GRANTSDALE_GND

GMCH-GRANTSDALE_PWR

Revision 1.0

SHEET TITLE

23

24

25

26

27

28

29

30

31

32

33

34

35

PCI EXPRESS*1 SLOT 1

PCI SLOT 1, 2

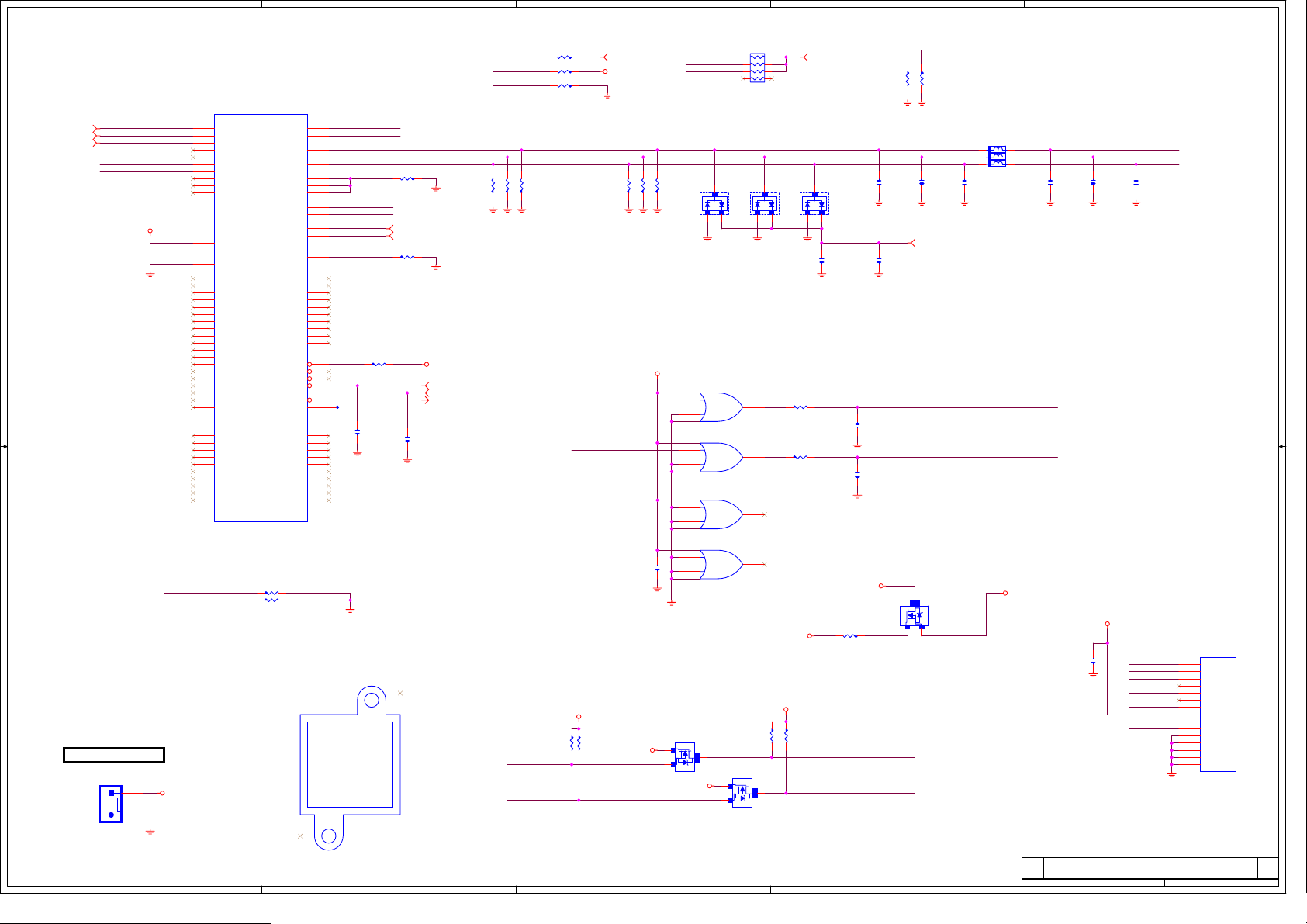

HWMO&PROCHOT

IDE&FDD

KB_MS&GAME PORT

FRONT PANEL

USBFRONT CONNECTOR

CPU_FAN & SYS_FAN

CODEC

AUDIO JACK

F_AUDIO

LAN

ALL POWER

B B

14

15

16

17

18

19

20

21

A A

22

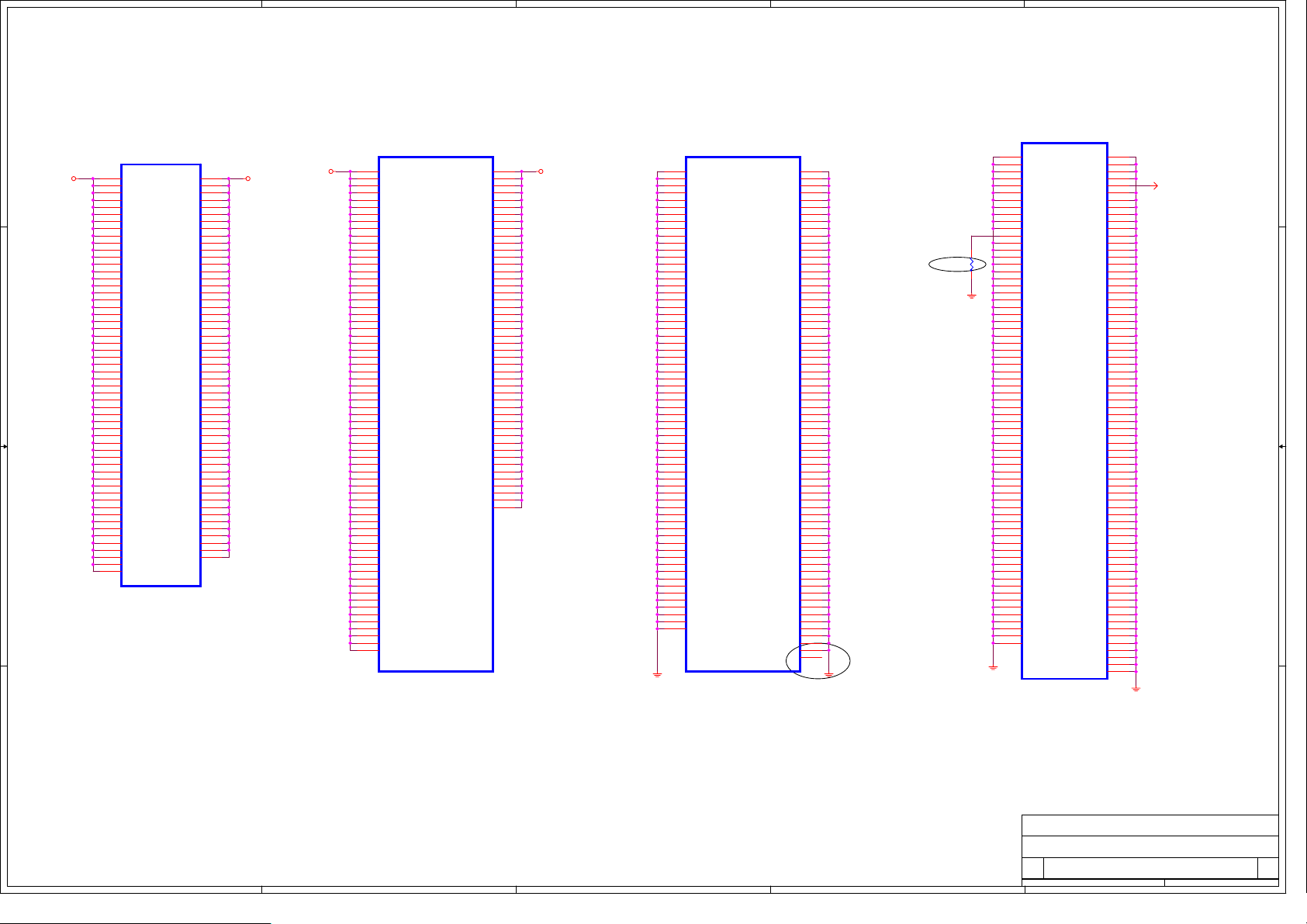

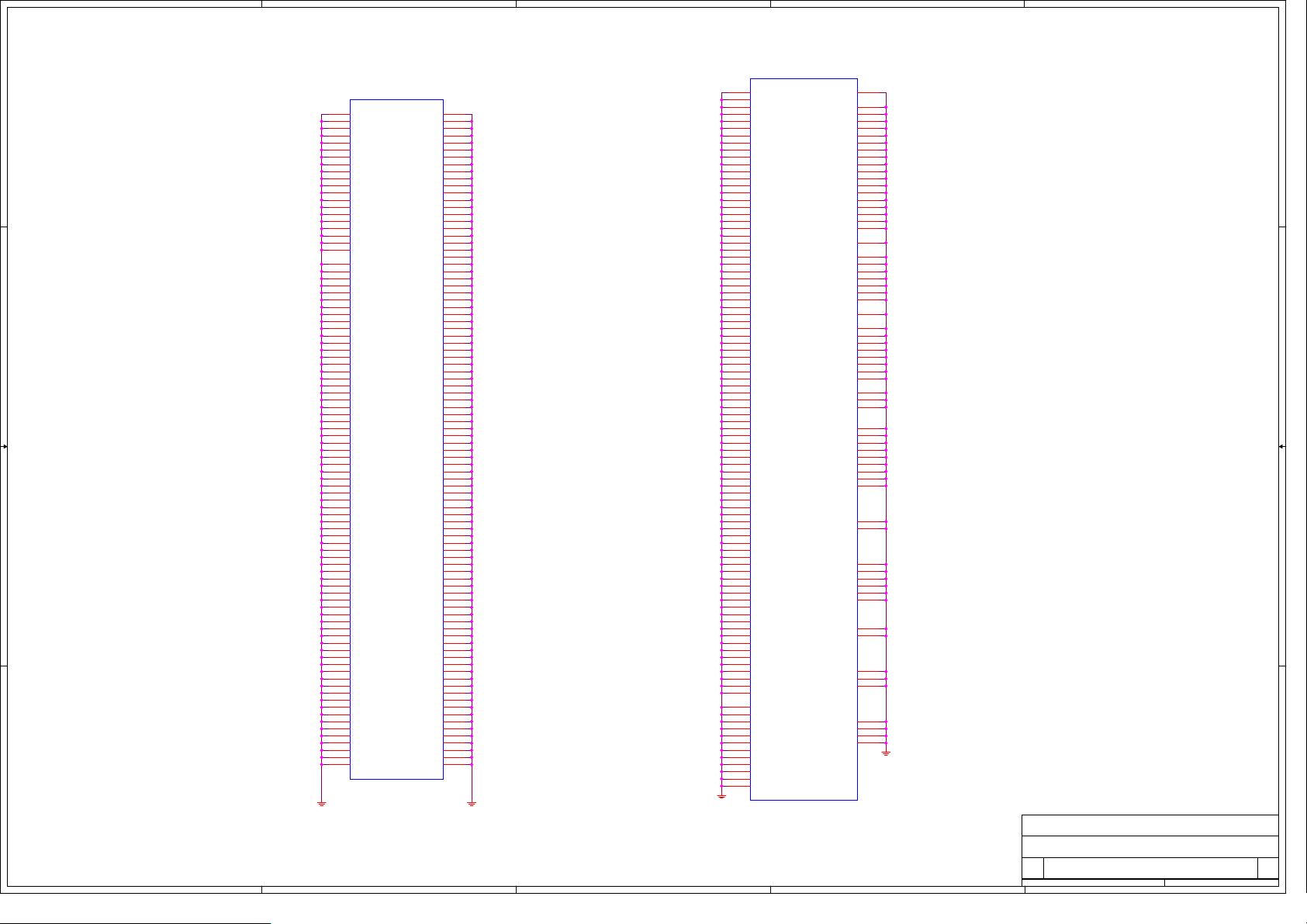

DDRI CHANNEL A

DDRI CHANNEL B

DDR TERMINATION

PCI EXPRESS*16 SLOT

ICH6 PCI, USB, DMI, LAN

ICH6 IDE, GPIO, SATA, CTRL

ICH6 VCC, GND

FWH

CK410M CLOCK.

5

4

3

36

37

38

39

40

ITE8712

COM & LPT

1394

VCORE POWER

ATX POWER CONN.

41 GPIO & RESET TABLE

& IR

2

COMPONENT SIDE

(1 oz. Copper)

VCC SIDE

(1 oz. Copper)

GND SIDE

(1 oz. Copper)

SOLDER SIDE

(1 oz. Copper)

GIGABYTE

Title

Size Document Number Rev

Custom

Date: Sheet

Cover Sheet

8I915G-YFD

1

of

142Wednesday, November 17, 2004

1.0

5

4

3

2

1

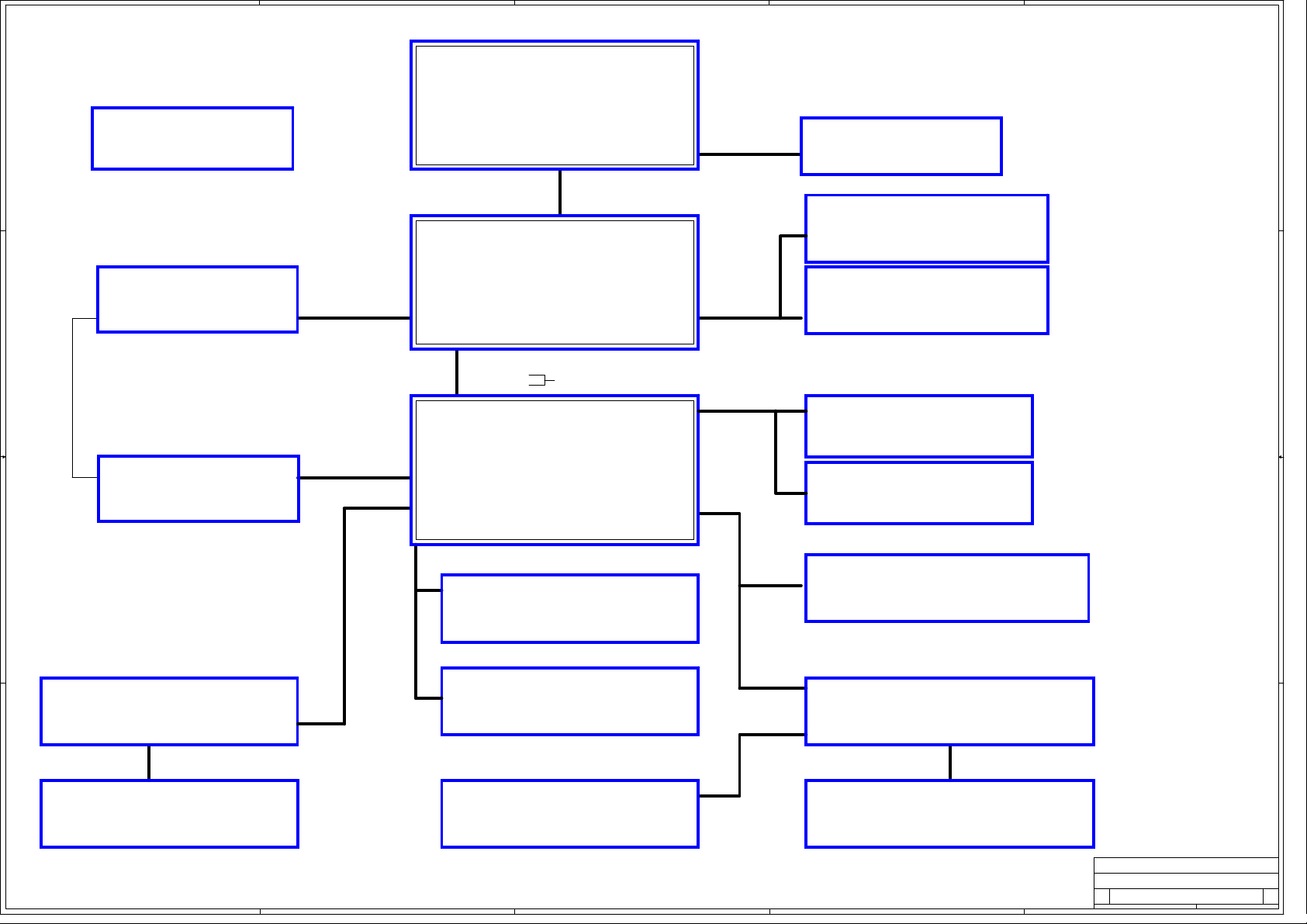

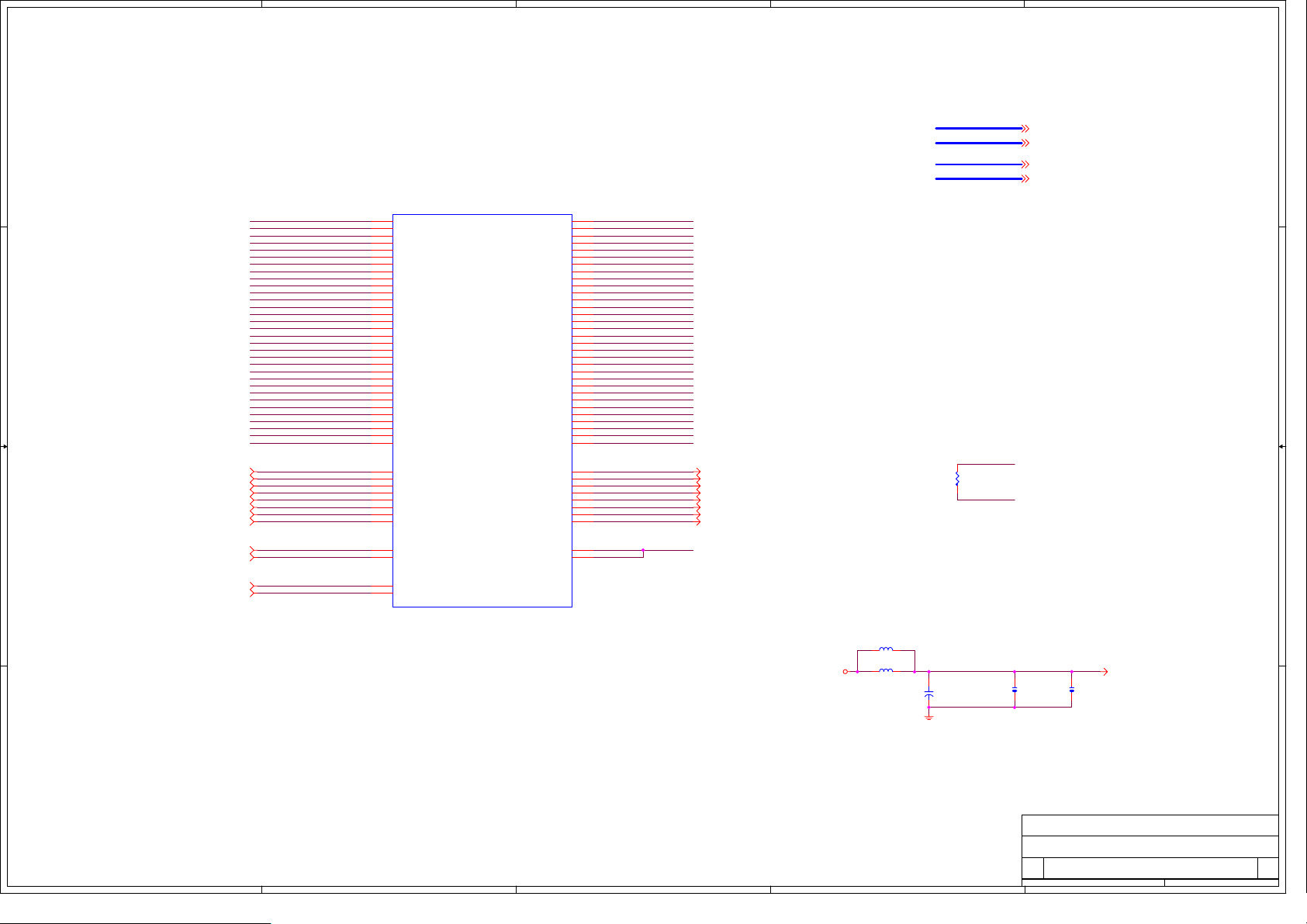

BLOCK DIAGRAM

INTEL Pentium4

LGA775

D D

CLOCK GENERATOR

CKVDD = 3.3V

PAGE 19

VCORE = 1.75V / SLEEP : 1.3V

VCC3

PAGE 4, 5, 6

VID0~4

PWM/OTHER POWER

VCORE = 1.75V (650-1100MHZ) / SLEEP : 1.3V

5VSB,-12V ,+12V,VCC,VCC3,3VDUAL

VTT_DDR,2_5VSTR

PAGE 32,33,34

CHANNEL A

GAD0~31

ADSTB0,ADSTB0ADSTB1,ADSTB1-

PCI EXPRESS

VDDQ = 1.5V (AGP POWER 4X)

VCC3 = 3.3V

+12V = 12V

3VDUAL = 3.3V

VCC = 5V

C C

AGPUSB+ / -

PAGE 14

SBA0~7

SBSTB,SBSTB-

GCBE0~3ST0~2

AGP BUS

GMCH

GRANTSDALE

VCORE = 1.75V / SLEEP : 1.3V

2_5VSTR = 2.5V(MEMORY)

VDDQ = 1.5V ( A GP POW ER 4X, HUBLINK)

HL0~10

CONTROL BUS

HUB LINK

PAGE 7 ,8 ,9,10

MAA0~14

MAA_CPC1~5

MAB_CPC1~5

MDD0~63

-DQSD0~7

DM0~7

ICH6

USB PORTS 0~7

VCC25 = 2.5V(I/O,MEMORY/I,VLINK/I)

3VDUAL = 3.3V(SUSPEND POWER)

VCC3 = 3.3V

RTCVDD = 3.3V

PAGE 15,16,17

AMRUSB+ / -

VCC = 5V

5VSB = 5V

5VUSB = 5V

PAGE 27

DDRII SDRAM DIMM X 2

2_5VSTR = 2.5V(MEMORY,SUSPEND POWER)

VTT_DDR = 1.25V

PAGE 11

CHANNEL B

DDRII SDRAM DIMM X 2

2_5VSTR = 2.5V(MEMORY,SUSPEND POWER)

VTT_DDR = 1.25V

PAGE 12

IDE Primary

VCC = 5V

PAGE 24

SERIAL ATA

VCC = 5V

PAGE 16

B B

PCI BUS

FWH/HWMO

PCI SLOT 1,2

+12 = 12V

-12 = -12V

VCC = 5V

VCC3 = 3V

3VDUAL = 3V

AC97/Azalia ALC880

+12V = 12V

VCC = 5V 5VSB = 5V

AVDD = 5V

A A

AUDIO PORTS :

LIN_ OUT

TELE

CD_IN

LINE_IN

AUX_IN

5

FRONT AUDIO

PAGE 29

MIC

PAGE 30, 31

AC97 LINK

4

KINNERTH-R/NORTHWAY

FRONT PANEL /CPU FAN

VCC = 5V

5VSB = 5V

+12 = 12V

PVCC = 5V

PAGE 20, 21

LPC BUS

PAGE 35

PAGE 28

3

VCC = 5V

VCC3 = 3V

LPC I/O ITE8712G

VCC = 5VVCC3 = 3.3V

VBAT = 3V

I/O PORTS :

COMB

COMA IR

LPT

2

PS2

FDD

PAGE 18, 23

PAGE 22

PAGE 25, 26

Title

Size Document Number Rev

Custom

Date: Sheet

GIGABYTE

BLOCK DIAGRAM

8I915G-YFD

1

of

242Wednesday, November 17, 2004

1.0

5

4

3

2

1

Model Name: 8I915G-YFD

Circuit or PCB layout change for next version

D D

C C

266.7mm*264.16mm/C/60/+-15%/Blue

Component value change history

DATE CHANGE ITEM REASON

2004/03/03 NEW BO M 0. 1 RELE ASE

2004/04/14 BOM 0. 2 RE LEASE

2004/07/17

2004/09/22

2004.11.17

BOM 0.3 RELEASE

BOM 0.4 RELEASE

1.0A BOM RELEASE

775+DDRII

SPECIFICATION CHAN GE.(DDRII --> DDRI)

.機構修改

Update 775 CPU issue, add ICT testing location.

R1139,R1136 change to 8.2K. Add RS3 beside IDE connector.

ADD EMI solution

Version: 1.0

DATE CHANGE ITEM REASON

2004.03.04 0.1 GER B ER O UT

2004.04.13 0.2 GER B ER O UT

2004.06.25 0.3 GER B ER O UT

0.4 GERBER OUT2004.09.22

2004.11.15 1.0 GER B ER O UT

B B

A A

Title

Size Document Number Re v

Custom

5

4

3

2

Date: Sheet

GIGABYTE

BOM & PCB MODIFY HISTORY

8I915G-YFD

1

342Wednesday, November 17, 2004

1.0

of

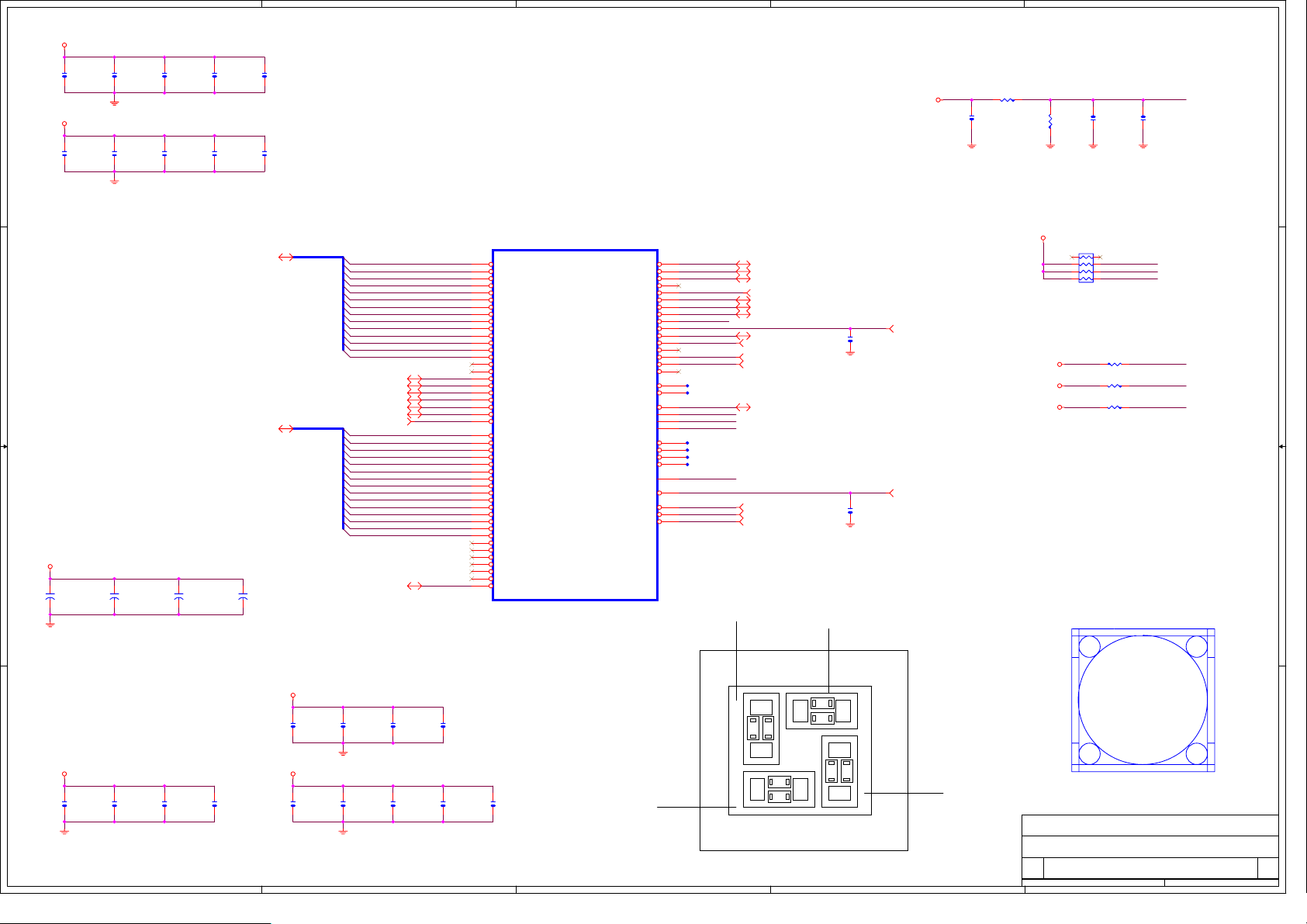

VCORE

5

4

3

2

1

BC1

10U/12/X/6.3V/X

D D

C C

B B

VCORE

VCORE

BC6

10U/12/X/6.3V/X

+

SBC2

100U/2V/SPCAP

BC2

10U/12/X/6.3V/X

BC7

10U/12/X/6.3V

+

SBC3

100U/2V/SPCAP

BC3

10U/12/X/6.3V/X

BC8

10U/12/X/6.3V

+

SBC4

100U/2V/SPCAP

BC4

10U/12/X/6.3V/X

BC9

10U/12/X/6.3V

HA[3..16]<8>

HA[17..31]<8>

+

SBC1

100U/2V/SPCAP

BC5

10U/12/X/6.3V/X

BC31

10U/12/X/6.3V

HA[3..16]

HA[17..31]

Closed to Pin-H1

TESTHI10

TESTHI9

TESTHI8

GTLREF

C1

220P/4/N/25V

-IERR

-BR0

-CPURST

VTT_OR

U1A

HA3

HA4

HA5

HA6

HA7

HA8

HA9

HA10

HA11

HA12

HA13

HA14

HA15

HA16

-HREQ0<8>

-HREQ1<8>

-HREQ2<8>

-HREQ3<8>

-HREQ4<8>

-HADSTB0<8>

-HPCREQ<8>

HA17

HA18

HA19

HA20

HA21

HA22

HA23

HA24

HA25

HA26

HA27

HA28

HA29

HA30

HA31

-HADSTB1<8>

-HREQ0

-HREQ1

-HREQ2

-HREQ3

-HREQ4

-HADSTB0

-HPCREQ

-HADSTB1

AB6

AA4

AD6

AA5

AB5

AC5

AB4

AF5

AF4

AG6

AG4

AG5

AH4

AH5

AC4

AE4

AD5

L5

A03#

P6

A04#

M5

A05#

L4

A06#

M4

A07#

R4

A08#

T5

A09#

U6

A10#

T4

A11#

U5

A12#

U4

A13#

V5

A14#

V4

A15#

W5

A16#

N4

RSVD

P5

RSVD

K4

REQ0#

J5

REQ1#

M6

REQ2#

K6

REQ3#

J6

REQ4#

R6

ADSTB0#

G5

PCREQ#

A17#

W6

A18#

Y6

A19#

Y4

A20#

A21#

A22#

A23#

A24#

A25#

A26#

A27#

A28#

A29#

A30#

A31#

A32#

A33#

AJ5

A34#

AJ6

A35#

RSVD

RSVD

ADSTB1#

LGA775

ADS#

BNR#

HIT#

RSP#

BPRI#

DBSY#

DRDY#

HITM#

IERR#

INIT#

LOCK#

TRDY#

BINIT#

DEFER#

EDRDY#

MCERR#

AP0#

AP1#

BR0#

TESTHI08

TESTHI09

TESTHI10

DP0#

DP1#

DP2#

DP3#

GTLREF

RESET#

RS0#

RS1#

RS2#

D2

C2

D4

H4

G8

B2

C1

E4

AB2

P3

C3

E3

AD3

G7

F2

AB3

U2

U3

F3

G3

G4

H5

J16

H15

H16

J17

H1

G23

B3

F5

A3

-HADS

-BNR

-HIT

-BPRI

-DBSY

-DRDY

-HITM

-IERR

-HINIT

-HLOCK

-HTRDY

-DEFER

-EDRDY

CPU_TP1

CPU_TP2

-BR0

TESTHI8

TESTHI9

TESTHI10

CPU_TP3

CPU_TP4

CPU_TP5

CPU_TP6

GTLREF

-CPURST

-RS0

-RS1

-RS2

10

上

0U/2V/SPCAP

-HADS <8>

-BNR <8>

-HIT <8>

-BPRI <8>

-DBSY <8>

-DRDY <8>

-HITM <8>

-HLOCK <8>

-HTRDY <8>

-DEFER <8>

-EDRDY <8>

-BR0 <8>

-RS0 <8>

-RS1 <8>

-RS2 <8>

上

10U/12/X

C2

33P/4/N/50V

C4

22P/4/N/50V

-HINIT <19>

-CPURST <8>

/6.3V X2

R1 49.9/6/1

BC11

0.01U/4/X/16V

顆

VTT_OL

VTT_OL

VTT_OL

VTT_OL

R2

100/6/1

7 8

5 6

3 4

1 2

62/8P4R

CR1

C3

1U/6/Y/10V

RN122

R6 62/6

R7 62/6

R8 62/6

SBC1

VCORE

10U/12/X/6.3V

BC21

BC22

10U/12/X/6.3V

BC23

10U/12/X/6.3V

BC24

10U/12/X/6.3V

SBC3

BC15/BC14

+

BC5/BC6

+

-

+

SBC2

BC1/BC2

2

10

上

0U/2V/SPCAP

CPU RETAINTION/X

Title

Size Document Number Re v

Custom

Date: Sheet

GIGABYTE

P4_LGA775-A

8I915G-YFD

1

of

442Wednesday, November 17, 2004

1.0

A A

BC30

10U/12/X/6.3V

BC20

10U/12/X/6.3V

BC14

10U/12/X/6.3V/X

BC15

10U/12/X/6.3V/X

VCOREVCORE

10U/12/X/6.3V

BC25

BC26

10U/12/X/6.3V

BC27

10U/12/X/6.3V

BC28

10U/12/X/6.3V

BC29

10U/12/X/6.3V

10U/12/X上/6.3V X2

顆

+

SBC4

BC3/BC4

5

4

3

5

D D

4

3

2

1

HD[0..15]<8>

C C

HD[16..31]<8>

B B

HD[0..15]

HD[16..31]

HD0

HD1

HD2

HD3

HD4

HD5

HD6

HD7

HD8

HD9

HD10

HD11

HD12

HD13

HD14

HD15

-DBI0<8>

STBN0<8>

STBP0<8>

-DBI1<8>

STBN1<8>

STBP1<8>

-DBI0

STBN0

STBP0

HD16

HD17

HD18

HD19

HD20

HD21

HD22

HD23

HD24

HD25

HD26

HD27

HD28

HD29

HD30

HD31

-DBI1

STBN1

STBP1

U1B

B4

D00#

C5

D01#

A4

D02#

C6

D03#

A5

D04#

B6

D05#

B7

D06#

A7

D07#

A10

D08#

A11

D09#

B10

D10#

C11

D11#

D8

D12#

B12

D13#

C12

D14#

D11

D15#

A8

DBI0#

C8

DSTBN0#

B9

DSTBP0

G9

D16#

F8

D17#

F9

D18#

E9

D19#

D7

D20#

E10

D21#

D10

D22#

F11

D23#

F12

D24#

D13

D25#

E13

D26#

G13

D27#

F14

D28#

G14

D29#

F15

D30#

G15

D31#

G11

DBI1#

G12

DSTBN1#

E12

DSTBP1

LGA775

D32#

D33#

D34#

D35#

D36#

D37#

D38#

D39#

D40#

D41#

D42#

D43#

D44#

D45#

D46#

D47#

DBI2#

DSTBN2#

DSTBP2

D48#

D49#

D50#

D51#

D52#

D53#

D54#

D55#

D56#

D57#

D58#

D59#

D60#

D61#

D62#

D63#

DBI3#

DSTBN3#

DSTBP3

HD32

G16

HD33

E15

HD34

E16

HD35

G18

HD36

G17

HD37

F17

HD38

F18

HD39

E18

HD40

E19

HD41

F20

HD42

E21

HD43

F21

HD44

G21

HD45

E22

HD46

D22

HD47

G22

-DBI2

D19

G20

G19

D20

D17

A14

C15

C14

B15

C18

B16

A17

B18

C21

B21

B19

A19

A22

B22

C20

A16

C17

STBN2

STBP2

HD48

HD49

HD50

HD51

HD52

HD53

HD54

HD55

HD56

HD57

HD58

HD59

HD60

HD61

HD62

HD63

-DBI3

STBN3

STBP3

-DBI2 <8>

STBN2 <8>

STBP2 <8>

-DBI3 <8>

STBN3 <8>

STBP3 <8>

HD[32..47] <8>

HD[48..63] <8>

A A

GIGABYTE

Title

Size Document Number Re v

Custom

5

4

3

2

Date: Sheet

P4_LGA775-C

8I915G-YFD

1

1.0

of

542Wednesday, November 17, 2004

5

Note:

VCCA & VCOREPLL

VTT_GMCH

10UH/8/100mA/S (10LI2-00100A-01/02/03)

D D

C C

B B

A A

L1

C6

1U/6/Y/10V

C7

VCC_SENSE<39>

VSS_SENSE<39>

1U/6/Y/10V

Q6

MMBT2222/SOT23/X

132

L2

10UH/8/100mA/S(10LI2-00100A-01/02/03)

VTT_GMCH

R40

1K/6/X

BC35

10U/12/X/6.3V

VCC

R41

8.2K/6/X

BC33

4.7U/8/Y/10V

BC32

4.7U/8/Y/10V

FSBSEL0

define doesn't same as

old P4 design kit

As close as possible to

CPU socket

CPU_TEMP<25,36>

THERMDC<36>

BC34

1N/4/X/50V

FSBSEL1

3

D

Q5

2N7002/SOT23/X

GS

2

1

VCCA

R17

0/SHT/X

VSSA

VCOREPLL

1N/4/X/50V

C9

4

Trace width doesn't

less than 12 Mil

-SMI

-SMI<19>

-A20M

-A20M<19>

-FERR

-FERR<19>

INTR TESTHI12

INTR<19>

NMI

NMI<19>

-IGNNE

-IGNNE<19>

-STPCLK

-STPCLK<19>

VCCA

VSSA

VCOREPLL

VID[0..5]

VID[0..5]<36,39>

CPUCLK<22>

-CPUCLK<22>

VCC_SENSE<39>

VSS_SENSE<39>

-SYS_RST<19,22,28>

FSBSEL1 FSBSEL11

R45 0/6

VID0

VID1

VID2

VID3

VID4

VID5

CPUCLK

-CPUCLK

R44 62/6/X

R28 62/6/X

CPU_TP10

TCK

TDI

TDO

TMS

-TRST

-BPM0

-BPM1

-BPM2

-BPM3

-BPM4

-BPM5

-SYS_RST

CPU_TP11

CPU_TP12

FSBSEL0

FSBSEL2

D23

C23

AM2

AM3

AK4

AM5

G28

AE8

AK1

AN3

AN4

AN5

AN6

GTL_DET<7,8>

P2

K3

R3

K1

L1

N2

M3

A23

B23

AL5

AL6

AL4

F28

AL1

F29

V1

W1

F6

AE1

AD1

AF1

AC1

AG1

AJ2

AJ1

AD2

AG2

AF2

AG3

AC2

AK3

AJ3

G29

H30

G30

U1C

SMI#

A20M#

FERR#/PBE#

LINT0

LINT1

IGNNE#

STPCLK#

VCCA

VSSA

RSVD

VCCIOPLL

VID0

VID1

VID2

VID3

VID4

VID5

RSVD

BCLK0

BCLK1

SKTOCC#

THERMDA

THERMDC

VCC_SENSE

VSS_SENSE

RSVD

RSVD

VTT_PKGSENSE

MSID1

MSID0

RSVD_F6

LGA775

U1D

TCK

TDI

TDO

TMS

TRST#

BPM0#

BPM1#

BPM2#

BPM3#

BPM4#

BPM5#

DBR#

ITPCLK0

ITPCLK1

BSEL0

BSEL1

BSEL2

LGA775

VCC3

R16

249/6/1

3

D

Q26

2N7002/SOT23

GS

2

1

SOT23

3

TESTHI0

TESTHI00

TESTHI01

TESTHI11

TESTHI12

TESTHI02

TESTHI03

TESTHI04

TESTHI05

TESTHII06

TESTHI07

FORCEPR#

RSVD

SLP#

RSVD

PWRGOOD

PROCHOT#

THERMTRIP#

COMP0

COMP1

COMP2

COMP3

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

GTLREF1

BOOTSELECT

LL_ID0

LL_ID1

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTTPWRGD

VTT_OUT

VTT_OUT

VTT_SEL

N/C

N/C

N/C

N/C

N/C

N/C

A29

B25

B29

B30

C29

A26

B27

C28

A25

A28

A27

C30

A30

C25

C26

C27

B26

D27

D28

D25

D26

B28

D29

D30

AM6

AA1

J1

F27

VCC3

VTT_OR

F26

W3

P1

W2

F25

G25

G27

G26

G24

F24

AK6

G6

L2

AH2

N1

AL2

M2

A13

T1

G2

R1

N5

AE6

C9

G10

D16

A20

E7

CPU_TP7

E23

CPU_TP8

E24

F23

CPU_TP9

GTLREF1

H2

J2

J3

BOOTSEL

Y1

V2

AA2

R52 1K/6/X

R12 110/6/1

R31 49.9/6/1/X

TESTHI0

TESTHI1

TESTHI11

TESTHI2_7

-FORCEPR

RSVD_G6

-CPUSLP

CPUPWROK

-PROCHOT

-THRMTRIP

COMP0

COMP1

COMP2

COMP3

R42 62/6/X

VTT_GMCH

VTT_PWRGD <35,39>

VTT_OR

VTT_OL

VCC3

-FORCEPR

-CPUSLP <19>

CPUPWROK <19>

-THRMTRIP <19>

VTT_GMCH

R13

61.9/6/1

R29

100/6/1/X

-PROCHOT <25>

2

TESTHI0

C11

0.1U/6/Y/25V

Closed to Pin-H2

C17

1U/6/Y/10V/X

GTLREF1

C18

220P/4/N/25V/X

Place outside of CPU socket

VTT_OL

C5

0.1U/6/Y/25V

VTT_GMCH

Locate at ICH6 Side

VTT_OL

VTT_OL

VTT_OR

C304

0.1U/6/Y/25V

C305

0.1U/6/Y/25V

C20

33P/4/N/50V

R10 100/6/1

R11 100/6/1

R14 60.4/6/1

R15 60.4/6/1

R32 60.4/6/1/X

R38 60.4/6/1/X

RN2

470/8P4R

7 8

5 6

3 4

1 2

R22 62/6

R24 62/6

R25 62/6

R26 62/6/X

R30 100/6

RN123

7 8

5 6

3 4

1 2

62/8P4R

RN1 680/8P4R

7 8

5 6

3 4

1 2

R33 680/6

R34 680/6

R35 120/6

R36 62/6/X

R37 62/6/X

7 8

RN124

5 6

62/8P4R

3 4

1 2

7 8

RN125

5 6

62/8P4R

3 4

1 2

R46 62/6

R48 62/6

R49 62/6

1

FSBSEL1

FSBSEL0

FSBSEL2

TESTHI2_7

-THRMTRIP

-FERR

RSVD_G6

CPUPWROK

C8

1N/4/X/50V

C19

33P/4/N/50V

C10

33P/4/N/50V

COMP2

COMP3

COMP0

COMP1

COMP2

COMP3

TESTHI12

TESTHI1

TESTHI11

VID2

VID5

VID0

VID4

VID1

VID3

-PROCHOT

BOOTSEL

-FORCEPR

-BPM0

-BPM1

-BPM5

-BPM3

-BPM4

-BPM2

TDI

TMS

TDO

-TRST

TCK

-PROCHOT-STPCLK

-CPUSLP

FSBSEL0<22>

FSBSEL1<22>

FSBSEL2<22>

5

4

FSBSEL0 BSEL0

FSBSEL1 BSEL1

FSBSEL2 BSEL2

R53 8.2K/6

R54 8.2K/6

R55 8.2K/6

BSEL0 <11>

BSEL1 <11>

BSEL2 <11>

3

2

Title

Size Document Number Re v

Custom

Date: Sheet

GIGABYTE

P4_LGA775-B

8I915G-YFD

1

1.0

of

642Wednesday, November 17, 2004

5

D D

U1E

VCORE

C C

B B

AA8

AB8

AC23

AC24

AC25

AC26

AC27

AC28

AC29

AC30

AC8

AD23

AD24

AD25

AD26

AD27

AD28

AD29

AD30

AD8

AE11

AE12

AE14

AE15

AE18

AE19

AE21

AE22

AE23

AE9

AF11

AF12

AF14

AF15

AF18

AF19

AF21

AF22

AF8

AF9

AG11

AG12

AG14

AG15

AG18

AG19

AG21

AG22

AG25

AG26

AG27

AG28

AG29

AG30

AG8

AG9

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

LGA775/VCC_1

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

AH11

AH12

AH14

AH15

AH18

AH19

AH21

AH22

AH25

AH26

AH27

AH28

AH29

AH30

AH8

AH9

AJ11

AJ12

AJ14

AJ15

AJ18

AJ19

AJ21

AJ22

AJ25

AJ26

AJ8

AJ9

AK11

AK12

AK14

AK15

AK18

AK19

AK21

AK22

AK25

AK26

AK8

AK9

AL11

AL12

AL14

AL15

AL18

AL19

AL21

AL22

AL25

AL26

AL29

AL30

AL8

AL9

VCORE

VCORE

AM11

AM12

AM14

AM15

AM18

AM19

AM21

AM22

AM25

AM26

AM29

AM30

AM8

AM9

AN11

AN12

AN14

AN15

AN18

AN19

AN21

AN22

AN25

AN26

AN29

AN30

AN8

AN9

K23

K24

K25

K26

K27

K28

K29

K30

M23

M24

M25

M26

M27

M28

M29

M30

4

U1F

N23

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

J10

VCC

J11

VCC

J12

VCC

J13

VCC

J14

VCC

J15

VCC

J18

VCC

J19

VCC

J20

VCC

J21

VCC

J22

VCC

J23

VCC

J24

VCC

J25

VCC

J26

VCC

J27

VCC

J28

VCC

J29

VCC

J30

VCC

J8

VCC

J9

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

K8

VCC

L8

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

M8

VCC

LGA775_4

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

N24

N25

N26

N27

N28

N29

N30

N8

P8

R8

T23

T24

T25

T26

T27

T28

T29

T30

T8

U23

U24

U25

U26

U27

U28

U29

U30

U8

V8

W23

W24

W25

W26

W27

W28

W29

W30

W8

Y23

Y24

Y25

Y26

Y27

Y28

Y29

Y30

Y8

VCORE

3

U1G

AA23

AA24

AA25

AA26

AA27

AA28

AA29

AA30

AB23

AB24

AB25

AB26

AB27

AB28

AB29

AB30

AE10

AE13

AE16

AE17

AE20

AE24

AE25

AE26

AE27

AE28

AE29

AE30

AF10

AF13

AF16

AF17

AF20

AF23

AF24

AF25

AF26

AF27

AF28

AF29

AF30

AC3

AC6

AC7

AD4

AD7

AE2

AE5

AE7

AF3

AF6

AF7

A12

A15

A18

A21

A24

AA3

AA6

AA7

AB1

AB7

VSS

VSS

VSS

A2

VSS

VSS

VSS

A6

VSS

A9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

LGA7555/VSS_1

AG10

VSS

AG13

VSS

AG16

VSS

AG17

VSS

AG20

VSS

AG23

VSS

AG24

VSS

AG7

VSS

AH1

VSS

AH10

VSS

AH13

VSS

AH16

VSS

AH17

VSS

AH20

VSS

AH23

VSS

AH24

VSS

AH3

VSS

AH6

VSS

AH7

VSS

AJ10

VSS

AJ13

VSS

AJ16

VSS

AJ17

VSS

AJ20

VSS

AJ23

VSS

AJ24

VSS

AJ27

VSS

AJ28

VSS

AJ29

VSS

AJ30

VSS

AJ4

VSS

AJ7

VSS

AK10

VSS

AK13

VSS

AK16

VSS

AK17

VSS

AK2

VSS

AK20

VSS

AK23

VSS

AK24

VSS

AK27

VSS

AK28

VSS

AK29

VSS

AK30

VSS

AK5

VSS

AK7

VSS

AL10

VSS

AL13

VSS

AL16

VSS

AL17

VSS

AL20

VSS

AL23

VSS

AL24

VSS

AL27

VSS

AL28

VSS

AL3

VSS

AL7

VSS

AM1

VSS

AM10

VSS

AM13

VSS

AM16

VSS

AM17

VSS

AM20

VSS

AM23

VSS

AM24

VSS

AM27

VSS

AM28

VSS

AM4

VSS

AM7

VSS

8/11 long NC pin.

2

U1H

AN1

8/31 long.

61.9/6/1

R39

AN10

AN13

AN16

AN17

AN2

AN20

AN23

AN24

AN27

AN28

AN7

C10

C13

C16

C19

C22

C24

D12

D15

D18

D21

D24

H10

H11

H12

H13

H14

H17

H18

H19

H20

H21

H22

H23

H24

B1

B11

B14

B17

B20

B24

B5

B8

C4

C7

D3

D5

D6

D9

E11

E14

E17

E2

E20

E25

E26

E27

E28

E29

E8

F10

F13

F16

F19

F22

F4

F7

G1

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

LGA775/VSS_2

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

1

H25

H26

H27

H28

H29

H3

H6

H7

H8

H9

J4

J7

K2

K5

K7

L23

L24

L25

L26

L27

L28

L29

L3

L30

L6

L7

M1

M7

N3

N6

N7

P23

P24

P25

P26

P27

P28

P29

P30

P4

P7

R2

R23

R24

R25

R26

R27

R28

R29

R30

R5

R7

T3

T6

T7

U1

U7

V23

V24

V25

V26

V27

V28

V29

V3

V30

V6

V7

W4

W7

Y2

Y5

Y7

GTL_DET <6,8>

A A

Title

Size Document Number Re v

Custom

5

4

3

2

Date: Sheet

GIGABYTE

P4_LGA775-D

8I915G-YFD

1

1.0

of

742Wednesday, November 17, 2004

5

D D

C C

B B

HA[3..31]

-HREQ0<4>

-HREQ1<4>

-HREQ2<4>

-HREQ3<4>

-HREQ4<4>

-HADSTB0<4>

-HADSTB1<4>

-BNR<4>

-CPURST<4>

-DBSY<4>

-DEFER<4>

-EDRDY<4>

-HLOCK<4>

-HPCREQ<4>

-HTRDY<4>

4

HA3

HA4

HA5

HA6

HA7

HA8

HA9

HA10

HA11

HA12

HA13

HA14

HA15

HA16

HA17

HA18

HA19

HA20

HA21

HA22

HA23

HA24

HA25

HA26

HA27

HA28

HA29

HA30

HA31

-HREQ0

-HREQ1

-HREQ2

-HREQ3

-HREQ4

-HADSTB0

-HADSTB1

STBP0

STBP0<5>

STBN0

STBN0<5>

-DBI0

-DBI0<5>

STBP1

STBP1<5>

STBN1

STBN1<5>

-DBI1

-DBI1<5>

STBP2

STBP2<5>

STBN2

STBN2<5>

-DBI2

-DBI2<5>

STBP3

STBP3<5>

STBN3

STBN3<5>

-DBI3

-DBI3<5>

-HADS

-HADS<4>

-BNR

-BPRI

-BPRI<4>

-BR0

-BR0<4>

-CPURST

-DBSY

-DEFER

-DRDY

-DRDY<4>

-HIT

-HIT<4>

-HITM

-HITM<4>

-HLOCK

-HPCREQ

-RS0

-RS0<4>

-RS1

-RS1<4>

-RS2

-RS2<4>

-HTRDY

U9A

H29

HA3*

K29

HA4*

J29

HA5*

G30

HA6*

G32

HA7*

K30

HA8*

L29

HA9*

M30

HA10*

L31

HA11*

L28

HA12*

J28

HA13*

K27

HA14*

K33

HA15*

M28

HA16*

R29

HA17*

L26

HA18*

N26

HA19*

M26

HA20*

N31

HA21*

P26

HA22*

N29

HA23*

P28

HA24*

R28

HA25*

N33

HA26*

T27

HA27*

T31

HA28*

U28

HA29*

T26

HA30*

T29

HA31*

F33

HREQ0*

E32

HREQ1*

H31

HREQ2*

G31

HREQ3*

F31

HREQ4*

J31

HADSTB0*

N27

HADSTB1*

E33

HDSTBP0

E35

HDSTBN0*

E34

HDINV0*

H26

HDSTBP1

F26

HDSTBN1*

J26

HDINV1*

J19

HDSTBP2

F19

HDSTBN2*

K19

HDINV2*

B29

HDSTBP3

C29

HDSTBN3*

B26

HDINV3*

M31

HADS*

M35

HBNR*

E30

HBPRI*

R33

HBREQ0*

G24

HCPURST*

L35

HDBSY*

J35

HDEFER*

M32

HDRDY*

P33

HEDRDY*

L34

HHIT*

N35

HHITM*

L33

HLOCK*

E31

HPCREQ*

K34

HRS0*

P34

HRS1*

J32

HRS2

N34

HTRDY*

GRANTSDALE/B1

CPU INTERFACE

HD0*

HD1*

HD2*

HD3*

HD4*

HD5*

HD6*

HD7*

HD8*

HD9*

HD10*

HD11*

HD12*

HD13*

HD14*

HD15*

HD16*

HD17*

HD18*

HD19*

HD20*

HD21*

HD22*

HD23*

HD24*

HD25*

HD26*

HD27*

HD28*

HD29*

HD30*

HD31*

HD32*

HD33*

HD34*

HD35*

HD36*

HD37*

HD38*

HD39*

HD40*

HD41*

HD42*

HD43*

HD44*

HD45*

HD46*

HD47*

HD48*

HD49*

HD50*

HD51*

HD52*

HD53*

HD54*

HD55*

HD56*

HD57*

HD58*

HD59*

HD60*

HD61*

HD62*

HD63*

HXSWING

HXSCOMP

HXRCOMP

HVREF

HCLKINP

HCLKINN

J33

H33

J34

G35

H35

G34

F34

G33

D34

C33

D33

B34

C34

B33

C32

B32

E28

C30

D29

H28

G29

J27

F28

F27

E27

E25

G25

J25

K25

L25

L23

K23

J22

J24

K22

J21

M21

H23

M19

K21

H20

H19

M18

K18

K17

G18

H18

F17

A25

C27

C31

B30

B31

A31

B27

A29

C28

A28

C25

C26

D27

A27

E24

B25

A23

D24

B23

A24

M23

M22

3

HD0

HD1

HD2

HD3

HD4

HD5

HD6

HD7

HD8

HD9

HD10

HD11

HD12

HD13

HD14

HD15

HD16

HD17

HD18

HD19

HD20

HD21

HD22

HD23

HD24

HD25

HD26

HD27

HD28

HD29

HD30

HD31

HD32

HD33

HD34

HD35

HD36

HD37

HD38

HD39

HD40

HD41

HD42

HD43

HD44

HD45

HD46

HD47

HD48

HD49

HD50

HD51

HD52

HD53

HD54

HD55

HD56

HD57

HD58

HD59

HD60

HD61

HD62

HD63

HSWNG

HSCOMP-EDRDY

HRCOMP

MCH_GTLREF

MCHCLK

-MCHCLK

HD[0..63]

MCHCLK <22>

-MCHCLK <22>

2

VTT_GMCH

R112

HD[0..63] <5>HA[3..31]<4>

100/6/1

BC43

0.01U/4/X/16V

R113

210/6/1

BC44

0.1U/6/Y/25V

1

MCH_GTLREF

C34

220P/6/Y/50V

VTT_GMCH

R114

301/6/1

HSWNG

R115

100/6/1

C35

0.01U/6/X/50V

VCORE

R137

+12V

R136

8.2K/6

GTL_DET<6,7>

619/6/1

GS

D

2

3

1

Q2

2N7002/SOT23

SOT23

MCH_GTLREF

VTT_GMCH

R116

60.4/6/1

HSCOMP

C36

2.2P/4/X/16V/X

R117

20/6/1

HRCOMP

A A

5

4

COUPON1

COUPON2

COUPON1 COUPON

COUPON2 COUPON

21

21

VCC

Title

Size Document Number Re v

Custom

3

2

Date: Sheet

GIGABYTE

GMCH-HOST

8I915G-YFD

1

1.0

of

842Wednesday, November 17, 2004

5

AN22

AP22

AN21

AP21

AM21

AP19

AR20

AN16

AN18

AM15

AN23

AP15

AP13

AN31

AP31

AL34

AN29

AN28

AP26

AR23

AM34

AL35

AK34

AL33

AL12

AN11

AP11

AR11

AP33

AR24

AR28

AR29

AM24

AN25

AN2

AN3

AB34

AC33

AP25

AN26

AM2

AM3

AC35

AC34

AB33

AH15

AE16

AJ12

AK12

AE7

U9E

SAMA0

SAMA1

SAMA2

SAMA3

SAMA4

SAMA5

SAMA6

SAMA7

SAMA8

SAMA9

SAMA10

SAMA11

SAMA12

RSV

SAWE*

SACAS*

SARAS*

SABA0

SABA1

RSV

SACS0*

SACS1*

SACS2*

SACS3*

SACKE0

SACKE1

SACKE2

SACKE3

RSV

RSV

RSV

RSV

SACK0

SACK0*

SACK1

SACK1*

SACK2

SACK2*

SACK3

SACK3*

SACK4

SACK4*

SACK5

SACK5*

SADDR1MA13

RSV_TP1

RSV_TP0

SMXSLEWIN0

SMXSLEWOUT0

SMVREF0

DDR INTERFACE

GRANTSDALE

MAAA0

MAAA1

MAAA2 DMA0

MAAA3

-SWEA<14,16>

SBAA0<14,16>

SBAA1<14,16>

-CSA0<14,16>

-CSA1<14,16>

-CSA2<14,16>

-CSA3<14,16>

CKEA0<14,16>

CKEA1<14,16>

CKEA2<14,16>

CKEA3<14,16>

MAAA4

MAAA5

MAAA6

MAAA7

MAAA8

MAAA9

MAAA10

MAAA11

MAAA12

-SWEA

-SCASA

-SRASA

SBAA0

SBAA1

-CSA0

-CSA1

-CSA2

-CSA3

CKEA0

CKEA1

CKEA2

CKEA3

DCLKA0

-DCLKA0

DCLKA1

-DCLKA1

DCLKA2

-DCLKA2

DCLKA3

-DCLKA3

DCLKA4

-DCLKA4

DCLKA5

-DCLKA5

MAAA13

TP2

TP4

SM_XSLEWIN

DDRVREFA

SC5

0.1U/6/Y/25V/X

D D

-SCASA<14,16>

-SRASA<14,16>

C C

DCLKA0<14>

-DCLKA0<14>

DCLKA1<14>

-DCLKA1<14>

DCLKA2<14>

-DCLKA2<14>

DCLKA3<14>

-DCLKA3<14>

DCLKA4<14>

-DCLKA4<14>

DCLKA5<14>

-DCLKA5<14>

B B

A A

5

SADQS0

RSV

SADM0

SADQ0

SADQ1

SADQ2

SADQ3

SADQ4

SADQ5

SADQ6

SADQ7

SADQS1

RSV

SADM1

SADQ8

SADQ9

SADQ10

SADQ11

SADQ12

SADQ13

SADQ14

SADQ15

SADQS2

RSV

SADM2

SADQ16

SADQ17

SADQ18

SADQ19

SADQ20

SADQ21

SADQ22

SADQ23

SADQS3

RSV

SADM3

SADQ24

SADQ25

SADQ26

SADQ27

SADQ28

SADQ29

SADQ30

SADQ31

SADQS4

RSV

SADM4

SADQ32

SADQ33

SADQ34

SADQ35

SADQ36

SADQ37

SADQ38

SADQ39

SADQS5

RSV

SADM5

SADQ40

SADQ41

SADQ42

SADQ43

SADQ44

SADQ45

SADQ46

SADQ47

SADQS6

RSV

SADM6

SADQ48

SADQ49

SADQ50

SADQ51

SADQ52

SADQ53

SADQ54

SADQ55

SADQS7

RSV

SADM7

SADQ56

SADQ57

SADQ58

SADQ59

SADQ60

SADQ61

SADQ62

SADQ63

4

DQSA0

AG1

AG2

AF2

MDA0

AE3

MDA1

AF3

MDA2

AH2

MDA3

AJ2

MDA4

AE2

MDA5

AE1

MDA6

AG3

MDA7

AH3

DQSA1

AL3

AL2

DMA1

AL1

MDA8

AJ1

MDA9

AK2

MDA10

AN4

MDA11

AP4

MDA12

AJ3

MDA13

AK3

MDA14

AP2

MDA15

AP3

DQSA2

AP7

AR7

DMA2

AN7

MDA16

AP5

MDA17

AR5

MDA18

AN8

MDA19

AP9

MDA20

AN5

MDA21

AP6

MDA22

AR8

MDA23

AN9

DQSA3

AF17

AG17

DMA3

AH16

MDA24

AK16

MDA25

AL17

MDA26

AD17

MDA27

AF19

MDA28

AF16

MDA29

AJ17

MDA30

AE19

MDA31

AH18

DQSA4

AM30

AL29

DMA4

AK29

MDA32

AH27

MDA33

AK27

MDA34

AN30

MDA35

AK31

MDA36

AL27

MDA37

AJ28

MDA38

AL30

MDA39

AL31

DQSA5

AG35

AG33

DMA5

AG34

MDA40

AJ34

MDA41

AH35

MDA42

AG32

MDA43

AF34

MDA44

AJ33

MDA45

AH33

MDA46

AF33

MDA47

AE33

DQSA6

AA34

AA35

DMA6

AA33

MDA48

AE35

MDA49

AE34

MDA50

Y33

MDA51

W34

MDA52

AD31

MDA53

AD35

MDA54

AA32

MDA55

Y35

DQSA7

U34

U35

DMA7

U33

MDA56

V34

MDA57

V33

MDA58

R32

MDA59

R34

MDA60

W35

MDA61

W33

MDA62

T33

MDA63

T35

4

3

SC6

0.1U/6/Y/25V/X

3

-DCLKB0<15>

-DCLKB1<15>

-DCLKB2<15>

-DCLKB3<15>

-DCLKB4<15>

-DCLKB5<15>

-SWEB<15,16>

-SCASB<15,16>

-SRASB<15,16>

SBAB0<15,16>

SBAB1<15,16>

CKEB0<15,16>

CKEB1<15,16>

CKEB2<15,16>

CKEB3<15,16>

DCLKB0<15>

DCLKB1<15>

DCLKB2<15>

DCLKB3<15>

DCLKB4<15>

DCLKB5<15>

-CSB0<15,16>

-CSB1<15,16>

-CSB2<15,16>

-CSB3<15,16>

SM_YSLEWIN

DDRVREFB

SMRCOMPP

SMRCOMPN

MAAB0

MAAB1

MAAB2

MAAB3

MAAB4

MAAB5

MAAB6

MAAB7

MAAB8

MAAB9

MAAB10

MAAB11

MAAB12

-SWEB

-SCASB

-SRASB

SBAB0

SBAB1

-CSB0

-CSB1

-CSB2

-CSB3

CKEB0

CKEB1

CKEB2

CKEB3

DCLKB0

-DCLKB0

DCLKB1

-DCLKB1

DCLKB2

-DCLKB2

DCLKB3

-DCLKB3

DCLKB4

-DCLKB4

DCLKB5

-DCLKB5

MAAB13

TP1

TP3

AM18

AP18

AN17

AR16

AR15

AN15

AP17

AL15

AP14

AN13

AN20

AR12

AM12

AL24

AR27

AN27

AP27

AM27

AR19

AP23

AP34

AN34

AN33

AM33

AN10

AM9

AP10

AR9

AN32

AP29

AP30

AP32

AH22

AG23

AL11

AJ11

AE26

AE25

AL23

AK22

AK9

AD29

AD28

AD32

AK15

AN14

AE10

AE8

AG8

AG4

AE5

AL9

AF9

AF5

U9F

SBMA0

SBMA1

SBMA2

SBMA3

SBMA4

SBMA5

SBMA6

SBMA7

SBMA8

SBMA9

SBMA10

SBMA11

SBMA12

RSV

SBWE*

SBCAS*

SBRAS*

SBBA0

SBBA1

RSV

SBCS0*

SBCS1*

SBCS2*

SBCS3*

SBCKE0

SBCKE1

SBCKE2

SBCKE3

RSV

RSV

RSV

RSV

SBCK0

SBCK0*

SBCK1

SBCK1*

SBCK2

SBCK2*

SBCK3

BLCK3*

SBCK4

SBCK4*

SBCK5

SBCK5*

SBDDR1MA13

RSV_TP3

RSV_TP2

SMYSLEWIN1

SMYSLEWOUT1

SMVREF1

SMRCOMP1

SMRCOMP0

RSV

RSV

SBDQS0

SBDM0

SBDQ0

SBDQ1

SBDQ2

SBDQ3

SBDQ4

SBDQ5

SBDQ6

SBDQ7

SBDQS1

SBDM1

SBDQ8

SBDQ9

SBDQ10

SBDQ11

SBDQ12

SBDQ13

SBDQ14

SBDQ15

SBDQS2

SBDM2

SBDQ16

SBDQ17

SBDQ18

SBDQ19

SBDQ20

SBDQ21

SBDQ22

SBDQ23

SBDQS3

SBDQS3*

SBDM3

SBDQ24

SBDQ25

SBDQ26

SBDQ27

SBDQ28

SBDQ29

SBDQ30

SBDQ31

SBDQS4

SBDM4

SBDQ32

SBDQ33

SBDQ34

SBDQ35

SBDQ36

SBDQ37

SBDQ38

SBDQ39

SBDQS5

SBDM5

SBDQ40

SBDQ41

SBDQ42

SBDQ43

SBDQ44

SBDQ45

SBDQ46

SBDQ47

SBDQS6

SBDM6

SBDQ48

SBDQ49

SBDQ50

SBDQ51

SBDQ52

SBDQ53

SBDQ54

SBDQ55

SBDQS7

SBDM7

SBDQ56

SBDQ57

SBDQ58

SBDQ59

SBDQ60

SBDQ61

SBDQ62

SBDQ63

GRANTSDALE

RSV

RSV

RSV

RSV

RSV

RSV

RSV

AK5

AL4

AJ5

AH7

AJ6

AL5

AN6

AG9

AH4

AM5

AL6

AK10

AH10

AH9

AJ7

AL7

AF11

AE11

AJ8

AL8

AG10

AG11

AK13

AL14

AH13

AE13

AF13

AG14

AD14

AD12

AH12

AF14

AD15

AD20

AF20

AG20

AD18

AK19

AE22

AH21

AL18

AH19

AF22

AD21

AH25

AG26

AG24

AF23

AF25

AL25

AJ26

AD23

AF24

AJ25

AL26

AH28

AH30

AH31

AJ29

AJ31

AG30

AG31

AK33

AK32

AG27

AF28

AB31

AC30

AD24

AE31

AF27

AB27

AB26

AE29

AE27

AC28

AC26

W27

Y28

W31

AA29

W29

U26

V29

Y26

AA28

W26

V28

2

DQSB0

DMB0

MDB0

MDB1

MDB2

MDB3

MDB4

MDB5

MDB6

MDB7

DQSB1

DMB1

MDB8

MDB9

MDB10

MDB11

MDB12

MDB13

MDB14

MDB15

DQSB2

DMB2

MDB16

MDB17

MDB18

MDB19

MDB20

MDB21

MDB22

MDB23

DQSB3

DMB3

MDB24

MDB25

MDB26

MDB27

MDB28

MDB29

MDB30

MDB31

DQSB4

DMB4

MDB32

MDB33

MDB34

MDB35

MDB36

MDB37

MDB38

MDB39

DQSB5

DMB5

MDB40

MDB41

MDB42

MDB43

MDB44

MDB45

MDB46

MDB47

DQSB6

DMB6

MDB48

MDB49

MDB50

MDB51

MDB52

MDB53

MDB54

MDB55

DQSB7

DMB7

MDB56

MDB57

MDB58

MDB59

MDB60

MDB61

MDB62

MDB63

2

1

DDR25V

R118

1K/6/1

R119

1K/6/1

BC45

DDR25V

R121

1K/6/1/X

R122

1K/6/1/X

DDR25V

R123 80.6/6/1

BC49

0.1U/6/Y/25V

R124 80.6/6/1

MAAB[0..13]<15,16>

DMB[0..7]<15,16>

MDB[0..63]<15,16>

DQSB[0..7]<15,16>

MAAA[0..13]<14,16>

DMA[0..7]<14,16>

MDA[0..63]<14,16>

DQSA[0..7]<14,16>

1U/6/Y/10V

BC47

1U/6/Y/16V

GIGABYTE

GMCH-DDRII

8I915G-YFD

R120

0/SHT/X

Title

Size Document Number Re v

Custom

Date: Sheet

BC46

0.1U/6/Y/25V

BC48

0.1U/6/Y/25V

MAAB[0..13]

DMB[0..7]

MDB[0..63]

DQSB[0..7]

MAAA[0..13]

DMA[0..7]

MDA[0..63]

DQSA[0..7]

1

DDRVREFA

DDRVREFB

SMRCOMPN

SMRCOMPP

942Wednesday, November 17, 2004

of

1.0

5

4

3

2

1

D D

EXP_A_RXP0

EXP_A_RXN0

EXP_A_RXP1

EXP_A_RXN1

EXP_A_RXP2

EXP_A_RXN2

EXP_A_RXP3

EXP_A_RXN3

EXP_A_RXP4

EXP_A_RXN4

EXP_A_RXP5

EXP_A_RXN5

EXP_A_RXP6

EXP_A_RXN6

EXP_A_RXP7

EXP_A_RXN7

C C

DMI_0RXP<18>

DMI_0RXN<18>

DMI_1RXP<18>

DMI_1RXN<18>

DMI_2RXP<18>

DMI_2RXN<18>

DMI_3RXP<18>

DMI_3RXN<18>

SRCCLK_MCH<22>

B B

-SRCCLK_MCH<22>

SDVO_CLDATA<17>

SDVO_CLCLK<17>

EXP_A_RXP8

EXP_A_RXN8

EXP_A_RXP9

EXP_A_RXN9

EXP_A_RXP10

EXP_A_RXN10

EXP_A_RXP11

EXP_A_RXN11

EXP_A_RXP12

EXP_A_RXN12

EXP_A_RXP13

EXP_A_RXN13

EXP_A_RXP14

EXP_A_RXN14

EXP_A_RXP15

EXP_A_RXN15

DMI_0RXP

DMI_1RXP

DMI_1RXN

DMI_2RXP

DMI_2RXN

DMI_3RXP

DMI_3RXN

For DVO Function

E11

F11

J11

H11

F9

E9

F7

E7

B3

B4

D5

E5

G6

G5

H8

H7

J6

J5

K8

K7

L6

L5

P10

R10

M8

M7

N6

N5

P7

P8

R6

R5

U5

U6

T9

T8

V7

V8

V10

U10

A11

B11

K13

J13

U9B

EXPARXP0

EXPARXN0

EXPARXP1

EXPARXN1

EXPARXP2

EXPARXN2

EXPARXP3

EXPARXN3

EXPARXP4

EXPARXN4

EXPARXP5

EXPARXN5

EXPARXP6

EXPARXN6

EXPARXP7

EXPARXN7

EXPARXP8

EXPARXN8

EXPARXP9

EXPARXN9

EXPARXP10

EXPARXN10

EXPARXP11

EXPARXN11

EXPARXP12

EXPARXN12

EXPARXP13

EXPARXN13

EXPARXP14

EXPARXN14

EXPARXP15

EXPARXN15

DMIRXP0

DMIRXN0

DMIRXP1

DMIRXN1

DMIRXP2

DMIRXN2

DMIRXP3

DMIRXN3

GCLKINP

GCLKINN

SDVOCTRLDATA

SDVOCTRLCLK

GRANTSDALE

EXPATXP0

EXPATXN0

EXPATXP1

EXPATXN1

EXPATXP2

EXPATXN2

EXPATXP3

EXPATXN3

EXPATXP4

EXPATXN4

EXPATXP5

EXPATXN5

EXPATXP6

EXPATXN6

EXPATXP7

EXPATXN7

EXPATXP8

EXPATXN8

EXPATXP9

EXPATXN9

EXPATXP10

EXPATXN10

EXPATXP11

EXPATXN11

EXPATXP12

EXPATXN12

EXPATXP13

EXPATXN13

EXPATXP14

EXPATXN14

EXPATXP15

EXPATXN15

DMITXP0

DMITXN0

DMITXP1

DMITXN1

DMITXP2

DMITXN2

DMITXP3

DMITXN3

EXPACOMPO

EXPACOMPI

C10

C9

A9

A8

C8

C7

A7

A6

C6

C5

C2

D2

E3

F3

F1

G1

G3

H3

H1

J1

J3

K3

K1

L1

L3

M3

M1

N1

N3

P3

P1

R1

R3

T3

T1

U1

U3

V3

V5

W5

Y10

W10

EXP_A_TXP0

EXP_A_TXN0

EXP_A_TXP1

EXP_A_TXN1

EXP_A_TXP2

EXP_A_TXN2

EXP_A_TXP3

EXP_A_TXN3

EXP_A_TXP4

EXP_A_TXN4

EXP_A_TXP5

EXP_A_TXN5

EXP_A_TXP6

EXP_A_TXN6

EXP_A_TXP7

EXP_A_TXN7

EXP_A_TXP8

EXP_A_TXN8

EXP_A_TXP9

EXP_A_TXN9

EXP_A_TXP10

EXP_A_TXN10

EXP_A_TXP11

EXP_A_TXN11

EXP_A_TXP12

EXP_A_TXN12

EXP_A_TXP13

EXP_A_TXN13

EXP_A_TXP14

EXP_A_TXN14

EXP_A_TXP15

EXP_A_TXN15

DMI_0TXP

DMI_0TXNDMI_0RXN

DMI_1TXP

DMI_1TXN

DMI_2TXP

DMI_2TXN

DMI_3TXP

DMI_3TXN

GRCOMP

DMI_0TXP <18>

DMI_0TXN <18>

DMI_1TXP <18>

DMI_1TXN <18>

DMI_2TXP <18>

DMI_2TXN <18>

DMI_3TXP <18>

DMI_3TXN <18>

100nH/1008/1.4A/S/X

VCC1_5

100NH/S/1.4A(10LC3-01100C-01)

L23

L8

100nH/1.4A

EXP_A_TXP[0..15]

EXP_A_TXN[0..15]

EXP_A_RXP[0..15]

EXP_A_RXN[0..15]

1

+

EC19

1000U/D/6.3V/8C

VCC1_5PCIEX

R125

24.9/6/1

GRCOMP

EXP_A_TXP[0..15] <17>

EXP_A_TXN[0..15] <17>

EXP_A_RXP[0..15] <17>

EXP_A_RXN[0..15] <17>

VCC1_5PCIEX

BC50

10U/8/Y/10V

BC51

10U/8/Y/10V

VCC1_5PCIEX <13>

10LC3-01100C-01

A A

Title

Size Document Number Re v

Custom

5

4

3

2

Date: Sheet

GIGABYTE

GMCH-PCI E & DMI

8I915G-YFD

1

1.0

of

10 42Wednesday, November 17, 2004

5

4

3

2

1

C38

3.3P/4/N/50V

DDR25V_DAC <13>

C44

0.1U/6/Y/25V/X

3

D

GS

2

2

GHSYNC

GVSYNC

R1490

8.2K/6/X

(TDK PN# MMZ2012S800A)

FB1 30/8/S/3A

FB2 30/8/S/3A

FB3 30/8/S/3A

C39

3.3P/4/N/50V

Q3

2N7002/SOT23

SOT23

1

VGA_R

VGA_G

VGA_B

3.3P/4/N/50V

GAMEVCC

HSYNC

VSYNC

C40

BC675

0.1U/6/Y/25V

3.3P/4/N/50V

C41

GAMEVCC

C42

3.3P/4/N/50V

VGA_R

VGA_G

VGA_B

VGADDCDATA

VGADDCCLK

HSYNC

VSYNC

VGA

1

R

2

G

3

B

11

MS0

12

MS1

4

MS2

15

MS3

9

NC

13

HS

14

VS

5

VSS

6

VSS

7

VSS

8

VSS

10

VSS

VGA/P

GIGABYTE

Title

Size Document Number Re v

Custom

Date: Sheet

GMCH-INTERNAL VGA

8I915G-YFD

1

11 42Wednesday, November 17, 2004

of

1.0

RN3

-RGB

R1485 0/6/X

DOTCLK

R1487 0/6/X

-DOTCLK

R1491 0/6/X

M10

AN19

AL28

AJ14

AH24

AG6

AD30

G12

AJ21

AK21

AK24

AL21

AL20

AK18

AJ24

AJ23

AJ18

AJ20

MTYPE

EXP_SLR

U9G

H16

BSEL0

E15

BSEL1

D17

BSEL2

M16

RSV

F15

RSV

C15

MTYPE

A16

EXP_SLR

B15

RSV

C14

RSV

K15

RSV

L10

VCCDREFSSCLKINP

VCCDREFSSCLKINN

NC

NC

NC

NC

NC

NC

P30

NC

L19

NC

L12

NC

K12

NC

J12

NC

H17

NC

H15

NC

H12

NC

NC

F24

NC

F12

NC

E16

NC

C16

NC

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

GRANTSDALE

CRTHSYNC

CRTVSYNC

CRTRED

CRTGREEN

CRTBLUE

CRTREDB

CRTGREENB

CRTBLUEB

CRTDDCDATA

CRTDDCCLK

DREFCLKINP

DREFCLKINN

CRTREF

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

EXTTS*

RSV

RSV

RSTIN*

PWORK

ICH_SYNC*

NC

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

R146 1K/6/X

R147 1K/6/X

E12

D12

F14

D14

H14

G14

E14

J14

L14

M15

M13

M12

A15

AR35

AR34

AR2

AR1

AP35

AP1

B35

B1

A34

A2

K16

G16

R35

AF7

AG7

M14

A35

V31

V30

U30

V32

Y30

AB29

R31

R30

AA31

AA30

NB_HEATSIN

2

DDCDATA

DDCCLK

DOTCLK

-DOTCLK

REFSET

R133 8.2K/6

TP34

GHSYNC

GVSYNC

R

G

B

-RGB

R1493 0/6

R132 255/6/1

-PFMRST2

PWROK1

-ICHSYNC

C1263

22P/6/N/50V

1

HEAT-SINK

4

DOTCLK <22>

-DOTCLK <22>

C1264

10P/6/N/50V

R126

150/6

FRONT(CHIPSET) REAR(CONN)

DDR25V_MCH

-PFMRST2 <36>

PWROK1 <19,35,36>

-ICHSYNC <19>

R127

150/6

DDCDATA

DDCCLK

R128

150/6

DDR25V_MCH

R140

8.2K/6

D D

C C

B B

BSEL0<6>

BSEL1<6>

BSEL2<6>

MTYPE

EXP_SLR

VCC1_5

NB HEAT SINK FAN

A A

NB_FAN

H1X2/NB_FAN/X

+12V

5

GHSYNC

GVSYNC

R141

8.2K/6

VCC1_5

R129

150/6

C1289

0.1U/6/Y/25V

R130

150/6

VCC3

R131

150/6

VCC3

2

1

SOT23

3

R

G

B

FOR GRANDTSDALE-P

U13-1

14

1

2

7

74LV32/74LCX32/SO14

U13-2

14

4

5

7

74LV32/74LCX32/SO14

U13-3

14

9

10

7

74LV32/74LCX32/SO14

U13-4

14

12

13

7

74LV32/74LCX32/SO14

Q22

2N7002/SOT23

GS

D

3

VCC3

1 2

3 4

5 6

7 8

0/8P4R/X

U10

BAV99/S

132

R138

8.2K/6

Q23

2N7002/SOT23

GS

2

1

SOT23

3

6

8

11

D

3

DDR25V_DAC <13>DDR25V_DAC <13>

U11

BAV99/S

132

R134 33/6

R135 33/6

+12V

VCC

R139

8.2K/6

U12

BAV99/S

132

C43

1U/6/Y/10V

FUSEVCC

R3 8.2K/6

R1489

8.2K/6/X

C37

3.3P/4/N/50V

C347

3.3P/4/N/50V

C348

3.3P/4/N/50V

VGADDCDATA

VGADDCCLK

5

A10

AA10

AA26

AA27

AB28

AB32

AB35

AC27

AC29

AC31

AC32

AD11

AD13

AD16

AD19

AD22

AD26

AD27

AD34

AE12

AE14

AE15

AE17

AE18

AE20

AE21

AE23

AE24

AE28

AE30

AE32

AF10

AF12

AF15

AF18

AF21

AF26

AF29

AF30

AF31

AF32

AF35

AG12

AG13

AG15

AG16

AG18

AG19

AG21

AG22

AG25

AG28

AG29

AG5

AH1

AH11

AH14

AH17

AH20

AH23

AH26

AH29

AH32

AH34

AH5

AH6

AH8

AJ10

AJ13

A18

A26

A3

A30

A33

A5

AA1

AA2

AA3

AA4

AA5

AA6

AA7

AA8

AA9

AE4

AE6

AE9

AF1

AF4

AF6

AF8

D D

C C

B B

A A

U9H

VSS_1

VSS_2

VSS_3

VSS_4

VSS_5

VSS_6

VSS_7

VSS_8

VSS_9

VSS_14

VSS_16

VSS_17

VSS_18

VSS_19

VSS_20

VSS_21

VSS_22

VSS_23

VSS_24

VSS_26

VSS_28

VSS_29

VSS_31

VSS_32

VSS_33

VSS_34

VSS_35

VSS_36

VSS_37

VSS_38

VSS_39

VSS_41

VSS_42

VSS_43

VSS_44

VSS_45

VSS_46

VSS_47

VSS_48

VSS_49

VSS_50

VSS_51

VSS_52

VSS_53

VSS_54

VSS_55

VSS_56

VSS_57

VSS_58

VSS_59

VSS_60

VSS_61

VSS_62

VSS_63

VSS_64

VSS_65

VSS_66

VSS_67

VSS_68

VSS_69

VSS_70

VSS_71

VSS_72

VSS_73

VSS_74

VSS_75

VSS_76

VSS_77

VSS_78

VSS_79

VSS_80

VSS_81

VSS_82

VSS_83

VSS_84

VSS_85

VSS_86

VSS_87

VSS_88

VSS_89

VSS_90

VSS_91

VSS_92

VSS_93

VSS_94

VSS_95

VSS_96

VSS_97

VSS_98

VSS_99

VSS_100

GRANTSDALE

4

AJ15

VSS_101

AJ16

VSS_102

AJ19

VSS_103

AJ22

VSS_104

AJ27

VSS_105

AJ30

VSS_106

AJ32

VSS_107

AJ35

VSS_108

AJ4

VSS_109

AJ9

VSS_110

AK1

VSS_111

AK11

VSS_112

AK14

VSS_113

AK17

VSS_114

AK20

VSS_115

AK23

VSS_116

AK25

VSS_117

AK26

VSS_118

AK28

VSS_119

AK30

VSS_120

AK4

VSS_121

AK6

VSS_122

AK7

VSS_123

AK8

VSS_124

AL10

VSS_125

AL13

VSS_126

AL16

VSS_127

AL19

VSS_128

AL22

VSS_129

AL32

VSS_130

AM29

VSS_131

AM31

VSS_132

AM4

VSS_133

AM6

VSS_134

AM7

VSS_135

AM8

VSS_136

AN1

VSS_137

AP8

VSS_138

AR13

VSS_139

AR17

VSS_140

AR21

VSS_141

AR25

VSS_142

AR3

VSS_143

AR30

VSS_144

AR6

VSS_145

B12

VSS_147

B14

VSS_148

B16

VSS_149

B10

VSS_146

B7

VSS_156

B18

VSS_150

B24

VSS_152

B2

VSS_151

C17

VSS_162

C18

VSS_163

C23

VSS_164

C3

VSS_165

C35

VSS_166

C4

VSS_167

D10

VSS_168

D11

VSS_169

D15

VSS_170

D16

VSS_171

D18

VSS_172

D23

VSS_173

D25

VSS_174

D26

VSS_175

D28

VSS_176

D3

VSS_177

D30

VSS_178

D31

VSS_179

D32

VSS_180

D4

VSS_181

D6

VSS_182

D7

VSS_183

D8

VSS_184

D9

VSS_185

E1

VSS_186

E10

VSS_187

E17

VSS_188

E18

VSS_189

E2

VSS_190

E23

VSS_191

E26

VSS_192

E29

VSS_193

E4

VSS_194

E6

VSS_195

E8

VSS_196

F10

VSS_197

F16

VSS_198

F18

VSS_199

F2

VSS_200

3

U9I

G10

G11

G13

G15

G17

G19

G20

G23

G26

G27

G28

H10

H13

H21

H24

H25

H27

H30

H32

H34

K10

K11

K14

K20

K24

K26

K28

K31

K32

K35

M17

M20

M24

M25

M27

M29

M34

F23

F25

F29

F30

F32

F35

F4

F5

F6

F8

G2

G4

G7

G8

G9

H2

H4

H5

H6

H9

J10

J15

J16

J17

J18

J2

J20

J23

J30

J4

J7

J8

J9

K2

K4

K5

K6

K9

L11

L13

L16

L17

L18

L2

L20

L21

L22

L24

L27

L30

L32

L4

L7

L8

L9

M2

M4

M5

M6

M9

VSS_201

VSS_202

VSS_203

VSS_204

VSS_205

VSS_206

VSS_207

VSS_208

VSS_209

VSS_210

VSS_211

VSS_212

VSS_213

VSS_214

VSS_215

VSS_216

VSS_217

VSS_218

VSS_219

VSS_220

VSS_221

VSS_222

VSS_223

VSS_224

VSS_225

VSS_226

VSS_227

VSS_228

VSS_229

VSS_230

VSS_231

VSS_232

VSS_233

VSS_234

VSS_235

VSS_236

VSS_237

VSS_238

VSS_239

VSS_240

VSS_241

VSS_242

VSS_243

VSS_244

VSS_245

VSS_246

VSS_247

VSS_248

VSS_249

VSS_250

VSS_251

VSS_252

VSS_253

VSS_254

VSS_255

VSS_256

VSS_257

VSS_258

VSS_259

VSS_260

VSS_261

VSS_262

VSS_263

VSS_264

VSS_265

VSS_266

VSS_267

VSS_268

VSS_269

VSS_270

VSS_272

VSS_273

VSS_274

VSS_275

VSS_276

VSS_277

VSS_278

VSS_279

VSS_280

VSS_281

VSS_282

VSS_283

VSS_284

VSS_285

VSS_286

VSS_289

VSS_290

VSS_291

VSS_292

VSS_293

VSS_294

VSS_295

VSS_296

VSS_297

VSS_298

VSS_299

VSS_300

GRANTSDALE

VSS_301

VSS_305

VSS_307

VSS_308

VSS_309

VSS_310

VSS_311

VSS_312

VSS_313

VSS_317

VSS_320

VSS_321

VSS_322

VSS_323

VSS_324

VSS_325

VSS_326

VSS_327

VSS_328

VSS_332

VSS_335

VSS_336

VSS_337

VSS_338

VSS_339

VSS_340

VSS_341

VSS_344

VSS_347

VSS_348

VSS_349

VSS_350

VSS_351

VSS_352

VSS_353

VSS_354

VSS_357

VSS_358

VSS_359

VSS_363

VSS_364

VSS_365

VSS_366

VSS_367

VSS_368

VSS_369

VSS_370

VSS_371

VSS_374

VSS_375

VSS_379

VSS_380

VSS_381

VSS_382

VSS_383

VSS_384

VSS_387

VSS_388

VSS_392

VSS_393

VSS_394

VSS_400

VSS_401

VSS_402

VSS_403

N10

N2

N28

N30

N32

N4

N7

N8

N9

P2

P27

P29

P31

P32

P35

P4

P5

P6

P9

R2

R26

R27

R4

R7

R8

R9

T10

T2

T28

T30

T32

T34

T4

T5

T6

T7

U17

U19

U2

U27

U29

U31

U32

U4

U7

U8

U9

V1

V18

V2

V26

V27

V35

V4

V6

V9

W17

W19

W28

W30

W32

Y29

Y31

Y32

Y34

2

1

Title

Size Document Number Re v

Custom

5

4

3

2

Date: Sheet

GIGABYTE

GMCH-GND

8I915G-YFD

1

1.0

of

12 42Wednesday, November 17, 2004

5

U9C

45mA

VCC1_5

AC11

VCCNCTF

AB11

VCCNCTF

Y20

VCCNCTF

Y19

VCCNCTF

Y17

VCCNCTF

Y16

VCCNCTF

W20

VCCNCTF

W16

VCCNCTF

U20

VCCNCTF

U16

VCCNCTF

T20

VCCNCTF

T19

VCCNCTF

T17

VCCNCTF

T16

VCCNCTF

AA13

VCCNCTF

AA14

VCCNCTF

AA16

VCCNCTF

AA18

VCCNCTF

AA20

VCCNCTF

AA21

VCCNCTF

AA22

VCCNCTF

AA23

VCCNCTF

AA24

VCCNCTF

AB13

VCCNCTF

AB14

VCCNCTF

AB15

VCCNCTF

AB16

VCCNCTF

AB17

VCCNCTF

AB18

VCCNCTF

AB19

VCCNCTF

AB20

VCCNCTF

AB21

VCCNCTF

AB22

VCCNCTF

AB23

VCCNCTF

AB24

VCCNCTF

N13

VCCNCTF

N14

VCCNCTF

N15

VCCNCTF

N16

VCCNCTF

N18

VCCNCTF

N20

VCCNCTF

N21

VCCNCTF

P13

VCCNCTF

P14

VCCNCTF

P15

VCCNCTF

P17

VCCNCTF

P19

VCCNCTF

P21

VCCNCTF

P22

VCCNCTF

R13

VCCNCTF

R14

VCCNCTF

R15

VCCNCTF

R16

VCCNCTF

R18

VCCNCTF

R20

VCCNCTF

R22

VCCNCTF

R23

VCCNCTF

T13

VCCNCTF

T14

VCCNCTF

T15

VCCNCTF

T21

VCCNCTF

T23

VCCNCTF

T24

VCCNCTF

U13

VCCNCTF

U14

VCCNCTF

U22

VCCNCTF

U24

VCCNCTF

V13

VCCNCTF

V14

VCCNCTF

V15

VCCNCTF

V21

VCCNCTF

V23

VCCNCTF

V24

VCCNCTF

W13

VCCNCTF

W14

VCCNCTF

W22

VCCNCTF

W24

VCCNCTF

Y13

VCCNCTF

Y14

VCCNCTF

Y15

VCCNCTF

Y21

VCCNCTF

Y23

VCCNCTF

Y24

VCCNCTF

GRANTSDALE

R148 0.51/6/1

BC60

4.7U/8/Y/10V

10UH/8/100mA/S (10LI2-00100A-01/02/03)

L11

45mA

BC695

4.7U/8/Y/10V

VCCA_GPLL

VCCA_HPLL

VCC1_5

D D

C C

B B

1UH/8/180mA/S(10LI2-07100B-01/10LI2-041001-04)

L10

VCC1_5

A A

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

C56

0.1U/6/Y/25V

C58

0.1U/6/Y/25V

AC25

AB25

AA25

AA11

Y25

Y18

Y11

W25

W11

V25

V20

V16

V11

U25

U11

T25

T18

T11

R25

R11

P25

P11

N25

AD25

N11

M11

AA15

AA17

AA19

N17

N19

P16

P18

P20

R17

R19

R21

T22

U15

U21

U23

V22

W15

W21

W23

Y22

AC12

AC13

AC14

AC15

AC16

AC17

AC18

AC19

AC20

AC21

AC22

N12

N22

N23

N24

P12

P23

P24

R12

R24

T12

U12

V12

W12

Y12

AA12

AB12

AC23

AC24

4

VCC1_5PCIEX<10>

DDR25V_MCH

VCC1_5

VCC1_5

VCC1_5

VCCA_HPLL

VCCA_MPLL

VCCA_DPLLA

VCCA_DPLLB

VCCA_GPLL

DDR25V_MCH

DDR25V_DAC

AD10

AD9

AD8

AD7

AD6

AD5

AD4

AD3

AD2

AD1

AC10

AC9

AC8

AC7

AC6

AC5

AC4

AC3

AC2

AC1

AB10

AB9

AB8

AB7

AB6

AB5

AB4

AB3

AB2

AB1

W18

V19

V17

U18

Y9

Y8

Y7

Y6

Y5

Y4

Y3

Y2

Y1

W9

W8

W7

W6

W4

W3

W2

W1

A17

B17

A12

B13

A14

A13

E13

D13

F13

10UH/8/100mA/S(10LI2-00100A-01/02/03)

L9

55mA

10UH/8/100mA/S(10LI2-00100A-01/02/03)

L12

60mA

U9D

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC3G

VCC3G

VCC3G

VCC3G

VCC3G

VCC3G

VCC3G

VCC3G

VCC3G

VCC3G

VCC3G

VCC3G

VCC3G

VCC3G

VCC3G

VCC3G

VCC3G

VCCA_HPLL

VCCA_SMPLL

VCCA_DPLLA

VCCA_DPLLB

VCCA_3GPLL

VCC2

VCCA_DAC

VCCA_DAC

VSSA_DAC

GRANTSDALE

BC694

4.7U/8/Y/10V

BC696

4.7U/8/Y/10V

3

VCCA_DPLLB

C55

0.1U/6/Y/25V

VCCA_MPLL

C59

0.1U/6/Y/25V

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

AR33

AR31

AR26

AR22

AR18

AR14

AR10

AP28

AP24

AP20

AP16

AP12

AN35

AM32

AM28

AM26

AM25

AM23

AM22

AM20

AM19

AM17

AM16

AM14

AM13

AM11

AM10

AK35

H22

G22

G21

F22

F21

F20

E22

E21

E20

E19

D22

D21

D20

D19

C22

C21

C20

C19

B22

B21

B20

B19

A22

A21

A20

A19

AB30

B28

B5

B6

B7

B8

B9

C1

C11

C13

L15

Y27

C60

0.01U/6/X/50V

DDR25V

VTT_GMCH

2

C45