Page 1

PIC32MX1XX/2XX

32-bit Microcontrollers (up to 128 KB Flash and 32 KB SRAM) with

Audio and Graphics Interfaces, USB, and Advanced Analog

Operating Conditions

• 2.3V to 3.6V, -40ºC to +105ºC, DC to 40 MHz

Core: 40 MHz MIPS32® M4K

• MIPS16e® mode for up to 40% smaller code size

• 1.56 DMIPS/MHz (Dhrystone 2.1) performance

• Code-efficient (C and Assembly) architecture

• Single-cycle (MAC) 32x16 and two-cycle 32x32 multiply

®

Clock Management

• 0.9% internal oscillator

• Programmable PLLs and oscillator clock sources

• Fail-Safe Clock Monitor (FSCM)

• Independent Watchdog Timer

• Fast wake-up and start-up

Power Management

• Low-power management modes (Sleep, Idle)

• Integrated Power-on Reset and Brown-out Reset

• 0.5 mA/MHz dynamic current (typical)

•20 μA I

PD current (typical)

Audio Interface Features

• Data communication: I2S, LJ, RJ, DSP modes

• Control interface: SPI and I

• Master clock:

- Generation of fractional clock frequencies

- Can be synchronized with USB clock

- Can be tuned in run-time

2

C™

Advanced Analog Features

• ADC Module:

- 10-bit 1.1 Msps rate with one S&H

- Up to 10 analog inputs on 28-pin devices and 13

analog inputs on 44-pin devices

• Flexible and independent ADC trigger sources

• Charge Time Measurement Unit (CTMU):

- Supports mTouch™ capacitive touch sensing

- Provides high-resolution time measurement (1 ns)

- On-chip temperature measurement capability

• Comparators:

- Up to three Analog Comparator modules

- Programmable references with 32 voltage points

Timers/Output Compare/Input Capture

• Five General Purpose Timers:

- Five 16-bit and up to two 32-bit Timers/Counters

• Five Output Compare (OC) modules

• Five Input Capture (IC) modules

• Peripheral Pin Select (PPS) to allow function remap

• Real-Time Clock and Calendar (RTCC) module

Communication Interfaces

• USB 2.0-compliant Full-speed OTG controller

• Two UART modules (10 Mbps)

- Supports LIN 2.0 protocols and IrDA

• Two 4-wire SPI modules (20 Mbps)

2

•Two I

• Peripheral Pin Select (PPS) to allow function remap

• Parallel Master Port (PMP)

C modules (up to 1 Mbaud) with SMBus support

®

support

Direct Memory Access (DMA)

• Four channels of hardware DMA with automatic data

size detection

• Two additional channels dedicated for USB

• Programmable Cyclic Redundancy Check (CRC)

Input/Output

• 15 mA source/sink on all I/O pins

• 5V-tolerant pins

• Selectable open drain, pull-ups, and pull-downs

• External interrupts on all I/O pins

Qualification and Class B Support

• AEC-Q100 REVG (Grade 2 -40ºC to +105ºC) planned

• Class B Safety Library, IEC 60730

Debugger Development Support

• In-circuit and in-application programming

•4-wire MIPS

• Unlimited program and six complex data breakpoints

• IEEE 1149.2-compatible (JTAG) boundary scan

®

Enhanced JTAG interface

Packages

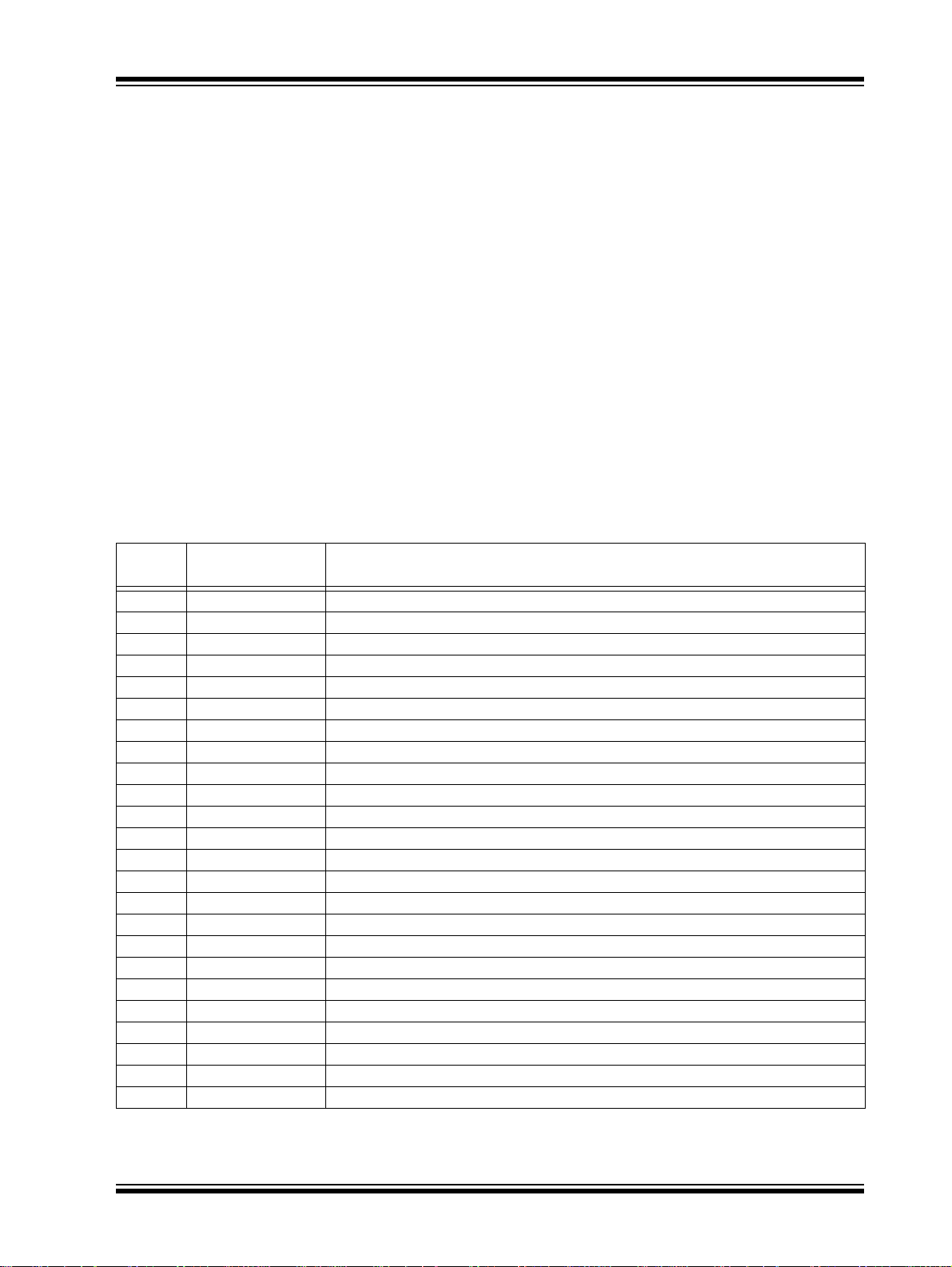

Type SOIC SSOP SPDIP QFN VTLA TQFP

Pin Count 28 28 28 28 44 36 44 44

I/O Pins (up to) 21 21 21 21 34 25 34 34

Contact/Lead Pitch 1.27 0.65 0.100'' 0.65 0.65 0.50 0.50 0.80

Dimensions 17.90x7.50x2.65 10.2x5.3x2 1.365x.285x.135'' 6x6x0.9 8x8x0.9 5x5x0.9 6x6x0.9 10x10x1

Note: All dimensions are in millimeters (mm) unless specified.

© 2011 Microchip Technology Inc. Preliminary DS61168C-page 1

Page 2

PIC32MX1XX/2XX

TABLE 1: PIC32MX1XX GENERAL PURPOSE FAMILY FEATURES

Remappable Peripherals

(1)

(3)

S

UART

2

SPI/I

Analog Comparators

External Interrupts

Device

PIC32MX110F016B 28 16+3 4 20 5/5/5 2253N2Y4/2Y10Y21Y

PIC32MX110F016C 36 16+3 4 24 5/5/5 2253N2Y4/2Y12Y25YVTLA

PIC32MX110F016D 44 16+3 4 32 5/5/5 2253N2Y4/2Y13Y34Y

PIC32MX120F032B 28 32+3 8 20 5/5/5 2253N2Y4/2Y10Y21Y

PIC32MX120F032C 36 32+3 8 24 5/5/5 2253N2Y4/2Y12Y25YVTLA

PIC32MX120F032D 44 32+3 8 32 5/5/5 2253N2Y4/2Y13Y34Y

PIC32MX130F064B 28 64+3 16 20 5/5/5 2253N2Y4/2Y10Y21Y

PIC32MX130F064C 36 64+3 16 24 5/5/5 2253N2Y4/2Y12Y25YVTLA

PIC32MX130F064D 44 64+3 16 32 5/5/5 2253N2Y4/2Y13Y34Y

PIC32MX150F128B 28 128+3 32 20 5/5/5 2253N2Y4/2Y10Y21Y

PIC32MX150F128C 36 128+3 32 24 5/5/5 2253N2Y4/2Y12Y25YVTLA

PIC32MX150F128D 44 128+3 32 32 5/5/5 2253N2Y4/2Y13Y34Y

Note 1: This device features 3 KB of boot Flash memory.

2: Four out of five timers are remappable.

3: Four out of five external interrupts are remappable.

Pins

Data Memory (KB)

Program Memory (KB)

Remappable Pins

/Capture/Compare

(2)

Timers

C™

2

PMP

I

USB On-The-Go (OTG)

CTMU

DMA Channels

(Programmable/Dedicated)

RTCC

10-bit 1 Msps ADC (Channels)

JTAG

I/O Pins

Packages

SOIC,

SSOP,

SPDIP,

QFN

VTLA,

TQFP,

QFN

SOIC,

SSOP,

SPDIP,

QFN

VTLA,

TQFP,

QFN

SOIC,

SSOP,

SPDIP,

QFN

VTLA,

TQFP,

QFN

SOIC,

SSOP,

SPDIP,

QFN

VTLA,

TQFP,

QFN

DS61168C-page 2 Preliminary © 2011 Microchip Technology Inc.

Page 3

TABLE 2: PIC32MX2XX USB FAMILY FEATURES

Remappable Peripherals

(1)

(3)

PIC32MX1XX/2XX

S

UART

2

SPI/I

Analog Comparators

External Interrupts

Device

PIC32MX210F016B 28 16+3 4 19 5/5/5 2253Y2Y4/2Y9Y19Y

PIC32MX210F016C 36 16+3 4 23 5/5/5 2253Y2Y4/2Y12Y23YVTLA

PIC32MX210F016D 44 16+3 4 31 5/5/5 2253Y2Y4/2Y13Y33Y

PIC32MX220F032B 28 32+3 8 19 5/5/5 2253Y2Y4/2Y9Y19Y

PIC32MX220F032C 36 32+3 8 23 5/5/5 2253Y2Y4/2Y12Y23YVTLA

PIC32MX220F032D 44 32+3 8 31 5/5/5 2253Y2Y4/2Y13Y33Y

PIC32MX230F064B 28 64+3 16

PIC32MX230F064C 36 64+3 16

PIC32MX230F064D 44 64+3 16

PIC32MX250F128B 28 128+3 32

PIC32MX250F128C 36 128+3 32

PIC32MX250F128D 44 128+3 32 31 5/5/52253Y2Y4/2Y13Y33Y

Note 1: This device features 3 KB of boot Flash memory.

2: Four out of five timers are remappable.

3: Four out of five external interrupts are remappable.

Pins

Program Memory (KB)

/Capture/Compare

Data Memory (KB)

(2)

Remappable Pins

Timers

19 5/5/52253Y2Y4/2Y9Y19Y

23 5/5/52253Y2Y4/2Y12Y23YVTLA

31 5/5/52253Y2Y4/2Y13Y33Y

19 5/5/52253Y2Y4/2Y9Y19Y

23 5/5/52253Y2Y4/2Y12Y23YVTLA

C™

2

PMP

I

USB On-The-Go (OTG)

CTMU

DMA Channels

(Programmable/Dedicated)

RTCC

10-bit 1 Msps ADC (Channels)

JTAG

I/O Pins

Packages

SOIC,

SSOP,

SPDIP,

QFN

VTLA,

TQFP,

QFN

SOIC,

SSOP,

SPDIP,

QFN

VTLA,

TQFP,

QFN

SOIC,

SSOP,

SPDIP,

QFN

VTLA,

TQFP,

QFN

SOIC,

SSOP,

SPDIP,

QFN

VTLA,

TQFP,

QFN

© 2011 Microchip Technology Inc. Preliminary DS61168C-page 3

Page 4

PIC32MX1XX/2XX

Note 1: The RPn pins can be used by remappable peripherals. See Tab le 1 for the available peripherals and Section 11.3 “Peripheral

Pin Select” for restrictions.

2: Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 “I/O Ports” for more

information.

MCLR

VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/RA0

V

REF-/CVREF-/AN1/RPA1/CTED2/RA1

AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15

PGED1/AN2/C1IND/C2INB/C3IND/RPB0/RB0 CV

REF/AN10/C3INB/RPB14/SCK1/CTED5/PMWR/RB14

PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/RB1 AN11/RPB13/CTPLS/PMRD/RB13

AN4/C1INB/C2IND/RPB2/SDA2/CTED13/RB2

AN12/PMD0/RB12

PGEC2/TMS/RPB11/PMD1/RB11

V

SS

PGED2/RPB10/CTED11/PMD2/RB10

OSC1/CLKI/RPA2/RA2

OSC2/CLKO/RPA3/PMA0/RA3 V

SS

SOSCI/RPB4/RB4

TDO/RPB9/SDA1/CTED4/PMD3/RB9

SOSCO/RPA4/T1CK/CTED9/PMA1/RA4

TCK/RPB8/SCL1/CTED10/PMD4/RB8

V

DD

TDI/RPB7/CTED3/PMD5/INT0/RB7

PGEC3/RPB6/PMD6/RB6

MCLR

AVDD

AVSS

AN5/C1INA/C2INC/RTCC/RPB3/SCL2/RB3

V

SS

VSS

SOSCO/RPA4/T1CK/CTED9/PMA1/RA4

V

DD

MCLR

VSS

VSS

SOSCO/RPA4/T1CK/CTED9/PMA1/RA4

V

DD

28-Pin SOIC, SPDIP, SSOP

(1,2)

= Pins are up to 5V tolerant

MCLR

VSS

VCAP

VSS

SOSCO/RPA4/T1CK/CTED9/PMA1/RA4

V

DD

PGED3/RPB5/PMD7/RB5

MCLR 128AVDD

PGED3/V

REF

+/CV

REF

+/AN0/C3INC/RPA0/CTED1/PMD7/RA0

227AVSS

PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1 3 26 AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15

PGED1/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0 4 25 CV

REF/AN10/C3INB/RPB14/VBUSON/SCK1/CTED5/RB14

PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/PMD1/RB1 5 24 AN11/RPB13/CTPLS/PMRD/RB13

AN4/C1INB/C2IND/RPB2/SDA2/CTED13/PMD2/RB2 6 23 V

USB

AN5/C1INA/C2INC/RTCC/RPB3/SCL2/PMWR/RB3 7 22 PGEC2/RPB11/D-/RB11

V

SS 8 21 PGED2/RPB10/D+/CTED11/RB10

OSC1/CLKI/RPA2/RA2 9 20 V

CAP

OSC2/CLKO/RPA3/PMA0/RA3 10 19 VSS

SOSCI/RPB4/RB4 11 18 TDO/RPB9/SDA1/CTED4/PMD3/RB9

SOSCO/RPA4/T1CK/CTED9/PMA1/RA4 12 17 TCK/RPB8/SCL1/CTED10/PMD4/RB8

V

DD 13 16 TDI/RPB7/CTED3/PMD5/INT0/RB7

TMS/RPB5/USBID/RB5 14 15 V

BUS

PIC32MX220F032B

PIC32MX220F016B

128

227

326

425

524

623

722

821

920

10 19

11 18

12 17

13 16

14 15

PIC32MX120F032B

PIC32MX120F016B

PIC32MX130F064B

PIC32MX150F128B

PIC32MX230F064B

PIC32MX250F128B

Pin Diagrams

DS61168C-page 4 Preliminary © 2011 Microchip Technology Inc.

Page 5

Pin Diagrams (Continued)

28-Pin QFN

(1,2,3)

= Pins are up to 5V tolerant

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 “Peripheral

Pin Select” for restrictions.

2: Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 “I/O Ports” for more

information.

3: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to V

SS externally.

VREF-/CVREF-/AN1/RPA1/CTED2/RA1

V

REF+/CVREF+/AN0/C3INC/RPA0/CTED1/RA0

MCLR

AVDD

AVSS

AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15

CV

REF/AN10/C3INB/RPB14/SCK1/CTED5/PMWR/RB14

28272625242322

PGED1/AN2/C1IND/C2INB/C3IND/RPB0/RB0 121AN11/RPB13/CTPLS/PMRD/RB13

PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/RB1 220AN12/PMD0/RB12

AN4/C1INB/C2IND/RPB2/SDA2/CTED13/RB2 319PGEC2/TMS/RPB11/PMD1/RB11

AN5/C1INA/C2INC/RTCC/RPB3/SCL2/RB3 4

PIC32MX120F032B

18 PGED2/RPB10/CTED11/PMD2/RB10

V

SS 517VCAP

OSC1/CLKI/RPA2/RA2 616VSS

OSC2/CLKO/RPA3/PMA0/RA3 715TDO/RPB9/SDA1/CTED4/PMD3/RB9

891011121314

SOSCI/RPB4/RB4

SOSCO/RPA4/T1CK/CTED9/PMA1/RA4

V

DD

PGED3/RPB5/PMD7/RB5

PGEC3/RPB6/PMD6/RB6

TDI/RPB7/CTED3/PMD5/INT0/RB7

TCK/RPB8/SCL1/CTED10/PMD4/RB8

PIC32MX120F016B

PIC32MX130F064B

PIC32MX150F128B

PIC32MX1XX/2XX

© 2011 Microchip Technology Inc. Preliminary DS61168C-page 5

Page 6

PIC32MX1XX/2XX

28-Pin QFN

(1,2,3)

= Pins are up to 5V tolerant

PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1

PGED3/V

REF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0

MCLR

AVDD

AVSS

AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15

CV

REF/AN10/C3INB/RPB14/VBUSON/SCK1/CTED5/RB14

28272625242322

PGED1/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0 121AN11/RPB13/CTPLS/PMRD/RB13

PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/PMD1/RB1 220V

USB

AN4/C1INB/C2IND/RPB2/SDA2/CTED13/PMD2/RB2 319PGEC2/RPB11/D-/RB11

AN5/C1INA/C2INC/RTCC/RPB3/SCL2/PMWR/RB3 4

PIC32MX220F032B

18 PGED2/RPB10/D+/CTED11/RB10

V

SS 517VCAP

OSC1/CLKI/RPA2/RA2 616VSS

OSC2/CLKO/RPA3/PMA0/RA3 715TDO/RPB9/SDA1/CTED4/PMD3/RB9

891011121314

SOSCI/RPB4/RB4

SOSCO/RPA4/T1CK/CTED9/PMA1/RA4

V

DD

TMS/RPB5/USBID/RB5

V

BUS

TDI/RPB7/CTED3/PMD5/INT0/RB7

TCK/RPB8/SCL1/CTED10/PMD4/RB8

PIC32MX220F016B

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 “Peripheral

Pin Select” for restrictions.

2: Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 “I/O Ports” for more

information.

3: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to V

SS externally.

PIC32MX230F064B

PIC32MX250F128B

Pin Diagrams (Continued)

DS61168C-page 6 Preliminary © 2011 Microchip Technology Inc.

Page 7

Pin Diagrams (Continued)

36-Pin VTLA

(1,2,3)

= Pins are up to 5V tolerant

Note 1: The RPn pins can be used by remappable peripherals. See Tab l e 1 for the available peripherals and Section 11.3 “Peripheral Pin

Select” for restrictions.

2: Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 “I/O Ports” for more

information.

3: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to V

SS externally.

4: This pin function is available on PIC32MX130F064C and PIC32MX150F128C devices only.

PIC32MX120F016C

1

PIC32MX120F032C

10

33 32 31 30 29 28

2

3

4

5

6

24

23

22

21

20

19

11 12 13 14 15

7

8

9

34

35

36

16

17

18

27

26

25

PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/RB1

PGED1/AN2/C1IND/C2INB/C3IND/RPB0/RB0

V

REF-/CVREF-/AN1/RPA1/CTED2/RA1VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/RA0

MCLR

AVDD

AVSS

AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15

CV

REF/AN10/C3INB/RPB14/SCK1/CTED5/PMWR/RB14

AN4/C1INB/C2IND/RPB2/SDA2/CTED13/RB2

AN11/RPB13/CTPLS/PMRD/RB13

AN5/C1INA/C2INC/RTCC/RPB3/SCL2/RB3

AN12/PMD0/RB12

PGED

(4)

/AN6/RPC0/RC0

PGEC2/TMS/RPB11/PMD1/RB11

PGEC

(4)

/AN7/RPC1/RC1

PGED2/RPB10/CTED11/PMD2/RB10

V

DD

VDD

VSS

VCAP

OSC1/CLKI/RPA2/RA2

V

SS

OSC2/CLKO/RPA3/PMA0/RA3

RPC9/CTED7/RC9

SOSCI/RPB4/RB4

TDO/RPB9/SDA1/CTED4/PMD3/RB9

SOSCO/RPA4/T1CK/CTED9/PMA1/RA4

RPC3/RC3

V

SS

VDD

VDD

PGED3/RPB5/PMD7/RB5

PGEC3/RPB6/PMD6/RB6

TDI/RPB7/CTED3/PMD5/INT0/RB7

TCK/RPB8/SCL1/CTED10/PMD4/RB8

PIC32MX130F064C

PIC32MX150F128C

PIC32MX1XX/2XX

© 2011 Microchip Technology Inc. Preliminary DS61168C-page 7

Page 8

PIC32MX1XX/2XX

36-Pin VTLA

(1,2,3)

= Pins are up to 5V tolerant

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 “Peripheral

Pin Select” for restrictions.

2: Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 “I/O Ports” for more

information.

3: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to V

SS externally.

4: This pin function is available on PIC32MX230F064C and PIC32MX250F128C devices only.

PIC32MX220F016C

1

PIC32MX220F032C

10

33 32 31 30 29 28

2

3

4

5

6

24

23

22

21

20

19

11 12 13 14 15

7

8

9

34

35

36

16

17

18

27

26

25

PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/PMD1/RB1

PGED1/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0

PGEC3/V

REF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1

PGED3/V

REF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0

MCLR

AVDD

AVSS

AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15

CV

REF/AN10/C3INB/RPB14/VBUSON/SCK1/CTED5/RB14

AN4/C1INB/C2IND/RPB2/SDA2/CTED13/PMD2/RB2

AN11/RPB13/CTPLS/PMRD/RB13

AN5/C1INA/C2INC/RTCC/RPB3/SCL2/PMWR/RB3

V

USB

PGED4

(4)

/AN6/RPC0/RC0

PGEC2/RPB11/D-/RB11

PGEC4

(4)

/AN7/RPC1/RC1

PGED2/RPB10/D+/CTED11/RB10

V

DD

VCAP

OSC1/CLKI/RPA2/RA2

V

SS

OSC2/CLKO/RPA3/PMA0/RA3

RPC9/CTED7/RC9

SOSCI/RPB4/RB4

TDO/RPB9/SDA1/CTED4/PMD3/RB9

SOSCO/RPA4/T1CK/CTED9/PMA1/RA4

AN12/RPC3/RC3

V

SS

VDD

VDD

TMS/RPB5/USBID/RB5

V

BUS

TDI/RPB7/CTED3/PMD5/INT0/RB7

TCK/RPB8/SCL1/CTED10/PMD4/RB8

VDD

VSS

PIC32MX230F064C

PIC32MX250F128C

Pin Diagrams (Continued)

DS61168C-page 8 Preliminary © 2011 Microchip Technology Inc.

Page 9

Pin Diagrams (Continued)

44-Pin QFN

(1,2,3)

= Pins are up to 5V tolerant

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 “Peripheral

Pin Select” for restrictions.

2: Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 “I/O Ports” for more

information.

3: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to V

SS externally.

4: This pin function is available on PIC32MX130F064D and PIC32MX150F128D devices only.

RPB8/SCL1/CTED10/PMD4/RB8

RPB7/CTED3/PMD5/INT0/RB7

PGEC3/RPB6/PMD6/RB6

PGED3/RPB5/PMD7/RB5

VDDVSS

RPC5/PMA3/RC5

RPC4/PMA4/RC4

RPC3/RC3

TDI/RPA9/PMA9/RA9

SOSCO/RPA4/T1CK/CTED9/RA4

4443424140393837363534

RPB9/SDA1/CTED4/PMD3/RB9 1 33 SOSCI/RPB4/RB4

RPC6/PMA1/RC6 2 32 TDO/RPA8/PMA8/RA8

RPC7/PMA0/RC7 3 31 OSC2/CLKO/RPA3/RA3

RPC8/PMA5/RC8 4 30 OSC1/CLKI/RPA2/RA2

RPC9/CTED7/PMA6/RC9 5 29 V

SS

VSS 6

PIC32MX120F032D

28 VDD

VCAP 7 27 AN8/RPC2/PMA2/RC2

PGED2/RPB10/CTED11/PMD2/RB10 8 26 AN7/RPC1/RC1

PGEC2/RPB11/PMD1/RB11 9 25 AN6/RPC0/RC0

AN12/PMD0/RB12 10 24 AN5/C1INA/C2INC/RTCC/RPB3/SCL2/RB3

AN11/RPB13/CTPLS/PMRD/RB13 11 23 AN4/C1INB/C2IND/RPB2/SDA2/CTED13/RB2

1213141516171819202122

PGED4

(4)

/TMS/PMA10/RA10

PGEC

(4)

/TCK/CTED8/PMA7/RA7

CV

REF/AN10/C3INB/RPB14/SCK1/CTED5/PMWR/RB14

AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15

AV

SS

AVDD

MCLR

VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/RA0

V

REF-/CVREF-/AN1/RPA1/CTED2/RA1

PGED1/AN2/C1IND/C2INB/C3IND/RPB0/RB0

PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/RB1

PIC32MX120F016D

PIC32MX130F064D

PIC32MX150F128D

PIC32MX1XX/2XX

© 2011 Microchip Technology Inc. Preliminary DS61168C-page 9

Page 10

PIC32MX1XX/2XX

44-Pin QFN

(1,2,3)

= Pins are up to 5V tolerant

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 “Peripheral

Pin Select” for restrictions.

2: Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 “I/O Ports” for more

information.

3: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to V

SS externally.

4: This pin function is available on PIC32MX230F064D and PIC32MX250F128D devices only.

RPB8/SCL1/CTED10/PMD4/RB8

RPB7/CTED3/PMD5/INT0/RB7

V

BUS

RPB5/USBID/RB5

VDDVSS

RPC5/PMA3/RC5

RPC4/PMA4/RC4

AN12/RPC3/RC3

TDI/RPA9/PMA9/RA9

SOSCO/RPA4/T1CK/CTED9/RA4

4443424140393837363534

1 33 SOSCI/RPB4/RB4

RPC6/PMA1/RC6 2 32 TDO/RPA8/PMA8/RA8

RPC7/PMA0/RC7 3 31 OSC2/CLKO/RPA3/RA3

RPC8/PMA5/RC8 4 30 OSC1/CLKI/RPA2/RA2

RPC9/CTED7/PMA6/RC9 5 29 V

SS

VSS 6

PIC32MX220F032D

28 VDD

VCAP 7 27 AN8/RPC2/PMA2/RC2

8 26 AN7/RPC1/RC1

PGEC2/RPB11/D-/RB11 9 25 AN6/RPC0/RC0

V

USB 10 24

AN5/C1INA/C2INC/RTCC/RPB3/SCL2/PMWR/CNB3/RB3

AN11/RPB13/CTPLS/PMRD/RB13 11 23

AN4/C1INB/C2IND/RPB2/SDA2/CTED13/PMD2/CNB2/RB2

1213141516171819202122

PGED

(4)

/TMS/PMA10/RA10

PGEC

(4)

/TCK/CTED8/PMA7/RA7

CV

REF/AN10/C3INB/RPB14/VBUSON/SCK1/CTED5/RB14

AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15

AV

SS

AVDD

MCLR

PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0

PGEC3/V

REF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1

PGED1/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0

PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/PMD1/RB1

PGED2/RPB10/D+/CTED11/RB10

RPB9/SDA1/CTED4/PMD3/RB9

PIC32MX220F016D

PIC32MX230F064D

PIC32MX250F128D

Pin Diagrams (Continued)

DS61168C-page 10 Preliminary © 2011 Microchip Technology Inc.

Page 11

Pin Diagrams (Continued)

44-Pin TQFP

(1,2,3)

= Pins are up to 5V tolerant

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 “Peripheral

Pin Select” for restrictions.

2: Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 “I/O Ports” for more

information.

3: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to V

SS externally.

4: This pin function is available on PIC32MX130F064D and PIC32MX150F128D devices only.

RPB8/SCL1/CTED10/PMD4/RB8

RPB7/CTED3/PMD5/INT0/RB7

PGEC3/RPB6/PMD6/RB6

PGED3/RPB5/PMD7/RB5

VDDVSS

RPC5/PMA3/RC5

RPC4/PMA4/RC4

RPC3/RC3

TDI/RPA9/PMA9/RA9

SOSCO/RPA4/T1CK/CTED9/RA4

4443424140393837363534

RPB9/SDA1/CTED4/PMD3/RB9 1 33 SOSCI/RPB4/RB4

RPC6/PMA1/RC6 2 32 TDO/RPA8/PMA8/RA8

RPC7/PMA0/RC7 3 31 OSC2/CLKO/RPA3/RA3

RPC8/PMA5/RC8 4 30 OSC1/CLKI/RPA2/RA2

RPC9/CTED7/PMA6/RC9 5 29 V

SS

VSS 6

PIC32MX120F032D

28 VDD

VCAP 7 27 AN8/RPC2/PMA2/RC2

PGED2/RPB10/CTED11/PMD2/RB10 8 26 AN7/RPC1/RC1

PGEC2/RPB11/PMD1/RB11 9 25 AN6/RPC0/RC0

AN12/PMD0/RB12 10 24 AN5/C1INA/C2INC/RTCC/RPB3/SCL2/RB3

AN11/RPB13/CTPLS/PMRD/RB13 11 23 AN4/C1INB/C2IND/RPB2/SDA2/CTED13/RB2

1213141516171819202122

PGED

(4)

/TMS/PMA10/RA10

PGEC

(4)

/TCK/CTED8/PMA7/RA7

CV

REF/AN10/C3INB/RPB14/SCK1/CTED5/PMWR/RB14

AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15

AV

SS

AVDD

MCLR

VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/RA0

V

REF-/CVREF-/AN1/RPA1/CTED2/RA1

PGED1/AN2/C1IND/C2INB/C3IND/RPB0/RB0

PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/RB1

PIC32MX120F016D

PIC32MX130F064D

PIC32MX150F128D

PIC32MX1XX/2XX

© 2011 Microchip Technology Inc. Preliminary DS61168C-page 11

Page 12

PIC32MX1XX/2XX

44-Pin VTLA

(1,2,3)

= Pins are up to 5V tolerant

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 “Peripheral

Pin Select” for restrictions.

2: Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 “I/O Ports” for more

information.

3: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to V

SS externally.

4: This pin function is available on PIC32MX130F064D and PIC32MX150F128D devices only.

RPB8/SCL1/CTED10/PMD4/RB8

RPB7/CTED3/PMD5/INT0/RB7

PGEC3/RPB6/PMD6/RB6

PGED3/RPB5/PMD7/RB5

VDDVSS

RPC5/PMA3/RC5

RPC4/PMA4/RC4

RPC3/RC3

TDI/RPA9/PMA9/RA9

SOSCO/RPA4/T1CK/CTED9/RA4

RPB9/SDA1/CTED4/PMD3/RB9

SOSCI/RPB4/RB4

RPC6/PMA1/RC6

TDO/RPA8/PMA8/RA8

RPC7/PMA0/RC7

OSC2/CLKO/RPA3/RA3

RPC8/PMA5/RC8

OSC1/CLKI/RPA2/RA2

RPC9/CTED7/PMA6/RC9

V

SS

VSS

PIC32MX120F032D

VDD

VCAP

AN8/RPC2/PMA2/RC2

PGED2/RPB10/CTED11/PMD2/RB10

AN7/RPC1/RC1

PGEC2/RPB11/PMD1/RB11

AN6/RPC0/RC0

AN12/PMD0/RB12

AN5/C1INA/C2INC/RTCC/RPB3/SCL2/RB3

AN4/C1INB/C2IND/RPB2/SDA2/CTED13/RB2

PGEC

(4)

/TCK/CTED8/PMA7/RA7

CV

REF/AN10/C3INB/RPB14/SCK1/CTED5/PMWR/RB14

AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15

AV

SS

AVDD

MCLR

VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/RA0

V

REF-/CVREF-/AN1/RPA1/CTED2/RA1

PGED1/AN2/C1IND/C2INB/C3IND/RPB0/RB0

PIC32MX120F016D

1

10

33

32

31

30

29

28

2

3

4

5

6

24

23

2221201911 12 13 14 15

7

8

9

343536

16 17 18

27

26

25

3738394041424344

PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/RB1

AN11/RPB13/CTPLS/PMRD/RB13

PIC32MX130F064D

PIC32MX150F128D

PGED

(4)

/TMS/PMA10/RA10

Pin Diagrams (Continued)

DS61168C-page 12 Preliminary © 2011 Microchip Technology Inc.

Page 13

Pin Diagrams (Continued)

44-Pin TQFP

(1,2,3)

= Pins are up to 5V tolerant

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 “Peripheral

Pin Select” for restrictions.

2: Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 “I/O Ports” for more

information.

3: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to V

SS externally.

4: This pin function is available on PIC32MX230F064D and PIC32MX250F128D devices only.

RPB8/SCL1/CTED10/PMD4/RB8

RPB7/CTED3/PMD5/INT0/RB7

V

BUS

RPB5/USBID/RB5

VDDVSS

RPC5/PMA3/RC5

RPC4/PMA4/RC4

AN12/RPC3/RC3

TDI/RPA9/PMA9/RA9

SOSCO/RPA4/T1CK/CTED9/RA4

4443424140393837363534

1 33 SOSCI/RPB4/RB4

RPC6/PMA1/RC6 2 32 TDO/RPA8/PMA8/RA8

RPC7/PMA0/RC7 3 31 OSC2/CLKO/RPA3/RA3

RPC8/PMA5/RC8 4 30 OSC1/CLKI/RPA2/RA2

RPC9/CTED7/PMA6/RC9 5 29 V

SS

VSS 6

PIC32MX220F032D

28 VDD

VCAP 7 27 AN8/RPC2/PMA2/RC2

8 26 AN7/RPC1/RC1

PGEC2/RPB11/D-/RB11 9 25 AN6/RPC0/RC0

V

USB 10 24

AN5/C1INA/C2INC/RTCC/RPB3/SCL2/PMWR/CNB3/RB3

AN11/RPB13/CTPLS/PMRD/RB13 11 23

AN4/C1INB/C2IND/RPB2/SDA2/CTED13/PMD2/CNB2/RB2

1213141516171819202122

PGED

(4)

/TMS/PMA10/RA10

PGEC

(4)

/TCK/CTED8/PMA7/RA7

CV

REF/AN10/C3INB/RPB14/VBUSON/SCK1/CTED5/RB14

AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15

AV

SS

AVDD

MCLR

PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0

PGEC3/V

REF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1

PGED1/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0

PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/PMD1/RB1

PGED2/RPB10/D+/CTED11/RB10

RPB9/SDA1/CTED4/PMD3/RB9

PIC32MX220F016D

PIC32MX230F064D

PIC32MX250F128D

PIC32MX1XX/2XX

© 2011 Microchip Technology Inc. Preliminary DS61168C-page 13

Page 14

PIC32MX1XX/2XX

44-Pin VTLA

(1,2,3)

= Pins are up to 5V tolerant

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 “Peripheral

Pin Select” for restrictions.

2: Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 “I/O Ports” for more

information.

3: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to V

SS externally.

4: This pin function is available on PIC32MX230F064D and PIC32MX250F128D devices only.

RPB8/SCL1/CTED10/PMD4/RB8

RPB7/CTED3/PMD5/INT0/RB7

V

BUS

RPB5/USBID/RB5

V

DD

V

SS

RPC5/PMA3/RC5

RPC4/PMA4/RC4

AN12/RPC3/RC3

TDI/RPA9/PMA9/RA9

SOSCO/RPA4/T1CK/CTED9/RA4

SOSCI/RPB4/RB4

RPC6/PMA1/RC6

TDO/RPA8/PMA8/RA8

RPC7/PMA0/RC7

OSC2/CLKO/RPA3/RA3

RPC8/PMA5/RC8

OSC1/CLKI/RPA2/RA2

RPC9/CTED7/PMA6/RC9

V

SS

V

SS

V

DD

V

CAP

AN8/RPC2/PMA2/RC2

AN7/RPC1/RC1

PGEC2/RPB11/D-/RB11

AN6/RPC0/RC0

V

USB

AN5/C1INA/C2INC/RTCC/RPB3/SCL2/PMWR/CNB3/RB3

AN11/RPB13/CTPLS/PMRD/RB13

AN4/C1INB/C2IND/RPB2/SDA2/CTED13/PMD2/CNB2/RB2

PGED

(4)

/TMS/PMA10/RA10

PGEC

(4)

/TCK/CTED8/PMA7/RA7

CV

REF

/AN10/C3INB/RPB14/VBUSON/SCK1/CTED5/RB14

AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15

AV

SS

AV

DD

MCLR

PGED3/V

REF

+/CV

REF

+/AN0/C3INC/RPA0/CTED1/PMD7/RA0

PGEC3/V

REF

-/CV

REF

-/AN1/RPA1/CTED2/PMD6/RA1

PGED1/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0

PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/PMD1/RB1

PGED2/RPB10/D+/CTED11/RB10

RPB9/SDA1/CTED4/PMD3/RB9

PIC32MX220F032D

PIC32MX220F016D

1

10

33

32

31

30

29

28

2

3

4

5

6

24

23

2221201911 12 13 14 15

7

8

9

343536

16 17 18

27

26

25

3738394041424344

PIC32MX230F064D

PIC32MX250F128D

Pin Diagrams (Continued)

DS61168C-page 14 Preliminary © 2011 Microchip Technology Inc.

Page 15

PIC32MX1XX/2XX

Table of Contents

1.0 Device Overview ........................................................................................................................................................................ 19

2.0 Guidelines for Getting Started with 32-bit Microcontrollers ........................................................................................................ 27

3.0 CPU............................................................................................................................................................................................ 33

4.0 Memory Organization ................................................................................................................................................................. 37

5.0 Flash Program Memory.............................................................................................................................................................. 79

6.0 Resets ........................................................................................................................................................................................ 83

7.0 Interrupt Controller ..................................................................................................................................................................... 87

8.0 Oscillator Configuration .............................................................................................................................................................. 95

9.0 Direct Memory Access (DMA) Controller ................................................................................................................................. 105

10.0 USB On-The-Go (OTG)............................................................................................................................................................ 121

11.0 I/O Ports ................................................................................................................................................................................... 143

12.0 Timer1 ...................................................................................................................................................................................... 151

13.0 Timer2/3, Timer4/5 ................................................................................................................................................................... 155

14.0 Input Capture............................................................................................................................................................................ 159

15.0 Output Compare....................................................................................................................................................................... 163

16.0 Serial Peripheral Interface (SPI)............................................................................................................................................... 165

17.0 Inter-Integrated Circuit™ (I

18.0 Universal Asynchronous Receiver Transmitter (UART) ........................................................................................................... 179

19.0 Parallel Master Port (PMP)....................................................................................................................................................... 185

20.0 Real-Time Clock and Calendar (RTCC)................................................................................................................................... 193

21.0 10-bit Analog-to-Digital Converter (ADC) ................................................................................................................................. 203

22.0 Comparator .............................................................................................................................................................................. 211

23.0 Comparator Voltage Reference (CV

24.0 Charge Time Measurement Unit (CTMU) ............................................................................................................................... 217

25.0 Power-Saving Features ........................................................................................................................................................... 221

26.0 Special Features ...................................................................................................................................................................... 225

27.0 Instruction Set .......................................................................................................................................................................... 239

28.0 Development Support............................................................................................................................................................... 241

29.0 Electrical Characteristics .......................................................................................................................................................... 245

30.0 DC and AC Device Characteristics Graphs.............................................................................................................................. 285

31.0 Packaging Information.............................................................................................................................................................. 289

The Microchip Web Site ..................................................................................................................................................................... 315

Customer Change Notification Service .............................................................................................................................................. 315

Customer Support.............................................................................................................................................................................. 315

Reader Response .............................................................................................................................................................................. 316

Product Identification System ............................................................................................................................................................ 317

2

C™).............................................................................................................................................. 173

REF) ................................................................................................................................. 215

© 2011 Microchip Technology Inc. Preliminary DS61168C-page 15

Page 16

PIC32MX1XX/2XX

TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip

products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and

enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department

via E-mail at docerrors@microchip.com or fax the Reader Response Form in the back of this data sheet to (480) 792-4150.

We welcome your feedback.

Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page.

The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current

devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision

of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

• Microchip’s Worldwide Web site; http://www.microchip.com

• Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are

using.

Customer Notification System

Register on our web site at www.microchip.com to receive the most current information on all of our products.

DS61168C-page 16 Preliminary © 2011 Microchip Technology Inc.

Page 17

PIC32MX1XX/2XX

Referenced Sources

This device data sheet is based on the following

individual chapters of the “PIC32 Family Reference

Manual”. These documents should be considered as

the general reference for the operation of a particular

module or device feature.

Note: To access the documents listed below,

browse to the documentation section of

the Microchip web site

(www.microchip.com).

• Section 1. “Introduction” (DS61127)

• Section 2. “CPU” (D S61113)

• Section 3. “Memory Organization” (DS61115)

• Section 5. “Flash Program Memory” (DS61121)

• Section 6. “Oscillator Configuratio n” (DS61112)

• Section 7. “Resets” (D S61118)

• Section 8. “Interrupt Controller” (DS61108)

• Section 9. “Watchdog Timer and Power-up Timer” (DS61114)

• Section 10. “Power-Saving Features” (DS61130)

• Section 12. “I/O Ports” (DS61120)

• Section 13. “Parallel Master Port (PMP)” (DS61128)

• Section 14. “Timers” (DS61105)

• Section 15. “Input Capture” (DS61122)

• Section 16. “Output Compare” (D S 6 1111 )

• Section 17. “10-bit Analog-to-Digital Converter (ADC)” (DS61104)

• Sect i o n 19 . “Comparator” (D S 6 111 0 )

• Section 20. “Comparator Voltage Reference (CV

• Section 21. “Universal Asynchronous Receiver Transmitter (UART)” (DS61107)

• Section 23. “Serial Peripheral Interface (SPI)” (DS61106)

• Section 24. “Inter-Integrated Circuit™ (I

• Section 27. “USB On-The-Go (OTG)” (DS61126)

• Section 29. “Real-Time Clock and Calendar (RTCC)” (DS61125)

• Section 31. “Direct Memory Access (DMA) Controller” (DS61117)

• Section 32. “Configuration” (DS61124)

• Section 33. “Programming and Diagnostics” (DS61129)

• Section 37. “Charge Time Measurement Unit (CTMU)” (DS61167)

2

REF)” (DS61109)

C™)” (DS61116)

© 2011 Microchip Technology Inc. Preliminary DS61168C-page 17

Page 18

PIC32MX1XX/2XX

NOTES:

DS61168C-page 18 Preliminary © 2011 Microchip Technology Inc.

Page 19

PIC32MX1XX/2XX

Note 1: Some features are not available on all device variants.

UART1-2

Comparators 1-3

PORTA

Remappable

PORTB

CTMU

JTAG

Priority

DMAC

ICD

MIPS32® M4K

®

IS DS

EJTAG INT

Bus Matrix

Data RAM

Peripheral Bridge

128

128-bit Wide

Flash

32

32

32

32

Peripheral Bus Clocked by PBCLK

Program Flash Memory

Controller

32

32

32

Interrupt

Controller

BSCAN

PORTC

PMP

I2C1-2

SPI1-2

IC1-5

PWM

OC1-5

OSC1/CLKI

OSC2/CLKO

V

DD, VSS

Timing

Generation

MCLR

Power-up

Timer

Oscillator

Start-up Timer

Power-on

Reset

Watchdog

Timer

Brown-out

Reset

Precision

Reference

Band Gap

FRC/LPRC

Oscillators

Regulator

Voltage

VCAP

OSC/SOSC

Oscillators

PLL

Dividers

SYSCLK

PBCLK

Peripheral Bus Clocked by SYSCLK

USB

PLL-USB

USBCLK

32

RTCC

10-bit ADC

Timer1-5

32

32

CPU Core

Pins

1.0 DEVICE OVERVIEW

Note 1: This data sheet summarizes the features

of the PIC32MX1XX/2XX family of

devices. It is not intended to be a

comprehensive reference source. To

complement the information in this data

sheet, refer to the related section of the

“PIC32 Family Reference Manual”, which

is available from the Microchip web site

(www.microchip.com/PIC32).

2: Some registers and associated bits

described in this section may not be

available on all devices. Refer to

Section 4.0 “Memory Organization” in

this data sheet for device-specific register

and bit information.

FIGURE 1-1: BLOCK DIAGRAM

(1)

This document contains device-specific information for

PIC32MX1XX/2XX devices.

Figure 1-1 illustrates a general block diagram of the

core and peripheral modules in the PIC32MX1XX/2XX

family of devices.

Table 1-1 lists the functions of the various pins shown

in the pinout diagrams.

© 2011 Microchip Technology Inc. Preliminary DS61168C-page 19

Page 20

PIC32MX1XX/2XX

TABLE 1-1: PINOUT I/O DESCRIPTIONS

Pin Number

Pin Name

AN0 27 2 33 19

AN1 28 3 34 20 I Analog

AN2 1 4 35 21 I Analog

AN3 2 5 36 22 I Analog

AN4 3 6 1 23 I Analog

AN5 4 7 2 24 I Analog

AN6 — — 3 25 I Analog

AN7 — — 4 26 I Analog

AN8 — — — 27 I Analog

AN9 23262915IAnalog

AN10 22 25 28 14 I Analog

AN11 21 24 27 11 I Analog

AN12 20

CLKI 6 9 7 30 I ST/CMOS External clock source input. Always

CLKO 7 10 8 31 O — Oscillator crystal output. Connects to

OSC1 6 9 7 30 I ST/CMOS Oscillator crystal input. ST buffer when

OSC2 7 10 8 31 I/O — Oscillator crystal output. Connects to

SOSCI 8 11 9 33 I ST/CMOS 32.768 kHz low-power oscillator crystal

SOSCO 9 12 10 34 O — 32.768 kHz low-power oscillator crystal

REFCLKI PPS PPS PPS PPS I ST Reference Input Clock

REFCLKO PPS PPS PPS PPS O — Reference Output Clock

IC1 PPS PPS PPS PPS I ST Capture Inputs 1-5

IC2 PPS PPS PPS PPS I ST

IC3 PPS PPS PPS PPS I ST

IC4 PPS PPS PPS PPS I ST

IC5 PPS PPS PPS PPS I ST

Legend: CMOS = CMOS compatible input or output Analog = Analog input P = Power

Note 1: Pin numbers are provided for reference only. See the “Pin Diagrams” section for device pin availability.

28-pin

QFN

(2)

ST = Schmitt Trigger input with CMOS levels O = Output I = Input

TTL = TTL input buffer PPS = Peripheral Pin Select — = N/A

2: Pin number for PIC32MX1XX devices only.

3: Pin number for PIC32MX2XX devices only.

28-pin

SSOP/

SPDIP/

SOIC

(2)

23

(1)

36-pin

VTLA

(2)

26

(3)

11

44-pin

QFN

(2)

10

(3)

36

Pin

Type

Buffer

Type

I Analog Analog input channels.

IAnalog

associated with OSC1 pin function.

crystal or resonator in Crystal Oscillator

mode. Optionally functions as CLKO in

RC and EC modes. Always associated

with OSC2 pin function.

configured in RC mode; CMOS

otherwise.

crystal or resonator in Crystal Oscillator

mode. Optionally functions as CLKO in

RC and EC modes.

input; CMOS otherwise.

output.

Description

DS61168C-page 20 Preliminary © 2011 Microchip Technology Inc.

Page 21

TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

Pin Number

(1)

PIC32MX1XX/2XX

Pin Name

28-pin

QFN

28-pin

SSOP/

SPDIP/

36-pin

VTLA

44-pin

QFN

Pin

Type

Buffer

Type

Description

SOIC

OC1 PPS PPS PPS PPS O — Output Compare Output 1

OC2 PPS PPS PPS PPS O — Output Compare Output 2

OC3 PPS PPS PPS PPS O — Output Compare Output 3

OC4 PPS PPS PPS PPS O — Output Compare Output 4

OC5 PPS PPS PPS PPS O — Output Compare Output 5

OCFA PPS PPS PPS PPS I ST Output Compare Fault A Input

OCFB PPS PPS PPS PPS I ST Output Compare Fault B Input

INT0 13 16 17 43 I ST External Interrupt 0

INT1 PPS PPS PPS PPS I ST External Interrupt 1

INT2 PPS PPS PPS PPS I ST External Interrupt 2

INT3 PPS PPS PPS PPS I ST External Interrupt 3

INT4 PPS PPS PPS PPS I ST External Interrupt 4

RA0 27 2 33 19

I/O ST PORTA is a bidirectional I/O port

RA1 28 3 34 20 I/O ST

RA2 6 9 7 30 I/O ST

RA3 7 10 8 31 I/O ST

RA4 9 12 10 34 I/O ST

RA7 — — — 13 I/O ST

RA8 — — — 32 I/O ST

RA9 — — — 35 I/O ST

RA10 — — — 12 I/O ST

RB0 1 4 35 21 I/O ST PORTB is a bidirectional I/O port

RB1 2 5 36 22 I/O ST

RB2 3 6 1 23 I/O ST

RB3 4 7 2 24 I/O ST

RB4 8 11 9 33 I/O ST

RB5 11141541I/OST

RB6 12

(2)

15

(2)

16

(2)

42

(2)

I/O ST

RB7 13161743I/OST

RB8 14171844I/OST

RB9 15 18 19 1 I/O ST

RB10 18 21 24 8 I/O ST

RB11 19 22 25 9 I/O ST

RB12 20

(2)

23

(2)

26

(2)

10

(2)

I/O ST

RB13 21 24 27 11 I/O ST

RB14 22 25 28 14 I/O ST

RB15 23 26 29 15 I/O ST

Legend: CMOS = CMOS compatible input or output Analog = Analog input P = Power

ST = Schmitt Trigger input with CMOS levels O = Output I = Input

TTL = TTL input buffer PPS = Peripheral Pin Select — = N/A

Note 1: Pin numbers are provided for reference only. See the “Pin Diagrams” section for device pin availability.

2: Pin number for PIC32MX1XX devices only.

3: Pin number for PIC32MX2XX devices only.

© 2011 Microchip Technology Inc. Preliminary DS61168C-page 21

Page 22

PIC32MX1XX/2XX

TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

Pin Number

(1)

Pin Name

RC0 — — 3 25 I/O ST PORTC is a bidirectional I/O port

RC1 — — 4 26 I/O ST

RC2 — — — 27 I/O ST

RC3 — — 11 36 I/O ST

RC4 — — — 37 I/O ST

RC5 — — — 38 I/O ST

RC6 — — — 2 I/O ST

RC7 — — — 3 I/O ST

RC8 — — — 4 I/O ST

RC9 — — 20 5 I/O ST

T1CK 9 12 10 34 I ST Timer1 external clock input

T2CK PPS PPS PPS PPS I ST Timer2 external clock input

T3CK PPS PPS PPS PPS I ST Timer3 external clock input

T4CK PPS PPS PPS PPS I ST Timer4 external clock input

T5CK PPS PPS PPS PPS I ST Timer5 external clock input

U1CTS

U1RTS

U1RX PPS PPS PPS PPS I ST

U1TX PPS PPS PPS PPS

U2CTS

U2RTS

U2RX PPS PPS PPS PPS

U2TX PPS PPS PPS PPS

SCK1 22 25 28 14

SDI1 PPS PPS PPS PPS

SDO1 PPS PPS PPS PPS

SS1

SCK2 23 26 29 15 I/O ST Synchronous serial clock input/output for

SDI2 PPS PPS PPS PPS

SDO2 PPS PPS PPS PPS

SS2

SCL1 28 3 34 20 I/O ST Synchronous serial clock input/output for

Legend: CMOS = CMOS compatible input or output Analog = Analog input P = Power

Note 1: Pin numbers are provided for reference only. See the “Pin Diagrams” section for device pin availability.

28-pin

QFN

PPS PPS PPS PPS I ST UART1 clear to send

PPS PPS PPS PPS O — UART1 ready to send

PPS PPS PPS PPS I ST UART2 clear to send

PPS PPS PPS PPS O — UART2 ready to send

PPS PPS PPS PPS I/O ST SPI1 slave synchronization or frame

PPS PPS PPS PPS I/O ST SPI2 slave synchronization or frame

ST = Schmitt Trigger input with CMOS levels O = Output I = Input

TTL = TTL input buffer PPS = Peripheral Pin Select — = N/A

2: Pin number for PIC32MX1XX devices only.

3: Pin number for PIC32MX2XX devices only.

28-pin

SSOP/

SPDIP/

SOIC

36-pin

VTLA

44-pin

QFN

Pin

Type

I/O ST

Buffer

Type

UART1 receive

O — UART1 transmit

IST

O—

IST

O—

IST

O—

UART2 receive

UART2 transmit

Synchronous serial clock input/output for

SPI1

SPI1 data in

SPI1 data out

pulse I/O

SPI2

SPI2 data in

SPI2 data out

pulse I/O

I2C1

Description

DS61168C-page 22 Preliminary © 2011 Microchip Technology Inc.

Page 23

TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

Pin Number

(1)

PIC32MX1XX/2XX

Pin Name

28-pin

QFN

28-pin

SSOP/

SPDIP/

36-pin

VTLA

44-pin

QFN

Pin

Type

Buffer

Type

Description

SOIC

SDA1 27 2 33 19 I/O ST Synchronous serial data input/output for

I2C1

SCL2 12

(2)

15

(2)

16

(2)

42

(2)

I/O ST Synchronous serial clock input/output for

I2C2

SDA2 11

(2)

14

(2)

15

(2)

41

(2)

I/O ST Synchronous serial data input/output for

I2C2

TMS

19

11

(2)

(3)

22

14

(2)

(3)

25

15

(2)

(3)

12 I ST JTAG Test mode select pin

TCK 14 17 18 13 I ST JTAG test clock input pin

TDI 13 16 17 35 O — JTAG test data input pin

TDO 15 18 19 32 O — JTAG test data output pin

RTCC 4 7 2 24 I ST Real-Time Clock alarm output

VREF- 28 3 34 20 I Analog

C

VREF+ 27 2 33 19 I Analog Comparator Voltage Reference (high)

C

VREFOUT 22 25 28 14 O Analog Comparator Voltage Reference output

C

C1INA 4 7 2 24

I Analog Comparator Inputs

Comparator Voltage Reference (low)

C1INB 3 6 1 23 I Analog

C1INC 2 5 36 22 I Analog

C1IND 1 4 35 21 I Analog

C2INA 2 5 36 22 I Analog

C2INB 1 4 35 21 I Analog

C2INC 4 7 2 24 I Analog

C2IND 3 6 1 23 I Analog

C3INA 23 262915IAnalog

C3INB 22 252814IAnalog

C3INC 27 2 33 19 I Analog

C3IND 1 4 35 21 I Analog

C1OUT PPS PPS PPS PPS O — Comparator Outputs

C2OUT PPS PPS PPS PPS O —

C3OUT PPS PPS PPS PPS O —

Legend: CMOS = CMOS compatible input or output Analog = Analog input P = Power

ST = Schmitt Trigger input with CMOS levels O = Output I = Input

TTL = TTL input buffer PPS = Peripheral Pin Select — = N/A

Note 1: Pin numbers are provided for reference only. See the “Pin Diagrams” section for device pin availability.

2: Pin number for PIC32MX1XX devices only.

3: Pin number for PIC32MX2XX devices only.

© 2011 Microchip Technology Inc. Preliminary DS61168C-page 23

Page 24

PIC32MX1XX/2XX

TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

Pin Number

(1)

Pin Name

28-pin

QFN

28-pin

SSOP/

SPDIP/

36-pin

VTLA

44-pin

QFN

Pin

Type

Buffer

Type

Description

SOIC

PMA0 7 10 8 3 I/O TTL/ST Parallel Master Port Address bit 0 input

(Buffered Slave modes) and output

(Master modes)

PMA1 9 12 10 2 I/O TTL/ST Parallel Master Port Address bit 1 input

(Buffered Slave modes) and output

(Master modes)

PMA2 — — 27 O — Parallel Master Port address

PMA3 — — 38 O —

(Demultiplexed Master modes)

PMA4 — — 37 O —

PMA5 — — 4 O —

PMA6 — — 5 O —

PMA7 — — 13 O —

PMA8 — — 32 O —

PMA9 — — 35 O —

PMA10 — — 12 O —

PMCS1 23 26 29 15 O — Parallel Master Port Chip Select 1 strobe

(2)

PMD0

PMD1

PMD2

20

19

18

(3)

1

(2)

(3)

2

(2)

(3)

3

PMD3 15 18 19 1

23

22

21

(2)

(3)

4

(2)

(3)

5

(2)

(3)

6

26

35

25

36

24

(2)

(3)

(2)

(3)

(2)

(3)

1

10

21

9

22

8

23

(2)

(2)

(2)

(3)

(3)

(3)

I/O TTL/ST

I/O TTL/ST

I/O TTL/ST

Parallel Master Port data (Demultiplexed

Master mode) or address/data

(Multiplexed Master modes)

I/O TTL/ST

PMD4 14 17 18 44 I/O TTL/ST

PMD5 13 16 17 43 I/O TTL/ST

PMD6 12

28

PMD7 11

27

(2)

(3)

(2)

(3)

15

14

(2)

(3)

3

(2)

(3)

2

16

34

15

33

(2)

(3)

(2)

(3)

42

20

41

19

(2)

(3)

(2)

(3)

I/O TTL/ST

I/O TTL/ST

PMRD 21 24 27 11 O — Parallel Master Port read strobe

PMWR

22

(2)

(3)

4

25

(2)

(3)

7

28

(2)

(3)

2

14

24

(2)

(3)

O — Parallel Master Port write strobe

VBUS 12 15 16 42 I Analog USB bus power monitor

VUSB 20 23 26 10 P — USB internal transceiver supply. If the

USB module is not used, this pin must be

connected to V

BUSON 22 25 28 14 O — USB Host and OTG bus power control

V

DD.

output

D+ 18 21 24 8 I/O Analog USB D+

D- 19 22 25 9 I/O Analog USB D-

Legend: CMOS = CMOS compatible input or output Analog = Analog input P = Power

ST = Schmitt Trigger input with CMOS levels O = Output I = Input

TTL = TTL input buffer PPS = Peripheral Pin Select — = N/A

Note 1: Pin numbers are provided for reference only. See the “Pin Diagrams” section for device pin availability.

2: Pin number for PIC32MX1XX devices only.

3: Pin number for PIC32MX2XX devices only.

DS61168C-page 24 Preliminary © 2011 Microchip Technology Inc.

Page 25

TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

Pin Number

(1)

PIC32MX1XX/2XX

Pin Name

28-pin

QFN

28-pin

SSOP/

SPDIP/

36-pin

VTLA

44-pin

QFN

Pin

Type

Buffer

Type

Description

SOIC

USBID 11 14 15 41 I ST USB OTG ID detect

CTED1 27 2 33 19 I ST CTMU External Edge Input

CTED2 28 3 34 20 I ST

CTED313161743IST

CTED4 15 18 19 1 I ST

CTED522252814IST

CTED623262915IST

CTED7 — — 20 5 I ST

CTED8 — — — 13 I ST

CTED9 9 12 10 34 I ST

CTED10 14 17 18 44 I ST

CTED11 18 21 24 8 I ST

CTED12 2 5 36 22 I ST

CTED13 3 6 1 23 I ST

CTPLS 21 24 27 11 O — CTMU Pulse Output

PGED1 1 4 35 21 I/O ST Data I/O pin for Programming/Debugging

Communication Channel 1

PGEC1 2 5 36 22 I ST Clock input pin for

Programming/Debugging

Communication Channel 1

PGED2 18 21 24 8 I/O ST Data I/O pin for Programming/Debugging

Communication Channel 2

PGEC2 19 22 25 9 I ST Clock input pin for

Programming/Debugging

Communication Channel 2

(2)

PGED3

PGEC3

11

27

12

28

(3)

(2)

(3)

PGED4 — — 3 12

PGEC4 — — 4 13

14

15

(2)

(3)

2

(2)

(3)

3

15

33

16

34

(2)

(3)

(2)

(3)

41

19

42

20

(2)

(3)

(2)

(3)

I/O ST

IST

I/O ST

IST

Data I/O pin for Programming/Debugging

Communication Channel 3

Clock input pin for Programming/

Debugging Communication Channel 3

Data I/O pin for Programming/Debugging

Communication Channel 4

Clock input pin for Programming/

Debugging Communication Channel 4

Legend: CMOS = CMOS compatible input or output Analog = Analog input P = Power

ST = Schmitt Trigger input with CMOS levels O = Output I = Input

TTL = TTL input buffer PPS = Peripheral Pin Select — = N/A

Note 1: Pin numbers are provided for reference only. See the “Pin Diagrams” section for device pin availability.

2: Pin number for PIC32MX1XX devices only.

3: Pin number for PIC32MX2XX devices only.

© 2011 Microchip Technology Inc. Preliminary DS61168C-page 25

Page 26

PIC32MX1XX/2XX

TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

Pin Number

(1)

Pin Name

MCLR 26 1 32 18 I/P ST Master Clear (Reset) input. This pin is an

DD 25 28 31 17 P — Positive supply for analog modules. This

AV

SS 24 27 30 16 P — Ground reference for analog modules

AV

DD 10 13 5, 13, 14,

V

CAP 17 20 22 7 P — CPU logic filter capacitor connection

V

SS 5, 16 8, 19 6, 12, 21 6, 29, 39 P — Ground reference for logic and I/O pins.

V

REF+ 27 2 33 19 I Analog Analog voltage reference (high) input

V

VREF- 28 3 34 20 I Analog Analog voltage reference (low) input

Legend: CMOS = CMOS compatible input or output Analog = Analog input P = Power

Note 1: Pin numbers are provided for reference only. See the “Pin Diagrams” section for device pin availability.

28-pin

QFN

ST = Schmitt Trigger input with CMOS levels O = Output I = Input

TTL = TTL input buffer PPS = Peripheral Pin Select — = N/A

2: Pin number for PIC32MX1XX devices only.

3: Pin number for PIC32MX2XX devices only.

28-pin

SSOP/

SPDIP/

SOIC

36-pin

VTLA

23

44-pin

QFN

28, 40 P — Positive supply for peripheral logic and

Pin

Type

Buffer

Type

Description

active-low Reset to the device.

pin must be connected at all times.

I/O pins

This pin must be connected at all times.

DS61168C-page 26 Preliminary © 2011 Microchip Technology Inc.

Page 27

PIC32MX1XX/2XX

PIC32

VDD

VSS

VDD

VSS

VSS

VDD

AVDD

AVSS

VDD

VSS

C

R

V

DD

MCLR

0.1 µF

Ceramic

VCAP

10Ω

R1

CBP

0.1 µF

Ceramic

C

BP

0.1 µF

Ceramic

C

BP

0.1 µF

Ceramic

C

BP

0.1 µF

Ceramic

C

BP

CEFC

VUSB

(1)

Note 1: If the USB module is not used, this pin

must be connected to VDD.

2.0 GUIDELINES FOR GETTING STARTED WITH 32-BIT MICROCONTROLLERS

Note 1: This data sheet summarizes the features

of the PIC32MX1XX/2XX family of

devices. It is not intended to be a

comprehensive reference source. To

complement the information in this data

sheet, refer to the related section of the

“PIC32 Family Reference Manual”, which

is available from the Microchip web site

(www.microchip.com/PIC32).

2: Some registers and associated bits

described in this section may not be

available on all devices. Refer to

Section 4.0 “Memory Organization” in

this data sheet for device-specific register

and bit information.

2.1 Basic Connection Requirements

Getting started with the PIC32MX1XX/2XX family of

32-bit Microcontrollers (MCUs) requires attention to a

minimal set of device pin connections before proceeding with development. The following is a list of pin

names, which must always be connected:

DD and VSS pins

• All V

(see Section 2.2 “Decoupling Capacitors”)

• All AVDD and AVSS pins, even if the ADC module

is not used

(see Section 2.2 “Decoupling Capac it ors”)

CAP pin

•V

(see Section 2.3 “Capacitor on Internal

Vo ltage Regulator (V

•MCLR

pin

(see Section 2.4 “Master Clear (MCLR) Pin”)

• PGECx/PGEDx pins, used for In-Circuit Serial

Programming (ICSP™) and debugging purposes

(see Section 2.5 “ICSP Pins”)

• OSC1 and OSC2 pins, when external oscillator

source is used

(see Section 2.7 “External Oscillator Pins”)

The following pin may be required, as well:

REF+/VREF- pins, used when external voltage

V

reference for the ADC module is implemented.

Note: The AV

connected, regardless of ADC use and

the ADC voltage reference source.

2.2 Decoupling Capacitors

The use of decoupling capacitors on power supply

pins, such as V

See Figure 2-1.

© 2011 Microchip Technology Inc. Preliminary DS61168C-page 27

DD, VSS, AVDD and AVSS is required.

CAP)”)

DD and AVSS pins must be

Consider the following criteria when using decoupling

capacitors:

• Value and type of capacitor: A value of 0.1 µF

(100 nF), 10-20V is recommended. The capacitor

should be a low Equivalent Series Resistance (lowESR) capacitor and have resonance frequency in

the range of 20 MHz and higher. It is further

recommended that ceramic capacitors be used.

• Placement on the printed circuit board: The

decoupling capacitors should be placed as close to

the pins as possible. It is recommended that the

capacitors be placed on the same side of the board

as the device. If space is constricted, the capacitor

can be placed on another layer on the PCB using a

via; however, ensure that the trace length from the

pin to the capacitor is within one-quarter inch

(6 mm) in length.

• Handling high frequency noise: If the board is

experiencing high frequency noise, upward of tens

of MHz, add a second ceramic-type capacitor in parallel to the above described decoupling capacitor.

The value of the second capacitor can be in the

range of 0.01 µF to 0.001 µF. Place this second

capacitor next to the primary decoupling capacitor.

In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the

power and ground pins as possible. For example,

0.1 µF in parallel with 0.001 µF.

• Maximizing performance: On the board layout

from the power supply circuit, run the power and

return traces to the decoupling capacitors first, and

then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally

important is to keep the trace length between the

capacitor and the power pins to a minimum thereby

reducing PCB track inductance.

FIGURE 2-1: RECOMMENDED

MINIMUM CONNECTION

Page 28

PIC32MX1XX/2XX

Note 1: R ≤ 10 kΩ is recommended. A suggested

starting value is 10 kΩ. Ensure that the MCLR

pin VIH and VIL specifications are met.

2: R1 ≤ 470Ω will limit any current flowing into

MCLR

from the external capacitor C, in the

event of MCLR

pin breakdown, due to

Electrostatic Discharge (ESD) or Electrical

Overstress (EOS). Ensure that the MCLR

pin

V

IH and VIL specifications are met.

3: The capacitor can be sized to prevent uninten-

tional Resets from brief glitches or to extend

the device Reset period during POR.

C

R1

R

V

DD

MCLR

PIC32

JP

2.2.1 BULK CAPACITORS

The use of a bulk capacitor is recommended to improve

power supply stability. Typical values range from 4.7 µF

to 47 µF. This capacitor should be located as close to

the device as possible.

2.3 Capacitor on Internal Voltage

Regulator (V

2.3.1 INTERNAL REGULATOR MODE

A low-ESR (1 ohm) capacitor is required on the VCAP

pin, which is used to stabilize the internal voltage regulator output. The VCAP pin must not be connected to

VDD, and must have a CEFC capacitor, with at least a

6V rating, connected to ground. The type can be

ceramic or tantalum. Refer to Section 29.0 “Electrical

Characteristics” for additional information on C

specifications.

CAP)

EFC

2.4 Master Clear (MCLR) Pin

The MCLR pin provides for two specific device

functions:

• Device Reset

• Device programming and debugging

Pulling The MCLR

Figure 2-2 illustrates a typical MCLR circuit. During

device programming and debugging, the resistance

and capacitance that can be added to the pin must

be considered. Device programmers and debuggers

drive the MCLR

levels (VIH and VIL) and fast signal transitions must

not be adversely affected. Therefore, specific values

of R and C will need to be adjusted based on the

application and PCB requirements.

For example, as illustrated in Figure 2-2, it is

recommended that the capacitor C, be isolated from

the MCLR

pin during programming and debugging

operations.

Place the components illustrated in Figure 2-2 within

one-quarter inch (6 mm) from the MCLR

FIGURE 2-2: EXAMPLE OF MCLR PIN

pin low generates a device Reset.

pin. Consequently, specific voltage

pin.

CONNECTIONS

(1,2,3)

DS61168C-page 28 Preliminary © 2011 Microchip Technology Inc.

Page 29

PIC32MX1XX/2XX

2.5 ICSP Pins

The PGECx and PGEDx pins are used for In-Circuit

Serial Programming™ (ICSP™) and debugging purposes. It is recommended to keep the trace length

between the ICSP connector and the ICSP pins on the

device as short as possible. If the ICSP connector is

expected to experience an ESD event, a series resistor

is recommended, with the value in the range of a few

tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes and capacitors on the

PGECx and PGEDx pins are not recommended as they

will interfere with the programmer/debugger communications to the device. If such discrete components are

an application requirement, they should be removed

from the circuit during programming and debugging.

Alternatively, refer to the AC/DC characteristics and

timing requirements information in the respective

device Flash programming specification for information

on capacitive loading limits and pin input voltage high

IH) and input low (VIL) requirements.

(V

Ensure that the “Communication Channel Select” (i.e.,

PGECx/PGEDx pins) programmed into the device

matches the physical connections for the ICSP to

MPLAB

For more information on ICD 3 and REAL ICE

connection requirements, refer to the following

documents that are available on the Microchip web

site.

• “Using MPLAB

• “MPLAB

• “MPLAB® REAL ICE™ In-Circuit Debugger

• “Using MPLAB

®

ICD 3 or MPLAB REAL ICE™.

®

®

User’s Guide” DS51616

DS51749

ICD 3” (poster) DS51765

ICD 3 Design Advisory” DS51764

®

REAL ICE™ Emulator” (poster)

2.6 JTAG

The TMS, TDO, TDI and TCK pins are used for testing

and debugging according to the Joint Test Action

Group (JTAG) standard. It is recommended to keep the

trace length between the JTAG connector and the

JTAG pins on the device as short as possible. If the

JTAG connector is expected to experience an ESD

event, a series resistor is recommended, with the value

in the range of a few tens of Ohms, not to exceed 100

Ohms.

Pull-up resistors, series diodes and capacitors on the

TMS, TDO, TDI and TCK pins are not recommended

as they will interfere with the programmer/debugger

communications to the device. If such discrete components are an application requirement, they should be

removed from the circuit during programming and

debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the

respective device Flash programming specification for

information on capacitive loading limits and pin input

voltage high (V

IH) and input low (VIL) requirements.

© 2011 Microchip Technology Inc. Preliminary DS61168C-page 29

Page 30

PIC32MX1XX/2XX

Main Oscillator

Guard Ring

Guard Trace

Secondary

Oscillator

2.7 External Oscillator Pins

Many MCUs have options for at least two oscillators: a

high-frequency primary oscillator and a low-frequency

secondary oscillator (refer to Section 8.0 “Oscillator

Configuration” for details).

The oscillator circuit should be placed on the same side

of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The

load capacitors should be placed next to the oscillator

itself, on the same side of the board. Use a grounded

copper pour around the oscillator circuit to isolate them

from surrounding circuits. The grounded copper pour

should be routed directly to the MCU ground. Do not

run any signal traces or power traces inside the ground

pour. Also, if using a two-sided board, avoid any traces

on the other side of the board where the crystal is

placed. A suggested layout is illustrated in Figure 2-3.

FIGURE 2-3: SUGGESTED OSCILLATOR

CIRCUIT PLACEMENT

2.8 Configuration of Analog and Digital Pins During ICSP Operations

If MPLAB ICD 2, ICD 3 or REAL ICE is selected as a

debugger, it automatically initializes all of the analog-todigital input pins (ANx) as “digital” pins by setting all bits

in the ADPCFG register.

The bits in this register that correspond to the analogto-digital pins that are initialized by MPLAB ICD 2, ICD

3 or REAL ICE, must not be cleared by the user

application firmware; otherwise, communication errors

will result between the debugger and the device.

If your application needs to use certain analog-to-digital

pins as analog input pins during the debug session, the

user application must clear the corresponding bits in

the ADPCFG register during initialization of the ADC

module.

When MPLAB ICD 2, ICD 3 or REAL ICE is used as a

programmer, the user application firmware must correctly configure the ADPCFG register. Automatic initialization of this register is only done during debugger

operation. Failure to correctly configure the register(s)

will result in all analog-to-digital pins being recognized

as analog input pins, resulting in the port value being

read as a logic ‘0’, which may affect user application

functionality.

2.9 Unused I/Os

Unused I/O pins should not be allowed to float as

inputs. They can be configured as outputs and driven

to a logic-low state.

Alternatively, inputs can be reserved by connecting the

pin to V

the pin as an input.

SS through a 1k to 10k resistor and configuring

DS61168C-page 30 Preliminary © 2011 Microchip Technology Inc.

Page 31

PIC32MX1XX/2XX

CTMU

Current Source

ADC

Microchip

mTouch™

Library

User

Application

Microchip

Graphics

Library

Read the Touch Sensors

Process Samples

Display Data

Parallel

Master

Port

LCD Controller

Frame

Buffer

Display

Controller

PMPD<7:0>

LCD

Panel

PIC32MX120F032D

To AN6 To AN7 To AN8 To AN11

C1

R3

C2

R2

R3

R1

C5

C5

C5

C1

R1

R1

R1

C3

R2

C3

R2

C1

R2

C2

R3

C2

R3

C3

AN0

AN1

AN11

To A N 0

To A N 1

To AN5

AN9

PMPWR

To A N 9

R1

C4

R2

C4

R3

C4

Audio

Codec

Display

PMP

I

2

S

SPI

USB

USB

PMPD<7:0>

3

3

Stereo Headphones

Speaker

PIC32MX220F032D

Host

PMPWR

MMC SD

3

SDI

2.10 Typical Application Connection Examples

Examples of typical application connections are shown

in Figure 2-4 and Figure 2-5.

FIGURE 2-4: CAPACITIVE TOUCH SENSING WITH GRAPHICS APPLICATION

FIGURE 2-5: AUDIO PLAYBACK APPLICATION

© 2011 Microchip Technology Inc. Preliminary DS61168C-page 31

Page 32

PIC32MX1XX/2XX

NOTES:

DS61168C-page 32 Preliminary © 2011 Microchip Technology Inc.

Page 33

PIC32MX1XX/2XX

Dual Bus I/F

System

Coprocessor

MDU

FMT

TAP

EJTAG

Power

Management

Off-Chip

Debug I/F

Execution

Core

(RF/ALU/Shift)

Bus Matrix

Bus Interface

CPU

3.0 CPU

Note 1: This data sheet summarizes the features

of the PIC32MX1XX/2XX family of

devices. It is not intended to be a

comprehensive reference source. To

complement the information in this data

sheet, refer to Section 2. “CPU”

(DS61113) in the “PIC32 Family

Reference Manual”, which is available

from the Microchip web site

(www.microchip.com/PIC32). Resources

for the MIPS32

are available at http://www.mips.com.

2: Some registers and associated bits

described in this section may not be

available on all devices. Refer to

Section 4.0 “Memory Organization” in

this data sheet for device-specific register

and bit information.

The the MIPS32® M4K® Processor Core is the heart of

the PIC32MX1XX/2XX family processor. The CPU

fetches instructions, decodes each instruction, fetches

source operands, executes each instruction and writes

the results of instruction execution to the proper

destinations.

3.1 Features

• 5-stage pipeline

• 32-bit address and data paths

• MIPS32 Enhanced Architecture (Release 2)

- Multiply-accumulate and multiply-subtract

instructions

- Targeted multiply instruction

- Zero/One detect instructions

- WAIT instruction

- Conditional move instructions (MOVN, MOVZ)

- Vectored interrupts

®

M4K® Processor Core

- Programmable exception vector base

- Atomic interrupt enable/disable

- GPR shadow registers to minimize latency

for interrupt handlers

- Bit field manipulation instructions

• MIPS16e

- 16-bit encoding of 32-bit instructions to

- Special PC-relative instructions for efficient

- SAVE and RESTORE macro instructions for

- Improved support for handling 8 and 16-bit

• Simple Fixed Mapping Translation (FMT)

mechanism

• Simple dual bus interface

- Independent 32-bit address and data busses

- Transactions can be aborted to improve