Gennum Corporation GS9023-CFJ Datasheet

GENNUM CORPORATION P.O. Box 489, Stn. A, Burlington, Ontario, Canada L7R 3Y3

Tel. +1 (905) 632-2996 Fax. +1 (905) 632-5946 E-mail: info@gennum.com

www.gennum.com

Revision Date: November 2000 Document No. 522 - 45 - 05

PRELIMINARY DATA SHEET

GS9023

FEATURES

• single chip embedded audio solution

• operates as an embedded audio mul tiplexer or

demultiplexer

• full support for 48kHz synchronous 20/24 bit audio

• 4 channels of audio per GS9023

• cascadable architecture supports additional audio

channels

• multiplexes and demultiplexes arbitrary ANC data

packets

• support for 143, 177, 270, 360 and 540 Mb/s video

standards

• full processing of audio parity, channel status and

user data

• multiplexes and demultiplexes audio control packets

• EDH generation and insertion when in Multiplex Mode

• 3.3V core with 3.3V or 5V I/O (requires 5V supply)

• complies with SMPTE 272M A, B, and C

APPLICATIONS

SDI Embedded Audio

DESCRIPTION

The GS9023 is a highly integrated, single chip solution for

the multiplexing/demultiplexing of digital audio channels

into and out of digital video signals. The GS9023 supports

the multiplexing/demultiplexing of 20 or 24 bit synchronous

audio data with a 48kHz sample rate. Audio signals with

different sample rates may be sample rate converted to

48kHz before and after the GS9023 using audio sample

rate converters.

Each GS9023 supports all the processing required to

handle the multiplexing/demultiplexing of four digital audio

channels. To simplify system design, the GS9023

seamlessly integrates with common AES/EBU digital audio

receivers and transmitters. The cascadable architecture

allows for the multiplexing/demultiplexing of additional

audio channels with no external glue logic.

The GS9023 supports video standards with rates from

143Mb/s to 540Mb/s. When in Multiplex Mode, the GS9023

supports the generation and insertion of EDH information

according to SMPTE RP165. In combination with Gennum’s

GS9032, the GS9023 provides a low power, highly

integrated two chip solution for SDI transmit applications. In

combination with Gennum’s GS7005, the GS9023 provides

a low power, highly integrated two chip solution for SDI

receive applications.

The GS9023 requires a 3.3V power supply for internal core

logic and a 3.3V or 5V power supply for device I/O.

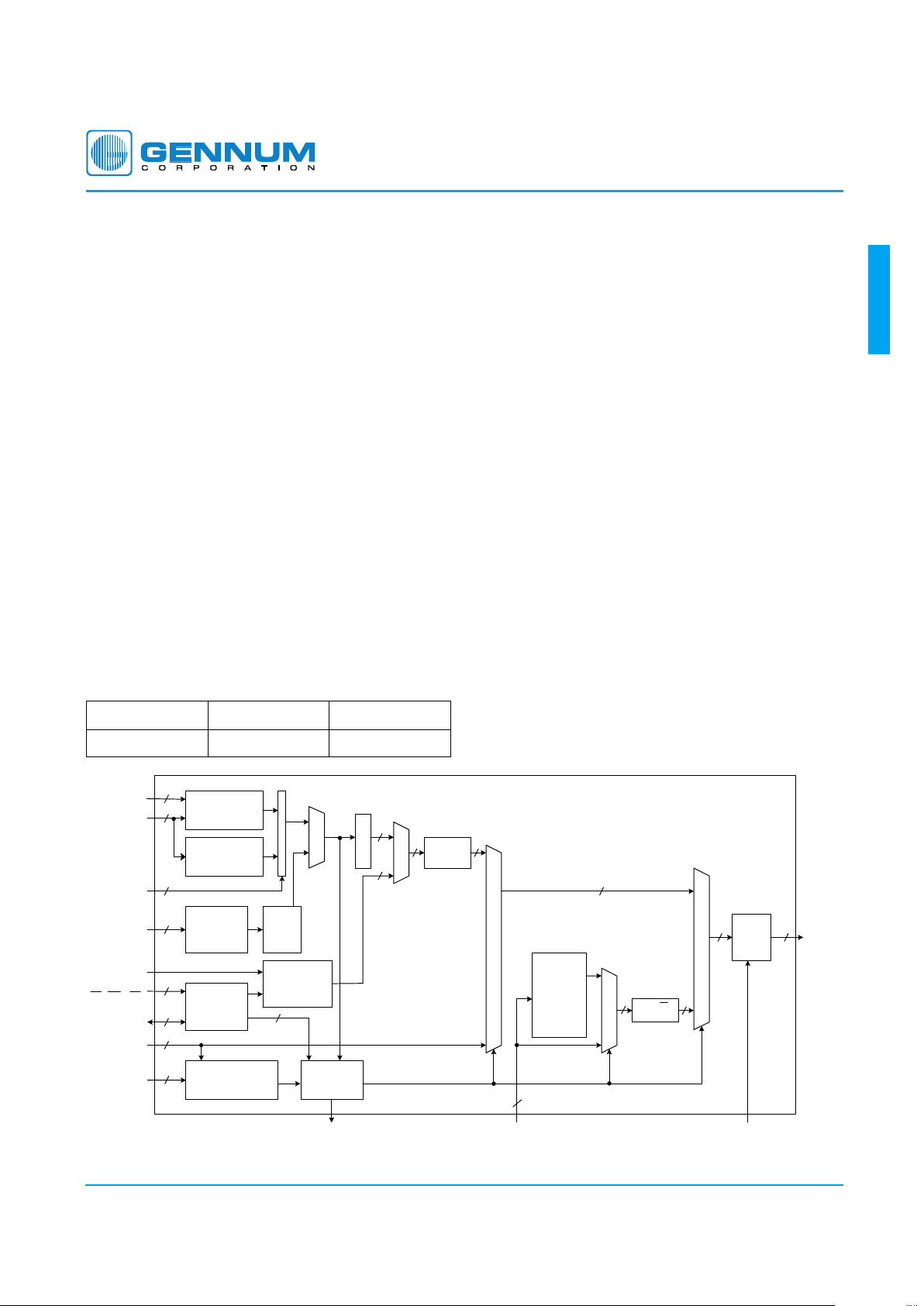

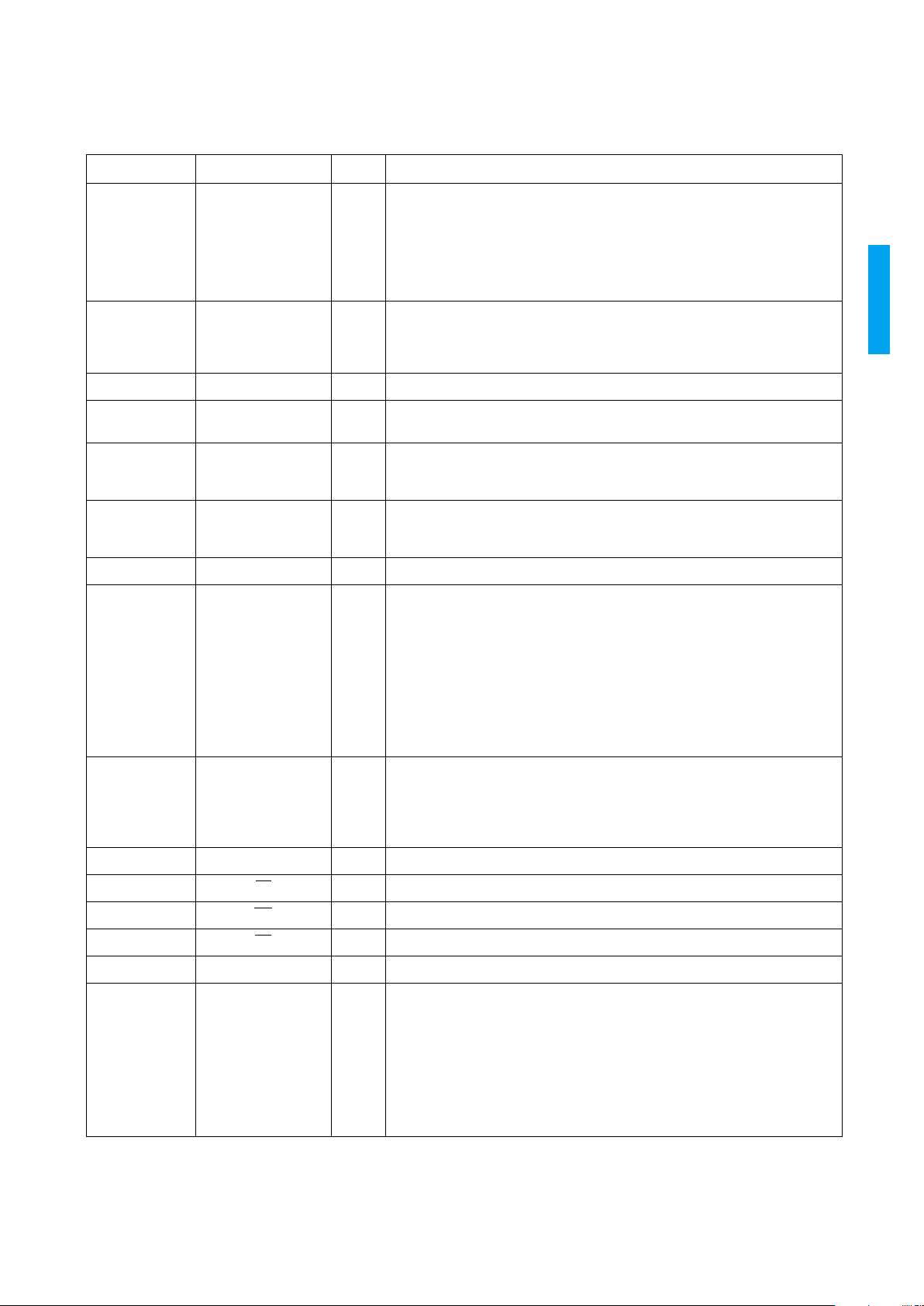

MULTIPLEX MODE BLOCK DIAGRAM

ORDERING INFORMATION

PART NUMBER PACKAGE TEMPERATURE

GS9023-CFY 100 pin LQFP 0°C to 70°C

Convert Input

Data Format

Convert

AES/EBU

Format

WCINA/B

AINA/B

AUXEN

AM[2:0]

MPX

Convert

Control

Code

Add

CRC

SAFA/B

CSA/B

UDA/B

VFLA/B

S/P

MPX

Control

Registers

Generate

Audio

Packets

ADDR[3:0]

CS, WE, RE

DATA[7:0]

Audio

Buffer

MPX

DIN[9:0]

10

10

10

10

3

3

8

10

7

8

Generate

ANCI area

8

Video Detection

& Synchronization

VM[2:0]

LOCK

Arbitrary

Packet

Buffer

PKT[8:0]

MPX

9

b9=b8

9

MPX

10

10

Add

EDH

10 10

DOUT[9:0]

EDH_INS

MUTE

3

2

GENLINX

™

II

GS9023

Embedded Audio CODEC

GENNUM CORPORATION

522 - 45 - 05

2

GS9023

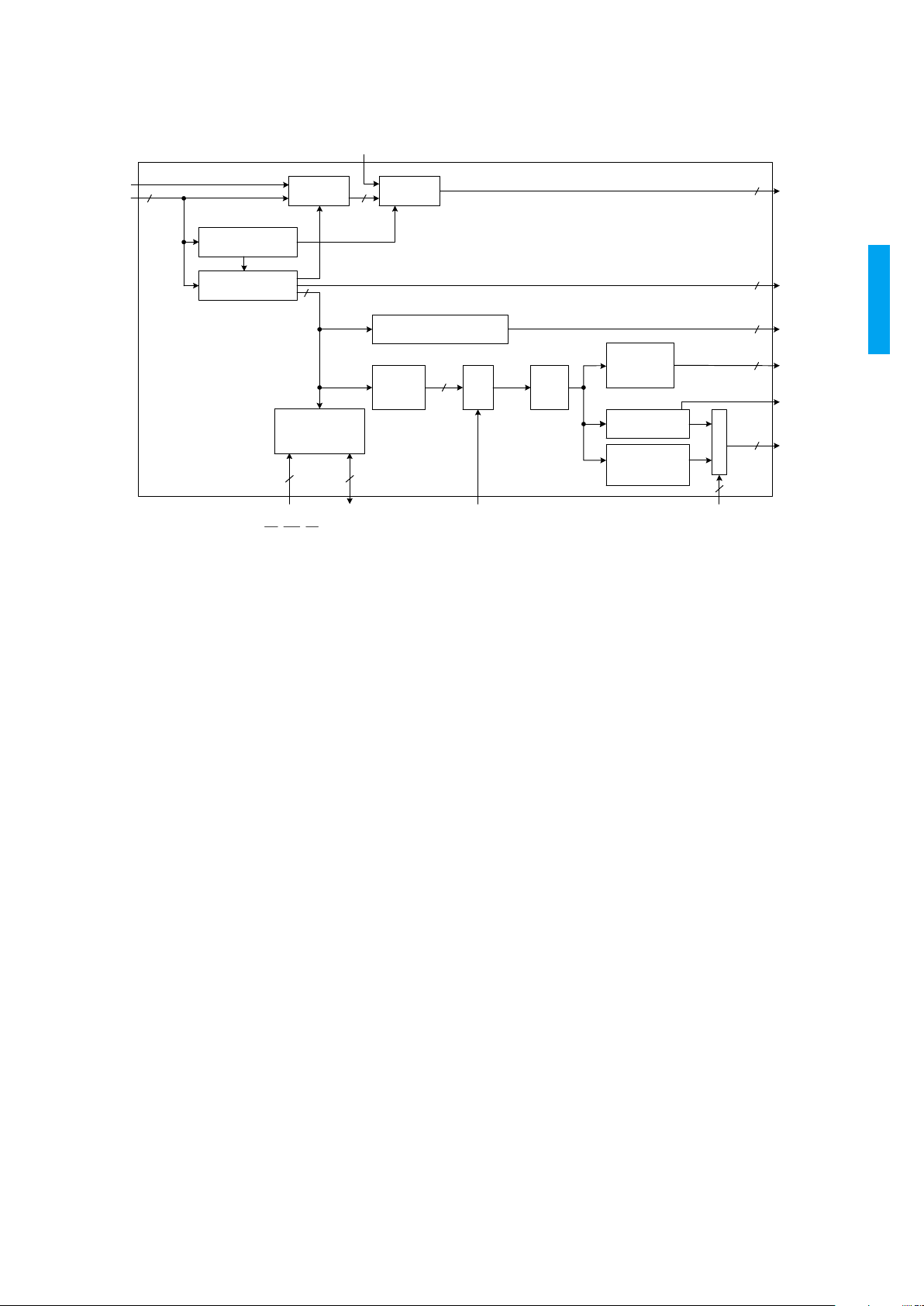

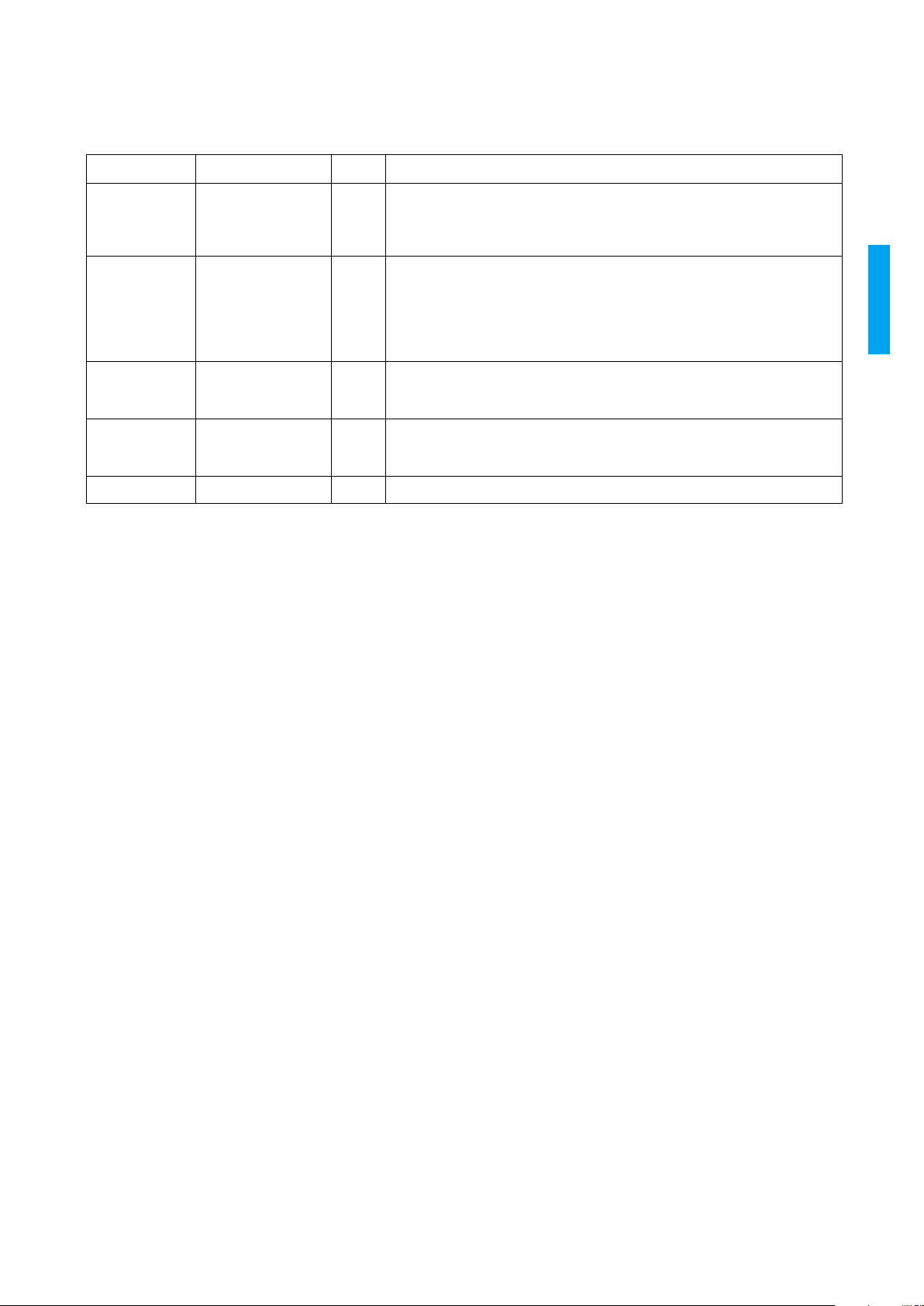

DEMULTIPLEX MODE BLOCK DIAGRAM

Convert Output

Data Format

Convert

AES/EBU

Format

ANCI

Output

Control

Code

Add

CRC

Control

Registers

DIN[9:0]

10

Video Detection &

Synchronization

10

DOUT[9:0]

Delete

ANCI

Delete

TRS

10

TRS

Detect ANCI

3

LOCK

BUFERR

AUXEN

AM[2:0]

AOUTA/B

8

SAFA/B

CSA/B

UDA/B

VFLA/B

P/S

Audio

Buffer

10

Output Arbitrary Packet PKT[8:0]

9

10

WCOUT

ADDR[3:0],

CS, WE, RE

7

8

DATA[7:0]

MUTE

2

3

GENNUM CORPORATION

522 - 45 - 05

3

GS9023

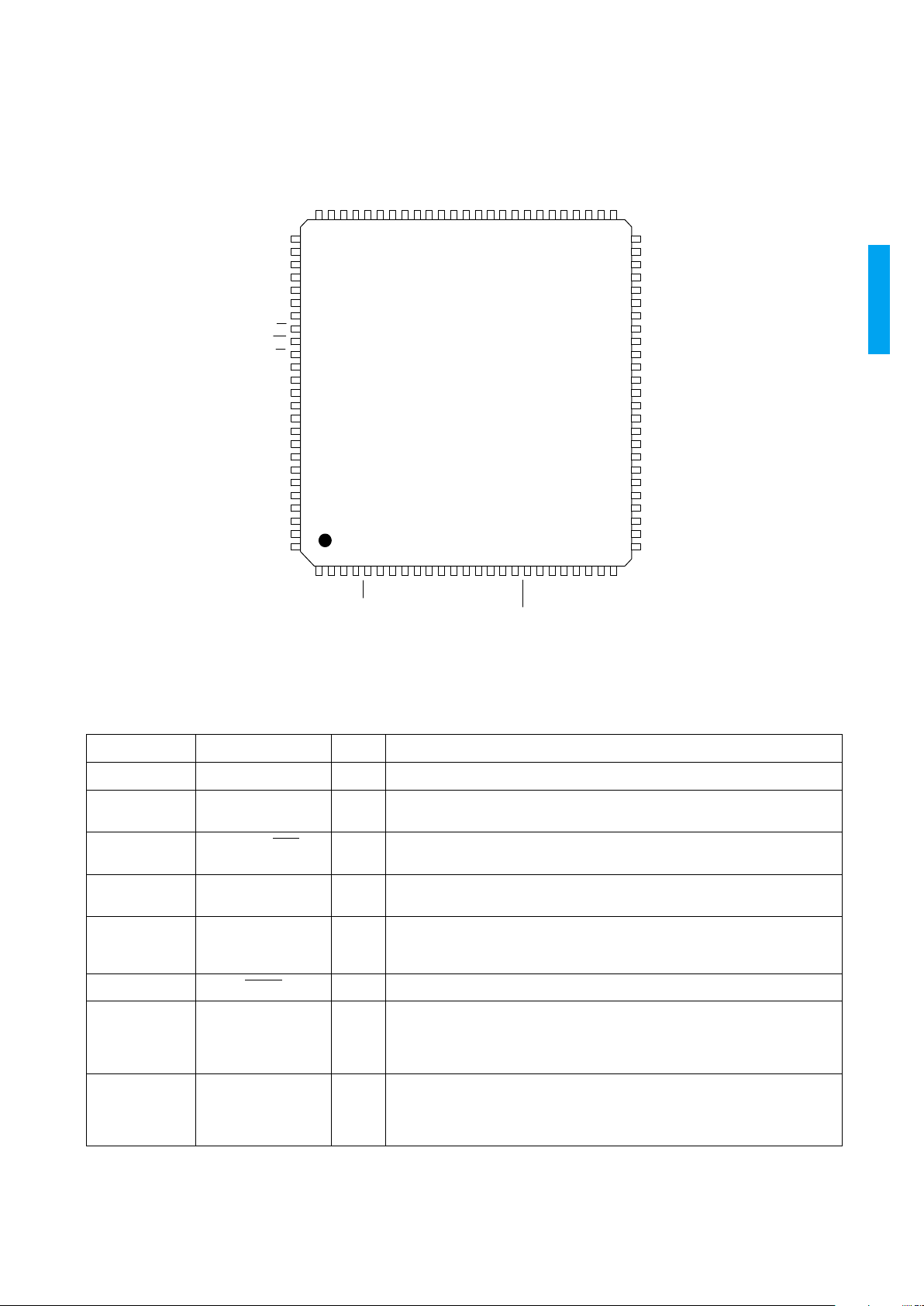

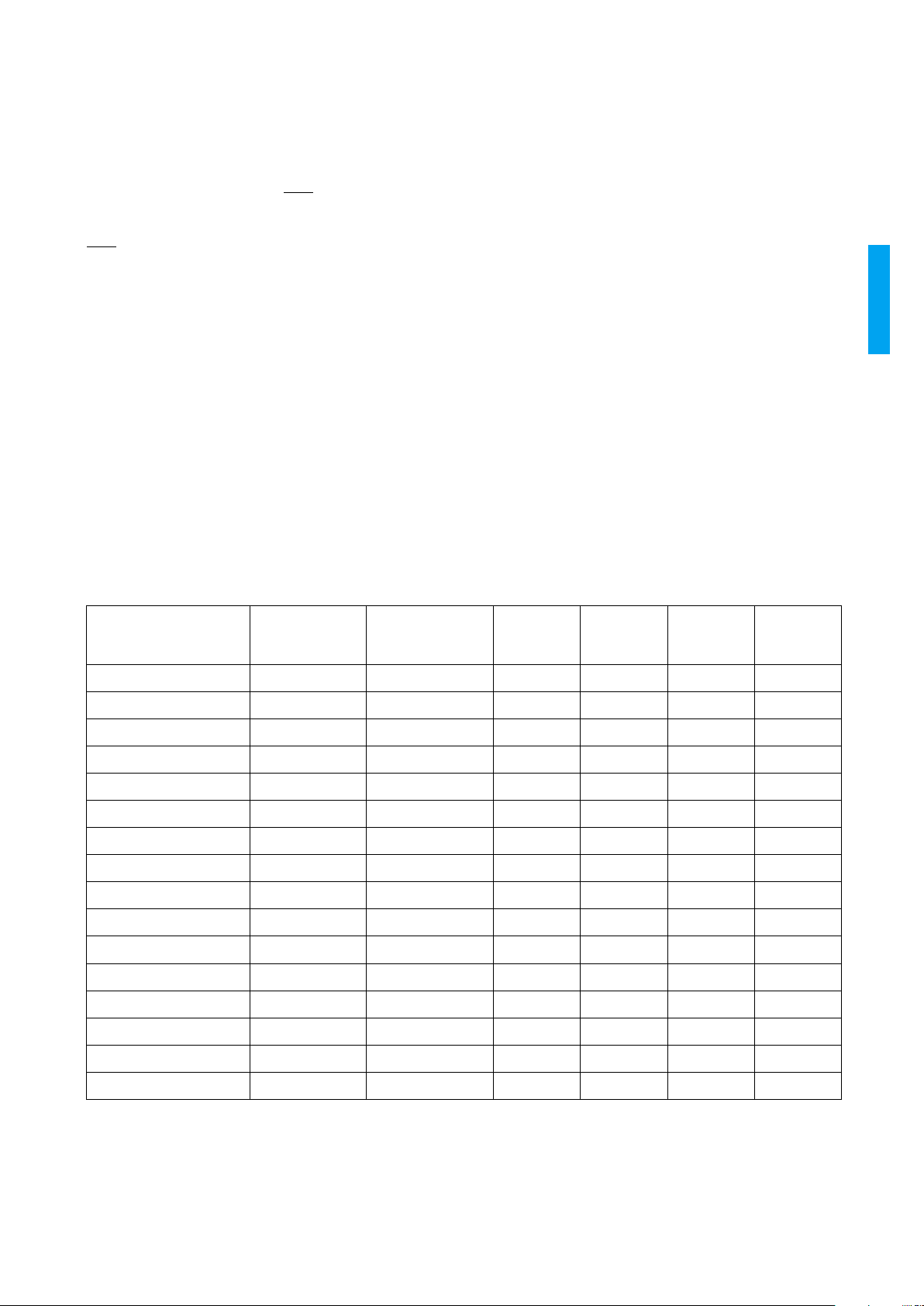

PIN CONNECTIONS

PIN DESCRIPTIONS

NUMBER SYMBOL TYPE DESCRIPTION

1, 17, 26, 90 VDDINT +3.3V power supply pins for core logic.

2-4 VM[2:0] I Video standard format. Used in conjunction with the TRS pin. VM[2] is the MSB

and VM[0] is the LSB.

See Table 1

.

5 DEMUX/MUX

I Mode of operation. When set HIGH, the GS9023 operates in Demultiplex Mode.

When set LOW, the GS9023 operates in Multiplex Mode.

6-10,12-16 DIN[9:0] I Parallel digital video signal input. DIN[9] is the MSB and DIN[0] is the LSB. The

digital video input should contain TRS information.

11, 23, 25, 29,

50, 58, 71, 82,

98, 100

GND Device ground.

18 RESET

I Device reset. Active low.

19 WCINA I 48kHz word clock for channels 1 and 2. Used only when operating in Multiplex

Mode and when the audio source is not an AES/EBU data stream. This pin

should be grounded when inputting AES/EBU digital audio data or when

operating in Demultiplex Mode.

20 WCINB I 48kHz word clock for channels 3 and 4. Used only when operating in Multiplex

Mode and when the audio source is not an AES/EBU data stream. This pin

should be grounded when inputting AES/EBU digital audio data or when

operating in Demultiplex Mode.

PCLK

DIN9

DIN8

DIN7

DIN6

DIN5

DIN4

DIN3

DIN1

D

OUT9

DIN2

DIN0

D

OUT0

D

OUT1

D

OUT2

D

OUT3

D

OUT4

D

OUT5

D

OUT6

D

OUT7

D

OUT8

WC

INA

WC

INB

VFLB

VFLA

A

OUTB

A

OUTA

A

INB

A

INA

WC

OUT

AUXEN

SAFB

CSA

CSB

UDA

UDB

SAFA

MUTE

PKT2

PKT3

PKT8

PKT7

PKT6

PKT5

PKT4

PKT1

PKT0

NC

VM2

VM1

VM0

AM2

AM1

EDH_INS

TRS

ANCI

LOCK

NC

BUFERR

ADDR3

ADDR2

ADDR1

ADDR0

DATA 7

DATA 6

DATA 5

DATA 4

DATA 3

DATA 2

DATA 0

DATA 1

198765432 10

27

26

24 25

28

23222120191817161514131211

37

36

35

34

33

32

31

30

29

50

49

48

47

46

45

44

43

42

41

40

39

38

75 6768697071727374 66 52 5153545556575859606162636465

99

100

98

89

90

91

92

93

94

95

96

97

76

77

78

79

80

81

82

83

84

85

86

87

88

GS9023

(TOP VIEW)

GND

ACLK

GND

VDDINT

GND

V

DDIO

GND

V

DDIO

GND

PKTEN

VDDIO

GND

VDDINT

GND

VDDINT

GND

VDDINT

GND

TEST

TEST

VDDIO

AM0

TEST

GND

RESET

DEMUX/MUX

RE

WE

CS

NOTE: The GS9023 DOUT[9:0] MSB to LSB convention is compatible with

the GS9022 but reversed with the GS9032 or GS7005.

See Interconnection with GS9032 or GS7005 section.

GENNUM CORPORATION

522 - 45 - 05

4

GS9023

21 AINA I Audio signal input for channels 1 and 2. AES/EBU digital audio data is bi-phase

mark encoded. For all non-AES/EBU input modes, bi-phase mark encoding is not

required.

22 AINB I Audio signal input for channels 3 and 4. AES/EBU digital audio data is bi-phase

mark encoded. For all non-AES/EBU input modes, bi-phase mark encoding is not

required.

24 PCLK I Video clock signal input.

27, 28, 75 TEST - Connect to ground.

30 SAFA I/O Start of audio frame indicator for channels 1 and 2. Valid only for non-AES/EBU

audio formats. This pin should be grounded when inputting AES/EBU audio data.

SAFA is HIGH for audio frame 0 and LOW for all other audio frames. In Multiplex

Mode, this pin is an input and is supplied by the user. In Demultiplex Mode, this

pin is an output and is generated by the GS9023.

31 SAFB I/O Start of audio frame indicator for channels 3 and 4. Valid only for non-AES/EBU

audio formats. This pin should be grounded when inputting AES/EBU audio data.

SAFB is set to HIGH for audio frame 0 and LOW for all other audio frames. In

Multiplex Mode, this pin is an input and is supplied by the user. In Demultiplex

Mode, this pin is an output and is generated by the GS9023.

32 VFLA I/O Validity flag for channels 1 and 2. Valid only for non-AES/EBU audio formats. This

pin should be grounded when inputting AES/EBU audio data. VFLA is HIGH

when audio is invalid and LOW when audio is valid. In Multiplex Mode, this pin is

an input and is supplied by the user. In Demultiplex Mode, this pin is an output

and is generated by the GS9023.

33 VFLB I/O Validity flag for channels 3 and 4. Valid only for non-AES/EBU audio formats. This

pin should be grounded when inputting AES/EBU audio data. VFLB is HIGH

when audio is invalid and LOW when audio is valid. In Multiplex Mode, this pin is

an input and is supplied by the user. In Demultiplex Mode, this pin is an output

and is generated by the GS9023.

34 UDA I/O User data for channels 1 and 2. Valid only for non-AES/EBU audio formats. This

pin should be grounded when inputting AES/EBU audio data. In Multiplex Mode,

this pin is an input and is supplied by the user. In Demultiplex Mode, this pin is

an output and is generated by the GS9023.

35 UDB I/O User data for channels 3 and 4. Valid only for non-AES/EBU audio formats. This

pin should be grounded when inputting AES/EBU audio data. In Multiplex Mode,

this pin is an input and is supplied by the user. In Demultiplex Mode, this pin is

an output and is generated by the GS9023.

36 CSA I/O Channel status for channels 1 and 2. Valid only for non-AES/EBU audio formats.

This pin should be grounded when inputting AES/EBU audio data. In Multiplex

Mode, this pin is an input and is supplied by the user. In Demultiplex Mode, this

pin is an output and is generated by the GS9023.

37 CSB I/O Channel status for channels 3 and 4. Valid only for non-AES/EBU audio formats.

This pin should be grounded when inputting AES/EBU audio data. In Multiplex

Mode, this pin is an input and is supplied by the user. In Demultiplex Mode, this

pin is an output and is generated by the GS9023.

38 AUXEN I/O Extended audio enable. When HIGH, the GS9023 processes 24-bit audio

samples. When LOW, the GS9023 processes 20-bit samples. In Multiplex Mode,

this pin is an input and is supplied by the user. In Demultiplex Mode, this pin is

an output and is generated by the GS9023.

39, 51, 67, 76 VDDIO +3.3V or +5V power supply pins for device I/Os. In order for device I/O to be +5V

tolerant VDDIO must be +5V. Device I/O are not +5V tolerant if VDDIO is +3.3V.

PIN DESCRIPTIONS (Continued)

NUMBER SYMBOL TYPE DESCRIPTION

GENNUM CORPORATION

522 - 45 - 05

5

GS9023

40-48 PKT[8:0] I/O Arbitrary data I/O bus. In Multiplex Mode, the user must input the arbitrary data

packet words starting from the secondary data identification (SDID) to the last

user data word (UDW) according to SMPTE 291M. The GS9023 internally

converts the data to 10 bits by generating the inversion bit (bit 9). The checksum

(CS) word is also generated internally. In Demultiplex Mode, the GS9023 outputs

the arbitrary data packet words starting from the SDID to the last UDW. PKT[8] is

the MSB and PKT[0] is the LSB.

See Figures 9 and 13

.

49 PKTEN I/O Arbitrary data packet enable. In Multiplex Mode, PKTEN must be set HIGH one

PCLK cycle before Arbitrary packet data is input to the device. In Demultiplex

Mode, the output is set HIGH when outputting Arbitrary packet data.

See Figures

9 and 13

.

52, 69 NC N/A No Connect. Do not connect these pins.

53 WCOUT O 48kHz word clock for channels 1, 2, 3 and 4. Valid only when operating in

Demultiplex Mode.

54 AOUTB O Audio signal output for channels 3 and 4. The AES/EBU digital audio output is bi-

phase mark encoded. In all non-AES/EBU modes, the output is not bi-phase

mark encoded.

55 AOUTA O Audio signal output for channels 1 and 2. The AES/EBU digital audio output is bi-

phase mark encoded. In all non-AES/EBU modes, the output is not bi-phase

mark encoded.

56, 57, 59-66 DOUT[9:0] O Parallel digital video signal output. DOUT[9] is the MSB and DOUT[0] is the LSB.

68 LOCK O Lock indicator. In Multiplex Mode, when HIGH, the video standard has been

identified, the start of a new video frame has been detected and the device is

multiplexing audio.

NOTE: LOCK will not be set HIGH unless at least one of the audio channel

enable bits is HIGH.

See “CHACT” description in Table 14.

In Demultiplex Mode, when HIGH, the video standard has been identified, the

‘lock’ process selected by “ACTSEL” has been validated and the device is

demultiplexing audio.

See “ACTSEL” description in Table 15.

NOTE: LOCK remains active regardless of the number of audio samples in the

video stream after ‘lock’ is achieved.

70 BUFERR O Buffer error. Indicates when an internal buffer overflow/underflow error has

occurred. Valid only when the device is configured to operate in Demultiplex

Mode.

NOTE: If an internal buffer overflow/underflow condition occurs, the GS9023

does not mute the audio output.

72-74, 77-81 DATA[7:0] I/O Host Interface data bus. DATA[7] is the MSB and DATA[0] is the LSB.

83 RE

I Read enable for Host Interface. Active LOW.

84 WE

I Write enable for Host Interface. Active LOW.

85 CS

I Chip select for Host Interface. Active LOW.

86-89 ADDR[3:0] I Host Interface address bus. ADDR[3] is the MSB and ADDR[0] is the LSB.

91 ANCI I ANCI Selection. Valid in Demultiplex Mode only. When set HIGH, each ancillary

data packet with a DID corresponding to either the audio packet DID, the

extended audio packet DID or the arbitrary packet DID is removed from the

video signal. The data contained in the packets are output at the corresponding

pins. The various DIDs are user programmable in the internal registers and are

accessible via the Host Interface.

NOTE: When ancillary data packets are deleted, the GS9023 does not

recalculate the EDH checkwords.

When set LOW, all ancillary data packets remain in the video signal.

PIN DESCRIPTIONS (Continued)

NUMBER SYMBOL TYPE DESCRIPTION

GENNUM CORPORATION

522 - 45 - 05

6

GS9023

92 TRS I TRS Selection. Used in conjunction with the VM[2:0] pins to select video

standard format. In Multiplex Mode, when the TRS pin is HIGH, TRS is added to a

composite video signal. In Demultiplex Mode, when HIGH, TRS is removed from

a composite video signal.

See Table 1.

93 EDH_INS I EDH Insert Selection. Valid in Multiplex Mode only. When set HIGH, the GS9023

performs EDH functions according to SMPTE RP165. When set LOW, EDH is not

inserted.

NOTE: Active picture and full field data words are updated from recalculated

values but error flag information is replaced with the values programmed in the

internal registers via the Host Interface.

94 MUTE I Audio mute. In Multiplex Mode, when set HIGH, the embedded audio packets

are forced to ‘0’. In Demultiplex Mode, when set HIGH, the output data is forced

to “0”.

95-97 AM[2:0] I Audio mode format. In Multiplex Mode, AM[2:0] indicates the input audio data

format. In Demultiplex Mode, AM[2:0] indicates the output audio data format.

AM[2] is the MSB and AM[0] is the LSB.

See Table 2

.

99 ACLK I Input audio signal clock (128 fs). Synchronous to PCLK.

NOTE: All unused inputs of the GS9023 should be connected to ground.

PIN DESCRIPTIONS (Continued)

NUMBER SYMBOL TYPE DESCRIPTION

GENNUM CORPORATION

522 - 45 - 05

7

GS9023

DETAILED DESCRIPTION

The GS9023 has two main modes of operation: Multiplex

Mode and Demultiplex Mode. In Multiplex Mode, which is

selected by setting the DEMUX/MUX

input pin LOW, digital

audio is embedded into a digital video stream. In

Demultiplex Mode, which is selected by setting the DEMUX/

MUX

input pin HIGH, digital audio is extracted from a digital

video stream. Tables 14 and 15 contain Host Interface

Register descriptions for the Multiplex and Demultiplex

Modes respectively.

MULTIPLEX MODE

Video Clock Input

A master video clock must be supplied to the PCLK pin

corresponding to the selected video standard. The

supported video input standards and corresponding clock

frequencies are listed in Table 1.

Video Data Input

The video data DIN[9:0] is clocked into the GS9023 on the

rising edge of PCLK. The video clock frequency must

correspond to the video input standard selected. This is

done via the “VSEL” bit of Host Interface Register #0h.

When “VSEL” is LOW, the video input standard is selected

by the VM[2:0] and TRS input pins. When “VSEL” is HIGH,

the video input standard is selected by the “VMOD[2:0]”

and “D2_TRS” bits in Host Interface Register #0h. The

supported video input standards are listed in Table 1.

After the user has specified the video input standard via the

VM[2:0] and TRS pins or by setting Host Interface

Register #0h, the GS9023 performs video standard

detection to verify that the input video stream corresponds

to the selected standard. When the selected video input

standard is verified, the “VXST” bit of Host Interface

Register #0h is set HIGH. The LOCK output pin and the

“LOCK” bit of Host Interface Register #0h are then set

HIGH if at least one of the audio channel enable bits

“CHACT(4-1)” of Host Interface Register #1h is HIGH and

the start of a video frame is detected.

NOTE: The user must ensure that the video input format

correctly corresponds to the video format being provided to

the GS9023.

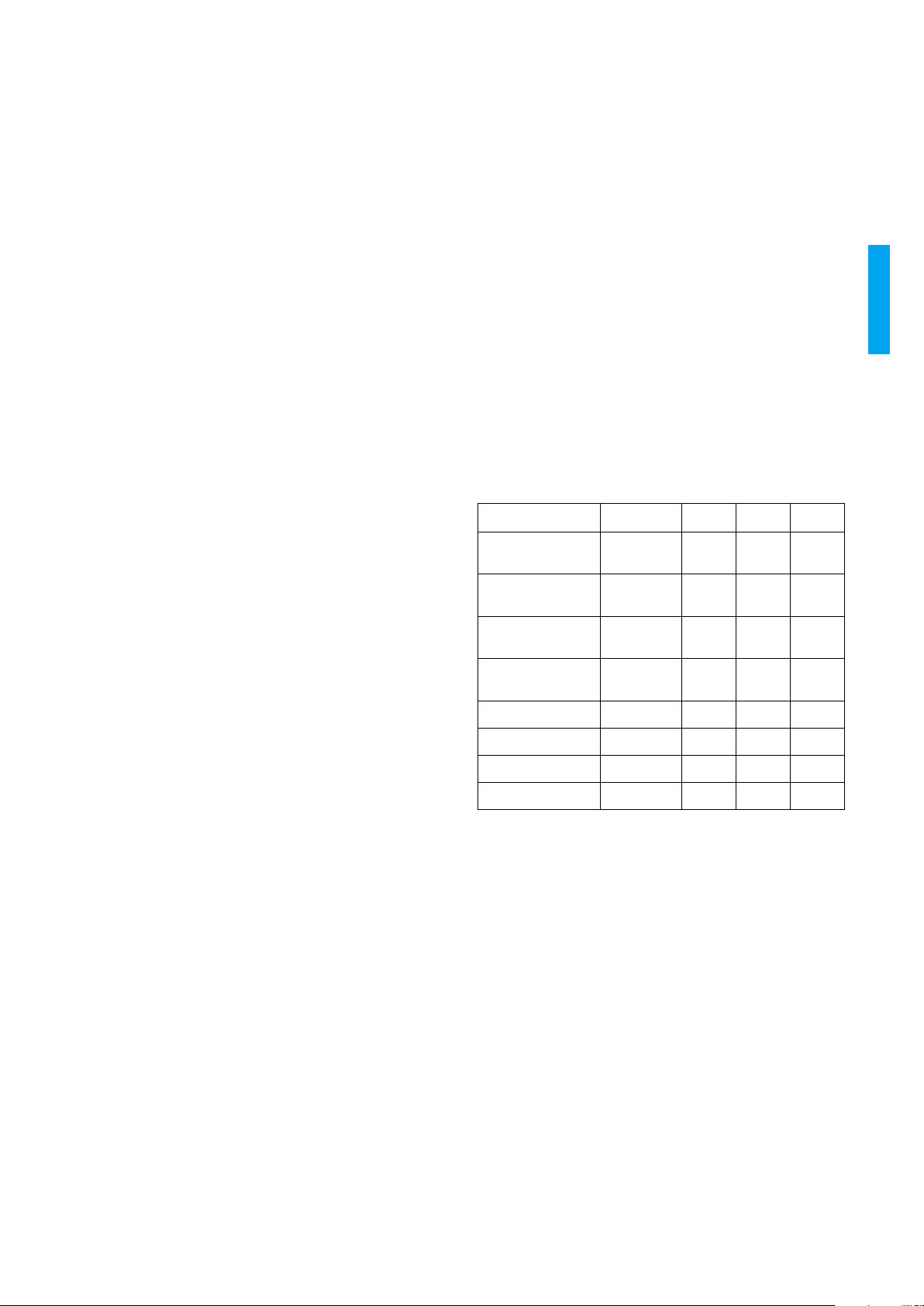

TABLE 1: Video Input Formats

VIDEO STANDARD

SERIAL DIGITAL

DATA RATE

(Mbps)

PCLK

FREQUENCY

(MHz)

VM[2] or

“VMOD[2]”

VM[1] or

“VMOD[1]”

VM[0] or

“VMOD[0]”

TRS or

“D2_TRS”

525/D2 (SMPTE259M) 143 14.3 0000

525/D2 (SMPTE244M) 143 14.3 0001

525/D1 270 27.0 0010

Reserved - - 0011

525/16:9 360 36.0 0100

Reserved - - 0101

525/4:4:4:4 (System #1) 540 54.0 0110

Reserved - - 0111

625/D2 (with TRS) 177 17.7 1000

625/D2 (without TRS) 177 17.7 1001

625/D1 270 27.0 1010

Reserved - - 1011

625/16:9 360 36.0 1100

Reserved - - 1101

625/4:4:4:4 (System #2) 540 54.0 1110

625/4:2:2P (System #4) 540 54.0 1111

GENNUM CORPORATION

522 - 45 - 05

8

GS9023

Video Data Output

The video signal is output at the DOUT[9:0] pins. The video

signal is synchronized to the rising edge of PCLK. When the

GS9023 is properly configured, audio packets, extended

audio packets, audio control packets and arbitrary data

packets are multiplexed into the output video signal. When

the video signal is a 525 line or 625 line D2 format, TRS

information is added to the video signal if the TRS input pin

or the “D2_TRS” and “VSEL” bits of Host Interface Register

#0h are HIGH. EDH packets can also be inserted into the

video signal by setting the EDH_INS pin HIGH or by setting

the “EDHON” bit HIGH of Host Interface Register #1h.

When selected, the GS9023 inserts EDH packets according

to SMPTE RP165.

NOTE: Active picture and full field data words are updated

from recalculated values but error flag information is

replaced with the values programmed in Host Interface

Registers #Eh and #Fh.

NOTE: In the 525/4:4:4:4 video standard, EDH packets

should not be inserted as this can lead to TRS signal

corruption. When EDH packets are not inserted, the

“EDHDEL” bit of Host Interface Register #0h controls the

deletion of EDH packets. When the “EDHDEL” bit is set

LOW, EDH packets are deleted from the incoming video

signal. When “EDHDEL” is set HIGH, EDH packets pass

through the device unchanged.

NOTE: “EDHDEL” functionality is valid only when the

“CASCADE” bit of Host Interface Register #4h is LOW.

Audio Clock Input

A master audio clock (128 fs: 6.144MHz) must be supplied

to the ACLK pin. This clock must be synchronized with the

video signal input to the GS9023. An audio word clock must

also be supplied (fs: 48kHz) to the WCINA/B pins when

using non-AES/EBU audio. The two 48kHz word clocks

must also be synchronized to the video signal.

Audio Data Input

The serial audio data for channels 1 and 2 are input to the

AINA pin. The serial audio data for channels 3 and 4 are

input to the AINB pin. The GS9023 can multiplex 20 or 24

bit audio data samples. When the AUXEN pin or bit “A4ON”

of Host Interface Register #1h is HIGH, the device

processes 24 bit audio samples. When the AUXEN pin or

“A4ON” register bit is LOW, the device processes 20 bit

audio samples. On power up, the “A4ON” bit default is

LOW.

The GS9023 offers five predefined audio data input formats,

selected via the AM[2:0] pins, which are listed in Table 2

and illustrated in Figure 1. The first four predefined formats

relate to non-AES/EBU audio data while the fifth format

corresponds to the AES/EBU audio format. The WCINA and

WCINB pins should be grounded when inputting AES/EBU

audio data as they are not used.

The GS9023 supports muting of the audio data input.

Multiplexed audio and extended data packets for all

channels are forced to zero when the MUTE pin or “MUTE”

bit of Host Interface Register #4h is set HIGH.

Control Code Input

When inputting non-AES/EBU audio data, the validity (V),

user data (U) and channel status (C) bits of each audio

data channel must be input to the corresponding pins

(VFLA, VFLB; UDA, UDB; CSA, CSB). The signals must be

updated on the rising edge of WCINA/B and remain

constant for the entire word clock period (64 ACLK cycles).

When inputting non-AES/EBU audio data, the SAFA and

SAFB pins must be high for one frame out of 192 frames

received to indicate the start of frame condition.

When inputting AES/EBU audio data, the control code input

pins should be grounded as they are not used.

TABLE 2: Audio Input Formats

FORMATS WCINA/B AM[2] AM[1] AM[0]

AIN-MODE 0 User

Supplied

000

AIN-MODE 1 User

Supplied

001

AIN-MODE 2 User

Supplied

010

AIN-MODE 3 User

Supplied

011

AIN-AES/EBU Not Used 1 0 0

Not Used - 1 0 1

Not Used - 1 1 0

Not Used - 1 1 1

GENNUM CORPORATION

522 - 45 - 05

9

GS9023

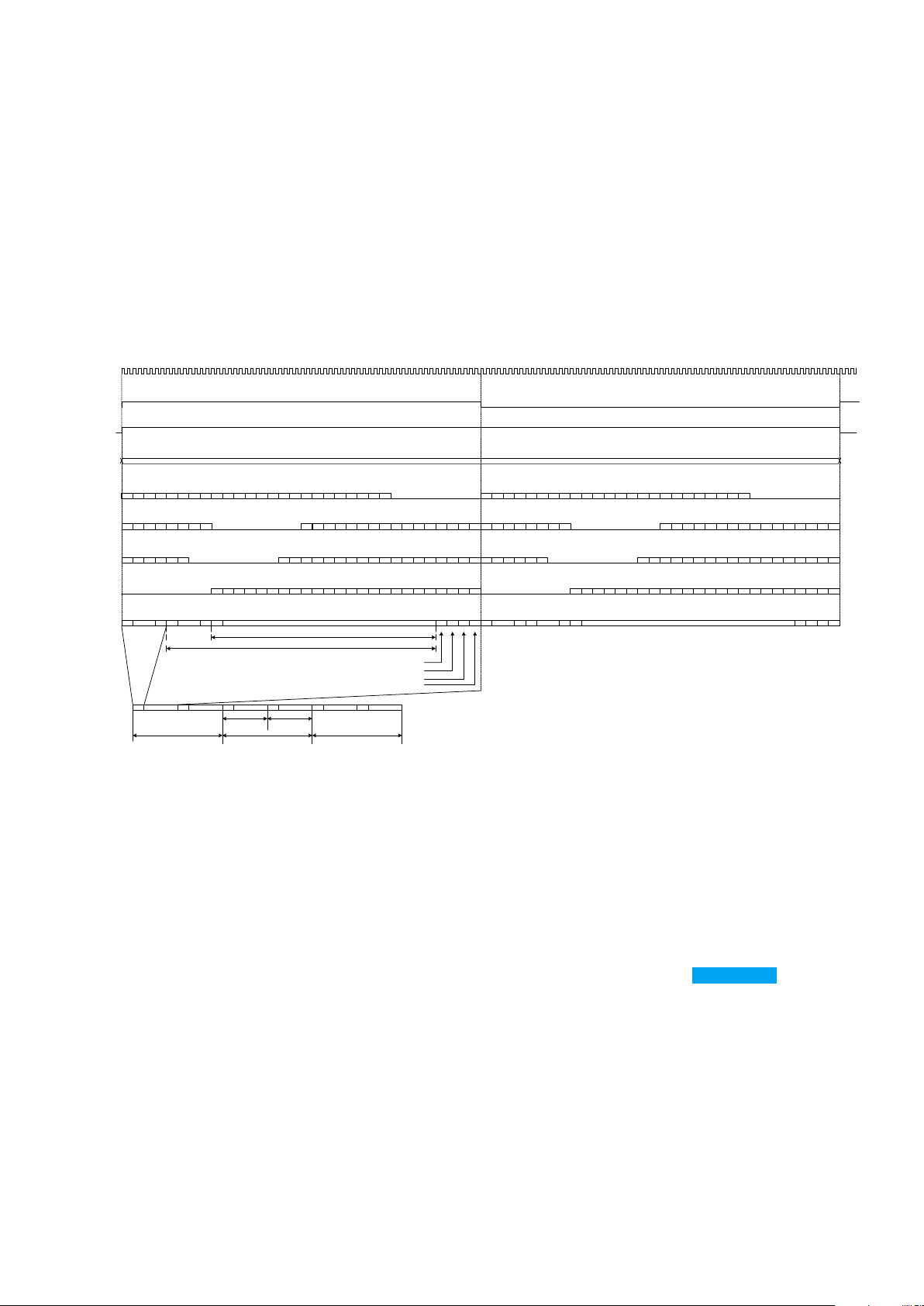

Fig. 1: Audio Input Format Timing Diagram

SAFA/B

ACLK

(128fs)

WCINA/B

AIN-MODE0

8 0

LSBLEFT CHANNEL

23

LSB

0

7

RIGHT CHANNEL RIGHT CHANNELMSB

23 8

AIN-MODE1

23 23

AIN-MODE3

6 0

LSBLEFT CHANNEL

23

LSB

05

RIGHT CHANNEL RIGHT CHANNELMSB

23 6

MSB

MSB

AIN-MODE2

LSB

LEFT CHANNEL

023

MSB LSB

RIGHT CHANNEL

MSB

0

LSB

4

MSBLEFT CHANNEL

0

LSB

4

MSBRIGHT CHANNEL

VFLA/B

UDA/B

CSA/B

DATA

AIN-AES/EBU

03

LSB

478

Audio sample word

27 28 29

30 31

MSBLSB

AES/EBU Sub-frame format

03

LSB

4

7 8 Audio sample word 27 28 29 30 31

MSBLSB

Synchronization

preamble

20bits

24bits

Validity flag

User data

Channel status

Parity bit

M Channel 1 Channel 2 Channel 1 Channel 2 Channel 1 Channel 2MWBW WM

Sub-frame Sub-frame

Frame 0 (Start of Block) Frame 1 Frame 2

23

0

2323

GENNUM CORPORATION

522 - 45 - 05

10

GS9023

Audio Data Packets

The GS9023 can multiplex up to four audio channels. The

channels are selectable via the “CHACT(4-1)” bits of Host

Interface Register #1h. The audio group (Audio packet data

ID) for each device is configured in “AD20ID[3:0]” of Host

Interface Register #3h. On power up, the four audio

channels and audio group 1 are selected by default.

NOTE: Do not rely on default value. Reprogram on power

up or reset.

The “CASCADE” bit in Host Interface Register #4h controls

the manner in which multiplexing is performed. When

“CASCADE” is LOW, the GS9023 deletes all existing

ancillary packets. New packets are multiplexed at the first

location after the end of active video (EAV) in the horizontal

ancillary space (HANC).

See Figure 2

.

When “CASCADE” is HIGH, the GS9023 multiplexes

packets at the first free location in the horizontal ancillary

(HANC) space after the end of active video (EAV) if there is

sufficient space remaining to insert the packet. The GS9023

does not check if existing audio group samples are present

in the video signal. Use caution in applications where the

video signal contains existing audio packets to avoid

adding identical group samples.

See Figure 3

.

The GS9023 assumes that the ancillary space from the first

free location is empty to the start of active video (SAV).

Existing ancillary data packets (inserted by previous

devices) in the video signal must be contiguous from the

beginning of the HANC space or the insertion of a new

audio data packet may overwrite existing data.

See

Figure 4

.

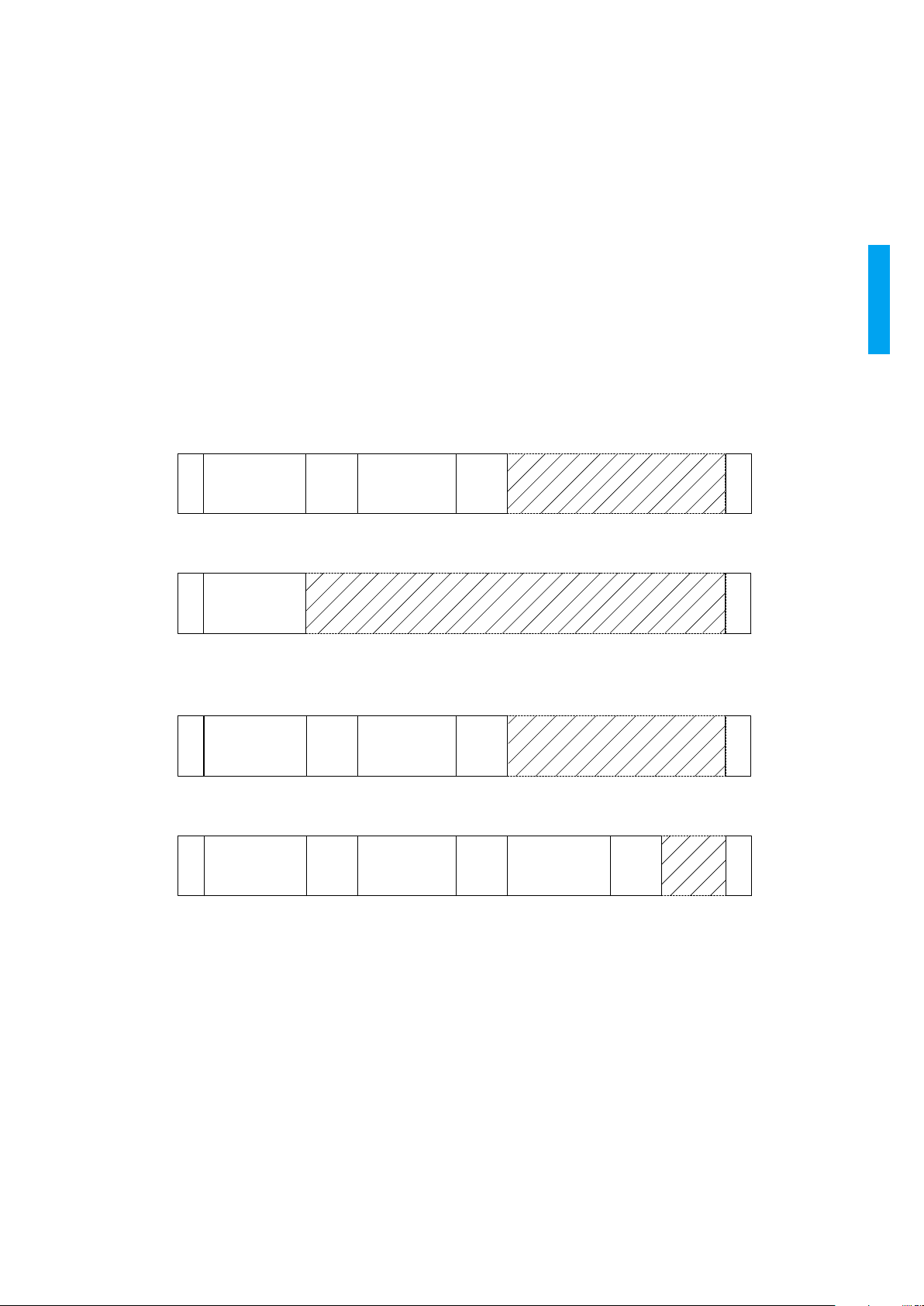

Fig. 2

Fig. 3

EAV

Audio

Group 1

Extended

Audio

Group 1

SAV

Empty

Audio

Group 2

Extended

Audio

Group 2

Video Signal before GS9023

EAV

SAV

Empty

Audio

Group 1

(New)

Video Signal after GS9023 Insertion of Audio Group 1 ("CASCADE" = LOW)

EAV

Audio

Group 3

Extended

Audio

Group 3

SAV

Empty

Audio

Group 4

Extended

Audio

Group 4

Video Signal before GS9023

EAV

SAV

Empty

Audio

Group 3

(New)

Extended

Audio

Group 3

(New)

Video Signal after GS9023 Insertion of Audio Group 3 ("CASCADE" = HIGH)

Audio

Group 3

(Old)

Extended

Audio

Group 3

(Old)

Audio

Group 4

(Old)

Extended

Audio

Group 4

(Old)

Loading...

Loading...