Gennum Corporation GS9000CCTJ, GS9000CCPJ Datasheet

GENLINX

GS9000C

™

GS9000C

Serial Digital Decoder

DATA SHEET

FEATURES

• fully compatible with SMPTE 259M

• decodes 8 and 10 bit serial digital signals for data

rates to 370Mb/s

• pin and function compatible with GS9000S, GS9000

and GS9000B

• 325mW power dissipation at 270MHz clock rates

• incorporates an automatic standards selection

function with the GS9005A Receiver or GS9015A

Reclocker

• operates from single +5 or -5 volt supply

• enables an adjustment-free Deserializer system

when used with GS9010A and GS9005A or

GS9015A

• 28 pin PLCC packaging

APPLICATIONS

•4ƒ

, 4:2:2 and 360Mb/s serial digital interfaces

SC

• Automatic standards select controller for serial routing

and distribution applications using GS9005A Receiver or

GS9015A Reclocker

DEVICE DESCRIPTION

The GS9000C is a CMOS integrated circuit specifically

designed to deserialize SMPTE 259M serial digital signals

at data rates to 370Mb/s.

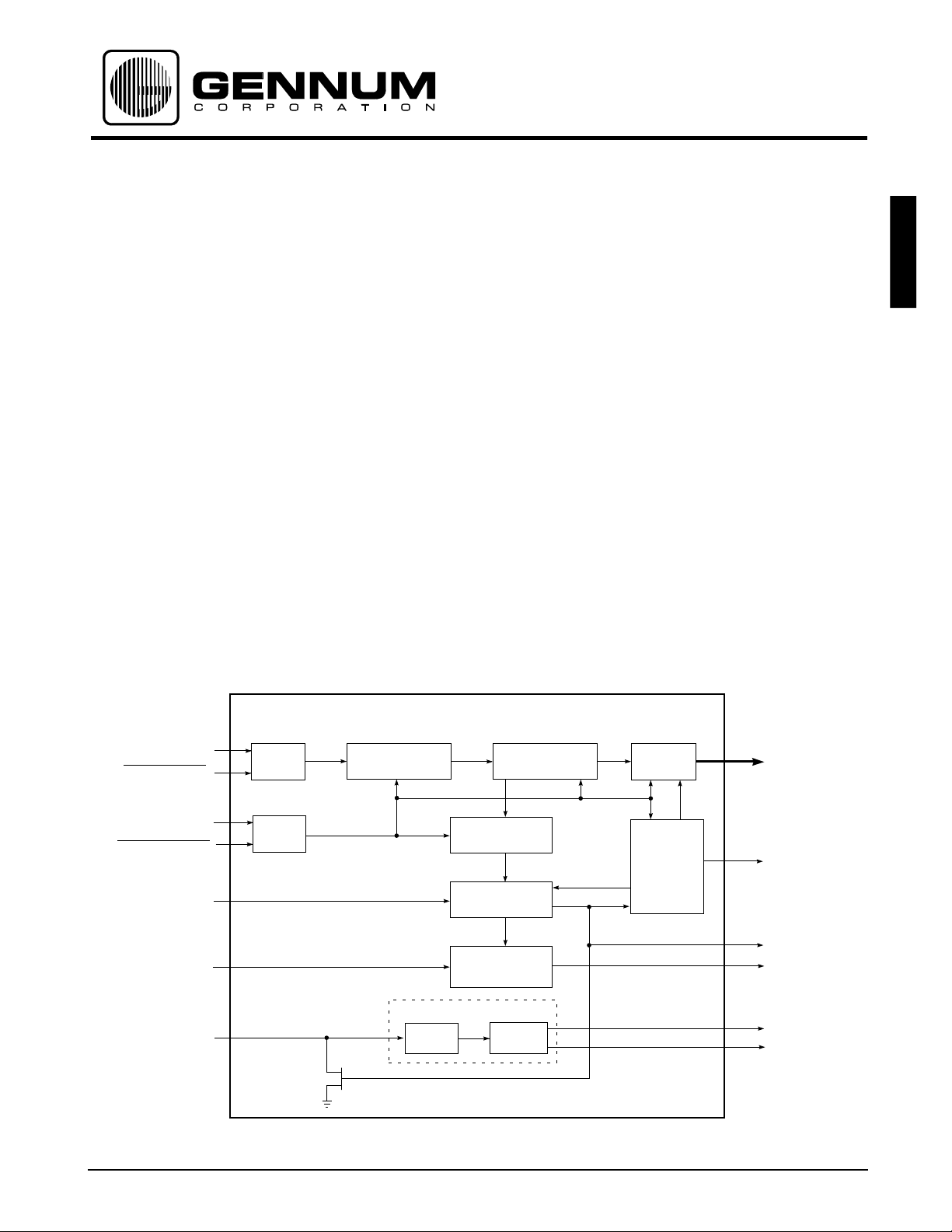

The device incorporates a descrambler, serial to parallel

convertor, sync processing unit, sync warning unit and

automatic standards select circuitry.

Differential pseudo-ECL inputs for both serial clock and

data are internally level shifted to CMOS levels. Digital

outputs such as parallel data, parallel clock, HSYNC,

Sync Warning and Standard Select are all TTL compatible.

The GS9000C is designed to directly interface with the

GS9005A Reclocking Receiver to form a complete

SMPTE-serial-in to CMOS level parallel-out deserializer.

The GS9000C may also be used with the GS9010A and

the GS9005A to form an adjustment-free receiving system

which automatically adapts to all serial digital data rates.

The GS9015A can replace the GS9005A in GS9000C

applications where cable equalization is not required.

The GS9000C is packaged in a 28 pin PLCC and operates

from a single 5 volt, ±5% power supply.

SERIAL DATA IN

SERIAL DATA IN

SERIAL CLOCK IN

SERIAL CLOCK IN

SYNC CORRECTION

STANDARDS SELECT

Revision Date: February 2000

ENABLE

SYNC WARNING

CONTROL

CONTROL

5

6

7

8

14

15

11

GS9000C

LEVEL

SHIFT

LEVEL

SHIFT

DESCRAMBLER

SCLK

AUTO STANDARD SELECT

OSC

SYNC DETECT

(3FF 000 000 HEX)

SYNC CORRECTION

SYNC WARNING

(Schmitt Trigger

Comparator)

Hsync Reset

30 - BIT

SHIFT REG

Sync

Sync Error

2 BIT

COUNTER

Word

Boundary

SP

PARALLEL

TIMING

GENERATOR

SYNC WARNING

FUNCTIONAL BLOCK DIAGRAM

GENNUM CORPORATION P.O. Box 489, Stn. A, Burlington, Ontario, Canada L7R 3Y3

Tel. +1 (905) 632-2996 Fax. +1 (905) 632-5946 E-mail: info@gennum.com

www.gennum.com

PARALLEL DATA

OUT (10 BITS)

PARALLEL CLOCK

OUT

HSYNC OUTPUT

FLAG

SS0

SS1

Document No. 522 - 49 - 01

GS9000C

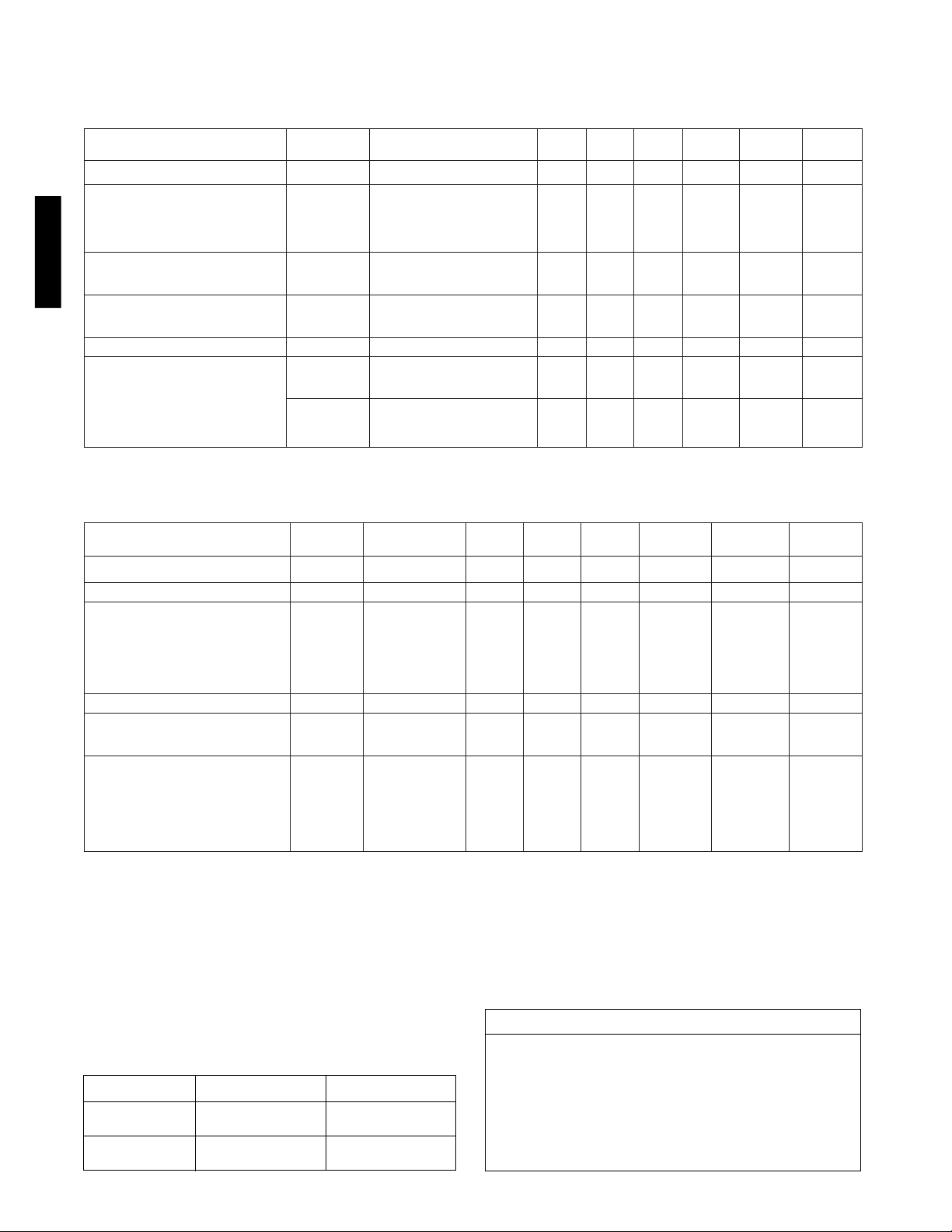

GS9000C DECODER - DC ELECTRICAL CHARACTERISTICS

V

= 5V, TA = 0°C to 70°C unless otherwise shown

DD

RETEMARAPLOBMYSSNOITIDNOCNIMPYTXAMSTINUSETON

egatloVylppuSV

noitpmusnoCrewoP

S

P

C

)dedaolnustuptuo(

egatloVtupnISOMC

egatloVtuptuO

tnerruCegakaeLtupnI I

HIV

LIV

HOV

HOV

NI

T

NIM

A

XAM

I

NIM

HO

I

XAM

LO

VNIV=

egnaRgnitarepO57.400.552.5V 1

zHM341=ƒ

zHM072=ƒ

zHM063=ƒ

C°52=4.3

C°52,Am4=

C°52,Am4=

Vro

DD

SS

-

-

-

-

4.2

-

532

-

523

-

583

-

-

-

-

5.1

5.4

-

2.0

5.0

Wm

Wm

Wm

V

V

V

V

-- 01±Aµ1

7

7

1

1

1

1

1

stupnIataDdnakcolClaireS

gniwSlangiS

tesffOlangiS

V

V

T

NI

T

SONI

V

C°52=

A

A

NI

,C°52=

p-pVm0001ot007=

007

0.3

008

-

0001

0.4

p-pVm

V

1

1

foertneC

gniws

GS9000C DECODER - AC ELECTRICAL CHARACTERISTICS

V

= 5V, TA = 0°C to 70°C unless otherwise shown

DD

RETEMARAPLOBMYSSNOITIDNOCNIMPYTXAMSTINUSETON

ycneuqerFkcolCtupnIlaireSƒ

etaRataDtupnIlaireSRD

:stupnIkcolCdnaataDlaireS

emitesiR

puteS

dloH

rettiJ:kcolClellaraPt

dnaemitesiR:ataDlellaraP

emitllaF

ICS

IDS

T

t

R

t

US

t

DLOH

T

KLCJ

T

t

DP-R

n

C

C°52=

A

C°52=-0.1- p-psn7

A

A

L

,C°52=

Fp01=

001073zHM1

001073s/bM1

-

0.1

0.1

-3- sn

006

-

-

-

-

-

sp

sn

sn

ot%02

%08

gnisiR

foegde

ecnareloTyaleDKLCPotnDPt

D

-- 3±sn

tibotKLCP

doirep

ertnec

Test Level Legend

1. Production test at room temperature and nominal supply voltage with guardbands for supply and temperature ranges.

2. Production test at room temperature and nominal supply voltage with guardbands for supply and temperature ranges using correlated test.

3. Production test at room temperature and nominal supply voltage.

4. QA sample test.

5. Calculated result based on Level 1, 2, or 3.

6. Not tested. Guaranteed by design simulations.

7. Not tested. Based on characterization of nominal parts.

8. Not tested. Based on existing design/characterization data

ABSOLUTE MAXIMUM RATINGS

of similar product.

PARAMETER VALUE

ORDERING INFORMATION

Supply Voltage (VS = VDD - VSS)7V

Input Voltage Range (any input) -0.3 to (VDD + 0.3)V

PART NUMBER PACKAGE TEMPERATURE

GS9000CCPJ 28 Pin PLCC 0°C to 70°C

DC Input Current (any one input) ±10µA

Operating Temperature Range 0°C to 70°C

Storage Temperature Range -65°C to +150°C

GS9000CCTJ 28 Pin PLCC Tape 0°C to 70°C

Lead Temperature (Soldering, 10 seconds) 260°C

TSET

LEVEL

7

7

7

7

7

TSET

LEVEL

522 - 49 - 01

2

GS9000C

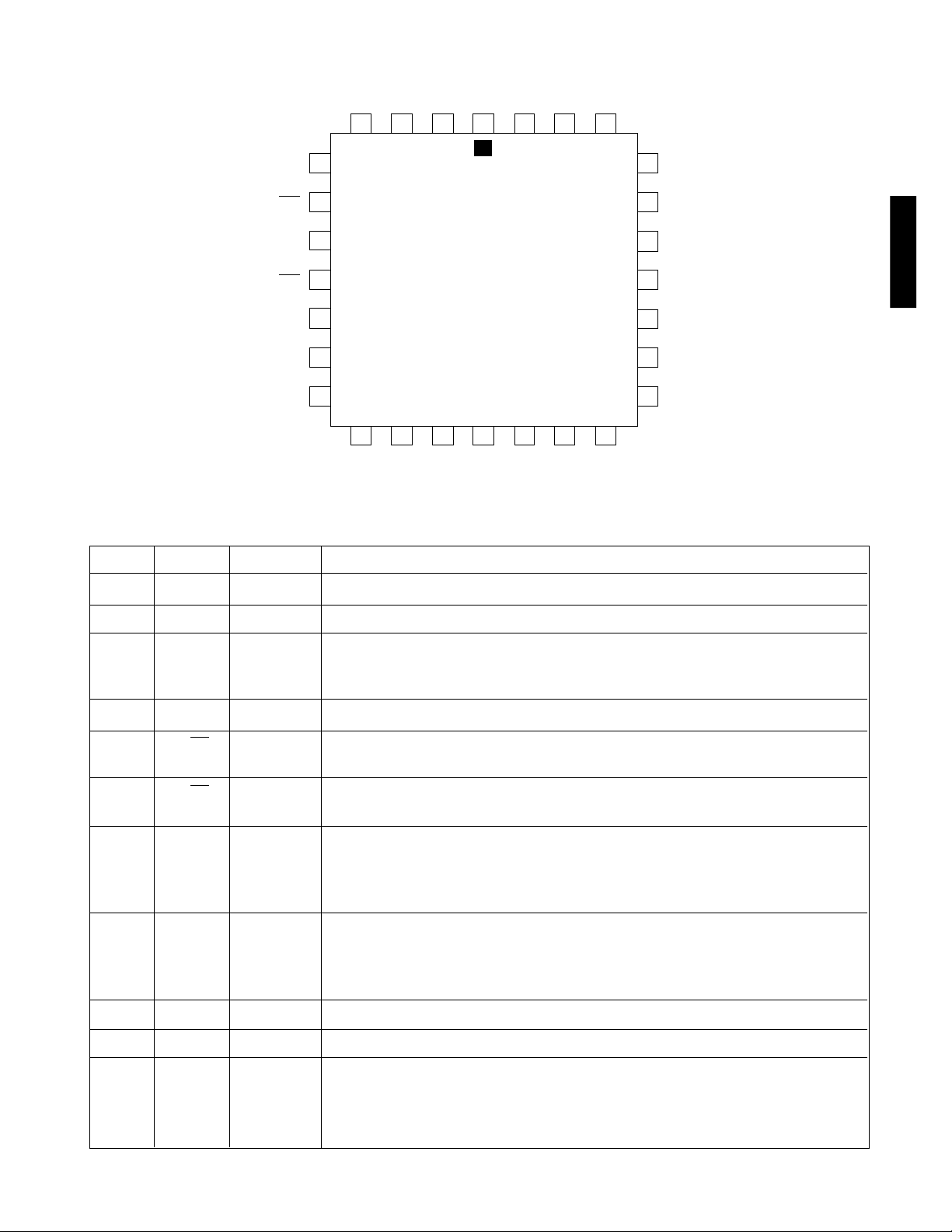

SDI

(MSB)

SWF VSS HSYNC PD9 PD8 V

V

SS

4 3 2 28 27 26

5

SS

25

PD7

SDI

SCI

6

7

24

23

PD6

PD5

GS9000C

SCI

SS1

SS0

SSC

8

9

10

11

12 13 14 15 16 17 18

VDD VDD SCE SWC PCLK PD0 V

Fig. 1 GS9000C Pin Outs, 28 Pin PLCC Package

TOP VIEW

22

21

20

19

DD

(LSB)

GS9000C PIN DESCRIPTIONS

PIN NO. SYMBOL TYPE DESCRIPTION

1 HSYNC Output Horizontal Sync Output. CMOS (TTL compatible) output that toggles for each TRS detected.

2V

SS

Power Supply. Most negative power supply connection.

3 SWF Output Sync Error Warning Flag. CMOS (TTL compatible) active high output that indicates the

preselected HSYNC Error Rate (HER). The HER is set with an RC time constant on the

SWC input.

PD4

PD3

PD2

PD1

4V

SS

Power Supply. Most negative power supply connection.

5,6 SDI/SDI Inputs Differential, pseudo-ECL serial data inputs. ECL voltage levels with offset of 3.0V to 4.0V

for operation up to 370MHz.

See AC Electrical Characteristics Table for details.

7,8 SCI/SCI Inputs Differential, pseudo-ECL serial clock inputs. ECL voltage levels with offset of 3.0V to 4.0V

for operation up to 370MHz.

See AC Electrical Characteristics Table for details

.

9,10 SS1/SS0 Output Standard Select Outputs. CMOS (TTL compatible) outputs used with the GS9005A Receiver in

order to perform an automatic standards select function. These outputs are generated by a 2

bit internal binary counter which stops cycling when there is no CARRIER present at the

GS9005A Receiver input or when a valid TRS is detected by the GS9000C.

11 SSC Input Standards Select Control. Analog input used to set a time constant for the standards select hunt

period. An external RC sets the time constant. When a GS9005A Receiver is used, the open

collector CARRIER DETECT output also connects to this pin in order to enable or disable the

internal 2 bit binary counter which controls the hunting process.

12 V

13 V

DD

DD

Power Supply. Most positive power supply connection.

Power Supply. Most positive power supply connection.

14 SCE Input Sync Correction Enable. Active high CMOS input which enables sync correction by not resetting

the GS9000C’s internal parallel timing on the first sync error. If the next incoming sync is in error,

internal parallel timing will be reset. This is to guard against spurious HSYNC errors. When SCE

is low, a valid sync will always reset the GS9000C’s parallel timing generator.

3

522 - 49 - 01

Loading...

Loading...