Gennum Corporation GS1501-CQR Datasheet

GENNUM CORPORATION P.O. Box 489, Stn. A, Burlington, Ontario, Canada L7R 3Y3

Tel. +1 (905) 632-2996 Fax. +1 (905) 632-5946 E-mail: info@gennum.com

www.gennum.com

Revision Date: November 2000 Document No. 522 - 34 - 00

PRELIMINARY DATA SHEET

GS1501

FEATURES

• SMPTE 292M compliant

• NRZ(I) encoding

• SMPTE 292M scrambler with BYPASS option

• internal FIFOs for ANC data insertion

(1024 Bytes on Y and C channels)

• selectable TRS insertion

• selectable line number insertion

• selectable line based CRC insertion

• selectable active picture illegal code re-mapping

• 20 bit 3.3V CMOS compatible input data bus

• optimized output interface to GS1522

• single +3.3V power supply

• 5V tolerant I/O

APPLICATIONS

SMPTE 292M Serial Digital Interfaces.

DESCRIPTION

The GS1501 HDTV Serial Digital Formatter formats the

HDTV Luma and Chroma data according to SMPTE 292M

prior to serialization by the GS1522 HDTV Serializer. The

GS1501 optionally inserts TRS and line number signals

based on externally supplied H, V and F signals. The

device also allows the insertion of CRCs based on TRS

signals embedded in the input data streams, should the

user choose not to supply external HVF signals.

Following the insertion of TRS, Line Number, and CRC,

protected words of 000-003 and 3FC to 3FF occurring

during the active video period are optionally re-mapped to

004 and 3FB respectively. In addition, ANC data may be

inserted into the video stream through an internal FIFO

interface. Prior to exiting the device SMPTE 292M compliant

NRZ(I) encoding and scrambling may be performed on the

data stream.

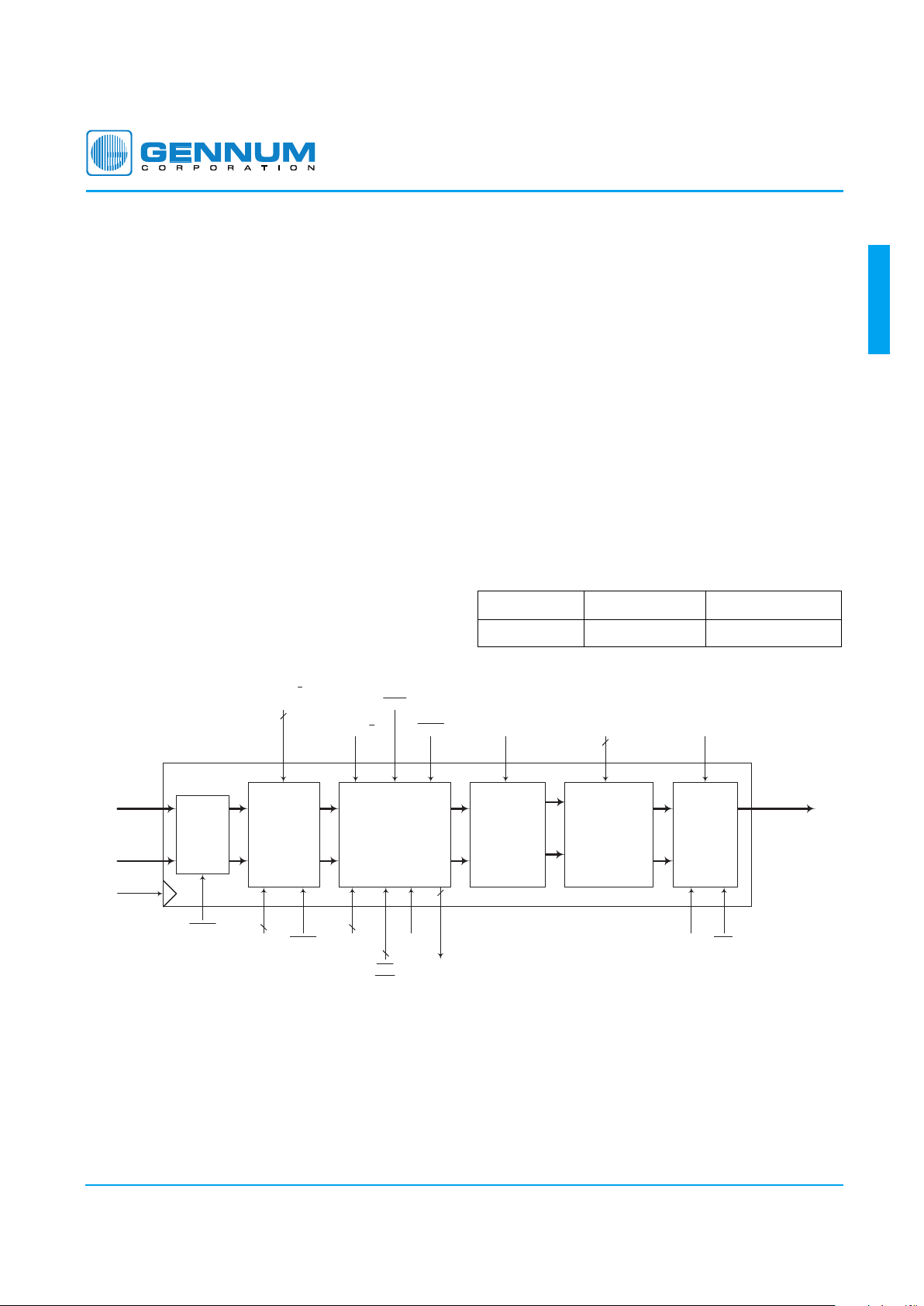

BLOCK DIAGRAM

ORDERING INFORMATION

PART NUMBER PACKAGE TEMPERATURE

GS1501-CQR 128 pin MQFP 0°C to 70°C

INPUT

BUFFER

and

BLANKER

TRS

and

LINE NUMBER

DETECTION

PCLK_IN

DATA_OUT

[19:0]

[H:V:F]

BP_SC

ILLEGAL CODE

REMAPPING

CODE

PROTECT

ANC_IN[9:0]

FF_STA

[2:0]

TRS_INS

LN_INS

CRC_INS

NRZI

ENCODER

SMPTE

SCAMBLER

ANC_Y/C

FFRST

REN

WEN

OEN

2

3

3

ANC DATA

INSERTION

FIFOS

TRS

INSERTION

LINE NUMBER

INSERTION

CRC INSERTION

DATA_IN

[19:10]

(LUMA)

DATA_IN

[9:0]

(CHROMA)

BLANK

TRS_Y/C

DET_TRS

2

FOEN

10

W_CLK

3

SRSTRSTLN

HD-LINX

™

GS1501

HDTV Serial Digital Formatter

with ANC FIFOs

GENNUM CORPORATION

522 - 34 - 00

2

GS1501

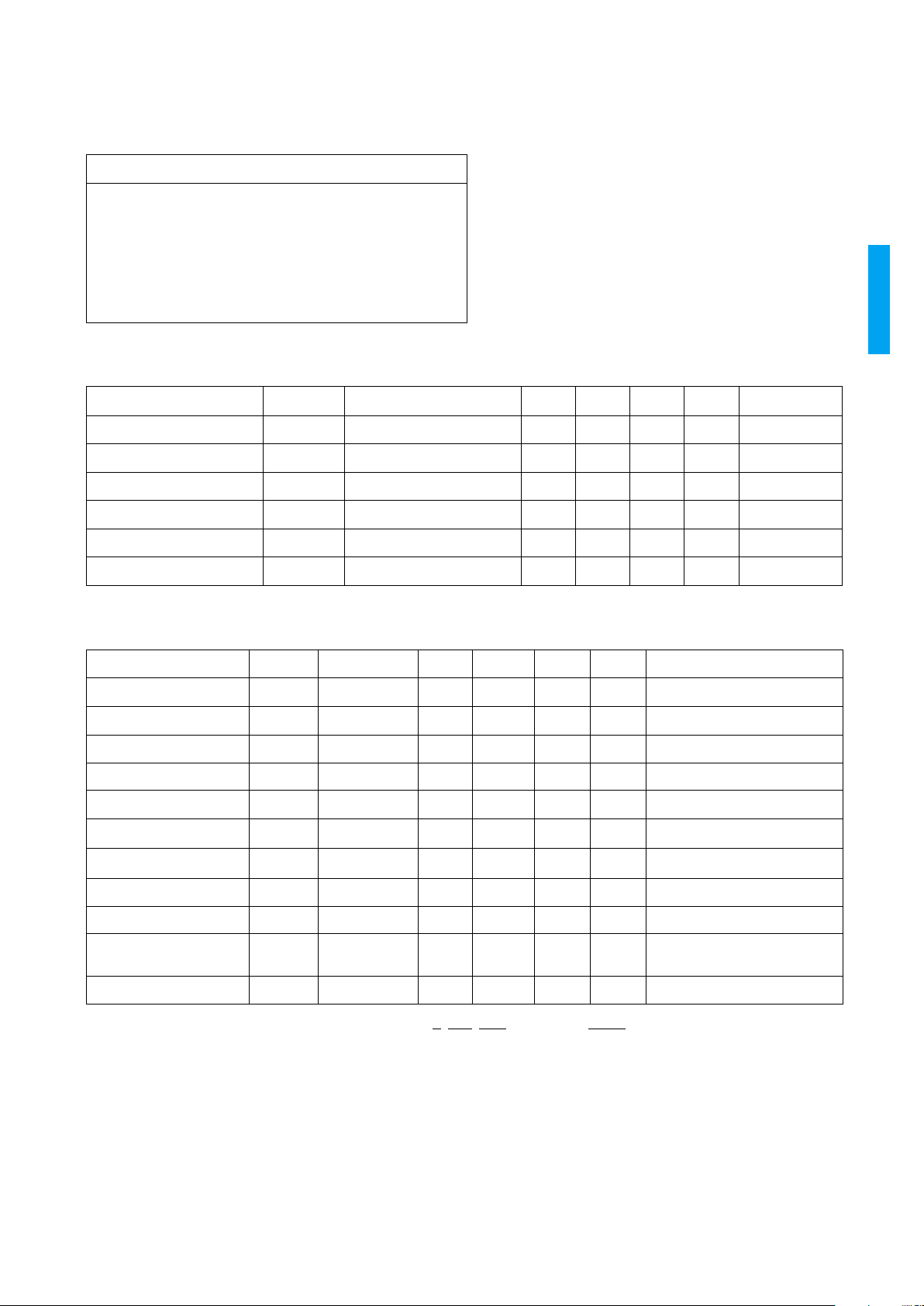

ABSOLUTE MAXIMUM RATINGS

PARAMETER VALUE

Supply Voltage -0.5V to +4.6V

Input Voltage Range (any input) -0.5V < V

IN

< 5.5V

Operating Temperature Range 0°C ≤ T

A

≤ 70°C

Storage Temperature Range -40°C ≤ T

S

≤ 125°C

Lead Temperature (soldering 10 seconds) 260°C

DC ELECTRICAL CHARACTERISTICS

VDD = 3.0 to 3.6V, TA = 0°C to 70°C, unless otherwise shown

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS NOTES

Positive Supply Voltage V

DD

3.0 3.3 3.6 V

Supply Current

Ι

DD

ƒ = 74.25MHz, TA = 25°C - 402 480 mA

Input Logic LOW Voltage V

IL

I

LEAKAGE

< 10µA - - 0.8 V

Input Logic HIGH Voltage V

IH

I

LEAKAGE

< 10µA 2.1 3.3 5.0 V

Output Logic LOW Voltage V

OL

VDD = 3.0 to 3.6V,

I

OL

= 4mA - 0.2 0.4 V

Output Logic HIGH Voltage V

OH

VDD = 3.0 to 3.6V,

I

OH

= -4mA 2.6 - - V

AC ELECTRICAL CHARACTERISTICS

VDD =3.0 to 3.6V, TA = 0°C to 70°C

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS NOTES

Clock Input Frequency F

HSCI

- 74.25 80 MHz Also supports 74.25/1.001MHz

Input Data Setup Time t

SU

2.5 - - ns 50% levels

Input Data Hold Time t

IH

1.5 - - ns 50% levels

Input Clock Duty Cycle 40 - 60 %

Output Data Hold Time t

OH

With 15pF load 2.0 - - ns

Output Enable Time t

oen

With 15pF load - - 8 ns

Output Disable Time t

odis

With 15pF load - - 9 ns

Output Data Delay Time t

OD

With 15pF load - - 10 ns Note 2

Output Data Rise/Fall Time With 15pF load - - 2.5 ns 20% to 80% levels

FIFO Input Data Setup

Time

t

FSU

8.0 - - ns Note 1

FIFO Input Data Hold Time t

FIH

4.0 - - ns Note 1

NOTES:

1. The following signals need to adhere to this timing: ANC_Y/C

, REN, WEN, ANC_IN[9:0], FFRST.

2. Timing of the FF_STA[2:0] outputs may be greater than specified.

GENNUM CORPORATION

522 - 34 - 00

3

GS1501

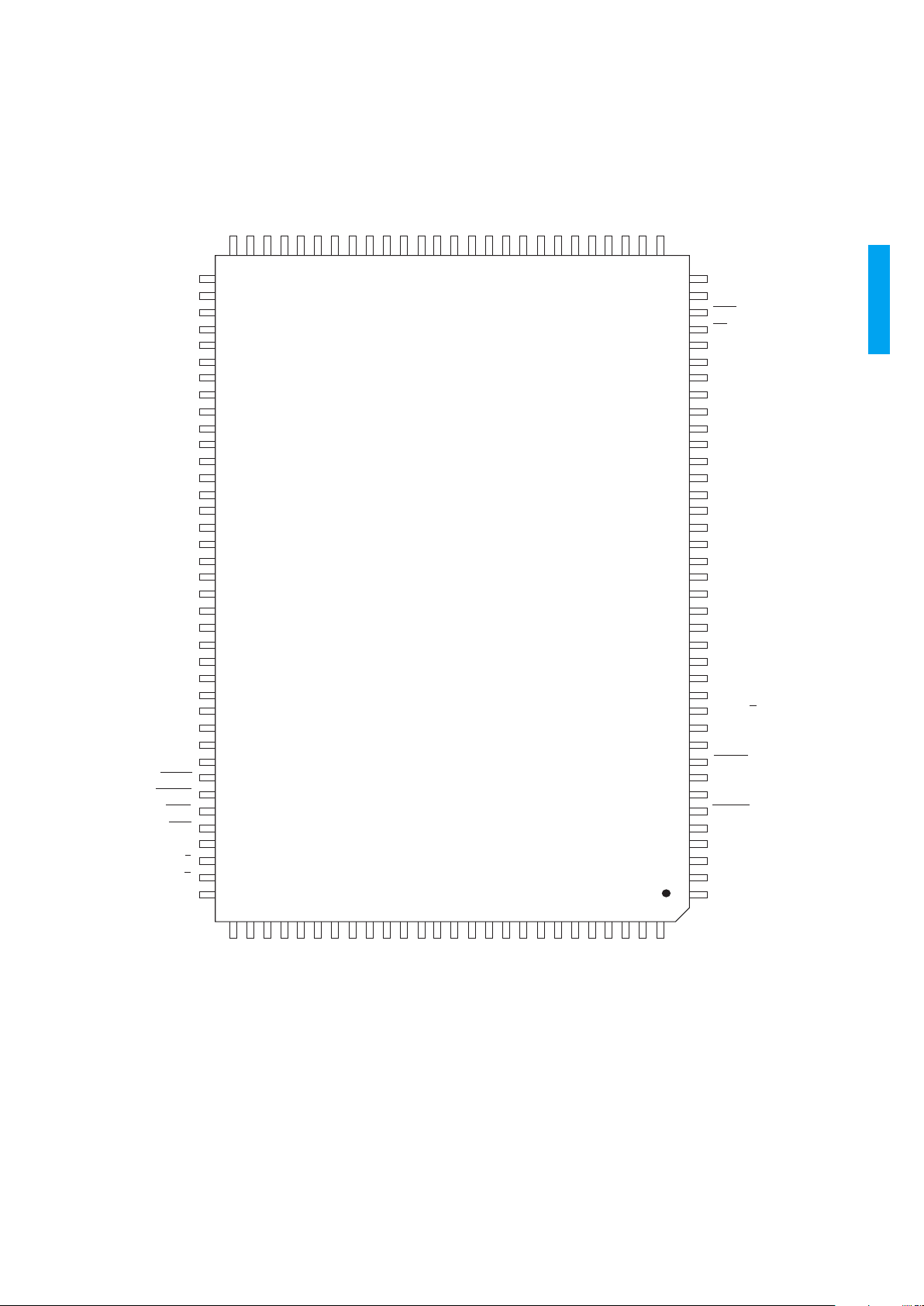

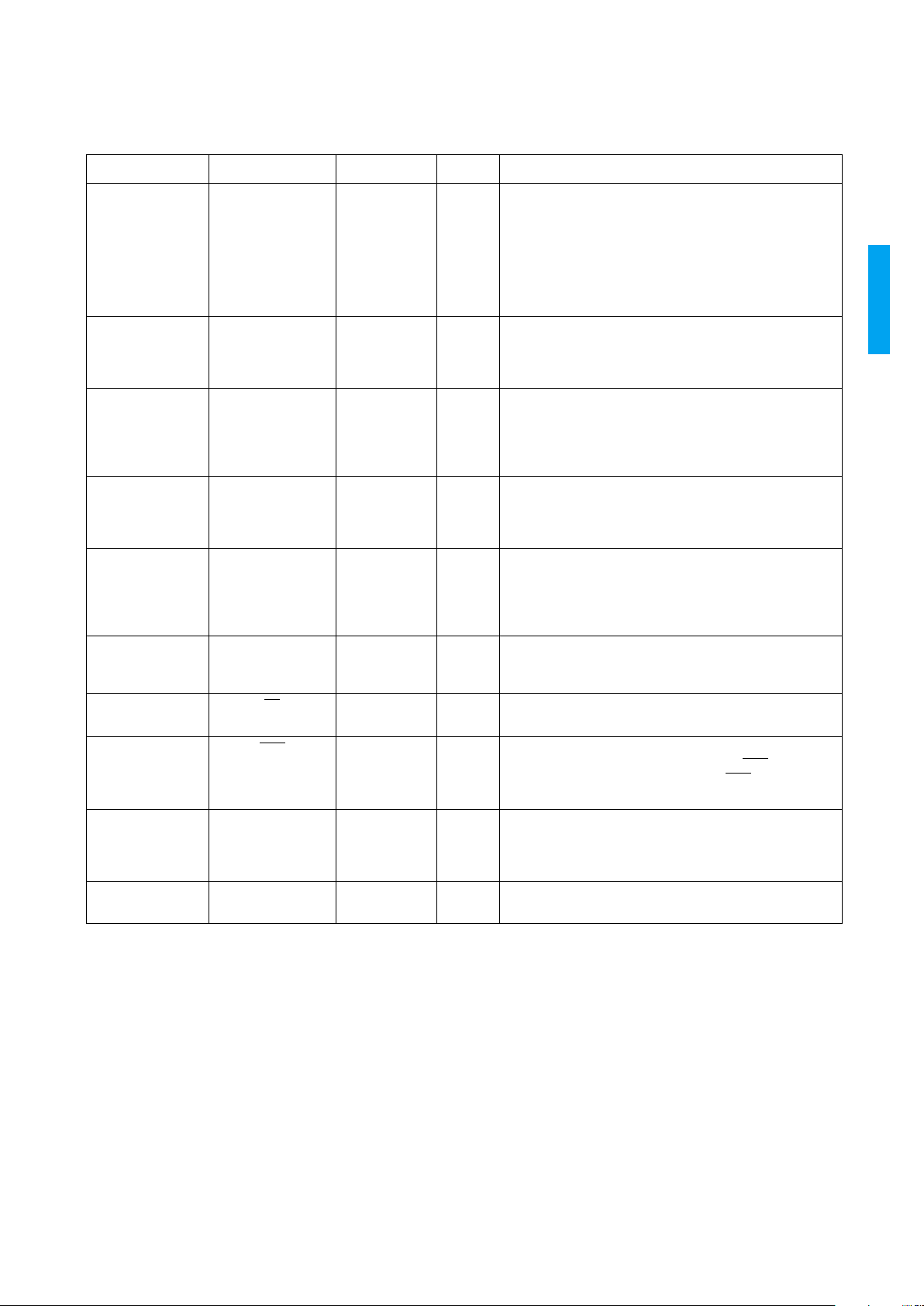

PIN CONNECTIONS

V

DD

GND

OEN

TN

NC

NC

NC

NC

NC

NC

NC

NC

NC

V

DD

GND

F

V

H

V

DD

GND

V

DD

GND

CRC_INS

LN_INS

GND

TRS_INS

TRS Y/C

SRST

BP_SC

RSTLN

CODE_PROTECT

GND

BLANK

DET_TRS

GND

V

DD

GND

PCLK_IN

NC

NC

NC

V

DD

GND

TEST

NC

NC

FF_STA[0]

FF_STA[1]

FF_STA[2]

ANC_IN[9]

ANC_IN[8]

V

DD

GND

ANC_IN[7]

V

DD

GND

ANC_IN[6]

ANC_IN[5]

ANC_IN[4]

ANC_IN[3]

ANC_IN[2]

ANC_IN[1]

ANC_IN[0]

V

DD

GND

W_CLK

V

DD

GND

FOEN

FFRST

WEN

REN

V

DD

FM_I/E

ANC_Y/C

V

DD

DATA_OUT[19]

DATA_OUT[18]

DATA_OUT[17]

DATA_OUT[16]

DATA_OUT[15]

VDDGND

DATA_OUT[14]

DATA_OUT[13]

DATA_OUT[12]

DATA_OUT[11]

DATA_OUT[10]

DATA_OUT[9]

VDDGND

DATA_OUT[8]

DATA_OUT[7]

VDDGND

DATA_OUT[6]

DATA_OUT[5]

DATA_OUT[4]

DATA_OUT[3]

DATA_OUT[2]

DATA_OUT[1]

DATA_OUT[0]

DATA_IN[19]

DATA_IN[18]

DATA_IN[17]

DATA_IN[16]

DATA_IN[15]

DATA_IN[14]

V

DD

GND

DATA_IN[13]

DATA_IN[12]

DATA_IN[11]

DATA_IN[10]

V

DD

GND

DATA_IN[9]

DATA_IN[8]

DATA_IN[7]

DATA_IN[6]

DATA_IN[5]

DATA_IN[4]

DATA_IN[3]

DATA_IN[2]

DATA_IN[1]

DATA_IN[0]

V

DD

GND

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

101

102

64636261605958575655545352515049484746454443424140

39

103

104

105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

GS1501

TOP

VIEW

GENNUM CORPORATION

522 - 34 - 00

4

GS1501

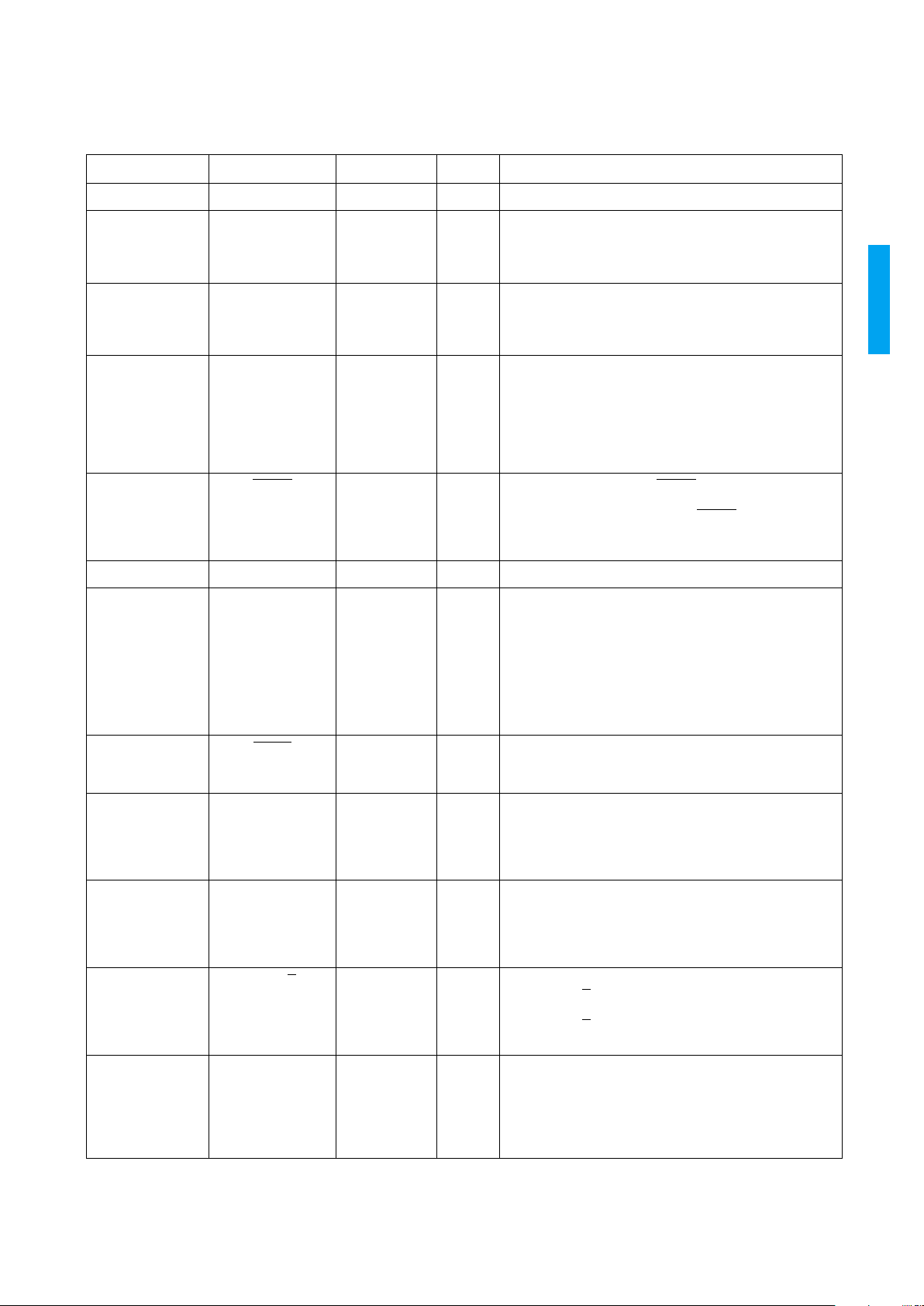

PIN DESCRIPTIONS

NUMBER SYMB OL TIMING TYPE DESCRIPTION

1 PCLK_IN Synchronous Input

Parallel data clock input.

74.25MHz or 74.25/1.001MHz.

2, 4, 14, 19, 24, 37,

46, 50, 58, 69, 79,

82, 91, 94, 110,

116, 128

GND N/A Ground

Ground.

Ground power supply connections.

3, 20, 25, 38, 47,

51, 59, 68, 78, 81,

90, 93, 109, 115,

127

V

DD

N/A Power

Power.

Positive power supply connections.

5 DET_TRS Non-

synchronous

Input

Control Signal Input.

Used to enable or disable the

detection of the TRS signals embedded in the video stream.

When DET _TRS is high, the device detects the TRS signals

embedded in the input video stream and uses the detected

HVF signals instead of the external HVF signals. When

DET _TRS is low, TRS detection is disabled. The device

uses the external supplied HVF signals.

6BLANK

Synchronous

wrt PCLK_IN

Input

Control Signal Input.

When BLANK is low, the device sets

the accompanying LUMA and CHROMA data to their

appropriate blanking levels. When BLANK

is high, the

LUMA and CHROMA data streams pass through this stage

of the device unaltered. See Figure 3.

7, 17 GND N/A This pin must be connected to GND for normal operation

8 CODE_PROTECT Non-

synchronous

Input

Control Signal Input.

Used to enable or disable re-mapping

of out-of-range words contained in the active portion of the

video signal. When this signal is high, the device re-maps

out-of-range words contained within the active portion of the

video signal into CCIR-601 compliant words. Values

between 000-003 are re-mapped to 004. Values between

3FC and 3FF are re-mapped to 3FB. When this signal is low,

out-of-range words in the active video region pass through

the device unaltered.

9 RSTLN

Synchronous

wrt PCLK_IN

Input

Control Signal Input.

This is the line number reset signal. A

high-to-low edge of this signal resets the line number

counter of the device to one (1). See Figure 2.

10 BP_SC Non-

synchronous

Input

Control Signal Input.

Used to enable or bypass the

SMPTE292M scrambler and NRZ(I) encoder. When BP_SC

is low, the video stream is scrambled according to SMPTE

292M and NRZ(I) encoded. When BP_SC is high, the

scrambler and NRZ(I) encoder are by-passed.

11 SRST Non-

synchronous

Input

Control Signal Input.

Used to reset the SMPTE292M

scrambler and NRZI encoder. When SRST is low, the

scrambler and encoder operate normally. A low to high

transition on SRST causes the scrambler and encoder to

reset.

12 TRS_Y/C

Non-

synchronous

Input

Control Signal Input.

Only used when DET_TRS is high.

When TRS_Y/C

is high, the device detects and uses TRS

signals embedded in the LUMA (DATA_IN[19:10]) channel.

When TRS_Y/C

is low, the device detects and uses TRS

signals embedded in the CHROMA (DATA_IN[9:0]) channel.

13 TRS_INS Non-

synchronous

Input

Control Signal Input.

Used to enable or disable insertion of

TRS into the video streams. When TRS_INS is high, the

device inserts SMPTE 292M compliant TRS signals into the

input LUMA and CHROMA data streams based on the

supplied HVF signals. When TRS_INS is low, the device

does not insert TRS signals.

GENNUM CORPORATION

522 - 34 - 00

5

GS1501

15 LN_INS Non-

synchronous

Input

Control Signal Input.

Used to enable or disable insertion of

line numbers into the video stream. When LN_INS is high,

the device inserts SMPTE 292M compliant line number

information into the LUMA and CHROMA channels. When

LN_INS is low, the device does not insert the line number

information into the LUMA and CHROMA channels. Line

number insertion is only available when user supplied

external FVH data is used (DET_TRS set LOW).

16 CRC_INS Non-

synchronous

Input

Control Signal Input.

Used to enable or disable insertion of

CRC's into the video stream. When CRC_INS is high, the

device calculates and inserts line based CRCs. When

CRC_INS is low, this feature is disabled.

21 H Synchronous

wrt PCLK_IN

Input

Control Signal Input.

This signal indicates the Horizontal

blanking period of the input video data stream. The device

inserts HDTV TRS based on the supplied HVF signals. Refer

to Figure 4 for required timing of H relative to LUMA

(DATA_IN[19:10]) and CHROMA (DATA_IN[9:0]).

22 V Synchronous

wrt PCLK_IN

Input

Control Signal Input.

This signal indicates the vertical

blanking period of the input video data streams. Refer to

Figure 4 for required timing of V relative to LUMA

(DATA_IN[19:10]) and CHROMA (DATA_IN[9:0]).

23 F Synchronous

wrt PCLK_IN

Input

Control Signal Input.

This signal indicates the ODD/EVEN

field of the input video data streams. Refer to Figure 4 for

required timing of F relative to LUMA (DATA_IN[19:10]) and

CHROMA (DATA_IN[9:0]). When the input video format is

progressive scan, F should remain low at all times.

26, 27, 28, 29, 30,

31, 32, 33, 34, 65,

66, 67, 71, 72,

NC N/A

No Connect.

Do not connect these pins

35 TN

N/A TEST

Test Pin.

Used for test purposes only. This pin must be

connected to V

DD

for normal operation

36 OEN

See A/C

Electrical

Characteristics

section

Input

Control Signal Input.

Used to enable DATA_OUT[19:0]

output bus or set it to a high Z state. When OEN

is low, the

DATA_OUT[19:0] bus is enabled. When OEN

is high, the

DATA_OUT[19:0] bus is disabled and in a high Z state.

39, 40, 41, 42, 43,

44, 45, 48, 49, 52,

53, 54, 55, 56, 57,

60, 61, 62, 63, 64

DATA_OUT[19:0] Synchronous

wrt PCLK_IN

Outputs

Output Data Bus.

The device generates a 20 bit wide data

stream running at 74.25 (or 74.25/1.001) MHz.

DATA_OUT[19] is the MSB and DATA_OUT[0] is the LSB.

70 TEST N/A TEST

Test Pin.

Used for test purposes only. This pin must be

connected to GND for normal operation.

PIN DESCRIPTIONS (Continued)

NUMBER SYMB OL TIMING TYPE DESCRIPTION

Loading...

Loading...