GENESYS LOGIC GL843 User Manual

Ru.4

Xu062 f

Genesys Logic, Inc.

GL843

High Speed USB 2.0 With ADF

2-in-1 Scanner Controller

For 3x Series

Datasheet

Revision 1.02

Mar. 13, 2006

GL843 High Speed USB2.0 With ADF 2-in-1 Scanner Controller For 3x

Copyright:

Copyright © 2006 Genesys Logic Incorporated. All rights reserved. No part of the materials may be

reproduced in any form or by any means without prior written consent of Genesys Logic Inc..

Disclaimer:

ALL MATERIALS ARE PROVIDED "AS IS" WITHOUT EXPRESS OR IMPLIED WARRANTY OF ANY

KIND. NO LICENSE OR RIGHT IS GRANTED UNDER ANY PATENT OR TRADEMARK OF

GENESYS LOGIC INC.. GENESYS LOGIC HEREBY DISCLAIMS ALL WARRANTIES AND

CONDITIONS IN REGARD TO MATERIALS, INCLUDING ALL WARRANTIES, IMPLIED OR

EXPRESS, OF MERCHANTABILITY, FITNESS FOR ANY PARTICULAR PURPOSE, AND

NON-INFRINGEMENT OF INTELLECTUAL PROPERTY. IN NO EVENT SHALL GENESYS LOGIC

BE LIABLE FOR ANY DAMAGES INCLUDING, WITHOUT LIMITATION, DAMAGES RESULTING

FROM LOSS OF INFORMATION OR PROFITS. PLEASE BE ADVISED THAT THE MATERIALS

MAY CONTAIN ERRORS OR OMMISIONS. GENESYS LOGIC MAY MAKE CHANGES TO THE

MATERIALS OR TO THE PRODUCTS DESCRIBED THEREIN AT ANY TIME WITHOUT NOTICE.

Trademarks:

is a registrated trademark of Genesys Logic Inc..

All trademarks are the properties of their respective owners.

Office:

Genesys Logic, Inc.

12F, No. 205, Sec. 3, Beishin Rd., Shindian City,

Taipei, Taiwan

Tel: (886-2) 8913-1888

Fax: (886-2) 6629-6168

http://www.genesyslogic.com

©2000-2006 Genesys Logic Inc. - All rights reserved. Page 2

GL843 High Speed USB2.0 With ADF 2-in-1 Scanner Controller For 3x

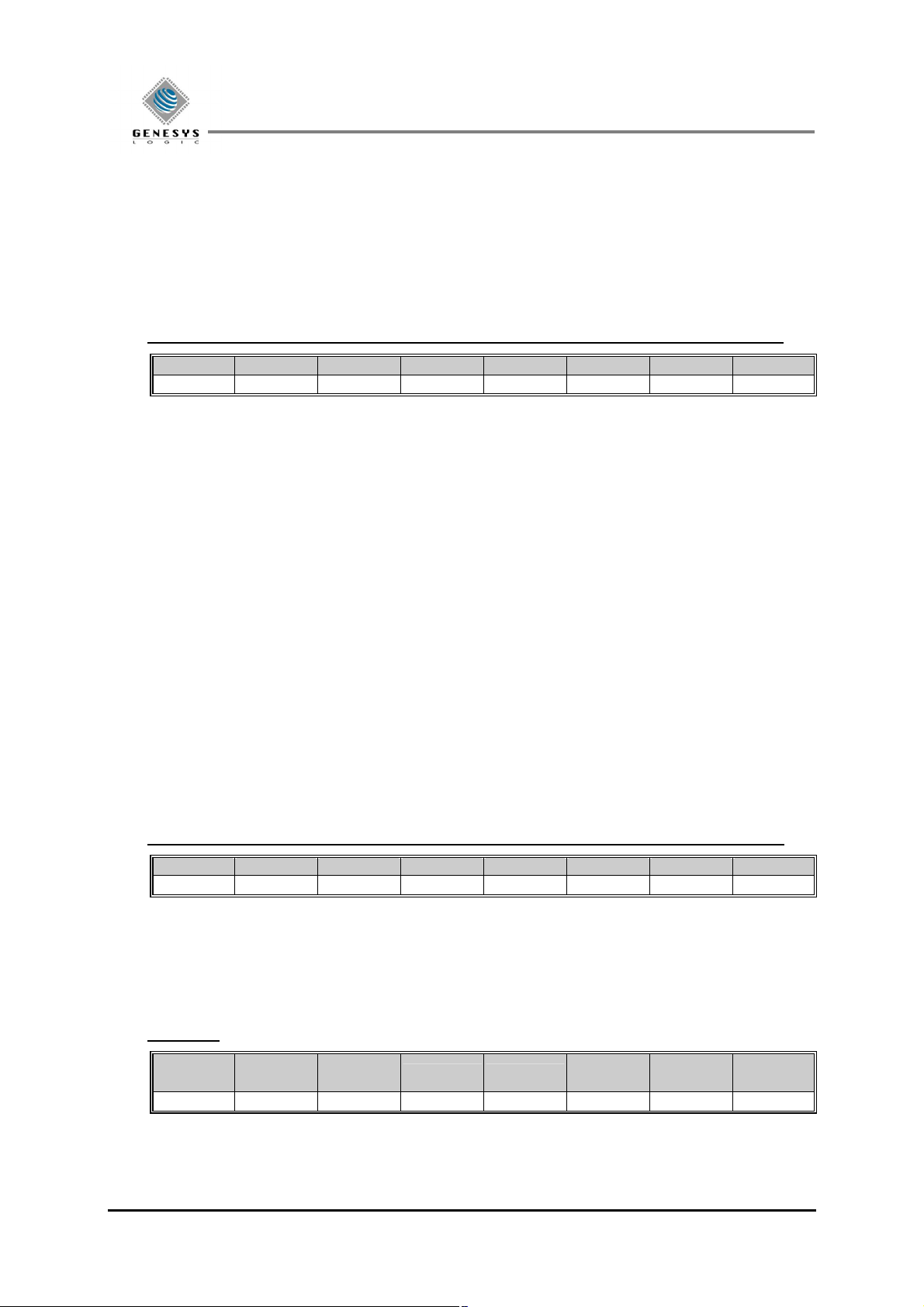

Revision History

Revision Date Description

1.00 04/14/2005 First formal release

1.01 11/10/2005 Add 208 QFP PinOut, Pin List, Package Dimension

1.02 03/13/2006 Delete”V

”, Table 7.1, P.81

ESD

©2000-2006 Genesys Logic Inc. - All rights reserved. Page 3

GL843 High Speed USB2.0 With ADF 2-in-1 Scanner Controller For 3x

TABLE OF CONTENTS

CHAPTER 1 GERERAL DESCRIPTION.................................................6

CHAPTER 2 FEATURES...........................................................................7

CHAPTER 3 PIN ASSIGNMENT..............................................................9

3.1 PINOUTS..................................................................................................9

3.2 PIN LIST ................................................................................................11

3.3 PIN DESCRIPTIONS ................................................................................14

CHAPTER 4 REGISTERS........................................................................17

4.1 REGISTERS BASE ADDRESS ...................................................................17

4.2 REGISTER DESCRIPTIONS......................................................................21

4.3 REGISTER MAPPING..............................................................................64

4.3.1 Shading Mapping (Chunky for Single Bank)..............................64

4.3.2 Shading Mapping (Chunky for Double Bank)............................64

4.3.3 Image Buffer Mapping.................................................................65

CHAPTER 5 BLOCK DIAGRAM............................................................68

5.1 USB2.0 SYSTEM BLOCK DIAGRAM .......................................................68

5.2 FUNCTION BLOCK DIAGRAM ................................................................68

CHAPTER 6 FUNCTIONAL DESCRIPTION........................................69

CHAPTER 7 ELECTRICAL CHARACTERISTICS..............................81

7.1 ABSOLUTE MAXIMUM RATINGS (VOLTAGE REFERENCED TO GND)...81

7.2 DC CHARACTERISTICS (DIGITAL PINS): 3.3 V LOGIC CORE OR PADS .81

7.3 DC CHARACTERISTICS (DIGITAL PINS): 5.0 V PADS ............................82

7.4 DC CHARACTERISTICS (D+/D-)............................................................82

CHAPTER 8 PACKAGE DIMENSION...................................................83

©2000-2006 Genesys Logic Inc. - All rights reserved. Page 4

GL843 High Speed USB2.0 With ADF 2-in-1 Scanner Controller For 3x

LIST OF FIGURES

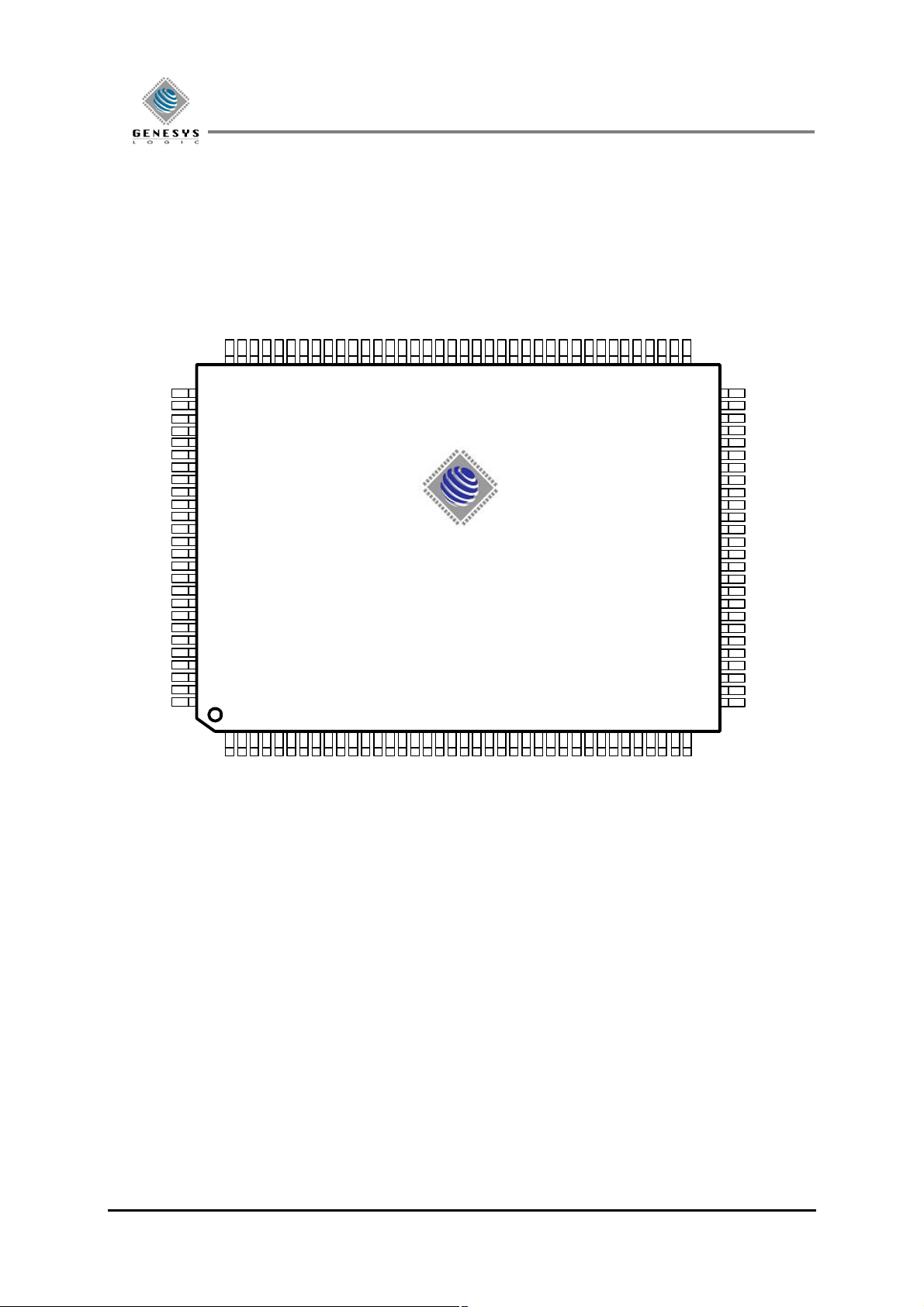

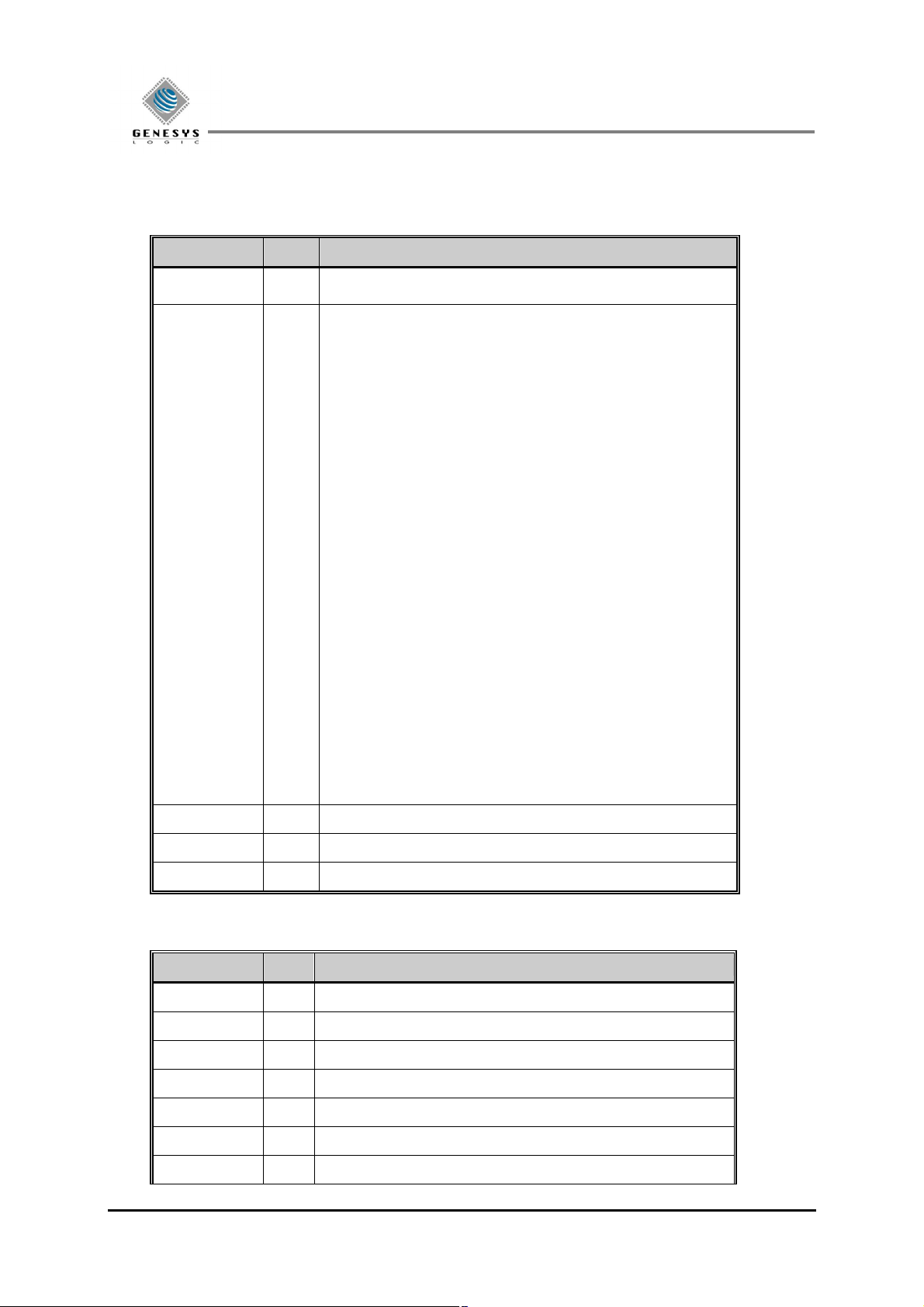

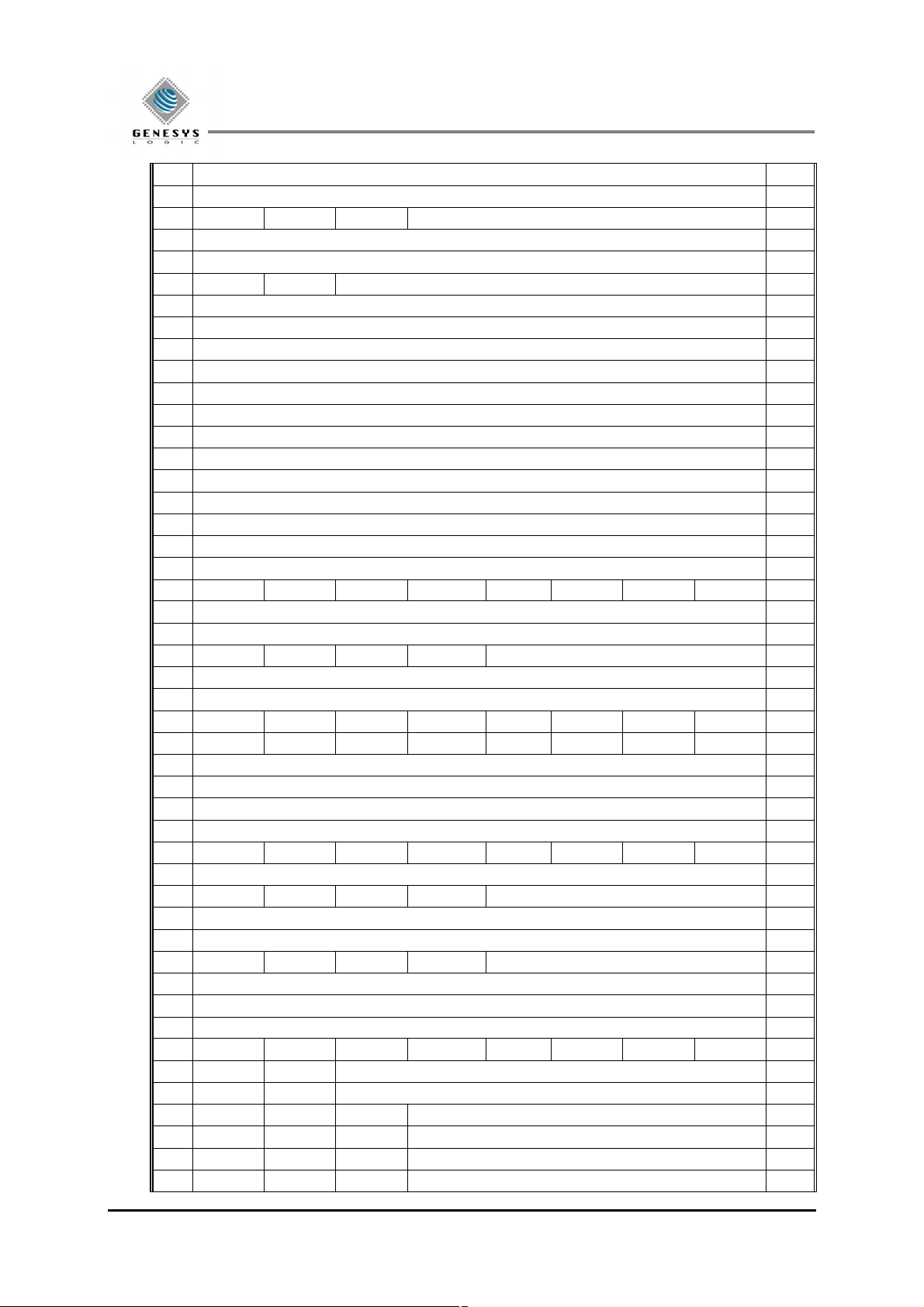

FIGURE 3.1 – 128 PIN QFP PINOUT DIAGRAM .................................................................9

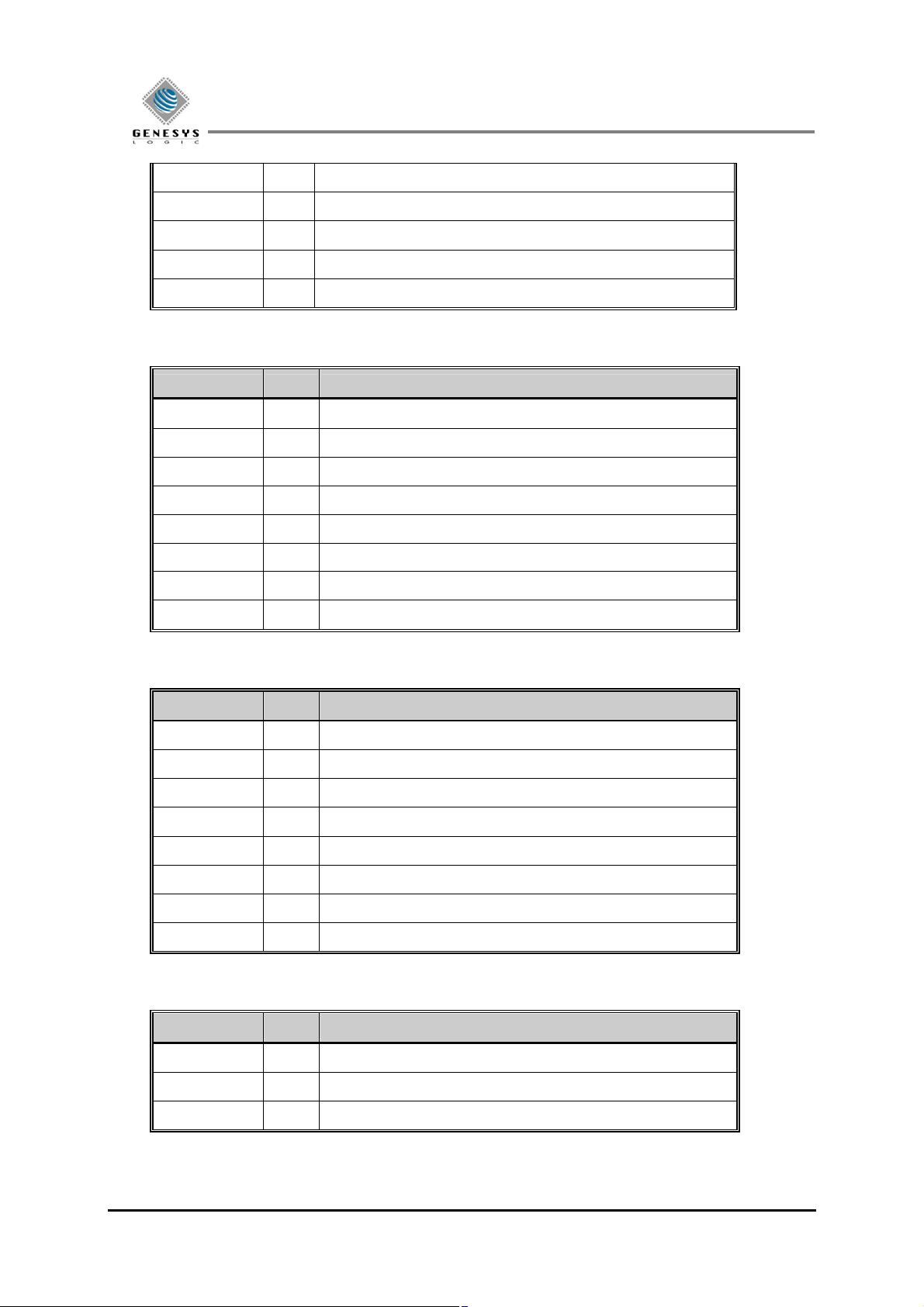

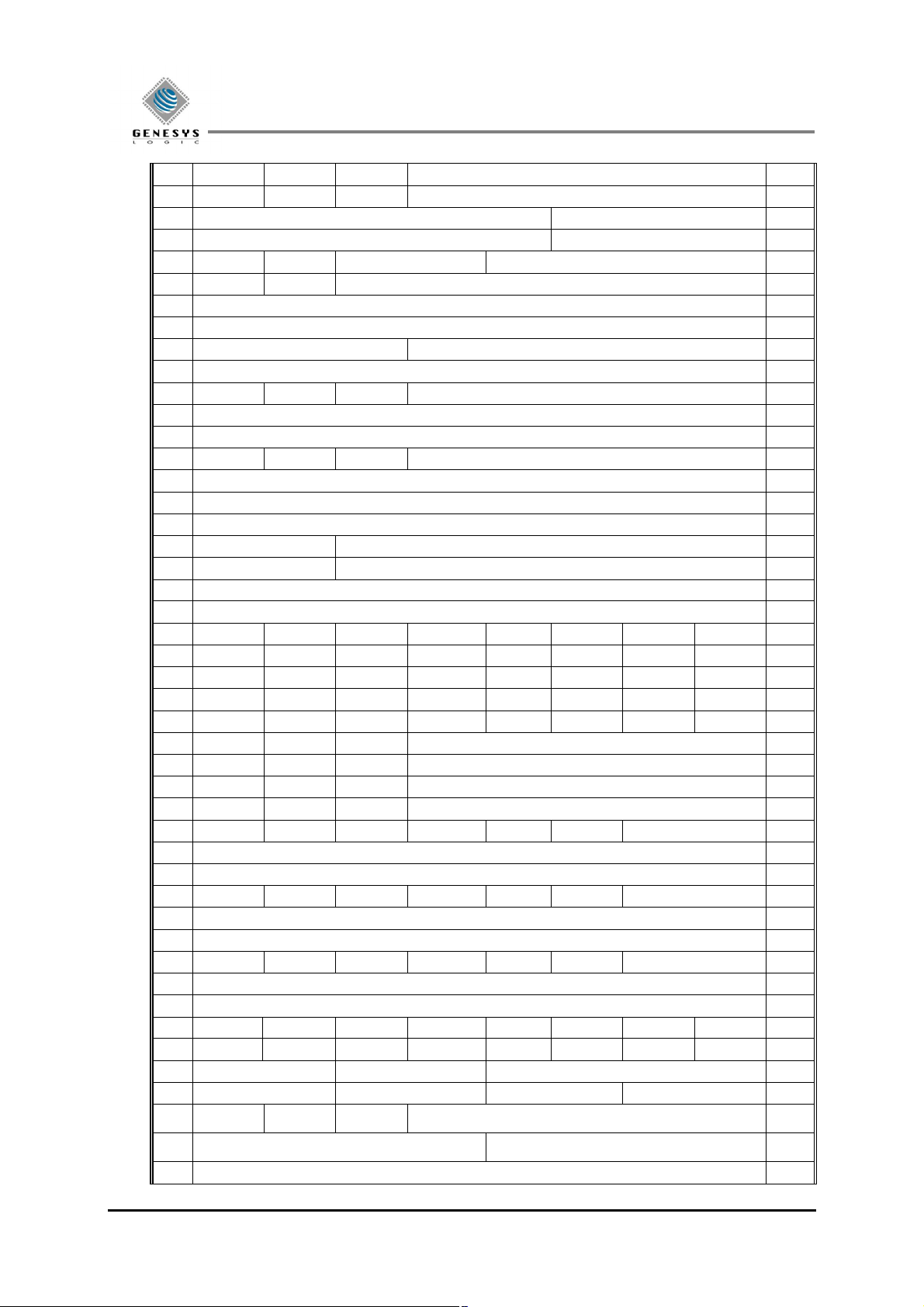

FIGURE 3.1 – 208 PIN QFP PINOUT DIAGRAM ...............................................................10

FIGURE 5.1 - USB2.0 SYSTEM BLOCK DIAGRAM ...........................................................68

FIGURE 5.2 - FUNCTION BLOCK DIAGRAM.....................................................................68

FIGURE 8.1 - GL843 128 PIN QFP PACKAGE.................................................................83

FIGURE 8.2- GL843 208 PIN QFP PACKAGE..................................................................84

LIST OF TABLES

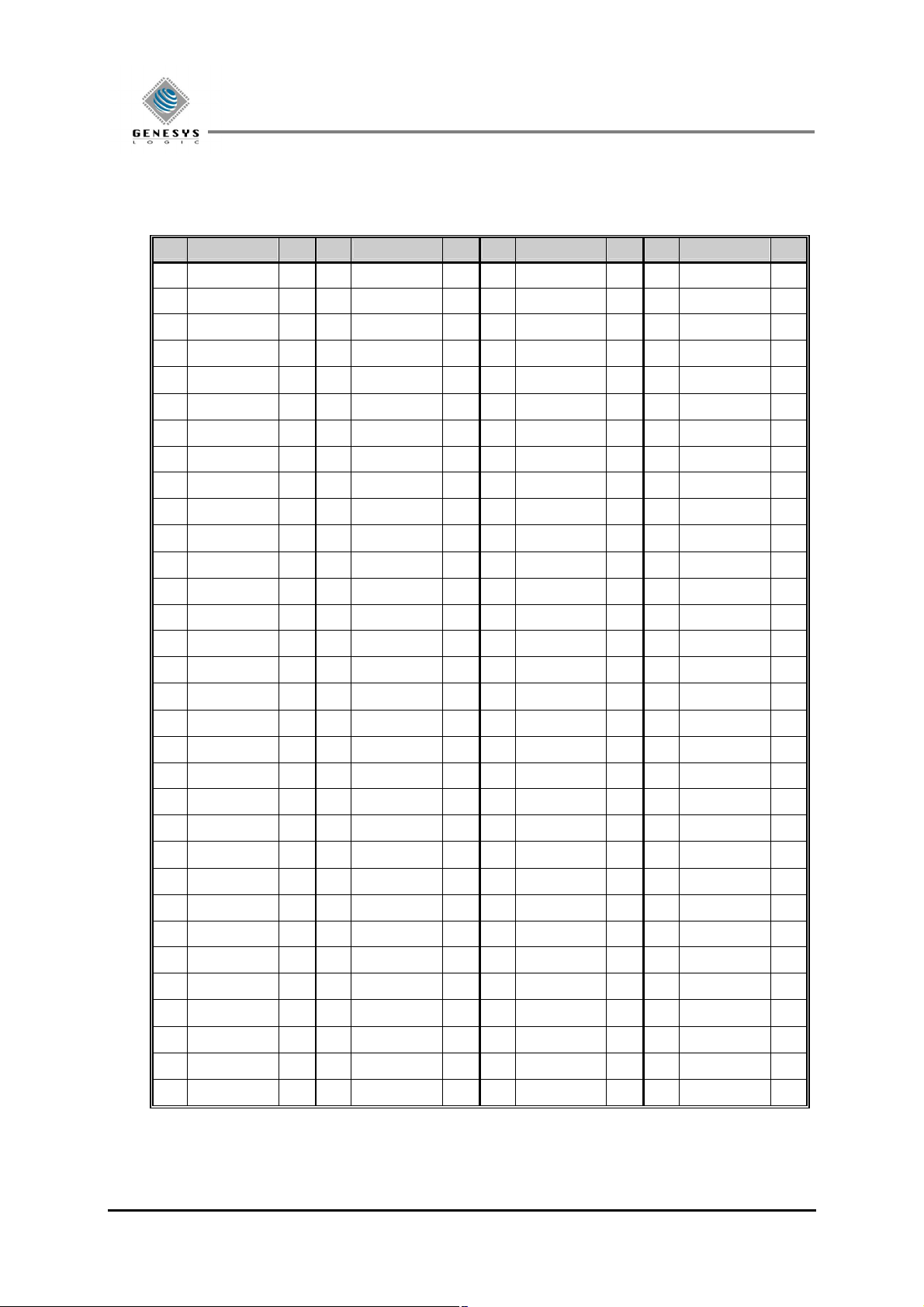

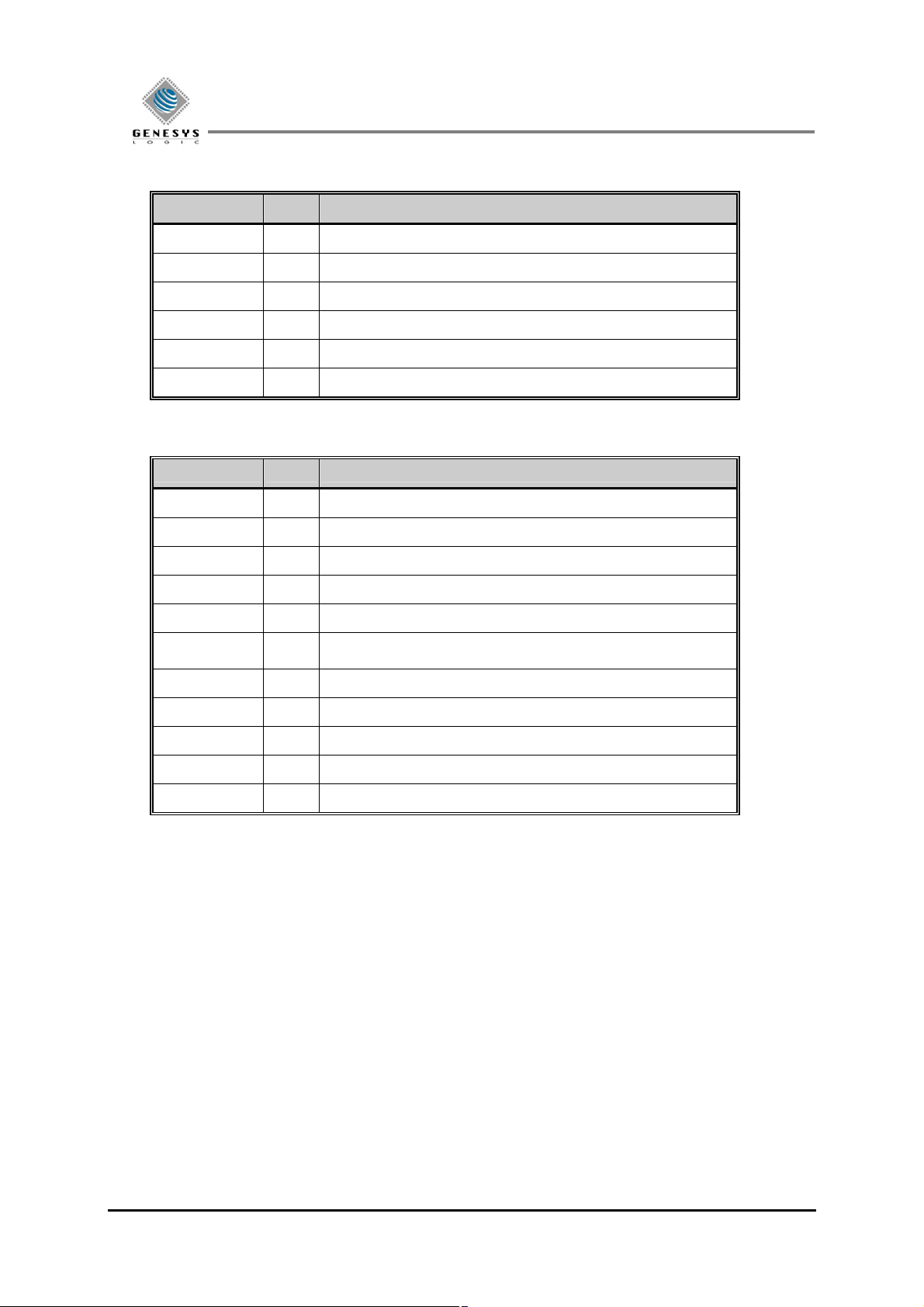

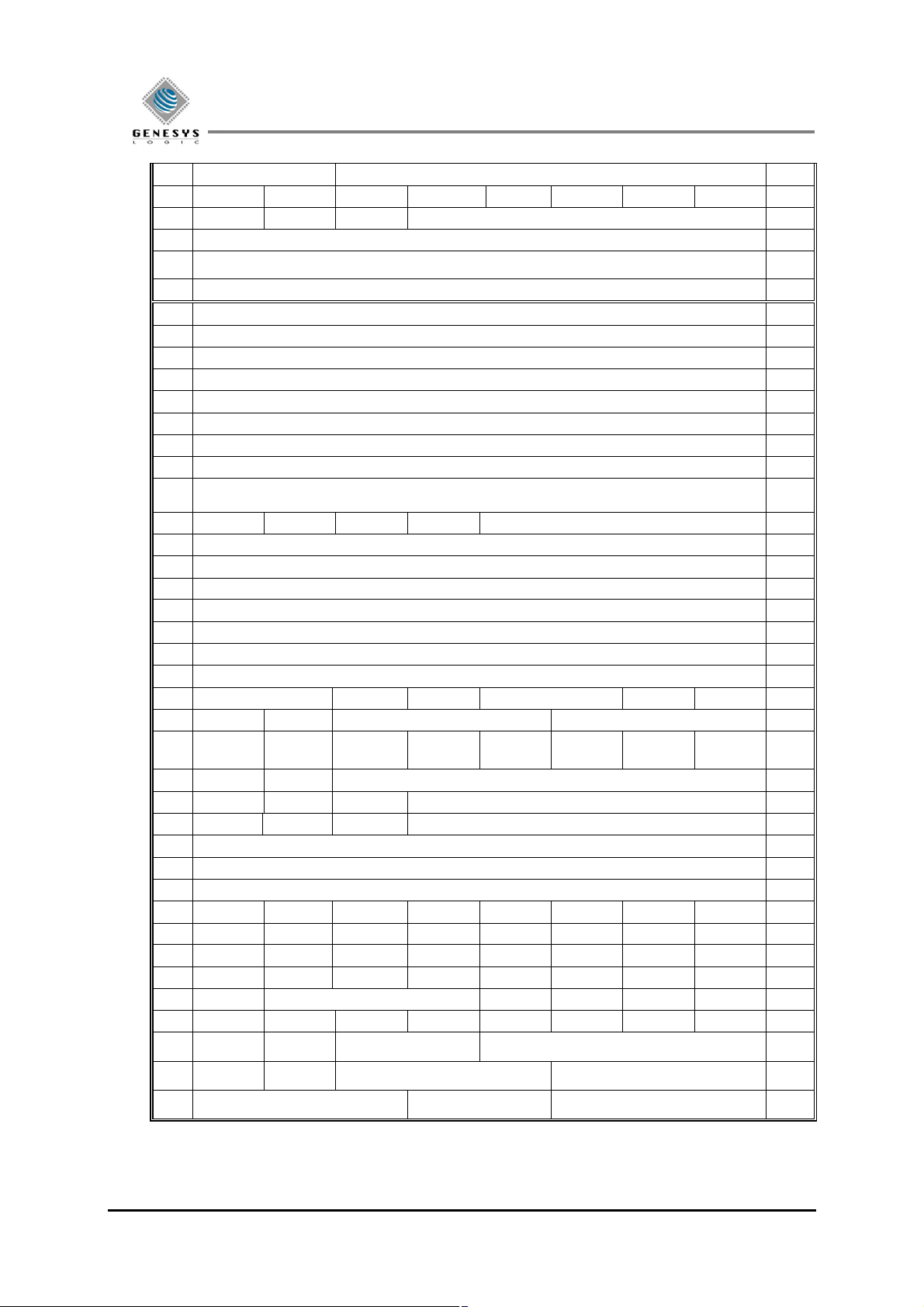

TABLE 3.1 – 128 PIN LIST...............................................................................................11

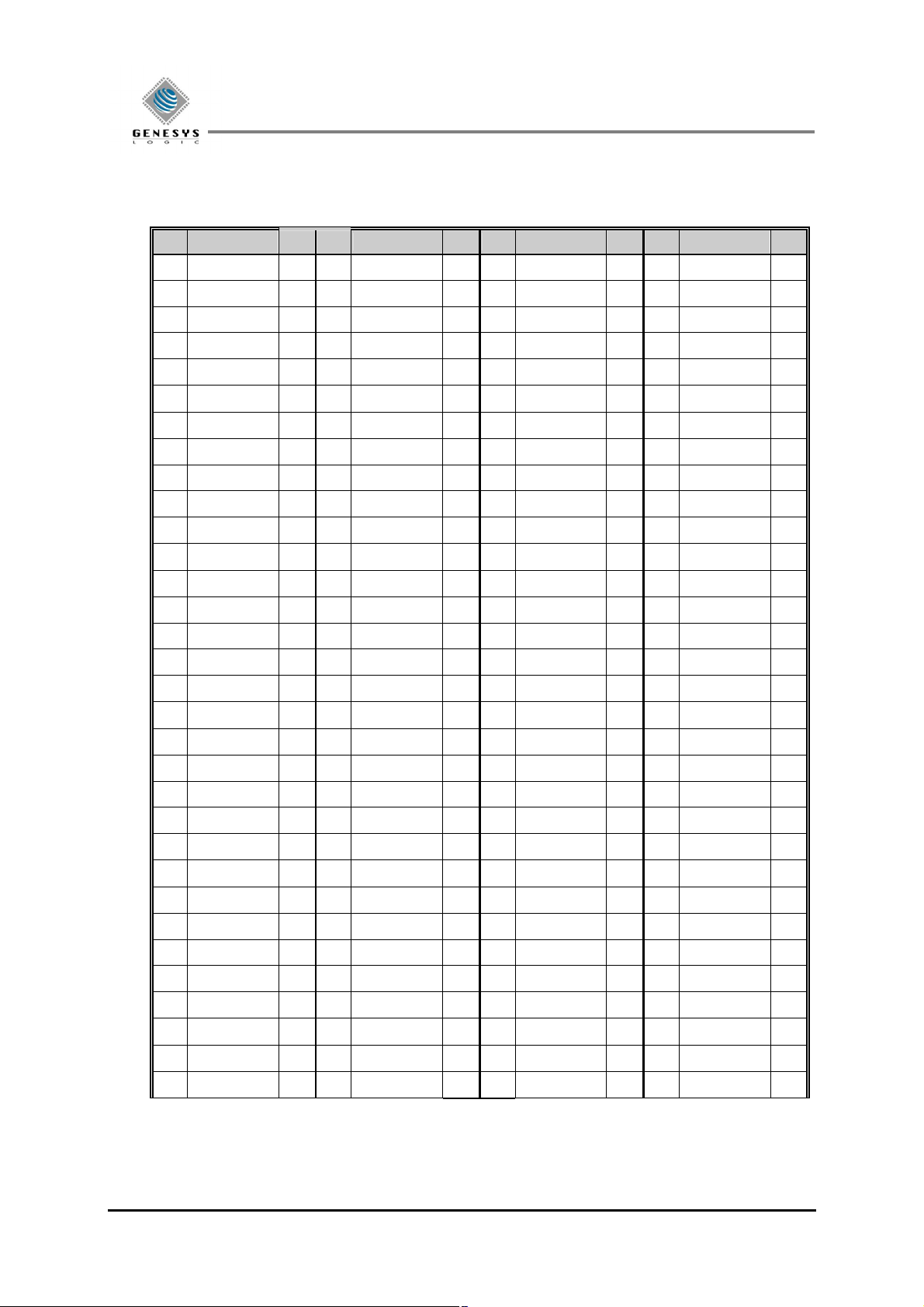

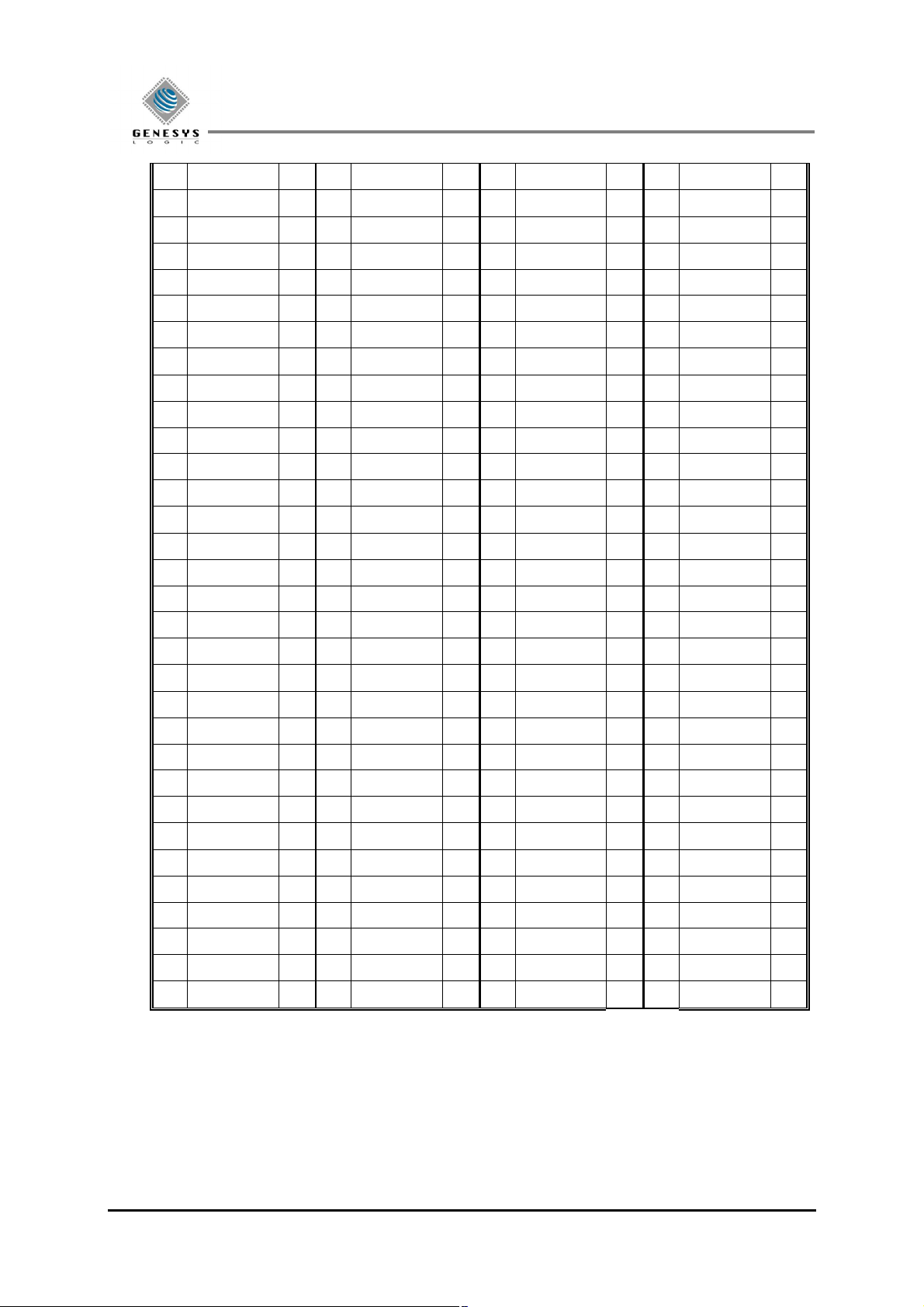

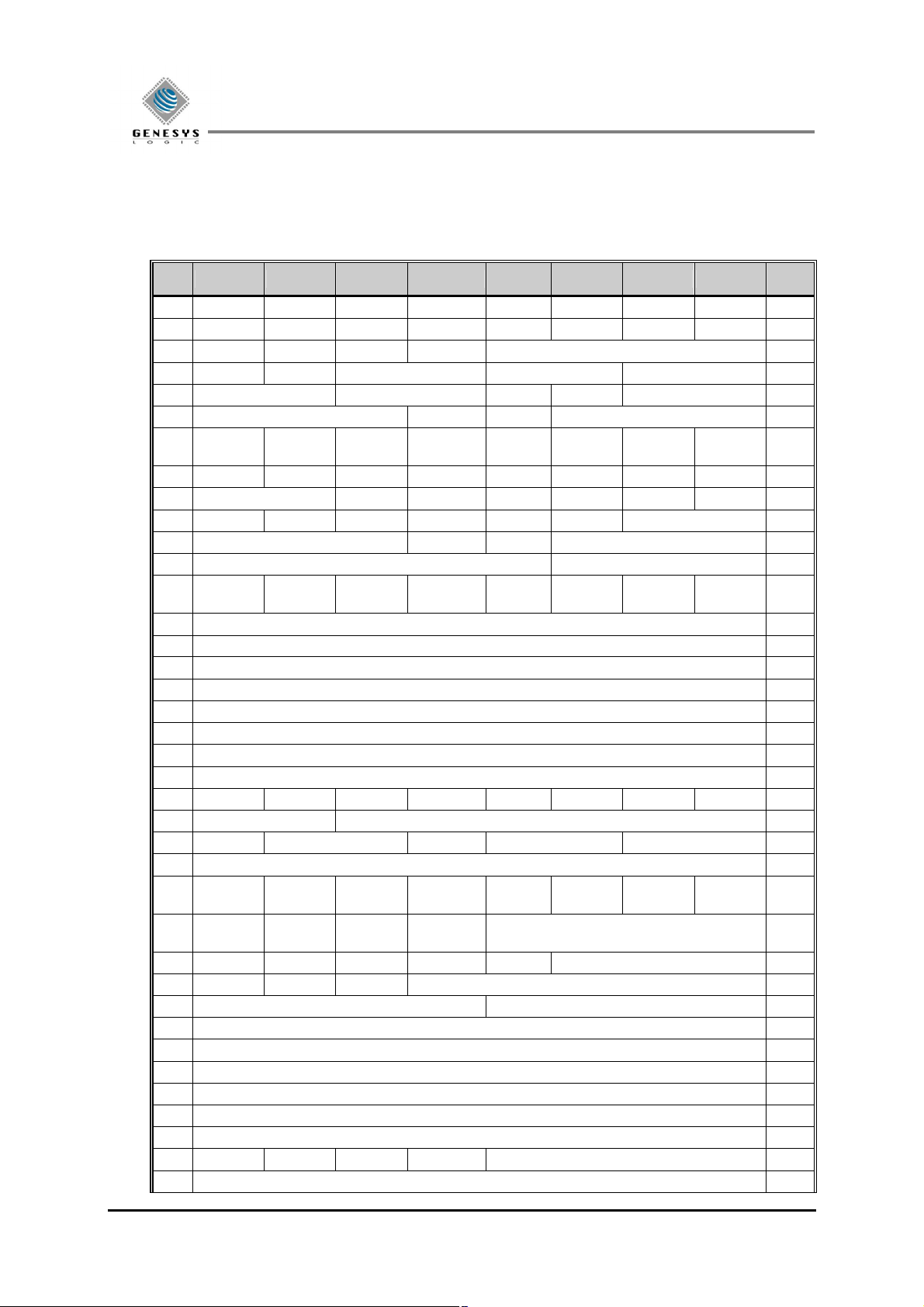

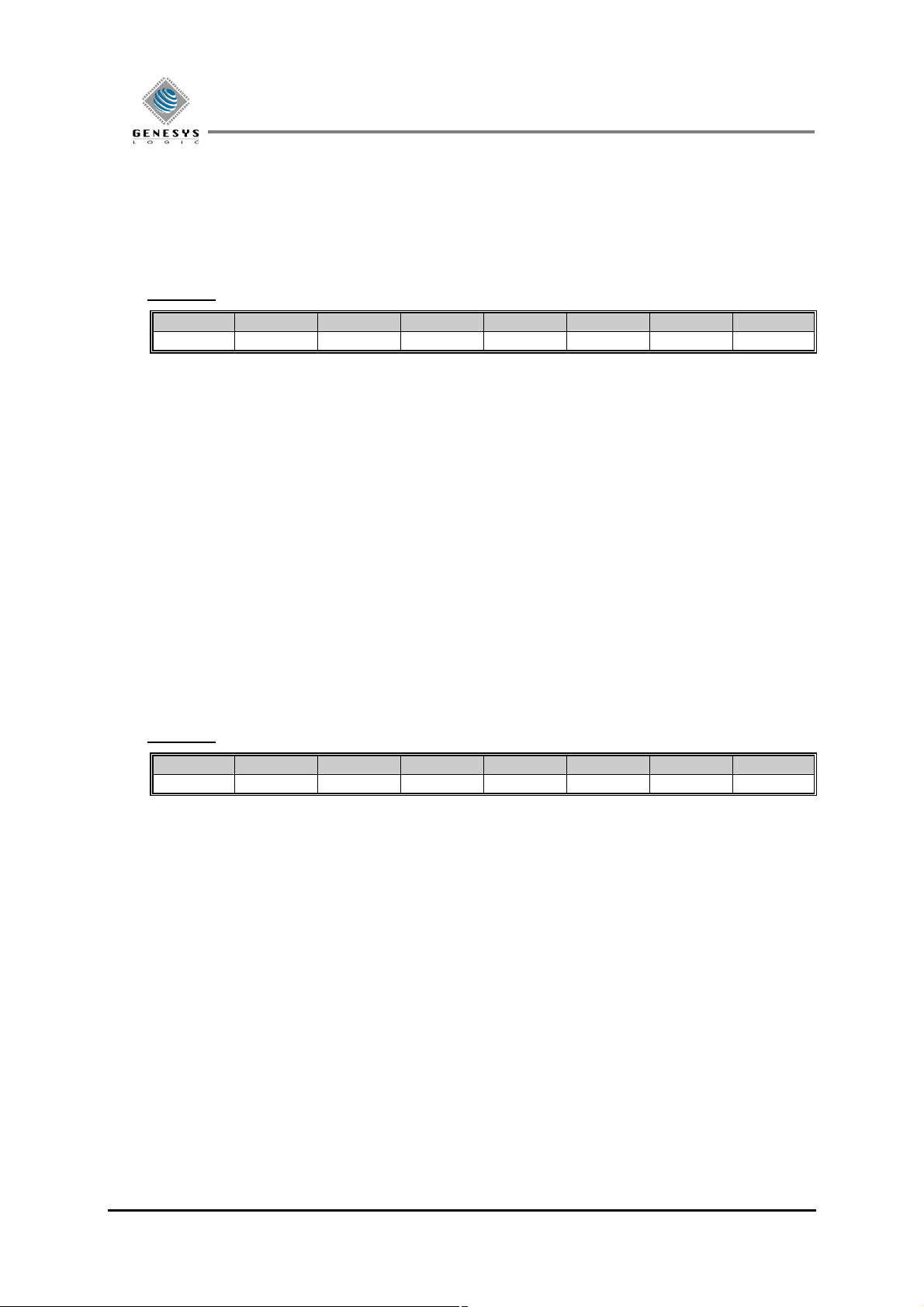

TABLE 3.2 – 208 PIN LIST...............................................................................................12

TABLE 3.3 - PIN DESCRIPTIONS......................................................................................14

TABLE 4.1 - BASE ADDRESS FOR REGISTERS..................................................................17

TABLE 4.2 - SHADING MAPPING (CHUNKY FOR SINGLE BANK)......................................64

TABLE 4.3 - SHADING MAPPING (CHUNKY FOR DOUBLE BANK)....................................64

TABLE 4.4 - IMAGE BUFFER MAPPING ...........................................................................65

TABLE 7.1 - ABSOLUTE MAXIMUM RATINGS (VOLTAGE REFERENCED TO GND)..........81

TABLE 7.2 - DC CHARACTERISTICS (DIGITAL PINS): 3.3 V LOGIC CORE OR PADS........81

TABLE 7.3 - DC CHARACTERISTICS (DIGITAL PINS): 5.0 V PADS ..................................82

TABLE 7.4 - DC CHARACTERISTICS (D+/D-)..................................................................82

©2000-2006 Genesys Logic Inc. - All rights reserved. Page 5

GL843 High Speed USB2.0 With ADF 2-in-1 Scanner Controller For 3x

CHAPTER 1 GERERAL DESCRIPTION

Genesys Logic's single-chip GL843 (GeneScanTM series) is a high speed, high performance, low cost and rich

scalability controller for scanner. It successfully integrates scanner function ASIC and USB 2.0 interface

controller into one single-chip. With its high performance design architecture, GL843 is not only ready for

supporting CIS or CCD image sensors (600, 1200, 2400, 3200, 3600, 4800dpi resolution) that are used in

sheetfed, flatbed or transparency scanners, but is able to co-work with unipolar or bipolar stepping motors.

Advanced features of GL843 include five motor acceleration/ deceleration curve tables for high speed motor

moving.

©2000-2006 Genesys Logic Inc. - All rights reserved. Page 6

GL843 High Speed USB2.0 With ADF 2-in-1 Scanner Controller For 3x

CHAPTER 2 FEATURES

l Highly integrated scanner controller chip (2-in-1; Scanner Controller and USB 2.0 Interface)

l USB 2.0 High Speed (480Mbit) compliant

l Designed for sheetfed, flatbed and transparency scanners

l Supports key-matrix with latch function

l Embedded RISC CPU for scanning, run-in and diagnostic tests

l Supports external 24Kbytes flash ROM or internal 24Kbyte mask ROM

l Firmware download to external flash ROM

l 12MHz low frequency clock input for better EMI

l Flexible 3.3V/5V operating voltage for I/O pads

l Adjustable working clock of scanner controller for different usage (12M, 24M, 30M, 40M, 48M, 60MHz)

l Supports linear or stagger CCD, such as NEC, Toshiba or Sony CCD

l Available sensor types: 600, 1200, 2400, 3200, 3600 and 4800dpi color CIS or CCD

l Multi-TG control for CCD (separately controls the R/G/B exposure time)

l Shutter-control for CCD (separately controls the R/G/B exposure time)

l Supports two scanning types: pixel-by-pixel (pixel rate), line-by-line (line rate)

l Support 48-bits color, 16-bits gray and 1-bit line-art

l “True gray” with R, G and B weightings

l 16 bits white/dark shading and 16-to-8 bits Gamma correction

l 0.3us per pixel for color scanning under 40MHz working clock

l 0.2us per pixel for color scanning under 60MHz working clock

l Supports LCM/LCD interface to display messages

l Supports RS232 interface for special applications

l Supports EEPROM (93C46) interface for special applications

l Supports ADF (Auto-Document-Feeder) function with document, ADF and cover sensors

l Lossless data compression

l Lines packing for stagger CCD or R/G/B line differences

l Fine CDS sampling adjustment to avoid the digital noise influence (8.33ns adjustment)

l Digital average and hardware deletion for various resolutions

l Hardware deletion for various resolutions (from 4800~1dpi with 1dpi decrement)

l Supports 1M*16, 4M*16, 8M*16, 16M*16 and 32M*16 SDRAM

l Supports 5 acceleration/deceleration motor tables for high speed motor moving and wall hitting protection

l Supports controllable bipolar motor in full, half, quarter and eighth steps moving

l Supports controllable unipolar motor in full and half steps moving

l Supports V-reference automatic control for motor driver Ics

l Build-in PWM control phase for unipolar motors

©2000-2006 Genesys Logic Inc. - All rights reserved. Page 7

GL843 High Speed USB2.0 With ADF 2-in-1 Scanner Controller For 3x

l Programmable dummy lines to resolve start/stop (discontinuous) problem

l Watchdog protection for lamp, motor and ASIC

l Lamp time-out (sleeping) control

l Supports 21 GPIO pins and 6 GPO pins for 128-pin package

l Supports 27 GPIO pins and 6 GPO pins for 208-pin package

l Supports 2 PWM outputs for flatbed/transparency lamp control with programmable duties and frequencies

l Supports LED blinking

l Supports back-scanning

l Supports multi-film scanning

©2000-2006 Genesys Logic Inc. - All rights reserved. Page 8

GL843 High Speed USB2.0 With ADF 2-in-1 Scanner Controller For 3x

CHAPTER 3 PIN ASSIGNMENT

3.1 Pinouts

GPIO2

GPIO1

MT_PH7

MT_PH6

MT_PH5

MT_PH4

MT_PH3

GndCore3

VccCore3

MT_PH2

MT_PH1

MT_PH0

OP0

OP1

OP2

OP3

OP4

OP5

OP6

OP7

GndIO4

VccIO4

SDO

SDI

GPIO3

GPIO4

GPIO5

GPIO6

GPIO7

VccIO5

GndIO5

SCLK

VSMP

MCLK

CCD_CK1X

SEN

BSMP

CCD_TGX

GPIO8

GPIO10

GPIO11

GPIO12

GPIO13

GPIO14

GPIO15

GPIO16

GPIO17

GPIO18

VccCore4

GndCore4

GPIO19

GPIO20

EXTRST_

GND

DVCC0

DGND0

RPU

AVDD

DPF

DPH

DMF

DMH

AGND

RREF

103

104

105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

101

100

102

23456

1

X1

X2

AVCC1

9493929190898887868584838281807978777675747372

999897

95

96

GL843

QFP - 128

910111213141516171819202122232425262728293031

7

8

DBUS9

DBUS8

VccIO1

DBUS7

DBUS6

DBUS5

DBUS4

DBUS3

DBUS2

DBUS1

DVCC1

DGND1

AGND1

DBUS14

DBUS13

DBUS12

DBUS11

DBUS15

DBUS10

GndIO1

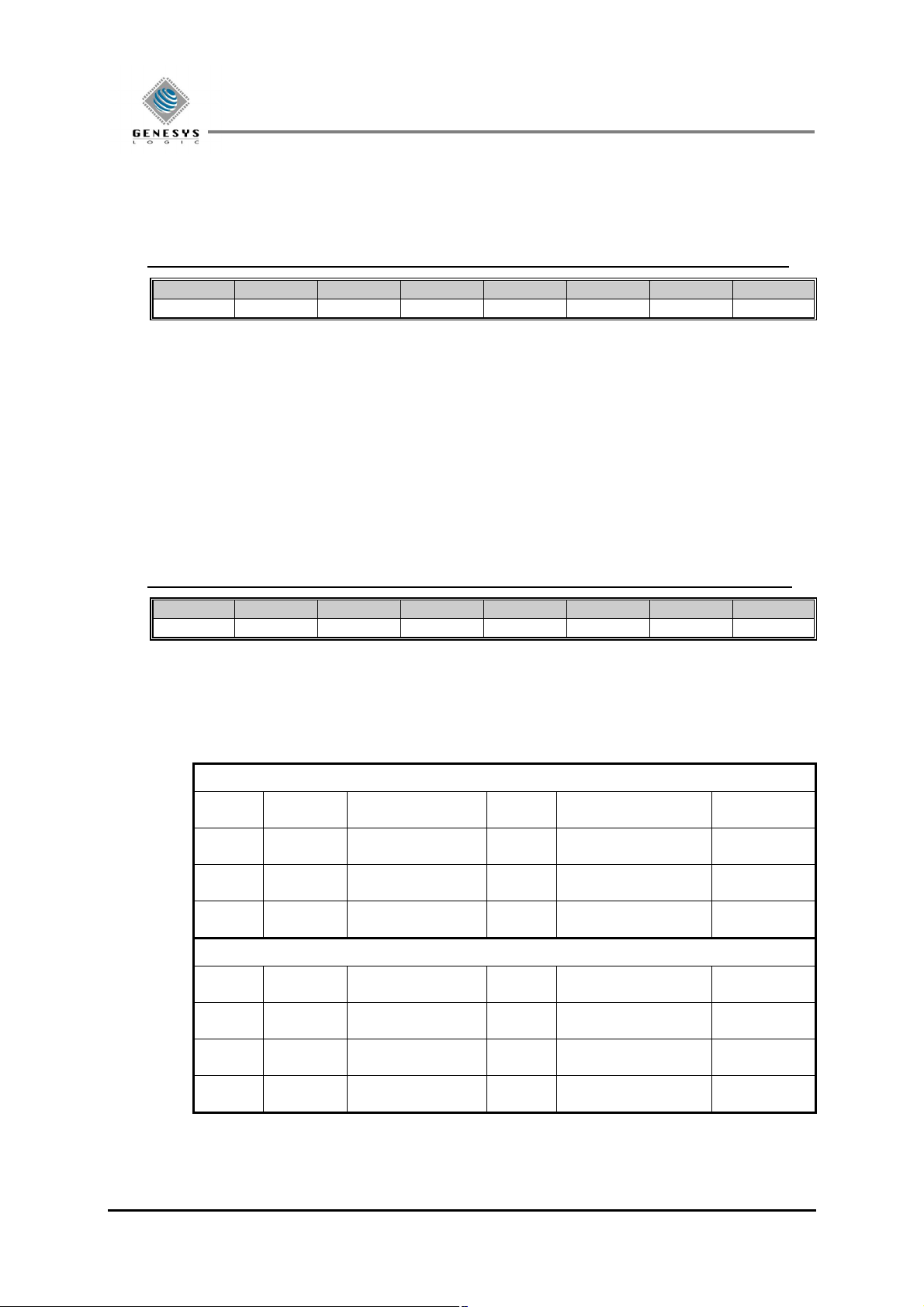

Figure 3.1 – 128 Pin QFP Pinout Diagram

DBUS0

VccCore1

71

686766

35

GndIO2

36

ABUS537ABUS438ABUS3

65

64

CCD_CK3X

63

CCD_CPX

62

CCD_RSX

61

CCD_CK2X

60

CCD_CK4X

59

GndIO3

58

VccIO3

57

CCD_TGG

56

CCD_TGB

55

LAMP_SW

GndCore2

54

53

VccCore2

52

XPA_SW

LED_B

51

HOME

50

ADF_SENR

49

48

RAMCLK

CKE

47

BANK0

46

BANK1

45

WEJ

44

CASJ

43

RASJ

42

ABUS0

41

ABUS1

40

ABUS2

39

70

69

32

33

ABUS9

ABUS8

ABUS7

ABUS12

ABUS11

ABUS10

GndCore1

ABUS634VccIO2

©2000-2006 Genesys Logic Inc. - All rights reserved. Page 9

GL843 High Speed USB2.0 With ADF 2-in-1 Scanner Controller For 3x

NC

NC

NC

NC

NC

156

155

154

153

GPIO5

NC

GPIO6

GPIO7

VccIO5

GndIO5

152

151

150

149

GPIO2

FSHD2

MT_PH7

GPIO1

MT_PH5

GPIO3

GPIO4

FSHD3

144

148

147

146

145

MT_PH6

MT_PH4

142

141

140

139

138

143

137

MT_PH2

FSHD1

MT_PH3

136

135

FSHD0

MT_PH0

MT_PH1

VccCore3

GndCore3

134

133

132

131

130

129

OP4

OP6

OP3

OP2

OP0

OP1

OP5

OP7

GndIO4

128

127

126

125

124

123

122

121

120

SEN

SDO

SCLK

SDI

VccIO4

119

118

117

116

CCD_CK1X

BSMP

VSMP

MCLK

CCD_TGX

115

114

113

112

111

110

NC

NC

NC

NC

106

105

109

108

107

FSHD4

GPIO8

GPIO9

FSHD5

GPIO10

GPIO11

GPIO12

FSHD6

GPIO13

GPIO14

GPIO15

FSHD7

GPIO16

GPIO17

GPIO18

GPIO21

VccCore4

GndCore4

GPIO19

GPIO20

GPIO22

EXTRST_

GND

DVCC0

DGND0

RPU

AVDD

DPF

DPH

DMF

DMH

AGND

RREF

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

157

158

159

160

161

162

163

164

165

166

167

168

169

170

171

172

173

174

175

176

177

178

179

180

181

182

183

184

185

186

187

188

189

190

191

192

193

194

195

196

197

198

199

200

201

202

203

204

205

206

207

208

GL843

QFP - 208

104

103

102

101

100

NC

NC

NC

GPIO23

CCD_CK3X

GPIO24

99

CCD_CPX

98

GPIO25

97

CCD_RSX

96

GPIO26

95

CCD_CK2X

94

FSH_WEB

93

FSH_OEB

92

CCD_CK4X

91

FSHA14

90

89

GndIO3

88

VccIo3

CCD_TGG

87

FSHA13

86

FSHA12

85

CCD_TGB

84

FSHA11

83

FSHA10

82

LAMP_SW

81

FSHA9

80

79

GndCore2

VccCore2

78

FSHA8

77

XPA_SW

76

FSHA7

75

FSHA6

74

LED_B

73

FSHA5

72

FSHA4

71

HOME

70

FSHA3

69

FSHA2

68

ADF_SENR

67

FSHA1

66

FSHA0

65

RAMCLK

64

CKE

63

BANK0

62

BANK1

61

60

WEJ

CASJ

59

RASJ

58

ABUS0

57

ABUS1

56

ABUS2

55

NC

54

53

NC

123456789101112131415161718192021222324252627282930313233343536373839404142434445464748495051

X2

NC

NC

NC

NC

NC

X1

NC

NC

DVCC1

AVCC1

AGND1

DGND1

DBUS14

DBUS13

DBUS15

VccIO1

GndIO1

DBUS9

DBUS8

DBUS7

DBUS6

DBUS5

DBUS3

DBUS1

DBUS0

DBUS12

DBUS10

DBUS11

DBUS2NCDBUS4

VccCore1

ABUS9

ABUS8

ABUS6

ABUS7

VccIO2

ABUS12

ABUS11

ABUS10

GndCore1

GndIO2

NC

ABUS4

ABUS3

ABUS5

52

NC

NC

NC

NC

NC

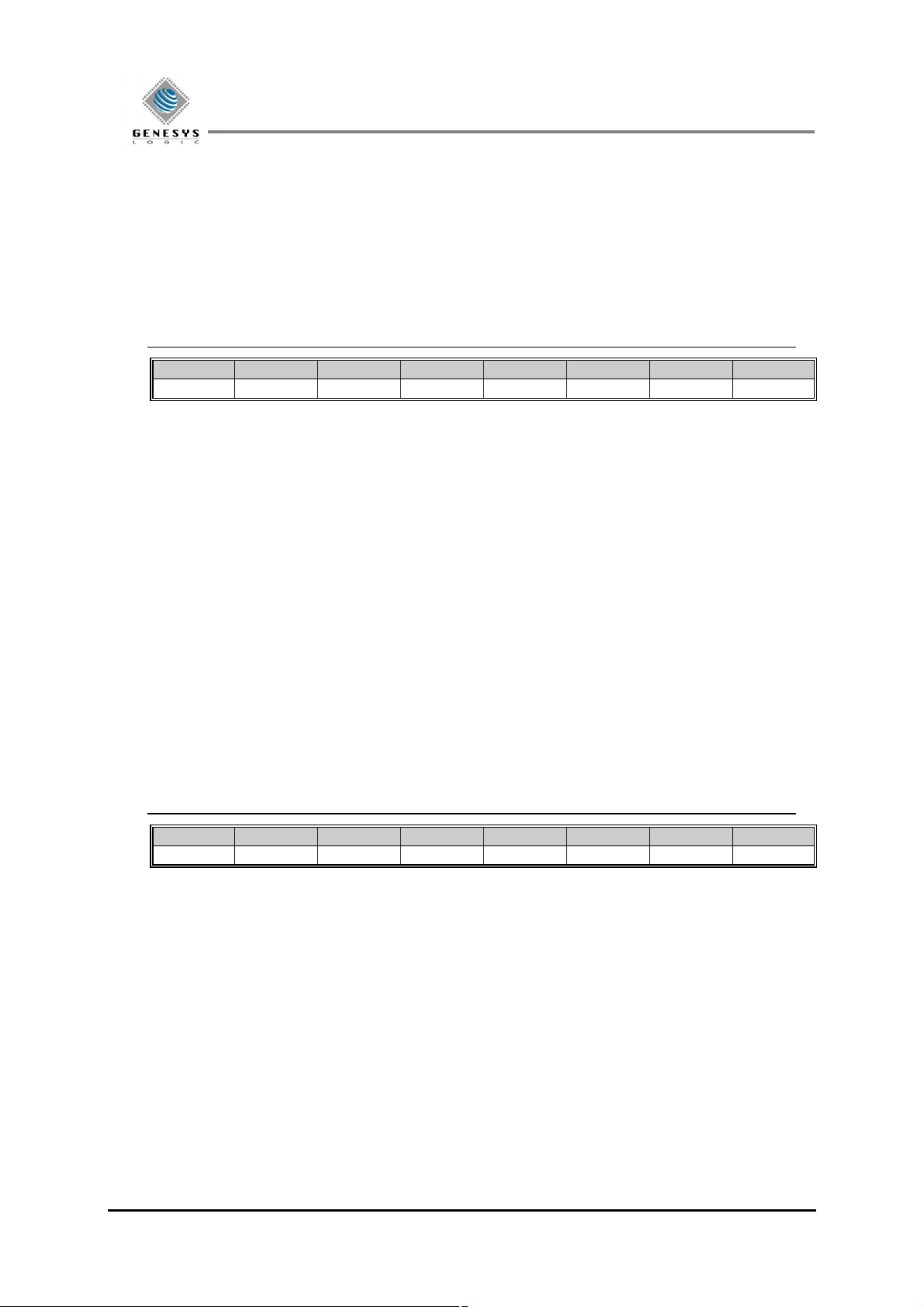

Figure 3.1 – 208 Pin QFP Pinout Diagram

©2000-2006 Genesys Logic Inc. - All rights reserved. Page 10

10

11

12

13

14

15

16

17

18

19

20

21

22

23

87

24

88

25

89

58

27

59

28

60

29

61

30

62

31

63

32

GL843 High Speed USB2.0 With ADF 2-in-1 Scanner Controller For 3x

3.2 Pin List

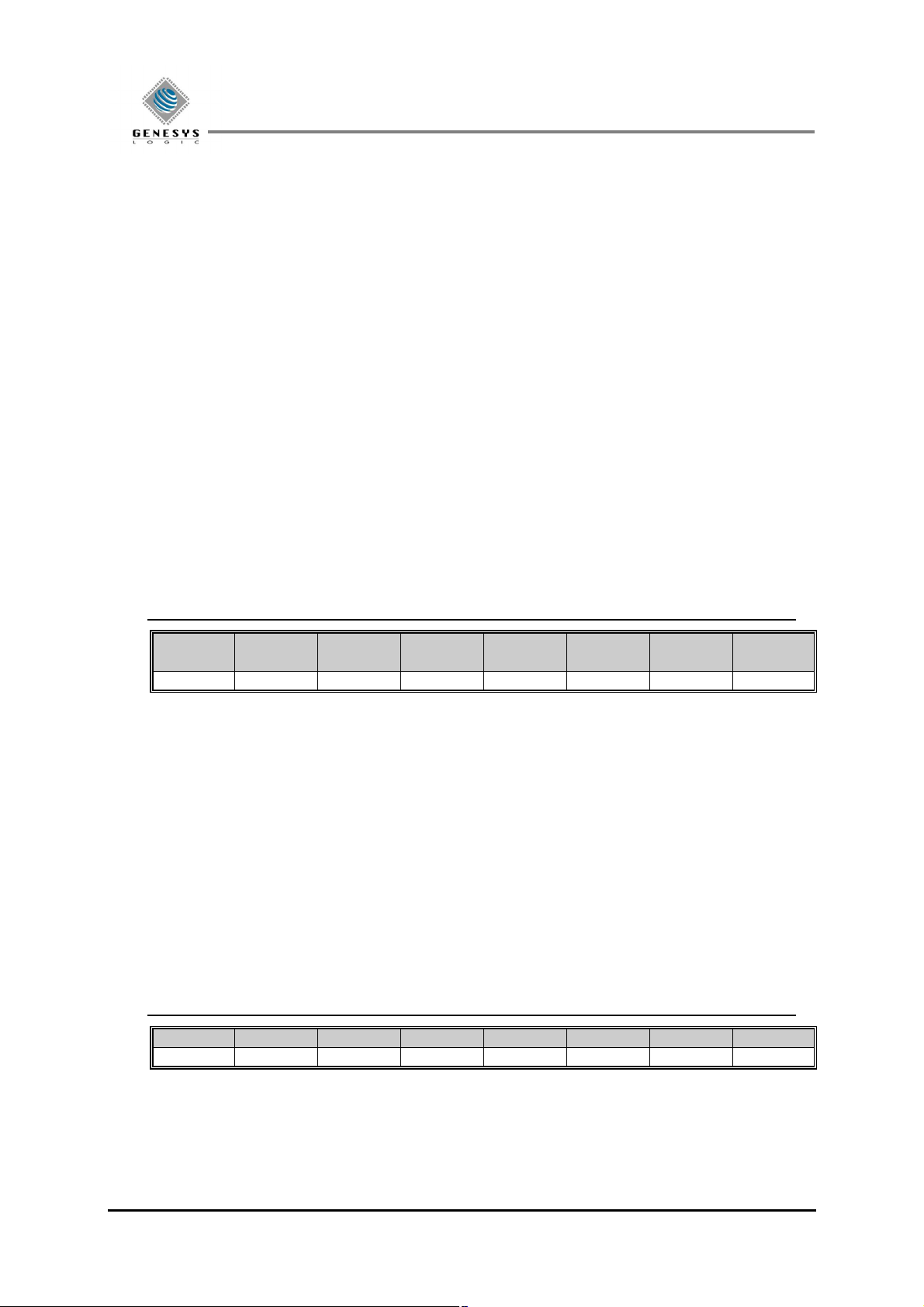

Table 3.1 – 128 Pin List

Pin# Pin Name Type Pin# Pin Name Type Pin# Pin Name Type Pin# Pin Name Type

1 AVCC1 P 33 ABUS6 O 65 CCD_TGX O 97 GPIO4 I/O

2 X2 O 34 VccIO2 P 66 CCD_CK1X O 98 GPIO5 I/O

3 X1 I 35 GndIO2 P 67 MCLK O 99 GPIO6 I/O

4 AGND1 P 36 ABUS5 O 68 VSMP O 100 GPIO7 I/O

5 DVCC1 P 37 ABUS4 O 69 BSMP O 101 VccIO5 P

6 DGND1 P 38 ABUS3 O 70 SEN O 102 GndIO5 P

7 DBUS15 I/O 39 ABUS2 O 71 SCLK O 103 GPIO8 I/O

8 DBUS14 I/O 40 ABUS1 O 72 SDI O 104 GPIO10 I/O

9 DBUS13 I/O 41 ABUS0 O 73 SDO I 105 GPIO11 I/O

DBUS12 I/O 42 RASJ O 74 VccIO4 P 106 GPIO12 I/O

DBUS11 I/O 43 CASJ O 75 GndIO4 P 107 GPIO13 I/O

DBUS10 I/O 44 WEJ O 76 OP7 I 108 GPIO14 I/O

DBUS9 I/O 45 BANK1 O 77 OP6 I 109 GPIO15 I/O

DBUS8 I/O 46 BANK0 O 78 OP5 I 110 GPIO16 I/O

VccIO1 P 47 CKE O 79 OP4 I 111 GPIO17 I/O

GndIO1 P 48 RAMCLK O 80 OP3 I 112 GPIO18 I/O

DBUS7 I/O 49 ADF_SENR I/O 81 OP2 I 113 VccCore4 P

DBUS6 I/O 50 HOME I 82 OP1 I 114 GndCore4 P

DBUS5 I/O 51 LED_B O 83 OP0 I 115 GPIO19 I/O

DBUS4 I/O 52 XPA_SW O 84 MT_PH0 O 116 GPIO20 I/O

DBUS3 I/O 53 VccCore2 P 85 MT_PH1 O 117 EXTRST_ O

DBUS2 I/O 54 GndCore2 P 86 MT_PH2 O 118

DBUS1 I/O 55

DBUS0 I/O 56

VccCore1 P 57

26 GndCore1 P

ABUS12 O

ABUS11 O

LAMP_SW O

CCD_TGB O

CCD_TGG O

VccIO3 P 90 MT_PH4 O 122 AVDD P

GndIO3 P 91 MT_PH5 O 123 DPF I/O

CCD_CK4X O 92 MT_PH6 O 124 DPH I/O

VccCore3 P 119 DVCC0 P

GndCore3 P 120 DGND0 P

MT_PH3 O 121 RPU -

GND

P

ABUS10 O

ABUS9 O

ABUS8 O

ABUS7 O 64 CCD_CK3X O 96 GPIO3 I/O 128 RREF I/O

CCD_CK2X O 93 MT_PH7 O 125 DMF I/O

CCD_RSX O 94 GPIO1 I/O 126 DMH I/O

CCD_CPX O 95 GPIO2 I/O 127 AGND P

©2000-2006 Genesys Logic Inc. - All rights reserved. Page 11

15

16

17

18

19

20

21

22

24

25

58

59

60

61

62

63

GL843 High Speed USB2.0 With ADF 2-in-1 Scanner Controller For 3x

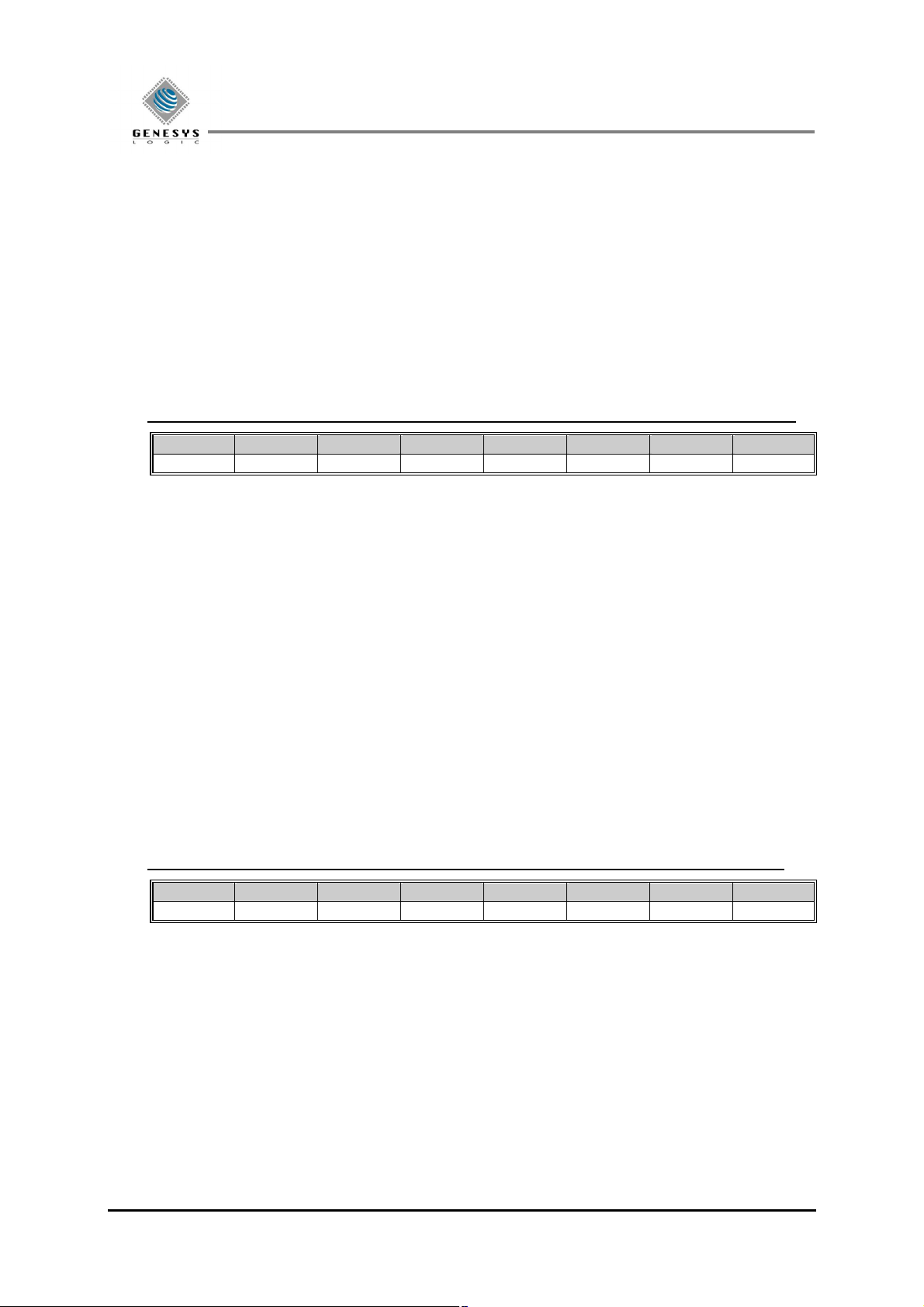

Table 3.2 – 208 Pin List

Pin# Pin Name Type Pin# Pin Name Type Pin# Pin Name Type Pin# Pin Name Type

1 33 GndCore1 P 65 FSHA0 O 97 GPIO25

2 34 ABUS12

3 NC 35 ABUS11

4 NC 36 ABUS10

5 NC 37 ABUS9

6 NC 38 ABUS8

7 NC 39 ABUS7

8 AVCC1 P 40 ABUS6

9 X2 O 41 VccIO2 P 73 LED_B O 105 NC

10 X1 I 42 GndIO2 P 74 FSHA6 O 106 NC

11 AGND1 P 43 ABUS5

12 DVCC1 P 44 ABUS4

13 DGND1 P 45 ABUS3

14 DBUS15 I/O 46 NC 78 VccCore2 P 110 CCD_TGX O

DBUS14 I/O 47 NC 79 GndCore2 P 111 CCD_CK1X O

DBUS13 I/O 48 NC 80 FSHA9 O 112 MCLK O

DBUS12 I/O 49 NC 81 LAMP_SW O 113 VSMP O

DBUS11 I/O 50 NC 82 FSHA10 O 114 BSMP O

O

66 FSHA1 O 98 CCD_CPX

O

67 ADF_SENR I/O 99 GPIO24

O

68 FSHA2 O 100 CCD_CK3X

O

69 FSHA3 O 101 GPIO23

O

70 HOME I 102 NC

O

71 FSHA4 O 103 NC

O

72 FSHA5 O 104 NC

O

75 FSHA7 O 107 NC

O

76 XPA_SW O 108 NC

O

77 FSHA8 O 109 NC

I/O

I/O

I/O

O

O

DBUS10 I/O 51 NC 83 FSHA11 O 115 SEN O

DBUS9 I/O 52 NC 84 CCD_TGB O 116 SCLK O

DBUS8 I/O 53 NC 85 FSHA12 O 117 SDI O

VccIO1 P 54 NC 86 FSHA13 O 118 SDO I

23 GndIO1 P 55 ABUS2 O 87 CCD_TGG O 119 VccIO4 P

DBUS7 I/O 56 ABUS1 O 88 VccIO3 P 120 GndIO4 P

DBU6 I/O 57 ABUS0 O 89 GndIO3 P 121 OP7 I

26 DBUS5 I/O

27 DBUS4 I/O

28 DBUS3 I/O

29 DBUS2 I/O

30 DBUS1 I/O

31 DBUS0 I/O

32 VccCore1 P 64 RAMCLK O 96 CCD_RSX O 128 OP0 I

RASJ O 90 FSHA14 O 122 OP6 I

CASJ O 91 CCD_CK4X O 123 OP5 I

WEJ O 92 FSH_OEB O 124 OP4 I

BANK1 O 93 FSH_WEB O 125 OP3 I

BANK0 O 94 CCD_CK2X O 126 OP2 I

CKE O 95 GPIO26 I/O 127 OP1 I

©2000-2006 Genesys Logic Inc. - All rights reserved. Page 12

GL843 High Speed USB2.0 With ADF 2-in-1 Scanner Controller For 3x

129 FSHD0 I/O 161 NC 193 AGND P

130 MT_PH0 O 162 FSHD4 I/O 194 RREF I/O

131 MT_PH1 O 163 GPIO8 I/O 195 NC

132 MT_PH2 O 164 GPIO9 I/O 196 NC

133 VccCore3 P 165 FSHD5 I/O 197 NC

134 GndCore3 P 166 GPIO10 I/O 198 NC

135 MT_PH3 O 167 GPIO11 I/O 199 NC

136 FSHD1 I/O 168 GPIO12 I/O 200 NC

137 MT_PH4 O 169 FSHD6 I/O 201 NC

138 MT_PH5 I/O 170 GPIO13 I/O 202 NC

139 MT_PH6 O 171 GPIO14 I/O 203 NC

140 MT_PH7 O 172 GPIO15 I/O 204 NC

141 FSHD2 I/O 173 FSHD7 I/O 205 NC

142 GPIO1 I/O 174 GPIO16 I/O 206 NC

143 GPIO2 I/O 175 GPIO17 I/O 207 NC

144 GPIO3 I/O 176 GPIO18 I/O 208 NC

145 GPIO4 I/O 177 GPIO21 I/O

146 FSHD3 I/O 178 VccCore4 P

147 GPIO5 I/O 179 GndCore4 P

148 GPIO6 I/O 180 GPIO19 I/O

149 GPIO7 I/O 181 GPIO20 I/O

150 VccIO5 P 182 GPIO22 I/O

151 GndIO5 P 183 EXTRST_ O

152 NC 184 GND P

153 NC 185 DVCC0 P

154 NC

155 NC

156 NC

157 NC

158 NC

159 NC

160 NC 192 DMH I/O

186

DGND0 P

187

RPU ?

188

AVDD P

189

DPF I/O

190

DPH I/O

191

DMF I/O

©2000-2006 Genesys Logic Inc. - All rights reserved. Page 13

GL843 High Speed USB2.0 With ADF 2-in-1 Scanner Controller For 3x

3.3 Pin Descriptions

Table 3.3 - Pin Descriptions

Pin Name Type

GPIO1~8,10~20

MT_PH0~5

MT_PH6~7

Description

General Purpose Input/Output, EEPROM serial data clock or

I/O

LCM data bit0

Bi-polar (3967): MT_PH5=RESETJ

MT_PH4=ENABLEJ

MT_PH3=DIR

MT_PH2=STEP

MT_PH1=MS2

MT_PH0=MS1

Bi-polar (3955): MT_PH7=PHASE_A

MT_PH6=PHASE_B

MT_PH5=D2A

MT_PH4=D1A

MT_PH3=D0A

MT_PH2=D2B

MT_PH1=D1B

O

Bi-polar (1939): MT_PH3=IN1

MT_PH0=ENA2

Bi-polar (2916 or 6219): MT_PH5=PHASE1

MT_PH3=I11

MT_PH2=I01

MT_PH1=I12

MT_PH0=I02

Uni-polar(2003): MT_PH3=PHASE A

MT_PH2=PHASE B

MT_PH1=PHASE /A

MT_PH0=PHASE /B

O Motor phase 6~7

MT_PH0=D0B

MT_PH2=IN2

MT_PH1=ENA1

MT_PH4=PHASE2

ADF_SENR

HOME I Document sensor for ADF

ADF sensor for ADF

I/O

Pin Name Type

CCD_CK1X O CCD Shift register clock1 or CIS clock output

CCD_CPX

CCD_TGX

CCD_CK2X

CCD_RSX

CCD_CK3X

CCD_CK4X

©2000-2006 Genesys Logic Inc. - All rights reserved. Page 14

O

CCD Clamp gate clock or CIS clock output

O CCD Transfer gate clock for R channel or CIS Line start pulse

O CCD Shift register clock2 or CIS clock output

O CCD Reset gate clock or CIS clock output

O CCD Shift register clock3

O CCD Shift register clock4

Description

GL843 High Speed USB2.0 With ADF 2-in-1 Scanner Controller For 3x

CCD_TGG

CCD_TGB

LAMP_SW

XPA_SW

LED_B

O

CCD Transfer gate clock for G channel

O

CCD Transfer gate clock for B channel

O Flatbed lamp power control or CIS Red LED array control

O Transparency lamp power control or CIS Green LED array control

O CIS Blue LED array control

Pin Name Type

OP7~0

SEN O Serial interface load pulse

SCLK O Serial interface clock output

SDI O Serial data output

SDO I Serial data input

BSMP

VSMP/CDSCLK2

MCLK/ADCCLK

I AFE digital data input

O Video sample synchronization pulse

O Video sample synchronization pulse

O Master clock.

Description

Pin Name Type

DBUS15~0

ABUS12~0 O DRAM address bus

RASJ SDRAM row address strobe

CASJ

WEJ

BANK0~1

CKE

RAMCLK

I/O DRAM data bus

SDRAM column address strobe

O

SDRAM write enable

O

SDRAM bank select

O

SDRAM clock enable

O

SDRAM clock

O

Pin Name Type

X1

X2

I

Clock input for crystal (12MHz)

I/O

Clock output for crystal

Description

Description

EXTRST_

I

Hardware reset input

©2000-2006 Genesys Logic Inc. - All rights reserved. Page 15

GL843 High Speed USB2.0 With ADF 2-in-1 Scanner Controller For 3x

Pin Name Type

RPU - 3.3V Pull up control for DPF

DPF

DPH

DMF

DMH

RREF - 510 Ω reference resistor input

I/O Positive USB differential data (Full Speed)

I/O Positive USB differential data (High Speed)

I/O Negative USB Differential Data (Full Speed)

I/O Negative USB Differential Data (High Speed)

Description

Pin Name Type

AVDD, AVCC1

AGND, AGND1 P Analog ground input for USB2.0 transceiver

DVCC0, DVCC1

DGND0, DGND1

VccCore1~4

GndCore1~4,

GndIO1~5

VccIO1~2 P For Pin7~Pin48 3.3V

P Analog power input for USB2.0 transceiver 3.3V

P Digital power input for USB2.0 controller 3.3V

P Digital ground input for USB2.0 controller.

Digital power input for scanner controller logic core 3.3V

P

P Digital ground input for scanner controller.

Description

VccIO3 P For Pin49~Pin66 3.3V

VccIO4 P For Pin67~Pin83 3.3V

VccIO5 P For Pin84~Pin117 3.3V

GND P Ground

Notation:

Type O Output

I Input

B Bi-directional

B/I Bi-directional, default input

B/O Bi-directional, default output

P Power / Ground

A Analog

SO Automatic output low when suspend

pu Internal pull up

pd Internal pull down

odpu Open drain with internal pull up

odpu Open drain with internal pull up

©2000-2006 Genesys Logic Inc. - All rights reserved. Page 16

(Hex)

DMASEL

CLRLNCNT

GL843 High Speed USB2.0 With ADF 2-in-1 Scanner Controller For 3x

CHAPTER 4 REGISTERS

4.1 Registers Base Address

Table 4.1 - Base Address for Registers

Offset

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

Default

01h CISSET DOGENB DVDSET

02h

03h

NOTHOME

LAMPDOG

ACDCDIS

AVEENB XPASEL

04h LINEART BITSET

05h

06h

07h

08h

DPIHW[1:0] MTLLAMP[1:0]

SCANMOD[2:0] PWRBIT GAIN4

LAMPSIM CCDCTL DRAMCTL MOVCTL RAMSEL FASTDMA

X DECFLAG GMMFFR GMMFFG

09h MCNTSET[1:0]

AGOHOME

AFEMOD[1:0] FILTER[1:0] FESET[1:0] 8’h00

EVEN1ST

STAGGER

MTRPWR

LAMPPWR

BLINE1ST

0Ah LCDSEL LCMSEL ADFSEL LPWMEN

0Bh

0Ch

JAMPCMD DOCCMD CCDCMD FULLSTP SEND CLRMCNT CLRDOCJM

0Dh

0Eh

CLKSET[2:0] RFHDIS

SWSH[4:0] CCDLMT[2:0 ] 8’h00

SCANRESET -

0Fh

10h

EXPR[15:8] 8’h00

11h

12h

EXPG[15:0] 8’h00

13h

14h

EXPB[15:8] 8’h00

15h

COMPENB TRUEGRAY

FASTFED

MTRREV

SHDAREA

HOMENEG

SCAN -

LONGCURV

-

LAMPTIM[3:0] 8’h94

GMMENB

ENB20M MTLBASE[1:0] 8’h00

OPTEST[2:0] 8’h00

GMMFFB

BACKSCAN

EPROMSEL

ENBDRAM

DMARDWR

GMMZR GMMZG GMMZB 8’h00

ENHANCE SHORTTG

RS232SEL

BAUDRAT[1:0] 8’h00

NWAIT 8’h00

DRAMSEL[2:0] 8’h00

8’h00

-

MOVE -

EXPR[7:0] 8’h00

EXPG[7:0] 8’h00

EXPB[7:0] 8’h00

16h CTRLHI TOSHIBA TGINV CK1INV CK2INV CTRLINV CKDIS CTRLDIS 8’h32

17h

18h CNSET

19h

TGMODE[1:0] TGW[5:0] 8’h14

DCKSEL[1:0]

CKTOGGLE

CKDELAY[1:0] CKSEL[1:0] 8’h00

EXPDMY[7:0] 8’h00

1Ah

TGLSW2 TGLSW1

1Bh

GRAYSET CHANSEL BGRENB

1Ch

CK4MTGL CK3MTGL CK1MTGL

1Dh CK4LOW CK3LOW CK1LOW

1Eh

1Fh

20h

21h

22h

23h

24h

25h

X X X X LINCNT[19:16] 8’h00

26h

MANUAL3 MANUAL1

ICGENB

CKAREA MTLWD

CK4INV CK3INV LINECLP

ICGDLY[3:0] 8’h00

TGTIME[2:0] 8’h00

X 8’h00

TGSHLD[4:0] 8’h04

WDTIME[3:0] LINESEL[3:0] 8’h20

SCANFED[7:0] 8’h00

BUFSEL[7:0] 8’h00

STEPNO[7:0] 8’h00

FWDSTEP[7:0] 8’h00

BWDSTEP[7:0] 8’h00

FASTNO[7:0] 8’h00

LINCNT[15:8] 8’h00

©2000-2006 Genesys Logic Inc. - All rights reserved. Page 17

GL843 High Speed USB2.0 With ADF 2-in-1 Scanner Controller For 3x

27h

28h

29h

2Ah

2Bh

2Ch

2Dh

2Eh

2Fh

30h

31h

32h

33h

34h

35h

36h

37h

38h

39h

3Ah

3Bh

3Ch

3Dh

3Eh

3Fh

40h DOCSNR ADFSNR

41h PWRBIT

42h

43h

44h

45h

46h

47h

48h

49h

4Ah

4Bh

4Ch

4Dh

4Eh

4Fh

50h

51h

52h

53h

54h

55h

©2000-2006 Genesys Logic Inc. - All rights reserved. Page 18

X X X RAMADDR[20:16] 8’h00

X X DPISET[13:8] 8’h00

X X X X X X X

X X X X FEEDL[19:16] 8’h00

COVERSNR

BUFEMPTY

X X X X X X X

X X X X FEDCNT[19:16] 8’h00

X X X X SCANCNT[19:16] 8’h00

X X DOGON ROMBSY

X X FERDA[5:0] 8’h00

X X FEWRA[5:0] 8’h00

X X X RHI[4:0] 8’h00

X X X RLOW[4:0] 8’h00

X X X GHI[4:0] 8’h00

X X X GLOW[4:0] 8’h00

FEEDFSH SCANFSH

LINCNT[7:0] 8’h00

“GMMWRDATA” -

RAMADDR[15:8] 8’h00

RAMADDR[7: 0] 8’h00

DPISET[7:0] 8’h00

BWHI[7:0] 8’h00

BWLOW[7:0] 8’h00

STRPIXEL[15:8] 8’h00

STRPIXEL[7:0] 8’h00

ENDPIXEL[15:8] 8’h00

ENDPIXEL[7:0] 8’h00

DUMMY[7:0] 8’h00

MAXWD[24:17] 8’h00

MAXWD[16:9] 8’h00

MAXWD[8:1] 8’h00

LPERIOD[15:8] 8’h2A

LPERIOD[7:0] 8’h30

FEWRDATA[8]

FEWRDATA[7:0] -

“RAMWRDATA” -

FEEDL[15:8] 8’h00

FEEDL[7:0] 8’h00

CHKVER

VALIDWORD[24:17] 8’h00

VALIDWORD[16:9] 8’h00

VALIDWORD[8:1] 8’h00

“RAMRDDATA” -

FERDDATA[7:0] -

FEDCNT[15:8] 8’h00

FEDCNT[7:0] 8’h00

SCANCNT[15:8] 8’h00

SCANCNT[7:0] 8’h00

“GMMRDDATA” -

DOCJAM HISPDFLG

HOMESNR

LCMBSY TX232BSY

LAMPSTS

MOTMFLG

FEBUSY

RX232BSY RXREADY

DATAENB

MOTORENB

FERDDATA[8]

-

-

-

-

-

GL843 High Speed USB2.0 With ADF 2-in-1 Scanner Controller For 3x

56h

57h

58h

59h

5Ah

5Bh

5Ch

5Dh

5Eh

5Fh

60h

61h

62h

63h

64h

65h

66h

67h

68h

69h

6Ah

6Bh

6Ch GPIO16 GPIO15 GPIO14 GPIO13 GPIO12 GPIO11 GPIO10 GPIO9 8’h00

6Dh GPIO8 GPIO7 GPOI6 GPIO5 GPIO4 GPIO3 GPIO2 GPIO1 8’h00

6Eh GPOE16 GPOE15 GPOE14 GPOE13 GPOE12 GPOE11 GPOE10 GPOE9 8’h00

6Fh GPOE8 GPOE7 GPOE6 GPOE5 GPOE4 GPOE3 GPOE2 GPOE1 8’h00

70h

71h

72h

73h

74h

75h

76h

77h

78h

79h

7Ah

7Bh

7Ch

7Dh CK1NEG CK3NEG CK4NEG RSNEG CPNEG

7Eh

7Fh BSMPDLY[1:0] VSMPDLY[1:0] LEDCNT[3:0] 8’h00

80h

81h

X X X BHI[4:0] 8’h00

X X X BLOW[4:0] 8’h00

VSMP[4:0] VSMPW[2:0] 8’h00

BSMP[4:0] BSMPW[2:0] 8’h00

ADCLKINV

X MTRTBL

X X X Z1MOD[20:16] 8’h00

X X X Z2MOD[20:16] 8’h00

STEPSEL[1:0] MTRPWM[5:0] 8’h7F

FSTPSEL[1:0] FASTPWM[5:0] 8’h7F

MULTFILM

X X X RSH[4:0] 8’h06

X X X RSL[4:0] 8’h08

X X X CPH[4:0] 8’h08

X X X CPL[4:0] 8’h0A

X X X X X X CK1MAP[17:16] 8’h00

X X X X X X CK3MAP[17:16] 8’h00

X X X X X X CK4MAP[17:16] 8’h00

GPOLED25

VRHOME[1:0] VRMOVE[1:0] VRBACK[1:0] VRSCAN[1:0] 8’h00

X X X LOADSET[4:0]

RLCSEL

DECSEL[2:0] STOPTIM[4:0] 8’h00

GPOM13

GPOLED24 GPOLED23 GPOLED22

CDSREF[1:0] RLC[3:0] 8’h00

GMMADDR[13:8] 8’h00

GMMADDR[7:0] 8’h00

HISPD[7:0] 8’h00

FMOVDEC[7:0] 8’h00

Z1MOD[15:8] 8’h00

Z1MOD[7:0] 8’h00

Z2MOD[15:8] 8’h00

Z2MOD[7:0] 8’h00

PHFREQ[7:0] 8’h00

FSHDEC[7:0] 8’h00

FMOVNO[7:0] 8’h00

GPOM12 GPOM11

CK1MAP[15:8] 8’h00

CK1MAP[7:0] 8’h00

CK3MAP[15:8] 8’h00

CK3MAP[7:0] 8’h00

CK4MAP[15:8] 8’h00

CK4MAP[7:0] 8’h00

GPOCK4 GOPCP GPOLEDB

BSMPNEG VSMPNEG

GPOLED21

GPOLED10 GPOLED9 GPOLED8

GPOADF 8’h00

DLYSET 8’h00

8’h00

8’h00

82h

83h

©2000-2006 Genesys Logic Inc. - All rights reserved. Page 19

CONTB[3:0] CONTA[3:0]

IMGSET[7:0] 8’h00

8’h00

GL843 High Speed USB2.0 With ADF 2-in-1 Scanner Controller For 3x

84h

87h

88h

89h

8Ah

8Bh

8Ch

8Dh

8Eh

8Fh

90h

91h

92h

93h

94h

95h

96h

97h

98h

99h

9Ah

9Bh

9Ch

9Dh RAMDLY[1:0] MOTLAG CMODE

9Eh

PACK[1:0] PACKCNT[5:0] 8’h00

X YENB YBIT

X X X RDNUM[4:0] 8’h00

X X X X SCANLEN[19:16] 8’h00

X SEL3INV

ACYCNRLC

RS232WD[7:0] -

RS232RD[7:0] -

ROMADDR[7:0] 8’h00

ROMWD[15:8] -

ROMWD[7:0] -

ROMRD[15:8] -

ROMRD[7:0] -

PREFED[15:8] 8’h00

PREFED[7:0] 8’h00

PSTFED[15:8] 8’h00

PSTFED[7:0] 8’h00

MTRPLS[7:0] 8’h00

SCANLEN[15:8] 8’h00

SCANLEN[7:0] 8’h00

ONDUR[15:8] 8’h00

ONDUR[7:0] 8’h00

OFFDUR[15:8] 8’h00

OFFDUR[7:0] 8’h00

LCMWD[7:0]

TGSTIME[2:0] TGWTIME[2:0] 8’h00

ENOFFSET

STEPTIM[1:0]

LEDADD CK4ADC

MULDMYLN

AUTOCONF

IFRS 8’h00

8’h00

-

LCDCTL LCMCTL EPROMCTL TGCTL MPUCTL

9Fh

A0h

A1h

A2h

A3h

A4h

A5h

A6h GPIO24 GPIO23 GPIO22 GPIO21 GPIO20 GPIO19 GPIO18 GPIO17 8’h00

A7h GPOE24 GPOE23 GPOE22 GPOE21 GPOE20 GPOE19 GPOE18 GPOE17 8’h00

A8h

A9h

ABh GPOM9

ACh

ADh

AEh

AFh

Notation:

R/W Read / Write

R/O Read Only

©2000-2006 Genesys Logic Inc. - All rights reserved. Page 20

X X LNOFSET[5:0] X

X X X STGSET[4:0] X

X X X RFHSET[4:0] 8’h00

TRUER[7:0]

TRUEG[7:0]

TRUEB[7:0] 8’h00

X X GPOE27 GPOE26 GPOE25 GPO27 GPO26 GPO25 8’h00

X X GPO33 GPO32 GPO31 GPO30 GPO29 GPO28 8’h00

MULSTOP[2:0]

VRHOME3 VRHOME2 VRMOME3 VRMOME2 VRBACK3 VRBACK2 VRSCAN3 VRSCAN2

X X ADFTYP[1:0] CCDTYP[3:0]

X X MOTSET[2:0] PROCESS[2:0]

SCANTYP[2:0] FEDTYP[1:0] ADFMOVE[2:0]

NODECEL

MOTMPU

TB3TB1 TB5TB2

NEC8884 DPI9600 X

FIX16CLK

-

-

8’h00

8’h00

GL843 High Speed USB2.0 With ADF 2-in-1 Scanner Controller For 3x

W/O Write Only

R/W1C Readable and Write-1-Clear

R/W/C Read / Write and hardware automatic Clear

4.2 Register Descriptions

Offset 01h

CISSET DOGENB DVDSET

STAGGER

COMPENB

TRUEGRAY

SHDAREA SCAN

R/W R/W R/W R/W R/W R/W R/W R/W

7 CISSET 0 CCD scan type.

1 CIS scan type.

6 DOGENB 0 Disable watchdog function.

1 Enable watchdog function (set time out duration in Reg1E[7:4]).

5 DVDSET 0 Disable shading function.

1 Enable shading function (include whole line shading and area shading).

4 STAGGER 1 Enable double shading.

0 Disable double shading.

3 COMPENB 0 Disable data compression.

1 Enable lossless data compression.

2 TRUEGRAY 0 Disable true gray function.

1 Enable true gray function. The weightings are stored in Reg A3,A4 and A5.

1 SHDAREA 0 Select whole-line shading.

1 Select area-shading (depend on scan area and scan dpi).

0 SCAN 0 Disable scanning process.

1 Enable scanning process.

Offset 02h

NOTHOME ACDCDIS

AGOHOME

MTRPWR FASTFED MTRREV HOMENEG

LONGCURV

R/W R/W R/W R/W R/W R/W R/W R/W

7 NOTHOME 0 In auto-go-home function, carriage will not stop until touching the home sensor.

1 In auto-go-home function, moving steps of carriage depends on steps setting

from software (Reg 3D, 3E and 3F).

6 ACDCDIS 0 Enable carriage backtracking when image buffer is full.

1 Disable carriage backtracking when image buffer is full.

5 AGOHOME 0 Disable auto-go-home function.

1 Enable auto-go-home function. It’s for carriage to go home automatically

after scanning finished.

4 MTRPWR 0 Turn off MOTOR power and phase to idle state.

1 Turn on MOTOR power and phase.

3 FASTFED 0 Move to scanning window by only one acceleration/deceleration tables.

1 Move to scanning window by two acceleration/deceleration tables.

2 MTRREV 0 Set motor to move in forward direction.

1 Set motor to move in reverse direction.

1 HOMENEG 0 Motor will be decelerated when home sensor input (HOME) changes from low

to high (rising edge).

1 Motor will be decelerated when home sensor input (HOME) changes from

high to low (falling edge).

0 LONGCURV 0 The deceleration curve of the fast moving is defined in table 4 or use default

©2000-2006 Genesys Logic Inc. - All rights reserved. Page 21

GL843 High Speed USB2.0 With ADF 2-in-1 Scanner Controller For 3x

curve.

1 The deceleration curve of the fast moving is defined in table 5 to protect

wall-hitting.

Offset 03h ……………………………………………..…………..……………. Default value = 8’h94

LAMPDOG AVEENB XPASEL LAMPPWR

R/W R/W R/W R/W R/W R/W R/W R/W

7 LAMPDOG 0 To disable sleep mode of lamp.

1 To start sleep mode of lamp (default on).

6 AVEENB 0 Select dpi deletion function

1 Select dpi average function.

5 XPASEL 0 Select flatbed lamp on.

1 Select transparency lamp on.

4 LAMPPWR 0 Turn off LAMP power.

1 Turn on LAMP power.

3-0 LAMPTIM[3:0] Counter of the sleep mode of lamp (default: 4).

The unit is minute.

LAMPTIM3 LAMPTIM2 LAMPTIM1 LAMPTIM0

Offset 04h ……………………………………………..…………..………..…… Default value = 8’h00

LINEART BITSET AFEMOD1 AFEMOD0 FILTER1 FILTER0 FESET1 FESET0

R/W R/W R/W R/W R/W R/W R/W R/W

7 LINEART 0 Color/Gray scanning.

1 Black/White scanning.

6 BITSET 0 8 bits image data type (= byte).

1 16 bits image data type (= word).

5-4 AFEMOD[1:0] AFE operation mode.

Wolfson Type

AFEMOD SCANMOD

2

1

0

AFEMOD SCANMOD

2 0,1,6,7

1 0,1,6,7 Mono Yes

0 0,1,6,7 Fast Mono Yes

0,1,7

0,1,6,7 Color pixel-by-pixel

0,1,4,5,6 Fast Mono Yes 13.3MSPS *1 channel

Description

Slow color

Pixel-by-pixel

Analog Device Type

Description

Slow color

Pixel-by-pixel

CDS

Available

Yes 5MSPS *3 channel

Yes 6.67MSPS *3 channel

CDS

Available

Yes

Max Sample Rate

Max Sample Rate

Timing

Requirements

MCLK:VSMP

Rate is 8:1

MCLK:VSMP

Rate is 6:1

MCLK:VSMP

Rate is 3:1

Timing

Requirements

MCLK:VSMP

Rate is 3:1

MCLK:VSMP

Rate is 2:1

MCLK:VSMP

Rate is 1:1

3-2 FILTER[1:0] Scan color type:

00 Color

©2000-2006 Genesys Logic Inc. - All rights reserved. Page 22

GL843 High Speed USB2.0 With ADF 2-in-1 Scanner Controller For 3x

01 R

10 G

11 B

1-0 FESET[1:0] Front end operation type:

00 ESIC type 1

01 ESIC type2

10 ADI type

Offset 05h ……………………………………………..…………..……..………. Default value = 8’h00

11 Reserved

DPIHW1 DPIHW0

MTLLAMP1 MTLLAMP0

GMMENB ENB20M

MTLBASE1 MTLBASE0

R/W R/W R/W R/W R/W R/W R/W R/W

7-6 DPIHW[1:0] To set CCD/CIS resolution.

00 600 dpi

01 1200 dpi

10 2400 dpi

11 4800 dpi

5-4 MTLLAMP[1:0] Multiply coefficient for time-out counter of lamp.

00 1* LAMPTIM

01 2* LAMPTIM

10 4* LAMPTIM

11 Reserved

3 GMMENB 0 Disable gamma correction.

1 Enable gamma correction.

2 ENB20M 0 CCD_CK1X output clocks according to designer’s settings .

1 CCD_CK1X generate 20MHz clock to CCD or CIS sensors.

1-0 MTLBASE[1:0] To set output CCD pixel number under each system pixel time.

00 1 CCD pixel/sstem pixel time.

01 2 CCD pixel/sstem pixel time.

10 3 CCD pixel/sstem pixel time.

11 4 CCD pixel/sstem pixel time.

Offset 06h ……………………………………………..…………..……..………. Default value = 8’h00

SCANMOD2 SCANMOD1 SCANMOD0

PWRBIT

GAIN4 OPTEST2 OPTEST1 OPTEST0

R/W R/W R/W R/W R/W R/W R/W R/W

7-5 SCANMOD[2:0] To set operation mode.

000 12 clocks/pixel ; normal mode operation for scanning.

Color scanning : 24 bits image with gamma correction

Gray scanning : 8 bits image with gamma correction

16 bits image without gamma correction

Line art scanning : 1 bit image with gamma correction

001 12 clocks/pixel ; bypass mode operation for calibration.

Include color(pixel rate) , gray line-art.

010 Reserved

011 Reserved

100 Reserved

101 Reserved

110 18 clocks/pixel.

Color scanning : 24 bits image with gamma correction

48 bits image without gamma correction

Gray scanning : 8 bits image with gamma correction

16 bits image without gamma correction

©2000-2006 Genesys Logic Inc. - All rights reserved. Page 23

GL843 High Speed USB2.0 With ADF 2-in-1 Scanner Controller For 3x

Line art scanning : 1 bit image with gamma correction

111 16 clocks/pixel.

Color scanning : 24 bits image with gamma correction

48 bits image without gamma correction

Gray scanning : 8 bits image with gamma correction

16 bits image without gamma correction

Line art scanning : 1 bit image with gamma correction

4 PWRBIT The hardware will reset this bit during power-on initial process. It can be set and

checked by S/W to know if the power had been turned off or not.

Default is reset.

3 GAIN4 0 Digital shading gain=8 times system.

1 Digital shading gain=4 times system.

Note: If you want to get more precise image quality,you can set GAIN4 bit.

2-0 OPTEST[2:0] Select ASIC operation type.

000 Set normal mode to capture AFE image.

001 Set SDRAM bank testing and power-on moving testing for ASIC simulation

010 Pixel count pattern for ASIC image test.

011 Line count pattern for ASIC image test.

100 Counter and adder test for ASIC simulation test.

101 Reserved.

110 Reserved.

111 Reserved.

Offset 07h ……………………………………………..…………..……..………. Default value = 8’h00

LAMPSIM CCDCTL DRAMCTL MOVCTL

RAMSEL FASTDMA DMASEL DMARDWR

R/W R/W R/W R/W R/W R/W R/W R/W

7 LAMPSIM for timer simulation

6 CCDCTL for CCD timing control

5 DRAMCTL for SRAM & DRAM access control

4 MOVCTL for motor driver IC style control

3 SRAMSEL 0 DMA access for DRAM.

1 DMA access for SRA

2 FASTDMA 0 4clocks/access,that is to say 4clocks/16bits or 4clocks/8bits for

DMA access.

1 2clocks/access,that is to say 2clocks/16bits or 2clocks/8bits for

DMA access.

1 DMASEL 0 MPU access DRAM under command mode.

1 DMA access DRAM under command mode.

0 DMARDWR 0 DMA read DRAM under command mode.

Note: Please do not write other values than 00H into this register under normal condition.

Offset 08h ……………………………………………..…………..……..………. Default value = 8’h00

X DECFLAG GMMFFR GMMFFG GMMFFB GMMZR GMMZG GMMZB

X R/W R/W R/W R/W R/W R/W R/W

7 RESERVED 6 DECFLAG 0 Select gamma table in increment type

1 Select gamma table in decrement type.

5 GMMFFR 0 This function is not enabled

1 Gamma table address FFH of red channel is a special value.

©2000-2006 Genesys Logic Inc. - All rights reserved. Page 24

0

GL843 High Speed USB2.0 With ADF 2-in-1 Scanner Controller For 3x

4 GMMFFG 0 This function is not enabled.

1 Gamma table address FFH of green channel is a special value.

3 GMMFFB 0 This function is not enabled.

1 Gamma table address FFH of blue channel is a special value.

2 GMMZR 0 This function is not enabled.

1 Gamma table address 00H of red channel is a special value.

1 GMMZG 0 This function is not enabled.

1 Gamma table address 00H of green channel is a special value.

0 GMMZB 0 This function is not enabled.

1 Gamma table address 00H of blue channel is a special value.

Offset 09h ……………………………………………..…………..……..………. Default value = 8’h00

MCNTSET1 MCNTSET0

EVEN1ST BLINE1ST

BACKSCAN

ENHANCE SHORTTG NWAIT

R/W R/W R/W R/W R/W R/W R/W R/W

7-6 MCNTSET[1:0] To select the unit of motor table counter.

00 Pixel count.

01 System clock*2.

10 System clock*3.

11 System clock*4.

5 EVEN1ST 0 The first pixel of stagger CCD is located at odd sensor line.

1 The first pixel of stagger CCD is located at even sensor line.

4 BLINE1ST 0 The first sensor of CCD is red line.

1 The first sensor of CCD is blue line.

3 BACKSCAN 0 Select forward scanning function.

1 Select backward scanning function.

2 ENHANCE 0 Select normal mode for embedded EPP interface.

1 Select enhance mode for embedded EPP interface.

1 SHORTTG 0 Disable this function.

1 Enable short CCD SH(TG) period for film scanning.

0 NWAIT 0 No delay for nWait.

1 To delay nWait (H_BUSY) for one clock.

Offset 0Ah …………………………………………..…………..……..………. Default value = 8’h00

LCDSEL LCMSEL ADFSEL LPWMEN

EPROMSEL

RS232SEL

R/W R/W R/W R/W R/W R/W R/W R/W

7 LCDSEL 0 Disable LCD display function.

1 Enable LCD display function and the specific GPIOs are defined to drive LCD.

6 LCMSEL 0 Disable LCM display function.

1 Enable LCM display function and the specific GPIOs are defined to drive LCM.

5 ADFSEL 0 Disable ADF function.

1 Enable ADF function and the specific GPIOs are defined to drive ADF module.

4 LPWMEN 0 Disable ADF function.

1 Enable PWM function of lamp.

3 EPROMSEL 0 Disable external EEPROM (93C46) interface.

1 Enable external EEPROM (93C46) interface and the specific GPIOs are

defined to connect EEPROM.

2 RS232SEL 0 Disable RS232 interface.

BAUDRAT1 BAUDRAT

©2000-2006 Genesys Logic Inc. - All rights reserved. Page 25

GL843 High Speed USB2.0 With ADF 2-in-1 Scanner Controller For 3x

1 Enable RS232 interface for special application and the specific GPIOs are

defined to implement RS232 protocol.

1-0 BAUDRAT[1:0] Set boud rate of RS232.

00 2400bps.

01 4800bps.

10 9600bps.

11 19200bps.

Offset 0Bh …………………………………………..…………..……..………. Default value = 8’h00

CLKSET2 CLKSET1 CLKSET0 RFHDIS

ENBDRAM DRAMSEL2 DRAMSEL1 DRAMSEL0

R/W R/W R/W R/W R/W R/W R/W R/W

7-5 CLKSET[2:0] To select the system clock frequency.

000 24MHz.

001 30MHz.

010 40MHz.

011 48MHz.

100 60MHz.

101 Reserved.

110 Reserved.

111 Reserved.

4 RFHDIS 0 Enable auto-refresh mode for SDRAM.

1 Enable self-refresh mode for SDRAM.

3 ENBDRAM A rising edge from low to high: to start power on sequence of SDRAM.

2-0 DRAMSEL[2:0] Select the SDRAM size.

000 Reserved.

001 16M bit.

010 64M bit.

011 128M bit.

100 256M bit.

101 512M bit.

110 Reserved.

111 Reserved.

Offset 0Ch …………………………………………..…………..……..………. Default value = 8’h00

SWSH4 SWSH3 SWSH2 SWSH1 SWSH0 CCDLMT2 CCDLMT1 CCDLMT0

R/W R/W R/W R/W R/W R/W R/W R/W

7-3 SWSH [4:0] To set the distance from SEL3 to TG for NEC8884. the width s

SWSH[4:2]*2

TGSTIME

2-0 CCDLMT[2:0] To set the lines count which is synchronized for CCD timing(like NEC8884).

Offset 0Dh

JAMPCMD DOCCMD CCDCMD

FULLSTP SEND

W W W W W W W W

Command: Scanner command.

7 JAMPCMD To control jamp when scanner is working on ADF.

©2000-2006 Genesys Logic Inc. - All rights reserved. Page 26

CLRMCNT CLRDOCJM CLRLNCNT

Loading...

Loading...