Genesis gm5060H Datasheet

Genesis Microchip Inc.

165 Commerce Valley Dr. West • Thornhill • ON • Canada L3T 7V8 • Tel: (905) 889-5400 • Fax: (905) 889-5422

2150 Gold Street • PO Box 2150 • Alviso • CA • USA 95002 • Tel: (408) 262-6599 • Fax: (408) 262-6365

4F, No. 24, Ln 123, Sec 6, Min-Chung E. Rd. • Taipei • Taiwan • Tel: (2) 2791-0118 • Fax: (2) 2791-0196

143-37 Hyundai Tower • Unit 902 • Samsung-dong • Kangnam-gu • Seoul • Korea • 135-090 • Tel: (82-2) 553-5693 • Fax: (82-2) 552-4942

www.genesis-microchip.com / info@genesis-microchip.com

Genesis Microchip Publication

DATA SHEET

gm5060/gm5060-H

Sections in this document and all other related documentation that mention HDCP refer

only to the gm5060-H (HDCP-enabled) chip. All other sections apply to both the gm5060-H

chip and the gm5060 (non-HDCP) chip.

Publication number: C5060-DAT-01G

Publication date: February 2002

Genesis Microchip gm5060 / gm5060-H Data Sheet

Trademarks: RealColor and Ultra-Reliable DVI are trademarks of Genesis Microchip Inc.

© Copyright 2002, Genesis Microchip Inc. All Rights Reserved.

Genesis Microchip Inc. reserves the right to change or modify the information contained herein without

notice. It is the customer’s responsibility to obtain the most recent revision of the document. Genesis

Microchip Inc. makes no warranty for the use of its products and bears no responsibility for any errors

or omissions that may appear in this document.

Genesis Microchip gm5060/gm5060-H Data Sheet

February 2002 C5060-DAT-01G

iii

Document history

Previous publication releases:

C5060-DAT-01A January 2001

C5060-DAT-01B February 2001

C5060-DAT-01C April 2001

C5060-DAT-01D April 2001

C5060-DAT-01E July 2001

C5060-DAT-01F November 2001

Current publication releases:

C5060-DAT-01G

Initial release February 2002

Genesis Microchip gm5060/gm5060-H Data Sheet

February 2002 C5060-DAT-01G

iv

Table Of Contents

1. Overview ................................................................................................................................... 1

1.1 gm5060 System Design Example....................................................................................... 2

1.2 gm5060/gm5060-H Features .............................................................................................. 3

2. Pinout Diagram ......................................................................................................................... 4

3. Pin List ...................................................................................................................................... 6

4. Functional Description............................................................................................................. 12

4.1 Clocking Options............................................................................................................... 13

4.1.1 TCLK Requirements............................................................................................... 13

4.1.2 Synthesized Clocks ................................................................................................ 16

4.2 Hardware and Software Resets........................................................................................ 17

4.2.1 Hardware Reset ..................................................................................................... 17

4.2.2 Software Reset....................................................................................................... 17

4.3 Analog to Digital Converter............................................................................................... 19

4.3.1 Pin Connection ....................................................................................................... 19

4.3.2 ADC Characteristics ............................................................................................... 20

4.3.3 Sync. Signal Support.............................................................................................. 21

4.3.4 Clock Recovery ...................................................................................................... 22

4.3.5 Sampling Phase Adjustment .................................................................................. 23

4.4 Ultra-Reliable Digital Visual Receiver (DVI Rx)................................................................. 25

4.4.1 DVI Receiver Characteristics.................................................................................. 25

4.4.2 HDCP (High-Bandwidth Digital Content Protection System) .................................. 26

4.5 ITU-R BT656 Video Input ................................................................................................. 27

4.5.1 YCbCr Input Clamping ........................................................................................... 27

4.6 Image Capture – Active Window Decoder ........................................................................ 28

4.6.1 ADC Capture Window ............................................................................................ 28

4.6.2 DVI Capture Window.............................................................................................. 30

4.6.3 ITU-R BT656 Capture Window............................................................................... 30

4.7 Image Measurement......................................................................................................... 32

4.7.1 Input Format Measurement (IFM)........................................................................... 32

4.7.2 Input Data Measurement........................................................................................ 34

4.8 Digital Color Controls........................................................................................................ 36

4.8.1 YUV Hue / Saturation Controls............................................................................... 36

4.8.2 RealColor Flesh tone Adjustment........................................................................... 37

4.8.3 RGB Black Level / Contrast / Brightness................................................................ 37

4.8.4 Input Look-up Table ............................................................................................... 38

4.9 Horizontal Shrink .............................................................................................................. 39

4.10 Frame Store Interface..................................................................................................... 40

4.10.1 Supported SDRAM Devices ................................................................................. 40

4.10.2 Adjustable Frame Store Interface Delays ............................................................. 40

Genesis Microchip gm5060/gm5060-H Data Sheet

February 2002 C5060-DAT-01G

v

4.10.3 Frame Store Bandwidth Requirements ................................................................ 40

4.10.4 SDRAM Power On Sequence .............................................................................. 41

4.10.5 SDRAM Power Down ........................................................................................... 41

4.10.6 Pan and Crop Operations..................................................................................... 41

4.10.7 Double Buffering Frame Store Bandwidth Requirements ..................................... 42

4.10.8 Freeze Frame....................................................................................................... 42

4.10.9 Interlaced Formats and De-interlacing ................................................................. 42

4.11 Scaling............................................................................................................................ 43

4.11.1 Pixel Replication Scaling ...................................................................................... 43

4.11.2 Vertical Shrink ...................................................................................................... 43

4.11.3 Adaptive Contrast Enhancement (ACE) ............................................................... 43

4.12 Gamma Correction LUT.................................................................................................. 44

4.12.1 Gamma Correction ............................................................................................... 44

4.12.2 Moiré Cancellation................................................................................................ 45

4.13 Display Timing and Control............................................................................................. 46

4.13.1 Display Clock Generation – Display Digital Direct Synthesis Block (DDDS) ........ 46

4.13.2 Display Synchronization ....................................................................................... 47

4.13.3 Display Port Timing .............................................................................................. 49

4.14 Data Path Bypass Options.............................................................................................. 51

4.15 OSD................................................................................................................................ 53

4.15.1 Character Mapped OSD....................................................................................... 53

4.15.2 Bitmapped OSD ................................................................................................... 59

4.15.3 Color Look-up Table (LUT)................................................................................... 59

4.15.4 Multiple OSD Windows......................................................................................... 59

4.15.5 OSD Stretch ......................................................................................................... 59

4.15.6 Blending ............................................................................................................... 59

4.15.7 OSD Merge .......................................................................................................... 60

4.16 On-Chip Microprocessor................................................................................................. 61

4.17 Bootstrap Configuration .................................................................................................. 62

4.18 Host Interface ................................................................................................................. 63

4.18.1 2-wire Configuration ............................................................................................. 63

4.18.2 6-Wire Configuration ............................................................................................ 66

4.19 Miscellaneous Functions ................................................................................................ 69

4.19.1 General Purpose Inputs and Outputs (GPIO’s) .................................................... 69

4.19.2 Pulse Width Modulation (PWM) Back Light Control ............................................. 69

4.19.3 Low Power State .................................................................................................. 69

5. Electrical Specifications .......................................................................................................... 70

5.1 DC Characteristics............................................................................................................ 70

5.2 Preliminary AC Characteristics ......................................................................................... 72

6. Ordering Information ............................................................................................................... 76

7. Mechanical Specifications....................................................................................................... 77

Genesis Microchip gm5060/gm5060-H Data Sheet

February 2002 C5060-DAT-01G

vi

List Of Tables

Table 1. ADC Signals ............................................................................................................. 6

Table 2. DVI Receiver Signals................................................................................................ 6

Table 3. RCLK and FCLK PLL Signals ................................................................................... 7

Table 4. Video Input Port Signals ........................................................................................... 7

Table 5. Host Controller Interface Signals .............................................................................. 7

Table 6. Display Port Signals.................................................................................................. 8

Table 7. Frame Store Interface Signals .................................................................................. 9

Table 8. Power and Ground Signals ..................................................................................... 11

Table 9. No Connects........................................................................................................... 11

Table 10. Pin Connection for RGB Input with HSYNC/VSYNC .............................................. 19

Table 11. ADC Characteristics ............................................................................................... 20

Table 12. DVI Receiver Characteristics.................................................................................. 25

Table 13. Framestore Bandwidth and Data Widths ................................................................ 41

Table 14. Bootstrap Signals.................................................................................................... 62

Table 15. Instruction Byte Map ............................................................................................... 64

Table 16. Absolute Maximum Ratings (Both gm5060 and gm5060-H).................................. 70

Table 17. DC Characteristics.................................................................................................. 71

Table 18. Maximum Speed of Operation ................................................................................ 72

Table 19. ITU-R BT656 Input Port Timing .............................................................................. 74

Table 20. Framestore Output Timing and Adjustments .......................................................... 74

Table 21. Framestore Readback Timing (for all conditions) ................................................... 74

Table 22. Display Timing and DCLK Adjustments .................................................................. 75

Table 23. 2-Wire Host I/F Port Timing .................................................................................... 75

Table 24. 6-Wire Host I/F Port Timing .................................................................................... 75

Genesis Microchip gm5060/gm5060-H Data Sheet

February 2002 C5060-DAT-01G

vii

List Of Figures

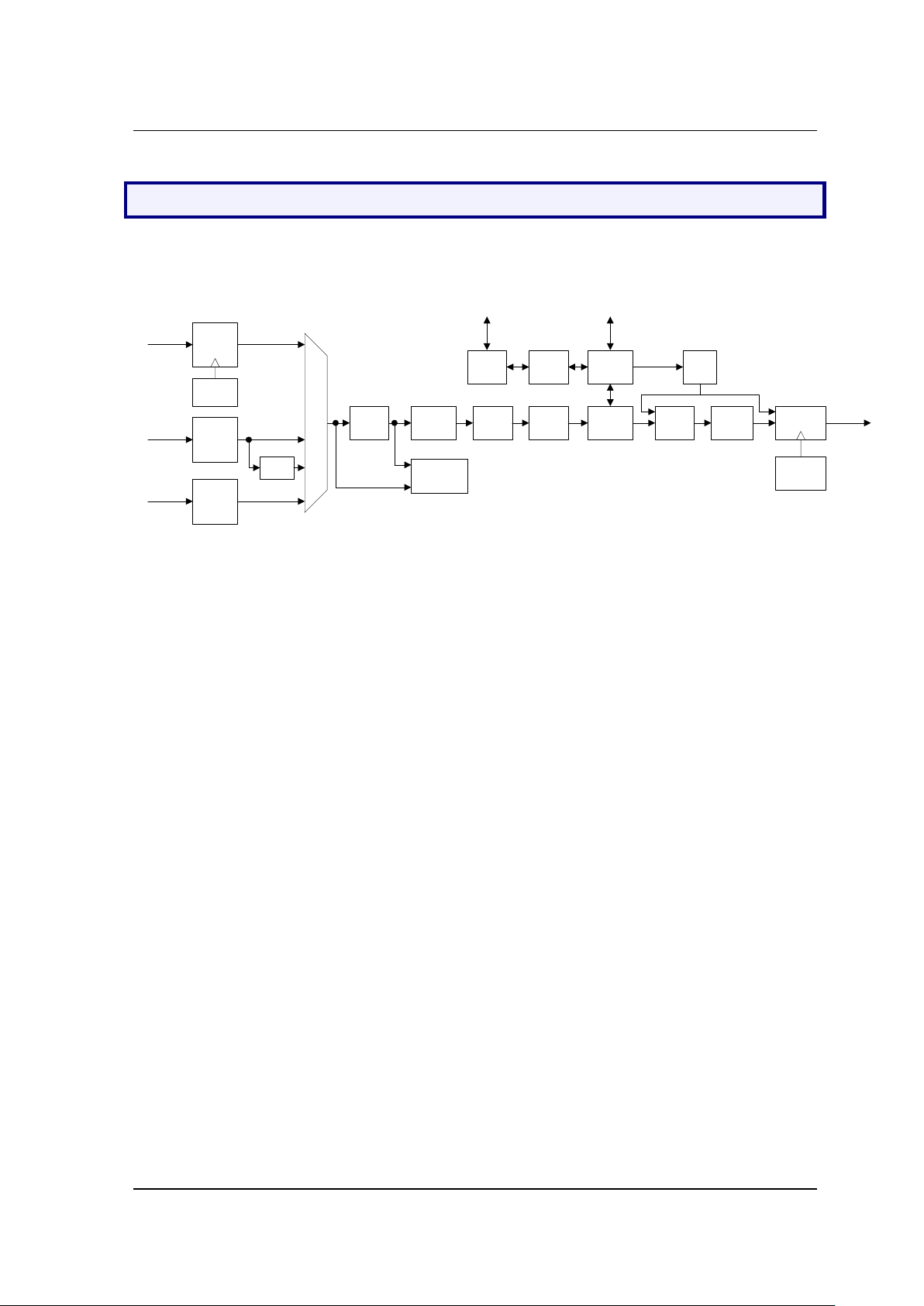

Figure 1. gm5060 System Design Example............................................................................. 2

Figure 2. gm5060 Pinout Diagram ........................................................................................... 5

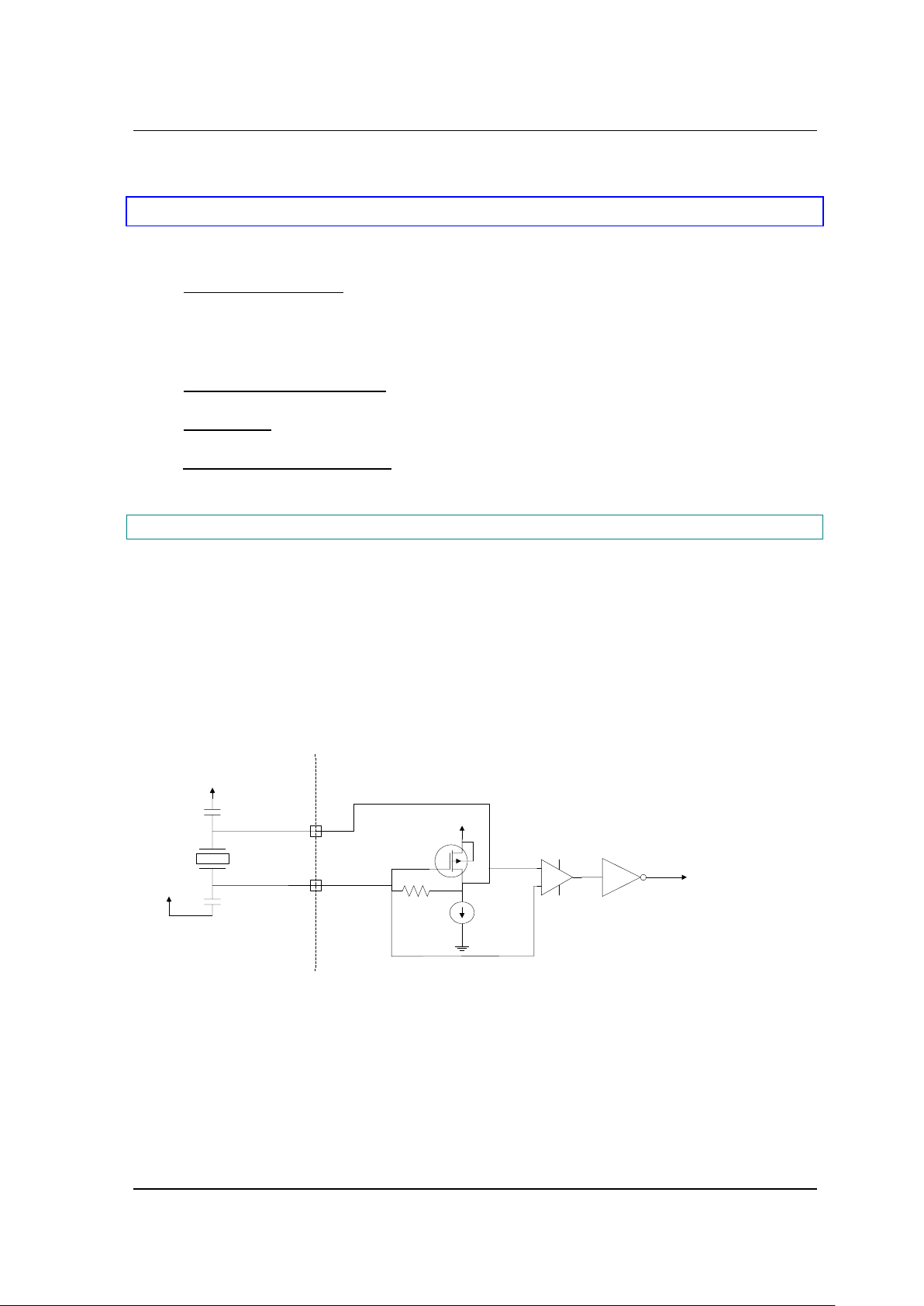

Figure 3. gm5060 Functional Block Diagram ......................................................................... 12

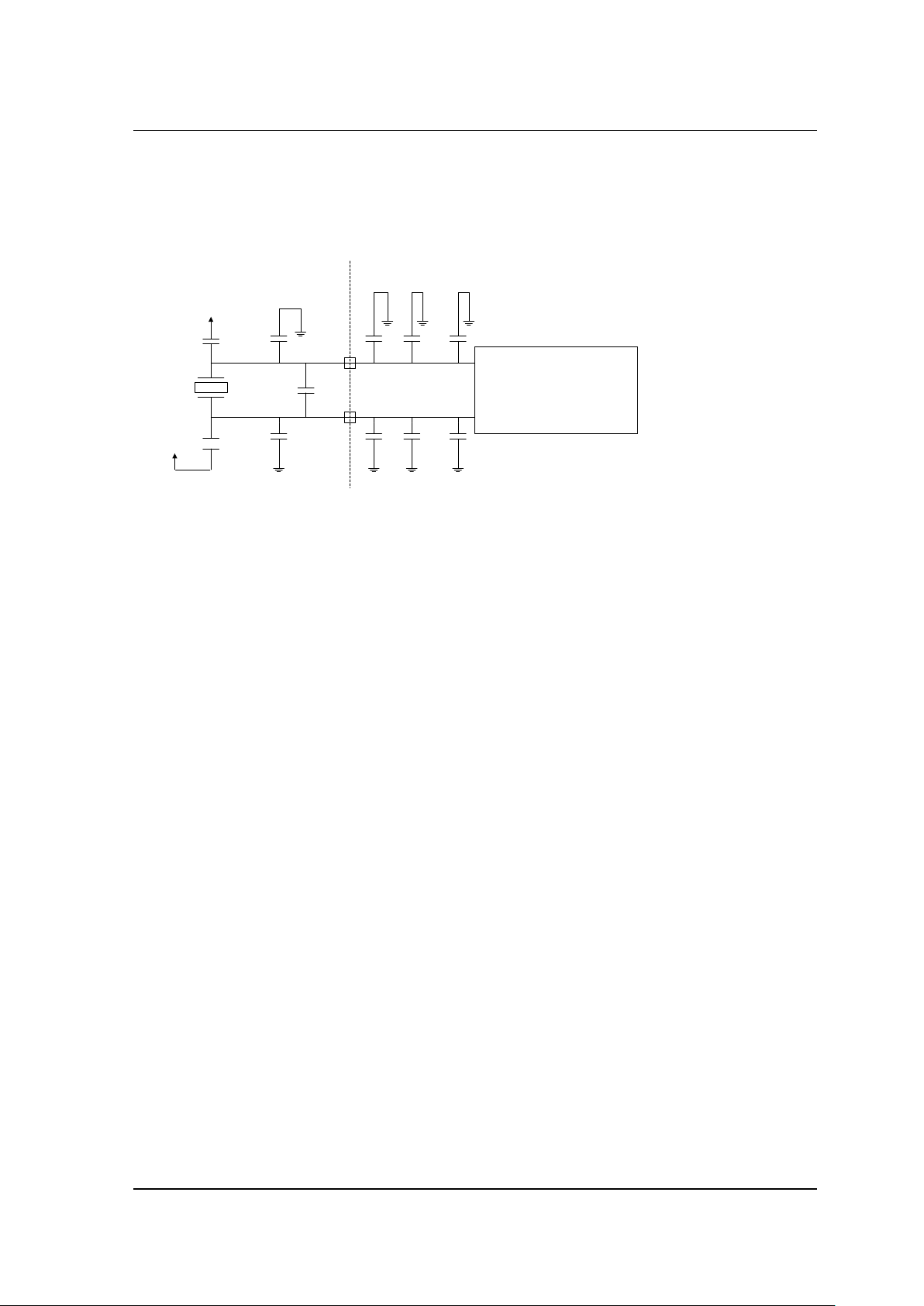

Figure 4. TCLK connection (with Crystal Resonator)............................................................. 13

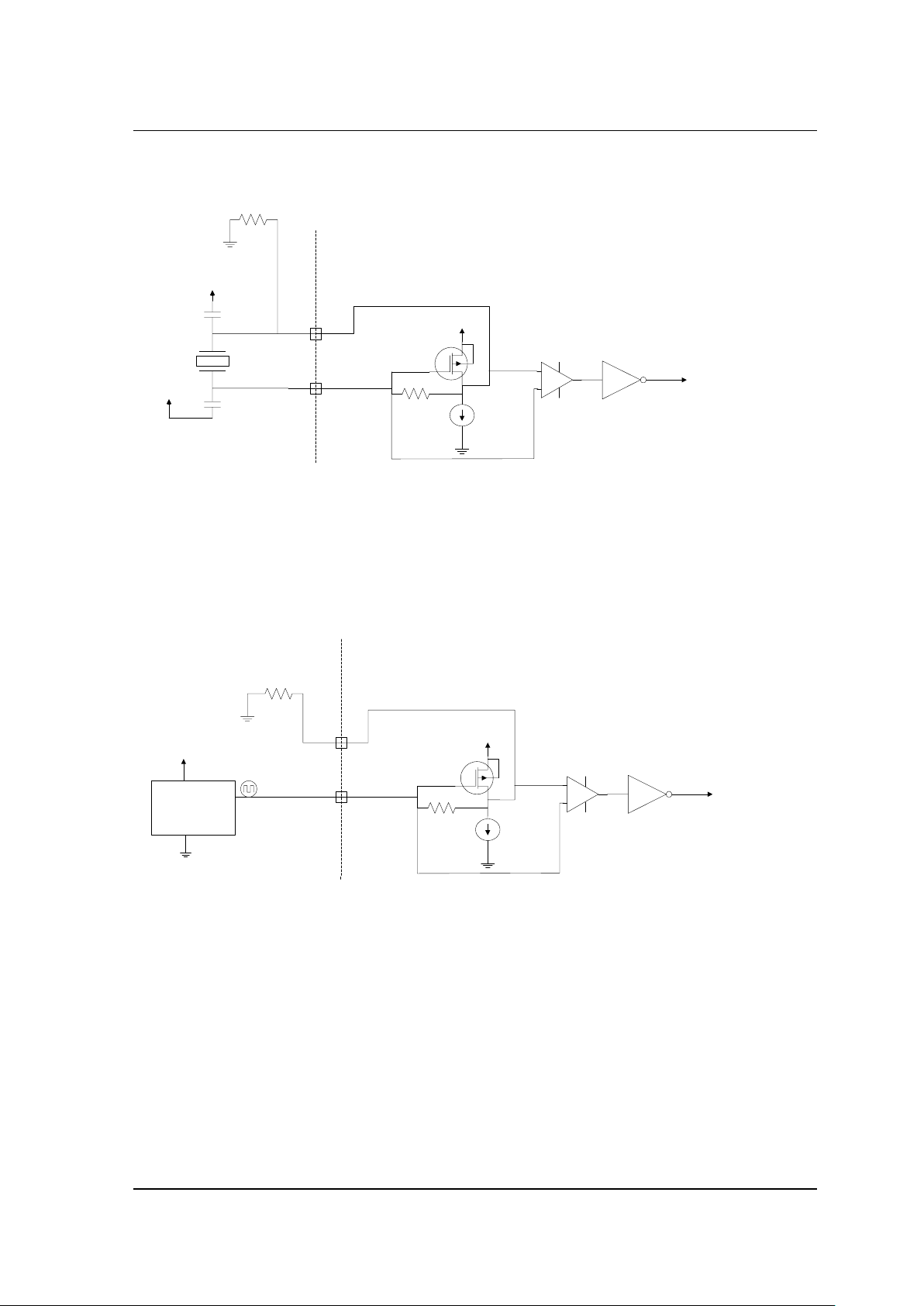

Figure 5. TCLK parasitic capacitances .................................................................................. 14

Figure 6. TCLK connection (with Optional Resistor) .............................................................. 15

Figure 7. TCLK connection (with Oscillator)........................................................................... 15

Figure 8. Internal Clock Sources............................................................................................ 16

Figure 9. Hardware Reset...................................................................................................... 18

Figure 10. ADC Block .............................................................................................................. 19

Figure 11. Example Signal Terminations ................................................................................. 20

Figure 12. Positive and negative polarity OR-type CSYNC ..................................................... 21

Figure 13. Positive and negative polarity XOR-type CSYNC ................................................... 21

Figure 14. Positive and negative polarity serration-type CSYNC............................................. 22

Figure 15. Positive and negative polarity "serration with equalization”-type CSYNC ............... 22

Figure 16. gm5060 Clock Recovery......................................................................................... 23

Figure 17. Phase Adjustment Delay Curve .............................................................................. 24

Figure 18. DVI Block................................................................................................................ 25

Figure 19. ITU-R BT656 Block................................................................................................. 27

Figure 20. Image Capture Block .............................................................................................. 28

Figure 21. Capture Window ..................................................................................................... 29

Figure 22. HSYNC Delay ......................................................................................................... 29

Figure 23. Active Data Crosses HSYNC Boundary ................................................................. 30

Figure 24. ITU-R BT656 Input.................................................................................................. 31

Figure 25. Image Measurement Block ..................................................................................... 32

Figure 26. ODD/EVEN Field Detection .................................................................................... 33

Figure 27. Pixel Grab............................................................................................................... 35

Figure 28. Digital Color Control Blocks .................................................................................... 36

Figure 29. YUV Color Controls ................................................................................................ 36

Figure 30. Black / Contrast / Brightness Transfer Function...................................................... 38

Figure 31. Input LUT and Dithering.......................................................................................... 38

Figure 32. Frame Store Interface Blocks ................................................................................. 40

Figure 33. FRC Required Parameters ..................................................................................... 42

Figure 34. Scaling Block .......................................................................................................... 43

Figure 35. Gamma Correction LUT Block ................................................................................ 44

Figure 36. Gamma Response Curve ....................................................................................... 45

Figure 37. Display Timing and Control Blocks ......................................................................... 46

Figure 38. DDDS Block............................................................................................................ 46

Figure 39. Lock Event Timing (Frame Sync Mode).................................................................. 49

Figure 40. Display Windows and Timing.................................................................................. 50

Figure 41. Single / Double-wide Display Data.......................................................................... 50

Figure 42. Capture Only Mode................................................................................................. 51

Figure 43. FRC Bypass Mode.................................................................................................. 51

Figure 44. Scaler Bypass Mode............................................................................................... 52

Genesis Microchip gm5060/gm5060-H Data Sheet

February 2002 C5060-DAT-01G

viii

Figure 45. OSD Block .............................................................................................................. 53

Figure 46. OSD Character Map ............................................................................................... 54

Figure 47. Non-Rotated SRAM Resident Font......................................................................... 56

Figure 48. Rotated SRAM Resident Font................................................................................. 57

Figure 49. User Define-able SRAM Resident Font .................................................................. 57

Figure 50. MCU Block.............................................................................................................. 61

Figure 51. System µC - Embedded µC Communication........................................................... 61

Figure 52. Host Interface Block................................................................................................ 63

Figure 53. 2-Wire External Interface ........................................................................................ 63

Figure 54. 2-wire Protocol Data Transfer................................................................................. 65

Figure 55. Write Address Increment and Write Address No Inc (0x10 & 0x20) ....................... 65

Figure 56. Read Address Increment and Read Address No Inc (0x90 & 0xA0)....................... 66

Figure 57. Direct Read............................................................................................................. 66

Figure 58. 6-Wire Write Operations (0x1x & 0x2x) .................................................................. 68

Figure 59. 6-Wire Read Operations (0x9x & 0xAx).................................................................. 68

Figure 60. Clock Reference Levels.......................................................................................... 72

Figure 61. Setup and Hold Reference Levels .......................................................................... 73

Figure 62. Propagation Delay Reference Levels ..................................................................... 73

Figure 63. gm5060 292-pin PBGA......................................................................................... 77

Genesis Microchip gm5060/gm5060-H Data Sheet

February 2002 C5060-DAT-01G

1

1. OVERVIEW

The gm5060 is a graphics processing IC providing high-quality images for LCD monitors and

other pixelated displays. It combines a triple ADC, the Genesis Ultra-Reliable DVI

™

receiver, a

high quality zoom and shrink scaling engine, frame rate conversion, an on-screen display (OSD)

controller, a microprocessor and many other functions in a single device. This high level of

integration enables simple, flexible, cost-effective solutions featuring fewer required

components.

The gm5060 is ideal for dual-interface (analog and digital) LCD monitors up to UXGA

resolutions.

Genesis Microchip gm5060/gm5060-H Data Sheet

February 2002 C5060-DAT-01G

2

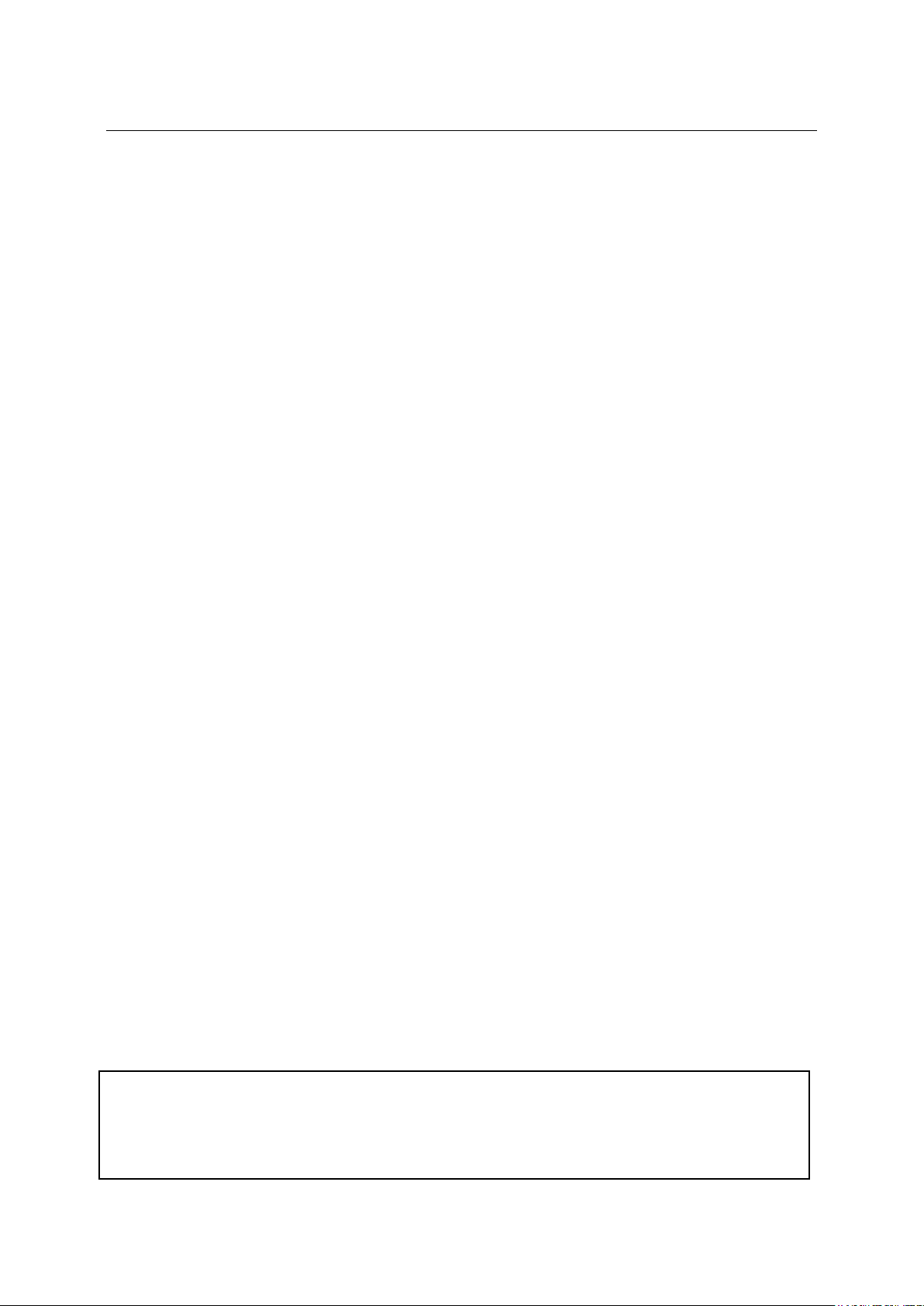

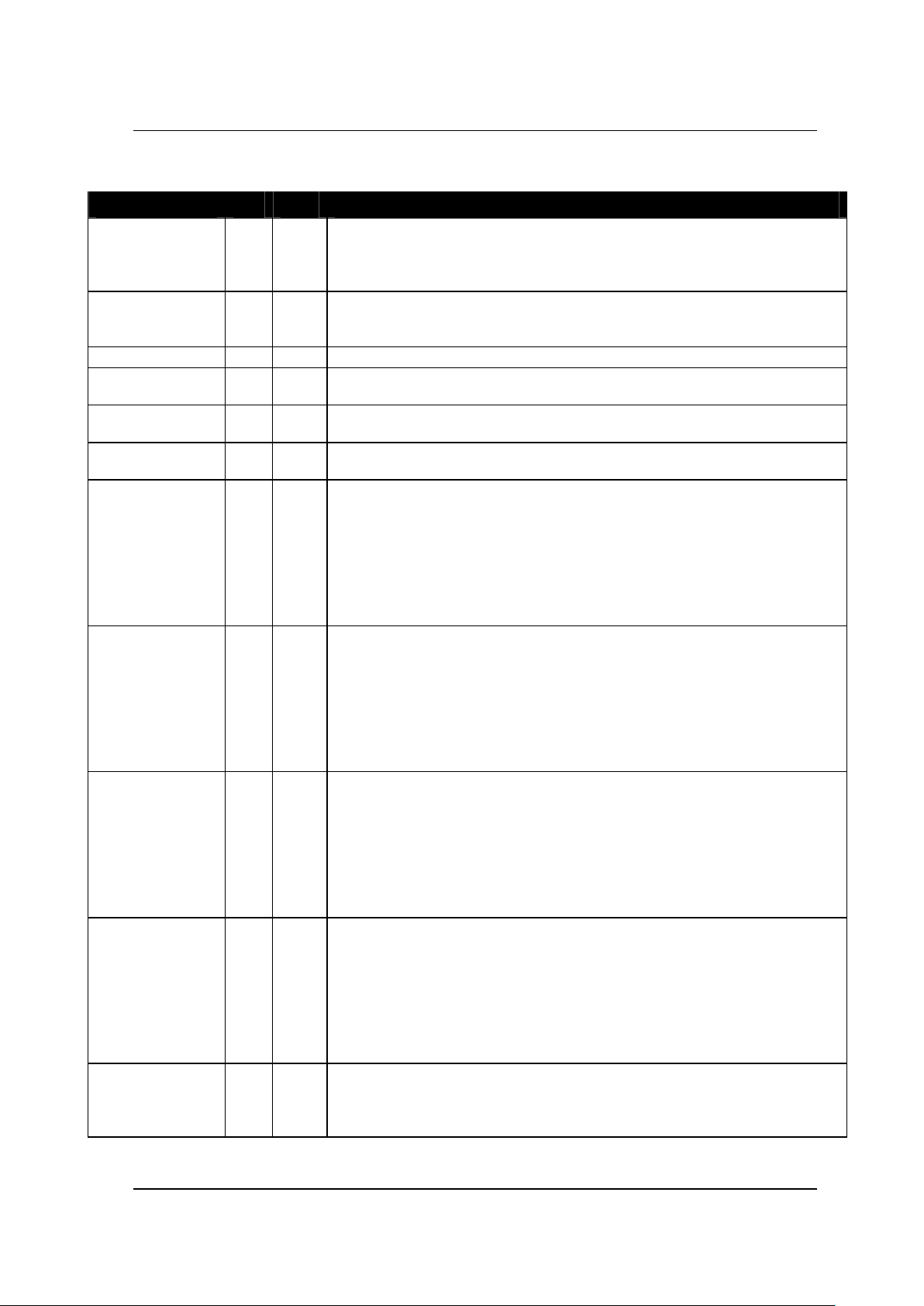

11..11 ggmm55006600 SSyysstteemm DDeessiiggnn EExxaammppllee

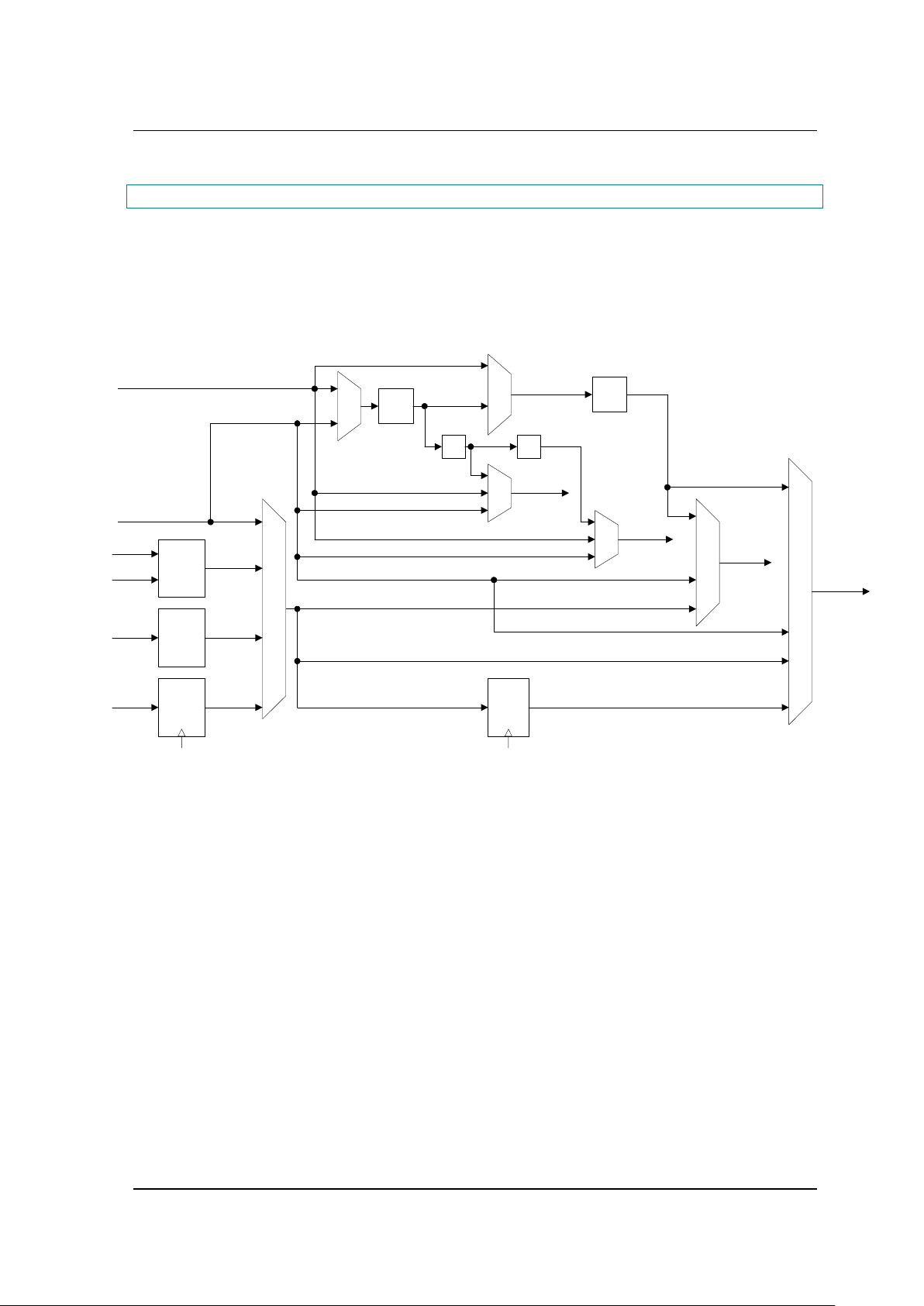

Figure 1 below shows a typical dual interface LCD monitor system based on the gm5060.

Designs based on the gm5060 have reduced system cost and simplified hardware and firmware

design because only a minimal number of components are required in the system. The chip can

be used in a variety of systems, ranging from 'single-chassis' solutions for XGA and UXGA

monitors with frame store memory and video inputs. In addition, the gm5060 can be used in midrange SXGA monitors with no frame store memory.

Analog

RGB

Digital

DVI

Panel

Interface

(24/48-bits)

DRAM

DRAM

DRAM

Video

Decoder

gm5060

MCUPROM

XTAL

Keypad

Power

Timing

Controller

LCD ROW

Drivers

LCD Column

Drivers

EDID

PROM

EDID

PROM

Video

(Y/C, Comp etc)

XTAL

EEPROM

+12V

+5V

+3.3V

+2.5v

**Optional - For

Video support only

**Optional - For

FRC support only

**Optional - For Rom-

less MCU only

.

Figure 1. gm5060 System Design Example

Genesis Microchip gm5060/gm5060-H Data Sheet

February 2002 C5060-DAT-01G

3

11..22 ggmm55006600//ggmm55006600--HH FFeeaattuurreess

FEATURES

• Zoom and shrink scaling (all resolutions from VGA to UXGA)

• Frame rate conversion

• Integrated 8-bit triple-channel ADC / PLL

• Integrated Genesis Ultra-Reliable DVI

TM

receiver (DVI 1.0)

• Integrated High-bandwidth Digital Content Protection (HDCP)

• Embedded microcontroller simplifies OSD creation

• On-chip versatile OSD engine

• All system clocks synthesized from a single external crystal

• Programmable gamma correction (CLUT)

• Hue, Saturation, Brightness, Contrast and Gamma controls for RGB

and YUV signals

• RealColor™ fleshtone adjustment

• PWM backlight intensity control

• 5 Volt tolerant inputs

• High-Quality Advanced Scaling

• Fully programmable zoom/shrink ratios

• Independent horizontal / vertical zoom and shrink

• Variable sharpness control

• Moiré cancellation

• Analog RGB Input Port

• Supports up to UXGA at 60Hz

• Support for Sync-on-Green (SOG) and Composite Sync

modes

• Ultra-Reliable DVI Receiver

• Single link on-chip DVI receiver

• Operating up to 165 MHz

• Direct connect to all DVI-compliant transmitters

•

High-bandwidth Digital Content Protection (HDCP)

•

Enhanced protection of HDCP secret keys

• Digital Video Port

• 8-bit ITU-R BT656 input video

• Seamless connection to commercially available video capture

devices

APPLICATIONS

• Multi-synchronous XGA, SXGA, or UXGA LCD monitors with

dual analog/digital interface

• Any fixed-resolution pixelated display device

• Auto-Configuration / Auto-Detection

• Phase and image positioning

• Input format detection

• Compatibility with all graphic cards and standard VESA

modes

• Frame Store Interface

• Fully-programmable 48 / 32-bit wide data path

• Optional use of data compression for more flexibility

and lower system solution cost

• Support for up to 143MHz SDRAM or SGRAM

• On-chip OSD Controller

• Bit-mapped OSD capability

• On-chip RAM for downloadable fonts

• Horizontal and vertical stretch of OSD images

• Blinking, transparency and blending

• Output Format

• Double wide up to UXGA 60Hz output

• Support for 8 or 6-bit panels (with high-quality dithering)

• Operating Modes

• Frame rate conversion and scaling of images

• Bypass mode with no filtering and/or frame buffering

• 1:1 centering

• De-interlaced zoom

• Frame Sync and Free Run display synchronization

modes

• Highly Integrated Solution Provides

Lowest System Cost

• Simplicity of Design Speeds Time to

Market

• Complete reference design kit

available (software and hardware)

PACKAGE

• 292-pin PBGA

Genesis Microchip gm5060/gm5060-H Data Sheet

February 2002 C5060-DAT-01G

4

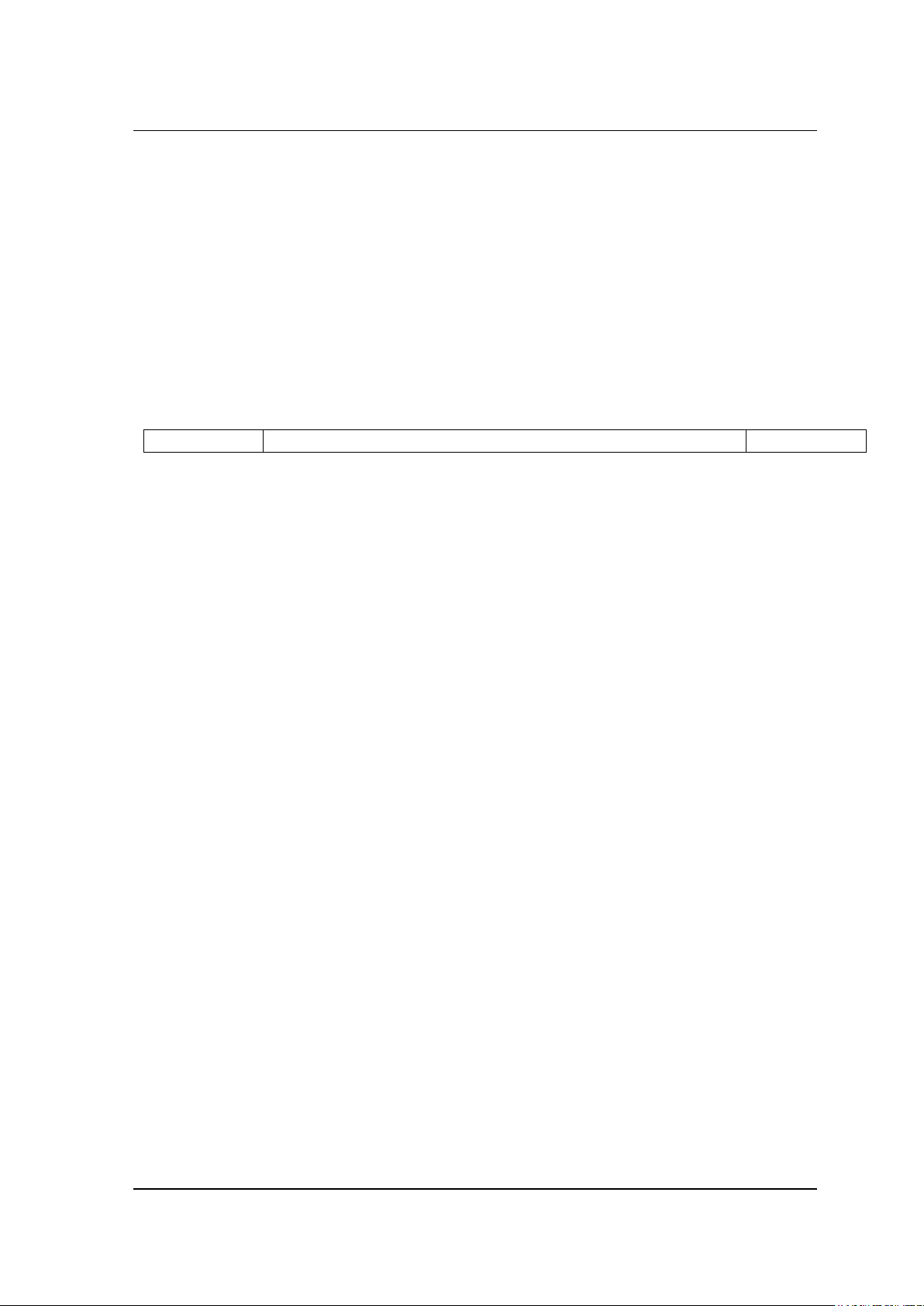

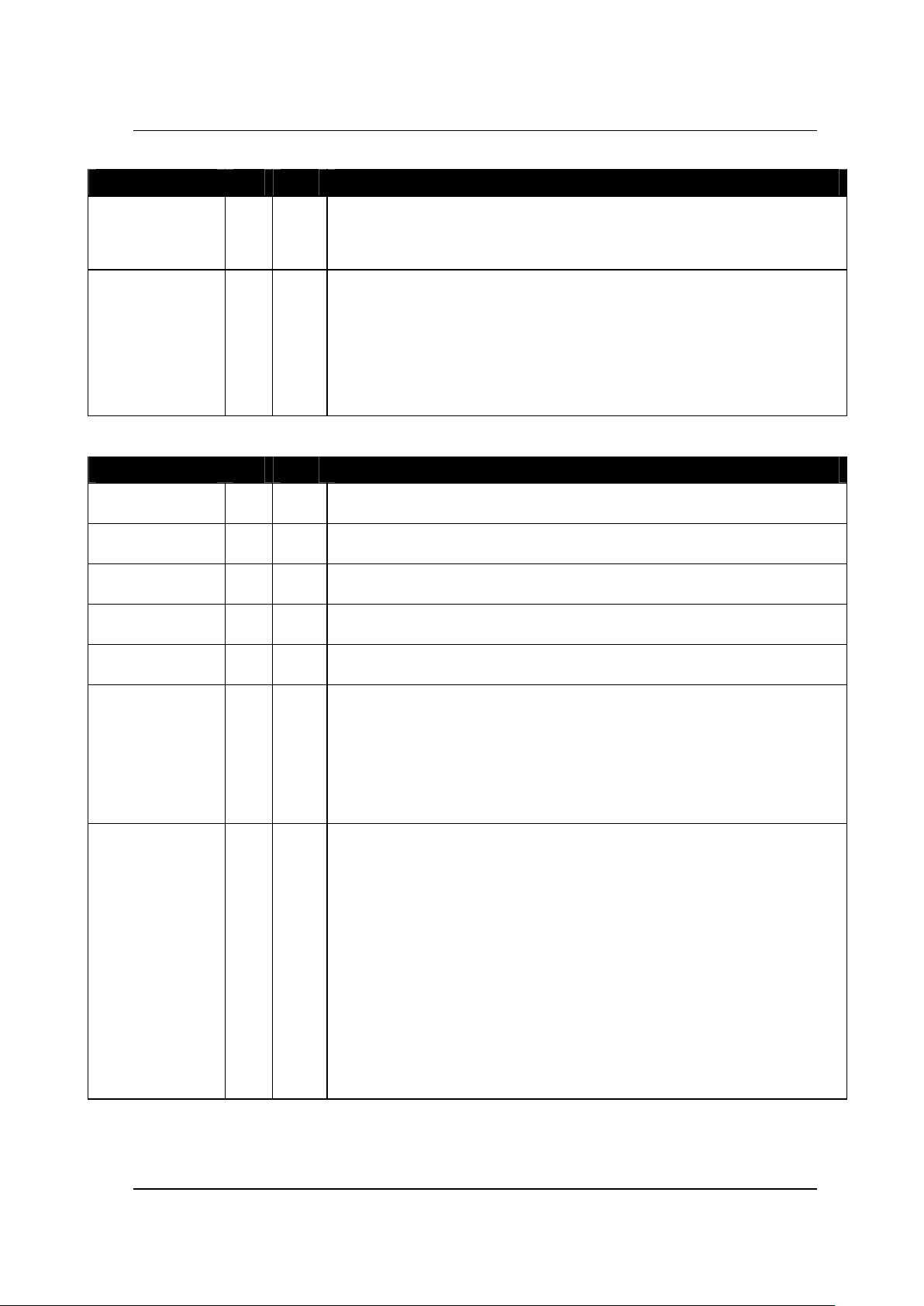

2. PINOUT DIAGRAM

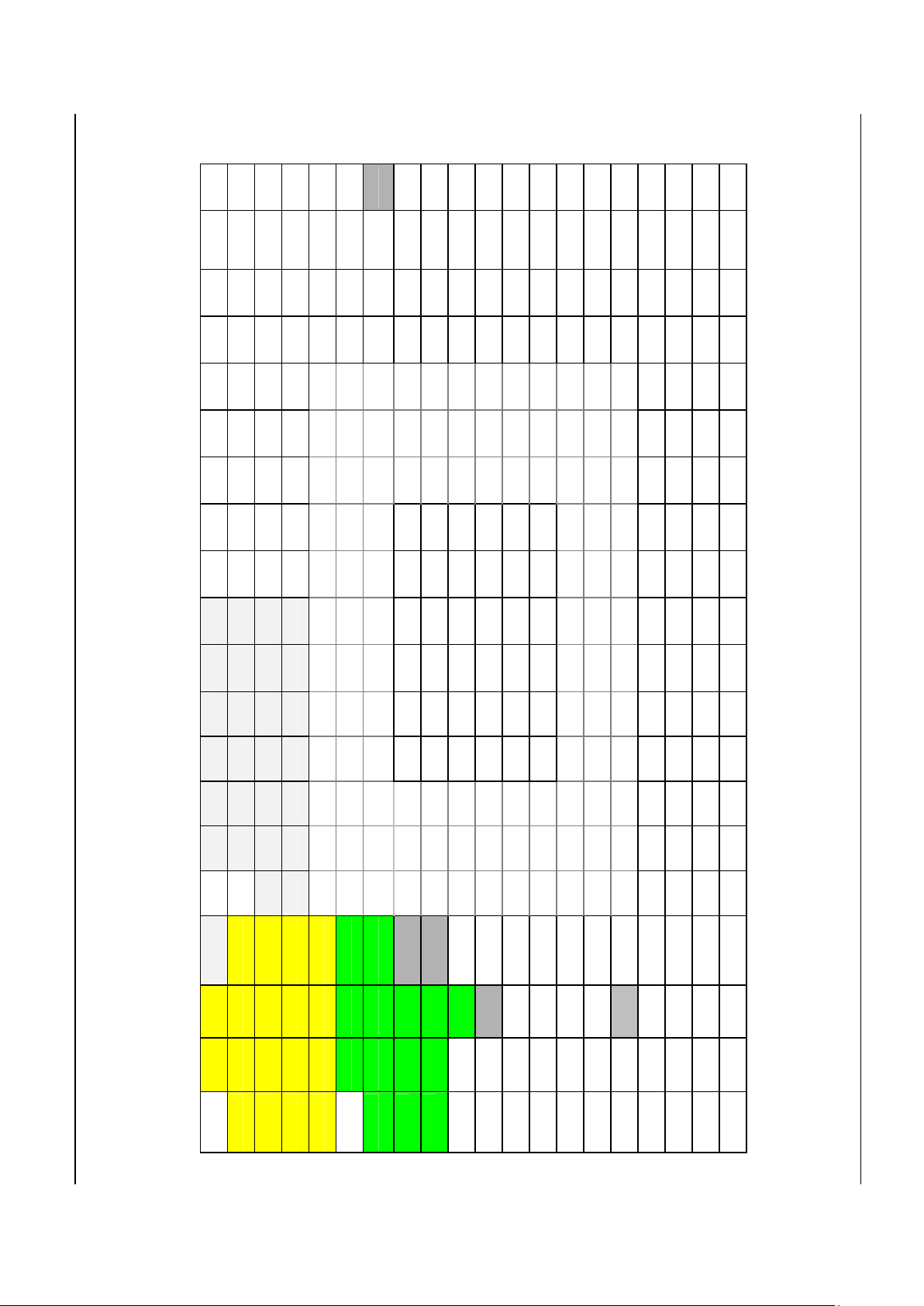

The gm5060 is available in a 292-pin PBGA (Ball Gate Array) package. Figure 2 below

provides the ball locations for all signals.

Power and Ground:

DGND

Periphery and Core Digital Ground

DVDD_3.3

Periphery Digital VDD (3.3V supply)

DVDD_2.5

Core Digital VDD (2.5V supply)

PGND

PLL Ground

PLLVDD_3.3

PLL VDD (3.3V supply)

AGND

Analog Ground

AVDD_3.3

Analog VDD (3.3V supply)

AVDD_2.5

Analog VDD (2.5V supply)

Pinout Legend:

DVI

High Frequency Clock

ADC

DDS and PLL

Genesis Microchip gm5060/gm5060-H Data Sheet

February 2002 C5060-DAT-01G

5

Figure 2. gm5060 Pinout Diagram

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20

A

N / C AGND AGND AGND N / C AVDD_2.5 AVDD_2.5 AVDD_2.5 AVDD_2.5 AVDD_2.5 AVDD_2.5 VCLK YUV 5 YUV2 DBRED7 DBRED4 DBRED1 DBGRN6 DBGRN3 DBGRN2

A

B

AGND AVDD_3.3 AGND AGND N / C AVDD_3.3 AVDD_3.3 AVDD_3.3 AVDD_3.3 REXT AVDD_3.3 YUV7 YUV4 YUV1 DBRED6 DBRED3 DBRED0 DBGRN5 DBGRN1 DBGRN0

B

C

BLUE+ BLUE- AVDD_3.3 AGND AGND RXC+ AGND RX 0+ RX1+ RX2+ AGND YUV6 YUV3 YUV0 DBRED5 DBRED2 DBGRN7 DBGRN4 DBBLU7 DBBLU6

C

D

GREEN- GREEN+ AVDD_3.3 AGND AGND RXC- AGND RX0- RX1- RX2- AGND DVDD_2.5 DVDD_3.3 DVDD_2.5 DVDD_3.3 DVDD_3.3 DVDD_2.5 DBBLU5 DBBLU4 DBBLU3

D

E

RED+ RED- AVDD_3.3 AGND DVDD_3.3 DBBLU2 DBB LU1 DBB LU0

E

F

N / C PLLVDD_3.3 PLLGND PLL VDD_3.3 DVDD_2.5 DEN DVS DHS

F

G

PLLVDD_3.3 PLLGND PLLVDD _3.3 PLLGND DVDD_3.3 GPIO6 /

DFSYNCn

GPIO7 / DOVL

DCLK

G

H

PLLVDD_3.3 PLLGND PLLGND

XTAL

DGND DGND DGND DGND DGND DGND DARED7 DARED6 DARED5 DARED4

H

J

PLLVDD_3.3 PLLGND PLLVDD _3.3

TCLK

DGND DGND DGND DGND DGND DGND DVDD_3.3 DARED3 DARED2 DARED1

J

K

VSYNC N / C PLLGND DVDD_2.5 DGND DGND DGND DGND DGND DGND DVDD_2.5 DARED0 DAGRN7 DAGRN6

K

L

GPIO5 HSYNC

EXTCLK

DVDD_3.3 DGND DGND DGND DGND DGND DGND DVDD_3.3 DAGRN3 DAGRN4 DAGRN5

L

M

GPIO4 GPIO3 GPIO2 GPIO1 / PWM1 DGND DGND DGND DGND DGND DGND DVDD_2.5 DAGRN0 DAGRN1 DAGRN2

M

N

GPIO0 / PWM0 DDC_S CL DDC_SDA DVDD_2.5 DGND DGND DGND DGND DGND DGND DVDD_3.3 DABLU5 DABLU6 DABLU7

N

P

HCLK / SCL HFSn / SDA HDATA3 HDAT A2 DVDD_2.5 DABLU2 DABLU3 DABLU4

P

R

HDATA1 HDATA0 IRQn IRQINn / GPIO8 DVDD_3.3 FSDATA47 DABLU0 DABLU1

R

T

RESETn DGND

FSCLK

DVDD_3.3 DVDD_2.5 FSDATA44 FSDATA45 FSDATA46

T

U

FSCKE FSWE FSCAS DVDD_2.5 DVDD_3.3 DVDD_3.3 DVDD_2.5 DVDD_3.3 DVDD_2.5 DVDD_3.3 DVDD_2.5 DVDD_3.3 DVDD_3.3 DVDD_2.5 DVDD_ 3.3 DVDD_2.5 DVDD_3.3 FSDATA41 FSDATA42 FSDATA43

U

V

FSRAS FSADDR13 FSADDR8 FSADDR5 FSADDR2 FSDATA0 FSDATA3 FSDATA6 FSDATA7 FSDATA10 FSDATA15 FSDQM2 FSDATA19 FSDATA22 FSDATA25 FSDATA28 FSDATA31 FSDATA34 FSDATA39 FSDATA40

V

W

FSADDR12 FSADDR10 FSADDR7 FSADDR4 FSADDR1 FSDATA1 FSDATA4 FSDQ M0 FSDATA8 FSDATA11 FSDATA14 FSDQM3 FSDATA18 FSDATA21 FSDATA24 FSDATA27 F SDATA30 FSDATA33 FSDATA36 FSDATA38

W

Y

FSADDR11 FSADDR9 FSADDR6 FSADD R3 FSADDR 0 FSDAT A2 FSDATA5 FSDQM1 FSDATA9 FSDATA12 FSDATA13 FSDATA16 FSDATA17 FSDATA20 FSDATA23 FSDATA26 FSDATA29 FSDATA32 FSDATA35 FSDATA37

Y

Genesis Microchip gm5060 / gm5060-H Data Sheet

February 2002 C5060-DAT-01G

6

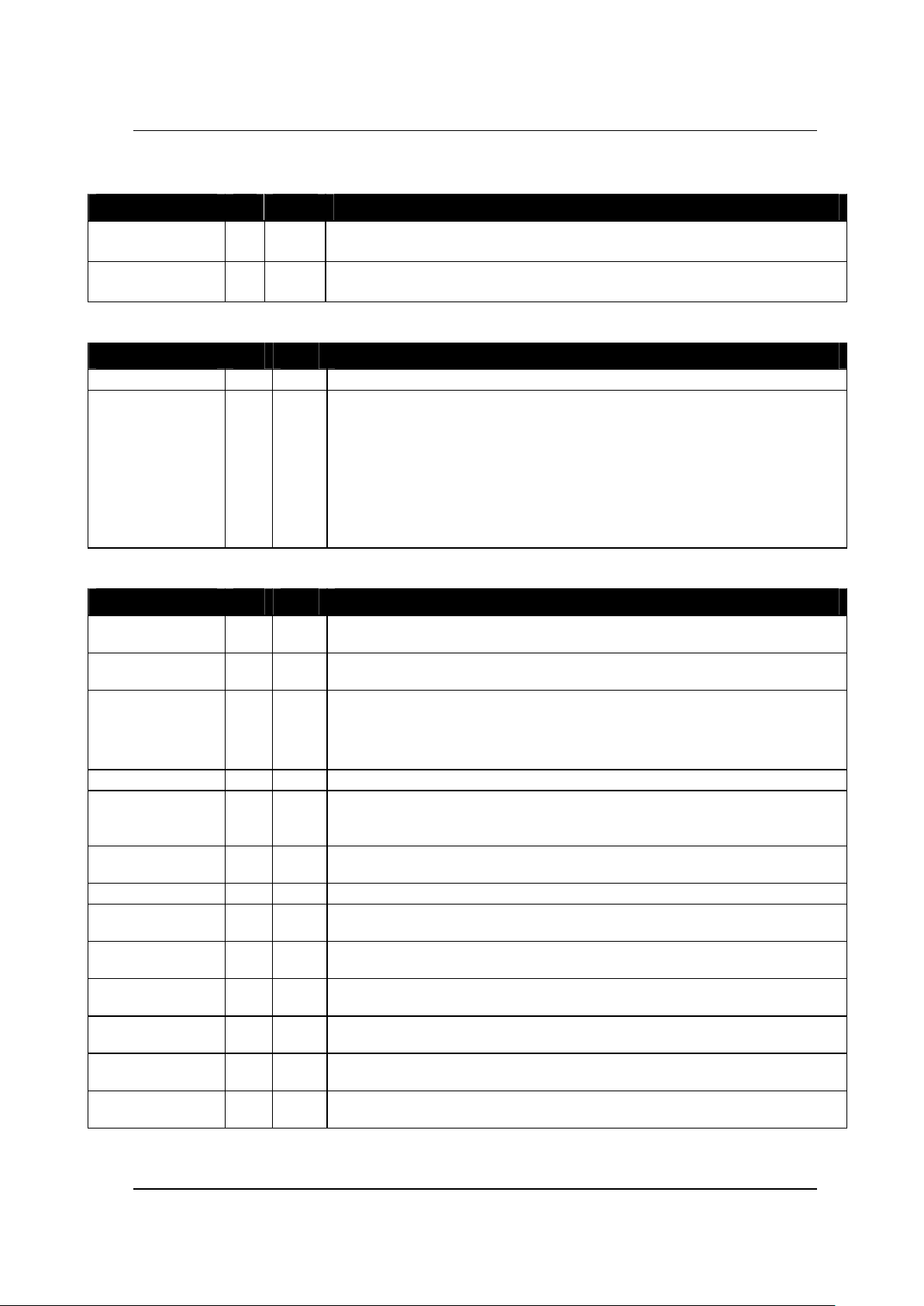

3. PIN LIST

I/O Legend: I = Input O = Output P = Power G= Ground

Table 1. ADC Signals

Name I/O Ball# Description

REXT I B10

External termination resistor. A 1% 1K ohm resistor must be connected from this pin to AVDD_3.3

(3.3V analog power supply). This termination resistor determines current references for both the DVI

receiver block and Analog HSYNC Delay block for both DVI and analog configurations.

RED+ I E1 Positive analog input for Red channel.

RED- I E2 Negative analog input for Red channel.

GREEN+ I D2 Positive analog input for Green channel.

GREEN- I D1 Negative analog input for Green channel.

BLUE+ I C1 Positive analog input for Blue channel.

BLUE- I C2 Negative analog input for Blue channel.

HSYNC I L2 ADC input horizontal sync or composite sync input.

[Input, schmitt trigger (400mV typical hysteresis), 5V-tolerant]

VSYNC I K1 ADC input vertical sync.

[Input, schmitt trigger (400mV typical hysteresis), 5V-tolerant]

Table 2. DVI Receiver Signals

Name I/O Ball# Description

REXT I B10

External termination resistor. A 1% 1K ohm resistor must be connected from this pin to AVDD_3.3

(3.3V analog power supply). This termination resistor determines current references for both the DVI

receiver block and Analog HSYNC Delay block for both DVI and analog configurations.

RX2+ I C10 DVI input channel 2 positive component; RED data and embedded CTL3

RX2- I D10 DVI input channel 2 negative component; RED data and embedded CTL3

RX1+ I C9 DVI input channel 1 positive component; GREEN data

RX1- I D9 DVI input channel 1 negative component; GREEN data

RX0+ I C8 DVI input channel 0 positive component; BLUE data

RX0- I D8 DVI input channel 0 negative component; BLUE data

RXC+ I C6 DVI input clock positive component

RXC- I D6 DVI input clock negative component

DDC_SCL I N2

For the gm5060-H (HDCP-enabled), this pin is used for DDC Interface for DVI-HDCP

communication. This is SCL for slave-only DDC communication.

[Input, Schmitt trigger (400mV typical hysteresis), 5V-tolerant]

For the gm5060 (non-HDCP), this pin is an unused CMOS input that may be left unconnected.

However, it is preferred that this pin be connected to a known logic state.

DDC_SDA IO N3

For the gm5060-H (HDCP-enabled), this pin is used for DDC Interface for DVI-HDCP

communication. This is SDA for slave-only DDC communication.

[Bidirectional, 4mA drive output, Schmitt trigger input (400mV typical hysteresis), 5V-tolerant]

For the gm5060 (non-HDCP), this pin is an unused CMOS input that may be left unconnected.

However, it is preferred that this pin be connected to a known logic state.

Genesis Microchip gm5060 / gm5060-H Data Sheet

February 2002 C5060-DAT-01G

7

Table 3. RCLK and FCLK PLL Signals

Name I/O Ball# Description

TCLK O J4 Feedback connection to crystal. If the reference clock source is a clock oscillator, this pin should be

grounded through a 2.7K pulldown resistor.

XTAL I H4 Crystal/oscillator input. For crystal, the frequency restrictions are: Min = 14MHz Max = 50MHz. For

oscillator, Min = 14 MHz, Max = 24 MHz [3.3V level]

Table 4. Video Input Port Signals

Name I/O Ball# Description

VCLK I A12 Input sample clock (27MHz) from video decoder. [Input, 5V-tolerant]

YUV7

YUV6

YUV5

YUV4

YUV3

YUV2

YUV1

YUV0

I B12

C12

A13

B13

C13

A14

B14

C14

Input YUV data in ITU-R BT656 format with embedded SAV and EAV.

These inputs feature internal pull-downs. Any external pull-ups used on these inputs should not exceed

10k ohms. Larger values run the risk of lowering the input high voltage to a value that would create

large currents in the input pads.

YUV(7:0) incorporate General Purpose Inputs (GPIs) . See Section 4.19.1.

[Input, 100KΩ pull-down, 5V-tolerant]

Table 5. Host Controller Interface Signals

Name I/O Ball# Description

HCLK / SCL I P1

Host Protocol input clock. HCLK for 6-wire nibble, SCL for 2-wire mode.

[Input, schmitt trigger (400mV typical hysteresis), 5V-tolerant]

HFSn / SDA IO P2

Host Protocol framing signal for 6-wire nibble mode. Also used as SDA (open drain) signal for 2-wire

mode. [Bidirectional, 4mA drive output, Schmitt trigger input (400mV typical hysteresis), 5V-tolerant]

HDATA3

HDATA2

HDATA1

HDATA0

IO P3

P4

R1

R2

Host Protocol data nibble for 6-wire mode. The upper nibble byte(3:0) is transferred first followed by

lower nibble byte(7:4).

[Bidirectional, 8mA drive output, Schmitt trigger input (400mV typical hysteresis), 5V-tolerant]

IRQn O R3

Interrupt output pin. May be active drive (active low) or open drain. [8mA drive, 5V-tolerant]

IRQINn / GPIO8 IO R4

Interrupt input to internal 8051 OCM is active low. OCM interrupt#0. This signal is also GPIO8.

Always open drain when in GPO mode.

[Bidirectional, schmitt trigger input (400mV typical hysteresis), 5V-tolerant, 8mA drive output]

RESETn I T1

Hardware Reset signals is active low.

[Input, schmitt trigger (400mV typical hysteresis), 5V-tolerant]

EXTCLK I L3

External clock. For test purposes only when Display DDS is unused. [Input, 5V-tolerant]

GPIO0 / PWM0 IO N1

General purpose input/output signal or PWM0. Open drain option via register bit.

[Bidirectional, 8mA drive output, Schmitt trigger input (400mV typical hysteresis0, 5V-tolerant]

GPIO1 / PWM1 IO M4

General purpose input/output signal or PWM1. Open drain option via register bit.

[Bidirectional, 8mA drive output, Schmitt trigger input (400mV typical hysteresis0, 5V-tolerant]

GPIO2 IO M3

General purpose input/output signals. Open drain option via register bit.

[Bidirectional, 8mA drive output, Schmitt trigger input (400mV typical hysteresis0, 5V-tolerant]

GPIO3 IO M2

General purpose input/output signals. Open drain option via register bit.

[Bidirectional, 8mA drive output, Schmitt trigger input (400mV typical hysteresis0, 5V-tolerant]

GPIO4 IO M1

General purpose input/output signals. Open drain option via register bit.

[Bidirectional, 8mA drive output, Schmitt trigger input (400mV typical hysteresis0, 5V-tolerant]

GPIO5 IO L1

General purpose input/output signals. Open drain option via register bit.

[Bidirectional, 8mA drive output, Schmitt trigger input (400mV typical hysteresis0, 5V-tolerant]

Genesis Microchip gm5060 / gm5060-H Data Sheet

February 2002 C5060-DAT-01G

8

Table 6. Display Port Signals

Name I/O Ball# Description

GPIO6 / DFSYNCn IO G18

GPIO6 by default. Open drain GPO option via register bit.

If DFSYNCn is register bit enabled, manual synchronization of display timing causes display timing to

jump to its H and V lock load location.

[Bidirectional, 8mA drive output, Schmitt trigger input (400mV typical hysteresis0, 5V-tolerant]

GPIO7 / DOVL IO G19

GPIO7 by default. Open drain GPO option via register bit.

If DOVL is register bit enabled, overlay valid display pixels are indicated by active DOVL.

[Bidirectional, 8mA drive output, Schmitt trigger input (400mV typical hysteresis0, 5V-tolerant]

DCLK O G20

Display output clock. [Tri-state output, programmable drive 0-24mA, not 5V-tolerant]

DVS O F19

Display vertical sync. [default = active high]

[Tri-state output, programmable drive 0-24mA, not 5V-tolerant]

DHS O F20

Display horizontal sync. [default = active high]

[Tri-state output, programmable drive 0-24mA, not 5V-tolerant]

DEN O F18

Display Enable frames the output background window.

[Tri-state output, programmable drive 0-24mA, not 5V-tolerant]

DARED7

DARED6

DARED5

DARED4

DARED3

DARED2

DARED1

DARED0

O H17

H18

H19

H20

J18

J19

J20

K18

Display output red data (even or left pixel).

[Tri-state output, programmable drive 0-24mA, not 5V-tolerant]

DAGRN7

DAGRN6

DAGRN5

DAGRN4

DAGRN3

DAGRN2

DAGRN1

DAGRN0

O K19

K20

L20

L19

L18

M20

M19

M18

Display output green data (even or left pixel).

[Tri-state output, programmable drive 0-24mA, not 5V-tolerant]

DABLU7

DABLU6

DABLU5

DABLU4

DABLU3

DABLU2

DABLU1

DABLU0

O N20

N19

N18

P20

P19

P18

R20

R19

Display output blue data (even or left pixel).

[Tri-state output, programmable drive 0-24mA, not 5V-tolerant]

DBRED7

DBRED6

DBRED5

DBRED4

DBRED3

DBRED2

DBRED1

DBRED0

O A15

B15

C15

A16

B16

C16

A17

B17

Display output red data (odd or right pixel).

[Tri-state output, programmable drive 0-24mA, not 5V-tolerant]

DBGRN7

DBGRN6

DBGRN5

DBGRN4

O C17

A18

B18

C18

Display output green data (odd or right pixel).

[Tri-state output, programmable drive 0-24mA, not 5V-tolerant]

Genesis Microchip gm5060 / gm5060-H Data Sheet

February 2002 C5060-DAT-01G

9

Name I/O Ball# Description

DBGRN3

DBGRN2

DBGRN1

DBGRN0

A19

A20

B19

B20

DBBLU7

DBBLU6

DBBLU5

DBBLU4

DBBLU3

DBBLU2

DBBLU1

DBBLU0

O C19

C20

D18

D19

D20

E18

E19

E20

Display output blue data (odd or right pixel).

[Tri-state output, programmable drive 0-24mA, not 5V-tolerant]

Table 7. Frame Store Interface Signals

Name I/O Ball# Description

FSCLK O T3 SDRAM clock. This signal is rising edge active.

[Tri-state output, Programmable Drive 0-24mA, not 5V-tolerant]

FSCKE O U1 SDRAM clock enable. This signal is active high.

[Tri-state output, 8mA drive, 5V-tolerant]

FSRAS O V1 SDRAM row address strobe. This signal is active low

[Tri-state output, 8mA drive, 5V-tolerant]

FSCAS O U3 SDRAM column address strobe. This signal is active low.

[Tri-state output, 8mA drive, 5V-tolerant]

FSWE O U2 SDRAM write enable. This signal is active low.

[Tri-state output, 8mA drive, 5V-tolerant]

FSDQM3

FSDQM2

FSDQM1

FSDQM0

O W12

V12

Y8

W8

SDRAM data masks. Each bit enables one of four SDRAM byte “lanes”. This allows host OSD access

to the SDRAM to be byte oriented. This signal is active high.

Bit 0 enables FSDATA(7:0).

Bit 1 enables FSDATA(15:8).

Bit 2 enables FSDATA(23:16).

Bit 3 enables FSDATA(31:24).

[Tri-state output, 8mA drive, 5V-tolerant]

FSADDR13

FSADDR12

FSADDR11

FSADDR10

FSADDR9

FSADDR8

FSADDR7

FSADDR6

FSADDR5

FSADDR4

FSADDR3

FSADDR2

FSADDR1

FSADDR0

IO V2

W1

Y1

W2

Y2

V3

W3

Y3

V4

W4

Y4

V5

W5

Y5

SDRAM multiplexed address bus.

FSADDR[13:0] are used for bootstrapping configuration. See Section 4.17.

[Bidirectional, 8mA drive output, 5V-tolerant]

Genesis Microchip gm5060 / gm5060-H Data Sheet

February 2002 C5060-DAT-01G

10

FSDATA47

FSDATA46

FSDATA45

FSDATA44

FSDATA43

FSDATA42

FSDATA41

FSDATA40

FSDATA39

FSDATA38

FSDATA37

FSDATA36

FSDATA35

FSDATA34

FSDATA33

FSDATA32

FSDATA31

FSDATA30

FSDATA29

FSDATA28

FSDATA27

FSDATA26

FSDATA25

FSDATA24

FSDATA23

FSDATA22

FSDATA21

FSDATA20

FSDATA19

FSDATA18

FSDATA17

FSDATA16

FSDATA15

FSDATA14

FSDATA13

FSDATA12

FSDATA11

FSDATA10

FSDATA9

FSDATA8

FSDATA7

FSDATA6

FSDATA5

FSDATA4

FSDATA3

FSDATA2

FSDATA1

FSDATA0

IO R18

T20

T19

T18

U20

U19

U18

V20

V19

W20

Y20

W19

Y19

V18

W18

Y18

V17

W17

Y17

V16

W16

Y16

V15

W15

Y15

V14

W14

Y14

V13

W13

Y13

Y12

V11

W11

Y11

Y10

W10

V10

Y9

W9

V9

V8

Y7

W7

V7

Y6

W6

V6

SDRAM data bus. Optionally programmable to 48 or 32 bits wide. Default is 32 bits wide.

[Bidirectional, 8mA drive output, 100KΩ pull-down, 5V-tolerant]

Genesis Microchip gm5060 / gm5060-H Data Sheet

February 2002 C5060-DAT-01G

11

Table 8. Power and Ground Signals

Group Name I/O Ball # Description

PLLGND G F3, G2, G4, H2, H3, J2, K3 Analog PLL / DDS Ground

PLLVDD_3.3 P F2, F4, G1, G3, H1, J1, J3 Analog PLL / DDS 3.3VDC Bypass to PLLGND (0.1uF)

AGND G A2, A3, A4, B1, B3, B4, C4, C5, C7, C11, D4, D5,

D7, D11, E4

Analog Ground

AVDD_2.5 P A6, A7, A8, A9, A10, A11 Analog 2.5VDC Supply Bypass to AGND (0.1uF)

AVDD_3.3 P B2, B6, B7, B8, B9, B11, C3, D3, E3 Analog 3.3VDC Supply Bypass to AGND (0.1uF)

DGND G H8, H9, H10, H11, H12, H13, J8, J9, J10, J11, J12,

J13, K8, K9, K10, K11, K12, K13, L8, L9, L10,

L11, L12, L13, M8, M9, M10, M11, M12, M13,

N8, N9, N10, N11, N12, N13, T2

Digital Ground (Periphery and Core Logic)

DVDD_2.5 P D17, D14, D12, F17, K4, K17, M17, N4, P17, T17,

U4, U7, U9, U11, U14, U16

Digital VDD, 2.5VDC (Core Logic. Bypass to DGND, 0.1uF)

DVDD_3.3 P D16, D15, D13, E17, G17, J17, L4, L17, N17, R17,

T4, U5, U6, U8, U10, U12, U13, U15, U17

Digital VDD, 3.3VDC (I/O pins. Bypass to DGND, 0.1uF)

Table 9. No Connects

Group Name I/O Ball # Description

N / C

- A1, A5, B5, F1, K2 No Connect. Leave these pins floating.

Genesis Microchip gm5060 / gm5060-H Data Sheet

February 2002 C5060-DAT-01G

12

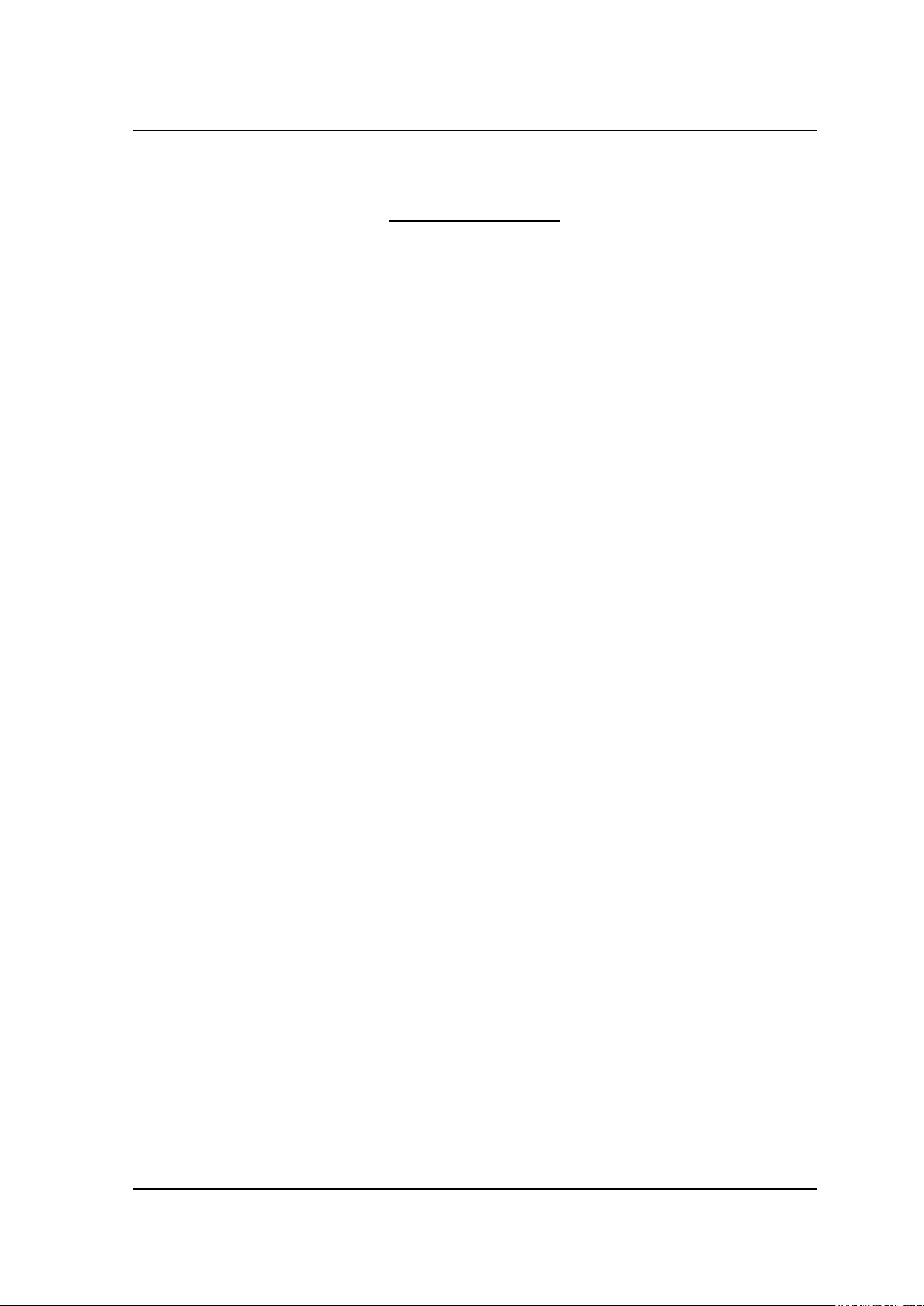

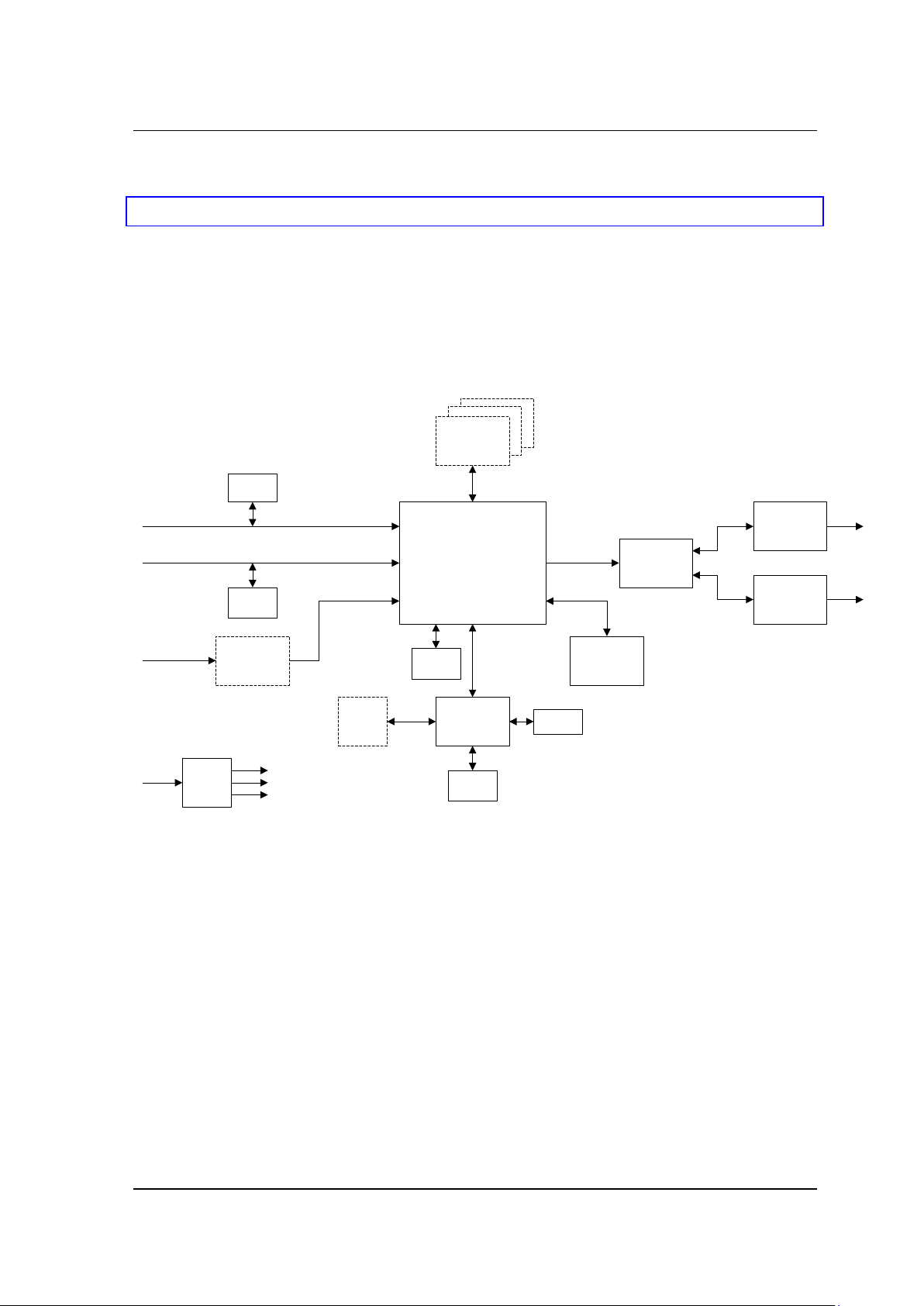

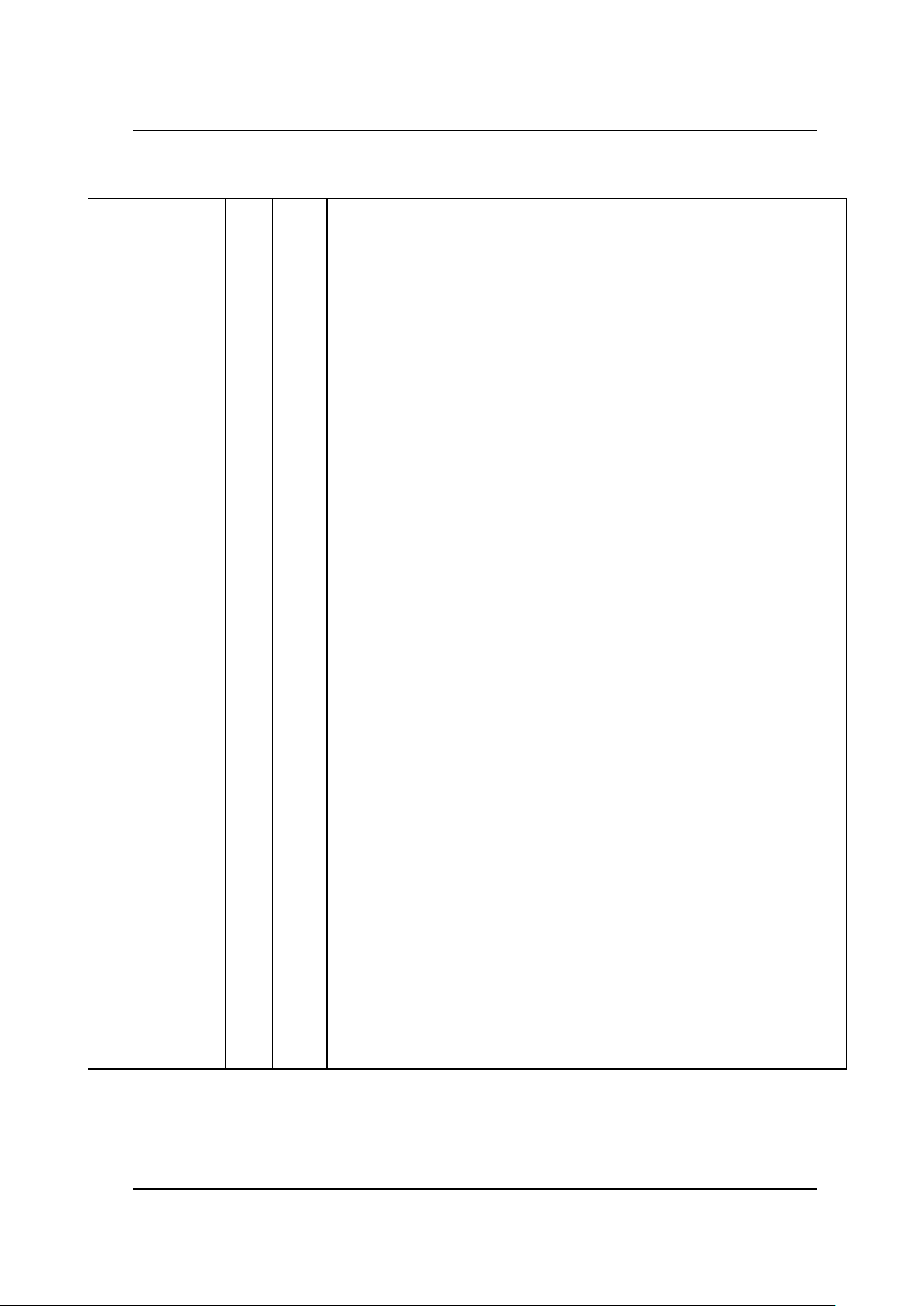

4. FUNCTIONAL DESCRIPTION

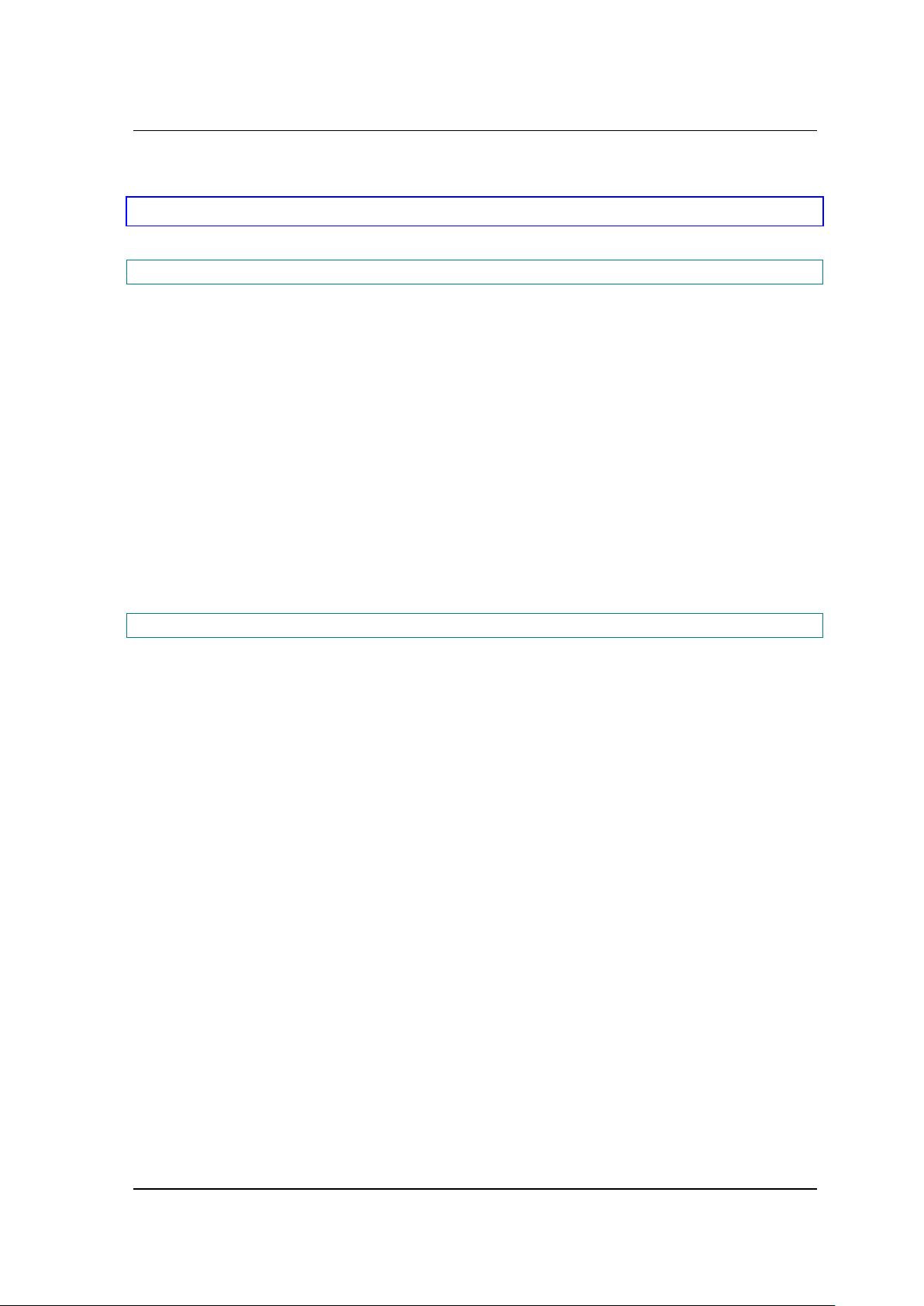

A functional block diagram is illustrated below. Each of the functional units shown is described

in the following sections.

Image

Capture

YUV

RealColor

Controls

RGB

Color

Controls

Frame Rate

Conversion

Zoom/

Shrink

Scaling

Triple

ADC

DVI

Rx

ITU656

Decoder

Gamma

Correction

LUT

HDCP

Image

Measurement

Display Timing

& Control

OSD

Frame

Store

Interface

Micro-

processor

(MCU)

Host

Interface

SDRAM

Interface

Analog

RGB

Digital

DVI

Digital YUV

Video

Serial

Interface

Panel

Interface

.

Clock

Recovery

Input

Color

LUT

(8-bits)

(24/48-bits)

Display

Clock

Generation

Figure 3. gm5060 Functional Block Diagram

Genesis Microchip gm5060 / gm5060-H Data Sheet

February 2002 C5060-DAT-01G

13

44..11 CClloocckkiinngg OOppttiioonnss

The gm5060 features four clock inputs:

1) Timing Clock (TCLK). This is a required clock used as a reference frequency source for

the gm5060. Additional clocks are synthesized internally using this reference. TCLK

may be connected to a crystal resonator or external oscillator and is further described

below.

2) DVI Differential Input Clock (RC+ and RC-). Provided by the external DVI interface.

3) Video Clock (VCLK) input pin. Provided by the external video decoder.

4) Host Interface Transfer Clock (HCLK for 6-Wire nibble; SCL for 2-wire serial). Provided

by the external micro controller (MCU).

4.1.1 TCLK Requirements

The TCLK may be generated using either a crystal resonator circuit (recommended) or an

external clock oscillator. The TCLK frequency should range between 14 and 50 MHz, though 24

MHz is preferred.

If TCLK is derived from a crystal resonator, an internal oscillator circuit generates a very low

jitter and low harmonic clock within the gm5060. The crystal should be connected between the

XTAL and TCLK pins and utilize appropriately sized loading capacitors. C

L1

and CL2 are

terminated to AVDD_33 to increase the power supply rejection ratio. This is shown in the

diagram below.

XTAL

TCLK

OSC_OUT

TCLK Distribution

gm5060

J4

H4

Vdd

180 uA

100 K

CL1

(5pF typ)

C

L2

(5pF typ)

AVDD_33

AVDD_33

Figure 4. TCLK connection (with Crystal Resonator)

The size of CL1 and CL2 are determined from the crystal manufacturer’s specification and the

parasitic capacitance of the gm5060 and PCB traces. To avoid start up problems with the internal

oscillator, the C

LOAD

parameter specified by the crystal manufacturer should not be exceeded.

C

LOAD

includes C

L1, CL2

as well as the parasitic capacitances. Specifically, these include the

Genesis Microchip gm5060 / gm5060-H Data Sheet

February 2002 C5060-DAT-01G

14

internal shunt capacitance between XTAL and TCLK (C

SHUNT

), the PCB board capacitance

(C

PCB

) and internal pin, pad and ESD protection capacitance. (C

PIN, CPAD

, C

ESD

)

XTAL

TCLK

gm5060

J4

H4

CL1

CL2

Internal Oscillator

CPCB

CSHUNT

CPCB

CPIN CPAD

CESD

CPIN CPAD CESD

AVDD_33

AVDD_33

Figure 5. TCLK parasitic capacitances

C

LOAD

= C

SHUNT

+ ((C

LOAD1

* C

LOAD2

) / (C

LOAD1

+ C

LOAD2

))

Where

C

LOAD1

= CL1 + C

PCB

+ C

PIN

+ C

PAD

+ C

ESD

C

LOAD2

= C

LOAD1

(i.e., CL2 = CL1)

The following values can be used for the gm5060:

C

SHUNT

~ 9pF

C

ESD

~ 5.3 pF

C

PAD

~ 1 pF

C

PIN

~ 1.1 pF

C

PCB

is layout dependent (usually 2 to 10 pF)

In addition to the above requirement, the crystal should be a parallel resonate cut and the

equivalent series resistance must be less than 90 ohms. If the equivalent series resistance is

greater than 90 ohms, the oscillator may not start. In this case, the internal oscillator gain may be

increased by adding a 2.2 kohm resistor from TCLK pin to ground.

Genesis Microchip gm5060 / gm5060-H Data Sheet

February 2002 C5060-DAT-01G

15

XTAL

TCLK

OSC_OUT

TCLK Distribution

gm5060

J4

H4

Vdd

180 uA

100 K

CL1

CL2

AVDD_33

AVDD_33

2.2 K or Larger

Optional Resistor

Figure 6. TCLK connection (with Optional Resistor)

If TCLK is derived from an external oscillator, the applied signal should be made to the XTAL

pin. A 2.7 kohm resistor from the TCLK pin to ground provides additional bias to keep the clock

symmetrical.

XTAL

TCLK

14 to 24 MHz

DVDD_33

J4

H4

gm5060

Vdd

180 uA

100 K

Oscillator

2.7 K

OSC_OUT

TCLK Distribution

Figure 7. TCLK connection (with Oscillator)

Genesis Microchip gm5060 / gm5060-H Data Sheet

February 2002 C5060-DAT-01G

16

4.1.2 Synthesized Clocks

The gm5060 synthesizes all additional clocks internally: Clock inputs to the DDDS and FCLK

PLL (as shown in the figure below) are selected via a host interface register.

Note that even when the system is designed without a frame store interface, an internally

synthesized frame store clock (FS_CLK) is required to clock data in and out of internal FIFOs.

DVI

ITU-656

SDDS

HSYNC

VCLK

CLK-

VCLK

DCLK

EXT_CLK

IP_CLK

TCLK

RCLK

PLL

FCLK

PLL

DDDS

/ 2

OCM_CLK

DP_CLK

FS_CLK

RCLK

IFM_CLK

/ 2

DVI_CLK

CLK+

RCLKRCLK

Notes: RCLK nominally ~200 MHz;

SDDS=Source Direct Digital Synthesis

DDDS = Display Direct Digital Synthesis

Figure 8. Internal Clock Sources

Genesis Microchip gm5060 / gm5060-H Data Sheet

February 2002 C5060-DAT-01G

17

44..22 HHaarrddwwaarree aanndd SSooffttwwaarree RReesseettss

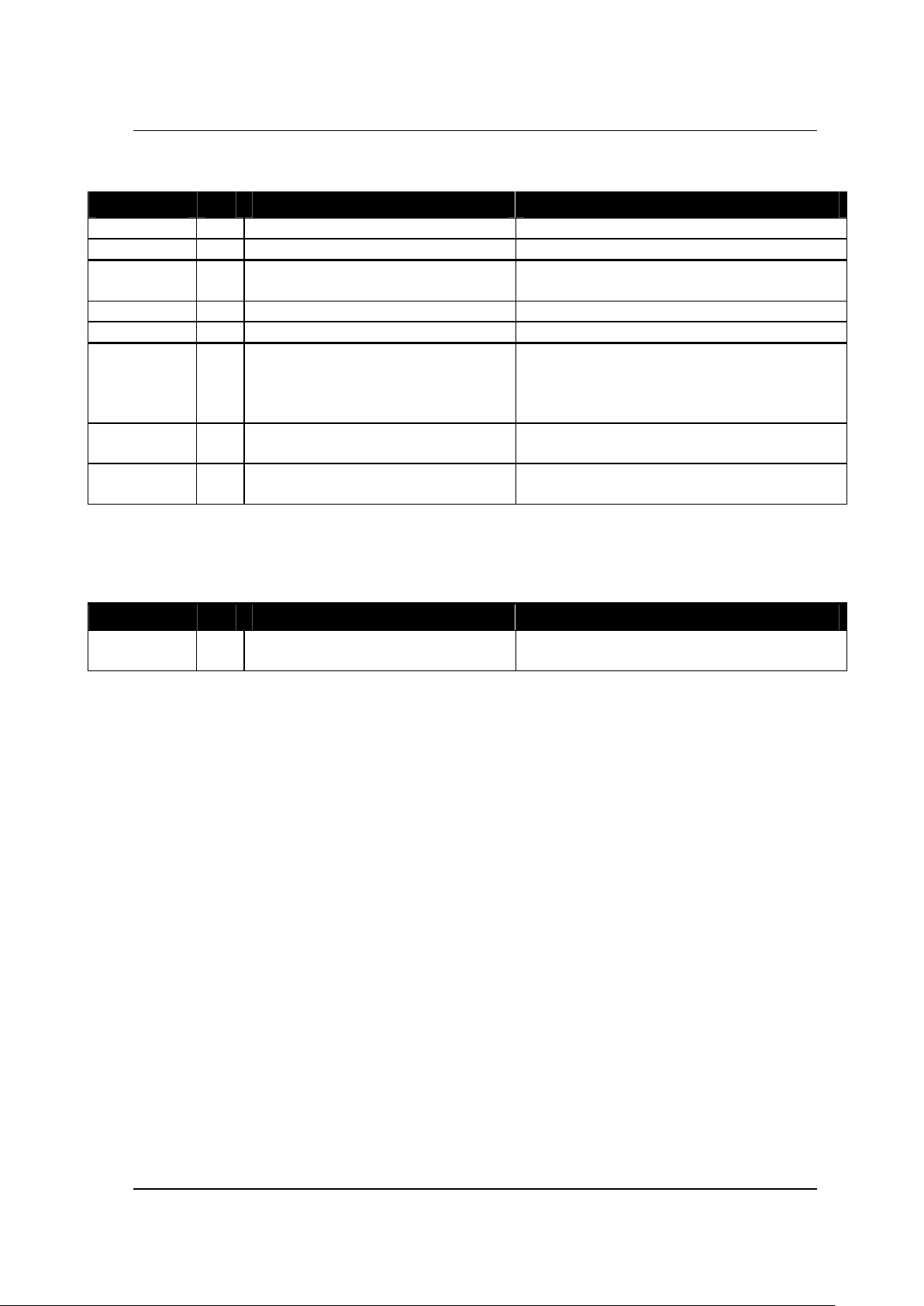

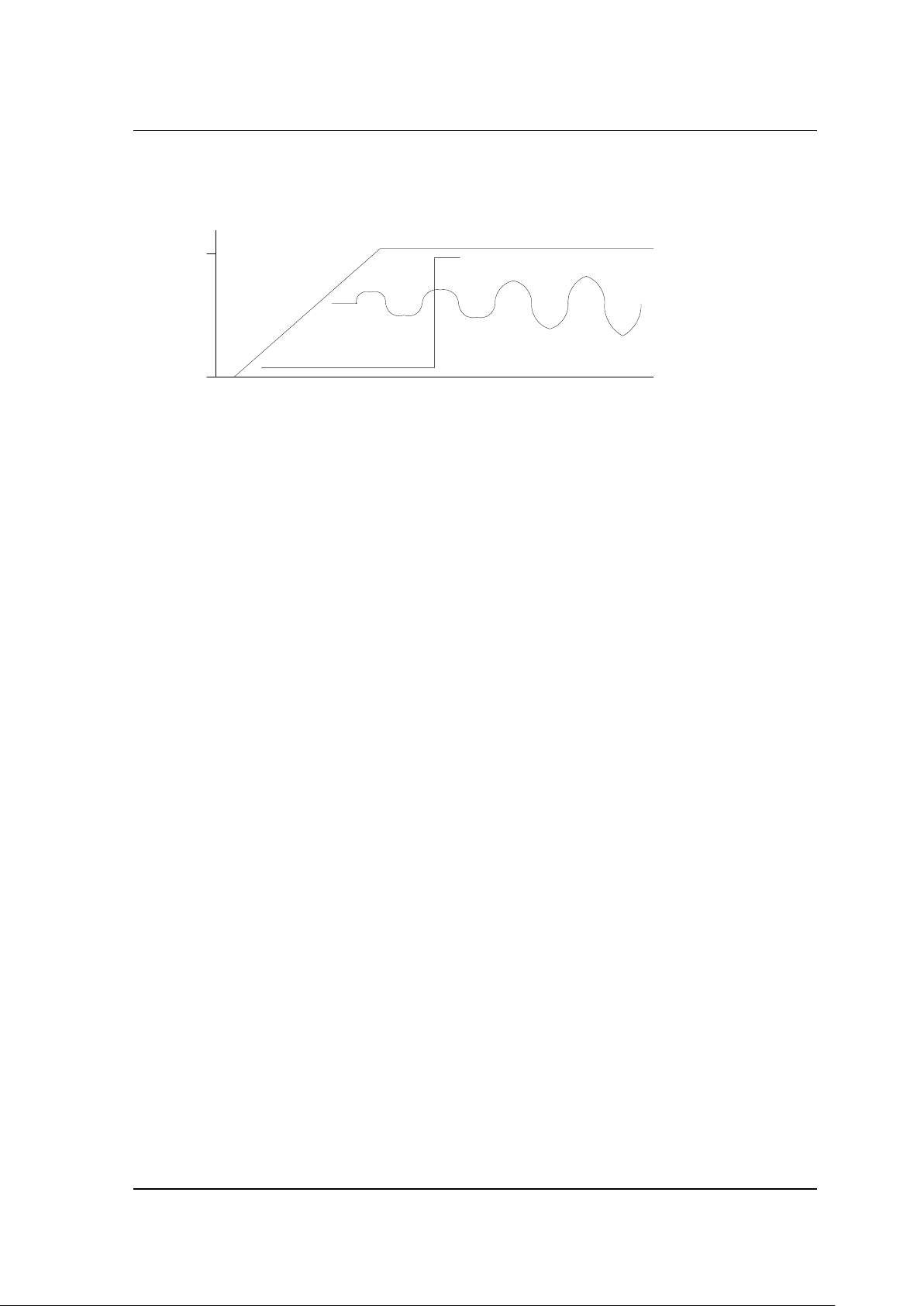

4.2.1 Hardware Reset

Hardware Reset is performed by holding the RESETn pin low for a minimum of 1µs after the

supply voltages are stable, as illustrated in Figure 9. A TCLK input (see Clock Options above)

must be applied during and after the reset. When the reset period is complete and RESETn is deasserted, the gm5060 follows an internal power up sequence:

1. All registers of all types are reset to their default state

2. Each clock domain is internally reset. The reset period remains asserted for 64 local clock

domain cycles following the de-assertion of RESETn.

3. The OCM_CLK domain operates at the T_CLK frequency during this period.

4. The RCLK PLL internally produces a 10x output clock (from TCLK reference).

5. The IC will wait for RCLK PLL to Lock and then switch the OCM_CLK to the bootstrap

selected clock.

6. The OCM will begin operating if bootstrapped to start operation after Hardware Reset,

otherwise it remains in reset until register enabled.

4.2.2 Software Reset

Software Reset is performed by programming the HOST_CONTROL register bit SOFT_RESET

= ’0’. The SOFT_RESET bit will self clear to ‘0’ upon completion of reset. The following

internal operations occur with software reset:

1. All active and status registers (i.e. the active part of PA bits, and CRO and RO bits unless

otherwise indicated) are reset to their default state. Pending and read/write registers remain

unaffected. PA, CRO, and RO bits are defined below:

PA Pending and active read write bit. Two registers are used to store these bits: a pending register and

an active register. The pending register is transferred to the active register on an update event. The

clock domain for each PA register is indicated within square brackets ‘[ ]’ in the register listing (e.g. the

active part of register 0x1B6 DISPLAY_CONTROL PA [DP_CLK] will be updated on an update event

synchronized to the rising edge of DP_CLK.)

Only the active register contents affect chip functionality. The active register bits are cleared to ‘0’,

unless otherwise specified, by software or hardware reset. The pending register bits are only cleared

by a hardware reset, and may be overwritten at any time.

CRO Clearable read only status bit. These are read only registers that may be cleared to ‘0’ when

overwritten with a ‘1’. This type is most commonly used for interrupt status registers. These are

cleared to ‘0’ by both software and hardware reset.

RO Read only status bit. These are read only registers. No effect to the chip will occur if an attempt is

made to write to these bits

2. Each clock domain in the gm5060 is internally reset for 64 local clock domain cycles, before

returning to normal operation.

Software Reset will NOT reset the analog components of the RCLK PLL, FCLK PLL, SDDS,

DDDS, DVI, or ADC blocks. Software reset does not affect the IFM.

Genesis Microchip gm5060 / gm5060-H Data Sheet

February 2002 C5060-DAT-01G

18

0 Volts

3.3 Volts

time

gm5060 Supply Voltage Ramp

Oscillator Startup

Reset Signal

Reset is to be held low until after

Supply voltage is stable

Figure 9. Hardware Reset

Loading...

Loading...