Genesis gm2121 Datasheet

Genesis Microchip Publication

PRELIMINARY DATA SHEET

gm2121

SXGA LCD Monitor Controller with

Integrated Analog Interface and Dual

LVDS Transmitter

Publication Number: C2121-DAT-01F

Publication Date: December 2002

Genesis Microchip Inc.

165 Commerce Valley Dr. West • Thornhill • ON • Canada • L3T 7V8 • Tel: (905) 889-5400 • Fax: (905) 889-5422

2150 Gold Street • PO Box 2150 • Alviso • CA • USA • 95002 • Tel: (408) 262-6599 • Fax: (408) 262-6365

143-37 Hyundai Tower • Unit 902 • Samsung-dong • Kangnam-gu • Seoul • Korea • 135-090 • Tel: (82-2) 553-5693 • Fax: (82-2) 552-4942

4F, No. 24, Ln 123, Sec 6, Min-Chung E. Rd. • Taipei • Taiwan • Tel: (2) 2791-0118 • Fax: (2) 2791-0196

www.genesis-microchip.com / info@genesis-microchip.com

.com

The following are trademarks or registered trademarks of Genesis Microchip, Inc.:

GenesisTM, Genesis Display PerfectionTM, ESMTM, RealColorTM, Ultra-Reliable DVITM, Real RecoveryTM, SageTM, JagASMTM,

TM

SureSync

, Adaptive Backlight Control™, FaroudjaTM, DCDiTM, TrueLifeTM, IntelliCombTM

Other brand or product names are trademarks of their respective holders.

© Copyright 2002 Genesis Microchip Inc. All Rights Reserved.

Genesis Microchip Inc. reserves the right to change or modify the information contained herein without notice. It is

the customer’s responsibility to obtain the most recent revision of the document. Genesis Microchip Inc. makes no

warranty for the use of its products and bears no responsibility for any errors or omissions that may appear in this

document.

gm2121 Preliminary Data Sheet

Table Of Contents

1 Overview ........................................................................................................................................8

1.1 gm2121 System Design Example..........................................................................................8

1.2 gm2121 Features ...................................................................................................................9

2 GM2121 Pinout............................................................................................................................10

3 GM2121Pin List...........................................................................................................................11

4 Functional Description .................................................................................................................16

4.1 Clock Generation.................................................................................................................16

4.1.1 Using the Internal Oscillator with External Crystal ........................................................17

4.1.2 Using an External Clock Oscillator.................................................................................19

4.1.3 Clock Synthesis...............................................................................................................20

4.2 Chip Initialization................................................................................................................21

4.2.1 Hardware Reset ...............................................................................................................21

4.2.2 Correct Power Sequencing ..............................................................................................22

4.3 Analog to Digital Converter ................................................................................................22

4.3.1 ADC Pin Connection.......................................................................................................23

4.3.2 ADC Characteristics........................................................................................................23

4.3.3 Clock Recovery Circuit...................................................................................................24

4.3.4 Sampling Phase Adjustment............................................................................................25

4.3.5 ADC Capture Window ....................................................................................................25

4.4 Test Pattern Generator (TPG)..............................................................................................26

4.5 Input Format Measurement .................................................................................................26

4.5.1 HSYNC / VSYNC Delay ................................................................................................27

4.5.2 Horizontal and Vertical Measurement ............................................................................28

4.5.3 Format Change Detection................................................................................................28

4.5.4 Watchdog ........................................................................................................................28

4.5.5 Internal Odd/Even Field Detection (For Interlaced Inputs to ADC Only) ......................28

4.5.6 Input Pixel Measurement ................................................................................................29

4.5.7 Image Phase Measurement..............................................................................................29

4.5.8 Image Boundary Detection..............................................................................................29

4.5.9 Image Auto Balance ........................................................................................................29

4.6 RealColorTM Digital Color Controls....................................................................................29

4.6.1 RealColor™ Flesh tone Adjustment ...............................................................................30

4.6.2 Color Standardization and sRGB Support.......................................................................30

4.7 High-Quality Scaling...........................................................................................................30

4.7.1 Variable Zoom Scaling....................................................................................................30

C2121-DAT-01F 3 December 2002

http://www.genesis-microchip.com

gm2121 Preliminary Data Sheet

4.7.2 Horizontal and Vertical Shrink........................................................................................30

4.8 Bypass Options....................................................................................................................30

4.9 Gamma LUT........................................................................................................................31

4.10 Display Output Interface .....................................................................................................31

4.10.1 Display Synchronization.............................................................................................31

4.10.2 Programming the Display Timing ..............................................................................31

4.10.3 Panel Power Sequencing (PPWR, PBIAS).................................................................33

4.10.4 Output Dithering .........................................................................................................33

4.11 Dual Four Channel LVDS Transmitter ...............................................................................34

4.12 Energy Spectrum Management (ESM)................................................................................34

4.13 OSD .....................................................................................................................................34

4.13.1 On-Chip OSD SRAM .................................................................................................35

4.13.2 Color Look-up Table (LUT) .......................................................................................36

4.14 On-Chip Microcontroller (OCM) ........................................................................................36

4.14.1 Standalone Configuration ...........................................................................................37

4.14.2 Full-Custom Configuration.........................................................................................38

4.14.3 In-System-Programming (ISP) of FLASH ROM Devices .........................................39

4.14.4 UART Interface ..........................................................................................................39

4.14.5 DDC2Bi Interface .......................................................................................................40

4.14.6 General Purpose Inputs and Outputs (GPIO’s)...........................................................40

4.15 Bootstrap Configuration Pins ..............................................................................................41

4.16 Host Interface ......................................................................................................................42

4.16.1 Host Interface Command Format................................................................................42

4.16.2 2-wire Serial Protocol .................................................................................................43

4.17 Miscellaneous Functions .....................................................................................................44

4.17.1 Low Power State.........................................................................................................44

4.17.2 Pulse Width Modulation (PWM) Back Light Control................................................45

5 Electrical Specifications ...............................................................................................................46

5.1 Preliminary DC Characteristics...........................................................................................46

5.2 Preliminary AC Characteristics...........................................................................................48

5.3 External ROM Interface Timing Requirements ..................................................................49

6 Ordering Information ...................................................................................................................50

7 Mechanical Specifications............................................................................................................51

C2121-DAT-01F 4 December 2002

http://www.genesis-microchip.com

gm2121 Preliminary Data Sheet

List Of Tables

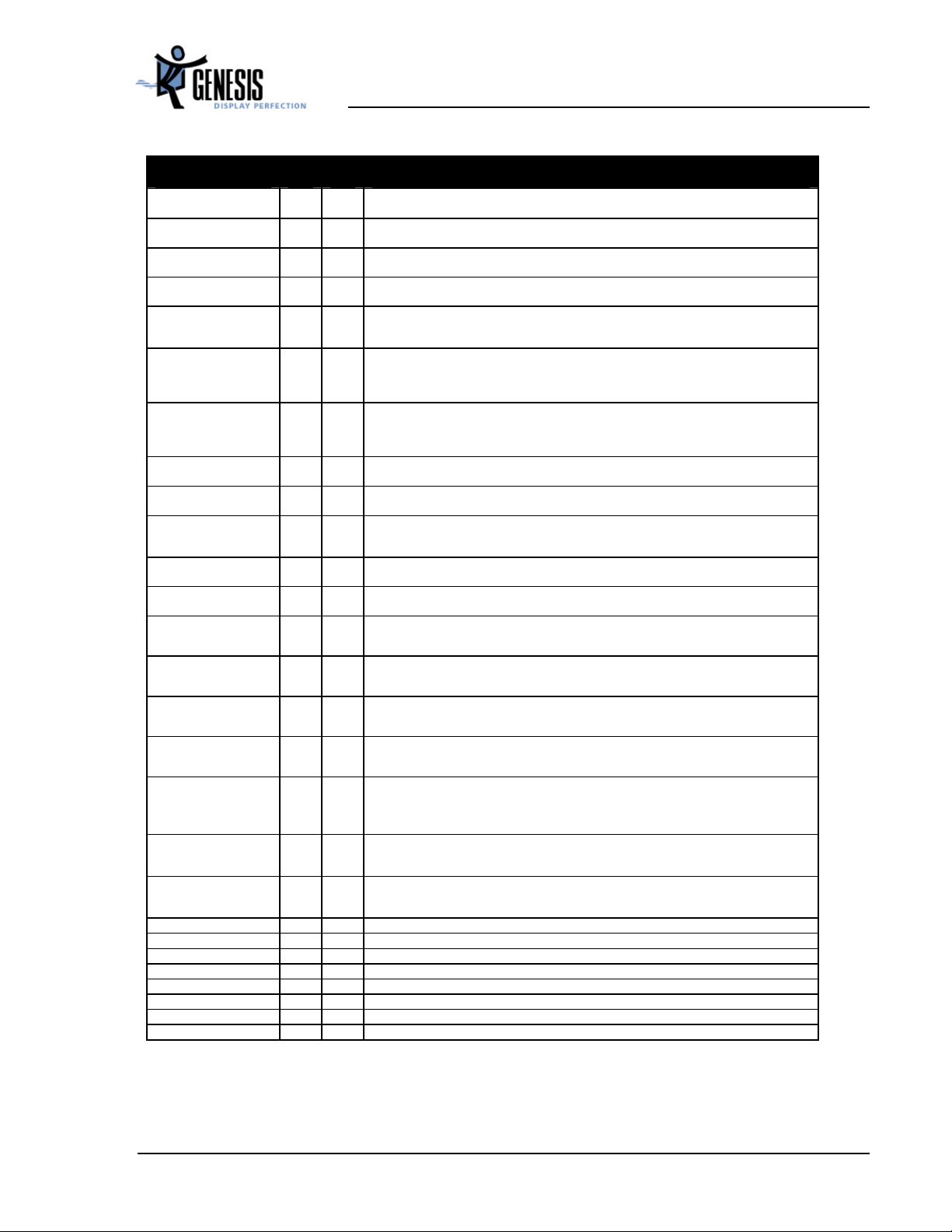

Table 1. Analog Input Port ................................................................................................................11

Table 2. RCLK PLL Pins ..................................................................................................................11

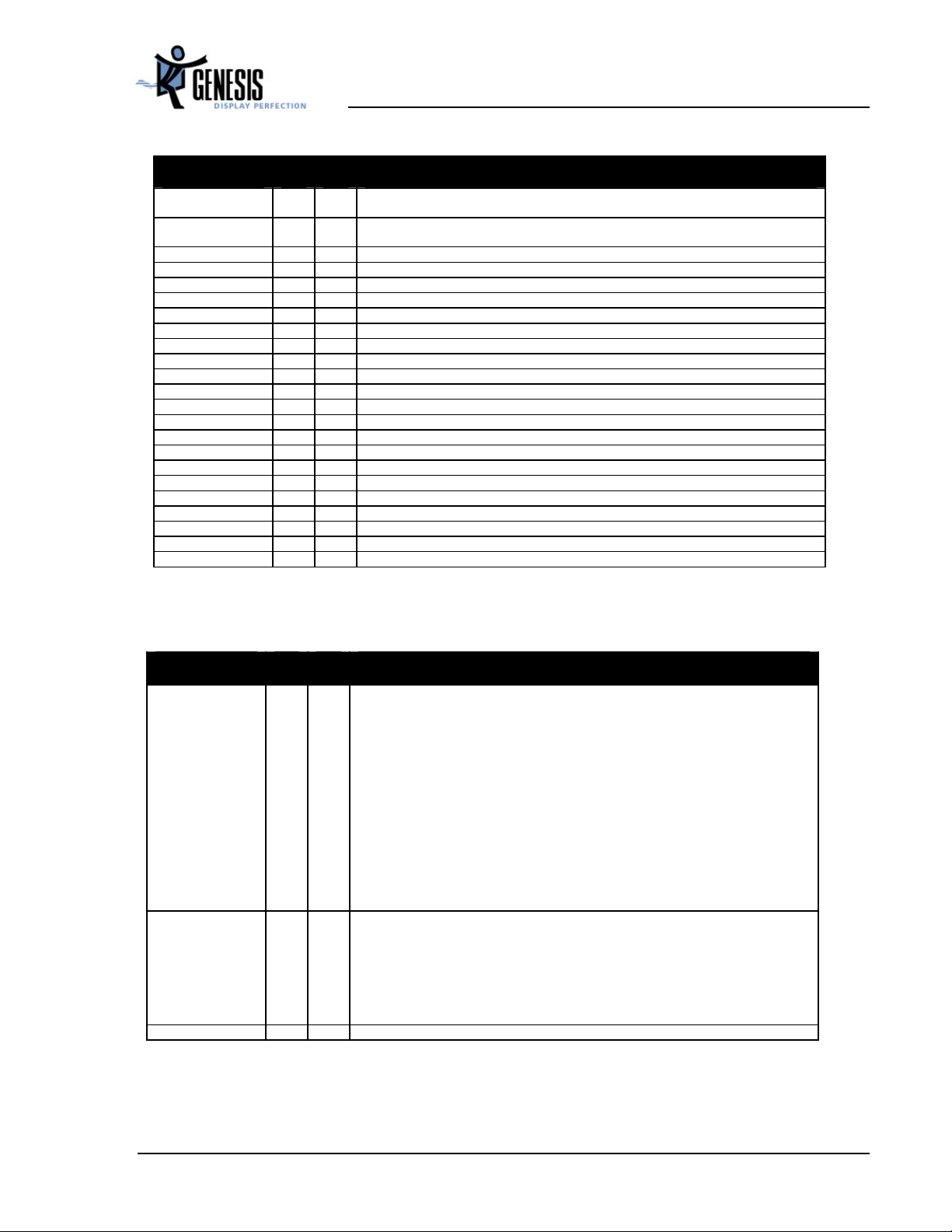

Table 3. System Interface and GPIO Signals ....................................................................................12

Table 4. Display Output Port.............................................................................................................13

Table 5. Parallel ROM Interface Port................................................................................................13

Table 6. Reserved Pins ...................................................................................................................14

Table 7. Power and Ground Pins for ADC Sampling Clock DDS ....................................................14

Table 8. Power and Ground Pins for Display Clock DDS ................................................................14

Table 9. I/O Power and Ground Pins.................................................................................................15

Table 10. Power and Ground Pins for LVDS Transmitter ..............................................................15

Table 11. TCLK Specification ........................................................................................................19

Table 12. Pin Connection for RGB Input with HSYNC/VSYNC...................................................23

Table 13. ADC Characteristics........................................................................................................24

Table 14. Supported LVDS 24-bit Panel Data Mapping.................................................................34

Table 15. Supported LVDS 18-bit Panel Data Mapping.................................................................34

Table 16. gm2121 GPIOs and Alternative Functions .....................................................................41

Table 17. Bootstrap Signals.............................................................................................................41

Table 18. Instruction Byte Map.......................................................................................................43

Table 19. Absolute Maximum Ratings............................................................................................46

Table 20. DC Characteristics...........................................................................................................47

Table 21. Maximum Speed of Operation ........................................................................................48

Table 22. Display Timing and DCLK Adjustments........................................................................48

Table 23. 2-Wire Host Interface Port Timing .................................................................................48

C2121-DAT-01F 5 December 2002

http://www.genesis-microchip.com

gm2121 Preliminary Data Sheet

List Of Figures

Figure 1. gm2121 System Design Example......................................................................................8

Figure 2. gm2121 Pin Out Diagram ...............................................................................................10

Figure 3. gm2121 Functional Block Diagram ................................................................................16

Figure 4. Using the Internal Oscillator with External Crystal ........................................................17

Figure 5. Internal Oscillator Output................................................................................................18

Figure 6. Sources of Parasitic Capacitance.....................................................................................18

Figure 7. Using an External Single-ended Clock Oscillator...........................................................19

Figure 8. Internally Synthesized Clocks .........................................................................................20

Figure 9. On-chip Clock Domains..................................................................................................21

Figure 10. Correct Power Sequencing ..............................................................................................22

Figure 11. Example ADC Signal Terminations................................................................................23

Figure 12. gm2121 Clock Recovery .................................................................................................24

Figure 13. ADC Capture Window ....................................................................................................25

Figure 14. Some of gm2121 built-in test patterns ............................................................................26

Figure 15. Factory Calibration and Test Environment .....................................................................26

Figure 16. HSYNC Delay.................................................................................................................27

Figure 17. Active Data Crosses HSYNC Boundary .........................................................................27

Figure 18. ODD/EVEN Field Detection...........................................................................................28

Figure 19. RealColorTM Digital Color Controls................................................................................29

Figure 20. Display Windows and Timing.........................................................................................32

Figure 21. Single Pixel Width Display Data.....................................................................................32

Figure 22. Double Pixel Wide Display Data ....................................................................................33

Figure 23. Panel Power Sequencing .................................................................................................33

Figure 24. OSD Cell Map .................................................................................................................35

Figure 25. OCM Full-Custom and Standalone Configurations ........................................................37

Figure 26. Programming OCM in Standalone Configuration...........................................................38

Figure 27. Programming the OCM in Full-Custom Configuration ..................................................39

Figure 28. 2-Wire Protocol Data Transfer ........................................................................................43

Figure 29. 2-Wire Write Operations (0x1x and 0x2x)......................................................................44

Figure 30. 2-Wire Read Operation (0x9x and 0xAx) .......................................................................44

Figure 31. External ROM Interface Timing Diagram ......................................................................49

Figure 32. gm2121 160-pin PQFP Mechanical Drawing ................................................................51

C2121-DAT-01F 6 December 2002

http://www.genesis-microchip.com

gm2121 Preliminary Data Sheet

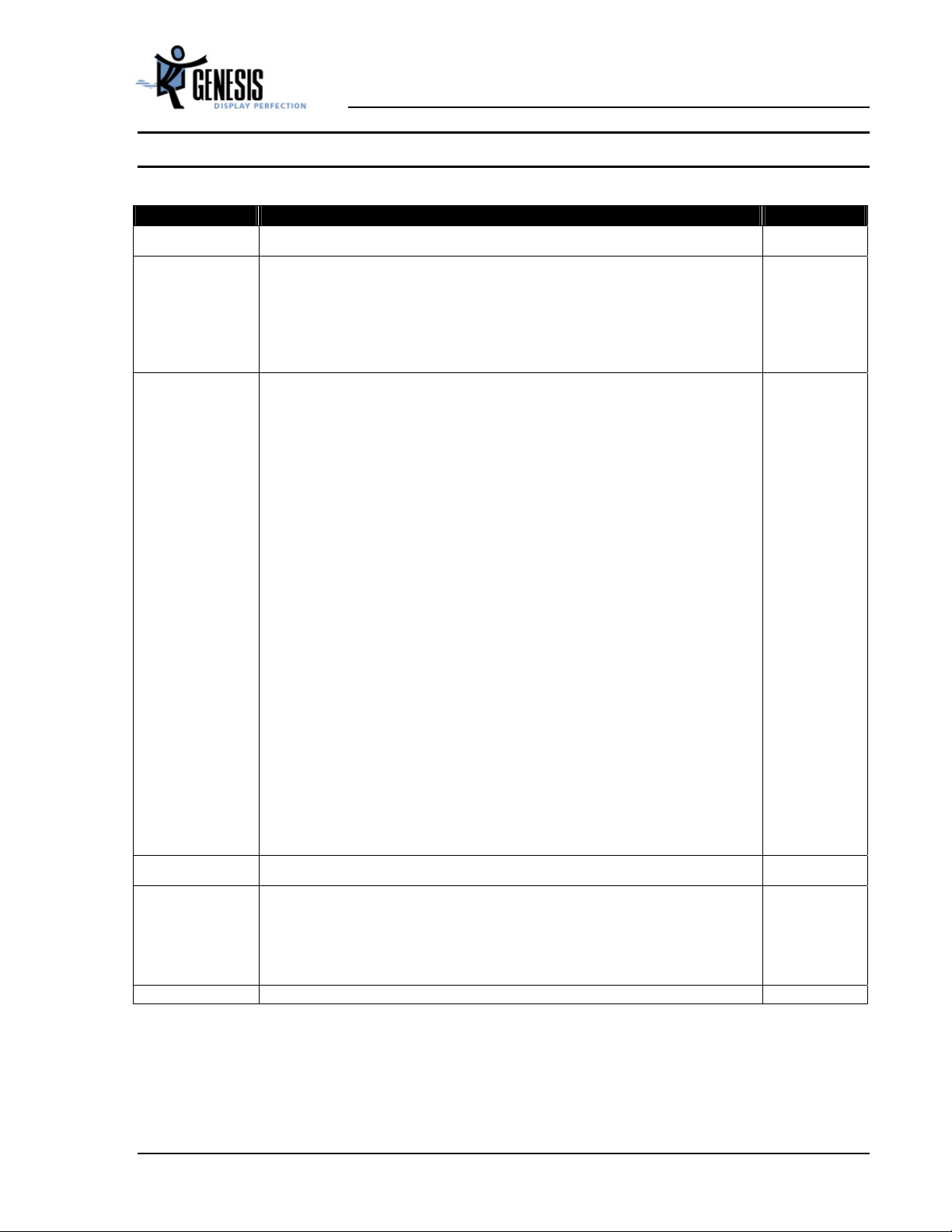

Revision History

Document Description Date

C2121-DAT-01A

C2121-DAT-01B

C2121-DAT-01C

• Initial release

• Corrected Pin out changes as follows:

o Figure 2, gm2121 Pin out Diagram (Pin #102 to 116)

o Table 2, RCLK PLL pins

o Table 7, Power & Ground Pins for ADC Sampling Clock DDS

o Table 8, Power & Ground Pins for Display Clock DDS

o Table10, AVSS_OUT_LV_E pin

o Table 6, one RESERVED pin and two RESERVED Pin name change to

VCO_LV & VBUFC

• Corrected Pinout as follows:

• Pins 88 to 97 changed from RESERVED to GPO [0..7]

• Pins 38 and 39 changed to STI_TM1 and STI_TM2

• Table 3, added GPO [0..7]

• Table 6, removed RESERVED pins 88 to 97

• Table 6, renamed pins 38 and 39 to STI_TM1 and STI_TM2 and added a clause that

these pins MUST be tied to GND.

• Updated 4.14.4. with TCLK_SEL0, TCLK_SEL1 and DDC_PORT_SEL information.

These signals are new bootstrap configuration pins in gm2121

• Updated 4.14.5 with the newly added GPO’s [0..7]

• Updated 4.15 with the new bootstrap configuration pins

• Table 20, updated DC Characteristics

• Updated 4.14.4 and 4.15 with clarifications for the UART baud rates and DDC2Bi pin

selection options in standalone configuration

• Changed Pin names:

o RVDD to RVDD_3.3

o CVDD to CVDD_2.5

o AVDD_OUT_LV_E to AVDD_OUT_LV_E_2.5

o AVDD_LV_E_ to AVDD_LV_E_2.5

o AVDD_OUT_LV_O to AVDD_OUT_LV_O_2.5

o AVDD_LV_O to AVDD_LV_O_2.5

o AVDD_RPLL to AVDD_RPLL_3.3

o VDD_DPLL to VDD_DPLL_3.3

o AVDD_DDDS to AVDD_DDDS_3.3

o VDD_DDDS to VDD_DDDS_3.3

o AVDD_SSDS to AVDD_SSDS_3.3

o VDD_SSDS to VDD_SSDS_3.3

o VDD2_ADC to VDD2_ADC_2.5

o VDD1_ADC to VDD1_ADC_2.5

o AVDD_ADC to AVDD_ADC_3.3

o AVDD_BLUE to AVDD_BLUE_3.3

o AVDD_GREEN to AVDD_GREEN_3.3

o AVDD_RED to AVDD_RED_3.3

May 2002

Jun 2002

Aug 2002

C2121-DAT-01D

C2121-DAT-01E

C2121-DAT-01F

C2121-DAT-01F 7 December 2002

• Added Section 4.2.2 – Correct Power Sequencing

•

Added the following note to Table 3 System Interface/GPIO signals GPIO4/UART_DI

and GPIO5/UART_DO: Add 10K Pull-up to VDD_3.3

• Added note to Table 17 bootstrap signal HOST_PORT_EN (ROM_ADDR8)

• Added note to Table 17 bootstrap signal OCM_ROM_CNFG(1) (ROM_ADDR14)

• Updated Table 17 bootstrap signal DDC_PORT_SEL (ROM_ADDR12)

• Documentation Fix: Pin Name Change GPIO16/HFS to GPIO16/HFSn

• Added section 5.3 External ROM Interface Timing Requirements

http://www.genesis-microchip.com

Sep 2002

Oct 2002

Dec 2002

p

gm2121 Preliminary Data Sheet

1 Overview

The gm2121 is a graphics processing IC for Liquid Crystal Display (LCD) monitors at SXGA resolution.

It provides all key IC functions required for the highest quality LCD monitors. On-chip functions include

a high-speed triple-ADC and PLL, a high quality zoom and shrink scaling engine, an on-screen display

(OSD) controller, digital color controls, an on-chip micro-controller (OCM) and industry standard dual

four channel LVDS transmitter for direct connect to LCD panels with LVDS interface. With this level of

integration, the gm2121 devices simplify and reduce the cost of LCD monitors while maintaining a highdegree of flexibility and quality.

1.1 gm2121 System Design Example

Figure 1 below shows a typical dual interface LCD monitor system based on the gm2121. Designs based

on the gm2121 have reduced system cost, simplified hardware and firmware design and increased

reliability because only a minimal number of components are required in the system.

Analog

RGB

gm2121

Direct

Connect to

LVDS IF

Panels

LCD Module

Back-light

NVRAM

Figure 1. gm2121 System Design Example

EEPROM

(o

tional)

C2121-DAT-01F 8 December 2002

http://www.genesis-microchip.com

1.2 gm2121 Features

gm2121 Preliminary Data Sheet

FEATURES

• Zoom (from VGA) and shrink (from UXGA) scaling

• Integrated 8-bit triple-channel ADC / PLL

• Embedded microcontroller with parallel ROM interface

• On-chip versatile OSD engine

• All system clocks synthesized from a single external crystal

• Programmable gamma correction (CLUT)

• RealColor controls provide sRGB compliance

• PWM back light intensity control

• 5-Volt tolerant inputs

• Low EMI and power saving features

High-Quality Advanced Scaling

• Fully programmable zoom ratios

• High-quality shrink capability from UXGA resolution

• Real Recovery function provides full color recovery image

for refresh rates higher than those supported by the LCD

panel

Analog RGB Input Port

• Supports up to 162MHz (SXGA 75Hz / UXGA 60Hz)

• On-chip high-performance PLLs

(only a single reference crystal required)

On-chip Microcontroller

• Requires no external micro-controller

• External parallel ROM interface allows

firmware customization with little additional

cost

• 21 general-purpose inputs/outputs (GPIO's)

and 8 general-purpose outputs (GPO’s)

available for managing system devices

(keypad, back-light, NVRAM, etc)

• Industry-standard firmware embedded onchip, requires no external ROM (configuration

settings stored in NVRAM)

• Low power mode (,0.15W) when no inputs are

active

• Support for DDC2Bi based In-systemProgramming of Flash ROM

Built in Flexible LVDS Transmitter

• Dual four channel 6/8-bit LVDS transmitter

(with high-quality dithering)

• Programmable channel swapping

• Programmable channel polarity

• Support up to SXGA 75Hz output

Highly Integrated System-on-a-Chip

Reduces Component Count for

Highly Cost Effective Solution

Auto-Configuration / Auto-Detection

• Automatic input format detection

• Robust phase and image positioning

RealColor Technology

• Digital brightness and contrast controls

• TV color controls including hue and saturation controls

• Flesh-tone adjustment

• Full color matrix allows end-users to experience the same

colors as viewed on CRTs and other displays (e.g. sRGB

compliance)

On-chip OSD Controller

• On-chip RAM for downloadable menus

• 1, 2 and 4-bit per pixel character cells

• Horizontal and vertical stretch of OSD menus

• Blinking, transparency and blending

Built in Test Pattern Generator

Stand-alone operation requires no

external ROM and no firmware

development for Fast Time to

Market

Firmware compatible Family of

Products:

- gm2110/20 Analog-Interface XGA/SXGA

- gm3110/gm3120 Digital-Interface XGA/SXGA

- gm5110/gm5120 Dual-Interface XGA/SXGA

C2121-DAT-01F 9 December 2002

http://www.genesis-microchip.com

gm2121 Preliminary Data Sheet

2 GM2121 Pinout

The gm2121 is available in a 160-pin Plastic Quad Flat Pack (PQFP) package. Figure 2 provides the pin

locations for all signals.

ROM_DATA6

ROM_DATA7

CRVSS

RVDD_3.3

ROM_ADDR0

ROM_ADDR1

ROM_ADDR2

ROM_ADDR3

ROM_ADDR4

ROM_ADDR5

ROM_ADDR6

ROM_ADDR7

ROM_ADDR8

ROM_ADDR9

ROM_ADDR10

ROM_ADDR11

CRVSS

RVDD_3.3

ROM_ADDR12

ROM_ADDR13

ROM_ADDR14

ROM_ADDR15

CVDD_2.5

CRVSS

AVDD_RED_3.3

RED+

RED-

AGND_RED

AVDD_GREEN_3.3

GREEN+

GREEN-

AGND_GREEN

AVDD_BLUE_3.3

BLUE+

BLUE-

AGND_BLUE

AVDD_ADC_3.3

ADC_TEST

AGND_ADC

SGND_ADC

GND1_ADC

ROM_DATA5

ROM_DATA4

ROM_DATA3

ROM_DATA2

ROM_DATA1

ROM_DATA0

ROM_OEn

GPIO22/HCLK

GPIO16/HFSn

GPIO20/HDATA3

GPIO19/HDATA2

GPIO18/HDATA1

GPIO17/HDATA0

RVDD_3.3

CRVSS

GPIO21/IRQn

RESETn

GPIO15/DDC_SCL

GPIO14/DDC_SDA

CVDD_2.5

CRVSS

GPIO8/IRQINn

GPIO0/PWM0

GPIO1/PWM1

GPIO2/PWM2

GPIO3/TIMER1

GPIO4/UART_DI

GPIO5/UART_DO

GPIO6

RVDD_3.3

CRVSS

GPIO7

GPIO9

GPIO11/ROM_WEn

GPIO12/NVRAM_SDA

GPIO13/NVRAM_SCL

GPIO10

STI_TM1

STI_TM2

PPWR

1

160

159

158

157

156

155

154

153

152

151

150

149

148

147

146

145

144

143

142

141

140

139

138

137

136

135

134

133

132

131

130

129

128

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

414243444546474849505152535455565758596061626364656667686970717273747576777879

gm2121

127

126

125

124

123

122

121

80

120

119

118

117

116

115

114

113

112

111

110

109

108

107

106

105

104

103

102

101

100

99

98

97

96

95

94

93

92

91

90

89

88

87

86

85

84

83

82

81

VDD1_ADC_2.5

GND2_ADC

VDD2_ADC_2.5

VSS_SDDS

VDD_SDDS_3.3

AVSS_SDDS

AVDD_SDDS_3.3

VBUFC

VSS_DDDS

VDD_DDDS_3.3

AVSS_DDDS

AVDD_DDDS_3.3

VSS_DPLL

VDD_DPLL_3.3

AVSS_RPLL

AVDD_RPLL_3.3

XTAL

TCLK

HSYNC

VSYNC

CRVSS

CVDD_2.5

GPO 7

GPO 6

GPO 5

GPO 4

GPO 3

GPO 2

CRVSS

RVDD_3.3

GPO 1

GPO 0

RESERVED

RESERVED

RESERVED

RESERVED

RESERVED

RESERVED

RESERVED

PBIAS

CRVSS

CVDD_2.5

CRVSS

VCO_LV

AVDD_OUT_LV_E_2.5

CLKP_LV_E

CH3P_LV_E

CLKN_LV_E

CH2P_LV_E

CH3N_LV_E

AVSS_OUT_LV_E

CH1P_LV_E

CH2N_LV_E

CH1N_LV_E

AVSS_LV_E

CH0P_LV_E

CH0N_LV_E

AVDD_LV_E_2.5

AVSS_OUT_LV_E

AVDD_OUT_LV_E_2.5

AVSS_OUT_LV_O

CH3P_LV_O

AVDD_OUT_LV_O_2.5

CH3N_LV_O

CLKP_LV_O

CLKN_LV_O

CH2P_LV_O

CH2N_LV_O

CH1P_LV_O

CH1N_LV_O

CH0P_LV_O

CH0N_LV_O

AVSS_OUT_LV_O

AVDD_OUT_LV_O_2.5

AVSS_LV_O

CRVSS

AVDD_LV_O_2.5

CVDD_2.5

RESERVED

Figure 2. gm2121 Pin Out Diagram

C2121-DAT-01F 10 December 2002

http://www.genesis-microchip.com

gm2121 Preliminary Data Sheet

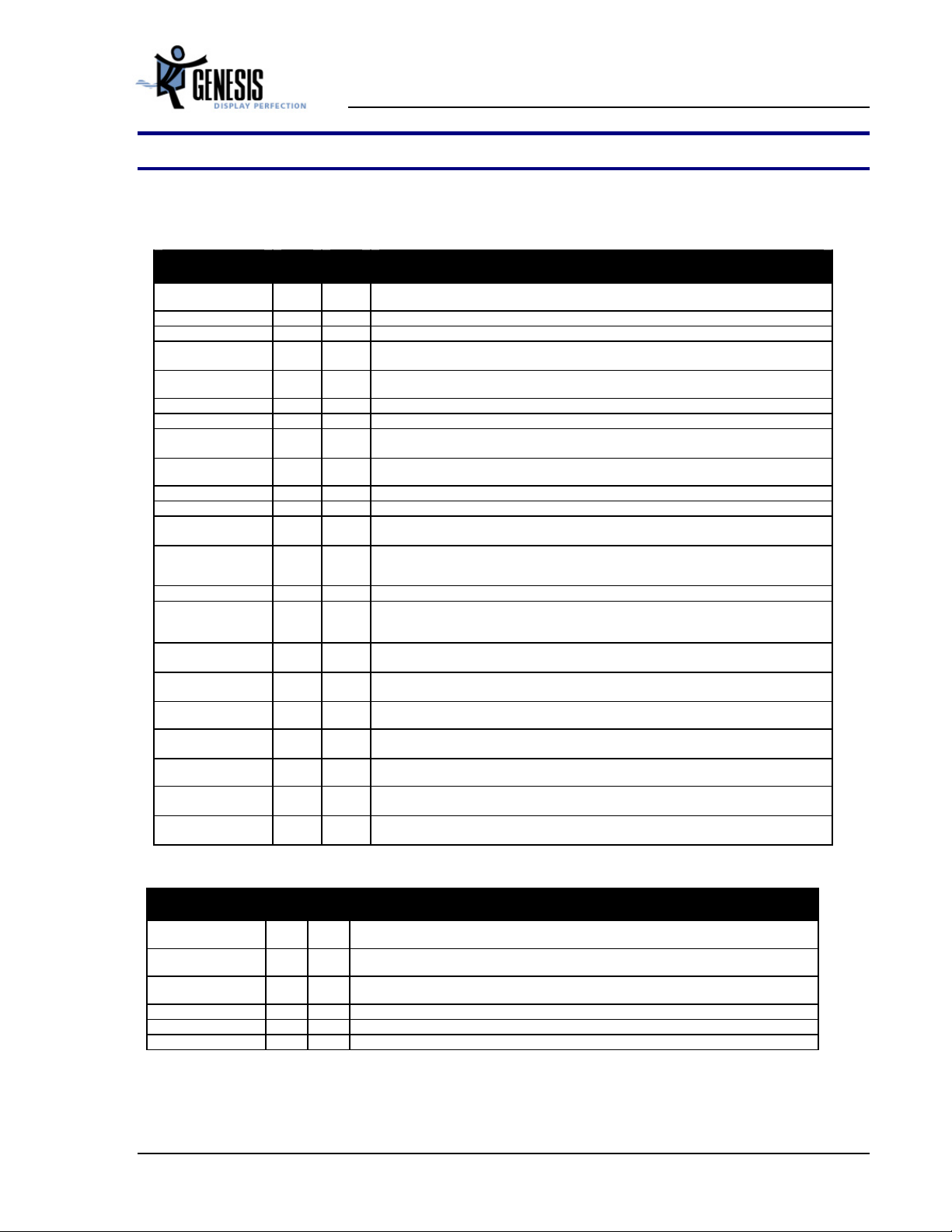

3 GM2121Pin List

I/O Legend: A = Analog, I = Input, O = Output, P = Power, G= Ground

Table 1. Analog Input Port

Pin Name No. I/O Description

AVDD_RED_3.3 136 AP Analog power (3.3V) for the red channel. Must be bypassed with decoupling capacitor to

AGND_RED pin on system board (as close as possible to the pin).

RED+ 135 AI Positive analog input for Red channel.

RED- 134 AI Negative analog input for Red channel.

AGND_RED 133 AG Analog ground for the red channel.

Must be directly connected to the system ground plane.

AVDD_GREEN_3.3 132 AP Analog power (3.3V) for the green channel. Must be bypassed with decoupling capacitor to

AGND_GREEN pin on system board (as close as possible to the pin).

GREEN+ 131 AI Positive analog input for Green channel.

GREEN- 130 AI Negative analog input for Green channel.

AGND_GREEN 129 AG Analog ground for the green channel.

Must be directly connected to the system ground plane.

AVDD_BLUE_3.3 128 AP Analog power (3.3V) for the blue channel. Must be bypassed with decoupling capacitor to

AGND_BLUE pin on system board (as close as possible to the pin).

BLUE+ 127 AI Positive analog input for Blue channel.

BLUE- 126 AI Negative analog input for Blue channel.

AGND_BLUE 125 AG Analog ground for the blue channel.

Must be directly connected to the system ground plane.

AVDD_ADC_3.3 124 AP Analog power (3.3V) for ADC analog blocks that are shared by all three channels. Includes

band gap reference, master biasing and full-scale adjust. Must be bypassed with

decoupling capacitor to AGND_ADC pin on system board (as close as possible to the pin).

ADC_TEST 123 AO Analog test output for ADC Do not connect.

AGND_ADC 122 AG Analog ground for ADC analog blocks that are shared by all three channels. Includes band

gap reference, master biasing and full-scale adjust.

Must be directly connected to system ground plane.

SGND_ADC 121 AG Dedicated pad for substrate guard ring that protects the ADC reference system.

Must be directly connected to the system ground plane.

GND1_ADC 120 G Digital GND for ADC clocking circuit.

Must be directly connected to the system ground plane

VDD1_ADC_2.5 119 P Digital power (2.5V) for ADC encoding logic. Must be bypassed with decoupling capacitor to

GND1_ADC pin on system board (as close as possible to the pin).

GND2_ADC 118 G Digital GND for ADC clocking circuit.

Must be directly connected to the system ground plane.

VDD2_ADC_2.5 117 P Digital power (2.5V) for ADC encoding logic. Must be bypassed with decoupling capacitor to

GND2_ADC pin on system board (as close as possible to the pin).

HSYNC 101 I ADC input horizontal sync input.

[Input, Schmitt trigger (400mV typical hysteresis), 5V-tolerant]

VSYNC 100 I ADC input vertical sync input.

[Input, Schmitt trigger (400mV typical hysteresis), 5V-tolerant]

Table 2. RCLK PLL Pins

Pin Name No I/O Description

AVDD_RPLL_3.3 104 AP Analog power for the Reference DDS PLL. Connect to 3.3V supply. Must be bypassed with a

AVSS_RPLL 105 AG Analog ground for the Reference DDS PLL.

TCLK 102 AI Reference clock (TCLK) from the 20.0MHz crystal oscillator (see Figure 4), or from single-

XTAL 103 AO Crystal oscillator output.

VDD_DPLL_3.3 106 P Digital power for FCLK and RCLK PLLs. Connect to 3.3V supply.

VSS_DPLL 107 G Digital ground for FCLK and RCLK PLLs.

C2121-DAT-01F 11 December 2002

0.1uF capacitor to pin AVSS_RPLL (as close to the pin as possible).

Must be directly connected to the system ground plane.

ended CMOS/TTL clock oscillator (see Figure 7). This is a 5V-tolerant input. See Table 12.

http://www.genesis-microchip.com

gm2121 Preliminary Data Sheet

Table 3. System Interface and GPIO Signals

Pin Name No I/O Description

RESETn 17 I

GPIO0/PWM0 23 IO General-purpose input/output signal or PWM0. Open drain option via register setting.

GPIO1/PWM1 24 IO General-purpose input/output signal or PWM1. Open drain option via register setting.

GPIO2/PWM2 25 IO General-purpose input/output signal or PWM2. Open drain option via register setting.

GPIO3/TIMER1 26 IO General-purpose input/output signal. Open drain option via register setting. This pin is also

GPIO4/UART_DI 27 IO General-purpose input/output signal. Open drain option via register setting. This pin is also

GPIO5/UART_DO 28 IO General-purpose input/output signal. Open drain option via register setting. This pin is also

GPIO6 29 IO General-purpose input/output signal.

GPIO7 32 IO General-purpose input/output signal.

GPIO8/IRQINn 22 IO General-purpose input/output signal. This is also active-low interrupt input to OCM and is

GPIO9 33 IO General-purpose input/output signal. Open drain option via register setting.

GPIO10 34 IO General-purpose input/output signal. Open drain option via register setting.

GPIO11/ROM_WEn 35 IO General-purpose input/output signal, or ROM write enable if a programmable FLASH

GPIO12/NVRAM_SDA

GPIO13/NVRAM_SCL

GPIO14/DDC_SCL

GPIO15/DDC_SDA

GPIO16/HFSn 9 IO General-purpose input/output signal when host port is disabled, or data signal for 2-wire

GPIO17/HDATA0

GPIO18/HDATA1

GPIO19/HDATA2

GPIO20/HDATA3

GPIO21/IRQn 16 IO General-purpose input/output signal when host port is disabled, or active-low and open-

GPIO22/HCLK 8 IO General-purpose input/output signal when host port is disabled, or clock for 2-wire serial

GPO 0 88 O General-purpose output signal.

GPO 1 89 O General-purpose output signal

GPO 2 92 O General-purpose output signal

GPO 3 93 O General-purpose output signal

GPO 4 94 O General-purpose output signal

GPO 5 95 O General-purpose output signal

GPO 6 96 O General-purpose output signal

GPO 7 97 O General-purpose output signal

36

37

18

19

13

12

11

10

Active-low hardware reset signal. The reset signal must be held low for at least 1µS.

[Input, Schmitt trigger (400mV typical hysteresis), 5V-tolerant]

[Bi-directional, Schmitt trigger (400mV typical hysteresis), 5V-tolerant]

[Bi-directional, Schmitt trigger (400mV typical hysteresis), 5V-tolerant]

[Bi-directional, Schmitt trigger (400mV typical hysteresis), 5V-tolerant]

connected to Timer 1 clock input of the OCM.

[Bi-directional, Schmitt trigger (400mV typical hysteresis), 5V-tolerant]

connected to the OCM UART data input signal by programming an OCM register. Add

10K Pull-up to VDD_3.3.

[Bi-directional, Schmitt trigger (400mV typical hysteresis), 5V-tolerant]

connected to the OCM UART data output signal by programming an OCM register. Add

10K Pull-up to VDD_3.3.

[Bi-directional, Schmitt trigger (400mV typical hysteresis), 5V-tolerant]

[Bi-directional, Schmitt trigger (400mV typical hysteresis), 5V-tolerant]

[Bi-directional, Schmitt trigger (400mV typical hysteresis), 5V-tolerant]

directly wired to OCM int_0n.

[Bi-directional, Schmitt trigger (400mV typical hysteresis), 5V-tolerant]

[Bi-directional, Schmitt trigger (400mV typical hysteresis), 5V-tolerant]

[Bi-directional, Schmitt trigger (400mV typical hysteresis), 5V-tolerant]

device is used. Open drain option via register setting.

[Bi-directional Input, Schmitt trigger (400mV typical hysteresis), 5V-tolerant]

IO

General-purpose input/output signals, or 2-wire master serial interface to NVRAM in

standalone mode. Open drain option via register setting.

IO

[Bi-directional Input, Schmitt trigger (400mV typical hysteresis), 5V-tolerant]

IO General-purpose input/output signals, or 2-wire master serial interface to NVRAM in

standalone mode. Open drain option via register setting.

[Bi-directional Input, Schmitt trigger (400mV typical hysteresis), 5V-tolerant]

serial host interface.

[Bi-directional, Schmitt trigger (400mV typical hysteresis), slew rate limited, 5V tolerant]

IO

General-purpose input/output signals.

IO

[Bi-directional, Schmitt trigger (400mV typical hysteresis), 5V-tolerant]

IO

IO

drain interrupt output pin.

[Bi-directional, 5V-tolerant]

host interface.

[Bi-directional, Schmitt trigger (400mV typical hysteresis), 5V-tolerant]

C2121-DAT-01F 12 December 2002

http://www.genesis-microchip.com

Table 4. Display Output Port

Pin Name No I/O Description

PBIAS 41 O Panel Bias Control (back light enable)

[Tri-state output, Programmable Drive]

PPWR 40 O Panel Power Control

[Tri-state output, Programmable Drive]

CH3P_LV_E 48 O Even LVDS Channel 3 positive

CH3N_LV_E 49 O Even LVDS Channel 3 negative

CLKP_LV_E 50 O Even LVDS Clock positive

CLKN_LV_E 51 O Even LVDS Clock negative

CH2P_LV_E 52 O Even LVDS Channel 2 positive

CH2N_LV_E 53 O Even LVDS Channel 2 negative

CH1P_LV_E 54 O Even LVDS Channel 1 positive

CH1N_LV_E 55 O Even LVDS Channel 1 negative

CH0P_LV_E 56 O Even LVDS Channel 0 positive

CH0N_LV_E 57 O Even LVDS Channel 0 negative

CH3P_LV_O 64 O Odd LVDS Channel 3 positive

CH3N_LV_O 65 O Odd LVDS channel 3 negative

CLKP_LV_O 66 O Odd LVDS Clock positive

CLKN_LV_O 67 O Odd LVDS Clock negative

CH2P_LV_O 68 O Odd LVDS Channel 2 positive

CH2N_LV_O 69 O Odd LVDS channel 2 negative

CH1P_LV_O 70 O Odd LVDS Channel 1 positive

CH1N_LV_O 71 O Odd LVDS channel 1 negative

CH0P_LV_O 72 O Odd LVDS Channel 0 positive

CH0N_LV_O 73 O Odd LVDS channel 0 negative

gm2121 Preliminary Data Sheet

Table 5. Parallel ROM Interface Port

Pin Name No I/O Description

ROM_ADDR15

ROM_ADDR14

ROM_ADDR13

ROM_ADDR12

ROM_ADDR11

ROM_ADDR10

ROM_ADDR9

ROM_ADDR8

ROM_ADDR7

ROM_ADDR6

ROM_ADDR5

ROM_ADDR4

ROM_ADDR3

ROM_ADDR2

ROM_ADDR1

ROM_ADDR0

ROM_DATA7

ROM_DATA6

ROM_DATA5

ROM_DATA4

ROM_DATA3

ROM_DATA2

ROM_DATA1

ROM_DATA0

ROM_OEn 7 O External PROM data Output Enable

139

140

141

142

145

146

147

148

149

150

151

152

153

154

155

156

159

160

1

2

3

4

5

6

IO

ROM address output. These pins also serve as 5V-tolerant bootstrap inputs on power up.

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

I

5V-tolerant external PROM data input

I

I

I

I

I

I

I

C2121-DAT-01F 13 December 2002

http://www.genesis-microchip.com

Table 6. Reserved Pins

Pin Name No I/O Description

Reserved 80 O For test purposes only. Do not connect

Reserved 81 O For test purposes only. Do not connect

Reserved 82 O For test purposes only. Do not connect

Reserved 83 O For test purposes only. Do not connect

Reserved 84 O For test purposes only. Do not connect

Reserved 85 O For test purposes only. Do not connect

Reserved 86 O For test purposes only. Do not connect

Reserved 87 O For test purposes only. Do not connect

VBUFC 112 O For test purposes only. Do not connect

VCO_LV 45 O For test purposes only. Do not connect

STI_TM1 38 I For test purposes only. MUST be tied to GND

STI_TM2 39 I For test purposes only. MUST be tied to GND

Table 7. Power and Ground Pins for ADC Sampling Clock DDS

Pin Name No I/O Description

AVDD_SDDS_3.3 113 AP Analog power for the Source DDS. Connect to 3.3V supply.

Must be bypassed with a 0.1uF capacitor to AVSS_SDDS pin

(as close to the pin as possible).

AVSS_SDDS 114 AG Analog ground for the Source DDS.

Must be directly connected to the system ground.

VDD_SDDS_3.3 115 P Digital power for the Source DDS. Connect to 3.3V supply.

VSS_SDDS 116 G Digital ground for the Source DDS.

gm2121 Preliminary Data Sheet

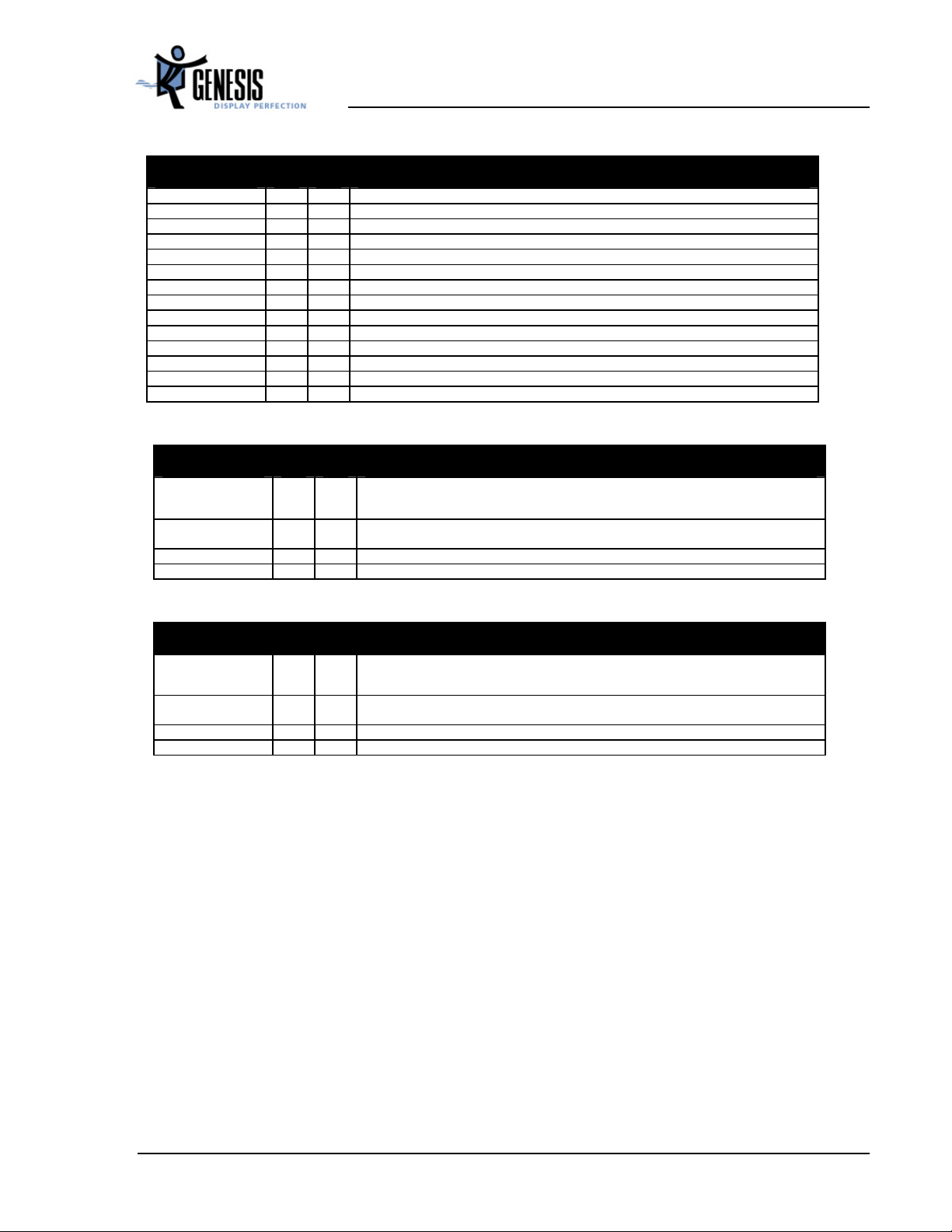

Table 8. Power and Ground Pins for Display Clock DDS

Pin Name No I/O Description

AVDD_DDDS_3.3 108 AP Analog power for Destination DDS. Connect to 3.3V supply.

AVSS_DDDS 109 AG Analog ground for Destination DDS.

VDD_DDDS_3.3 110 P Digital power for the Destination DDS. Connect to 3.3V supply.

VSS_DDDS 111 G Digital ground for the Destination DDS.

Must be bypassed with a 0.1uF capacitor to AVSS_DDDS pin

(as close to the pin as possible).

Must be directly connected to the system ground plane.

C2121-DAT-01F 14 December 2002

http://www.genesis-microchip.com

gm2121 Preliminary Data Sheet

Table 9. I/O Power and Ground Pins

Pin Name No I/O Description

RVDD_3.3 14

143

157

CRVSS 15

137

144

158

CVDD_2.5 20

138

Note, “AP” indicates a power supply that is analog in nature and does not have large switching currents.

These should be isolated from other digital supplies that do have large switching currents.

30

90

21

31

42

44

78

91

99

43

79

98

P

Connect to 3.3V digital supply.

P

Must be bypassed with a 0.1uF capacitor to CRVSS (as close to the pin as possible).

P

P

P

G

Connect to digital ground.

G

G

G

G

G

G

G

G

G

G

P

Connect to 2.5V digital supply.

P

Must be bypassed with a 0.1uF capacitor to CRVSS (as close to the pin as possible).

P

P

P

Table 10.

Power and Ground Pins for LVDS Transmitter

Pin Name No I/O Description

AVDD_OUT_LV_E_

2.5

AVDD_LV_E_2.5 61 AP Analog power for on-chip LVDS transmitter. Connect to 2.5V supply

AVSS_OUT_LV_E 47

AVSS_LV_E 60 G Analog ground for on-chip LVDS transmitter.

AVDD_OUT_LV_O_

2.5

AVDD_LV_O_2.5 77 AP Analog power for on-chip LVDS transmitter. Connect to 2.5V supply.

AVSS_OUT_LV_O 62

AVSS_LV_O 76 G Analog ground for on-chip LVDS transmitter.

46

AP Analog power for on-chip LVDS output buffer. Connect to 2.5V supply.

59

58

63

74

75

G Analog ground for on-chip LVDS output buffer.

Must be directly connected to the system ground plane

Must be directly connected to the system ground plane

AP Analog power for on-chip LVDS output buffer. Connect to 2.5V supply.

G Analog ground for on-chip LVDS output buffer.

Must be directly connected to the system ground plane.

Must be directly connected to the system ground plane.

C2121-DAT-01F 15 December 2002

http://www.genesis-microchip.com

gm2121 Preliminary Data Sheet

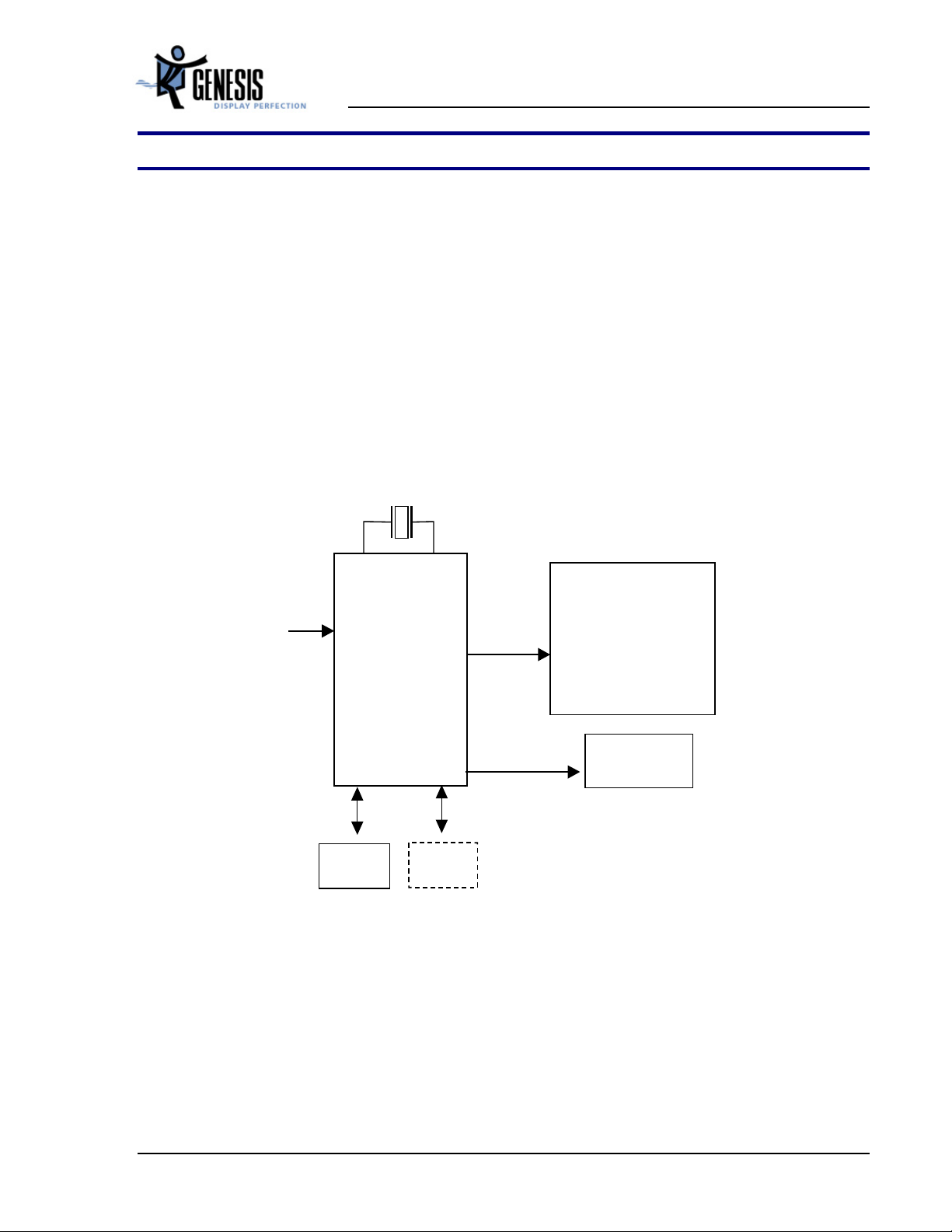

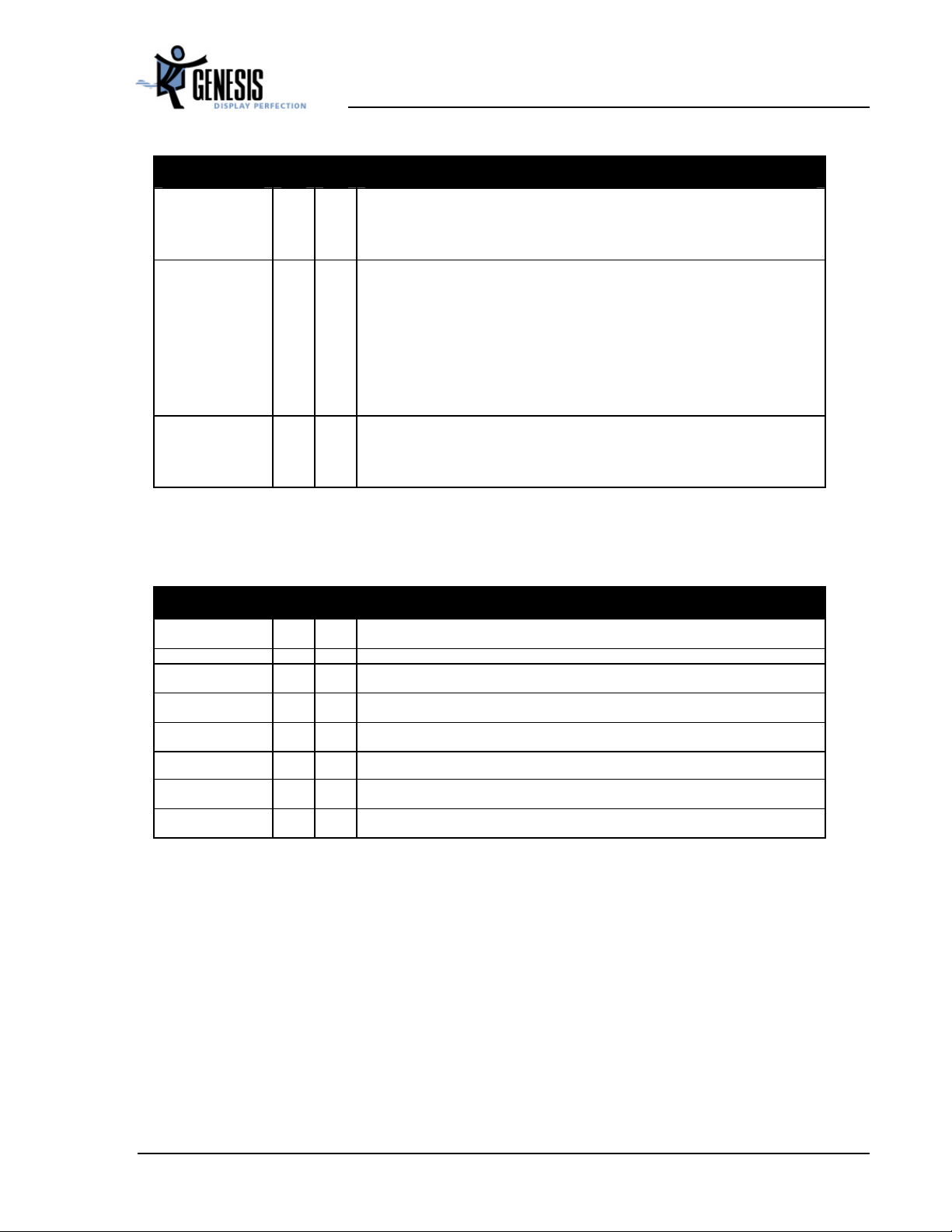

4 Functional Description

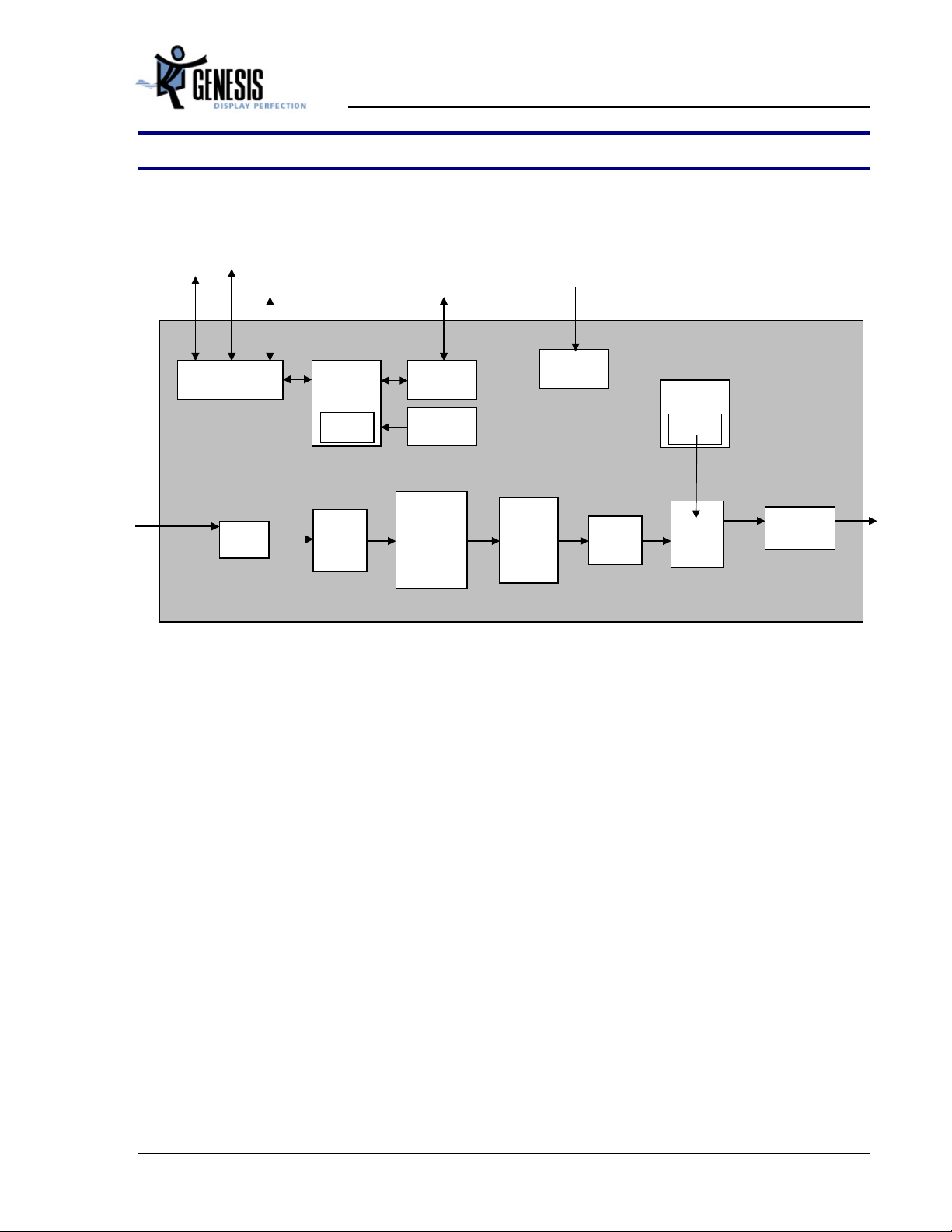

A functional block diagram is illustrated below. Each of the functional units shown is described in the

following sections.

NVRAM

Serial I/F

Serial Host I/F

GPIO

Parallel

ROM IF

Crystal

Reference

Host

Interface

8051-style

Micro-

controller

MCU

RAM

External

ROM I/F

Internal

ROM

Clock

Generation

OSD

Controller

OSD

RAMs

Analog

RGB

Triple

ADC

Image

Capture /

Measure-

ment

Figure 3. gm2121 Functional Block Diagram

Brightness /

Contrast /

Hue / Sat /

RealColor /

Moire

Zoom /

Shrink /

Filter

Gamma

Control

Output

Data

Path

Dual LVDS

Transmitter

Panel Data

and Control

4.1 Clock Generation

The gm2121 features two clock inputs. All additional clocks are internal clocks derived from one or more

of these:

1. Crystal Input Clock (TCLK and XTAL). This is the input pair to an internal crystal oscillator and

corresponding logic. A 20.0 MHz crystal is recommended. Other crystal frequencies may be used, but

require custom programming. This is illustrated in Figure 4 below. Alternatively, a single-ended

TTL/CMOS clock oscillator can be driven into the TCLK pin (leave XTAL as N/C in this case). This

is illustrated in Figure 7 below. This option is selected by connecting a 10KΩ pull-up to

ROM_ADDR13 (refer to Table 17). See also Table 12.

2. Host Interface Transfer Clock (HCLK)

The gm2121 TCLK oscillator circuitry is a custom designed circuit to support the use of an external

oscillator or a crystal resonator to generate a reference frequency source for the gm2121 device.

C2121-DAT-01F 16 December 2002

http://www.genesis-microchip.com

Loading...

Loading...