查询2N7002供应商

2N7002

DMOS Transistors (N-Channel)

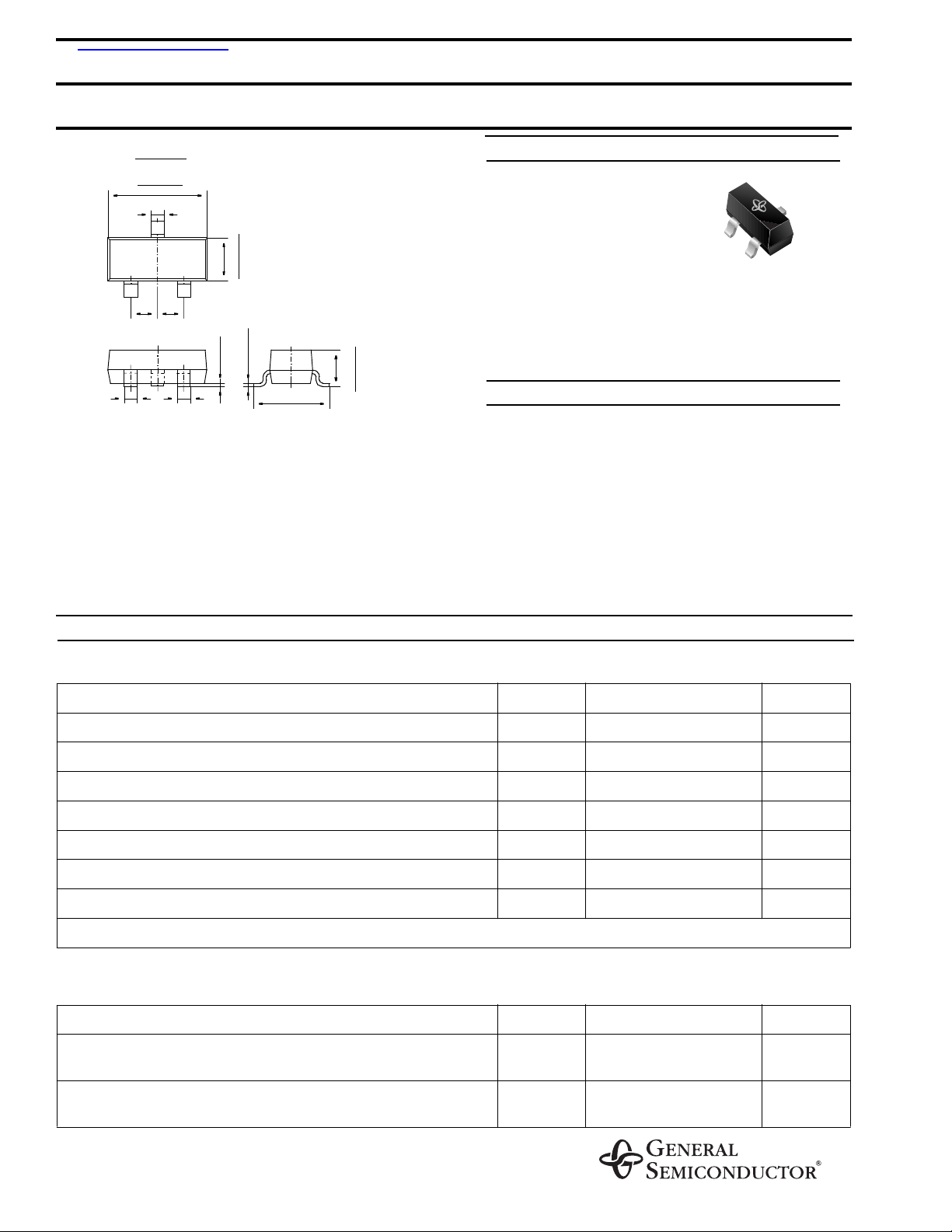

SOT-23

.122 (3.1)

.118 (3.0)

.016 (0.4)

3

12

.037(0.95)

.037(0.95)

.016 (0.4) .016 (0.4)

Dimensions in inches and (millimeters)

Pin configuration

1 = Gate, 2 = Source, 3 = Drain

Top Vi ew

)

.056 (1.43

max. .004 (0.1)

)

.052 (1.33

.007 (0.175)

.005 (0.125)

.102 (2.6)

.094 (2.4)

FEATURES

♦ High input impedance

♦ High-speed switching

♦ No minority carrier storage time

♦ CMOS logic compatible i nput

♦ No minority carrier storage time

♦ CMOS logic compatible input

♦ No thermal runawa y

♦ No secondary breakdown

.045 (1.15)

.037 (0.95)

SOT-23 Plastic Package

Case:

Weight:

Marking

S72

MECHANICAL DATA

approx. 0.008 g

Ratings at

Drain-So urce Voltage V

Drain-Gate Voltage V

Gate-Source-Voltage (pulsed) V

Drain Current (continuous) I

Po w er Dissi pation at T

Junction Temperature T

Storage Temperature Range T

1)

Ceramic Substrate 0.7mm; 2.5 cm2 area.

Invers e Diode

Max. Forw a rd Current (cont inuous )

at T

Forward V oltage Drop (typ.)

at V

ambient temperature unless otherwise specified

25 °C

= 50 °C P

C

= 25 °C

amb

= 0, IF = 0.3 A, Tj = 25 °C

GS

MAXIMUM RATINGS AND ELECTRICAL CHARACTERISTICS

Symbol Value Unit

DSS

DGS

GS

D

tot

j

S

60 V

60 V

±20 V

250 mA

1)

0.310

W

150 °C

–55 to +150 °C

Symbol V alue Unit

I

F

V

F

0.3 A

0.85 V

4/98

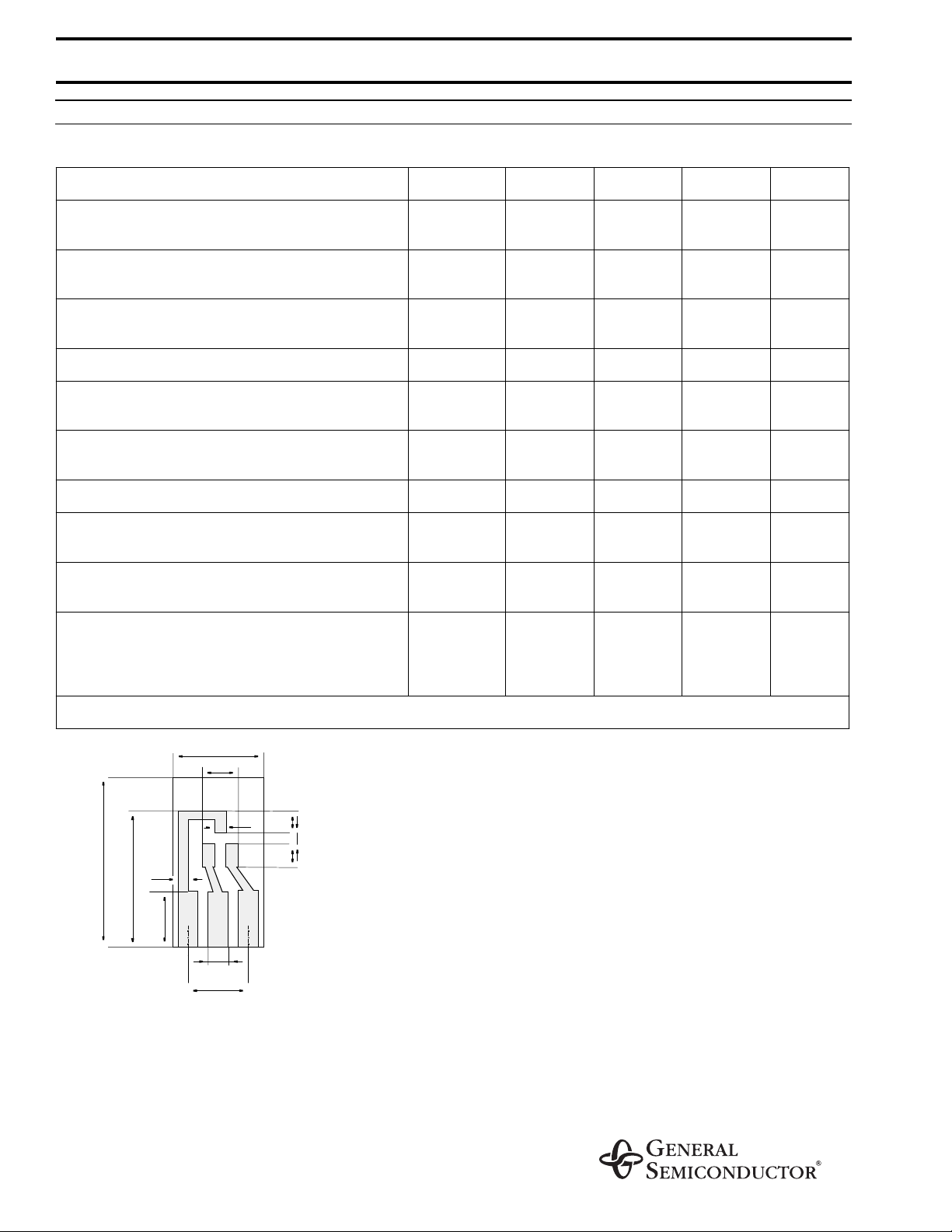

Ratings at

ambient temperature unless otherwise specified

25 °C

Drain-Source Breakdo wn Voltage

at I

= 100 µA, V

D

= 0 V

GS

Gate Threshold Voltage

at V

= VDS, ID = 1 mA V

GS

Gate-Body Leakage Current

= 15 V, VDS = 0 I

at V

GS

2N7002

ELECTRICAL CHARACTERISTICS

Symbol Min. Typ. Max. Unit

(BR)DSS

GS(th)

GSS

60 90 – V

–22.5V

––10nA

Drain Cutoff Curr ent at V

= 25 V, VGS = 0 I

DS

Drain-Source ON Resis tance

= 10 V, ID = 500 mA r

at V

GS

Thermal Resistance Junction t o Substrat e

Backside R

Thermal Resistance Junction t o Ambient Air R

Forw ard Transconductance

at V

= 10 V, ID = 200 mA, f = 1 MHz

DS

Input Capacit ance

at V

= 10 V, VGS = 0, f = 1 MHz

DS

Switching Times

at V

= 10 V, VDS = 10 V, RD = 100

GS

Ω

Turn-On Time

Turn-Off Time

1)

Device on fiberglas s substrat e, see la y out

.30 (7.5)

.12 (3)

DSS

DS(ON)

thSB

thJA

g

m

C

iss

t

on

t

off

––0.5µA

–57.5

– – 320

– – 450

1)

1)

Ω

K/W

K/W

– 200 – mS

–60–pF

–

–

5

25

–

–

ns

ns

.04 (1)

.08 ( 2)

.04 (1)

.59 (15)

.03 (0.8)

.47 (12)

0.2 (5)

Layout fo r R

thJA

.06 ( 1.5)

.20 (5.1)

test

.08 (2)

Dim ensions in inches (mil limete r s)

Thickness: Fiberglass 0.059 in (1.5 mm)

Copper leads 0.012 in (0.3 mm)

RATINGS AND CHARACTERISTIC CURVES 2N7002

RATINGS AND CHARACTERISTIC CURVES 2N7002

RATINGS AND CHARACTERISTIC CURVES 2N7002

Loading...

Loading...