Page 1

Cinterion® ALAS5V

Hardware Interface Description

Version: 00.030a

DocId: ALAS5V_HID_v00.030a

GEMALTO.COM/M2M

Page 2

Cinterion® ALAS5V Hardware Interface Description

2

Page 2 of 124

Document Name:

Version:

Date:

DocId:

Status

Cinterion® ALAS5V Hardware Interface Description

00.030a

2019-03-20

ALAS5V_HID_v00.030a

Confidential / Preliminary

GENERAL NOTE

THE USE OF THE PRODUCT INCLUDING THE SOFTWARE AND DOCUMENTATION (THE "PRODUCT") IS SUBJECT TO THE RELEASE NOTE PROVIDED TOGETHER WITH PRODUCT. IN ANY

EVENT THE PROVISIONS OF THE RELEASE NOTE SHALL PREVAIL. THIS DOCUMENT CONTAINS

INFORMATION ON GEMALTO M2M PRODUCTS. THE SPECIFICATIONS IN THIS DOCUMENT ARE

SUBJECT TO CHANGE AT GEMALTO M2M'S DISCRETION. GEMALTO M2M GMBH GRANTS A NONEXCLUSIVE RIGHT TO USE THE PRODUCT. THE RECIPIENT SHALL NOT TRANSFER, COPY,

MODIFY, TRANSLATE, REVERSE ENGINEER, CREATE DERIVATIVE WORKS; DISASSEMBLE OR

DECOMPILE THE PRODUCT OR OTHERWISE USE THE PRODUCT EXCEPT AS SPECIFICALLY

AUTHORIZED. THE PRODUCT AND THIS DOCUMENT ARE PROVIDED ON AN "AS IS" BASIS ONLY

AND MAY CONTAIN DEFICIENCIES OR INADEQUACIES. TO THE MAXIMUM EXTENT PERMITTED

BY APPLICABLE LAW, GEMALTO M2M GMBH DISCLAIMS ALL WARRANTIES AND LIABILITIES.

THE RECIPIENT UNDERTAKES FOR AN UNLIMITED PERIOD OF TIME TO OBSERVE SECRECY

REGARDING ANY INFORMATION AND DATA PROVIDED TO HIM IN THE CONTEXT OF THE DELIVERY OF THE PRODUCT. THIS GENERAL NOTE SHALL BE GOVERNED AND CONSTRUED

ACCORDING TO GERMAN LAW.

Copyright

Transmittal, reproduction, dissemination and/or editing of this document as well as utilization of its contents and communication thereof to others without ex press autho rization are prohib ited. Offenders will be

held liable for payment of damages. All rights created by patent grant or registration of a utility model or

design patent are reserved.

Copyright © 2019, Gemalto M2M GmbH, a Gemalto Company

Trademark Notice

Gemalto, the Gemalto logo, are trademarks and service marks of Gemalto and are registered in certain

countries. Microsoft and Win dows are e ither regis tered trademarks or trademarks of Microsoft Corporation in the United States and/or other countries. All other register ed trademarks or trademarks mention ed

in this document are property of their respective owners.

ALAS5V_HID_v00.030a 2019-03-20

Confidential / Preliminary

Page 3

Cinterion® ALAS5V Hardware Interface Description

Contents

124

Page 3 of 124

Contents

1 Introduction.................................................................................................................8

1.1 Product Variants ................................................................................................8

1.2 Key Features at a Glance..................................................................................9

1.2.1 Supported Frequency Bands.............................................................. 12

1.2.2 Supported CA Configurations............................................................. 13

1.3 ALAS5V System Overview ..............................................................................15

1.4 Circuit Concept ................................................................................................16

2 Interface Characteristics.......................................................................................... 17

2.1 Application Interface ........................................................................................17

2.1.1 Pad Assignment..................................................................................17

2.1.2 Signal Properties.................................................................................21

2.1.2.1 Absolute Maximum Ratings ................................................29

2.1.3 USB Interface......................................................................................30

2.1.4 Serial Interface ASC0 ......................................................................... 31

2.1.5 Serial Interface ASC1 ......................................................................... 32

2.1.6 Inter-Integrated Circuit Interface......................................................... 33

2.1.7 UICC/SIM/USIM Interface...................................................................34

2.1.8 Enhanced ESD Protection for SIM Interfaces.....................................36

2.1.9 Digital Audio Interface.........................................................................37

2.1.9.1 Pulse Code Modulation Interface (PCM).............................37

2.1.9.2 Inter-IC Sound Interface......................................................38

2.1.10 Analog-to-Digital Converter (ADC)......................................................39

2.1.11 RTC Backup........................................................................................39

2.1.12 GPIO Interface....................................................................................39

2.1.13 Control Signals....................................................................................40

2.1.13.1 PWR_IND Signal.................................................................40

2.1.13.2 Remote Wakeup..................................................................41

2.1.13.3 Firmware Swap...................................................................41

2.1.14 JTAG Interface....................................................................................41

2.1.15 eMMC Interface ..................................................................................42

2.1.15.1 eMMC Power Supply .......................................... ........... .....42

2.2 GSM/UMTS/LTE Antenna Interface.................................................................43

2.2.1 Antenna Interface Specifications ........................................................44

2.2.2 Antenna Installation ............................................................................49

2.2.3 RF Line Routing Design......................................................................50

2.2.3.1 Line Arrangement Instructions ............................................50

2.2.3.2 Routing Examples...............................................................52

2.2.4 RF Antenna Diagnostic.......................................................................53

2.3 GNSS Antenna Interface .................................................................................56

2.3.1 GNSS Antenna Diagnostic..................................................................57

ALAS5V_HID_v00.030a 2019-03-20

Confidential / Preliminary

Page 4

Cinterion® ALAS5V Hardware Interface Description

Contents

124

Page 4 of 124

2.4 Sample Application..........................................................................................58

2.4.1 Prevent Back Powering.......................................................................60

2.4.2 Sample Level Conversion Circuit........................................................61

2.4.3 Sample Circuit for Antenna Detection.................................................62

3 GNSS Interface..........................................................................................................65

3.1 GNSS Interface Characteristics.......................................................................66

4 Operating Characteristics........................................................................................68

4.1 Operating Modes .............................................................................................68

4.2 Power Up/Power Down Scenarios...................................................................69

4.2.1 Turn on ALAS5V.................................................................................69

4.2.2 Signal States after First Startup..........................................................70

4.2.3 Turn off or Restart ALAS5V................................................................73

4.2.3.1 Switch off ALAS5V Using AT Shutdown Command ............ 73

4.2.3.2 Restart ALAS5V Using AT Command ................................. 74

4.2.3.3 Turn off ALAS5V Using IGT Line......................................... 75

4.2.3.4 Turn off or Restart ALAS5V in Case of Emergency ............ 76

4.2.3.5 Overall Shutdown Sequence...............................................77

4.2.4 Automatic Shutdown...........................................................................78

4.2.4.1 Thermal Shutdown..............................................................79

4.2.4.2 Deferred Shutdown at Extreme Temperature Conditions.... 80

4.2.4.3 Undervoltage Shutdown......................................................81

4.2.4.4 Overvoltage Shutdown........................................................81

4.3 Power Saving...................................................................................................82

4.3.1 Power Saving while Attached to GSM Networks................................82

4.3.2 Power Saving while Attached to WCDMA Networks ..........................84

4.3.3 Power Saving while Attached to LTE Networks..................................85

4.4 Power Supply...................................................................................................86

4.4.1 Power Supply Ratings.........................................................................87

4.4.2 Minimizing Power Losses ...................................................................94

4.4.3 Monitoring Power Supply by AT Command........................................94

4.5 Operating Temperatures..................................................................................95

4.6 Electrostatic Discharge....................................................................................96

4.7 Reliability Characteristics.................................................................................96

5 Mechanical Dimensions and Mounting...................................................................97

5.1 Mechanical Dimensions of ALAS5V ................................................................ 97

5.2 Mounting ALAS5V onto the Application Platform.............................................99

5.2.1 SMT PCB Assembly ........................................................................... 99

5.2.1.1 Land Pattern and Stencil.....................................................99

5.2.1.2 Board Level Characterization............................................100

5.2.2 Moisture Sensitivity Level .................................................................101

5.2.3 Soldering Conditions and Temperature............................................ 101

5.2.3.1 Reflow Profile....................................................................101

5.2.3.2 Maximum Temperature and Duration................................ 102

ALAS5V_HID_v00.030a 2019-03-20

Confidential / Preliminary

Page 5

Cinterion® ALAS5V Hardware Interface Description

Contents

124

Page 5 of 124

5.2.4 Durability and Mechanical Handling..................................................103

5.2.4.1 Storage Conditions............................................................103

5.2.4.2 Processing Life..................................................................103

5.2.4.3 Baking...............................................................................104

5.2.4.4 Electrostatic Discharge ..................................................... 104

5.3 Packaging......................................................................................................105

5.3.1 Trays.................................................................................................105

5.3.2 Shipping Materials ............................................................................105

5.3.2.1 Moisture Barrier Bag.........................................................105

5.3.2.2 Transportation Boxes........................................................107

6 Regulatory and Type Approval Information......................................................... 108

6.1 Directives and Standards...............................................................................108

6.2 SAR requirements specific to portable mobiles............................................. 111

6.3 Reference Equipment for Type Approval.......................................................112

6.4 Compliance with FCC and ISED Rules and Regulations...............................113

7 Document Information............................................................................................116

7.1 Revision History.............................................................................................116

7.2 Related Documents .......................................................................................118

7.3 Terms and Abbreviations...............................................................................118

7.4 Safety Precaution Notes................................................................................121

8 Appendix..................................................................................................................122

8.1 List of Parts and Accessories.........................................................................122

ALAS5V_HID_v00.030a 2019-03-20

Confidential / Preliminary

Page 6

Cinterion® ALAS5V Hardware Interface Description

Tables

124

Page 6 of 124

Tables

Table 1: Supported frequency bands for each product variant.................................... 12

Table 2: Supported CA configurations......................................................................... 13

Table 3: Overview: Pad assignments........................................................................... 18

Table 4: Signal description........................................................................................... 21

Table 5: Absolute maximum ratings (TBD.)................................................................. 29

Table 6: DCE-DTE wiring of ASC0 .............................................................................. 32

Table 7: Signals of the SIM interface (SMT application interface)............................... 34

Table 8: Overview of PCM pin functions...................................................................... 37

Table 9: Overview of I

Table 10: GPIO lines and possible alternative assignment............................................ 39

Table 11: Remote wakeup lines..................................................................................... 41

Table 12: Return loss in the active band........................................................................ 43

Table 13: RF Antenna interface GSM/UMTS/LTE (at operating temperature range).... 44

Table 14: Possible GPIOx signal states if used for antenna diagnosis.......................... 54

Table 15: Assured antenna diagnostic states................................................................ 55

Table 16: GSM/UMTS/LTE antenna diagnostic decision threshold............................... 55

Table 17: Sample ranges of the GNSS antenna diagnostic measurements and

their possible meaning................................................................................... 57

Table 18: Antenna detection reference circuit - parts list............................................... 64

Table 19: GNSS properties............................................................................................ 66

Table 20: Power supply for active GNSS antenna......................................................... 67

Table 21: Overview of operating modes ........................................................................ 68

Table 22: Signal states................................................................................................... 70

Table 23: Board temperature warning and switch off level............................................ 79

Table 24: Voltage supply ratings.................................................................................... 87

Table 25: Current consumption ratings.......................................................................... 88

Table 26: Board temperature......................................................................................... 95

Table 27: Electrostatic values........................................................................................ 96

Table 28: Reflow temperature recommendations........................................................ 102

Table 29: Storage conditions ....................................................................................... 103

Table 30: Directives ..................................................................................................... 108

Table 31: Standards of North American type approval................................................ 108

Table 32: Standards of European type approval.......................................................... 109

Table 33: Requirements of quality ............................................................................... 109

Table 34: Standards of the Ministry of Information Industry of the

People’s Republic of China.......................................................................... 110

Table 35: Toxic or hazardous substances or elements with defined concentration

limits............................................................................................................. 110

Table 36: Antenna gain limits for FCC for ALAS5V-W (TBD.)..................................... 113

Table 37: Antenna gain limits for FCC and ISED for ALAS5V-US (TBD.)................... 114

Table 38: List of parts and accessories........................................................................ 122

Table 39: Molex sales contacts (subject to change).................................................... 123

Table 40: Hirose sales contacts (subject to change)................................................... 123

2

S pin functions......................................................................... 38

ALAS5V_HID_v00.030a 2019-03-20

Confidential / Preliminary

Page 7

Cinterion® ALAS5V Hardware Interface Description

Figures

124

Page 7 of 124

Figures

Figure 1: ALAS5V system overview.............................................................................. 15

Figure 2: ALAS5V block diagram.................................................................................. 16

Figure 3: ALAS5V bottom view: Pad assignments........................................................ 19

Figure 4: ALAS5V top view: Pad assignments.............................................................. 20

Figure 5: USB circuit ..................................................................................................... 30

Figure 6: Serial interface ASC0..................................................................................... 31

Figure 7: Serial interface ASC1..................................................................................... 32

Figure 8: I

Figure 9: First UICC/SIM/USIM interface...................................................................... 35

Figure 10: Second UICC/SIM/USIM interface................................................................. 35

Figure 11: SIM interfaces - enhanced ESD protection.................................................... 36

Figure 12: PCM timing short frame (master, 4096KHz, 16kHz sample rate).................. 37

Figure 13: I

Figure 14: PWR_IND signal............................................................................................ 40

Figure 15: eMMC power supply ...................................................................................... 42

Figure 16: Antenna pads (top view)................................................................................ 49

Figure 17: Embedded Stripline line arrangement............................................................ 50

Figure 18: Micro-Stripline line arrangement samples...................................................... 51

Figure 19: Routing to application‘s RF connector ........................................................... 52

Figure 20: Resistor measurement used for antenna detection....................................... 53

Figure 21: Basic circuit for antenna detection................................................................. 54

Figure 22: Supply voltage for active GNSS antenna....................................................... 56

Figure 23: ESD protection for passive GNSS antenna................................................... 57

Figure 24: ALAS5V sample application........................................................................... 59

Figure 25: Sample level conversion circuits.................................................................... 61

Figure 26: Antenna detection circuit sample - Overview................................................. 62

Figure 27: Antenna detection circuit sample - Schematic............................................... 63

Figure 28: Power-on with IGT ......................................................................................... 69

Figure 29: Signal states during turn-off procedure.......................................................... 74

Figure 30: Timing of IGT if used as ON/OFF switch ....................................................... 75

Figure 31: Shutdown by EMERG_OFF signal................................................................. 76

Figure 32: Restart by EMERG_OFF signal..................................................................... 76

Figure 33: Overall shutdown sequence........................................................................... 77

Figure 34: Power saving and paging in GSM networks .................................................. 83

Figure 35: Power saving and paging in WCDMA networks............................................. 84

Figure 36: Power saving and paging in LTE networks.................................................... 85

Figure 37: Decoupling capacitor(s) for BATT+................................................................ 86

Figure 38: Power supply limits during transmit burst....................................................... 94

Figure 39: Board and ambient temperature differences.................................................. 95

Figure 40: ALAS5V – top and bottom view ..................................................................... 97

Figure 41: Dimensions of ALAS5V (all dimensions in mm)............................................. 98

Figure 42: Land pattern (top layer).................................................................................. 99

Figure 43: Recommended design for 110 micron thick stencil (top layer).................... 100

Figure 44: Reflow Profile............................................................................................... 101

Figure 45: Shipping tray dimensions............................................................................. 105

Figure 46: Moisture Sensitivity Label ............................................................................ 106

Figure 47: Humidity Indicator Card - HIC...................................................................... 107

Figure 48: Reference equipment for type approval....................................................... 112

2

C interface connected to VEXT ................................................................... 33

2

S timing (master mode) ............................................................................... 38

ALAS5V_HID_v00.030a 2019-03-20

Confidential / Preliminary

Page 8

Cinterion® ALAS5V Hardware Interface Description

1 Introduction

16

Page 8 of 124

1 Introduction

This document1 describes the hardware of the Cinterion® ALAS5V module. It helps you quickly

retrieve interface specifications, electrical and mechanical details and information on the requirements to be considered for integrating further components.

1.1 Product Variants

This document applies to the following Gemalto M2M modules:

®

•Cinterion

interion

•C

•C

interion

•C

interion

re necessary a note is made to differentiate between the various product variants and re-

Whe

ALAS5V-W

®

ALAS5V-CN

®

ALAS5V-E

®

ALAS5V-US

leases.

1. The document is effective only if listed in the appropriate Release Notes as part of the technical documentation delivered with your Gemalto M2M product.

ALAS5V_HID_v00.030a 2019-03-20

Confidential / Preliminary

Page 9

Cinterion® ALAS5V Hardware Interface Description

1.2 Key Features at a Glance

16

Page 9 of 124

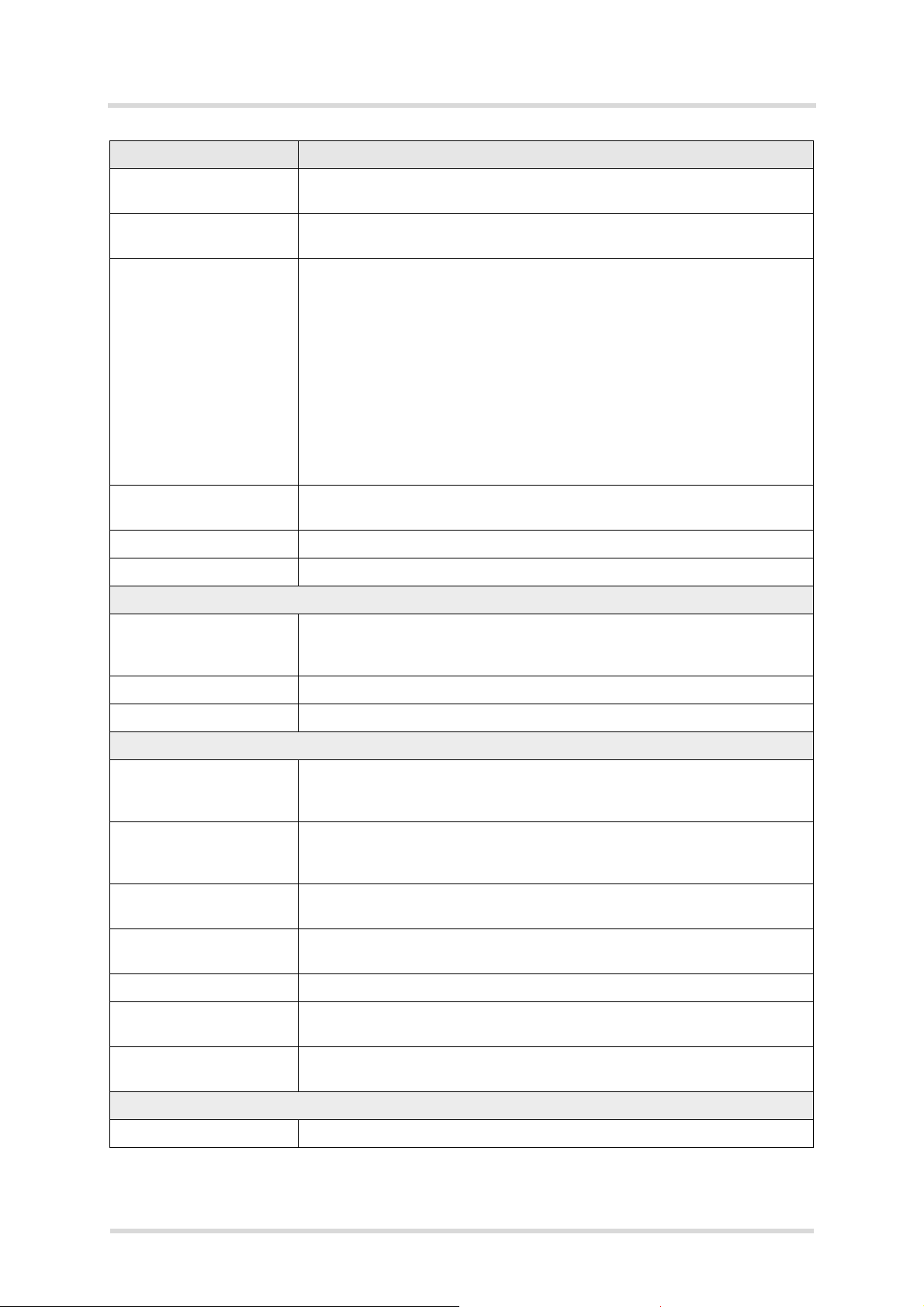

1.2 Key Features at a Glance

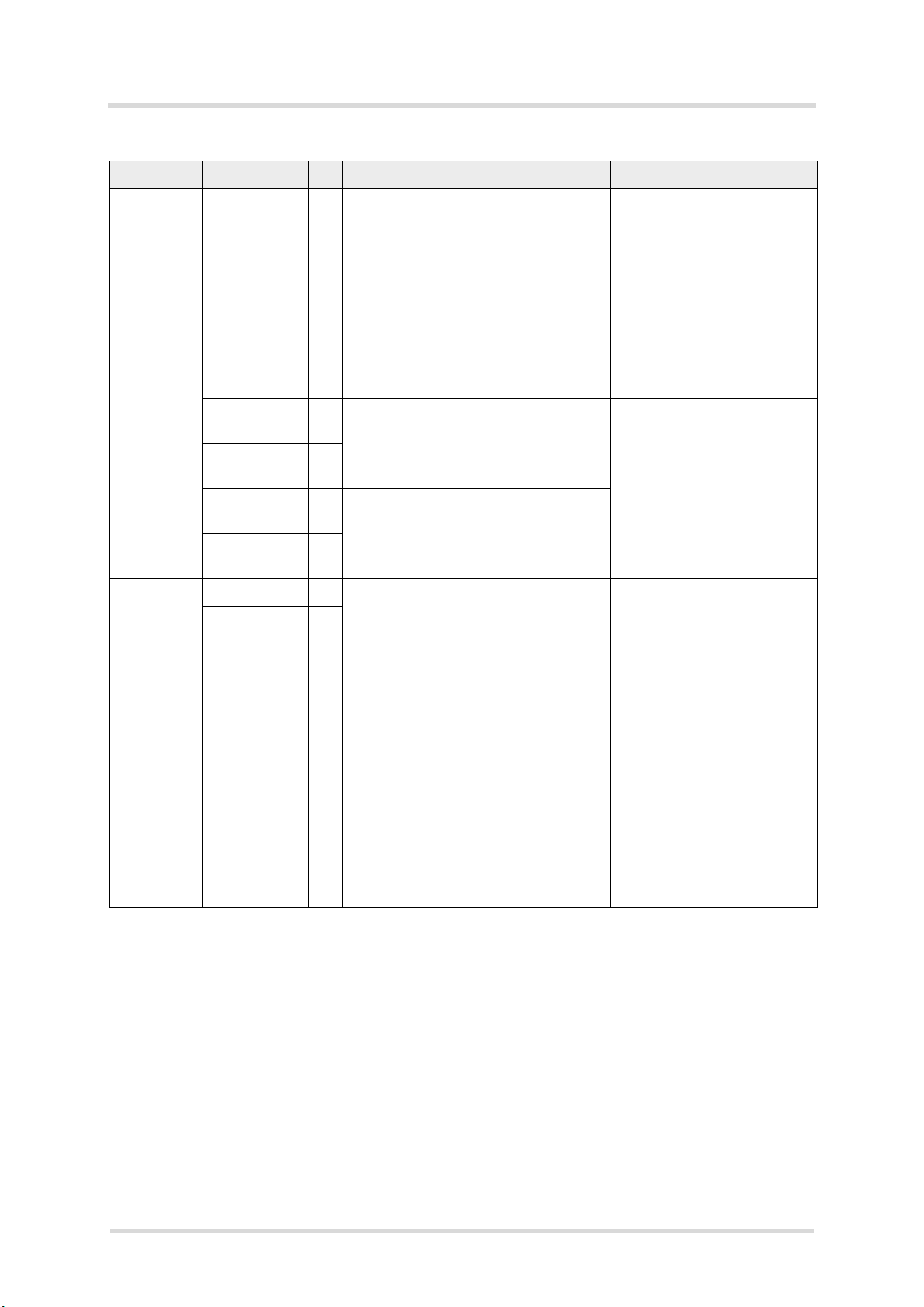

Feature Implementation

General

Frequency bands Note: Not all of the frequency bands (and 3GPP technologie s) mentio ned

throughout this document are supported by every

ant. Please refer to Section 1.2.1 for an overview of the frequency bands

supported by each

GSM class Small MS

ALAS5V product variant.

ALAS5V product vari-

Output power

(according to Release 99)

Output power

(according to Release 4)

Output power

(according to Release 8)

Power supply 3.3V <

Operating temperature

(board temperature)

Physical Dimensions: 40mm x 36mm x 3mm

RoHS All hardware components fully compliant with EU RoHS Directive

LTE features

GSM/GPRS/UMTS:

Class 4 (+33dBm ±2dB) for EGSM850 and EGSM900

Class 1 (+30dBm ±2dB) for GSM1800 and GSM1900

Class E2 (+27dBm ± 3dB) for GSM 850 8-PSK and GSM 900 8-PSK

Class E2 (+26dBm +3 /-4dB) for GSM 1800 8-PSK and GSM 1900 8-PSK

Class 3 (+24dBm +1/-3dB) for all supported WCDMA FDD bands

TD-SCDMA:

Class 2 (+24dBm +1/-3dB) for TD-SCDMA 1900 (Bd39) and TD-SCDMA

2000 (Bd34)

LTE (FDD):

Class 3 (+23dBm ±2dB) for all supported LTE FDD bands

LTE (TDD):

Class 3 (+23dBm ±2dB) for all supported LTE TDD bands

V

Normal operation: -30°C to +85°C

Restricted operation: -40°C to +95°C

Weight: 8.8g

BATT+

< 4.2V

3GPP Release 13 Down- and Uplink carrier aggregation (CA) to increase bandwidth, and

thereby increase bitrate:

• Maximum aggregated bandwidth: 80MHz

• Maximum number of component carriers: 2

• Inter-band FDD

• Intra-band FDD, TDD, contiguous, non-contiguous

• Supported inter- and intra-band CA configurations: See Section 1.2.2

CAT 6 supported

DL 300Mbps, UL 50Mbps

2x2 MIMO in DL direction

HSPA features

3GPP Release 8 UE CAT. 14, 24

DC-HSPA+ – DL 42Mbps

HSUPA – UL 5.76Mbps

Compressed mode (CM) supported according to 3GPP TS25.212

ALAS5V_HID_v00.030a 2019-03-20

Confidential / Preliminary

Page 10

Cinterion® ALAS5V Hardware Interface Description

1.2 Key Features at a Glance

16

Feature Implementation

UMTS features

3GPP Release 8 PS data rate – 384 kbps DL / 384 kbps UL

TD-SCDMA features

3GPP Release 4 2.8 Mbps DL / 2.2Mbps UL

GSM / GPRS / EGPRS features

Data transfer GPRS:

• Multislot Class 12

• Mobile Station Class B

• Coding Scheme 1 – 4

EGPRS:

• Multislot Class 12

• EDGE E2 power class for 8 PSK

• Downlink coding schemes – CS 1-4, MCS 1-9

• Uplink coding schemes – CS 1-4, MCS 1-9

• SRB loopback and test mode B

• 8-bit, 11-bit RACH

• 1 phase/2 phase access procedures

• Link adaptation and IR

• NACC, extended UL TBF

• Mobile Station Class B

Page 10 of 124

SMS Point-to-point MT and MO, Cell broadcast,

Text and PDU mode

Software

AT commands Hayes, 3GPP TS 27.007 and 27.005, and proprietary Gemalto M2M com-

mands

SIM Application Toolkit SAT Release 99, letter classes b, c, e with BIP and RunAT support

Firmware update Firmware update supported

GNSS Features

Protocol NMEA

Modes Standalone GNSS (GPS, GLONASS, Beidou, Galileo)

Integrated gpsOne 9HT support (GPS, GLONASS, Beidou, Galileo)

QZSS and SBAS support

General Power saving modes

DC feed bridge and control of power supply for active antenna via GPIO

Interfaces

Module interface Surface mount device with solderable connection pads (SMT application

interface).

Land grid array (LGA) technology ensures high solder joint reliability and

provides the possibility to use an optional module mounting socket.

For more information on how to integrate SMT modules see also [3]. This

application note comprises chapters on module mounting and app lication

layout issues as well as on additional SMT application development equip-

ment.

ALAS5V_HID_v00.030a 2019-03-20

Confidential / Preliminary

Page 11

Cinterion® ALAS5V Hardware Interface Description

Page 11 of 124

1.2 Key Features at a Glance

16

Feature Implementation

Antenna 50. GSM/UMTS/LTE main antenna, LTE Diversity/MIMO antenna,

(active/passive) GNSS antenna

USB USB 2.0 High Speed (480Mbit/s) device interface or

USB 3.0 Super Speed (5Gbit/s) device interface

Serial interface ASC0:

• 8-wire (plus GND line) interface unbalanced, asynchronous

• Fixed baud rates from 115,200 to 921,600bps

• Supports RTS0/CTS0 hardware flow control

Linux controlled only:

ASC1:

• 4-wire, unbalanced asynchronous interface

• Fixed baud rates: 115,200bps to 921,60bps

• Supports RTS1/CTS1 hardware flow control

ASC2:

2-wire, unbalanced asynchronous interface at RXD2 and T XD2 lines used

for tracing and debugging purposes (optional)

UICC interface 2 UICC interfaces (switchable)

Supported chip cards: UICC/SIM/USIM 2.85V, 1.8V

2

I

C interface 1 I2C interface

Audio 2 digital interfaces (I

2

S) - first DAI reserved for future use

Power on/off, Reset

Power on/off Switch-on by hardware signal IGT

Switch-off by AT command (AT^SMSO) or IGT (option)

Automatic switch-off in case of critical temperature or voltage conditions

Reset Orderly shutdown and reset by AT command

Emergency-off Emergency-off by hardware signal EMERG_OFF

Special Features

Antenna SAIC (Single Antenna Interference Cancellation) / DARP (Downlink

Advanced Receiver Performance)

Rx Diversity (receiver type 3i - 64-QAM) / MIMO

GPIO 15 I/O pins of the application interface programmable as GPIO.

GPIO1 can be configured as dead reckoning synchronization signal.

Programming can be done via AT commands.

Emergency call handling

(not for -US variant)

EU eCall 3GPP Release 10 compliant (modem)

ERA compliant (modem and GNSS)

ADC inputs Analog-to-Digital Converter with four unbalanced analog inputs for (exter-

nal) antenna diagnosis

JTAG JTAG interface for debug purposes

eMMC Linux controlled:

Embedded Multi-Media Card interface

PCIe Linux controlled:

PCIe interface

Evaluation kit

Evaluation module ALAS5V module soldered onto a dedicated PCB.

ALAS5V_HID_v00.030a 2019-03-20

Confidential / Preliminary

Page 12

Cinterion® ALAS5V Hardware Interface Description

1.2 Key Features at a Glance

16

Page 12 of 124

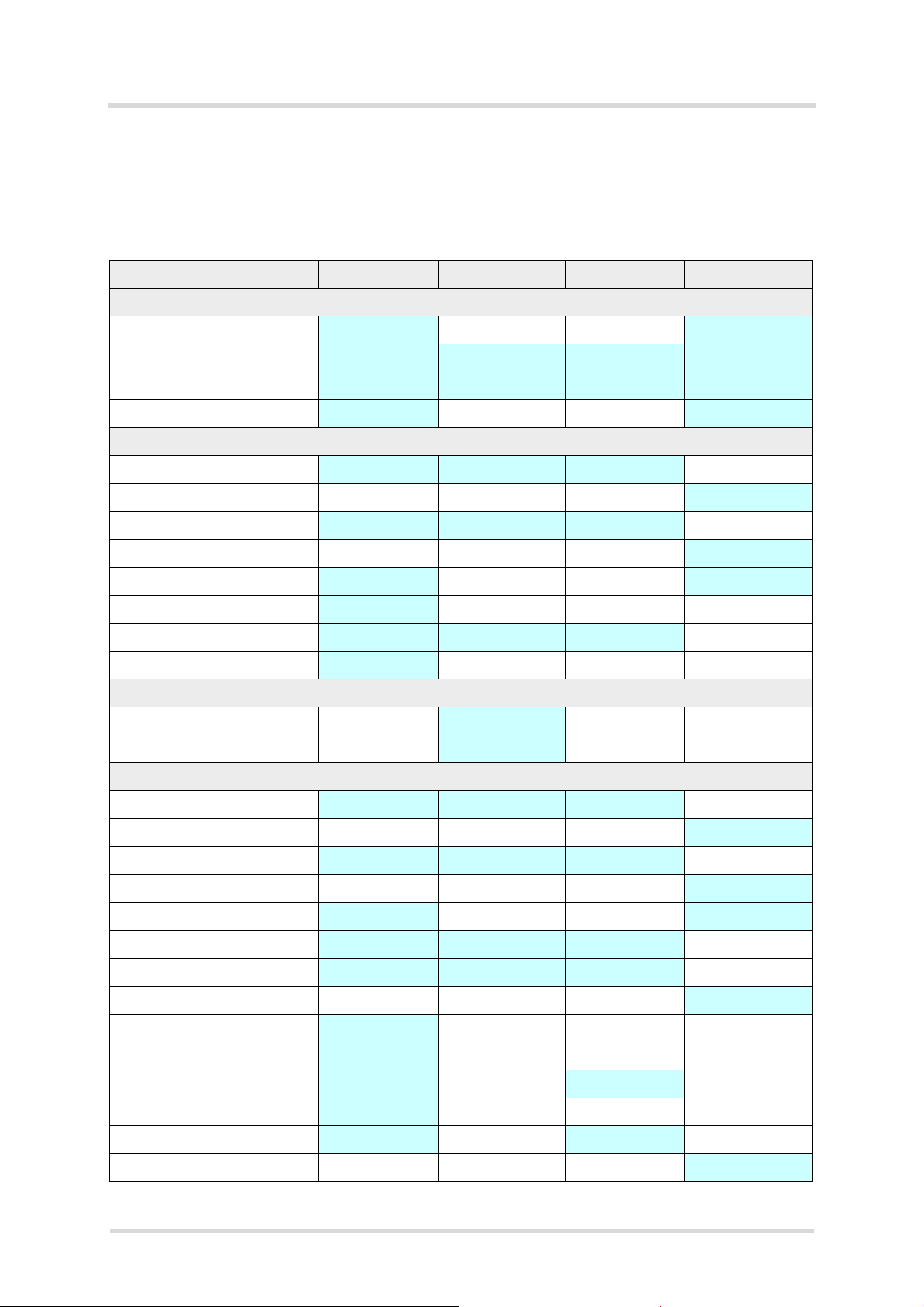

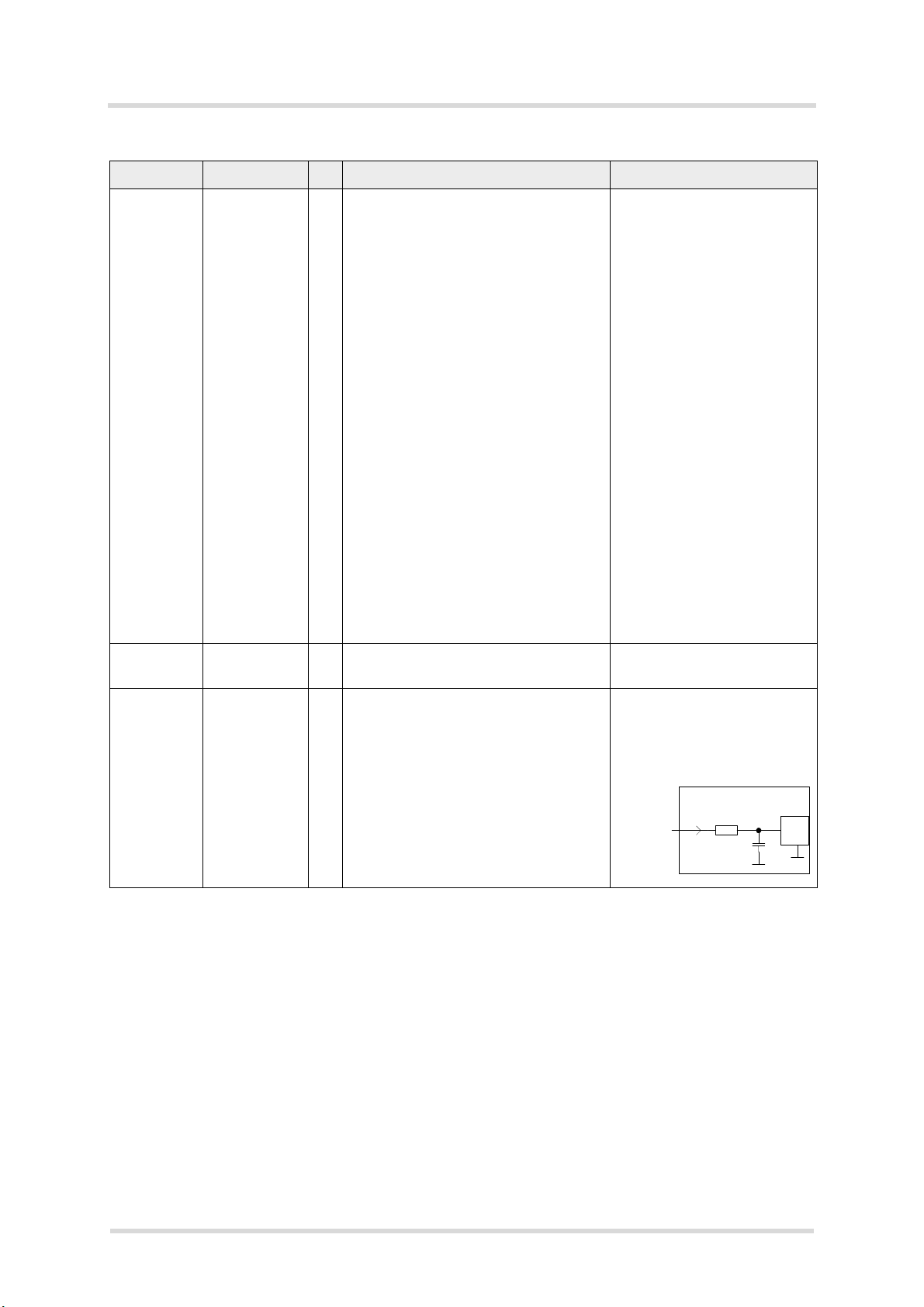

1.2.1 Supported Frequency Bands

The following table lists the supported frequency bands for each of the ALAS5V product variants mentioned in Section 1.1. Supported CA configurations can be found in Section 1.2.2.

Table 1: Supported frequency bands for each product variant

Band ALAS5V-W ALAS5V-CN ALAS5V-E ALAS5V-US

GSM/GPRS/EDGE

850MHz x x

900MHz

1800MHz

1900MHz

UMTS/HSPA

Bd.I (2100MHz) x x x

Bd.II (1900MHz)

Bd.III (1800MHz)

Bd.IV (1700MHz)

Bd.V (850MHz)

Bd.VI (850MHz)

Bd.VIII (900MHz)

Bd.XIX (850MHz)

TD-SCDMA

Bd.34 (2000MHz) x

Bd.39 (1900MHz)

LTE-FDD

Bd.1 (2100MHz) x x x

x x x x

x x x x

x x

x x x

x x

x

x x x

x

x

x

x

Bd.2 (1900MHz)

Bd.3 (1800MHz)

Bd.4 (1700MHz)

Bd.5 (850MHz)

Bd.7 (2600MHz)

Bd.8 (900MHz)

Bd.12 (700MHz)

Bd.18 (850MHz)

Bd.19 (850MHz)

Bd.20 (800MHz)

Bd.26 (850MHz)

Bd.28 (700MHz)

Bd.66 (1700MHz)

ALAS5V_HID_v00.030a 2019-03-20

x x x

x x

x x x

x x x

x

x

x x

x

x x

Confidential / Preliminary

x

x

x

x

Page 13

Cinterion® ALAS5V Hardware Interface Description

Page 13 of 124

1.2 Key Features at a Glance

16

Table 1: Supported frequency bands for each product variant

Band ALAS5V-W ALAS5V-CN ALAS5V-E ALAS5V-US

LTE-TDD

Bd.38 (2600MHz) x x

Bd.39 (1900MHz)

Bd.40 (2300MHz)

Bd.41 (2600MHz)

1. Note: Out of the 3GPP specified frequency range for LTE Band 41, only that part which is used in China and

apan (2545MHz to 2655MHz) is supported by ALAS5V. For the US market LTE Band 41 is disabled by

J

software.

1

x x

x x

x x

1.2.2 Supported CA Configurations

The following table lists the supported CA configurations (aka supported band combinations)

for each of the ALAS5V product variants mentioned in Section 1.1.

Table 2: Supported CA configurations

Downlink CA Bandwidth

combination set

Intra-band continuous

CA_1C 0, 1 E, W, CN

CA_2C 0 US

CA_3C 0 E, W, CN

CA_5B 0, 1 US, W

CA_7B 0 E, US, W, CN

CA_7C 0, 1, 2 E, US, W, CN

CA_8B 0 W

CA_12B 0 US

CA_38C 0 W, CN

CA_39C 0 W, CN

CA_40C 0, 1 W, CN

CA_41C 0, 1, 2, 3 CN

CA_66B 0 US

CA_66C 0 US

Intra-band non-continuous

CA_2A-2A 0 US

CA_3A-3A 0, 1, 2 E, W, CN

CA_4A-4A 0, 1 US

CA_7A-7A 0, 1, 2, 3 E, US, W, CN

CA_40A-40A 0, 1 W, CN

CA_41A-41A 0, 1 CN

CA_66A-66A 0 US

CA_66A-66B 0 US

Product variant

(ALAS5V-...)

ALAS5V_HID_v00.030a 2019-03-20

Confidential / Preliminary

Page 14

Cinterion® ALAS5V Hardware Interface Description

1.2 Key Features at a Glance

16

Table 2: Supported CA configurations

Downlink CA Bandwidth

combination set

Inter-band (two bands)

CA_1A-5A 0, 1 W

CA_1A-8A 0, 1, 2 E, W, CN

CA_1A-18A 0, 1 W

CA_1A-19A 0 W

CA_1A-20A 0 E, W

CA_1A-26A 0, 1 W

CA_1A-28A 0, 1 E, W

CA_2A-5A 0, 1 US

CA_2A-5B 0 US

CA_2A-12A 0, 1, 2 US

CA_2A-12B 0 US

CA_2A-28A 0 US

CA_2A-29A 0, 1, 2 US

CA_3A-5A 0, 1, 2, 3,4 W

CA_3A-8A 0, 1, 2, 3 E, W, CN

CA_3A-19A 0 W

CA_3A-20A 0, 1 E, W

CA_3A-26A 0, 1 W

CA_3A-28A 0, 1 E, W

CA_3C-8A 0 CN

CA_4A-5A 0, 1 US

CA_4A-12A 0, 1, 2, 3, 4, 5 US

CA_4A-12B 0 US

CA_4A-28A 0 US

CA_4A-29A 0, 1, 2 US

CA_5A-7A 0, 1 US, W

CA_5A-30A 0 US

CA_5A-40A 0, 1 W

CA_5B-30A 0 US

CA_5A-66A 0 US

CA_5A-66B 0 US

CA_5B-66A 0 US

CA_7A-8A 0, 1, 2 E, W, CN

CA_7A-12A 0 US

CA_7A-20A 0, 1 E, W

CA_7A-28A 0, 1 E, US, W

CA_7B-28A 0 E, US, W

CA_8A-40A 0, 1 W, CN

CA_8A-41A 0, 1 CN

CA_12A-30A 0 US

CA_12A-66A 0, 1, 2, 3, 4, 5 US

Product variant

(ALAS5V-...)

Page 14 of 124

ALAS5V_HID_v00.030a 2019-03-20

Confidential / Preliminary

Page 15

Cinterion® ALAS5V Hardware Interface Description

Power

Supply

IGT

EMERG_OFF

Application Interfaces

ALAS5

Application

VEXT

PWR_IND

GNSS

Application

UICC

SIM

Card

GSM/UMTS/LTE

GPIO

Antenna-

diagnostic

2 x

ADC

I2C

USB

2.0/3.0

I2C

2x

Digital

Audio

GPIO

PCM/I2S

USB

Antenna-

diagnostic

ANT_MAIN ANT_DRX_MIMOGNSS

GPIO

Power

Supply

eMMC

eMMC Interface

Power

Supply

PCIe

PCIe

Serial Interface

ASC0

Serial Interface

ASC1

SIM

Card

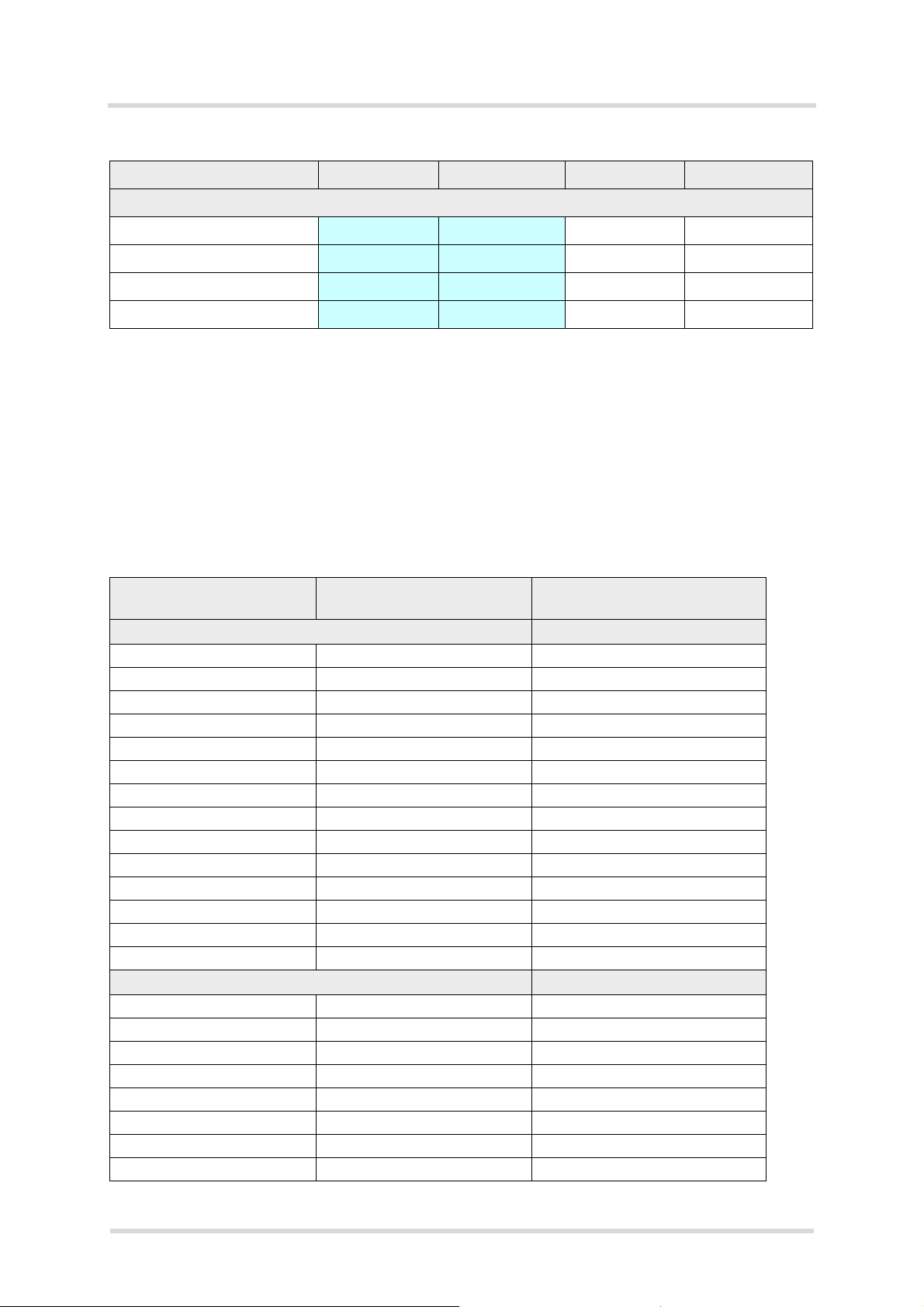

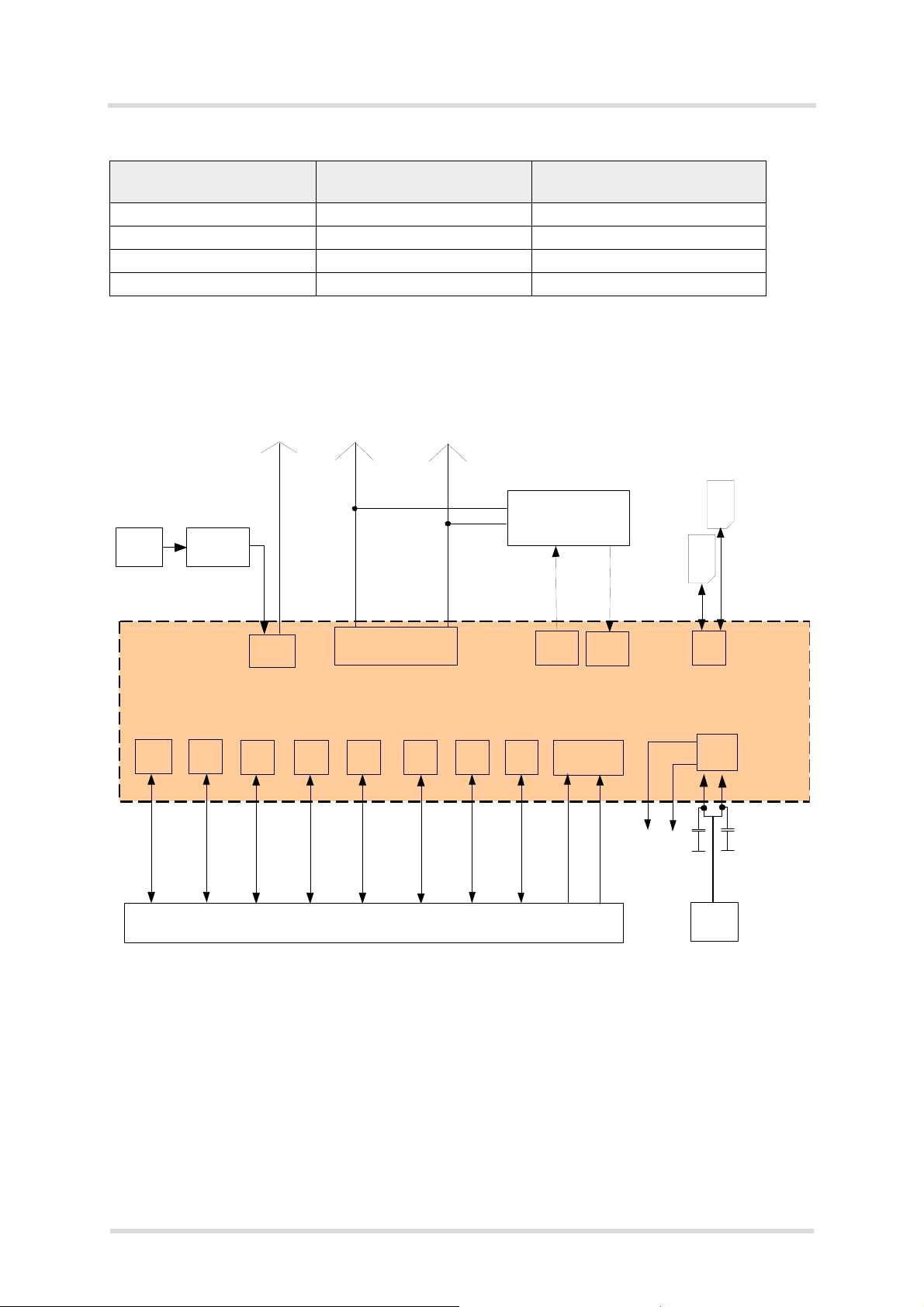

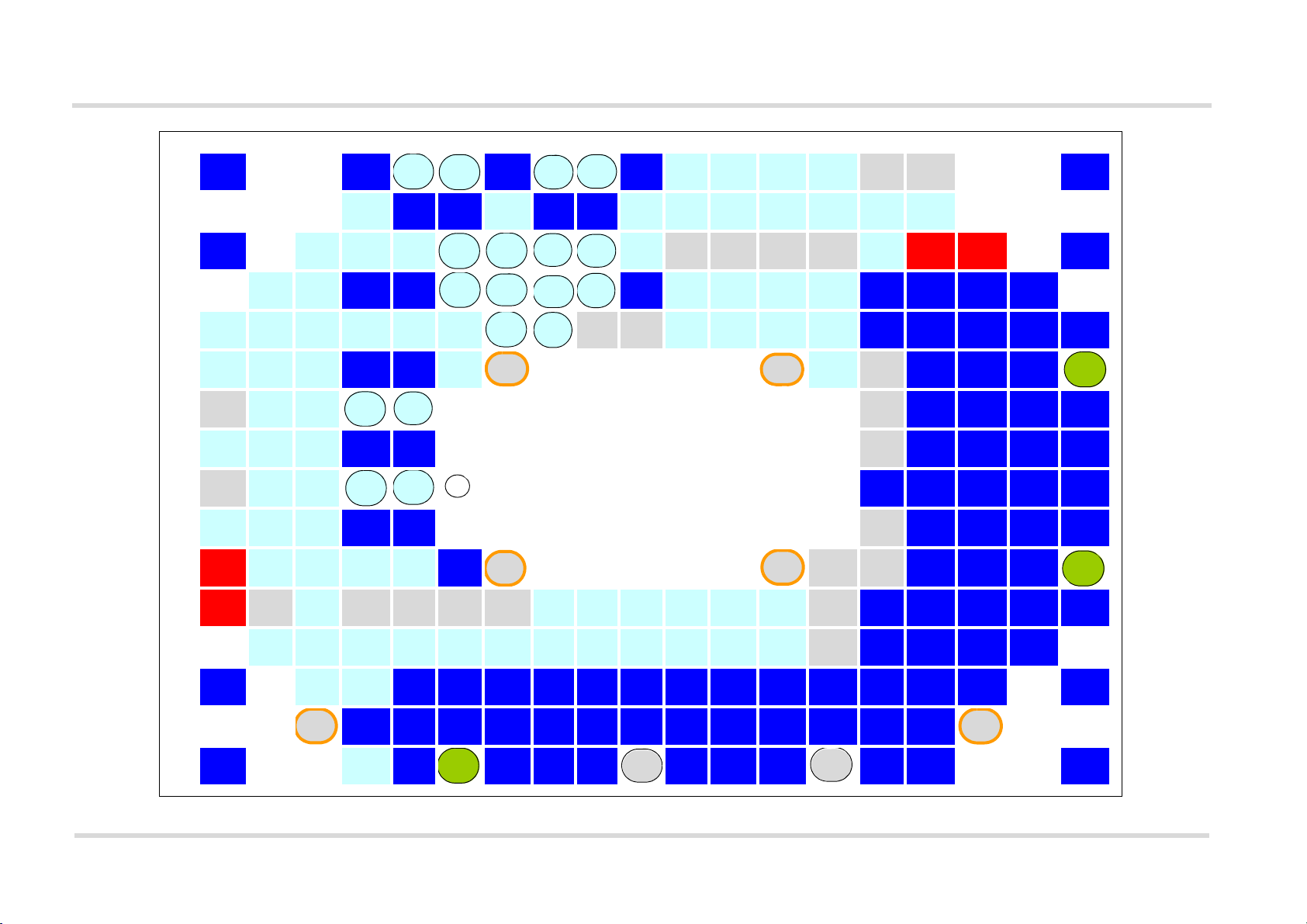

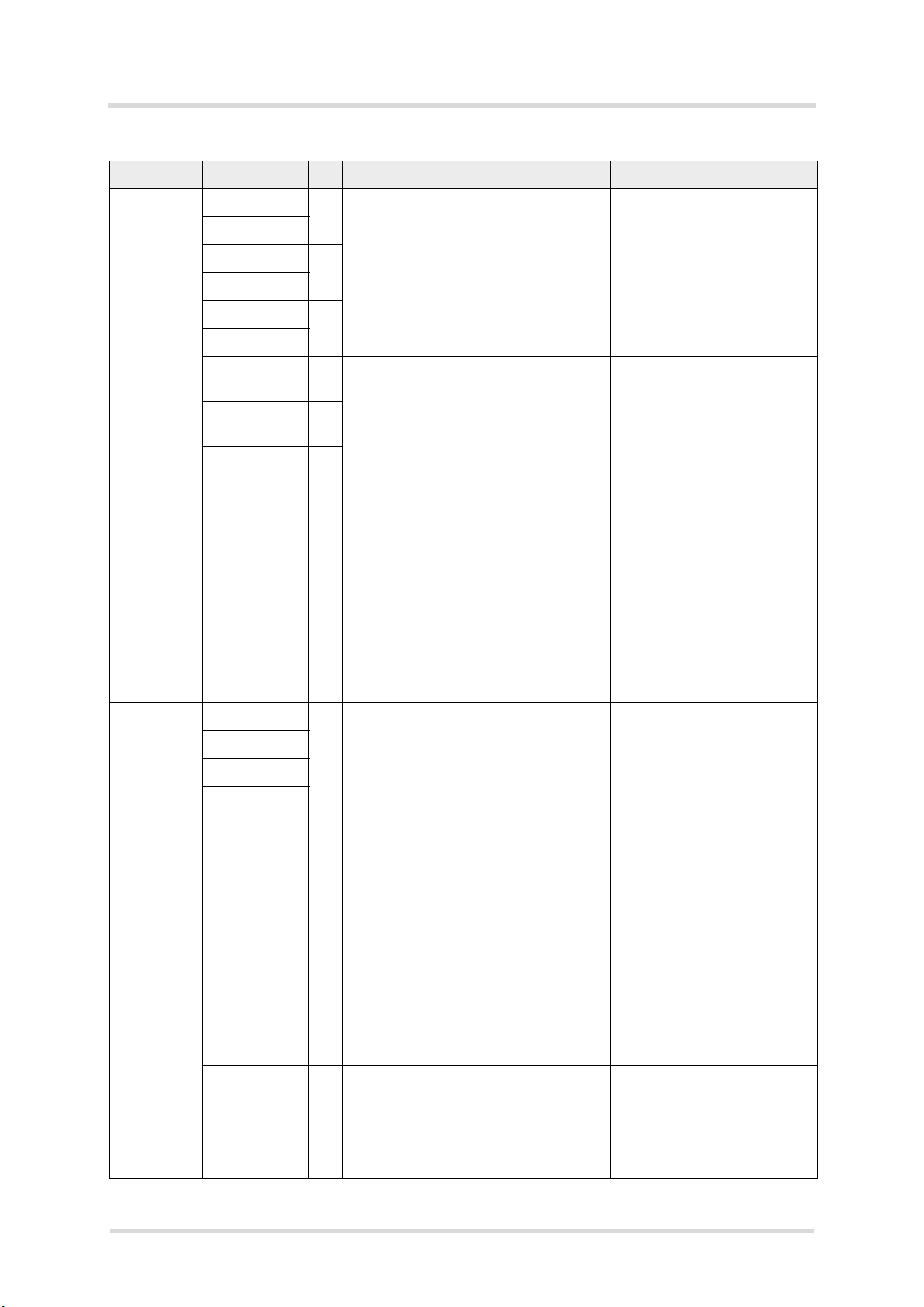

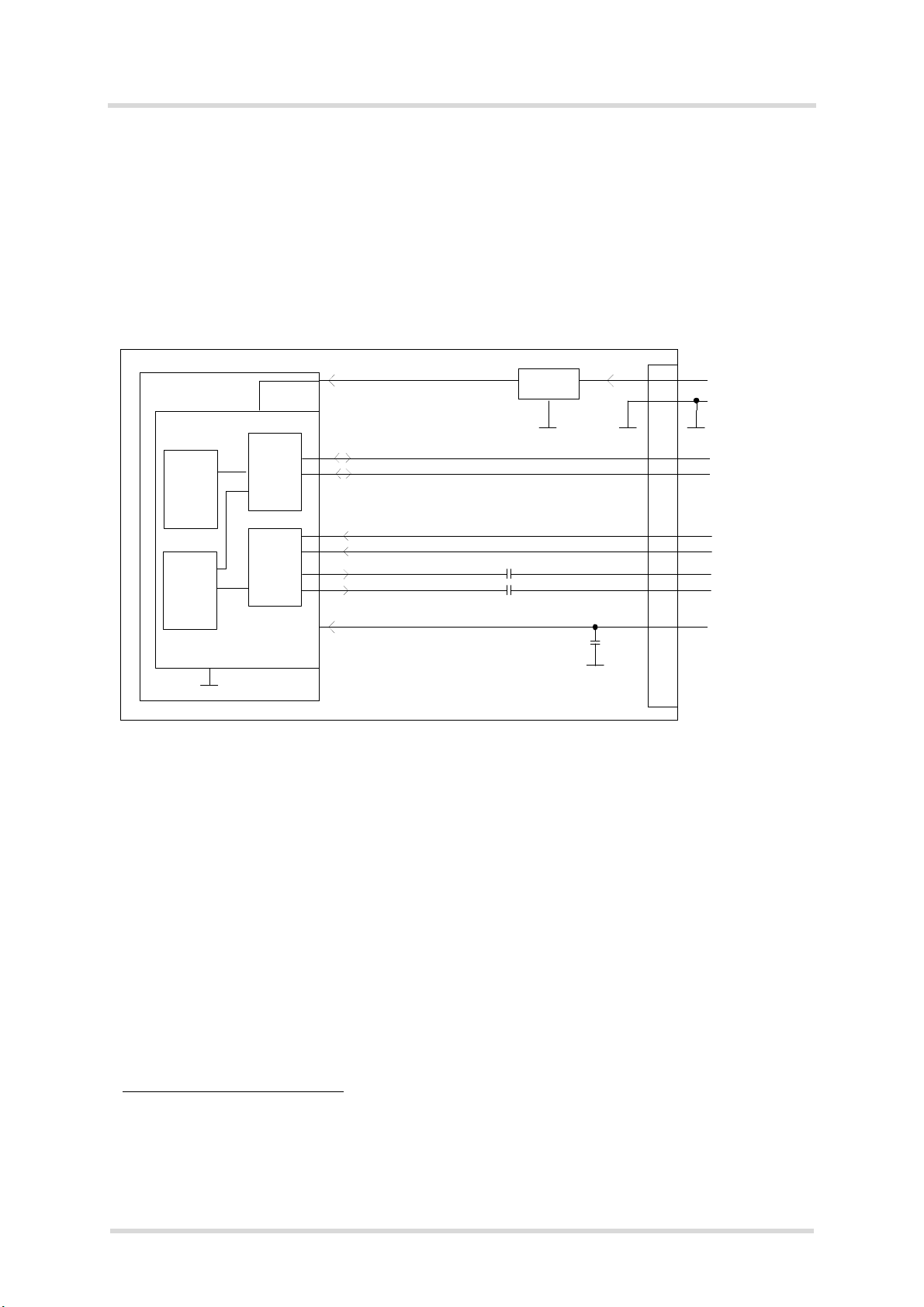

1.3 ALAS5V System Overview

16

Table 2: Supported CA configurations

Downlink CA Bandwidth

combination set

CA_20A-38A 0 W

CA_20A-40A 0 W

CA_28A-40A 0 W

CA_29A-66A 0 US

Product variant

(ALAS5V-...)

1.3 ALAS5V System Overview

Page 15 of 124

Figure 1: ALAS5V system overview

ALAS5V_HID_v00.030a 2019-03-20

Confidential / Preliminary

Page 16

Cinterion® ALAS5V Hardware Interface Description

LPDDR2SDRAM

2GBit

NANDFlash

4GBit

38.4MHz

PowerManagement

Basebandcontroller

RFpart

Clocks

LDO

LDO

LDO

LDO

LDO

S1

S2

S3

S4

S5

PMU

LB/MB /HB

PA

GSM

PA

Filter

&

Switches

QLINK RFFE

EBI 1

EBI 2

GRFC

BATT+

LGAPads

IGT

EMERGO FF

PWR_IND

USB 3.0

USB 2.0

ASC0

ASC1

I2C

2xPCM/I2S

I2S_MCLK

eMMC

2xSIM

GPIO

PCIe

4xADC

ADC

BATT+ _RF

GND

ALAS5

ANT_MAIN

ANT_DRX_

MIMO

ANT_GNSS

GNSS_EN

ANT_GNSS_DC

Page 16 of 124

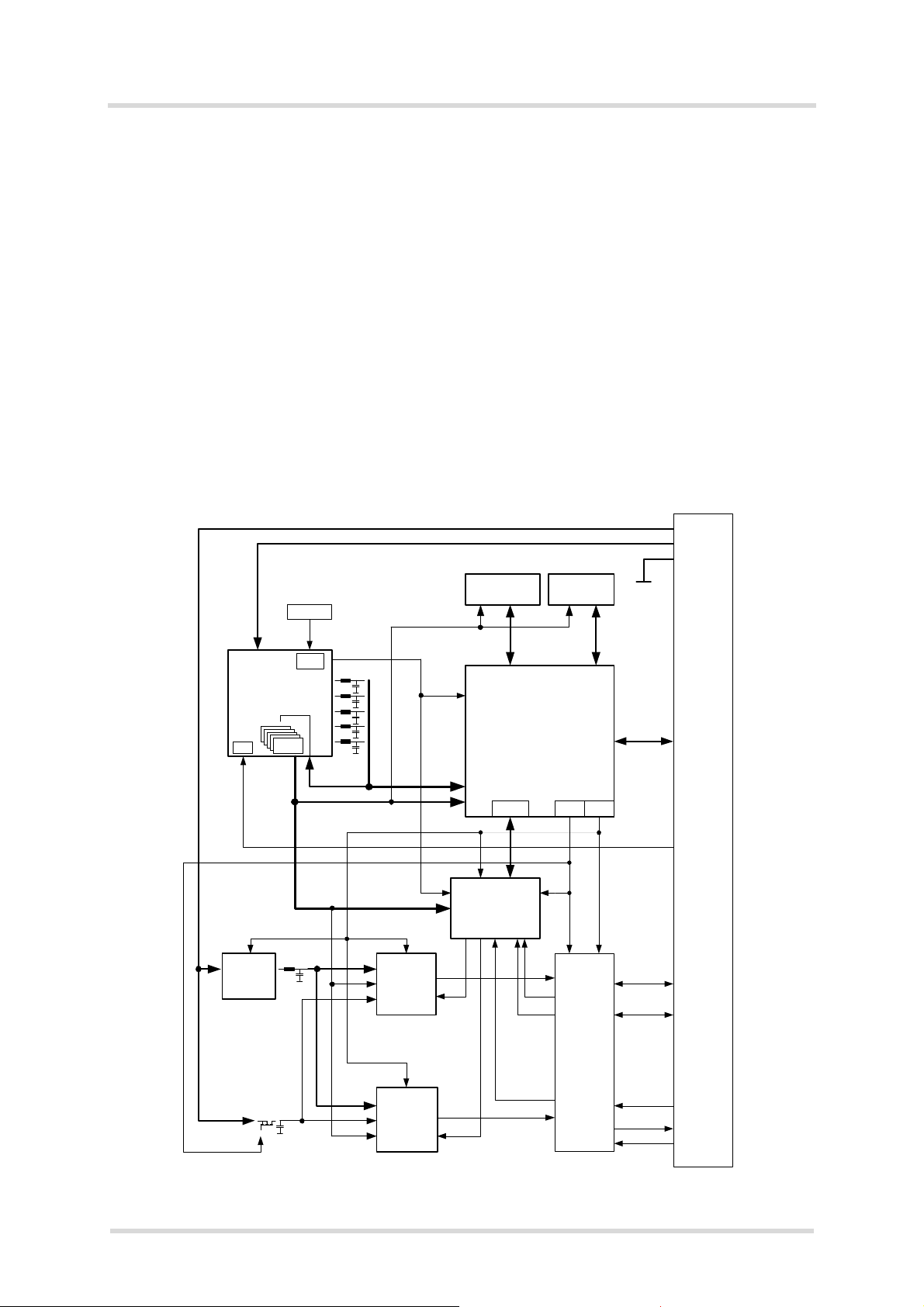

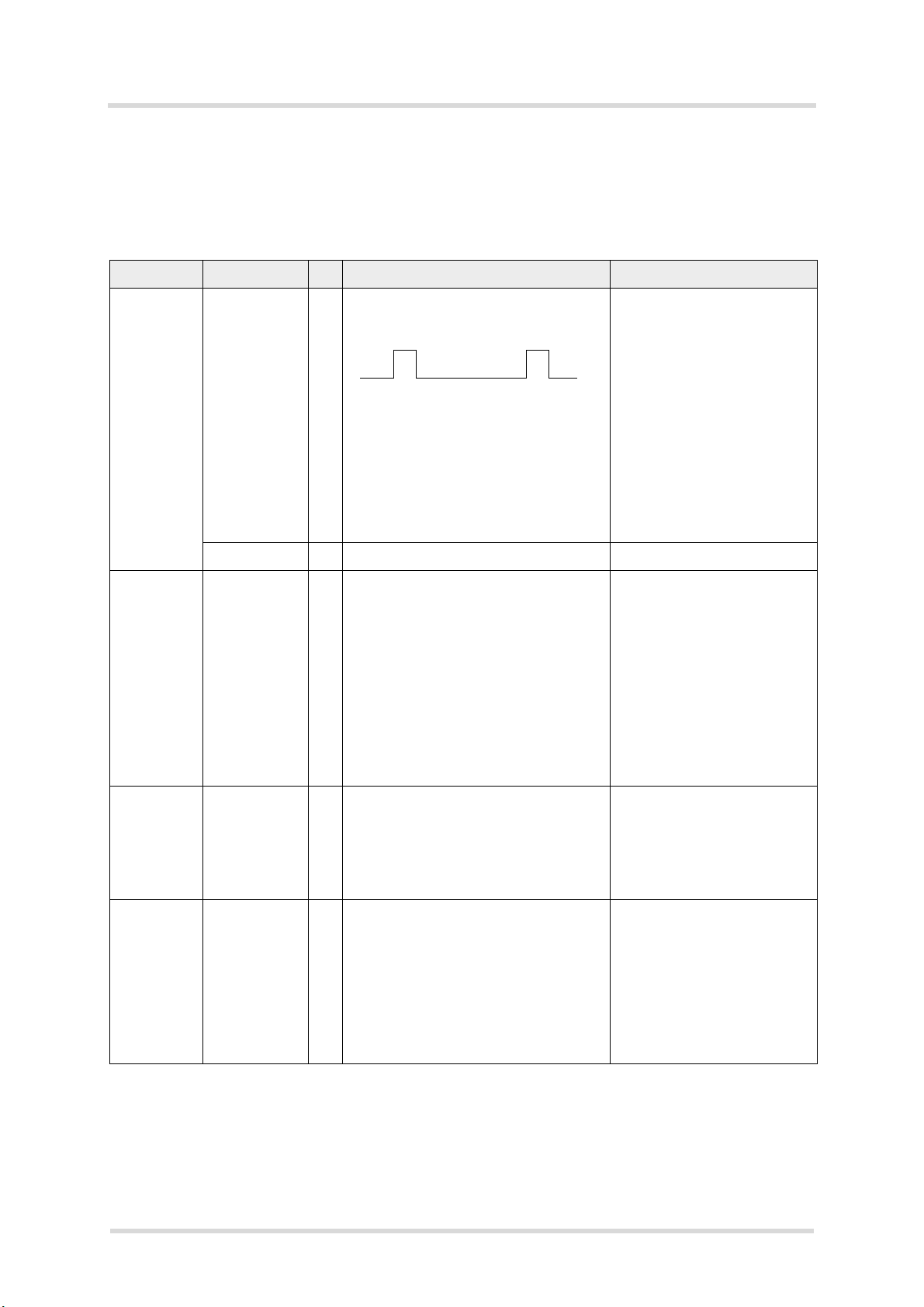

1.4 Circuit Concept

16

1.4 Circuit Concept

Figure 2 shows a block diagram of the ALAS5V module and illustrates the major functional

components:

Baseband block:

• GSM/UMTS/LTE controller/transceiver/power supply

• NAND/LPDDR2 memory devices

• Application interface (SMT with connecting pads)

RF section:

• RF transceiver

• RF power amplifier/frontend

• RF filter

• GNSS receiver/Front end

• Antenna pad

ALAS5V_HID_v00.030a 2019-03-20

Figure 2: ALAS5V block diagram

Confidential / Preliminary

Page 17

Cinterion® ALAS5V Hardware Interface Description

2 Interface Characteristics

67

Page 17 of 124

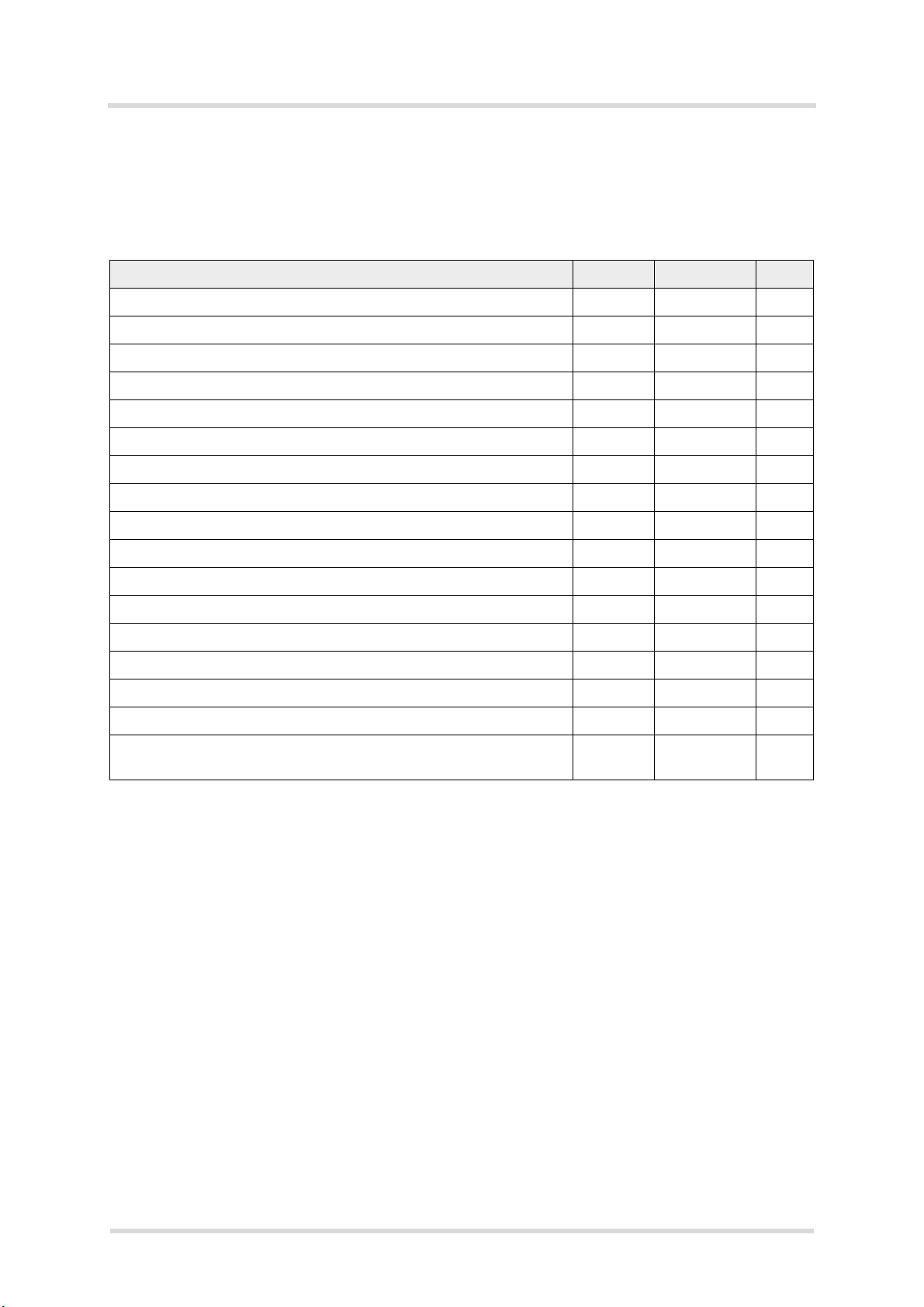

2 Interface Characteristics

ALAS5V is equipped with an SMT application interface that connects to the external application. The SMT application interface incorporates the various application interfaces as well as

the RF antenna interface.

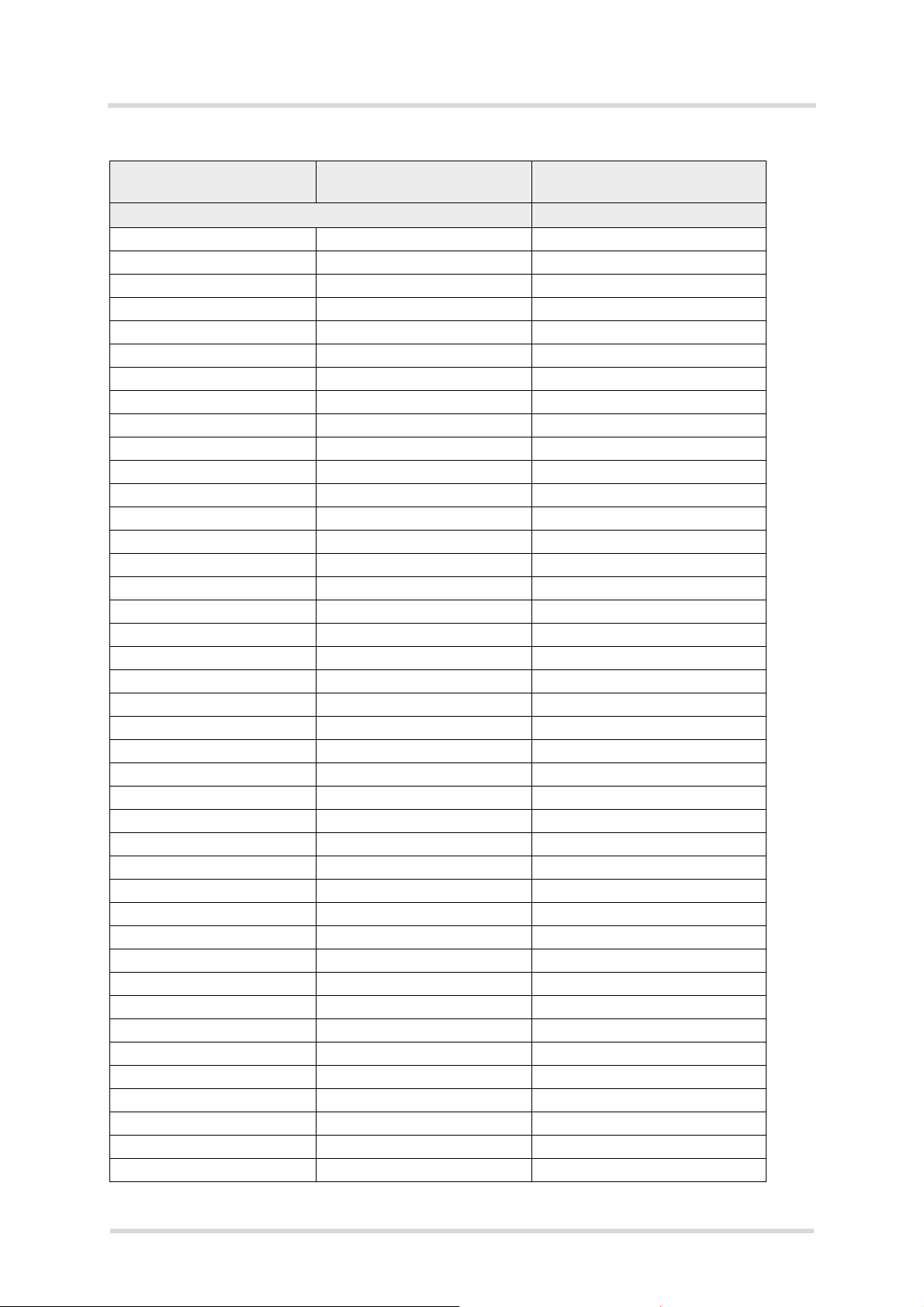

2.1 Application Interface

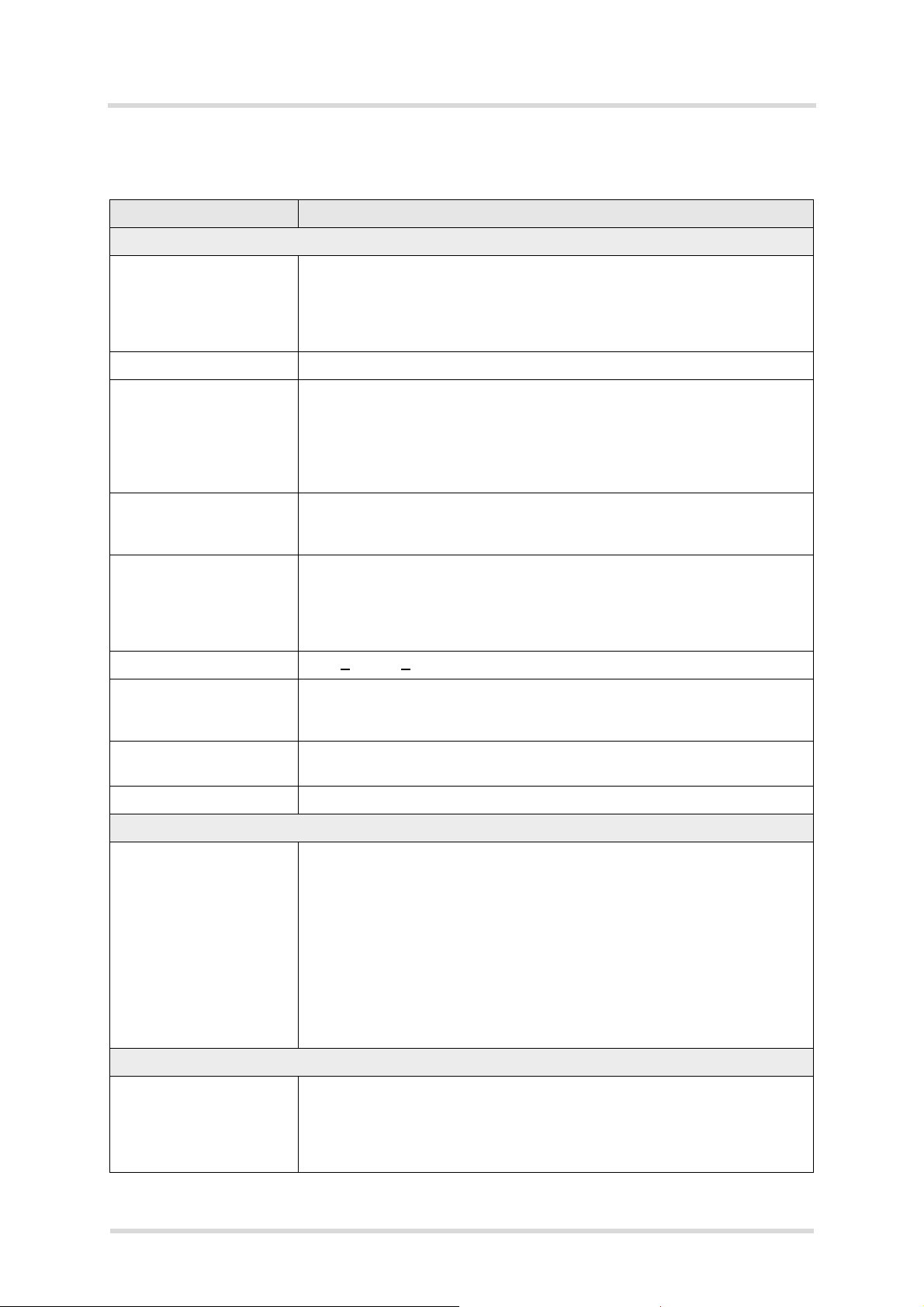

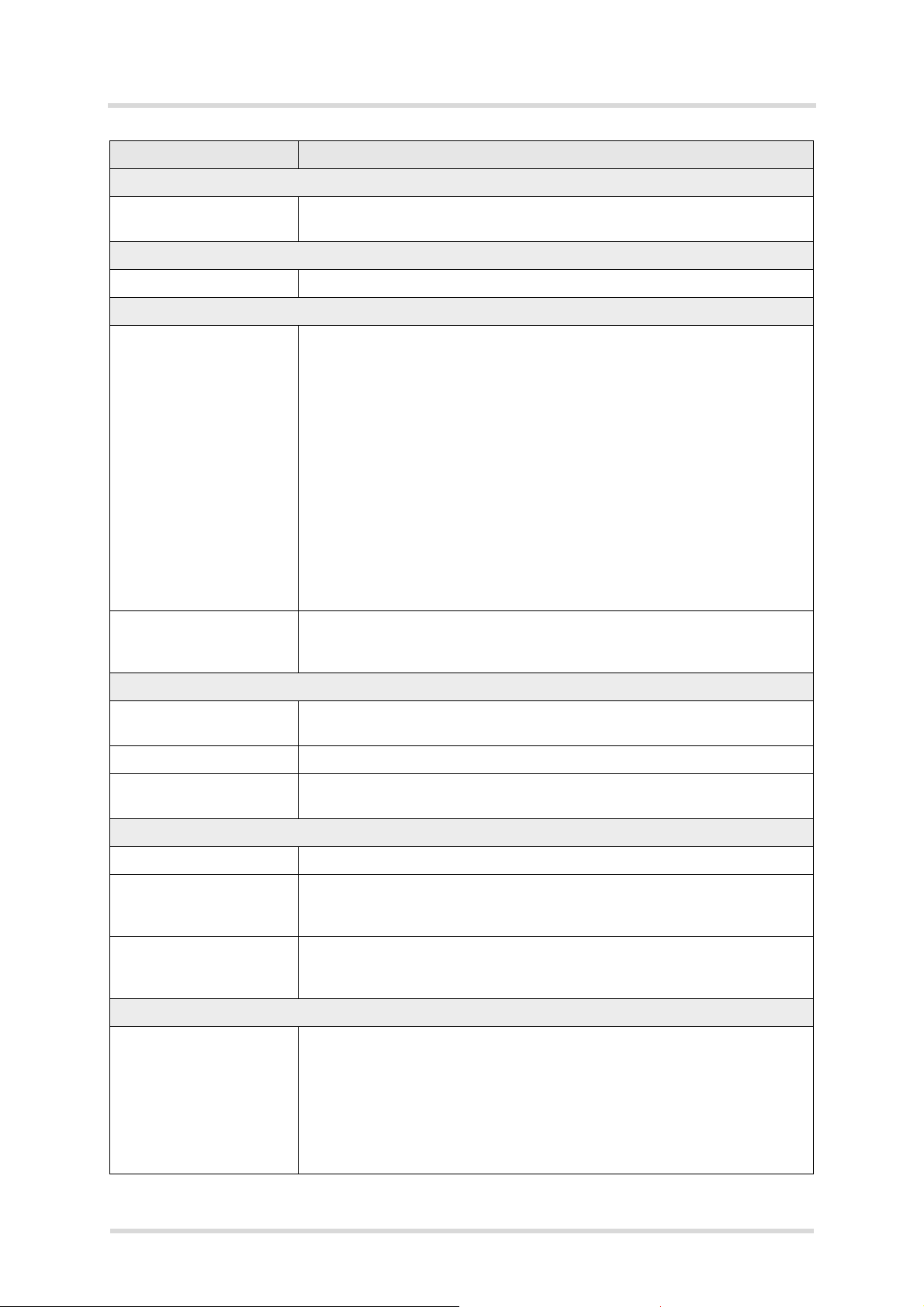

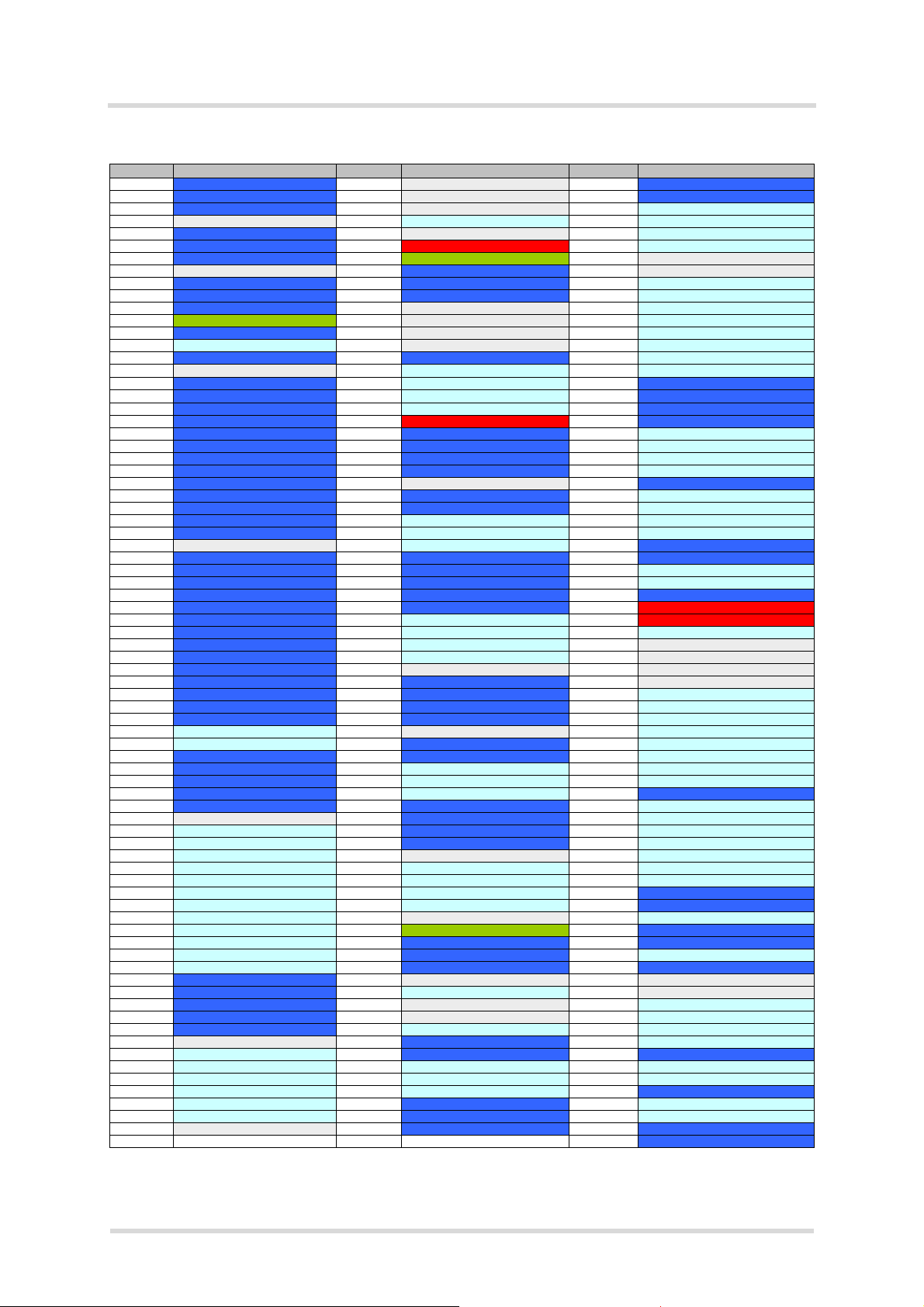

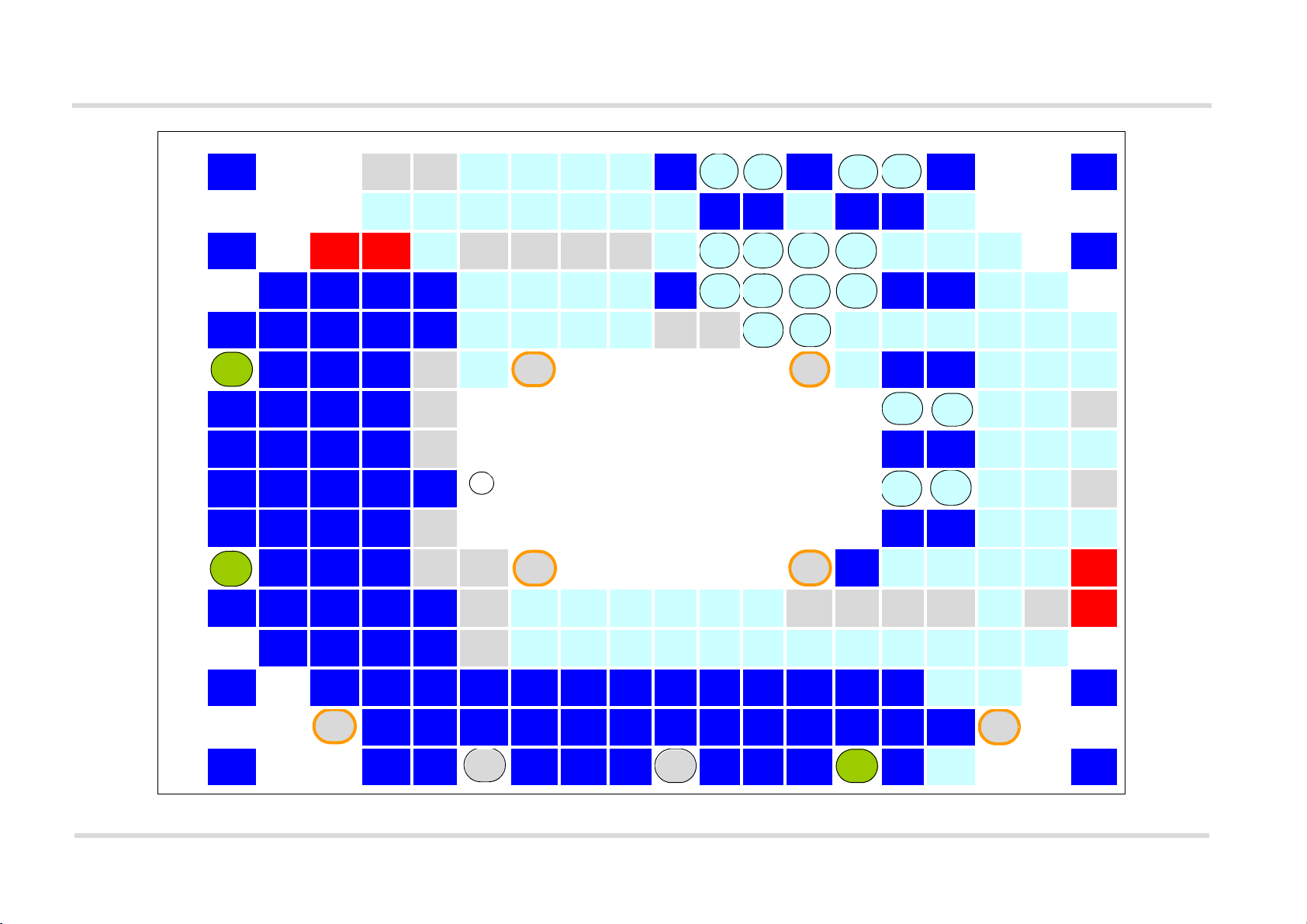

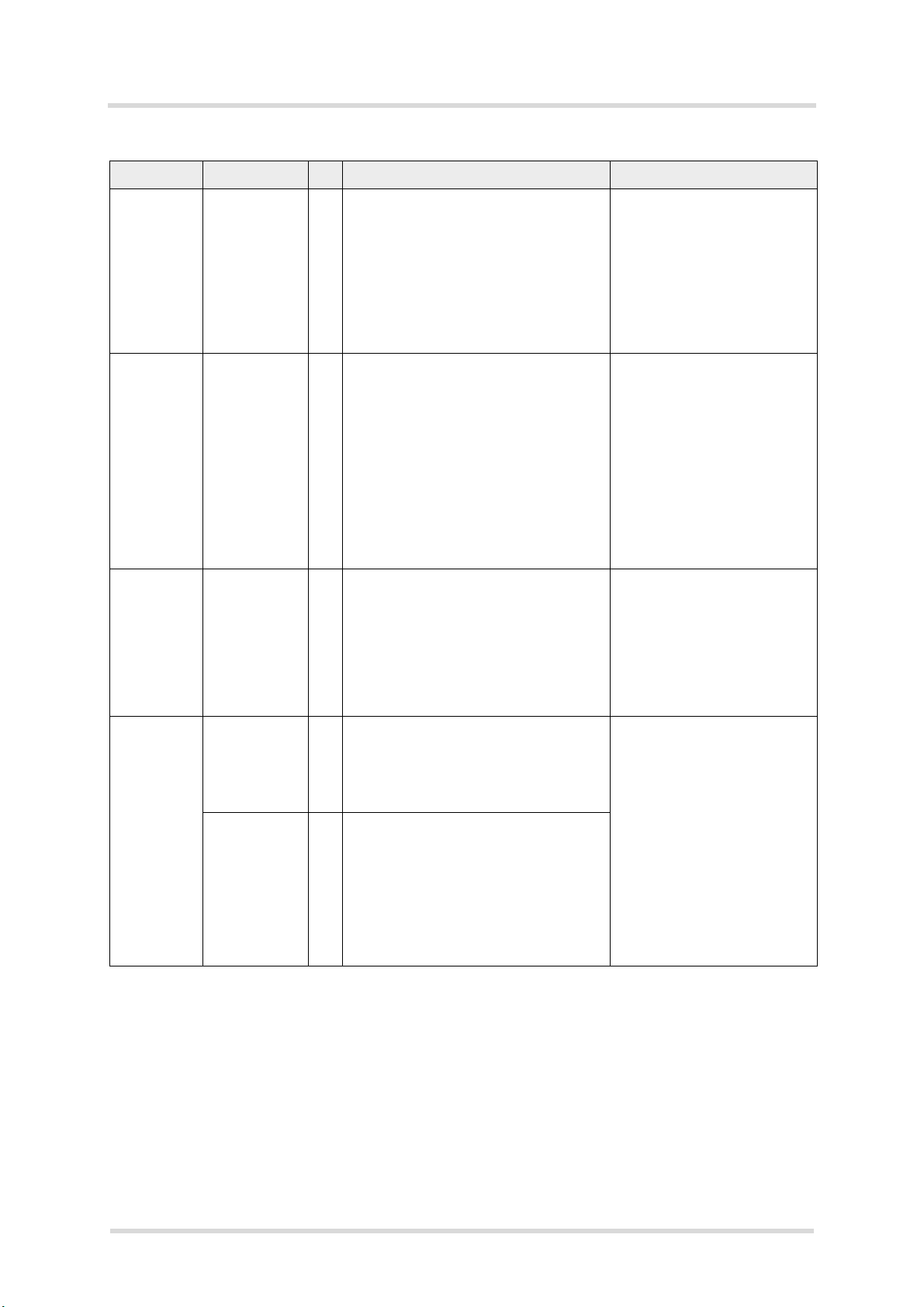

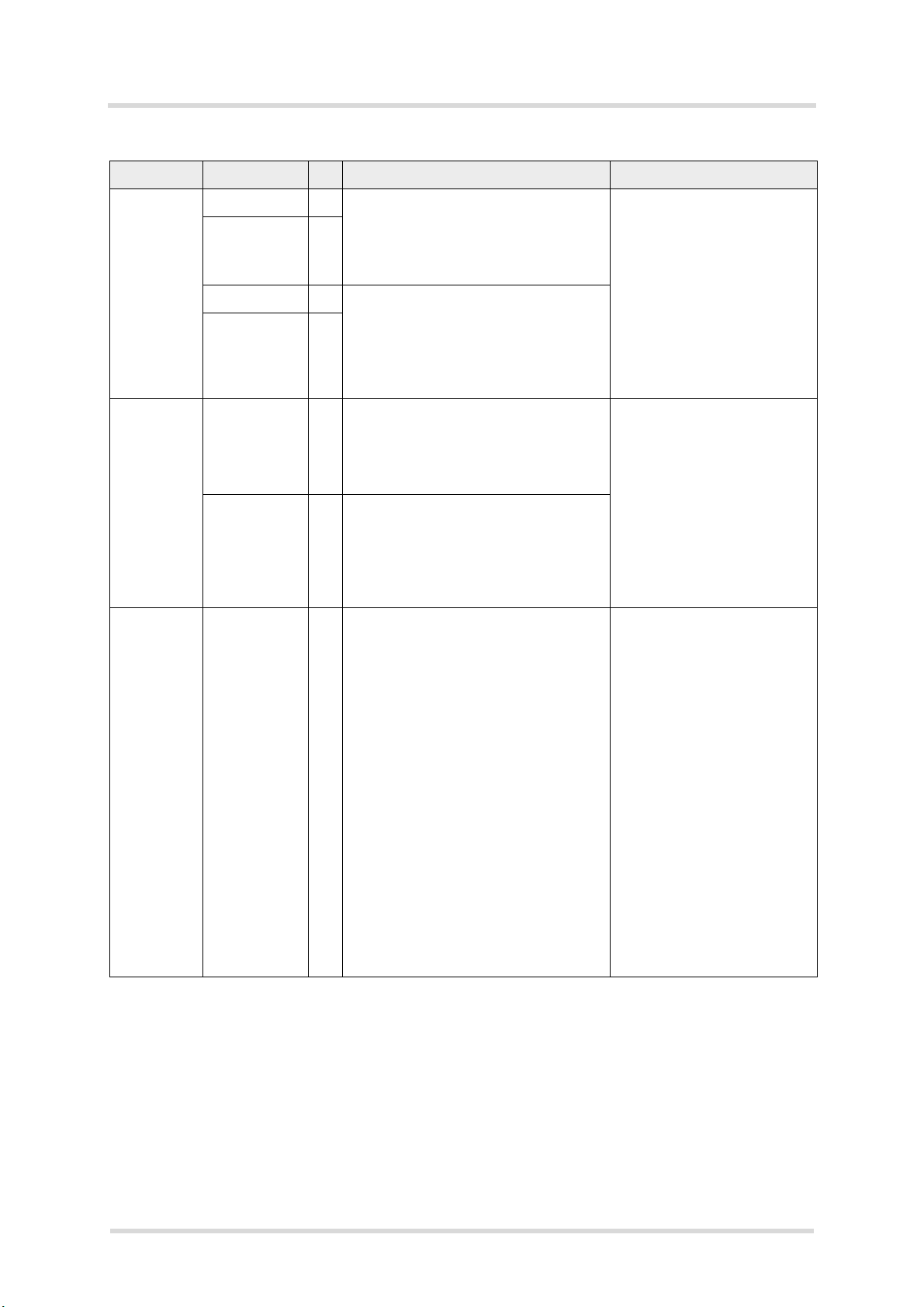

2.1.1 Pad Assignment

The SMT application interface on the ALAS5V provides connecting pads to integrate the module into external applications. Table 3 lists the pads’ assignments. Figure 3 (bottom view) and

Figure 4 (top view) show the connecting pads’ numbering plan.

Please note that a number of connecting pads are marked as reserved for future use (rfu) and

further qualified as either (<name>), (dnu), (GND) or (nc):

• Pads marked as “rfu“ and q ualified as “<name>“ (signal name) may be soldered and could

be connected to an external application compliant to the signals’ electrical characteristics

as described in Table 4.

• Pads marked "rfu" and qualified as "dnu" (do not use) may be soldered but should not be

connected to an external application.

• Pads marked "rfu" and qualified as "GND" (ground) are assigned to ground with ALAS5V

modules, but may have different assignments with future Gemalto M2M p roducts using the

same pad layout.

• Pads marked "rfu" and qualified as "nc" (not connected) are internally not connected with

ALAS5V modules, but may be soldered and arbitrarily be connected to external ground.

Also note that some pads are marked with a circle ( ). These pads have a round shape for

improved impedance control.

Gemalto strongly recommends to solder all connecting pads for mechanical stability and heat

dissipation.

Also, Gemalto strongly recommends to provide test points for certain signal lines to and from

the module while developing SMT applications – for debug and/or test purposes during the

manufacturing process. In this way it is possible to detect soldering problems. Please refer to

[3] for more information on test points and how to implement them. The signal lines for which

test points should be provided for are marked as “Test point required” or “Test point recommended“ in Section 2.1.2: Table 4 describing signal characteristics.

ALAS5V_HID_v00.030a 2019-03-20

Confidential / Preliminary

Page 18

Cinterion® ALAS5V Hardware Interface Description

Page 18 of 124

2.1 Application Interface

67

Table 3: Overview: Pad assignments

Pad No. Signal Name Pad No. Signal Name Pad No. Signal Name

A2 GND E15 rfu (dnu) M5 GND

A5 GND E16 rfu (dnu) M6 GND

A6 GND E17 rfu (dnu) M7 GPIO17

A7 rfu (dnu) E18 VEXT M8 JTAG_WD_DISABLE

A8 GND E19 rfu (dnu) M9 I2CDAT1

A9 GND E20 BATT+ M10 I2CCLK1

A10 GND F2 ANT_DRX_MIMO M11 rfu (d nu )

A11 rfu (dnu) F3 GND M12 rfu (dnu)

A12 GND F4 GND M13 EMMC_D6

A13 GND F5 GND M14 EMMC_D1

A14 GND F6 rfu (dnu) M15 GPIO22

A15 ANT_GNSS F7 rfu (dnu) M16 USB_DP

A16 GND F8 rfu (nc) M17 USB_DN

A17 ANT_GNSS_DC F14 rfu (nc) M18 CCCLK2

A20 GND F15 GND M19 CCCLK1

B4 rfu (dnu)

B5

B6

B7 GND F19 DTR0 N5 GND

B8

B9 GND G2 GND N7 FSC2

B10

B11

B12 GND G5 GND N10 BCLK2

B13

B14

B15 GND G17 GND N13 EMMC_D5

B16 GND G18 DCD0 / Download N14 EMMC_D2

B17 GND G19 CTS0 N15 EMMC_D0

B18 rfu (dnu) G20 RTS0 N16 GND

C2 GND H2 GND N17 GND

C4 GND H3 GND N18 CCIN2

C5 GND H4 GND N19 CCIN1

C6 GND H5 GND P2 GND

C7 GND H6 GND P4 BATT+_RF

C8 GND H16 USB_SSTX_P P5 BATT+_RF

C9 GND H17 USB_SSTX_N P6 GPIO5 (Interrupt)

C10 GND H18 GPIO6 (Interrupt) P7 rfu (DIN1)

C11 GND H19 TXD0 P8 rfu (DOUT1)

C12 GND H20 rfu (BATT_ID) P9 rfu (BCLK1)

C13 GND J2 GND P10 rfu (FSC1)

C14 GND J3 GND P11 MCLK

C15 GND J4 GND P12 EMMC_D7

C16 GND J5 GND P13 EMMC_CMD

C17 GPIO3 (Interrupt) J6 rfu (dnu) P14 EMMC_D3

C18 JTAG_TCK J16 GND P15 EMMC_CLK

C20 GND J17 GND P16 PCIE_CLK_P

D3 GND J18 CCIO2 P17 PCIE_CLK_N

D4 GND J19 CCIO1 P18 VUSB_IN

D5 GND J20 RING0 P20 GND

D6 GND K2 GND R5 PWR_IND

D7

D8

D9 ADC5_IN K5 GND R8 TXD1

D10

D11

D12 GPIO11 K17 USB_SSRX_N R11 PCIE_HOST_RST

D13

D14

D15

D16

D17 JTAG_SRST L3 GND R16 GND

D18 JTAG_TDO L4 GND R17 GPIO16 (Interrupt)

D19 IGT L5 GND T2 GND

E2 GND L6 rfu (dnu) T5 rfu (dnu)

E3 GND L7 EMMC_DETECT T6 rfu (dnu)

E4 GND L8 rfu (nc) T7 FwSwap

E5 GND L14 rfu (nc) T8 TXD2

E6 GND L15 EMMC_PWR T9 GPIO15

E7 rfu (dnu) L16 GND T10 RXD2

E8 GPIO1/ DR_SYNC L17 GND T11 GND

E9 GPIO7 (Interrupt) L18 CCVCC2 T12 PCIE_RX_P

E10 GPIO14 L19 CCRST1 T13 PCIE_RX_N

E11 GPIO13 L20 GPIO4 T14 GND

E12 GPIO12 M2 GND T15 PCIE_TX_P

E13 JTAG_PS_HOLD M3 GND T16 PCIE_TX_N

E14 rfu (dnu) M4 GND T17 GND

GND F17 DSR0 N3 GND

GND F18 RXD0

GND F20 BATT+ N6 GND

GND G3 GND N8 DOUT2

GND G4 GND N9 DIN2

GND G6 rfu (dnu) N11 GND

GND G16 GND N12 EMMC_D4

rfu (dnu) K3 GND R6 RTS1

ADC4_IN K4 GND R7 CTS1

ADC1_IN K6 rfu (dnu) R9 RXD1

ADC2_IN K16 USB_SSRX_P R10 PCIE_HOST_WAKE

GNSS_EN K18 CCRST2 R12 GND

JTAG_TMS K19 CCVCC1 R13 GND

JTAG_TRST K20 rfu (dnu) R14 PCIE_CLK_REQ

JTAG_TDI L2 ANT_MAIN R15 GND

F16 EMERG_OFF

M20 GPIO8 (Interrupt)

N4 GND

T20 GND

ALAS5V_HID_v00.030a 2019-03-20

Confidential / Preliminary

Page 19

Cinterion® ALAS5V Hardware Interface Description

2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20

T

GND rfu

(dnu)

rfu

(dnu)

FwSwap TXD2 GPIO15 RXD2 GND

PCIE_

RX_P

PCIE_

RX_N

GND

PCIE_

TX_P

PCIE_

TX_N

GND GND

R

PWR_

IND

RTS1 CTS1 TXD1 RXD1 PCIE_

HOST_

WAKE

PCIE_

HOST_

RST

GND GND PCIE_

CLK_

REQ

GND GND GPIO16

(Interrupt)

P

GND BATT+_RFBATT+_RFGPIO5

(Inter-

rupt)

rfu

(DIN1)

rfu

(DOUT1)

rfu

(BCLK1)

rfu

(FSC1)

MCLK

EMMC_D7EMMC_

CMD

EMMC_D3EMMC_

CLK

PCIE_CLK_P

PCIE_

CLK_N

VUSB_

IN

GND

N

GND GND GND GND FSC2 DOUT2 DIN2 BCLK2 GND

EMMC_D4EMMC_

D5

EMMC_D2EMMC_

D0

GND GND CCIN2 CCIN1 GND

M

GND GND GND GND GND GPIO17 JTAG_

WD_

DISABLE

I2CDAT1 I2CCLK1 rfu

(dnu)

rfu

(dnu)

EMMC_D6EMMC_

D1

GPIO22 USB_DP USB_DN CCCLK2 CCCLK1 GPIO8

(Interrupt)

L

ANT_

MAIN

GND GND GND rfu

(dnu)

EMMC_

DETECT

rfu

(nc)

rfu

(nc)

EMMC_

PWR

GND GND CCVCC2 CCRST1 GPIO4

K

GND GND GND GND rfu

(dnu)

USB_

SSRX_P

USB_

SSRX_N

CCRST2 CCVCC1 rfu

(dnu)

J

GND GND GND GND rfu

(dnu)

GND GND CCIO2 CCIO1 RING0

H

GND GND GND GND GND

USB_

SSTX_P

USB_

SSTX_N

GPIO6

(Inter-

rupt)

TXD0 rfu

(BATT_

ID)

G

GND GND GND GND rfu

(dnu)

GND GND DCD0 /

Down-

load

CTS0 RTS0

F

ANT_

DRX_

MIMO

GND GND GND rfu

(dnu)

rfu

(dnu)

rfu

(nc)

rfu

(nc)

GND EMERG

_OFF

DSR0 RXD0 DTR0 BATT+

E

GND GND GND GND GND rfu

(dnu)

GPIO1 /

DR_SYNC

GPIO7

(Inter-

rupt)

GPIO14 GPIO13 GPIO12 JTAG_

PS_

HOLD

rfu

(dnu)

rfu

(dnu)

rfu

(dnu)

rfu

(dnu)

VEXT rfu

(dnu)

BATT+

D

GND GND GND GND rfu

(dnu)

ADC4_IN ADC5_IN ADC1_INADC2_INGPIO11 GNSS_ENJTAG_

TMS

JTAG_

TRST

JTAG_

TDI

JTAG_

SRST

JTAG_

TDO

IGT

C

GND GND GND GND GND GND GND GND GND GND GND GND GND GND GPIO3

(Interrupt)

JTAG_

TCK

GND

B

rfu

(dnu)

GND GND GND GND GND GND GND GND GND GND GND GND GND

rfu

(dnu)

A

GND GND GND

rfu

(dnu)

GND GND GND

rfu

(dnu)

GND GND GND

ANT_

GNSS

GND ANT_

GNSS_

DC

GND

rfu: Reserved for future use (may be connected to external application

(nc): Internally not connected (may be arbitrarily connected to external GND)

(dnu): Do not use (should not be connected to external application)

Circle marks round shaped pads designed for improved impedance.

Orange: Keep out areas on external application’s PCB.

Round shaped: No solder pads, should therefore not be soldered. No further tracks on PCB’s first layer.

2.1 Application Interface

67

Page 19 of 124

ALAS5V_HID_v00.030a 2019-03-20

Figure 3: ALAS5V bottom view: Pad assignments

Confidential / Preliminary

Page 20

Cinterion® ALAS5V Hardware Interface Description

20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2

T

GND GND

PCIE_

TX_N

PCIE_

TX_P

GND

PCIE_

RX_N

PCIE_

RX_P

GND RXD2 GPIO15 TXD2 FwSwap rfu

(dnu)

rfu

(dnu)

GND

R

GPIO16

(Interrupt)

GND GND PCIE_

CLK_

REQ

GND GND PCIE_

HOST_

RST

PCIE_

HOST_

WAKE

RXD1 TXD1 CTS1 RTS1 PWR_

IND

P

GND VUSB_INPCIE_

CLK_N

PCIE_CLK_P

EMMC_

CLK

EMMC_D3EMMC_

CMD

EMMC_

D7

MCLK rfu

(FSC1)

rfu

(BCLK1)

rfu

(DOUT1)

rfu

(DIN1)

GPIO5

(Inter-

rupt)

BATT+_RFBATT+_

RF

GND

N

GND CCIN1 CCIN2 GND GND

EMMC_D0EMMC_D2EMMC_D5EMMC_

D4

GND BCLK2 DIN2 DOUT2 FSC2 GND GND GND GND

M

GPIO8

(Interrupt)

CCCLK1 CCCLK2 USB_DN USB_DP GPIO22

EMMC_D1EMMC_

D6

rfu

(dnu)

rfu

(dnu)

I2CCLK1 I2CDAT1 JTAG_

WD_

DISABLE

GPIO17 GND GND GND GND GND

L

GPIO4 CCRST1 CCVCC2 GND GND EMMC_

PWR

rfu

(nc)

rfu

(nc)

EMMC_

DETECT

rfu

(dnu)

GND GND GND

ANT_

MAIN

K

rfu

(dnu)

CCVCC1 CCRST2

USB_

SSRX_N

USB_

SSRX_P

rfu

(dnu)

GND GND GND GND

J

RING0 CCIO1 CCIO2 GND GND rfu

(dnu)

GND GND GND GND

H

rfu

(BATT_

ID)

TXD0 GPIO6

(Inter-

rupt)

USB_

SSTX_N

USB_

SSTX_P

GND GND GND GND GND

G

RTS0 CTS0 DCD0 /

Down-

load

GND GND rfu

(dnu)

GND GND GND GND

F

BATT+ DTR0 RXD0 DSR0 EMERG

_OFF

GND

rfu

(nc)

rfu

(nc)

rfu

(dnu)

rfu

(dnu)

GND GND GND

ANT_

DRX_

MIMO

E

BATT+ rfu

(dnu)

VEXT rfu

(dnu)

rfu

(dnu)

rfu

(dnu)

rfu

(dnu)

JTAG_

PS_

HOLD

GPIO12 GPIO13 GPIO14 GPIO7

(Inter-

rupt)

GPIO1 /

DR_SYNC

rfu

(dnu)

GND GND GND GND GND

D

IGT JTAG_

TDO

JTAG_

SRST

JTAG_

TDI

JTAG_

TRST

JTAG_

TMS

GNSS_ENGPIO11 ADC2_INADC1_INADC5_IN ADC4_IN rfu

(nc)

GND GND GND GND

C

GND JTAG_

TCK

GPIO3

(Interrupt)

GND GND GND GND GND GND GND GND GND GND GND GND GND GND

B

rfu

(dnu)

GND GND GND GND GND GND GND GND GND GND GND GND GND

rfu

(dnu)

A

GND ANT_

GNSS_

DC

GND

ANT_

GNSS

GND GND GND

rfu

(nc)

GND GND GND

rfu

(nc)

GND GND GND

rfu: Reserved for future use (may be connected to external application

(nc): Internally not connected (may be arbitrarily connected to external GND)

(dnu): Do not use (should not be connected to external application)

Circle marks round shaped pads designed for improved impedance.

Orange: Keep out areas on external application’s PCB.

Round shaped: No solder pads, should therefore not be soldered. No further tracks on PCB’s first layer.

2.1 Application Interface

67

Page 20 of 124

ALAS5V_HID_v00.030a 2019-03-20

Figure 4: ALAS5V top view: Pad assignments

Confidential / Preliminary

Page 21

Cinterion® ALAS5V Hardware Interface Description

Page 21 of 124

2.1 Application Interface

67

2.1.2 Signal Properties

Please note that the reference voltages listed in Table 4 are the values measured directly on

the ALAS5V module. They do not apply to the accessories connected.

Table 4: Signal description

Function Signal name IO Signal form and level Comment

Power supply

External

supply voltage

BATT+

BATT+_RF

IV

max = 4.2V

I

V

min = 3.3V (on board)

I

Supply voltage lines for general power management and

the RF power amplifier.

Lines of BATT+/BATT+_RF

n Tx = n x 577µs peak current every

4.615ms

Imax = see Table 25

WCDMA TX continuous current

Imax = see Table 25

LTE TX continuous current

Imax = see Table 25

and GND respectively must

be connected in parallel for

supply purposes because

higher peak currents may

occur.

Minimum voltage must not

fall below 3.3V including

drop, ripple, spikes.

GND Ground Application Ground

VEXT O C

max = 1µF

L

VEXT may be used for application circuits.

V

= 1.80V -2.4%, +2%

O

If unused keep line open.

Normal operation:

I

max = -50mA

O

Test point recommended.

The external digital logic

SLEEP mode operation:

I

max = -1mA

O

must not cause any spikes

or glitches on voltage VEXT.

Supply voltage for

active

GNSS

antenna

(Input)

External

GNSS supply voltage

enable

(output)

ANT_GNSS_DCIV

max = 5V

I

Imax = 50mA

GNSS_EN O V

max = 0.45V at I = 2mA

OL

V

nom = 0.1V at I = 100µA

OL

V

OH

V

OH

V

OH

min = 1.30V at I = -2mA

nom = 1.65V at I = -100µA

max = 1.84V

Do not exceed I

max in any

O

operation mode.

If unused connect to GND.

The input current must be

limited to 50mA (antenna

short circuit protection).

Enable signal for an external

voltage regulator (intended

for active GNSS antenna,

high=active).

No external pull-up allowed

during startup until the mod-

ule has been secured in fac-

tory.

ALAS5V_HID_v00.030a 2019-03-20

Confidential / Preliminary

Page 22

Cinterion® ALAS5V Hardware Interface Description

2.1 Application Interface

67

Table 4: Signal description

Function Signal name IO Signal form and level Comment

Page 22 of 124

Ignition IGT I R

Emergency off

Firmware

EMERG_

IR

OFF

FwSwap I V

switch

200k

PU

V

max = 1.84V

OH

V

max =2.00V

IH

V

min = 1.30V

IH

V

max = 0.50V

IL

Low impulse width > 100ms

40k

PU

V

max = 1.84V

OH

V

max = 2.00V

IH

V

min = 1.30V

IH

V

max = 0.50V

IL

~~|___|~~

low impulse width up to 2000ms

(as long as PWR_IND stays low)

max = 0.50V

IL

V

min = 1.30V

IH

V

max = 2.0V

IH

I

= 27.5µA…97.5µA

IHPD

I

= -27.5µA…-97.5µA

ILPU

I

High-Z max

= ±1µA

This signal switches the

module on.

It is required to drive this line

low by an open drain or open

collector driver connected to

GND.

Test point recommended.

It is required to drive this line

low by an open drain or open

collector driver connected to

GND until the module finally

switches off.

If unused keep line open.

Test point recommended.

Note that a low impulse of

more than 2000ms will reset

the module’s RTC.

Input during the startup

phase:

If FwSwap's state is High, a

switch to the possible other,

and currently not active firm-

ware image is triggered.

SIM card

detection

CCIN1 I R

V

V

V

V

CCIN2 I V

V

V

I

24kto VEXT

PU

max=1.84V

OH

min = 1.25V at -25µA

IH

max= 2.0V

IH

max = 0.35V at -60µA

IL

(max) = 0.5V

IL

(min) = 1.30V

IH

(max) = 2.0V

IH

(max) = ±1µA

High-Z

Test point required.

CCIN = Low means SIM

card inserted.

If SIM card holder does not

support CCINx, connect to

GND.

CCIN2: External pull-up

required - for details please

refer to Section 2.1.7.

nd

If 2

SIM interface not used,

keep line open.

ALAS5V_HID_v00.030a 2019-03-20

Confidential / Preliminary

Page 23

Cinterion® ALAS5V Hardware Interface Description

2.1 Application Interface

67

Table 4: Signal description

Function Signal name IO Signal form and level Comment

Page 23 of 124

2.85V SIM

card interfaces

1.8V SIM

card interface

CCRST1

CCRST2

CCCLK1

CCCLK2

CCIO1

CCIO2

CCVCC1

CCVCC2

CCRST1

CCRST2

CCCLK1

CCCLK2

CCIO1

CCIO2

OV

OL

V

OL

V

OH

V

OH

V

OH

I/O R

PU

V

IL

V

IH

V

IH

V

OL

V

OL

V

OH

V

OH

OV

O

V

O

V

O

I

max = -50mA

O

OV

OL

V

OL

V

OH

V

OH

V

OH

I/O R

PU

V

IL

V

IH

V

IH

max = 0.4V at I = 2mA

nom = 0.1V at I = 100µA

min = 2.2V at I = -2mA

nom = 2.65V at I = -100µA

max = 2.91V

6.7..8.5k

max = 0.55V

min = 2.35V

max = 3.05V

max = 0.4V at I = 2mA

nom = 0.1V at I = 100µA

min = 2.35V at I > -45µA

max = 2.91V

min = 2.75V

typ =2.85V

max = 2.91V

max = 0.4V at I = 2mA

nom = 0.1V at I = 100µA

min = 1.40V at I = -2mA

min = 1.65V at I = -100µA

max = 1.84V

6.7..8.5k

max = 0.30V

min = 1.30V

max = 1.84V

Maximum cable length or

copper track should be not

longer than 100mm to SIM

card holder.

CCIO2: External 10kW pull-

up required - for details

please refer to Section 2.1.7.

If unused keep lines open.

Maximum cable length or

copper track should be not

longer than 100mm to SIM

card holder.

CCIO2: External 10kW pull-

up required - for details

please refer to Section 2.1.7.

If unused keep lines open.

SIM interface shutdown

Serial

Modem

Interface

ASC0

V

max = 0.4V at I = 2mA

OL

V

nom = 0.1V at I = 100µA

OL

V

min = 1.40V at I > -50µA

OH

max = 1.84V

V

OH

CCVCC1

CCVCC2

OV

O

V

O

V

O

I

max = -50mA

O

min = 1.74V

typ = 1.80V

max = 1.84V

BATT_ID I External pull up to VEXT and pull

down resistor within battery case

RXD0 O V

CTS0 O

DSR0 O

RING0 O

required. R

max = 0.45V at I = 2mA

OL

V

nom = 0.1V at I = 100µA

OL

V

min = 1.30V at I = -2mA

OH

V

nom = 1.65V at I = -100µA

OH

V

max = 1.84V

OH

= 100kRPD = 10k

PU

DCD0 I/O

TXD0 I V

RTS0 I

DTR0 I

max = 0.50V

IL

min = 1.30V

V

IH

V

max = 2.0V

IH

I

= 27.5µA…97.5µA

IHPD

= -27.5µA…-97.5µA

I

ILPU

I

High-Z max

= ±1µA

Reserved for future use.

Connect line to GND.

Test points recommended

for TXD0, RXD0, DCD0,

RTS0, and CTS0.

If DCD0 is driven low during

startup-phase, module

enters Download Mode (see

Section 4.2.2)

If unused keep line open.

ALAS5V_HID_v00.030a 2019-03-20

Confidential / Preliminary

Page 24

Cinterion® ALAS5V Hardware Interface Description

2.1 Application Interface

67

Table 4: Signal description

Function Signal name IO Signal form and level Comment

Page 24 of 124

Serial

Modem

Interface

ASC1

Serial

Debug

Interface

ASC2

(Gemalto

internal)

Power indicator

RXD1 O V

CTS1 O

TXD1 I V

RTS1 I

RXD2 O V

TXD2 I V

PWR_IND O V

max = 0.45V at I = 2mA

OL

V

nom = 0.1V at I = 100µA

OL

V

min = 1.30V at I = -2mA

OH

V

nom = 1.65V at I = -100µA

OH

V

max = 1.84V

OH

max = 0.50V

IL

V

min = 1.30V

IH

V

max = 2.0V

IH

I

= 27.5µA…97.5µA

IHPD

I

= -27.5µA…-97.5µA

ILPU

I

High-Z max

V

V

V

V

V

V

I

IHPD

I

ILPU

I

High-Z max

V

= ±1µA

max = 0.45V at I = 2mA

OL

nom = 0.1V at I = 100µA

OL

min = 1.30V at I = -2mA

OH

nom = 1.65V at I = -100µA

OH

max = 1.84V

OH

max = 0.50V

IL

min = 1.30V

IH

max = 2.0V

IH

= 27.5µA…97.5µA

= -27.5µA…-97.5µA

= ±1µA

max = 5.5V

IH

max = 0.45V at Imax = 2mA

OL

Test points recommended

for RXD1, TXD1, CTS1,

RTS1.

If unused keep line open.

No external pull-up / pull-

down resistors allowed.

Test points required.

If unused keep line open.

PWR_IND (Power Indicator)

notifies the module’s on/off

state.

PWR_IND is an open collec-

tor that needs to be con-

nected to an external pull-up

resistor. Low state of the

open collector indicates that

the module is on. Vice versa,

high level notifies the Power

Down mode.

Therefore, the signal may be

used to enable external vol-

tage regulators that supply

an external logic for commu-

nication with the module,

e.g. level converters.

Test point recommended.

ALAS5V_HID_v00.030a 2019-03-20

Confidential / Preliminary

Page 25

Cinterion® ALAS5V Hardware Interface Description

2.1 Application Interface

67

Table 4: Signal description

Function Signal name IO Signal form and level Comment

Page 25 of 124

USB VUSB_IN I V

USB_DN I/O Full and High speed signal (differenUSB_DP I/O

USB_

I Super Speed signal (differential) Rx

SSRX_N

USB_

I

SSRX_P

USB_

O Super Speed signal (differential) Tx

SSTX_N

USB_

O

SSTX_P

Digital

audio interface

(PCM/I

DIN2 I V

BCLK2 I/O

2

S)

FSC2 I/O

DOUT2 O

MCLK O V

min = 3.0V

IN

V

max = 5.75V

IN

I

max = 100µA

I

Cin=1µF

tial) characteristics according to USB

2.0 specification.

characteristics according USB 3.0

specification.

characteristics according USB 3.0

specification.

max = 0.45V at I = 2mA

OL

V

nom = 0.1V at I = 100µA

OL

V

min = 1.30V at I = -2mA

OH

V

nom = 1.65V at I = -100µA

OH

V

max = 1.84V

OH

V

max = 0.50V

IL

V

min = 1.30V

IH

V

max = 2.0V

IH

I

= 27.5µA…97.5µA

IHPD

I

= -27.5µA…-97.5µA

ILPU

I

High-Z max

V

V

V

V

= ±1µA

max = 0.45V at I = 2mA

OL

nom = 0.1V at I = 100µA

OL

min = 1.30V at I = -2mA

OH

nom = 1.65V at I = -100µA

OH

max = 1.84V

OH

fo = TBD. MHz

USB detection.

Test point recommended.

If unused keep lines open.

Test point recommended.

USB High Speed mode

operation requires a differ-

ential impedance of 90

If unused keep lines open.

USB Super Speed mode

operation requires a differ-

ential impedance of 90

Digital audio interface con-

figurable as PCM or I

2

S

interface.

If unused keep lines open.

First digital audio interface

(DIN1, BCLK1, FSC1, and

DOUT1) reserved for future

use.

2

For I

S: Master clock output

Test point recommended in

2

case I

S interface is not

used.

ALAS5V_HID_v00.030a 2019-03-20

Confidential / Preliminary

Page 26

Cinterion® ALAS5V Hardware Interface Description

MUX,

ADC

module

1k

10n

ADCx_IN

2.1 Application Interface

67

Table 4: Signal description

Function Signal name IO Signal form and level Comment

Page 26 of 124

GPIO

interface

GPIO1,

GPIO3...8,

GPIO11...17,

GPIO22

I/O V

max = 0.45V at I = 2mA

OL

V

nom = 0.1V at I = 100µA

OL

V

min = 1.30V at I = -2mA

OH

V

nom = 1.65V at I = -100µA

OH

V

max = 1.84V

OH

V

max = 0.50V

IL

V

min = 1.30V

IH

V

max = 2.0V

IH

I

= 27.5µA…97.5µA

IHPD

I

= -27.5µA…-97.5µA

ILPU

I

High-Z max

= ±1µA

GPIO3, GPIO5...GPIO7,

GPIO8, and GPIO16 are

interrupt enabled. They can

be used to for instance wake

up the module (see Section

2.1.12).

Following functions can be

configured for GPIOs using

AT commands:

GPIO1 --> DR_SYNC

There is a 2.2k decoupling

resistor between GPIO17

and JTAG_WD_DISABLE.

Test points recommended

for GPIO1, GPIO3.

If unused keep lines open.

However, GPIO7 and

GPIO17, must be low during

module startup until the

module has been secured in

factory.

1PPS interface

ADC

interface

GPIO1

(DR_SYNC)

ADC1_IN,

ADC2_IN,

ADC4_IN,

ADC5_IN

O Clock signal with 1 pulse per second,

frequency 1Hz, accuracy +/- 5ms

I Full specification compliance range

V

>=0.10V

Imin

V

<=1.70V

Imax

R

10M

I

Resolution: 14 Bit

Accuracy: < ±2mV

ADC conversion time t (max) = 550µs

at 4.8MHz sample clock

If the feature is enabled (see

Chapter 3).

If unused keep line open.

Prepared for general pur-

pose and antenna diagnos-

tic use.

ALAS5V_HID_v00.030a 2019-03-20

Confidential / Preliminary

Page 27

Cinterion® ALAS5V Hardware Interface Description

2.1 Application Interface

67

Table 4: Signal description

Function Signal name IO Signal form and level Comment

PCIe PCIE_RX_N I According to PCI Express Specifica-

PCIE_RX_P

PCIE_TX_N O

PCIE_TX_P

PCIE_CLK_N I/O

PCIE_CLK_P

tion, Revision 2.0/2.1 (one lane, 5

GBit/s)

Page 27 of 124

2

I

C inter-

face

JTAG interface

PCIE_CLK_REQ

PCIE_HOST_

RST

PCIE_HOST_

WAKE

IO V

O

I

max = 0.45V at I = 2mA

OL

V

nom = 0.1V at I = 100µA

OL

V

min = 1.30V at I = -2mA

OH

V

nom = 1.65V at I = -100µA

OH

V

max = 1.84V

OH

V

max = 0.50V

IL

V

min = 1.30V

IH

V

max = 2.0V

IH

I

= 27.5µA…97.5µA

IHPD

I

= -27.5µA…-97.5µA

ILPU

I

High-Z max

= ±1µA

I2CDAT1 I/O VILmax = 1.30V

V

min = 0.50V

I2CCLK1 O

JTAG_SRST I V

JTAG_TCK

JTAG_TDI

JTAG_TMS

JTAG_TRST

JTAG_TDO O

JTAG_WD_DISABLE

IH

V

max = 2.0V

IH

V

max = 0.3V at I = 3mA

OL

V

OH

I

ILPU

max = 0.45V at I = 2mA

OL

V

nom = 0.1V at I = 100µA

OL

V

OH

V

OH

V

OH

V

max = 0.50V

IL

V

min = 1.30V

IH

V

max = 2.0V

IH

I

IHPD

I

ILPU

I

High-Z max

IV

max = 0.3V at -100µA

IL

V

min = 1.50V at 100µA

IH

V

max = 2.0V

IH

max = 1.84V

= -27.5µA…-97.5µA

min = 1.30V at I = -2mA

nom = 1.65V at I = -100µA

max = 1.84V

= 27.5µA…97.5µA

= -27.5µA…-97.5µA

= ±1µA

Additional PCIe control sig-

nals

Open Drain Output (internal

pull up)

External pull up resistors

required.

Maximum load 510 Ohm.

Debug interface.

Test point recommended for

all JTAG lines.

High during reset and start-

up does disable the watch-

dog timer (jumper to VEXT).

There is a 2k2Ohm decou-

pling resistor between

JTAG_WD_DISABLE and

GPIO17.

JTAG_

PS_HOLD

IV

min = 1.65V at 680µA

IH

max = 0.20V at 680µA

V

IL

High holds the power supply

during debugging (jumper to

VEXT).

V

max = 1.84V

OH

min = 1.30V at 150µA

V

OH

V

max = 0.5V at -200µA

OL

ALAS5V_HID_v00.030a 2019-03-20

Confidential / Preliminary

Page 28

Cinterion® ALAS5V Hardware Interface Description

2.1 Application Interface

67

Table 4: Signal description

Function Signal name IO Signal form and level Comment

Page 28 of 124

eMMC

interface

1.8V

eMMC

2.95V

eMMC

EMMC_

IV

DETECT

EMMC_PWR O V

EMMC_CLK O V

EMMC_CMD O

EMMC_D[0...7]I/O

EMMC_CLK O V

EMMC_CMD O

EMMC_D[0...7]I/O

max = 0.45V at I = 2mA

OL

V

nom = 0.1V at I = 100µA

OL

V

min = 1.30V at I = -2mA

OH

V

nom = 1.65V at I = -100µA

OH

V

max = 1.84V

OH

V

max = 0.50V

IL

V

min = 1.30V

IH

V

max = 2.0V

IH

I

= 27.5µA…97.5µA

IHPD

I

= -27.5µA…-97.5µA

ILPU

I

High-Z max

I

OUT (max)

V

V

V

V

V

I

High-Z max

V

V

V

V

V

I

High-Z max

= ±1µA

OUT (nom)

= 2.95V / 1.8V

= 150mA

max = 0.45V at rated drive strength

OL

min = 1.40V at rated drive strength

OH

max = 1.84V

OH

max = 0.58V at rated drive strength

IL

min = 1.27V at rated drive strength

IH

max = 2.0V

IH

= ±5µA

max = 0.36V at rated drive strength

OL

min = 2.05V at rated drive strength

OH

max = 2.91V

OH

max = 0.68V at rated drive strength

IL

min = 1.82V at rated drive strength

IH

max = 3.05V

IH

= ±10µA

eMMC

ALAS5V_HID_v00.030a 2019-03-20

Confidential / Preliminary

Page 29

Cinterion® ALAS5V Hardware Interface Description

2.1 Application Interface

67

Page 29 of 124

2.1.2.1 Absolute Maximum Ratings

The absolute maximum ratings stated in Table 5 are stress ratings under any conditions.

Stresses beyond any of these limits will cause permanent damage to ALAS5V.

Table 5: Absolute maximum ratings (TBD.)

Parameter Min Max Unit

Supply voltage BATT+ -0.3 +5.5 V

Voltage at all digital lines in Power Down mode (except VEXT) -0.3 +0.5 V

Voltage at VEXT in Power Down mode -0.3 +0.3 V

Voltage at digital lines in normal operation -0.3 +2.3 V

Voltage at UICC interface, CCVCC 1.8V in normal operation -0.3 +2.3 V

Voltage at UICC interface, CCVCC 3.0V in normal operation -0.3 +3.4 V

Voltage at ADC lines if the module is powered by BATT+ -0.5 V

Voltage at ADC lines if the module is not powered -0.5 +0.5 V

VEXT maximum current shorted to GND -600 mA

VUSB_IN -0.3 5.75 V

USB 3.0 data lines -0.3 +1.4 V

USB 2.0 data lines -0.3 +3.6 V

PCIe data and clock lines -0.3 +1.4 V

PCIe control lines -0.3 2.1 V

Voltage at PWR_IND line -0.5 5.5 V

PWR_IND input current if PWR_IND= low 2 mA

Voltage at following signals:

IGT, EMERG_OFF

-0.3 2.1 V

BATT+

+0.5V V

ALAS5V_HID_v00.030a 2019-03-20

Confidential / Preliminary

Page 30

Cinterion® ALAS5V Hardware Interface Description

BATT+

USB_DP

c)

lin. reg.

GND

Module

Detection only

VUSB_IN

b)

USBpart

a)

a)

All ser ial (including RS) and pull-up resistors for data lines are implemented .

USB_DN

c)

c)

If the USB interface is opera te d with super or high speeds, it is recommende d to take special care routing the data

lines. Application layout should implement a differential impedance of 90 ohms for proper signal integrity .

VBUS

1µF

b)

Since VUSB_IN is used for detection only it is recommended not to add any further blocking capacitors on

the VUSB_IN line.

USB_SSRX_N

c)

USB_SSRX_P

c)

USB_SSTX_N

c)

USB_SSTX_P

c)

USB_SS

_PHY

USB_HS

_PHY

USB 2.0

Controller

USB 3.0

Controller

2.0

2.0

3.0

100nF

100nF

SMT

Page 30 of 124

2.1 Application Interface

67

2.1.3 USB Interface

ALAS5V supports a USB 3.0 Super Speed (5Gbps) device interface, and alternatively a USB

2.0 device interface that is High Speed compatible. The USB interface is primarily intended f or

use as command and data interface, and for downloading firmware.

The USB host is responsible for supplying the VUSB_IN line. This line is for voltage detection

only. The USB part (driver and transceiver) is supplied by means of BATT+. This is because

ALAS5V is designed as a self-powered device compliant with the “Universal Serial Bus Specification Revision 3.0”

1

.

Figure 5: USB circuit

To properly connect the module's USB interface to the external application, a USB 3.0 or 2.0

compatible connector and cable or hardware design is required. For further guidelines on implementing the external application’s USB 3.0 or 2.0 interface see [4] and [5]. For more information on the USB related signals see Table 4. Furthermore, the USB modem driver distributed

with ALAS5V needs to be installed.

While a USB connection is active, the module will never switch into SLEEP mode. Only if the

USB interface is in Suspended state or Detached (i.e., VUSB_IN = 0) is the module able to

switch into SLEEP mode thereby saving power

1. The specification is ready for download on http://www.usb.org/developers/docs/

2. Please note that if the USB interface is employed, and a USB cable is connected, there should also be

a terminal program linked to the USB port in order to receive and process the initial SYSSTART URC

after module startup. Otherwise, the SYSSTART URC remains pending in the USB driver's output buffer

and this unprocessed data prevents the module from power saving.

ALAS5V_HID_v00.030a 2019-03-20

2

.

Confidential / Preliminary

Page 31

Cinterion® ALAS5V Hardware Interface Description

2.1 Application Interface

67

Page 31 of 124

2.1.4 Serial Interface ASC0

ALAS5V offers an 8-wire (plus GND) unbalanced, asynchronous modem interface ASC0 conforming to ITU-T V.24 protocol DCE signaling. The electrical characteristics do not comply with

ITU-T V.28. The significant levels are 0V (for low data bit or active state) and 1.8V (for high data

bit or inactive state). For electrical characteristics please refer to Table 4.

ALAS5V is designed for use as a DCE. Based on the conventions for DCE-DTE connections it

communicates with the customer application (DTE) using the following signals:

• Port TXD @ application sends data to the module’s TXD0 signal line

• Port RXD @ application receives data from the module’s RXD0 signal line

Figure 6: Serial interface ASC0

Features: