Page 1

5

MODEL

MA2A M/B

D D

REV

3A

3B

E200505-0479

E200505-3796

3C E200507-2695

C C

B B

4

CHANGE LIST

3

2

Model

Page

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

1

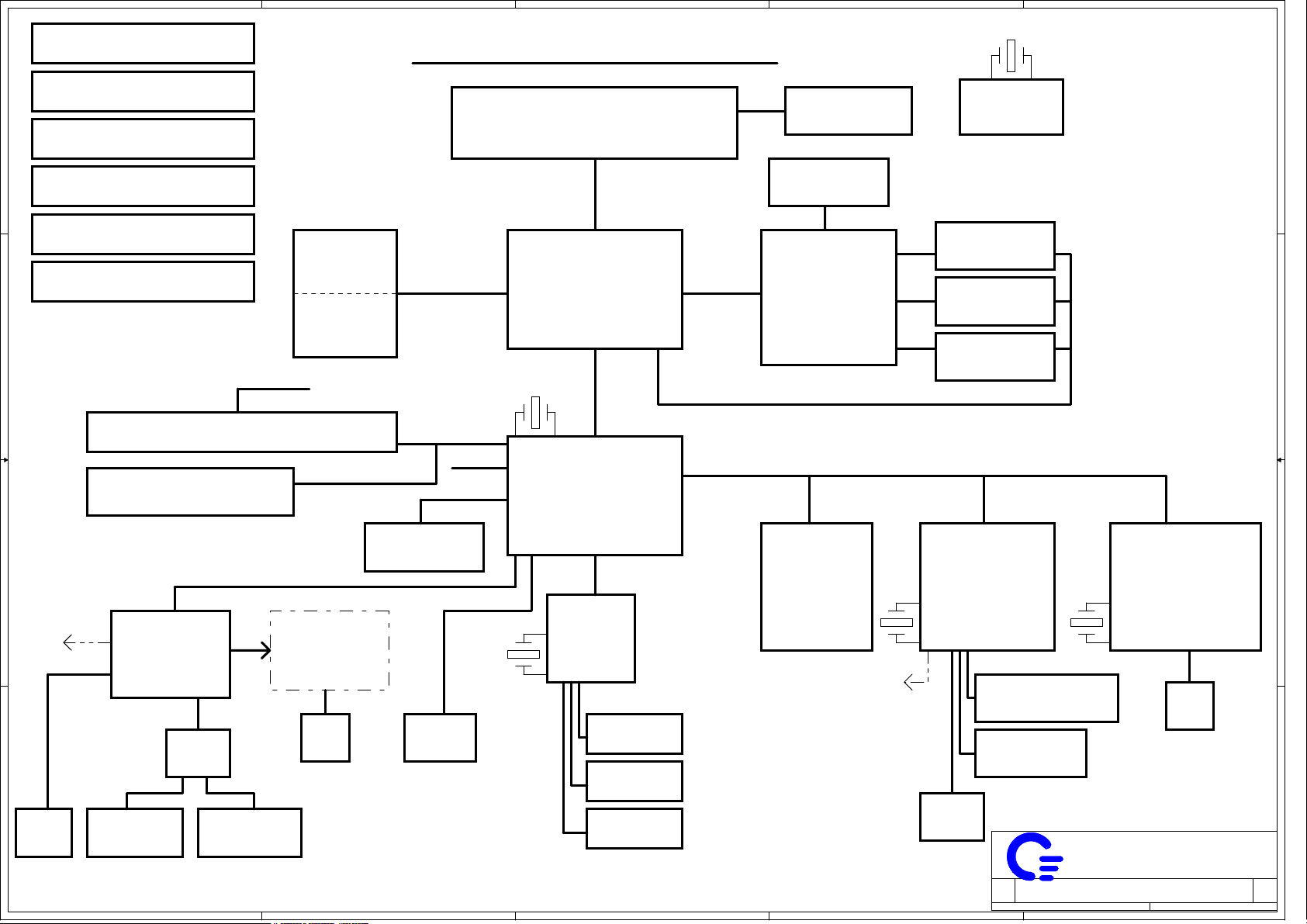

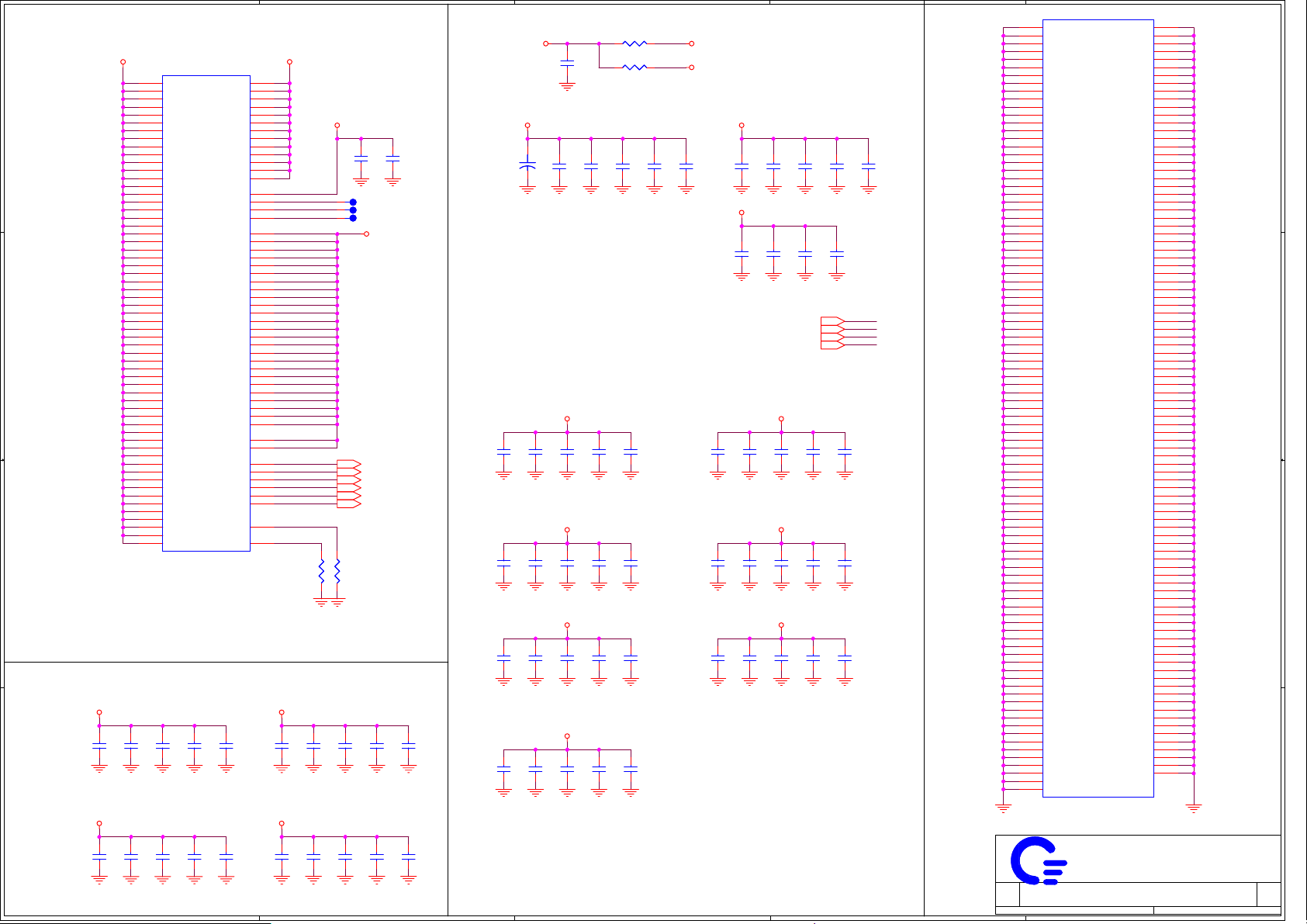

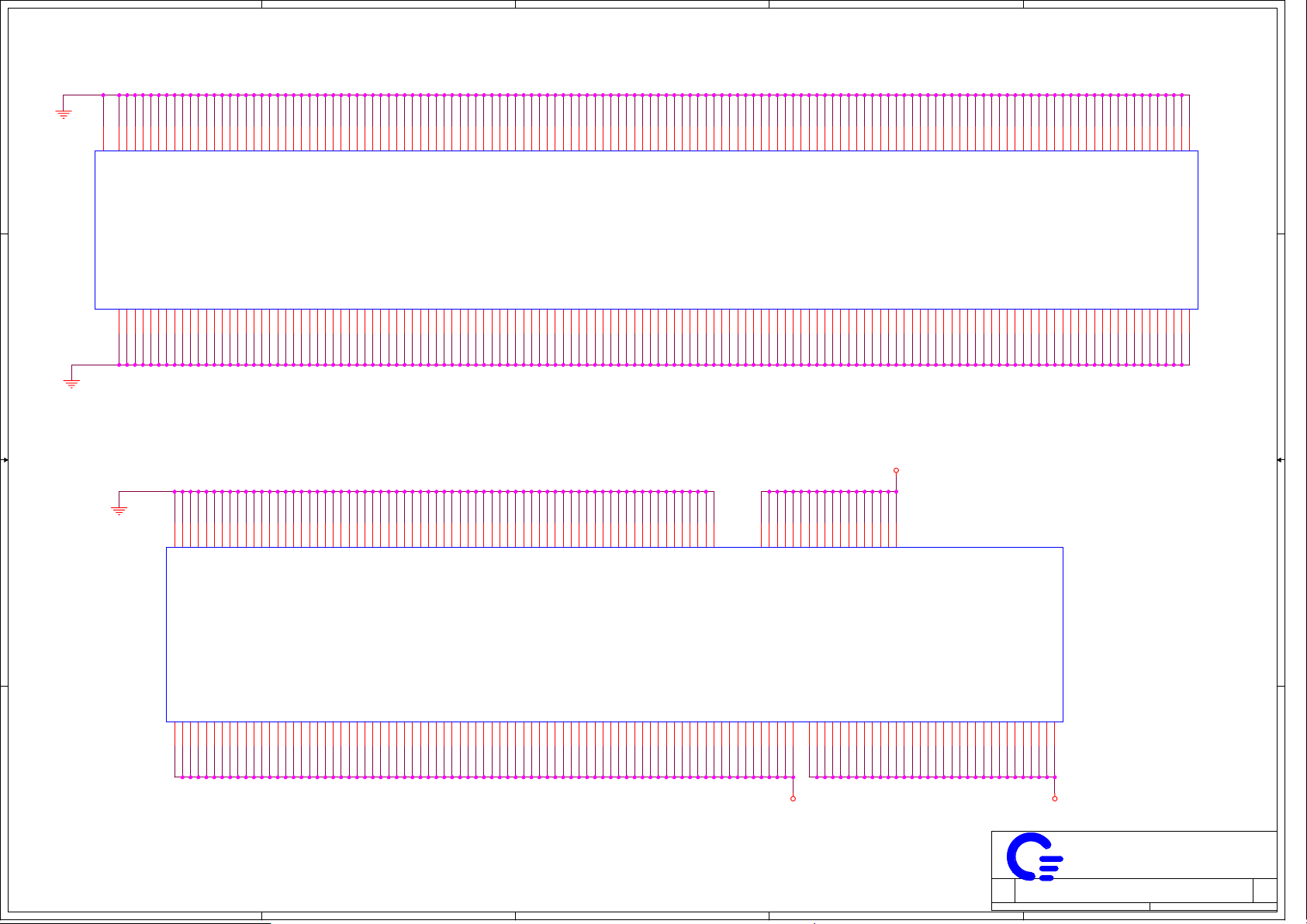

NT2 M/B BOARD

FM

TO

3A

3A

3A

3A

3A

3A

3A

3A

3A

3A

3A

3B

3A

3A

3A

3A

3A

3A

3A

3A

3A

3A

3A

3A

3A

3B

3A

3A

3B

3B

3A

3A

3A

3A

3A

3A

3A

3A

3A

3C

3C

3C

3C

A A

Quanta Computer Inc.

5

PROJECT:MA2A

APPROVED BY :

Ashen

PCBA NO.

4

CHECK BY:Bryan Huang

31MA2MB0044

3

REV:3C

DRAWING BY:Bryan Huang

2

DOC. NO: 204

DATE :08/19/2005

SHEET 1

1

Page 2

5

4

3

2

1

MAX1845 ( 1.5V & 1.8V )

P34

SC1470 ( VCCP1.05V )

P35

D D

SC1470 ( VGA_CORE )

P36

MAX1999 ( 3VPCU & 5VPCU)

P37

MAX1907 ( CPU_CORE )

P38

DDR II

DISCHARGE

P39

SODIMM0

SMDDR_VTERM

1.8VSUS

DDR II

SODIMM1

C C

SATA 0

HDD (PATA OR SATA)

+5V

BAYVCC

P22

P10

P22

ODD

USB Port 0 ~ 3

5VSUS

B B

TO Port

Replicator

Line-in

CODEC

CONEXANT

20468-31

+5V

+3V

P23

AMP

MAX9755

P24

A A

MIC IN

JACK

P24

HeadPhone

5

INT. SPEAKER

P24

AC'97

MODEM DAA

CONEXANT

20493-21

+5V

+3V

3VSUS

WIRE

RJ11

P30

P24

P23

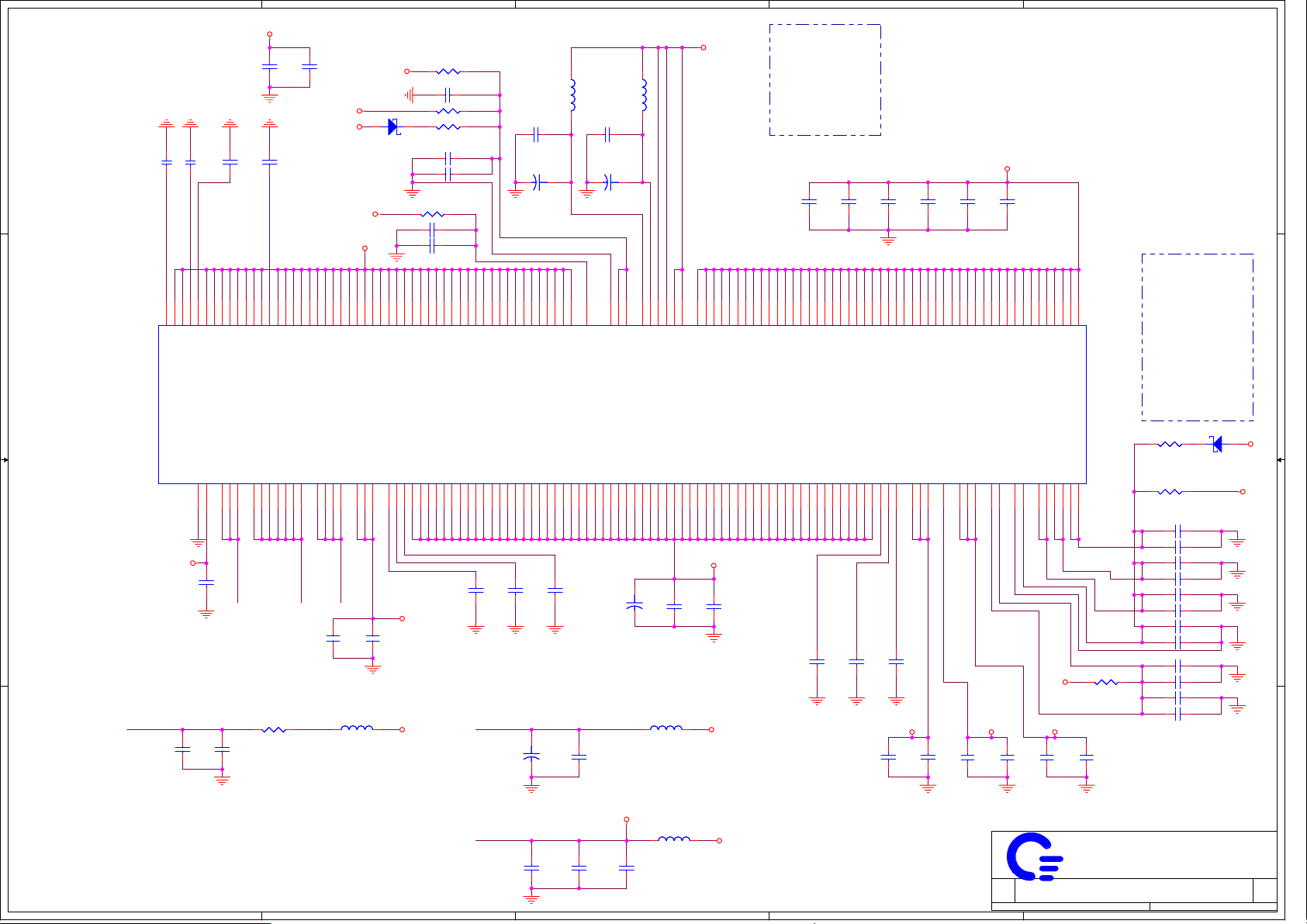

MA2A SYSTEM BLOCK DIAGRAM

Intel Dothan Processor

VCC_CORE

Dual Channel DDR

Master

Slave

USB 2.0

USB 2.0

Finger

Printer

5VSUS

4

GMCH_VTT

VCCA

PATA

SATA

P21

P26

X'TAL

32.768K

478 uFCPGA

FSB

533/400MHz

Alviso-PM/GM

GMCH

82875GM/GME

GMCH_VTT

1.8VSUS

+1.5V

1257 PCBGA

+2.5V

+3V

X'TAL

32.768K

DMI interface

ICH6-M

+3V

3VSUS

+2.5V

+1.5V

1.5VSUS

VCCRTC

GMCH_VTT

609 BGA

EC/KBC

PC97551

3VPCU

+3V

VCCRTC

TOUCHPAD

Keyboard

LPC

P25

BIOS

P5,6,7,8,9

P18,19,20

3VPCU

P25

P26

P26

3

+5V

P3,4

PCI-EXPRESS

CPU Thermal

Sensor

+5V

P3

VIDEO RAM

+2.5V

P14,15

ATI

M22/M24/M26

708 PCBGA

VGA_CORE

VGA1.2V

+1.8V

VDD_MEM

+2.5V

+3V

FOR Alviso-G (LCD/CRT/S-VIDEO)

TYPE III

MINI-PCI

Socket

3VSUS

5VSUS

P11,12,13

PCI Bus interface

X'TAL

INTB/C

REQ1

GNT1

AD20

24.576M

P28

IEEE 1394

PORT B

TO Port

Replicator

2

X'TAL

14.318M

+3V

VIN

LCD/INV

+5V

+3V

CONN

+5V

+2.5V

S-VIDEO

TI PCI7411

288 PBGA

( PCMCIA+1394

+Cardreader )

+3V

3VSUS+3V

5VSUS

+1.5V

IEEE 1394

PORT A

1394

Conn.

P33

CK-GEN

CK410M

ICS954206

CRT

P2

P16

P17

P17

Marvell

88E8036/88E8053 LAN

X'TAL

25M

INTA/B/C

REQ0 AD16

GNT0

AD25

P31, 32

LANVCC

LANVCC18

LANVCC10

INTD

REQ2

GNT2

P29, 30

4 in 1 Cardreader

Socket

P32

RJ45

P30

CARDBUS

Slot

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet of

Date: Sheet of

P31

PROJECT : MA2A

PROJECT : MA2A

Quanta Computer Inc.

Quanta Computer Inc.

Block Diagram

Block Diagram

Block Diagram

139Thursday, March 17, 2005

139Thursday, March 17, 2005

139Thursday, March 17, 2005

1

of

3ACustom

3ACustom

3ACustom

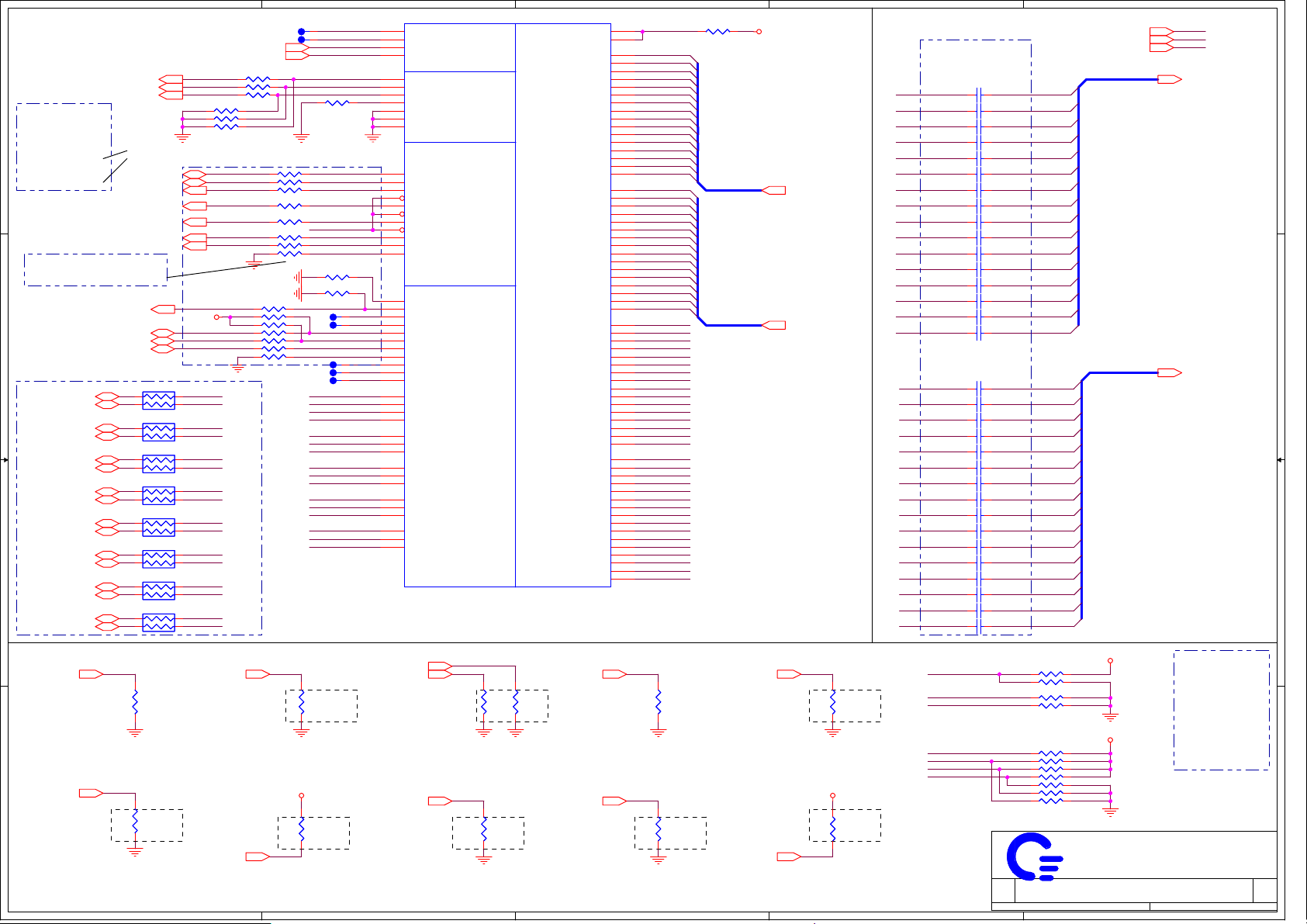

Page 3

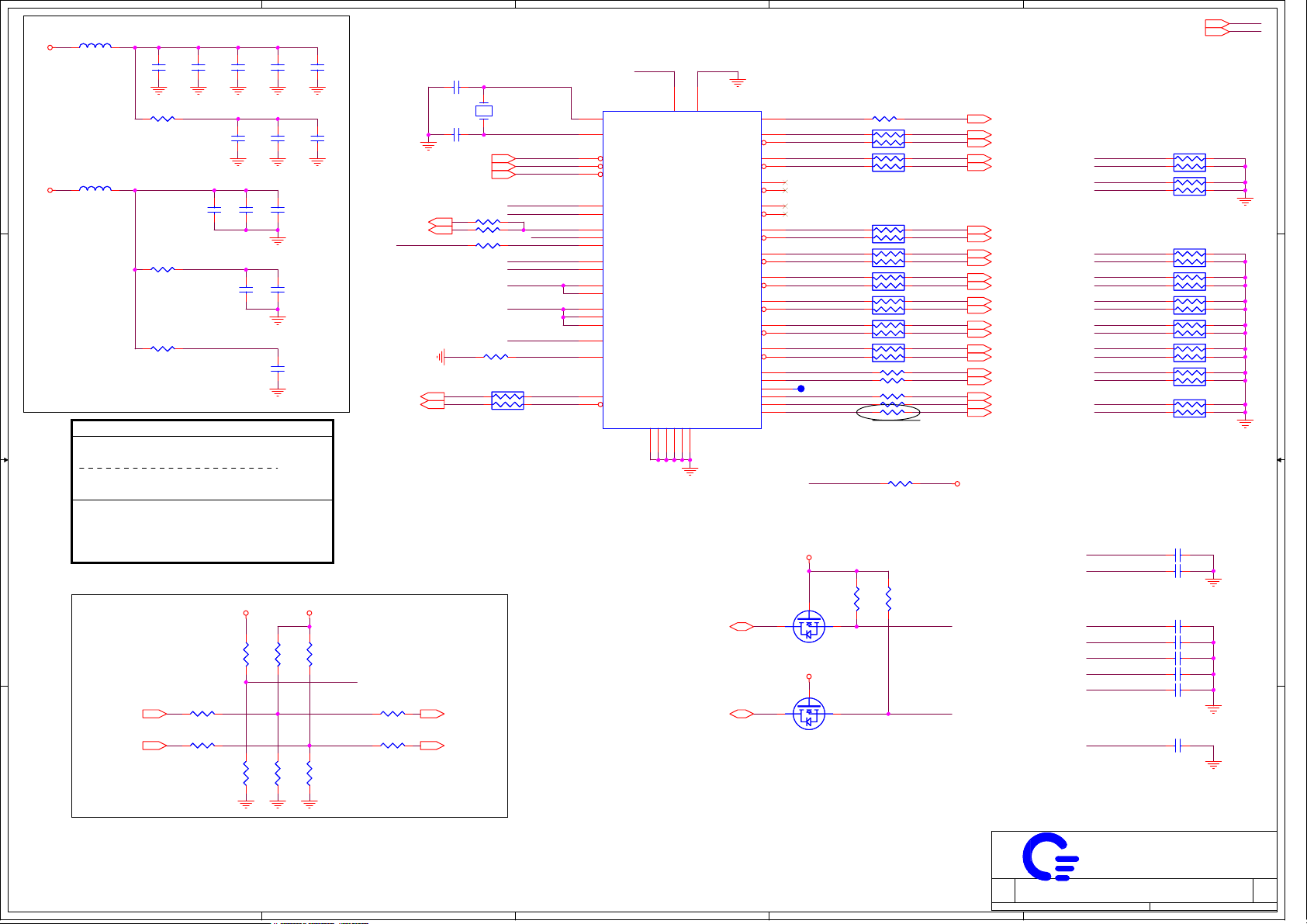

5

L30

+3V

D D

+3V

C C

L30

ACB2012L-120

ACB2012L-120

120 ohms@100Mhz

L19

L19

ACB2012L-120

ACB2012L-120

120 ohms@100Mhz

CLKVDD

C619

C619

0.047U

0.047U

R131 2.2R131 2.2

R345 2.2R345 2.2

R150 1R150 1

C622

C622

0.047U

0.047U

CLK_VDDA

CLKVDD1

C611

C611

0.047U

0.047U

CLK_VDD48

CLK_VDDREF

C620

C620

0.047U

0.047U

C327

C327

0.047U

0.047U

C608

C608

0.047U

0.047U

C617

C617

0.047U

0.047U

C621

C621

0.047U

0.047U

C309

C309

4.7U/10V

4.7U/10V

C368

C368

4.7U/10V

4.7U/10V

C618

C618

4.7U/10V

4.7U/10V

C348

C348

0.047U

0.047U

C340

C340

0.047U

0.047U

C322

C322

0.01U

0.01U

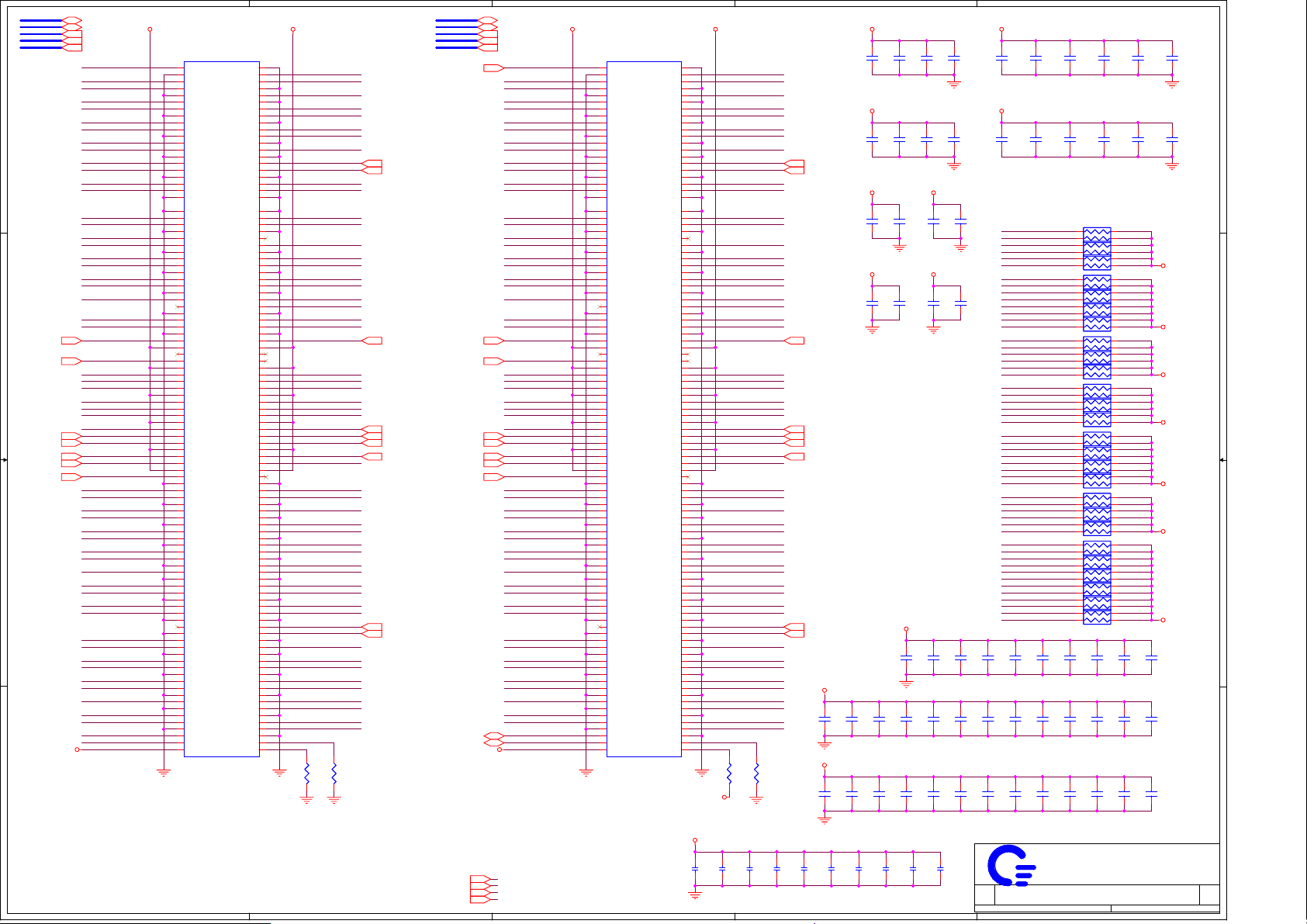

FSC FSB FSA CPU SRC PCI

1 0 1 100 100 33

0 0 1 133 100 33

Default

0 1 1 166 100 33

0 1 0 200 100 33

4

Place these termination to close CK410M.

C369

CLK48_7411(31)

CLK48_USB(19)

Iref=5mA,

Ioh=4*Iref

DOT96(5)

DOT96#(5)

CG_BSEL2

C369

27P

27P

C370

C370

27P

27P

CLK_EN#(37) HCLK_MCH (5)

STP_PCI#(19)

STP_CPU#(19,37)

R146 15R146 15

R143 15R143 15

R352 4.7KR352 4.7K

R138 475/FR138 475/F

DOT96

DOT96#

21

RP21

RP21

1

3

Y1

Y1

14.318MHZ

14.318MHZ

33X2

33X2

CG_XIN

CG_XOUT

CLK_EN#

STP_PCI#

STP_CPU#

CGCLK_SMB

CGDAT_SMB

CG_BSEL0

CG_BSEL1

FSC_BSEL2

CLK_VDDREF

CLKVDD

CLKVDD1

CLKVDD

CLK_VDD48

IREF

R_DOT96

2

R_DOT96#

4

50

49

10

55

54

46

47

12

16

53

48

42

1

7

21

28

34

11

39

14

15

3

CLK_VDDA

U12

U12

XTAL_IN

XTAL_OUT

VTT_PWRGD#/PD

PCI_STOP#

CPU_STOP#

SCLK

SDATA

FSA/USB_48

FSB/TEST_MODE

FSC/TEST_SEL

VDD_REF

VDD_CPU

VDD_PCI_1

VDD_PCI_2

VDD_SRC0

VDD_SRC1

VDD_SRC2

VDD_48

IREF

DOT96

DOT96#

CK-410M

CK-410M

ICS954206

37

VDDA

CK-410M

CK-410M

GND_REF

GND_PCI_26GND_SRC29GND_CPU

GND_PCI_1

GND_48

2

51

13

38

VSSA

CPU0#

CPU1#

CPU2_ITP/SRC7

CPU2#_ITP/SRC7#

SRC6#

SRC5#

SRC4#

SRC3#

SRC2#

SRC1#

SRC0#

PCIF1

PCIF0/ITP_EN

45

250mA ( MAX. )

REF

CPU0

CPU1

SRC6

SRC5

SRC4

SRC3

SRC2

SRC1

SRC0

PCI5

PCI4

PCI3

PCI2

52

44

43

41

40

36

35

33

32

31

30

26

27

24

25

22

23

19

20

17

18

5

4

3

56

9

8

14M_REF

RHCLK_CPU

RHCLK_CPU#

RHCLK_MCH

RHCLK_MCH#

RSRC_LAN

RSRC_LAN#

RSRC_MCH

RSRC_MCH#

RSRC_SATA

RSRC_SATA#

RSRC_ICH

RSRC_ICH#

RSRC_PEG

RSRC_PEG#

RDREFSSCLK

RDREFSSCLK#

R_PCLK_591

R_PCLK_7411

T130T130

R_PCLK_MINI

R_PCLK_LAN

R_PCLK_ICH

R_PCLK_LAN

2

R159 12.1/FR159 12.1/F

RP22 33X2RP22 33X2

1

3

RP18 33X2RP18 33X2

1

3

RP77 33X2RP77 33X2

1

3

RP8 33X2RP8 33X2

3

1

RP9 33X2RP9 33X2

3

1

RP10 33X2RP10 33X2

3

1

RP11 33X2RP11 33X2

3

1

RP19 33X2RP19 33X2

3

1

rev:E changepin

3 &pin 8

R155 33R155 33

R158 33R158 33

R161 33R161 33

R149 33R149 33

R152 33R152 33

R151 10KR151 10K

2

4

2

4

2

4

4

2

4

2

4

2

4

2

4

2

1

14M_ICH (19)

HCLK_CPU (3)

HCLK_CPU# (3)

HCLK_MCH# (5)

+LANCLK (29)

-LANCLK (29)

SRC_MCH (6)

SRC_MCH# (6)

SRC_SATA (18)

SRC_SATA# (18)

SRC_ICH (19)

SRC_ICH# (19)

SRC_PEG (11)

SRC_PEG# (11)

DREFSSCLK (5)

DREFSSCLK# (5)

PCLK_591 (25)

PCLK_7411 (31)

PCLK_MINI (28)

PCLK_LAN

PCLK_ICH (18)

HCLK_CPU

HCLK_CPU#

HCLK_MCH

HCLK_MCH#

+LANCLK

-LANCLK

SRC_MCH#

SRC_MCH

SRC_SATA#

SRC_SATA

SRC_ICH#

SRC_ICH

SRC_PEG#

SRC_PEG

DREFSSCLK#

DREFSSCLK

DOT96#

DOT96

RP23 49.9/FX2RP23 49.9/FX2

RP20 49.9/FX2RP20 49.9/FX2

RP78 49.9/FX2RP78 49.9/FX2

RP58 49.9/FX2RP58 49.9/FX2

RP57 49.9/FX2RP57 49.9/FX2

RP56 49.9/FX2RP56 49.9/FX2

RP55 49.9/FX2RP55 49.9/FX2

RP54 49.9/FX2RP54 49.9/FX2

RP53 49.9/FX2RP53 49.9/FX2

Place these termination to close CK410M.

+3V

+3V(3,8,10,11,12,13,16,17,18,19,20,22,25,26,28,34,35,36,37,39)

VCCP(3,4,5,6,8,9,18,20,34,39)

1

3

1

3

1

3

1

3

1

3

1

3

1

3

1

3

1

3

2

4

2

4

2

4

2

4

2

4

2

4

2

4

2

4

2

4

0 0 0 266 100 33

1 0 0 333 100 33

1 1 0 400 100 33

Q21

Q21

2N7002E

2N7002E

3

Q22

Q22

2N7002E

2N7002E

3

+3V

+3V

R184

R184

R191

2

1

2

1

10K

10K

R191

10K

10K

CGDAT_SMB

CGCLK_SMB

1 1 1 RESERVED

B B

+3V

SELPSB1_CLK(3)

R135

R135

10K

10K

R349

R349

*1K

*1K

VCCP

R351

R351

*1K

*1K

CG_BSEL0

CG_BSEL1

PDAT_SMB(10,19,29)

R129 1KR129 1KR128 0R128 0

MCH_BSEL1 (5)

PCLK_SMB(10,19,29)

( 48 MHz )

CLK48_USB

CLK48_7411

( 33 MHz )

PCLK_LAN

PCLK_MINI

PCLK_ICH

PCLK_7411

PCLK_591

( 14 MHz )

C338 *10PC338 *10P

C346 *10PC346 *10P

C616 *10PC616 *10P

C361 *10PC361 *10P

C607 *10PC607 *10P

C609 *10PC609 *10P

C613 *10PC613 *10P

SELPSB0_CLK(3)

A A

R122 0R122 0

R136

R136

*10K

*10K

5

R348*0R348

*0

CG_BSEL2

R350*0R350

*0

R121 1KR121 1K

4

MCH_BSEL2 (5)

These are for backdrive issue

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet of

3

2

Date: Sheet of

14M_ICH

Quanta Computer Inc.

Quanta Computer Inc.

CLOCK GENERATOR

CLOCK GENERATOR

CLOCK GENERATOR

C355 *10PC355 *10P

PROJECT : MA2A

PROJECT : MA2A

239Thursday, March 17, 2005

239Thursday, March 17, 2005

239Thursday, March 17, 2005

1

3A

3A

3A

of

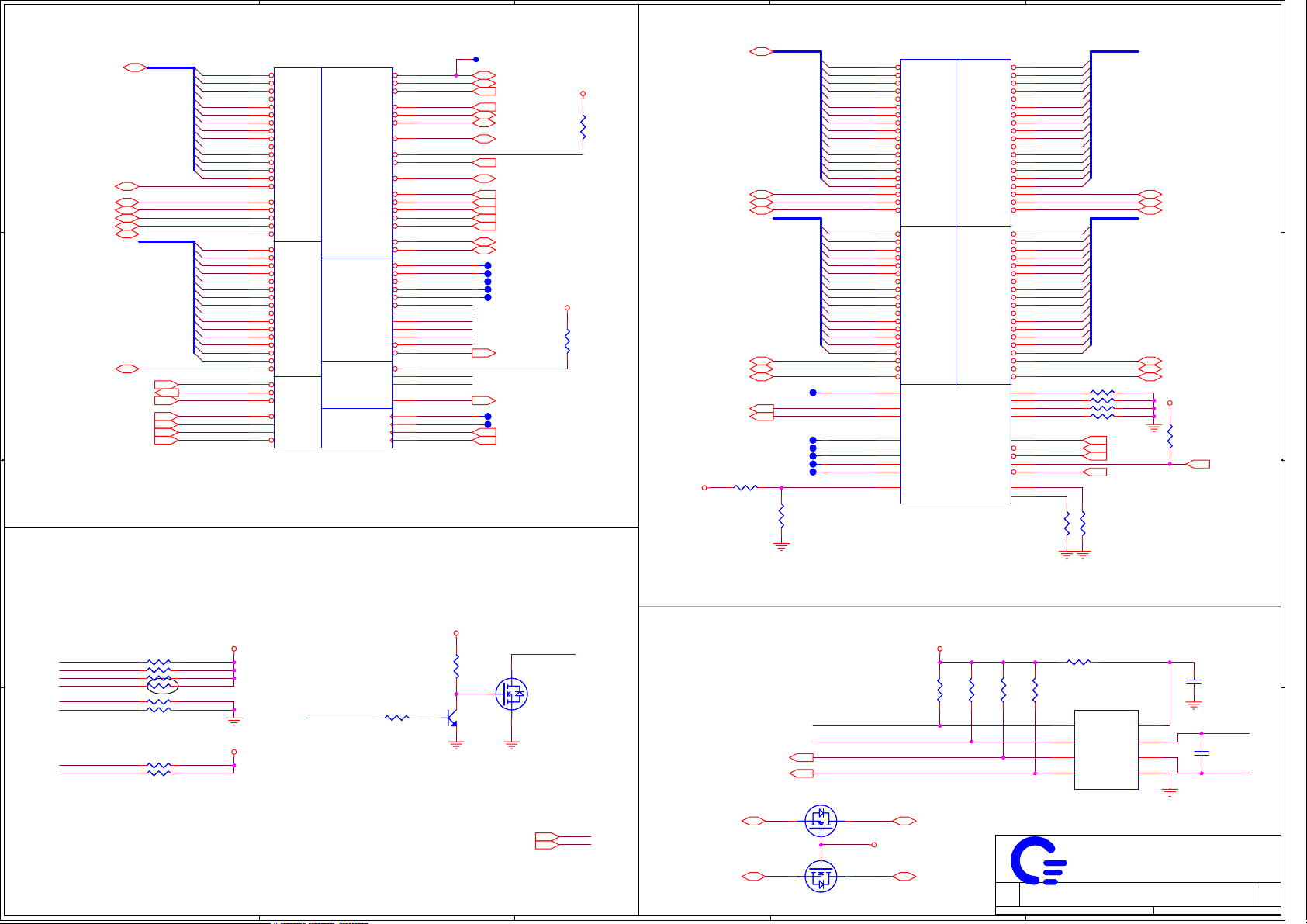

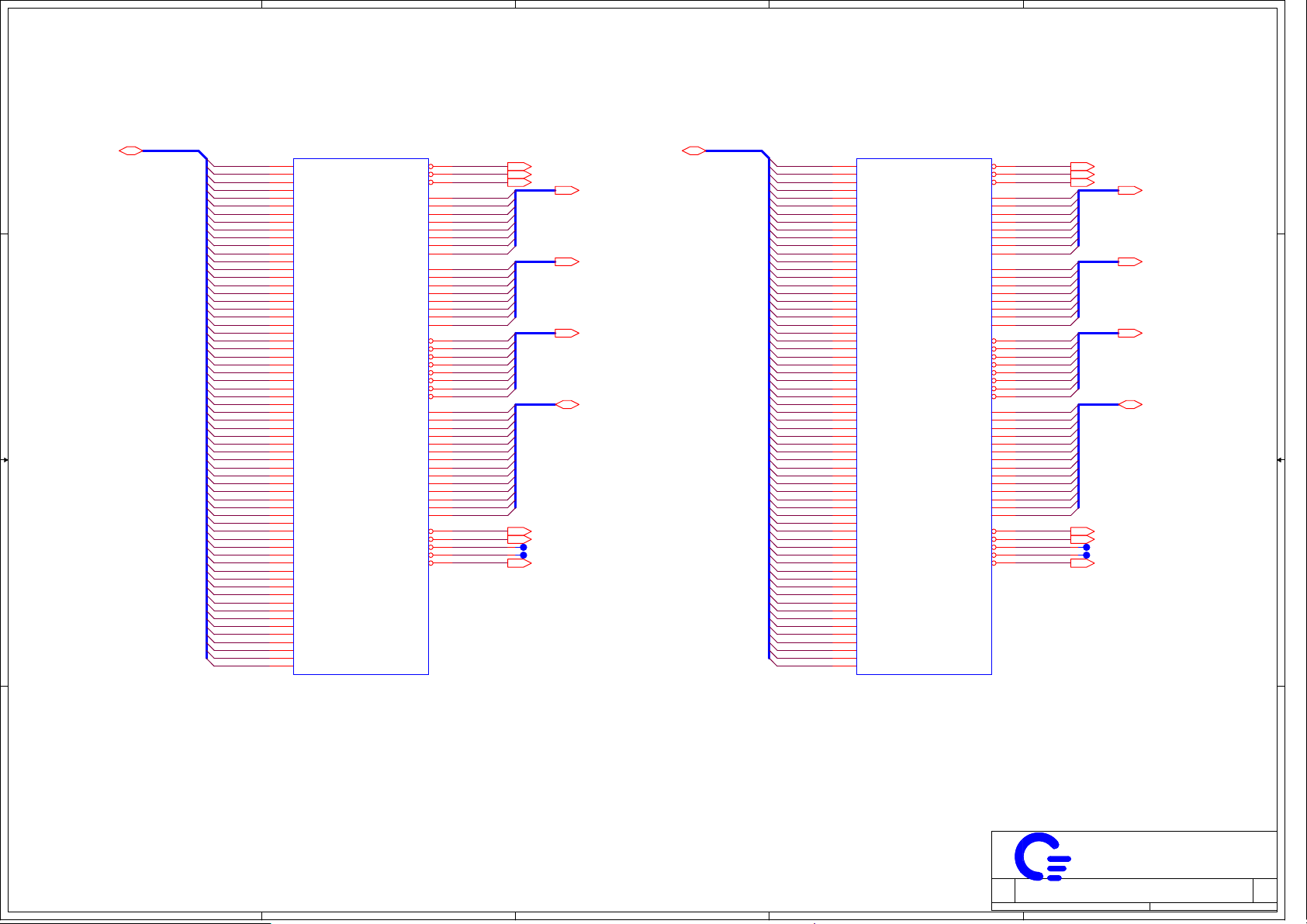

Page 4

A

B

C

D

E

HD#[0..63]

HD#0

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

T96T96

T90T90

T1T1

T99T99

T100T100

T97T97

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

PM_PSI#

SELPSB0_CLK

SELPSB1_CLK

H_GTLREF

AD26

HDSTBN0#

HDSTBP0#

HD#[0..63]

HDSTBN1#

HDSTBP1#

Layout note: 0.5" max length.

R3

2K/FR32K/F

G25

M26

G24

M23

M25

AC1

A19

A25

A22

B21

A24

B26

A21

B20

C20

B24

D24

E24

C26

B23

E23

C25

C23

C22

D25

H23

L23

H24

F25

L26

N24

H26

N25

K25

K24

L24

C16

C14

AF7

E26

J23

J25

J26

E1

B2

C3

U46B

U46B

D0#

D1#

D2#

D3#

D4#

D5#

D6#

D7#

D8#

D9#

D10#

D11#

D12#

D13#

D14#

D15#

DSTBN0#

DSTBP0#

DINV0#

D16#

D17#

D18#

D19#

D20#

D21#

D22#

D23#

D24#

D25#

D26#

D27#

D28#

D29#

D30#

D31#

DSTBN1#

DSTBP1#

DINV1#

PSI#

BSEL0

BSEL1

RSVD

RSVD

RSVD

RSVD

RSVD

GTLREF

Dothan_478P

Dothan_478P

DATA GRP 2 DATA GRP 3

DATA GRP 2 DATA GRP 3

DATA GRP 0DATA GRP 1

DATA GRP 0DATA GRP 1

MISC

MISC

RSVD/DPRSTP#

PWRGOOD

D32#

D33#

D34#

D35#

D36#

D37#

D38#

D39#

D40#

D41#

D42#

D43#

D44#

D45#

D46#

D47#

DSTBN2#

DSTBP2#

DINV2#

D48#

D49#

D50#

D51#

D52#

D53#

D54#

D55#

D56#

D57#

D58#

D59#

D60#

D61#

D62#

D63#

DSTBN3#

DSTBP3#

DINV3#

COMP0

COMP1

COMP2

COMP3

DPSLP#

DPWR#

SLP#

TEST1

TEST2

Y26

AA24

T25

U23

V23

R24

R26

R23

AA23

U26

V24

U25

V26

Y23

AA26

Y25

W25

W24

T24

AB25

AC23

AB24

AC20

AC22

AC25

AD23

AE22

AF23

AD24

AF20

AE21

AD21

AF25

AF22

AF26

AE24

AE25

AD20

P25

P26

AB2

AB1

G1

B7

C19

E4

A6

C5

F23

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

COMP0

COMP1

COMP2

COMP3

DPRSLP#

DPSLP#

DPWR#

CPUPWRGD

CPUSLP#

H_TEST1

H_TEST2

R511

R511

*1K

*1K

VCCP

SELPSB0_CLK(2)

SELPSB1_CLK(2)

HD#[0..63](5)

HDSTBN0#(5)

HDSTBP0#(5)

DINV#0(5)

HDSTBN1#(5)

HDSTBP1#(5)

DINV#1(5)

R2 1K/FR2 1K/F

HA#[3..31](5)

4 4

HADSTB0#(5)

HREQ#0(5)

HREQ#1(5)

HREQ#2(5)

HREQ#3(5)

HREQ#4(5)

3 3

HADSTB1#(5)

2 2

HA#[3..31]

HA#[3..31]

A20M#(18)

FERR#(18)

IGNNE#(18)

STPCLK#(18)

INTR(18)

NMI(18)

SMI#(18)

A20M#

FERR#

IGNNE#

STPCLK#

INTR

NMI

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HADSTB0#

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

HA#17

HA#18

HA#23

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

HADSTB1#

AA3

AA2

AF4

AC4

AC7

AC3

AD3

AE4

AD2

AB4

AC6

AD5

AE2

AD6

AF3

AE1

AF1

AE5

P4

U4

V3

R3

V2

W1

T4

W2

Y4

Y1

U1

Y3

U3

R2

P3

T2

P1

T1

C2

D3

A3

C6

D1

D4

B4

U46A

U46A

A3#

A4#

A5#

A6#

A7#

A8#

A9#

A10#

A11#

A12#

A13#

A14#

A15#

A16#

ADSTB#0

REQ0#

REQ1#

REQ2#

REQ3#

REQ4#

A17#

A18#

A19#

A20#

A21#

A22#

A23#

A24#

A25#

A26#

A27#

A28#

A29#

A30#

A31#

ADSTB#1

A20M#

FERR#

IGNNE#

STPCLK#

LINT0

LINT1

SMI#

Dothan_478P

Dothan_478P

ADDR GROUP 0 ADDR GROUP 1

ADDR GROUP 0 ADDR GROUP 1

DEFER#

DRDY#

DBSY#

LOCK#

CONTROLXTP/ITP SIGNALS

CONTROLXTP/ITP SIGNALS

RESET#

TRDY#

BPM#0

BPM#1

BPM#2

BPM#3

PRDY#

PREQ#

TRST#

PROCHOT#

THERMDA

THERMDC

THERMTRIP#

THERM

THERM

ITP_CLK1

ITP_CLK0

BCLK1

BCLK0

H CLK

H CLK

ADS#

BNR#

BPRI#

BR0#

IERR#

INIT#

RS0#

RS1#

RS2#

HIT#

HITM#

TCK

TDO

TMS

DBR#

ADS#

N2

BNR#

L1

BPRI#

J3

DEFER#

L4

DRDY#

H2

DBSY#

M2

HBREQ0#

N4

IERR#

A4

CPUINIT#

B5

HLOCK#

J2

CPURST#

B11

RS#0

H1

RS#1

K1

RS#2

L2

HTRDY#

M3

HIT#

K3

HITM#

K4

BPM#0HA#19

C8

BPM#1HA#20

B8

BPM#2HA#21

A9

BPM#3HA#22

C9

PRDY#

A10

PREQ#HA#24

B10

TCK

A13

TDI

C12

TDI

A12

C11

B13

A7

B17

B18

A18

C17

A15

A16

B14

B15

TDO

TMS

TRST#

DBR#

CPU_PROCHOT#

THERMDA

THERMDC

THRMTRIP#

HCLK_CPU#

HCLK_CPU

TP1TP1

ADS# (5)

BNR# (5)

BPRI# (5)

DEFER# (5)

DRDY# (5)

DBSY# (5)

HBREQ0# (5)

CPUINIT# (18)

HLOCK# (5)

CPURST# (5)

RS#0 (5)

RS#1 (5)

RS#2 (5)

HTRDY# (5)

HIT# (5)

HITM# (5)

T94T94

T87T87

T89T89

T86T86

T88T88

DBR# (19)

THRMTRIP# (5,18)

T93T93

T92T92

HCLK_CPU# (2)

HCLK_CPU (2)

VCCP

VCCP

R50056R500

56

R50156R501

56

HD#[0..63]

HDSTBN2#

HDSTBP2#

HD#[0..63]

HDSTBN3#

HDSTBP3#

R518 27.4R518 27.4

R517 54.9R517 54.9

R4 27.4R4 27.4

R5 54.9R5 54.9

DPRSLP# (18)

DPSLP# (18)

DPWR# (5)

CPUSLP# (5,18)

R8

*1KR8*1K

HDSTBN2# (5)

HDSTBP2# (5)

DINV#2 (5)

HDSTBN3# (5)

HDSTBP3# (5)

DINV#3 (5)

VCCP

R7

*200R7*200

CPUPWRGD (18)

CPUSLP#

1). Connected between Dothan and

ICH6 for Dothan A Stepping.

2). .Connected between Dothan and

Alviso for Dothan B Stepping.

G1: NC for Dothan and

DPRSTP# for Yonah

+3V

VCCP +3V

TDI 6648VCC

TMS

TDO

CPURST#

TCK

TRST#

PREQ#

THRMTRIP# SYS_SHDN#

1 1

R483 150R483 150

R486 39.2R486 39.2

R484 *54.9R484 *54.9

R485 *54.9R485 *54.9

R482 27.4R482 27.4

R481 680R481 680

R487 56R487 56

R499 *56R499 *56

A

rev:e del

VCCP

THRMTRIP#

R503 *470R503 *470

B

R14

R14

*4.7K

*4.7K

Q1

Q1

2

*MMBT3904

*MMBT3904

1 3

SYS_SHDN#

3

R11

R11

R13

2

Q2

Q2

*2N7002E

*2N7002E

1

+3V(2,8,10,11,12,13,16,17,18,19,20,22,25,26,28,34,35,36,37,39)

VCCP(2,4,5,6,8,9,18,20,34,39)

6648_ALERT#(25)

SYS_SHDN#(36)

THCLK_SMB(11,25)

THDAT_SMB(11,25)

C

1

1

2

2

THCLK_SMB

THDAT_SMB

6648_ALERT#

Q46

Q46

2N7002E

2N7002E

3

3

Q45

Q45

2N7002E

2N7002E

ABCLK

ABDATA

ABCLK (25)

+3V

ABDATA (25)

D

10K

10K

R13

10K

10K

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

R16

R16

10K

10K

R12 200R12 200

R15

R15

*10K

*10K

U45

U45

8

SCLK

7

SDA

6

ALERT#

4

OVERT#

MAX6648MUA

MAX6648MUA

VCC

DXP

DXN

GND

1

2

3

5

ADDRESS: 98H

PROJECT : MA2A

PROJECT : MA2A

Quanta Computer Inc.

Quanta Computer Inc.

Dothan CPU (Host Bus)

Dothan CPU (Host Bus)

Dothan CPU (Host Bus)

C69

C69

0.1U

0.1U

THERMDA

C777

C777

2200P

2200P

THERMDC

3A

3A

3A

of

of

of

339Thursday, March 17, 2005

339Thursday, March 17, 2005

339Thursday, March 17, 2005

E

Page 5

A

CPU_CORE CPU_CORE

U46C

U46C

AA11

VCC0

AA13

VCC1

AA15

VCC2

AA17

VCC3

AA19

4 4

3 3

2 2

CPU_CORE

C21

C21

0.1U

0.1U

1 1

CPU_CORE

AA21

AA5

AA7

AA9

AB10

AB12

AB14

AB16

AB18

AB20

AB22

AB6

AB8

AC11

AC13

AC15

AC17

AC19

AC9

AD10

AD12

AD14

AD16

AD18

AD8

AE11

AE13

AE15

AE17

AE19

AE9

AF10

AF12

AF14

AF16

AF18

AF8

D18

D20

D22

E17

E19

E21

F18

F20

F22

G21

C64

C64

0.1U

0.1U

D6

D8

E5

E7

E9

F6

F8

Dothan_478P

Dothan_478P

VCC4

VCC5

VCC6

VCC7

VCC8

VCC9

VCC10

VCC11

VCC12

VCC13

VCC14

VCC15

VCC16

VCC17

VCC18

VCC19

VCC20

VCC21

VCC22

VCC23

VCC24

VCC25

VCC26

VCC27

VCC28

VCC29

VCC30

VCC31

VCC32

VCC33

VCC34

VCC35

VCC36

VCC37

VCC38

VCC39

VCC40

VCC41

VCC42

VCC43

VCC44

VCC45

VCC46

VCC47

VCC48

VCC49

VCC50

VCC51

VCC52

VCC53

VCC54

VCC55

VCC56

VCC57

VCC58

C56

C56

0.1U

0.1U

VCCA1/RSVD

VCCA2/RSVD

VCCA3/RSVD

VCCSENSE

VSSSENSE

C68

C68

0.1U

0.1U

VCC59

VCC60

VCC61

VCC62

VCC63

VCC64

VCC65

VCC66

VCC67

VCC68

VCC69

VCC70

VCC71

VCCA0

VCCP0

VCCP1

VCCP2

VCCP3

VCCP4

VCCP5

VCCP6

VCCP7

VCCP8

VCCP9

VCCP10

VCCP11

VCCP12

VCCP13

VCCP14

VCCP15

VCCP16

VCCP17

VCCP18

VCCP19

VCCP20

VCCP21

VCCP22

VCCP23

VCCP24

VCCQ0

VCCQ1

VID0

VID1

VID2

VID3

VID4

VID5

C14

C14

0.1U

0.1U

G5

H22

H6

J21

J5

K22

U5

V22

V6

W21

W5

Y22

Y6

F26

B1

N1

AC26

D10

D12

D14

D16

E11

E13

E15

F10

F12

F14

F16

K6

L21

L5

M22

M6

N21

N5

P22

P6

R21

R5

T22

T6

U21

P23

W4

E2

F2

F3

G3

G4

H4

TP_VCCSENSE

AE7

TP_VSSSENSE

AF6

CPU_CORE

CPU_CORE

TP_VCCA1

TP_VCCA2

TP_VCCA3

CPU_VID0

CPU_VID1

CPU_VID2

CPU_VID3

CPU_VID4

CPU_VID5

R520

R520

*54.9

*54.9

C15

C15

0.1U

0.1U

CPU_VCCA

C16

C16

0.1U

0.1U

C783

C783

0.01U

0.01U

T91T91

T95T95

T98T98

VCCP

CPU_VID0 (37)

CPU_VID1 (37)

CPU_VID2 (37)

CPU_VID3 (37)

CPU_VID4 (37)

CPU_VID5 (37)

R519

R519

*54.9

*54.9

C17

C17

0.1U

0.1U

B

C18

C18

0.1U

0.1U

C784

C784

10U

10U

C19

C19

0.1U

0.1U

CPU_VCCA

+

+

C43

C43

C28

C28

0.1U

0.1U

150U

150U

270U/2.0V(CC7343) 12 mΩ * 4

04/13 Intel recommend

CPU_CORE

C42

C42

C38

C38

10U

10U

10U

10U

CPU_CORE

C29

C29

C30

C30

10U

10U

10U

10U

CPU_CORE

C46

C46

C47

C47

10U

10U

10U

10U

CPU_CORE

C6

C786

C786

10UC610U

10U

10U

C782

C782

0.1U

0.1U

C37

C37

10U

10U

C52

C52

10U

10U

C48

C48

10U

10U

C27

C27

10U

10U

R513 0R513 0

R512 *0R512 *0

C59

C59

C44

C44

0.1U

0.1U

0.1U

0.1U

C36

C36

10U

10U

C39

C39

10U

10U

C50

C50

10U

10U

C787

C787

10U

10U

C

C31

C31

10U

10U

C789

C789

10U

10U

C51

C51

10U

10U

C33

C33

10U

10U

C41

C41

0.1U

0.1U

+1.5V

+1.8V

VCCPVCCP

C35

C35

0.1U

0.1U

C57

C57

0.1U

0.1U

VCCP

C61

C61

0.1U

0.1U

C12

C12

C13

C13

10U

10U

10U

10U

C10

C10

C4

10U

10U

10UC410U

C24

C24

C9

10U

10U

10UC910U

10U/6.3V/X5R(CC0805)

5 mOhm*35

---> 10U/4V/X5R(CC0603)

C32

C32

0.1U

0.1U

C58

C58

0.1U

0.1U

CPU_CORE(37,39)

CPU_CORE

CPU_CORE

CPU_CORE

C3

10UC310U

C5

10UC510U

C785

C785

10U

10U

VCCP(2,3,5,6,8,9,18,20,34,39)

+1.5V(8,12,19,20,32,33,39)

+1.8V(12,13,33,35,39)

C60

C60

0.1U

0.1U

C40

C40

0.1U

0.1U

C11

C11

10U

10U

C788

C788

10U

10U

C23

C23

10U

10U

Murata

C62

C62

0.1U

0.1U

C34

C34

0.1U

0.1U

C8

10UC810U

C45

C45

10U

10U

C7

10UC710U

C63

C63

0.1U

0.1U

D

AA1

AA4

AA6

AA8

AA10

AA12

AA14

AA16

AA18

AA20

AA22

AA25

AB3

AB5

AB7

AB9

AB11

AB13

AB15

AB17

AB19

AB21

AB23

AB26

AC2

AC5

AC8

AC10

AC12

AC14

AC16

AC18

AC21

AC24

AD1

AD4

AD7

AD9

AD11

AD13

AD15

AD17

AD19

AD22

AD25

AE3

AE6

AE8

AE10

AE12

AE14

AE16

AE18

AE20

AE23

AE26

AF2

AF5

AF9

AF11

AF13

AF15

AF17

AF19

AF21

AF24

B12

B16

B19

B22

B25

C10

C13

C15

C18

C21

C24

D11

A11

A14

A17

A20

A23

A26

U46D

U46D

A2

A5

A8

B3

B6

B9

C1

C4

C7

D2

D5

D7

D9

Dothan_478P

Dothan_478P

VSS0

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

VSS161

VSS162

VSS163

VSS164

VSS165

VSS166

VSS167

VSS168

VSS169

VSS170

VSS171

VSS172

VSS173

VSS174

VSS175

VSS176

VSS177

VSS178

VSS179

VSS180

VSS181

VSS182

VSS183

VSS184

VSS185

VSS186

VSS187

VSS188

VSS189

VSS190

VSS191

E

D13

D15

D17

D19

D21

D23

D26

E3

E6

E8

E10

E12

E14

E16

E18

E20

E22

E25

F1

F4

F5

F7

F9

F11

F13

F15

F17

F19

F21

F24

G2

G6

G22

G23

G26

H3

H5

H21

H25

J1

J4

J6

J22

J24

K2

K5

K21

K23

K26

L3

L6

L22

L25

M1

M4

M5

M21

M24

N3

N6

N22

N23

N26

P2

P5

P21

P24

R1

R4

R6

R22

R25

T3

T5

T21

T23

T26

U2

U6

U22

U24

V1

V4

V5

V21

V25

W3

W6

W22

W23

W26

Y2

Y5

Y21

Y24

C20

C20

0.1U

0.1U

PROJECT : MA2A

C53

C53

C55

C22

C22

0.1U

0.1U

A

C25

C25

0.1U

0.1U

C26

C26

0.1U

0.1U

C49

C49

0.1U

0.1U

0.1U

0.1U

C55

0.1U

0.1U

C65

C65

0.1U

0.1U

C66

C66

0.1U

0.1U

B

C67

C67

0.1U

0.1U

C

D

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

PROJECT : MA2A

Quanta Computer Inc.

Quanta Computer Inc.

Dothan CPU (Power)

Dothan CPU (Power)

Dothan CPU (Power)

E

of

of

of

439Thursday, March 17, 2005

439Thursday, March 17, 2005

439Thursday, March 17, 2005

3A

3A

3A

Page 6

5

HD#[0..63](3)

D D

C C

B B

HD#[0..63]

HXRCOMP

HXSCOMP

HXSWING

HYRCOMP

HYSCOMP

HYSWING

HD#0

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

E4

E1

F4

H7

E2

F1

E3

D3

K7

F2

J7

J8

H6

F3

K8

H5

H1

H2

K5

K6

J4

G3

H3

J1

L5

K4

J5

P7

L7

J3

P5

L3

U7

V6

R6

R5

P3

T8

R7

R8

U8

R4

T4

T5

R1

T3

V8

U6

W6

U3

V5

W8

W7

U2

U1

Y5

Y2

V4

Y7

W1

W3

Y3

Y6

W2

C1

C2

D1

T1

L1

P1

U37A

U37A

HD0#

HD1#

HD2#

HD3#

HD4#

HD5#

HD6#

HD7#

HD8#

HD9#

HD10#

HD11#

HD12#

HD13#

HD14#

HD15#

HD16#

HD17#

HD18#

HD19#

HD20#

HD21#

HD22#

HD23#

HD24#

HD25#

HD26#

HD27#

HD28#

HD29#

HD30#

HD31#

HD32#

HD33#

HD34#

HD35#

HD36#

HD37#

HD38#

HD39#

HD40#

HD41#

HD42#

HD43#

HD44#

HD45#

HD46#

HD47#

HD48#

HD49#

HD50#

HD51#

HD52#

HD53#

HD54#

HD55#

HD56#

HD57#

HD58#

HD59#

HD60#

HD61#

HD62#

HD63#

HXRCOMP

HXSCOMP

HXSWING

HYRCOMP

HYSCOMP

HYSWING

ALVISO

ALVISO

HADSTB0#

HADSTB1#

HCPURST#

HOST

HOST

HDEFER#

HDSTBN0#

HDSTBN1#

HDSTBN2#

HDSTBN3#

HDSTBP0#

HDSTBP1#

HDSTBP2#

HDSTBP3#

HEDRDY#

HPCREQ#

HCPUSLP#

HA3#

HA4#

HA5#

HA6#

HA7#

HA8#

HA9#

HA10#

HA11#

HA12#

HA13#

HA14#

HA15#

HA16#

HA17#

HA18#

HA19#

HA20#

HA21#

HA22#

HA23#

HA24#

HA25#

HA26#

HA27#

HA28#

HA29#

HA30#

HA31#

HADS#

HVREF

HBNR#

HBPRI#

BREQ0#

HCLKINN

HCLKINP

HDBSY#

HDINV#0

HDINV#1

HDINV#2

HDINV#3

HDPWR#

HDRDY#

HHIT#

HHITM#

HLOCK#

HREQ0#

HREQ1#

HREQ2#

HREQ3#

HREQ4#

HRS0#

HRS1#

HRS2#

HTRDY#

G9

C9

E9

B7

A10

F9

D8

B10

E10

G10

D9

E11

F10

G11

G13

C10

C11

D11

C12

B13

A12

F12

G12

E12

C13

B11

D13

A13

F13

F8

B9

E13

J11

A5

D5

E7

H10

AB1

AB2

C6

E6

H8

K3

T7

U5

G6

F7

G4

K1

R3

V3

G5

K2

R2

W4

F6

D4

D6

B3

A11

A7

D7

B8

C7

A8

A4

C5

B4

G8

B5

4

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

ADS#

HADSTB0#

HADSTB1#

HVREF

BNR#

BPRI#

HBREQ0#

CPURST#

HCLK_MCH#

HCLK_MCH

DBSY#

DEFER#

DINV#0

DINV#1

DINV#2

DINV#3

DPWR#

DRDY#

HDSTBN0#

HDSTBN1#

HDSTBN2#

HDSTBN3#

HDSTBP0#

HDSTBP1#

HDSTBP2#

HDSTBP3#

HIT#

HITM#

HLOCK#

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

RS#0

RS#1

RS#2

HCPUSLP#

HTRDY#

HA#[3..31]

HA#[3..31] (3)

ADS# (3)

HADSTB0# (3)

HADSTB1# (3)

BNR# (3)

BPRI# (3)

HBREQ0# (3)

CPURST# (3)

HCLK_MCH# (2)

HCLK_MCH (2)

DBSY# (3)

DEFER# (3)

DINV#0 (3)

DINV#1 (3)

DINV#2 (3)

DINV#3 (3)

DPWR# (3)

DRDY# (3)

HDSTBN0# (3)

HDSTBN1# (3)

HDSTBN2# (3)

HDSTBN3# (3)

HDSTBP0# (3)

HDSTBP1# (3)

HDSTBP2# (3)

HDSTBP3# (3)

HIT# (3)

HITM# (3)

HLOCK# (3)

HREQ#0 (3)

HREQ#1 (3)

HREQ#2 (3)

HREQ#3 (3)

HREQ#4 (3)

RS#0 (3)

RS#1 (3)

RS#2 (3)

HTRDY# (3)

VCCP

R456

R456

100/F

100/F

C745

C745

R455

R455

0.1U

0.1U

200/F

200/F

T4T4

T79T79

R454 0R454 0

R2027 should be populated to

support Dothan B stepping

3

CPUSLP# (3,18)

DMI_TXN0(19)

DMI_TXN1(19)

DMI_TXN2(19)

DMI_TXN3(19)

DMI_TXP0(19)

DMI_TXP1(19)

DMI_TXP2(19)

DMI_TXP3(19)

DMI_RXN0(19)

DMI_RXN1(19)

DMI_RXN2(19)

DMI_RXN3(19)

DMI_RXP0(19)

DMI_RXP1(19)

DMI_RXP2(19)

DMI_RXP3(19)

CLK_SDRAM0(10)

CLK_SDRAM1(10)

CLK_SDRAM3(10)

CLK_SDRAM4(10)

CLK_SDRAM0#(10)

CLK_SDRAM1#(10)

CLK_SDRAM3#(10)

CLK_SDRAM4#(10)

CKE0(10)

CKE1(10)

CKE2(10)

CKE3(10)

SM_CS0#(10)

SM_CS1#(10)

SM_CS2#(10)

SM_CS3#(10)

M_ODT0(10)

M_ODT1(10)

M_ODT2(10)

M_ODT3(10)

SMDDR_VREF

It's point to point, 55ohm trace,

keep as short as possible.

DMI_TXN0

DMI_TXN1

DMI_TXN2

DMI_TXN3

DMI_TXP0

DMI_TXP1

DMI_TXP2

DMI_TXP3

DMI_RXN0

DMI_RXN1

DMI_RXN2

DMI_RXN3

DMI_RXP0

DMI_RXP1

DMI_RXP2

DMI_RXP3

CLK_SDRAM0

CLK_SDRAM1

CLK_SDRAM2

T18T18

CLK_SDRAM3

CLK_SDRAM4

CLK_SDRAM5

T14T14

CLK_SDRAM0#

CLK_SDRAM1#

CLK_SDRAM2#

T20T20

CLK_SDRAM3#

CLK_SDRAM4#

CLK_SDRAM5#

T15T15

CKE0

CKE1

CKE2

CKE3

SM_CS0#

SM_CS1#

SM_CS2#

SM_CS3#

M_OCDCOMP0

T68T68

M_OCDCOMP1

T69T69

M_ODT0

M_ODT1

M_ODT2

M_ODT3

M_RCOMPN

M_RCOMPP

SMXSLEW

SMYSLEW

AA31

AB35

AC31

AD35

Y31

AA35

AB31

AC35

AA33

AB37

AC33

AD37

Y33

AA37

AB33

AC37

AM33

AL1

AE11

AJ34

AF6

AC10

AN33

AK1

AE10

AJ33

AF5

AD10

AP21

AM21

AH21

AK21

AN16

AM14

AH15

AG16

AF22

AF16

AP14

AL15

AM11

AN10

AK10

AK11

AF37

AD1

AE27

AE28

AF9

AF10

2

U37C

U37C

DMIRXN0

DMIRXN1

DMIRXN2

DMIRXN3

DMIRXP0

DMIRXP1

DMIRXP2

DMIRXP3

DMITXN0

DMITXN1

DMITXN2

DMITXN3

DMITXP0

DMITXP1

DMITXP2

DMITXP3

SM_CK0

SM_CK1

SM_CK2

SM_CK3

SM_CK4

SM_CK5

SM_CK0#

SM_CK1#

SM_CK2#

SM_CK3#

SM_CK4#

SM_CK5#

SM_CKE0

SM_CKE1

SM_CKE2

SM_CKE3

SM_CS0#

SM_CS1#

SM_CS2#

SM_CS3#

SM_OCDCOMP0

SM_OCDCOMP1

SM_ODT0

SM_ODT1

SM_ODT2

SM_ODT3

SMRCOMPN

SMRCOMPP

SMVREF0

SMVREF1

SMXSLEWIN

SMXSLEWOUT

SMYSLEWIN

SMYSLEWOUT

ALVISO

ALVISO

1

CFG0

MCH_BSEL1

MCH_BSEL2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG17

CFG18

CFG19

CFG20

PM_BMBUSY#

PM_EXTTS#0

PM_EXTTS#1

R453 0R453 0

R382 100R382 100

DOT96#

DOT96

TP_NC1

TP_NC2

TP_NC3

TP_NC4

TP_NC5

TP_NC6

TP_NC7

TP_NC8

TP_NC9

TP_NC10

TP_NC11

C744

C744

0.1U

0.1U

R468

R468

10K

10K

VCCP

+2.5V

R4501KR450

1K

T85T85

MCH_BSEL1 (2)

MCH_BSEL2 (2)

CFG3 (6)

T10T10

CFG5 (6)

CFG6 (6)

CFG7 (6)

T7T7

CFG9 (6)

T8T8

CFG11 (6)

CFG12 (6)

CFG13 (6)

T78T78

T5T5

CFG16 (6)

T6T6

CFG18 (6)

CFG19 (6)

T3T3

R467

R467

10K

10K

PM_BMBUSY# (19)

THRMTRIP# (3,18)

IMVP_PWG (19,37)

PLTRST# (11,18,19,22,29)

DOT96# (2)

DOT96 (2)

DREFSSCLK# (2)

DREFSSCLK (2)

T71T71

T75T75

T70T70

T73T73

T72T72

T74T74

T81T81

T83T83

T76T76

T77T77

T84T84

、

100MHz ( LVDS)

SMDDR_VREF(10,33)

1.8VSUS(8,9,10,33)

VCCP(2,3,4,6,8,9,18,20,34,39)

+2.5V(6,8,12,20,34,39)

G16

CFG0

H13

CFG1

G14

CFG2

F16

CFG3

F15

CFG4

G15

CFG5

E16

CFG6

D17

CFG7

J16

CFG8

D15

CFG9

E15

CFG10

D14

CFG11

E14

CFG12

H12

CFG13

C14

CFG14

H15

CFG15

DMIDDR MUXING

DMIDDR MUXING

CFG/RSVDPMLCKNC

CFG/RSVDPMLCKNC

BM_BUSY#

THRMTRIP#

DREF_CLKN

DREF_CLKP

DREF_SSCLKN

DREF_SSCLKP

DREF_CLKN

Display Clock Frequency at 96MHz ( CRT,SDVO and TVOUT)

DREF_SSCLKN、DREF_SSCLKP

Display Clock Frequency (with SSC) at 96

CFG16

CFG17

CFG18

CFG19

CFG20

RSVD21

RSVD22

RSVD23

RSVD24

RSVD25

RSVD26

RSVD27

EXT_TS0#

EXT_TS1#

PWROK

RSTIN#

NC1

NC2

NC3

NC4

NC5

NC6

NC7

NC8

NC9

NC10

NC11

、

J15

H14

G22

G23

D23

G25

G24

J17

A31

A30

D26

D25

J23

J21

H22

F5

AD30

AE29

A24

A23

C37

D37

AP37

AN37

AP36

AP2

AP1

AN1

B1

A2

B37

A36

A37

DREF_CLKP

VCCP VCCP VCCP

R420 54.9R420 54.9

R408

A A

R408

221/F

221/F

R409

R409

100/F

100/F

HXSWING

C727

C727

0.1U

0.1U

5

R399

R399

221/F

221/F

R397

R397

100/F

100/F

HYSWING

C711

C711

0.1U

0.1U

R418 24.9/FR418 24.9/F

VCCP

R401 54.9R401 54.9

R395 24.9/FR395 24.9/F

HXSCOMP

HXRCOMP

R381

R381

40.2/F

HYSCOMP

HYRCOMP

4

40.2/F

Route as short

as possible.

M_OCDCOMP0

M_OCDCOMP1

R380

R380

40.2/F

40.2/F

3

1.8VSUS

R383

R383

80.6/F

80.6/F

R384

R384

80.6/F

80.6/F

M_RCOMPN

M_RCOMPP

PROJECT : MA2A

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet of

2

Date: Sheet of

PROJECT : MA2A

Quanta Computer Inc.

Quanta Computer Inc.

Alviso Host(1/5)

Alviso Host(1/5)

Alviso Host(1/5)

1

of

539Thursday, March 17, 2005

539Thursday, March 17, 2005

539Thursday, March 17, 2005

3A

3A

3A

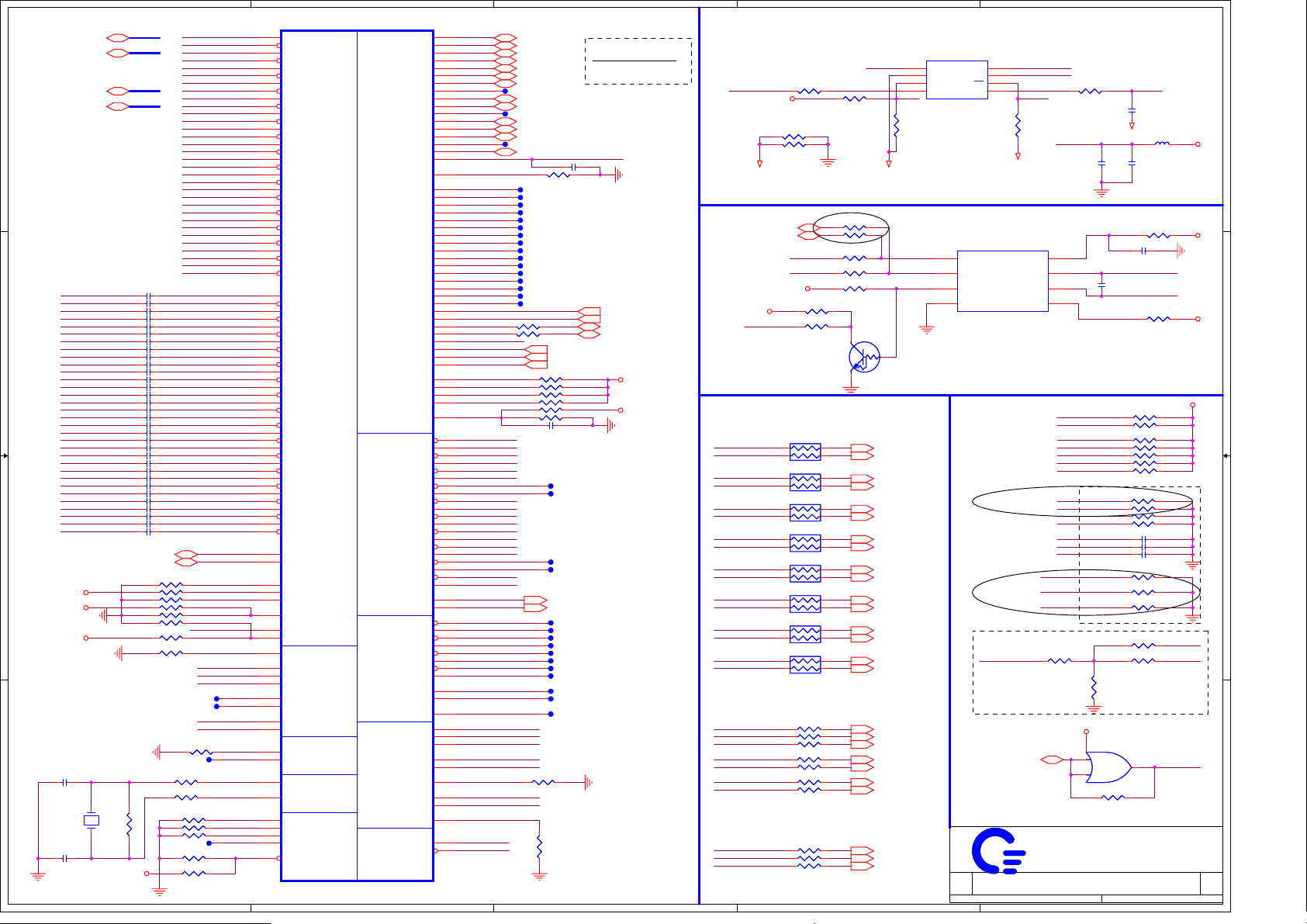

Page 7

5

T9T9

T12T12

SRC_MCH#(2)

SRC_MCH(2)

TV_COMP

TV_COMP(11,17)

TV_Y/G(11,17)

TV_C/R(11,17)

ATI

INTEL

X

R504

D D

R505

R506

R492

R491

R490

R452

R466

I - 255/F(CS12553F906)

A - NC

C C

B B

0

X

0

X

0

0

150/F

0

150/F

0

150/F

0

4.99K/F

150/F(CS11502FB04)

4.99K/F(CS24992FB00)

DDCCLK(11,17)

DDCDATA(11,17)

CRT_B_COM(11,17)

CRT_G_COM(11,17)

CRT_R_COM(11,17)

VSYNC_COM(11,17)

HSYNC_COM(11,17)

EXT VGA NC

BLON(11,16)

DDC_CLK(11,16)

DDC_DATA(11,16)

DISP_ON(11,16)

RP65 *0X2RP65 *0X2

RP61 *0X2RP61 *0X2

RP68 *0X2RP68 *0X2

RP67 *0X2RP67 *0X2

RP66 *0X2RP66 *0X2

RP64 *0X2RP64 *0X2

RP63 *0X2RP63 *0X2

RP62 *0X2RP62 *0X2

2

4

2

4

2

4

2

4

2

4

2

4

2

4

2

4

TXLCLKOUT-(11,16)

TXLCLKOUT+(11,16)

TXUCLKOUT-(11,16)

TXUCLKOUT+(11,16)

TXLOUT0-(11,16)

TXLOUT0+(11,16)

TXLOUT1-(11,16)

TXLOUT1+(11,16)

TXLOUT2-(11,16)

TXLOUT2+(11,16)

TXUOUT0-(11,16)

TXUOUT0+(11,16)

TXUOUT1-(11,16)

TXUOUT1+(11,16)

TXUOUT2-(11,16)

TXUOUT2+(11,16)

1

3

1

3

1

3

1

3

1

3

1

3

1

3

1

3

R504 *0R504 *0

TV_Y/G

R505 *0R505 *0

TV_C/R

R506 *0R506 *0

R492 0R492 0

R491 0R491 0

R490 0R490 0

DDCCLK

DDCDATA

CRT_B_COM

CRT_G_COM

CRT_R_COM

VSYNC_COM

HSYNC_COM

+2.5V

TLCO-_1

TLCO+_1

TUCO-_1

TUCO+_1

TLO0-_1

TLO0+_1

TLO1-_1

TLO1+_1

TLO2-_1

TLO2+_1

TUO0-_1

TUO0+_1

TUO1-_1

TUO1+_1

TUO2-_1

TUO2+_1

R502 *0R502 *0

R498 *0R498 *0

R493 *0R493 *0

R494 *0R494 *0

R495 *0R495 *0

R496 *39R496 *39

R497 *39R497 *39

R466 *255/FR466 *255/F

R439 *0R439 *0

R457 *2.2KR457 *2.2K

R463 *2.2KR463 *2.2K

R440 *0R440 *0

R464 *0R464 *0

R469 *0R469 *0

R433 *1.5K/FR433 *1.5K/F

EXT VGA NC

SRC_MCH#

SRC_MCH

TV_Y/G_A

TV_C/R_A

R452 0R452 0

DDCCLK_R

DDCDATA_R

CRT_BLUE

CRT_GREEN

CRT_RED

CRT_COM#

VSYNC

HSYNC

REFSET

R458 *100KR458 *100K

R38 *100KR38 *100K

T2T2

T82T82

T80T80

T13T13

T11T11

TLCO-_1

TLCO+_1

TUCO-_1

TUCO+_1

TLO0-_1

TLO1-_1

TLO2-_1

TLO0+_1

TLO1+_1

TLO2+_1

TUO0-_1

TUO1-_1

TUO2-_1

TUO0+_1

TUO1+_1

TUO2+_1

D_CLK_1

D_DATA_1

H24

H25

AB29

AC29

C16

D21

C20

H21

G21

C23

C22

C33

C31

C25

C24

C29

D28

C27

C28

D27

C26

A15

A17

J18

B15

B16

B17

E24

E23

E21

B20

A19

B19

J20

E25

F25

F23

F22

F26

F28

F27

B30

B29

B34

B33

B32

A34

A33

B31

4

U37F

U37F

SDVOCTRL_DATA

SDVOCTRL_CLK

GCLKN

GCLKP

TVDAC_A

TVDAC_B

TVDAC_C

TV_REFSET

TV_IRTNA

TV_IRTNB

TV_IRTNC

DDCCLK

DDCDATA

BLUE

BLUE#

GREEN

GREEN#

RED

RED#

VSYNC

HSYNC

REFSET

LBKLT_CTRL

LBKLT_EN

LCTLA_CLK

LCTLB_DATA

LDDC_CLK

LDDC_DATA

LVDD_EN

LIBG

LVBG

LVREFH

LVREFL

LACLKN

LACLKP

LBCLKN

LBCLKP

LADATAN0

LADATAN1

LADATAN2

LADATAP0

LADATAP1

LADATAP2

LBDATAN0

LBDATAN1

LBDATAN2

LBDATAP0

LBDATAP1

LBDATAP2

ALVISO

ALVISO

EXP_RXN0

EXP_RXN1

EXP_RXN2

EXP_RXN3

EXP_RXN4

EXP_RXN5

EXP_RXN6

EXP_RXN7

EXP_RXN8

EXP_RXN9

EXP_RXP0

EXP_RXP1

EXP_RXP2

EXP_RXP3

EXP_RXP4

EXP_RXP5

EXP_RXP6

EXP_RXP7

EXP_RXP8

EXP_RXP9

EXP_TXN0

EXP_TXN1

EXP_TXN2

EXP_TXN3

EXP_TXN4

EXP_TXN5

EXP_TXN6

EXP_TXN7

EXP_TXN8

EXP_TXN9

EXP_TXP0

EXP_TXP1

EXP_TXP2

EXP_TXP3

EXP_TXP4

EXP_TXP5

EXP_TXP6

EXP_TXP7

EXP_TXP8

EXP_TXP9

D36

D34

E30

F34

G30

H34

J30

K34

L30

M34

N30

P34

R30

T34

U30

V34

W30

Y34

D30

E34

F30

G34

H30

J34

K30

L34

M30

N34

P30

R34

T30

U34

V30

W34

E32

F36

G32

H36

J32

K36

L32

M36

N32

P36

R32

T36

U32

V36

W32

Y36

D32

E36

F32

G36

H32

J36

K32

L36

M32

N36

P32

R36

T32

U36

V32

W36

MISC

MISC

TV VGA LVDS

TV VGA LVDS

EXP_COMPI

EXP_ICOMPO

EXP_RXN10

EXP_RXN11

EXP_RXN12

EXP_RXN13

EXP_RXN14

EXP_RXN15

EXP_RXP10

EXP_RXP11

EXP_RXP12

EXP_RXP13

EXP_RXP14

EXP_RXP15

PCI-EXPRESS GRAPHICS

PCI-EXPRESS GRAPHICS

EXP_TXN10

EXP_TXN11

EXP_TXN12

EXP_TXN13

EXP_TXN14

EXP_TXN15

EXP_TXP10

EXP_TXP11

EXP_TXP12

EXP_TXP13

EXP_TXP14

EXP_TXP15

3

EXP_COMP

PEG_RXN0

PEG_RXN1

PEG_RXN2

PEG_RXN3TV_COMP_A

PEG_RXN4

PEG_RXN5

PEG_RXN6

PEG_RXN7

PEG_RXN8

PEG_RXN9

PEG_RXN10

PEG_RXN11

PEG_RXN12

PEG_RXN13

PEG_RXN14

PEG_RXN15

PEG_RXP0

PEG_RXP1

PEG_RXP2

PEG_RXP3

PEG_RXP4

PEG_RXP5

PEG_RXP6

PEG_RXP7

PEG_RXP8

PEG_RXP9

PEG_RXP10

PEG_RXP11

PEG_RXP12

PEG_RXP13

PEG_RXP14

PEG_RXP15

PEG_TXN0

PEG_TXN1

PEG_TXN2

PEG_TXN3

PEG_TXN4

PEG_TXN5

PEG_TXN6

PEG_TXN7

PEG_TXN8

PEG_TXN9

PEG_TXN10

PEG_TXN11

PEG_TXN12

PEG_TXN13

PEG_TXN14

PEG_TXN15

PEG_TXP0

PEG_TXP1

PEG_TXP2

PEG_TXP3

PEG_TXP4

PEG_TXP5

PEG_TXP6

PEG_TXP7

PEG_TXP8

PEG_TXP9

PEG_TXP10

PEG_TXP11

PEG_TXP12

PEG_TXP13

PEG_TXP14

PEG_TXP15

R430 24.9/FR430 24.9/F

PEG_RXN[0..15]

PEG_RXP[0..15]

VCC3G_PCIE

PEG_RXN[0..15] (11)

PEG_RXP[0..15] (11)

+1.5V

2

DC Blocked Cap.

PEG_TXN0

C719 0.1UC719 0.1U

C723 0.1UC723 0.1U

PEG_TXN1

PEG_TXN2

C713 0.1UC713 0.1U

PEG_TXN3

C720 0.1UC720 0.1U

PEG_TXN4

C706 0.1UC706 0.1U

PEG_TXN5

C717 0.1UC717 0.1U

C700 0.1UC700 0.1U

PEG_TXN6

PEG_TXN7

C709 0.1UC709 0.1U

PEG_TXN8

C694 0.1UC694 0.1U

PEG_TXN9

C705 0.1UC705 0.1U

PEG_TXN10

C690 0.1UC690 0.1U

C698 0.1UC698 0.1U

PEG_TXN11

PEG_TXN12

C684 0.1UC684 0.1U

PEG_TXN13

C693 0.1UC693 0.1U

PEG_TXN14

C676 0.1UC676 0.1U

PEG_TXN15

C669 0.1UC669 0.1U

INT VGA NC

C721 0.1UC721 0.1U

PEG_TXP0

PEG_TXP1

C724 0.1UC724 0.1U

PEG_TXP2

C716 0.1UC716 0.1U

PEG_TXP3

C722 0.1UC722 0.1U

PEG_TXP4

C708 0.1UC708 0.1U

C718 0.1UC718 0.1U

PEG_TXP5

PEG_TXP6

C703 0.1UC703 0.1U

PEG_TXP7

C712 0.1UC712 0.1U

PEG_TXP8

C697 0.1UC697 0.1U

PEG_TXP9

C707 0.1UC707 0.1U

C692 0.1UC692 0.1U

PEG_TXP10

PEG_TXP11

C701 0.1UC701 0.1U

PEG_TXP12

C687 0.1UC687 0.1U

PEG_TXP13

C696 0.1UC696 0.1U

PEG_TXP14

C681 0.1UC681 0.1U

C672 0.1UC672 0.1U

PEG_TXP15

PEG_TXN_C0

PEG_TXN_C1

PEG_TXN_C2

PEG_TXN_C3

PEG_TXN_C4

PEG_TXN_C5

PEG_TXN_C6

PEG_TXN_C7

PEG_TXN_C8

PEG_TXN_C9

PEG_TXN_C10

PEG_TXN_C11

PEG_TXN_C12

PEG_TXN_C13

PEG_TXN_C14

PEG_TXN_C15

PEG_TXP_C0

PEG_TXP_C1

PEG_TXP_C2

PEG_TXP_C3

PEG_TXP_C4

PEG_TXP_C5

PEG_TXP_C6

PEG_TXP_C7

PEG_TXP_C8

PEG_TXP_C9

PEG_TXP_C10

PEG_TXP_C11

PEG_TXP_C12

PEG_TXP_C13

PEG_TXP_C14

PEG_TXP_C15

+2.5V(5,8,12,20,34,39)

VCC3G_PCIE(8)

VCCP(2,3,4,5,8,9,18,20,34,39)

PEG_TXN_C[0..15]

PEG_TXP_C[0..15]

1

PEG_TXN_C[0..15] (11)

PEG_TXP_C[0..15] (11)

CFG5 CFG9

R434

R434

*2.2K

*2.2K

Low=DMIx2

High=DMIx4

CFG7

A A

CFG7(5)

Low=DT/Transportable CPU

High=Movile CPU

R52

R52

*2.2K

*2.2K

5

CFG9(5)CFG5(5)

Low=PCIE Reverse Lanes

High=PCIE Normal Operation

+2.5V +2.5V

CFG18(5)

Low=CPU core VCC 1.05V

High=CPU core VCC 1.5V

CFG18

R56

R56

*2.2K

*2.2K

R44

R44

*1K

*1K

CFG12(5)

CFG13(5) CFG6(5)

CFG11(5)

4

CFG12

CFG13

R424

R424

*2.2K

*2.2K

00 : Reserved

01 : XOR Mode Enabled

10 : All Z Mode Enabled

11 : Normal Operation

CFG11

R65

R65

*2.2K

*2.2K

Low=FSB533

R435

R435

*2.2K

*2.2K

CFG6

R54

R54

2.2K

2.2K

Low=DDR II

High=DDR

CFG3

CFG3(5)

R61

R61

*2.2K

*2.2K

Low=DDR533

3

CFG16(5)

CFG19(5)

CFG16

R451

R451

*2.2K

*2.2K

Low=FSB Dynamic ODT Disabled

High=FSB Dynamic ODT Enabled

R43

R43

*1K

*1K

CFG19

Low=CPU VTT 1.05V

High=CPU VTT 1.2V

CRT_COM#

VSYNC

HSYNC

REFSET

CRT_BLUE

CRT_GREEN

CRT_RED

2

R475 0R475 0

R471 *0R471 *0

R479 0R479 0

R480 0R480 0

R26 0R26 0

R507 0R507 0

R508 0R508 0

R509 0R509 0

R478 *150/FR478 *150/F

R477 *150/FR477 *150/F

R476 *150/FR476 *150/F

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet of

Date: Sheet of

VCCP

VCCP

PROJECT : MA2A

PROJECT : MA2A

Quanta Computer Inc.

Quanta Computer Inc.

VGA DMI(2/5)

VGA DMI(2/5)

VGA DMI(2/5)

R475

R471

R479

R480

R26

R507

R508

R509

R478

R477

R476

639Thursday, March 17, 2005

639Thursday, March 17, 2005

639Thursday, March 17, 2005

1

ATI

0

X

0

0

0

0

0

0

X

X

X

of

INTEL

X

0

X

X

X

X

X

X

150/F

150/F

150/F

3A

3A

3A

Page 8

5

D D

A_MD[0..63]

A_MD0

A_MD1

A_MD2

A_MD3

A_MD4

A_MD5

A_MD6

A_MD7

A_MD8

A_MD9

A_MD10

A_MD11

A_MD12

A_MD13

A_MD14

A_MD15

A_MD16

A_MD17

A_MD18

A_MD19

A_MD20

A_MD21

A_MD22

C C

B B

A_MD23

A_MD24

A_MD25

A_MD26

A_MD27

A_MD28

A_MD29

A_MD30

A_MD31

A_MD32

A_MD33

A_MD34

A_MD35

A_MD36

A_MD37

A_MD38

A_MD39

A_MD40

A_MD41

A_MD42

A_MD43

A_MD44

A_MD45

A_MD46

A_MD47

A_MD48

A_MD49

A_MD50

A_MD51

A_MD52

A_MD53

A_MD54

A_MD55

A_MD56

A_MD57

A_MD58

A_MD59

A_MD60

A_MD61

A_MD62

A_MD63

AG35

AH35

AL35

AL37

AH36

AJ35

AK37

AL34

AM36

AN35

AP32

AM31

AM34

AM35

AL32

AM32

AN31

AP31

AN28

AP28

AL30

AM30

AM28

AL28

AP27

AM27

AM23

AM22

AL23

AM24

AN22

AP22

AM9

AL9

AL6

AP7

AP11

AP10

AL7

AM7

AN5

AN6

AN3

AP3

AP6

AM6

AL4

AM3

AK2

AK3

AG2

AG1

AL3

AM2

AH3

AG3

AF3

AE3

AD6

AC4

AF2

AF1

AD4

AD5

U37B

U37B

SADQ0

SADQ1

SADQ2

SADQ3

SADQ4

SADQ5

SADQ6

SADQ7

SADQ8

SADQ9

SADQ10

SADQ11

SADQ12

SADQ13

SADQ14

SADQ15

SADQ16

SADQ17

SADQ18

SADQ19

SADQ20

SADQ21

SADQ22

SADQ23

SADQ24

SADQ25

SADQ26

SADQ27

SADQ28

SADQ29

SADQ30

SADQ31

SADQ32

SADQ33

SADQ34

SADQ35

SADQ36

SADQ37

SADQ38

SADQ39

SADQ40

SADQ41

SADQ42

SADQ43

SADQ44

SADQ45

SADQ46

SADQ47

SADQ48

SADQ49

SADQ50

SADQ51

SADQ52

SADQ53

SADQ54

SADQ55

SADQ56

SADQ57

SADQ58

SADQ59

SADQ60

SADQ61

SADQ62

SADQ63

ALVISO

ALVISO

4

A_BS0#

AK15

SA_BS0#

SA_BS1#

SA_BS2#

SA_DM0

SA_DM1

SA_DM2

SA_DM3

SA_DM4

SA_DM5

SA_DM6

SA_DM7

SA_DQS0

SA_DQS1

SA_DQS2

SA_DQS3

SA_DQS4

SA_DQS5

SA_DQS6

SA_DQS7

SA_DQS0#

SA_DQS1#

SA_DQS2#

SA_DQS3#

SA_DQS4#

SA_DQS5#

SA_DQS6#

SA_DQS7#

SA_MA0

SA_MA1

SA_MA2

SA_MA3

SA_MA4

SA_MA5

SA_MA6

SA_MA7

SA_MA8

SA_MA9

SA_MA10

SA_MA11

SA_MA12

SA_MA13

DDR SYSTEM MEMORY A

DDR SYSTEM MEMORY A

SA_CAS#

SA_RAS#

SA_RCVENIN#

SA_RCVENOUT#

SA_WE#

AK16

AL21

AJ37

AP35

AL29

AP24

AP9

AP4

AJ2

AD3

AK36

AP33

AN29

AP23

AM8

AM4

AJ1

AE5

AK35

AP34

AN30

AN23

AN8

AM5

AH1

AE4

AL17

AP17

AP18

AM17

AN18

AM18

AL19

AP20

AM19

AL20

AM16

AN20

AM20

AM15

AN15

AP16

SA_RCVENIN#

AF29

SA_RCVENOUT#

AF28

AP15

A_BS1#

A_BS2#

A_DM0

A_DM1

A_DM2

A_DM3

A_DM4

A_DM5

A_DM6

A_DM7

A_DQS0

A_DQS1

A_DQS2

A_DQS3

A_DQS4

A_DQS5

A_DQS6

A_DQS7

A_DQS#0

A_DQS#1

A_DQS#2

A_DQS#3

A_DQS#4

A_DQS#5

A_DQS#6

A_DQS#7

A_MA0

A_MA1

A_MA2

A_MA3

A_MA4

A_MA5

A_MA6

A_MA7

A_MA8

A_MA9

A_MA10

A_MA11

A_MA12

A_MA13

A_SCASA#

A_SRASA#

A_BMWEA#

A_BS0# (10)

A_BS1# (10)

A_BS2# (10)

A_SCASA# (10)

A_SRASA# (10)

A_BMWEA# (10)

A_DM[0..7] (10)

A_DQS[0..7] (10)

A_DQS#[0..7] (10)

A_MA[0..13] (10)

3

B_MD[0..63](10)A_MD[0..63](10)

B_MD[0..63]

B_MD0

B_MD1

B_MD2

B_MD3

B_MD4

B_MD5

B_MD6

B_MD7

B_MD8

B_MD9

B_MD10

B_MD11

B_MD12

B_MD13

B_MD14

B_MD15

B_MD16

B_MD17

B_MD18

B_MD19

B_MD20

B_MD21

B_MD22

B_MD23

B_MD24

B_MD25

B_MD26

B_MD27

B_MD28

B_MD29

B_MD30

B_MD31

B_MD32

B_MD33

B_MD34

B_MD35

B_MD36

B_MD37

B_MD38

B_MD39

B_MD40

B_MD41

B_MD42

B_MD43

B_MD44

B_MD45

B_MD46

B_MD47

B_MD48

B_MD49

B_MD50

B_MD51

B_MD52

B_MD53

B_MD54

B_MD55

B_MD56

B_MD57

B_MD58

B_MD59

B_MD60

B_MD61

B_MD62

B_MD63

AE31

AE32

AG32

AG36

AE34

AE33

AF31

AF30

AH33

AH32

AK31

AG30

AG34

AG33

AH31

AJ31

AK30

AJ30

AH29

AH28

AK29

AH30

AH27

AG28

AF24

AG23

AJ22

AK22

AH24

AH23

AG22

AJ21

AG10

AG9

AG8

AH8

AH11

AH10

AJ9

AK9

AJ7

AK6

AJ4

AH5

AK8

AJ8

AJ5

AK4

AG5

AG4

AD8

AD9

AH4

AG6

AE8

AD7

AC5

AB8

AB6

AA8

AC8

AC7

AA4

AA5

U37G

U37G

SBDQ0

SBDQ1

SBDQ2

SBDQ3

SBDQ4

SBDQ5

SBDQ6

SBDQ7

SBDQ8

SBDQ9

SBDQ10

SBDQ11

SBDQ12

SBDQ13

SBDQ14

SBDQ15

SBDQ16

SBDQ17

SBDQ18

SBDQ19

SBDQ20

SBDQ21

SBDQ22

SBDQ23

SBDQ24

SBDQ25

SBDQ26

SBDQ27

SBDQ28

SBDQ29

SBDQ30

SBDQ31

SBDQ32

SBDQ33

SBDQ34

SBDQ35

SBDQ36

SBDQ37

SBDQ38

SBDQ39

SBDQ40

SBDQ41

SBDQ42

SBDQ43

SBDQ44

SBDQ45

SBDQ46

SBDQ47

SBDQ48

SBDQ49

SBDQ50

SBDQ51

SBDQ52

SBDQ53

SBDQ54

SBDQ55

SBDQ56

SBDQ57

SBDQ58

SBDQ59

SBDQ60

SBDQ61

SBDQ62

SBDQ63

ALVISO

ALVISO

2

AJ15

SB_BS0#

AG17

SB_BS1#

AG21

SB_BS2#

AF32

SB_DM0

AK34

SB_DM1

AK27

SB_DM2

AK24

SB_DM3

AJ10

SB_DM4

AK5

SB_DM5

AE7

SB_DM6

AB7

SB_DM7

AF34

SB_DQS0

AK32

SB_DQS1

AJ28

SB_DQS2

AK23

SB_DQS3

AM10

SB_DQS4

AH6

SB_DQS5

AF8

SB_DQS6

AB4

SB_DQS7

SB_MA0

SB_MA1

SB_MA2

SB_MA3

SB_MA4

SB_MA5

SB_MA6

SB_MA7

SB_MA8

SB_MA9

SB_MA10

SB_MA11

SB_MA12

SB_MA13

SB_CAS#

SB_RAS#

SB_WE#

AF35

AK33

AK28

AJ23

AL10

AH7

AF7

AB5

AH17

AK17

AH18

AJ18

AK18

AJ19

AK19

AH19

AJ20

AH20

AJ16

AG18

AG20

AG15

AH14

AK14

AF15

AF14

AH16

SB_DQS0#

SB_DQS1#

SB_DQS2#

SB_DQS3#

SB_DQS4#

SB_DQS5#

SB_DQS6#

SB_DQS7#

DDR SYSTEM MEMORY B

DDR SYSTEM MEMORY B

SB_RCVENIN#

SB_RCVENOUT#

B_BS0#

B_BS1#

B_BS2#

B_DM0

B_DM1

B_DM2

B_DM3

B_DM4

B_DM5

B_DM6

B_DM7

B_DQS0

B_DQS1

B_DQS2

B_DQS3

B_DQS4

B_DQS5

B_DQS6

B_DQS7

B_DQS#0

B_DQS#1

B_DQS#2

B_DQS#3

B_DQS#4

B_DQS#5

B_DQS#6

B_DQS#7

B_MA0

B_MA1

B_MA2

B_MA3

B_MA4

B_MA5

B_MA6

B_MA7

B_MA8

B_MA9

B_MA10

B_MA11

B_MA12

B_MA13

B_SCASA#

B_SRASA#

SB_RCVENIN#

SB_RCVENOUT#

B_BMWEA#

B_BS0# (10)

B_BS1# (10)

B_BS2# (10)

B_SCASA# (10)

B_SRASA# (10)

T16T16T21T21

T17T17T19T19

B_BMWEA# (10)

1

B_DM[0..7] (10)

B_DQS[0..7] (10)

B_DQS#[0..7] (10)

B_MA[0..13] (10)

A A

PROJECT : MA2A

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet of

5

4

3

2

Date: Sheet of

PROJECT : MA2A

Quanta Computer Inc.

Quanta Computer Inc.

ALVISO DDR(3/5)

ALVISO DDR(3/5)

ALVISO DDR(3/5)

1

of

739Thursday, March 17, 2005

739Thursday, March 17, 2005

739Thursday, March 17, 2005

3A

3A

3A

Page 9

5

VCCP

C752

C752

C746

C746

4.7U/10V

4.7U/10V

2.2U

2.2U

VCC3G1

VCC3G2

W37

VCC3G0

AE37

VCC3G_PCIE

VCCA_SM3

AF18

VCCP

VCCP

VCCA_SM1

VCCA_SM2

AF19

AP19

AF20

C742

C742

0.1U

0.1U

L39

L39

BLM11A121S

BLM11A121S

D D

C747

VCCP_GMCH_CAP3

C704

C704

0.22U

0.22U

VCCP_GMCH_CAP2

VSSA_3GBG

G37

VCCA_3GBG

F37

C751

C751

0.1U

0.1U

Y27

C747

0.47U/10V

0.47U/10V

VCCA_3GPLL0

VCCA_3GPLL1

VCCA_3GPLL2

Y29

Y28

VCCA_3GPLL

R374 0.5/FR374 0.5/F

C660

C660

10U

10U

VCC3G6

J37

L37

VCCP_GMCH_CAP1

VCC3G4

VCC3G5

N37

C748

C748

0.47U

0.47U

N6

VTT37M6VTT38A6VTT39N5VTT40M5VTT41N4VTT42M4VTT43N3VTT44M3VTT45N2VTT46M2VTT47B2VTT48V1VTT49N1VTT50M1VTT51

VCC3G3

U37

R37

C725

C725

0.22U

0.22U

VCCP_GMCH_CAP4

G1

C C

VCCA_3GPLL

+2.5V

C659

C659

0.1U

0.1U

B B

2 1

D31 *RB751V-40D31 *RB751V-40

+2.5V

VCCP

U9

VTT26R9VTT27P9VTT28N9VTT29M9VTT30L9VTT31J9VTT32N8VTT33M8VTT34N7VTT35M7VTT36

VCCTX_LVDS1

VCCTX_LVDS2

VCCA_SM0

B28

A28

A27

VCC_DDRDLL

4

R489 *0R489 *0

+2.5V

L14

C775 10UC775 10U

R488 0R488 0

R449 *10R449 *10

C738 0.1UC738 0.1U

C739 0.022UC739 0.022U

R459 *0R459 *0

C741 0C741 0

C766 *10UC766 *10U

M11

L11

K11

W10

V10

U10

T10

R10

P10

N10

M10

K10

J10

VTT15

VTT16

VTT17

VTT18

VTT19

VTT20

VTT21

VTT22

VTT23Y9VTT24W9VTT25

VCCSM56

VCCSM57

VCCSM58

VCCSM59

VCCSM60

VCCSM61

VCCSM62

VCCSM63

VCCSM64

VCCTX_LVDS0

AB9

AP8

AE1

AM1

+2.5V

C761

C761

4.7U/10V

4.7U/10V

+1.5V +1.5V

AF12

AE12

AB11

AB10

AD11

AC11

V1.8_DDR_CAP6

V1.8_DDR_CAP3

V1.8_DDR_CAP4

Note: All VCCSM pins

shorted internally.

VTT13

VTT14

VCCSM54

VCCSM55

AG12

N11

VTT10

VTT11

VTT12

VCCSM51

VCCSM52

VCCSM53

AJ12

AL12

AK12

AH12

C686

C686

0.1U

0.1U

VCC_DDRDLL

P11

VTT9

VCCSM50

AM12

BLM11A121S

BLM11A121S

C209 0.1UC209 0.1U

C245 470U

C245 470U

+

+

V11

U11

T11

R11

VTT4

VTT5

VTT6

VTT7

VTT8

VCCSM45

VCCSM46

VCCSM47

VCCSM48

VCCSM49

AF13

AE13

AP12

AN12

C673

C673

0.1U

0.1U

+

+

C264

C264

100U

100U

W11

AG13

L14

K12

VTT3

VCCSM44

AH13

J13

VTT2

VCCSM43

AJ13

C662

C662

0.1U

0.1U

VTT1

VCCSM42

C699 0.1UC699 0.1U

C168 470U

C168 470U

H20

K13

VTT0

VCC_SYNC

VCCSM39

VCCSM40

VCCSM41

AL13

AK13

AM13

C229

C229

0.1U

0.1U

BLM11A121S

BLM11A121S

AN13

3

L45

L45

+

+

F19

E19

AA1

G19

VCCSM37

VCCSM38

AE14

AP13

C35

AA2

VCCA_HPLL

VCCA_MPLL

VVSSA_CRTDAC

VCCSM36

VCCA_DPLLB

VCCA_CRTDAC0

VCCA_CRTDAC1

VCCSM30

VCCSM31

VCCSM32

VCCSM33

VCCSM34

VCCSM35

AE20

AE19

AE18

AE17

AE16

AE15

+

+

C262

C262

330uF

330uF

L16

L16

BLM11A121S

BLM11A121S

2

ATI

INTEL

X

K22

VCC36

VCCSM13

AH26

10U

0

X

X

0.1U

0.022U

X

0

X

K23

VCC34

VCC35

VCCSM11

VCCSM12

AJ26

C128

C128

0.1U

0.1U

K24

VCC33

VCCSM10

AK26

V1.8_DDR_CAP5

J25

VCC32

VCCSM9

AL26

C661

C661

0.1U

0.1U

K25

AM26

0

10U

X

RB751V-40

10

0.1U

0.022U

0

0.1U

10U

C144

C144

0.1U

0.1U

H27

K26

H26

VCC29

VCC30

VCC31

VCCSM6

VCCSM7

VCCSM8

AP26

AC27

AN26

V1.8_DDR_CAP2

C110

C110

C127

C127

10U

10U

0.1U

0.1U

J28

H28

G28

V27

U27

T27

R27

P27

N27

M27

L27

K27

J27

VCC15

VCC16

VCC17

VCC18

VCC19

VCC20

VCC21

VCC22

VCC23

VCC24

VCC25

VCC26

VCC27

VCC28

VCCD_LVDS2

VCCA_LVDS

VCCHV0

VCCHV1

VCCHV2

VCCSM0

VCCSM1

VCCSM2

VCCSM3

VCCSM4

VCCSM5

A25

A35

B22

B21

A21

AP29

AH37

AD28

AD27

AM37

V1.8_DDR_CAP1

C671

C671

C667

C667

0.1U

0.1U

0.1U

0.1U

+2.5V +2.5V +1.5V

C740

C740

C762

C762

0.1U

0.1U

10U

10U

K28

VCC14

VCCD_LVDS1

B25

C117

C117

10U

10U

L28

VCC13

VCCD_LVDS0

B26

C749

C749

0.01U

0.01U

M28

N28

VCC12

H17

VCCP

P28

VCC11

VCCDQ_TVDAC

D19

R28

VCC10

VCCD_TVDAC

VCC9

C104

C104

10U

10U

T28

VCC8

VSSA_TVBG

G18

C750

C750

0.1U

0.1U

U28

H18

VCC7

VCCA_TVBG

V28

VCC6

E18

VCC5

VCCA_TVDACC1

F18

+1.5V

VCC4

VCCA_TVDACC0

C18

C737

C737

0.1U

0.1U

VCC3

VCCA_TVDACB1

D18

VCC2

VCCA_TVDACB0

E17

U37H

U37H

ALVISO

ALVISO

VCC0

VCC1

VCCA_TVDACA0

VCCA_TVDACA1

F17

R470 *0R470 *0

C776

C776

10U

10U

T29

R29

N29

M29

K29

J29

R489

+1.5V

W18

V18

T18

K18

K17

B23

AC1

AC2

VCC45

VCC46

VCC47

VCC48

VCCA_DPLLA

VCCH_MPLL0

VCCH_MPLL1

POWER

POWER