Page 1

1

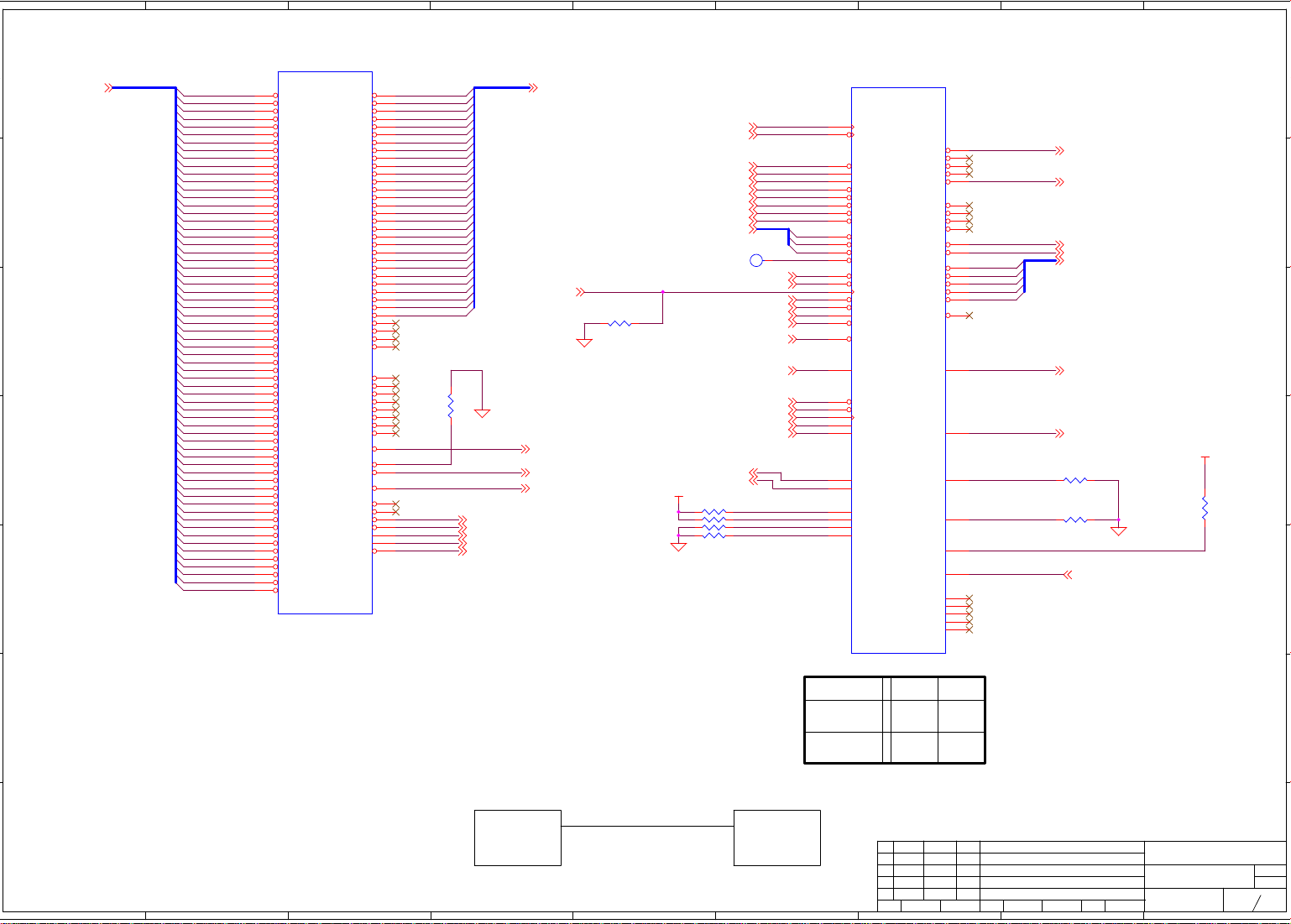

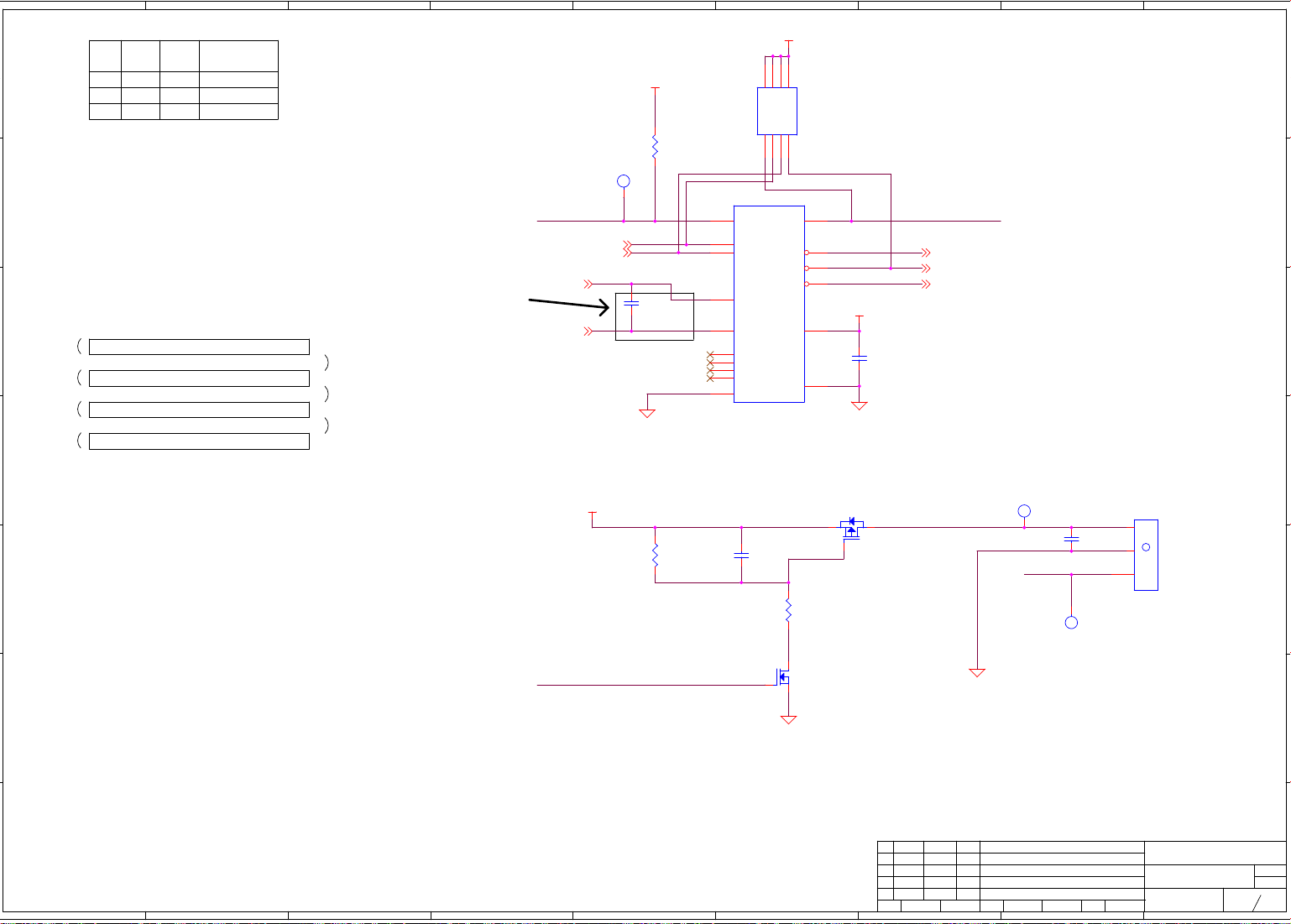

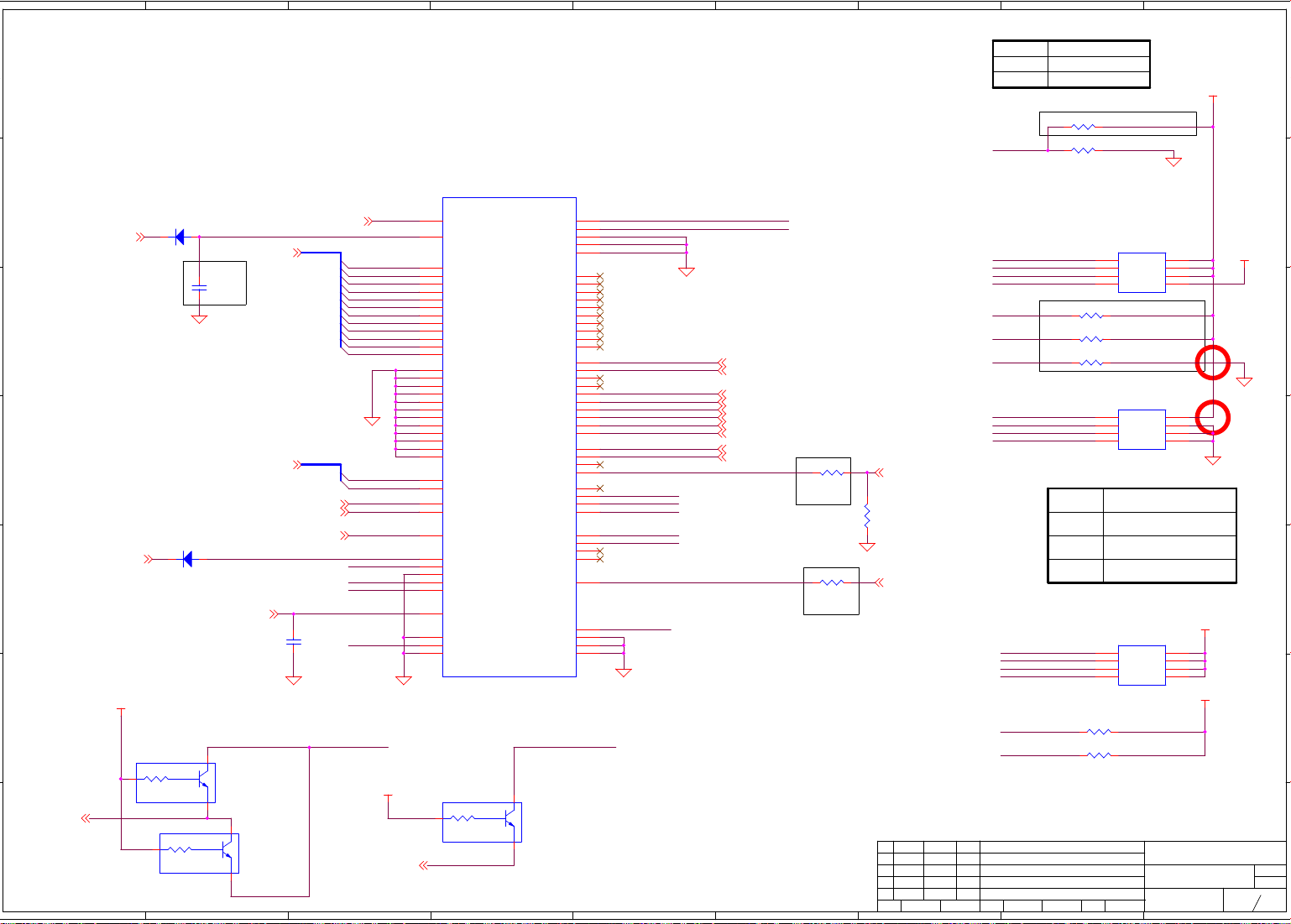

Laurel Main Board REV.02

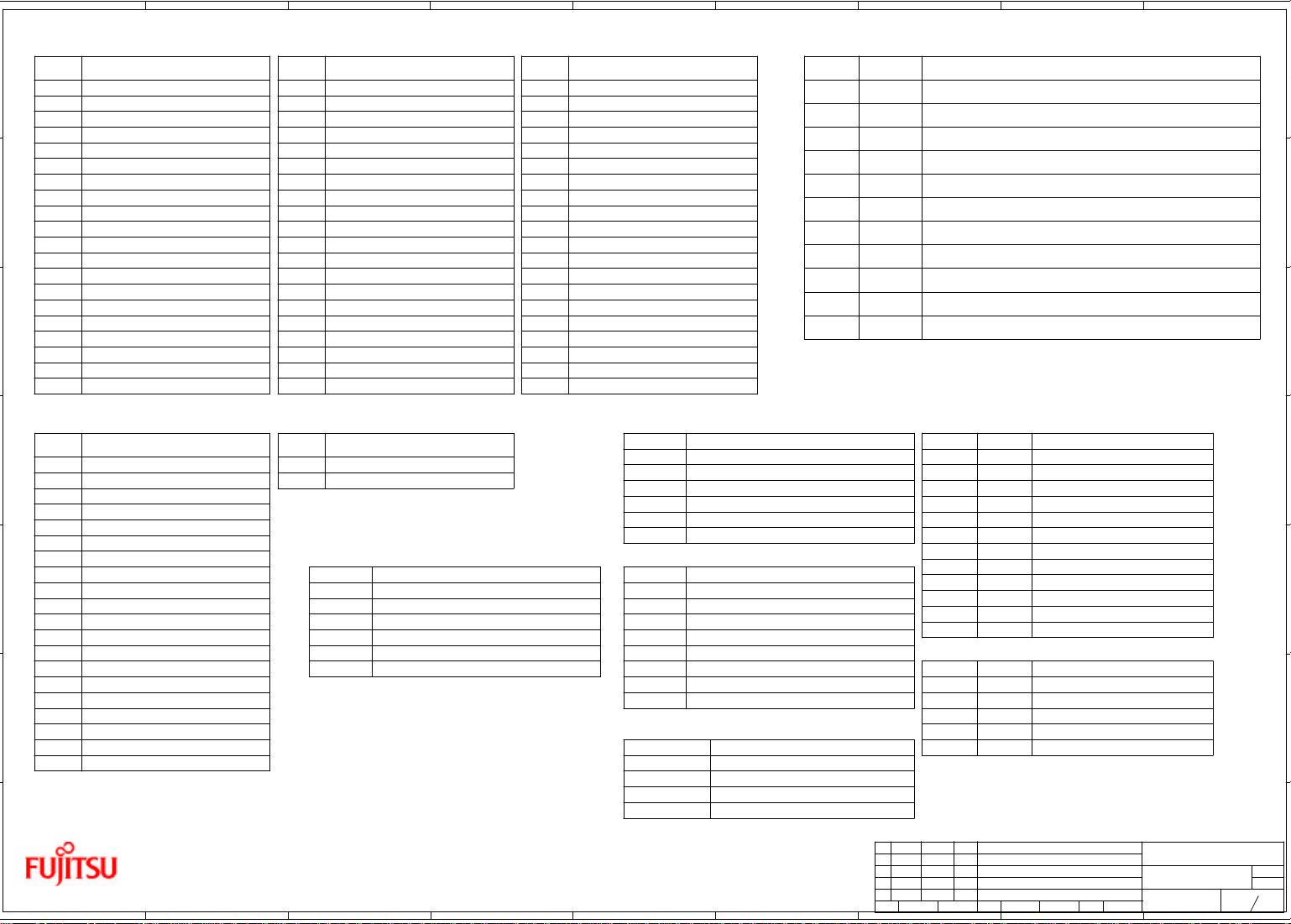

Index

2

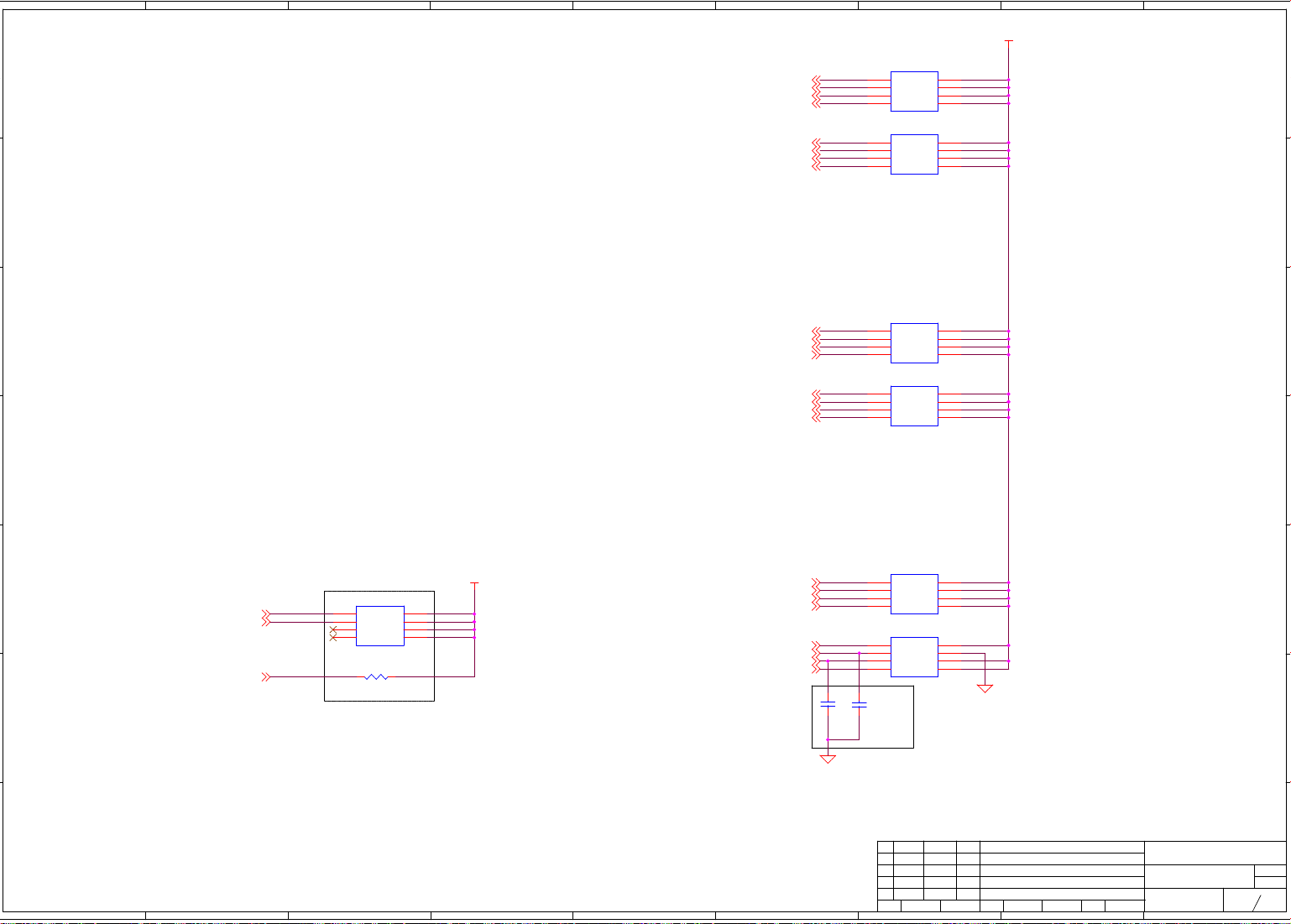

System Block

PAGE CONTENTS

01

02

03

04

05

06

07

08

09

10

11

12

13

14

15

16

17

18

19

20

TOP PAGE

Block Diagram

R-C for EMI

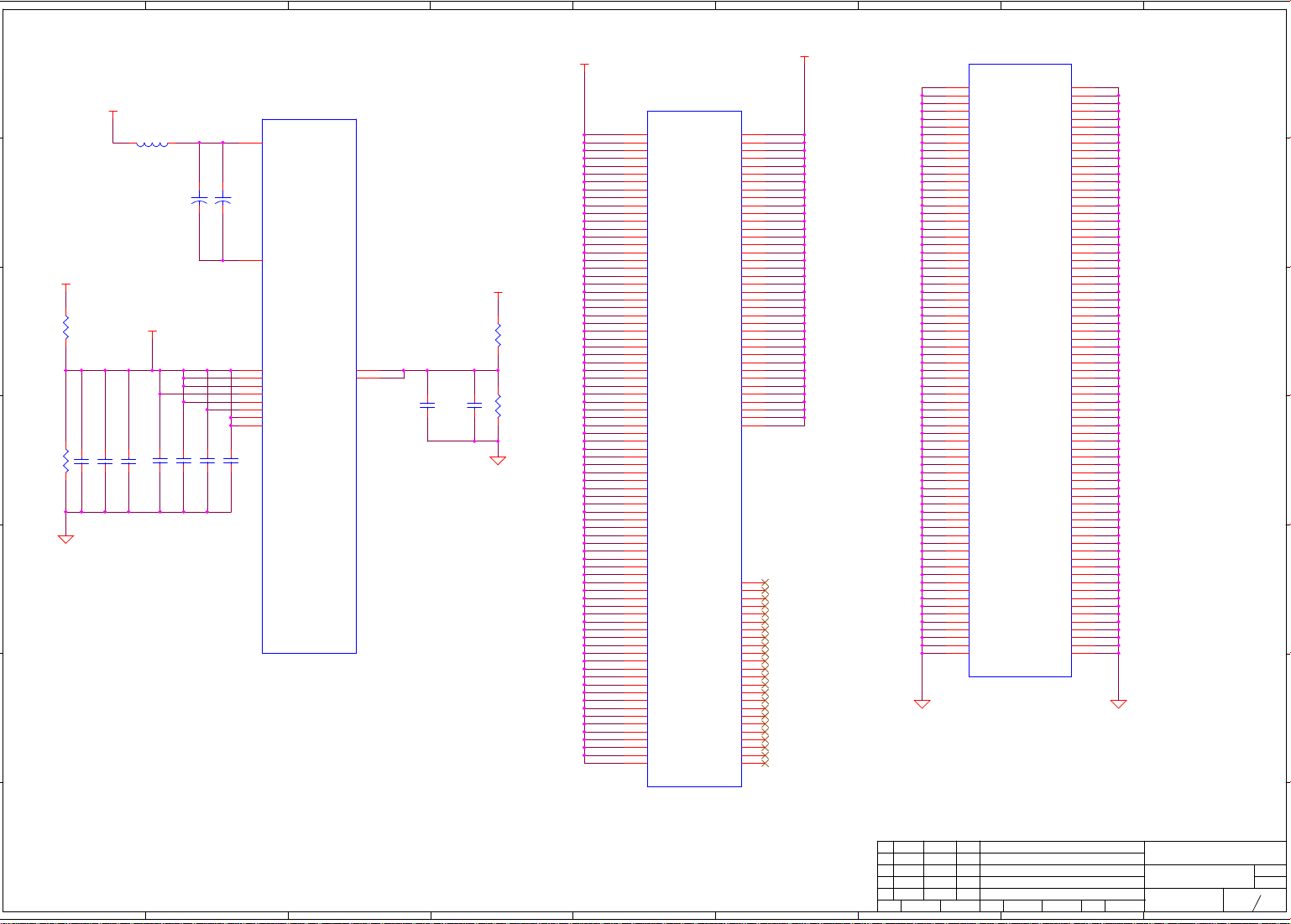

PLL

CPU(Tualatin)

CPU(Tualatin)

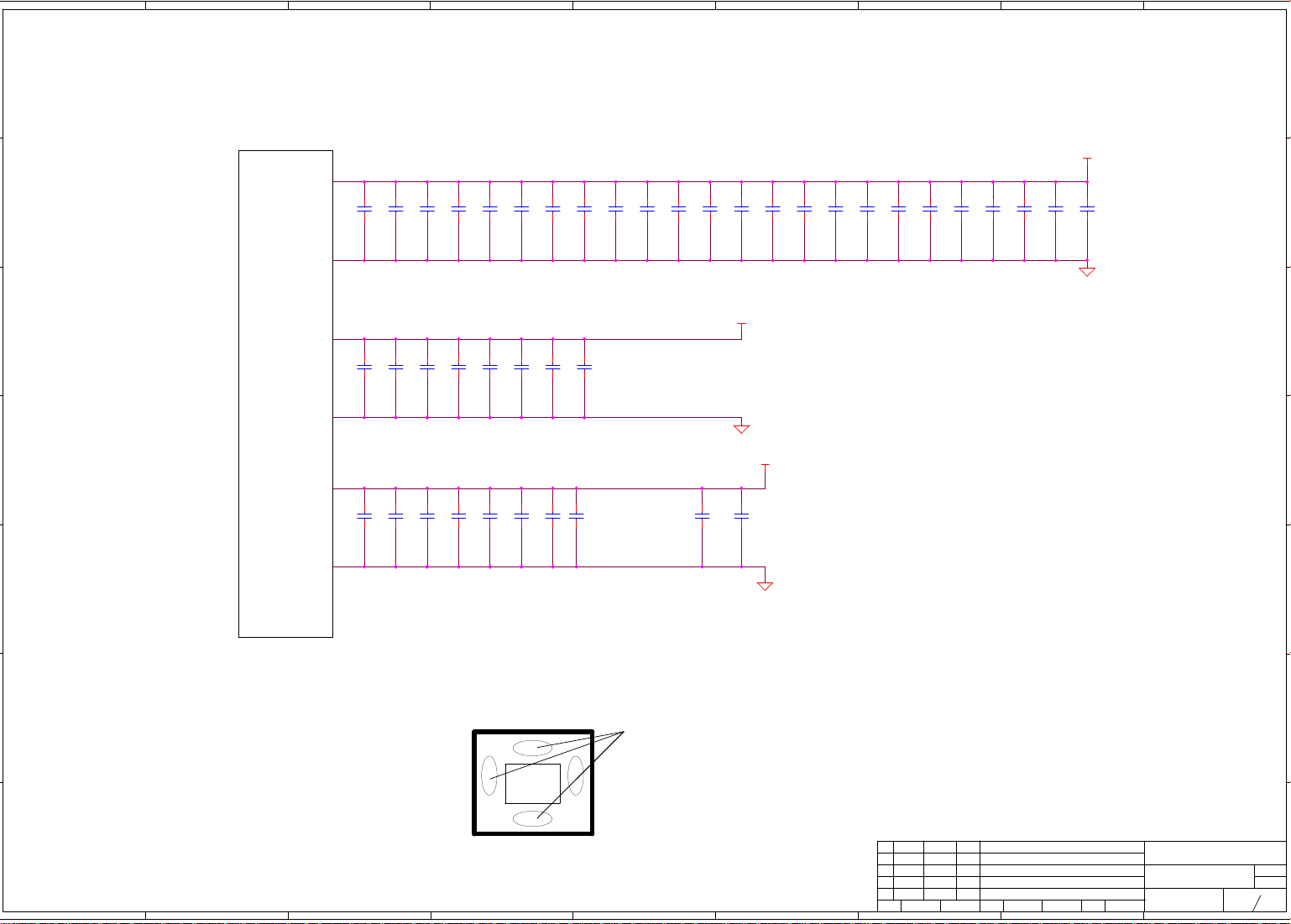

PassC for CPU

Pull up for CPU

BLANK

BLANK

GMCH(Almador-M)

GMCH(Almador-M)

GMCH(Almador-M),STRAP

PassC for GMCH(Almador-M)

Thermister, FAN

ICH3-M

ICH3-M

Pullup for ICH3-M

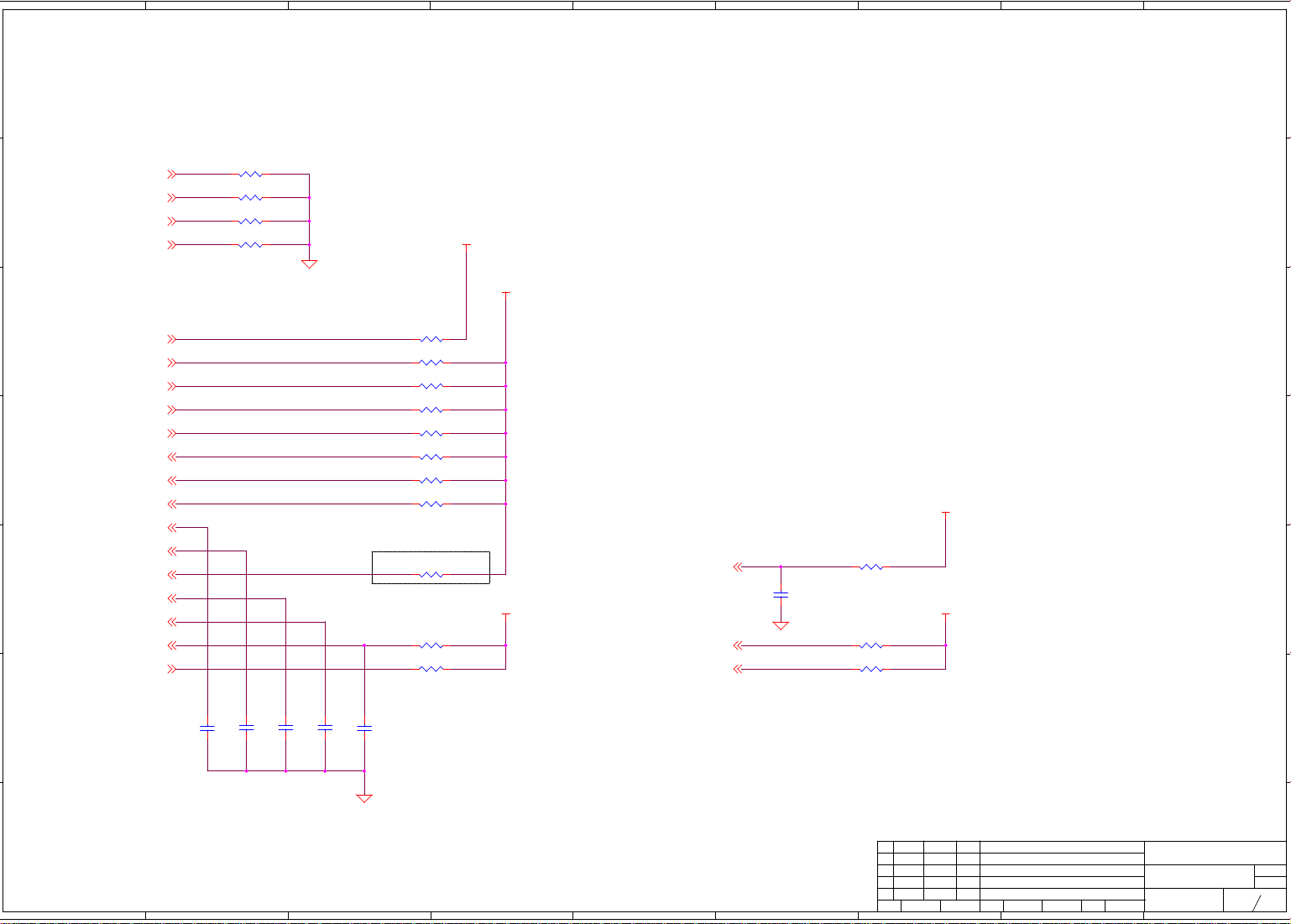

Pullup for AGP,PCI,LPC

FWH(BIOS)

PAGE CONTENTS

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

3

BLANK

SDRAM Dumping

DIMM CN

VCH

VCH

S-VIDEO

BLANK

IEEE1394

BLANK

PCIC

PCIC

PCIC POW

PCMCIA SLOT

CODEC

Audio AMP

MIC AMP

BLANK

Super-IO

KBC

HOOP

4

5

6

7

8

9

Version History

PAGE

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

CONTENTS

HOOP

Pullup for HOOP

LAN

LAN

BLANK

RESET

S-OUT CN

KBD/POINTING/LCD CN

APPLI CN/LID SW/MAIN SW

USB/IEEE1394 CN

MiniPCI CN

BLANK

FingerPrint CN

P-R CN

AUDIO CN

DOCK CN

HDD CN

ConnectorBoard CN

Power Interface require

Version Date

01-01 2001/Jul/18 First Edition for PCB placement

2001/Aug/24

First Edition for PCB desgin01-02

02-01

Description

Power Block

PAGE CONTENTS

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

Proprietary & Confidential

Power/TopPage

Power /DDC/CPU Core

Power/DDC/CPU Bus

Power/DDC/3V,5V

Power/DDC/Charger

Power/LDO/System

Power/LDO/Audio

Power/LDO/PMU

Power/Node/DCIn

Power/Node/Battery

Power/PMU/Etc3

Power/Node/Switch1

Power/Node/Switch2

Power/PMU/PMU

Power/PMU/AmMeter

Power/PMU/VolMeter

Power/PMU/Etc1

Power/PMU/Etc2

1

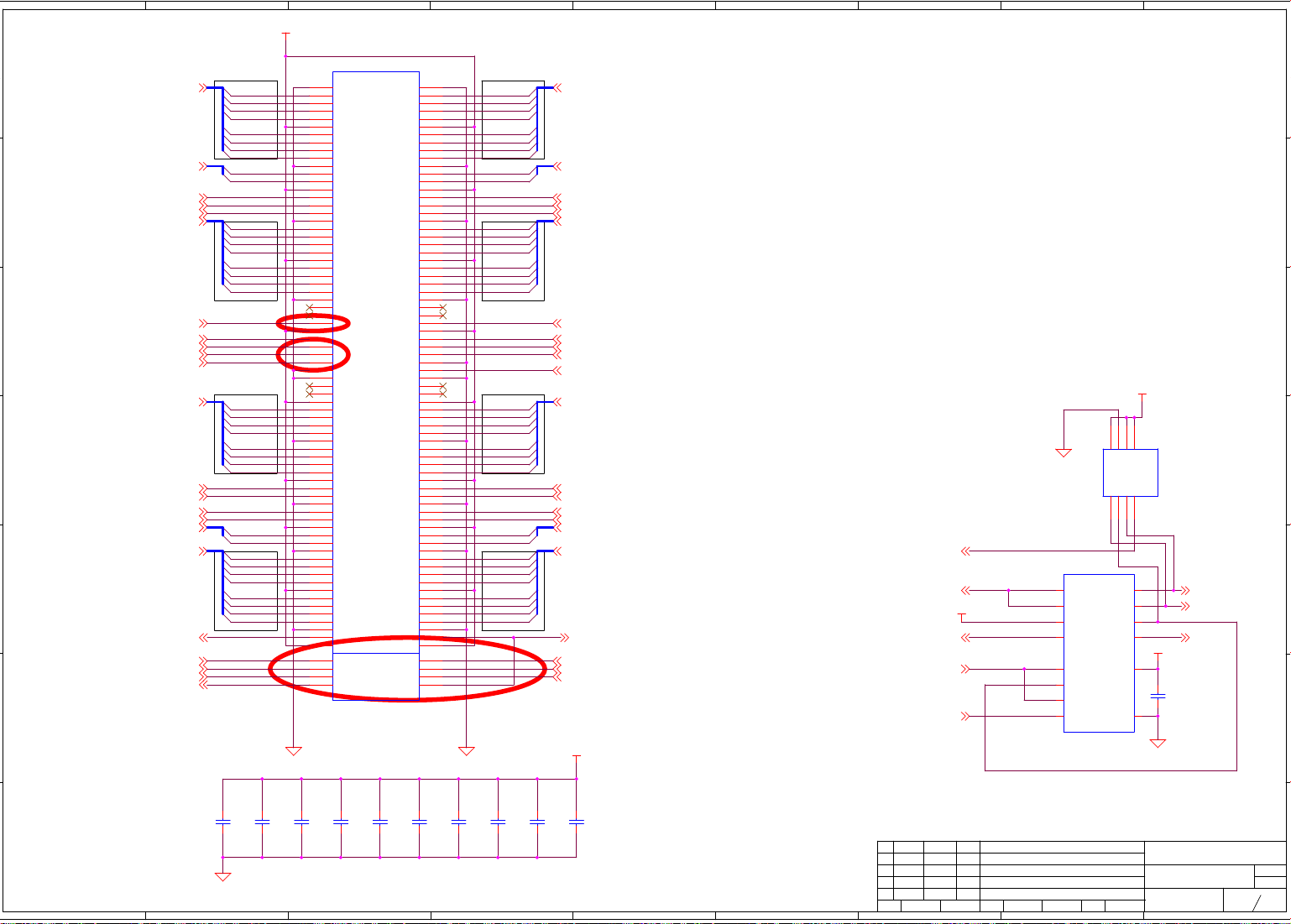

PCI REQ#/GNT#

PAGE CONTENTS

81

82

Power/PMU/Etc2

Power/Reserved

USB CHANEL

PCIINT#

USB1

USB2

USB3

USB4

USB5

USB6

Device

USB CN1

USB CN2 / Port Replicator

BAY USB

Blue-Tooth / TachPAD

Finger-P

Unused

REQ#/GNT# Device

REQ#0

REQ#1

REQ#2

REQ#3

REQ#4

REQ#5

IEEE1394 (Programable arbitration latency)

PCIC

MiniPCI

On Board LAN

Unused

Unused

PCI INTERRUPT

PCIINT#

INT#0

INT#1

INT#2

INT#3

INT#4

INT#5

INT#6

INT#7

Device

PCIC

PCIC

Mini-PCI

Mini-PCI

IEEE1394

On Board LAN

Unused

Unused

ICH-LAN /

SMBus / AC97-0,1

USB-0

USB-1

SMBus

PLL,ADM1030,KBC0,0,0

0,0,1

0,1,0

0,1,1

2

3

4

5

007,DOCK,PMU

DIMM Slot 1

DIMM Slot 2

6

PCI BUS NUMBER = #0

IDSEL

AD16

AD17

AD18

PCI BUS NUMBER = #2

IDSEL Device

AD24

AD26 0Ah

AD28 0Ch

AD29SMBCNT[2:0] Device

Rev.

DATE Design

2001.02.15

7

00h

01h

02h

1Fh

Dev.ID

08h ICH2_M(LAN)

0Dh

Appr.

CheckDesign

Konaka

DeviceDev.ID

GMCH(HOST/DRAM BRIDGE)

GMCH(AGP BRIDGE)

GMCH(INTERNAL GRAPHICS)

ICH2M(HUB IF)1Eh

ICH2-M(LPC,IDE,USB,SMBUS,AC97)

OnBoard LAN09hAD25

OZ711

IEEE1394

MiniPCI

Description

Fuchida Fukuda

Appr.

8

TITLE

Laurel

DRAW. No.

C1CPxxxxxx-X1

FUJITSU

LTD.

9

SHEET

CAST

1 82

Page 2

1

2

3

4

5

6

7

8

9

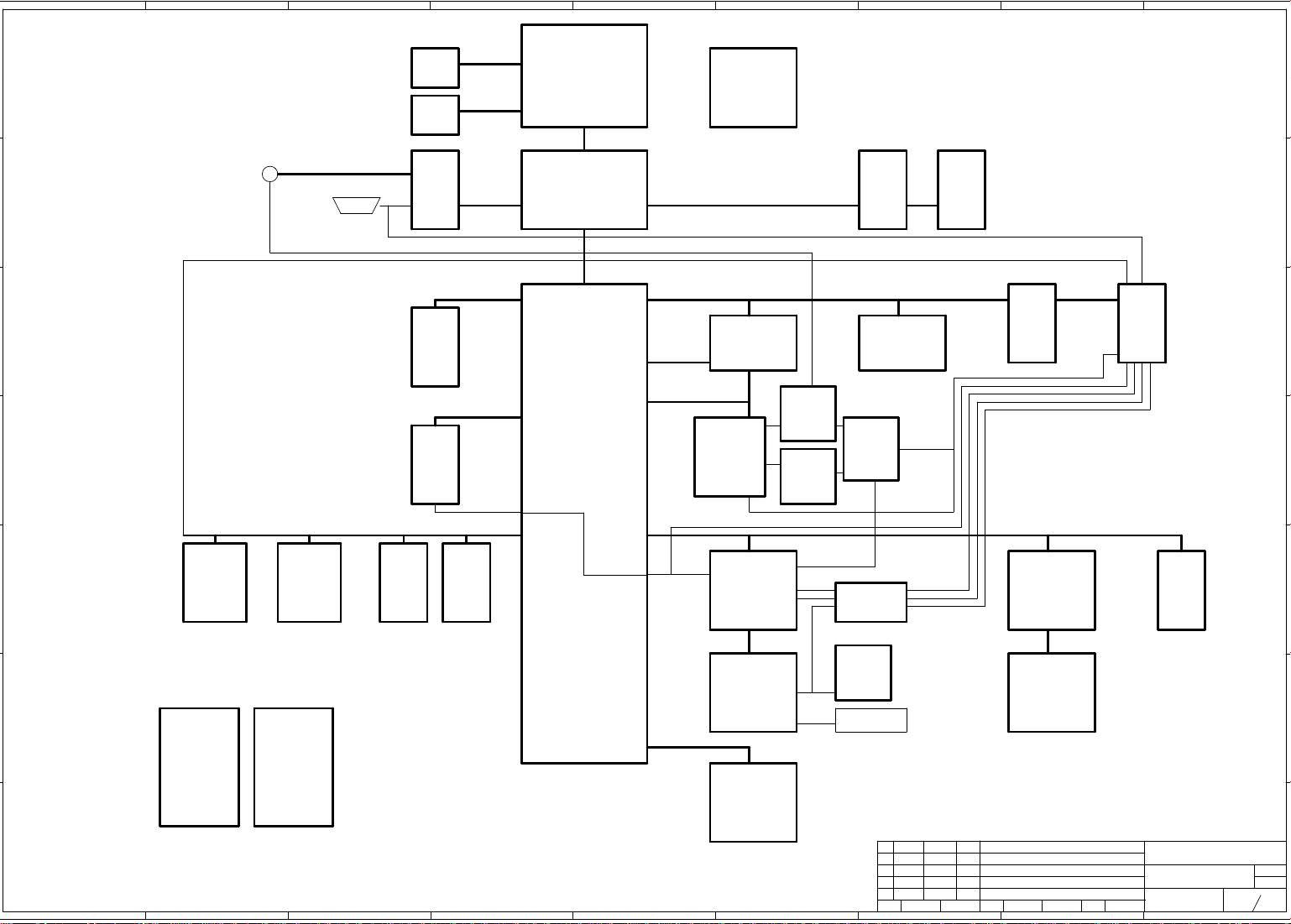

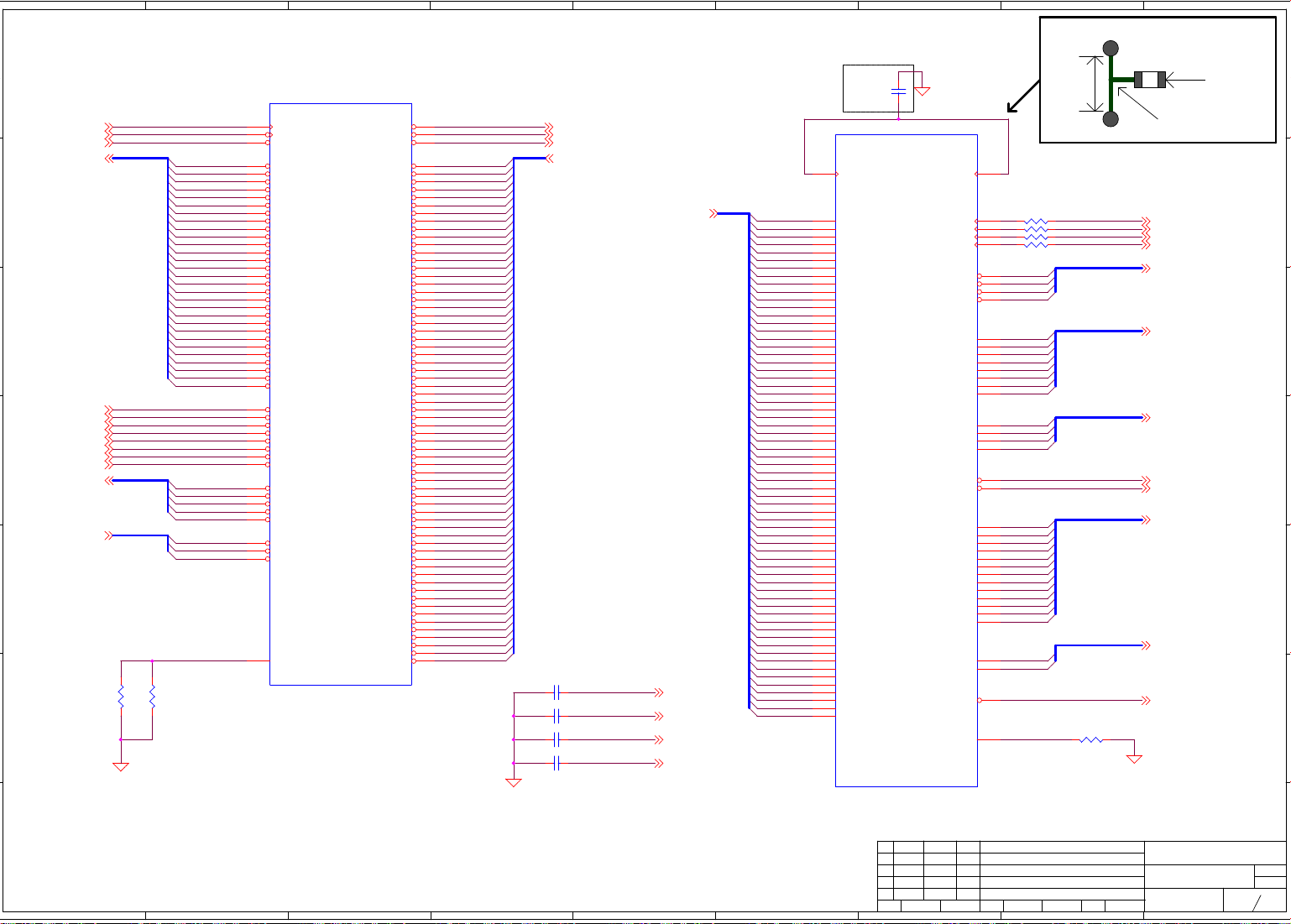

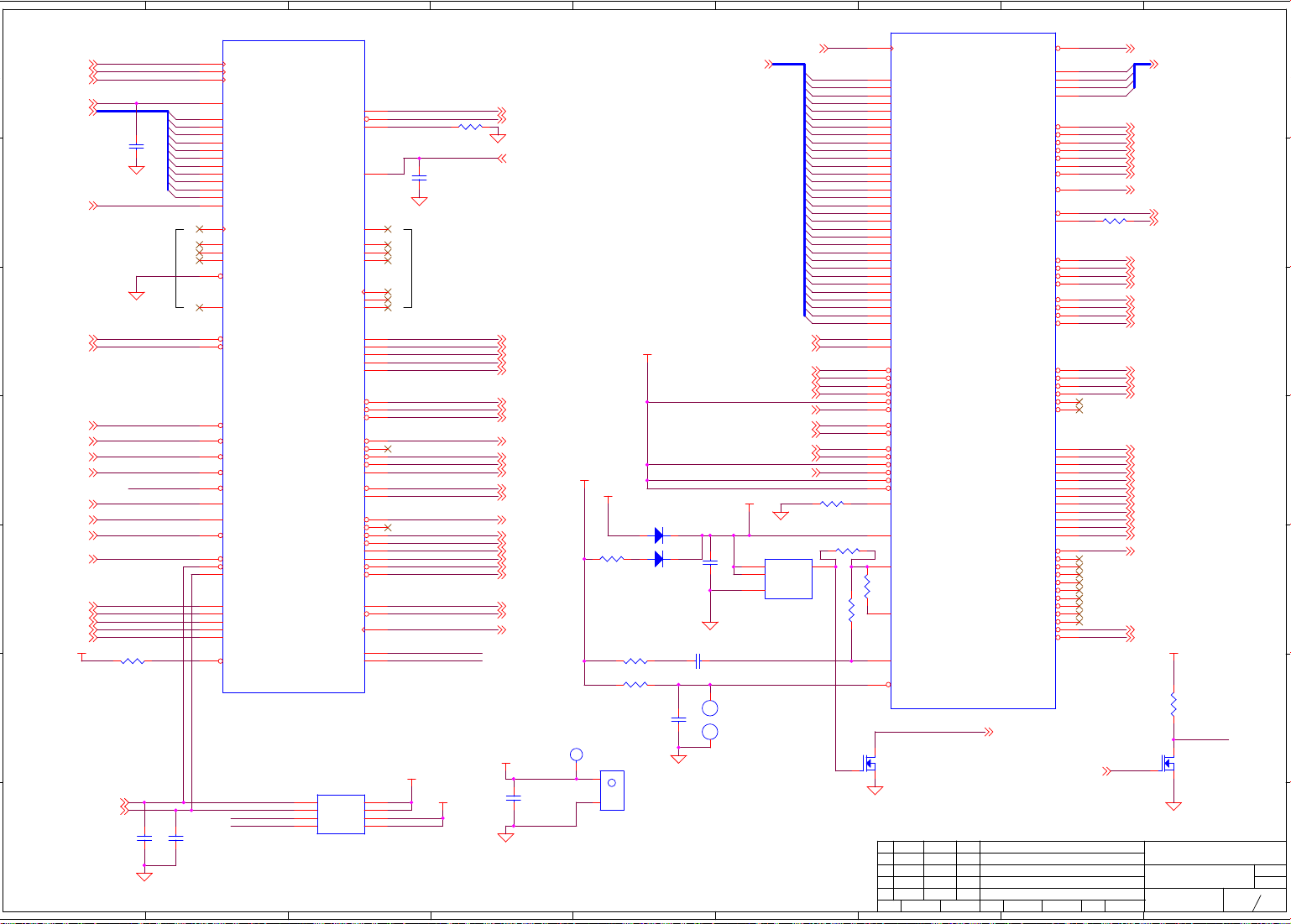

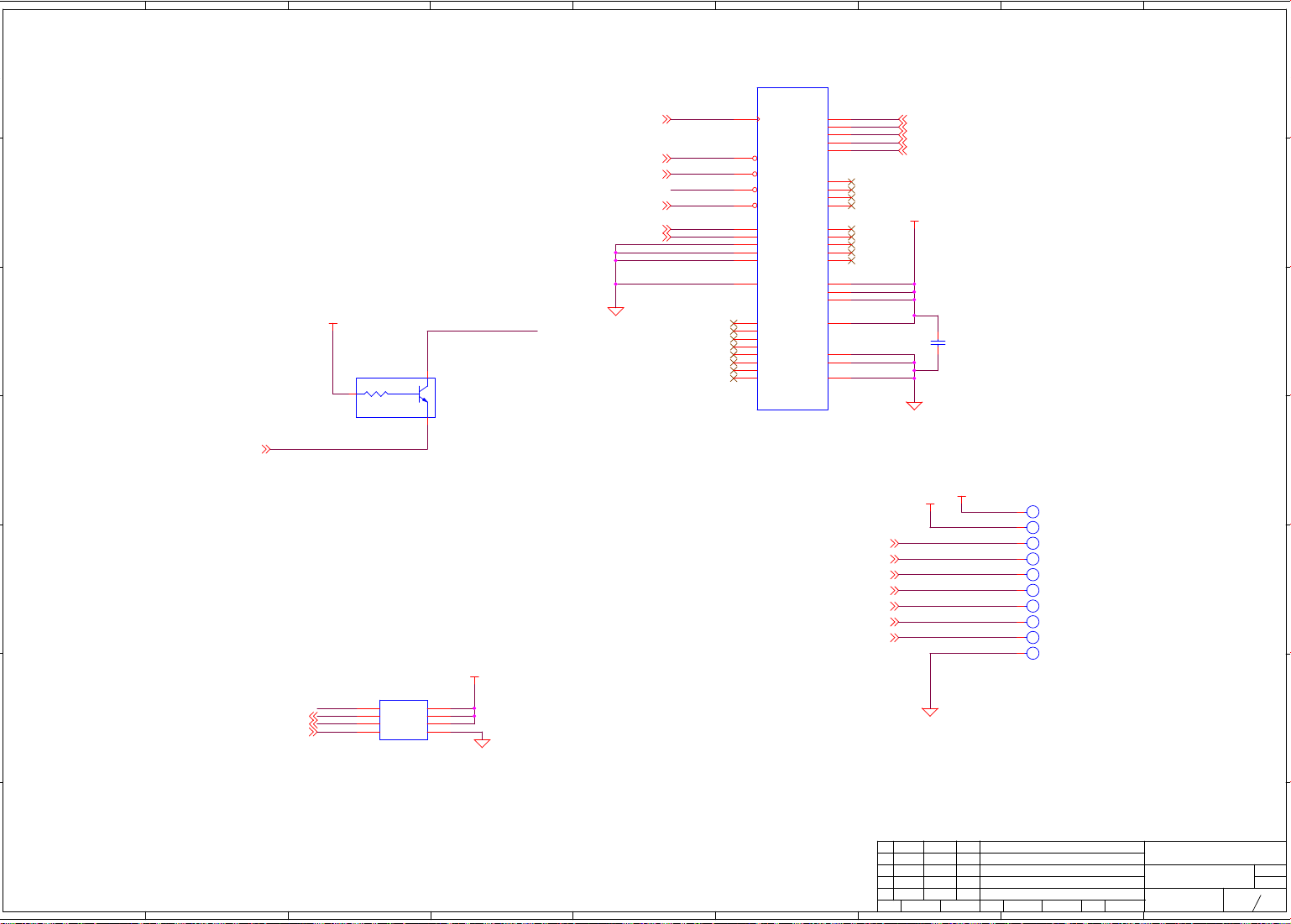

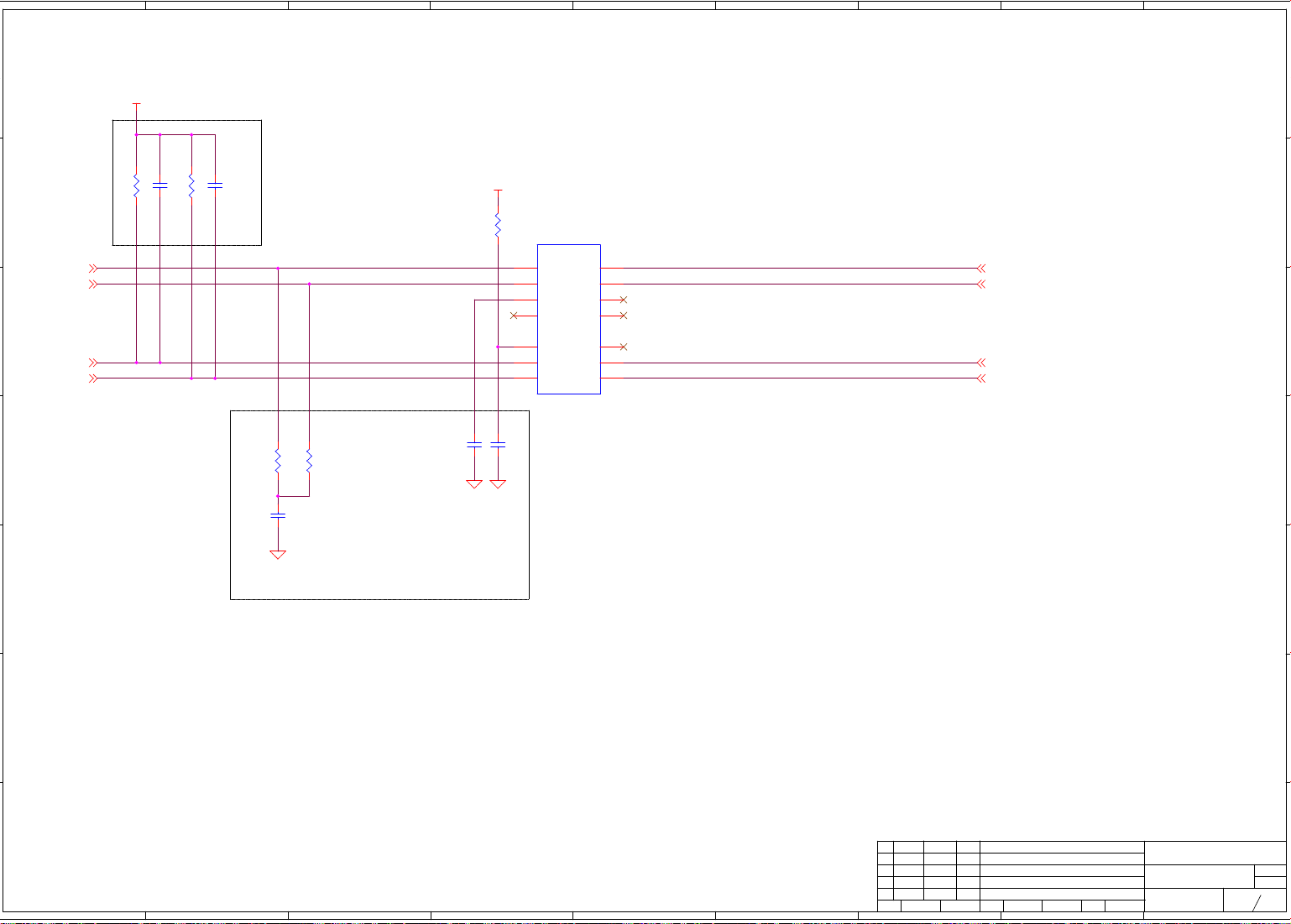

Laurel system block diagram

P28 LCD CN

LVDS

P29 CRT

ITP

Thermal

Sensor

VGA

P24

P25

P26

IDE0 ATA66/100

HDD

P40

IDE1 ATA66/100

BAY0

P41

P10

P15

AGPx4 1.5V

USB

Moblle

Tualatin

Coppermine-T

Micro-FCPGA

479pin

P5,P6

PSB 1.2V 133MHz

Almador-M

625

BGA

P11,P12,P13

Hublink 1.8V 266MHz

ICH3-M

421 BGA

P16,P17

PLL

SDRAM 3.3V 133MHz

PCI 3.3V 33MHz

LAN

AC97

Audio

CODEC

P35

P4

P23 P23

SODIMM0

INT_MIC

OZ711E1Mini PCI

P34 P30,P31 P56 P57

MIC

AMP

P37

Audio

AMP

P36

Audio

CN

P38

PHONE,MIC

LINE-IN

SODIMM1

CRT

USB4,USB5

PCI_D

Q-SW

FDD

Serial

Parallel

PS/2

LPC 3.3V 33MHz

DOCK

CN

P58

USB3

Bluetooth

P52

System

DC/DC

Module

USB2

FingerPrint

P52

Battery

Module

USB0USB1

P51 P51

FDD

SIO

P42

KBC

P43

ISA

FIR

I/O_CN

P46

DMC

P45

KB

P44

HOOP

P47,P48

80PORT

P20

Power

Controler

P77

FWH

P61-P82 P61-P82

1

2

3

4

5

P20

Resource

TITLE

Laurel

DRAW. No.

Rev.

DATE Design

6

2001.01.16 Komahara

Appr.

7

Description

CheckDesign

Yoshida Aoki

Appr.

8

C1CPxxxxxx-X1

FUJITSU

LTD.

9

SHEET

CAST

2 82

Page 3

1

2

3

4

5

6

7

8

9

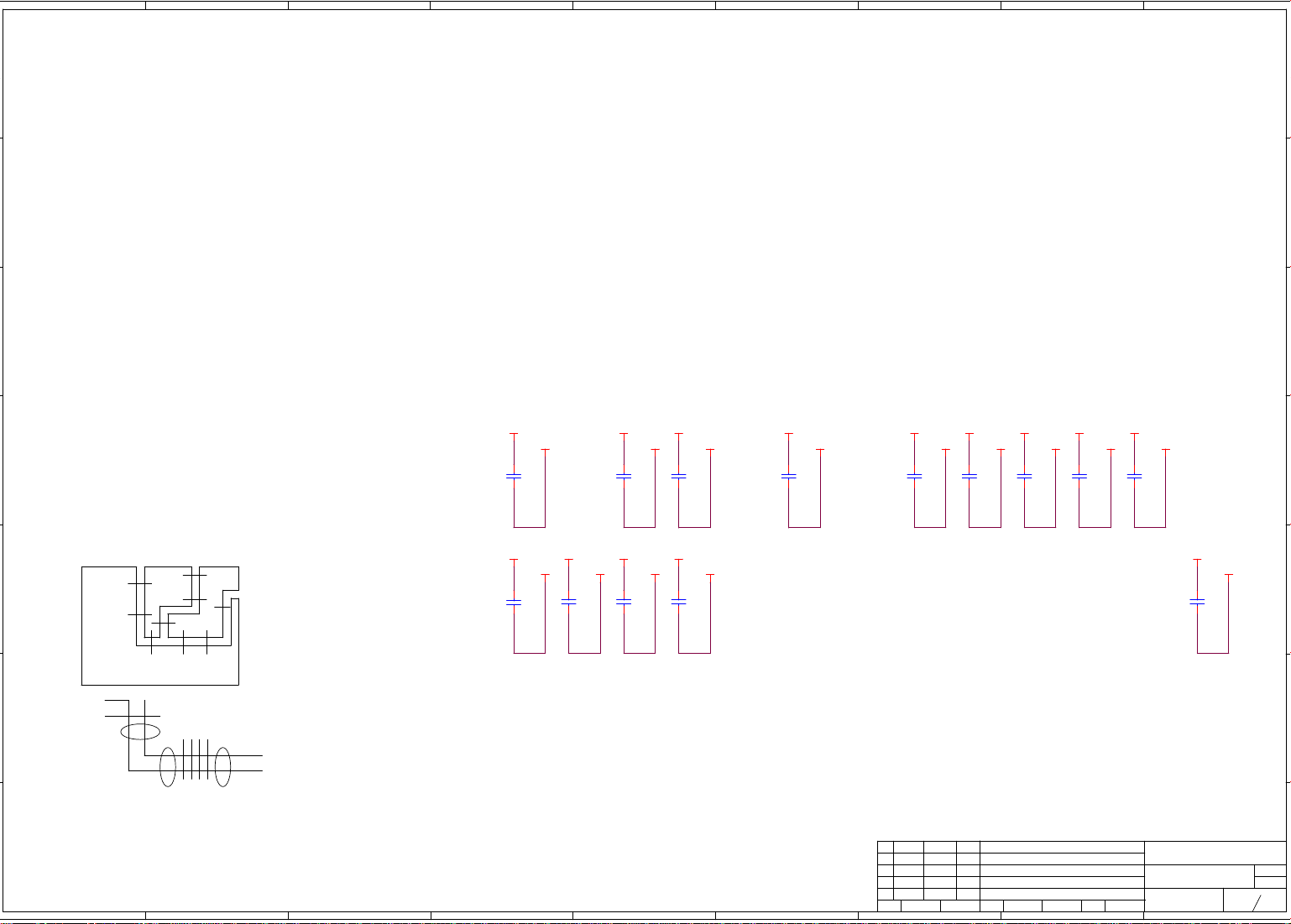

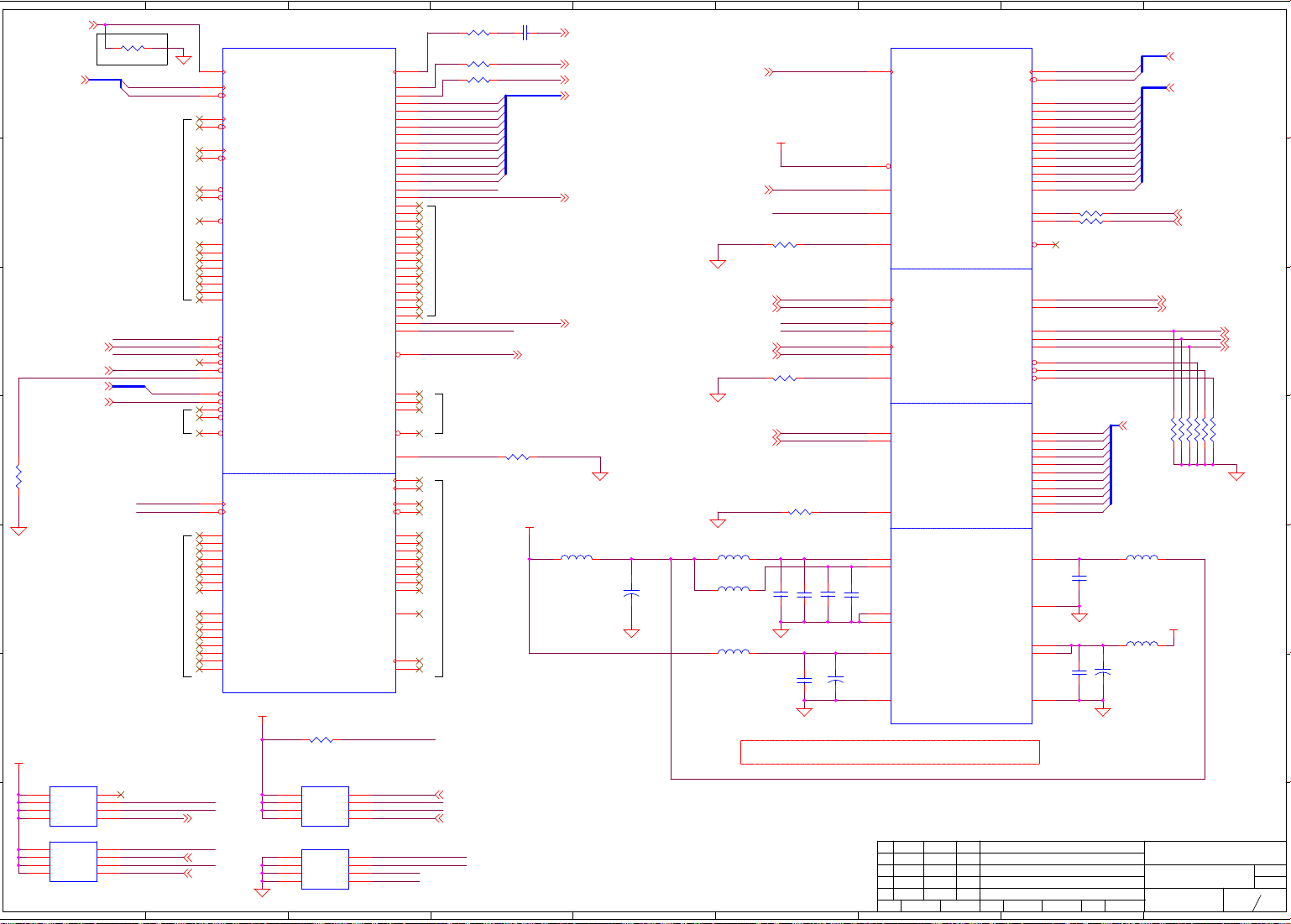

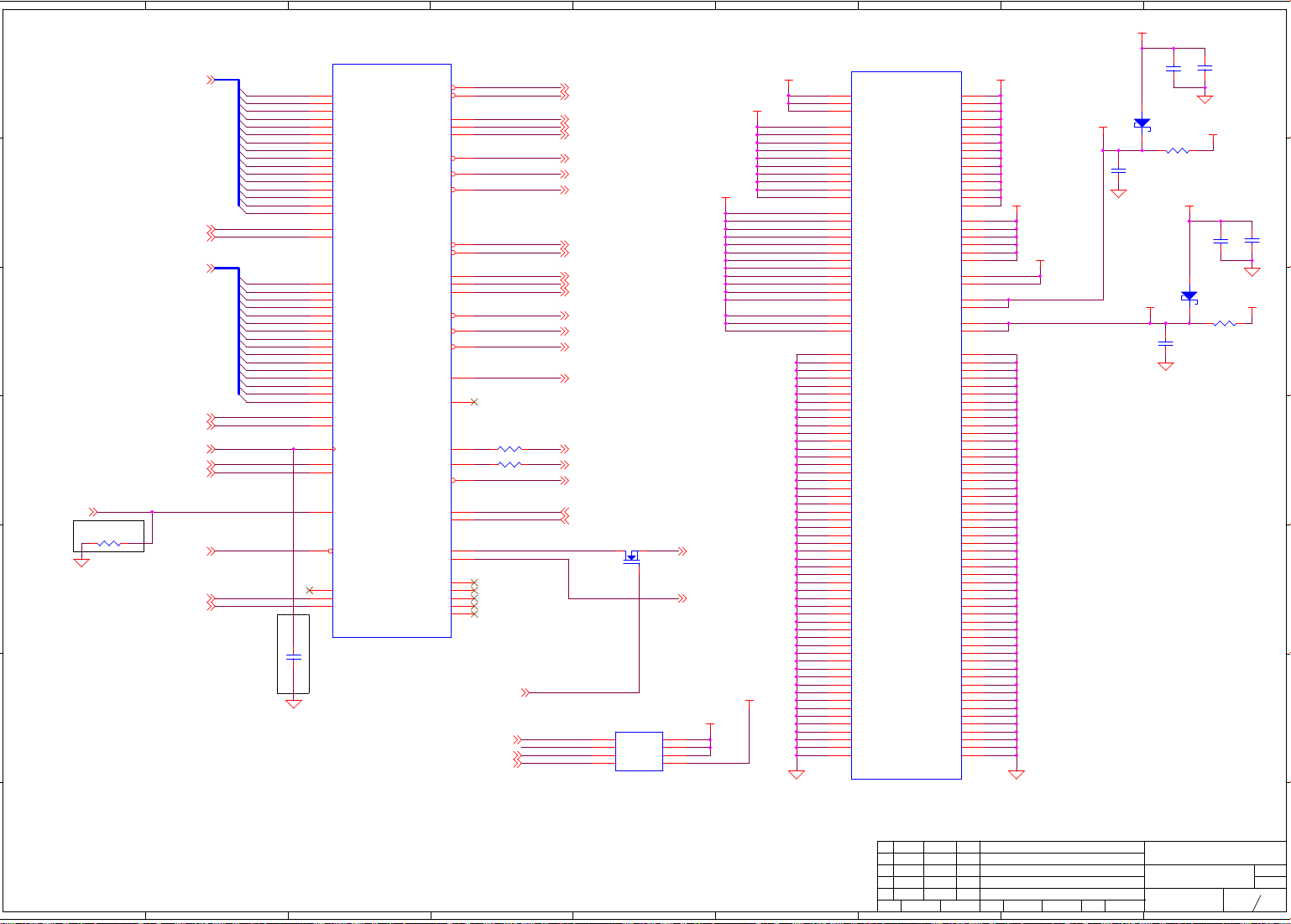

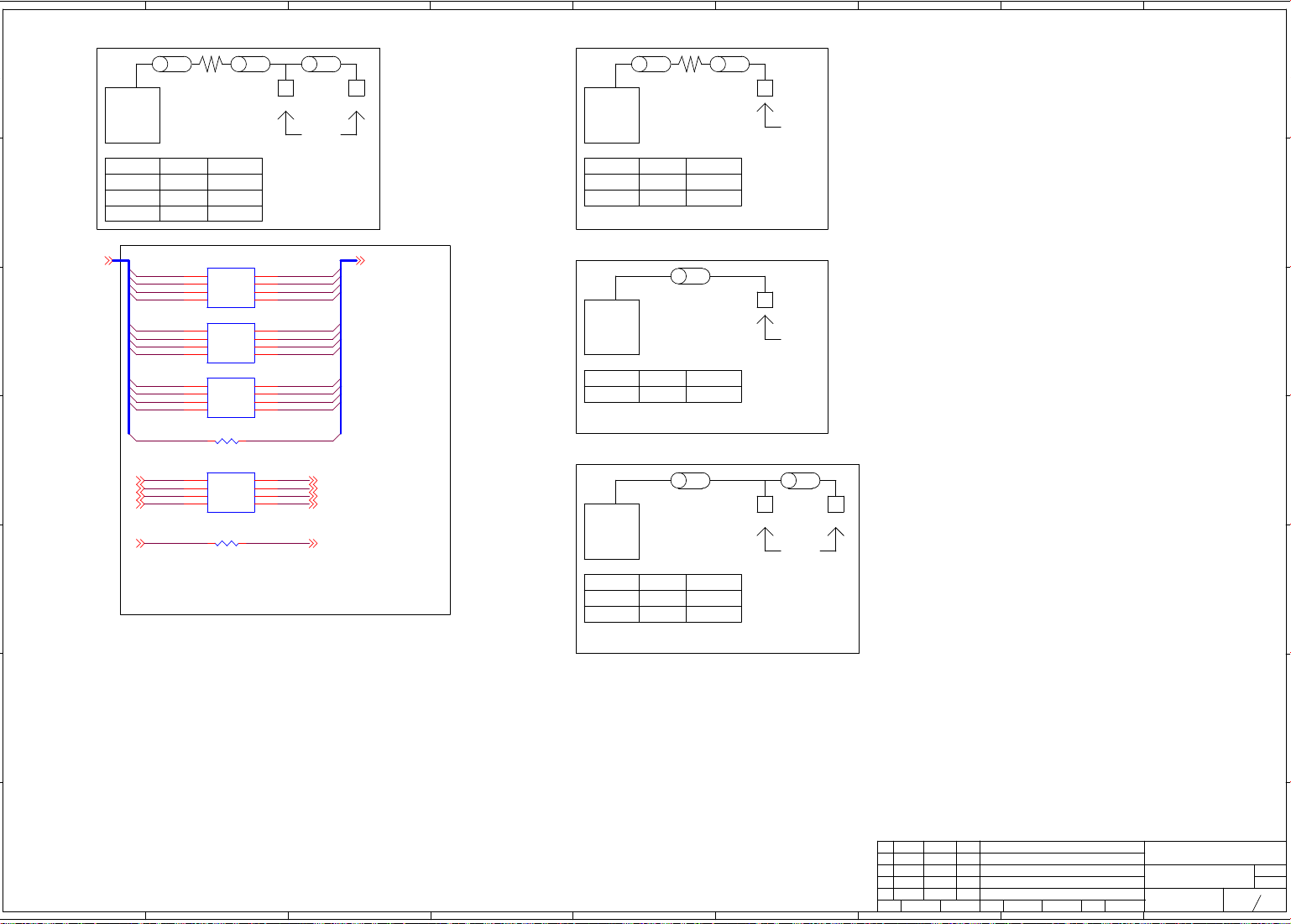

CLK

BUS

本コンデンサは電源/グランド層に発生するベタプレーン同士を接続するためのものである。

そのため、上記のようなベタ構成であれば、ポイントとなる個所にコンデンサ

を配置する。

‑クロックがベタをまたいで引く場合

‑Bus系がベタをまたいで引く場合(数本毎に1個間隔で)

個数については、適宜増やすこと。

1

2

3

PWR_1

PWR_5VMAIN

12

CC1

680pF 25V

PWR_5VMAIN PWR_5VMAIN PWR_3VSTD PWR_1.8VMAIN

CC10

2 1

680pF 25V

4

PWR_5VMAIN PWR_1 PWR_DCIN

12

CC2

680pF 25V

CC11

680pF 25V

12

CC12

680pF 25V

5

12

PWR_3VSUSPWR_3VMAINPWR_3VMAIN

12

CC3

680pF 25V

PWR_3VSUSPWR_3VMAINPWR_5VSUSPWR_3VMAIN

12

CC13

680pF 25V

12

CC4

680pF 25V

6

PWR_3VSUS PWR_3VSUS PWR_5VSUS PWR_5VSUS PWR_3VSUS

12

Rev.

DATE Design

2001.01.16 Komahara

CC5

680pF 25V

7

12

CC6

680pF 25V

Appr.

CheckDesign

Yoshida Aoki

12

Description

CC7

680pF 25V

PWR_5VMAIN

12

CC8

Appr.

8

680pF 25V

PWR_3VMAINPWR_3VMAINPWR_5VSUSPWR_3VMAIN

12

CC9

680pF 25V

TITLE

Laurel

DRAW. No.

C1CPxxxxxx-X1

FUJITSU

LTD.

PWR_1

21

PWR_5VSUS

CC21

680pF 25V

SHEET

9

EMI

CAST

3 82

Page 4

PWR_3VSUS

1

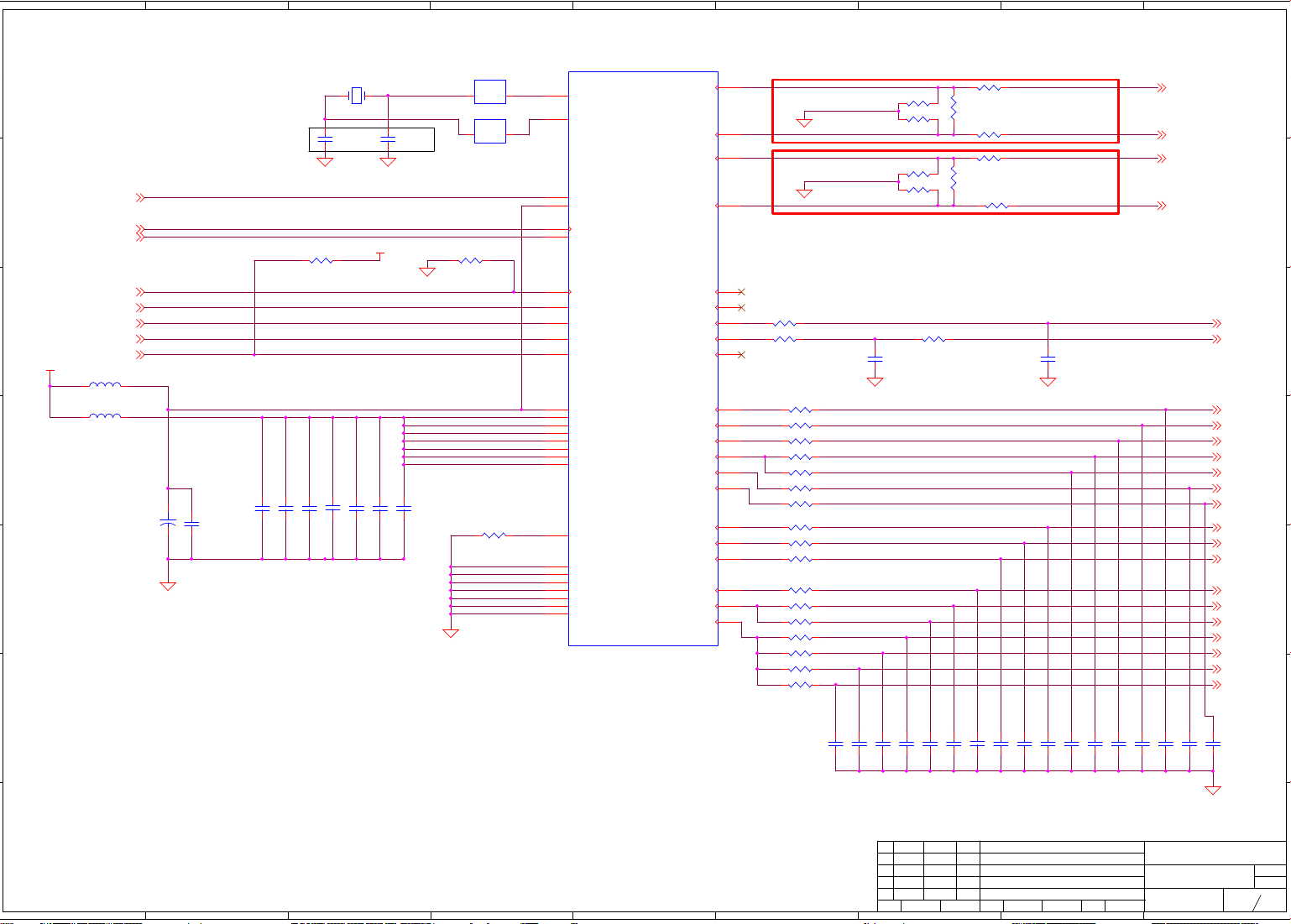

CPU_BSEL15,8

SMB_CLK_ICH17,23,25,50

SMB_DATA_ICH17,23,25,50

CLK_GBO6612

SUSB#

STP_CPU#16

STP_PCI#16

VTTPWRGD#76

FL3

2 1

BLM21P300S

FL4

1 2

BLM21P300S

12

+

C6

10uF 6.3V (TA)

GND1

1 2

C7 0.1uF 16V 20%

2

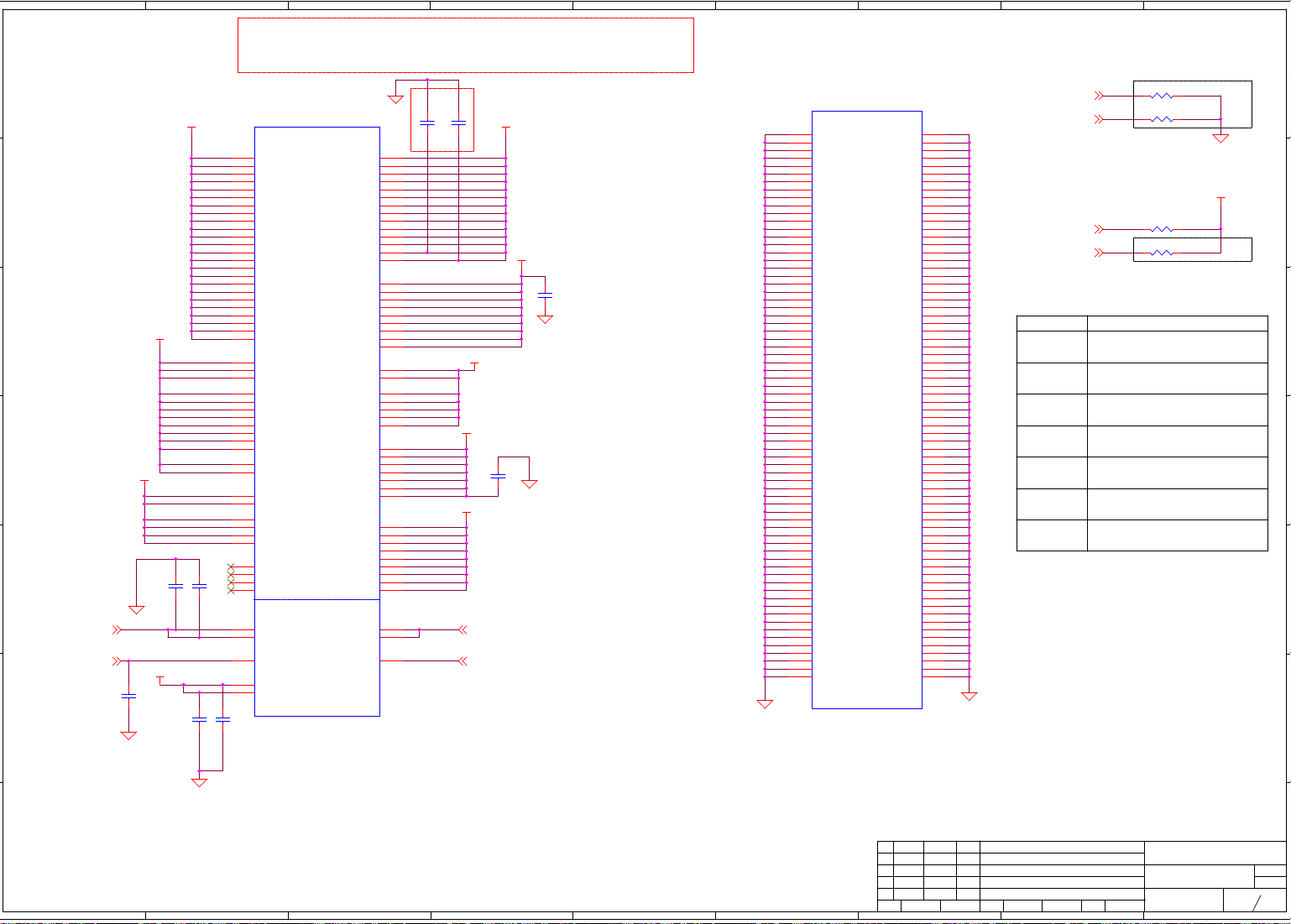

Placecyrstalwithin500milsofClkTITAN

(byALMADOR-MCHIPSET/MOBILETUALATIN

PROCESSOR

CUSTMERREFERENCEBOARDSCHEMATICS

rev.0.80)

2 1

10k 1/16W 5%

1 2

1 2

C8 0.1uF 16V 20%

C9 0.1uF 16V 20%

3

X1

12

14.31818MHz

C1

16pF 25V

2 1

Reserve

GND1 GND1

12

2 1

C11 1uF 10V 20%

C10 0.1uF 16V 20%

PWR_3VSUS

R11

1 2

C2

16pF 25V

1 2

Reserve

2 1

2 1

C12 0.1uF 16V 20%

C13 0.1uF 16V 20%

1 2

240k 1/16W 5%

GND1

PLL_VCCA_33

PLL_VCC_33

C14 0.1uF 16V 20%

GND1

R12

4

FL1

<FILTER>

BLM10B750B

FL2

<FILTER>

BLM10B750B

R22

330 1/16W 1%

5

M1

1

21

12

12

XTAL_IN

2

XTAL_OUT

46

S1

36

S2

26

SCLK

25

SDATA

20

66MHz_IN/3V66_5

21

PWR_DWN#

45

CPU_STOP#

30

PCI_STOP#

24

PWR_DG#

22

VDD_CORE

33

VDD48

48

VDD_REF

11

VDD_PCI

28

VDD_3V66_1

15

VDD_3V66_2

44

VDD_CPU1

40

VDD_CPU2

37

IREF

23

GND_CORE

7

GND_PCI

16

GND_3V66_1

27

GND_3V66_2

3

GND_REF

32

GND_48MHZ

41

GND_CPU

CY28322

本ページのコンデンサは、PLLの近傍に

配置すること。

Place these capacitors near PLL.

CPU1

CPU#1

CPU2

CPU#2

3V66_0

3V66_1/VCH

66BUFF0/3V66_2

66BUFF1/3V66_3

66BUFF2/3V66_4

PCI_F0

PCI_F1

PCI_F2

REF0

PCI0

PCI1

PCI2

PCI3

PCI4

PCI5

DOT

USB

6

※のパターンのライン・インピーダンスは、55Ωで引くこと。(5mil幅)

また、各対のクロックライン同士の間隔(CPUCLK0,CPUCLK0#間など3対)

は、信号線間インピーダンス100Ωで引くこと。(9mil幅)

Control the impedance of signals that "*" are marked are 55 ohm. (the width is 5mil)

Control the impedance between the pair of clock (CPUCLK0 & CPCLK0#, etc) 100 ohm.

(the width is 9mil)

※

43

※

42

39

※

38

※

R2 62 1/16W 1%

R4 62 1/16W 1%

GND1

R7 62 1/16W 1%

R9 62 1/16W 1%

GND1

7

R1 33 1/16W 1%

R3

470 1/16W 1%

R8

470 1/16W 1%

12

R5 33 1/16W 1%

12

R6 33 1/16W 1%

12

12

12

12

12

12

21

12

8

R10 33 1/16W 1%

#B 枠内部品は、M2(CPU)裏面 PAD直裏に配置のこと。

#C枠内部品は、M3(GMCH)裏面PAD直裏に配置のこと。

29

31

17

18

19

8

9

10

12

13

14

4

5

6

34

35

47

R13 BLM15AG700

12

R14 BLM15AG700

12

R15 BLM15AG700

12

R16 BLM15AG700

12

R17 BLM15AG700

12

R18 BLM15AG700

12

R19 BLM15AG700

12

R20 BLM15AG700

12

R449 BLM15AG700

12

R21 BLM15AG700

12

R23 47 1/16W 5%

12

R24 BLM15AG700

12

R25 BLM15AG700

21

R26 BLM15AG700

21

R27 BLM15AG700

21

R28 BLM15AG700

21

R29 BLM15AG700

21

R30 BLM15AG700

21

R31 BLM15AG700

21

R490 0 1/16W

12

C4

1 2

5pF 25V

GND1

C5

1 2

5pF 25V

GND1

#B

#C

9

CPUCLK1 5

CPUCLK1# 5

CPUCLK2 11

CPUCLK2# 11

CLK_ICH66 16

CLK_GBI66 12

CLK_FWH33 20

CLK_71133 29

CLK_SIO33 37

CLK_ASIC33 39

CLK_MINI33 50

CLK_1394 27

CLK_LAN33 42

CLK_ICH33 16

CLK_CPUAPIC33 5

CLK_ICHAPIC33 17

CLK_MCH_DREF48 12

CLK_ASIC48 39

CLK_ICH48 16

CLK_ICH14 16

CLK_SIO14 37

CLK_VCH14 24

CLK_TVO14 26

12

2 1

2 1

1 2

2 1

1 2

1 2

1 2

1 2

1 2

1 2

1 2

2 1

2 1

C1710pF 25V

C1810pF 25V

C1910pF 25V

C2010pF 25V

C2110pF 25V

Appr.

C2218pF 25V

CheckDesign

C1610pF 25V

C1510pF 25V

各クロックのダンピング抵抗はチップから

1cm以内に配置すること。

Place each dumping resistor of clock line near PLL as

possible.(less than 10mm)

Rev.

DATE Design

1

2

3

4

5

6

2001.01.16 Komahara

7

1 2

C2310pF 25V

C2510pF 25V

C2610pF 25V

C2410pF 25V

Description

Yoshida Aoki

C2710pF 25V

Appr.

8

C2810pF 25V

1 2

C2910pF 25V

C3010pF 25V

TITLE

Lauurel

DRAW. No.

C1CPxxxxxx-X1

FUJITSU

LTD.

1 2

C65910pF 25V

GND1

9

SHEET

PLL

CAST

4 82

Page 5

1

2

3

4

5

6

7

8

9

M2A

CPU_D#[0:63]11

CPU_D#0

CPU_D#1

CPU_D#2

CPU_D#3

CPU_D#4

CPU_D#5

CPU_D#6

CPU_D#7

CPU_D#8

CPU_D#9

CPU_D#10

CPU_D#11

CPU_D#12

CPU_D#13

CPU_D#14

CPU_D#15

CPU_D#16

CPU_D#17

CPU_D#18

CPU_D#19

CPU_D#20

CPU_D#21

CPU_D#22

CPU_D#23

CPU_D#24

CPU_D#25

CPU_D#26

CPU_D#27

CPU_D#28

CPU_D#29

CPU_D#30

CPU_D#31

CPU_D#32

CPU_D#33

CPU_D#34

CPU_D#35

CPU_D#36

CPU_D#37

CPU_D#38

CPU_D#39

CPU_D#40

CPU_D#41

CPU_D#42

CPU_D#43

CPU_D#44

CPU_D#45

CPU_D#46

CPU_D#47

CPU_D#48

CPU_D#49

CPU_D#50

CPU_D#51

CPU_D#52

CPU_D#53

CPU_D#54

CPU_D#55

CPU_D#56

CPU_D#57

CPU_D#58

CPU_D#59

CPU_D#60

CPU_D#61

CPU_D#62

CPU_D#63

M24

U26

R24

R26

M25

M26

AA26

U24

W26

AB25

W24

AB24

AA24

A16

B17

A17

D23

B19

C20

C16

A20

A22

A19

A23

A24

C18

D24

B24

A18

E23

B21

B23

E26

C24

F24

D25

E24

B25

G24

H24

F26

L24

H25

C26

K24

G26

K25

J24

K26

F25

N26

J26

P25

L26

V25

T24

P24

T26

Y25

V26

T25

Y24

Y26

V24

D#0

D#1

D#2

D#3

D#4

D#5

D#6

D#7

D#8

D#9

D#10

D#11

D#12

D#13

D#14

D#15

D#16

D#17

D#18

D#19

D#20

D#21

D#22

D#23

D#24

D#25

D#26

D#27

D#28

D#29

D#30

D#31

D#32

D#33

D#34

D#35

D#36

D#37

D#38

D#39

D#40

D#41

D#42

D#43

D#44

D#45

D#46

D#47

D#48

D#49

D#50

D#51

D#52

D#53

D#54

D#55

D#56

D#57

D#58

D#59

D#60

D#61

D#62

D#63

CopperMine-T

A#10

A#11

A#12

A#13

A#14

A#15

A#16

A#17

A#18

A#19

A#20

A#21

A#22

A#23

A#24

A#25

A#26

A#27

A#28

A#29

A#30

A#31

A#32

A#33

A#34

A#35

DEP#0

DEP#1

DEP#2

DEP#3

DEP#4

DEP#5

DEP#6

DEP#7

FERR#

BREQ0#

HITM#

HIT#

AP#0

AP#1

LOCK#

PRDY#

PICD0

PICD1

ADS#

K1

J1

G2

K3

J2

H3

G1

A3

J3

H1

D3

F3

G3

C2

B5

B11

C6

B9

B7

C8

A8

A10

B3

A13

A9

C3

C12

C10

A6

A15

A14

B13

A12

AE24

AD25

AE25

AC24

AF24

AD26

AC26

AD24

AF6

A7

U2

AA2

AB3

P3

V3

AE22

AD19

AD17

AA3

CPU_A#3

CPU_A#4

CPU_A#5

CPU_A#6

CPU_A#7

CPU_A#8

CPU_A#9

CPU_A#10

CPU_A#11

CPU_A#12

CPU_A#13

CPU_A#14

CPU_A#15

CPU_A#16

CPU_A#17

CPU_A#18

CPU_A#19

CPU_A#20

CPU_A#21

CPU_A#22

CPU_A#23

CPU_A#24

CPU_A#25

CPU_A#26

CPU_A#27

CPU_A#28

CPU_A#29

CPU_A#30

CPU_A#31

CPU_BREQ0#

12

R33

10 1/16W 5%

GND1

CPU_HLOCK# 11

ITP_PRDY# 8

CPU_APICD0 8,17

CPU_APICD1 8,17

CPU_ADS# 11

A#3

A#4

A#5

A#6

A#7

A#8

A#9

CPU_A#[3:31] 11

CLK_CPUAPIC334

R32はM2.AF20の近くに置くこと

CPU_FERR# 8,16

CPU_HITM# 11

CPU_HIT# 11

GND1

R32

68 1/16W 5%

CPUCLK1,CPUCLK1#

のビアのうち、

本CPUに一番近いビアに対し、

シルクで表示すること。

CPUCLK14

CPUCLK1#4

CPU_A20M#16

CPU_INTR8,16

CPU_NMI8,16

CPU_IGNNE#16

CPU_FLUSH#8

CPU_RST#8,11

CPU_INIT#8,16,20

CPU_SMI#8,16

CPU_RS#[0:2]11

TP1RS#P

CPU_STPCLK#16

CPU_DEFER#11

CPU_BPRI#11

ITP_PREQ#8

21

PWR_CPUBUS

GND1

CPU_PWRGD8,16

CPU_DPSLP#8,16,60

GLO/HI#16

CPU_THMDA15 CPU_THMDC 15

ITP_TRST#8

CPU_TRDY#11

ITP_TCK8

ITP_TMS8

ITP_TDI8

CPU_BSEL08

CPU_BSEL14,8

R36 1k 1/16W 5%

12

R37 1k 1/16W 5%

12

R39 1k 1/16W 5%

21

R40 1k 1/16W 5%

2 1

M2B

AC1

BCLK

AD1

BCLK#

AC3

A20M#

AD15

INTR/LINT0

AE14

NMI/LINT1

AD9

IGNNE#

AF5

FLUSH#

B15

RESET#

AE6

INIT#

AD3

SMI#

Y3

CPU_RS#0

CPU_RS#1

CPU_RS#2

☆ ☆

AE4

AF20

AF19

AB4

AF8

AF13

AF15

AD10

AF7

AD7

AE12

AF10

AF11

V1

U3

M5

T3

R2

L5

W1

E2

M1

Y4

RS#0

RS#1

RS#2

RS#P

STPCLK#

DEFER#

PICCLK

BPRI#

PREQ#

PWRGOOD

DPSLP#

GHI#

THERMDA

TRST#

TRDY#

TCK

TMS

TDI

BSEL0

BSEL1

TESTHI

TESTHI

TESTLO

TESTLO

THERMDC

RTTIMPEDP

EDGECTRLP

VTTPWRGD

IERR#

AERR#

BERR#

BINIT#

BNR#

BPM#0

BPM#1

BP#2

BP#3

DBSY#

DRDY#

REQ#0

REQ#1

REQ#2

REQ#3

REQ#4

RP#

TDO

NCTRL

VID0

VID1

VID2

VID3

VID4

AF4

W2

C14

AF23

L2

AD22

AD21

AF22

AE20

W3

Y1

R1

L3

T1

U1

L1

T4

AF14

AD11

AE16

AF16

AD16

E3

AB1

AC2

AE2

AF3

R3

CPU_REQ#0

CPU_REQ#1

CPU_REQ#2

CPU_REQ#3

CPU_REQ#4

CPU_RTTIMPEDP

CPU_EDGECTRLP

CPU_IERR# 8

CPU_BNR# 11

CPU_DBSY# 11

CPU_DRDY# 11

CPU_REQ#[0:4] 11

ITP_TDO 8

R34

12

56 1/16W 1%

R38

1 2

110 1/16W 1%

VTTPWRGD 8,76

GND1

PWR_CPUBUS

21

R35 14 1/16W 1%

CopperMine-T

BSEL0

PSB Freq.

100MHz

BSEL1

0

1133MHz

1

1

☆印のついた信号線はGND1で両側をガードすること。

M2

Cuppermine GMCH

M2からM3への信号線は上記の条件を厳守すること。

1

2

3

4

Total Trace Length:50.8-101.6mm

Trace Width:5mils

Spacing to Other Traces:10mils

5

M6

Rev.

DATE Design

6

2001.01.16 Komahara

Appr.

7

Description

CheckDesign

Yoshida Aoki

Appr.

8

TITLE

DRAW. No.

FUJITSU

LTD.

CPU-1

Laurel

C1CPxxxxxx-X1

SHEET

9

CAST

5 82

Page 6

1

2

3

4

5

6

7

8

9

PWR_CPUBUS

R44

2K 1/16W 0.5%

1 2

12

GND1

PWR_CPUBUS

R41

1K 1/16W 0.5%

2 1

2 1

C691 1uF 6.3V

M2C

L1

12

4.7uH

C694

VGTLREF

2 1

C35 0.1uF 10V R12C36 0.1uF 10V R12C37 0.1uF 10V R12C38 0.1uF 10V R

C692 1uF 6.3V

C693 1uF 6.3V

◎のついた信号線は25mil以上の太さで配線し、

周りをベタのGNDで配線すること。

10uF 6.3V (TA)

12

+

C695

10uF 6.3V (TA)

N3

PLL1

12

+

N2

PLL2

A4

VREF

A21

VREF

N1

VREF

AF9

VREF

AF21

VREF

AA1

VREF

AB26

VREF

H26

VREF

12

CopperMine-T

CMOSREF

CMOSREF

AD5

AF12

このページの抵抗・キャパシタ・インダクタはCPUの近傍に置くこと

12

C32

0.1uF 10V R

C34 0.1uF 10V R

PWR_1.5VMAIN

1 2

12

12

GND1

R42

560 1/16W 0.5%

R43

1.1K 1/16W 0.5%

PWR_CPUCORE

W21

AA11

AA13

AA15

AA17

AA19

AA21

AB10

AB12

AB14

AB16

AB18

AB20

AB22

AC5

AC7

AC9

AC11

AC13

AC15

AC17

AC19

AC21

D10

D12

D14

D16

D18

D20

D22

E11

E13

E15

E17

E19

E21

F10

F12

F14

F16

F18

F20

F22

G21

H22

K22

M22

N21

P22

R21

T22

U21

V22

Y22

AA5

AA7

AA9

AB6

AB8

PWR_CPUBUS

M2D

D6

VCC

D8

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

E5

VCC

E7

VCC

E9

VCC

VCC

VCC

VCC

VCC

VCC

VCC

F6

VCC

F8

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

G5

VCC

VCC

H6

VCC

VCC

J5

VCC

J21

VCC

K6

VCC

VCC

L21

VCC

M6

VCC

VCC

N5

VCC

VCC

P6

VCC

VCC

R5

VCC

VCC

T6

VCC

VCC

U5

VCC

VCC

V6

VCC

VCC

W5

VCC

VCC

Y6

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

A26

C5

C7

C9

C11

C13

C15

C17

C19

C21

D5

E4

E6

G4

G23

J4

J23

L4

L23

N23

R23

U23

V4

W23

AA4

AA23

AC4

AC23

AD6

AD8

AD12

AD14

AD18

AD20

AE3

AE18

AF1

AF2

A2

NC

A5

NC

A11

NC

B1

NC

C1

NC

C4

NC

C22

NC

D1

NC

D26

NC

E1

NC

F1

NC

N4

NC

N24

NC

P1

NC

P4

NC

P5

NC

P26

NC

AD4

NC

AD13

NC

AD23

NC

AE8

NC

AE10

NC

AF17

NC

AF18

NC

M21

M23

N22

N25

A25

B10

B12

B14

B16

B18

B20

B22

B26

C23

C25

D11

D13

D15

D17

D19

D21

E10

E12

E14

E16

E18

E20

E22

E25

F11

F13

F15

F17

F19

F21

F23

G22

G25

H21

H23

J22

J25

K21

K23

L22

L25

B2

B4

B6

B8

D2

D4

D7

D9

E8

F2

F4

F5

F7

F9

G6

H2

H4

H5

J6

K2

K4

K5

L6

M2

M3

M4

N6

M2E

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

CopperMine-T

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

P2

P21

P23

R4

R6

R22

R25

T2

T5

T21

T23

U4

U6

U22

U25

V2

V5

V21

V23

W4

W6

W22

W25

Y2

Y5

Y21

Y23

AA6

AA8

AA10

AA12

AA14

AA16

AA18

AA20

AA22

AA25

AB2

AB5

AB7

AB9

AB11

AB13

AB15

AB17

AB19

AB21

AB23

AC6

AC8

AC10

AC12

AC14

AC16

AC18

AC20

AC22

AC25

AD2

AE1

AE5

AE7

AE9

AE11

AE13

AE15

AE17

AE19

AE21

AE23

AE26

AF25

AF26

GND1GND1

CopperMine-T

TITLE

DRAW. No.

Rev.

DATE Design

1

2

3

4

5

6

2001.01.16 Komahara

Appr.

7

Description

CheckDesign

Yoshida Aoki

Appr.

8

FUJITSU

LTD.

CPU-2

Laurel

C1CPxxxxxx-X1

SHEET

9

CAST

6 82

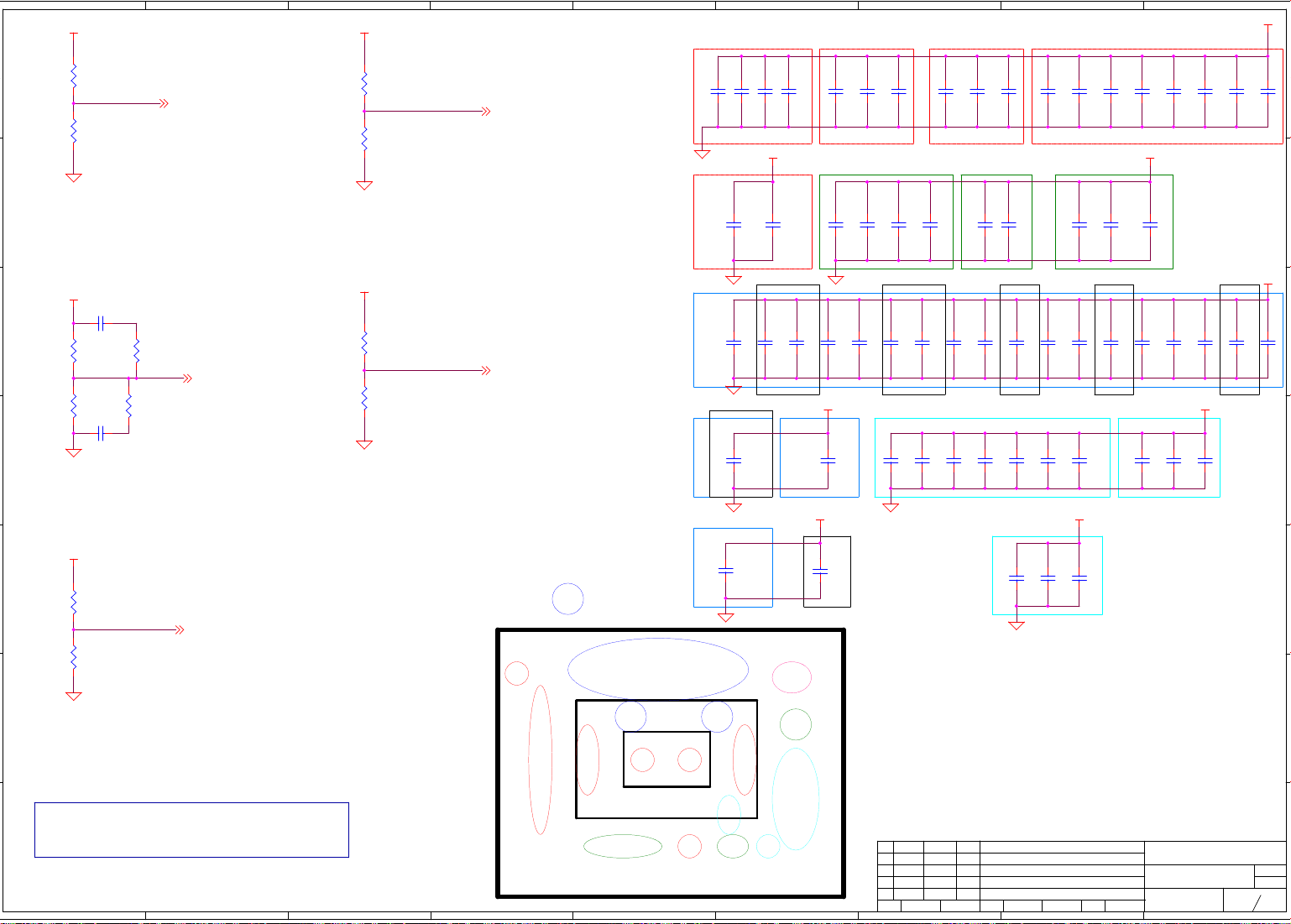

Page 7

1

2

MOBILE

Coppermine-T

Tualatin

3

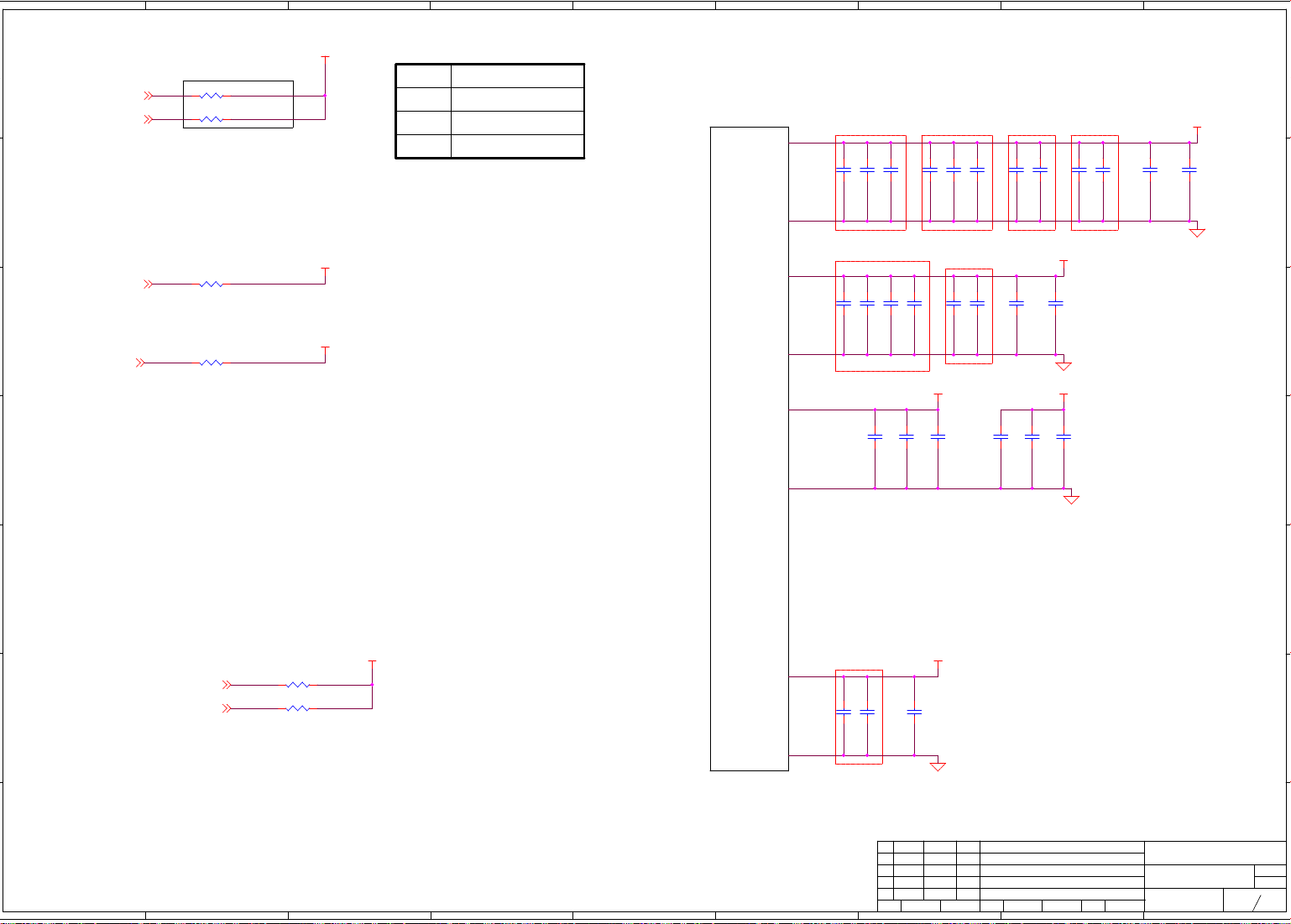

At least x24 0.47uF & x10 10uF CPUCOREVCC(PWR_CPUCORE)

decoupling capacitors.

At least x10 1.0uF CPUBUSVCC(PWR_CPUBUS) de capaciters.

(by Tualatin / Coppermine-T SpecSheet)

21

C39 0.22uF 10V

C40 0.22uF 10V12C41 0.22uF 10V12C42 0.22uF 10V21C43 0.22uF 10V12C44 0.22uF 10V12C45 0.22uF 10V21C46 0.22uF 10V21C47 0.22uF 10V12C48 0.22uF 10V12C49 0.22uF 10V12C50 0.22uF 10V21C51 0.22uF 10V12C52 0.22uF 10V12C53 0.22uF 10V12C54 0.22uF 10V21C55 0.22uF 10V21C56 0.22uF 10V21C57 0.22uF 10V21C58 0.22uF 10V12C59 0.22uF 10V12C60 0.22uF 10V21C61 0.22uF 10V12C62 0.22uF 10V

1 2

2 1

2 1

C63 10uF 6.3V B

C64 10uF 6.3V B

C65 10uF 6.3V B

1 2

1 2

C66 10uF 6.3V B

4

1 2

C67 10uF 6.3V B

1 2

C68 10uF 6.3V B

1 2

C69 10uF 6.3V B

5

PWR_CPUCORE

C70 10uF 6.3V B

GND1

PWR_CPUBUS

6

7

8

PWR_CPUCORE

12

GND1

9

1 2

1 2

2 1

1 2

2 1

1 2

1 2

1 2

C75 1uF 6.3V

C76 1uF 6.3V

C77 1uF 6.3V

C78 1uF 6.3V

C79 1uF 6.3V

C80 1uF 6.3V

C81 1uF 6.3V

C82 1uF 6.3V

上記のコンデンサはM2(CPU)の各電源ピンの近傍に均等に配置すること

複数の種類のコンデンサは、容量の小さいものを優先的に、

M2の電源PINの直近に配置すること

上記コンデンサ

0.47uF10VR(C36‑C59),10uF6.3VB(C60‑C71)はCPU裏の中央に配置し、

1.0uF10V(C72‑C84)はCPUBUS電源(VCCT)のPIN近くに均等に配置すること。

2 1

2 1

C86 10uF 6.3V B

C87 10uF 6.3V B

GND1

1.0uF10V

10uF6.3V B

0.47uF10VR

PassC for CPU

TITLE

Laurel

DRAW. No.

Rev.

DATE Design

1

2

3

4

5

6

2001.01.16 Komahara

Appr.

7

Description

CheckDesign

Yoshida Aoki

Appr.

8

C1CPxxxxxx-X1

FUJITSU

LTD.

9

SHEET

CAST

7 82

Page 8

1

ITP_TCK5

ITP_TDI5

ITP_TMS5

ITP_TRST#5

VTTPWRGD5,76

CPU_APICD05,17

CPU_APICD15,17

ITP_TDO5

ITP_PREQ#5

CPU_FLUSH#5

CPU_FERR#5,16

CPU_IERR#5

CPU_INTR5,16

CPU_NMI5,16

CPU_DPSLP#5,16,60

CPU_SMI#5,16

CPU_INIT#5,16,20

CPU_RST#5,11

ITP_PRDY#5

2

R45 10 1/16W 5%

1 2

R46 10 1/16W 5%

1 2

R47 10 1/16W 5%

1 2

R48 10 1/16W 5%

1 2

GND1

3

R49 1.5k 1/16W 5%

1 2

R50 150 1/16W 5%

R51 150 1/16W 5%

R52 150 1/16W 5%

1 2

R53 10 1/16W 5%

1 2

R54 3k 1/16W 5%

1 2

R55 1.5k 1/16W 5%

1 2

R56 1.5k 1/16W 5%

1 2

R58 10k 1/16W 5% Reserve

1 2

R59 56 1/16W 5%

2 1

R61 56 1/16W 5%

PWR_CPUBUS

21

21

21

4

PWR_1.5VMAIN

ITP_PREQ# Pull-up signal change to 10ohm from 200ohm for ESD protection

PWR_CPUBUS

5

CPU_PWRGD5,16

CPU_BSEL05

CPU_BSEL14,5

6

2 1

GND1

R57 1.5k 1/16W 5%

C696

100pF 25V

R60 10k 1/16W 5%

R62 10k 1/16W 5%

1 2

1 2

1 2

7

PWR_1.8VMAIN

PWR_3VMAIN

8

9

21

12

C89

C88

2 1

100pF 25V

100pF 25V

CPURST#は上記抵抗までの分岐配線を0.1inch以下にすること。

C90

100pF 25V

21

C92

C91

2 1

100pF 25V

100pF 25V

GND1

本ページの抵抗・コンデンサはCPUの近くに配置すること

1

2

3

Pullup for CPU

Rev.

DATE Design

4

5

6

2001.01.16 Komahara

Appr.

7

Description

CheckDesign

Yoshida Aoki

Appr.

8

TITLE

Laurel

DRAW. No.

C1CPxxxxxx-X1

FUJITSU

LTD.

9

SHEET

CAST

8 82

Page 9

1

2

3

4

5

GMCHA24,GMCHC24間の信号<CLKSYSMEM>は0.15inch(+/‑50mil)で配線すること。

またコンデンサはその信号線の中間に配置すること。

6

7

8

PAD(A24)

9

M3A

Almador-M

HOST I/F

3

CPURST#

BPRI#

DEFER#

HD#0

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

R6

L4

J4

U4

CPU_D#0

P1

CPU_D#1

W6

CPU_D#2

U2

CPU_D#3

U6

CPU_D#4

R1

CPU_D#5

N3

CPU_D#6

W5

CPU_D#7

V4

CPU_D#8

P3

CPU_D#9

CPU_D#10

R3

U1

CPU_D#11

V6

CPU_D#12

W4

CPU_D#13

T3

CPU_D#14

P2

CPU_D#15

V3

CPU_D#16

R2

CPU_D#17

T1

CPU_D#18

W3

CPU_D#19

U3

CPU_D#20

Y4

CPU_D#21

AA3

CPU_D#22

W1

CPU_D#23

V1

CPU_D#24

Y1

CPU_D#25

Y6

CPU_D#26

AD3

CPU_D#27

AB4

CPU_D#28

AB5

CPU_D#29

V2

CPU_D#30

Y3

CPU_D#31

Y2

CPU_D#32

AA4

CPU_D#33

AA1

CPU_D#34

AA6

CPU_D#35

AB1

CPU_D#36

AC4

CPU_D#37

AA2

CPU_D#38

AB3

CPU_D#39

AD2

CPU_D#40

AD1

CPU_D#41

AC2

CPU_D#42

AB6

CPU_D#43

AC6

CPU_D#44

AC1

CPU_D#45

AF3

CPU_D#46

AD4

CPU_D#47

AD6

CPU_D#48

AC3

CPU_D#49

AH3

CPU_D#50

AE5

CPU_D#51

AE3

CPU_D#52

AG2

CPU_D#53

AF4

CPU_D#54

AF2

CPU_D#55

AJ3

CPU_D#56

AE4

CPU_D#57

AG1

CPU_D#58

AE1

CPU_D#59

AG4

CPU_D#60

AH4

CPU_D#61

AG3

CPU_D#62

AF1

CPU_D#63

R82,R83,R84の抵抗はGMCH(M6)から0.5inch以内に置き、

※のついた信号線は10mil幅以上で配線すること。

Place R82,R83,R84 near GMCH (within 0.5 inch) and

the width of patterns must be more than 10 mil.

4

C699 22pF 25V Reserve

1 2

C700 22pF 25V Reserve

1 2

C701 22pF 25V Reserve

1 2

C702 22pF 25V Reserve

1 2

GND1

CPU_RST# 5,8

CPU_BPRI# 5

CPU_DEFER# 5

CPUCLK24

CPUCLK2#4

PCI_RST#

CPU_A#[3:31]5 CPU_D#[0:63] 5

CPU_ADS#5

CPU_DBSY#5

CPU_DRDY#5

CPU_HIT#5

CPU_HITM#5

CPU_HLOCK#5

CPU_TRDY#5

CPU_BNR#5

CPU_REQ#[0:4]5

CPU_RS#[0:2]5

GTL_RCOMP must be pulled down

to GND with 80.6 ohm resistor.

12

R67

160 1/16W 1%

12

CPU_A#3

CPU_A#4

CPU_A#5

CPU_A#6

CPU_A#7

CPU_A#8

CPU_A#9

CPU_A#10

CPU_A#11

CPU_A#12

CPU_A#13

CPU_A#14

CPU_A#15

CPU_A#16

CPU_A#17

CPU_A#18

CPU_A#19

CPU_A#20

CPU_A#21

CPU_A#22

CPU_A#23

CPU_A#24

CPU_A#25

CPU_A#26

CPU_A#27

CPU_A#28

CPU_A#29

CPU_A#30

CPU_A#31

CPU_REQ#0

CPU_REQ#1

CPU_REQ#2

CPU_REQ#3

CPU_REQ#4

CPU_RS#0

CPU_RS#1

CPU_RS#2

R68

160 1/16W 1%

AJ4

HTCLK

AH5

HTCLK#

AB24

RESET#

H2

HA#3

E3

HA#4

G3

HA#5

N4

HA#6

M6

HA#7

F1

HA#8

F2

HA#9

J3

HA#10

F3

HA#11

P6

HA#12

G1

HA#13

N5

HA#14

H1

HA#15

P4

HA#16

T4

HA#17

M2

HA#18

J2

HA#19

L2

HA#20

R4

HA#21

K1

HA#22

L3

HA#23

L1

HA#24

J1

HA#25

N1

HA#26

T5

HA#27

H3

HA#28

M3

HA#29

M1

HA#30

K3

HA#31

C1

ADS#

G5

DBSY#

F4

DRDY#

D3

HIT#

D1

HITM#

J6

HLOCK#

G4

HTRDY#

E1

BNR#

K6

HREQ#0

M4

HREQ#1

K5

HREQ#2

K4

HREQ#3

L6

HREQ#4

H6

RS#0

H4

RS#1

G6

RS#2

C2

※

GTL_RCOMP

※

GND1

1

2

MEM_D[0:63]23

5

CLK_DIMM0 23

CLK_DIMM1 23

CLK_DIMM2 23

CLK_DIMM3 23

21

C93

GND1

CLK_SYSMEM

M3B

22pF 25V

Reserve

Memory I/F

C24

SM_RCLK

SM_OCLK

A24

下記の抵抗はGMCHの各PINから0.25inch以内に配置すること。

Place these resistors near GMCH. (within 0.25inch)

MEM_D0

MEM_D1

MEM_D2

MEM_D3

MEM_D4

MEM_D5

MEM_D6

MEM_D7

MEM_D8

MEM_D9

MEM_D10

MEM_D11

MEM_D12

MEM_D13

MEM_D14

MEM_D15

MEM_D16

MEM_D17

MEM_D18

MEM_D19

MEM_D20

MEM_D21

MEM_D23

MEM_D24

MEM_D25

MEM_D26

MEM_D27

MEM_D28

MEM_D29

MEM_D30

MEM_D31

MEM_D32

MEM_D33

MEM_D34

MEM_D35

MEM_D36

MEM_D37

MEM_D38

MEM_D39

MEM_D40

MEM_D42

MEM_D43

MEM_D44

MEM_D45

MEM_D46

MEM_D47

MEM_D48

MEM_D49

MEM_D50

MEM_D51

MEM_D52

MEM_D53

MEM_D54

MEM_D55

MEM_D56

MEM_D57

MEM_D58

MEM_D59

MEM_D60

MEM_D61

MEM_D62

MEM_D63

D29

SM_MD0

C29

SM_MD1

D27

SM_MD2

C27

SM_MD3

A27

SM_MD4

B26

SM_MD5

E24

SM_MD6

C25

SM_MD7

E23

SM_MD8

B25

SM_MD9

C23

SM_MD10

F22

SM_MD11

B23

SM_MD12

C22

SM_MD13

E21

SM_MD14

B22

SM_MD15

C12

SM_MD16

D10

SM_MD17

C11

SM_MD18

A10

SM_MD19

C10

SM_MD20

C8

SM_MD21

A7

SM_MD22

E9

SM_MD23

C7

SM_MD24

E8

SM_MD25

A5

SM_MD26

F8

SM_MD27

C5

SM_MD28

D6

SM_MD29

B4

SM_MD30

C4

SM_MD31

E27

SM_MD32

C28

SM_MD33

B28

SM_MD34

E26

SM_MD35

C26

SM_MD36

D25

SM_MD37

A26

SM_MD38

D24

SM_MD39

F23

SM_MD40

A25

SM_MD41

G22

SM_MD42

D22

SM_MD43

A23

SM_MD44

F21

SM_MD45

D21

SM_MD46

A22

SM_MD47

F11

SM_MD48

A11

SM_MD49

B11

SM_MD50

F10

SM_MD51

B10

SM_MD52

B8

SM_MD53

D9

SM_MD54

B7

SM_MD55

F9

SM_MD56

A6

SM_MD57

C6

SM_MD58

D7

SM_MD59

B5

SM_MD60

E6

SM_MD61

A4

SM_MD62

D4

SM_MD63

Almador-M

SM_CLK0

SM_CLK1

SM_CLK2

SM_CLK3

SM_CS#0

SM_CS#1

SM_CS#2

SM_CS#3

SM_DQM0

SM_DQM1

SM_DQM2

SM_DQM3

SM_DQM4

SM_DQM5

SM_DQM6

SM_DQM7

SM_CKE0

SM_CKE1

SM_CKE2

SM_CKE3

SM_RAS#

SM_CAS#

SM_MA0

SM_MA1

SM_MA2

SM_MA3

SM_MA4

SM_MA5

SM_MA6

SM_MA7

SM_MA8

SM_MA9

SM_MA10

SM_MA11

SM_MA12

SM_BA0

SM_BA1

SM_WE#

SM_RCOMP

1 2

A15

2 1

B2

B14

1 2

A3

1 2

E17

MEM_CS#0

F16

MEM_CS#1

D16

MEM_CS#2

D15

MEM_CS#3

F18

MEM_DQM0

D18

MEM_DQM1

D13

MEM_DQM2

D12

MEM_DQM3

E18

MEM_DQM4

F17

MEM_DQM5

F14

MEM_DQM6

F13

MEM_DQM7MEM_D22

A13

MEM_CKE0

C9

MEM_CKE1

C13

MEM_CKE2

A9

MEM_CKE3

C20

MEM_RAS#

D19

MEM_CAS#

A20

MEM_AA0

B20

MEM_AA1

B19

MEM_AA2MEM_D41

C19

MEM_AA3

A18

MEM_AA4

A19

MEM_AA5

C17

MEM_AA6

C18

MEM_AA7

B17

MEM_AA8

A17

MEM_AA9

A16

MEM_AA10

C15

MEM_AA11

C14

MEM_AA12

B16

MEM_BA0

C16

MEM_BA1

A21

MEM_WE#

F6

MEM_COMPA

SM_RCOMP must be pulled down

to GND with 27.5 ohm resistor.

Memoryの配線条件については、回路図Page22を参照すること。

Rev.

DATE Design

6

2001.01.16 Komahara

Appr.

7

Description

CheckDesign

Yoshida Aoki

0.15inch

+/-50mil

PAD(C24)

R63 10 1/16W 5%

R64 10 1/16W 5%

R65 10 1/16W 5%

R66 10 1/16W 5%

R69

※ ※

27.4 1/16W 1%

Appr.

8

12

C

Board trace

CLK_DIMM0 23

CLK_DIMM1 23

CLK_DIMM2 23

CLK_DIMM3 23

MEM_CS#[0:3] 23

MEM_DQM[0:7] 23

MEM_CKE[0:3] 23

MEM_RAS# 22

MEM_CAS# 22

MEM_AA[0:12] 22

MEM_BA[0:1] 22

MEM_WE# 22

GND1

GMCH-M-1

TITLE

Laurel

DRAW. No.

C1CPxxxxxx-X1

FUJITSU

LTD.

Connect to

GND

SHEET

11 82

9

CAST

Page 10

1

CLK_GBI664

DVOB_CLKIN[0:1]24

VCH_GMBSCL_B24

VCH_GMBSDA_B24

DVOB_DATA[0:11]24

DVOB_BLANK#24

R85

330 1/16W 5%

1 2

GND1

-NOTE

G_PAR/DVO_DETECT signal use for DVO B/C detection.

Rx Unprpurated : AGP or Internal graphics with DVOA

Rx Popurated : DVO B/C selected.

This G_PAR/DVO_DETECT pin had internall pull up resister.

PWR_1.5VMAIN

RM2

8

7

6

5

SMT8

10kx4 1/32W 5%

RM4

1

2

3

4

10kx4 1/32W 5%

下記抵抗(R85)はM6‑AD24から0.5inch以内に配置すること。

R71

DVOB_CLKIN0

DVOB_CLKIN1

Open

Intel confermed

DDC2_B_CLK_PU15

VCH_GMBSCL_B

DDC2_B_DATA_PU15

VCH_GMBSDA_B

Open

Intel confermed

Open

Intel confermed

1

DVOA_PCLK

2

3

DVOB_CLKINT_PU15

4

8

DDC2_B_CLK_PU15

7

VCH_GMBSDA_B

6

DDC2_B_DATA_PU15

5

VCH_GMBSCL_B

12

GND1

DVOB_DATA7

CTM_PDGND

CTM#_PDGND

AG26

L29

L28

U29

U28

AA27

AA28

AB25

AB29

AB26

AA29

AA24

AA25

Y24

Y27

Y26

W24

Y28

R29

P26

P27

N25

R28

P28

L27

P29

R27

T25

AC27

AH15

AJ15

AG17

AJ17

AG18

AJ18

AG19

AJ19

AG20

AJ20

AJ11

AH10

AJ10

AG10

AJ9

AG9

AJ8

AG8

DVOB_INT# 24

VCH_GMBSDA_B 24

VCH_GMBSCL_B 24

r240k 1/16W 5%

SMT8

1

2

M3C

GBIN

AD_STB0/DVOB_CLK

AD_STB#0/DVOB_CLK#

AD_STB1/DVOC_CLK

AD_STB#1/DVOC_CLK#

SB_STB/ZV_D4

SB_STB#/ZV_D3

RBF#/ZV_D11

WBF#/ZV_D9

PIPE#/ZV_D10

SBA0/ZV_D8(UV0)

SBA1/ZV_D7(Y7)

SBA2/ZV_D6

SBA3/ZV_D5

SBA4/ZV_D2

SBA5/ZV_D1

SBA6/ZV_D0(Y0)

SBA7/ZV_HREF

G_AD30/DVOBC_INTR#/DPMS_CLK

G_FRAME#/M_DDC2_DATA

G_IRDY#/M_I2C_CLK

G_TRDY#/M_DDC2_CLK

G_STOP#

G_DEVSEL#/M_I2C_DATA

G_PAR/DVO_DETECT

G_C/BE#0/DVOB_D7

G_C/BE#1/DVOB_BLANK#

G_C/BE#2/ZV_VSYNC

G_C/BE#3/DVOC_D5

G_REQ#/ZV_CLK

RDRAM I/F

CTM

CTM#

DQ_A0

DQ_A1

DQ_A2

DQ_A3

DQ_A4

DQ_A5

DQ_A6

DQ_A7

DQ_B0

DQ_B1

DQ_B2

DQ_B3

DQ_B4

DQ_B5

DQ_B6

DQ_B7

Almador-M

PWR_3VMAIN

GND1

2

3

AGP I/F

G_AD13/DVOB_CLKINT#

G_AD14/DVOB_FLD/STL

G_AD16/DVOC_VSYNC

G_AD17/DVOC_HSYNC

G_AD18/DVOC_BLOCK#

G_AD31/DVOC_FLD/STL

AGP_RCOMP/DVOBC_RCOMP

R491

10K 1/16W 5%

2 1

RM3

1

2

3

4

10kx4 1/32W 5%

RM5

4

3

2

1

10kx4 1/32W 5%

GBOUT

G_AD0/DVOB_HSYNC

G_AD1/DVOB_VSYNC

G_AD2/DVOB_D0

G_AD3/DVOB_D0

G_AD4/DVOB_D3

G_AD5/DVOB_D2

G_AD6/DVOB_D5

G_AD7/DVOB_D4

G_AD8/DVOB_D6

G_AD9/DVOB_D9

G_AD10/DVOB_D8

G_AD11/DVOB_D11

G_AD12/DVOB_D10

G_AD15

G_AD19/DVOC_D0

G_AD20/DVOC_D1

G_AD21/DVOC_D2

G_AD22/DVOC_D3

G_AD23/DVOC_D4

G_AD24/DVOC_D7

G_AD25/DVOC_D6

G_AD26/DVOC_D9

G_AD27/DVOC_D8

G_AD28/DVOC_D11

G_AD29/DVOC_D10

AGP_BUSY#

ST0/ZV_D14

ST1/ZV_D13

ST2/ZV_D12

G_GNT#/ZV_D15(UV7)

GM_GCLK

GM_RCLK

CFM#

AGP_BUSY_PU33

8

DDC2_A_DATA_PU33

7

6

DDC2_A_CLK_PU33

5

SMT8

SMT8

5

6

CTM_PDGND

7

CTM#_PDGND

8

3

AD24

J29

J28

K26

K25

L26

J27

K29

K27

M29

M28

L24

M27

N29

M25

N26

N27

R25

R24

T29

T27

T26

U27

V27

V28

U26

V29

W29

V25

W26

W25

W27

Y29

AC24

AC28

AC29

AB27

AD29

K24

AGP_RCOMP

AG6

AJ6

AJ16

CFM

AH16

AG11

RQ0

AJ12

RQ1

AG12

RQ2

AH13

RQ3

AG13

RQ4

AJ13

RQ5

AG14

RQ6

AJ14

RQ7

AH7

CMD

AF7

SCK

AJ7

SIO

VCH_GMBSDA_A

VCH_GMBSCL_A

DVOA_FIELD_PDGND

DVOC_FIELD_PDGND

4

R70

C94

47 1/16W 5%

0.01uF 16V R

1 2

1 2

1 2

DVOB_DATA1

DVOB_DATA0

DVOB_DATA3

DVOB_DATA2

DVOB_DATA5

DVOB_DATA4

DVOB_DATA6

DVOB_DATA9

DVOB_DATA8

DVOB_DATA11

DVOB_DATA10

DVOB_CLKINT_PU15

Open

Intel confermed

DVOC_FIELD_PDGND

AGP_BUSY_PU33

Open

Intel confermed

AGP_RCOMP must be pulled down

to GND with 55 ohm resistor.

Open

Intel confermed

VCH_GMBSDA_A 26

VCH_GMBSCL_A 26

1 2

R72 47 1/16W 5%

R73 47 1/16W 5%

R84 54.9 1/16W 1%

4

AGP_BUSY_PU33 16

21

PWR_CPUBUS

FL5

BLM21P300S

CLK_GBO66 4

DVOB_HSYNC 24

DVOB_VSYNC 24

DVOB_DATA[0:11] 24

DVOB_STALL 24

DVOB_INT# 24

GND1

21

5

CLK_MCH_DREF484

DVOA_PCLK26

DVOA_RCOMP must be pulled down

GND1

to GND with 55 ohm resistor.

CRT_DDC1_CLK25

CRT_DDC1_CLK/DATA pullup had

CRT connector sections via Q-SW.

12

+

10uF 6.3V (TA)

C96

CRT_DDC1_DATA25

VCH_GMBSCL_A26

VCH_GMBSDA_A26

GND1

HL_STRB16

HL_STRB#16

GND1

FL6

BLM11B102S

FL8

BLM11B102S

FL10

BLM11B102S

6

PWR_1.5VMAIN

DVOA_PCLK

DVOA_FIELD_PDGND

R76 54.9 1/16W 1%

HL_RCOMP must be pulled down

to GND with 55 ohm resistor.

12

CRT_DDC1_CLK

CRT_DDC1_DATA

DDC2_A_CLK_PU33

DDC2_A_DATA_PU33

VCH_GMBSCL_A

VCH_GMBSDA_A

R77 255 1/16W 1%

1 2

R86 54.9 1/16W 1%

21

21

2 1

C98 1uF 10V12C99 1uF 10V

C725 0.1uF 16V 20%

GND1GND1

21

12

C101

GND1

C95,C96はGMCHF25,GMCHAC20ピンの近くに配置すること。

R87,R88,R90,R91,R92,R93,R94は、GMCH(M6)

から0.5inch以内に置き、配線は10mil以上にすること

Place R87,R88,R90,R91,R92,R93,R94 near GMCH (within 0.5 inch) and

the width of patterns must be more than 10 mil.

5

6

12

21

1uF 10V

2 1

C726 0.1uF 16V 20%

12

+

10uF 6.3V (TA)

C97

AC19

AE21

AD20

AE22

AC22

AE27

AD27

AE26

AD26

AD25

AC25

AJ27

AC20

AE20

G29

G24

AE6

AD7

F28

J23

F25

Rev.

7

M3D

DREFCLK

DVOA_INTR#

DVOA_CLKINT

DVOA_FLD/STL

DVOA_RCOMP

DVOA I/F

Analog Display I/F

DDC1_CLK

DDC1_DATA

DDC2_CLK

DDC2_DATA

I2C_CLK

I2C_DATA

REFSET

HUB I/F

HLSTRB

HLSTRB#

HL_RCOMP

Analogue Power

VCCA_DPLL0

VCCA_DPLL1

VSSA_DPLL0

VSSA_DPLL1

VCCA_HPLL

VSSA_HPLL

Almador-M

DATE Design

2001.01.16 Komahara

7

DVOA_CLK

DVOA_CLK#

DVOA_D0

DVOA_D1

DVOA_D2

DVOA_D3

DVOA_D4

DVOA_D5

DVOA_D6

DVOA_D7

DVOA_D8

DVOA_D9

DVOA_D10

DVOA_D11

DVOA_HSYNC

DVOA_VSYNC

DVOA_BLANK#

HSYNC

VSYNC

RED

GREEN

BLUE

RED#

GREEN#

BLUE#

HL0

HL1

HL2

HL3

HL4

HL5

HL6

HL7

HL8

HL9

HL10

VCCA_CPLL

VSSA_CPLL

VCCA_DAC

VCCA_DAC

VSSA_DAC

Appr.

CheckDesign

Yoshida Aoki

AJ24

AG24

AJ22

AH22

AG22

AJ23

AH23

AG23

AE23

AE24

AJ25

AH25

AG25

AJ26

AF22

AF23

AD21

AD28

AE29

AF29

AG29

AH28

AF28

AG28

AH27

G26

H28

H29

H27

F29

F27

E29

E28

G25

G27

H26

G7

G8

AF26

AG27

AH26

Description

8

DVOA_CLKIN0

DVOA_CLKIN1

DVOA_DATA0

DVOA_DATA1

DVOA_DATA2

DVOA_DATA3

DVOA_DATA4

DVOA_DATA5

DVOA_DATA6

DVOA_DATA7

DVOA_DATA8

DVOA_DATA9

DVOA_DATA10

DVOA_DATA11

R74 47 1/16W 5%

1 2

R75 47 1/16W 5%

2 1

CRT_HSYNC

CRT_VSYNC

CRT_RED

CRT_GREEN

CRT_BLUE

CRT_RED#

CRT_GREEN#

CRT_BLUE#

HL[0:10] 16

HL0

HL1

HL2

HL3

HL4

HL5

HL6

HL7

HL8

HL9

HL10

FL7

21

BLM11B102S

C95

1uF 10V

GND1

FL9

12

BLM11B102S

12

+

C100

1uF 10V

C686

10uF 6.3V (TA)

GND1

Appr.

8

DVOA_CLKIN[0:1] 26

DVOA_DATA[0:11] 13,26

DVOA_HSYNC 26

DVOA_VSYNC 26

CRT_HSYNC 25

CRT_VSYNC 25

1 2

2 1

2 1

1 2

1 2

2 1

R79 75 1/16W 1%

R80 75 1/16W 1%

R81 37.4 1/16W 1%

R82 37.4 1/16W 1%

R78 75 1/16W 1%

12

PWR_1.8VMAIN

12

GMCH-M-2

TITLE

Laurel

DRAW. No.

C1CPxxxxxx-X1

FUJITSU

LTD.

9

CRT_RED 53,57

CRT_GREEN 53,57

CRT_BLUE 53,57

GND1

R83 37.4 1/16W 1%

SHEET

12 82

9

CAST

Page 11

1

PWR_1.5VMAIN

PWR_1.8VMAIN

GND1

C108

GND1

12

0.01uF 16V R

◎

VGTLREF

SM_VREF14

HL_REF14,16

1

2

C99,C100はGMCHA8,GMCHA12に直接接続すること。

A8,A12pinは可能な限り広い電源ベタに貫通VIAで接続すること。(電源層が望ましい)

またGNDへの接続も貫通VIAで接続すること。

コンデンサはGMCHA8,GMCHA12の90mil(2.286mm)以内に配置すること。

PWR_CPUBUS PWR_3VSUS

M3E

Digital Power

N6

VCC

T6

VCC

H7

VCC

K7

VCC

L7

VCC

W7

VCC

Y7

VCC

AB7

VCC

P12

VCC

R12

VCC

T12

VCC

M14

VCC

M15

VCC

M16

VCC

P18

VCC

R18

VCC

T18

VCC

H23

VCC

K23

VCC

Y23

VCC

M24

VCC

P24

VCC

T24

VCC

V24

VCC

AC21

VCC_DVO

AF21

VCC_DVO

AF24

VCC_DVO

L23

VCC_AGP

U24

VCC_AGP

J26

VCC_AGP

M26

VCC_AGP

R26

VCC_AGP

V26

VCC_AGP

AA23

VCC_AGP

AA26

VCC_AGP

W23

VCCQ_AGP

N24

VCCQ_AGP

J24

VCC_HUB

F26

VCC_HUB

AC8

VCC_CMOS

AC9

VCC_CMOS

AE7

VCC_CMOS

AF6

VCC_CMOS

E11

NC

E20

21

C106 0.1uF 10V R21C107 0.1uF 10V R

◎

◎

21

GND1

◎のついた信号線は25mil以上の太さで配線し、

周りをベタのGNDで配線すること。

Thewidthofsignalsthatmarked"◎"mustbelaidout

morethan25milandguardatthebothsides,topand

bottombyGND1pattern.

NC

F12

NC

F20

NC

REF Voltage

E5

SM_REFA

F24

SM_REFB

H24

HLREF

J7

GTL_REFA

AA7

GTL_REFB

12

Almador-M

C103,C104,C105,C106,C107は各PINの近くに配置すること。

C110 0.1uF 10V R

C109 0.1uF 10V R

2

3

VCC_SM

VCC_SM

VCC_SM

VCC_SM

VCC_SM

VCC_SM

VCC_SM

VCC_SM

VCC_SM

VCC_SM

VCC_SM

VCC_SM

VCC_SM

VCC_SM

VCC_LM

VCC_LM

VCC_LM

VCC_LM

VCC_LM

VCC_LM

VCC_LM

VCC_LM

VCC_LM

VCC_GPIO

VCC_GPIO

VCCQ_SM

VCCQ_SM

VCCQ_SM

VCCQ_SM

VCCQ_SM

VDD_LM

VDD_LM

VDD_LM

VDD_LM

VDD_LM

VDD_LM

VDD_LM

RAM_REFA

RAM_REFB

AGPREF

3

4

GND1

21

12

0.1uF 10V R

C102

D5

D8

D11

G11

D14

D17

D20

D23

G23

D26

G10

E12

A8

A12

AC10

AC11

AD11

AD12

AD13

AD17

AD18

AD19

AE18

AD23

AE25

E15

F7

F15

G19

G20

V14

V15

V16

AD15

AD16

AE15

AE16

E2

VTT

F5

VTT

J5

VTT

M5

VTT

R5

VTT

V5

VTT

AA5

VTT

AD5

VTT

AG5

VTT

AD14

AE14

J25

0.1uF 10V R

C103

PWR_3VSUS

PWR_CPUBUS

PWR_CPUBUS

◎

RAM_REF 14

◎

AGP_MCHREF 14,24,26

21

C105

4

PWR_1.8VMAIN

GND1

68pF 25V

5

12

68pF 25V

C104

GND1

C102はAE15,AE16の近くに配置すること。

Place C102 near AE15 and AE16 on

GMCH.

5

GND1

6

AD10

AE10

AF10

AE11

AF11

AH11

AE12

AF12

AH12

AE13

AF13

6

C21

AH2

AC5

AF5

AH6

AC7

AG7

AD8

AE8

AF8

AH8

AD9

AE9

AF9

AH9

M12

N12

U12

M13

N13

R13

U13

N14

R14

U14

7

M3F

A14

VSS

B13

VSS

C3

VSS

VSS

E14

VSS

F19

VSS

D2

VSS

G2

VSS

K2

VSS

N2

VSS

T2

VSS

W2

VSS

AB2

VSS

AE2

VSS

VSS

B3

VSS

E4

VSS

H5

VSS

L5

VSS

P5

VSS

U5

VSS

Y5

VSS

VSS

VSS

AJ5

VSS

B6

VSS

VSS

E7

VSS

VSS

VSS

VSS

VSS

VSS

VSS

B9

VSS

G9

VSS

VSS

VSS

VSS

VSS

E10

VSS

VSS

VSS

VSS

VSS

VSS

VSS

B12

VSS

VSS

VSS

VSS

V12

VSS

VSS

VSS

VSS

E13

VSS

VSS

VSS

P13

VSS

VSS

T13

VSS

VSS

V13

VSS

VSS

VSS

VSS

P14

VSS

VSS

T14

VSS

VSS

Almador-M

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

Rev.

DATE Design

2001.01.16 Komahara

AF14

AH14

B15

N15

P15

R15

T15

U15

AF15

AG15

E16

N16

P16

R16

T16

U16

AF16

AG16

M17

N17

P17

R17

T17

U17

V17

AE17

AF17

AH17

B18

M18

N18

U18

V18

AF18

AH18

E19

AE19

AF19

AH19

AF20

AH20

B21

G21

AG21

AH21

AJ21

E22

AD22

AB23

AC23

B24

AH24

E25

H25

L25

P25

U25

Y25

AF25

AC26

B27

AF27

D28

G28

K28

N28

T28

W28

AB28

AE28

7

Almador-M Strapping Options

GND1

Appr.

CheckDesign

Yoshida Aoki

8

DVOA_DATA012,26

DVOA_DATA112,26

DVOA_DATA512,26

DVOA_DATA612,26

R87 2.2k 1/16W 5% Reserve

R88 2.2k 1/16W 5%

R89 2.2k 1/16W 5%

R90 2.2k 1/16W 5% Reserve

21

12

PWR_1.5VMAIN

21

21

9

Reserve

GND1

Signal Notes

DVOA_D0

DVOA_D1

DVOA_D5

DVOA_D6

DVOA_D7

DVOA_D8

G_PAR 0=DVO B/C Device connected.

Description

0=Reserved

1=133MHz(default)

0=IOQD1

1=IOQD8(default)

0=Desktop(default)

1=Mobile

0=dual ended termination(default)

1=single ended termination

0=Normal opration (default)

1=XOR Chain test mode

0=Normal operation(default)

1=Tri-state all i830M outputs

1=AGP Device (Default)

GMCH-M-3,STRAP

Appr.

8

TITLE

Rickwood Main Board

DRAW. No.

C1CPxxxxxx-X1

FUJITSU

LTD.

SHEET

9

CAST

13 82

Page 12

1

PWR_3VSUS

21

R91

240 1/16W 1%

C138

2 1

470pF 25V

C158

1 2

470pF 25V

◎

12

R97

82 1/16W 1%

12

R100

82 1/16W 1%

◎

12

R93

47 1/16W 1%

GND1

上記信号<SMVREF>は配線が最短になるように部品を

GMCHの近くに配置すること。

PWR_1.5VMAIN

21

R96

1K 1/16W 1%

21

R99

1K 1/16W 1%

GND1

上記信号<AGPVGAREF>は配線が最短になるように部品を

GMCH(M6)の近くに配置すること。

2

SM_VREF 13

AGP_MCHREF 13,24,26

3

PWR_1.8VMAIN

12

R92

300 1/16W 1%

12

R94

300 1/16W 1%

GND1

上記抵抗とコンデンサは、極力GMCHとICH3の

中間になるよう配置し、それぞれの配線長は10cm

以内とすること

PWR_1.8VMAIN

21

R95

300 1/16W 1%

21

R98

300 1/16W 1%

GND1

上記信号<HUBVSWG>は配線が最短になるように部品を

ICH3の近くに配置すること。

◎

◎

4

HL_REF 13,16

HUBVSWG 16

5

21

C687 0.22uF 10V

PWR_CPUBUS

GND1

21

GND1

21

H

GND1

21

C159

J JKK

21

C127 0.1uF 16V

C139 0.1uF 16V

1uF 10V

21

C688 0.22uF 10V

21

21

Reserve

6

21

C689 0.22uF 10V

A

C128 0.1uF 16V

D

21

Reserve

C140 0.1uF 16V

PWR_3VSUS

C690 0.22uF 10V

Reserve

C141 0.1uF 16V

C160

GND1

21

12

21

21

C142 82pF 25V

1uF 10V

12

21

C113

C111 0.1uF 16V

C112 0.1uF 16V

B B

21

21

C131

C129 0.1uF 16V

C130 0.1uF 16V

21

21

C144 0.1uF 16V

C143 0.1uF 16V

21

C161 0.1uF 16V

GND1GND1

7

12

21

1uF 10V

C114 0.1uF 16V

C132 0.1uF 16V

21

Reserve

C145 0.1uF 16V

21

C162 0.1uF 16V

21

C133

21

C146 82pF 25V

21

C164

C163 0.1uF 16V

21

82pF 25V

E F

21

Reserve

21

12

C116

C115 0.1uF 16V

21

82pF 25V

C147 0.1uF 16V

82pF 25V

1uF 10V

C134 0.1uF 16V

21

21

21

21

C148 0.1uF 16V

Reserve

21

C165 0.1uF 16V

8

21

C117 0.1uF 16V

12

C135

21

C150

C149 0.1uF 16V

12

C167

C166 0.1uF 16V

PWR_1.5VMAINPWR_3VSUS

21

C118 0.1uF 16V

12

C136

0.1uF 10V R

21

82pF 25V

82pF 25V

21

C120 0.1uF 16V

C119 0.1uF 16V

PWR_1.8VMAIN

12

C137

0.1uF 10V R

G

21

C152 0.1uF 16V

C151 0.1uF 16V

Reserve

21

L

C168 0.1uF 16V

21

1uF 10V

21

21

9

21

C122 0.1uF 16V

C121 0.1uF 16V

21

C154 0.1uF 16V

C153 0.1uF 16V

PWR_1.5VMAIN

12

C170

1uF 10V

C169 0.1uF 16V

PWR_CPUBUS

21

C123 0.1uF 16V

PWR_3VSUS

21

Reserve

C155 0.1uF 16V

12

C124 0.1uF 16V

C

21

C156 82pF 25V

PWR_1.8VMAIN

12

R101

160 1/16W 5%

◎

12

R102

560 1/16W 5%

GND1

上記信号<RAMREF>は配線が最短になるように部品を

GMCH(M6)の近くに配置すること。

◎のついた信号線BGAPAD横に貫通THを空け

その裏面直下に部品を搭載、配線すること。

1

RAM_REF 13

2

A

1

Topview

C

12

C171

1uF 10V

J

J

GND1

H

J

J

2 1

Reserve

C706 10uF 6.3V B

H

12

C173

C172 0.1uF 16V

C174

82pF 25V

21

1uF 10V

12

M

GND1

G

B B

C

A A

L

PassC for GMCH-M

E

AJ

3

4

D

F

M

Rev.

DATE Design

5

6

2001.01.16 Komahara

Appr.

7

Description

CheckDesign

Yoshida Aoki

Appr.

8

TITLE

Rickwood Main Board

DRAW. No.

C1CPxxxxxx-X1

FUJITSU

LTD.

9

SHEET

CAST

14 82

Page 13

1

ADD

pin

GND01

0

N.C

VCC

☆印の付いた信号線(CPUTHMDA,CPUTHMDC)は、

GND1で両側をガードすること

(下図参照)

10mil

10mil

10mil

10mil

GND1

CPUTHMDA

CPUTHMDC

GND1

2

A0

Address

01011,100

0A101011,00

1 01011,01

3

コンデンサは本ICの近くに配置

10mil

10mil

10mil

4

FAN_TACH

SMBCLK38,50,52

SMBDATA38,50,52

CPU_THMDA5 FANFAULT# 41

CPU_THMDC5

5

M4

2

TACH

16

SMBCLK

SMBDATA15INT#

10

DX+

9

DX-

3

NC

4

NC0

11

NC1

12

NC2

13

ADD

124

875

PWM_OUT

FANFAULT#

ADM1030_Rev3

PWR_5VMAIN

12

R103

10k 1/16W 5%

TP2

TACK

☆

12

C175

2200pF 25V

Reserve

☆

GND1

本ICはCPUの近くに配置願います。

6

PWR_3VMAIN

3

SMT8

6

THERM#

VCC

GND0

RM6

10kx4 1/32W 5%

1

14

7

8

PWR_3VMAIN

6

5

GND1

12

C176

0.1uF 16V

7

ADFANON

ATFINT# 38

THLTL# 16

8

9

TP95

FAN

FAN_TACH

GND1

Description

CheckDesign

Yoshida Aoki

CN22

01

TP96

TACK

21

C177

4.7uF 10V

8

Appr.

-

02

+

03

NC

FAN CN

Thermister,FAN

TITLE

Rickwood Main Board

DRAW. No.

C1CPxxxxxx-X1

FUJITSU

LTD.

9

SHEET

CAST

15 82

21

R105

47k 1/16W 5%

32

Q2

2SK3019

6

Q1

Si2305DS

1

32

Rev.

DATE Design

2001.01.16 Komahara

Appr.

7

PWR_5VSUS

12

R104

470k 1/16W 5%

ADFANON

1

2

3

4

5

2 1

C178

1000pF 25V

1

GND1

Page 14

1

CLK_ICH144

CLK_ICH484

CLK_ICH664

HUBVSWG14

HL[0:10]12

C158はM8‑L19pinの

近くに配置すること。

HL1118

LPC_DRQ#019,37

LPC_DRQ#119

BSRBTN#40

THLTL#15

AGP_BUSY_PU3312

RIOUT#39

VGATE45

ICHPWROK17,25,40

RSMRST#40,45

CPU_FERR#5,8

EXTSMI#19,39

KBCSCI38

EXTSCI#39

BLUE_RI17,57

BLID40

PWR_RTC

R124はM8‑Y6pinの

近くに配置すること。

KBINIT#38

KBA20G38

1

21

GND1

GND1

R112

2 1

100k 1/16W 5%

GND1

C179

1uF 10V

PLLB#

2 1

C187

2 1

1000pF 25V

HL0

HL2

HL3

HL4

HL5

HL6

HL7

HL8

HL9

HL10

J23

F20

T19

L19

L22

M21

M23

N20

P21

R22

R20

T23

M19

P19

N19

R19

AB1

AA1

AB3

V19

AA6

AA7

J22

U22

Y22

W2

C188

1000pF 25V

C9

C8

A8

A9

Y5

D8

T2

U4

U5

V4

C4

V2

Y4

Y2

Y6

2

M5A

CLK14

CLK48

CLK66

HITERM

HI0

HI1

HI2

HI3

HI4

HI5

HI6

HI7

HI8

HI9

HI10

HI11

LAN_CLK

LAN_RXD0

LAN_RXD1

LAN_RXD2

LAN_RST#

EE_DIN

LDRQ#0

LDRQ#1

PWRBTN#

THRM#

AGPBUSY#

RI#

BATLOW#

VGATE/VRMPWRGD

PWROK

RSMRST#

FERR#

RCIN#

A20GATE

GPIO0/REQ#A

GPIO7

GPIO8

GPIO12

GPIO13

INTRUDER#

ICH3-M

SMLINK0_PU33

SMLINK1_PU33

2

HI_STB

HI_STB#

HICOMP

HIREF

LAN_RSTSYNC

LAN_TXD0

LAN_TXD1

LAN_TXD2

EE_SHCLK

EE_DOUT

EE_CS

FWH0/LAD0

FWH1/LAD1

FWH2/LAD2

FWH3/LAD3

FWH4/LFRAME#

SLP_S1#

SLP_S3#

SLP_S5#

SUS_STAT#/LPCPD#

C3_STAT#/GPIO21

STP_PCI#

STP_CPU#

DPRSLPVR

CPUPERF#

SSMUXSEL

A20M#

CPUSLP#

IGNNE#

INIT#

INTR

SMI#

STPCLK#

CPUPWRGD

DPSLP#

SUSCLK

SMLINK0

SMLINK1

RM7

8

7

5

6

SMT8

10kx4 1/32W 5%

3

◎のついた信号線は25mil以上の太さで配線し、

左右と下をベタのGND線で囲むこと

※抵抗R117はM8から0.5inch以内に置き、

10mil幅以上で配線すること。

N22

P23

K19

HL_COMPIAHL1

L20

◎

D7

B9

C10

A10

D10

E8

E9

V1

U3

T3

U2

U1

W20

AA5

AA2

AB4

V5

U21

V21

AB21

Y20

U20

V23

W21

AA21

AB23

AA23

Y21

NMI

Y23

U23

W23

AB22

AA4

CLK_32K_STD

AC3

SMLINK0_PU33

SMLINK1_PU33

AB2

PWR_5VMAIN

1

2

4

3

3

2 1

R106 36.5 1/16W 1%

12

C180

1uF 10V

GND1

Intel Checking!!!Intel Checking!!!

PWR_3VSTD

4

HL_STRB 12

HL_STRB# 12

GND1

HL_REF 13,14

C159はM8‑L20pinの

近くに配置すること。

LPC_AD0 20,37,39

LPC_AD1 20,37,39

LPC_AD2 20,37,39

LPC_AD3 20,37,39

LPC_FRAME# 19,20,37,39

SUSA# 71

SUSB# 4,37,40,42,45,60,61,62,69,76

SUSC# 50,62,70,71

SUSTAT# 37,40

STP_PCI# 4

STP_CPU# 4

DPRSLPVR 60

GLO/HI# 5

VR_HI/LO# 60

CPU_A20M# 5

CPU_IGNNE# 5

CPU_INIT# 5,8,20

CPU_INTR 5,8

CPU_NMI 5,8

CPU_SMI# 5,8

CPU_STPCLK# 5

CPU_PWRGD 5,8

CPU_DPSLP# 5,8,60

CLK_32K_STD 50

PWR_RTCBATT

12

C186

0.1uF 16V

GND1

4

PWR_RTCBATT

PWR_PMU

R110

1k 1/16W 5%

TP3

PWR_RTCBATT

CN20

1

2

RTC BAT CN

5

PCI_AD[0:31]27,29,42,50

PWR_3VMAIN

PWR_RTC

1SS400

D60

2 1

D61 1SS400

21

2 1

R113

1 2

1k 1/16W 5%

2 1

R114

15k 1/16W 5%

+

-

上記振動子(X2)は、ICH3(M7)の近傍に配置すること。

また、振動子両端のパターンに隣接して、

高速な信号を走らせてはならない。(層構成も考慮のこと)

5

C184 0.047uF 10V

2 1

RTCRST#

21

GND1

C181

GND1

C185 1uF 10V

12

1uF 10V

CL1

CL2

IRQ1456

IRQ1555,56

PCI_REQ#019,27

PCI_REQ#119,25

PCI_REQ#219,25

ICH_GPI117

PCI_SERR#19,27,29,42,50

WAKEOUT#39

USB_OC#049

USB_OC#149

USB_OC#549

4

1

2

CLK_ICH334

X2

VDD

VIO

GND

32.768KHz

GND1

6

PCI_AD0

PCI_AD1

PCI_AD2

PCI_AD3

PCI_AD4

PCI_AD5

PCI_AD6

PCI_AD7

PCI_AD8

PCI_AD9

PCI_AD10

PCI_AD11

PCI_AD12

PCI_AD13

PCI_AD14

PCI_AD15

PCI_AD16

PCI_AD17

PCI_AD18

PCI_AD19

PCI_AD20

PCI_AD21

PCI_AD22

PCI_AD23

PCI_AD24

PCI_AD25

PCI_AD26

PCI_AD27

PCI_AD28

PCI_AD29

PCI_AD30

PCI_AD31

1 2

R108

33K 1/16W 1%

PWR_RTC

R504 150K 1/16W 5%

3

OUT

6

2 1

1 2

R111 10M 1/16W 5%

1

T5

PCICLK

J2

AD0

K1

AD1

J4

AD2

K3

AD3

H5

AD4

K4

AD5

H3

AD6

L1

AD7

L2

AD8

G2

AD9

L4

AD10

H4

AD11

M4

AD12

J3

AD13

M5

AD14

J1

AD15

F5

AD16

N2

AD17

G4

AD18

P2

AD19

G1

AD20

P1

AD21

F2

AD22

P3

AD23

F3

AD24

R1

AD25

E2

AD26

N4

AD27

D1

AD28

P4

AD29

E1

AD30

P5

AD31

AB14

IRQ14

W19

IRQ15

D3

REQ#0

F4

REQ#1

A3

REQ#2

R4

REQ#3

E4

REQ#4

D4

REQ#5/REQ#B/GPIO1

L5

SERR#

W1

PME#

E12

OC#0/GPIO32

D12

OC#1/GPIO33

C12

OC#2/GPIO34

B12

OC#3/GPIO35

A12

OC#4/GPIO36

A11

OC#5/GPIO37

B21

USBRBIAS

AB6

VCCRTC

AC7

RTCX1

2 1

AC6

RTCX2

R503

10M 1/16W 5%

Reserve

AB7

VBIAS

Y7

RTCRST#

32

Q58

2SK3019

GND1

Rev.

7

M5B

ICH3-M

DATE Design

2001.01.16 Komahara

7

PIRQ#E/GPIO2

PIRQ#F/GPIO3

PIRQ#G/GPIO4

PIRQ#H/GPIO5

GNT#5/GNT#B/GPIO17

USBLEDA#0/GPIO32

USBLEDA#1/GPIO33

USBLEDA#2/GPIO34

USBLEDA#3/GPIO35

USBLEDA#4/GPIO36

USBLEDA#5/GPIO37

USBLEDG#0/GPIO38

USBLEDG#1/GPIO39

USBLEDG#2/GPIO40

USBLEDG#3/GPIO41

USBLEDG#4/GPIO42

USBLEDG#5/GPIO43

CLK_PMU32K 39,71

Appr.

CheckDesign

Yoshida Aoki

PCIRST#

C/BE#0

C/BE#1

C/BE#2

C/BE#3

DEVSEL#

FRAME#

IRDY#

TRDY#

STOP#

PAR

PLOCK#

PERR#

CLKRUN#

SERIRQ

PIRQ#A

PIRQ#B

PIRQ#C

PIRQ#D

GNT#0

GNT#1

GNT#2

GNT#3

GNT#4

USBP0P

USBP0N

USBP1P

USBP1N

USBP2P

USBP2N

USBP3P

USBP3N

USBP4P

USBP4N

USBP5P

USBP5N

Description

PLLB40,71

8

Y1

K2

PCI_C/BE#0

K5

PCI_C/BE#1

N1

PCI_C/BE#2

R2

PCI_C/BE#3

M3

F1

N3

H1

H2

G5

M1

M2

AC2

H22

R107 22 1/16W 5%

B1

C1

B2

A2

A6

B5

C5

A5

A4

E3

D2

D5

B4

B3

D19

D18

A19

A18

E17

E16

B17

B16

D15

D14

A15

A14

H20

G22

F21

G19

E22

E21

H21

G23

F23

G21

D23

E23

Appr.

8

9

PCI_RST# 11,19,20,24,26,27,37,40

PCI_C/BE#[0:3] 27,29,42,50

PCI_DEVSEL# 19,27,29,42,50

PCI_FRAME# 19,27,29,42,50

PCI_IRDY# 19,27,29,42,50

PCI_TRDY# 19,27,29,42,50

PCI_STOP# 19,27,29,42,50

PCI_PAR 27,29,42,50

PCI_LOCK# 19,29

PCI_PERR# 19,27,29,42,50

PCI_CLKRUN# 19,27,29,37,42,50

21

SERIRQ 19,29,37

R118はM8‑H22pinの

近くに配置すること。

PCI_INT#0 19,29

PCI_INT#1 19,29

PCI_INT#2 19,50

PCI_INT#3 19,50

PCI_INT#4 19,27

PCI_INT#5 19,42

PCI_INT#6 19

PCI_INT#7 19

PCI_GNT#0 27

PCI_GNT#1 29

PCI_GNT#2 50

PCI_GNT#3 42PCI_REQ#319,42

USB_P0P 49

USB_P0N 49

USB_P1P 49,53

USB_P1N 49,53

USB_P2P 55

USB_P2N 55

USB_P5P 52

USB_P5N 52

USB_P4P 52

USB_P4N 52

USB_P3P 57

USB_P3N 57

FR_USBON 52

ICH_GPIO42 18

ICH_GPIO43 18

PWR_3VSTD

21

R115

100k 1/16W 5%

PLLB#

32

Q3

2SK3019

1

GND1

ICH3-M-1

TITLE

Rickwood Main Board

DRAW. No.

C1CPxxxxxx-X1

FUJITSU

LTD.

SHEET

9

CAST

16 82

Page 15