Page 1

1

2

3

4

5

6

7

8

9

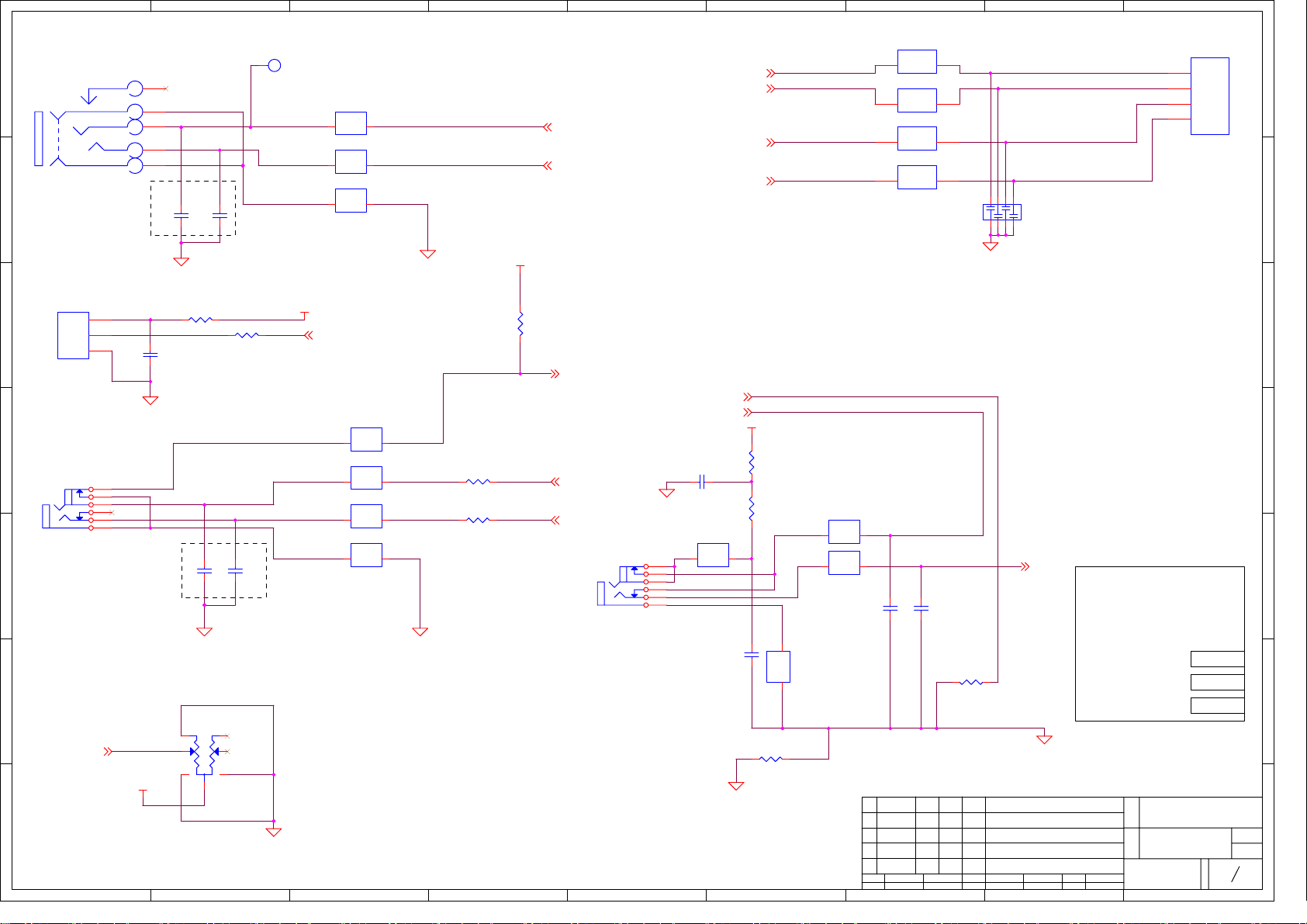

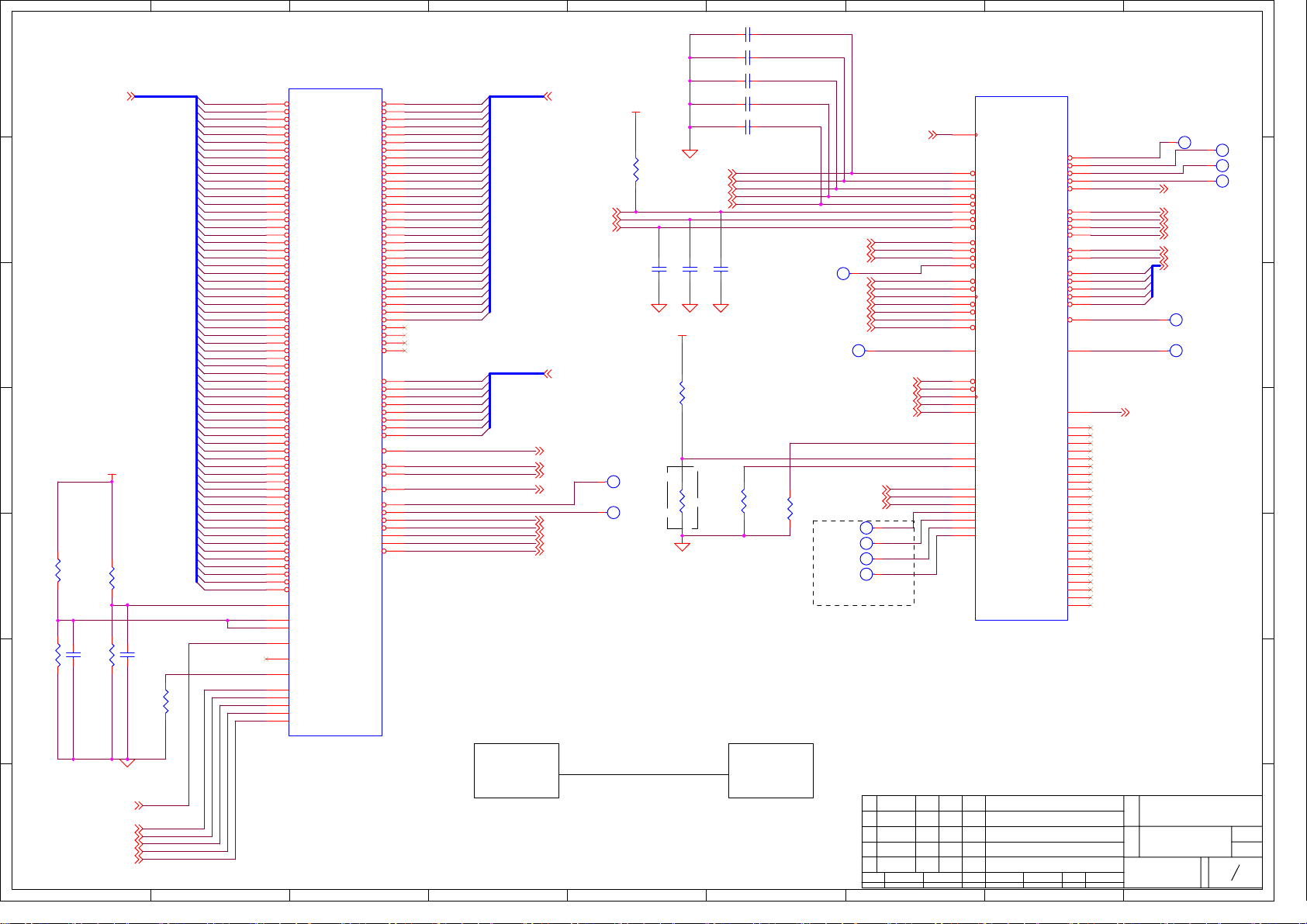

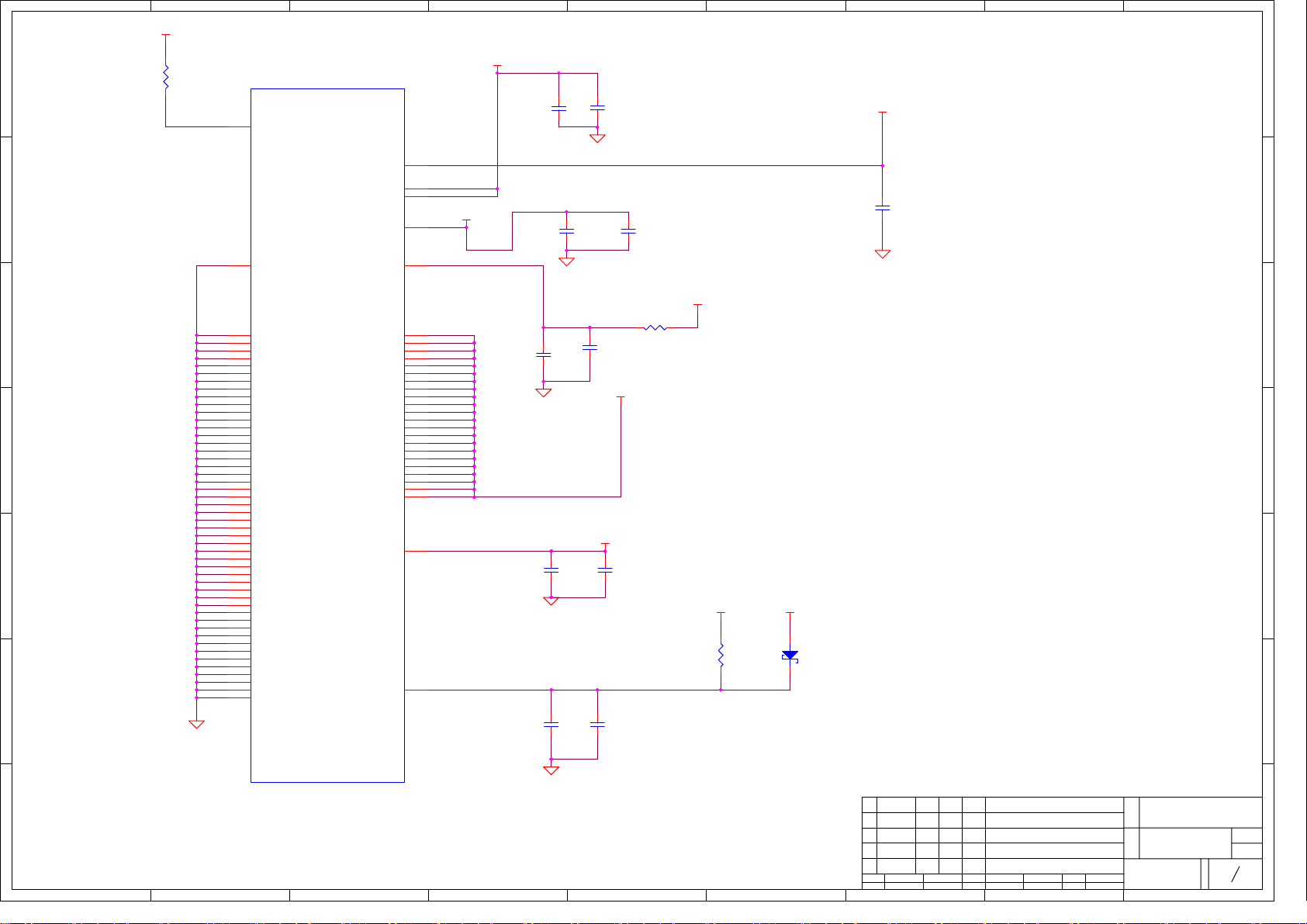

ANISE-E2 Main 04 (VB67Ax)

A A

PAGE CONTENTS

01

02

03

04

05

B B

06

07

08

09

10

11

12

13

C C

14

15

16

17

18

19

20

21

D D

22

23

24

25

26

27

MENU

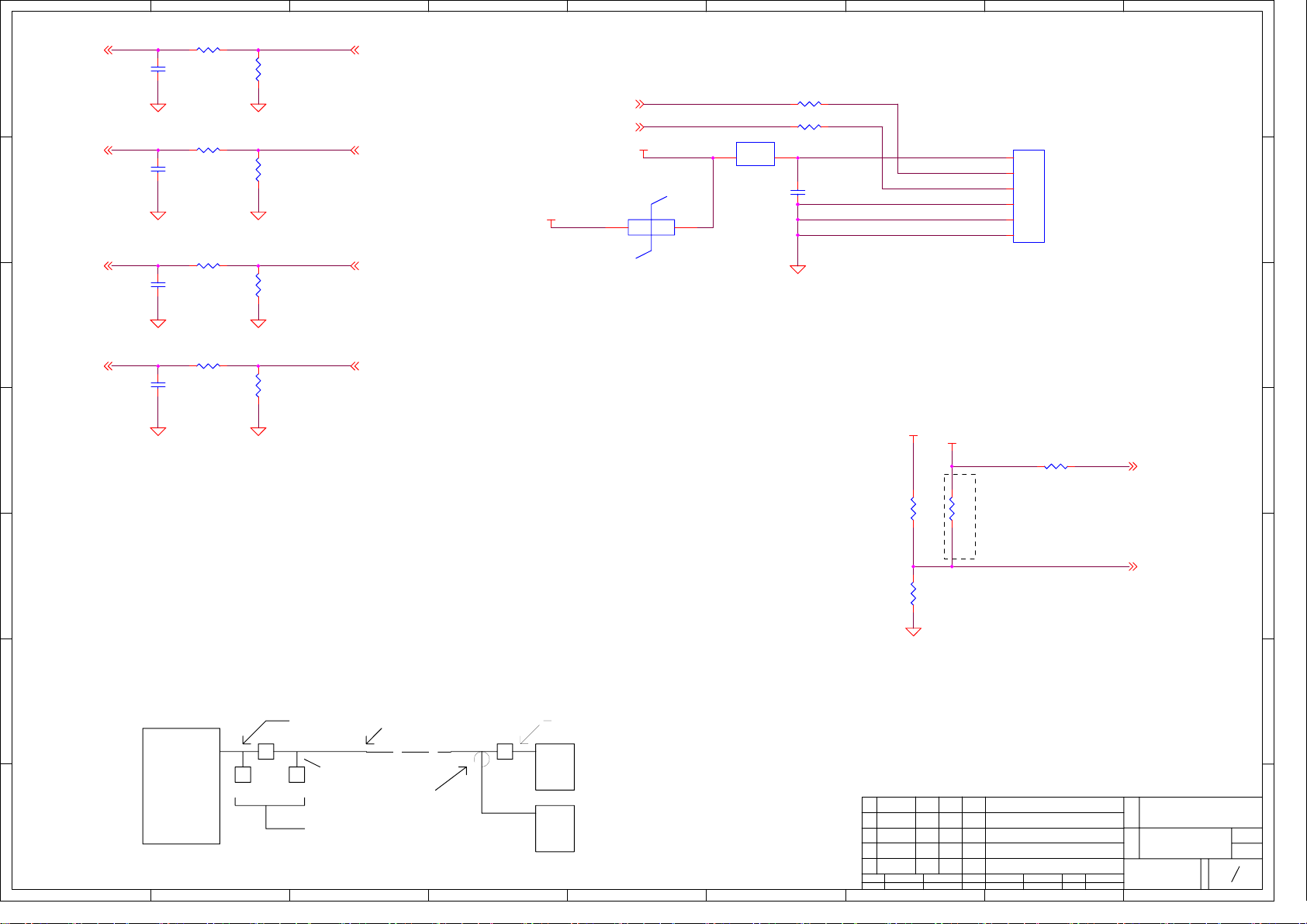

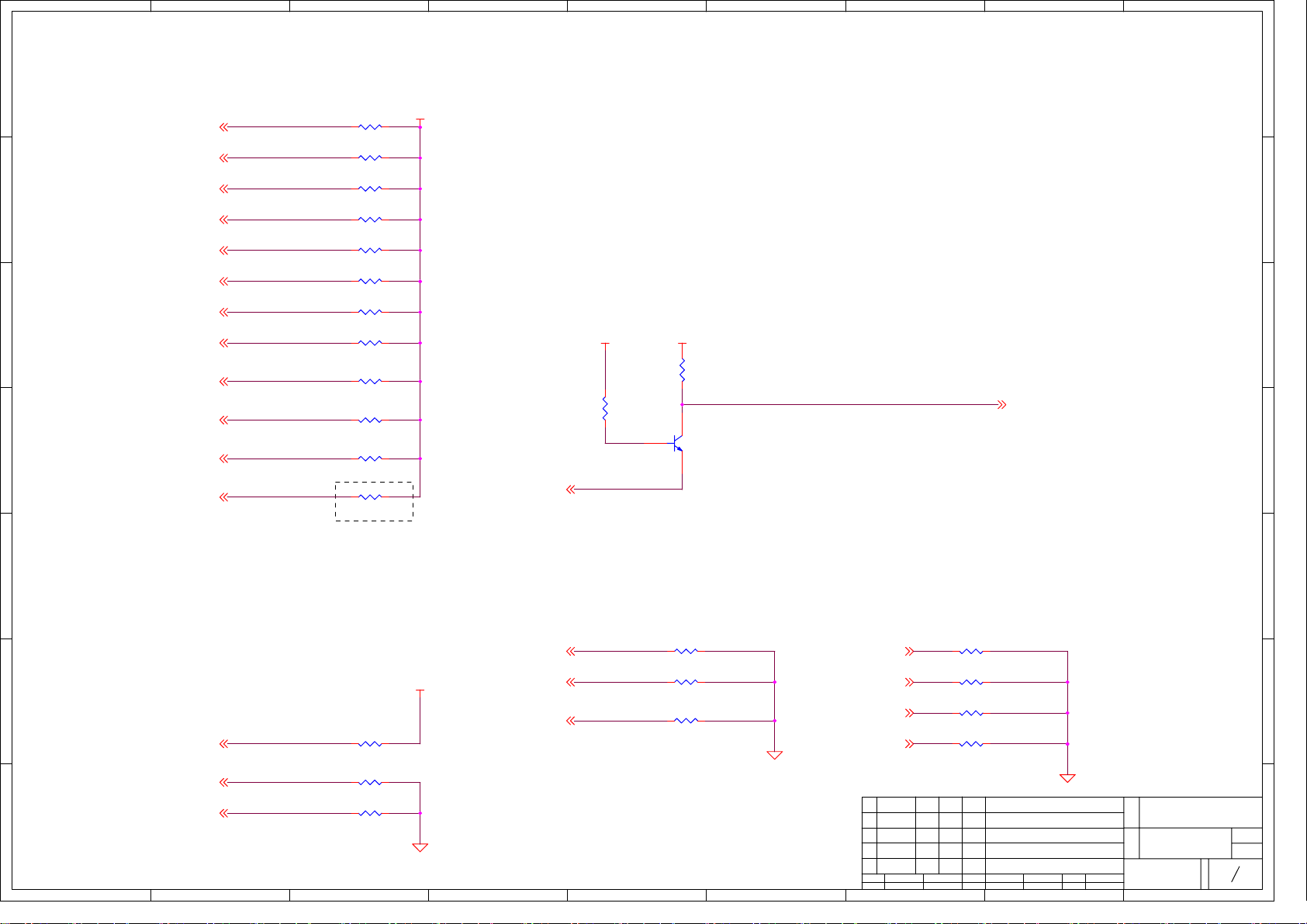

EMI RC

DOCKING/LAN CN

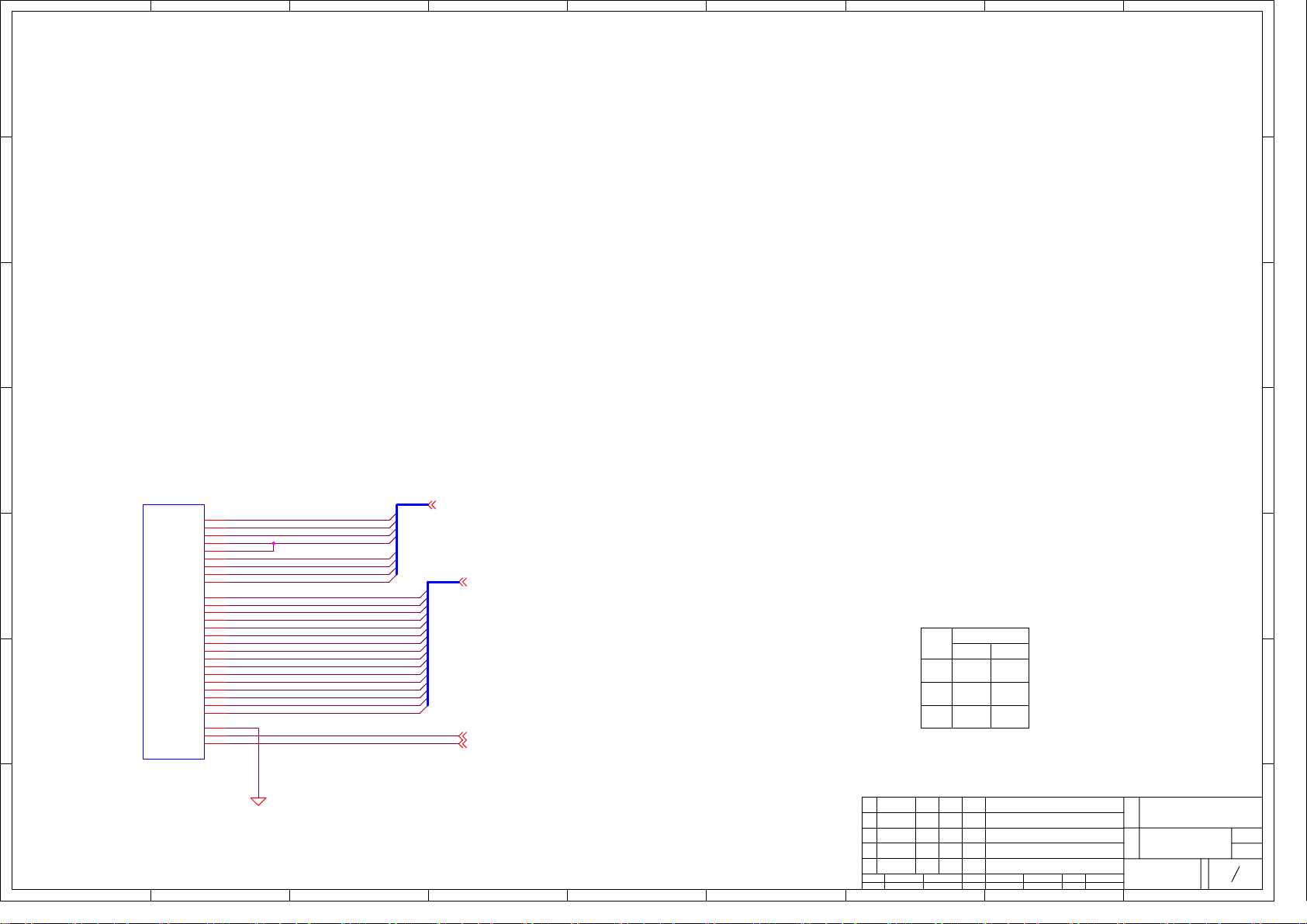

Connector Board I/F

FDD,PRINTER PULL UP

HDD,Pointing CN

Bay CN

BLANK

INTR KB CN

USB POWAUSB CN

RESET/3VIR/IrDA

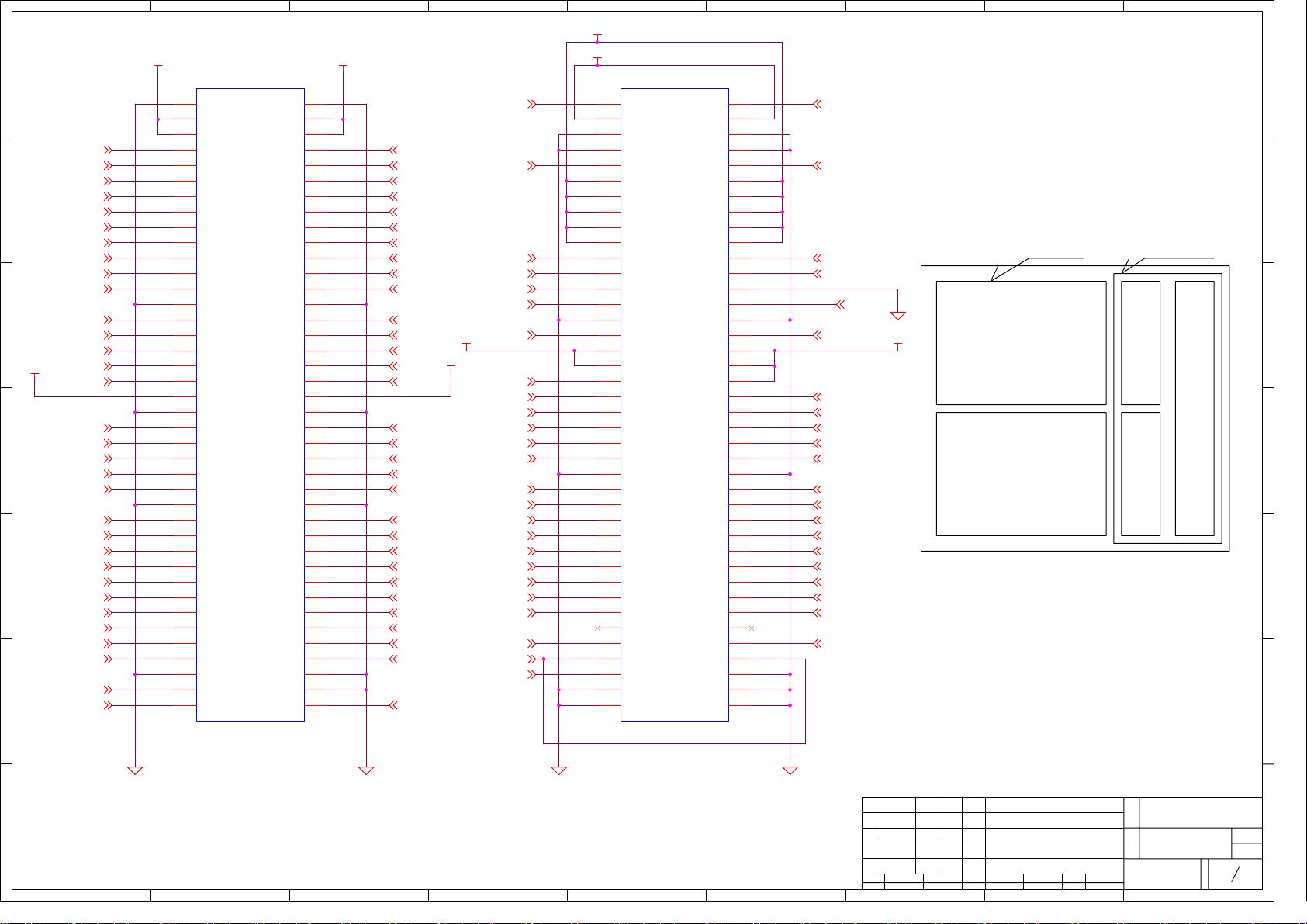

DIMM SLOT

AUDIO CN,Volume

LAN/MODEM CN,PDCA CN

PCMCIA SLOT

DEBUG CN

BLANK

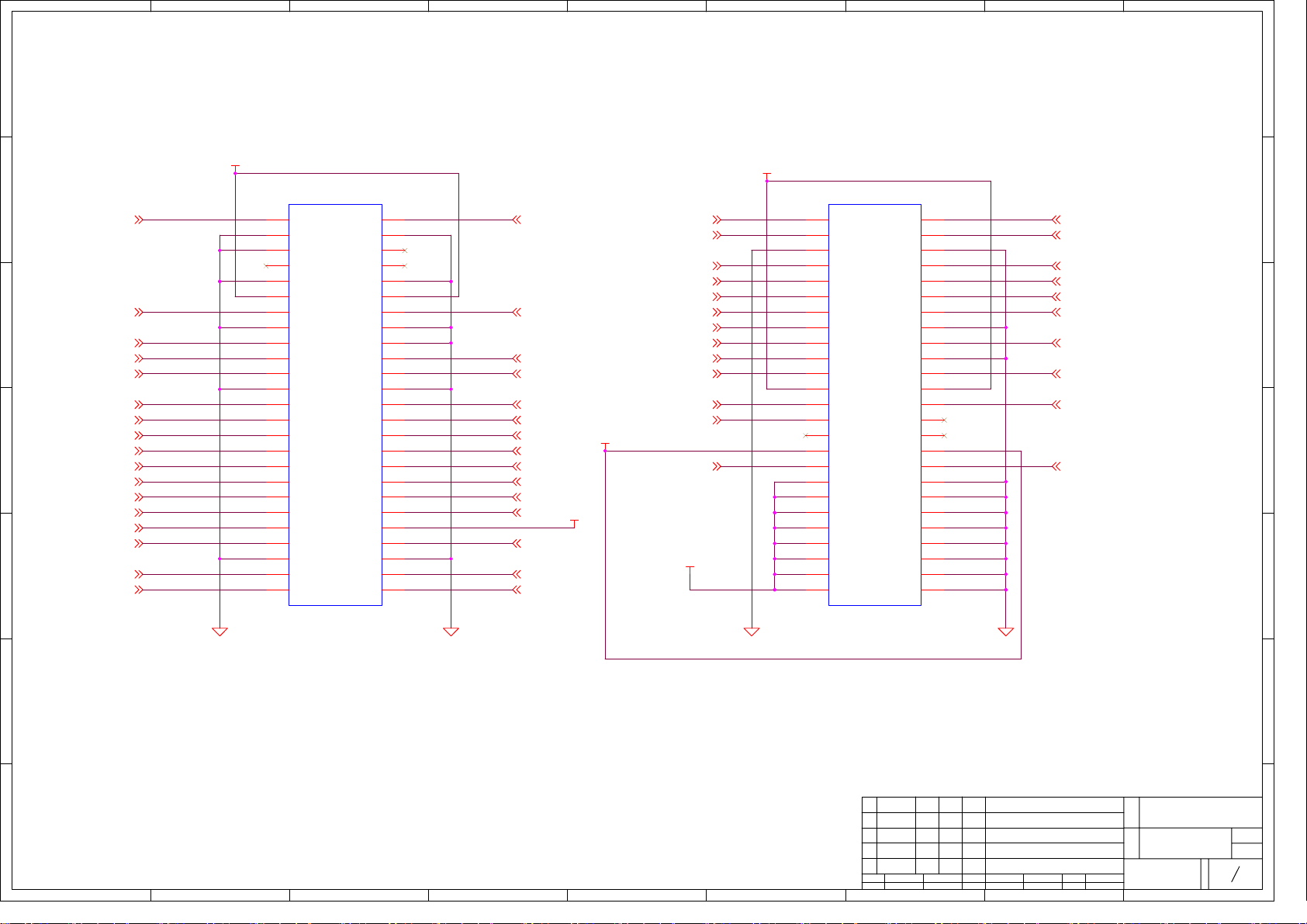

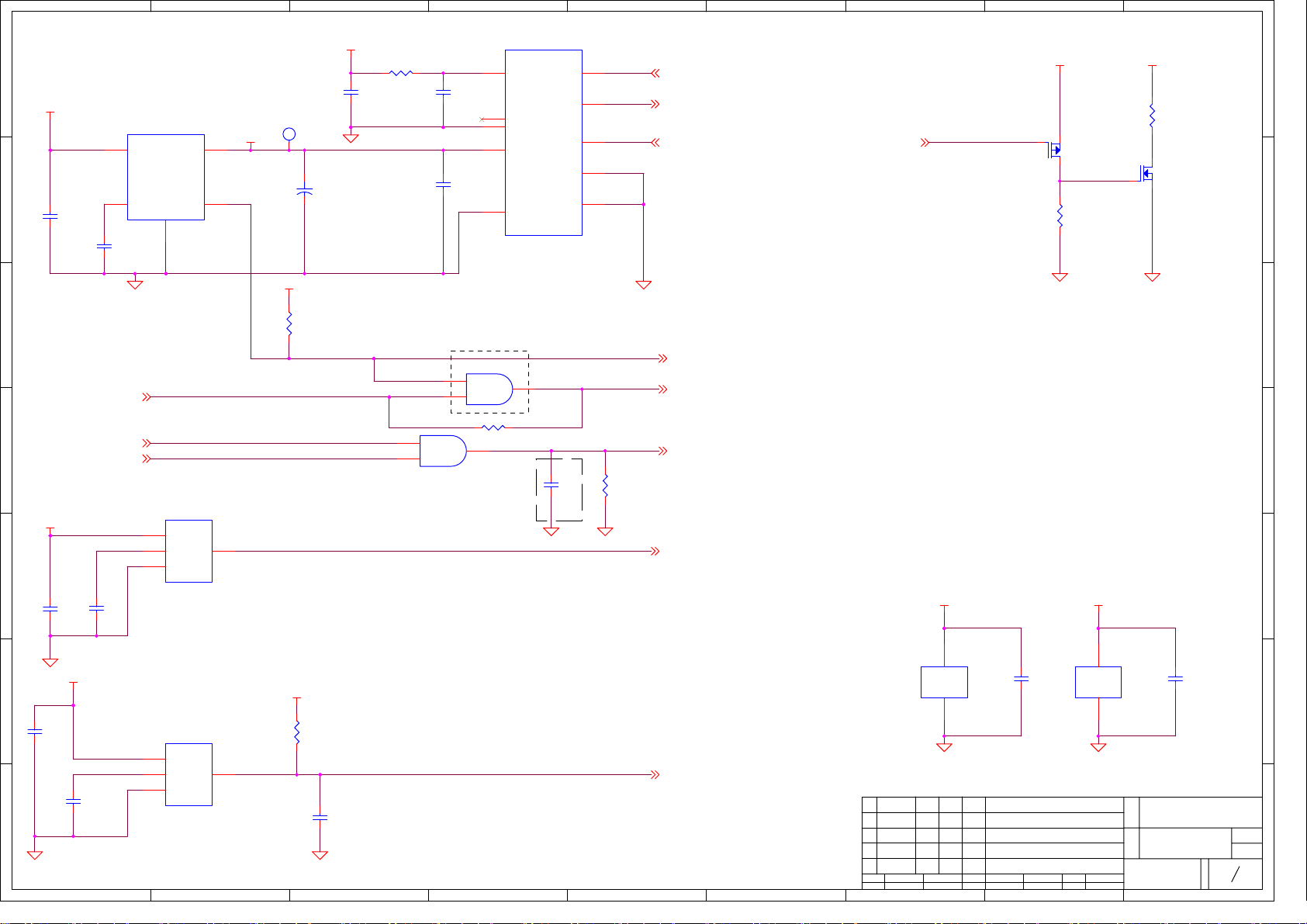

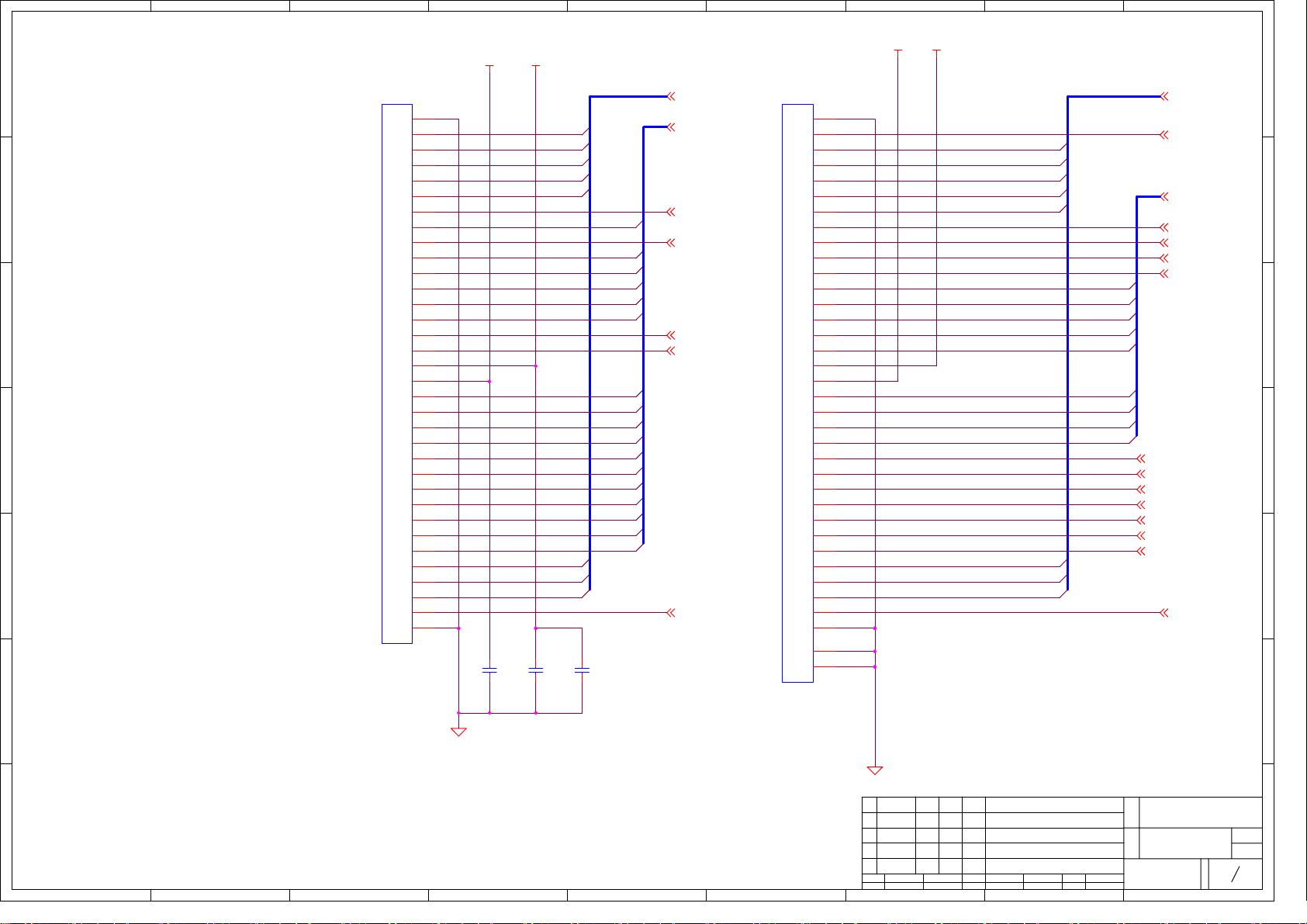

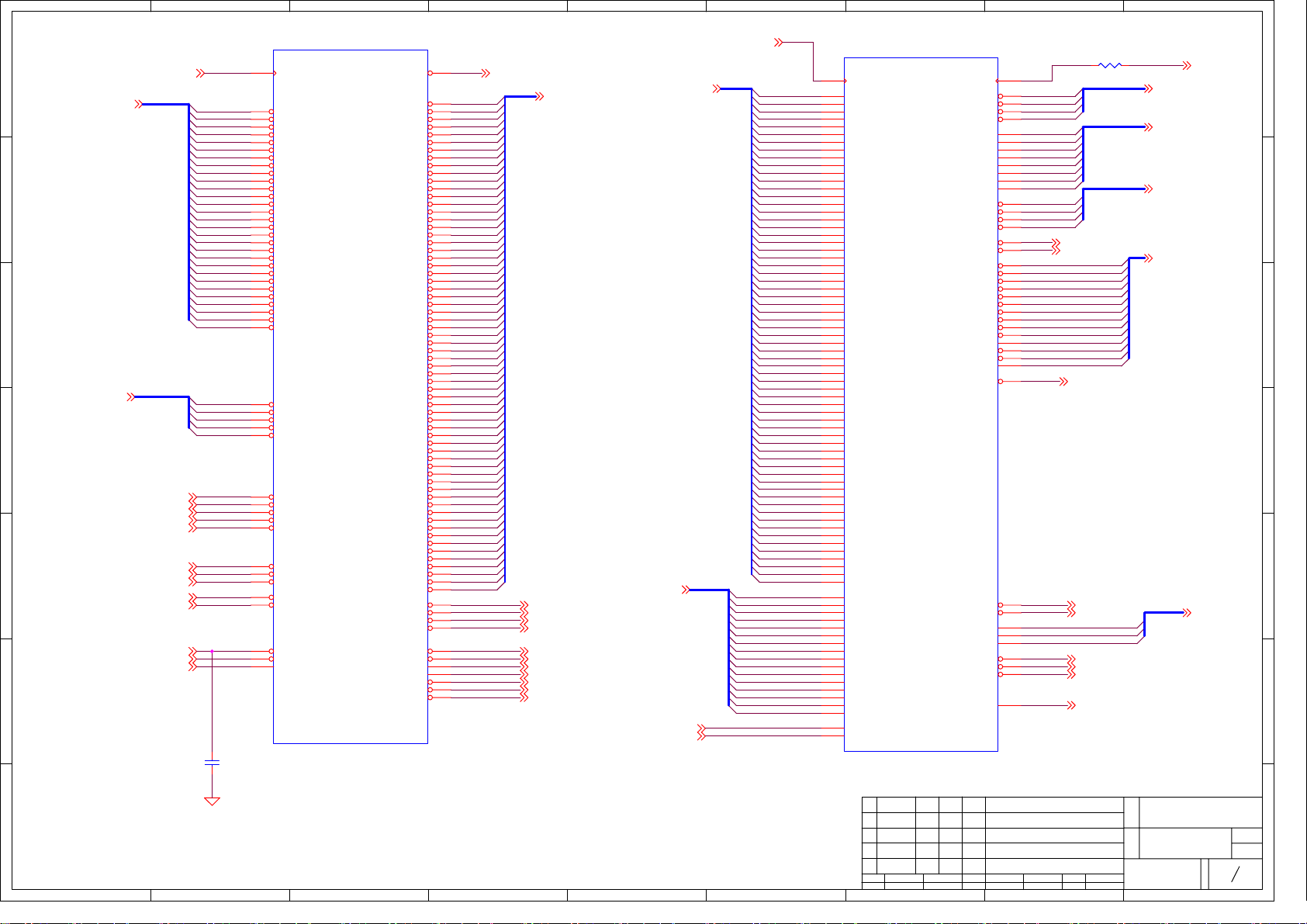

Coppermine-1

Coppermine-2

PASSCON for Coppermine

BLANK

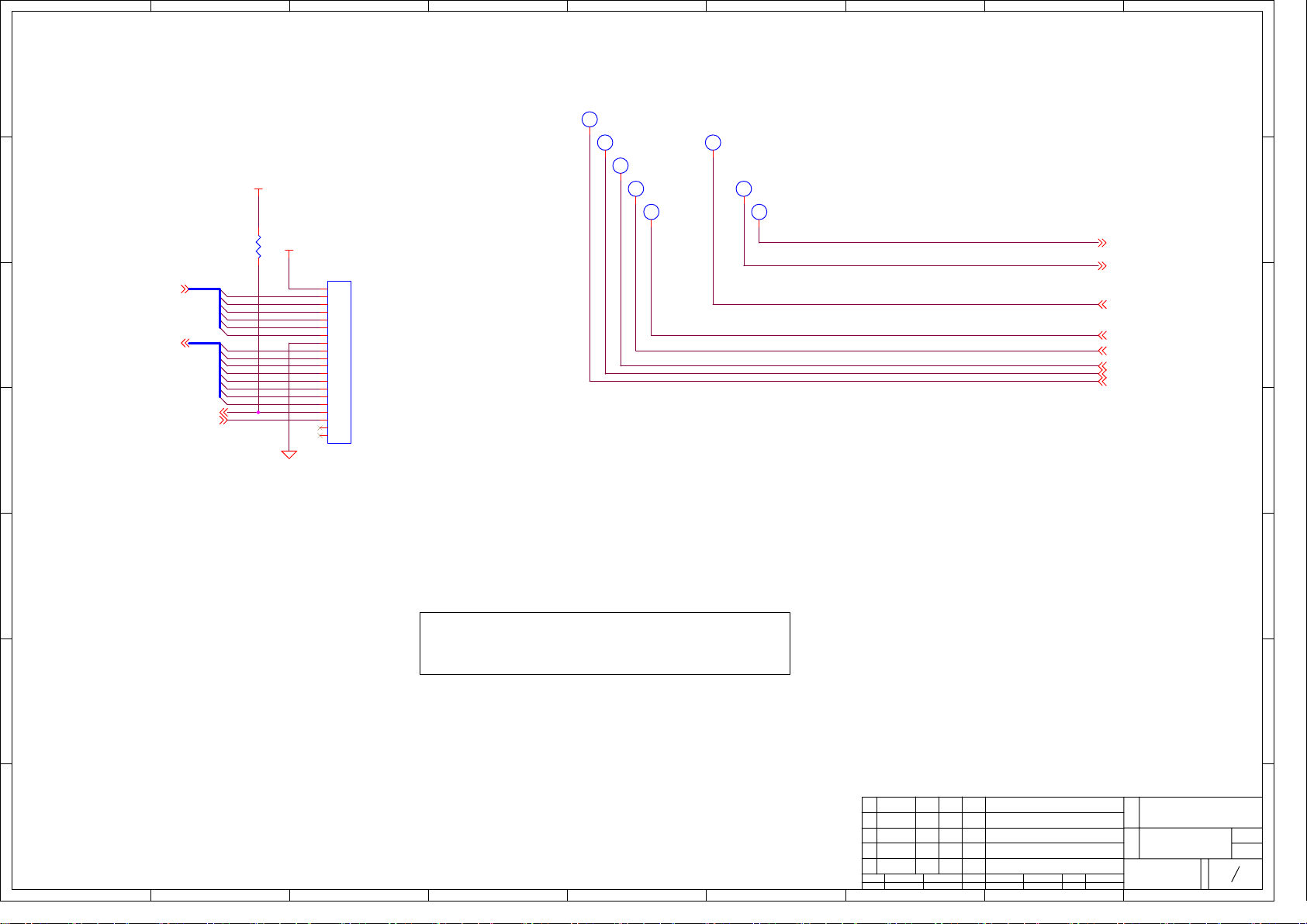

SideBand Signals Pullup

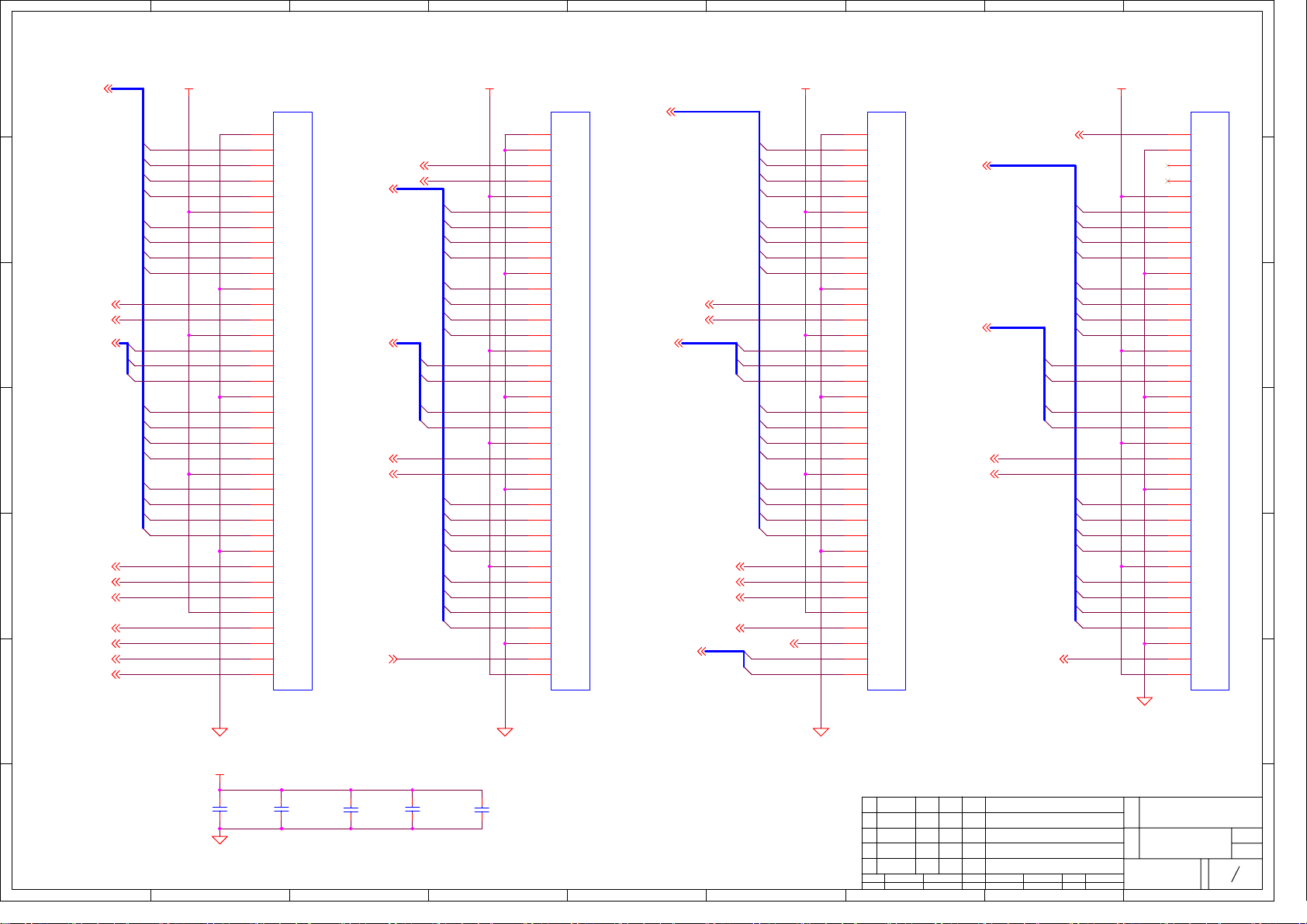

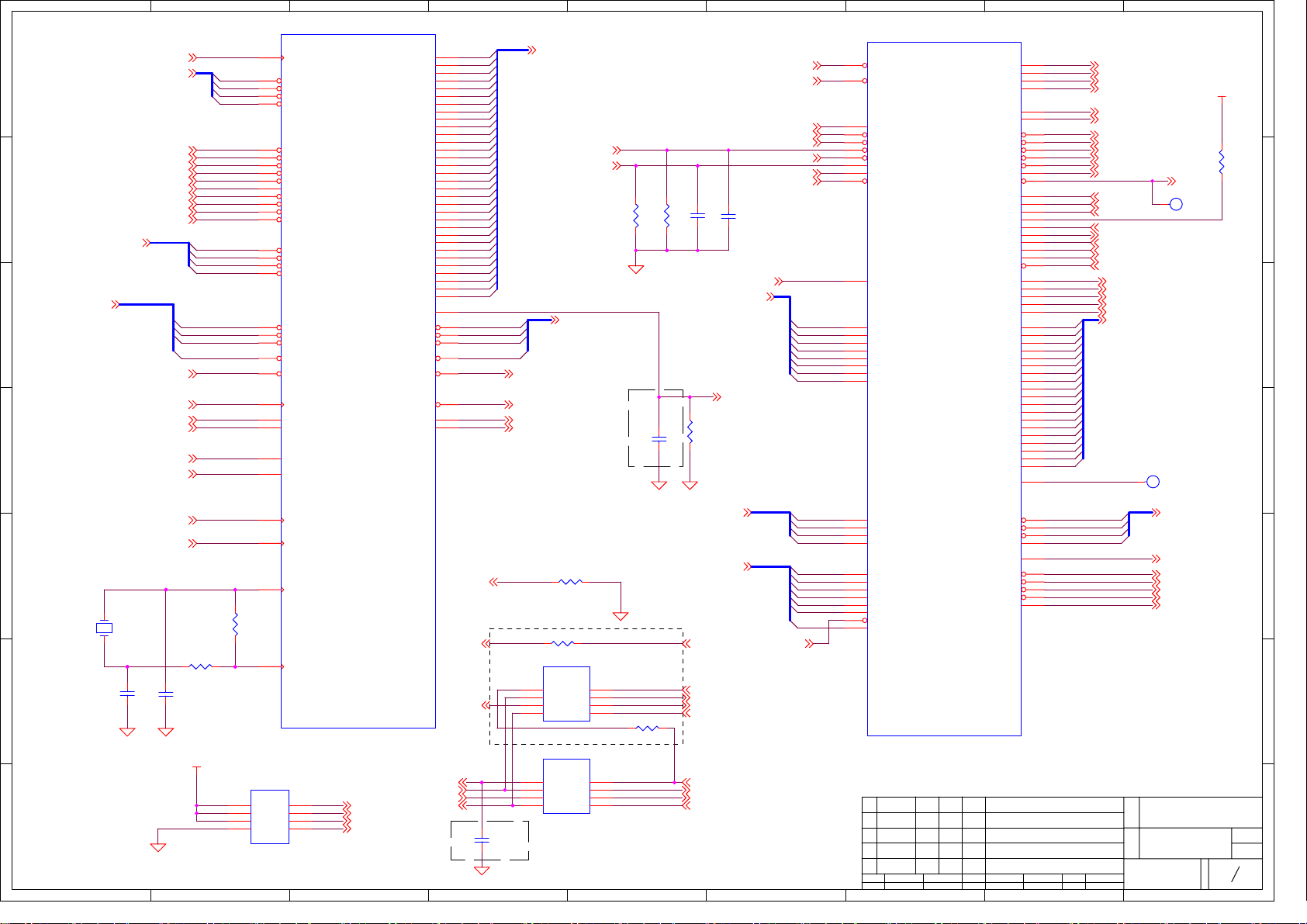

BANISTER -1

BANISTER -2

BANISTER -3

BANISTER Strap Options

SPEED STEP (Geyserville SCL)

28

29

E E

30

31

32

33

34

35

36

37

F F

38

39

40

G G

BLANK

BLANK

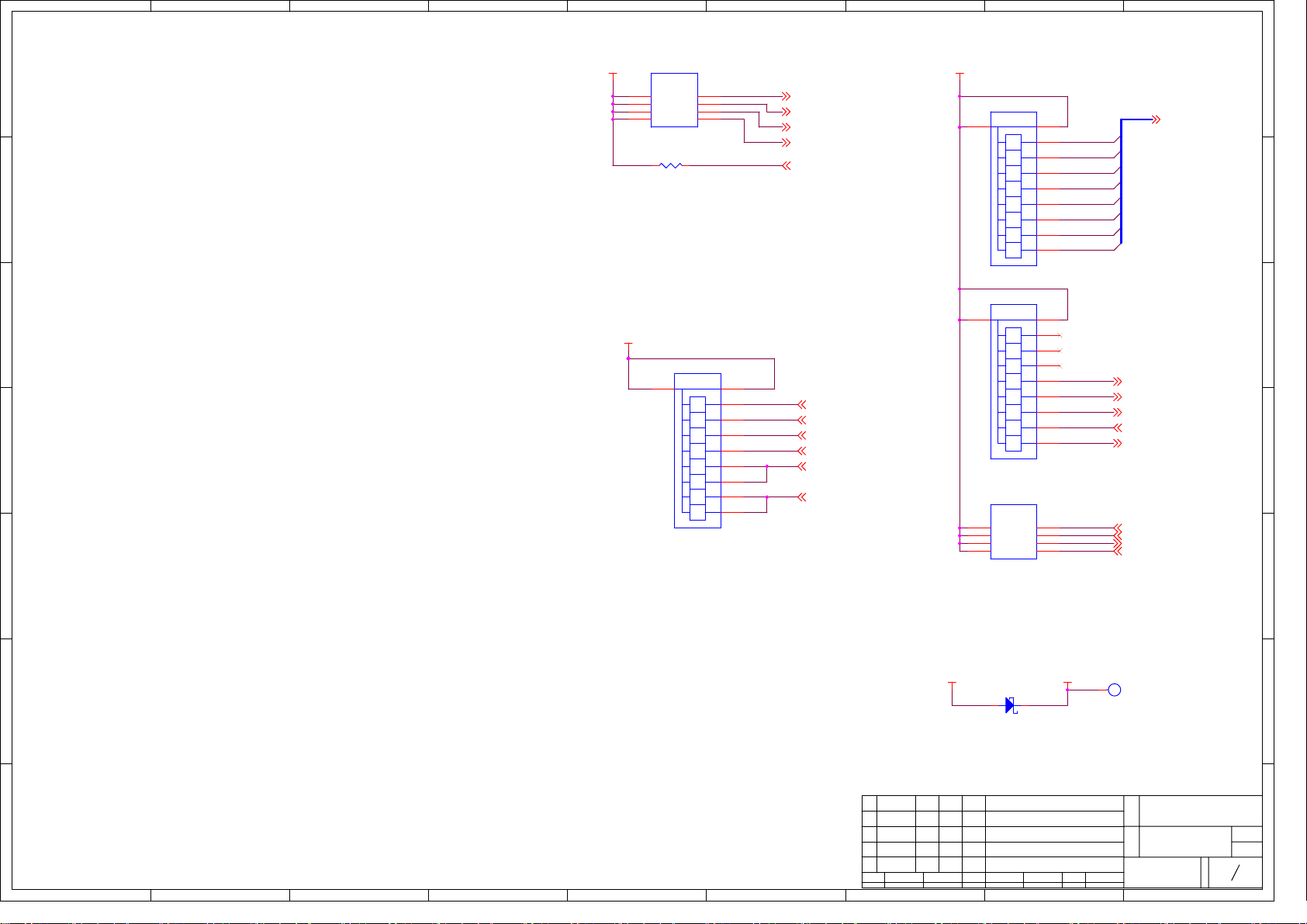

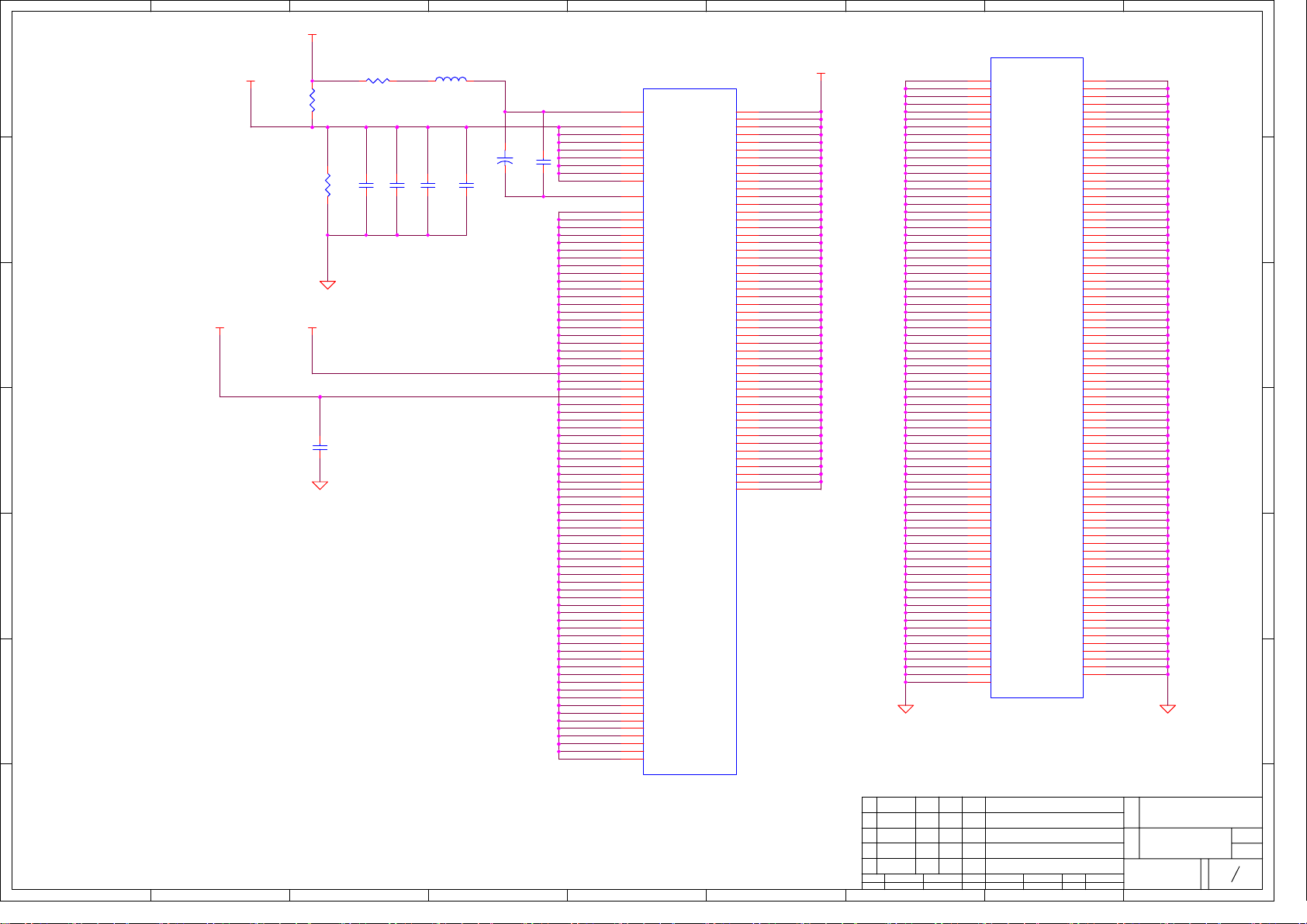

SDRAM DUMPING

CLOCK BUFFER

BLANK

PULL UP for PCI/ISA

BAY Q-SW, IDE PULL-UP

BLANK

BAY ID

VGA(Trident 9525DVD) Config

VGA(Trident 9525DVD) -1

VGA(Trident 9525DVD) -2

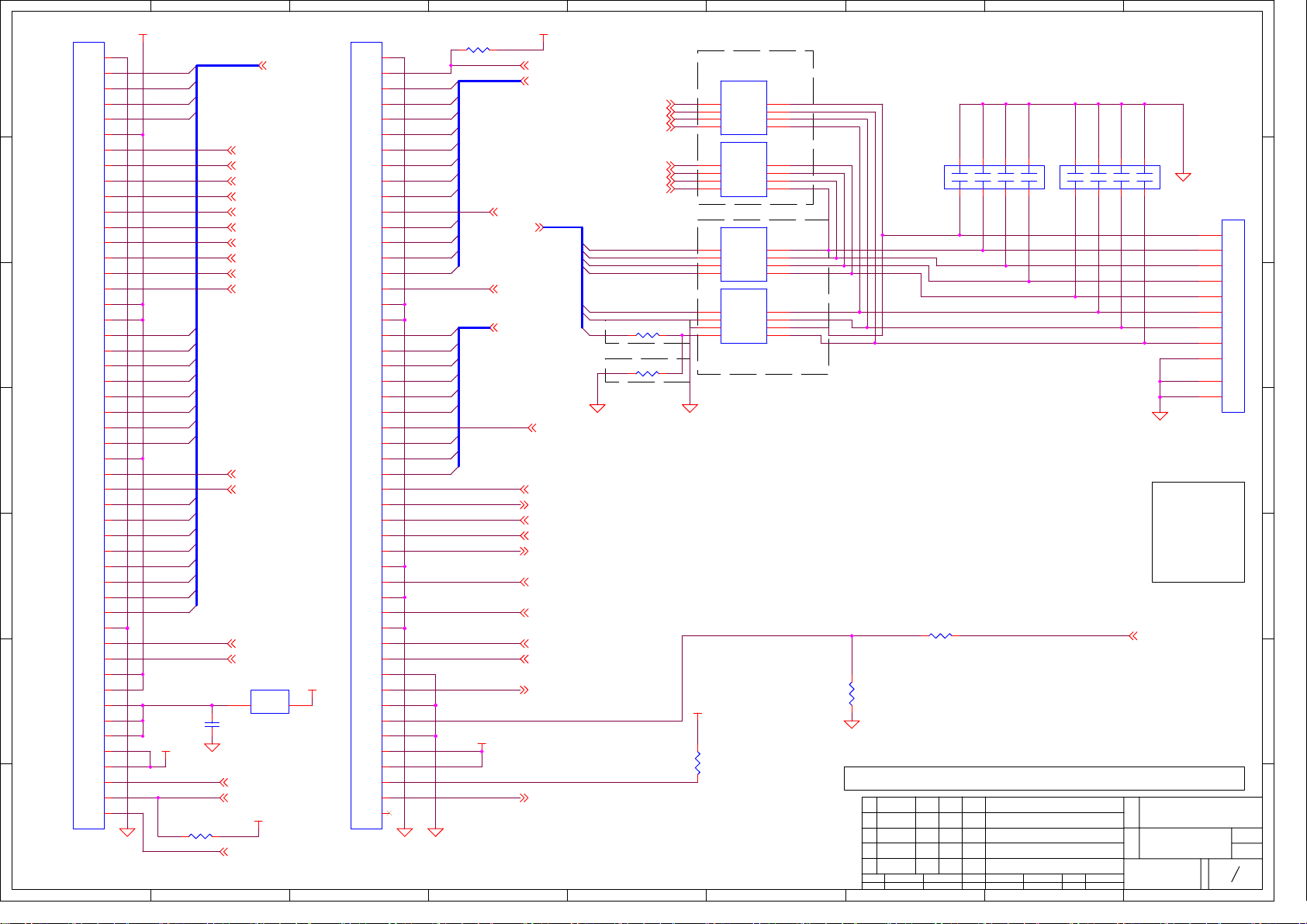

MENU

1

2

PAGE CONTENTS

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

DACVCC LCDVCC

LCD FILTER

ZV-BUF

CARDBUS CTRL -1

CARDBUS CTRL -2

CARDBUS POWER

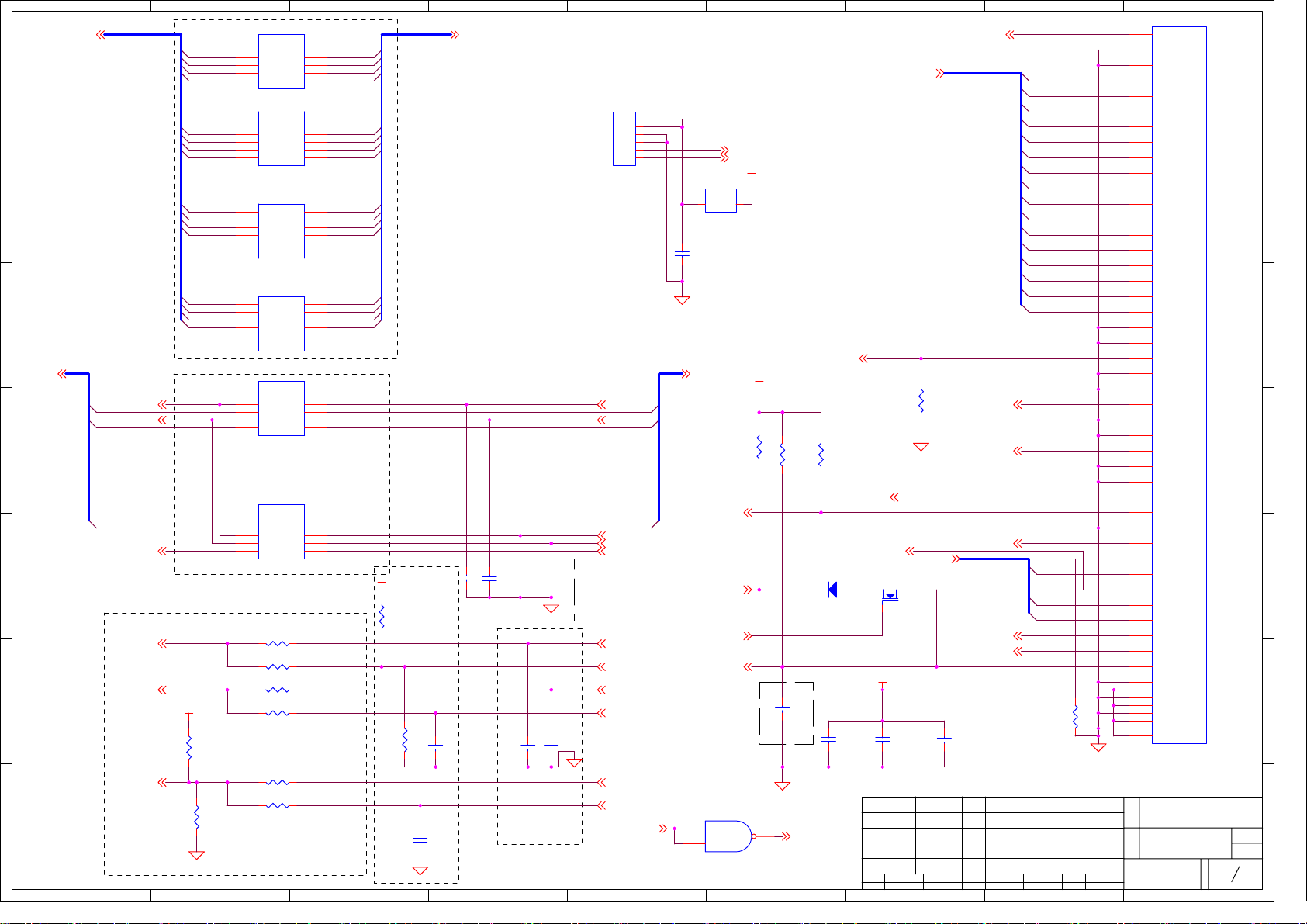

CLOCK GENERATOR

BLANK

IDSEL-QSW / SMBUS SELCTOR

BLANK

SUPER I/O

AC97CODEC(YMF743 / STAC9721T)

AUDIO AMP

AVCC/ AUDIO MISC

BLANK

RING -1

RING -2

KBC

BIOS ROM,MISK

RS232C DRV

3VSTD,RSMRST#,RTCVCC,LLB#

BLANK

BLANK

BLANK

TEMP SENSOR,FAN CONTROL

POW INDEX

DC-IN

BATTx CNVID CONTROL

POW1,BTxDCHG

BTxVOL

ACON,BTxALM

5VSTB,PMUVCC,VREF

SCONTx

PMU

BUS SW

5VSUS,3VSUS

CPUVCC

CHARGER

PLLVCC

5VMAIN,3VMAIN,BAYVCC

BUSVCC

3

D/3

G/1 S/2 G/1 S/2

LM45C

3

4

w/TQFP Card Controller

PCI REQ#/GNT#

REQ0

REQ1

REQ2

REQ3

PCI (ID) SEL ALLOCATION

AD11

AD12

AD13

AD14

AD15

AD18

AD24

AD26

AD27

AD28

AD29

AD30

AD31

PCIINT#

PCIINT0 PCIC-A

PCIINT1

PCIINT2

PCIINT3

21

5

PCIC

LAN/MODEM 2nd

LAN/MODEM 1st

VGA

BANISTER

BANISTER

LAN/MODEM

LAN/MODEM

PCIC

VGA

PCIC-B

LAN/MODEM

VGA

TP0610T

D/3

1SS226

3

21

Revision history

Rev Date

01-00

'99/12/24 Initial

01-01 '99/12/24

特記事項

1)電源用ダイオード RB151L-40Fは通常許可されている、原点方向に1pin(カソード方向)

以外に任意の1角度方向追加を追加許可する B

追加1角度あ、RB151L-40Fで共通である必要がある。(RB151-40Fは3角度選択可能)

2)L11(1),L12(1),L13(1),L14(1)に接続されているノードの配線直下層

~電源層までの間には電源部以外のパターンは配線禁止とする。

但し、直下層にGND1層を入れた場合は、この限りではない B

3)L11(1),L12(1),L13(1),L14(1)の接続されるSOPのトランジスタおよび

RB151L-40Fダイオードは可能な限り同一面にて表層を使用し配

を実施すること。 このような配線により、制約のあるノードを集約できる。

RB415D

HSM2838

3

配線幅条件 (Page1-Page66分抜粋 j

-USBVCC0,USBVCC1 1.5mm

-EXDCIN,DCIN1A(PC1,PC2)端子配線 3mm

-LCDVCC 1.5mm

-BAYVCC 2mm

-PCMVCC0,PCMVCC1 1.5mm

-PCMVPP0,PCMVPP1 1mm

-M3(10)端子配線,M4(1)端子配線 1mm

21

-VREF_GTL 1mm

-CPUBUSVCCT M6~M8間 1mm

それ以外は、内層分割指定

-DACVCC 1mm

-AVCC,M31(1)端子配線,Q9(4)端子配線 1.5mm

-3VSTD

,M87(5)端子配線,Q15(4)端子配線 1.5mm

-FANVCC,Q23(4)端子配線 0.5mm

指定以外の配線は、最低でも1A

1mm幅とする。 ミニバイアは1個0.3Aが限界とする B

部品実装に関する緩和条件

-部品搭載が困難な場合、以下ファンクションは一括削除を許可する。

削除部品:M29,C450,R322,R323,M18,D57,R762 (ZV Audio機 \)

版 年 月日設計 調査 承認 変 更 内

設計

6

00.05.04

小中

7

容

渡部

ٛ

ٛ

ٛ

ٛ

ٛ

ٛ

名

ANISE-E2 04

称

図

C1CP051300-X4

番

福田

富士通株式会社

承認調査

8

ペ

|

181

ジ

9

提出先

Page 2

1

2

3

4

5

6

7

8

9

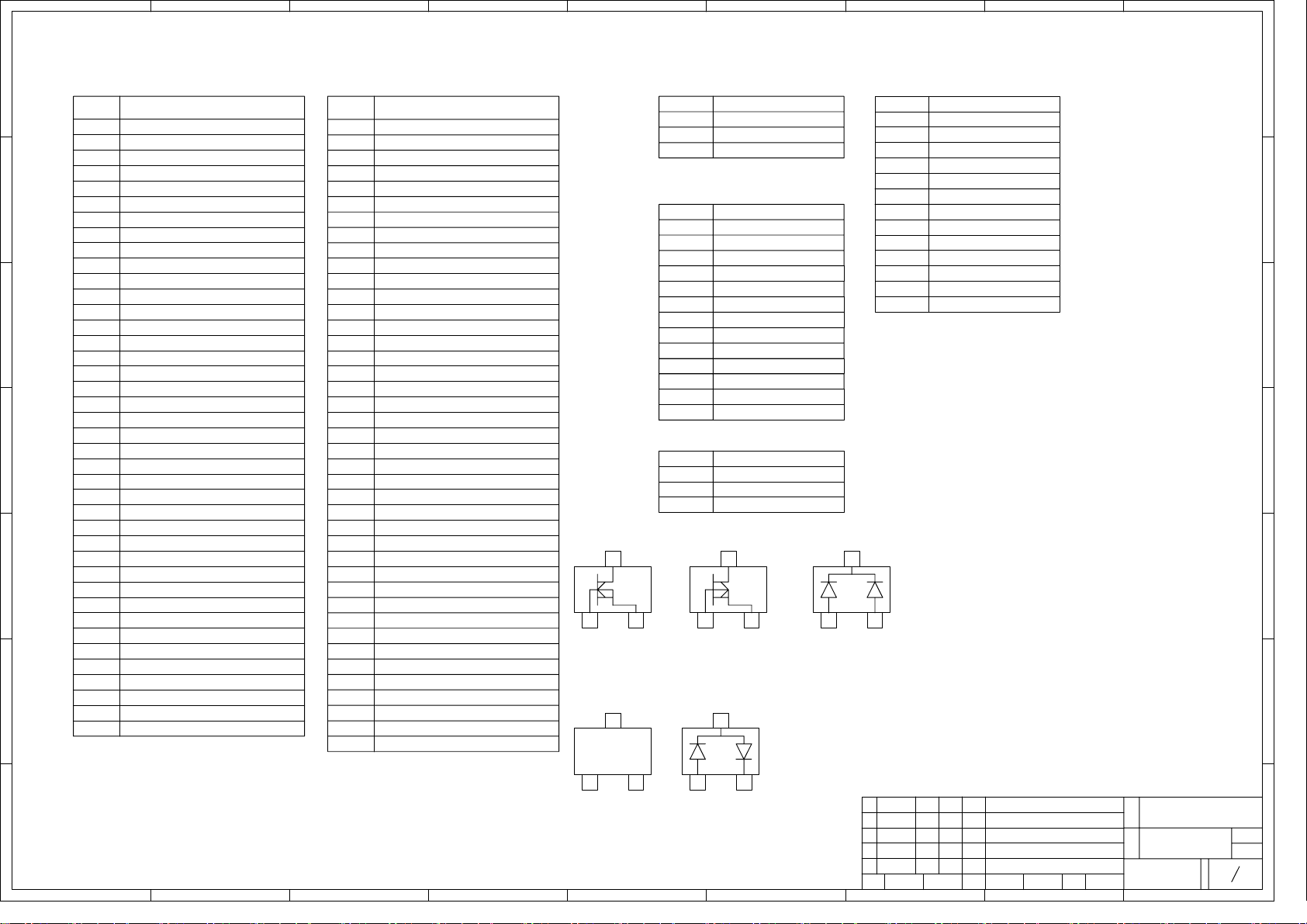

Configration List

A A

B B

C C

D D

E E

F F

名

ANISE-E2 04

G G

BLANK

版 年 月日設計 調査 承認 変 更 内

1

2

3

4

5

6

設計

7

容

承認調査

8

称

図

C1CP051300-X4

番

富士通株式会社

ペ

|

281

ジ

9

提出先

Page 3

1

2

3

4

5

6

7

8

9

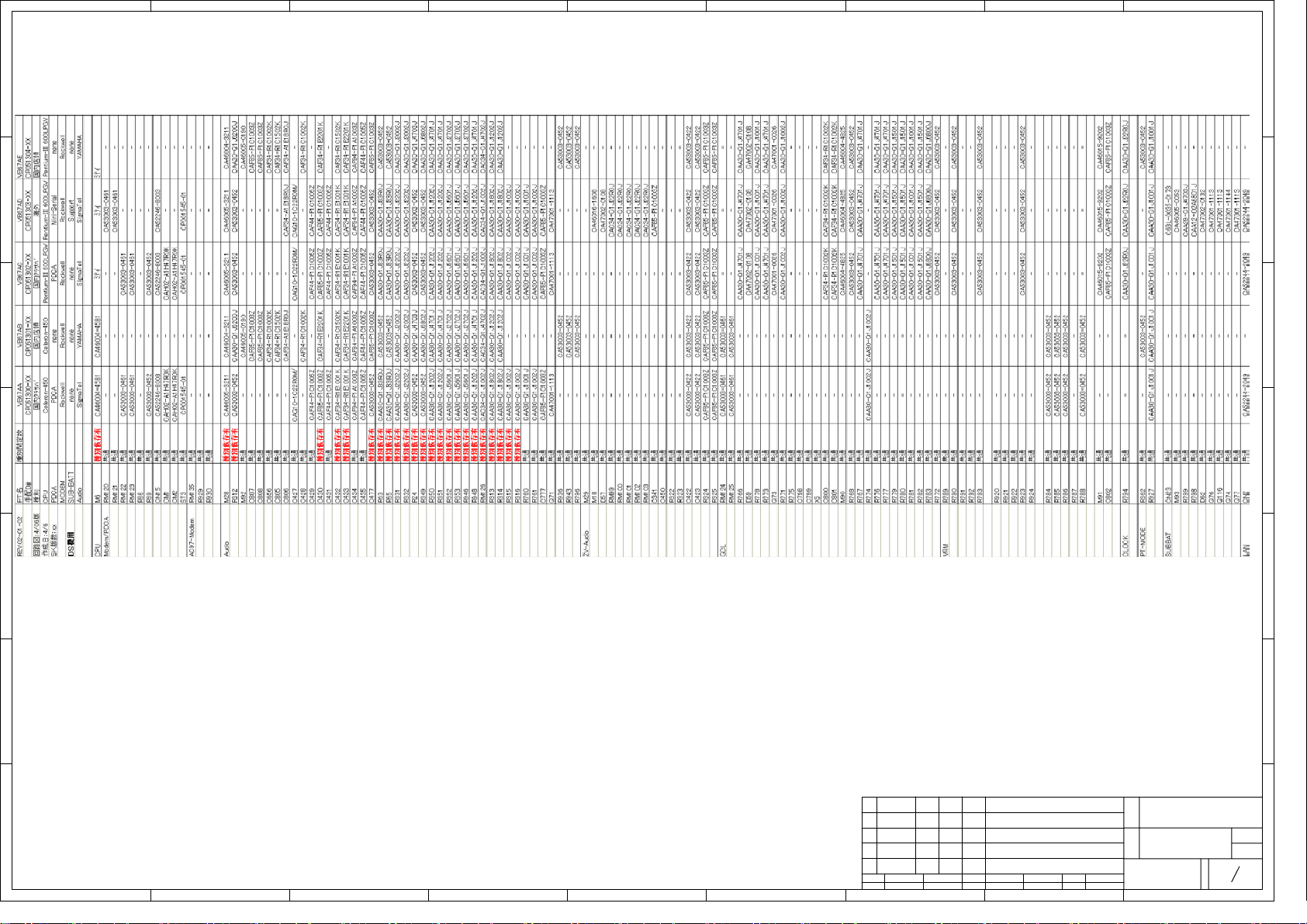

A A

B B

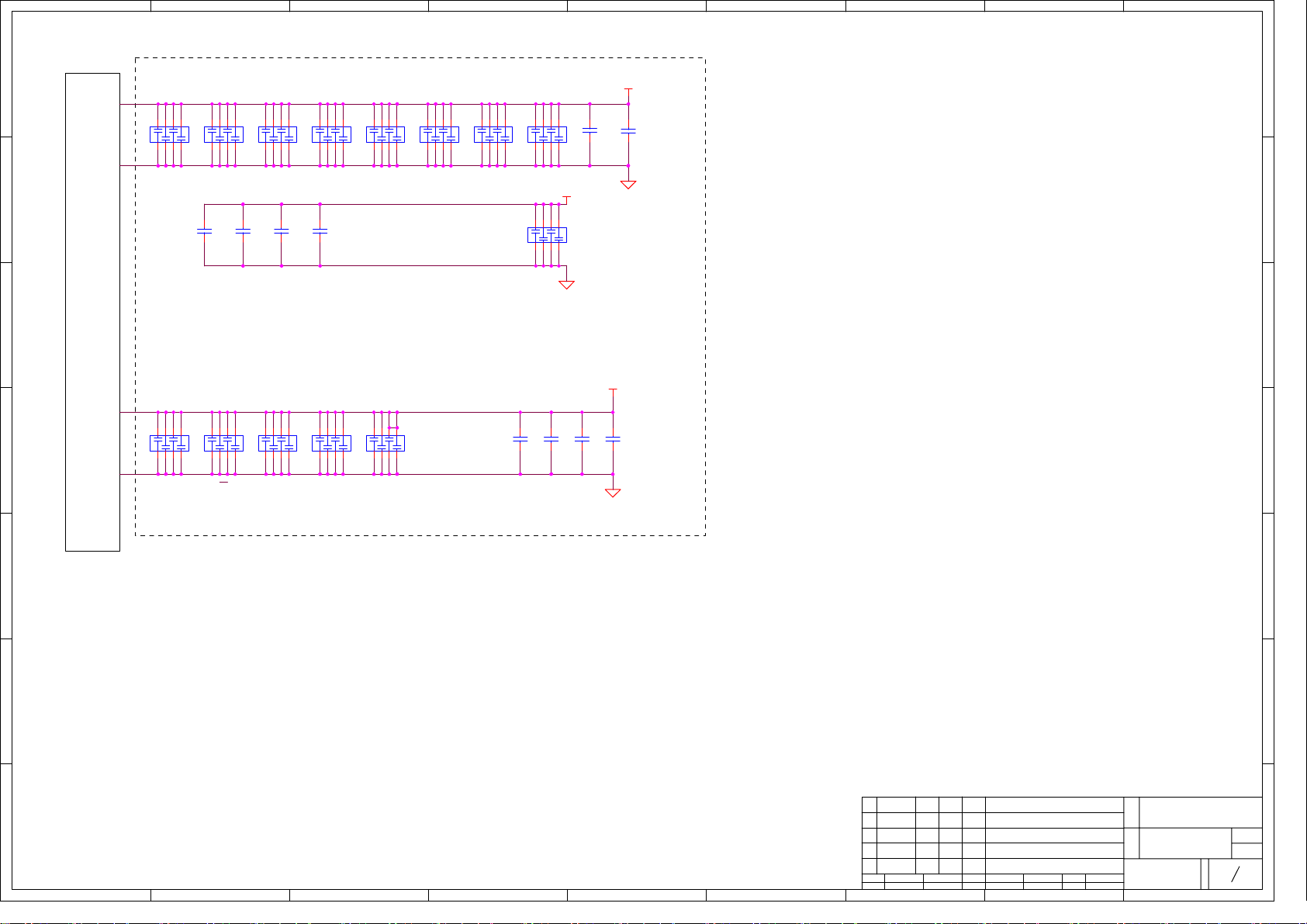

本部品は電波対策用の部品であり、基板の周囲で電源とグランド ヤに挿入するフィルタである。

特に電源の種別は未接続状態にしているので、適宜、配置する 齒鰍ノより電源を設定すること

C C

ٛ

ٛ

3VSUS

1 2

5VSUS

100pF 25V

C23

3VSUS

1 2

3VMAIN

100pF 25V

C24

3VSUS

3VMAIN 3VMAIN

12

100pF 25V

C25

3VSUS

1 2

100pF 25V

C27

D D

5VMAIN

本コンデンサは電源/グランド層にして発生する島プレーン同士 凰レ続するためにものである。

ٛ

1 2

AVCC

5VSUS

100pF 25V

C28

1 2

5VMAIN

100pF 25V

C29

AVCC

12

5VMAIN

C30

100pF 25V

AVCC

12

5VMAIN

100pF 25V

C31

5VMAIN

1 2

3VSUS

100pF 25V

C32

5VMAIN

12

3VSUS

C34

100pF 25V

3VSUS

1 2

5VMAIN

C36

100pF 25V

3VMAIN

1 2

3VSUS

100pF 25V

C37

そのため、上記のような島構成であれば、ポイントとなる個所にコンデンサを配置するようにする

1 2

GND1

3VMAIN

100pF 25V

C41

r100pF 25V

100pF 25V

1 2

CPUBUSVCC

CPUCOREVCC

1 2

C54

1 2

C49

100pF 25V

C42

r100pF 25V

5VSUS

CPUCOREVCC

1 2

C55

1 2

6

C43

100pF 25V

r100pF 25V

5VSUS

AUDIOGND

3VMAIN

3VMAIN

12

100pF 25V

C44

12

C56

Reserve

版 年 月日設計 調査 承認 変 更 内

設計

12

3VSUS

100pF 25V

C45

3VMAIN

100pF 25V

1 2

7

3VSUS

C46

5VSUS

GND1GND1

12

100pF 25V

100pF 25V

GNDA

5VMAIN

C47

C57

1 2

容

3VSUS

GNDA

1 2

8

3VMAIN

100pF 25V

C48

12

GND1

承認調査

100pF 25V

C58

GND1

12

100pF 25V

C59

GNDA

名

ANISE-E2-04

称

図

C1CP051300-X4

番

富士通株式会社

ペ

|

381

ジ

9

提出先

CPUBUSVCC

3VMAIN

100pF 25V

C40

1 2

r100pF 25V

C51

1 2

AUDIOGND AUDIOGND

GND1 GND1 GND1

100pF 25V

C35

C38

100pF 25V

1 2

1 2

1 2

3VMAIN

100pF 25V

C39

100pF 25V

1 2

3VSUS

AUDIOGND

C33

E E

また、クロックを、島をまたいで引く場合には、クロック信号の近くにコンデンサを配置すること

また、レイアウトに関連するので、未接 ア状態にしている。

ٛ

ٛ

CLK信

CPUCOREVCC

F F

3VSUS

1 2

100pF 25V

C53

100pF 25V

1 2

C50

G G

EMI RC

1

2

3

4

5

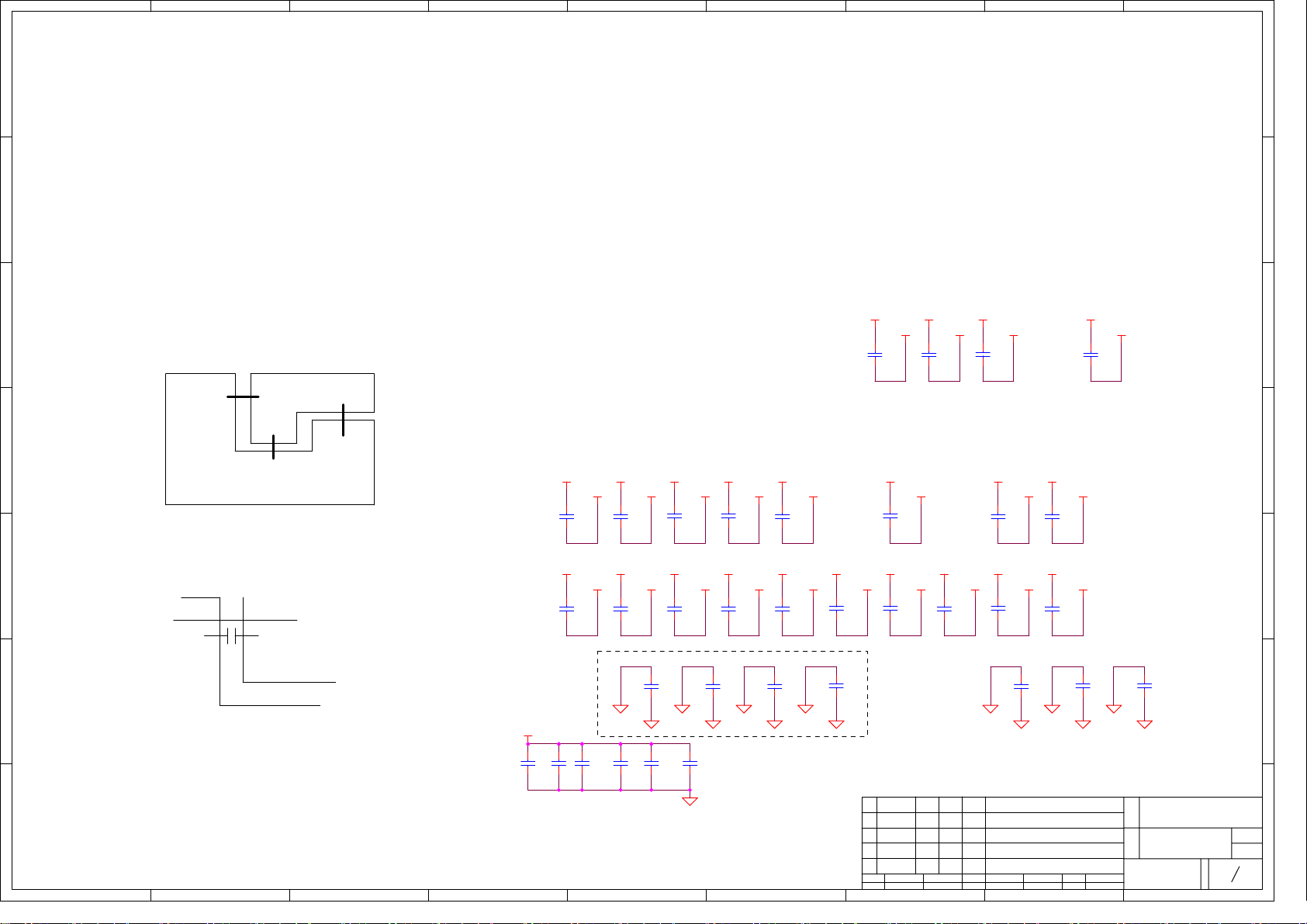

Page 4

1

A A

2

3

4

FL1

<FILTER>

BLM41P600S

EXDCIN

12

※MAX 3A

5

6

7

8

9

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

PC4

5VMAIN5VMAIN USBVCC0

PRD2 5,51

PRD3 5,51

PRD5 5,51

PRD7 5,51

PBUSY 5,51

PSLCT 5,51

DDCCLK 4,41

DDCDATA 4,41

VGAVS 4,41

VGAHS 4,41

DKUSBP0+ 10

KMDATA 58

KMCLOCK 58

LANTXD-

LANTXD+

5VMAIN

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

PC2

CN1B

PINIT#

PSLIN#

PRD4

PRD6

PACK#

PPE

VGAGND

VGAB

VGAG

VGAR

VGAGND

USBVCC0

USB0-

USBGND

KDATA

KCLOCK

5VMAIN

N.C

N.C

LANRXD-

LANRXD+

N.C

N.C

PRPATCH#1

GND1

DCIN1RTN

PRD2

PRD3

PRD5

PRD7

PBUSY

PSLCT

VGAGND

DDCCLK

DDCDATA

VGAVS

VGAHS

USBVCC0

USB0+

USBGND

MDATA

MCLK

5VMAIN

N.C

N.C

LANTXD-

LANTXD+

N.C

N.C

SYSDET#2

GND1

DCIN1RTN

P-R_CN_AN

CN1A

PC1

DCIN

1

B B

FSIDE#5,51

FRDDT#5,51

C C

D D

E E

FMODE#56

FINDEX#5,51

FTRK0#5,51

FSTEP#5,51

FMOTOR#5,51

RIA14,60

CTSA14,60

RTSA14,60

DSRA14,60

PAFD#5,51

PPERR#5,51

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

GND1

SYSDET1

GND1

N.C

N.C

FSIDE#

GND1

FRDDT#

GND1

FMODE#

FINDEX#

5VMAIN

FTRK0#

GND1

FSTEP#

FMOTOR#

GND1

RIA

CTSA

RTSA

DSRA

GND1

GND1

PAFD#

PPERR#

PRPATCH#2

DCIN

GND1

GND1

FDATCH#

GND1

FWD#

GND1

FDSELO#

FWP#

5VMAIN

FWG#

GND1

FDIR#

FDCHG#

GND1

DTRA

SOUTA#

SINA#

DCDA

GND1

PSTB#

PRD0

PRD1

P-R_CN_AN

PC3

51

52

53

54

N.C

55

N.C

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

PRCD1# 56

FDATCH# 57

FWD# 5,51

FDSELO# 57

FWP# 5,51

FWG# 5,51

FDIR# 5,51

FDCHG# 5,51

DTRA 14,60

SOUTA# 14,60

SINA# 14,60

DCDA 14,60

PSTB# 5,51

PRD0 5,51

PRD1 5,51

PINIT#5,51

PSLIN#5,51

PRD45,51

PRD65,51

PACK#5,51

PPE5,51

VGAB4,40

VGAG4,40

VGAR4,40

DKUSBP0-10

KDATA58

KCLOCK58

LANRXD-

LANRXD+

PRCD2#56

※MAX 3A ※MAX 3A

GND1 GND1 GND1 GND1

注)LAN信号線(LANTXD+,LANTXD-,LANRXD+,LANRXD-)は A

LANTXD+ - LANTXD- , LANRXD+ - LANRXD- をそれぞ

対で配線し、対の距離は、最低配線距離、TXD,RXD間はその

5倍の距離を離すこと。

F F

G G

また、この4本を通している上下2層は配線領域から横方向に

3mmを内層クリアとする。

上下3層目は、GND1にて、配線の上をGND1でガードすること。

但し、ガードも含め、本信号線のスルホールおよび、配線から3mm

以内は、絶縁距離として確保し、いかなる信号線も3mm以下の

距離になってはならない。

但し、例外条件として、上下3層目は本信号と完全に直行する

場合のみ他の信号線の布線を許可する。(必要最低限に抑える

こと)

注)FIL1 - P-R_CONN間は、コネクタ引出し部 スルホール各3 ツ

計6個で引き出し、3mm以上のパターン幅、最短距離でFIL1 ヨ

接続すること。

EXDCINは3mm以上のパターン幅で布線することが要求される B

ٛ

ٛ

ٛ

ٛ

ٛ

DOCKING/LAN CONNECTOR

1

2

3

4

5

6

CN2

1

TX+

2

TX-

3

RX+

4

TIP

5

RING

6

RX-

7

RJ45-7

8

RJ45-8

LAN-RJ

版 年 月日設計 調査 承認 変 更 内

設計

LANTXD+

LANTXD-

LANRXD+

LANRXD-

容

7

名

ANISE-E2 04

称

図

C1CP051300-X4

番

承認調査

富士通株式会社

8

ペ

|

481

ジ

9

提出先

Page 5

1

2

3

4

5

6

7

8

9

A A

5VMAIN

B B

INTMICIN13

VGAHS3,41

C C

VGAR3,40

VGAG3,40

VGAB3,40

SLCDC074

SLCDC274

SLCDS174

D D

E E

SLCDS374

SLCDS574

SLCDS774

LCDCL#56,59

SUSSW#57,59

RSMRST#24,61

OZSMBCLK41

P042

P242

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

CN4A

MIC

USBG

USBP0-

USBVCC0

USBP1-

5VMAIN

VGAHS

GND1

VGAR

VGAG

VAGB

GND1

SLCDC0

SLCDC2

SLCDS1

LCDS3

LCDS5

LCDS7

LCDCL#

SUSSW#

RSMRST#

OZSMBCLK

GND1

P0

P2

GNDA

USBG

USBP0+

USBVCC0

USBP1+

5VMAIN

VGAVS

GND1

VGAGND

DDCDATA

DDCCLK

GND1

SLCDC1

SLCDS0

SLSDS2

LCDS4

LCDS6

LCDS8

MAINON#

SMBALERT#

3VSTD

OZSMBDATA

GND1

Connector_BD2

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

P1

75

P3

INTMICRTN 13

VGAVS 3,41

DDCDATA 3,41

DDCCLK 3,41

SLCDC1 74

SLCDS0 74

SLCDS2 74

SLCDS4 74

SLCDS6 74

SLCDS8 74

MAINON# 57,74

SMBALERT# 24

OZSMBDATA 41

P1 42

P3 42

P442

P642

P842

P1042

P1242

P1442

P1642

P1742

FLM42

LP42

EBLEN56

BKLVOL56

POW2

VGAID138,56

3VSTD

DCIN

LCDVCC

CN4B

26

P4

27

P6

28

GND1

29

P8

30

P10

31

P12

32

P14

33

P16

34

P17

35

FLM

36

LP

37

LCDVCC

38

EBLEN

39

BKVOL

40

41

42

43

44

45

46

47

48

49

50

TPNCLK

POW2

VGAID2

DCIN

DCIN

DCIN

DCIN

DCIN

DCIN

DCIN

DCIN

LCDIDSYS1

P5

P7

GND1

P9

P11

P13

P15

GND1

SHFCLK

GND1

M./DE

LCDVCC

LCDEN

TPNLDAT

POW2

VGAID1

DCINRTN

DCINRTN

DCINRTN

DCINRTN

DCINRTN

DCINRTN

DCINRTN

DCINRTN

Connector_BD2

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

P5 42

P7 42

P9 42

P11 42

P13 42

P15 42

SHFCLK 42

M/DE 42

LCDEN 40,41

VGAID0 38

GND1 GND1 GND1 GND1

F F

名

ANISE-E2 04

G G

Connector Board I/F

1

版 年 月日設計 調査 承認 変 更 内

2

3

4

5

6

設計

7

容

承認調査

8

称

図

C1CP051300-X4

番

富士通株式会社

ペ

|

581

ジ

9

提出先

Page 6

1

2

3

4

5

6

7

8

9

5VMAIN

RM1

A A

FLOPPY関連信号のPULL UP

上記の集合抵抗および抵抗はSUPER

I/O(FDC37N769)

の近くに配置配線すること。

FLOPPY control signals

Above register array and register must be placed near

super I/O chip (FDC37N769) and routed with short trace from it.

ARRAY

1

2

3

4

1Kx4 1/32W 5%

R26

10K 1/16W 5%

8

7

6

5

FRDDT# 3,51

FTRK0# 3,51

FDCHG# 3,51

FWP# 3,51

FINDEX# 3,51

B B

C C

D D

5VMAIN

RM4

ARRAY

680x8 1/20W 5%

109

1

2

3

4

5

6

7

8

FSIDE# 3,51

FSTEP# 3,51

FDIR# 3,51

FMOTOR# 3,51

FWD# 3,51

FWG# 3,51

E E

5V669

RM2

ARRAY

109

1

2

3

4

5

6

7

8

10Kx8 1/20W 5%

RM3

ARRAY

109

1

2

3

4

5

6

7

8

10Kx8 1/20W 5%

RM5

ARRAY

8

7

6

5

4.7Kx4 1/32W 5%

PARARELL関連信号のPULL

UP

1

2

3

4

PRD0

PRD1

PRD2

PRD3

PRD4

PRD5

PRD6

PRD7

PACK# 3,51

PBUSY 3,51

PPE 3,51

PSLCT 3,51

PPERR# 3,51

PSTB# 3,51

PAFD# 3,51

PINIT# 3,51

PSLIN# 3,51

PRD[0:7] 3,51

5VMAIN 5V669

D1

F F

2 1

RB521S-30

G G

FDD,PRINTER PULL UP

1

版 年 月日設計 調査 承認 変 更 内

2

3

4

5

6

設計

7

容

8

TP1

5V669

名

ANISE-E2 04

称

図

C1CP051300-X4

番

承認調査

富士通株式会社

提出先

ペ

|

681

ジ

9

Page 7

1

PDD[0:15]23,35

PDD[0:15]

A A

B B

C C

PDA[0:2]23

PDA[0:2]

PDCS3#23

PDCS1#23

D D

PDDREQ23

E E

M8

Banisterの元端子直裏面に搭載すること

PDIOR#23

PDIOW#23

F F

PIORDY23

G G

HDD,POINTING CN

1

2

このモジュール間でのピンスワップ可

PDD3

PDD2

PDD1

PDD0

PDD4

PDD5

PDD6

PDD7

PDD15

PDD8

PDD10

PDD9

PDD11

PDD12

PDD13

PDD14

このモジュール間でのピンスワップ可

PDA2

PDA0

PDA1

5VMAIN

R31

1K 1/16W 5%

R750

2K 1/16W 5%

GND1

RM7

ARRAY

1

2

3

4

22x4 1/32W 5%

RM8

ARRAY

1

2

3

4

22x4 1/32W 5%

RM9

4

3

2

1

22x4 1/32W 5%

RM10

4

3

2

1

22x4 1/32W 5%

RM11

ARRAY

8

7

6

5

10x4 1/32W 5%

RM12

ARRAY

8

7

6

5

10x4 1/32W 5%

R744

R745

R746

R747

R748

R749

ARRAY

ARRAY

2

8

7

6

5

8

7

6

5

5

6

7

8

5

6

7

8

1

2

3

4

1

2

3

4

22 1/16W 5%

22 1/16W 5%

22 1/16W 5%

22 1/16W 5%

22 1/16W 5%

33 1/16W 5%

BPDD3

BPDD2

BPDD1

BPDD0

BPDD4

BPDD5

BPDD6

BPDD7

BPDD15

BPDD8

BPDD10

BPDD9

BPDD11

BPDD12

BPDD13

BPDD14

BPDA2

BPDA0

BPDA1

3

3

5VMAIN

R743

1K 1/16W 5%

BPDD[0:15] 35

C71 r 0.1uF 10V

C72 r 0.1uF 10V

C73 2K 1/16W 5%

C74 r 0.1uF 10V

C770,R743,C73,C74は、Page35

M76直横に実装すること。

GND1

C770 r 0.1uF 10V

RESERVE

4

C75 r 0.1uF 10V

C69 r 0.1uF 10V

GND1

C76 r 0.1uF 10V

C70 r 0.1uF 10V

CN6

GND1

1

2

3

4

5

6

POINTING CN

BPDCS3#

BPDCS1#

SPDCS3# 35

SPDCS1# 35

BPDDREQ 35

BPDIOR#

SPDIOR# 35

BPDIOW#

SPDIOW# 35

BPDIORDY

SPDIORDY 35

DASPON#57

5

1

2

3

4

5

6

C69,C70はCN5直ぐ横に実装すること。

4

5

FL2

<FILTER>

1 2

C64

0.1uF 10V

GND1

BPDA[0:2]

BPDA[0:2] 35

PDDACK#23,35

BAYLMP1#35,57

DASPON

HDDLED#57

M26D

12

13

LV00A

3VMAIN

KGPDATA 58

KGPCLOCK 58

BLM11A121S

5VMAIN

5VMAIN

Reserve

11

6

R28 10K 1/16W 5%

R29 10K 1/16W 5%

r 2200pF 25V

C65

12

GND1

DASPON

6

7

5.6K 1/16W 5%

GND1

BPDA[0:2]35

BPDD[0:15]

R27

BPDA[0:2]

C68

0.1uF 10V

BPDD[0:15]35

BPDDREQ35

R30 10K 1/16W 5%

BPDIORDY

BPDIAG#35

Q1

D2

1SS400

12

2SK3019

21

10uF 10V

C66

32

1

5VMAIN

10uF 10V

C67

12

版 年 月日設計 調査 承認 変 更 内

設計

7

IDERST#35,57

BPDIOW#

BPDIOR#

BPDCS1#

BPDCS3#

8

25

50

BPDD7

BPDD8

BPDD6

BPDD9

BPDD5

BPDD10

BPDD4

BPDD11

BPDD3

BPDD12

BPDD2

BPDD13

BPDD1

BPDD14

BPDD0

BPDD15

IRQ1424,35,60

BPDA1

BPDA0

BPDA2

R32

1K 1/16W 5%

GND1

容

承認調査

24

49

23

48

22

47

21

46

20

45

19

44

18

43

17

42

16

41

15

40

14

39

13

38

12

37

11

36

10

35

9

34

8

33

7

32

6

31

5

30

4

29

3

28

2

27

1

26

名

ANISE-E2 04

称

図

C1CP051300-X4

番

富士通株式会社

8

CN5

RSTDRV#

GND1

GND1

BPDD7

BPDD8

BPDD6

BPDD9

BPDD5

BPDD10

BPDD4

BPDD11

BPDD3

BPDD12

BPDD2

BPDD13

BPDD1

BPDD14

BPDD0

BPDD15

GND1

GND1

BPDDREQ

GND1

GND1

BPDIOW#

GND1

GND1

BPDIOR#

GND1

GND1

PIORDY

PDDACK#

GND1

IRQ14

IOCS16#

BPDA1

PDIAG#

BPDA0

BPDA2

BPDCS1#

BPDCS3#

HDDLED#

GND1

5VMAIN

GND1

5VMAIN

GND1

5VMAIN

GND1

5VMAIN

9

HDD CN_ANISE_R1

ペ

|

781

ジ

9

提出先

Page 8

1

PCMVCC1 PCMVCC1

A A

JWPB44,45

JDB245

JDB145

B B

C C

PCMVPP1

D D

E E

F F

JDB045

JAB045

JAB145

JAB245

JAB345

JAB445

JAB545

JAB645

JAB745

JAB1245

JAB1545

JAB1645

JBSYB#45,57

JWEB#45

JAB1445

JAB1345

JAB845

JAB945

JAB1145

JOEB#45

JAB1045

JCE1B#44,45

JDB745

JDB645

JDB545

JDB445

JDB345

DKBAYID237

DKBAYID037

CN7A

80

GND1

79

PCMVCC1

78

PCMVCC1

77

JWPA

76

JDB2

75

JDB1

74

JDB0

73

JAB0

72

JAB1

71

JAB2

70

JAB3

69

JAB4

68

JAB5

67

GND1

66

JAB6

65

JAB7

64

JAB12

63

JAB15

62

JAB16

61

PCMVPP1

60

GND1

59

JBSYB#

58

JWEB#

57

JAB14

56

JAB13

55

JAB8

54

GND1

53

JAB9

52

JAB11

51

JOEB#

50

JAB10

49

JCE1B

48

JDB7

47

JDB6

46

JDB5

45

JDB4

44

JDB3

43

GND1

42

BAYID2

41

BAYID0

DOCK_INT_CN_R6

2

160

GND1

159

PCMVCC1

158

PCMVCC1

157

JCD2B#

156

JDB10

155

JDB9

154

JDB8

153

JBVD1B

152

JBVD2B

151

JREGB#

JWAITB#

JRTSB

GND1

JVS2B#

JAB25

JAB24

JAB23

JAB22

PCMVPP1

GND1

JAB21

JAB20

JAB19

JAB18

JAB17

GND1

JIOWRB#

JIORDB#

JVS1B#

JCE2B#

JDB15

JDB14

JDB13

JDB12

JDB11

JCD1B#

GND1

GND1

BAYID1

150

149

148

147

146

145

144

143

142

141

140

139

138

137

136

135

134

133

132

131

130

129

128

127

126

125

124

123

122

121

JINPACKB#

3

JCD2B# 45

JDB10 45

JDB9 45

JDB8 45

JBVD1B 45

JBVD2B 45

JREGB# 45

JINPACKB# 45

JWAITB# 45

JRSTB 45

JVS2B# 45

JAB25 45

JAB24 45

PCMVPP1

JAB23 45

JAB22 45

JAB21 45

JAB20 45

JAB19 45

JAB18 45

JAB17 45

JIOWRB# 45

JIORDB# 45

JVS1B# 45

JCE2B# 44,45

JDB15 45

JDB14 45

JDB13 45

JDB12 45

JDB11 45

JCD1B# 45

DKBAYID1 37

4

BATT2

5VMAIN

DKUSBP1+10

VSENSE270,73

BATTM2+68 BT2IN 68,74

BATTC768

BT2DAT75

DKBAYCD2#56

DKBAYLMP1#35

BAYVCC

DKSPDCS1#35

DKBPDA035

DKBPDA135

DKIRQ1435

DKSPDIOR#35

DKSPDIOW#35

DKPDD035

DKPDD135

DKPDD235

DKPDD335

DKPDD435

DKPDD535

DKPDD635

DKPDD735 DKPDD9 35

DKRSTDRV#35

CDL52 CDR 52

CDRTN52

DKBAYCD1#56

CN7B

40

USBP1+

39

USBVCC1

38

GND1

37

GND1

36

VSENSE

35

BATT2

34

BATT2

33

BATT2

32

BATT2

31

BATT2

30

BATTM2

29

CINT1

28

BT2DAT

27

BAYATCH

26

GND1

25

DASP#

24

5VBAY

23

5VBAY

22

BPDCS1#

21

BPDA0

20

BPDA1

19

IRQ14

18

SPDIOR#

17

SPDIOW#

16

GND1

15

BPDD0

14

BPDD1

13

BPDD2

12

BPDD3

11

BPDD4

10

BPDD5

9

BPDD6

8

BPDD7

7

RSTDRV#

6

GND1

5

CDL

4

CDRTN

3

BAYATCH

2

GND1

1

GND1

DOCK_INT_CN_R6

5

USBP1-

USBVCC1

GND1

GND1

SCONT2

BATT2

BATT2

BATT2

BATT2

BATT2

BT2IN

BT2CLK

GNDA

N.C

GND1

BPDCS3#

5VBAY

5VBAY

5VBAY

BPDA2

PDIAG

N.C

PDDACK#

PIORDY

GND1

BPDDREQ

BPDD15

BPDD14

BPDD13

BPDD12

BPDD11

BPDD10

BPDD9

BPDD8

GND1

CDR

CDRTN

GND1

GND1

GND1

6

120

119

118

117

116

115

114

113

112

111

110

109

108

107

106

105

104

103

102

101

100

99

98

97

96

95

94

93

92

91

90

89

88

87

86

85

84

83

82

81

DKUSBP1- 10

SCONT2 73

BT2CLK 75

BAY2ON 57

DKSPDCS3# 35

DKBPDA2 35

DKBPDIAG# 35

BAYRI# 56

DKPDDACK# 35

DKPIORDY 35

DKBPDDREQ 35

DKPDD15 35

DKPDD14 35

DKPDD13 35

DKPDD12 35

DKPDD11 35

DKPDD10 35

DKPDD8 35

GNDA

BAYVCC

7

CD-ROM

DRIVE

PC-Card Slot

8

BayConnectorBoardBayUnit

Lower Side

Lower Side

A1B1

IDE/USB/BATTCARD/USB

A34B34

A1B1

A44B44

12

49 50

1

35

34

69

Upper Side

Upper Side

9

81

160 80

1

GND1 GND1 GND1 GND1

名

ANISE-E2 04

G G

BAY CN

版 年 月日設計 調査 承認 変 更 内

1

2

3

4

5

6

設計

7

容

承認調査

8

称

図

C1CP051300-X4

番

富士通株式会社

ペ

|

881

ジ

9

提出先

Page 9

1

2

3

4

5

6

7

8

9

A A

B B

C C

D D

CN8

28

ROW#0

17

ROW#1

16

ROW#2

13

ROW#3A

9

ROW#3B

12

ROW#4

11

ROW#5

8

ROW#6

E E

F F

INT_KBD

G G

ROW#7

CLM#0

CLM#1

CLM#2

CLM#3

CLM#4

CLM#5

CLM#6

CLM#7

CLM#8

CLM#9

CLM#10

CLM#11

CLM#12

CLM#13

CLM#14

CLM#15

ID-C

7

27

26

25

24

23

22

21

20

19

18

15

14

10

6

5

4

3

2

ID0

1

ID1

Keyboard Strap (N86C-7664-0203-E)

ID1:ID0 (KBC Side)

GND1

JP 0 0

US 0 1

UK 1 0

JP 1 1 ('00 Summer model)

ROW#0

ROW#1

ROW#2

ROW#3

ROW#4

ROW#5

ROW#6

ROW#7

CLM#0

CLM#1

CLM#2

CLM#3

CLM#4

CLM#5

CLM#6

CLM#7

CLM#8

CLM#9

CLM#10

CLM#11

CLM#12

CLM#13

CLM#14

CLM#15

INTR KB CN

1

2

3

ROW#[0:7] 58

CLM#[0:15] 58

KSHIPID1 58

KSHIPID0 58

SHIPID

ID0 ID1

US

10

JP

UK

版 年 月日設計 調査 承認 変 更 内

4

5

6

設計

7

00

1

0

名

ANISE-E2 04

称

図

C1CP051300-X4

番

容

承認調査

富士通株式会社

8

ペ

|

981

ジ

9

提出先

Page 10

1

2

3

4

5

6

7

8

9

USBP0-24

A A

USBP0+24

◆◆

R37

27 1/16W 5%

C78

47pF 25V

GND1 GND1

R39

27 1/16W 5%

C79

47pF 25V

B B

GND1 GND1

USBP1-24

C C

USBP1+24

◆◆

R41

27 1/16W 5%

C80

47pF 25V

GND1 GND1

R43

27 1/16W 5%

C81

47pF 25V

GND1 GND1

D D

◆◆

R38

15K 1/16W 5%

R40

15K 1/16W 5%

◆◆

R42

15K 1/16W 5%

R44

15K 1/16W 5%

DKUSBP0- 3

DKUSBP0+ 3

DKUSBP1- 7

DKUSBP1+ 7

5VMAIN

DKUSBP0-3

DKUSBP0+3

USBVCC0

PS1

1 2

MINISMDC100(1.00A)

FL24

<FILTER>

BLM41P600S

R638

0 1/16W

R639

0 1/16W

12

C689

12

10uF 10V

GND1

USBVCC0

3VMAIN

CN22

1

VCC

2

-DATA

3

+DATA

4

GND

5

FG1

6

FG2

USB_CON_STD

R48

100K 1/16W 5%

OVERCRNT1# 24

1K 1/16W 5%

R47

Reserved

10K 1/16W 5%

r100K 1/16W 5%

OVERCRNT0# 24

名

ANISE-E2 04

称

図

C1CP051300-X4

番

容

承認調査

富士通株式会社

8

9

ペ

|

10 81

ジ

提出先

R932

本項中◆印のついたパターンは、通常の信号線の0.2mmの太さで配線すること。

E E

F F

G G

また、本信号はGND1でガードし、その上下はGND1のベタパターンで覆うこと。

The following guideline is applied to USB signal traces.

Less than

1 inch

USBn-,+

47pF

R

27ohm

RC

15kohm

BANISTER

USB POW

1

2

[NOTE] : CTL is control(input) function : Noninverting TTL control input.

High(>1.8V typical)=On, Low(<1.6V typical)=Off.

This trace must be guarded along with

USBG traces on both sides.

The length of this stub mest be

as short as possible.

This point must be appeared on

surficial layer to be cuttable.

Those three components must be located as

near to BANISTER as possible.

3

R

0ohm

4

Less than

1 inch

USB CN

Docking CN

R933

GND1

版 年 月日設計 調査 承認 変 更 内

5

6

設計

7

Page 11

1

2

3

4

5

6

7

8

9

MAX 1A

10

M88A

rTC7SZ08FU

R763

0 1/16W 5%

4

M3

LEDA

6

NC

7

GND

1

VCC

2

AGND

Reserved

12

4

FIR_SEL

QSDL-M137#00

4

12

GND1 GND1

TXD

RXD

MD0

MD1

r 2200pF 25V

C516

RESERVED

9

8

3

4

5

1

R404

4.7K 1/16W 5%

2

IRTX 51

IRRXA# 51

IRMODE 51

GND1

POWERGOOD2 57

ISAPWR 44,57

5

VR_ON 27,41

SYSPWR 57

PWGDCPU 18

PMUVCC 3VSUS

↓70mA

R407

47 1/4W 5%

1

TC7SZ08FU

名

称

図

C1CP051300-X4

番

富士通株式会社

1 2

32

Q21

2SK3019

GND1GND1

C519

0.1uF 10V

1 2

ANISE-E2 04

9

ペ

|

11 81

ジ

提出先

1 2

1

容

C926

0.1uF 10V

8

3 2

2

1

Q18

TP0610T

R408

M45B

承認調査

100K 1/16W 5%

PLLVCC

53

GND1

SUSC#26,59,74,76

3VSUS

53

M88B

rTC7SZ08FU

GND1

版 年 月日設計 調査 承認 変 更 内

6

設計

7

5VMAIN

R51

5.6 1/2W 5%

A A

5VMAIN

M4

5

VIN

B B

1 2

C92

12

0.1uF 10V

C788

0.033uF 25V

Td(Typ)=190ms

GND1

1

VOUT

43

VORCD

VSS

S-873325BUP-ALA-T2

2

C C

VRPWRGD27

PMUVCC

2200pF 25V

1 2

GND1

2200pF 25V

C520

5VSUS

12

CPUPWRGD27

PCIRST#24,44,57

12

C521

Td(Typ)=125ms

0.033uF 16V

C518

0.01uF 16V

Td(Typ)=57ms

M46

2

VDD

5

CD

3

GND

S-80927AL

M47

2

VDD

5

CD

3

GND

S-80942ANMP

OUT

OUT

1

1

D D

E E

C517

F F

12

G G

3VIR

TP3

3VIR

3VMAIN

1 2

R402

3VSUS

12

12

+

C88

15uF 16V

(TA)

10K 1/16W 5%

10K 1/16W 5%

R409

C522

2200pF 25V

1 2

GND1GND1

GND1

12

C86

4.7uF 10V

12

M45A

1

2

TC7SZ08FU

(CPUIOVCC)

12

C87

0.1uF 10V

12

C89

0.47uF 16V

・C87,C89はM3pin直横に配置

・M4はM3の近くに配置し、C88はM4の近くに配置すること。

・C759はRing(M34の接続pin)直横に配置すること。

1

2

RESET/3VIR/IRDA

1

2

3

Page 12

1

2

3

4

5

6

7

8

9

SO-DIMM SLOT (FOR EXPANSION MEMORY)

A A

MD[0:63]31

B B

DQM031

C C

DQM131

MA[0:13]31

D D

E E

SDCLK2B32

SDCLK2A32

SDCLK1A32

SRASB#31

WEB#31

CS#031

CS#131

F F

MD0

MD1

MD2

MD3

MD4

MD5

MD6

MD7

MA0

MA1

MA2

MD8

MD9

MD10

MD11

MD12

MD13

MD14

MD15

3VSUS

CN9A

1

3

5

7

9

11

13

15

17

19

21

23

25

27

29

31

33

35

37

39

41

43

45

47

49

51

53

55

57

59

61

63

65

67

69

71

DIMM SOCKET

CS#231

CS#331

MD[0:63]31

MA[0:13]31

DQM231

DQM331

BSMBDATA24,32,41,49

MD16

MD17

MD18

MD19

MD20

MD21

MD22

MD23

MA6

MA8

MA9

MA10

MD24

MD25

MD26

MD27

MD28

MD29

MD30

MD31

3VSUS

73

75

77

79

81

83

85

87

89

91

93

95

97

99

101

103

105

107

109

111

113

115

117

119

121

123

125

127

129

131

133

135

137

139

141

143

CN9B

DIMM SOCKET

3VSUS

MD[0:63]31

MD32

MD33

MD34

MD35

MD36

MD37

MD38

MD39

DQM431

DQM531

MA[0:13]31

CKE331

CKE231

CKE031

SCASB#31

MA[0:13]31

CKE131

MA3

MA4

MA5

MD40

MD41

MD42

MD43

MD44

MD45

MD46

MD47

MA12

MA13

CN9C

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

54

56

58

60

62

64

66

68

70

72

SDCLK1B32

MD[0:63]31

MA[0:13]31

DQM631

DQM731

BSMBCLK24,32,41,49,59

DIMM SOCKET

MD48

MD49

MD50

MD51

MD52

MD53

MD54

MD55

MD56

MD57

MD58

MD59

MD60

MD61

MD62

MD63

MA7

MA11

MA12

MA13

3VSUS

GND1

CN9D

74

76

78

80

82

84

86

88

90

92

94

96

98

100

102

104

106

108

110

112

114

116

118

120

122

124

126

128

130

132

134

136

138

140

142

144

DIMM SOCKET

GND1 GND1 GND1

3VSUS

12

C93

10uF 10V

G G

GND1

Dimm Slot

1

2

12

C94

0.1uF 10V

12

1 2

C95

0.1uF 10V

C96

0.1uF 10V

1 2

C97

0.1uF 10V

上記のコンデンサはDIMMスロットの電源端子の近くに配置・配線すること B

3

4

5

名

ANISE-E2 04

称

図

C1CP051300-X4

ٛ

6

版 年 月日設計 調査 承認 変 更 内

設計

容

7

承認調査

8

番

富士通株式会社

9

ペ

|

12 81

ジ

提出先

Page 13

1

2

3

4

5

6

7

8

9

TP78

CN11A

A A

Line-OPT

B B

CN11B

Line-OPT

8

C C

VCC

GND

7

Vin

9

C9

GND1

5

4

3

2

1

1 2

12

C102

r1800pF 25V

AUDIOGND

1 2

0.1u 16V

R936

0 1005

C103

r1800pF 25V

D D

CN12

HP JACK

E E

5

4

3

6

2

1

C115

AUDIOGND

上記のフィルタ、コンデンサ、抵抗 ヘ

HP JACKの近くに配置すること。

F F

VR1 RK10J12RK1

5

AVCC

4

1

EVRCTRL53

G G

LINER

FL7

<FILTER>

12

BLM11B102S

FL9

<FILTER>

12

BLM11B102S

FL29

<FILTER>

12

Reserve

上記のフィルタ、コンデンサ、抵抗 ヘ

LINE IN JACKの近くに配置すること B

R943

1 2

0 1005

3VMAIN

SPDIFO 52

※

C116

r1000pF 25V

r1000pF 25V

Reserve

BLM11B102S

FL30

<FILTER>

BLM11B102S

FL13

<FILTER>

BLM11B102S

FL14

<FILTER>

BLM11B102S

FL31

<FILTER>

BLM11B102S

12

12

12

12

12

ٛ

本ページ中に記載されているフィルタ(FLxx)はそれぞれ接 ア

されているコネクタの近くに配置し、フィルターコネクタ間の z

線は非常に短く配線すること。

3

2

FGFG

AUDIOGND

The filters in this page (refered with FLxx) have to

be placed near each connector connecting to respective

filters. The traces between connector and filter have

to be short as much as possible.

本項中※印のついたパターンは、AUDIOGND ナガードし、その上

下はAUDIOGNDのベタパターンで覆うこと。 ワた、Mxの下の基板

面およびその下の層には、ディジタル系の信号線を配線しないこ

と。

The traces marked with ※ have to be guarded both side and

both adjacent layer with AUDIOGND. Underneath Mx on

surface layer and in one more internal layer don't allow

digital traces to be run.

※

※

ٛ

AUDIOGND

ٛ

0 1/16W 5%

R63

0 1/16W 5%

R65

12

12

※※

AUDIOGND

5VSUS

R61 100K 1/16W 5%

※※※

ٛ

ٛ

LINEINR 52

LINEINL 52

FHPIN 57

HPOUTR 53

HPOUTL 53

CN13

MIC IN JACK

AUDIOGND

5

4

3

6

2

1

ٛ

ٛ

C114

1uF 10V

SPOUT1L53

SPOUT2L53

SPOUT1R53

SPOUT2R53

INTMICRTN4

INTMICIN4

12

FL33

<FILTER>

BLM11B102S

12

C790

GND1

AVCC

1000pF 25V

1 2

R62

R66

12

R937

0 1005

※

※

※

※

1K 1/16W 5%

2.2K 1/16W 5%

12

<FILTER>

BLM11B102S

FL32

FL15 BLM11B102S

<FILTER>

FL17 BLM11B102S

<FILTER>

AUDIO CN

1

2

3

4

5

6

FL5

<FILTER>

12

BLM11A121S

FL6

<FILTER>

12

BLM11A121S

FL8

<FILTER>

12

BLM11A121S

FL10

<FILTER>

12

BLM11A121S

12

12

12

12

4700pF 25V

1000pF 25V

C742

C118

版 年 月日設計 調査 承認 変 更 内

設計

678

CM3

0.1uFx4 16V

123

4 5

GND1

※

R764

0 1/16W 5%

FL15,FL17~FL19,C118はMIC IN

JACKの近くに配置すること。

R62,R66,R68,R69,C114,C117はSTAC9721の近くに実装し A

基板の端面をとおして配線すること B

AUDIOGND

容

7

MICIN 54

Placement location of audio connectors

名

称

図

番

承認調査

富士通株式会社

8

ٛ

CN10

1

SPL1

2

SPL2

3

SPR1

4

SPR2

SPK CN

CN13

MIC

CN11

LINE IN

CN12

PHONE

ANISE-E2 04

C1CP051300-X4

ペ

|

13 81

ジ

9

ٛ

提出先

Page 14

1

CN14A

A A

B B

C C

D D

E E

F F

G G

3VSUS

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

AD12

AD13

AD14

AD15

AD16

AD17

AD18

AD19

AD20

AD21

AD22

AD23

AD24

AD25

AD26

AD27

AD28

AD29

AD30

AD31

5VMAIN

R919

LAN/MODEM CN

1

GND1

10K 1/16W 5%

1 2

2

AD[0:31]

C/BE#1 24,39,44

PAR 24,39,44

SERR# 24,34,44

PERR# 34,44

STOP# 24,34,39,44

DEVSEL# 24,34,39,44

TRDY# 24,34,39,44

IRDY# 24,34,39,44

FRAME# 24,34,39,44

C/BE#2 24,39,44

CIDSEL0 49

C/BE#3 24,39,44

BPCIREQ#2 41

PCIGNT#2 24,34

1 2

C691

10uF 10V

1 2

PME# 24,44,56

LANATCH# 24

ACMDMINST# 24

2

AD[0:31] 24,39,44,49

FL27

<FILTER>

BLM11A121S

3VMAIN

3VSUS

3

CN14B

R70

51

52

AD0

53

AD1

54

AD2

55

AD3

56

AD4

57

AD5

58

AD6

59

AD7

60

61

AD8

62

AD9

63

AD10

64

AD11

65

66

67

68

PDC1

69

PDC2

70

PDC3

71

PDC4

72

PDC5

73

PDC6

74

75

PDC8

76

PDC9

77

PDC10

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

GND1GND1

AUDIOGND

10K 1/16W 5%

1 2

AD[0:31]

5VMAIN

4

C/BE#0 24,39,44

PDC[1:15]24

PME# 24,44,56

PDC[1:15] 24

R93はLAN/MODEMコネクタの近くに配置・配線すること。

3

4

3VMAIN

MDMATCH# 24

AD[0:31] 24,39,44,49

MDMSTBY# 56

PCIINT#2 24,34,39,57

CPCIRST#1 56

BPCIREQ#1 41

PCIGNT#1 24,34

MDMAVSL 56

CLKRUN# 24,34,39,44

PCLKMDM 47

LANMDRST# 57

PCIINT#2 24,34,39,57

SPKTEL 54

CIDSEL1 49

5

注意:モジュール間でのピンスワップ禁止

DCDA3,60

DTRA3,60

RIA3,60

CTSA3,60

SOUTA#3,60

DSRA3,60

SINA#3,60

RTSA3,60

PDC1

PDC2

PDC3

PDC4

PDC5

PDC6

R86 r 0 1005

PDC10

Reserve

R89 0 1005

Reserved for JP model

GND1 GND1

12

12

Reserved for overseas model

RM120 0x4 1/32W 5%

RM121 0x4 1/32W 5%

ARRAY

1

2

3

4

ARRAY

1

2

3

4

RM122 0x4 1/32W 5%

RM123 0x4 1/32W 5%

ARRAY

1

2

3

4

ARRAY

1

2

3

4

Reserved for JP model

5VSUS

R95

1K 1/16W 5%

5

6

8

7

6

5

8

7

6

5

8

7

6

5

8

7

6

5

※※

R94

5.6K 1/16W 5%

AUDIOGND

※MICAMP,SPKTELはAUDIOGNDでガードし、なおかつAUDIOGNDのベ ^パターンで上下を覆うこと

版 年 月日設計 調査 承認 変 更 内

設計

6

7

CM1

47pFx4 50V

1

8

R92 27K 1/16W 5%

1 2

7

8

CM2

47pFx4 50V

1

2

3

2

3

45

6

7

8

45

6

7

MICAMP 52

9

GND1

FG1

FG2

GND1

PDC1:TCH-T

PDC2:TCH-F

PDC3:TCH-CLK

PDC4:UPMS

PDC5:DWMS

PDC6:TCH-R

PDC10:ADP

CN15

1

2

3

4

5

6

7

8

9

PDC CN

ٛ

名

ANISE-E2 04

称

図

C1CP051300-X4

番

容

承認調査

富士通株式会社

8

9

ペ

|

14 81

ジ

提出先

Page 15

1

2

3

4

5

6

7

8

9

PCMVPP0 PCMVCC0

PCMVPP0 PCMVCC0

A A

CN16-1

1

2

3

4

5

6

B B

C C

D D

E E

PCMCIA CN

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

12

0.1uF 10V

C119

F F

JDA3

JDA4

JDA5

JDA6

JDA7

JAA10

JAA11

JAA9

JAA8

JAA13

JAA14

JAA16

JAA15

JAA12

JAA7

JAA6

JAA5

JAA4

JAA3

JAA2

JAA1

JDA0

JDA1

JDA2

12

0.1uF 10V

C120

JAA0

12

C121 2.2uF 16V

JDA[0:15] 45

JAA[0:25] 43,45

JCE1A# 44,45

JOEA# 45

JWEA# 45

JBSYA# 45,57

JWPA 43,44,45

CN16-2

PCMCIA CN

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

FG1

FG2

JDA11

JDA12

JDA13

JDA14

JDA15

JAA17

JAA18

JAA19

JAA20

JAA21

JAA22

JAA23

JAA24

JAA25

JDA8

JDA9

JDA10

JDA[0:15] 45

JCD1A# 45

JAA[0:25] 43,45

JCE2A# 44,45

JVS1A# 45

JIORDA# 45

JIOWRA# 45

JVS2A# 45

JRSTA 45

JWAITA# 45

JINPACKA# 43,45

JREGA# 45

JBVD2A 43,45

JBVD1A 45

JCD2A# 45

GND1

GND1

名

ANISE-E2 04

G G

PCMCIA SLOT

1

版 年 月日設計 調査 承認 変 更 内

2

3

4

5

6

設計

7

容

承認調査

8

称

図

C1CP051300-X4

番

富士通株式会社

9

ペ

|

15 81

ジ

提出先

Page 16

1

2

3

4

5

6

7

8

9

A A

**TP5-TP14はCeleron CPU M6 接続先PAD直裏付近、実装のこと。

TP5

TDO

TP7

TDI

TP9

5VMAIN

B B

5VMAIN

R97 100K 1/16W 5%

SA[0:18]24,51,56,58,59

C C

SD[0:7]24,51,56,58,59,60

008XIN#56

0080W#56

D D

SA4

SA5

SA6

SA7

SA8

SA9

SD0

SD1

SD2

SD3

SD4

SD5

SD6

SD7

GND1

CN17

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

DEBUG CN

TRST#

TP11

TMS

TP13

TCK

TP8

PREQ#

TP12

CPURSTITP#

TP14

PRDY#

PRDY# 18

CPURST# 18,23,27

PREQ# 18,22

TCK 18,22

TMS 18,22

TRST# 18,22

TDI 18,22

TDO 18

E E

本ページ記載のコネクタはデバッグの為のものである。

なるべくコネクタの配置は、基板端にすること。

もし実装上困難であれば、上記コネクタの形状変更を検討しま

すので、別途相談願います。

F F

名

ANISE-E2 04

G G

DEBUG CN

1

版 年 月日設計 調査 承認 変 更 内

2

3

4

5

6

設計

7

容

承認調査

8

称

図

C1CP051300-X4

番

富士通株式会社

9

ペ

|

16 81

ジ

提出先

Page 17

1

2

3

4

5

6

7

8

9

A A

B B

C C

D D

E E

F F

名

ANISE-E2 04

G G

CPU TEMP. MONITOR

1

版 年 月日設計 調査 承認 変 更 内

2

3

4

5

6

設計

7

容

承認調査

8

称

図

C1CP051300-X4

番

富士通株式会社

9

ペ

|

17 81

ジ

提出先

Page 18

1

A A

HD#[0:63]23

B B

C C

D D

PLLVCC

12

E E

R706 1.5K 1/16W 0.5%

12

R708 1K 1/16W 0.5%

F F

G G

12

GLO/HI#22,27

VIDC0

VIDC1

VIDC2

VIDC3

VIDC4

12

1.5K 1/16W 0.5%

R707

12

0.1uF 10V

C728

R709 1.5K 1/16W 0.5%

GND1

12

0.1uF 10V

C729

12

R710 56ohm 1/16W 0.5%

Coppermine

1

2

HD#0

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

2

D20

D21

H18

E20

H19

E21

H21

G20

P18

G21

K18

K21

M18

R19

K19

M19

U18

R18

AA9

AD18

AB19

AD19

AD2

AD3

AD4

AC4

AB4

D10

D11

C10

B11

C12

B13

A14

B12

E12

B16

A13

D13

D15

D12

B14

E14

C13

A19

B17

A18

C17

D17

C18

B19

D18

B20

A20

B21

D19

C21

E18

C20

F19

F18

J18

F21

J20

L18

L21

T20

J21

L20

C7

C8

B9

A9

P2

R2

M6A

D0#

D1#

D2#

D3#

D4#

D5#

D6#

D7#

D8#

D9#

D10#

D11#

D12#

D13#

D14#

D15#

D16#

D17#

D18#

D19#

D20#

D21#

D22#

D23#

D24#

D25#

D26#

D27#

D28#

D29#

D30#

D31#

D32#

D33#

D34#

D35#

D36#

D37#

D38#

D39#

D40#

D41#

D42#

D43#

D44#

D45#

D46#

D47#

D48#

D49#

D50#

D51#

D52#

D53#

D54#

D55#

D56#

D57#

D58#

D59#

D60#

D61#

D62#

D63#

CLKREF

CMOSREF

CMOSREF

GHI#

RSVD

RTTIMPEDP

VID0

VID1

VID2

VID3

VID4

Mobile Pentium III

3

A3#

A4#

A5#

A6#

A7#

A8#

A9#

A10#

A11#

A12#

A13#

A14#

A15#

A16#

A17#

A18#

A19#

A20#

A21#

A22#

A23#

A24#

A25#

A26#

A27#

A28#

A29#

A30#

A31#

A32#

A33#

A34#

A35#

DEP0#

DEP1#

DEP2#

DEP3#

DEP4#

DEP5#

DEP6#

DEP7#

FERR#

BREQ0#

HITM#

HIT#

AP0#

AP1#

LOCK#

PRDY#

PICD0

PICD1

ADS#

3

L3

K3

J2

L4

L1

K5

K1

J1

J3

K4

G1

H1

E4

F1

F4

F2

E1

C4

D3

D1

E2

D5

D4

C3

C1

B3

A3

B2

C2

A4

A5

B4

C5

V20

T21

U21

R21

V18

P21

P20

U19

AC12

C6

Y4

V1

AB1

Y2

R1

W20

AB21

Y20

AB2

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

DEP#0

DEP#1

DEP#2

DEP#3

DEP#4

DEP#5

DEP#6

DEP#7

4

HA#[3:35] 23

CPURST#16,23,27

GINIT#22,27

GSMI#22,27

DEP#[0:7]

FERR# 22

BREQ#0 23

HITM# 23

HIT# 23

HLOCK# 23

PRDY# 16

PICD0 22

PICD1 22

ADS# 23

CPUBUSVCC

R726

56ohm 1/16W 0.5%

RESERVE

TP59 AP0

AP1

TP60

5

12

GND1

A20M#22,23

GINTR22,27

GNMI22,27

IGNNE#22,23

FLUSH#22

12

12

100pF 25V

C127

GND1 GND1 GND1

CPUBUSVCC

12

R105 1K 1/16W 5%

R107

r 0 1005

1 2

GND1

100pF 25V

C128

1 2

C753 100pF 25V

1 2

C754 100pF 25V

1 2

C755 100pF 25V

1 2

C756 100pF 25V

1 2

C757 100pF 25V

12

100pF 25V

C129

0 1005

R705

1 2

R106

*CPU

PAD裏面に最短距離で配置、配線のこと。

下図はGTL+系信号の配線トポロジーである。

CPU(Coppermine)

M6

CPU(Coppermine)からCHIPSET(Banister)への信号線は上記の条件

を厳守すること。

注意:最低50.8mmの基準は厳しい為、不可能な場合は設計元に連絡のこと。

・50.8mmを実施する為にラーメンパターンになるのは避けること。

・CPU-チップセット間は、非貫通スルホール領域で配線のこと。(内層は

基本的に避ける)

4

50.8-110mm

5

CHIPSET

(BANISTER)M8

6

RS#023

RS#123

RS#223

TP55

RSP#

GSTPCLK#22,27

DEFER#23

PICCLK22

BPRI#23

PREQ#16,22

PWGDCPU11

SLP#22

12

110 1/16W 0.5%

6

7

AD10

AB18

AC19

AC13

AC9

AA10

AB10

AA2

AC11

AA18

AB20

AB12

AA14

AA11

AD14

AD13

AA16

AA12

AB15

AD17

AD20

AA17

M3

A6

U1

W1

Y1

U3

U4

V5

U2

Y5

N5

H4

G4

HCLKCPU47

TP57

THERMDA

TRST#16,22

HTRDY#23

TCK16,22

TMS16,22

TDI16,22

TESTHI22

TESTLO122

TESTLO222

TP61

TP_AD20

TP62

TP_H4

TP63

TP_AA17

TP64

TP_G4

版 年 月日設計 調査 承認 変 更 内

設計

7

M6B

BCLK

A20M#

INTR/LINT0

NMI/LINT1

IGNNE#

FLUSH#

RESET#

INIT#

SMI#

RS0#

RS1#

RS2#

RSP#

STPCLK#

DEFER#

PICCLK

BPRI#

PREQ#

PWRGOOD

SLP#

TRST#

TRDY#

TCK

TMS

TDI

EDGECTRLP

BSEL0

BSEL1

TESTHI

TESTLO1

TESTLO2

TESTP

TESTP

TESTP

TESTP

Mobile Pentium III

8

AD9

IERR#

AA1

AERR#

E6

BERR#

V21

BINIT#

T4

BNR#

W21

BPM0#

W19

BPM1#

AA21

BP2#

Y21

BP3#

AA3

DBSY#

T1

DRDY#

REQ0#

REQ1#

REQ2#

REQ3#

REQ4#

RP#

THERMDCTHERMDA

TDO

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

容

承認調査

T2

V4

V2

W3

W5

W2

AB16AA15

AC15

A15

A16

A17

C14

D8

D14

D16

E15

G2

G5

G18

H3

H5

J5

M4

M5

P3

P4

AA5

AA19

AC3

AC17

AC20

AD15

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

TDO 16

名

称

図

番

富士通株式会社

C1CP051300-X4

8

9

TP15 IERR#

BNR# 23

BPM#0

BPM#1

BP#2

BP#3

DBSY# 23

DRDY# 23

HREQ#[0:4] 23

TP56

RP#

TP58

THERMDC

ANISE-E2 04

ペ

|

ジ

9

TP52

AERR#

TP53

BERR#

TP54

BINIT#

提出先

18 81

Page 19

1

A A

B B

注意:CPUの4隅に近い部分のVREF端子よりスルホールにてコンデンサに

接続する。

GND1側にもスルホール必須

C C

注意:CPU.(P1)端子は、0.4mm幅にてCPUCOREVCC電源プレーン

に接続すること。

CPU(P1)端子の直裏にC999を搭載すること B

※本信号は、CPU内部Core CLKバッファ電源の為、重 v

D D

注)・C132,L1は、CPUに最短距離で、通常の信号線の3倍の太さにて

接続すること。(C132,L1の下にはクロストーク防止の為、他信号線を

E E

配置しないこと)

・C130,C131,R108,R109は、CPUに最短距離で配線すること。

VREF_GTLは、アナログ信号の為、Banisterまでの配線は

GND1によるガードパターンを両サイド゙、上下層にて必要とする。

F F

G G

Coppermine

1

2

VREF_GTL

CPUCOREVCC

ٛ

2

3

CPUBUSVCC

12

R108

1K 1/16W 0.5%

R109 2K 1/16W 0.5%

GND1

CPUBUSVCC

12

R711

1 2

0 1/16W 5%

1 2

C927 0.1uF 10V

C928 0.1uF 10V

L3

1 2

4.7uH(NLC322522T-4R7M)

1 2

1 2

C130 0.1uF 10V

ٛ

1 2

C999 r0.1uF 10V

GND1

3

1 2

C131 0.1uF 10V

4

12

+

C132

47uF 6.3V

4

1 2

C943

0.1uF 10V

E16

E17

F17

Y17

Y18

G10

G11

G12

G13

G14

G15

G16

G17

H17

K17

L17

M17

N17

P17

R17

T17

U17

V10

V11

V12

V13

V14

V15

V16

V17

W10

W11

W12

W13

W14

W15

W16

W17

AA6

AA7

AA8

AB6

AB7

AB8

AC6

AC7

AC8

AD6

AD7

AD8

L2

E5

F5

U5

M2

G6

G7

G8

G9

H6

J6

J17

K6

L6

M6

N6

P1

P6

R6

T6

U6

V6

V7

V8

V9

W6

W7

W8

W9

Y6

Y7

Y8

5

M6C

PLL1

VREF

VREF

VREF

VREF

VREF

VREF

VREF

VREF

PLL2

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

5

Mobile Pentium III

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

H8

H10

H12

H14

H16

J7

J9

J11

J13

J15

K8

K10

K12

K14

K16

L7

L9

L11

L13

L15

M8

M10

M12

M14

M16

N7

N9

N11

N13

N15

P8

P10

P12

P14

P16

R7

R9

R11

R13

R15

T8

T10

T12

T14

T16

U7

U9

U11

U13

U15

6

CPUCOREVCC

版 年 月日設計 調査 承認 変 更 内

設計

6

7

M6D

A2

VSS

A7

VSS

A8

VSS

A12

VSS

A21

VSS

B1

VSS

B5

VSS

B6

VSS

B7

VSS

B8

VSS

B10

VSS

B15

VSS

B18

VSS

C9

VSS

C11

VSS

C15

VSS

C16

VSS

C19

VSS

D2

VSS

D6

VSS

D7

VSS

D9

VSS

E3

VSS

E7

VSS

E8

VSS

E9

VSS

E10

VSS

E11

VSS

E13

VSS

E19

VSS

F3

VSS

F6

VSS

F7

VSS

F8

VSS

F9

VSS

F10

VSS

F11

VSS

F12

VSS

F13

VSS

F14

VSS

F15

VSS

F16

VSS

F20

VSS

G3

VSS

G19

VSS

H2

VSS

H7

VSS

H9

VSS

H11

VSS

H13

VSS

H15

VSS

H20

VSS

J4

VSS

J8

VSS

J10

VSS

J12

VSS

J14

VSS

J16

VSS

J19

VSS

K2

VSS

K7

VSS

K9

VSS

K11

VSS

K13

VSS

K15

VSS

K20

VSS

L5

VSS

L8

VSS

L10

VSS

L12

VSS

L14

VSS

L16

VSS

L19

VSS

M7

VSS

M9

VSS

M11

VSS

M13

VSS

M15

VSS

M20

VSS

Mobile Pentium III

7

8

N2

VSS

N3

VSS

N4

VSS

N8

VSS

N10

VSS

N12

VSS

N14

VSS

N16

VSS

N18

VSS

N19

VSS

N20

VSS

P5

VSS

P7

VSS

P9

VSS

P11

VSS

P13

VSS

P15

VSS

P19

VSS

R3

VSS

R4

VSS

R5

VSS

R8

VSS

R10

VSS

R12

VSS

R14

VSS

R16

VSS

R20

VSS

T3

VSS

T5

VSS

T7

VSS

T9

VSS

T11

VSS

T13

VSS

T15

VSS

T18

VSS

T19

VSS

U8

VSS

U10

VSS

U12

VSS

U14

VSS

U16

VSS

U20

VSS

V3

VSS

V19

VSS

W4

VSS

W18

VSS

Y3

VSS

Y9

VSS

Y10

VSS

Y11

VSS

Y12

VSS

Y13

VSS

Y14

VSS

Y15

VSS

Y16

VSS

Y19

VSS

AA4

VSS

AA13

VSS

AA20

VSS

AB3

VSS

AB5

VSS

AB9

VSS

AB11

VSS

AB13

VSS

AB14

VSS

AB17

VSS

AC1

VSS

AC2

VSS

AC5

VSS

AC10

VSS

AC14

VSS

AC16

VSS

AC18

VSS

AC21

VSS

AD1

VSS

AD5

VSS

AD16

VSS

AD21

VSS

名

称

図

C1CP051300-X4

番

容

承認調査

富士通株式会社

8

9

GND1GND1

ANISE-E2 04

ペ

|

ジ

9

提出先

19 81

Page 20

1

が必須。

電源と接続のこと。 各モジュールの端子は2端子に1個は貫通スルホール

注意:これらのパスコンはCPUの直下に搭載し、スルホールでCPUの e

A A

Cuppermine

45

678

0.1uFx4 16V

CM4

B B

123

2

45

678

0.1uFx4 16V

CM5

12

C791

0.1uF 10V

123

12

45

678

0.1uFx4 16V

CM6

12

C792

0.1uF 10V

123

C793

0.1uF 10V

45

678

0.1uFx4 16V

CM7

12

C794

3

123

0.1uF 10V

45

678

0.1uFx4 16V

CM8

123

ٛ

45

678

0.1uFx4 16V

CM9

123

4

45

678

0.1uFx4 16V

CM10

123

45

678

0.1uFx4 16V

CM11

45

678

0.1uFx4 16V

CM12

123

CPUCOREVCC

123

GND1

5

CPUCOREVCC

12

C147

C162

1 2

10uF 10V

10uF 10V

GND1

6

7

8

9

C C

注意:CPUBUSVCCは電源の為、貫通にてCPU裏面のコンデンサモジュールと接続すること。

各モジュールの端子は2端子に2個は貫通スルホールが必 v

CPUBUVCCはCPU搭載面層での表層でもPAD-PAD間を接 ア

することによる強化を実施CM13については、CPU横 表層にて

CPUVCCT強化パターンとスルホール無しで直接接続すること B

123

45

D D

678

0.1uFx4 16V

CM13

45

678

0.1uFx4 16V

CM14

123

45

678

0.1uFx4 16V

CM15

123

45

0.1uFx4 16V

CM16

678

123

ٛ

ٛ

ٛ

45

678

0.1uFx4 16V

CM17

CPUBUSVCC

123

12

C795

12

0.1uF 10V

C796

0.1uF 10V

12

12

C797

C783

0.1uF 10V

0.1uF 10V

GND1

E E

F F

名

ANISE-E2 04

G G

PassCon for Celeron

1

版 年 月日設計 調査 承認 変 更 内

2

3

4

5

6

設計

7

容

承認調査

8

称

図

C1CP051300-X4

番

富士通株式会社

9

ペ

|

20 81

ジ

提出先

Page 21

1

2

3

4

5

6

7

8

9

A A

B B

C C

D D

E E

F F

名

ANISE-E2 04

G G

HOST Signals Pullups

1

版 年 月日設計 調査 承認 変 更 内

2

3

4

5

6

設計

7

容

承認調査

8

称

図

C1CP051300-X4

番

富士通株式会社

9

ペ

|

21 81

ジ

提出先

Page 22

1

2

3

4

5

6

7

8

9

A A

12

12

12

12

12

12

12

12

12

CPUBUSVCC

3VMAINCPUBUSVCC

R124

1

1.5K 1/16W 5%

1 2

Q4

2SC2412K

2 3

BFERR# 23

12

R126

1K 1/16W 5%

FERR#18

R114

A20M#18,23

FERR#18

FLUSH#18

B B

IGNNE#18,23

GINTR18,27

GNMI18,27

SLP#18

C C

GSMI#18,27

GSTPCLK#18,27

GINIT#18,27

D D

PREQ#16,18

GLO/HI#18,27

1 2

1.5K 1/16W 5%

R115

1.5K 1/16W 5%

R117

1.5K 1/16W 5%

R118

1.5K 1/16W 5%

R120

1.5K 1/16W 5%

R121

1 2

1.5K 1/16W 5%

R122

1.5K 1/16W 5%

R123

220 1/16W 5%

R125

2 1

680 1/16W 5%

R127

1K 1/16W 5%

R129

1.5K 1/16W 5%

R765

r1.5K 1/16W 5%

Reserved

E E

R133

5

1 2

1K 1/16W 5%

R136

1 2

1K 1/16W 5%

R139

1 2

1K 1/16W 5%

TCK16,18

TMS16,18

TDI16,18

TRST#16,18

GND1

版 年 月日設計 調査 承認 変 更 内

設計

6

PICD018

CPUBUSVCC

PICD118

F F

R140

TESTHI18

TESTLO118

TESTLO218

G G

1.5K 1/16W 5%

R142

1K 1/16W 5%

R135

1 2

1K 1/16W 5%

12

12

GND1

PICCLK18

重要:

本ページ記載の抵抗については、特に記載が無い限り、CPUの

間近に配置・配線すること。

SideBand Signals Pull Up

1

2

3

4

R134

1 2

1K 1/16W 5%

R137

1 2

1K 1/16W 5%

R138

1 2

1K 1/16W 5%

R141

12

1K 1/16W 5%

GND1

名

ANISE-E2 04

称

図

C1CP051300-X4

番

容

7

承認調査

8

富士通株式会社

9

ペ

|

22 81

ジ

提出先

Page 23

1

2

3

4

5

6

7

8

9

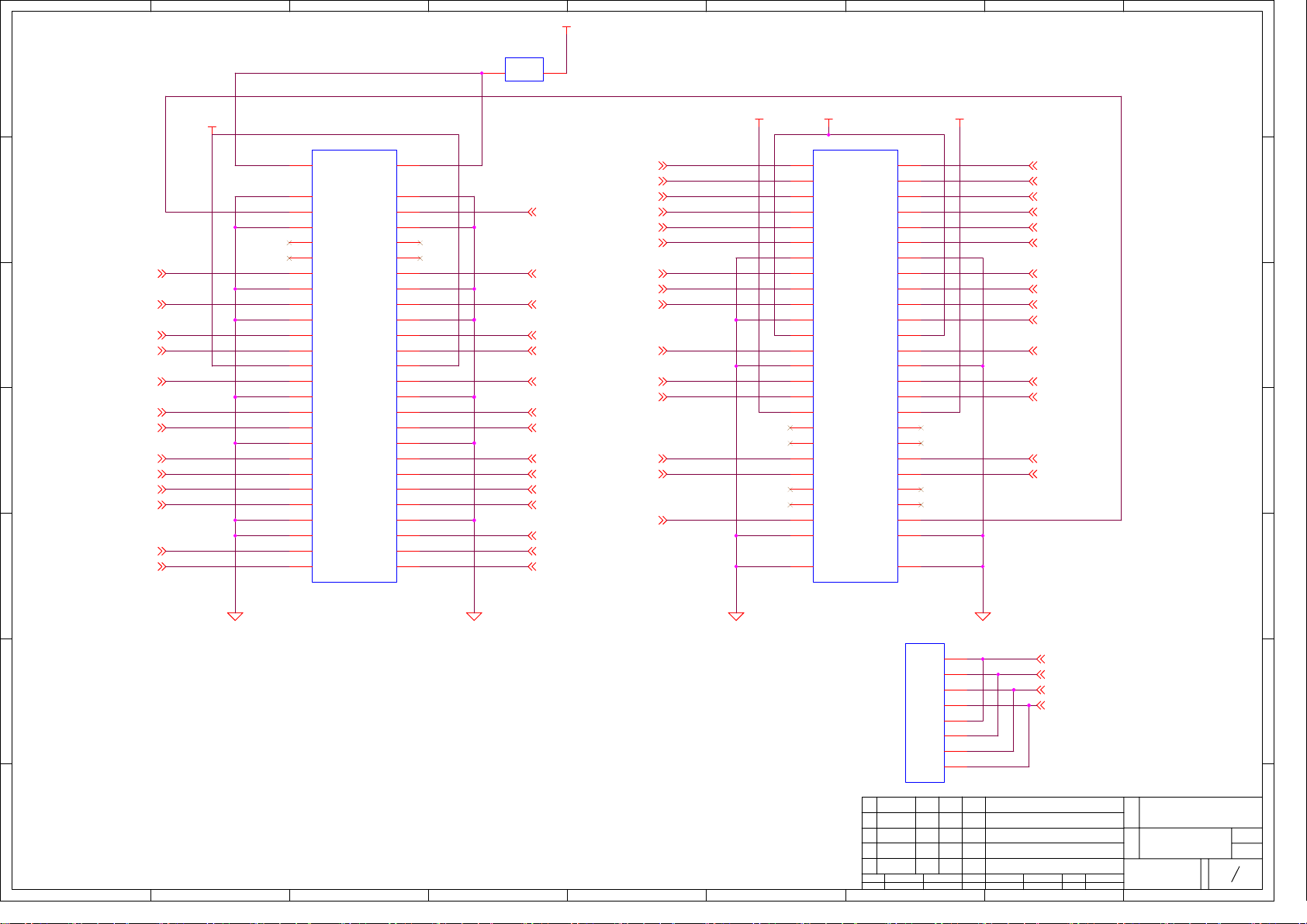

M8A

HCLKIN

A#3

A#4

A#5

A#6

A#7

A#8

A#9

A#10

A#11

A#12

A#13

A#14

A#15

A#16

A#17

A#18

A#19

A#20

A#21

A#22

A#23

A#24

A#25

A#26

A#27

A#28

A#29

A#30

A#31

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

BANISTER

R23

N22

R25

N24

M24

M23

M22

N26

N25

M25

M26

H23

N23

U25

J24

P25

P22

T25

P23

P26

L22

L26

J21

K23

L23

K22

L25

J23

L24

K26

K25

T26

T23

T22

V25

A A

HA#[3:35]18

B B

C C

HREQ#[0:4]18

HCLKBANI47

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#31

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

D D

ADS#18

DRDY#18

DBSY#18

HIT#18

HITM#18

RS#018

E E

RS#118

RS#218

HLOCK#18

HTRDY#18

BFERR#22

KBINIT#58

KBA20G58

V26

U22

U21

V23

U26

W26

V24

V21

U23

T24

ADS#

DRDY#

DBSY#

HIT#

HITM#

RS#0

RS#1

RS#2

HLOCK#

HTRDY#

B1

FERR#

D4

RCIN#

C4

A20GATE

F F

12

GND1

C758

r 100pF 25V

RESERVE

BANISTER

CPURST#

HD#0

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

BNR#

DEFER#

BPRI#

BREQ0#

IGNNE#

INIT#

INTR

A20M#

SMI#

STPCLK#

NMI

J26

G24

G26

E26

D24

H26

F25

J25

E25

H21

J22

G25

F23

G23

C25

F26

H25

B25

F24

D25

D26

D23

C24

G22

H22

B24

E22

C26

C23

A23

A25

E23

B26

E21

B23

C21

A24

B22

D21

F19

D22

C17

B20

A21

B21

D20

D19

E20

F18

E19

C20

E16

A22

C18

A20

E17