Page 1

1

2

3

4

5

6

7

8

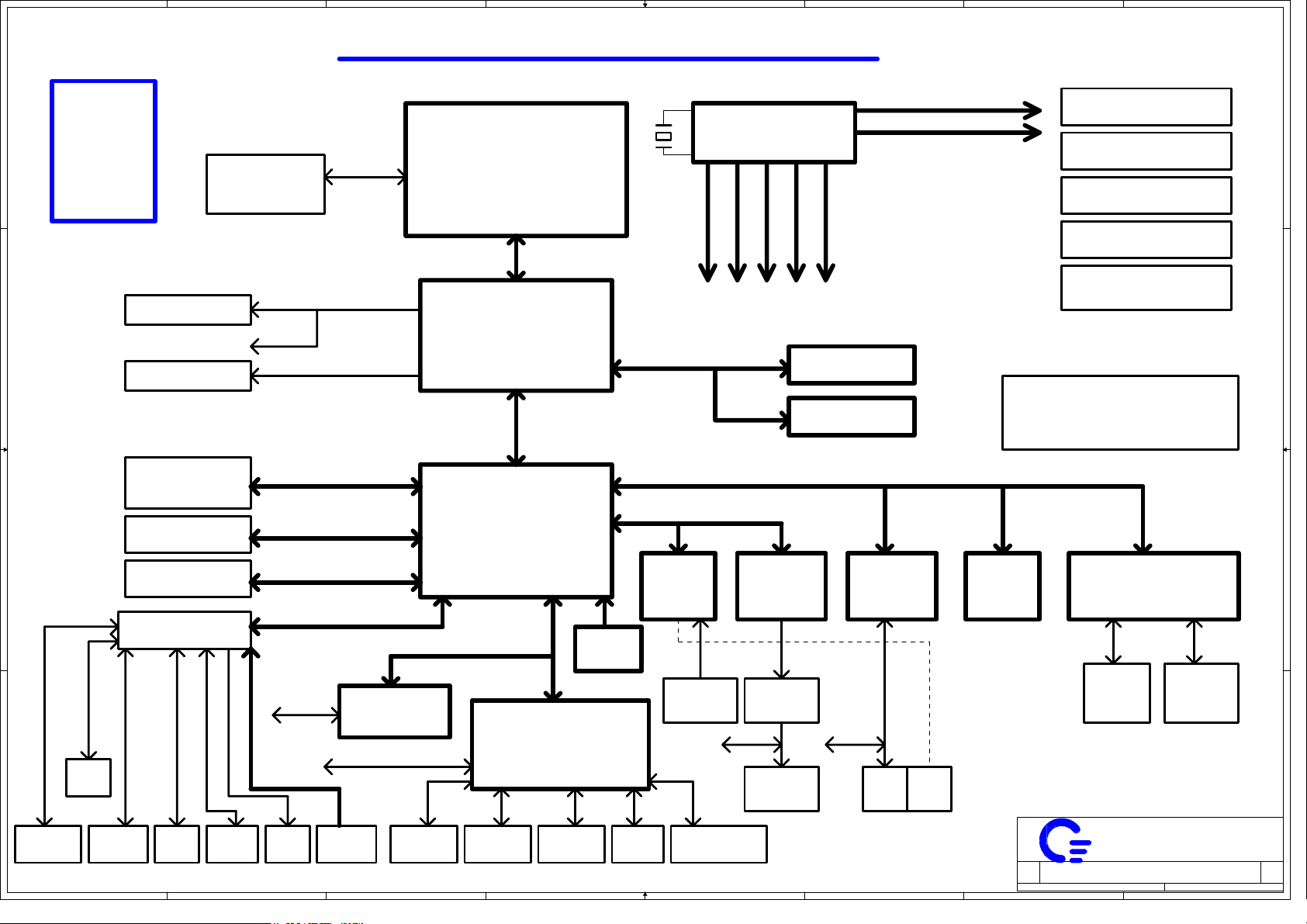

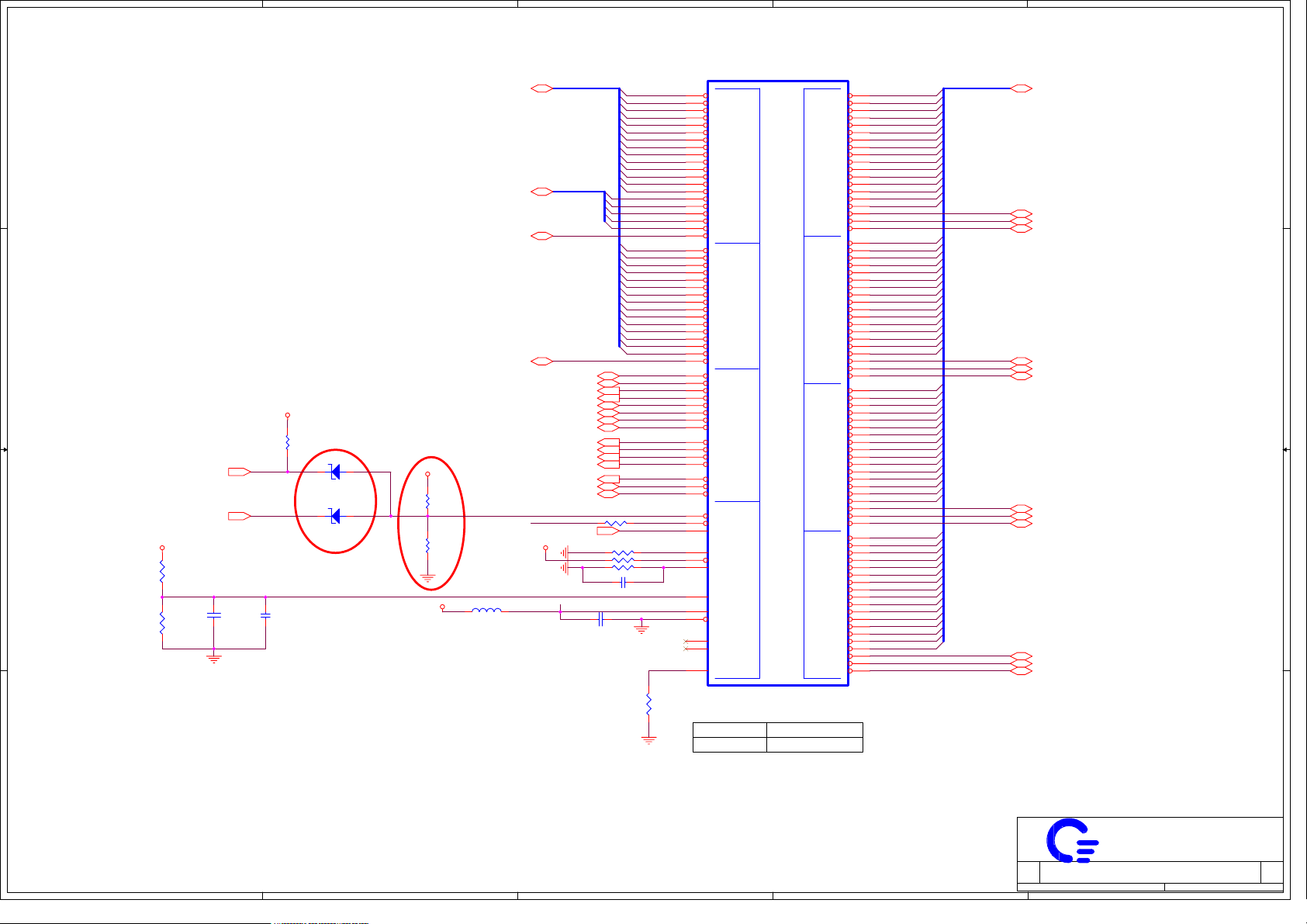

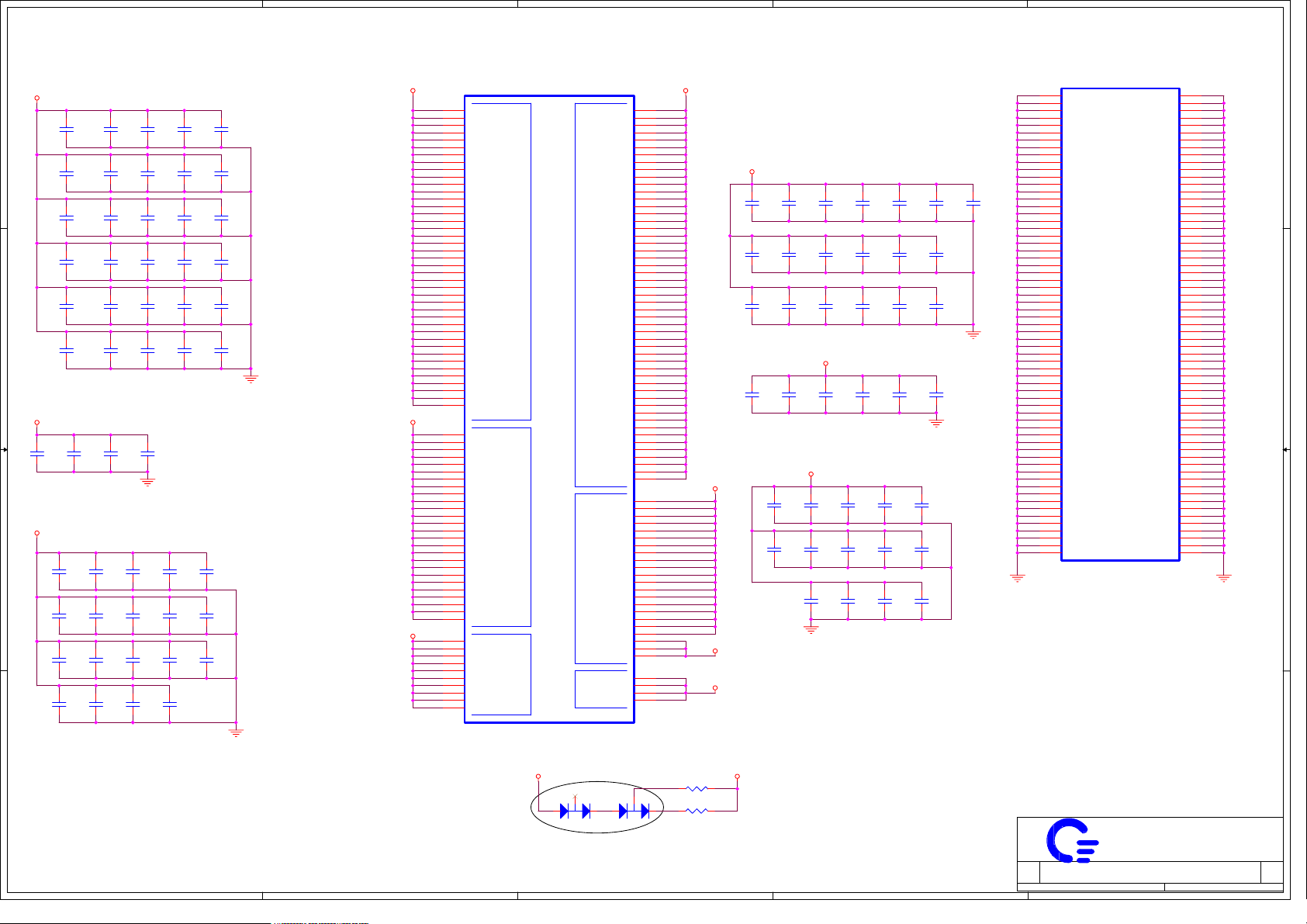

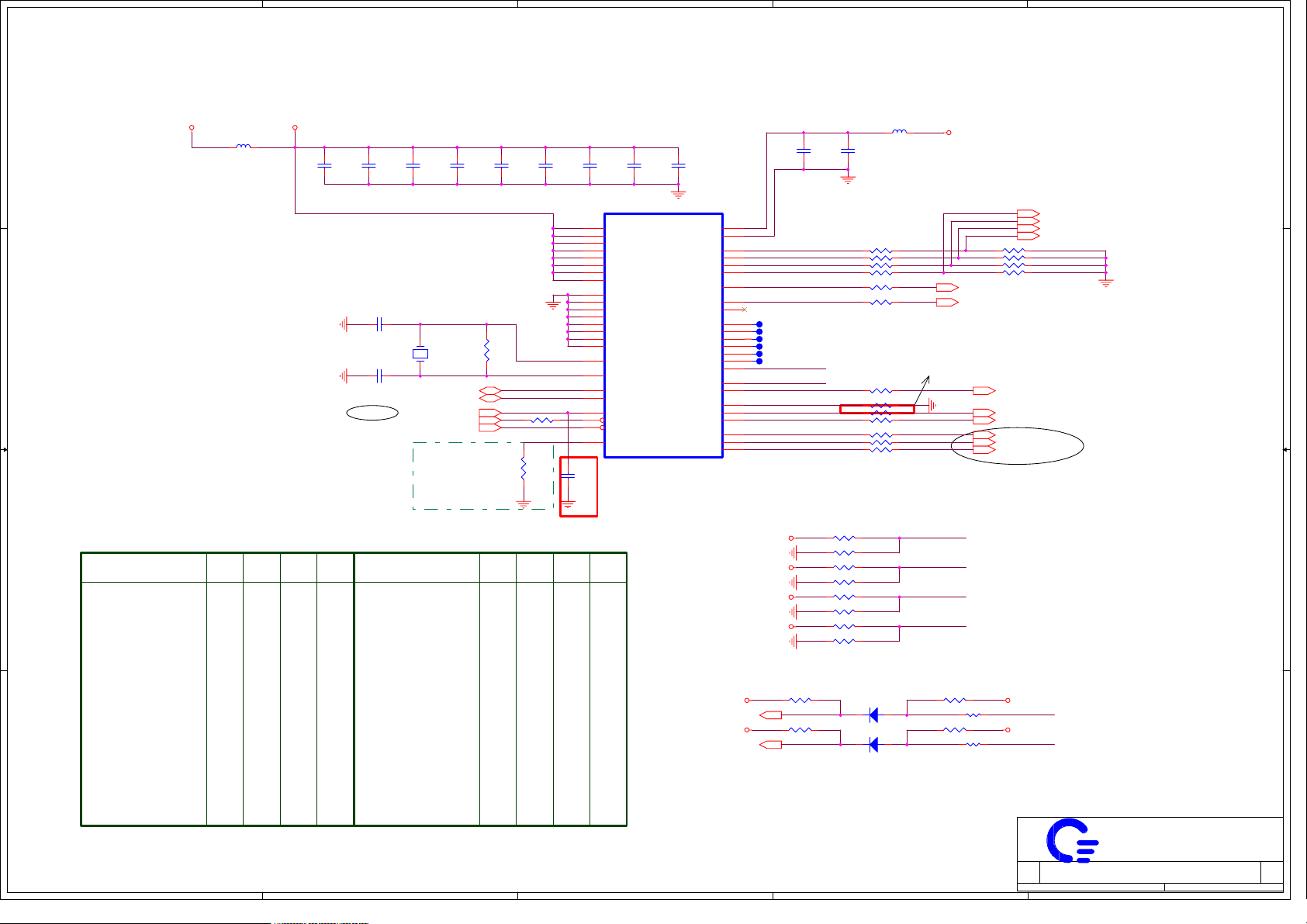

EF5 BLOCK DIAGRAM

PCB STACK UP

LAYER 1 : TOP

A A

LAYER 2 : VCC

LAYER 3 : IN1

LAYER 4 : IN2

LAYER 5 : GND

LAYER 6 : BOT

CPU THERMAL

SENSOR

GMT781

PAGE 3

NORTHWOOD-PRESCOOT/RC300ML/IXP150

HCLK_CPU/HCLK_CPU#

HCLK_NB/HCLK_NB#

CLK_SB_14M

IIC BUS

INTEL CPU

NORTHWOOD/ PRESCOOT

478 Pins (micro FC-PGA)

PAGE 3, 4

14.318MHz

CLOCK GENERATOR

ICS 951402

CLK_ALINK_SB

AGPCLK

NB_DDRCLK

REFCLK1_NB

PAGE 13

PSB

4X133MHZ

CRT port

B B

LCD CONN

PAGE 14

To P/R

PAGE 14

USB PORT 0,1

USB PORT 2,3

PAGE 26

1st IDE - HDD

PAGE 25

C C

CRT

D D

PORT

2nd IDE - CDROM

PAGE 25

PORT-REPLICATOR

PAGE 34

R.G,B

NORTH BRIDGE

RC300ML

718 BGA

LVDS

INTEGRADED VGA FUNCTION

PAGE 5, 6, 7, 8, 9, 10

ALINK

66MHZ

USB 2.0 * 4

SOUTH BRIDGE

ATA 66/100

ATA 66/100

INTEGRADED PCI-CLK FUNCTION

USB 2.0 * 2

To P/R

COM*1

PRT*1 To P/R

To P/R

SIO PC87383

MTDPA-64P

PAGE 33

PS/2 Interface

IXP150

457 BGA

PAGE 15,16,17,18

3.3V LPC, 33MHz

PCPP97551VPC

TQFP 176S

DDR I/F 2.5V, 333/400MHz

33MHZ, 3.3V PCI

AC-LINK

AMCODEC

CONEXANT

20468-31 20463-31

RTC

Power

PAGE 29

PAGE 30

PAGE 27

MIC IN

JACK

PAGE 29

MODEM DAA

CONEXANT

WIRE

PAGE 28

AMP

TPA0212

PAGE 29

To P/R

H/P JACK

PAGE 29

DDR-SODIMM1

PAGE 11,12

DDR-SODIMM2

PAGE 11,12

LAN

BROADCOM

4401(10/100M)

RJ45

JACK

PAGE 22

RJ11

JACK

MINI-PCI

WIRELESS

LAN

POWER-SOURCE CONTROL

AC-IN_BATT CHARGER

MAX1772

CPU CORE POWER

ISL6248

SYSTEM POWER(3/5V)

MAX1999

SYSTEM POWER(1.5V/2.5V)

MAX1845

SYSTEM POWER

DDR_VTERM

GMT-LP2996,SC1565

PCI BUS ROUTING TABLE

====================================

VGA -- INTA#

PCMCIA -- AD17, INTB#, INTC#, REQ0#, GNT0#

MINIPCI -- AD18, INTC#, INTD#, REQ1#, GNT1#

LAN -- AD16, INTD#, REQ2#, GNT2#

CARDBUS CONTROLLER

( EMBEDDED CARDER I/F )

TI 1610

PAGE 24

CARDBUS

SLOT

PAGE 20

PAGE 35

PAGE 36,37

PAGE 38

PAGE 39

1.25V/1.8V

PAGE 39

CAREADER

CONN.(3*1)

01

PAGE 19

PAGE 21

COM&PRT

PORT

USB PORT

5,6

1

RJ45

JACK

PS/2

CONN.

H/P

JACK

2

POWER

JACK

FAN

3

PAGE 32

Touchpad

PAGE 34 PAGE 31 PAGE 30

Keyboard

4

FLASH

SWITCH & LED

PAGE 31

5

PROJECT : EF5

Quanta Computer Inc.

Size Document Number Rev

6

Date: Sheet

7

BLOCK DIAGRAM

140Thursday, June 10, 2004

8

1ACustom

of

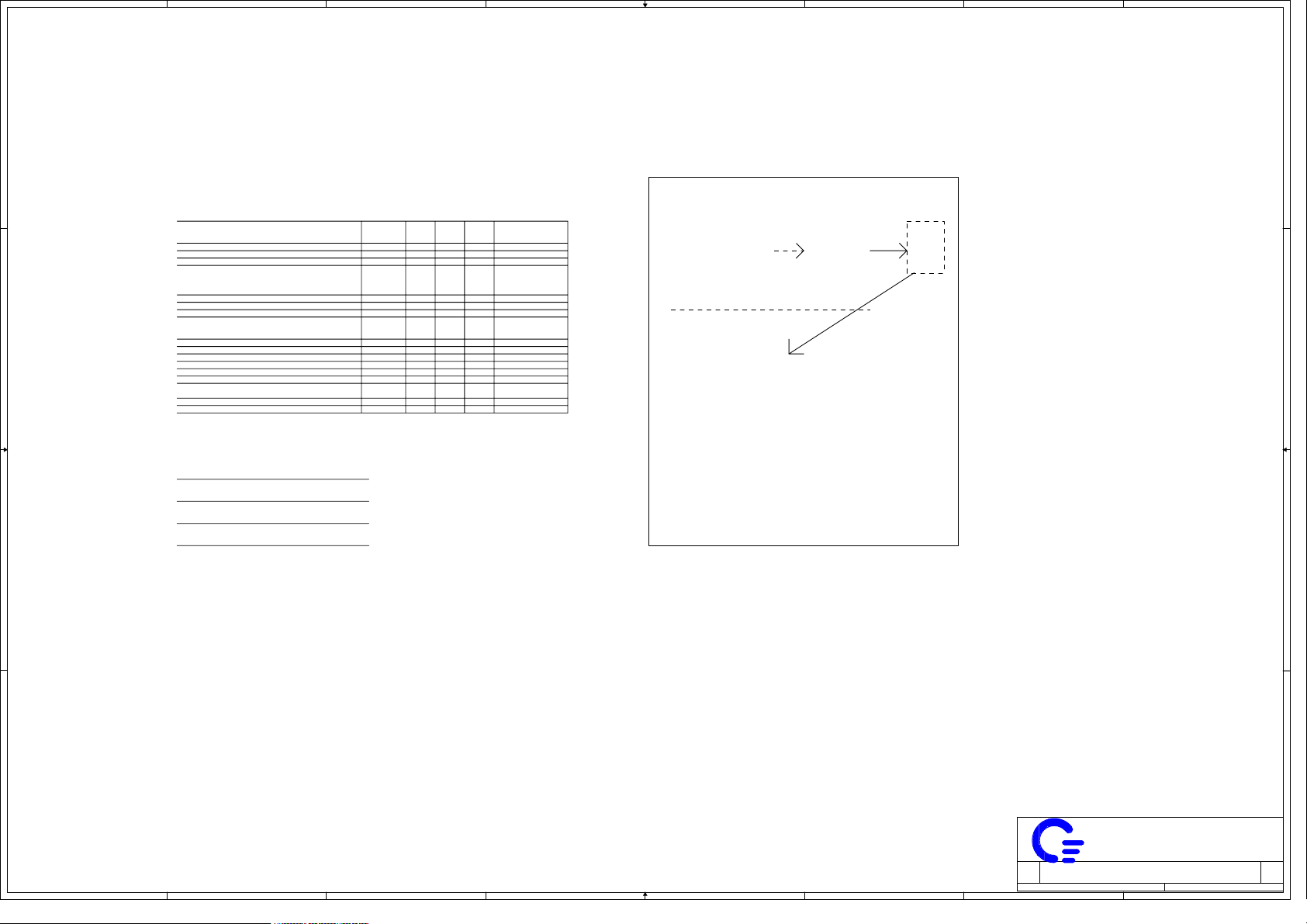

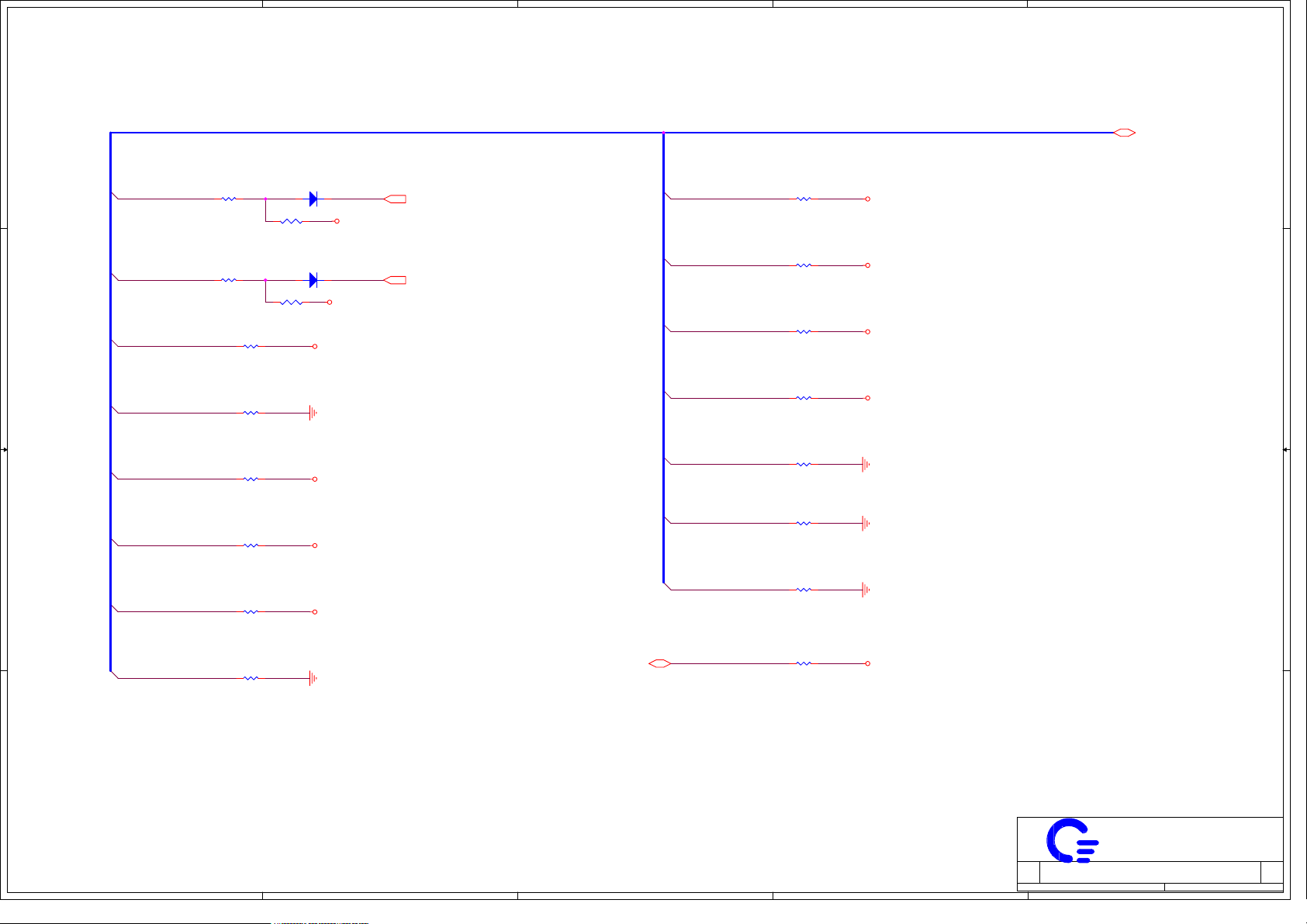

Page 2

1

2

3

4

5

6

7

8

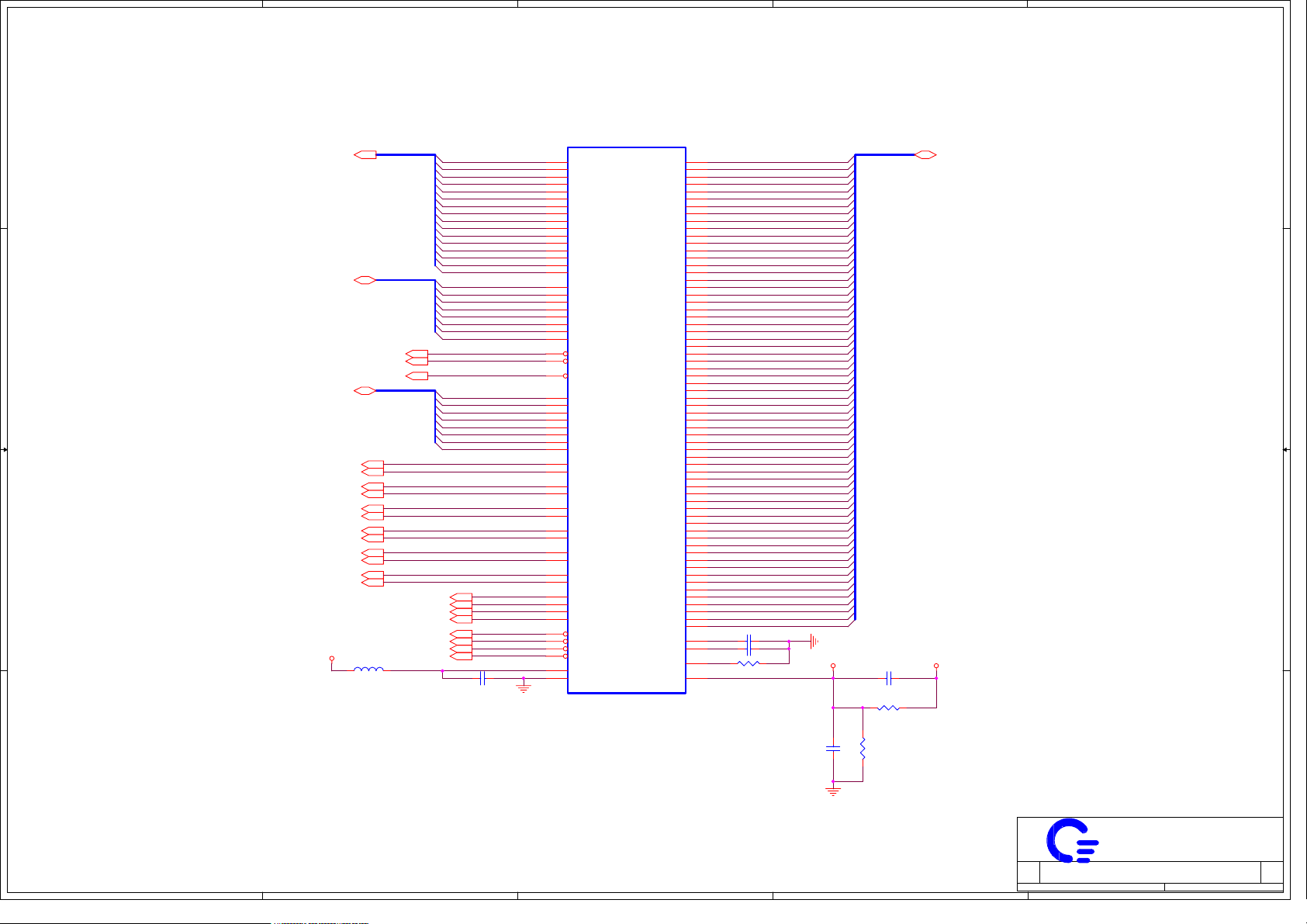

SYSTEM INFORMATION 02

A A

POWER SEQUENCE

Voltage Rails ON S0~S1

VCC_CORE

SMDDR_VREF 1.25V for DDR Reference voltage

SMDDR_VTERM

1.5V

1.8V

B B

C C

2.5VSUS

2.5V

2.5VPCU X X X

3VPCU

3VSUS

3V

5VPCU

5VSUS

5V

PCI DEVICE REQ/GNT#

LAN(10/100) AD16

CARDBUS

MINI-PCI

Core voltage for Processor

Core voltage for Processor X

1.25V for DDR Termination voltage X MAINON

IDSEL#

AD17

AD18

Interrupts

2/2

0/0

1/1

INTD#

INTB#, INTC#

INTC#, INTD#

ON S3 ON S4 ON S5

X SUSONX

X

X

X

X

X

X

X XXX

XX

X

X XXX

XX

X

Control signal

VR_ON

MAINON

MAINON

SUSON

MAINON

VL

VL

SUSON

MAINON

VL

SUSON

MAINON

VIN

NBSWON#

3VPCU

RSMRST#

5VPCU

10V

NBSWON#

S5_ON

SUSON

SUS-POWER (2.5VSUS.....etc)

MAINON

S0-POWER (3V,5V.....etc)

CPU_VIDPGD

VCORE_PGD_CPU

***

***

HWPG

NB_PWRGD

PWROK

NB_RST#

CPUPWRGD

NB_RST#

CPURST#

SUSB#

SUSC#

PWSW

D D

PROJECT : EF5

Quanta Computer Inc.

Size Document Number Rev

1

2

3

4

5

6

Date: Sheet

7

SYSTEM INFORMATION

240Thursday, June 10, 2004

8

1ACustom

of

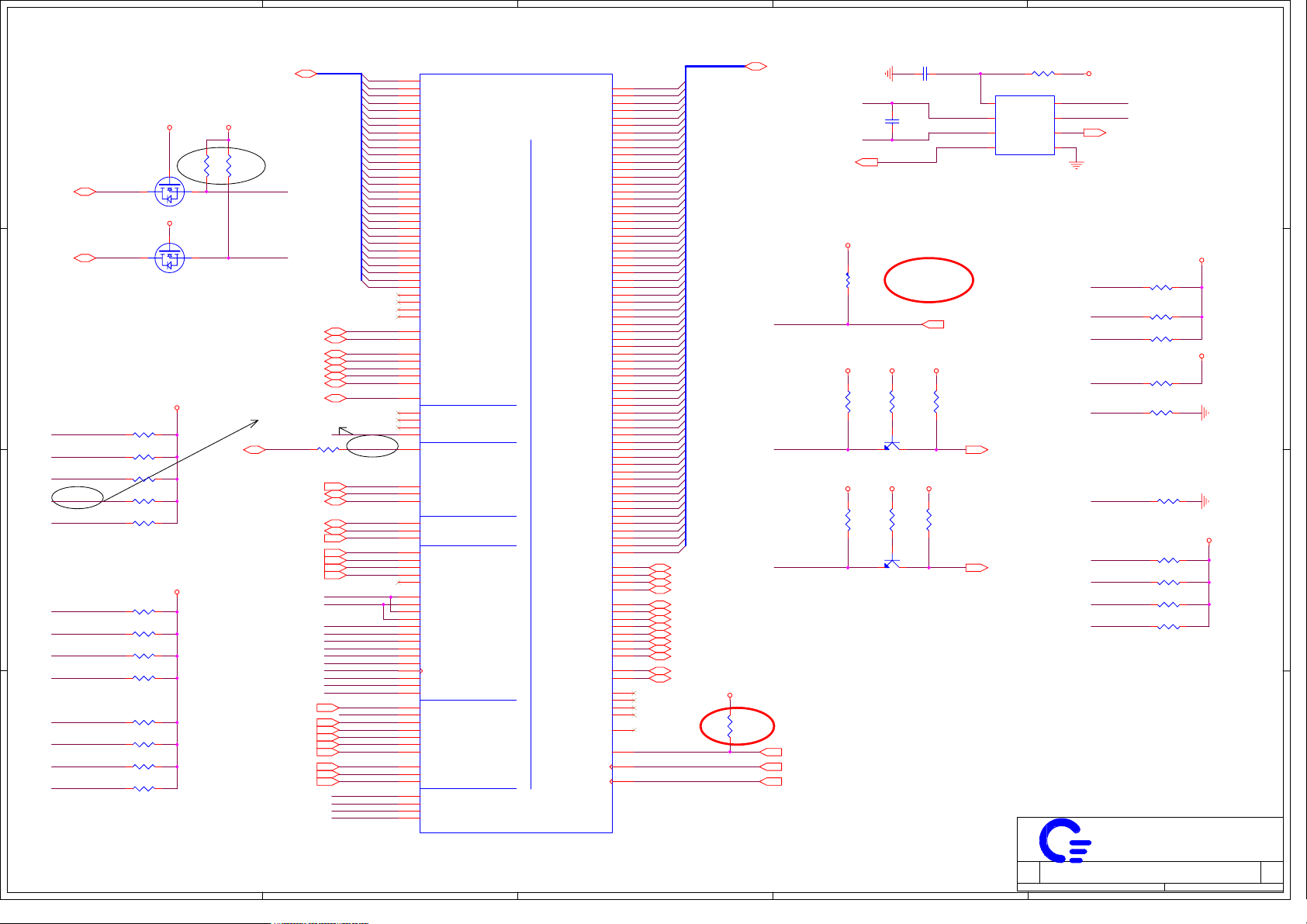

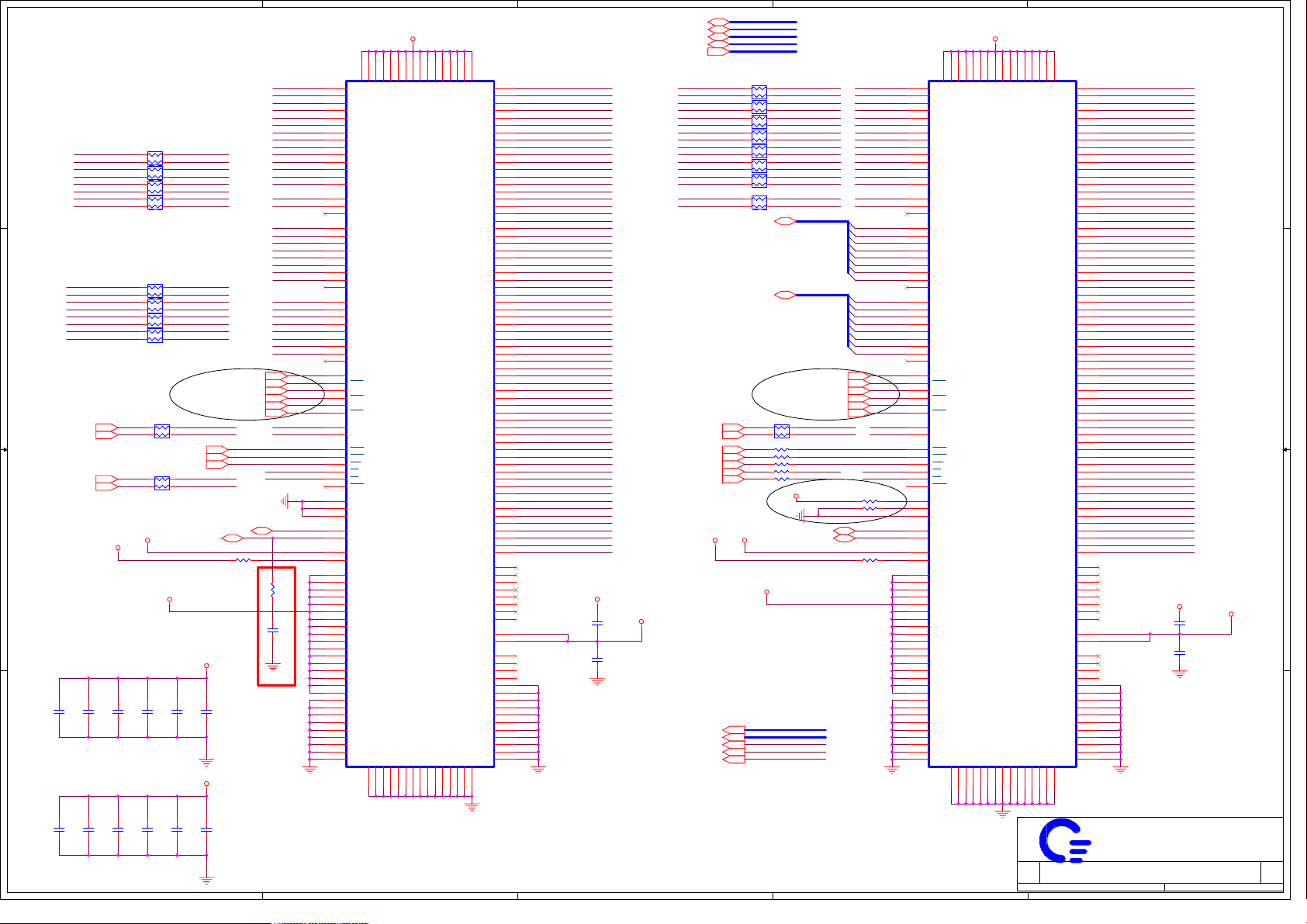

Page 3

A

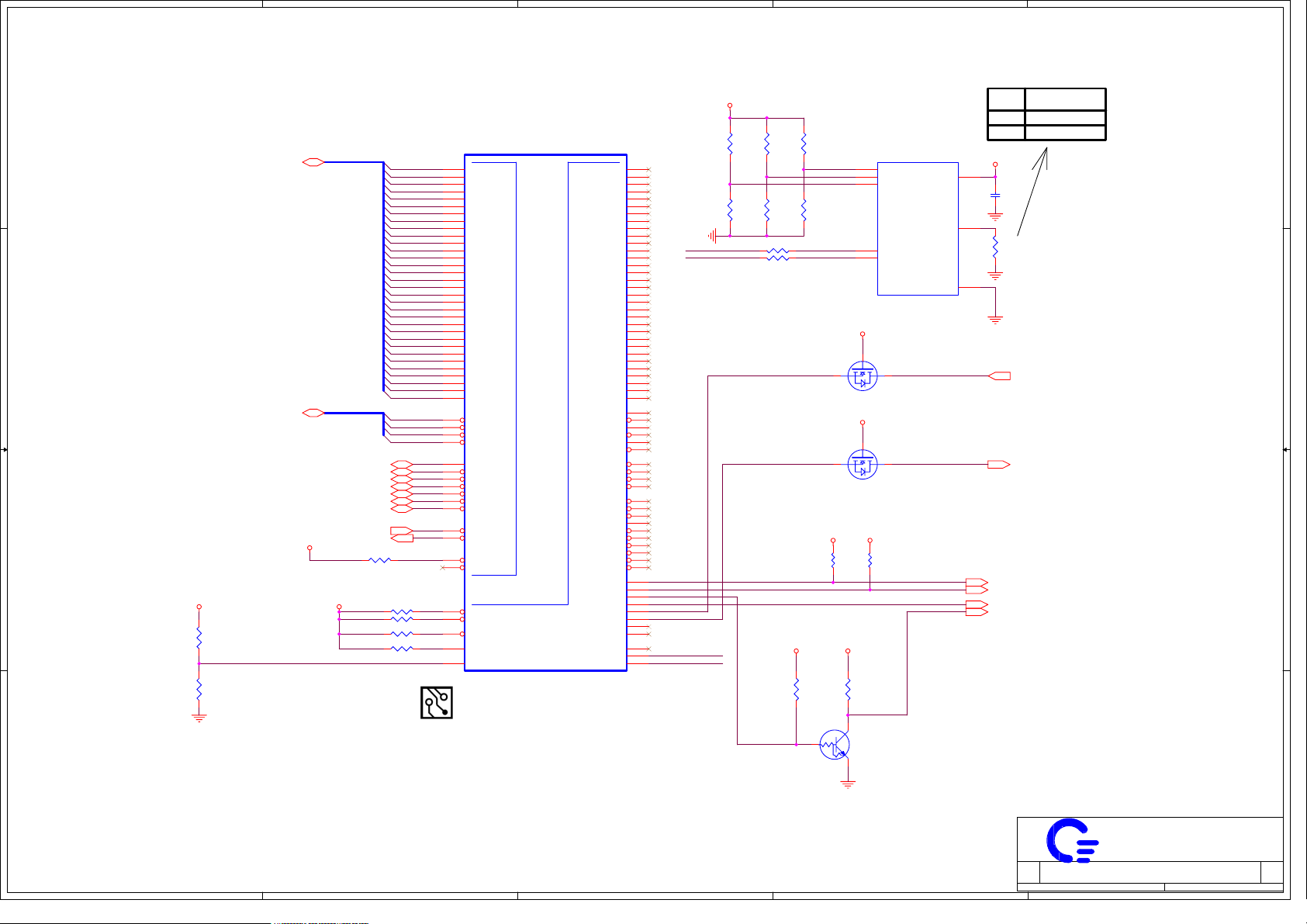

NORTHWOOD/Mobile-PRESCOTT CPU - HOST BUS

HADSTB0#5

HADSTB1#5

HREQ#05

HREQ#15

HREQ#25

HREQ#35

HREQ#45

R742 *0

BPRI#5

HLOCK#5

HITM#5

DEFER#5

HTRDY#5

A20M#15

IGNNE#15

SMI#15

CPUINIT#15

CPU_SLP#15

STPCLK#15

INTR15

NMI15

ADS#5

BNR#5

RS#05

RS#15

RS#25

HA#[3..31]

HIT#5

HA#[3..31]5

R395

10K

1

Q37

2N7002E

1

Q38

2N7002E

3V5V

EC1,Apr/04

R260

10K

DAT_SMBMBDATA

EC2,Apr/04

HBREQ0#5

CPUPWRGD15

4 4

2

MBCLK CLK_SMB

MBCLK30,35

MBDATA30,35

3 3

H_IERR#

ITP_CLK

ITP_CLK#

HBREQ#

CPUPWRGD

2 2

A20M#

IGNNE#

SMI#

CPU_SLP#

STPCLK#

INTR

NMI

1 1

CPUINIT#

3

5V

2

3

VCC_CORE

R48 51

R391 62/F

R393 62/F

R96 51

R387 300/F

VCC_CORE

R100 200

R105 200

R101 200

R390 200

R61 200

R107 200

R103 200

R70 200

A

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

H_IERR#

HBREQ#HBREQ0#

BPM0#

BPM1#

BPM4#

BPM5#

ITP_TDO

ITP_TDI

ITP_TMS

ITP_TRST#

ITP_TCK

ITP_CLK

ITP_CLK#

ITP_DBR#

A20M#

FERR#_R

IGNNE#

CPUPWRGD

SMI#

CPUINIT#

CPU_SLP#

STPCLK#

INTR

NMI

THERMDA

THERMDC

THERMTRIP#

CPUPROCHOT#

B

U35A

K2

A3#

K4

A4#

L6

A5#

K1

AB1

AC1

AA3

AC3

AB2

AC6

AB5

AC4

AA5

AB4

AC26

AD26

AE25

AB23

AB26

L3

M6

L2

M3

M4

N1

M1

N2

N4

N5

T1

R2

P3

P4

R3

T2

U1

P6

U3

T4

V2

R6

W1

T5

U4

V3

W2

Y1

L5

R5

J1

K5

J4

J3

H3

G1

V5

H6

D2

G2

G4

F3

E3

E2

J6

F1

G5

F4

Y6

D5

C1

F7

E6

D4

C6

B6

B2

B5

W5

Y4

D1

E5

B3

C4

A2

C3

A6#

A7#

A8#

A9#

A10#

A11#

A12#

A13#

A14#

A15#

A16#

A17#

A18#

A19#

A20#

A21#

A22#

A23#

A24#

A25#

A26#

A27#

A28#

A29#

A30#

A31#

A32#

A33#

A34#

A35#

ADSTB0#

ADSTB1#

REQ0#

REQ1#

REQ2#

REQ3#

REQ4#

ADS#

AP0#

AP1#

BINIT#

IERR#

BR0#

BPRI#

BNR#

LOCK#

HIT#

HITM#

DEFER#

TRDY#

RS0#

RS1#

RS2#

RSP#

BPM0#

BPM1#

BPM2#

BPM3#

BPM4#/ITP_PRDY#

BPM5#/ITP_PREQ#

TDO

TDI

TMS

TRST#

TCK

ITP_CLK0

ITP_CLK1

DBRESET#

A20M#

FERR#

IGNNE#

PWRGOOD

SMI#

INIT#

SLP#

STPCLK#

INTR/LINT0

NMI/LINT1

THERMDA

THERMDC

THERMTRIP#

PROCHOT#

PRESCOTT

1 OF 3

REQUEST

PHASE

SIGNALS

ERROR

SIGNALS

ARBITRATION

PHASE

SIGNALS

SNOOP PHASE

SIGNALS

RESPONSE

PHASE

SIGNALS

ITP

PC

COMPATIBILITY

SIGNALS

EXECUTION

CONTROL

SIGNALS

THERMAL DIODE

NORTHWOOD/Mobile-PRESCOTT

B

DATA

PHASE

SIGNALS

D10#

D11#

D12#

D13#

D14#

D15#

D16#

D17#

D18#

D19#

D20#

D21#

D22#

D23#

D24#

D25#

D26#

D27#

D28#

D29#

D30#

D31#

D32#

D33#

D34#

D35#

D36#

D37#

D38#

D39#

D40#

D41#

D42#

D43#

D44#

D45#

D46#

D47#

D48#

D49#

D50#

D51#

D52#

D53#

D54#

D55#

D56#

D57#

D58#

D59#

D60#

D61#

D62#

D63#

DBI0#

DBI1#

DBI2#

DBI3#

DSTBN0#

DSTBP0#

DSTBN1#

DSTBP1#

DSTBN2#

DSTBP2#

DSTBN3#

DSTBP3#

DBSY#

DRDY#

DP0#

DP1#

DP2#

DP3#

MCERR#

RESET#

BCLK1

BCLK0

C

D

E

03

HD#[0..63]

HD#0

B21

D0#

D1#

D2#

D3#

D4#

D5#

D6#

D7#

D8#

D9#

B22

A23

A25

C21

D22

B24

C23

C24

B25

G22

H21

C26

D23

J21

D25

H22

E24

G23

F23

F24

E25

F26

D26

L21

G26

H24

M21

L22

J24

K23

H25

M23

N22

P21

M24

N23

M26

N26

N25

R21

P24

R25

R24

T26

T25

T22

T23

U26

U24

U23

V25

U21

V22

V24

W26

Y26

W25

Y23

Y24

Y21

AA25

AA22

AA24

E21

G25

P26

V21

E22

F21

K22

J23

R22

P23

W22

W23

H5

H2

J26

K25

K26

L25

V6

AB25

AF23

AF22

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

C

HDBI0# 5

HDBI1# 5

HDBI2# 5

HDBI3# 5

HDSTBN0# 5

HDSTBP0# 5

HDSTBN1# 5

HDSTBP1# 5

HDSTBN2# 5

HDSTBP2# 5

HDSTBN3# 5

HDSTBP3# 5

DBSY# 5

DRDY# 5

CPURST#

HCLK_CPU#

HCLK_CPU

VCC_CORE

R388

*51

HD#[0..63] 5

1999RESET#38

CPUPROCHOT#

THERMTRIP#

FERR#_R

EC37,May/14

CPURST# 5

HCLK_CPU# 13

HCLK_CPU 13

C190 .1U

C180

2200P

Route both signals on the same layer

VCC_CORE

R89

51

R90

56

1 3

R92

51

1 3

EC36,May/14

3VSUSVCC_CORE VCC_CORE

R94

10K

2

Q16

MMBT3904

3VSUSVCC_CORE VCC_CORE

R91

10K

2

Q15

MMBT3904

D

CPU Thermal Sensor.

6657VCC

THERMDA

THERMDC

GMT_G781/MAX6657

CPUPROCHOT# 35

R95

10K

R93

10K

R114 100/F

U10

1

SMBC

VCC

2

DXP

SMBD

3 6

DXN ALERT#

4

GND

OVERT#

SOIC8

Address : 4C

THERMTRIP_SIO# 16

FERR# 15

8

7

5

3V

CLK_SMB

DAT_SMB

ITP_TDI

ITP_TMS

ITP_TDO

ITP_DBR#

ITP_TCK

TEMP_ALARM# 16

R110 150/F

R119 39/F

R118 75/F

R45 150/F

R258 27.4/F

ITP_TRST#

BPM0#

BPM1#

BPM4#

BPM5#

VCC_CORE

3V

R99 680

VCC_CORE

R50 51

R59 51

R60 51

R49 51

Close to CPU

PROJECT : EF5

Quanta Computer Inc.

Size Document Number Rev

Date: Sheet

PRESCOTT(HOST BUS)

E

1ACustom

of

340Thursday, June 10, 2004

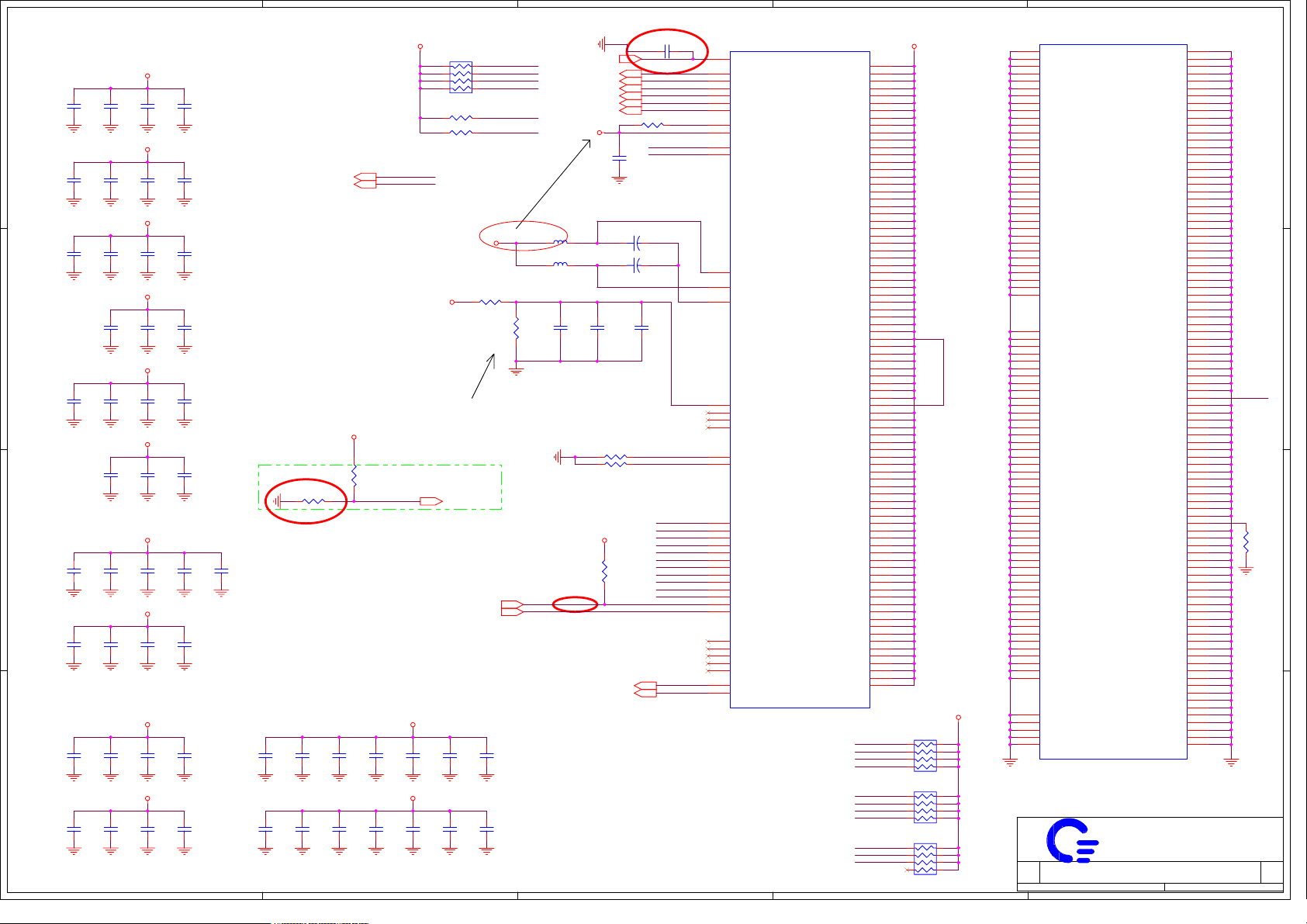

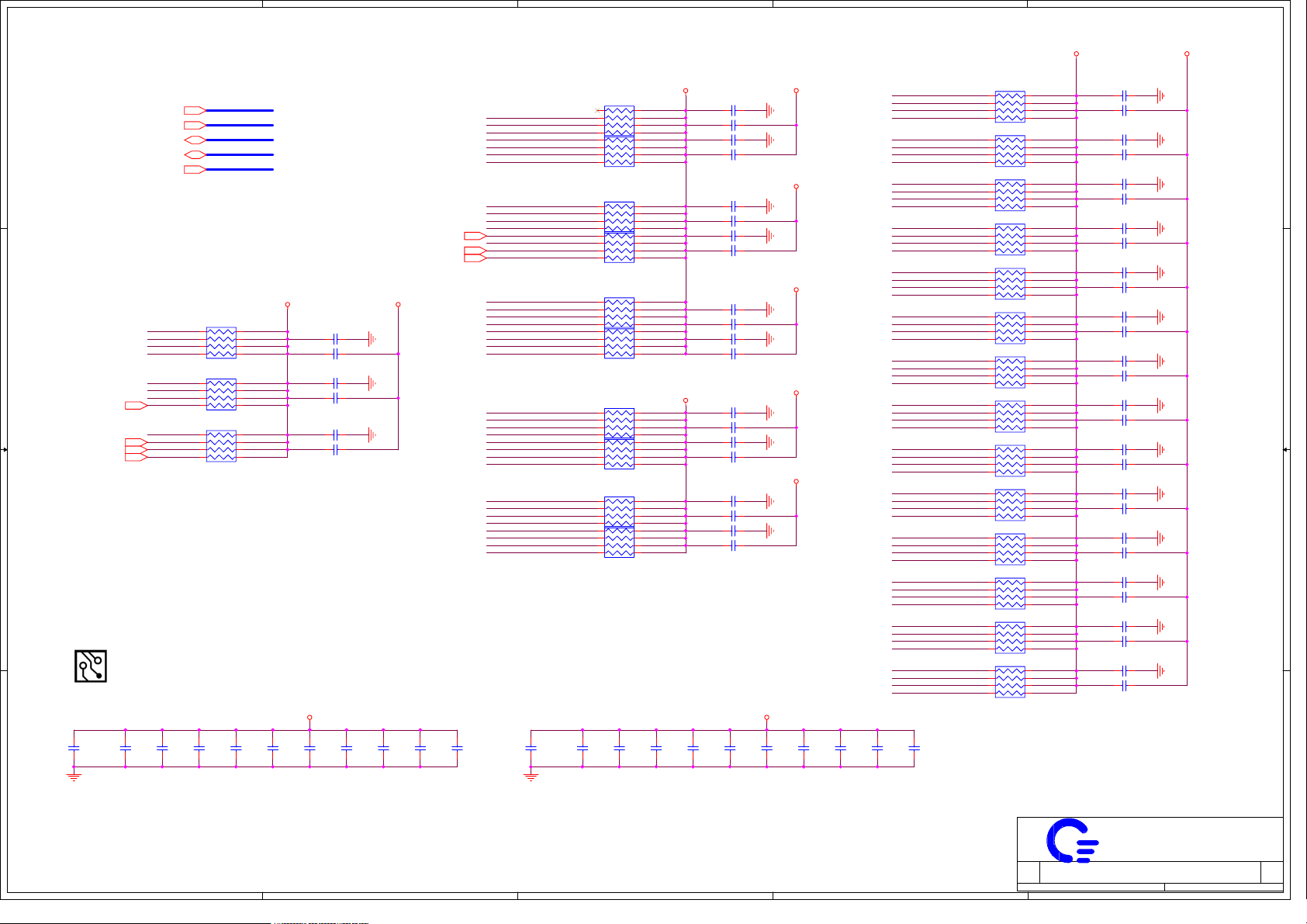

Page 4

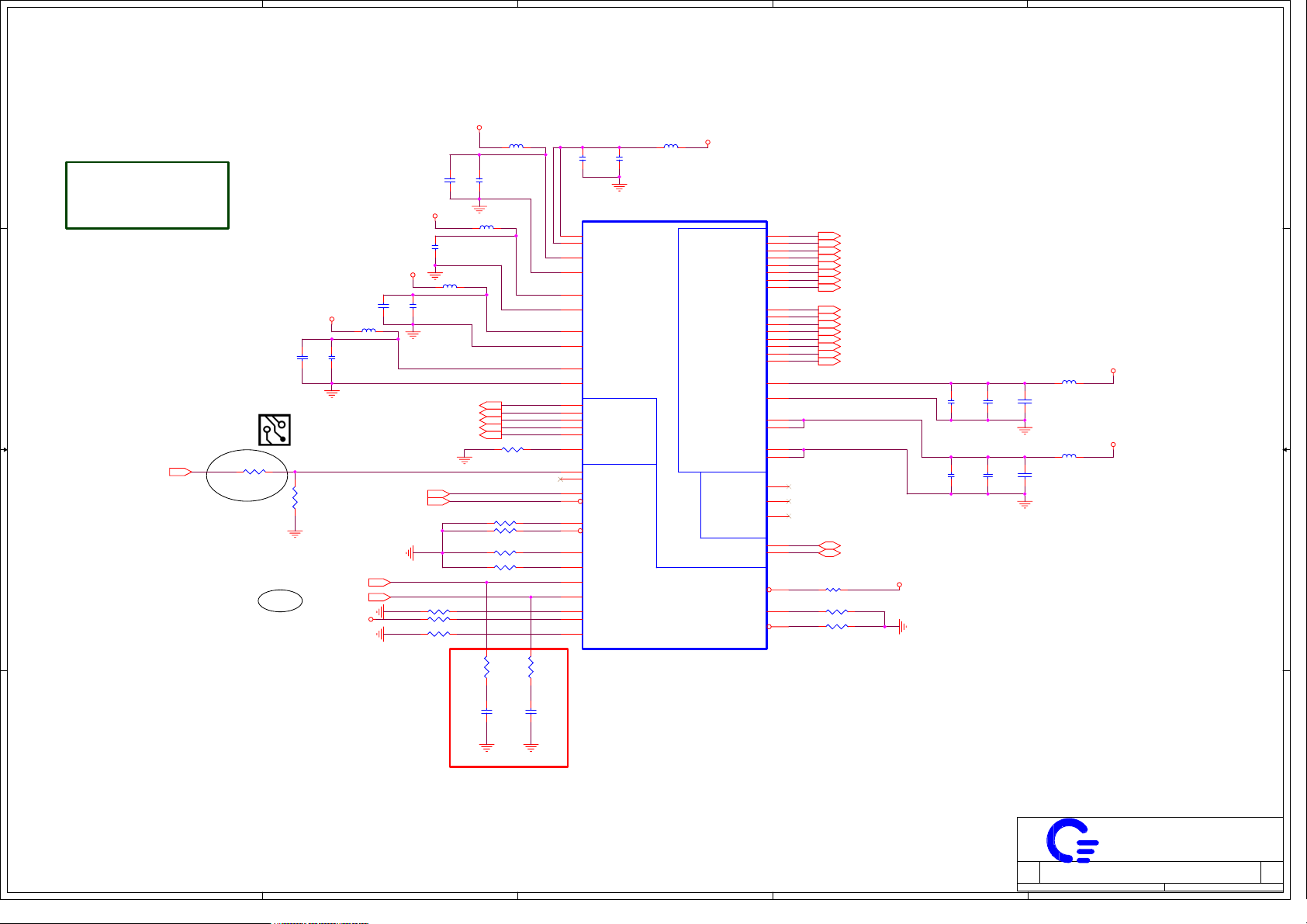

A

NORTHWOOD/Mobile-PRESCOTT CPU - PWR/GND

VCC_CORE

C174

4 4

3 3

2 2

1 1

.47U/10V

10V

X7R

C173

.47U/10V

10V

X7R

C95

.47U/10V

10V

X7R

C109

.47U/10V

10V

X7R

C44

10U/6.3V

X5R

C45

10U/6.3V

X5R

C91

.47U/10V

10V

X7R

C183

.47U/10V

10V

X7R

C93

.47U/10V

10V

X7R

VCC_CORE

C187

.47U/10V

10V

X7R

VCC_CORE

C169

.47U/10V

10V

X7R

VCC_CORE

C111

.47U/10V

10V

X7R

VCC_CORE

C178

.47U/10V

10V

X7R

VCC_CORE

C94

.47U/10V

10V

X7R

VCC_CORE

C38

10U/6.3V

X5R

VCC_CORE

C49

10U/6.3V

X5R

VCC_CORE

C168

.47U/10V

10V

X7R

VCC_CORE

C175

.47U/10V

10V

X7R

C82

C171

.47U/10V

.47U/10V

10V

10V

X7R

X7R

C185

.47U/10V

10V

X7R

C170

.47U/10V

10V

X7R

C110

.47U/10V

10V

X7R

C106

.47U/10V

10V

X7R

C108

.47U/10V

10V

X7R

C92

.47U/10V

10V

X7R

C97

.47U/10V

10V

X7R

C184

.47U/10V

10V

X7R

C96

.47U/10V

10V

X7R

C105

.47U/10V

10V

X7R

VCCSENSE36

VSSSENSE36

R743 *1K

VCC_CORE

NORTHWOOD/PRESCOOT REQUIRED

EC39,May/24

C43

C71

C39

10U/6.3V

X5R

C34

10U/6.3V

X5R

C182

.47U/10V

10V

X7R

C172

.47U/10V

10V

X7R

A

10U/6.3V

X5R

C59

10U/6.3V

X5R

C186

.47U/10V

10V

X7R

C107

.47U/10V

10V

X7R

10U/6.3V

X5R

C37

10U/6.3V

X5R

C123

10U/6.3V

X5R

C50

10U/6.3V

X5R

C138

10U/6.3V

X5R

R41

*1K

C60

10U/6.3V

X5R

C162

10U/6.3V

X5R

SELECT

C72

10U/6.3V

X5R

C70

10U/6.3V

X5R

B

VCCSENSE

VSSSENSE

B

3V

R40 1K

R33 1K

EC3,Apr/04

VCC_CORE

VCC_CORE

C161

10U/6.3V

X5R

VCC_CORE

C131

10U/6.3V

X5R

RP3

8P4R-1K

0.63VCC_VORE of GTLREF voltage

for Prescott CPU .

SELECT 36

12

34

56

78

VCC_CORE

R71

49.9/F

CPU_VID0

CPU_VID1

CPU_VID2

CPU_VID3

CPU_VID4

CPU_VID5

R65

86.6/F

CPU_VIDPGD13,16,36

CPU_VID036

CPU_VID136

CPU_VID236

CPU_VID336

CPU_VID436

CPU_VID536

VCCVID

21

L7 4.7UH

21

L6 4.7UH

C129

1U/10V

The 220p needs to close

to CPU AA21 pin.

R74 61.9/F

R73 61.9/F

VCC_CORE

EC40,May/24

CPU_GHI#16

DPSLP#_CPU15

BSEL010,13

BSEL110,13

C33

C58

10U/6.3V

10U/6.3V

X5R

X5R

C134

C154

10U/6.3V

10U/6.3V

X5R

X5R

C

C884 *100P

R36 0

VCCSENSE

VSSSENSE

C81

.1U

RL_CPU_PLL

+

C546 33U_10V

+

C554 33U_10V

RL_CPU_VCCA

VAGTLREF1

C122

C113

220P

220P

CPU_COMP0

CPU_COMP1

HTEST0

HTEST1

HTEST2

HTEST3

HTEST4

HTEST5

R84

200

HTEST6

HTEST7

HTEST8

HTEST9

HTEST10

CPUPERF#

DPSLP#_CPU

C

EC38,May/24

U35B

AD2

VIDPWRGD

AE5

VID0

A5

A4

F6

L24

P1

U6

W4

Y3

A6

A7

VID1

VID2

VID3

VID4

VID5

VCCVIDPRG

VCCVID0

VCCSENSE

VSSSENSE

VCCIOPLL

VCCA

VSSA

GTLREF0

GTLREF1

GTLREF2

GTLREF3

COMP0

COMP1

TESTHI0

TESTHI1

TESTHI2

TESTHI3

TESTHI4

TESTHI5

TESTHI6

TESTHI7

TESTHI8

TESTHI9

TESTHI10

TESTHI11

TESTHI12

NC

NC

NC

NC

NC

BSEL0

BSEL1

PRESCOOT

2 OF 3

VID

POWER

VCC10

VCC11

VCC12

VCC13

VCC14

VCC15

VCC16

VCC17

VCC18

VCC19

VCC20

VCC21

VCC22

VCC23

VCC24

VCC25

VCC26

VCC27

VCC28

VCC29

VCC30

VCC31

VCC32

VCC33

VCC34

VCC35

VCC36

VCC37

VCC38

VCC39

VCC40

VCC41

VCC42

VCC43

VCC44

VCC45

VCC46

VCC47

VCC48

VCC49

VCC50

VCC51

VCC52

VCC53

VCC54

VCC55

VCC56

VCC57

VCC58

VCC59

VCC60

VCC61

VCC62

VCC63

VCC64

VCC65

VCC66

VCC67

VCC68

VCC69

VCC70

VCC71

VCC72

VCC73

VCC74

VCC75

VCC76

VCC77

VCC78

VCC79

VCC80

VCC81

VCC82

VCC83

VCC84

VSSA

AE23

AD20

AD22

AA21

AD24

AC21

AC20

AC24

AC23

AA20

AB22

AD25

AE21

AF24

AF25

AE4

AE3

AE2

AE1

AD3

AF3

AF4

AA6

F20

AA2

A22

AD6

AD5

NORTHWOOD/Mobile-PRESCOTT

VCC0

VCC1

VCC2

VCC3

VCC4

VCC5

VCC6

VCC7

VCC8

VCC9

A10

A12

A14

A16

A18

A20

A8

AA10

AA12

AA14

AA16

AA18

AA8

AB11

AB13

AB15

AB17

AB19

AB7

AB9

AC10

AC12

AC14

AC16

AC18

AC8

AD11

AD13

AD15

AD17

AD19

AD7

AD9

AE10

AE12

AE14

AE16

AE18

AE20

AE6

AE8

AF11

AF13

AF15

AF17

AF19

AF2

AF21

AF5

AF7

AF9

B11

B13

B15

B17

B19

B7

B9

C10

C12

C14

C16

C18

C20

C8

D11

D13

D15

D17

D19

D7

D9

E10

E12

E14

E16

E18

E20

E8

F11

F13

F15

F17

F19

F9

HTEST7

HTEST1

HTEST2

HTEST3

HTEST4

HTEST5

HTEST0

HTEST6

HTEST10

HTEST8

HTEST9

D

VCC_CORE

RP2

56X4

7 8

5 6

3 4

1 2

RP1

56X4

7 8

5 6

3 4

1 2

RP4

56X4

7 8

5 6

3 4

1 2

D

VCC_CORE

E

H1

H4

H23

H26

A11

A13

A15

A17

A19

A21

A24

A26

A3

A9

AA1

AA11

AA13

AA15

AA17

AA19

AA23

AA26

AA4

AA7

AA9

AB10

AB12

AB14

AB16

AB18

AB20

AB21

AB24

AB3

AB6

AB8

AC11

AC13

AC15

AC17

AC19

AC2

AC22

AC25

AC5

AC7

AC9

AD1

AD10

AD12

AD14

AD16

AD18

AD21

AD23

AD4

AD8

AE11

AE13

AE15

AE17

AE19

AE22

AE24

AE26

AE7

AE9

AF1

AF10

AF12

AF14

AF16

AF18

AF20

AF26

AF6

AF8

B10

B12

B14

B16

B18

B20

B23

B26

B4

B8

C11

C13

C15

C17

C19

C2

C22

C25C5

04

SELECT

R46

*100/F

W21

W24

D14

D16

D18

D20

D21

D24

E11

E13

E15

E17

E19

E23

E26

F10

F12

F14

F16

F18

F22

F25

G21

G24

K21

K24

M22

M25

N21

N24

P22

P25

R23

R26

T21

T24

U22

U25

V23

V26

Y22

Y25

D12

D10

D3

D6

D8

E1

E4

E7

E9

F2

F5

F8

G3

G6

J22

J25

K3

K6

L1

L23

L26

L4

M2

M5

N3

N6

P2

P5

R1

R4

T3

T6

U2

U5

V1

V4

W3

W6

Y2

Y5

C9

C7

U35C

J2

J5

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

PRESCOOT

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

VSS161

VSS162

VSS163

VSS164

VSS165

VSS166

VSS167

VSS168

VSS169

VSS170

VSS171

VSS172

VSS173

VSS174

VSS175

VSS176

VSS177

VSS178

VSS179

VSS180

VSS181

VSS182

VSS183

VSS184

VSS185

VSS99

VSS98

VSS97

VSS96

3 OF 3

GROUND

VSS0

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

SKTOCC#

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94VSS95

NORTHWOOD/Mobile-PRESCOTT

PROJECT : EF5

Quanta Computer Inc.

Size Document Number Rev

Date: Sheet

PRESCOTT(POWER/NC)

E

of

440Thursday, June 10, 2004

1ACustom

Page 5

5

4

NorthBridge-ATI RC300M - AGTL+ I/F

3

2

1

05

U36A

HD#0

M28

A3#

P25

A4#

M25

A5#

N29

A6#

N30

A7#

M26

A8#

N28

A9#

P29

A10#

P26

A11#

R29

A12#

P30

A13#

P28

A14#

N26

A15#

N27

A16#

M29

REQ0#

N25

REQ1#

R26

REQ2#

L28

REQ3#

L29

REQ4#

R27

ADSTB0#

U30

A17#

T30

A18#

R28

A19#

R25

A20#

U25

A21#

T28

A22#

V29

A23#

T26

A24#

U29

A25#

U26

A26#

V26

A27#

T25

A28#

V25

A29#

U27

A30#

U28

A31#

T29

ADSTB1#

L27

ADS#

K25

BNR#

H26

BPRI#

J27

DEFER#

L26

DRDY#

G27

DBSY#

F25

BR0#

K26

LOCK#

A17

CPURST#

G25

RS2#

G26

RS1#

J25

RS0#

F26

TRDY#

J26

HIT#

H25

HITM#

AH5

SUS_STAT#

AG5

SYSRST#

C7

POWERGOOD

1%

W29

V28

W28

H23

Y28

Y29

B17

A9

J23

COMP_P

COMP_N

RSET

GTLVREF

CPVDD

CPVSS

THERMAL_D_P

THERMAL_D_N

TESTMODE

1%

1%

1/6

ADDR. GROUP 1 ADDR. GROUP 0CONTROLMISC.

AGTL+ I/F

CPU

D0#

D1#

D2#

D3#

D4#

D5#

D6#

D7#

D8#

D9#

D10#

D11#

DATA GROUP 0DATA GROUP 1DATA GROUP 2DATA GROUP 3

D12#

D13#

D14#

D15#

DBI0#

DSTBN0#

DSTBP0#

D16#

D17#

D18#

D19#

D20#

D21#

D22#

D23#

D24#

D25#

D26#

D27#

D28#

D29#

D30#

D31#

DBI1#

DSTBN1#

DSTBP1#

D32#

D33#

D34#

D35#

D36#

D37#

D38#

D39#

D40#

D41#

D42#

D43#

D44#

D45#

D46#

D47#

DBI2#

DSTBN2#

DSTBP2#

D48#

D49#

D50#

D51#

D52#

D53#

D54#

D55#

D56#

D57#

D58#

D59#

D60#

D61#

D62#

D63#

DBI3#

DSTBN3#

DSTBP3#

L30

K29

J29

H28

K28

K30

H29

J28

F28

H30

E30

D29

G28

E29

D30

F29

E28

G30

G29

B26

C30

A27

B29

C28

C29

B28

D28

D26

B27

C26

E25

E26

A26

B25

C25

A28

D27

E27

F24

D24

E23

E24

F23

C24

B24

A24

F21

A23

B23

C22

B22

C21

E21

D22

D23

E22

F22

B21

F20

A21

C20

E20

D20

A20

D19

C18

B20

E18

B19

D18

B18

C17

A18

F19

E19

F18

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

HD#[0..63]

HD#[0..63] 3

HDBI0# 3

HDSTBN0# 3

HDSTBP0# 3

HDBI1# 3

HDSTBN1# 3

HDSTBP1# 3

HDBI2# 3

HDSTBN2# 3

HDSTBP2# 3

HDBI3# 3

HDSTBN3# 3

HDSTBP3# 3

RC300ML

VCC_COREVCC_CORE

HA#[3..31]

ADS#3

BNR#3

BPRI#3

DEFER#3

DRDY#3

DBSY#3

HBREQ0#3

HLOCK#3

CPURST#3

RS#23

RS#13

RS#03

HTRDY#3

HIT#3

HITM#3

NB_SUS_SAT#

ALINK_RST#

NB_PWRGD31

C191 1U/10V

R651 270K

R117 49.9/F

R116 24.9/F

R439 330/F

C676 .1U

NB_GTLREF

NB_CPVDD

1 2

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

RS#2

RS#1

RS#0

R375

4.7K

HA#[3..31]3

D D

HREQ#[4..0]3

HADSTB0#3

C C

HADSTB1#3

2.5VSUS

R650

27K

SUS_STAT#16,19,33

ALINK_RST#15,25,33

B B

R113

49.9/F

R112

86.6/F

0.63VCC_VORE of GTLREF voltage

for Prescott CPU .

ALINK_RST#

PLACE CLOSE TO NB, USE

20/20 WIDTH/SPACE

12

C189

1U/10V

C196

220P

D48

CH751H/BAT254

D49

CH751H/BAT254

EC41,May/24

21

21

1.8V

R141

27K

R126

330K

1.8V

L25 SBK160808T-121

RS300M MODERESISTOR

R375

NORMAL MODE

A A

PROJECT : EF5

Quanta Computer Inc.

Size Document Number Rev

5

4

3

2

Date: Sheet

RC300M-AGTL+ I/F

1

540Thursday, June 10, 2004

1ACustom

of

Page 6

5

NorthBridge-ATI RC300ML-DDR I/F

D D

MA_ADD[15..0]11

MA_DM_R[7..0]11

C C

MA_DQS_R[7..0]11

MA_CLKOUT#011

MA_CLKOUT011

MA_CLKOUT#111

MA_CLKOUT111

MA_CLKOUT#211

MA_CLKOUT211

MB_CLKOUT#311

MB_CLKOUT311

MB_CLKOUT#411

B B

MB_CLKOUT411

MB_CLKOUT#511

MB_CLKOUT511

1.8V

L28 SBK160808T-121

4

MA_ADD[15..0]

MA_DM_R[7..0]

MA_RAS#11

MA_CAS#11

MA_WE#11

MA_DQS_R[7..0]

3

2

1

06

U36C

MA_ADD0

MA_ADD1

MA_ADD2

MA_ADD3

MA_ADD4

MA_ADD5

MA_ADD6

MA_ADD7

MA_ADD8

MA_ADD9

MA_ADD10

MA_ADD11

MA_ADD12

MA_ADD13

MA_ADD14

MA_ADD15

MA_DM_R0

MA_DM_R1

MA_DM_R2

MA_DM_R3

MA_DM_R4

MA_DM_R5

MA_DM_R6

MA_DM_R7

MA_RAS#

MA_CAS#

MA_WE#

MA_DQS_R0

MA_DQS_R1

MA_DQS_R2

MA_DQS_R3

MA_DQS_R4

MA_DQS_R5

MA_DQS_R6

MA_DQS_R7

MA_CKE011

MA_CKE111

MA_CKE211

MA_CKE311

MA_CS#011

MA_CS#111

MA_CS#211

MA_CS#311

MEM_MPVDD

1 2

C228 1U/10V

MA_CKE0

MA_CKE1

MA_CKE2

MA_CKE3

MA_CS#0

MA_CS#1

MA_CS#2

MA_CS#3

AH19

AJ17

AK17

AH16

AK16

AF17

AE18

AF16

AE17

AE16

AJ20

AG15

AF15

AE23

AH20

AE25

AH7

AF10

AJ14

AF21

AH23

AK28

AD29

AB26

AF24

AF25

AE24

AJ8

AF9

AH13

AE21

AJ23

AJ27

AC28

AA25

AH10

AK10

AJ19

AH18

AG29

AG30

AJ11

AK11

AJ18

AH17

AG28

AF28

AF13

AE13

AG14

AF14

AH26

AH27

AF26

AG27

AC18

AD18

DDR_A0

DDR_A1

DDR_A2

DDR_A3

DDR_A4

DDR_A5

DDR_A6

DDR_A7

DDR_A8

DDR_A9

DDR_A10

DDR_A11

DDR_A12

DDR_A13

DDR_A14

DDR_A15

MEM_DM0

DDR_DM1

DDR_DM2

DDR_DM3

DDR_DM4

DDR_DM5

DDR_DM6

DDR_DM7

DDR_RAS#

DDR_CAS#

DDR_WE#

DDR_DQS0

DDR_DQS1

DDR_DQS2

DDR_DQS3

DDR_DQS4

DDR_DQS5

DDR_DQS6

DDR_DQS7

DDR_CK0#

DDR_CK0

DDR_CK1#

DDR_CK1

DDR_CK2#

DDR_CK2

DDR_CK3#

DDR_CK3

DDR_CK4#

DDR_CK4

DDR_CK5#

DDR_CK5

DDR_CKE0

DDR_CKE1

DDR_CKE2

DDR_CKE3

DDR_CS0#

DDR_CS1#

DDR_CS2#

DDR_CS3#

MPVDD

MPVSS

3/6

MEM I/F

DDR_COMP

MEM_DQ0

MEM_DQ1

MEM_DQ2

MEM_DQ3

MEM_DQ4

MEM_DQ5

MEM_DQ6

MEM_DQ7

MEM_DQ8

MEM_DQ9

MEM_DQ10

MEM_DQ11

MEM_DQ12

MEM_DQ13

MEM_DQ14

MEM_DQ15

MEM_DQ16

MEM_DQ17

MEM_DQ18

MEM_DQ19

MEM_DQ20

MEM_DQ21

MEM_DQ22

MEM_DQ23

MEM_DQ24

MEM_DQ25

MEM_DQ26

MEM_DQ27

MEM_DQ28

MEM_DQ29

MEM_DQ30

MEM_DQ31

MEM_DQ32

MEM_DQ33

MEM_DQ34

MEM_DQ35

MEM_DQ36

MEM_DQ37

MEM_DQ38

MEM_DQ39

MEM_DQ40

MEM_DQ41

MEM_DQ42

MEM_DQ43

MEM_DQ44

MEM_DQ45

MEM_DQ46

MEM_DQ47

MEM_DQ48

MEM_DQ49

MEM_DQ50

MEM_DQ51

MEM_DQ52

MEM_DQ53

MEM_DQ54

MEM_DQ55

MEM_DQ56

MEM_DQ57

MEM_DQ58

MEM_DQ59

MEM_DQ60

MEM_DQ61

MEM_DQ62

MEM_DQ63

MEM_CAP2

MEM_CAP1

DDR_VREF

AG6

AJ7

AJ9

AJ10

AJ6

AH6

AH8

AH9

AE7

AE8

AE12

AF12

AF7

AF8

AE11

AF11

AJ12

AH12

AH14

AH15

AH11

AJ13

AJ15

AJ16

AF18

AG20

AG21

AF22

AF19

AF20

AE22

AF23

AJ21

AJ22

AJ24

AK25

AH21

AH22

AH24

AJ25

AK26

AK27

AJ28

AH29

AH25

AJ26

AJ29

AH30

AF29

AE29

AB28

AA28

AE28

AD28

AC29

AB29

AC26

AB25

Y26

W26

AE26

AD26

AA26

Y27

AA29

AF6

AK19

AK20

RC300ML

MEM_DQ0

MEM_DQ1

MEM_DQ2

MEM_DQ3

MEM_DQ4

MEM_DQ5

MEM_DQ6

MEM_DQ7

MEM_DQ8

MEM_DQ9

MEM_DQ10

MEM_DQ11

MEM_DQ12

MEM_DQ13

MEM_DQ14

MEM_DQ15

MEM_DQ16

MEM_DQ17

MEM_DQ18

MEM_DQ19

MEM_DQ20

MEM_DQ21

MEM_DQ22

MEM_DQ23

MEM_DQ24

MEM_DQ25

MEM_DQ26

MEM_DQ27

MEM_DQ28

MEM_DQ29

MEM_DQ30

MEM_DQ31

MEM_DQ32

MEM_DQ33

MEM_DQ34

MEM_DQ35

MEM_DQ36

MEM_DQ37

MEM_DQ38

MEM_DQ39

MEM_DQ40

MEM_DQ41

MEM_DQ42

MEM_DQ43

MEM_DQ44

MEM_DQ45

MEM_DQ46

MEM_DQ47

MEM_DQ48

MEM_DQ49

MEM_DQ50

MEM_DQ51

MEM_DQ52

MEM_DQ53

MEM_DQ54

MEM_DQ55

MEM_DQ56

MEM_DQ57

MEM_DQ58

MEM_DQ59

MEM_DQ60

MEM_DQ61

MEM_DQ62

MEM_DQ63

C677 .47U

C678 .47U

P/N

R442 49.9/F

DDR_VREF

At least 20 mil

MEM_DQ[63..0]

C205 .1U

R657 1K/F

MEM_DQ[63..0] 11,12

2.5VSUSDDR_VREF

R658

C206

1K/F

.1U

A A

PROJECT : EF5

Quanta Computer Inc.

Size Document Number Rev

5

4

3

2

Date: Sheet

RC300ML-DDR I/F

640Thursday, June 10, 2004

1

1ACustom

of

Page 7

5

4

3

NorthBridge-ATI RC300ML-AGP & A_LINK I/F

2

1

07

3V

D D

R711

*2.2K

R714

*2.2K

3V 3V

R152

2K

R712

*2.2K

R715

*2.2K

LVDS_SSOUTAGP_ST1_R

3V 3V

U64

6

S0

7

S1

8

SD

1

ICLK

4

CLK

5V

2

5V

R146

2K

2

Q54

2N7002E

Q55

2N7002E

R149

4.7K

BKLON

3

3

1

1

R144

4.7K

VDD

LEE

GND

*MK1707S

R710

A_AD[31..0]10,15

C C

A_C/BE#[3..0]15

B B

1.5V

1K

AGP 4X

R157

1K

A_AD[31..0]

A_C/BE#[3..0]

A_PAR10,15

A_STROBE#15

A_ACAT#15

A_END#15

A_INTA#15

A_DEVSEL#15

A_OFF#15

A_SBREQ#15

A_SBGNT#15

3V

R139 8.2K

1.5V

A_AD0

A_AD1

A_AD2

A_AD3

A_AD4

A_AD5

A_AD6

A_AD7

A_AD8

A_AD9

A_AD10

A_AD11

A_AD12

A_AD13

A_AD14

A_AD15

A_AD16

A_AD17

A_AD18

A_AD19

A_AD20

A_AD21

A_AD22

A_AD23

A_AD24

A_AD25

A_AD26

A_AD27

A_AD28

A_AD29

A_AD30

A_AD31

A_C/BE#0

A_C/BE#1

A_C/BE#2

A_C/BE#3

R443 8.2K

R444 8.2K

R445 51R164

R446 10K

U36B

AK5

AJ5

AJ4

AH4

AJ3

AJ2

AH2

AH1

AG2

AG1

AG3

AF3

AF1

AF2

AF4

AE3

AE4

AE5

AE6

AC2

AC4

AB3

AB2

AB5

AB6

AA2

AA4

AA5

AA6

Y3

Y5

Y6

AG4

AE2

AC3

AA3

AD5

AC6

AC5

AD2

W4

AD3

AD6

W5

W6

V5

V6

K5

K6

1%

J5

M5

J6

PLACE THIS CAP CLOSE

TO U200 AS POSSIBLE

A_AD0

A_AD1

A_AD2

A_AD3

A_AD4

A_AD5

A_AD6

A_AD7

A_AD8

A_AD9

A_AD10

A_AD11

A_AD12

A_AD13

A_AD14

A_AD15

A_AD16

A_AD17

A_AD18

A_AD19

A_AD20

A_AD21

A_AD22

A_AD23

A_AD24

A_AD25

A_AD26

A_AD27

A_AD28

A_AD29

A_AD30

A_AD31

A_CBE0#

A_CBE1#

A_CBE2#

A_CBE3#

A_PAR

A_FRAME#

A_IRDY#

A_TRDY#

A_INTA#

A_DEVSEL#

A_STOP#

A_SBREQ#

A_SBGNT#

A_REQ0#

A_GNT0#

AGP_GNT#

AGP_REQ#

AGP_COMP

AGP8X_DET#

AGP_VREF4X

2/6

A_LINK

I/F

A_LINK/AGP I/F

AGP8X

AGP_SBSTB#

AGP_ADSTB0

AGP_ADSTB0#

AGP_ADSTB1

AGP_ADSTB1#

AGP_DEVSEL#

AGP_FRAME#

AGP_PIPE#DBI_HI

RC300ML

AGP_AD0

AGP_AD1

AGP_AD2

AGP_AD3

AGP_AD4

AGP_AD5

AGP_AD6

AGP_AD7

AGP_AD8

AGP_AD9

AGP_AD10

AGP_AD11

AGP_AD12

AGP_AD13

AGP_AD14

AGP_AD15

AGP_AD16

AGP_AD17

AGP_AD18

AGP_AD19

AGP_AD20

AGP_AD21

AGP_AD22

AGP_AD23

AGP_AD24

AGP_AD25

AGP_AD26

AGP_AD27

AGP_AD28

AGP_AD29

AGP_AD30

AGP_AD31

I/F

AGP_SBSTB

AGP_CBE#0

AGP_CBE#1

AGP_CBE#2

AGP_CBE#3

AGP_IRDY#

AGP_PAR

AGP_DBI_LO

AGP_RBF#

AGP_STOP#

AGP_TRDY#

AGP_WBF#

AGP_SBA0

AGP_SBA1

AGP_SBA2

AGP_SBA3

AGP_SBA4

AGP_SBA5

AGP_SBA6

AGP_SBA7

AGP_ST0

AGP_ST1

AGP_ST2

Y2

W3

W2

V3

V2

V1

U1

U3

T2

R2

P3

P2

N3

N2

M3

M2

L1

L2

K3

K2

J3

J2

J1

H3

F3

G2

F2

F1

E2

E1

D2

D1

E5

E6

T3

U2

G3

H2

R3

M1

L3

H1

R5

P6

P5

T5

C1

D3

N6

T6

R6

N5

C3

C2

D4

E4

F6

F5

G6

G5

L6

M6

L5

SBA0

SBA1

SBA2

SBA3

SBA4

SBA5

AGP_ST1_R

AGP_ST2_R

*2.2K

R713

*2.2K

R717 *33

AGP_ST2_R LVDS_SSIN_R

R718 *33

2

5

3

R716

3V

C826

*.1U

R716

*0

AGPSTP# 16

AGP_BUSY# 16

EDIDCLK 14

EDIDDATA 14

DISP_ON 14

BKLON 14

LVDS SPECTRUM

ENABLEOPEN

DISABLEGND

SBA2

A A

2

Q21

DTC144EUA

1 3

PROJECT : EF5

Quanta Computer Inc.

Size Document Number Rev

5

4

3

2

Date: Sheet

RC300ML-AGP & A_LINK I/F

1

740Thursday, June 10, 2004

1ACustom

of

Page 8

5

4

3

NorthBridge-ATI RC300ML-VIDEO I/F & CLKGEN

2

1

08

1.8V

C237

.1U

CRTVS_VGA14,34

CRTHS_VGA14,34

2.5V

C851

.1U

L72

SBK160808T-121

21

CRT_R14

CRT_G14

CRT_B14

R376 715/F

HCLK_NB

HCLK_NB#

R661 *10K

R662 *10K

R663 *10K

R664 *10K

L71

SBK160808T-121

C232

.1U

21

AGPCLK

NB_DDRCLK

R789

*68

3V

21

21

C279

.1U

L70

SBK160808T-121

C815

.1U

U36D

TXCLK_UN

TXCLK_UP

TXCLK_LN

TXCLK_LP

LPVDD

LPVSS

LVDDR

LVSSR

C_R

Y_G

COMP_B

DACSCL

DACSDA

CPUSTOP#

SYSCLK

SYSCLK#

D12

E12

F11

F12

D13

D14

E13

F13

E10

D10

B9

C9

D11

E11

B10

C10

A12

A11

B12

C12

B11

C11

E15

C15

D15

D6

C6

D5

A8

B8

TXUOUT0- 14

TXUOUT0+ 14

TXUOUT1- 14

TXUOUT1+ 14

TXUOUT2- 14

TXUOUT2+ 14

TXUCLKOUT- 14

TXUCLKOUT+ 14

TXLOUT0- 14

TXLOUT0+ 14

TXLOUT1- 14

TXLOUT1+ 14

TXLOUT2- 14

TXLOUT2+ 14

TXLCLKOUT- 14

TXLCLKOUT+ 14

DDCCLK 14,34

DDCDAT 14,34

R447 4.7K

R665 *10K

R666 *10K

L31

C253

.1U

C263

.1U

SBK160808T-121

C262

10U/10V/R

L32

SBK160808T-121

C269

10U/10V/R

C245

.1U

C256

.1U

3V

1.8V

21

1.8V

21

R790

1%

*68

G9

+3.3V

H9

+3.3V#H9

A14

AVDD

B13

AVSSN

B14

AVDDDI

C13

AVSSDI

A15

AVDDQ

B15

AVSSQ

H11

PLLVDD

G11

PLLVSS

F14

RED

F15

GREEN

E14

BLUE

D9

DACVSYNC

C8

DACHSYNC

C14

RSET

A4

XTLIN

B4

XTLOUT

A5

HCLKIN

B5

HCLKIN#

B6

SYS_FBCLKOUT

A6

SYS_FBCLKOUT#

D8

ALINK_CLK

B2

AGPCLKOUT

B3

AGPCLKIN

A3

EXT_MEM_CLK

D7

USBCLK

B7

REF27

C5

OSC

4/6

CRT

CLK. GEN.

TXOUT_U0N

TXOUT_U0P

TXOUT_U1N

TXOUT_U1P

TXOUT_U2N

TXOUT_U2P

TXOUT_L0N

TXOUT_L0P

TXOUT_L1N

TXOUT_L1P

TXOUT_L2N

TXOUT_L2P

LVDS

LVDDR#C12

LVSSR#C11

SVID

RC300ML

D D

DAC VDD (2.5V)

AVDD

AVDDDI

DIGITAL VDD (1.8V)

AVDDQ

DAC2 BANDGAP REF (1.8V)

PUT 3vsus,2.5vsus,1_8v

DECOUPLING CAPS ON THE

BOTTOM, CLOSE TO BALLS

PLLVDD PLL VDD (1.8V)

1.8V

L73

SBK160808T-121

C852

1.8V

L74

C C

REFCLK1_NB13

R659 15

SBK160808T-121

C853

C209

.1U

.1U

TERMINATION PLACE

CLOSE TO U3

NB_X1

R660

56/F

C220

.1U

.1U

21

HCLK_NB13

HCLK_NB#13

EC4,Apr/04

B B

AGPCLK13

NB_DDRCLK13

EC5,Apr/04

3V

R702 *10K

R371 10K

R667 *10K

C886

C885

*.15P

*.15P

A A

EC38,May/24

PROJECT : EF5

Quanta Computer Inc.

Size Document Number Rev

5

4

3

2

Date: Sheet

RC300ML-VIDEO I/F & CLKGEN

840Thursday, June 10, 2004

1

1ACustom

of

Page 9

5

4

NorthBridge-ATI RC300ML-POWER

3

2

1

09

1.5V

D D

C C

VCC_CORE

B B

C207

22U

C265

.1U

C316

22U

C276

.1U

C314

22U

C225

.1U

1.8V VCC_CORE

C208

C281

.1U

.1U

C284

C268

.1U

.1U

C227

C274

.1U

.1U

C211

C229

.1U

.1U

C249

C233

.1U

.1U

C230

.1U

C252

.1U

C250

.1U

C246

.1U

C241

.1U

C212

.1U

C285

.1U

C297

.1U

C306

.1U

C243

.1U

C242

.1U

C307

.1U

C236

.1U

C273

.1U

C235

.1U

C271

.1U

C240

.1U

C202

.1U

C298

.1U

C222

.1U

C239

.1U

C244

.1U

C258

.1U

C247

.1U

C217

.1U

C234

.1U

C215

.1U

C296

.1U

C302

.1U

C254

.1U

C213

.1U

C282

.1U

C259

.1U

C275

.1U

C224

.1U

C257

.1U

C267

.1U

1.5V

3V

M12

M13

M14

M17

M18

M19

W12

W13

W14

W17

W18

W19

M23

W30

AC7

AC8

AD1

AD7

AD8

G12

H12

H13

N12

N13

N14

N17

N18

N19

P12

P13

P14

P17

P18

P19

U12

U13

U14

U17

U18

U19

V12

V13

V14

V17

V18

V19

C16

D16

D17

E16

E17

G17

G21

G23

G24

H16

H17

H19

H21

H24

K23

K24

P23

P24

U23

U24

AA1

AA7

AA8

AK3

F9

F10

F16

F17

T23

T24

W8

U36E

VDD_CORE#F9

VDD_CORE

VDD_CORE#G12

VDD_CORE#H12

VDD_CORE#H13

VDD_CORE#M12

VDD_CORE#M13

VDD_CORE#M14

VDD_CORE#M17

VDD_CORE#M18

VDD_CORE#M19

VDD_CORE#N12

VDD_CORE#N13

VDD_CORE#N14

VDD_CORE#N17

VDD_CORE#N18

VDD_CORE#N19

VDD_CORE#P12

VDD_CORE#P13

VDD_CORE#P14

VDD_CORE#P17

VDD_CORE#P18

VDD_CORE#P19

VDD_CORE#U12

VDD_CORE#U13

VDD_CORE#U14

VDD_CORE#U17

VDD_CORE#U18

VDD_CORE#U19

VDD_CORE#V12

VDD_CORE#V13

VDD_CORE#V14

VDD_CORE#V17

VDD_CORE#V18

VDD_CORE#V19

VDD_CORE#W12

VDD_CORE#W13

VDD_CORE#W14

VDD_CORE#W17

VDD_CORE#W18

VDD_CORE#W19

VDD_CPU#C16

VDD_CPU#D16

VDD_CPU#D17

VDD_CPU

VDD_CPU#E17

VDD_CPU#F16

VDD_CPU#F17

VDD_CPU#G17

VDD_CPU#G21

VDD_CPU#G23

VDD_CPU#G24

VDD_CPU#H16

VDD_CPU#H17

VDD_CPU#H19

VDD_CPU#H21

VDD_CPU#H24

VDD_CPU#K23

VDD_CPU#K24

VDD_CPU#M23

VDD_CPU#P23

VDD_CPU#P24

VDD_CPU#T23

VDD_CPU#T24

VDD_CPU#U23

VDD_CPU#U24

VDD_CPU#W30

VDD_A#W8

VDD_A

VDD_A#AA7

VDD_A#AA8

VDD_A#AC7

VDD_A#AC8

VDD_A#AD1

VDD_A#AD7

VDD_A#AD8

VDD_A#AK3

CORE

PWR

CPU I/F

PWR

ALINK

PWR

5/6

POWER

VDD_MEM#AG11

VDD_MEM#AG12

VDD_MEM#AG17

VDD_MEM#AG18

VDD_MEM#AG23

VDD_MEM#AG24

VDD_MEM#AG26

VDD_MEM#V23

VDD_MEM#W23

VDD_MEM#W24

VDD_MEM#W25

VDD_MEM#Y25

VDD_MEM#AA23

VDD_MEM#AA27

VDD_MEM#AB30

VDD_MEM#AC10

VDD_MEM#AC12

VDD_MEM#AC13

VDD_MEM#AC15

VDD_MEM#AC17

VDD_MEM#AC19

VDD_MEM#AC21

VDD_MEM#AC23

VDD_MEM#AC24

VDD_MEM#AC25

VDD_MEM#AC27

VDD_MEM#AD10

VDD_MEM#AD12

VDD_MEM#AD13

VDD_MEM#AD15

VDD_MEM#AD17

VDD_MEM#AD19

MEM I/F

PWR

VDD_MEM#AD21

VDD_MEM#AD23

VDD_MEM#AD24

VDD_MEM#AD25

VDD_MEM#AD27

VDD_MEM#AE9

VDD_MEM#AE10

VDD_MEM#AE14

VDD_MEM

VDD_MEM#AE19

VDD_MEM#AE20

VDD_MEM#AE30

VDD_MEM#AF27

VDD_MEM#AG8

VDD_MEM#AG9

VDD_MEM#AJ30

VDD_MEM#AK8

VDD_MEM#AK14

VDD_MEM#AK23

VDD_AGP

VDD_AGP#G4

VDD_AGP#H5

VDD_AGP#H6

VDD_AGP#H7

VDD_AGP#J4

VDD_AGP#K8

VDD_AGP#L4

VDD_AGP#M7

VDD_AGP#M8

VDD_AGP#N4

AGP PWR

VDD_AGP#P1

VDD_AGP#P7

VDD_AGP#P8

VDD_AGP#R4

VDD_AGP#T8

VDD_AGP#U4

VDD_AGP#U5

VDD_AGP#U6

VDD_AGP3.3

VDD_AGP3.3#F7

VDD_AGP3.3#G8

VDD_18#AC22

VDD_18#AC9

VDD_18#H22

VDD_18

V23

W23

W24

W25

Y25

AA23

AA27

AB30

AC10

AC12

AC13

AC15

AC17

AC19

AC21

AC23

AC24

AC25

AC27

AD10

AD12

AD13

AD15

AD17

AD19

AD21

AD23

AD24

AD25

AD27

AE9

AE10

AE14

AE15

AE19

AE20

AE30

AF27

AG8

AG9

AG11

AG12

AG17

AG18

AG23

AG24

AG26

AJ30

AK8

AK14

AK23

A2

G4

H5

H6

H7

J4

K8

L4

M7

M8

N4

P1

P7

P8

R4

T8

U4

U5

U6

E7

F7

G8

AC22

AC9

H22

H10

2.5VSUS

1.5V

3V

1.8V

2.5VSUS

C315

10U

C199

.1U

C292

.1U

C305

22U

C278

22U

C293

.1U

C195

.1U

C231

.1U

C266

.1U

C304

.1U

1.5V

C248

.1U

C270

.1U

C277

.1U

U36F

A29

VSS

B1

VSS#B1

B16

VSS#B16

B30

VSS#B30

C4

VSS#C4

C19

VSS#C19

C23

VSS#C23

C27

VSS#C27

D21

VSS#D21

D25

VSS#D25

E3

VSS#E3

E8

VSS#E8

E9

VSS#E9

F4

VSS#F4

F8

C219

C201

C197

C261

.1U

C238

.1U

C251

.1U

C288

.1U

C286

.1U

C260

.1U

.1U

C200

.1U

C203

.1U

C283

.1U

C287

.1U

C295

.1U

.1U

C280

.1U

C226

.1U

3V

C290

.1U

C214

.1U

C223

.1U

.1U

C303

.1U

C193

.1U

C289

.1U

C198

.1U

G14

G15

G18

G20

H14

H15

H18

H20

H27

K27

M15

M16

M27

N15

N16

N23

N24

P15

P16

P27

R12

R13

R14

R15

R16

R17

R18

R19

R23

VSS#F8

F27

VSS#F27

VSS#G14

VSS#G15

VSS#G18

VSS#G20

H4

VSS#H4

H8

VSS#H8

VSS#H14

VSS#H15

VSS#H18

VSS#H20

VSS#H27

J7

VSS#J7

J8

VSS#J8

K4

VSS#K4

VSS#K27

L7

VSS#L7

L8

VSS#L8

L23

VSS#L23

L24

VSS#L24

L25

VSS#L25

M4

VSS#M4

VSS#M15

VSS#M16

VSS#M27

N8

VSS#N8

VSS#N15

VSS#N16

VSS#N23

VSS#N24

P4

VSS#P4

VSS#P15

VSS#P16

VSS#P27

R1

VSS#R1

R7

VSS#R7

R8

VSS#R8

VSS#R12

VSS#R13

VSS#R14

VSS#R15

VSS#R16

VSS#R17

VSS#R18

VSS#R19

VSS#R23

T4

VSS#T4

T12

VSS#T12

6/6

GND

VSS#T13

VSS#T14

VSS#T15

VSS#T16

VSS#T17

VSS#T18

VSS#T19

VSS#T27

VSS#U7

VSS#U8

VSS#U15

VSS#U16

VSS#V4

VSS#V7

VSS#V8

VSS#V15

VSS#V16

VSS#V27

VSS#W15

VSS#W16

VSS#W27

VSS#Y1

VSS#Y4

VSS#Y7

VSS#Y8

VSS#Y23

VSS#Y24

VSS#Y30

VSS#AB4

VSS#AB8

VSS#AB23

VSS#AB24

VSS#AB27

VSS#AC1

VSS#AC11

VSS#AC14

VSS#AC16

VSS#AC20

VSS#AC30

VSS#AD4

VSS#AD11

VSS#AD14

VSS#AD16

VSS#AD20

VSS#AE27

VSS#AF5

VSS#AF30

VSS#AG7

VSS#AG10

VSS#AG13

VSS#AG16

VSS#AG19

VSS#AG22

VSS#AG25

VSS#AH3

VSS#AH28

VSS#AJ1

VSS#AK2

VSS#AK4

VSS#AK7

VSS#AK13

VSS#AK22

VSS#AK29

T13

T14

T15

T16

T17

T18

T19

T27

U7

U8

U15

U16

V4

V7

V8

V15

V16

V27

W15

W16

W27

Y1

Y4

Y7

Y8

Y23

Y24

Y30

AB4

AB8

AB23

AB24

AB27

AC1

AC11

AC14

AC16

AC20

AC30

AD4

AD11

AD14

AD16

AD20

AE27

AF5

AF30

AG7

AG10

AG13

AG16

AG19

AG22

AG25

AH3

AH28

AJ1

AK2

AK4

AK7

AK13

AK22

AK29

RC300ML

C221

.1U

C216

.1U

C272

.1U

RC300ML

3V 1.8V

A A

1.8V (NB) should ramp up with 3V, < 2.1V

5

4

EC6,Apr/04

3

1

2

D16 BAV99

R121 0

3

R120 *0

1

2

D17BAV99

PROJECT : EF5

Quanta Computer Inc.

Size Document Number Rev

3

2

Date: Sheet

RC300ML-POWER

1

940Thursday, June 10, 2004

1ACustom

of

Page 10

5

4

NorthBridge-ATI RC300ML-STRAPS

3

2

1

10

D D

A_AD[31..0]

A_AD[31..0] 7,15

FSB speed need to fixed by H/W seeting .

D51 1SS355

A_AD31

A_AD30

C C

B B

A_AD29

A_AD28

A_AD27

A_AD26

A_AD25

A_AD17

R155

4.7K

R173

D52 1SS355

4.7K

R150

10K

R174

4.7K

R151

10K

R156

10K

R140

10K

R175

4.7K

2 1

R163

10K

2 1

R171

10K

3V

3V

3V

3V

BSEL1 4,13

3V

3V

AD[31..30] : FSB CLK SPEED

DEFAULT: 00

00: 100 MHZ

01: 133 MHZ

10: 166MHZ

11: 66 MHZ

BSEL0 4,13

AD29: STRAP CONFIGURATION

DEFAULT:1

0: REDUCEDE SET

1: FULL SET

AD28: SPREAD SPECTRUM ENABLE

DEFAULT:0

0: DISABLE SS

1: ENABLE SS

AD27: FrcShortReset#

DEFAULT: 1

0: TESTE MODE

1: NORMAL MODE

AD26: ENABLE IOQ

DEFAULT : 1

0: IOQ=1

1: IOQ=12

AD25, AD17: CPU VOLTAGE [1], CPU VOLTAGE [0]

DEFAULT : 01

00: 1.05V (MOBILE CPU)

01: 1.35V (MOBILE CPU)

10: 1.45V ( DESKTOP )

11: 1.75V ( DESKTOP )

A_PAR7,15

A_AD24

A_AD23

A_AD22

A_AD21

A_AD20

A_AD19

A_AD18

A_PAR

R159

10K

R158

10K

R134

10K

R154

10K

R153

4.7K

R362

*4.7K

R161

4.7K

R136

4.7K

3V

3V

3V

3V

3V

AD24 : MOBILE CPU SELECT

DEFAULT : 1

0: BANIAS CPU

1: NOT BANIAS CPU

AD23 : CLOCK BYPASS DISABLE

DEFAULT : 1

0: TEST MODE

1: NORMAL OPERATION

AD22 : OSC PAD OUTPUT PCICLK

DEFAULT : 1

0: OSC PIN DRIVES PCICLK

1: OSC PIN DRIVES OSC CLK

AD21 : AUTO_CAL ENABLE

DEFAULT : 1

0: DISABLE AUTO-CAL

1: ENABLE AUTO-CAL

AD20 : INTERNAL CLK GEN ENABLE

DEFAULT : 1

0: EXTERNAL CLOCK GENERATOR

1: INTERNAL CLOCK GENERATOR

AD19: MEMORY IO VOLTAGE SELECTION

DEFAULT : 1

0: 1.8V

1: 2.5V

AD18 : ENABLE PHASE CALIBRATION

DEFAULT : 0

0: ENABLE

1: DISABLE

PAR : EXTENDED DEBUG MODE

DEFAULT : 1

0: DEBUG MODE

1: NORMAI OPERATION

A A

PROJECT : EF5

Quanta Computer Inc.

Size Document Number Rev

5

4

3

2

Date: Sheet

RC300ML-STRAPS

1

10 40Thursday, June 10, 2004

1ACustom

of

Page 11

5

DDR SO-DIMM * 2

MA_ADD0

MA_ADD1

MA_ADD2

MA_ADD3

D D

MA_DQS_R1

MA_DM_R1

MA_DM_R2

MA_DQS_R2

MA_DQS_R5

MA_DM_R5

MA_DQS_R7

MA_DM_R7

MA_DQS_R0

MA_DM_R0

MA_DQS_R3

MA_DM_R3

MA_DM_R4

MA_DQS_R4

MA_DM_R6

C C

MA_DQS_R6

1 2

3 4

RP20 0

1 2

3 4

RP18 0

1 2

3 4

RP16 0

1 2

3 4

RP33 0

1 2

3 4

RP31 0

1 2

3 4

RP29 0

1 2

3 4

RP27 0

1 2

3 4

P/N

RP22 0

MDQS1

M_DM1

M_DM2

MDQS2

MDQS5

M_DM5

MDQS7

M_DM7

MDQS0

M_DM0

MDQS3

M_DM3

M_DM4

MDQS4

M_DM6

MDQS6

EC7,Apr/04 EC7,Apr/04

MA_CLKOUT16

MA_CLKOUT#16

MA_CLKOUT06

MA_CLKOUT#06

MA_CLKOUT26

RP59 0

RP66 0

2.5VSUS

1 2

3 4

1 2

3 4

3V

MA_CKE36

MA_CKE16

MA_CS#26

MA_CS#06

B B

MA_CLKOUT#26

MMA_CKE3

MMA_CKE1

MA_RAS#6

MA_CAS#6

MA_WE#6

MMA_CS#2

MMA_CS#0

SMBDATA13,16

SMBCLK13,16

R129 10K

EC38,May/24

2.5VSUS

C840

C839

.1U

A A

C841

.1U

.1U

C842

.1U

C843

.1U

2.5VSUS

C844

.1U

MA_ADD4

MA_ADD5

MA_ADD6

MA_ADD7

MA_ADD8

MA_ADD9

MA_ADD10

MA_ADD11

MA_ADD12

MA_ADD15

MA_ADD13

MA_ADD14

M_DM7

M_DM6

M_DM5

M_DM4

M_DM3

M_DM2

M_DM1

M_DM0

MDQS7

MDQS6

MDQS5

MDQS4

MDQS3

MDQS2

MDQS1

MDQS0

MMA_CKE0

MMA_CKE1

MMA_CS#0

MMA_CS#1

R794

*68

C899

*15P

112

111

110

109

108

107

106

105

102

101

115

100

99

123

117

116

98

12

26

48

62

134

148

170

184

78

11

25

47

61

133

147

169

183

77

35

37

160

158

89

91

96

95

118

120

119

121

122

86

194

196

198

193

195

197

199

93

94

113

114

131

132

143

144

155

156

157

167

168

179

180

191

192

201

3

4

15

16

27

28

38

39

4

2.5VSUS

91021223334364645575869708182

A0

A1

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VSS

VSS

VSS

VSS

VSS

150

159

161

162

173

VDD

SO-DIMM

VSS

VSS

138

149

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

BA0

BA1

BA2

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

DM8

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS8

CK0

CK0

CK1

CK1

CK2

CK2

CKE0

CKE1

RAS

CAS

WE

S0

S1

RSET

SA0

SA1

SA2

SDA

SCL

VDDspd

VDDid

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

PADGND1

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

186

VSS

VSS

174

185

92

J2

5

DQ0

7

DQ1

VDD

VDD

VDD

VDD

VDD

VDD

13

DQ2

17

DQ3

6

DQ4

8

DQ5

14

DQ6

18

DQ7

19

DQ8

23

DQ9

29

DQ10

31

DQ11

20

DQ12

24

DQ13

30

DQ14

32

DQ15

41

DQ16

43

DQ17

49

DQ18

53

DQ19

42

DQ20

44

DQ21

50

DQ22

54

DQ23

55

DQ24

59

DQ25

65

DQ26

67

DQ27

56

DQ28

60

DQ29

66

DQ30

68

DQ31

127

DQ32

129

DQ33

135

DQ34

139

DQ35

128

DQ36

130

DQ37

136

DQ38

140

DQ39

141

DQ40

145

DQ41

151

DQ42

153

DQ43

142

DQ44

146

DQ45

152

DQ46

154

DQ47

163

DQ48

165

DQ49

171

DQ50

175

DQ51

164

DQ52

166

DQ53

172

DQ54

176

DQ55

177

DQ56

181

DQ57

187

DQ58

189

DQ59

178

DQ60

182

DQ61

188

DQ62

190

DQ63

71

CB0

73

CB1

79

CB2

83

CB3

72

CB4

74

CB5

80

CB6

(Reverse)

84

CB7

1

VREF

2

VREF

85

DU

97

DU

124

DU

200

DU

202

PADGND2

40

VSS

51

VSS

52

VSS

63

VSS

64

VSS

75

VSS

76

VSS

87

VSS

88

VSS

90

VSS

VSS

VSS

VSS

VSS

VSS

VSS

103

104

125

126

137

SO_DIMM_200_pin_Reverse

MEM_DQ59

MEM_DQ58

MEM_DQ57

MEM_DQ56

MEM_DQ63

MEM_DQ62

MEM_DQ61

MEM_DQ60

MEM_DQ55

MEM_DQ51

MEM_DQ53

MEM_DQ49

MEM_DQ54

MEM_DQ50

MEM_DQ48

MEM_DQ52

MEM_DQ47

MEM_DQ43

MEM_DQ45

MEM_DQ41

MEM_DQ42

MEM_DQ46

MEM_DQ40

MEM_DQ44

MEM_DQ39

MEM_DQ38

MEM_DQ33

MEM_DQ32

MEM_DQ35

MEM_DQ34

MEM_DQ37

MEM_DQ36

MEM_DQ27

MEM_DQ31

MEM_DQ29

MEM_DQ25

MEM_DQ26

MEM_DQ30

MEM_DQ24

MEM_DQ28

MEM_DQ19

MEM_DQ22

MEM_DQ18

MEM_DQ21

MEM_DQ23

MEM_DQ16

MEM_DQ17

MEM_DQ20

MEM_DQ10

MEM_DQ14

MEM_DQ8

MEM_DQ9

MEM_DQ15

MEM_DQ11

MEM_DQ13

MEM_DQ12

MEM_DQ3

MEM_DQ7

MEM_DQ1

MEM_DQ0

MEM_DQ2

MEM_DQ6

MEM_DQ4

MEM_DQ5

2.5VSUS2.5VSUS

C141

.1U

C148

.1U

3

MA_DQS_R[7..0]6

DDR_VREF

MEM_DQ[63..0]6,12

MA_ADD[15..0]6

MA_DM_R[7..0]6

DDR_SMA[15..0]12

MA_ADD14

MA_ADD0

MA_ADD12

MA_ADD6

MA_ADD8

MA_ADD11

MA_ADD2

MA_ADD4

MA_ADD3

MA_ADD5

MA_ADD7

MA_ADD9

MA_ADD15

MA_ADD13

MA_ADD10

MA_ADD1

MA_CKE26

MA_CKE06

MA_RAS#6

MA_CAS#6

MA_WE#6

MA_CS#16

MA_CS#36

EC8,Apr/04

2.5VSUS

MMA_CKE[3..0]12

MMA_CS#[3..0]12

MMA_RAS#12

MMA_CAS#12

MMA_WE#12

MEM_DQ[63..0]

MA_ADD[15..0]

MA_DM_R[7..0]

MA_DQS_R[7..0]

DDR_SMA[15..0]

RP51 10

1 2

3 4

RP67 10

1 2

3 4

RP53 10

1 2

3 4

RP54 10

1 2

3 4

RP55 10

1 2

3 4

RP56 10

1 2

3 4

RP65 10

1 2

3 4

RP58 10

1 2

3 4

M_DM[7..0]12

MDQS[7..0]12

RP60 0

1 2

3 4

R653 10

R652 10

R654 10

R766 0

R767 0

3V

2.5VSUS

MMA_CKE[3..0]

MMA_CS#[3..0]

MMA_RAS#

MMA_CAS#

MMA_WE#

DDR_SMA14

DDR_SMA0

DDR_SMA12

DDR_SMA6

DDR_SMA8

DDR_SMA11

DDR_SMA2

DDR_SMA4

DDR_SMA3

DDR_SMA5

DDR_SMA7

DDR_SMA9

DDR_SMA15

DDR_SMA13

DDR_SMA10

DDR_SMA1

M_DM[7..0]

MDQS[7..0]

MB_CLKOUT46

MB_CLKOUT#46

MB_CLKOUT36

MB_CLKOUT#36

MB_CLKOUT56

MB_CLKOUT#56

MMA_CS#1

MMA_CS#3

3V

SMBDATA13,16

SMBCLK13,16

MMA_CKE2

MMA_CKE0

DDR_SMA0

DDR_SMA1

DDR_SMA2

DDR_SMA3

DDR_SMA4

DDR_SMA5

DDR_SMA6

DDR_SMA7

DDR_SMA8

DDR_SMA9

DDR_SMA10

DDR_SMA11

DDR_SMA12

DDR_SMA15

DDR_SMA13

DDR_SMA14

M_DM7

M_DM6

M_DM5

M_DM4

M_DM3

M_DM2

M_DM1

M_DM0

MDQS7

MDQS6

MDQS5

MDQS4

MDQS3

MDQS2

MDQS1

MDQS0

MMA_CKE2

MMA_CKE3

MMA_RAS#

MMA_CAS#

MMA_WE#

MMA_CS#2

MMA_CS#3

R138 4.7K

R131 4.7K

R130 10K

2

91021223334364645575869708182

112

A0

111

A1

VDD

VDD

110

A2

109

A3

108

A4

107

A5

106

A6

105

A7

102

A8

101

A9

115

A10

100

A11

99

A12

123

A13

117

BA0

116

BA1

98

BA2

12

DM0

26

DM1

48

DM2

62

DM3

134

DM4

148

DM5

170

DM6

184

DM7

78

DM8

11

DQS0

25

DQS1

47

DQS2

61

DQS3

133

DQS4

147

DQS5

169

DQS6

183

DQS7

77

DQS8

35

CK0

37

CK0

160

CK1

158

CK1

89

CK2

91

CK2

96

CKE0

95

CKE1

118

RAS

120

CAS

119

WE

121

S0

122

S1

86

RSET

194

SA0

196

SA1

198

SA2

193

SDA

195

SCL

197

VDDspd

199

VDDid

93

VDD

94

VDD

113

VDD

114

VDD

131

VDD

132

VDD

143

VDD

144

VDD

155

VDD

156

VDD

157

VDD

167

VDD

168

VDD

179

VDD

180

VDD

191

VDD

192

VDD

201

PADGND1

3

VSS

4

VSS

15

VSS

16

VSS

27

VSS

28

VSS

38

VSS

39

VSS

VSS

186

1

2.5VSUS

92

J3

5

DQ0

7

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VSS

VSS

VSS

VSS

VSS

VSS

VSS

149

150

159

161

162

173

174

185

DQ1

VDD

VDD

VDD

VDD

VDD

VDD

VDD

13

DQ2

17

DQ3

6

DQ4

8

DQ5

14

DQ6

18

DQ7

19

DQ8

23

DQ9

29

DQ10

31

DQ11

20

DQ12

24

DQ13

30

DQ14

32

DQ15

41

DQ16

43

DQ17

49

DQ18

53

DQ19

42

DQ20

44

DQ21

50

DQ22

54

DQ23

55

DQ24

59

DQ25

65

DQ26

67

DQ27

56

DQ28

60

DQ29

66

DQ30

68

DQ31

127

DQ32

129

DQ33

135

DQ34

139

DQ35

128

DQ36

130

DQ37

136

DQ38

140

DQ39

141

DQ40

145

DQ41

151

DQ42

153

DQ43

142

DQ44

146

DQ45

152

DQ46

154

DQ47

163

DQ48

165

DQ49

171

DQ50

175

DQ51

164

DQ52

166

DQ53

172

DQ54

176

DQ55

177

DQ56

181

DQ57

187

DQ58

189

DQ59

178

DQ60

182

DQ61

188

DQ62

190

DQ63

71

CB0

73

CB1

79

CB2

83

CB3

72

CB4

74

CB5

80

CB6

SO-DIMM

(Reverse)

84

CB7

1

VREF

2

VREF

85

DU

97

DU

124

DU

200

DU

202

PADGND2

40

VSS

51

VSS

52

VSS

63

VSS

64

VSS

75

VSS

76

VSS

87

VSS

88

VSS

90

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

103

104

125

126

137

138

SO_DIMM_200_pin_Reverse_B

MEM_DQ59

MEM_DQ58

MEM_DQ57

MEM_DQ56

MEM_DQ63

MEM_DQ62

MEM_DQ61

MEM_DQ60

MEM_DQ55

MEM_DQ51

MEM_DQ53

MEM_DQ49

MEM_DQ54

MEM_DQ50

MEM_DQ48

MEM_DQ52

MEM_DQ47

MEM_DQ43

MEM_DQ45

MEM_DQ41

MEM_DQ42

MEM_DQ46

MEM_DQ40

MEM_DQ44

MEM_DQ39

MEM_DQ38

MEM_DQ33

MEM_DQ32

MEM_DQ35

MEM_DQ34

MEM_DQ37

MEM_DQ36

MEM_DQ27

MEM_DQ31

MEM_DQ29

MEM_DQ25

MEM_DQ26

MEM_DQ30

MEM_DQ24

MEM_DQ28

MEM_DQ19

MEM_DQ22

MEM_DQ18

MEM_DQ21

MEM_DQ23

MEM_DQ16

MEM_DQ17

MEM_DQ20

MEM_DQ10

MEM_DQ14

MEM_DQ8

MEM_DQ9

MEM_DQ15

MEM_DQ11

MEM_DQ13

MEM_DQ12

MEM_DQ3

MEM_DQ7

MEM_DQ1

MEM_DQ0

MEM_DQ2

MEM_DQ6

MEM_DQ4

MEM_DQ5

2.5VSUS

C139

.1U

C147

.1U

11

DDR_VREF

C845

.1U

C846

.1U

C847

.1U

C849

.1U

C850

.1U

PROJECT : EF5

C848

.1U

Quanta Computer Inc.

Size Document Number Rev

5

4

3

2

Date: Sheet

DDR SO-DIMM * 2

11 40Thursday, June 10, 2004

1

1ACustom

of

Page 12

5

DDR TERMINATION

4

3

2

1

12

SMDDR_VTERM

2.5VSUS

CA54

.1U

CA23

.1U

CA104

.1U

CA81

.1U

CA65

.1U

CA66

.1U

CA88

.1U

CA82

.1U

CA43

.1U

CA68

.1U

CA56

.1U

CA85

.1U

CA29

.1U

CA63

.1U

CA103

.1U

CA99

.1U

CA22

.1U

CA33

.1U

CA76

.1U

CA28

.1U

2.5VSUS

2.5VSUS

2.5VSUS

2.5VSUS

2.5VSUS

MEM_DQ20

M_DM2

MEM_DQ23

MEM_DQ16

MEM_DQ28

MEM_DQ24

M_DM3

MEM_DQ26

MEM_DQ29

MEM_DQ25

MEM_DQ22

MEM_DQ19

MEM_DQ17

MEM_DQ18

MDQS2

MEM_DQ21

MEM_DQ36

M_DM4

MEM_DQ37

MEM_DQ34

MEM_DQ44

M_DM5

MEM_DQ46

MEM_DQ42

MEM_DQ39

MEM_DQ33

MDQS4

MEM_DQ32

MEM_DQ43

MEM_DQ47

MDQS5

MEM_DQ40

MEM_DQ41

MEM_DQ45

MEM_DQ35

MEM_DQ38

MEM_DQ52

M_DM6

MEM_DQ48

MEM_DQ50

MEM_DQ51

MEM_DQ53

MDQS6

MEM_DQ49

MEM_DQ60

M_DM7

MEM_DQ62

MEM_DQ63

MEM_DQ58

MEM_DQ59

MDQS7

MEM_DQ61

MEM_DQ56

MEM_DQ57

MEM_DQ54

MEM_DQ55

RN61 56X4

6

4

2

RN57 56X4

6

4

2

RN56 56X4

6

4

2