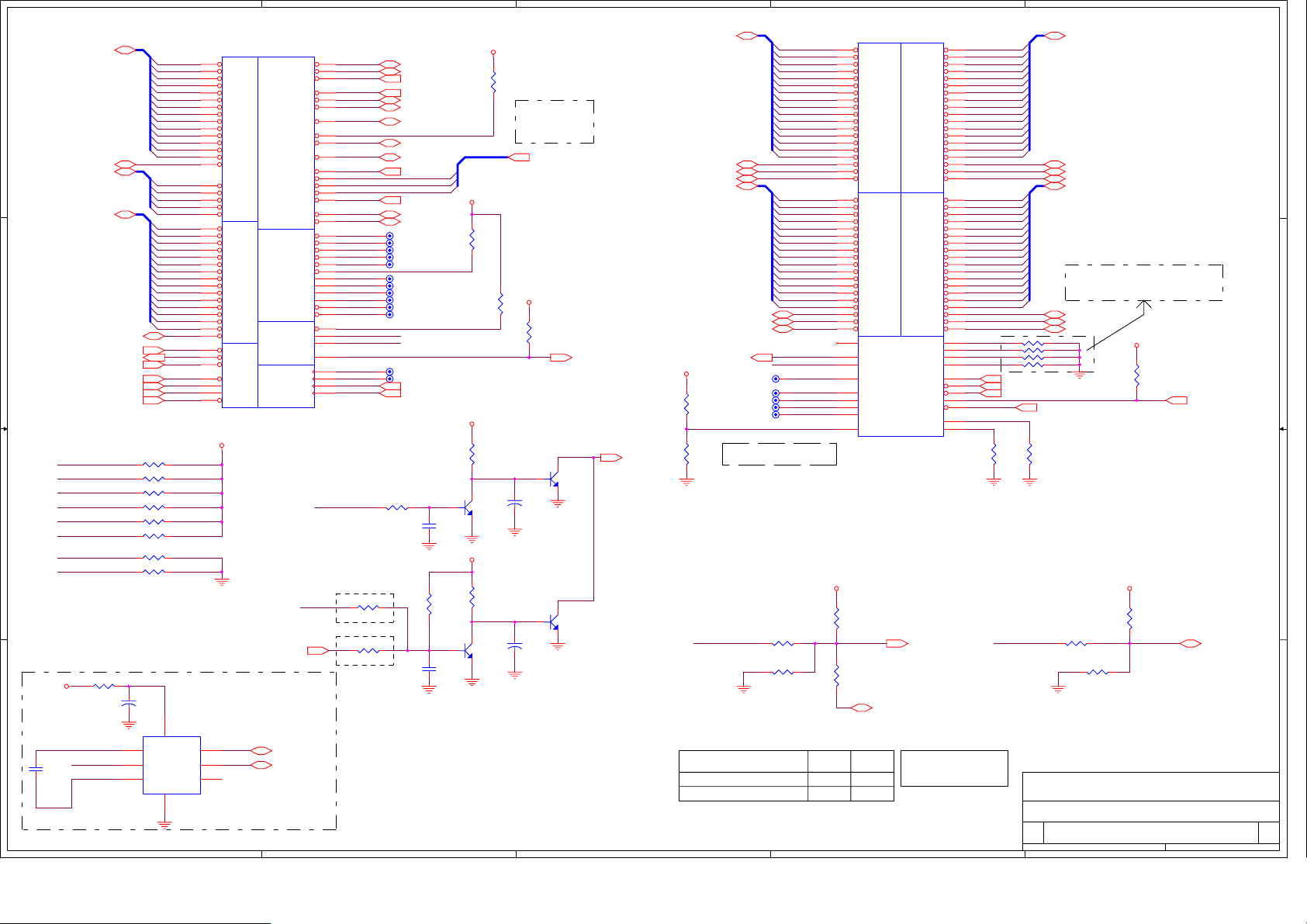

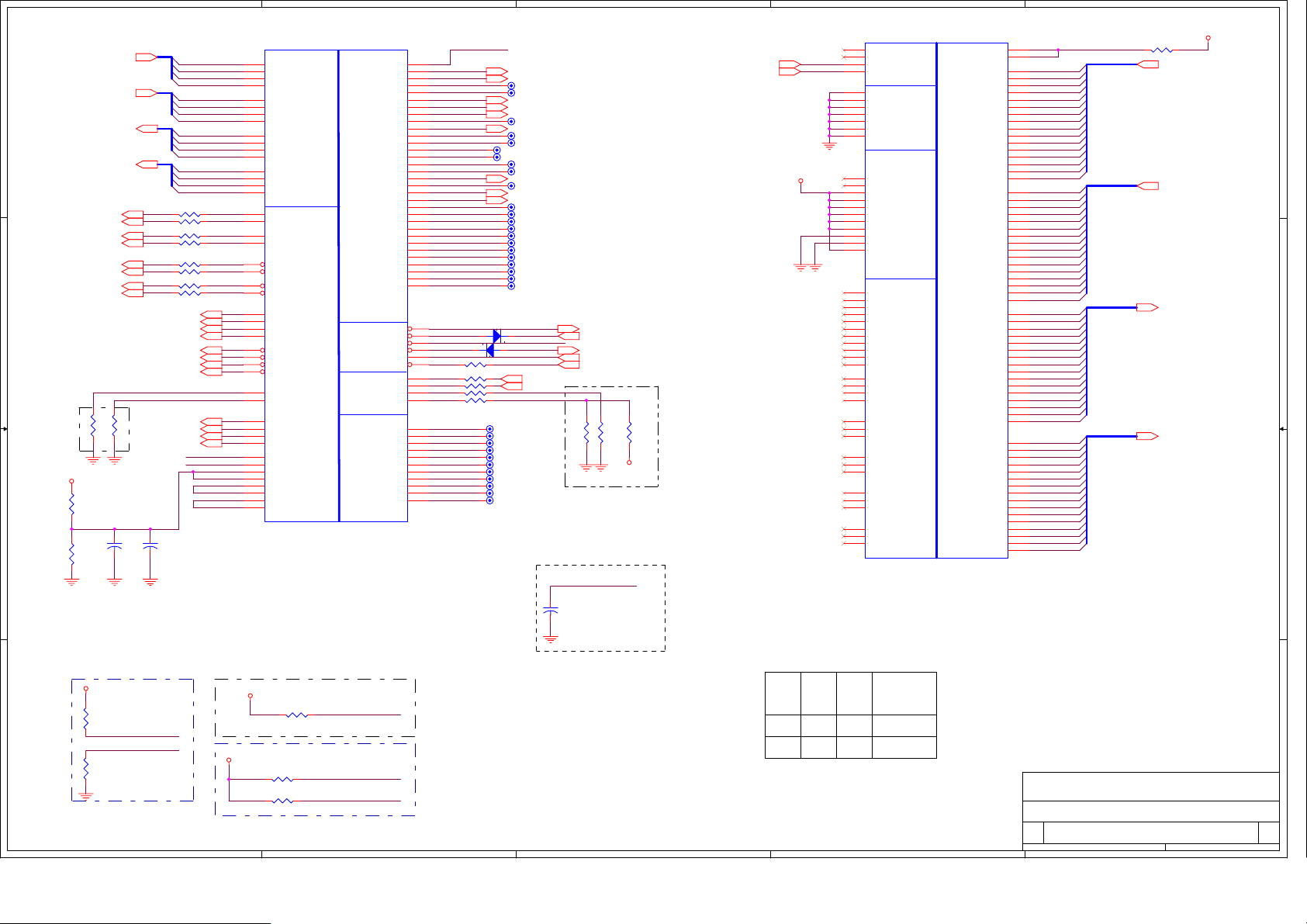

FUJITSU SIEMENS M3438, M4438 Schematics

5

D D

Model : P71EN0

4

3

2

Revision History

A

10/2004

B

1/2005

ORIGINAL RELEASE

REV.B RELEASE

1

Mobile Dothan with INTEL 915PM / ICH6-M Chipset

PG01 INDEX

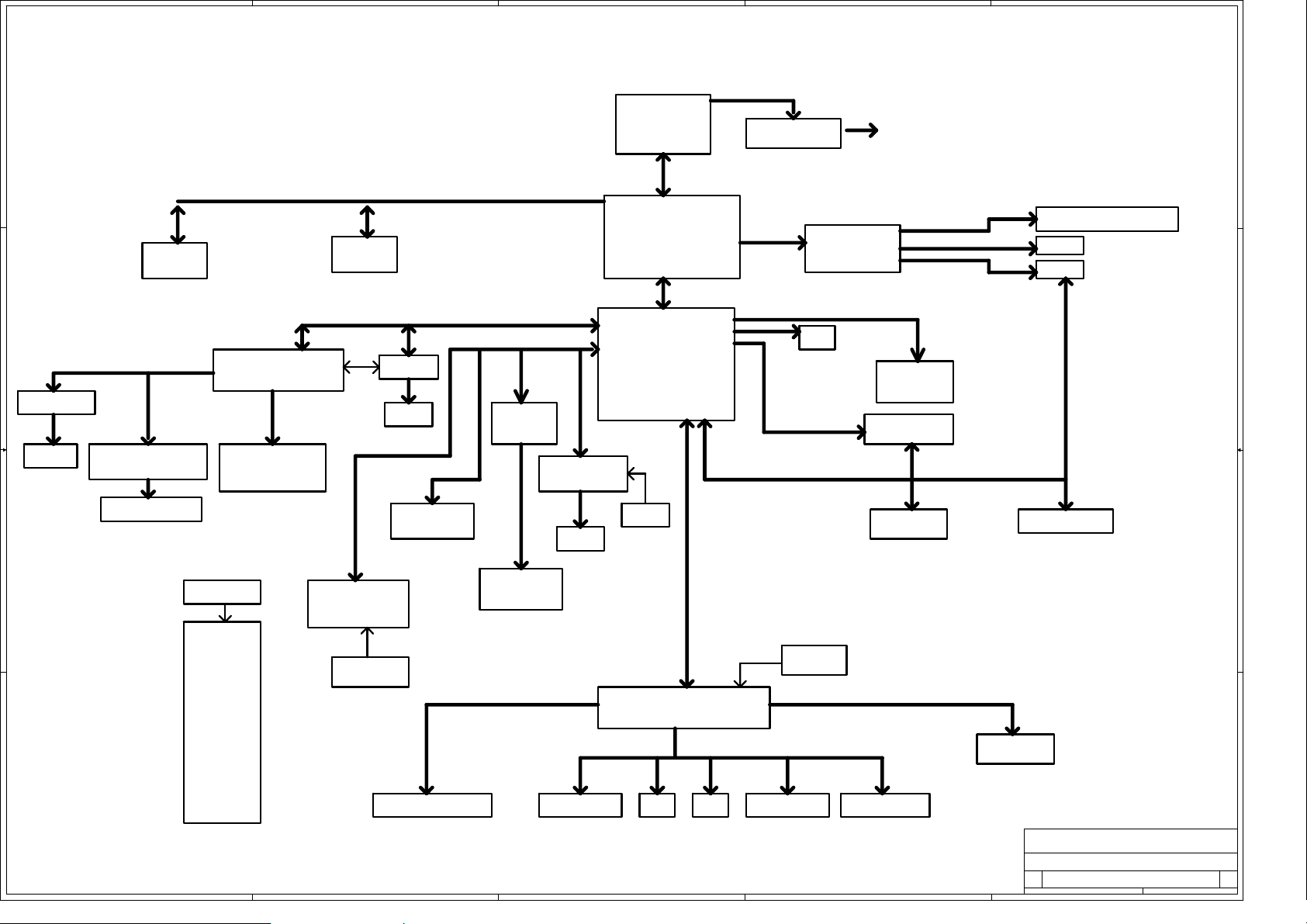

PG02 SYSTEM BLOCK DIAGRAM

C C

PG03 POWER DIAGRAM & SEQUENCE

PG04 GPIO & POWER CONSUMPTION

PG05 CPU Banias/Dothan-1/2

PG06 CPU Banias/Dothan-2/2

PG07 CLOCK GEN ICS954127

PG08 NB_Alviso Host-1/5

PG09 NB DDRCLK_VGA_PCIEXPR-2/5

PG10 NB DDR_MEM SYSTEM-3/5

PG11 NB POWER-4/5

PG12 NB VSS_NCTF-5/5

PG13 DDR2 CHANNELA,B

PG14 DDR2 Terminate

B B

PG15 PWR S/W& LCD/INVERTOR/CRT/TV

PG16 AC IN

PG21 RAID IC VT6421

PG22 NEW CARD

PG23 MINI PCI(Wireless)

PG24 I/O PORT CON

PG25 AUDIO POWER / FAN CTL

PG26 GIGA LAN RTL8110SBL

PG27 IEEE1394A TSB43AB22A

PG28 EC IT8510E / BIOS / TP CON

PG29 VGA MXM CON

PG30 CPU_CORE

PG31 1.05V/1.5V/1.8V/2.5V/0.9V

PG32 +3.3V/+5V/+12V

PG33 VCC SW/+1.05VS/+1.5VS

PG34 BATT IN / Charger

PG35 Appendix A. Ver. History

PG17 SB ICH-6M-1/3

PG18 SB ICH-6M-2/3

PG19 SB ICH-6M-3/3

PG20 HDD / CD-ROM

A A

P71EN0 P/N: 37-UJ0000-00B ; 82-UJ0001-00B

5

4

3

2

Title

Size Document Number Rev

Date: Sheet

UNIWILL COMPUTER CORP.

P71EN0

2963

INDEX

1

135Thursday, January 13, 2005

B

of

5

4

3

2

1

P71EN0

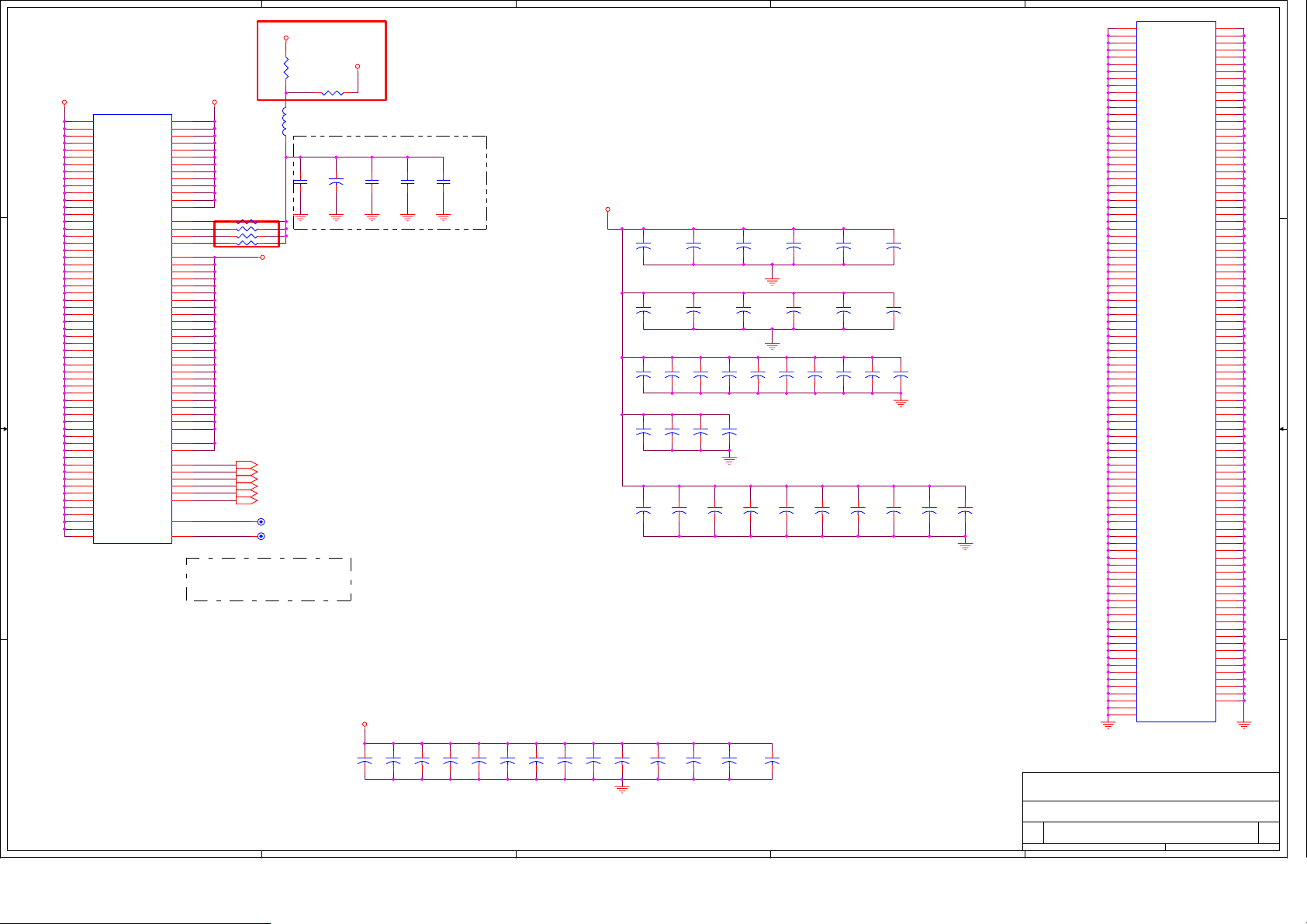

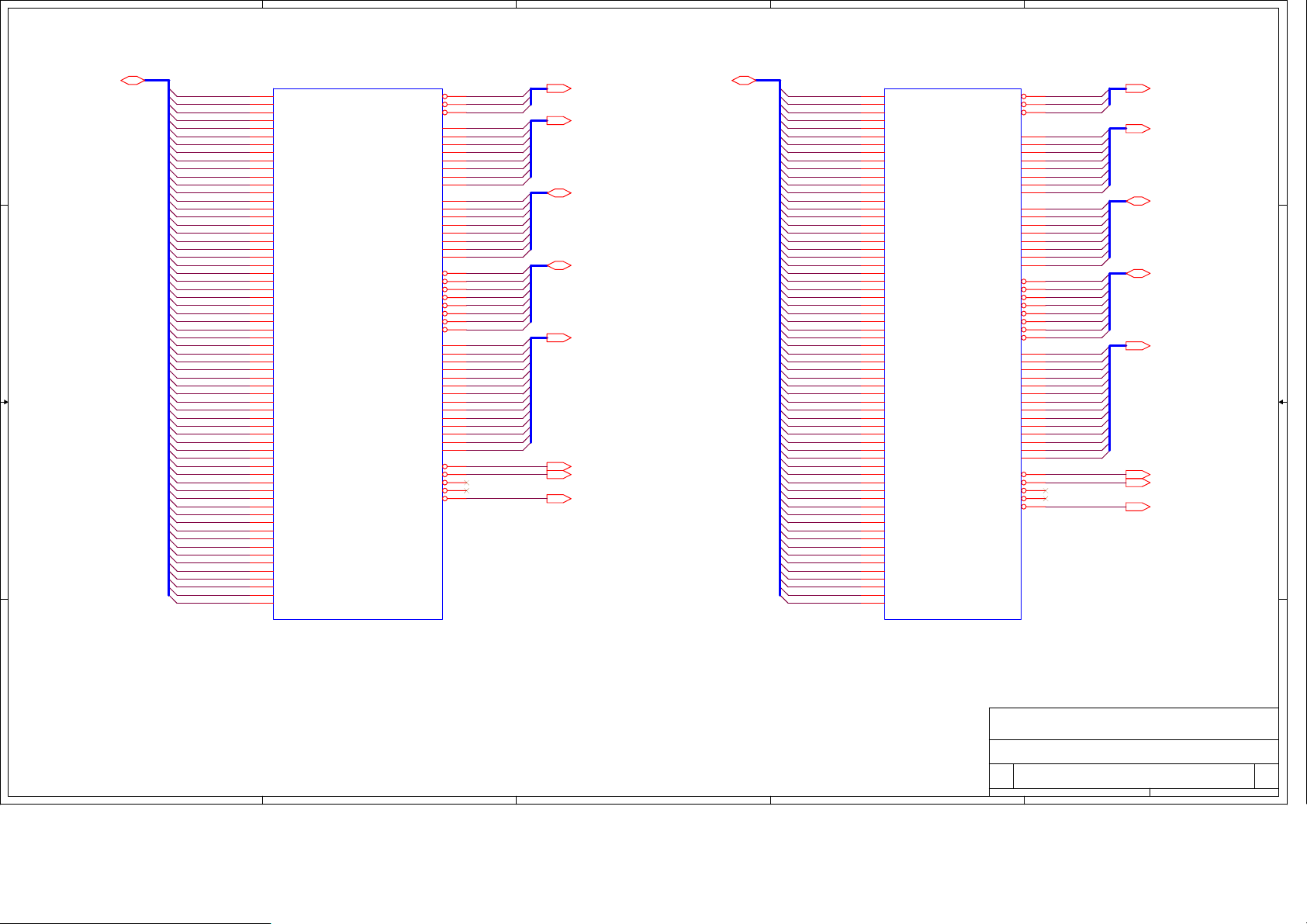

D D

BLOCK DIAGRAM

CPU

Dothan

Socket 478

THERMAL

ADM1032

EC

HOST BUS

400/533MHZ

SODIMM1

+1.8VS

+0.9V terminal

C C

SODIMM0

+1.8VS

+0.9V terminal

AUDIO CODEC

ALC880

Amplifier

LM4991

WOOFER

SPK

B B

AMPLIFIER

TPA6011A4

INTERNAL SPK

Clock Gen

EARPHONE

JACK(SPDIF) X 1

MICPHONE JACK X 1

CRYSTAL

14.318MHz

ICS

ICS954127

IEEE-1394A

TSB43AB22

CRYSTAL

24.576M HZ

DDR2 RAM BUS

AZALIA

MDC

RJ11

MINI PCI CONN

(Wireless)

PCI BUS

RAID

VT6421

SATA HDD X2

2.5"

PRIMARY

MASTER

North Bridge

South Bridge

GIGA LAN

RTL8110SBL

RJ45

EC

K/B CONTROLLER

INTEL

915PM

INTEL

ICH6-M

CRYSTAL

25M HZ

LPC BUS

DMI

ITE8510

PCIE

PS/2 & GPIO

RTC

SECONDARY

MASTER

PCIE

USBX8

CRYSTAL

32.768K

NV41-M

IDE

NEW CARD

USB CONNx4

PS/2 & GPIO

LVDS

TMDS&CRT

CD-ROM

+5V

S-Video TV

LCD

DVI

CARD READER

REMOTE IR

A A

3

T/P

FAN

CHARGER

BATTERY

2

Title

Size Document Number Rev

Date: Sheet

UNIWILL COMPUTER CORP.

P71EN0

SYSTEM BLOCK DIAGRAM

2963

1

235Thursday, January 13, 2005

of

B

FLASH ROM

5

4

INT K/B

5

4

3

2

1

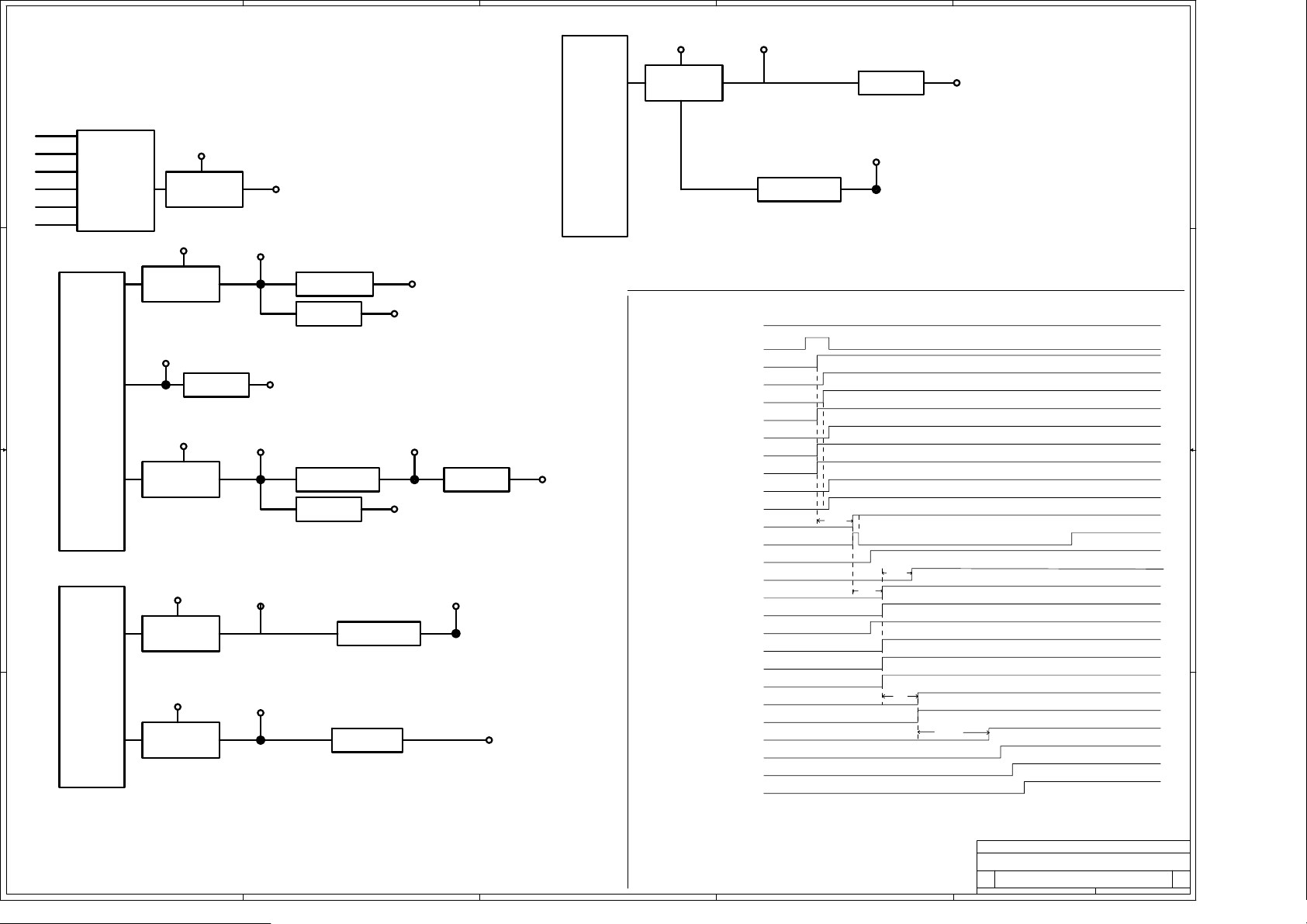

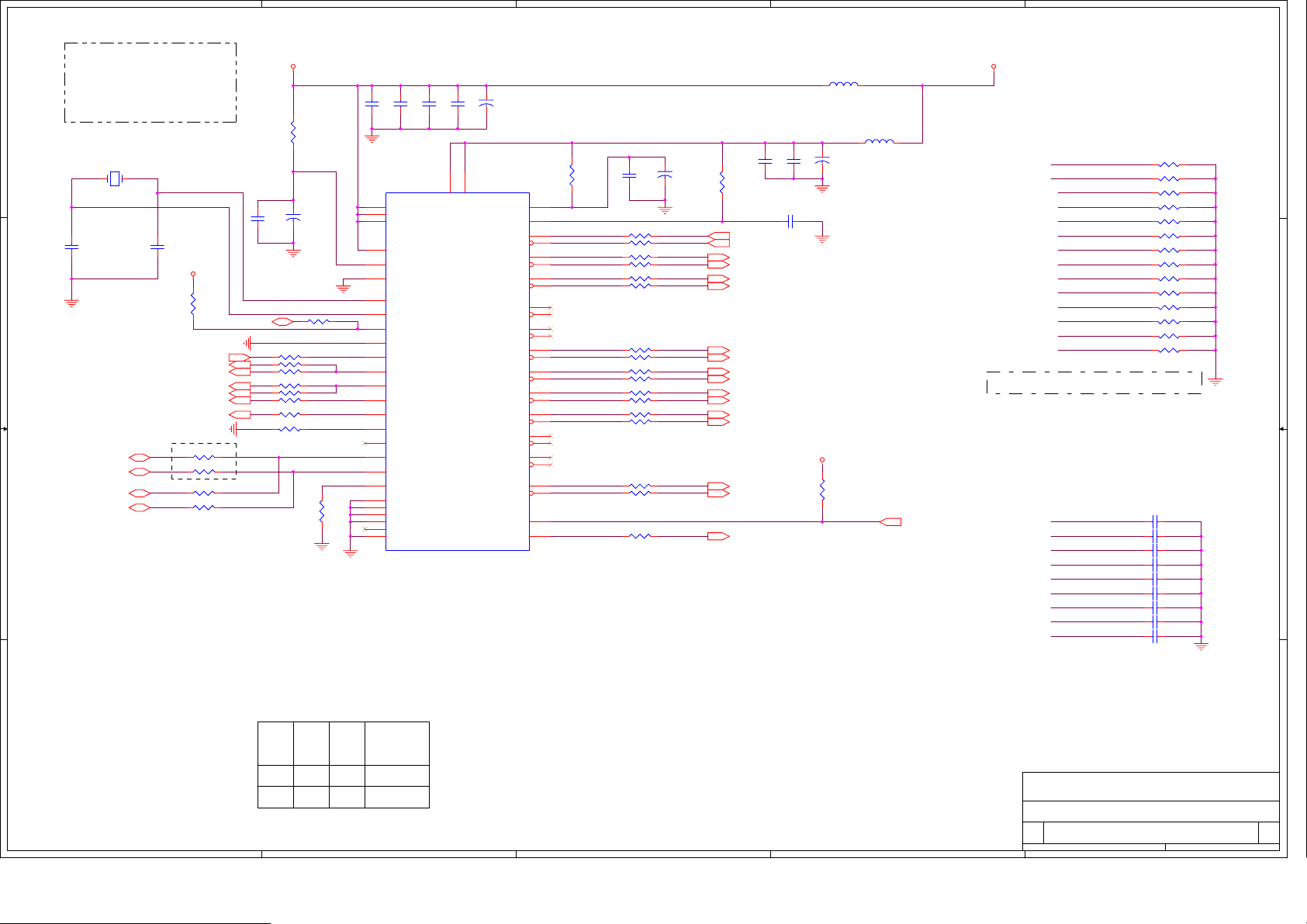

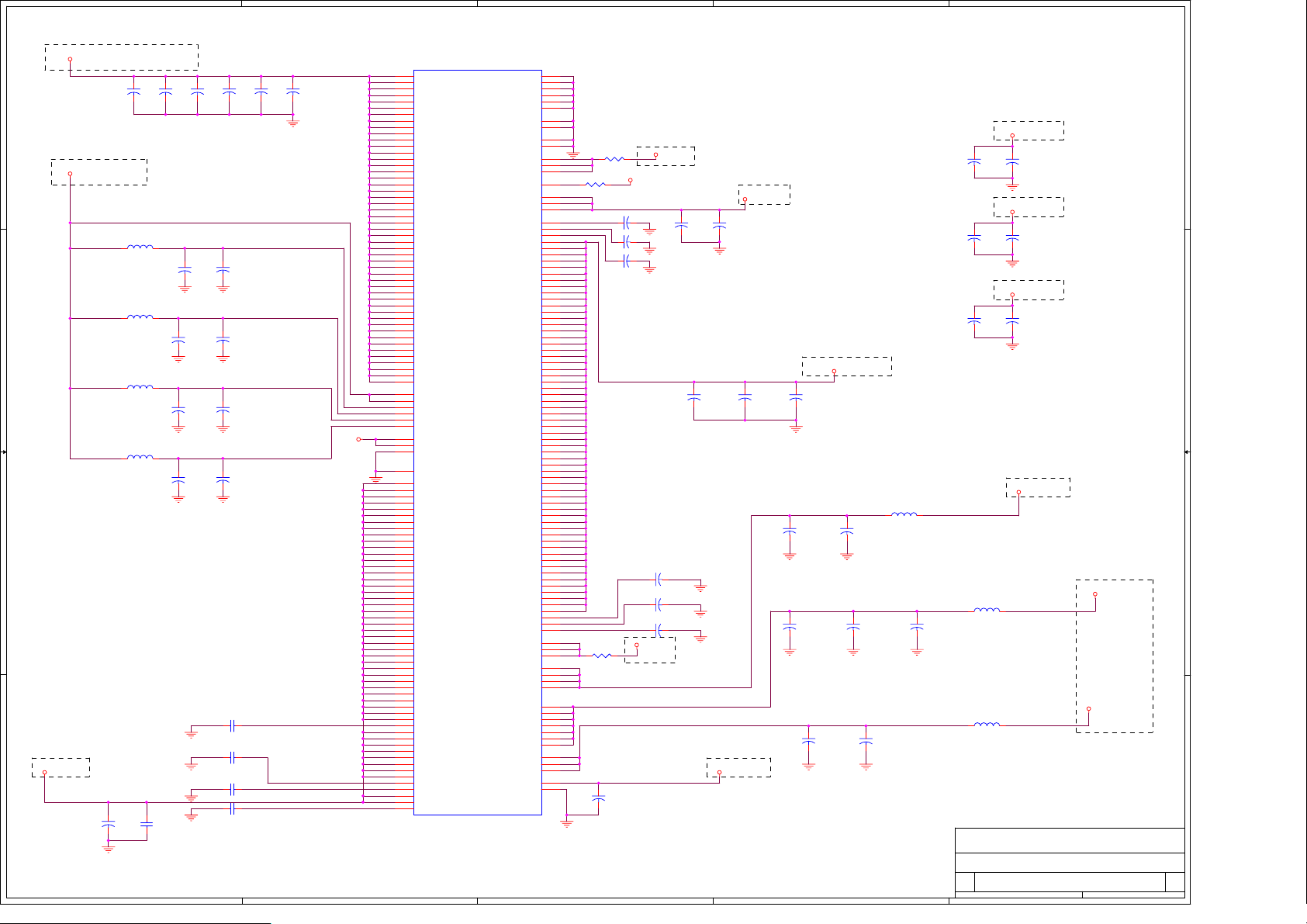

POWER BLOCK DIAGRAM

ISL6224

D D

VID0

VID1

VID2

VID3

VID4

SC451

VIN

RSS090N03

SI4362

CPU_CORE

VIN

RSS090N03

+1.8VS

AO4422

RT9173B

+1.8V

+0.9VS

VID5

VIN

RSS090N03

C C

SC1404

+12VA

SI2301

VIN

RSS090N03

B B

VIN

ISL6225

RSS090N03

VIN

RSS090N03

A A

+5VA

+12VS

+3.3VA

+1.5VS/4.5A

+1.05VS/4.5A

AO4422

SI4835

AO4422

SI4835

AO4422

AO4422

+5VS

+5V

+3.3VS

+3.3V/

+1.5V

RT9173B

>

0.9A

+2.5VS

+1.05V/1.8A

POWER Sequence

+3VA,+5VA,+12VA

PWRSW

.

+3.3VS_ON

+5VS,+12VS

+3.3VS

+1.5VS_ON

.

+1.5VS

.

+1.05VS_ON

+1.8V_DDR_ON

.

+1.8VS

+1.05VS

RSMRST#

.

.

PWRBTN#

.

+5V_ON

+1.8V_ON

.

+1.8V

+1.05V

+1.5V

.

Vcore_ON

Vcore

.

PWROK/VR_PWRGD

H_PWRGD

PCIRST#/PLTRST#

CPURST#

+5V

+3.3V

+2.5V

1ms

1ms

1ms

50ms

10ms

40ms

1s

5.8ms

7ms

110ms

.

EC Control Pin

5

4

3

2

UNIWILL COMPUTER CORP.

Title

Size Document Number Rev

C

2963

Date: Sheet

P71EN0

POWER DIAGRAM

1

of

335Thursday, January 13, 2005

B

5

4

3

2

1

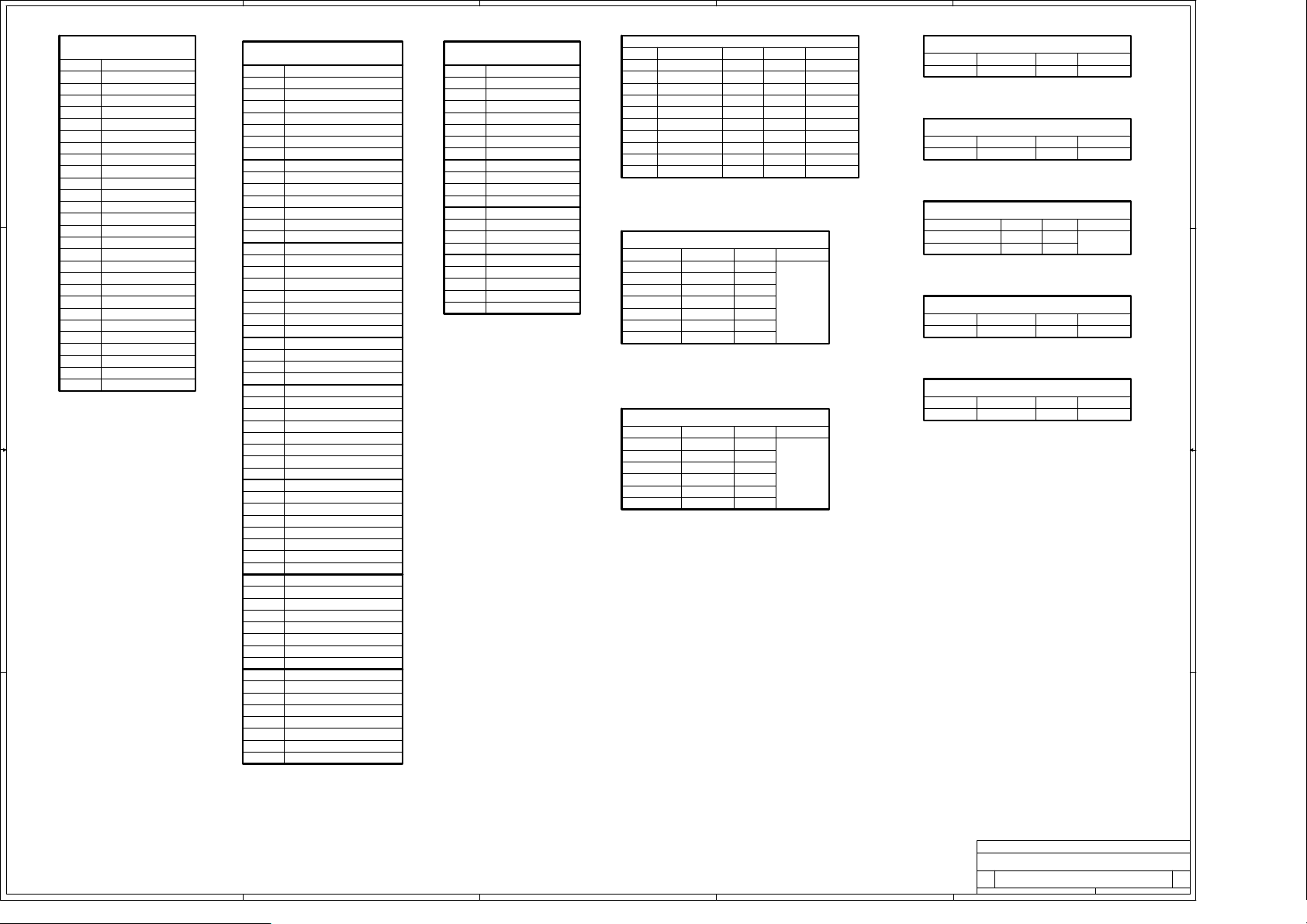

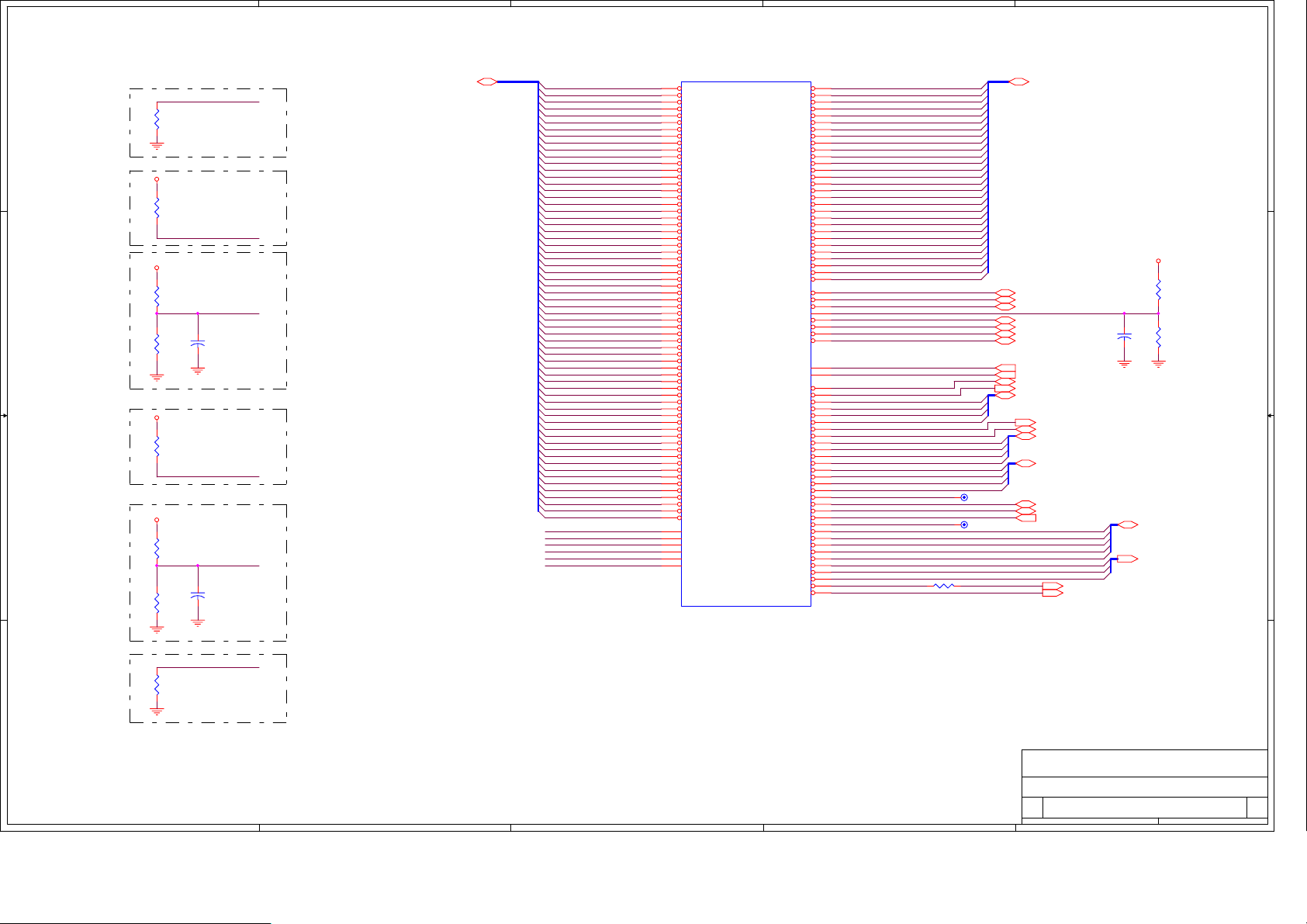

ICH6-M

GPIO

BM_BUSY#

GPI6

GP7

EC_EXTSMI#

GP8

SMB_ALERT#

GPI11

D D

C C

B B

GPI12

GPI13

GPO18

GPO19

GPO20

GPO21

GPO23

GPIO24

GPIO25

GPIO26

GPIO27

GPIO28

GPIO29

GPIO30

GPIO31

GPIO32

GPIO33

GPIO34

PM_STPPCI_ICH#

PM_STPCPU_ICH#

TPM_EN

SATA0_GP

PNLSW1

PNLSW2

PNLSW0

PM_CLKRUN#

ITE8510E

GPIO

GPCF0

RF_SW#

GPCF1

SILENT#/

GPCF2

IR_PS2CLK1

GPCF3

IR_PS2DAT1

GPCF4

TP_CLK

GPCF5

TP_DATA

MAIL#

GPCF6

BROWSER#

GPCF7

GPI0

SCROLL#

GPI1

CAPS#

GPI2

NUM#

GPI3

CHG_R_LED#

CHG_G_LED#

GPI4

GPI5

SUSLED_LED#

GPI6

VOLMAX

GPH0

+1.8V_DDR_ON

+1.8V_ON

GPH1

GPH2

+1.05VS_ON

GPH3

+3.3VS_ON

+5V_ON

GPH4

GPH5

SET_V

GPH6

+1.5VS_ON

VCORE_ON

GPH7

GPG4

TP_DISABLE

LCDSW

GPG5

GPG6

MUTE#

GPG7

EXTTS#0

CELERON_VO_DET

GPB0

GPB1

CPPE#

PM_RSMRST#

GPB2

GPB3

BAT_SMBCLK

GPB4

BAT_SMBDAT

H_A20GATE

GPB5

H_RCIN#

GPB6

GPB7

RFLED_ON#

GPE0

NA

CPU_BSEL0

GPE1

GPE2

NA

GPE3

NA

GPE4

PWRSW

GPE5

LID#

GPE6

PCM#

PM_SLP_S3#

GPE7

GPD0

ADAP_IN

GPD1

REMOTE_ON#

PCI_RST#/PLT_RST#

GPD2

GPD3

EC_EXTSMI#

GPD4

PM_SLP_S4#

GPD5

PM_THROTTLING#

FAN_SPD#

GPD6

EC_PREST#

GPD7

BTL_BEEP

GPA0

EC_VID1

GPA1

GPA2

EC_VID2

GPA3

EC_VID3

GPA4

EC_VID4

GPA5

SMP1_EN#

GPA6

SMP2_EN#

GPA7

PWRBTN#

GPC0

GPC1

GPC2

GPC3

GPC4

GPC5

GPC6

GPC7

ADC0

ADC1

ADC2

ADC3

DAC0

DAC1

DAC2

DAC3

ITE8510E

GPIO

PWROK

BAT2_SMBCLK

BAT2_SMBDAT

SB_ALERT#1

SB_ALERT#2

TP_LED#

CHG_ON

SILENT_LED#

BAT_TEMP

ADAPTOR_I

DDR2_TEMP

VGA_TEMP

BRIGHTADJ

CHG_I

FAN_CTRL0

NA

CPU CORE(V)

2.0G

2.2G

2.26G

2.4G

2.5G

2.53G

2.6G

2.66G

2.8G

3.06G

VCC

+3.3V

+3.3VA

+2.5V

+1.5V

+VCCP

+VCC_GMCH_CORE

VCC

+3.3V

+3.3VA

+1.5V

+1.5VA

+3.3VA_RTC

CPU

ICC(mA)

1.525

1.525

1.525

1.525

1.525

1.525

1.525

1.525

1.525

1.525

35.7

37.5

38.1

39.3

40

40.4

41.05

43.35

44.86

55.9

MCHE

ICC(mA)

108.19

501.3

1390

33.4

10

266

ICH6-M

ICC(mA) W

275

487

27

0.003

W

0.357

1.254

2.502

0.084

0.018

0.452

0.315

0.909

0.876

0.049

0.00001

W

54.3

57.1

58.0

59.8

61.0

61.5

62.6

66.1

68.4

85.2

TEMP( )

70

TEMP( )

70

TEMP( )

℃

69

70

70

71

72

72

72

74

75

81

℃

℃

VCC

+3.3V

VCC

+3.3V

VCC

+3.3V(DVDD)

VCC

3.3V9630

VCC

+3.3V

ITE8510E

ICC(mA)

300

W

1

CLOCK GENERATOR

ICC(mA)

180

W

0.594

ALC880

ICC(mA)

W

0.234

71

TPA6011A4

ICC(mA)

W

0.099W

ADM1032

ICC

170uA

W

0.56mW

TEMP( )

℃

70

TEMP( )

℃

70

℃

TEMP( )

70

TEMP( )

℃

85

TEMP( )

℃

150

A A

UNIWILL COMPUTER CORP.

Title

Size Document Number Rev

C

2963

5

4

3

2

Date: Sheet

P71EN0

GPIO & POWER CONSU

1

B

of

435Thursday, January 13, 2005

5

4

3

2

1

H_D#[63:0]8

H_DSTBP#08

H_DINV#08

H_DSTBN#18

H_DSTBP#18 H_DSTBP#3 8

H_DINV#18

CPU_BSEL028

+1.05V

TP1

R62

100_1

H_GTLREF

R63

Layout note: 0.5" max length.

200_1

CPU_BSEL0

PSB400 1

PSB533(dafault)

C345

0.1u

R348

100K

C320

0.1u

H_RS#[2:0]

+1.05V

CPU_CORE

B

+3.3V

B

E C

E C

+1.05V

R35

56_OP

R360

100K

Z0510

Q62

2N3904

R341

100K

Z0512

Q53

2N3904

R334

56

Place testpoint on

H_IERR# with a GND

0.1" away

H_RS#[2:0] 8

R49

+1.05V

56

R48

75_1

B

C344

1u/10V

B

C307

1u/10V

PM_THRMTRIP# 9,17

Q61

2N3904

E C

Q55

2N3904

E C

AUX_OFF# 32

3

H_A#[31:3]8

D D

H_ADSTB#08

H_REQ#[4:0]8

H_A#[31:3]8

C C

B B

H_STPCLK#17

H_STPCLK#

TDO

TMS

TDI

H_CPURST#

DBR#

TRST#

TCK

H_ADSTB#18

H_A20M#17

H_FERR#17

H_IGNNE#17

H_INTR17

H_NMI17

H_SMI#17

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

R34 150_1

R36 54.9_1_OP

R342 39.2_1

R37 150_1

R44 54.9_1_OP

R340 150_1_OP

R45 680

R43 27.4_1

P4

U4

V3

R3

V2

W1

T4

W2

Y4

Y1

U1

AA3

Y3

AA2

U3

R2

P3

T2

P1

T1

AF4

AC4

AC7

AC3

AD3

AE4

AD2

AB4

AC6

AD5

AE2

AD6

AF3

AE1

AF1

AE5

C2

D3

A3

C6

D1

D4

B4

+1.05V

U4A

A3#

A4#

A5#

A6#

A7#

A8#

A9#

A10#

A11#

A12#

A13#

A14#

A15#

A16#

ADSTB#0

REQ0#

REQ1#

REQ2#

REQ3#

REQ4#

A17#

A18#

A19#

A20#

A21#

A22#

A23#

A24#

A25#

A26#

A27#

A28#

A29#

A30#

A31#

ADSTB#1

A20M#

FERR#

IGNNE#

STPCLK#

LINT0

LINT1

SMI#

ADDR GROUP 0 ADDR GROUP 1

ADS#

BNR#

BPRI#

DEFER#

DRDY#

DBSY#

BR0#

IERR#

CONTROLITP SIGNALSTHERMH CLK

INIT#

LOCK#

RESET#

RS0#

RS1#

RS2#

TRDY#

HIT#

HITM#

BPM#0

BPM#1

BPM#2

BPM#3

PRDY#

PREQ#

TDO

TMS

TRST#

DBR#

PROCHOT#

THERMDA

THERMDC

THERMTRIP#

ITP_CLK1

ITP_CLK0

BCLK1

BCLK0

TCK

N2

L1

J3

L4

H2

M2

N4

H_IERR#

A4

B5

J2

H_CPURST#

B11

H_RS#0

H1

H_RS#1

K1

H_RS#2

L2

M3

K3

K4

Z0501

C8

Z0502

B8

Z0503

A9

Z0504

C9

Z0505

A10

Z0506

B10

TCK

A13

TDI

C12

TDI

TDO

A12

TMS

C11

TRST#

B13

DBR#

A7

H_PROCHOT#

B17

H_THERMDA

B18

H_THERMDC

A18

PM_THRMTRIP#

C17

Z0507

A15

Z0508

A16

B14

B15

H_ADS# 8

H_BNR# 8

H_BPRI# 8

H_DEFER# 8

H_DRDY# 8

H_DBSY# 8

H_BREQ#0 8

H_INIT# 17

H_LOCK# 8

H_CPURST# 8

H_TRDY# 8

H_HIT# 8

H_HITM# 8

TP4

TP5

TP7

TP6

TP8

TP11

TP12

TP2

TP9

TP10

TP3

TP14

TP13

CLK_CPU_BCLK# 7

CLK_CPU_BCLK 7

R361 1K

Z0509PM_THRMTRIP#

Modify 2

H_THERM#

R700 0

Modify 1

DK_MXM_THERM#29

R349 0

Z0511

CPU Thermal Sensor

+3.3V

R374 200_1

2.2U_X5R

C357

2200p

H_THERMDA

H_THERM#

H_THERMDC

A A

C359

2

4

3

5

Z0513

U15

D+

THERM#

D-

1

VDD

GND

ADM1032

5

ADATA

SCLK

ALERT

7

8

6

SMBDAT_EC 7,28

SMBCLK_EC 7,28

4

CPU_BSEL1

TP53

TP56

TP52

TP15

R57 0

R50 0_OP

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

CPU_BSEL0

TP_CPU_NC1

TP_NC_2

TP_NC_3

TP_NC_4

TP_NC_5

BSEL0

U4B

A19

D0#

A25

D1#

A22

D2#

B21

D3#

A24

D4#

B26

D5#

AD26

A21

B20

C20

B24

D24

E24

C26

B23

E23

C25

C23

C22

D25

H23

G25

M26

H24

F25

G24

M23

N24

M25

H26

N25

K25

K24

C16

C14

AF7

AC1

E26

L23

J23

J25

L26

L24

J26

E1

B2

C3

R58

470

R60

1K_1

DATA GRP0

D6#

D7#

D8#

D9#

D10#

D11#

D12#

D13#

D14#

D15#

DSTBN0#

DSTBP0#

DINV0#

D16#

D17#

D18#

D19#

D20#

D21#

D22#

D23#

D24#

D25#

D26#

D27#

D28#

D29#

D30#

D31#

DSTBN1#

DSTBP1#

DINV1#

PSI#

BSEL0

BSEL1

MISC

NC1

RSVD2

RSVD3

RSVD4

RSVD5

GTLREF0

MCH_BSEL0 9

BSEL1

0

00

Y26

D32#

AA24

D33#

T25

D34#

U23

D35#

V23

D36#

R24

D37#

R26

D38#

R23

D39#

AA23

D40#

U26

D41#

V24

D42#

U25

D43#

V26

D44#

Y23

DATA GRP2

D45#

AA26

D46#

Y25

D47#

W25

DSTBN2#

W24

DSTBP2#

T24

DINV2#

AB25

D48#

AC23

D49#

AB24

D50#

AC20

D51#

AC22

D52#

DATA GRP1

2

AC25

D53#

AD23

D54#

AE22

D55#

AF23

D56#

AD24

D57#

AF20

D58#

AE21

D59#

DATA GRP3

AD21

D60#

AF25

D61#

AF22

D62#

AF26

D63#

AE24

DSTBN3#

AE25

DSTBP3#

AD20

DINV3#

P25

COMP0

P26

COMP1

AB2

COMP2

AB1

COMP3

G1

DPRSTP#

B7

DPSLP#

C19

DPWR#

E4

PWRGOOD

A6

SLP#

C5

TEST1

F23

TEST2

ICS954206 BSEL Settings:

01=PSB400(BSEL0=1 BSEL1=0)

00=PSB533(BSEL1=0 BSEL0=0)

TEST1

TEST2

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

COMP0

COMP1

COMP2

COMP3

H_D#[63:0] 8

H_DSTBN#2 8H_DSTBN#08

H_DSTBP#2 8

H_DINV#2 8

H_D#[63:0] 8H_D#[63:0]8

Layout note:

Comp0 ,2 connect with Zo = 27.4 Ohm,make

trace length shorter than 0.5"

Comp1 ,3 connect with Zo = 55 Ohm,make

trace length shorter than 0.5"

H_DSTBN#3 8

R69 27.4_1

R70 54.9_1

R30 27.4_1

R25 54.9_1

H_DPRSTP# 17

H_DPSLP# 17

H_DPWR# 8

H_CPUSLP# 8,17

R72

R33

1K_OP

1K_OP

CPU_BSEL1

H_DINV#3 8

R56 0

R59 0_OP

+1.05V+1.05V

+1.05V

R28

200_1

R51

1K_1

H_PWRGD 17

MCH_BSEL1 9CLK_BSEL0 7

UNIWILL COMPUTER CORP.

Title

Size Document Number Rev

2963

Date: Sheet

P71EN0

CPU Banias/Dothan-1/2

1

535Thursday, January 13, 2005

B

of

5

+1.5V

R65

0_OP

Z0601

CPU_CORE

D D

C C

B B

AA11

AA13

AA15

AA17

AA19

AA21

AB10

AB12

AB14

AB16

AB18

AB20

AB22

AC11

AC13

AC15

AC17

AC19

AD10

AD12

AD14

AD16

AD18

AE11

AE13

AE15

AE17

AE19

AF10

AF12

AF14

AF16

AF18

AC9

AD8

AE9

AF8

D18

D20

D22

G21

U4C

VCC0

VCC1

VCC2

VCC3

VCC4

VCC5

AA5

VCC6

AA7

VCC7

AA9

VCC8

VCC9

VCC10

VCC11

VCC12

VCC13

VCC14

VCC15

AB6

VCC16

AB8

VCC17

VCC18

VCC19

VCC20

VCC21

VCC22

VCC23

VCC24

VCC25

VCC26

POWER

VCC27

VCC28

VCCP10

VCC29

VCCP11

VCC30

VCCP12

VCC31

VCCP13

VCC32

VCCP14

VCC33

VCCP15

VCC34

VCCP16

VCC35

VCCP17

VCC36

VCCP18

VCC37

VCCP19

VCC38

VCCP20

VCC39

VCCP21

VCC40

VCCP22

VCC41

VCCP23

VCC42

VCCP24

VCC43

VCC44

D6

VCC45

D8

VCC46

E17

VCC47

E19

VCC48

E21

VCC49

E5

VCC50

E7

VCC51

E9

VCC52

F18

VCC53

F20

VCC54

F22

VCC55

F6

VCC56

F8

VCC57

VCC58

VCCQ0

VCCQ1

VCCSENSE

VSSSENSE

VCC59

VCC60

VCC61

VCC62

VCC63

VCC64

VCC65

VCC66

VCC67

VCC68

VCC69

VCC70

VCC71

VCCA0

VCCA1

VCCA2

VCCA3

VCCP0

VCCP1

VCCP2

VCCP3

VCCP4

VCCP5

VCCP6

VCCP7

VCCP8

VCCP9

VID0

VID1

VID2

VID3

VID4

VID5

G5

H22

H6

J21

J5

K22

U5

V22

V6

W21

W5

Y22

Y6

F26

B1

N1

AC26

D10

D12

D14

D16

E11

E13

E15

F10

F12

F14

F16

K6

L21

L5

M22

M6

N21

N5

P22

P6

R21

R5

T22

T6

U21

P23

W4

E2

F2

F3

G3

G4

H4

AE7

AF6

CPU_CORE

Z0602

Z0603

Z0604

Z0605

Z0607

Z0608

R71 0

R24 0

R9 0

R68 0

H_VID0 14

H_VID1 14

H_VID2 14

H_VID3 14

H_VID4 14

H_VID5 14

R64 0

B4

FCM1608K-121T06

Z0606

C58

0.01u

4.7U_10V_0805

Reserved for FSB400 MHz

+1.05V

TP55

TP54

Layout note :

VCCSENSE and VSSSENSE line

should be of equal length

+1.8V

Close to Pin

C59

0.01u

+1.05V

4

C9

C3

C57

0.01u

0.01u

CPU_CORE

3

C310

4.7U_10V_0805

C316

4.7U_10V_0805

C319

C346

1u/10V

1u/10V

C347

C51

1u/10V

1u/10V

C49

1000p

4.7U_10V_0805

4.7U_10V_0805

C336

1000p

C317

C324

C329

1u/10V

C41

1u/10V

C349

1000p

4.7U_10V_0805

4.7U_10V_0805

C53

1u/10V

C343

1u/10V

C28

C342

C331

1000p

C27

1u/10V

C37

4.7U_10V_0805

C341

4.7U_10V_0805

C318

C29

1u/10V

1u/10V

C312

1000p

C314

1000p

C321

4.7U_10V_0805

C315

4.7U_10V_0805

C46

C45

1u/10V

1u/10V

C323

1000p

2

C340

4.7U_10V_0805

C332

4.7U_10V_0805

C334

1u/10V

C52

1000p

C26

1000p

C35

1000p

AA10

AA12

AA14

AA16

AA18

AA20

AA22

AA25

AB11

AB13

AB15

AB17

AB19

AB21

AB23

AB26

AC2

AC5

AC8

AC10

AC12

AC14

AC16

AC18

AC21

AC24

AD1

AD4

AD7

AD9

AD11

AD13

AD15

AD17

AD19

AD22

AD25

AE3

AE6

AE8

AE10

AE12

AE14

AE16

AE18

AE20

AE23

AE26

AF2

AF5

AF9

AF11

AF13

AF15

AF17

AF19

AF21

AF24

C10

C13

C15

C18

C21

C24

D11

1

U4D

A2

VSS0

A5

VSS1

A8

VSS2

A11

VSS3

A14

VSS4

A17

VSS5

A20

VSS6

A23

VSS7

A26

VSS8

AA1

VSS9

AA4

VSS10

AA6

VSS11

AA8

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

AB3

VSS21

AB5

VSS22

AB7

VSS23

AB9

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

B3

VSS75

B6

VSS76

B9

VSS77

B12

VSS78

B16

VSS79

B19

VSS80

B22

VSS81

B25

VSS82

C1

VSS83

C4

VSS84

C7

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

D2

VSS92

D5

VSS93

D7

VSS94

D9

VSS95

VSS96

VSS

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

VSS161

VSS162

VSS163

VSS164

VSS165

VSS166

VSS167

VSS168

VSS169

VSS170

VSS171

VSS172

VSS173

VSS174

VSS175

VSS176

VSS177

VSS178

VSS179

VSS180

VSS181

VSS182

VSS183

VSS184

VSS185

VSS186

VSS187

VSS188

VSS189

VSS190

VSS191

D13

D15

D17

D19

D21

D23

D26

E3

E6

E8

E10

E12

E14

E16

E18

E20

E22

E25

F1

F4

F5

F7

F9

F11

F13

F15

F17

F19

F21

F24

G2

G6

G22

G23

G26

H3

H5

H21

H25

J1

J4

J6

J22

J24

K2

K5

K21

K23

K26

L3

L6

L22

L25

M1

M4

M5

M21

M24

N3

N6

N22

N23

N26

P2

P5

P21

P24

R1

R4

R6

R22

R25

T3

T5

T21

T23

T26

U2

U6

U22

U24

V1

V4

V5

V21

V25

W3

W6

W22

W23

W26

Y2

Y5

Y21

Y24

A A

5

C43

0.1u

C54

C50

0.1u

C38

0.1u

0.1u

4

C47

0.1u

C44

0.1u

C18

0.1u

C19

0.1u

C42

0.1u

C32

C36

C48

C55

0.1u

4.7U_10V_0805

3

4.7U_10V_0805

4.7U_10V_0805

C31

4.7U_10V_0805

UNIWILL COMPUTER CORP.

Title

Size Document Number Rev

2963

2

Date: Sheet

P71EN0

CPU Banias/Dothan-2/2

1

635Thursday, January 13, 2005

B

of

5

4

3

2

1

Ce = 2*CL - ( Cs + Ci )

CL = Crystal Load Cap = 20P

Ci = IC internal Cap = 5P

Cs = 2P

D D

C C

Ce = Crystal external Cap = 33P

Y2

14.318MHz_DIP

C497

33p

C503

33p

PCICLK_MINIPCI23

PCICLK_1394_A27

+3.3V

R150

10K

CLK_USB4818

CLK_BSEL05

PCICLK_RAID21

PCICLK_LAN26

CLK_PCI18

CLK_PCI_LPC28

Modify 3

SB_SMB_CLK13,18,19

SB_SMB_DATA13,18,19

SMBCLK_EC5,28

SMBDAT_EC5,28

B B

R151 0_OP

R152 0_OP

R147 0

R149 0

+3.3VS_CLKVDD

FB1

C137

0.1u

QT1608RL600

C513

4.7U_10V_0805

+3.3V

R154

10K

FB2

QT1608RL600

VTT_PWRGD# 30

C124

C122

FSA

FSC

PCI5

PCI4

PCI3

PCI2

PCIF1

Z0701

Z0702

0.1u

U22

19

VDDSRC

28

VDD_PCIEX

34

VDD_PCIEX1

42

VDD_CPU

37

VDDA

38

GNDA

50

XTAL_IN

49

XTAL_OUT

12

FSA/USB_48

16

GND

8

FSC/PCICLK_F0

5

PCI3

4

PCI2

3

PCI1

56

PCICLK0~

9

FSB/PCICLK_F1

53

RTFS_0

46

SCLK

47

SDATA

39

IREF

13

VSS_48

29

VSS_PCIE

45

VSS_CPU

2

VSS_PCI

6

RESET#

51

VSS_REF

ICS 954127

R121

2.2

VDD_A_CR

C482

C129

4.7U_10V_0805

0.1u

XTAL_IN

XTAL_OUT

R481 33 R131 49.9_1

R157 4.7K

R489 56

R156 56

R502 56

R159 56

R510 56

R160 56

R148 10K

IREF

R141

475_1

0.1u

C130

0.1u

C128

0.1u

7

1

VDD_PCI1

VDD_PCI0

VTT_PWRGD#/PD

C483

4.7U_10V_0805

VDD_48

VDD_REF

RTFS_2

RTFS_1

CPUCLKT1

CPUCLKC1

CPUCLKT0

CPUCLKC0

PCIEXT6

PCIEXC6

PCIEXT5

PCIEXC5

PCIEXT4

PCIEXC4

PCIEXT3

PCIEXC3

PCIEXT2

PCIEXC2

PCIEXT1

PCIEXC1

PCIEXT0

PCIEXC0

SRC0

SRC0#

DOT96

DOT96#

REFOUT

11

48

55

54

41

40

44

43

36

35

33

32

31

30

26

27

24

25

22

23

20

21

17

18

14

15

10

52

Z0703

R153

2.2

Z0708

VDD_REF_CR

Z0704

Z0705

CPU1

CPU#1

CPU0

CPU#0

PCIE5

PCIE#5

PCIE4

PCIE#4

PCIE3

PCIE#3

PCIE2

PCIE#2

DOT96

DOT96#

VTT_PWRGD#

REF

C132

0.1u

R511 0_OP

R507 0_OP

R455 33

R450 33

R478 33

R467 33

R447 33

R441 33

R446 33

R433 33

R451 33

R449 33

R465 33

R456 33

R479 33

R469 33

R501 22

C504

4.7U_10V_0805

C140

0.1u

R155

1

C134 0.1u

PM_STPPCI# 18

PM_STPCPU# 18,30

CLK_MCH_BCLK 8

CLK_MCH_BCLK# 8

CLK_CPU_BCLK 5

CLK_CPU_BCLK# 5

GCLK 9

GCLK# 9

CLK_PCIE_NEW_CARD 22

CLK_PCIE_NEW_CARD# 22

CLK_PCIE_ICH 18

CLK_PCIE_ICH# 18

CLK_PCIE_MXM 29

CLK_PCIE_MXM# 29

DREFCLK 9

DREFCLK# 9

CLK_ICH14 18

+3.3V

CLK_PCIE_NEW_CARD

CLK_PCIE_NEW_CARD#

CLK_CPU_BCLK

CLK_CPU_BCLK#

CLK_MCH_BCLK

CLK_MCH_BCLK#

DREFCLK#

DREFCLK

CLK_PCIE_ICH#

CLK_PCIE_ICH

GCLK#

GCLK

CLK_PCIE_MXM

CLK_PCIE_MXM#

Place termination close to source IC

CLK_USB48

PCICLK_RAID

PCICLK_LAN

PCICLK_MINIPCI

CLK_PCI_LPC

CLK_PCI

CLK_ICH14

IO_CLK

PCICLK_1394_A

R130 49.9_1

R118 49.9_1

R145 49.9_1

R143 49.9_1

R138 49.9_1

R133 49.9_1

R144 49.9_1

R146 49.9_1

R132 49.9_1

R134 49.9_1

R122 49.9_1

R140 49.9_1

R139 49.9_1

C498 10p_OP

C506 10p_OP

C136 10p_OP

C507 10p_OP

C143 10p_OP

C512 10p_OP

C138 10p_OP

C135 10p_OP

C139 10p_OP

Reserved FOR EMI

Host

FSC

FSB

A A

5

FSA

BSEL2

1

1

BSEL1

0

0

BSEL0

1

0

Clock

frequency

100

133

4

UNIWILL COMPUTER CORP.

Title

Size Document Number Rev

2963

3

2

Date: Sheet

P71EN0

CLOCK GEN ICS954127

1

735Thursday, January 13, 2005

B

of

5

4

3

2

1

W6

W8

W7

W1

W3

W2

E4

E1

F4

H7

E2

F1

E3

D3

K7

F2

J7

J8

H6

F3

K8

H5

H1

H2

K5

K6

J4

G3

H3

J1

L5

K4

J5

P7

L7

J3

P5

L3

U7

V6

R6

R5

P3

T8

R7

R8

U8

R4

T4

T5

R1

T3

V8

U6

U3

V5

U2

U1

Y5

Y2

V4

Y7

Y3

Y6

C1

C2

D1

T1

L1

P1

U16A

HD0#

HD1#

HD2#

HD3#

HD4#

HD5#

HD6#

HD7#

HD8#

HD9#

HD10#

HD11#

HD12#

HD13#

HD14#

HD15#

HD16#

HD17#

HD18#

HD19#

HD20#

HD21#

HD22#

HD23#

HD24#

HD25#

HD26#

HD27#

HD28#

HD29#

HD30#

HD31#

HD32#

HD33#

HD34#

HD35#

HD36#

HD37#

HD38#

HD39#

HD40#

HD41#

HD42#

HD43#

HD44#

HD45#

HD46#

HD47#

HD48#

HD49#

HD50#

HD51#

HD52#

HD53#

HD54#

HD55#

HD56#

HD57#

HD58#

HD59#

HD60#

HD61#

HD62#

HD63#

HXRCOMP

HXSCOMP

HXSWING

HYRCOMP

HYSCOMP

HYSWING

ALVISO_90

HOST

HA3#

HA4#

HA5#

HA6#

HA7#

HA8#

HA9#

HA10#

HA11#

HA12#

HA13#

HA14#

HA15#

HA16#

HA17#

HA18#

HA19#

HA20#

HA21#

HA22#

HA23#

HA24#

HA25#

HA26#

HA27#

HA28#

HA29#

HA30#

HA31#

HADS#

HADSTB#0

HADSTB#1

HVREF

HBNR#

HBPRI#

HBREQ0#

HCPURST#

HCLKINN

HCLKINP

HDBSY#

HDEFER#

HDINV#0

HDINV#1

HDINV#2

HDINV#3

HDPWR#

HDRDY#

HDSTBN#0

HDSTBN#1

HDSTBN#2

HDSTBN#3

HDSTBP#0

HDSTBP#1

HDSTBP#2

HDSTBP#3

HEDRDY#

HHIT#

HHITM#

HLOCK#

HPCREQ#

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

HRS0#

HRS1#

HRS2#

HCPUSLP#

HTRDY#

G9

C9

E9

B7

A10

F9

D8

B10

E10

G10

D9

E11

F10

G11

G13

C10

C11

D11

C12

B13

A12

F12

G12

E12

C13

B11

D13

A13

F13

F8

B9

E13

J11

A5

D5

E7

H10

AB1

AB2

C6

E6

H8

K3

T7

U5

G6

F7

G4

K1

R3

V3

G5

K2

R2

W4

F6

D4

D6

B3

A11

A7

D7

B8

C7

A8

A4

C5

B4

G8

B5

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_VREF

H_DINV#0

H_DINV#1

H_DINV#2

H_DINV#3

H_DSTBN#0

H_DSTBN#1

H_DSTBN#2

H_DSTBN#3

H_DSTBP#0

H_DSTBP#1

H_DSTBP#2

H_DSTBP#3

Z0801

Z0802

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_RS#0

H_RS#1

H_RS#2

H_CPUSLP#_GMCH

TP18

TP23

R392 0_OP

H_A#[31:3] 5

H_ADS# 5

H_ADSTB#0 5

H_ADSTB#1 5

H_BNR# 5

H_BPRI# 5

H_BREQ#0 5

H_CPURST# 5

CLK_MCH_BCLK# 7

CLK_MCH_BCLK 7

H_DBSY# 5

H_DEFER# 5

H_DINV#[3:0] 5

H_DPWR# 5

H_DRDY# 5

H_DSTBN#[3:0] 5

H_DSTBP#[3:0] 5

H_HIT# 5

H_HITM# 5

H_LOCK# 5

H_CPUSLP# 5,17

H_TRDY# 5

+1.05V

C435

0.1u

H_REQ#[4:0] 5

H_RS#[2:0] 5

R394

100_1

R393

200_1

H_D#[63:0]5

D D

+1.05V

+1.05V

C C

+1.05V

B B

+1.05V

R79

24.9_1

R80

54.9_1

R77

221_1

R78

100_1

R384

54.9_1

R377

221_1

R378

100_1

H_XRCOMP

H_XSCOMP

H_XSWING

C78

0.1u

H_YSCOMP

H_YSWING

C398

0.1u

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_XRCOMP

H_XSCOMP

H_XSWING

H_YRCOMP

H_YSCOMP

H_YSWING

H_YRCOMP

R383

24.9_1

A A

Reference from demo circuit

UNIWILL COMPUTER CORP.

Title

Size Document Number Rev

2963

5

4

3

2

Date: Sheet

P71EN0

NB_Alviso Host-1/5

1

835Thursday, January 13, 2005

B

of

5

4

3

2

1

+1.5V

PEG_RXN[15..0] 29

PEG_RXP[15..0] 29

PEG_TXN[15..0] 29

PEG_TXP[15..0] 29

DMI_TXN[3:0]18

DMI_TXP[3:0]18

D D

C C

B B

DMI_RXN[3:0]18

DMI_RXP[3:0]18

MA_CK013

MA_CK113

MB_CK313

MB_CK413

MA_CK#013

MA_CK#113

MB_CK#313

MB_CK#413

as short as possible

R89

R91

40.2_1

40.2_1

+1.8VS

R448

150_1

M_VREF_MCH

0.05A

C480

R445

0.1u

150_1

R412 0

R379 0

R444 0

R381 0

R422 0

R380 0

R443 0

R382 0

MA_CKE013,14

MA_CKE113,14

MB_CKE213,14

MB_CKE313,14

MA_CS#013,14

MA_CS#113,14

MB_CS#213,14

MB_CS#313,14

M_OCDCOMP0

M_OCDCOMP1

C416

0.1u

MA_ODT013,14

MA_ODT113,14

MB_ODT213,14

MB_ODT313,14

DMI_TXN0

DMI_TXN1

DMI_TXN2

DMI_TXN3

DMI_TXP0

DMI_TXP1

DMI_TXP2

DMI_TXP3

DMI_RXN0

DMI_RXN1

DMI_RXN2

DMI_RXN3

DMI_RXP0

DMI_RXP1

DMI_RXP2

DMI_RXP3

Z0901

Z0902

Z0903

Z0904

Z0905

Z0906

Z0907

Z0908

M_RCOMPN

M_RCOMPP

SMXSLEW

SMYSLEW

AA31

AB35

AC31

AD35

AA35

AB31

AC35

AA33

AB37

AC33

AD37

AA37

AB33

AC37

AM33

AJ34

AF6

AN33

AK1

AJ33

AF5

AP21

AM21

AH21

AK21

AN16

AM14

AH15

AG16

AF22

AF16

AP14

AL15

AM11

AN10

AK10

AK11

AF37

AD1

AE27

AE28

AF9

AF10

Y31

Y33

AL1

U16B

DMIRXN0

DMIRXN1

DMIRXN2

DMIRXN3

DMIRXP0

DMIRXP1

DMIRXP2

DMIRXP3

DMITXN0

DMITXN1

DMITXN2

DMITXN3

DMITXP0

DMITXP1

DMITXP2

DMITXP3

SM_CK0

SM_CK1

SM_CK3

SM_CK4

SM_CK0#

SM_CK1#

SM_CK3#

SM_CK4#

SM_CKE0

SM_CKE1

SM_CKE2

SM_CKE3

SM_CS0#

SM_CS1#

SM_CS2#

SM_CS3#

SM_OCDCOMP0

SM_OCDCOMP1

SM_ODT0

SM_ODT1

SM_ODT2

SM_ODT3

SMRCOMPN

SMRCOMPP

SMVREF0

SMVREF1

SMXSLEWIN

SMXSLEWOUT

SMYSLEWIN

SMYSLEWOUT

DMI

DDR MUXING

ALVISO_90

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG/RSVD

CFG14

CFG15

CFG16

CFG17

CFG18

CFG19

CFG20

RSVD21

RSVD22

RSVD23

RSVD24

RSVD25

RSVD26

RSVD27

RSVD28

RSVD29

RSVD30

RSVD31

BM_BUSY#

EXT_TS0#

EXT_TS1#

PM

THRMTRIP#

PWROK

RSTIN#

DREF_CLKN

DREF_CLKP

DREF_SSCLKN

DREF_SSCLKP

CLK

NC

NC10

NC11

NC1

NC2

NC3

NC4

NC5

NC6

NC7

NC8

NC9

G16

H13

G14

F16

F15

G15

E16

D17

J16

D15

E15

D14

E14

H12

C14

H15

J15

H14

G22

G23

D23

G25

G24

J17

A31

A30

D26

D25

AE11

AE10

AC10

AD10

J23

J21

H22

F5

AD30

AE29

A24

A23

C37

D37

AP37

AN37

AP36

AP2

AP1

AN1

B1

A2

B37

A36

A37

Z0909

Z0910

Z0911

Z0912

Z0913

Z0914

Z0915

Z0916

Z0917

Z0918

Z0919

Z0920

Z0921

Z0922

Z0923

Z0924

Z0925

Z0926

Z0927

Z0928

Z0929

Z0930

PM_EXTTS#0

Z0931

Z0932

Z0933

Z0934

Z0935

Z0936

Z0937

Z0938

Z0939

Z0940

Z0941

Z0942

Z0943

Z0944

Z0945

Z0946

Z0947

CFG0

A C

R117 100

R405 0

R403 0

R440 0

R438 0

MCH_BSEL1 5

MCH_BSEL0 5

TP30

TP31

CFG5 12

CFG6 12

CFG7 12

TP33

CFG9 12

TP29

TP26

TP27

TP24

TP25

TP32

CFG16 12

TP28

CFG18 12

CFG19 12

TP35

TP63

TP64

TP34

TP68

TP67

TP66

TP65

TP22

TP21

TP19

TP20

PM_EXTTS#1

BAT54D7

AC

BAT54_OPD6

DREFCLK# 7

DREFCLK 7

TP73

TP74

TP69

TP17

TP16

TP58

TP57

TP59

TP71

TP70

TP72

BM_BUSY# 18

EXTTS#0 16,28

PM_THRMTRIP# 5,17

DELAY_VR_PWRGOOD 18

PLT_RST# 18,19,20,28,29

Z0948

Z0949

R454

R439

0

0_OP

+1.5V

Reserved for spread clock

Colse to NB

DELAY_VR_PWRGOOD

C700

0.1u

R453

1K

GCLK#7

GCLK7

+1.05V

AB29

AC29

H24

H25

A15

C16

A17

J18

B15

B16

B17

E24

E23

E21

D21

C20

B20

A19

B19

H21

G21

J20

E25

F25

C23

C22

F23

F22

F26

C33

C31

F28

F27

B30

B29

C25

C24

B34

B33

B32

A34

A33

B31

C29

D28

C27

C28

D27

C26

U16G

SDVOCTRL_DATA

SDVOCTRL_CLK

GCLKN

GCLKP

TVDAC_A

TVDAC_B

TVDAC_C

TV_REFSET

TV_IRTNA

TV_IRTNB

TV_IRTNC

DDCCLK

DDCDATA

BLUE

BLUE#

GREEN

GREEN#

RED

RED#

VSYNC

HSYNC

REFSET

LBKLT_CRTL

LBKLT_EN

LCTLA_CLK

LCTLB_DATA

LDDC_CLK

LDDC_DATA

LVDD_EN

LIBG

LVBG

LVREFH

LVREFL

LACLKN

LACLKP

LBCLKN

LBCLKP

LADATAN0

LADATAN1

LADATAN2

LADATAP0

LADATAP1

LADATAP2

LBDATAN0

LBDATAN1

LBDATAN2

LBDATAP0

LBDATAP1

LBDATAP2

MISCTVVGALVDS

ALVISO_90

EXP_COMPI

EXP_ICOMPO

EXP_RXN0

EXP_RXN1

EXP_RXN2

EXP_RXN3

EXP_RXN4

EXP_RXN5

EXP_RXN6

EXP_RXN7

EXP_RXN8

EXP_RXN9

EXP_RXN10

EXP_RXN11

EXP_RXN12

EXP_RXN13

EXP_RXN14

EXP_RXN15

EXP_RXP0

EXP_RXP1

EXP_RXP2

EXP_RXP3

EXP_RXP4

EXP_RXP5

EXP_RXP6

EXP_RXP7

EXP_RXP8

EXP_RXP9

EXP_RXP10

EXP_RXP11

EXP_RXP12

EXP_RXP13

EXP_RXP14

EXP_RXP15

EXP_TXN0

EXP_TXN1

EXP_TXN2

EXP_TXN3

EXP_TXN4

EXP_TXN5

EXP_TXN6

EXP_TXN7

EXP_TXN8

EXP_TXN9

EXP_TXN10

EXP_TXN11

PCI-EXPRESS GRAPHICS

EXP_TXN12

EXP_TXN13

EXP_TXN14

EXP_TXN15

EXP_TXP0

EXP_TXP1

EXP_TXP2

EXP_TXP3

EXP_TXP4

EXP_TXP5

EXP_TXP6

EXP_TXP7

EXP_TXP8

EXP_TXP9

EXP_TXP10

EXP_TXP11

EXP_TXP12

EXP_TXP13

EXP_TXP14

EXP_TXP15

D36

D34

E30

F34

G30

H34

J30

K34

L30

M34

N30

P34

R30

T34

U30

V34

W30

Y34

D30

E34

F30

G34

H30

J34

K30

L34

M30

N34

P30

R34

T30

U34

V30

W34

E32

F36

G32

H36

J32

K36

L32

M36

N32

P36

R32

T36

U32

V36

W32

Y36

D32

E36

F32

G36

H32

J36

K32

L36

M32

N36

P32

R36

T32

U36

V32

W36

PEG_RXN15

PEG_RXN14

PEG_RXN13

PEG_RXN12

PEG_RXN11

PEG_RXN10

PEG_RXN9

PEG_RXN8

PEG_RXN7

PEG_RXN6

PEG_RXN5

PEG_RXN4

PEG_RXN3

PEG_RXN2

PEG_RXN1

PEG_RXN0

PEG_RXP15

PEG_RXP14

PEG_RXP13

PEG_RXP12

PEG_RXP11

PEG_RXP10

PEG_RXP9

PEG_RXP8

PEG_RXP7

PEG_RXP6

PEG_RXP5

PEG_RXP4

PEG_RXP3

PEG_RXP2

PEG_RXP1

PEG_RXP0

PEG_TXN15

PEG_TXN14

PEG_TXN13

PEG_TXN12

PEG_TXN11

PEG_TXN10

PEG_TXN9

PEG_TXN8

PEG_TXN7

PEG_TXN6

PEG_TXN5

PEG_TXN4

PEG_TXN3

PEG_TXN2

PEG_TXN1

PEG_TXN0

PEG_TXP15

PEG_TXP14

PEG_TXP13

PEG_TXP12

PEG_TXP11

PEG_TXP10

PEG_TXP9

PEG_TXP8

PEG_TXP7

PEG_TXP6

PEG_TXP5

PEG_TXP4

PEG_TXP3

PEG_TXP2

PEG_TXP1

PEG_TXP0

PEG_COMP

R437 24.9_1

Modify 19

+1.8VS

R84

80.6_1

M_RCOMPN

A A

M_RCOMPP

R83

80.6_1

5

+2.5V

+1.05V

R87 10K

R94 10K

R92 10K

CFG0

PM_EXTTS#0

PM_EXTTS#1

CFG0

CFG10CFG2

1

1

0

4

3

1

0

Host

Clock

frequency

100

133

2

UNIWILL COMPUTER CORP.

Title

Size Document Number Rev

2963

Date: Sheet

P71EN0

NB DDRCLK_VGA_PCIEXPR-2/5

1

935Thursday, January 13, 2005

of

B

5

4

3

2

1

MA_DQ[63:0]13

D D

C C

B B

MA_DQ0

MA_DQ1

MA_DQ2

MA_DQ3

MA_DQ4

MA_DQ8

MA_DQ9

MA_DQ10

MA_DQ11

MA_DQ12

MA_DQ13

MA_DQ14

MA_DQ15

MA_DQ16

MA_DQ17

MA_DQ18

MA_DQ19

MA_DQ20

MA_DQ21

MA_DQ22

MA_DQ23

MA_DQ24

MA_DQ25

MA_DQ26

MA_DQ27

MA_DQ28

MA_DQ29

MA_DQ30

MA_DQ31

MA_DQ32

MA_DQ33

MA_DQ34

MA_DQ35

MA_DQ36

MA_DQ37

MA_DQ38

MA_DQ39

MA_DQ40

MA_DQ41

MA_DQ42

MA_DQ43

MA_DQ44

MA_DQ45

MA_DQ46

MA_DQ47

MA_DQ48

MA_DQ49

MA_DQ50

MA_DQ51

MA_DQ52

MA_DQ53

MA_DQ54

MA_DQ55

MA_DQ56

MA_DQ57

MA_DQ58

MA_DQ59

MA_DQ60

MA_DQ61

MA_DQ62

MA_DQ63

AG35

AH35

AL35

AL37

AH36

AJ35

AK37

AL34

AM36

AN35

AP32

AM31

AM34

AM35

AL32

AM32

AN31

AP31

AN28

AP28

AL30

AM30

AM28

AL28

AP27

AM27

AM23

AM22

AL23

AM24

AN22

AP22

AM9

AP11

AP10

AM7

AN5

AN6

AN3

AM6

AM3

AG2

AG1

AM2

AH3

AG3

AD6

AC4

AD4

AD5

AL9

AL6

AP7

AL7

AP3

AP6

AL4

AK2

AK3

AL3

AF3

AE3

AF2

AF1

U16C

SADQ0

SADQ1

SADQ2

SADQ3

SADQ4

SADQ5

SADQ6

SADQ7

SADQ8

SADQ9

SADQ10

SADQ11

SADQ12

SADQ13

SADQ14

SADQ15

SADQ16

SADQ17

SADQ18

SADQ19

SADQ20

SADQ21

SADQ22

SADQ23

SADQ24

SADQ25

SADQ26

SADQ27

SADQ28

SADQ29

SADQ30

SADQ31

SADQ32

SADQ33

SADQ34

SADQ35

SADQ36

SADQ37

SADQ38

SADQ39

SADQ40

SADQ41

SADQ42

SADQ43

SADQ44

SADQ45

SADQ46

SADQ47

SADQ48

SADQ49

SADQ50

SADQ51

SADQ52

SADQ53

SADQ54

SADQ55

SADQ56

SADQ57

SADQ58

SADQ59

SADQ60

SADQ61

SADQ62

SADQ63

ALVISO_90

SA_BS0#

SA_BS1#

SA_BS2#

SA_DM0

SA_DM1

SA_DM2

SA_DM3

SA_DM4

SA_DM5

SA_DM6

SA_DM7

SA_DQS0

SA_DQS1

SA_DQS2

SA_DQS3

SA_DQS4

SA_DQS5

SA_DQS6

SA_DQS7

SA_DQS0#

SA_DQS1#

SA_DQS2#

SA_DQS3#

SA_DQS4#

SA_DQS5#

SA_DQS6#

SA_DQS7#

SA_MA0

SA_MA1

SA_MA2

SA_MA3

SA_MA4

SA_MA5

SA_MA6

SA_MA7

SA_MA8

SA_MA9

SA_MA10

SA_MA11

SA_MA12

SA_MA13

SA_CAS#

DDR SYSTEM MEMORY A

SA_RAS#

SA_RCVENIN#

SA_RCVENOUT#

SA_WE#

AK16

AL21

AJ37

AP35

AL29

AP24

AP9

AP4

AJ2

AD3

AK36

AP33

AN29

AP23

AM8

AM4

AJ1

AE5

AK35

AP34

AN30

AN23

AN8

AM5

AH1

AE4

AL17

AP17

AP18

AM17

AN18

AM18

AL19

AP20

AM19

AL20

AM16

AN20

AM20

AM15

AN15

AP16

AF29

AF28

AP15

MA_BA1

MA_BA2

MA_DM0

MA_DM1MA_DQ5

MA_DM2MA_DQ6

MA_DM3MA_DQ7

MA_DM4

MA_DM5

MA_DM6

MA_DM7

MA_DQS0

MA_DQS1

MA_DQS2

MA_DQS3

MA_DQS4

MA_DQS5

MA_DQS6

MA_DQS7

MA_DQS#0

MA_DQS#1

MA_DQS#2

MA_DQS#3

MA_DQS#4

MA_DQS#5

MA_DQS#6

MA_DQS#7

MAA_A0

MAA_A1

MAA_A2

MAA_A3

MAA_A4

MAA_A5

MAA_A6

MAA_A7

MAA_A8

MAA_A9

MAA_A10

MAA_A11

MAA_A12

MAA_A13

MA_BA0

AK15

MA_BA[2:0] 13,14

MA_DM[7:0] 13

MA_DQS[7:0] 13

MA_DQS#[7:0] 13

MAA_A[13:0] 13,14

MA_CAS# 13,14

MA_RAS# 13,14

MA_WE# 13,14

MB_DQ[63:0]13

MB_DQ0

MB_DQ1

MB_DQ2

MB_DQ3

MB_DQ4

MB_DQ5

MB_DQ6

MB_DQ7

MB_DQ8

MB_DQ9

MB_DQ10

MB_DQ11

MB_DQ12

MB_DQ13

MB_DQ14

MB_DQ15

MB_DQ16

MB_DQ17

MB_DQ18

MB_DQ19

MB_DQ20

MB_DQ21

MB_DQ22

MB_DQ23

MB_DQ24

MB_DQ25

MB_DQ26

MB_DQ27

MB_DQ28

MB_DQ29

MB_DQ30

MB_DQ31

MB_DQ32

MB_DQ33

MB_DQ34

MB_DQ35

MB_DQ36

MB_DQ37

MB_DQ38

MB_DQ39

MB_DQ40

MB_DQ41

MB_DQ42

MB_DQ43

MB_DQ44

MB_DQ45

MB_DQ46

MB_DQ47

MB_DQ48

MB_DQ49

MB_DQ50

MB_DQ51

MB_DQ52

MB_DQ53

MB_DQ54

MB_DQ55

MB_DQ56

MB_DQ57

MB_DQ58

MB_DQ59

MB_DQ60

MB_DQ61

MB_DQ62

MB_DQ63

AE31

AE32

AG32

AG36

AE34

AE33

AF31

AF30

AH33

AH32

AK31

AG30

AG34

AG33

AH31

AJ31

AK30

AJ30

AH29

AH28

AK29

AH30

AH27

AG28

AF24

AG23

AJ22

AK22

AH24

AH23

AG22

AJ21

AG10

AG9

AG8

AH8

AH11

AH10

AJ9

AK9

AJ7

AK6

AJ4

AH5

AK8

AJ8

AJ5

AK4

AG5

AG4

AD8

AD9

AH4

AG6

AE8

AD7

AC5

AB8

AB6

AA8

AC8

AC7

AA4

AA5

U16D

SBDQ0

SBDQ1

SBDQ2

SBDQ3

SBDQ4

SBDQ5

SBDQ6

SBDQ7

SBDQ8

SBDQ9

SBDQ10

SBDQ11

SBDQ12

SBDQ13

SBDQ14

SBDQ15

SBDQ16

SBDQ17

SBDQ18

SBDQ19

SBDQ20

SBDQ21

SBDQ22

SBDQ23

SBDQ24

SBDQ25

SBDQ26

SBDQ27

SBDQ28

SBDQ29

SBDQ30

SBDQ31

SBDQ32

SBDQ33

SBDQ34

SBDQ35

SBDQ36

SBDQ37

SBDQ38

SBDQ39

SBDQ40

SBDQ41

SBDQ42

SBDQ43

SBDQ44

SBDQ45

SBDQ46

SBDQ47

SBDQ48

SBDQ49

SBDQ50

SBDQ51

SBDQ52

SBDQ53

SBDQ54

SBDQ55

SBDQ56

SBDQ57

SBDQ58

SBDQ59

SBDQ60

SBDQ61

SBDQ62

SBDQ63

ALVISO_90

SB_BS0#

SB_BS1#

SB_BS2#

SB_DM0

SB_DM1

SB_DM2

SB_DM3

SB_DM4

SB_DM5

SB_DM6

SB_DM7

SB_DQS0

SB_DQS1

SB_DQS2

SB_DQS3

SB_DQS4

SB_DQS5

SB_DQS6

SB_DQS7

SB_DQS0#

SB_DQS1#

SB_DQS2#

SB_DQS3#

SB_DQS4#

SB_DQS5#

SB_DQS6#

SB_DQS7#

SB_MA0

SB_MA1

SB_MA2

SB_MA3

SB_MA4

SB_MA5

SB_MA6

SB_MA7

SB_MA8

SB_MA9

SB_MA10

SB_MA11

SB_MA12

SB_MA13

SB_CAS#

DDR SYSTEM MEMORY B

SB_RAS#

SB_RCVENIN#

SB_RCVENOUT#

SB_WE#

AG17

AG21

AF32

AK34

AK27

AK24

AJ10

AK5

AE7

AB7

AF34

AK32

AJ28

AK23

AM10

AH6

AF8

AB4

AF35

AK33

AK28

AJ23

AL10

AH7

AF7

AB5

AH17

AK17

AH18

AJ18

AK18

AJ19

AK19

AH19

AJ20

AH20

AJ16

AG18

AG20

AG15

AH14

AK14

AF15

AF14

AH16

MB_BA1

MB_BA2

MB_DM0

MB_DM1

MB_DM2

MB_DM3

MB_DM4

MB_DM5

MB_DM6

MB_DM7

MB_DQS0

MB_DQS1

MB_DQS2

MB_DQS3

MB_DQS4

MB_DQS5

MB_DQS6

MB_DQS7

MB_DQS#0

MB_DQS#1

MB_DQS#2

MB_DQS#3

MB_DQS#4

MB_DQS#5

MB_DQS#6

MB_DQS#7

MBA_A0

MBA_A1

MBA_A2

MBA_A3

MBA_A4

MBA_A5

MBA_A6

MBA_A7

MBA_A8

MBA_A9

MBA_A10

MBA_A11

MBA_A12

MBA_A13

MB_BA0

AJ15

MB_BA[2:0] 13,14

MB_DM[7:0] 13

MB_DQS[7:0] 13

MB_DQS#[7:0] 13

MBA_A[13:0] 13,14

MB_CAS# 13,14

MB_RAS# 13,14

MB_WE# 13,14

A A

UNIWILL COMPUTER CORP.

Title

Size Document Number Rev

2963

5

4

3

2

Date: Sheet

P71EN0

NB DDR_MEM SYSTEM-3/5

10 35Thursday, January 13, 2005

1

B

of

5

4

3

2

1

+1.05V

D D

+1.5V

C C

B B

+1.05V

640mA

A A

1.05V--->3700mA

1.5V--->6750mA

C102

4.7U_10V_0805

Total 320mA

40mA

B7

QT1608RL060

40mA

B24

QT1608RL060

45mA

B21

QT1608RL060

45mA

B20

QT1608RL060

C490

4.7U_10V_0805

5

C94

4.7U_10V_0805

150mA

4.7U_10V_0805

4.7U_10V_0805

4.7U_10V_0805

C104

2.2U_X5R

C95

4.7U_10V_0805

C453

C472

C379

C378

4.7U_10V_0805

C103

0.1u

C456

0.1u

C470

0.1u

C397

0.1u

C396

0.1u

C428 0.47u

C424 0.47u

C417 0.22u/25V

C414 0.22u/25V

U16E

T29

VCC0

R29

C81

C82

0.1u

0.1u

Z1101

Z1102

Z1103

Z1104

+1.05V

Z1109

Z1110

Z1111

Z1112

N29

M29

K29

J29

V28

U28

T28

R28

P28

N28

M28

L28

K28

J28

H28

G28

V27

U27

T27

R27

P27

N27

M27

L27

K27

J27

H27

K26

H26

K25

J25

K24

K23

K22

K21

W20

U20

T20

K20

V19

U19

K19

W18

V18

T18

K18

K17

AC2

AC1

B23

C35

AA1

AA2

F19

E19

G19

H20

K13

J13

K12

W11

V11

U11

T11

R11

P11

N11

M11

L11

K11

W10

V10

U10

T10

R10

P10

N10

M10

K10

J10

Y9

W9

U9

R9

P9

N9

M9

L9

J9

N8

M8

N7

M7

N6

M6

A6

N5

M5

N4

M4

N3

M3

N2

M2

B2

V1

N1

M1

G1

VCC1

VCC2

VCC3

VCC4

VCC5

VCC6

VCC7

VCC8

VCC9

VCC10

VCC11

VCC12

VCC13

VCC14

VCC15

VCC16

VCC17

VCC18

VCC19

VCC20

VCC21

VCC22

VCC23

VCC24

VCC25

VCC26

VCC27

VCC28

VCC29

VCC30

VCC31

VCC32

VCC33

VCC34

VCC35

VCC36

VCC37

VCC38

VCC39

VCC40

VCC41

VCC42

VCC43

VCC44

VCC45

VCC46

VCC47

VCC48

VCCH_MPLL1

VCCH_MPLL0

VCCA_DPLLA

VCCA_DPLLB

VCCA_HPLL

VCCA_MPLL

VCCA_CRTDAC0

VCCA_CRTDAC1

VSSA_CRTDAC

VCC_SYNC

VTT0

VTT1

VTT2

VTT3

VTT4

VTT5

VTT6

VTT7

VTT8

VTT9

VTT10

VTT11

VTT12

VTT13

VTT14

VTT15

VTT16

VTT17

VTT18

VTT19

VTT20

VTT21

VTT22

VTT23

VTT24

VTT25

VTT26

VTT27

VTT28

VTT29

VTT30

VTT31

VTT32

VTT33

VTT34

VTT35

VTT36

VTT37

VTT38

VTT39

VTT40

VTT41

VTT42

VTT43

VTT44

VTT45

VTT46

VTT47

VTT48

VTT49

VTT50

VTT51

ALVISO_90

VCCA_TVDACA0

VCCA_TVDACA1

VCCA_TVDACB0

VCCA_TVDACB1

VCCA_TVDACC0

VCCA_TVDACC1

VCCD_TVDAC

VCCDQ_TVDAC

POWER

VCCTX_LVDS0

VCCTX_LVDS1

VCCTX_LVDS2

VCCA_3GPLL0

VCCA_3GPLL1

VCCA_3GPLL2

VCCA_TVBG

VSSA_TVBG

VCCD_LVDS0

VCCD_LVDS1

VCCD_LVDS2

VCCA_LVDS

VCCHV0

VCCHV1

VCCHV2

VCCSM0

VCCSM1

VCCSM2

VCCSM3

VCCSM4

VCCSM5

VCCSM6

VCCSM7

VCCSM8

VCCSM9

VCCSM10

VCCSM11

VCCSM12

VCCSM13

VCCSM14

VCCSM15

VCCSM16

VCCSM17

VCCSM18

VCCSM19

VCCSM20

VCCSM21

VCCSM22

VCCSM23

VCCSM24

VCCSM25

VCCSM26

VCCSM27

VCCSM28

VCCSM29

VCCSM30

VCCSM31

VCCSM32

VCCSM33

VCCSM34

VCCSM35

VCCSM36

VCCSM37

VCCSM38

VCCSM39

VCCSM40

VCCSM41

VCCSM42

VCCSM43

VCCSM44

VCCSM45

VCCSM46

VCCSM47

VCCSM48

VCCSM49

VCCSM50

VCCSM51

VCCSM52

VCCSM53

VCCSM54

VCCSM55

VCCSM56

VCCSM57

VCCSM58

VCCSM59

VCCSM60

VCCSM61

VCCSM62

VCCSM63

VCCSM64

VCCA_SM0

VCCA_SM1

VCCA_SM2

VCCA_SM3

VCC3G0

VCC3G1

VCC3G2

VCC3G3

VCC3G4

VCC3G5

VCC3G6

VCCA_3GBG

VSSA_3GBG

F17

E17

D18

C18

F18

E18

H18

G18

D19

H17

B26

B25

A25

A35

B22

B21

A21

AM37

AH37

AP29

AD28

AD27

AC27

AP26

AN26

AM26

AL26

AK26

AJ26

AH26

AG26

AF26

AE26

AP25

AN25

AM25

AL25

AK25

AJ25

AH25

AG25

AF25

AE25

AE24

AE23

AE22

AE21

AE20

AE19

AE18

AE17

AE16

AE15

AE14

AP13

AN13

AM13

AL13

AK13

AJ13

AH13

AG13

AF13

AE13

AP12

AN12

AM12

AL12

AK12

AJ12

AH12

AG12

AF12

AE12

AD11

AC11

AB11

AB10

AB9

AP8

AM1

AE1

B28

A28

A27

AF20

AP19

AF19

AF18

AE37

W37

U37

R37

N37

L37

J37

Y29

Y28

Y27

F37

G37

Z1113

Z1114

Z1115

Z1116

Z1117

Z1118

Z1119

Z1106

Z1105

R406 0

R421 0

R407 0

Z1120

Z1121

Z1108

C485 0.1u

C486 0.1u

C466 0.1u

C115

0.1u

+2.5V

+2.5V

+1.5V

10mA

C434 0.1u

C415 0.1u

C418 0.1u

60mA

60mA

C101

0.1u

C441

4.7U_10V_0805

+2.5V

C448

4.7U_10V_0805

for 3A trace

+2.5V

0.15mA

2mA

C458

4.7U_10V_0805

+1.8VS

C105

4.7U_10V_0805

C455

0.1u

C489

4.7U_10V_0805

C491

0.1u

B22

QT1608RL060

C454

4.7U_10V_0805

for 1.5A trace

C488

4.7U_10V_0805

for 1.5A trace

C481

4.7U_10V_0805

C487

4.7U_10V_0805

+1.5V

C460

0.1u

+2.5V

C449

0.1u

+2.5V

C468

0.1u

+1.5V

B25

QT2012RL030HC_3A_0805

B26

QT2012RL030HC_3A_0805

60mA

C461

4.7U_10V_0805

10mA

C100

0.01u

60mA

C447

4.7U_10V_0805

250mA

+1.5V

total 1500mA

+1.5V

UNIWILL COMPUTER CORP.

Title

Size Document Number Rev

2963

4

3

2

Date: Sheet

P71EN0

NB POWER-4/5

1

11 35Thursday, January 13, 2005

B

of

Loading...

Loading...