5

4

3

2

1

First International Computer,Inc

D D

Portable Computer Group HW Department

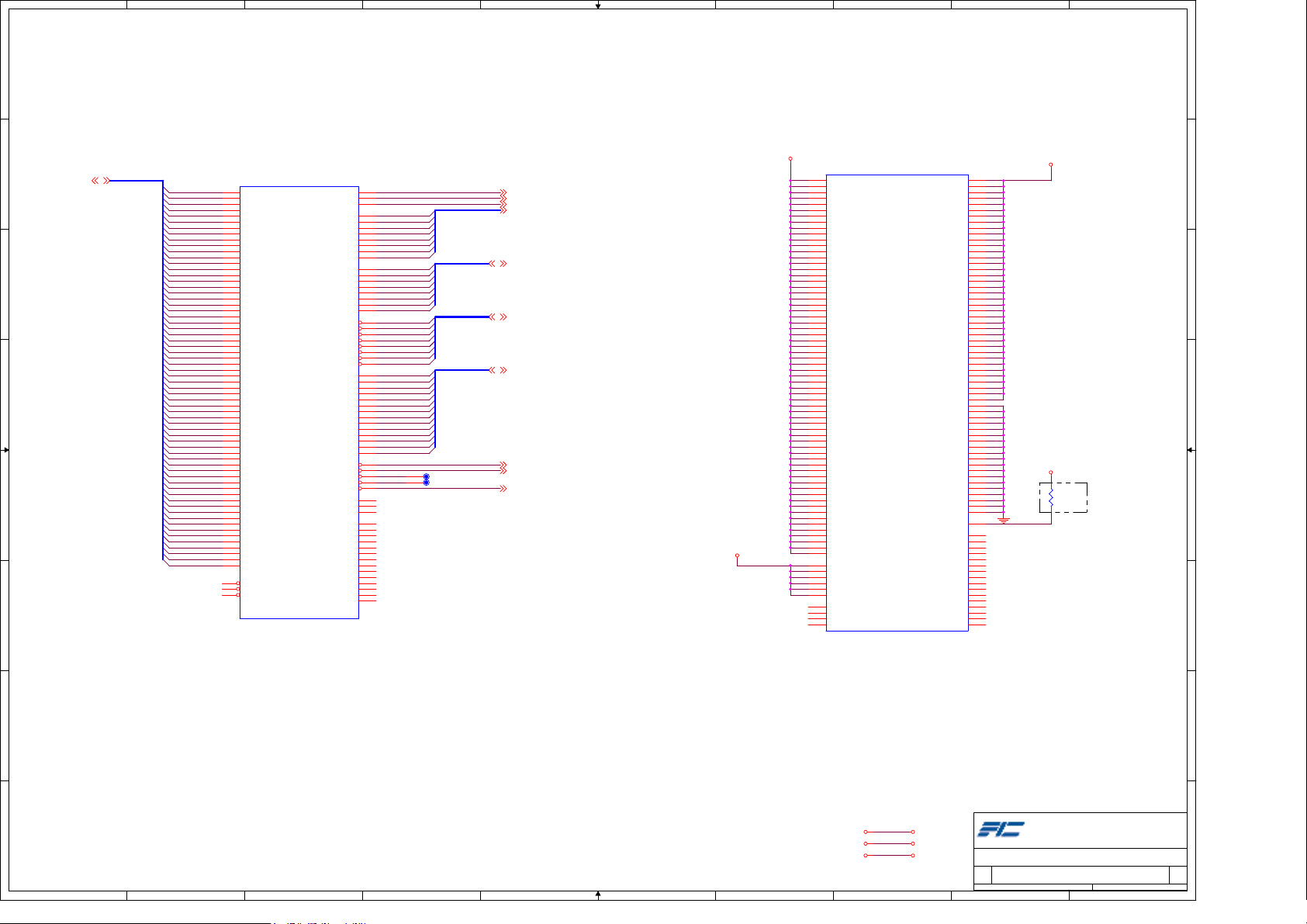

Board name : Mother Board Schematic

Project : CW0A0 ( Diamondville+945GMS+ICH7M )

C C

Version : 0.1

Initial Date : March 04, 2008

1. Schematic Page Description :

2. PCI & IRQ & DMA Description :

3. Block Diagram :

4. Nat name Description :

5. Board Stack up Description :

6. Schematic modify Item and History :

7. power on & off & S3 Sequence :

8. Layout Guideline :

9. switch setting

B B

Manager Sign by:Avery Lee

Drawing by : Beckham Chen/Leon Lee

Total confirm by:Jason Lee

LAN Circuit check by:

A A

Audio Circuit check by:

5

4

Title

Size Document Number Rev

C

3

2

Date: Sheet

First International Computer, Inc.

2FL.,NO.300,Yang Guang St.,NeiHu

114 TAIPEI, TAIWAN ,ROC

(886-2)875 1-8751

CW0A0

Title

1

1 47Thursday, June 26, 2008

0.1

of

8

7

6

5

4

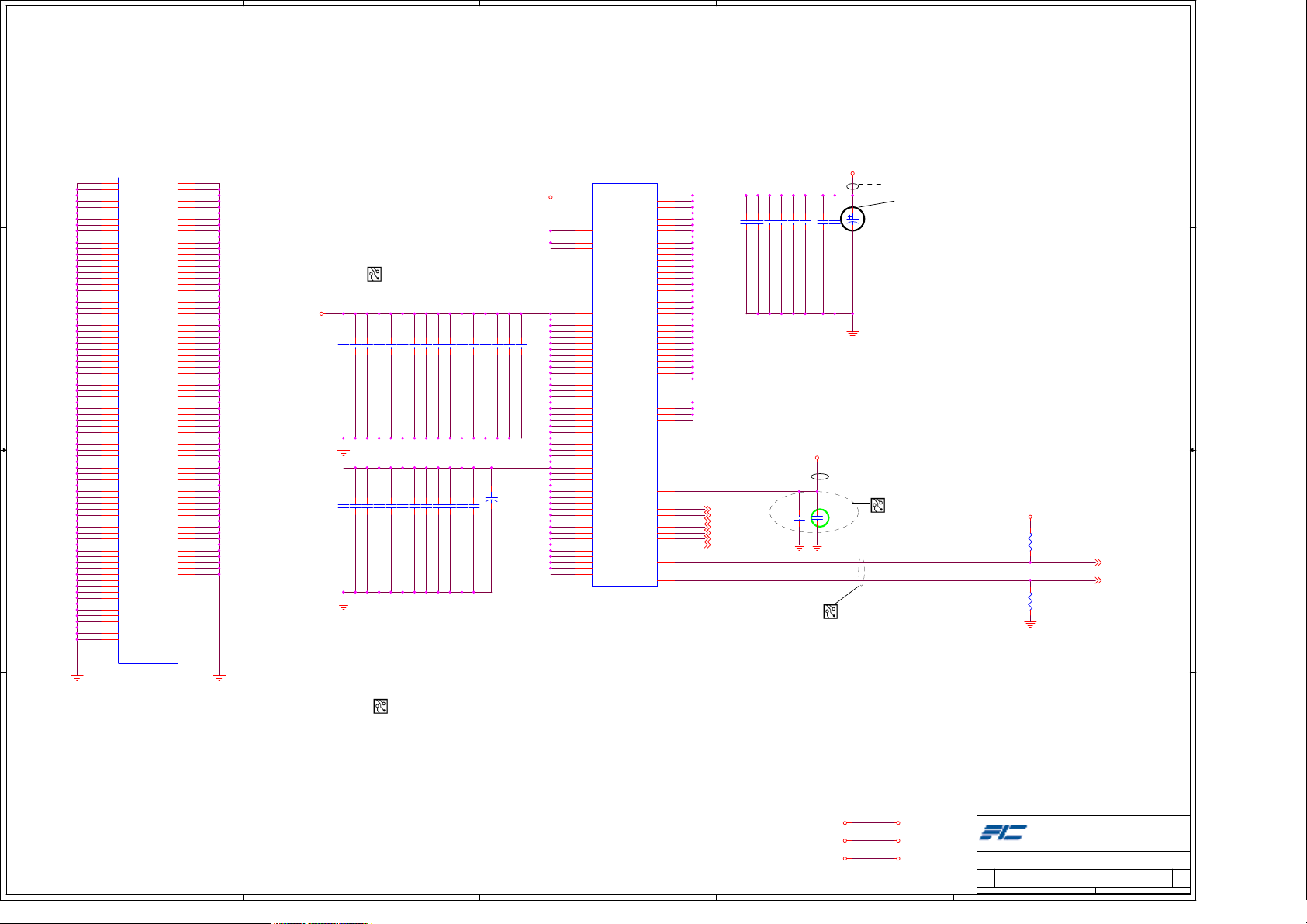

1. Schematic Page Description :

CW0A0 Schematic Ver : 0.1

3

2

1

D D

Page 01 Title

Page 02 Schematic Page Description

Page 03 Block Diagram

Page 04 Annotations

Page 05 Schematic Modify

Page 06 Timing Diagram

Page 07 DDR2 Layout Guide

Page 08 Diamondville (1/2)

Page 09 Diamondville (2/2)

Page 10 CPU Thermal

Page 11 945GMS Host(1/5)

C C

Page 12 945GMS DMI/Graph(2/5)

Page 13 945GMS DDR2(3/5)

Page 14 945GMS Power(4/5)

Page 15 945GMS Power(5/5)

Page 16 Clock Generator

Page 17 DDR2 SDRAM SO-DIMM0

Page 18 ICH7m PCI/PCIE/DMI(1/4)

Page 19 ICH7m CPU/IDE/SATA(2/4)

Page 21 ICH7m Power/GND(4/4)

Page 22 CRT Port

Page 23 LCD Conn

Page 24 HDD / DOM / KB

Page 25 Power Good

Page 26 Bios / Screw

Page 27 New Card

Page 28 Mini Card

Page 29 LAN RTL8102E (NEW)*

Page 30 Transformer

Page 31 Card Reader(RTS5158)

Page 32 Audio Codec(ALC269)

Page 33 HP / INT MIC / EXT MIC

Page 34 EXT USB / GPS / WEB-CAM

Page 35 BT / Touch Screen Cnn

Page 36 LID / GP / SW

Page 37 Touch Panel

Page 38 EC_PMX

Page 39 LED

POWER CIRCUIT

Page 40 Power Block

Page 41 CPU Core Power

Page 42 ACIN / Battery CNN

Page 43 Charger Circuit

Page 44 5V / 5VDDM, 3VDDA / M

Page 45 5V/1.8V/ 0.9V/1.05V

DAUGHT BOARD

P46 Module Transfer Board

Page 20 ICH7m GPIO(3/4)

2. PCI & IRQ & DMA Description :

B B

IDSEL

AD19

AD23

IRQA

IRQB

IRQC

IRQD

BUSMASTER

A A

REQ

REQ0 / GNT0

REQ1 / GNT1

REQ2 / GNT2

REQ3 / GNT3

REQ4 / GNT4

CHIP

CHIPPCIINT

CHIP

8

7

6

IRQ0

IRQ1

IRQ2

IRQ3

IRQ4

IRQ5

IRQ6

IRQ7

IRQ8

IRQ9

IRQ10

IRQ11

IRQ12

IRQ13

IRQ14

IRQ15

System timer

Keyboard

(Cascade)

LAN / MODEM

Serial Port

AUDIO / VGA / USB

FLOPPY DISK

LPT

RTC

ACPI

(Disable by default)

FIR

Cardbus

PS/2 mouse

FPU

HDD

CDROM

5

(MODEM/LAN)

4

DMA Channel

DMA0 FIR

DMA1

DMA2

DMA3

DMA4

DMA5

DMA6

DMA7

3

DeviceIRQ Channel Desciption

(disable by default)

ECP

FLOPPY DISK

AUDIO

(Cascade)

Unused

Unused

Unused

(MODEM / LAN)

First International Computer, Inc.

5FL.,NO.300,Yang Guang St.,NeiHu

114 TAIPEI, TAIWAN ,ROC

Title

Size Document Number Rev

C

Date: Sheet

2

(886-2) 8751-8751

CW0A0

Page Description

2 47Thursday, June 26, 2008

of

1

0.1

8

7

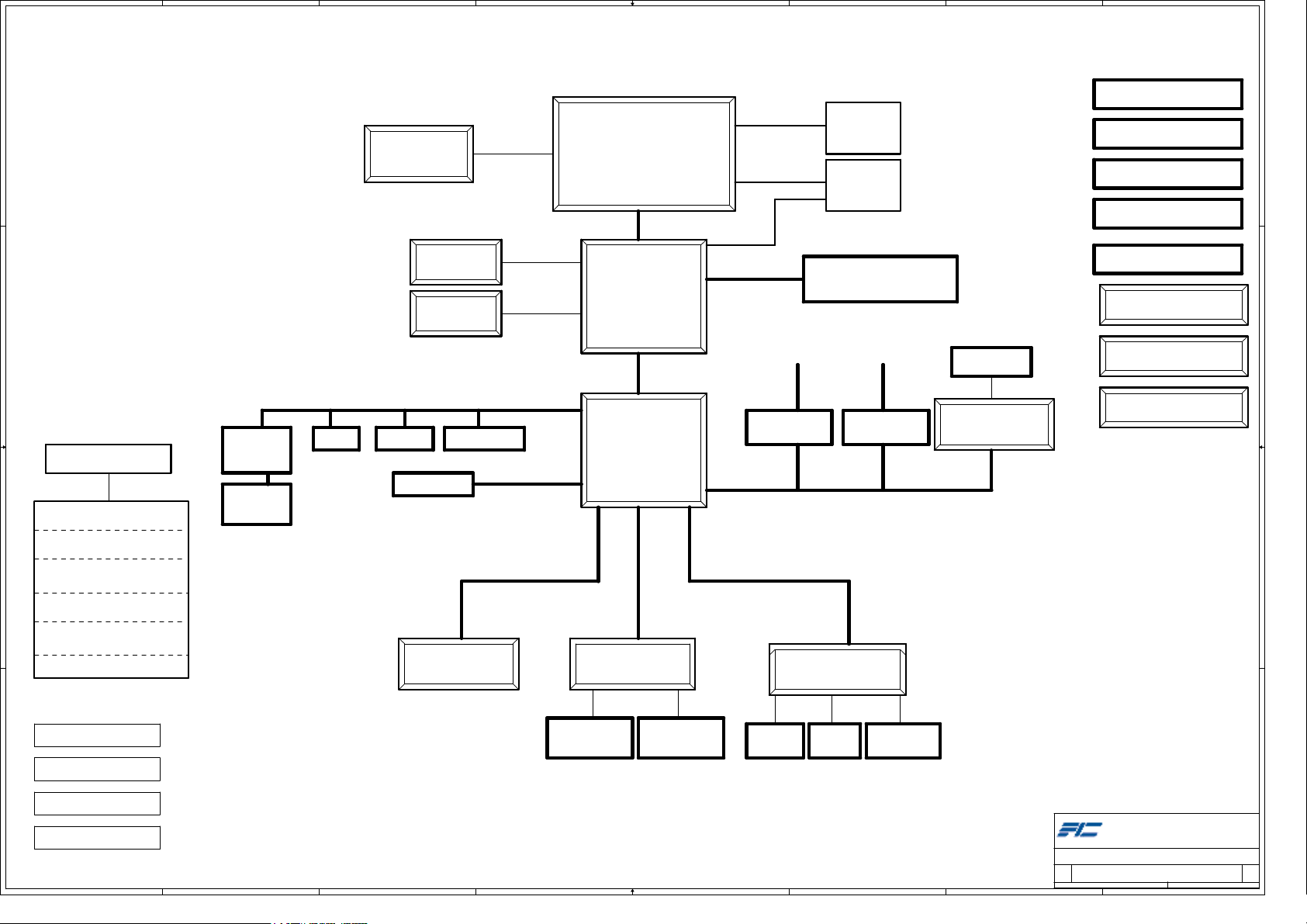

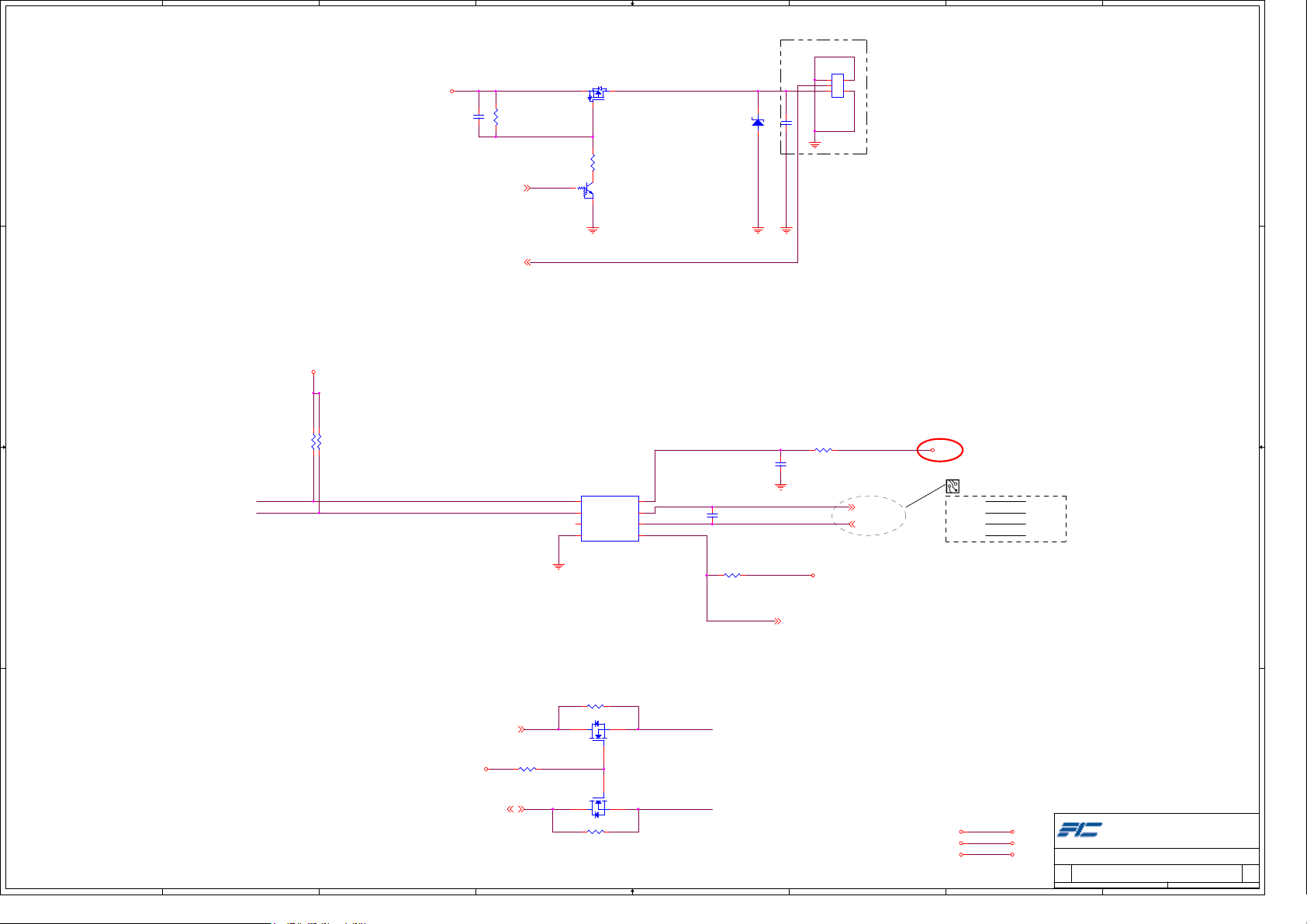

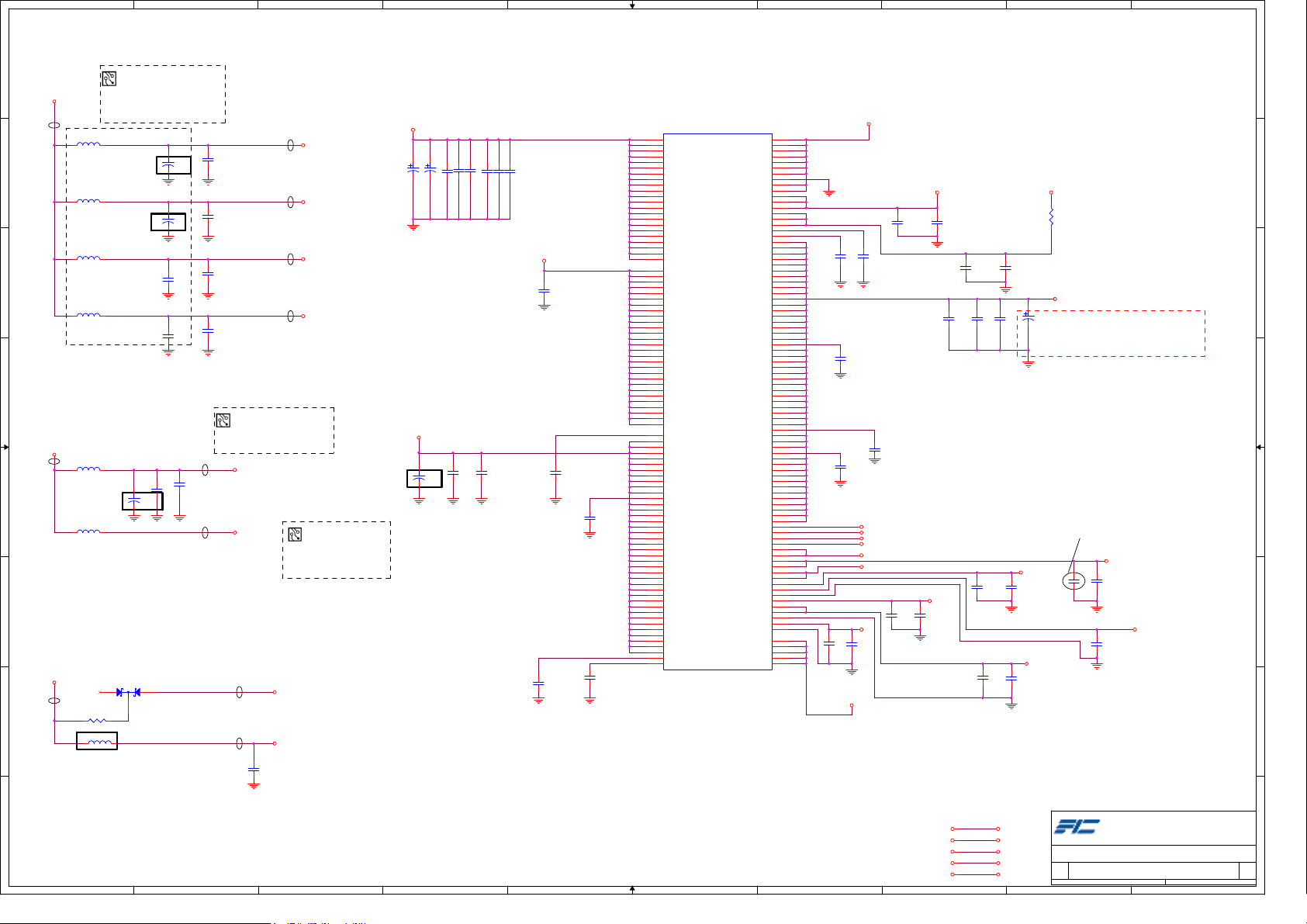

3. Block Diagram :

6

5

4

3

2

1

RTC Bat

D D

Thermal

Sensor

P10

Intel

Diamondville

Processor

P8~9

Host Bus

CRT

P22

LCD

C C

P23

USB 2.0

Intel

Calistoga/

945GMS

P12~P17

DMI

Intel

CCD

ACIN / DCIN

P41

Realtek

RTS5158E

P31

CardReader

3 in 1

PMU3V/5V

3VDDA/5VDDA

B B

3VDDM/5VDDM

DDRII Power

1.5VDDM/1.05VDDM

OVP

P44

P44

P44

P45

P45

P41

P31

P34

B / T

HDD

USB0,1

P35

P24

Flash ROM

8M

P34

IDE BUS

P46

ICH7m

SPI BUS

PMX

M38859

P21~24

LPC BUS

P39

Mem_A Bus

Express Card

PCI-E

Azalia

Azalia Codec

ALC269

CPU

CORE

P09

CPU

VCCP

P43

DDRII SODIMM0

USB 2.0

P26

USB 2.0

Mini Card

P34

P17

Lan10/100M

RTL8102E

P28

RJ-45

P30

P29

Fan CNN

Lid Switch

Switch Board/LED/DIP SW

MAIN SW CNN

CLK

ICS9LPRS501PKLFT

Reset Circuit

Brightness Control

P22

P10

P36

P36

P36

P16

P25

P23

DCIN+

Battery Voltage Sense

A A

Battery Charger

Battery CON

8

P41

P39

P42

P42

7

6

Int. KB

5

P24

Glide Pad

P36

Mic In

4

SPK

P37

P37

Headphone

3

P37

First International Computer, Inc.

2FL.,NO.300,Yang Guang St.,NeiHu

114 TAIPEI, TAIWAN ,ROC

Title

Size Document Number Rev

C

Date: Sheet

2

(886-2)875 1-8751

CW0A0

Block Diagram

3 47Thursday, June 26, 2008

1

0.1

of

8

7

6

5

4

3

2

1

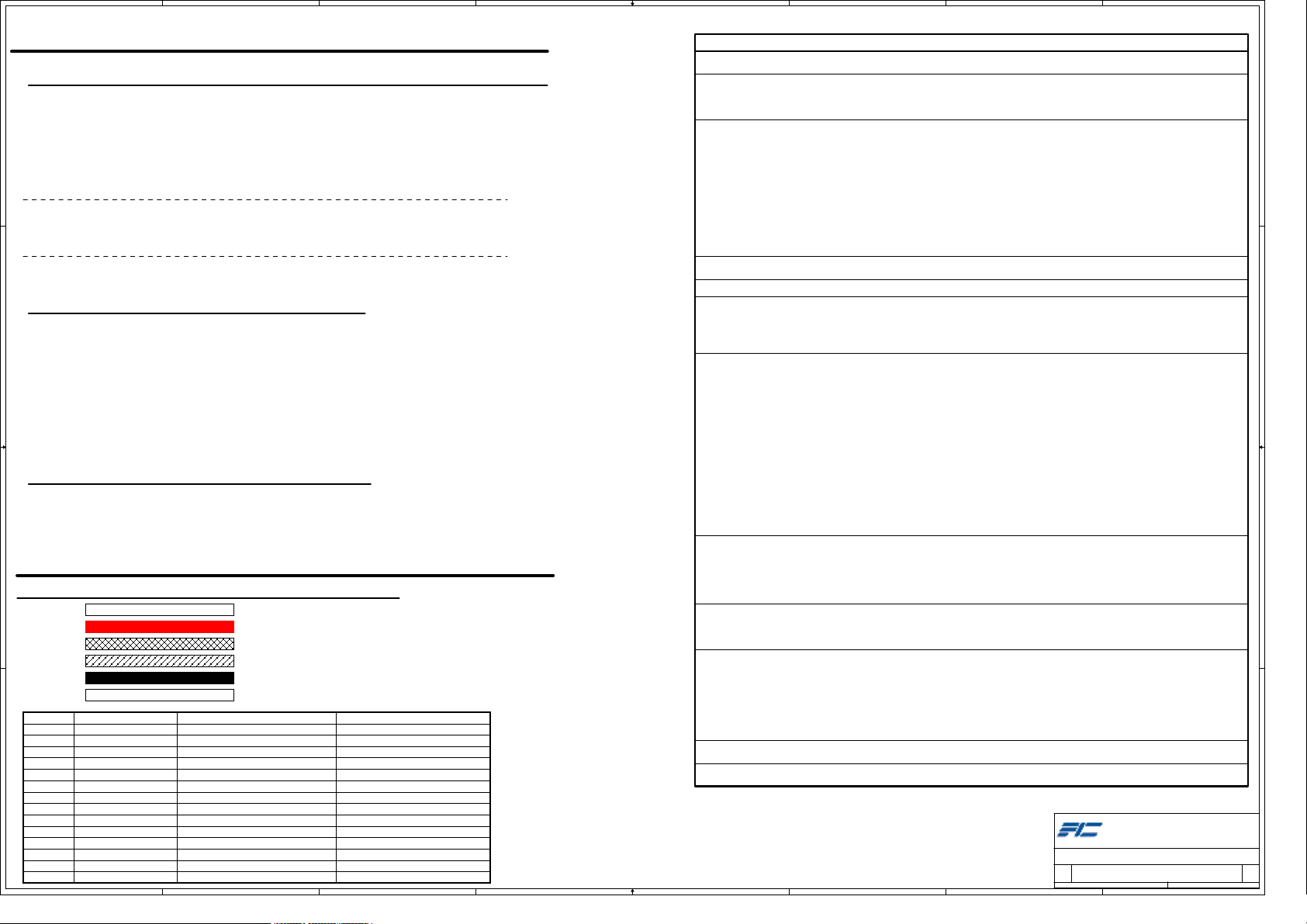

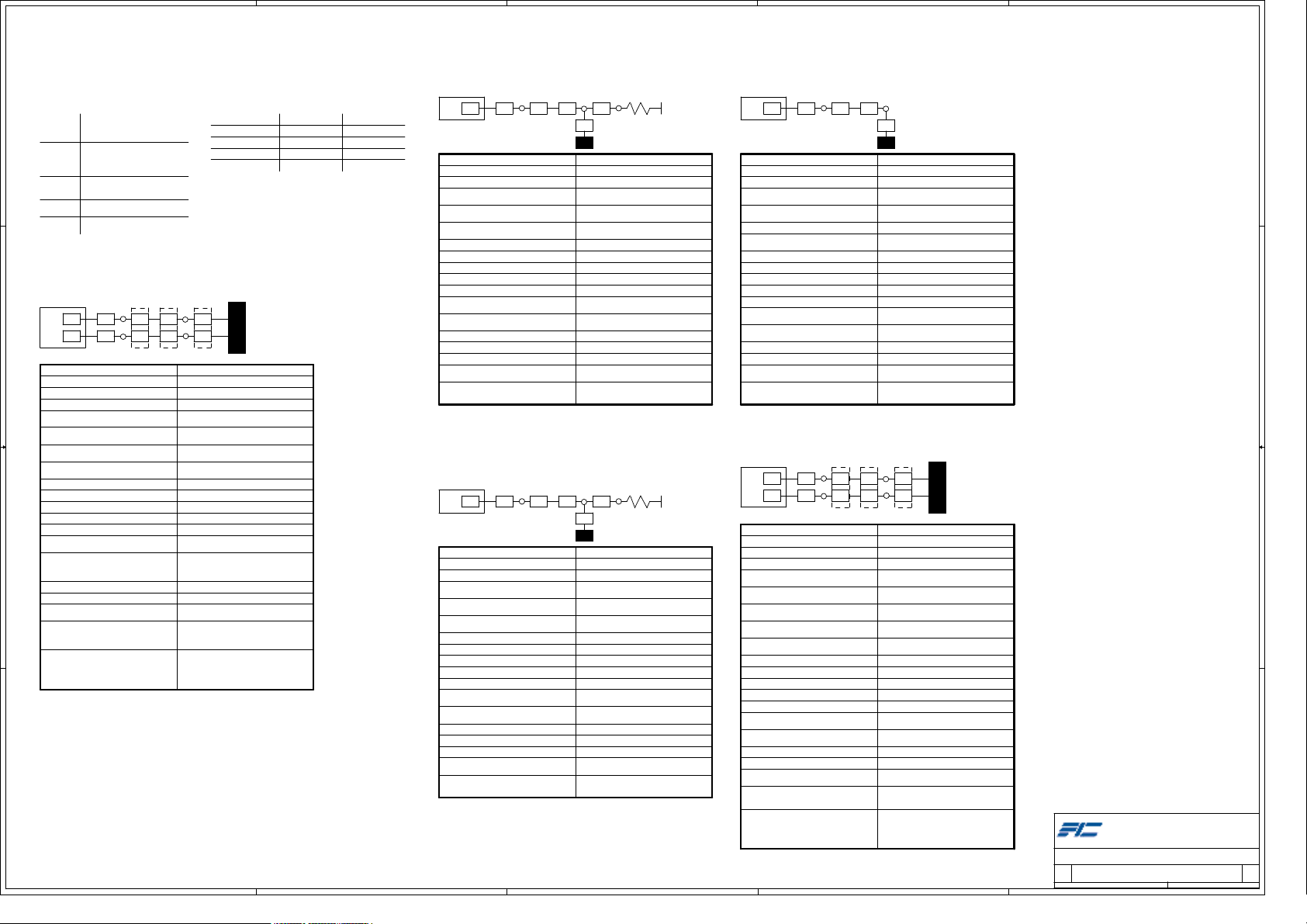

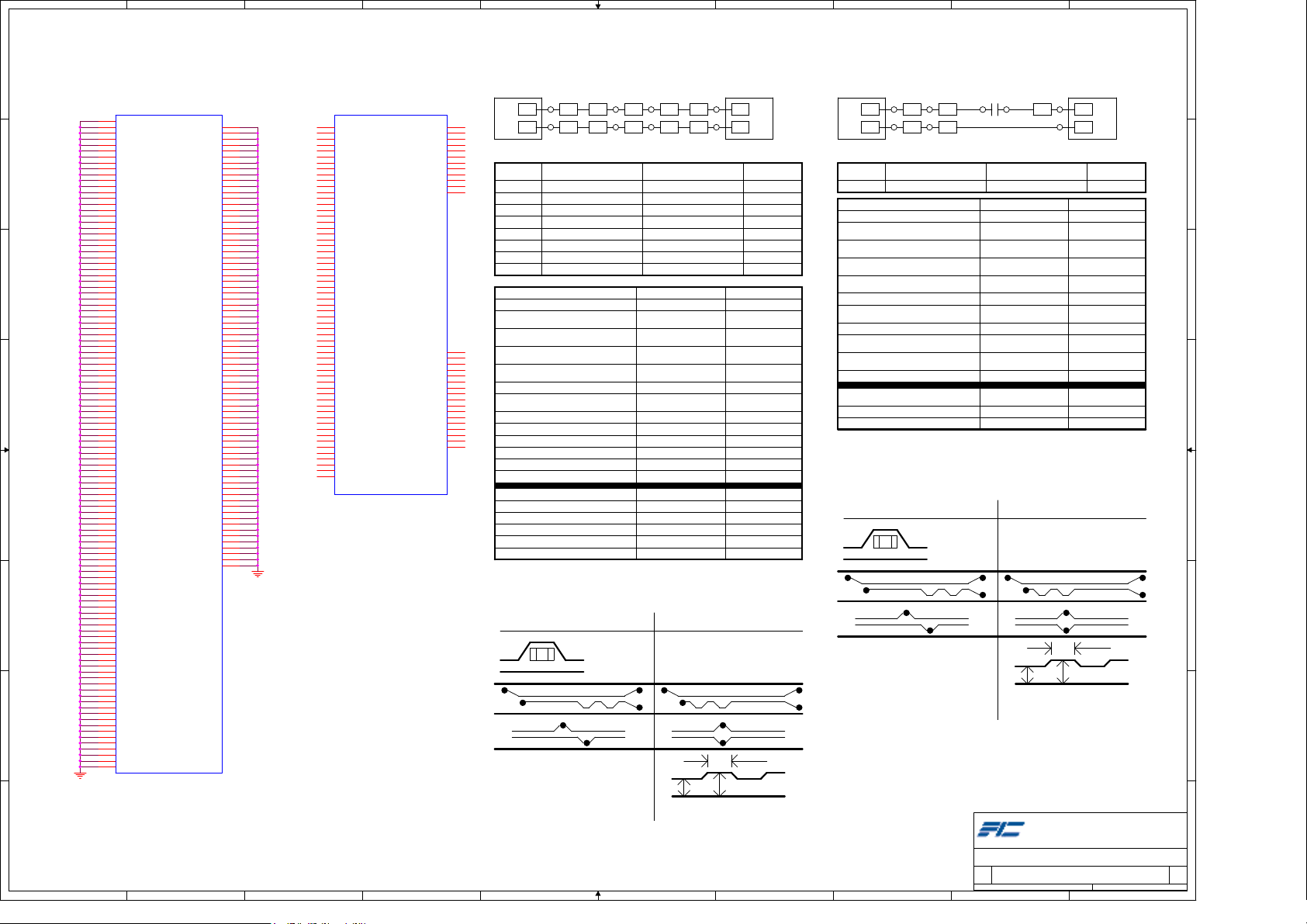

4. Nat name Description :

Voltage Rails

DCIN

PMU5V 5.0V always on power rail by LATCH or ACIN

D D

PMU3V 3.3V always on power rail by LATCH or ACIN

3VDDA 3.3V always on power rail by DCON

3VDDS 3.3V power rail by PSUSC#

5VDDS 5.0V power rail by PSUSC#

3VDDM

VCC_CORE

1.05VDDM

1.5VDDM

1.8VDDS

0.9VDDT_DDRII

Part Naming Conventions

C

=

C C

CN

D

F

L

Q

R

RP

U

Y

Capacitor

Connector

=

Diode

=

Fuse

=

Inductor

=

Transistor

=

Resistor

=

Resistor Pack

=

Arbitrary Logic Device

=

Crystal and Osc

=

Primary DC system power supply

5.0V always on power rail by DCON5VDDA

3.3V switched power rail by SUSTAT_B#

5.0V switched power rail by SUSTAT_B#5VDDM

Core Voltage for CPU

1.05V power rail for AGTL+ termination/Core for GMCH by SUSTAT_B#

1.5V power rail for CPU PLL/DMI;PCIE;DDRII DLLs for GMCH/Core;PCIE

for ICH7m by SUSTAT_B#

1.8V power rail for DDRII by PSUSC#

0.9V DDRII Termination Voltage by SUSTAT_B#

Power Rail

VCC_CORE

1.05VDDM

1.5VDDM

1.8VDDS:

0.9VDDT_DDRII: DDRII Terminator:

2.5VDDM

3VDDM

Net Name Suffix

# =

B B

5. Board Stack up Description

Active Low signal

3VDDS CardBus:

PCB Layers

Layer 1

Component Side, Microstrip signal Layer

Layer 2 Power Plane

Layer 3

Layer 4

Layer 5

Layer 6

Host Clock

SRC Clock

Host Bus

DDR2 CLK

DDR2 Strobe

A A

DDR2 Bus

DMI Bus

PCIE Bus

SATA

SDVO

LVDS

USB

IEEE1394

Lan

Single End Impedance Differential Impedance for Microstrip Differential Impedance for Stripline

55 ohm +/- 15%

55 ohm +/- 15%

42 ohm +/- 15%

55 ohm +/- 15%

55 ohm +/- 15%

55 ohm +/- 15%

55 ohm +/- 15%

55 ohm +/- 15%

50 ohm +/- 15%

8

95 ohm +/- 15% 100 ohm +/- 15%

95 ohm +/- 15% 100 ohm +/- 15%55 ohm +/- 15%

70 ohm +/- 20% 70 ohm +/- 20%

95 ohm +/- 15% 100 ohm +/- 15%

95 ohm +/- 15% 100 ohm +/- 15%

90 ohm +/- 15% 90 ohm +/- 15%

110 ohm +/- 15% 110 ohm +/- 15%

Stripline Layer(AGTL,CLOCK,DDR)

Stripline Layer(Analog,LVDS,other)

Ground Plane

Solder Side,Microstrip signal Layer

85 ohm +/- 20%

100 ohm +/- 15%95 ohm +/- 15%

100 ohm +/- 15%95 ohm +/- 15%

100 ohm +/- 15%100 ohm +/- 15%

7

6

5

3VDDA

5VDDM Mini PCI:

5VDDS CardBus: Slot voltage

PMU3V

4

Destination

Diamondville

Diamondville: AGTL+ termination

945GMs: Core

945GMs: AGTL+ termination

ICH7m:

Diamondville PLL

945GMs: PCIE

945GMs: LVDS

945GMs: TVDAC

945GMs: Various PLLS analog supply

945GMs: DDR DLLS,DDRII,FSB HSIO 1.25A1.425V~1.5V~1.575V

ICH7m:

ICH7m:

ICH7m:

ICH7m:

Mini Card:

Express Card:

945GMs: DDRII System Memory 1.72A

SO-DIMM:

945GMs: PCIE analog

945GMs: LVDS analog

945GMs: LVDS I/O

945GMs: CRT DAC

CH7307:

945GMs: HV CMOS

945GMs: TVDAC analog

ICH7m:

ICH7m:

ICH7m:

ICH7m:

ICH7m:

Mini Card:

Express Card:

CLK Generator: ICS9LPRS501PKLFT 400mA3.135V~3.3V~3.465V

Mini PCI: WirelessLan

KBC:

Flash ROM: BIOS

Azalia Codec: ALC269

Azalia MDC:

HDD: SATA

CardBus:

Lan: Realtek RTL8102E

Card Reader: RTS5158E

Azalia MDC:

Mini PCI: For wake up

ICH7m:

ICH7m:

ICH7m:

LCD:

Azalia Codec: ALC269

Azalia MDC:

HDD: PATA

ODD:

Audio AMP:

Woofer AMP:

Inverter:

USB: x 4 ports

EC: PMX

ICH7m: RTC

HFM:

LFM:

3

Voltage

0.9V~1.1V

0.75V~1.00V

1.0V~1.05V~1.1V

1.0V~1.05V~1.1V

0.9975V~1.05V~1.1025V

1.425V~1.5V~1.575V

1.425V~1.5V~1.575V

1.425V~1.5V~1.575V

1.425V~1.5V~1.575V

1.425V~1.5V~1.575V

1.7V~1.8V~1.9V

0.855V~0.9V~0.945V

2.32V~2.5V~2.625V

2.375V~2.5V~2.625V

2.375V~2.5V~2.625V

2.32V~2.5V~2.625V

3.135V~3.3V~3.465V

3.135V~3.3V~3.465V

3.0V~3.3V~3.6V

3.0V~3.3V~3.6V 1.0A

3.0V~3.3V~3.6V

4.75V~5.0V~5.25V Max: 1.0A ; R/W: 460mA ; STDBY: 70mA

5V 2.0A

2

S0 Current

2.2A

1.5A

2.5A

2.94A

1.4A

120mA

400mA

20mA

24mA

320mA

10uA

2mA

10mA

60mA

70mA

40mA

120mA

Title

CW0A0

Size Document Number Rev

C

Annotations

Date: Sheet

%Recommend Design Target 4A

First International Computer, Inc.

2FL.,NO.300,Yang Guang St.,NeiHu

114 TAIPEI, TAIWAN ,ROC

(886-2)875 1-8751

4 47Thursday, June 26, 2008

of

1

0.1

5

4

3

2

1

6.Schematic modify Item and History :

1025

D D

R479 change from 150ohm(NU) to 75ohm(NU)

C C

B B

A A

First International Computer, Inc.

2FL.,NO.300,Yang Guang St.,NeiHu

114 TAIPEI, TAIWAN ,ROC

Title

Size Document Number Rev

C

5

4

3

2

Date: Sheet

(886-2)875 1-8751

CW0A0

Schematic Modify

1

5 47Thursday, June 26, 2008

0.1

of

5

4

3

2

1

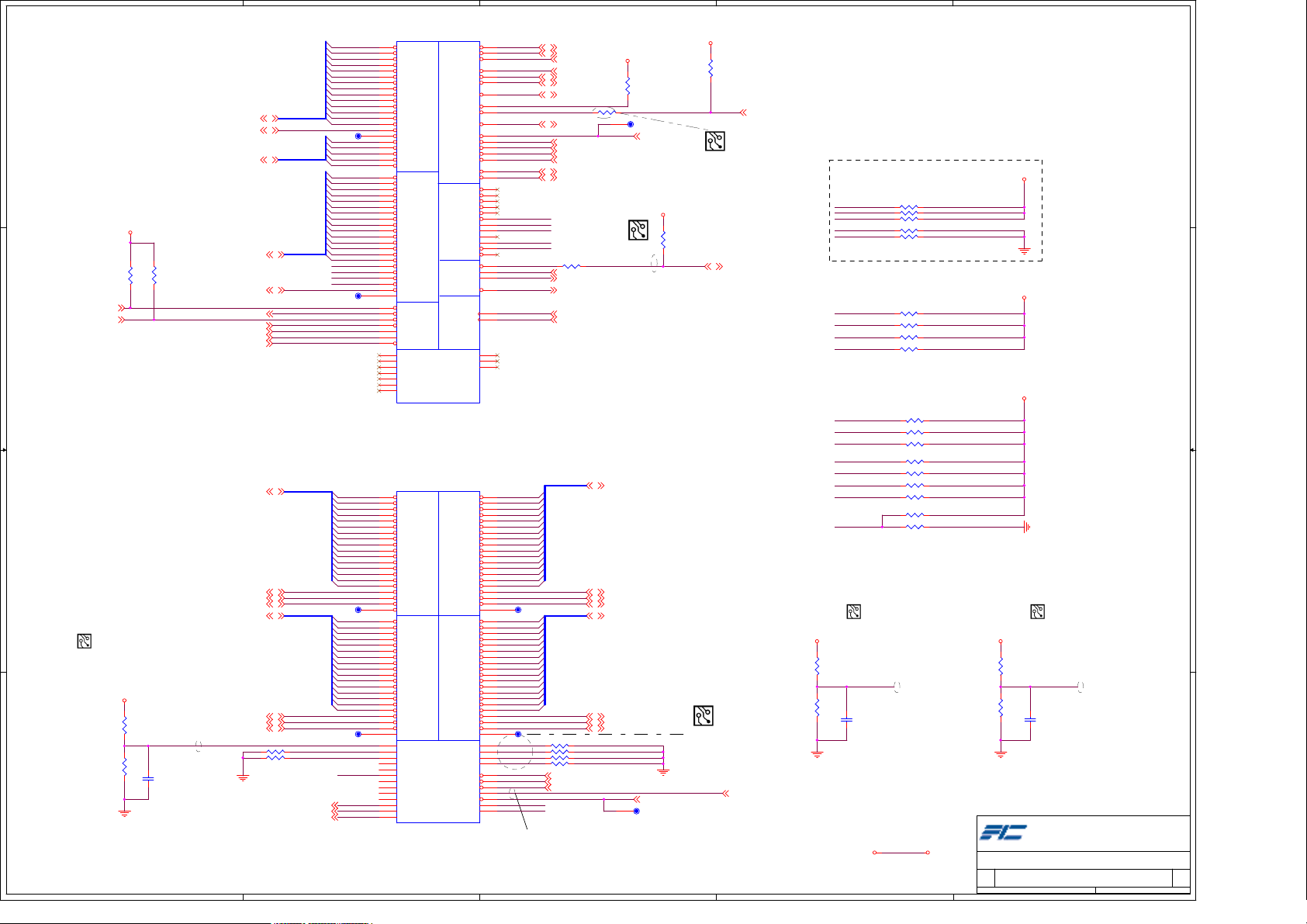

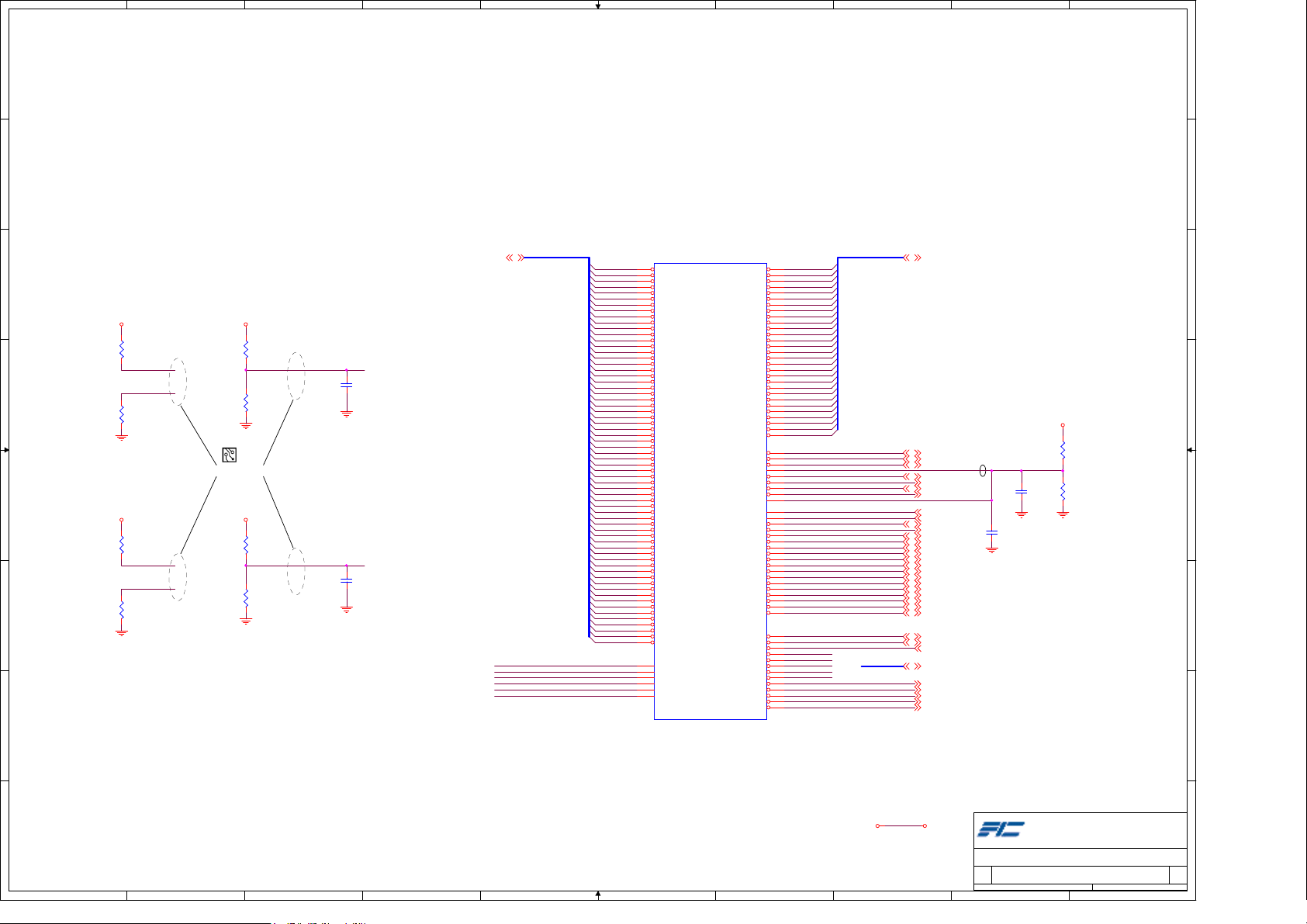

7. power on & off & S3 Sequence :

IMVP6 Power On Sequencing Timing Diagram

D D

C C

B B

A A

VID

VR_ON

Vcc-core

CPU_UP

Tsft_star_vcc(3ms max)

Tboot

Tcpu_up

Vid

Vboot

Tboot-vid-tr(100uS max)

Vccp

Vccp_UP

Tvccp_up

Vccgmch

GMCHPWRGD

Tgmch_pwrgd

CLK_ENABLE#

IMVP4_PWRGD

BATTERY ONLY POWER ON TIMING

POWSW0

PMU5V/PMU3V

DCON

VDDA

MAINSW0_ICH

PM_RSTRST0

PM_SLP_S30/S40/S50

PSUSC0

SUSTAT_B0

VDDM,VDDS

PM_PWROK

SYS_PWROK

VRON_VCCP

VCCP/1.2VDDM

VCORE_ON

VR_ON

VCORE_CPU

CK408_PWRGD0

PM_VGATE

CPU_PWRGD

PCI_RST0

AGTL+_CPURST0

Tcpu_pwrgd(3~20mS)

Tboot:10-100uS

To ICH4

To ICH4

From ICH4

From ASIC_B0

From ASIC_B0

To clock generator

To ODEM and ICH4

From ICH4 to CPU

To ODEM/other PCI device

From ODEM to CPU

S3 SUSPEND AND RESUME TIMING

POWSW0

PMU5V/PMU3V

PM_RSMRST0

PM_SLP_S30

PM_SLP_S40/S50

SUSTAT_B0

PM_PWROK

SYS_PWROK

VRON_VCCP

VCCP,1.2VDDM

VCORE_ON

VCORE_CPU

CK408_PWRGD0

PM_VGATE

CPU_PWRGOOD

PCI_RST0

AGTL+_CPURST0

DCON

VDDA

PSUSC0

VDDS

VDDM

VR_ON

H

H

H

H

H

H

H

To ICH4_M

From ICH4_M

From ICH4_M

From ASIC_B0

From ASIC_B0

1.5VDDS AND

DDR_PWRGD

Generator

To clock

ToICH4 and ODEM

From ICH4 to CPU

To ODEM/other

PCI device

From ODEM to CPU

First International Computer, Inc.

2FL.,NO.300,Yang Guang St.,NeiHu

114 TAIPEI, TAIWAN ,ROC

Title

Size Document Number Rev

C

5

4

3

2

Date: Sheet

(886-2)875 1-8751

CW0A0

Timing Diagram

1

6 47Thursday, June 26, 2008

0.1

of

5

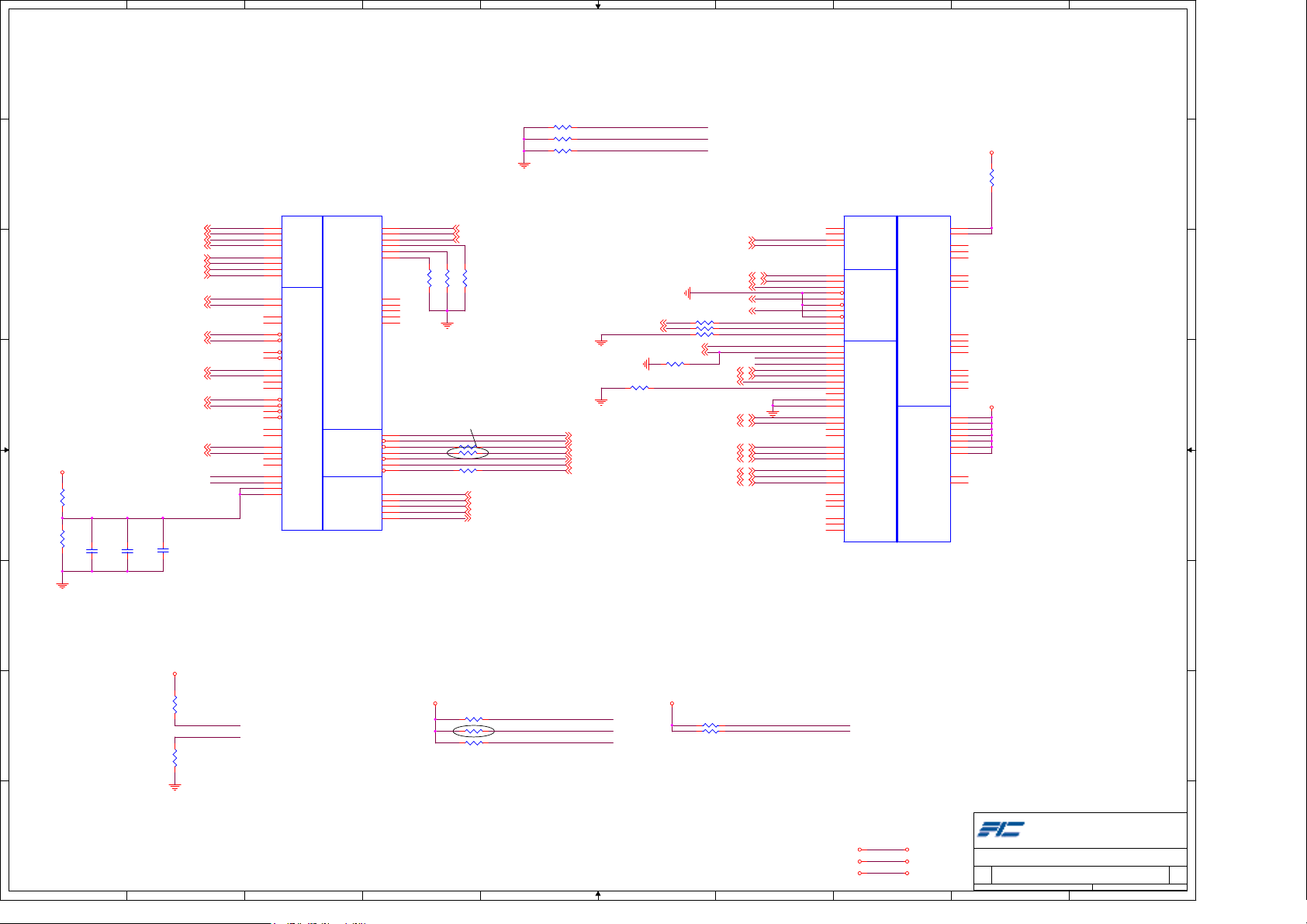

8. Layout Guideline :

4

3

2

1

Calistoga (945GM) DDRII Layout Guidelines

DDRII Signal Groups

Group Signal Name

D D

Data

SA_DQ[63..0]/SB_DQ[63..0]

SA_DM[7..0]/SB_DM[7..0]

SA_DQS[7..0]/SA_DQS#[7..0]

SB_DQS [7..0]/SB_DQS#[7..0]

SA_MA[13..0]/SB_MA[13..0]Address

SA_BS[2..0]/SB_BS[2..0]

SA_RAS#/SB_RAS#

SA_CAS#/SB_CAS#

SA_WE#/SB_WE#

SM_CS#[3..0]Control

SM_CKE[3..0]

SM_ODT[3..0]

Clock SM_CK[3..0]

SM_CK#[3..0]

SA_ RCVENOUT#/S B_RCVENOUT#FeedBack

SA_RC VENIN#/SB_RCVENIN#

CLK group : SM_CK[3..0],SM_CK#[3..0]

GMCH

P1P1L0L0L1L1L2L2S1

C C

Topology

Reference Plane

Sin gle End ed Trace Impe dance

Differ ential Mode Impedance

Nominal Trace Width Inner Layer : 7 mils

Nominal CK to CK # Spacing

(edge to edge)

Min imum Serpent ine Spacing Inner Layer : 12 mils

Min imum Spaci ng to Othe r DDR2 Inner Layer : 16 mils

Min imum Iso lation Spaci ng to non -DDR2 25 mils

Packag e Length R ange - P1 1000 mils +/- 250 mils

Trace Length Limit - L0 Max = 50 mils (Escape)

Trace Length Limit - L1 Max = 500 mils (Breakout)

Stu b Len gth S 1-Stu b from via to SO-DIMM Max = 200 mils (Breakin)

MB Le ngth Limits - L0 + L1 + L2 + S1 Min = 500 mils

B B

Maximim Via Count 2 (Per side)

SCK to S CK# Leng th Matching Mat ch total l ength to within 5 mil s

Clo ck to Clock L ength Match

(Total Length)

Bre akout Exce ption s (Red uce geometr ies

for GM CH break-o ut region)

Bre akin Excep tions (Reduce geo metries

for SO-DIMM br eak-in reg ion)

Feedback group :

SA_RCVENIN#],SA_RCVENOUT#,SB_RCVENIN#],SB_RCVENOUT#

The se sig nals are r outed inte rnall y on the G MCH p ackag e and don't requ ire an y

rou ting on th e MB. As a resu lt, can be left as NC .

A A

4/4/12 7/4/16 8/5/15

Escape

Breakout Breakin

5

SLMS SL MS

Length Matching and Length Formulas

Signal Group Minimum Length Maximum Length

Control-to-Clock

Command-to-Clock

Strobe-to-Clock

Data-to-Strobe

Clock - 1.0"

Clock - 1.0"

Clock - 0.5"

Strobe - 220mils

SO-DIMM

S1

Differe ntial Pair Point-to-Point

Ground

42 +/- 15%

70 +/- 20%

Outer Layer : 8 mils

Inner Layer : 4 mils

Outer Layer : 5 mils

Outer Layer : 15 mils

Outer Layer : 20 mils

Max = 4000 mils

Max = 4500 milsTotal Length - P1 + L0 + L 1 + L2 + S1

Total Length fo r Channel A : X0

Total Length fo r Channel B : X1

Mat ch Cha nnel A clocks to X0 +/- 20mi ls

Mat ch Cha nnel A clocks to X1 +/- 20mi ls

Inner Layer : 4/1 2 mils to o ther DDR2

Out er Layer : 5/15 mils to other D DR2

Max. b reakout le ngth is 500 mils

CK to CK# spaci ng rule w aived at

con necto r spacing o f 15 mils to

other DDR2

Max. b reakin leng th is 200 mils

Clock - 0.0"

Clock + 1.0"

Clock + 1.0"

Strobe - 180mils

4

Control group : SM_CKE[3..0],SM_CS#[3..0],SM_ODT[3..0]

4/4/12

7/4/16

GMCH

Escape

P1

L0

MS SL/MS

L1

Breakout

SL

8/5/15

L2

L3

SL/MS

S1

MS

Vtt

SO-DIMM

Topology

Reference Plane

Cha racte ristic Tr ace Impedance

Nominal Trace Width

Minimum CTRL Trace Spacing

Min imum Spaci ng to Othe r DDR2

Min imum Iso lation Spaci ng to non -DDR2

Package Length P1

Trace Length Limit - L0

Trace Length Limit - L1

Stu b Len gth S 1-Stu b from via to SO-DIMM

MB Le ngth Limits - L0 + L1 + L2 + S1 Fro m GMC H ball to SO-DIMM pad

Total Length - P1 + L0 + L 1 + L2 + S1 Fro m GMC H die to SO-DIMM pad

Parall el Terminat ion Resistor 56 +/- 5%

Maximim Via Count

CTR L to SCK/S CK# Length Matching

(Total Length in cluding pack age)

Bre akout Exce ption s (Red uce geometr ies

for GM CH break-o ut region)

Command group :

SA_MA[13..0],SB_MA[13..0],SA_BS[2..0],SB_BS[2..0],SA_RAS#,

SB_RAS#,SA_CAS#,SB_CAS#,SA_WE#,SB_WE#

GMCH

P1

Escape

L0

4/4

Breakout

Poin t-to-Point with parall el terminat ion

Ground

55 +/- 15%

Inner Layer : 4 mils

Outer Layer : 5 mils

Inner Layer : 8 mils

Outer Layer : 10 mils

Inner Layer : 12 mils

Outer Layer : 15 mils

25 mils

750 mils +/- 200 mils

Max = 50 mils (Escape)

Max = 500 mils (Breakout)

Max = 200 mils (Breakin)

Min = 500 mils

Max = 4500 mils

Max = 5000 mils

Max = 1500 milsTrace Length L3

3

(CLK- 1.0") </= CTRL </= (CLK-0.0")

Inner Layer : 4 mils spacing allowed

Oute r Layer : 5 mils spacin g allowed

Max. b reakout le ngth is 500 mils

4/6,5/10

4/6,5/10

L1

L2

SL/MS

SL/MSMS SL

S1

MS

L3

Vtt

SO-DIMM

Topology

Reference Plane

Cha racte ristic Tr ace Impedance

Nominal Trace Width

Min imum C MD Bus Tr ace Spacing

Min imum Spaci ng to Othe r DDR2

Min imum Iso lation Spaci ng to non -DDR2

Package Length P1

Trace Length Limit - L0

Trace Length Limit - L1

Stu b Len gth S 1-Stu b from via to SO-DIMM

MB Le ngth Limits - L0 + L1 + L2 + S1 Fro m GMC H ball to SO-DIMM pad

Total Length - P1 + L0 + L 1 + L2 + S1 Fro m GMC H die to SO-DIMM pad

Trace Length L3

Parall el Terminat ion Resistor

Maximim Via Count

CTR L to SCK/S CK# Length Matching

(Total Length in cluding pack age)

for GM CH break-o ut region)

Poin t-to-Point with parall el terminat ion

Ground

55 +/- 15%

Inner Layer : 4 mils

Outer Layer : 5 mils

Inner Layer : 6 mils

Outer Layer : 10 mils

Inner Layer : 12 mils

Outer Layer : 15 mils

25 mils

750 mils +/- 350 mils

Max = 50 mils (Escape)

Max = 500 mils (Breakout)

Max = 200 mils (Breakin)

Min = 500 mils

Max = 4500 mils

Max = 5000 mils

Max = 1500 mils

56 +/- 5%

3

(CLK- 1.0") </= CMD </= (CLK+1.0")

Inner Layer : 4 mils spacing allowedBre akout Exce ption s (Red uce geometr ies

Oute r Layer : 5 mils spacin g allowed

Max. b reakout le ngth is 500 mils

3

Data group : SA_DQ[63..0],SB_DQ[63..0],SA_DM[7..0],SB_DM[7..0]

4/4

L1

Breakout

4/6

L2

S1

GMCH

Escape

P1 L0

MS SLSL MS

SO-DIMM

Topology

Reference Plane

Cha racte ristic Tr ace Impedance

Nominal Trace Width

Min imum DQ Bus Trace S pacing

Min imum Serpent ine Spacing S ame as DQ-to -DQ routing

Min imum Spaci ng to Othe r DDR2

Min imum Iso lation Spaci ng to non -DDR2

Package Length P1

Trace Length Limit - L0

Trace Length Limit - L1

Stu b Len gth S 1-Stu b from via to SO-DIMM

MB Le ngth Limits - L0 + L1 + L2 + S1 Fro m GMC H ball to SO-DIMM pad

Total Length - P1 + L0 + L 1 + L2 + S1 Fro m GMC H die to SO-DIMM pad

Trace Length L3

Maximim Via Count

DQ/ DM to DQS L ength Matching

(Total Length including

Bre akout Exce ption s (Red uce geometr ies

package)

for GM CH break-o ut region)

Point-to-Point

Ground

55 +/- 15%

Inner Layer : 4 mils

Outer Layer : 5 mils

Inner Layer : 6 mils

Outer Layer : 8 mils

Inner Layer : 12 mils

Outer Layer : 15 mils

25 mils

750 mils +/- 350 mils

Max = 50 mils (Escape)

Max = 500 mils (Breakout)

Max = 200 mils (Breakin)

Min = 500 mils

Max = 4500 mils

Max = 5000 mils

Max = 1500 mils

2

Mat ch DQ/DM to [SDQS - 2 00mils]

+/- 20m ils, per byte lane

Inner Layer : 4 mils spacing allowed

Oute r Layer : 5 mils spacin g allowed

Max. b reakout le ngth is 500 mils

Data Strobe group : SA_DQS[7..0],SA_DQS[7..0]#,SB_DQS[7..0],SB_DQS[7..0]#

GMCH

P1

P1

Topology

Reference Plane

Sin gle End ed Trace Impe dance

Differ ential Mode Impedance

Nominal Trace Width

Nom inal DQS to DQS# Spacin g

(edge to edge)

Min imum Serpent ine Spacing

Min imum Spaci ng to Othe r DDR2

Min imum Iso lation Spaci ng to non -DDR2

Packag e Length R ange - P1

Trace Length Limit - L0

Trace Length Limit - L1

Stu b Len gth S 1-Stu b from via to SO-DIMM

MB Le ngth Limits - L0 + L1 + L2 + S1 Fro m GMC H ball to SO-DIMM pad

Total Length - P1 + L0 + L 1 + L2 + S1 Fro m GMC H die to SO-DIMM pad

Maximim Via Count

DQS to D QS# L ength Matc hing

Clo ck to Clock L ength Match

(Tota l Length include pack age)

Bre akout Exce ption s (Red uce geometr ies

for GM CH break-o ut region)

Bre akin Excep tions (Reduce geo metries

for SO-DIMM br eak-in reg ion)

Escape

L0

L0

4/4/8

L1

L1

Breakout

SL SL MS

4/4/12

L2

L2

SO-DIMM

5/5/10

S1

S1

Breakin

Differe ntial Pair Point-to-Point

Ground

55 +/- 15%

85 +/- 20%

Inner Layer : 4 mils

Outer Layer : 5 mils

Inner Layer : 4 mils

Outer Layer : 5 mils

Inner Layer : 12 milsMinimu m DQS to DQ Spacing

Outer Layer : 15 mils

Inner Layer : 8 mils

Outer Layer : 10 mils

Inner Layer : 12 mils

Outer Layer : 15 mils

25 mils

750 mils +/- 350 mils

Max = 50 mils (Escape)

Max = 500 mils (Breakout)

Max = 200 mils (Breakin)

Min = 500 mils

Max = 4500 mils

Max = 5000 mils

2 (Per side)

Mat ch total length to within 5 mi ls

(CLK- 0.5") </= DQS </= (CLK+1.0")

Inner Layer : 8 mils to oth er DDR2

Out er Layer : 10 mils to other DDR 2

Max. b reakout le ngth is 500 mils

DQS to DQS# sp acing rule

wai ved at connecto r spacing o f

10 mils to other DDR2

Max. b reakin leng th is 200 mils

2

Title

Size Document Number Rev

C

Date: Sheet

First International Computer, Inc.

2FL.,NO.300,Yang Guang St.,NeiHu

114 TAIPEI, TAIWAN ,ROC

(886-2)875 1-8751

CW0A0

DDRII Layout Guideline

1

7 47Thursday, June 26, 2008

0.1

of

5

4

3

2

1

1.05VDDM

R226

330Ω 5% 1/16W SMT0402 LR

H_INIT# 19

close to processor

R149

68Ω 5% 1/16W SMT0402 TIN LR

H_PROCHOT# 43

COMP0,2 connect with Zo=27.4ohm, make

trace length shorter than 0.5"

COMP1,3connect with Zo=55ohm, make

trace length shorter than 0.5"

H_PWRGD 19

XDP P/U & P/D

XDP_TMS

R171 RES 56Ω 5% 1/16W SMT0402 LR

XDP_TDI

R174 RES 56Ω 5% 1/16W SMT0402 LR

XDP_BPM#5

R167 RES 56Ω 5% 1/16W SMT0402 LR

R175 RES 56Ω 5% 1/16W SMT0402 LR

XDP_TCK

XDP_TRST#

R169 RES 56Ω 5% 1/16W SMT0402 LR

H_A#32

R536 1KΩ 1% 1/16W SMT0402 LR

H_A#33

R529 1KΩ 1% 1/16W SMT0402 LR

H_A#34

R534 1KΩ 1% 1/16W SMT0402 LR

H_A#35

R533 1KΩ 1% 1/16W SMT0402 LR

H_NMI

H_SMI#

H_INTR

H_STPCLK#

H_DPSLP#

H_DPRSTP#

H_PWRGD

H_DPWR#

R185

1KΩ 1% 1/16W SMT0402 LR

R184

RES 2KΩ 1% 1/16W SMT 0402 LR

2

R186 51Ω 5% 1/16W SMT0402 LR(NU)

R214 51Ω 5% 1/16W SMT0402 LR(NU)

R194 51Ω 5% 1/16W SMT0402 LR(NU)

R179 56Ω 5% 1/16W SMT0402 LR(NU)

R196 1KΩ 5% 1/16W SMT0402 LR(NU)

R188 1KΩ 5% 1/16W SMT0402 LR(NU)

R211 1KΩ 5% 1/16W SMT0402 LR(NU)

R203 1KΩ 5% 1/16W SMT0402 LR(NU)

R210 1KΩ 5% 1/16W SMT0402 LR(NU)

Layout note:Zo=55 ohm,

0.5'' max for EXTGBTEF

10mils 10mils

EXTBGREF

C137

0.1uF 10V ±10% SMT0402 X5R LR

1.05VDDM9,11,13,14,16,19,21,45

1.05VDDM

1.05VDDM

1.05VDDM

Layout note:Zo=55 ohm,

0.5'' max for

1.05VDDM1.05VDDM

EXTGBTEF

R110

1KΩ 1% 1/16W SMT0402 LR

CPU_CMREF

R111

RES 2KΩ 1% 1/16W SMT 0402 LR

C92

0.1uF 10V ±10% SMT0402 X5R LR

First International Computer, Inc.

5FL.,NO.300,Yang Guang St.,NeiHu

114 TAIPEI, TAIWAN ,ROC

1.05VDDM

Title

Size Document Number Rev

C

Date: Sheet

(886-2) 8751-8751

CW0A0

Diamondville (1/2)

1

8 47Thursday, June 26, 2008

0.1

of

1

1

1

1

4

U35A

P21

A[3]#

H20

A[4]#

N20

A[5]#

R20

A[6]#

J19

A[7]#

N19

A[8]#

G20

A[9]#

M19

A[10]#

H21

A[11]#

L20

A[12]#

M20

A[13]#

K19

A[14]#

J20

A[15]#

L21

A[16]#

K20

ADSTB[0]#

D17

AP0

N21

REQ[0]#

J21

REQ[1]#

G19

REQ[2]#

P20

REQ[3]#

R19

REQ[4]#

C19

A[17]#

F19

A[18]#

E21

A[19]#

A16

A[20]#

D19

A[21]#

C14

A[22]#

C18

A[23]#

C20

A[24]#

E20

A[25]#

D20

A[26]#

B18

A[27]#

C15

A[28]#

B16

A[29]#

B17

A[30]#

C16

A[31]#

A17

A[32]#

B14

A[33]#

B15

A[34]#

A14

A[35]#

B19

ADSTB[1]#

M18

AP1

U18

A20M#

T16

FERR#

J4

IGNNE#

R16

STPCLK#

T15

LINT0

R15

LINT1

U17

SMI#

D6

NC1

G6

NC2

H6

NC3

K4

NC4

K5

NC5

M15

NC6

L16

NC7

Diamondville_SC_Rev1

U35B

Y11

D[0]#

W10

D[1]#

Y12

D[2]#

AA14

D[3]#

AA11

D[4]#

W12

D[5]#

AA16

D[6]#

Y10

D[7]#

Y9

D[8]#

Y13

D[9]#

W15

D[10]#

AA13

D[11]#

Y16

D[12]#

W13

D[13]#

AA9

D[14]#

W9

D[15]#

Y14

DSTBN[0]#

Y15

DSTBP[0]#

W16

DINV[0]#

V9

DP#0

AA5

D[16]#

Y8

D[17]#

W3

D[18]#

U1

D[19]#

W7

D[20]#

W6

D[21]#

Y7

D[22]#

AA6

D[23]#

Y3

D[24]#

W2

D[25]#

V3

D[26]#

U2

D[27]#

T3

D[28]#

AA8

D[29]#

V2

D[30]#

W4

D[31]#

Y4

DSTBN[1]#

Y5

DSTBP[1]#

Y6

DINV[1]#

R4

DP#1

A7

GTLREF

U5

ACLKPH

V5

DCLKPH

T17

BINIT#

R6

EDM

M6

EXTBGREF

N15

FORCEPR#

N6

HFPLL

P17

MCERR#

T6

RSP#

J6

BSEL[0]

H5

BSEL[1]

G5

BSEL[2]

Diamondville_SC_Rev1

V19

ADS#

Y19

BNR#

U21

BPRI#

ADDR

GROUP

0

ADDR GROUP

1

DEFER#

DRDY#

DBSY#

BR0#

IERR#

INIT#

LOCK#

CONTROLXDP/ITP SIGNALS

RESET#

RS[0]#

RS[1]#

RS[2]#

TRDY#

HITM#

BPM[0]#

BPM[1]#

BPM[2]#

BPM[3]#

PRDY#

PREQ#

TRST#

BR1#

PROCHOT#

THRMDA

THRMDC

THERMTRIP#

BCLK[0]

BCLK[1]

T21

T19

Y18

T20

H_IERR#

F16

V16

W20

D15

W18

Y17

U20

W19

AA17

HIT#

V20

K17

J18

H15

J15

K18

XDP_BPM#5

J16

XDP_TCK

M17

TCK

XDP_TDI

N16

TDI

M16

TDO

XDP_TMS

L17

TMS

XDP_TRST#

K16

V15

G17

E4

E5

H17

V11

V12

H_ADS# 11

H_BNR# 11

H_BPRI# 11

H_DEFER# 11

H_DRDY# 11

H_DBSY# 11

H_BREQ# 11

H_LOCK# 11

H_RS#0 11

H_RS#1 11

H_RS#2 11

H_TRDY# 11

H_HIT# 11

H_HITM# 11

1.05VDDM

R148

RES 56Ω 5% 1/16W SMT0402 LR

R225 1KΩ 5% 1/16W SMT0402 LR

1

T48

H_CPURST# 11

0'' ~ 3''

R144 22Ω 1% 1/16W SMT0402 LR

H_THERMDA 10

H_THERMDC 10

PM_THRMTRIP# 12,19

CLK_CPU_BCLK 16

CLK_CPU_BCLK# 16

1.05VDDM

H CLK THERM

C21

RSVD3

C1

RSVD2

A3

NC

RSVD1

.

MISC

DATA GRP 0 DATA GRP 1

D[32]#

D[33]#

D[34]#

D[35]#

D[36]#

D[37]#

D[38]#

D[39]#

D[40]#

D[41]#

D[42]#

D[43]#

DATA GRP 2DATA GRP 3

D[44]#

D[45]#

D[46]#

D[47]#

DSTBN[2]#

DSTBP[2]#

DINV[2]#

DP#2

D[48]#

D[49]#

D[50]#

D[51]#

D[52]#

D[53]#

D[54]#

D[55]#

D[56]#

D[57]#

D[58]#

D[59]#

D[60]#

D[61]#

D[62]#

D[63]#

DSTBN[3]#

DSTBP[3]#

DINV[3]#

DP#3

COMP[0]

COMP[1]

COMP[2]

COMP[3]

DPRSTP#

DPSLP#

DPWR#

PWRGOOD

SLP#

CORE_DET

CMREF[1]

H_D#[63..0]

H_D#32

R3

H_D#33

R2

H_D#34

P1

H_D#35

N1

H_D#36

M2

H_D#37

P2

H_D#38

J3

H_D#39

N3

H_D#40

G3

H_D#41

H2

H_D#42

N2

H_D#43

L2

H_D#44

M3

H_D#45

J2

H_D#46

H1

H_D#47

J1

K2

K3

L1

1

M4

T29

H_D#[63..0]

H_D#48

C2

H_D#49

G2

H_D#50

F1

H_D#51

D3

H_D#52

B4

H_D#53

E1

H_D#54

A5

H_D#55

C3

H_D#56

A6

H_D#57

F2

H_D#58

C6

H_D#59

B6

H_D#60

B3

H_D#61

C4

H_D#62

C7

H_D#63

D2

E2

F3

C5

D4

1

T25

COMP0

T1

T2

F20

F21

R18

R17

U4

V17

N18

A13

B7

R557 RES 27.4Ω 1% 1/16W SMT 0402 LR

COMP1

R558 54.9Ω 1% 1/16W SMT0402 LR Sn

COMP2

R143 RES 27.4Ω 1% 1/16W SMT 0402 LR

COMP3

R150 54.9Ω 1% 1/16W SMT0402 LR Sn

H_DPRSTP# 19,43

H_DPSLP# 19

H_DPWR#

H_DPWR# 11

CORE_DET

CPU_CMREF

H_PWRGD rise time :

Max : 15ns

H_D#[63..0] 11

H_DSTBN#2 11

H_DSTBP#2 11

H_DINV#2 11

H_D#[63..0] 11

H_DSTBN#3 11

H_DSTBP#3 11

H_DINV#3 11

3

H_CPUSLP# 11

1

T33

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#[31..3]

H_REQ#[4..0]

H_A#[31..3]

H_FERR#19

H_INTR19

H_NMI19

H_SMI#19

H_D#[63..0]

H_D#[63..0]

R207 1KΩ 5% 1/16W SMT0402 LR(NU)

R212 1KΩ 5% 1/16W SMT0402 LR(NU)

10mils

H_A#[31..3]11

H_ADSTB#011

H_REQ#[4..0]11

H_A#[31..3]11

H_ADSTB#111

H_STPCLK#19

H_D#[63..0]11

H_DSTBN#011

H_DSTBP#011

H_DINV#011

H_D#[63..0]11

H_DSTBN#111

H_DSTBP#111

H_DINV#111

D D

1.05VDDM

R205

R168

1KΩ 5% 1/16W SMT0402 LR(NU)

1KΩ 5% 1/16W SMT0402 LR(NU)

H_A20M#19

H_IGNNE#19

C C

B B

Zo=55ohm, 0.5" max for GTLREF, Space any other switch signals away from

GTLREF with a minimum of 25mils.

Don't allow the GTLREF routing to create splits or discontinuities

in the reference planes of the FSB signals

1.05VDDM

R521

1KΩ 1% 1/16W SMT0402 LR

R520

RES 2KΩ 1% 1/16W SMT 0402 LR

C403

A A

0.1uF 10V ±10% SMT0402 X5R LR

5

H_A#15

H_A#16

T23

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_A#32

H_A#33

H_A#34

H_A#35

T30

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

T32

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

T31

H_GTLREF

EXTBGREF

CPU_BSEL016

CPU_BSEL116

CPU_BSEL216

A

4 4

B

C

D

E

U35D

A2

VSS1

A4

VSS2

A8

VSS4

A15

VSS5

A18

VSS6

A19

VSS7

A20

VSS8

B1

VSS9

B2

VSS10

B5

VSS11

B8

VSS12

B13

VSS13

B20

VSS14

B21

VSS15

C8

VSS16

C17

VSS17

D1

VSS18

D5

VSS19

D8

VSS20

D14

VSS21

D18

VSS22

D21

VSS23

E3

VSS24

E6

VSS25

E7

VSS26

E8

VSS27

E15

3 3

2 2

VSS28

E16

VSS29

E19

VSS30

F4

VSS31

F5

VSS32

F6

VSS33

F7

VSS34

F17

VSS35

F18

VSS36

G1

VSS37

G4

VSS38

G7

VSS39

G9

VSS41

G13

VSS42

G21

VSS45

H3

VSS46

H4

VSS48

H7

VSS49

H9

VSS51

H13

VSS52

H16

VSS53

H18

VSS54

H19

VSS55

J5

VSS56

J7

VSS57

J9

VSS58

J13

VSS59

J17

VSS60

K1

VSS61

K6

VSS62

K7

VSS63

K9

VSS64

K13

VSS65

K15

VSS66

K21

VSS67

L3

VSS68

L4

VSS69

L5

VSS70

L6

VSS71

L7

VSS72

L9

VSS73

L13

VSS74

L15

VSS75

L18

VSS76

L19

VSS77

M1

VSS78

M5

VSS79

M7

VSS80

M9

VSS81

M13

VSS82

M21

VSS83

N4

VSS84

Diamondville_SC_Rev1

VSS162

VSS161

VSS160

VSS159

VSS158

VSS157

VSS156

VSS155

VSS154

VSS153

VSS152

VSS151

VSS149

VSS148

VSS147

VSS146

VSS145

VSS144

VSS143

VSS142

VSS141

VSS140

VSS139

VSS138

VSS137

VSS136

VSS135

VSS134

VSS133

VSS132

VSS131

VSS130

VSS129

VSS128

VSS127

VSS126

VSS125

VSS124

VSS123

VSS122

VSS121

VSS120

VSS119

VSS118

VSS117

VSS116

VSS115

VSS114

VSS113

VSS112

VSS111

VSS110

VSS109

VSS108

VSS107

VSS106

VSS105

VSS104

VSS103

VSS102

VSS101

VSS100

VSS99

VSS98

VSS97

VSS96

VSS95

N5

N7

N9

N13

N17

P3

P4

P5

P6

P7

P9

P13

P15

P16

P18

P19

R1

R5

R7

R9

R13

R21

T4

T5

T7

T9

T10

T11

T12

T13

T18

U3

U6

U7

U15

U16

U19

V1

V4

V6

V7

V8

V13

V14

V18

V21

W1

W5

W8

W11

W14

W17

W21

Y1

Y2

Y20

Y21

AA2

AA3

AA4

AA7

AA10

AA12

AA15

AA18

AA19

AA20

VCORE_CPU

Place these inside socket cavity on

L8 (South side secondary)

C95 1uF 6.3V 10% SMT0402 X5R LR

C126 1uF 6.3V 10% SMT0402 X5R LR

C107 1uF 6.3V 10% SMT0402 X5R LR

C93 1uF 6.3V 10% SMT0402 X5R LR

C141 10uF 6.3V 20% SMT0603 X5R LR

C86 10uF 6.3V 20% SMT0603 X5R LR

C85 10uF 6.3V 20% SMT0603 X5R LR

C135 1uF 6.3V 10% SMT0402 X5R LR

C100 1uF 6.3V 10% SMT0402 X5R LR

C101 1uF 6.3V 10% SMT0402 X5R LR

C119 1uF 6.3V 10% SMT0402 X5R LR

C113 1uF 6.3V 10% SMT0402 X5R LR

C142 10uF 6.3V 20% SMT0603 X5R LR

C68 10uF 6.3V 20% SMT0603 X5R LR

C69 10uF 6.3V 20% SMT0603 X5R LR

C80 10uF 6.3V 20% SMT0603 X5R LR

C77 10uF 6.3V 20% SMT0603 X5R LR

C88 10uF 6.3V 20% SMT0603 X5R LR

C120 1uF 6.3V 10% SMT0402 X5R LR

C106 1uF 6.3V 10% SMT0402 X5R LR

C136 1uF 6.3V 10% SMT0402 X5R LR

C131 1uF 6.3V 10% SMT0402 X5R LR

C89 10uF 6.3V 20% SMT0603 X5R LR

C81 10uF 6.3V 20% SMT0603 X5R LR

C76 10uF 6.3V 20% SMT0603 X5R LR

1.05VDDM

C127 1uF 6.3V 10% SMT0402 X5R LR

C112 1uF 6.3V 10% SMT0402 X5R LR

C132 1uF 6.3V 10% SMT0402 X5R LR

C397 P-CAP (SP-CAP) 220uF 2V -35 to +10% 9mΩ SMT7343 EEFSX0D221EY PANASONIC LR

+

U35C

V10

VCCF

A9

VCCQ1

B9

VCCQ2

A10

VCCP1

A11

VCCP2

A12

VCCP3

B10

VCCP4

B11

VCCP5

B12

VCCP6

C10

VCCP7

C11

VCCP8

C12

VCCP9

D10

VCCP10

D11

VCCP11

D12

VCCP12

E10

VCCP13

E11

VCCP14

E12

VCCP15

F10

VCCP16

F11

VCCP17

F12

VCCP18

G10

VCCP19

G11

VCCP20

G12

VCCP21

H10

VCCP22

H11

VCCP23

H12

VCCP24

J10

VCCP25

J11

VCCP26

J12

VCCP27

K10

VCCP28

K11

VCCP29

K12

VCCP30

L10

VCCP31

L11

VCCP32

L12

VCCP33

M10

VCCP34

M11

VCCP35

M12

VCCP36

N10

VCCP37

N11

VCCP38

N12

VCCP39

P10

VCCP40

P11

VCCP41

P12

VCCP42

R10

VCCP43

R11

VCCP44

R12

VCCP45

Diamondville_SC_Rev1

VTT1

VTT2

VTT3

VTT4

VTT5

VTT6

VTT7

VTT8

VTT9

VTT10

VTT11

VTT12

VTT13

VTT14

VTT15

VTT16

VTT17

VTT18

VTT19

VTT20

VTT21

VTT22

VTT23

VTT24

VTT25

VTT26

VTT27

VTT28

VTT29

VTT30

VTT31

VTT32

VCCPC64

VCCPC63

VCCPC62

VCCPC61

VCCA

VID[0]

VID[1]

VID[2]

VID[3]

VID[4]

VID[5]

VID[6]

VCCSENSE

VSSSENSE

C9

D9

E9

F8

F9

G8

G14

H8

H14

J8

J14

K8

K14

L8

L14

M8

M14

N8

N14

P8

P14

R8

R14

T8

T14

U8

U9

U10

U11

U12

U13

U14

F14

F13

E14

E13

D7

F15

D16

E18

G15

G16

E17

G18

C13

D13

H_VID0 43

H_VID1 43

H_VID2 43

H_VID3 43

H_VID4 43

H_VID5 43

H_VID6 43

C149 1uF 6.3V 10% SMT0402 X5R LR

C103 0.1uF 10V ±10% SMT0402 X5R LR

C130 1uF 6.3V 10% SMT0402 X5R LR

C144 0.1uF 10V ±10% SMT0402 X5R LR

1.05VDDM

C117 1uF 6.3V 10% SMT0402 X5R LR

C150 1uF 6.3V 10% SMT0402 X5R LR

C84

C116

10uF 6.3V ±20% SMT0805 X5R CM21X5R106M06AT AVX/CYOCERA LR

10uF 6.3V ±20% SMT0805 X5R CM21X5R106M06AT AVX/CYOCERA LR

1.5VDDM

Intel CRB don't stuff

C118

T 220uF 2.5V ±20% ESR=15mΩ SMT7343 2R5TPE220MF SANYO LR(NU)

ICCA=130mA, 20mils

Place C? Close

C96

C102

10uF 6.3V 20% SMT0603 X5R LR(NU)

0.1uF 10V ±10% SMT0402 X5R LR

Route VCCSENSE and VSSSENSE traces

at 27.4 ohms with 50mil spacing.

Place PU and PD within 1 inch of CPU

To pin D7

VCORE_CPU

R133

100Ω 1% 1/16W SMT0402 LR

R132

100Ω 1% 1/16W SMT0402 LR

VCCSENSE 43

VSSSENSE 43

Place these inside socket cavity on L8

(North side secondary)

1 1

VCORE_CPU43

1.05VDDM8,11,13,14,16,19,21,45

1.5VDDM12,13,14,18,21,27,28,45

A

B

C

D

VCORE_CPU

1.05VDDM

1.5VDDM

First International Computer, Inc.

5FL.,NO.300,Yang Guang St.,NeiHu

114 TAIPEI, TAIWAN ,ROC

Title

Size Document Number Rev

C

Date: Sheet

(886-2) 8751-8751

CW0A0

Diamondville (2/2)

9 47Thursday, June 26, 2008

E

of

0.1

8

7

6

5

4

3

2

1

FAN Power Control

Q42

30mil 30mil

5VDDM

D D

C C

0.1uF 16V 80-20% 0402 Y5V(NU)

C504

R586

470Ω 5% 1/16W SMT040 2 LR

0Ω 5% 1/16W SMT0402 LR

FAN_PW M39

FAN_SPEED39

TRANS M-FET-P APM2301AAC-TRL -20V -3A SOT23 3PIN ANPEC LR

DS

G

R587

Q43

B

TRANS NPN RT1N44HM-T111-1 50V 100mA SC-70 3PIN IDC LR

E C

D55

DIODE ZENER GLZ6.2B 6.2V 20mA MIN I-MELF 2PIN PSI LR

P N

3VDDM

CN24

1

1

2

2

345

345

CON ACES 1.25MM S/T WIRE TO BOARD SMT TYPE 85205-0300L (LEAD FREE) 3PIN P=1

C496 1000pF 50V 10% 0402 X7R LR

20-24197-10

THERMAL SENSOR

4

3

10KΩ 5% SMT1010 1/16W 4P2R LR(NU)

B B

RP33

QSMCLK_PMU

QSMDAT_PMU

20mil

1

2

10mil

10mil

U31

8

SCLK

7

SDATA

6

ALRT#

LNR-IC Temperature Sensor G780P81U 3.0-5.5V MSOP-8 8PIN GMT LR

1

VCC

2

D+

3

D-

45

THM#GND

THRM_VCC

C405

2200pF 50V 10% SMT040 2 X7R LR

R519

10KΩ 5% 1/16W SMT040 2 LR

R509

100Ω 5% 1/16W SMT040 2 LR

C396

0.1uF 16V 80-20% SMT0402 Y5V L R

H_THERMDA

H_THERMDC

H_THERMDA 8

H_THERMDC 8

3VDDA

3VDDM

10 mil

10 mil

10 mil

Minimum

10 mil

GND

THERMDA

THERMDC

GND

HOT_DOWN#

R348 0Ω 5% 1/16W SMT0402 LR

SMCLK_PMU39,41

R358

5VDDM

A A

8

7

6

2.2KΩ 5% 1/16W SMT0402 LR(NU)

SMDAT_PMU39,41

D S

Q14 TRANS M-FET-N 2N7002 60V 115mA SOT-23 3PIN PSI LR(NU)

G

G

Q15 TRANS M-FET-N 2N7002 60V 115mA SOT-23 3PIN PSI LR(NU)

D S

R349 0Ω 5% 1/16W SMT0402 LR

5

QSMCLK_PMU

QSMDAT_PMU

4

HOT_DOWN# 39

First International Computer, Inc.

3VDDA18,20,21,23,25,26,27,28,29,35,36,38,39,41,4 4,45

3VDDM12,13,14,16,17,18,19,20,21,22,23,24,25,27,28,29,31,32,33,36,38,39, 43,44

5VDDM21,22,23,24,32,36,37,43,44, 45

3

3VDDA

3VDDM

Title

5VDDM

Size Document Number Rev

C

Date: Sheet

2

5FL.,NO.300,Yang Guang St.,NeiHu

114 TAIPEI, TAIWAN ,ROC

(886-2)875 1-8751

CW0A0

CPU Thermal

Confidential

10 47Thursday, June 26, 2008

of

1

0.1

10

9

8

7

6

5

4

3

2

1

H H

G G

H_XRCOMP

H_XSCOMP

H_XSWING

H_YRCOMP

H_YSCOMP

H_YSWING

H_D#[63..0]

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

U39A

C4

HD0#

F6

HD1#

H9

HD2#

H6

HD3#

F7

HD4#

E3

HD5#

C2

HD6#

C3

HD7#

K9

HD8#

F5

HD9#

J7

HD10#

K7

HD11#

H8

HD12#

E5

HD13#

K8

HD14#

J8

HD15#

J2

HD16#

J3

HD17#

N1

HD18#

M5

HD19#

K5

HD20#

J5

HD21#

H3

HD22#

J4

HD23#

N3

HD24#

M4

HD25#

M3

HD26#

N8

HD27#

N6

HD28#

K3

HD29#

N9

HD30#

M1

HD31#

V8

HD32#

V9

HD33#

R6

HD34#

T8

HD35#

R2

HD36#

N5

HD37#

N2

HD38#

R5

HD39#

U7

HD40#

R8

HD41#

T4

HD42#

T7

HD43#

R3

HD44#

T5

HD45#

V6

HD46#

V3

HD47#

W2

HD48#

W1

HD49#

V2

HD50#

W4

HD51#

W7

HD52#

W5

HD53#

V5

HD54#

AB4

HD55#

AB8

HD56#

W8

HD57#

AA9

HD58#

AA8

HD59#

AB1

HD60#

AB7

HD61#

AA2

HD62#

AB5

HD63#

A10

HXRCOMP

A6

HXSCOMP

C15

HXSWING

J1

HYRCOMP

K1

HYSCOMP

H1

HYSWING

945GMS

HADSTB0#

HADSTB1#

H_AVREF

HBREQ0#

HCPURST#

HDVREF

HOST

HDEFER#

HDINV0#

HDINV1#

HDINV2#

HDINV3#

HDPWR#

HDRDY#

HDSTBN0#

HDSTBN1#

HDSTBN2#

HDSTBN3#

HDSTBP0#

HDSTBP1#

HDSTBP2#

HDSTBP3#

HCPUSLP#

HA3#

HA4#

HA5#

HA6#

HA7#

HA8#

HA9#

HA10#

HA11#

HA12#

HA13#

HA14#

HA15#

HA16#

HA17#

HA18#

HA19#

HA20#

HA21#

HA22#

HA23#

HA24#

HA25#

HA26#

HA27#

HA28#

HA29#

HA30#

HA31#

HADS#

HBNR#

HBPRI#

HCLKN

HCLKP

HDBSY#

HHIT#

HHITM#

HLOCK#

HREQ0#

HREQ1#

HREQ2#

HREQ3#

HREQ4#

HRS0#

HRS1#

HRS2#

HTRDY#

H_A#3

F8

H_A#4

D12

H_A#5

C13

H_A#6

A8

H_A#7

E13

H_A#8

E12

H_A#9

J12

H_A#10

B13

H_A#11

A13

H_A#12

G13

H_A#13

A12

H_A#14

D14

H_A#15

F14

H_A#16

J13

H_A#17

E17

H_A#18

H15

H_A#19

G15

H_A#20

G14

H_A#21

A15

H_A#22

B18

H_A#23

B15

H_A#24

E14

H_A#25

H13

H_A#26

C14

H_A#27

A17

H_A#28

E15

H_A#29

H17

H_A#30

D17

H_A#31

G17

F10

C12

H16

E2

B9

C7

G8

B10

E1

AA6

AA5

C10

C6

H5

J6

T9

U6

G7

E6

F3

M8

T1

AA3

F4

M7

T2

AB3

C8

B4

C5

H_REQ#0

G9

H_REQ#1

E9

H_REQ#2

G12

H_REQ#3

B8

H_REQ#4

F12

A5

B6

G10

E8

E10

H_D#[63..0]8

F F

1.05VDDM 1.05VDDM

R573

54.9Ω 1% 1/16W SMT0402 LR

H_XSCOMP

E E

H_XRCOMP

R574

RES 24.9Ω 1% 1/16W SMT0402 LR

R279

RES 221Ω 1% 1/16W SMT0402 LR

H_XSWING

R280

100Ω 1% 1/16W SMT0402 LR

C212

0.1uF 10V ±10% SMT0402 X5R LR

Trace should be 10-mil wide with 20-mil spacing

D D

C C

B B

1.05VDDM 1.05VDDM

R563

54.9Ω 1% 1/16W SMT0402 LR

H_YSCOMP

H_YRCOMP

R564

RES 24.9Ω 1% 1/16W SMT0402 LR

R561

RES 221Ω 1% 1/16W SMT0402 LR

H_YSWING

R562

100Ω 1% 1/16W SMT0402 LR

C462

0.1uF 10V ±10% SMT0402 X5R LR

H_A#[31..3]

H_REQ#[4..0]

H_A#[31..3] 8

H_ADS# 8

H_ADSTB#0 8

H_ADSTB#1 8

H_BNR# 8

H_BPRI# 8

H_BREQ# 8

H_CPURST# 8

CLK_MCH_BCLK# 16

CLK_MCH_BCLK 16

H_DBSY# 8

H_DEFER# 8

H_DINV#0 8

H_DINV#1 8

H_DINV#2 8

H_DINV#3 8

H_DPWR# 8

H_DRDY# 8

H_DSTBN#0 8

H_DSTBN#1 8

H_DSTBN#2 8

H_DSTBN#3 8

H_DSTBP#0 8

H_DSTBP#1 8

H_DSTBP#2 8

H_DSTBP#3 8

H_HIT# 8

H_HITM# 8

H_LOCK# 8

H_REQ#[4..0] 8

H_RS#0 8

H_RS#1 8

H_RS#2 8

H_CPUSLP# 8

H_TRDY# 8

1.05VDDM

10mils

H_VREF

C162

0.1uF 10V ±10% SMT0402 X5R LR

C164

0.1uF 10V 10% SMT0402 X5R LR(NU)

R243

100Ω 1% 1/16W SMT0402 LR

R241

200Ω 1% 1/16W SMT0402 LR

A A

1.05VDDM8,9,13,14,16,19,21,45

10

9

8

7

6

5

4

1.05VDDM

Title

Size Document Number Rev

C

3

Date: Sheet

First International Computer, Inc.

2FL.,NO.300,Yang Guang St.,NeiHu

114 TAIPEI, TAIWAN ,ROC

(886-2)8751-8751

CW0A0

945GMS Host (1/5)

2

11 47Thursday, June 26, 2008

1

0.1

of

10

9

8

7

6

5

4

3

2

1

H H

R293 RES 150Ω 1% 1/16W SMT0402 LR

R296 RES 150Ω 1% 1/16W SMT0402 LR

R294 RES 150Ω 1% 1/16W SMT0402 LR

G G

DMI_TXN0

DMI_TXN018

DMI_TXN1

DMI_TXN118

DMI_TXP0

DMI_TXP018

DMI_TXP1

DMI_TXP118

DMI_RXN0

DMI_RXN018

DMI_RXN1

DMI_RXN118

DMI_RXP0

DMI_RXP018

DMI_RXP1

F F

E E

1.8VDDS

R332

D D

10KΩ 1% 1/16W SMT0402 LR

R333

10KΩ 1% 1/16W SMT0402 LR

C457

0.1uF 10V ±10% SMT0402 X5R LR

DMI_RXP118

M_CLK_DDR017

M_CLK_DDR117

M_CLK_DDR#017

M_CLK_DDR#117

M_CKE017

M_CKE117

M_CS#017

M_CS#117

M_ODT017

M_ODT117

M_RCOMP#

M_RCOMP

M_VREF_MCH

C274

C269

MO-CAP 2.2uF 6.3V 10% SMT0603 X5R H=0.9mm CM105X5R225K06AT AVX LR

0.1uF 10V ±10% SMT0402 X5R LR

U39B

Y29

DMI_RXN0

Y32

DMI_RXN1

Y28

DMI_RXP0

Y31

DMI_RXP1

V28

DMI_TXN0

V31

DMI_TXN1

V29

DMI_TXP0

V32

DMI_TXP1

AF33

SM_CK0

AG1

SM_CK1

AJ1

SM_CK2

AM30

SM_CK3

AG33

SM_CK0#

AF1

SM_CK1#

AK1

SM_CK2#

AN30

SM_CK3#

AN21

SM_CKE0

AN22

SM_CKE1

AF26

SM_CKE2

AF25

SM_CKE3

AG14

SM_CS0#

AF12

SM_CS1#

AK14

SM_CS2#

AH12

SM_CS3#

AJ21

SMOCDCOMP0

AF11

SMOCDCOMP1

AE12

SM_ODT0

AF14

SM_ODT1

AJ14

SM_ODT2

AJ12

SM_ODT3

AN12

SMRCOMPN

AN14

SMRCOMPP

AA33

SMVREF0

AE1 A27

SMVREF1 DREF_CLKN

945GMS

DMI

MCH_RSVD1

MCH_RSVD2

MCH_RSVD7

MCH_RSVD8

MCH_RSVD9

CFG/RSVD

DDR2 MUXING

ICHSYNC#

BM_BUSY#

EXT_TS0#

PM

EXT_TS1#/DPRSLPVR

THRMTRIP#

PWROK

RSTIN#

DREF_CLKP

CLK

DREF_SSCLKN

DREF_SSCLKP

CLKREQB

CFG0

CFG1

CFG2

CFG3

CFG5

CFG6

C18

E18

G20

G18

J20

J18

K32

K31

C17

F18

A3

E31

G21

R_PM_EXTTS#0

F26

PM_EXTTS#1

H26

J15

AB29

W27

A26

J33

H33

J22

MCH_CLKREQ#

MCH_BSEL0 16

MCH_BSEL1 16

MCH_BSEL2 16

R281

R282

R285

2.2KΩ 5% 1/16W SMT0402 LR(NU)

2.2KΩ 5% 1/16W SMT0402 LR

2.2KΩ 5% 1/16W SMT0402 LR(NU)

5/26 V02

R330 0Ω 5% 1/16W SMT0402 LR

R319 0Ω 5% 1/16W SMT0402 LR

R579 100Ω 1% 1/16W SMT0402 LR

DREFCLK# 16

DREFCLK 16

DREFSSCLK# 16

DREFSSCLK 16

MCH_CLKREQ# 16

CRT_VSYNC22

CRT_HSYNC22

R307

RES 1.5KΩ 1% 1/16W SMT0402 LR

MCH_ICH_SYNC# 18

PM_BMBUSY# 20

PM_EXTTS#0 17

PM_DPRSLPVR 20,43

PM_THRMTRIP# 8,19

DELAY_VR_PWRGOOD 20,43

PLTRST# 18,20,24,27,28,29,39

CRT_BLUE

CRT_GREEN

CRT_RED

CLK_PCIE_3GPLL#16

CLK_PCIE_3GPLL16

CRT_DDC_CLK22

CRT_DDC_DATA22

CRT_BLUE22

CRT_GREEN22

R312 RES 39 5% 1/16W SMT0402 LR

R311 RES 39 5% 1/16W SMT0402 LR

R301 255Ω 1% 1/16W SMT0402 LR

L_BKLTCTL23

LVDS_ENABKL39

CRT_RED22

L_CTLA_CLK

R326100KΩ 5% 1/16W SMT0402 LR

LVDS_DDC_CLK23

LVDS_DDC_DATA23

LVDS_ENALCD23

LVDS_TXCLK1_LN23

LVDS_TXCLK1_LP23

LVDS_TXOUT_L0N23

LVDS_TXOUT_L1N23

LVDS_TXOUT_L2N23

LVDS_TXOUT_L0P23

LVDS_TXOUT_L1P23

LVDS_TXOUT_L2P23

L_CTLB_DATA

LVDS_DDC_CLK

LVDS_DDC_DATA

CRT_BLUE

CRT_GREEN

CRT_RED

AA26

H27

J27

Y26

H20

H22

A24

A23

E25

F25

C25

D25

F27

D27

H25

H30

G29

F28

E28

G28

H28

K30

K27

J29

J30

K29

D30

C30

A30

A29

G31

F32

D31

H31

G32

C31

F33

D33

F30

E33

D32

F29

U39F

SDVOCTRL_DATA

SDVOCTRL_CLK

GCLKN

GCLKP

DDCCLK

DDCDATA

BLUE

BLUE#

GREEN

GREEN#

RED

RED#

VSYNC

HSYNC

REFSET

LBKLT_CTRL

LBKLT_EN

LCTLA_CLK

LCTLB_CLK

LDDC_CLK

LDDC_DATA

LVDD_EN

LIBG

LVBG

LVREFH

LVREFL

LACLKN

LACLKP

LBCLKN

LBCLKP

LADATAN0

LADATAN1

LADATAN2

LADATAP0

LADATAP1

LADATAP2

LBDATAN0

LBDATAN1

LBDATAN2

LBDATAP0

LBDATAP1

LBDATAP2

SDV0_TVCLKIN#

SDVO_FLDSTALL#

MISC

SDVO_TVCLKIN

SDVO_FLDSTALL

SDVO

SDVOB_GREEN#

SDVOB_BLUE#

SDVOB_GREEN

LVDS VGA

TV_DCONSEL0

TV_DCONSEL1

945GMS

EXP_COMPI

EXP_ICOMPO

SDVO_INT#

SDVO_INT

SDVOB_RED#

SDVOB_CLKN

SDVOB_RED

SDVOB_BLUE

SDVOB_CLKP

TVDAC_A

TVDAC_B

TVDAC_C

TV_REFSET

TV_IRTNA

TV

TV_IRTNB

TV_IRTNC

1.5VDDM

R28

M28

N30

R30

T29

M30

P30

T30

P28

N32

P32

T32

N28

M32

P33

R32

1.5VDDM

A21

C20

E20

G23

B21

C21

D21

G26

J26

R310

RES 24.9Ω 1% 1/16W SMT0402 LR

PEG_COMP

C C

1.8VDDS

R266

RES 80.6Ω 1% 1/16W SMT0402 RR0510S-80R6-FN CYNTEC LR

B B

M_RCOMP#

M_RCOMP

R577

RES 80.6Ω 1% 1/16W SMT0402 RR0510S-80R6-FN CYNTEC LR

A A

10

9

8

3VDDM 3VDDM

5/26 V02

R331 10KΩ 5% 1/16W SMT0402 LR

R318 10KΩ 5% 1/16W SMT0402 LR(NU)

R286 10KΩ 5% 1/16W SMT0402 LR

7

R_PM_EXTTS#0

PM_EXTTS#1

MCH_CLKREQ#

6

5

RP25

10KΩ 5% SMT1010 1/16W 4P2R LR

124

3

L_CTLB_DATA

L_CTLA_CLK

First International Computer, Inc.

2FL.,NO.300,Yang Guang St.,NeiHu

114 TAIPEI, TAIWAN ,ROC

1.5VDDM9,13,14,18,21,27,28,45

1.8VDDS14,17,45

3VDDM10,13,14,16,17,18,19,20,21,22,23,24,25,27,28,29,31,32,33,36,38,39,43,44

4

1.5VDDM

1.8VDDS

3VDDM

3

Title

CW0A0

Size Document Number Rev

C

Date: Sheet

(886-2)8751-8751

945GMS DMI/Graph (2/5)

2

12 47Thursday, June 26, 2008

1

0.1

of

10

9

8

7

6

5

4

3

2

1

H H

1.05VDDM

AB10

AA10

T25

R25

P25

N25

M25

P24

N24

M24

Y22

W22

V22

U22

T22

R22

P22

N22

M22

Y21

W21

V21

U21

T21

R21

P21

N21

M21

Y20

W20

V20

U20

T20

R20

P20

N20

M20

Y19

P19

N19

M19

Y18

P18

N18

M18

Y17

P17

N17

M17

Y16

P16

N16

M16

Y15

P15

N15

M15

Y14

W14

V14

U14

T14

R14

P14

N14

M14

T10

R10

P10

N10

L10

M10

A18

D1

U39H

VCC_NCTF1

VCC_NCTF2

VCC_NCTF3

VCC_NCTF4

VCC_NCTF5

VCC_NCTF6

VCC_NCTF7

VCC_NCTF8

VCC_NCTF9

VCC_NCTF10

VCC_NCTF11

VCC_NCTF12

VCC_NCTF13

VCC_NCTF14

VCC_NCTF15

VCC_NCTF16

VCC_NCTF17

VCC_NCTF18

VCC_NCTF19

VCC_NCTF20

VCC_NCTF21

VCC_NCTF22

VCC_NCTF23

VCC_NCTF24

VCC_NCTF25

VCC_NCTF26

VCC_NCTF27

VCC_NCTF28

VCC_NCTF29

VCC_NCTF30

VCC_NCTF31

VCC_NCTF32

VCC_NCTF33

VCC_NCTF34

VCC_NCTF35

VCC_NCTF36

VCC_NCTF37

VCC_NCTF38

VCC_NCTF39

VCC_NCTF40

VCC_NCTF41

VCC_NCTF42

VCC_NCTF43

VCC_NCTF44

VCC_NCTF45

VCC_NCTF46

VCC_NCTF47

VCC_NCTF48

VCC_NCTF49

VCC_NCTF50

VCC_NCTF51

VCC_NCTF52

VCC_NCTF53

VCC_NCTF54

VCC_NCTF55

VCC_NCTF56

VCC_NCTF57

VCC_NCTF58

VCC_NCTF59

VCC_NCTF60

VCC_NCTF61

VCC_NCTF62

VCC_NCTF63

VCC_NCTF64

VTT_NCTF1

VTT_NCTF2

VTT_NCTF3

VTT_NCTF4

VTT_NCTF5

VTT_NCTF6

MCH_RSVD3

MCH_RSVD4

MCH_RSVD5

MCH_RSVD6

NCTF

945GMS

VCCAUX_NCTF1

VCCAUX_NCTF2

VCCAUX_NCTF3

VCCAUX_NCTF4

VCCAUX_NCTF5

VCCAUX_NCTF6

VCCAUX_NCTF7

VCCAUX_NCTF8

VCCAUX_NCTF9

VCCAUX_NCTF10

VCCAUX_NCTF11

VCCAUX_NCTF12

VCCAUX_NCTF13

VCCAUX_NCTF14

VCCAUX_NCTF15

VCCAUX_NCTF16

VCCAUX_NCTF17

VCCAUX_NCTF18

VCCAUX_NCTF19

VCCAUX_NCTF20

VCCAUX_NCTF21

VCCAUX_NCTF22

VCCAUX_NCTF23

VCCAUX_NCTF24

VCCAUX_NCTF25

VCCAUX_NCTF26

VCCAUX_NCTF27

VCCAUX_NCTF28

VCCAUX_NCTF29

VCCAUX_NCTF30

VCCAUX_NCTF31

VCCAUX_NCTF32

VCCAUX_NCTF33

VCCAUX_NCTF34

VCCAUX_NCTF35

VCCAUX_NCTF36

VCCAUX_NCTF37

VCCAUX_NCTF38

VSS_NCTF1

VSS_NCTF2

VSS_NCTF3

VSS_NCTF4

VSS_NCTF5

VSS_NCTF6

VSS_NCTF7

VSS_NCTF8

VSS_NCTF9

VSS_NCTF10

VSS_NCTF11

VSS_NCTF12

VSS_NCTF13

VSS_NCTF14

VSS_NCTF15

VSS_NCTF16

VSS_NCTF17

VSS_NCTF18

VSS_NCTF19

CFG19

MCH_RSVD10

MCH_RSVD11

MCH_RSVD12

MCH_RSVD13

MCH_RSVD14

MCH_RSVD15

MCH_RSVD16

MCH_RSVD17

MCH_RSVD18

MCH_RSVD19

MCH_RSVD20

MCH_RSVD21

MCH_RSVD22

MCH_RSVD23

MCH_RSVD24

MCH_RSVD25

AD25

AC25

AB25

AD24

AC24

AD22

AD21

AD20

AD19

AD18

AD17

AD16

AD15

AD14

K14

AD13

Y13

W13

V13

U13

T13

R13

P13

N13

M13

AD12

Y12

W12

V12

U12

T12

R12

P12

N12

M12

AD11

AD10

K10

AN33

AA25

V25

U25

AA22

AA21

AA20

AA19

AA18

AA17

AA16

AA15

AA14

AA13

A4

A33

B2

AN1

C1

K28

K25

K26

R24

T24

K21

K19

K20

K24

K22

J17

K23

K17

K12

K13

K16

K15

G G

M_A_DQ[63..0]17

F F

E E

D D

C C

M_A_DQ[63..0]

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

AC31

AB28

AE33

AF32

AC33

AB32

AB31

AE31

AH31

AK31

AL28

AK27

AH30

AL32

AJ28

AJ27

AH32

AF31

AH27

AF28

AJ32

AG31

AG28

AG27

AN27

AM26

AJ26

AJ25

AL27

AN26

AH25

AG26

AM12

AL11

AM11

AK11

AG11

AG19

AG21

AG20

U39C

SA_DQ0

SA_DQ1

SA_DQ2

SA_DQ3

SA_DQ4

SA_DQ5

SA_DQ6

SA_DQ7

SA_DQ8

SA_DQ9

SA_DQ10

SA_DQ11

SA_DQ12

SA_DQ13

SA_DQ14

SA_DQ15

SA_DQ16

SA_DQ17

SA_DQ18

SA_DQ19

SA_DQ20

SA_DQ21

SA_DQ22

SA_DQ23

SA_DQ24

SA_DQ25

SA_DQ26

SA_DQ27

SA_DQ28

SA_DQ29

SA_DQ30

SA_DQ31

SA_DQ32

SA_DQ33

AH9

SA_DQ34

AK9

SA_DQ35

SA_DQ36

SA_DQ37

AM8

SA_DQ38

AK8

SA_DQ39

AG9

SA_DQ40

AF9

SA_DQ41

AF8

SA_DQ42

AK6

SA_DQ43

AF7

SA_DQ44

SA_DQ45

AJ6

SA_DQ46

AH6

SA_DQ47

AN6

SA_DQ48

AM6

SA_DQ49

AK3

SA_DQ50

AL2

SA_DQ51

AM5

SA_DQ52

AL5

SA_DQ53

AJ3

SA_DQ54

AJ2

SA_DQ55

AG2

SA_DQ56

AF3

SA_DQ57

AE7

SA_DQ58

AF6

SA_DQ59

AH5

SA_DQ60

AG3

SA_DQ61

AG5

SA_DQ62

AF5

SA_DQ63

SB_CAS#

SB_RAS#

SB_WE#

DDR2 SYSTEM MEMORY

SA_RCVENOUTB

945GMS

SA_BS_0

SA_BS_1

SA_BS_2

SA_DM0

SA_DM1

SA_DM2

SA_DM3

SA_DM4

SA_DM5

SA_DM6

SA_DM7

SA_DQS0

SA_DQS1

SA_DQS2

SA_DQS3

SA_DQS4

SA_DQS5

SA_DQS6

SA_DQS7

SA_DQS0#

SA_DQS1#

SA_DQS2#

SA_DQS3#

SA_DQS4#

SA_DQS5#

SA_DQS6#

SA_DQS7#

SA_MA0

SA_MA1

SA_MA2

SA_MA3

SA_MA4

SA_MA5

SA_MA6

SA_MA7

SA_MA8

SA_MA9

SA_MA10

SA_MA11

SA_MA12

SA_MA13

SA_CAS#

SA_RAS#

SA_RCVENINB

SA_WEB

SB_BS_0

SB_BS_1

SB_BS_2

SB_MA0

SB_MA1

SB_MA2

SB_MA3

SB_MA4

SB_MA5

SB_MA6

SB_MA7

SB_MA8

SB_MA9

SB_MA10

SB_MA11

SB_MA12

SB_MA13

AK12

AH11

AG17

AB30

AL31

AF30

AK26

AL9

AG7

AK5

AH3

AC28

AJ30

AK33

AL25

AN9

AH8

AM2

AE3

AC29

AK30

AJ33

AM25

AN8

AJ8

AM3

AE2

AJ15

AM17

AM15

AH15

AK15

AN15

AJ18

AF19

AN17

AL17

AG16

AL18

AG18

AL14

AJ17

AK18

AN28

AM28

AH17

AH21

AJ20

AE27

AN20

AL21

AK21

AK22

AL22

AH22

AG22

AF21

AM21

AE21

AL20

AE22

AE26

AE20

M_A_DM0

M_A_DM1

M_A_DM2

M_A_DM3

M_A_DM4

M_A_DM5

M_A_DM6

M_A_DM7

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

M_A_DQS#0

M_A_DQS#1

M_A_DQS#2

M_A_DQS#3

M_A_DQS#4

M_A_DQS#5

M_A_DQS#6

M_A_DQS#7

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_BS0 17

M_A_BS1 17

M_A_DM[7..0]

M_A_DQS[7..0]

M_A_DQS#[7..0]

M_A_A[13..0]

1

T38

1

T39

M_A_BS2 17

M_A_DM[7..0] 17

M_A_DQS[7..0] 17

M_A_DQS#[7..0] 17

M_A_A[13..0] 17

M_A_CAS# 17

M_A_RAS# 17

M_A_WE# 17

1.05VDDM

1.5VDDM

3VDDM

R317

1KΩ 5% 1/16W SMT0402 LR(NU)

Low: Normal

High:Lanes reversed(945GMS

not support)

B B

First International Computer, Inc.

A A

10

9

8

7

6

5

4

1.05VDDM8,9,11,14,16,19,21,45

1.5VDDM9,12,14,18,21,27,28,45

3VDDM10,12,14,16,17,18,19,20,21,22,23,24,25,27,28,29,31,32,33,36,38,39,43,44

1.05VDDM

1.5VDDM

3VDDM

3

Title

Size Document Number Rev

C

Date: Sheet

2FL.,NO.300,Yang Guang St.,NeiHu

114 TAIPEI, TAIWAN ,ROC

(886-2)8751-8751

CW0A0

945GMS DDR2 (3/5)

2

13 47Thursday, June 26, 2008

1

0.1

of

10

9

8

7

6

5

4

3

2

1

H H

1.5VDDM

30mils

G G

F F

E E

1.5VDDM

D D

C C

2.5VDDM

B B

120Ω±25% 100MHz 2500mA SMT0603 MLB-160808-0120P- N2 MAG.LAYERS LR

0.1uf caps in 1.5VDDM_xPLL

need to be located as edge caps

within 200mils

L17

INDUCTOR 10µH ±10% GLF2012T100KT TDK LR

L20

INDUCTOR 10µH ±10% GLF2012T100KT TDK LR

L53

120Ω±25% 100MHz 2500mA SMT0603 MLB-160808-0120P- N2 MAG.LAYERS LR

L52

120Ω±25% 100MHz 2500mA SMT0603 MLB-160808-0120P- N2 MAG.LAYERS LR

+

T100uF 2V ±20% ESR=18mΩ SMT7343 EEFCD0D101ER PANASONIC LR

+

T100uF 2V ±20% ESR=18mΩ SMT7343 EEFCD0D101ER PANASONIC LR

Close to GMCH

L21

82nH ±5% 300mA SMT0603 CLH1608T-82NJ-N CHILISIN LR

L22

INDUCTOR 1µH ±20% GLF2012T1R0MT TDK LR

20mils

10Ω 1% 1/10W SMT0603 LR

C494

C492

10uF 6.3V ±20% SMT0805 X5R CM21X5R106M06AT AVX /CYOCERA LR

+

P-CAP (SP-CAP) 220uF 2V -35 to +10% 9mΩ SMT7343 EEFSX0D221EY PANASONIC LR

DN4 DIODE STKY BAT54C 30V 200mA SOT-23 3PIN PHILIPS LR

12

3

R578

L15

(70mA)

C249

0.1uF 10V ±10% SMT0402 X5 R LR

C218

C491

C495

0.1uF 10V ±10% SMT0402 X5 R LR

C459

C455

0.1uF 10V ±10% SMT0402 X 5R LR

10uF 6.3V ±20% SMT0805 X5R CM21X5R106M06AT AVX/ CYOCERA LR

C458

0.1uF 10V ±10% SMT0402 X 5R LR

C454

10uF 6.3V ±20% SMT0805 X5R CM21X5R106M06AT AVX/ CYOCERA LR

Used in 1.5VDDM_PCIE should

be on top layer

C493

10uF 6.3V ±20% SMT0805 X5R CM21X5R106M06AT AVX /CYOCERA LR

10mils

20mils

(40mA)

(40mA)

(45mA)

(45mA)

>60mils(1500mA)

10mils

1.5VDDM_DPLLA

10mils

1.5VDDM_DPLLB

10mils

1.5VDDM_HPLL

10mils

1.5VDDM_M PLL

1.5VDDM_PCIE

1.5VDDM_3GP LL

10uf caps used in

1.5VDDM_3GPLL should be

placed in cavity

1.05VDDM

2.5VDDM_CRTDAC

C219

10uF 6.3V ±20% SMT0805X5R CM21X5R106M06AT AV X/CYOCERA LR

Via:5A

1.05VDDM

200mils

C229

T 220uF 2.5V ±20% ESR=15mΩ SMT7343 2R5TPE220MF SANYO LR

1.05VDDM

+

T100uF 2V ±20% ESR=18mΩ SMT7343 EEFCD0D101ER PANASONIC LR

C169

C213

C205

C204

C159

MO-CAP 4.7uF 10V 10% SMT0603 X5R H=0.8mm LMK107BJ475KA-T TA IYO LR

10uF 6.3V ±20% SMT0805 X5R CM21X5R106M06AT AVX /CYOCERA LR

T 220uF 2.5V ±20% ESR=15mΩ SMT7343 2R5TPE220MF SANYO L R

C153

C157

MO-CAP 4.7uF 10V 10% SMT0603 X5R H=0.8mm LMK107BJ475KA-T TAI YO LR

C230

C214

0.1uF 10V ±10% SMT0402 X5 R LR

0.1uF 10V ±10% SMT0402 X 5R LR

0.1uF 10V ±10% SMT0402 X5 R LR

MO-CAP 4.7uF 10V 10% SMT0603 X5R H=0.8mm LMK107BJ475KA-T TA IYO LR

1.5VDDM

C171

MO-CAP 4.7uF 10V 10% SMT0603 X5R H=0.8mm LMK107BJ475KA-T TA IYO LR

MO-CAP 0.47UF 6.3V 10% SMT0402 X5R LR

C460

MO-CAP 0.47UF 6.3V 10% SMT0402 X5R LR

C209

0.1uF 10V ±10% SMT0402 X5 R LR

C486

MO-CAP 0.47UF 6.3V 10% SMT0402 X5R LR

C480

C461

MO-CAP 0.47UF 6.3V 10% SMT0402 X5R LR

AD33

AD32

AD31

AD30

AD29

AD28

AD27

AC27

AD26

AC26

AB26

AE19

AE18

AF17

AE17

AF16

AE16

AF15

AE15

R26

P26

N26

M26

V19

U19

W18

V18

R18

W17

U17

R17

W16

V16

R16

V15

U15

H10

AE9

AD9

AD8

AD7

AD6

A14

D10

AA1

T26

T19

T18

T16

T15

J14

J10

U9

P9

L9

D9

P8

L8

D8

P7

L7

D7

A7

P6

L6

G6

D6

U5

P5

L5

G5

D5

Y4

U4

P4

L4

G4

D4

Y3

U3

P3

L3

G3

D3

Y2

U2

P2

L2

G2

D2

F1

U39D

VCC0

VCC1

VCC2

VCC3

VCC4

VCC5

VCC6

VCC7

VCC8

VCC9

VCC10

VCC11

VCC12

VCC13

VCC14

VCC15

VCC16

VCC17

VCC18

VCC19

VCC20

VCC21

VCC_AUX1

VCC_AUX2

VCC_AUX3

VCC_AUX4

VCC_AUX5

VCC_AUX6

VCC_AUX7

VCC_AUX8

VCC_AUX9

VCC_AUX10

VCC_AUX11

VCC_AUX12

VCC_AUX13

VCC_AUX14

VCC_AUX15

VCC_AUX16

VCC_AUX17

VCC_AUX18

VCC_AUX19

VCC_AUX20

VCC_AUX21

VCC_AUX22

VCC_AUX23

VCC_AUX24

VCC_AUX25

VCC_AUX26

VCC_AUX27

VCC_AUX28

VTT0

VTT1

VTT2

VTT3

VTT4

VTT5

VTT6

VTT7

VTT8

VTT9

VTT10

VTT11

VTT12

VTT13

VTT14

VTT15

VTT16

VTT17

VTT18

VTT19

VTT20

VTT21

VTT22

VTT23

VTT24

VTT25

VTT26

VTT27

VTT28

VTT29

VTT30

VTT31

VTT32

VTT33

VTT34

VTT36

VTT35

VTT37

VTT38

VTT39

VTT40

945GMS

VCCA_TVDACA0

VCCA_TVDACA1

VCCA_TVDACB0

VCCA_TVDACB1

VCCA_TVDACC0

VCCA_TVDACC1

VCCA_TVBG

VSSA_TVBG

VCCD_TVDAC

VCCDQ_TVDAC

VCCD_LVDS0

VCCD_LVDS1

VCCD_LVDS2

VCCHV0

VCCHV1

VCCHV2

VCCSM0

VCCSM1

VCCSM2

VCCSM3

VCCSM4

VCCSM5

VCCSM6

VCCSM7

VCCSM8

VCCSM9

VCCSM10

VCCSM11

VCCSM12

VCCSM13

VCCSM14

VCCSM15

VCCSM16

VCCSM17

VCCSM18

VCCSM19

VCCSM20

VCCSM21

VCCSM22

VCCSM23

VCCSM24

VCCSM25

VCCSM26

VCCSM27

VCCSM28

VCCSM29

VCCSM30

VCCSM31

VCCSM32

VCCSM33

VCCSM34

VCCSM35

VCCSM36

VCCSM37

VCCSM38

VCCSM39

VCCSM40

VCCSM41

VCCSM42

VCCSM43

VCCSM44

VCCSM45

VCCSM46

VCCSM47

VCCSM48

VCCSM49

VCCSM50

VCCSM51

VCCA_MPLL

VCCA_HPLL

VCCA_DPLLA

POWER

VCCA_DPLLB

VCCD_HMPLL1