Page 1

5

4

3

2

1

255KIX

01

COVER PAGE

02

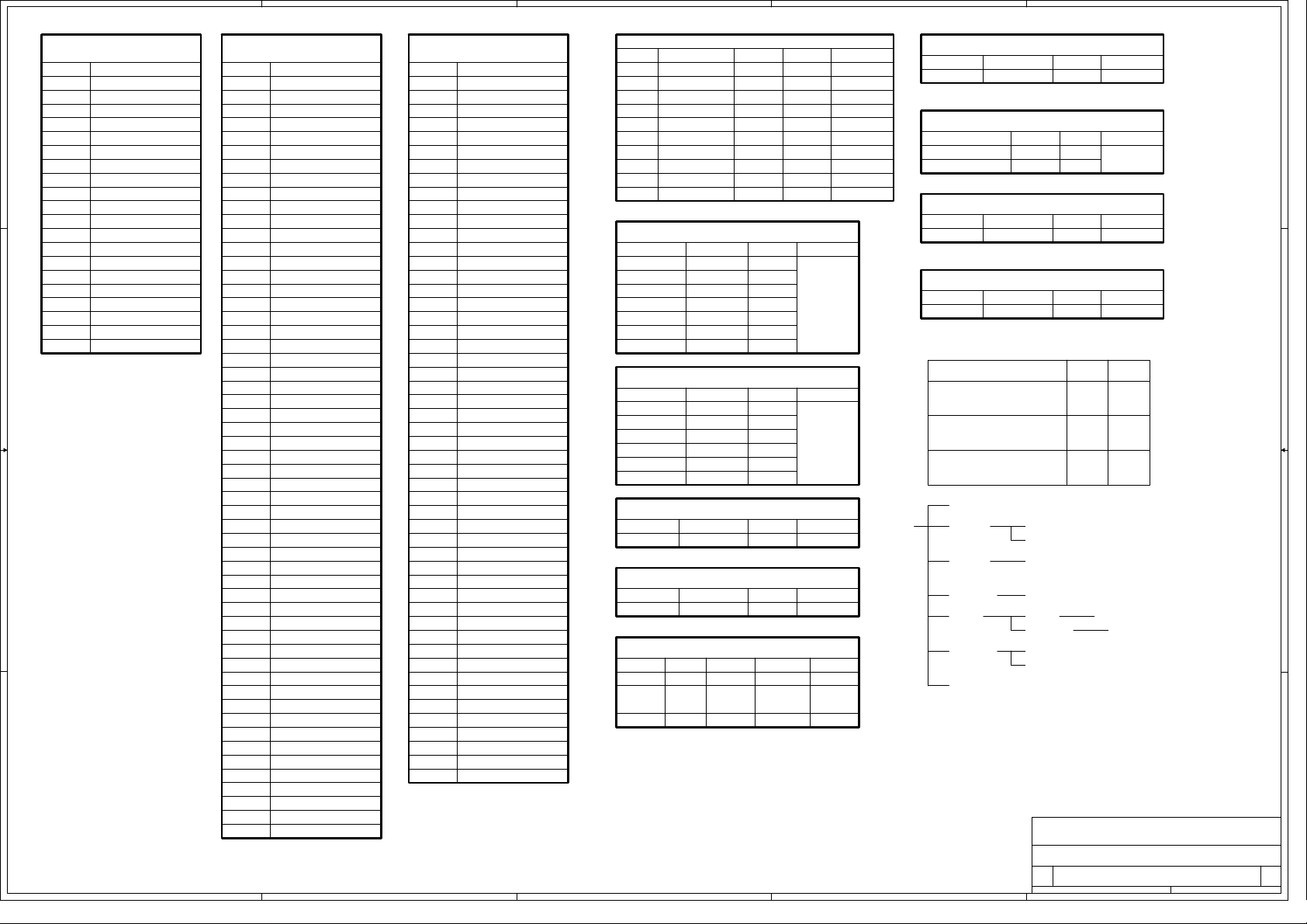

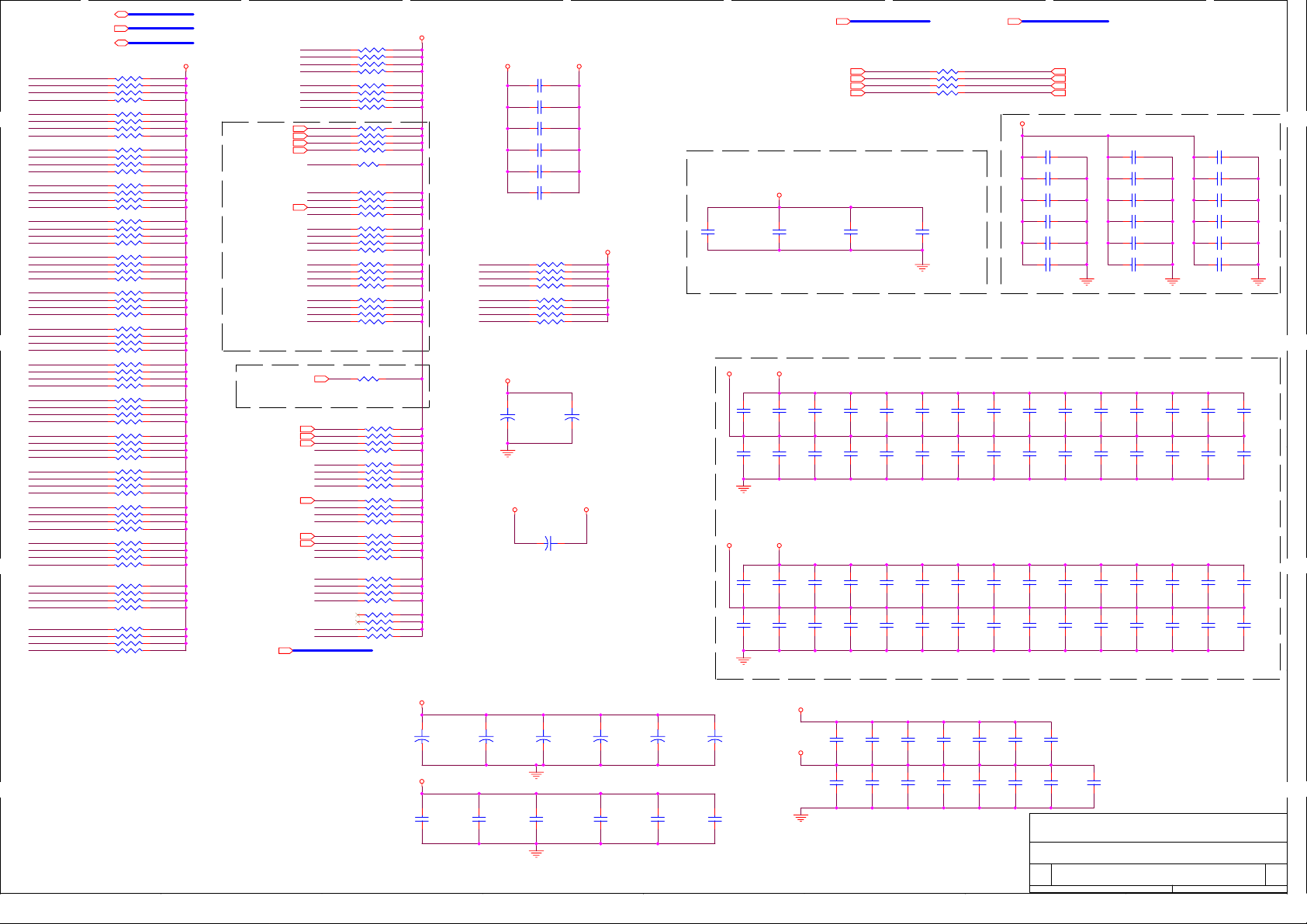

GPIO DEFINITION & POWER CONSUMPTION

03

D D

C C

B B

A A

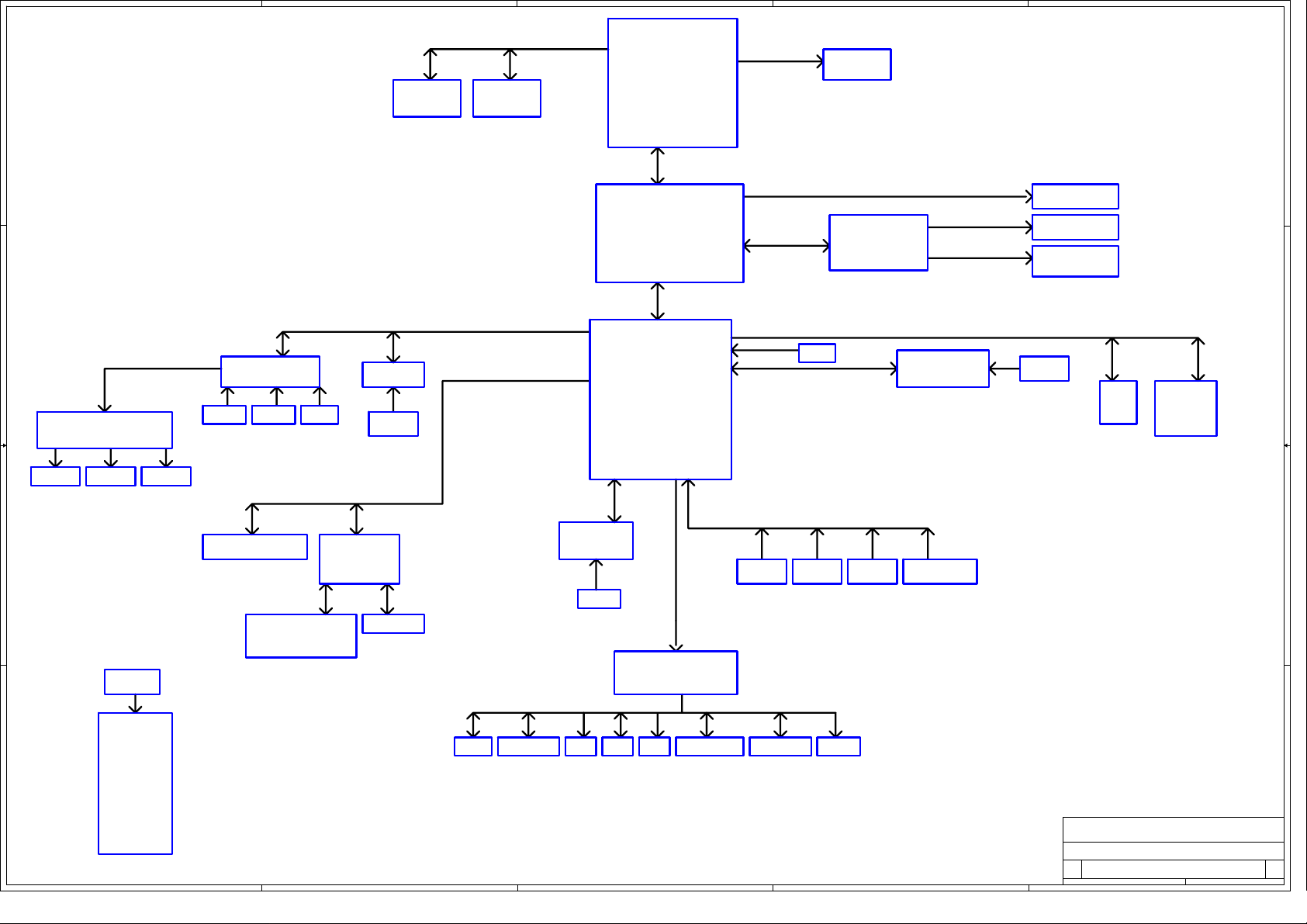

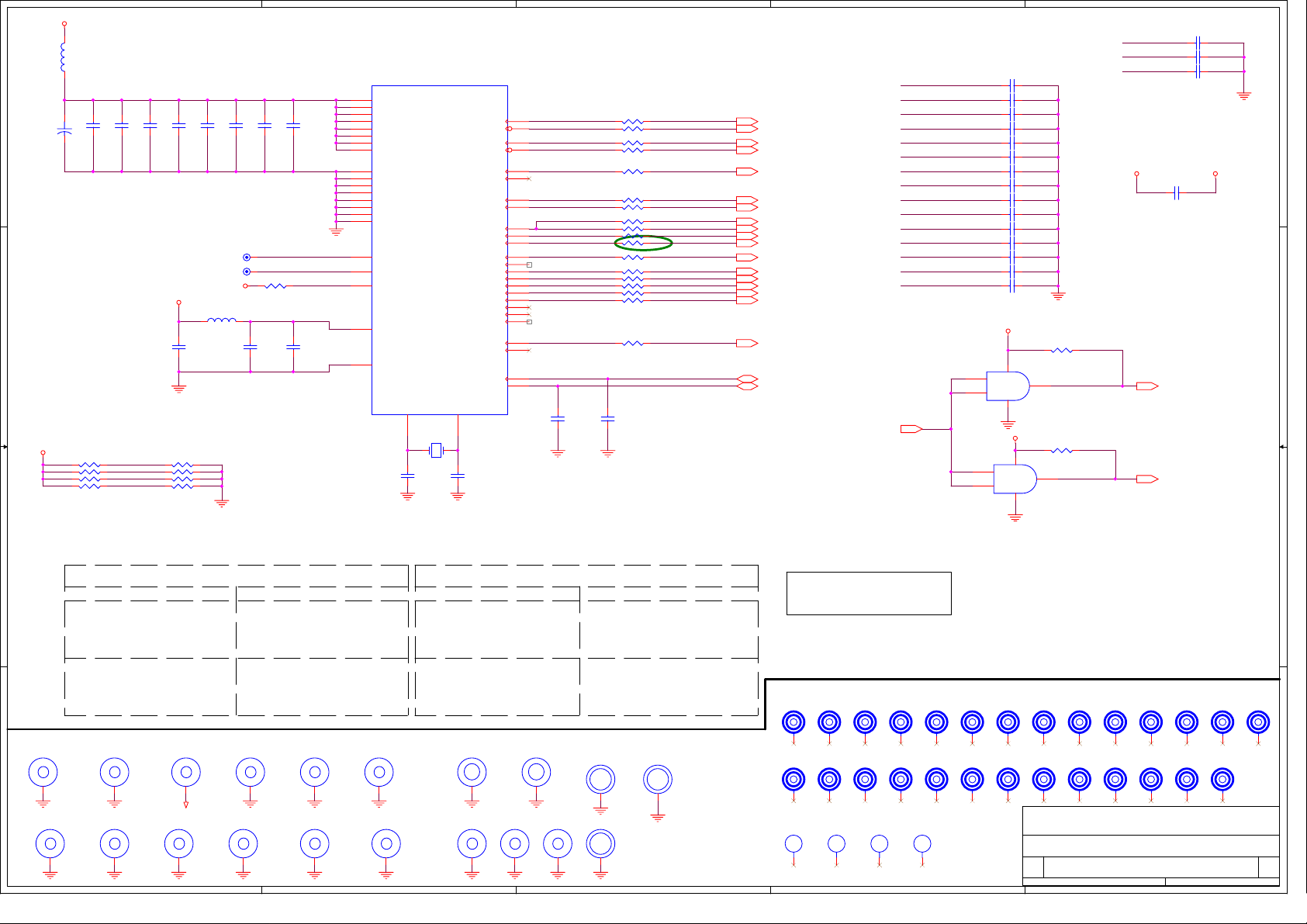

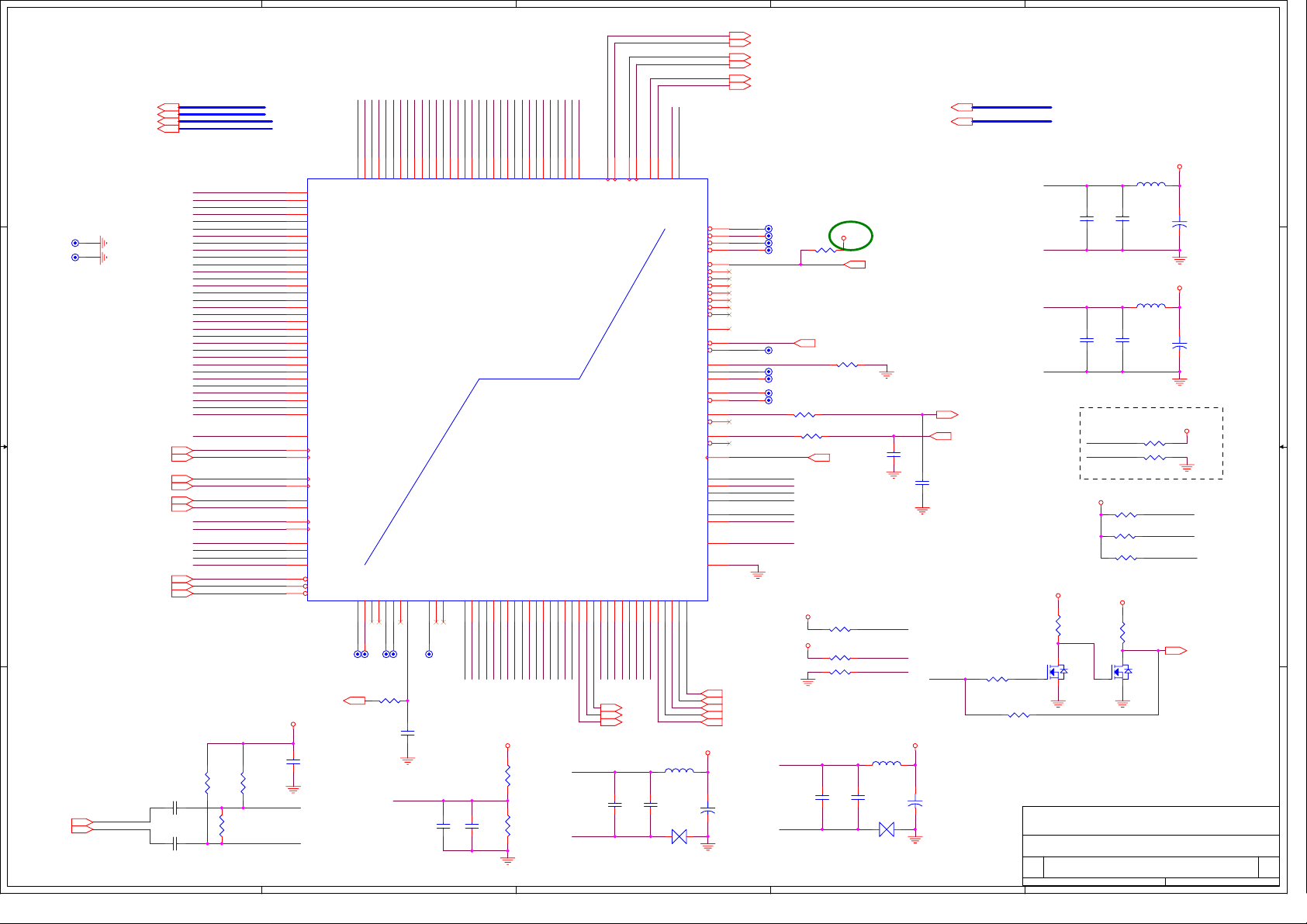

BLOCK DIAGRAM

04

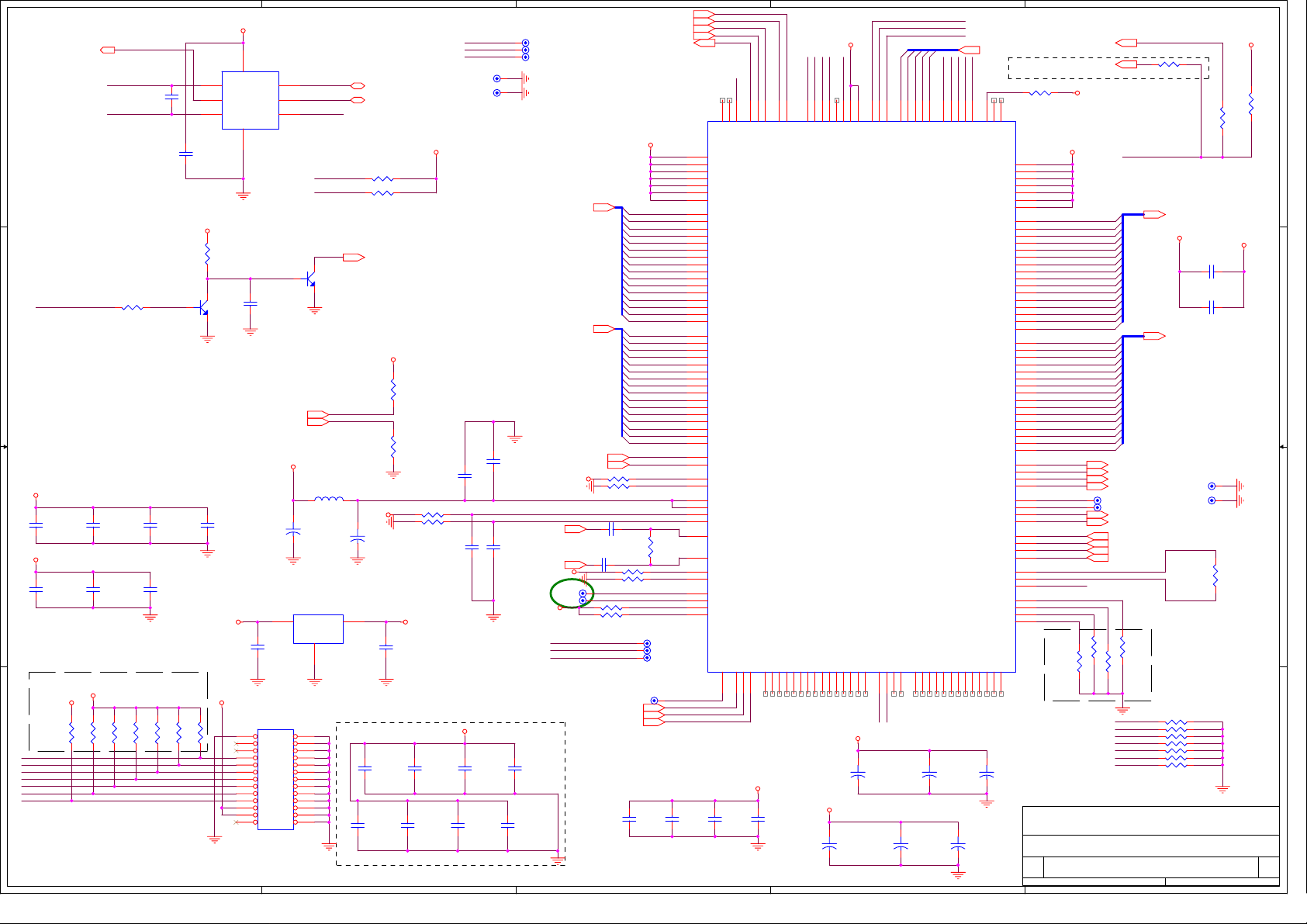

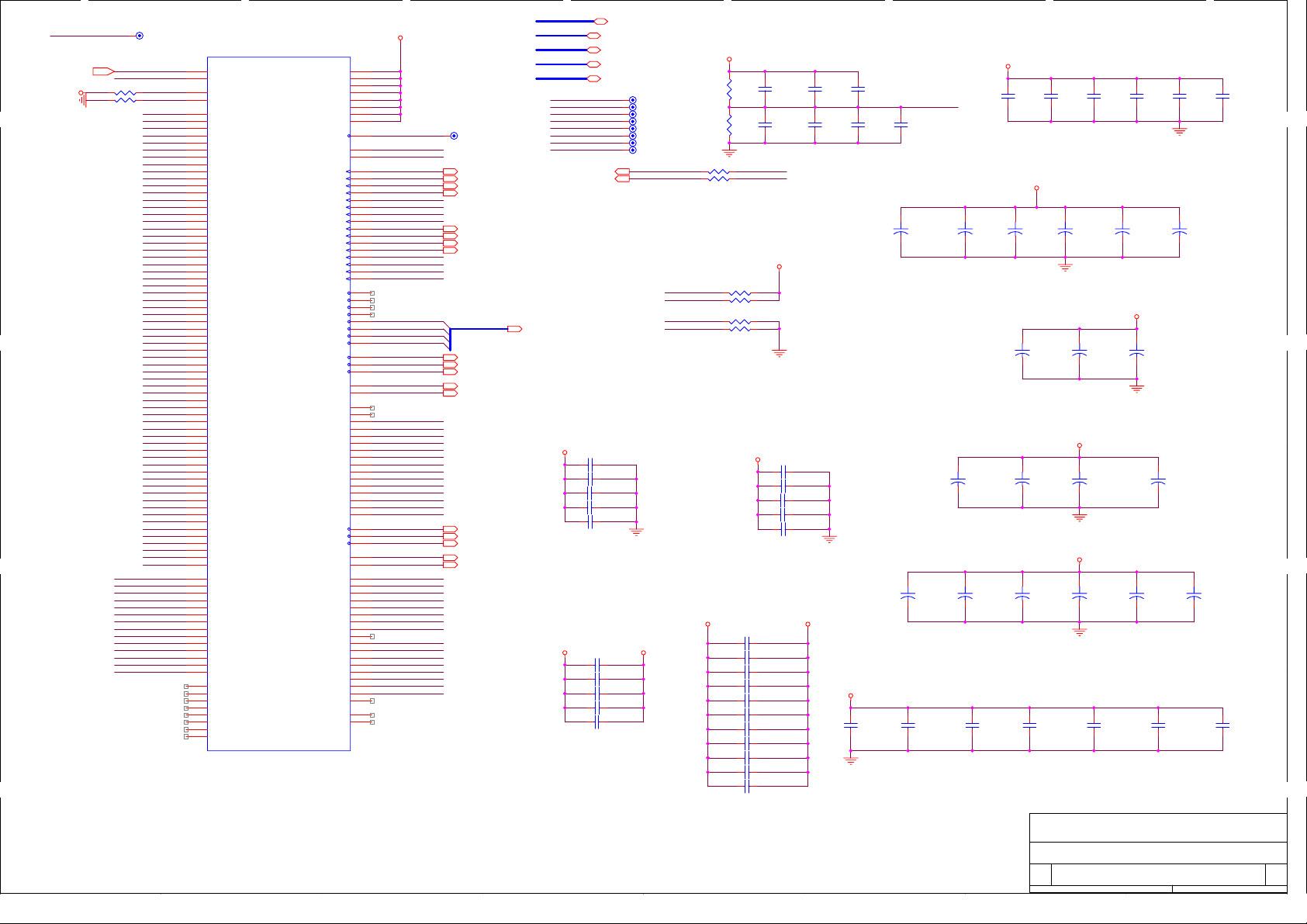

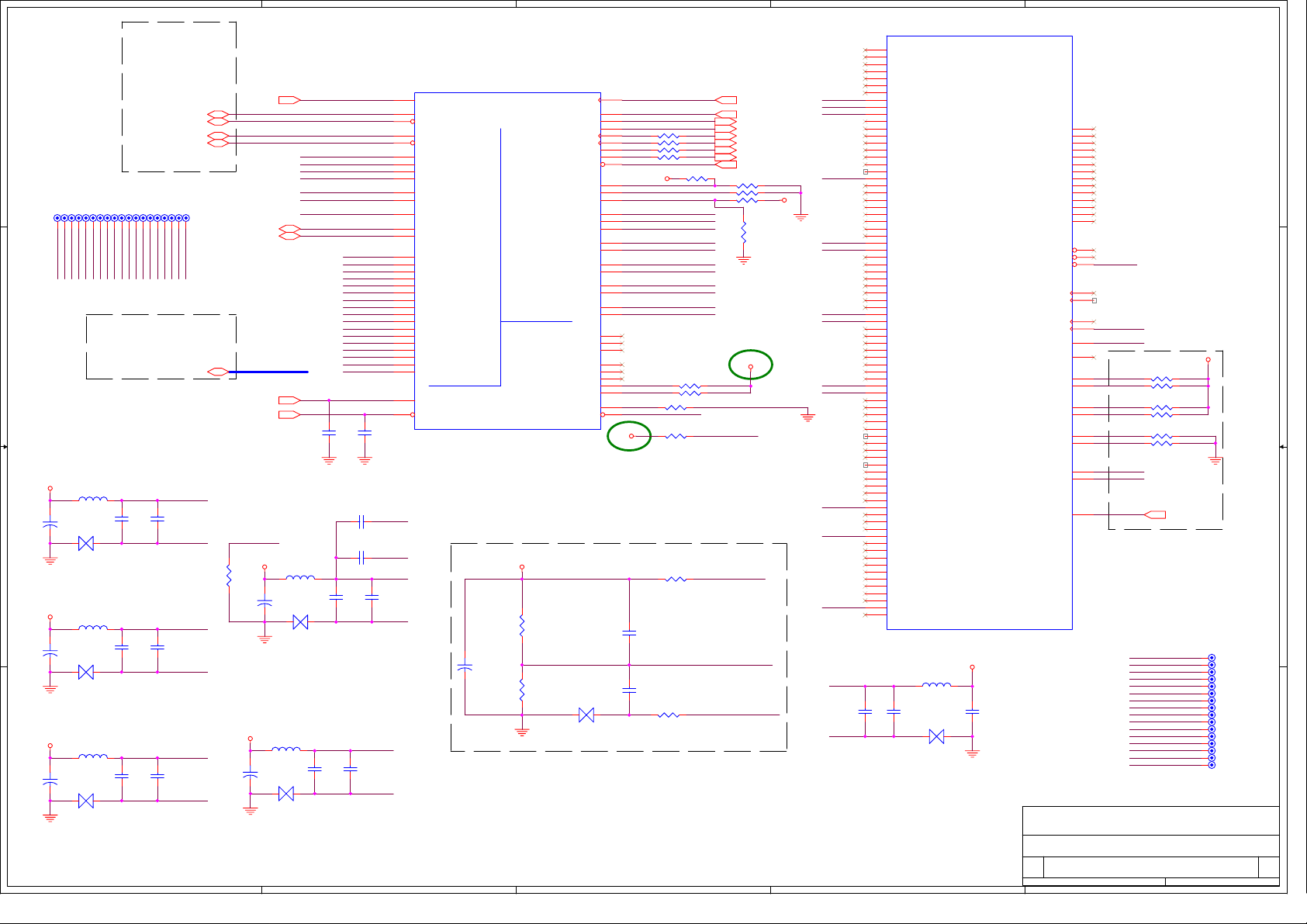

CPU-ATHLON64-HT

05

CPU-ATHLON64-DDR

06

CPU-ATHLON64-PWR & GND

07

MAIN CLOCK & PCB HOLE

08

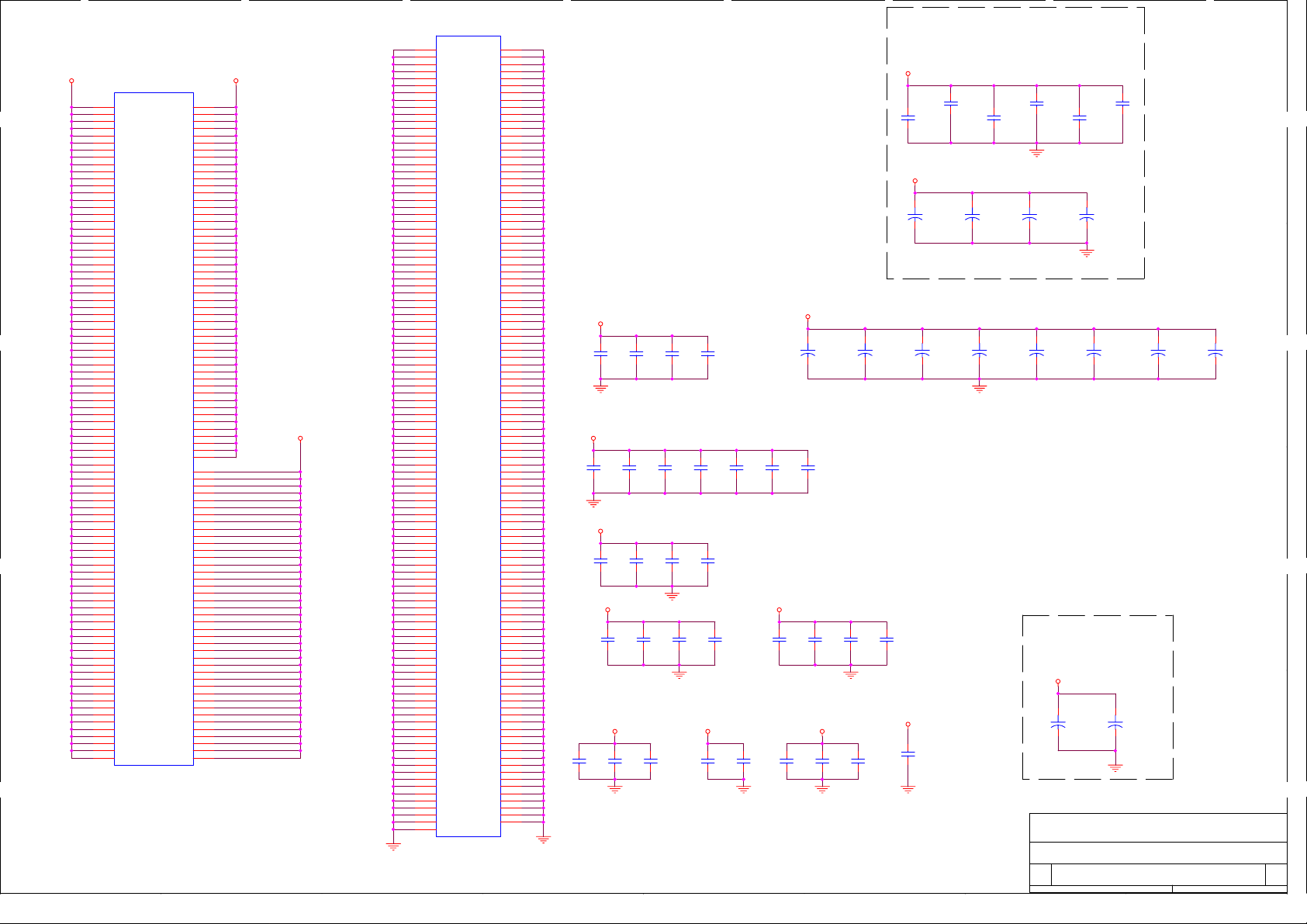

DDR CONN

09

DDR PULL UP TERMINATION

10

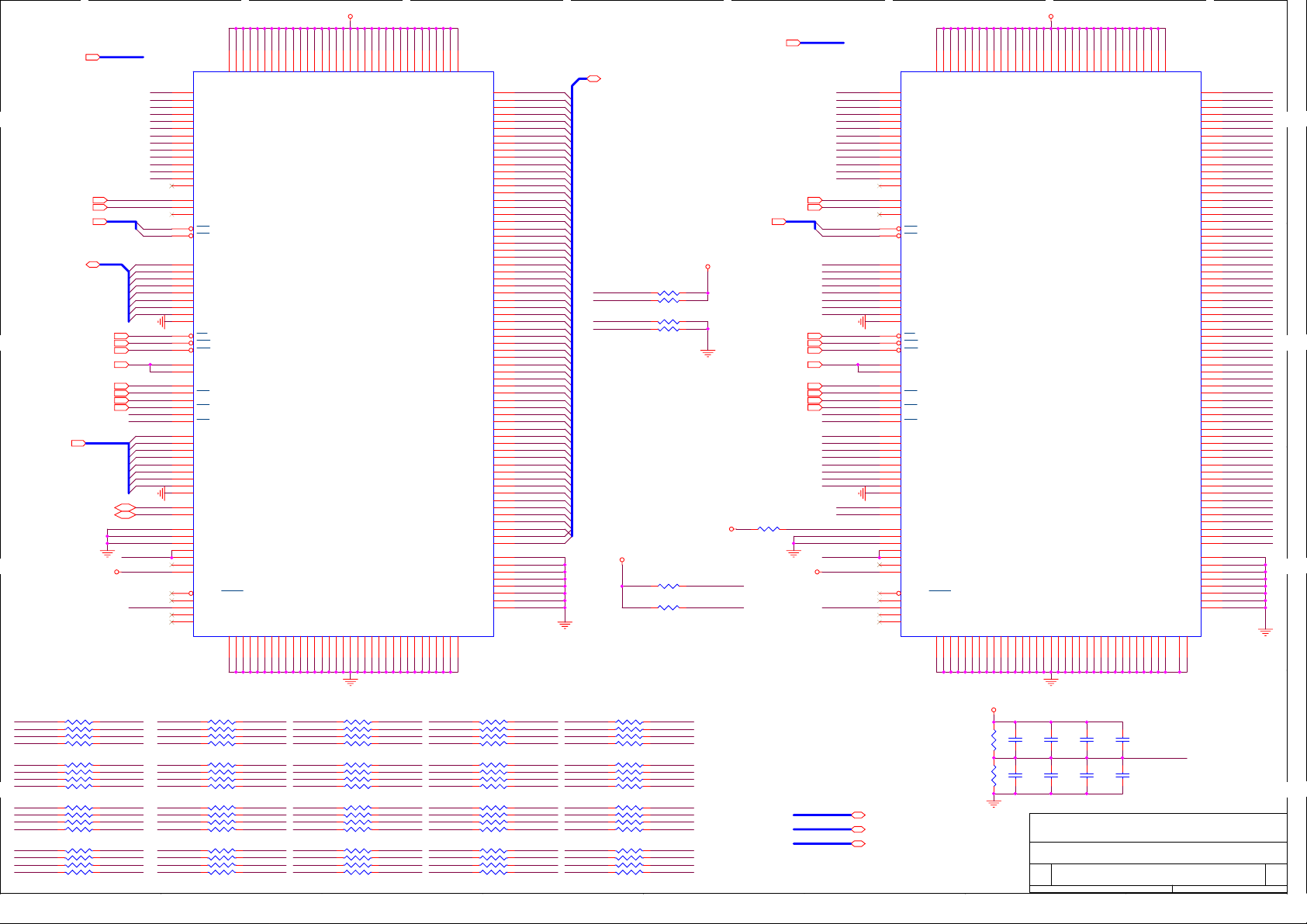

SIS760 HOST& AGP BUS

11

SIS760 MUTIOL&HW TRAP

12

SIS755 POWER & GND

13

SIS302LV

14

SIS963L (HYPERZIP & PCI & IDE )

15

SIS963L(HOST,AC97,MII,GPIO)

16

SIS963L(POWER &USB & 1394)

17

HDD & CD-ROM & USB CONN

18

LAN(PHY) & MDC CONN & S/P

19

1394 Controler & MINI_PCI

20

CARDBUS OZ711MC1 & MMC

21

AUDIO & AMP & Boonmer

22

IT8510E & BIOS & T/P & SW

23

LVDS & INVERTER & CRT

24

FAN & TV & 2nd AUDIO &HALL

25

VCC SWITCH&BATT CONTROL

26

CPUCORE_MAX1937

27

+1.2V & VCORE STOP-DOWN

28

+1.25V & +1.8V & +2.5V

29

DC-DC 5V/3.3V

30

Charger & Total Power

31

TP BOARD

32

LAN BOARD

33

USB BOARD

34

Change Notes B to 01

5

4

3

255KI1 REV:01

PCB P / N ASSY P/N

MB ID1

MB ID3

USB

HDD

LAN

T/P

LED ID1

SW ID1

37-UH0000-01

37-UH0003-01

35-UG5020-00A

35-UG5070-00A

35-UG5030-00C

35-UG5010-00B

35-UG5040-01

35-UG5000-00B

LED ID3

SW ID3

35-UG5000-00C 80-UG5001-00C

MADE IN TAIWAN / RD1-HW3

UNIWILL COMPUTER CORP.

Title

COVER PAGE

Size Document Number Rev

2756

Date: Sheet

2

255KIX

82-UH0000-01

82-UH0003-01

80-UG5020-00A

80-UG5070-00A

80-UG5030-00C

80-UG5010-00B

80-UG5040-01

80-UG5000-00B

80-UG5041-0135-UG5040-01

134Tuesday, August 10, 2004

1

01

of

Page 2

5

4

3

2

1

SIS963L

GPIO0

GPIO1

GPIO2

GPIO3

D D

GPIO4

GPIO5

GPIO6

GPIO7

GPIO8

GPIO9

GPIO10

GPIO11

GPIO12

GPIO13

GPIO14

GPIO15

GPIO16

GPIO17

GPIO18

GPIO19

C C

GPIO20

B B

A A

GPIO

NC

NC

SB_THROTTLING#

EXTSMI#

CLKRUN#

HDDCDROM_RST#

NC

NC

PNLSW2

PNLSW0

PNLSW1

NC

NC

NC

S3AUXSW#

NC

NC

NC

NC

SMBCLK

SMBDAT

5

IT8510E

GPA0

GPA1

GPA2

GPA3

GPA4

GPIO

BTL_BEEP

NC

NC

NC

NC

GPA5 NC

GPA6

GPA7

GPB0

GPB1

GPB2

GPB3

GPB4

GPB5

GPB6

GPB7

GPC0

GPC1

GPC2

GPC3

GPC4

GPC5

GPC6

GPC7

GPD0

GPD1

GPD2

GPD3

IOPD4

IOPD5

GPD6

GPD7

GPE0

GPE1

GPE2

GPE3

GPE4

GPE5

GPE6

GPE7

GPCF0

GPCF1

GPCF2

GPCF3

GPCF4

GPCF5

GPCF6

GPCF7

GPH0

GPH1

GPH2

GPH3

GPH4

GPH5

GPH6

GPH7

SMP1_EN#

PWRBTN#

SUS_SKIP

IDE_LED#

NC

BAT_SMBCLK

BAT_SMBDATA

NC

NC

RF LED#

PWROK1

SMBCLK1

SMBDAT1

NC

NC

NC

CHG_ON

NC

AC_IN

USERSW

PCIRST#

EXTSMI#

PSON#

THROTTLING#

NC

FAN_SPEED#

NC

NC

NC

NC

PWRSW

LID#

RF_OFF#

S3AUXSW#

CS

WR

DA

LCM_BKL

TP_CLK

TP_DATA

E_MAIL#

WWW#

+2.5VS_ON

+2.5V_ON

+1.8V_ON

+1.8VS_ON

+5V_ON

+3VS_ON

+1.2V_ON

CORE_ON

GPI0

GPI1

GPI2

GPI3

GPI4

GPI5

GPI6

ADC0

ADC1

ADC2

ADC3

ADC4

ADC5

ADC6

ADC7

ADC8

ADC9

DA0

DA1

DA2

DA3

IT8510E

GPIO

SCROLED#

CAPLED#

NUMLED#

CHG_LED#

NC

SUS_LED#

PWR_LED#

BATT_IN

ADAPTOR_I

I_CPU

V_CPU

NC

NC

NC

NC

NC

NC

BRIGHTADJ

CHG_I

FAN_CTRL0

NC

1.525

CPU

W

CPU CORE(V)ICC(mA) TEMP( )

2.0G

1.5252.2G

2.26G

2.4G

2.5G

2.53G

2.6G

2.66G

2.8G

3.06G

1.525

1.525

1.525

1.525

1.525

1.525

1.525

1.525

SIS760

VCC TEMP( )

+3V

+1.2V 88 0.1056

+1.8V

AGPVDD

+1.5V

ICC(mA)

100.2 0.4575

2208.2

401.7

2.1261

0.5107

W

SIS963L

VCC

+3V

+1.8V

+1.8V_AUX

+3V_AUX

RTCVDD

VTT(+1.8V)

ICC(mA)

96

487

27

275

0.003

15

W

0.315

0.876

0.049

0.909

0.00001

0.027

TEMP( )

IT8510E

TEMP( )

+3V

ICC(mA)VCC

W

70

70

701300

℃

+3V

+3V(DVDD) 70

+3V(AMPVDD) 36 0.118

VCC

+3V

℃

VCC

+3V

+5VS

℃

℃

+3VS

+2.5V_DDR

+5V

+3V

+1.8V

+1.2V

+3V_AUX ON

+1.8V_AUX

CPU_CORE

45A

VIN

+3V_AUX

6A

+5V_AUX

6A

RTL8201CL

ICC(mA)VCC

VT1612A

ICC(mA)

71

ADM1032

OZ711MC1

ICC(mA)

30

+1.8VS

+1.25_DDR

+12V

+2.5V

+1.5V

+5V_AUXON+12V_AUX

+3V

+3VS

+5V

W

WVCC

0.234

WICC

0.56mW

W

0.1

S3

OFF

ON

TEMP( )

℃

700.66200

TEMP( )

℃

TEMP( )

℃

150170uA

TEMP( )

℃

70

S5

OFF

OFF

CLOCK GENERATOR

ICC(mA)VCC W

180+3V

0.594

TEMP( )

℃

70

DEVICE ID

DEVICE

PCMCIA INT#B

4

IDSEL

AD17

1394 PREQ#2

MINI

AD22

PCI

REQ

PREQ#1

AD20 PREQ#0

3

GNT#

PGNT#2

PGNT#1

PGNT#0

INT

INT#D

INT#B

INT#D

2

100mA

6A

6A

+12V_AUX

+2.5V

+1.8V_AUX

+1.5V

+12V

+2.5V

+2.5V_DDR +1.25V_DDR

+1.8V

+1.8VS

0.8A

+1.2V

1.5A

UNIWILL COMPUTER CORP.

Title

GPIO DEFINITION & POWER CONSUMPTION

Size Document Number Rev

2756

Date: Sheet

255KIX

234Tuesday, August 10, 2004

1

of

01

Page 3

5

4

3

2

1

DDR RAM BUS

DDR 1

D D

DDR 2

CPU

AMD ATHLON 64

Socket 754

THERMAL

ADM 1032

255KI1

BLOCK DIAGRAM

HyperTransport I/O BUS

North Bridge

SIS

760

VL BUS

SIS302LV

Video Bridge

CRT

S-Video TV

LCD

Mutiol BUS

C C

AMPLIFIER

TI

TPA6011A4

AUDIO CODEC

VT1612A

MICLINE INLINE IN

MDC

RJ-11

AC Link

PCI BUS

South Bridge

SIS

963L

RTC

IDE BUS

LAN(PHY)

REALTEK

RTL8201CL

RJ-45

HDD

2.5"

PRIMARY

MASTER

CD-ROM

DVD

CD-RW

COMBO

SECONDARY

MASTER

L-SPKR SPDIFR-SPKR

IEEE-1394

B B

Mini PCI

CARD READER

CARDBUS

O2 MICRE

OZ711MC1

PCMCIA

MMC/SD/MS/MS Pro

CRYSTAL

14.318MHz

BIOS LED

Clock Gen

A A

ICS

ICS952802

5

4

INT K/B

TI

TSB43AB22A

1394

T/P

LPC BUS

K/B CONTROLLER

ITE

IT8510E

FAN

3

USB2USB0 USB1

BATTERYCHARGER

DC/DC

Bluetooth

2

Title

Size Document Number Rev

Date: Sheet

UNIWILL COMPUTER CORP.

BLOCK DIAGRAM

2756

255KIX

1

334Tuesday, August 10, 2004

of

01

Page 4

5

+3V

THERM#[24]

THERMDA_CPU SMBDAT_THM

C502

2200p X7R

+2.5V

R1 *680

THERMDC_CPU

C507

0.22u/6.3V_0603

C337

0.22u/6.3V_0603

R2 *680

R3 *680

R211

1K

N.C.

R4 *680

Z0417THERMTRIP_CPU_L_EC

C287

0.22u/6.3V_0603

C332

0.22u/6.3V_0603

R5 *680

C523

0.1u

B

R6 *680

D D

C C

+1.25V_DDR

C277

0.22u/6.3V_0603

+2.5V_DDR

B B

C346

0.22u/6.3V_0603

+2.5V

DBREQ_L#

DBRDY

TCK

TMS

A A

TDI

TRST_L

TDO

HDT Connectors

5

2

4

3

+2.5V

R205

100K

Q21

2N3904

E C

C496

0.22u/6.3V_0603

+2.5V

R7 *680

U8

D+

THERM#

D-

1

ADATA

VDD

SCLK

ALERT

GND

ADM1032

5

Z0416

C534

1u_0603

VCORE_SENSE[26]

VSS_SENSE[26]

C363

1u_0603

CN11

12

34

56

78

910

11 12

13 14

15 16

17 18

19 20

21 22

23 24

25 26

*HDT CONNECTOR

ASP-68200-07

7

SMBCLK_THM

8

ALERT

6

ALERT

THERM#

Q19

B

2N3904

E C

+2.5V_CPU

L36

100nH

C344

+

150u/6.3V_SMT

SE-4A

U5

AME8800DEFT

C E

VIN VOUT

GND

B

VCORE_SENSE

VSS_SENSE

eight high frequncy cap. must close CPU side.

4

SMBDAT_THM [22]

SMBCLK_THM [22]

R207 4.7K

R190 4.7K

AUX_OFF# [29]

CPU_CORE

+1.2V

C347

+

4.7u/10V_0805

+2.5V/300mA

+2.5V_CPU

C355

0.1u

C427

0.22u/6.3V_0603

C428

0.22u/6.3V_0603

4

+3V

PR136

10

PR135

10

C339

3300p

X7R

R132 44.2_1%

R133 44.2_1%

+2.5V_CPU+3V

C500

0.22u/6.3V_0603

C499

0.22u/6.3V_0603

LDTSTOP_L

PWROK_CPU

LDTREST#

TP4

TP5

NEAR 760

C343

1000p

+1.2V

C357

0.22u/6.3V_0603

C498

0.22u/6.3V_0603

TP1

TP108

TP3

L0_CADIN_H[0..15][10]

L0_CADIN_L[0..15][10]

C341

0.22u/6.3V_0603

CPUCLK[7]

C351

1000p

CPUCLK#[7]

+2.5V_DDR

01

+2.5V

C390

0.22u/6.3V_0603

C497

0.22u/6.3V_0603

L0_CLKIN1[10]

L0_CLKIN#1[10]

+1.2V

C294 3900p_0603

TP173

TP174

VDDIOFB_H

VDDIOFB_L

VDD_2.5_SENSE

R148 49.9_1%

R151 49.9_1%

C295 3900p_0603

R94 820

R104 820

R199 680

R198 680

VDDIOFB_H[27]

VDDIOFB_L[27]

VDD_2.5_SENSE[27]

3

VCORE_SENSE[26]

VSS_SENSE[26]

LDTREST#[10]

PWROK_CPU[7]

LDTSTOP_L[10]

+1.2V

L0_CADIN_H15

L0_CADIN_H14

L0_CADIN_H13

L0_CADIN_H12

L0_CADIN_H11

L0_CADIN_H10

L0_CADIN_H9

L0_CADIN_H8

L0_CADIN_H7

L0_CADIN_H6

L0_CADIN_H5

L0_CADIN_H4

L0_CADIN_H3

L0_CADIN_H2

L0_CADIN_H1

L0_CADIN_H0

L0_CADIN_L15

L0_CADIN_L14

L0_CADIN_L13

L0_CADIN_L12

L0_CADIN_L11

L0_CADIN_L10

L0_CADIN_L9

L0_CADIN_L8

L0_CADIN_L7

L0_CADIN_L6

L0_CADIN_L5

L0_CADIN_L4

L0_CADIN_L3

L0_CADIN_L2

L0_CADIN_L1

L0_CADIN_L0

Z0401

Z0402

Z0403

Z0404

Z0405

Z0406

R130

169_1%_0603

Z0407

Z0408

Z0409

Z0419

Z0420

Z0410

Z0411 Z0414

TP10

TP2

TP11

TP13

CORE_SENSE

VDDIOFB_H

VDDIOFB_L

VDD_2.5_SENSE

C358

0.1u

3

C501

0.1u

AA27

AB25

AC27

AD25

AB29

AB27

AD29

AD27

AA26

AA25

AC26

AC25

AA29

AB28

AC29

AD28

AH25

AJ25

AF27

AE26

AJ21

AH21

AJ23

AH23

AE24

AF24

W27

W26

W29

W25

U6A

D29

D27

D25

C28

C26

B29

B27

T25

U27

V25

T27

V29

V27

Y29

R25

U26

U25

T28

U29

V28

Y25

R27

R26

C18

A19

VCORE_SENSE

VSS_SENSE

LDTREST#

PWROK_CPU

LDTSTOP_L

TDO

A28

AJ28

A22

TDO

KEY1

KEY0

VLDT0_A6

VLDT0_A5

VLDT0_A4

VLDT0_A3

VLDT0_A2

VLDT0_A1

VLDT0_A0

L0_CADIN_H15

L0_CADIN_H14

L0_CADIN_H13

L0_CADIN_H12

L0_CADIN_H11

L0_CADIN_H10

L0_CADIN_H9

L0_CADIN_H8

L0_CADIN_H7

L0_CADIN_H6

L0_CADIN_H5

L0_CADIN_H4

L0_CADIN_H3

L0_CADIN_H2

L0_CADIN_H1

L0_CADIN_H0

L0_CADIN_L15

L0_CADIN_L14

L0_CADIN_L13

L0_CADIN_L12

L0_CADIN_L11

L0_CADIN_L10

L0_CADIN_L9

L0_CADIN_L8

L0_CADIN_L7

L0_CADIN_L6

L0_CADIN_L5

L0_CADIN_L4

L0_CADIN_L3

L0_CADIN_L2

L0_CADIN_L1

L0_CADIN_L0

L0_CLKIN_H1

L0_CLKIN_L1

L0_CTLIN_H1

L0_CTLIN_L1

VDDA1

VDDA2

L0_REF1

L0_REF0

CLKIN_H

CLKIN_L

NC_AJ23

NC_AH23

NC_AE24

NC_AF24

NC_C18

NC_A19

CORE_SENSE

VDDIOFB_H

B23

AE12

AF12

C446

0.1u

AF20

AE18

AJ27

PWROK

RESET_L

LDTSTOP_L

VDDIOFB_L

VDDIO_SENSE

FREE29

AE11

C1J3R3

+1.2V

C510

0.1u

+1.25V_DDR

TDI

TMS

TCK

TRST_L

DBRDY

A23

A24

COREFB_L

COREFB_H

A21

B21

TDI

E17

TCK

TRST_L

E20

C15

TMS

AG15

AH17

DBRDY

NC_C15

HYPER TRANSPORT - LINK0

FREE31

FREE33

FREE35

FREE1

FREE37

FREE4

FREE38

FREE41

FREE7

FREE11

FREE12

AA2D3AG2

B18

AH1

AE21

C20

AG4C6AG6

+1.2V

+

+1.2V

C529

+

330u/6.3V_LESR

6.3*7

C16

A20

VTT_A5

VTT_B5

THERMTRIP_L

FREE40

FREE13

FREE14

AE9

AG9

C384

150u/6.3V_SMT

SE-4A

2

THERMTRIP_CPU_L

THERMDA_CPU

THERMDC_CPU

VID4

A26

A27

AG13

VID4

THERMDA

THERMDC

NC_AG18

NC_AH18

NC_AG17

NC_AJ18

AG18

AH18

AG17

AJ18

NC_AG17

NC_AJ18

C509

+

2

VID0

VID1

VID3

VID2

AF14

AG14

AF15

AE15

VID3

VID2

VID1

VID0

FREE24

FREE25

FREE27

AE22

C24

A25

C9

C371

+

4.7u/10V_0805

4.7u/10V_0805

NC_D20

NC_C21

NC_D18

D20

C21

D18

NC_D20

NC_C21

NC_D18

L0_CADOUT_H15

L0_CADOUT_H14

L0_CADOUT_H13

L0_CADOUT_H12

L0_CADOUT_H11

L0_CADOUT_H10

L0_CADOUT_H9

L0_CADOUT_H8

L0_CADOUT_H7

L0_CADOUT_H6

L0_CADOUT_H5

L0_CADOUT_H4

L0_CADOUT_H3

L0_CADOUT_H2

L0_CADOUT_H1

L0_CADOUT_H0

L0_CADOUT_L15

L0_CADOUT_L14

L0_CADOUT_L13

L0_CADOUT_L12

L0_CADOUT_L11

L0_CADOUT_L10

L0_CADOUT_L9

L0_CADOUT_L8

L0_CADOUT_L7

L0_CADOUT_L6

L0_CADOUT_L5

L0_CADOUT_L4

L0_CADOUT_L3

L0_CADOUT_L2

L0_CADOUT_L1

L0_CADOUT_L0

L0_CLKOUT_H1

L0_CLKOUT_H0

L0_CTLOUT_H1

L0_CTLOUT_H0

G_FBCLKOUT_H

G_FBCLKOUT_L

FREE10

FREE18

FREE19

FREE42

AG7

+

VID[0..4] [26]

NC_C19

NC_B19

Z0418

C19

B19

AF18

D22

NC_B19

NC_C19

NC_AF18

RSVD_SCL

VLDT0_B6

VLDT0_B5

VLDT0_B4

VLDT0_B3

VLDT0_B2

VLDT0_B1

VLDT0_B0

L0_CLKOUT_L1

L0_CLKOUT_L0

L0_CTLOUT_L1

L0_CTLOUT_L0

L0_CTLIN_L0

L0_CTLIN_H0

L0_CLKIN_L0

L0_CLKIN_H0

DBREQ_L

NC_AF21

NC_AF22

NC_AF23

NC_AE23

FREE28

FREE30

FREE32

FREE34

FREE36

B7C3K1R2AA3F3C23

C386

+

4.7u/10V_0805

C478

4.7u/10V_0805

C22B13

RSVD_SDAFREE26

1

Low active to short

down system.

THERMTRIP_CPU_L_SB[15]

THERMTRIP_CPU_L_EC[22]

R95 680

AH29

AH27

AG28

AG26

AF29

AE28

AF25

N26

L25

L26

J25

G25

G26

E25

E26

N29

M28

L29

K28

H28

G29

F28

E29

N27

M25

L27

K25

H25

G27

F25

E27

P29

M27

M29

K27

H27

H29

F27

F29

J26

J27

J29

K29

N25

P25

P28

P27

L0_CTLIN#0

R29

L0_CTLIN0

T29

L0_CLKIN#0

Y28

L0_CLKIN0

Y27

AH19

AJ19

DBREQ_L#

AE19

Z0412

AF21

Z0413

AF22

AF23

Z0415

AE23

+1.2V

L0_CADOUT_H15

L0_CADOUT_H14

L0_CADOUT_H13

L0_CADOUT_H12

L0_CADOUT_H11

L0_CADOUT_H10

L0_CADOUT_H9

L0_CADOUT_H8

L0_CADOUT_H7

L0_CADOUT_H6

L0_CADOUT_H5

L0_CADOUT_H4

L0_CADOUT_H3

L0_CADOUT_H2

L0_CADOUT_H1

L0_CADOUT_H0

L0_CADOUT_L15

L0_CADOUT_L14

L0_CADOUT_L13

L0_CADOUT_L12

L0_CADOUT_L11

L0_CADOUT_L10

L0_CADOUT_L9

L0_CADOUT_L8

L0_CADOUT_L7

L0_CADOUT_L6

L0_CADOUT_L5

L0_CADOUT_L4

L0_CADOUT_L3

L0_CADOUT_L2

L0_CADOUT_L1

L0_CADOUT_L0

L0_CTLOUT1

L0_CTLOUT#1

R102 820

+2.5V_DDR

L0_CLKOUT1 [10]

L0_CLKOUT#1 [10]

L0_CLKOUT0 [10]

L0_CLKOUT#0 [10]

TP7

TP9

L0_CTLOUT0 [10]

L0_CTLOUT#0 [10]

L0_CTLIN#0 [10]

L0_CTLIN0 [10]

L0_CLKIN#0 [10]

L0_CLKIN0 [10]

R103 820

R105 820

THERMTRIP_CPU_L_SB

R208 0

THERMTRIP_CPU_L

R106 820

NC_AJ18

NC_AG17

NC_D20

NC_C21

NC_D18

NC_C19

NC_B19

L0_CADOUT_H[0..15] [10]

CPU_CORE

L0_CADOUT_L[0..15] [10]

TP6

TP8

NEAR CPU

FBCLKOUT_H

FBCLKOUT_L

<1000MIL

R96 680

R97 680

R192 680

R191 680

R200 680

R196 680

R197 680

C360

39p

NPO

C516

39p

NPO

+2.5V

R202

*0

+1.2V

R131

80.6_1%

UNIWILL COMPUTER CORP.

Title

Size Document Number Rev

Date: Sheet

2756

ATHLON64-HT

255KIX

434Tuesday, August 10, 2004

1

of

R195

680

01

Page 5

8

A

+1.25V_DDR_SENSE

+1.25V_DDR_SENSE[27]

+2.5V_DDR

D D

C C

B B

+1.25V_DDR_SENSE

DDRVREF_CPU

R189 34.8_1%

R188 34.8_1%

MAB0

MAB1

MAB2

MAB3

MAB4

MAB5

MAB6

MAB7

MAB8

MAB9

MAB10

MAB11

MAB12

MAB13

TP12

Z0501

Z0502

MMDATA63

MMDATA62

MMDATA61

MMDATA60

MMDATA59

MMDATA58

MMDATA57

MMDATA56

MMDATA55

MMDATA54

MMDATA53

MMDATA52

MMDATA51

MMDATA50

MMDATA49

MMDATA48

MMDATA47

MMDATA46

MMDATA45

MMDATA44

MMDATA43

MMDATA42

MMDATA41

MMDATA40

MMDATA39

MMDATA38

MMDATA37

MMDATA36

MMDATA35

MMDATA34

MMDATA33

MMDATA32

MMDATA31

MMDATA30

MMDATA29

MMDATA28

MMDATA27

MMDATA26

MMDATA25

MMDATA24

MMDATA23

MMDATA22

MMDATA21

MMDATA20

MMDATA19

MMDATA18

MMDATA17

MMDATA16

MMDATA15

MMDATA14

MMDATA13

MMDATA12

MMDATA11

MMDATA10

MMDATA9

MMDATA8

MMDATA7

MMDATA6

MMDATA5

MMDATA4

MMDATA3

MMDATA2

MMDATA1

MMDATA0

AE13

AG12

D14

C14

A16

B15

A12

B11

A17

A15

C13

A11

A10

C11

AC1

AC3

AC2

AD1

AE1

AE3

AG3

AJ4

AE2

AF1

AH3

AJ3

AJ5

AJ6

AJ7

AH9

AG5

AH5

AJ9

AJ10

AH11

AJ11

AH15

AJ15

AG11

AJ12

AJ14

AJ16

AB3

AA5

AD4

AC5

AD5

AF4

AF6

U6B

C7

C5

G2

G1

G3

M1

W1

W3

W2

M3

U5

W5

M4

U2

U1

N2

U3

N1

N3

B9

A6

A9

A5

B5

A4

E2

E1

A3

B3

E3

F1

L3

L1

L2

Y1

T4

Y4

E9

P1

V1

J2

VTT_SENSE

MEMVREF1

MEMZN

MEMZP

MEMDATA63

MEMDATA62

MEMDATA61

MEMDATA60

MEMDATA59

MEMDATA58

MEMDATA57

MEMDATA56

MEMDATA55

MEMDATA54

MEMDATA53

MEMDATA52

MEMDATA51

MEMDATA50

MEMDATA49

MEMDATA48

MEMDATA47

MEMDATA46

MEMDATA45

MEMDATA44

MEMDATA43

MEMDATA42

MEMDATA41

MEMDATA40

MEMDATA39

MEMDATA38

MEMDATA37

MEMDATA36

MEMDATA35

MEMDATA34

MEMDATA33

MEMDATA32

MEMDATA31

MEMDATA30

MEMDATA29

MEMDATA28

MEMDATA27

MEMDATA26

MEMDATA25

MEMDATA24

MEMDATA23

MEMDATA22

MEMDATA21

MEMDATA20

MEMDATA19

MEMDATA18

MEMDATA17

MEMDATA16

MEMDATA15

MEMDATA14

MEMDATA13

MEMDATA12

MEMDATA11

MEMDATA10

MEMDATA9

MEMDATA8

MEMDATA7

MEMDATA6

MEMDATA5

MEMDATA4

MEMDATA3

MEMDATA2

MEMDATA1

MEMDATA0

MEMADDB0

MEMADDB1

MEMADDB2

MEMADDB3

MEMADDB4

MEMADDB5

MEMADDB6

MEMADDB7

MEMADDB8

MEMADDB9

MEMADDB10

MEMADDB11

MEMADDB12

MEMADDB13

MEMCHECK0

MEMCHECK1

MEMCHECK2

MEMCHECK3

MEMCHECK4

MEMCHECK5

MEMCHECK6

MEMCHECK7

7

MEMRESET_L

RSVD_MEMADDA15

RSVD_MEMADDA14

RSVD_MEMADDB15

RSVD_MEMADDB14

MEMORY INTERFACE

VTT_A4

VTT_A1

VTT_A2

VTT_A3

VTT_B1

VTT_B2

VTT_B3

VTT_B4

MEMCKEA

MEMCKEB

MEMCLK_H7

MEMCLK_H6

MEMCLK_H5

MEMCLK_H4

MEMCLK_H3

MEMCLK_H2

MEMCLK_H1

MEMCLK_H0

MEMCLK_L7

MEMCLK_L6

MEMCLK_L5

MEMCLK_L4

MEMCLK_L3

MEMCLK_L2

MEMCLK_L1

MEMCLK_L0

MEMCS_L7

MEMCS_L6

MEMCS_L5

MEMCS_L4

MEMCS_L3

MEMCS_L2

MEMCS_L1

MEMCS_L0

MEMRASA_L

MEMCASA_L

MEMWEA_L

MEMBANKA1

MEMBANKA0

MEMADDA13

MEMADDA12

MEMADDA11

MEMADDA10

MEMADDA9

MEMADDA8

MEMADDA7

MEMADDA6

MEMADDA5

MEMADDA4

MEMADDA3

MEMADDA2

MEMADDA1

MEMADDA0

MEMRASB_L

MEMCASB_L

MEMWEB_L

MEMBANKB1

MEMBANKB0

MEMDQS0

MEMDQS1

MEMDQS2

MEMDQS3

MEMDQS4

MEMDQS5

MEMDQS6

MEMDQS7

MEMDQS8

MEMDQS9

MEMDQS10

MEMDQS11

MEMDQS12

MEMDQS13

MEMDQS14

MEMDQS15

MEMDQS16

MEMDQS17

D17

A18

B17

C17

AF16

AG16

AH16

AJ17

AG10

AE8

AE7

D10

E12

AF8

AF10

V3

K5

R5

P3

C10

E11

AG8

AE10

V4

K4

P5

P4

D8

C8

E8

E7

D6

E6

C4

E5

H5

D4

G5

K3

H3

E13

C12

E10

AE6

AF3

M5

AE5

AB5

AD3

Y5

AB4

Y3

V5

T5

T3

N5

H4

F5

F4

L5

J5

AJ13

AJ8

AJ2

AB1

J1

D1

A8

A14

T1

AH13

AH7

AG1

AA1

H1

C2

A7

A13

R1

E14

D12

6

+1.25V_DDR

MEMRESET_L

MMCKEA

MMCKEB

MEMCLK_H7

MEMCLK_H6

MEMCLK_H5

MEMCLK_H4

MEMCLK_H3

MEMCLK_H2

MEMCLK_H1

MEMCLK_H0

MEMCLK_L7

MEMCLK_L6

MEMCLK_L5

MEMCLK_L4

MEMCLK_L3

MEMCLK_L2

MEMCLK_L1

MEMCLK_L0

MEMCS_L3

MEMCS_L2

MEMCS_L1

MEMCS_L0

MAA13

MAA12

MAA11

MAA10

MAA9

MAA8

MAA7

MAA6

MAA5

MAA4

MAA3

MAA2

MAA1

MAA0

MMDQS0

MMDQS1

MMDQS2

MMDQS3

MMDQS4

MMDQS5

MMDQS6

MMDQS7

MEMDQS9

MEMDQS10

MEMDQS11

MEMDQS12

MEMDQS13

MEMDQS14

MEMDQS15

MEMDQS16

TP20

MEMCLK_H7 [8,9]

MEMCLK_H6 [8,9]

MEMCLK_H5 [8,9]

MEMCLK_H4 [8,9]

MEMCLK_L7 [8,9]

MEMCLK_L6 [8,9]

MEMCLK_L5 [8,9]

MEMCLK_L4 [8,9]

MEMRASA_L [8,9]

MEMCASA_L [8,9]

MEMWEA_L [8,9]

MEMBANKA1 [8,9]

MEMBANKA0 [8,9]

MEMRASB_L [8,9]

MEMCASB_L [8,9]

MEMWEB_L [8,9]

MEMBANKB1 [8,9]

MEMBANKB0 [8,9]

5

MEMDQS[9..16]

MMDQS[0..7]

MMDATA[0..63]

MAA[0..13]

MAB[0..13]

MEMCLK_H0

MEMCLK_H1

MEMCLK_H3

MEMCLK_H2

MEMCLK_L3

MEMCLK_L2

MEMCLK_L1

MEMCLK_L0

MEMCS_L[0..3] [8,9]

+1.25V_DDR

C511 1u_0603

C531 1u_0603

C310 1000p

C315 1000p

C495 100p

MEMDQS[9..16] [8]

MMDQS[0..7] [8]

MMDATA[0..63] [8]

MAA[0..13] [8,9]

MAB[0..13] [8,9]

MEMCKEA[8,9]

MEMCKEB[8,9]

C469 1u_0603

C468 1u_0603

C181 1u_0603

C180 1u_0603

C464 0.1u

+2.5V_DDR+1.25V_DDR

TP15

TP16

TP17

TP18

TP19

TP21

TP22

TP23

MEMCKEA

MEMCKEB

4

+2.5V_DDR

R93

75_1%_0603

R99

75_1%_0603

R128 10

R129 10

MEMCLK_L1

MEMCLK_L0

MEMCLK_H1

MEMCLK_H0

+1.25V_DDR +2.5V_DDR

MMCKEA

MMCKEB

+2.5V_DDR

R143 10K_1%

R145 10K_1%

R140 10K_1%

R146 10K_1%

+1.25V_DDR

C528 1u_0603

C296 1u_0603

C517 1000p

C512 1000p

C309 100p

C249 0.22u/6.3V_0603

C273 0.22u/6.3V_0603

C261 0.22u/6.3V_0603

C233 0.22u/6.3V_0603

C220 0.22u/6.3V_0603

C461 0.22u/6.3V_0603

C424 0.22u/6.3V_0603

C470 0.22u/6.3V_0603

C415 0.22u/6.3V_0603

C199 0.22u/6.3V_0603

C179 0.22u/6.3V_0603

C258

0.1u

C267

0.1u

C257

1000p

C264

1000p

+2.5V_DDR

3

C259

0.1u

DDRVREF_CPU

C266

0.1u

+

C525

0.22u/6.3V_0603

C265

0.1u

C11

*4.7u/10V_0805

C4

+

*4.7u/10V_0805

C1

*0.22u/6.3V_0603

C513

+

4.7u/10V_0805

C18

+

220u/4V_SMT

M-C7343

+

+2.5V_DDR

C9

*39p

NPO

+2.5V_DDR

C521

+

4.7u/10V_0805

+

Put near Athlon 64

+

C524

+

4.7u/10V_0805

C533

0.22u/6.3V_0603

2

C520

4.7u/10V_0805

C150

560u/4V_8*13

OS-CON

C7

*4.7u/10V_0805

C16

*0.22u/6.3V_0603

C5

*39p

NPO

C157

+

4.7u/10V_0805

C282

+

4.7u/10V_0805

+2.5V_DDR

+

+2.5V_DDR

+

EMI

C503

*39p

NPO

C153

+

4.7u/10V_0805

+1.25V_DDR

C361

330u/6.3V_LESR

6.3*7

C508

4.7u/10V_0805

C13

*0.22u/6.3V_0603

C6

*39p

NPO

C19

+

330u/3V_SMT

M-C7343

C2

+

*4.7u/10V_0805

+

C519

+

560u/4V_8*9

OS-CON

C530

0.22u/6.3V_0603

1

C17

*39p

NPO

C518

4.7u/10V_0805

C522

+

4.7u/10V_0805

C3

*39p

NPO

C15

*0.22u/6.3V_0603

A

UNIWILL COMPUTER CORP.

Title

Size Document Number Rev

8

7

6

5

4

3

Date: Sheet

2756

2

ATHLON64-DDR

255KIX

534Tuesday, August 10, 2004

01

of

1

Page 6

8

A

U6C

L7

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDD9

VDD10

VDD11

VDD12

VDD13

VDD14

VDD15

VDD16

VDD17

VDD18

VDD19

VDD20

VDD21

VDD22

VDD23

VDD24

VDD25

VDD26

VDD27

VDD28

VDD29

VDD30

VDD31

VDD32

VDD33

VDD34

VDD35

VDD36

VDD39

VDD38

VDD37

VDD40

VDD41

VDD42

VDD43

VDD44

VDD45

VDD46

VDD47

VDD48

VDD49

VDD50

VDD51

VDD52

VDD53

VDD54

VDD55

VDD56

VDD57

VDD58

VDD59

VDD60

VDD61

VDD62

VDD63

VDD64

VDD65

VDD66

VDD67

VDD68

VDD69

VDD70

VDD71

VDD72

VDD73

VDD74

VDD75

VDD76

VDD77

VDD78

VDD79

VDD80

VDD81

VDD82

VDD83

VDD84

VDD85

VDD86

VDD87

VDD88

VDD89

VDD90

VDD91

VDD92

VDDIO1

VDDIO2

VDDIO3

VDDIO4

VDDIO5

VDDIO7

VDDIO8

VDDIO9

VDDIO10

VDDIO11

VDDIO12

VDDIO13

VDDIO14

VDDIO15

VDDIO16

VDDIO17

VDDIO18

VDDIO19

VDDIO20

VDDIO21

VDDIO22

VDDIO23

VDDIO24

VDDIO25

VDDIO26

VDDIO27

VDDIO28

VDDIO29

VDDIO30

VDDIO31

VDDIO32

VDDIO33

VDDIO34

VDDIO35

VDDIO36

VDDIO37

VDDIO38

VDDIO39

VDDIO40

VDDIO41

VDDIO42

VDDIO43

VDDIO44

VDDIO45

VDDIO46

VDDIO47

VDDIO48

VDDIO49

VDDIO50

VDDIO6

VDD96

VDD97

VDD98

VDD99

VDD100

VDD101

VDD102

VDD103

VDD104

VDD105

VDD106

VDD107

VDD108

VDD109

VDD110

VDD111

VDD112

VDD113

VDD114

VDD115

VDD116

VDD117

VDD118

VDD119

VDD120

VDD121

VDD122

VDD123

VDD124

VDD125

VDD126

VDD127

VDD128

VDD129

VDD130

VDD131

VDD132

VDD133

VDD93

VDD94

VDD95

AC15

AB14

AA15

AB16

AA17

AC17

AE17

AB18

AD18

AG19

AC19

AA19

AB20

AD20

AA21

AC21

AB22

AD22

AA23

AC23

AB24

AD24

AH24

AE25

H18

B20

E21

H22

H24

V10

G13

K14

Y14

G15

H16

K16

Y16

G17

K18

Y18

E19

G19

H20

K20

M20

P20

V20

Y20

G21

N21

R21

U21

W21

K22

M22

P22

V22

Y22

E23

G23

N23

R23

U23

W23

B24

D24

K24

M24

P24

V24

Y24

K26

P26

V26

J23

F26

N7

L9

J15

J17

F18

J19

F20

T20

J21

L21

F22

T22

L23

F24

T24

D D

C C

B B

POWER

8

E4

G4

J4

L4

N4

U4

W4

AA4

AC4

AE4

D5

AF5

F6

H6

K6

M6

P6

T6

V6

Y6

AB6

AD6

D7

G7

J7

AA7

AC7

AF7

F8

H8

AB8

AD8

D9

G9

AC9

AF9

F10

AD10

D11

AF11

F12

AD12

D13

AF13

F14

AD14

F16

AD16

D15

R4

N28

U28

AA28

AE27

R7

U7

W7

K8

M8

P8

T8

V8

Y8

J9

N9

R9

U9

W9

AA9

H10

K10

M10

P10

T10

Y10

AB10

G11

J11

AA11

AC11

H12

K12

Y12

AB12

J13

AA13

AC13

H14

AB26

E28

J28

7

+2.5V_DDRCPU_CORE

CPU_CORE

7

6

U6D

AH20

AB21

W22

M23

AG25

AG27

AA8

AB9

AA10

AE16

G20

W20

AA20

AC20

AE20

AG20

AJ20

M21

AD21

AG21

G22

AG29

AA22

AC22

AG22

AH22

AJ22

AB23

AD23

AG23

G24

W24

AA24

AC24

AG24

AJ24

M26

AD26

AF26

AH26

G28

AB17

AD17

G18

AA18

AC18

AB19

AD19

AF19

B2

VSS1

VSS3

VSS4

VSS5

VSS6

L24

VSS7

VSS8

VSS9

D2

VSS10

AF2

VSS11

W6

VSS12

Y7

VSS13

VSS14

VSS15

VSS16

J12

VSS17

B14

VSS18

Y15

VSS19

VSS20

J18

VSS21

VSS22

R20

VSS23

U20

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

D21

VSS31

F21

VSS32

H21

VSS33

K21

VSS34

VSS35

P21

VSS36

T21

VSS37

V21

VSS38

Y21

VSS39

VSS40

VSS41

B22

VSS42

E22

VSS43

VSS44

J22

VSS45

L22

VSS46

N22

VSS47

R22

VSS48

U22

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

D23

VSS56

F23

VSS57

H23

VSS58

K23

VSS59

P23

VSS60

T23

VSS61

V23

VSS62

Y23

VSS63

VSS64

VSS65

VSS66

E24

VSS67

VSS68

J24

VSS69

N24

VSS70

R24

VSS71

U24

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

B25

VSS78

C25

VSS79

B26

VSS80

D26

VSS81

H26

VSS82

VSS83

T26

VSS84

Y26

VSS85

VSS86

VSS87

VSS88

C27

VSS89

B28

VSS90

D28

VSS91

VSS92

F15

VSS187

H15

VSS188

VSS206

VSS207

B16

VSS208

VSS209

VSS210

VSS211

D19

VSS212

F19

VSS213

H19

VSS214

K19

VSS215

Y19

VSS216

VSS217

VSS218

VSS219

J20

VSS220

L20

VSS221

N20

VSS222

GROUND

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

VSS161

VSS162

VSS163

VSS164

VSS165

VSS166

VSS167

VSS168

VSS169

VSS170

VSS171

VSS172

VSS173

VSS174

VSS175

VSS176

VSS177

VSS178

VSS179

VSS180

VSS181

VSS182

VSS183

VSS184

VSS185

VSS186

VSS189

VSS190

VSS191

VSS192

VSS194

VSS195

VSS196

VSS197

VSS198

VSS199

VSS223

VSS201

VSS202

VSS203

VSS204

VSS205

L28

R28

W28

AC28

AF28

AH28

C29

F2

H2

K2

M2

P2

T2

V2

Y2

AB2

AD2

AH2

B4

AH4

B6

G6

J6

L6

N6

R6

U6

AA6

AC6

AH6

F7

H7

K7

M7

P7

T7

V7

AB7

AD7

B8

G8

J8

L8

N8

R8

U8

W8

AC8

AH8

F9

H9

K9

M9

P9

T9

V9

Y9

AD9

B10

G10

J10

L10

N10

R10

U10

W10

AC10

AH10

F11

H11

K11

Y11

AB11

AD11

B12

G12

AA12

AC12

AH12

F13

H13

K13

Y13

AB13

AD13

AF17

G14

J14

AA14

AC14

AE14

D16

E15

K15

AB15

AD15

AH14

E16

G16

J16

AA16

AC16

AE29

AJ26

E18

F17

H17

K17

Y17

6

5

Put near Socket

CPU_CORE

0.22u/6.3V_0603

CPU_CORE

5

C270

C288

0.1u

CPU_CORE

C506

0.1u

CPU_CORE

+2.5V_DDR

C336

0.1u

0.22u/6.3V_0603

C418

0.1u

C331

0.1u

C305

C289

0.1u

C505

0.22u/6.3V_0603

C247

0.1u

C311

0.1u

C320

0.1u

C345

0.1u

0.22u/6.3V_0603

C322

C301

0.1u

C290

0.1u

C291

0.1u

+1.25V_DDR

C526

0.1u

C314

0.1u

4

C275

0.1u

4

C388

0.1u

C297

0.1u

C319

0.1u

CPU_CORE

C251

0.1u

CPU_CORE

C302

+

4.7u/10V_0805

0.1u

C445

0.1u

C328

C387

0.1u

+1.2V

C389

0.1u

C504

+

4.7u/10V_0805

3

Put near CPU Socket

cavity Bottom Side

CPU_CORE

0.22u/6.3V_0603

C402

C379

C515

4.7u/10V_0805

0.22u/6.3V_0603

C398

+

10u/10V_0805

X5R

C300

+

4.7u/10V_0805

0.22u/6.3V_0603

CPU_CORE

C380

+

10u/10V_0805

X5R

+

0.22u/6.3V_0603

C400

+

2

C377

C399

10u/10V_0805

X5R

C334

+

4.7u/10V_0805

Put on the Backside of the Processor

C321

C327

0.1u

C372

0.1u

0.1u

CPU_CORE

C262

4.7u/10V_0805

3

Put near CPU Socket

cavity TOP Side

CPU_CORE

+

Title

Size Document Number Rev

Date: Sheet

2

0.22u/6.3V_0603

C378

C401

0.22u/6.3V_0603

C381

+

10u/10V_0805

X5R

+

C20

*10u/10V_0805

X5R

C303

4.7u/10V_0805

+

+

C10

*10u/10V_0805

X5R

C326

4.7u/10V_0805

UNIWILL COMPUTER CORP.

ATHLON64-PWR&GND

2756

255KIX

1

+

634Tuesday, August 10, 2004

1

C268

4.7u/10V_0805

01

of

A

Page 7

+3V

L56

QT2012RL060

VCC3_CLKGN

D D

C609

+

4.7u/10V_0805

C C

+3V

R221 *2.7K

R230 *2.7K

R241 *2.7K

R260 *2.7K

5

C554

C607

0.1u

0.1u

Frequency Selection

FS0

FS1

FS2

FS3

C585

C608

0.1u

0.1u

+3V

L54

QT2012RL060

C574

0.1u

R231 *2.7K

R220 *2.7K

R236 *2.7K

R266 *2.7K

C590

0.1u

TP26

TP14

+3V

C552

0.1u

C570

0.1u

C542

C576

0.1u

0.1u

Z0701

Z0702

R271

PD#

10K_1%

VCC3_CLKGN_VDDA

C571

1000p

Main Clock Generator

4

U12

REALTEK RTM360-755R / ICS952802

44

VDDCPU

43

VDDCPU

33

VDDAGP

31

VDD48

24

VDDPCI

15

VDDPCI

11

VDDZ

1

VDDREF

47

VSSCPU

40

VSSCPU

36

VSSF

28

VSS48

23

VSSPCI

16

VSSPCI

8

VSSZ

5

VSSREF

48

*CPUSTOP#

12

*PCISTOP#

37

*PD#

38

VDDA

39

VSSA

X1

6

Z0716

C543

10p

NPO

Y5

14.318MHz

CPUCLK_0T

CPUCLK_0C

CPUCLK_1T

CPUCLK_1C

AGPCLK0

AGPCLK1

ZCLK0

ZCLK1

**FS0/REF0

**FS1/REF0

**FS2/REF0

**FS3/PCICLK_F0

**FS4/PCICLK_F1

PCICLK0

PCICLK1

PCICLK2

PCICLK3

PCICLK4

PCICLK5

PCICLK6

PCICLK7

48MHz

24_48MHz

SCLK

SDATA

X2

7

Z0717

C544

10p

NPO

3

Damping Resistors

Place near to the

Clock Outputs

Z0703

42

Z0704

41

Z0705

46

Z0706

45

Z0707

35

34

Z0708

9

Z0709

10

FS0

2

FS1

3

FS2

4

FS3

13

14

Z0710

17

Z0711 PCM_SCLK

18

Z0712

19

Z0713

20

Z0714

21

22

25

26

Z0715

30

29

32

27

R248 15_1%

R259 15_1%

R219 10

R229 10

R274 22

R261 22

R270 10

R214 10

R213 33

R240 *33

R267 33

R273 33

R276 33

R281 33

R287 33

R290 33

R279 22

C617

10p

NPO

01

C616

10p

NPO

Delete R288, R292

CPUCLK

CPUCLK#

760CLK

760CLK#

760ZCLK

963ZCLK

VOSCIE

VOSCI

963OSCI

AUDIO_CLK

963PCICLK

PCICLK1

PCICLK_M

PCICLK_EC

PCICLK_1394

USB_48M

CPUCLK [4]

CPUCLK# [4]

760CLK [10]

760CLK# [10]

AGPCLK0 [10]

760ZCLK [11]

963ZCLK [14]

VOSCIE [11]

VOSCI [11]

963OSCI [15]

AUDIO_CLK [18]

963PCICLK [14]

PCICLK1 [20]

PCM_SCLK [20]

PCICLK_M [19]

PCICLK_EC [22]

PCICLK_1394 [19]

USB_48M [16]

SMBCLK [8,15,22]

SMBDAT [8,15,22]

2

By-Pass Capacitors

Place near to the Clock Outputs

760CLK

760CLK#

760ZCLK

963ZCLK

963OSCI

AGPCLK0

963PCICLK

PCICLK1

VOSCI

PCICLK_M

PCICLK_EC

VOSCIE

USB_48M

PCICLK_1394

PCM_SCLK

PWROK1[22]

C546 10p NPO

C550 10p NPO

C561 10p NPO

C567 10p NPO

C539 10p NPO

C592 10p NPO

C569 10p NPO

C589 10p NPO

C540 10p NPOR254 22

C594 10p NPO

C598 10p NPO

C575 10p NPO

C596 10p NPO

C599 10p NPO

C591 10p NPO

+3V

53

U34

1

2

TC7SH08FU

+2.5V

53

1

2

R322 470

4

R309 680

U35

4

TC7SH08FU

1

CPUCLK

CPUCLK#

AUDIO_CLK

C558 *10pNPO

C562 *10pNPO

C553 10p NPO

+3V +5V

C776 0.01u

PWROK [11,15]

PWROK_CPU [4]

B B

CLK Table for SiS755/760 ( For ICS-952802)

(FS4)

(FS3)

H3

C276D107

H13

0

0

0

0

0

0

0

1

1

1

1

1

1

1

(FS2)

0

0

0

1

1

1

0

0

0

0

1

1

1

1

HOLEC314D106

5

HOLEC314D106

0

0

0

0

0

0

0

0

0

0 0

0

0

0 133.33

0

0

H9

HOLEC314D106

A A

H10

HOLEC314D106

HOLEC314D106

(FS1)

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

H19

AUDGND

H16

SiS 755/760 CLOCK

(FS0)

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

HOLEC314D106

HOLEC314D106

H18

(MHz)

160.00

200

200

200

186.66

233.33

233.33

233.33

213.34

266.67

266.67

266.671

133.34

166.67

166.67

166.67

H12

ZCLK

CPU

(MHz)

106.66

133.33

133.33

160.00

106.67

133.33

106.66

133.33

106.66

133.33

166.66

H6

HOLEC314D106

H20

HOLEC314D106

PCI

AGPCLK

(MHz)

(MHz)

53.33

26.66

33.33

66.67

33.33

66.67

33.330

66.67

26.66

53.33

66.67

33.33

33.33 0

66.67

66.67155.55

33.33

53.33

26.66

33.33

66.67

33.33

66.67

33.33

66.67

26.66

53.33

66.67

33.33

66.67

33.33

66.671

H8

HOLEC314D106

H7

HOLEC314D106

4

(FS4)

1

1

1

1

1

1

1

10

1

1133.33

1

1

1

1

1

(FS3)

0

0

0

0

0

0

1

10

1

1

1

1

1

1

H15

HOLEC276D157

H1

C276D87

(FS2)

00

0

0

0

1

1

1

10

0

0

0

1

1

1

1

H2

C276D87

(FS1)

(FS0)

0

0

1

1

0

0

1

1

0

0

1

1160.00

0

0

1

1

H17

HOLEC276D157

H4

C276D87

SiS 755/760 CLOCK

0

1

0

1

0

1

0

1

0

1

1

0

1

0

133.33

CPU

(MHz)

206.00

210.00

202.00

202.00

240.331

245.00

235.661133.33

235.66

106.66

133.33

133.33

133.33

171.67

175.00

168.34

168.34

CPUMDC

H5

HOLEC314D181

H14

HOLEC314D181

ZCLK

(MHz)

137.33

140.00

134.66

161.60

137.33

140.00

134.67

157.11

106.66

133.33

133.33

177.77

137.33

140.00

134.66

168.33

H11

HOLEC314D181

3

ICS 952802 Pin2 ( *FS0 ) is internal pull up

AGPCLK

(MHz)

68.67

70.00

67.33

67.33

68.67

70.00

67.33

67.33

53.33

66.67

66.67

66.67

68.67

70.00

67.33

67.33

PCI

(MHz)

34.33

35.00

33.66

33.66

34.33

35.00

33.66

33.66

26.66

33.33

33.33

33.33

34.33

35.00

33.66

33.66

* internal pull up

* * internal pull down

M22

M21

M12

M-MARK1

M8

M-MARK1

H21

C158D158

M-MARK1

M14

M-MARK1

H22

C158D158

M-MARK1

M18

M-MARK1

H23

C158D158

M23

M-MARK1

M6

M-MARK1

2

M24

M-MARK1

M20

M-MARK1

H24

C158D158

Delete R336, C630, R302, Q31, R307,

Q30, R322, C622, R309, Q29, C615.

M27

M25

M-MARK1

M3

M-MARK1

M26

M-MARK1

M2

M-MARK1

M-MARK1

M1

M-MARK1

M28

M-MARK1M9M-MARK1

M19

M15

M-MARK1

M-MARK1

UNIWILL COMPUTER CORP.

Title

Size Document Number Rev

Date: Sheet

CLOCK GENERATOR & PCB HOLE

2756

M7

M-MARK1

M17

M-MARK1

255KIX

1

M10

M-MARK1

M11

M-MARK1

734Tuesday, August 10, 2004

M16

M-MARK1

M13

M-MARK1

of

M4

M-MARK1

01

Page 8

8

A

7

+2.5V_DDR

6

5

4

3

2

+2.5V_DDR

1

MEMCKEB[5,9]

MEMCLK_H6[5,9]

MEMCLK_L6[5,9]

MEMCLK_L4[5,9]

+2.5V_DDR

MAB[0..13]

MEMCS_L2

MEMCS_L3

MAB13

MAB0

MAB1

MAB2

MAB3

MAB4

MAB5

MAB6

MAB7

MAB8

MAB9

MAB10

MAB11

MAB12

MEMBANKB0

MEMBANKB1

RDQM7

RDQM6

RDQM5

RDQM4

RDQM3

RDQM2

RDQM1

RDQM0

MEMWEB_L

MEMCASB_L

MEMRASB_L

MEMCKEB

MEMCLK_H6

MEMCLK_L6

MEMCLK_H4

MEMCLK_L4

DCLK1

DCLK#1

MEMDQS7MEMDQS7

MEMDQS6

MEMDQS5

MEMDQS4

MEMDQS3

MEMDQS2

MEMDQS1

MEMDQS0

SMBDAT

SMBCLK

Z0801

DDRVREF

112

111

110

109

108

107

106

105

102

101

115

100

99

97

117

116

98

121

122

12

26

48

62

134

148

170

184

78

119

120

118

96

95

35

37

160

158

89

91

11

25

47

61

133

147

169

183

77

193

195

194

196

198

1

2

199

197

86

85

123

124

200

921334557698193113

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10/AP

A11

A12

DU/A13

BA0

BA1

DU/BA2

CS0

CS1

DQM0

DQM1

DQM2

DQM3

DQM4

DQM5

DQM6

DQM7

DQM8

WE

CAS

RAS

CKE0

CKE1

CK0

CK0

CK1

CK1

CK2

CK2

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS8

SDA

SCL

SA0

SA1

SA2

VREF

VREF

VDDID

VDDSPD

NC//DU/RESET

NC/DU

NC/DU

NC/DU

NC/DU

3

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

GND

GND

GND

GND

GND

15273951637587

VDDQ

GND

VDDQ

GND

VDDQ

GND

103

131

VDDQ

GND

125

143

VDDQ

GND

137

155

VDDQ

GND

149

157

VDDQ

GND

159

167

VDDQ

GND

161

179

1911022343646587082

VDD

VDD

VDD

VDD

VDD

VDD

VDDQ

VDDQ

GND

GND

GND

GND

GND

GND

GND

GND

173

1854162838405264768890

VDD

GND

VDD

GND

9294114

VDD

GND

VDD

GND

VDD

GND

CN29

192

132

144

156

168

180

VDD

VDD

VDD

VDD

VDD

VDD

VDDQ

GND

GND

GND

GND

GND

GND

GND

GND

104

138

150

162

174

126

186

201

5

D0

7

D1

13

D2

17

D3

6

D4

8

D5

14

D6

18

D7

19

D8

23

D9

29

D10

31

D11

20

D12

24

D13

30

D14

32

D15

41

D16

43

D17

49

D18

53

D19

42

D20

44

D21

50

D22

54

D23

55

D24

59

D25

65

D26

67

D27

56

D28

60

D29

66

D30

68

D31

127

D32

129

D33

135

D34

139

D35

128

D36

130

D37

136

D38

140

D39

141

D40

145

D41

151

D42

153

D43

142

D44

146

D45

152

D46

154

D47

163

D48

165

D49

171

D50

175

D51

164

D52

166

D53

172

D54

176

D55

177

D56

181

D57

187

D58

189

D59

178

D60

182

D61

188

D62

190

D63

71

CB0

73

CB1

79

CB2

83

CB3

72

CB4

74

CB5

80

CB6

84

CB7

GND

202

DDR REV CONN

MEMDATA63

MEMDATA62

MEMDATA61

MEMDATA60

MEMDATA59

MEMDATA58

MEMDATA57

MEMDATA56

MEMDATA55

MEMDATA54

MEMDATA53

MEMDATA52

MEMDATA51

MEMDATA50

MEMDATA49

MEMDATA48

MEMDATA47

MEMDATA46

MEMDATA45

MEMDATA44

MEMDATA43

MEMDATA42

MEMDATA41

MEMDATA40

MEMDATA39

MEMDATA38

MEMDATA37

MEMDATA36

MEMDATA35

MEMDATA34

MEMDATA33

MEMDATA32

MEMDATA31

MEMDATA30

MEMDATA29

MEMDATA28

MEMDATA27

MEMDATA26

MEMDATA25

MEMDATA24

MEMDATA23

MEMDATA22

MEMDATA21

MEMDATA20

MEMDATA19

MEMDATA18

MEMDATA17

MEMDATA16

MEMDATA15

MEMDATA14

MEMDATA13

MEMDATA12

MEMDATA11

MEMDATA10

MEMDATA9

MEMDATA8

MEMDATA7

MEMDATA6

MEMDATA5

MEMDATA4

MEMDATA3

MEMDATA2

MEMDATA1

MEMDATA0

MAA[0..13][5,9]

D D

MEMBANKA0[5,9]

MEMBANKA1[5,9]

MEMCS_L[0..3][5,9]

RDQM[0..7][9]

C C

MEMDQS[0..7][9]

B B

MAA[0..13]

MAA0

112

MAA1

111

MAA2

110

MAA3

109

MAA4

108

MAA5

107

MAA6

106

MAA7

105

MAA8

102

MAA9

101

MAA10

115

MAA11

100

MAA12

99

MEMCS_L0

MEMCS_L1

RDQM7

RDQM6

RDQM5

RDQM4

RDQM3

RDQM2

RDQM1

RDQM0

MEMWEA_L

MEMCASA_L

MEMRASA_L

MEMCKEA

MEMCLK_H7

MEMCLK_L7

MEMCLK_H5

MEMCLK_L5

DCLK0

DCLK#0

MEMDQS6

MEMDQS5

MEMDQS4

MEMDQS3

MEMDQS2

MEMDQS1

MEMDQS0

SMBDAT

SMBCLK

MAA13

97

117

116

98

121

122

12

26

48

62

134

148

170

184

78

119

120

118

96

95

35

37

160

158

89

91

11

25

47

61

133

147

169

183

77

193

195

194

196

198

199

197

86

85

123

124

200

MEMBANKA0

MEMBANKA1

MEMWEA_L[5,9]

MEMCASA_L[5,9]

MEMRASA_L[5,9]

MEMCKEA[5,9]

MEMCLK_H7[5,9]

MEMCLK_L7[5,9]

MEMCLK_H5[5,9] MEMCLK_H4[5,9]

MEMCLK_L5[5,9]

SMBDAT[7,15,22]

SMBCLK[7,15,22]

DDRVREF

+2.5V_DDR

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10/AP

A11

A12

DU/A13

BA0

BA1

DU/BA2

CS0

CS1

DQM0

DQM1

DQM2

DQM3

DQM4

DQM5

DQM6

DQM7

DQM8

WE

CAS

RAS

CKE0

CKE1

CK0

CK0

CK1

CK1

CK2

CK2

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS8

SDA

SCL

SA0

SA1

SA2

1

VREF

2

VREF

VDDID

VDDSPD

NC//DU/RESET

NC/DU

NC/DU

NC/DU

NC/DU

921334557698193113

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

GND

GND

GND

GND

GND

GND

GND

3

GND

15273951637587

179

131

143

155

157

167

1911022343646587082

VDD

VDD

VDD

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

Address:0000h Address:0001h

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

103

125

137

149

159

161

173

1854162838405264768890

VDD

GND

VDD

GND

VDD

GND

VDD

GND

VDD

GND

9294114

VDD

VDD

GND

GND

VDD

GND

104

VDD

GND

CN28

192

132

144

156

168

180

VDD

VDD

VDD

VDD

VDD

VDDQ

GND

GND

GND

GND

GND

GND

138

150

162

174

126

186

5

D0

7

D1

13

D2

17

D3

6

D4

8

D5

14

D6

18

D7

19

D8

23

D9

29

D10

31

D11

20

D12

24

D13

30

D14

32

D15

41

D16

43

D17

49

D18

53

D19

42

D20

44

D21

50

D22

54

D23

55

D24

59

D25

65

D26

67

D27

56

D28

60

D29

66

D30

68

D31

127

D32

129

D33

135

D34

139

D35

128

D36

130

D37

136

D38

140

D39

141

D40

145

D41

151

D42

153

D43

142

D44

146

D45

152

D46

154

D47

163

D48

165

D49

171

D50

175

D51

164

D52

166

D53

172

D54

176

D55

177

D56

181

D57

187

D58

189

D59

178

D60

182

D61

188

D62

190

D63

71

CB0

73

CB1

79

CB2

83

CB3

72

CB4

74

CB5

80

CB6

84

CB7

DDR REV CONN

MEMDATA63

MEMDATA62

MEMDATA61

MEMDATA60

MEMDATA59

MEMDATA58

MEMDATA57

MEMDATA56

MEMDATA55

MEMDATA54

MEMDATA53

MEMDATA52

MEMDATA51

MEMDATA50

MEMDATA49

MEMDATA48

MEMDATA47

MEMDATA46

MEMDATA45

MEMDATA44

MEMDATA43

MEMDATA42

MEMDATA41

MEMDATA40

MEMDATA39

MEMDATA38

MEMDATA37

MEMDATA36

MEMDATA35

MEMDATA34

MEMDATA33

MEMDATA32

MEMDATA31

MEMDATA30

MEMDATA29

MEMDATA28

MEMDATA27

MEMDATA26

MEMDATA25

MEMDATA24

MEMDATA23

MEMDATA22

MEMDATA21

MEMDATA20

MEMDATA19

MEMDATA18

MEMDATA17

MEMDATA16

MEMDATA15

MEMDATA14

MEMDATA13

MEMDATA12

MEMDATA11

MEMDATA10

MEMDATA9

MEMDATA8

MEMDATA7

MEMDATA6

MEMDATA5

MEMDATA4

MEMDATA3

MEMDATA2

MEMDATA1

MEMDATA0

MEMDATA[63..0] [9]

DCLK#1

R107 10K_1%

DCLK#0

R101 10K_1%

DCLK1

R108 10K_1%

DCLK0

R112 10K_1%

+3V

R77 *10K

R78 *10K

+2.5V_DDR

+2.5V_DDR

SMBDAT

SMBCLK

MAB[0..13][5,9]

MEMBANKB0[5,9]

MEMBANKB1[5,9]

MEMCS_L[0..3][5,9]

MEMWEB_L[5,9]

MEMCASB_L[5,9]

MEMRASB_L[5,9]

R76

8.2K

MEMDQS3

MEMDATA29

RDQM3

MEMDATA25

RDQM4

MEMDATA34

MEMDATA38

MEMDATA33

MEMDATA32

MEMDATA37

MEMDATA36

MEMDATA42

MEMDATA43

MEMDATA46

MEMDATA47

1

2

3

4 5

RP21

8P4RX10

4 5

3

2

1

RP33

8P4RX10

1

2

3

4 5

RP31

8P4RX10

4 5

3

2

1

RP39

8P4RX10

8

MMDQS3

8

MMDATA29

7

MEMDQS12

6

MMDATA25

MEMDQS13

MMDATA34

6

MMDQS4MEMDQS4

7

MMDATA38

8

MMDATA33

8

MMDATA32

7

MMDATA37

6

MMDATA36

MMDATA42

MMDATA43

6

MMDATA46

7

MMDATA47

8

MEMDQS5

MEMDATA45

RDQM5

MEMDATA41

MEMDATA49

MEMDATA48

MEMDATA53

MEMDATA52

RDQM6

MEMDATA50

MEMDQS6

MEMDATA54

MEMDATA58

MEMDATA59

MEMDATA62

MEMDATA63

1

2

3

4 5

RP37

8P4RX10

1

2

3

4 5

RP41

8P4RX10

4 5

3

2

1

RP43

8P4RX10

4 5

3

2

1

RP49

8P4RX10

MMDQS5

8

MMDATA45

7

MEMDQS14

6

MMDATA41

MMDATA49

8

MMDATA48

7

MMDATA53

6

MMDATA52

MEMDQS15

MMDATA50

6

MMDQS6

7

MMDATA54

8

MMDATA58

MMDATA59

6

MMDATA62

7

MMDATA63

8

7

MEMDQS7

MEMDATA61

MEMDATA57

MEMDATA21

MEMDATA20

MEMDATA17

MEMDATA16

MEMDATA26

MEMDATA27

MEMDATA30

MEMDATA31

MEMDATA5

MEMDATA4

MEMDATA1

MEMDATA0

1

2

3

4 5

RP47

8P4RX10

1

2

3

4 5

RP15

8P4RX10

4 5

3

2

1

RP22

8P4RX10

1

2

3

4 5

RP5

8P4RX10

MMDQS7

8

MMDATA61

7

MEMDQS16RDQM7

6

MMDATA57

MMDATA21

8

MMDATA20

7

MMDATA17

6

MMDATA16

MMDATA26

MMDATA27

6

MMDATA30

7

MMDATA31

8

MMDATA5

8

MMDATA4

7

MMDATA1

6

MMDATA0

+2.5V_DDR

DDRVREF GEN. & DECOUPLING

R150

75_1%

R149

75_1%

C406

0.1u

C405

0.1u

C397

1000p

C396

1000p

C410

1000p

C411

1000p

C395

1000p

C374

1000p

DDRVREF

UNIWILL COMPUTER CORP.

Title

Size Document Number Rev

2756

Date: Sheet

2

DDR CONN

255KIX

834Tuesday, August 10, 2004

of

1

A

01

RP9

8P4RX10

RP13

8P4RX10

RP17

8P4RX10

RP7

8P4RX10

MMDATA3

MMDATA7

6

MMDATA12

7

MMDATA8

8

MMDATA15

8

MMDATA14

7

MMDATA11

6

MMDATA10

MEMDQS11

MMDATA18

6

MMDQS2

7

MMDATA22

8

MMDQS0

8

MMDATA6

7

MMDATA2

6

MEMDQS9

MEMDQS1

MEMDATA13

RDQM1

MEMDATA9

MEMDATA24

MEMDATA28

MEMDATA23

MEMDATA19

MEMDATA40

MEMDATA44

MEMDATA39

MEMDATA35

MEMDATA51

MEMDATA55

MEMDATA60

MEMDATA56

5

1

2

3

4 5

RP11

8P4RX10

1

2

3

4 5

RP19

8P4RX10

1

2

3

4 5

RP35

8P4RX10

4 5

3

2

1

RP45

8P4RX10

MMDQS1

8

MMDATA13

7

MEMDQS10

6

MMDATA9

MMDATA24

8

MMDATA28

7

MMDATA23

6

MMDATA19

MMDATA40

8

MMDATA44

7

MMDATA39

6

MMDATA35

MMDATA51

MMDATA55

6

MMDATA60

7

MMDATA56

8

MMDATA[0..63]

MMDQS[0..7]

MEMDQS[9..16]

4

MMDATA[0..63] [5]

MMDQS[0..7] [5]

MEMDQS[9..16] [5]

3

MEMDATA3

4 5

MEMDATA7

3

MEMDATA12

2

MEMDATA8

1

MEMDATA15

1

MEMDATA14

2

MEMDATA11

3

MEMDATA10

4 5

RDQM2

4 5

MEMDATA18

3

MEMDQS2

2

MEMDATA22

1

MEMDQS0

1

MEMDATA6

2

MEMDATA2

3

RDQM0

4 5

6

Page 9

8

A

RDQM[0..7][8]

MEMDQS[0..7][8]

MEMDATA[63..0][8]

MEMDATA2

RDQM0

MEMDATA1

MEMDATA0

RDQM1

MEMDATA9

D D

MEMDATA8

MEMDATA3

MEMDATA5

MEMDATA4

MEMDATA11

MEMDATA10

MEMDATA12

MEMDATA7

MEMDATA6

MEMDQS0

MEMDATA22

MEMDQS2

MEMDATA21

MEMDATA20

RDQM3

MEMDATA25

MEMDATA24

MEMDATA19

MEMDATA31

MEMDATA30

MEMDQS3

MEMDATA29

MEMDATA28

MEMDATA23

MEMDATA27

C C

MEMDATA26

MEMDATA33

MEMDATA32

MEMDATA37

MEMDATA36

MEMDATA34

RDQM4

MEMDATA38

MEMDQS4

RDQM5

MEMDATA41

MEMDQS5

MEMDATA45

MEMDATA40

MEMDATA35

MEMDATA44

MEMDATA39

MEMDATA56

MEMDATA51

MEMDATA60

MEMDATA55

MEMDATA50

RDQM6

MEMDATA54

MEMDQS6

B B

RDQM7

MEMDATA57

MEMDQS7

MEMDATA61

MEMDATA59

MEMDATA58

MEMDATA63

MEMDATA62

RP1

8P4RX68

RP2

8P4RX68

RP3

8P4RX68

RP4

8P4RX68

RP10

8P4RX68

RP12

8P4RX68

RP16

8P4RX68

RP14

8P4RX68

RP34

8P4RX68

RP36

8P4RX68

RP40

8P4RX68

RP38

8P4RX68

RP48

8P4RX68

RP46

8P4RX68

RP50

8P4RX68

RP51

8P4RX68

8

7

6

8

7

6

8

7

6

8

7

6

8

7

6

8

7

6

8

7

6

8

7

6

8

7

6

8

7

6

8

7

6

8

7

6

8

7

6

8

7

6

8

7

6

8

7

6

RDQM[0..7]

MEMDQS[0..7]

MEMDATA[63..0]

+1.25V_DDR

1

2

3

45

1

2

3

45

1

2

3

45

1

2

3

45

1

2

3

45

1

2

3

45

1

2

3

45

1

2

3

45

1

2

3

45

1

2

3

45

1

2

3

45

1

2

3

45

1

2

3

45

1

2

3

45

1

2

3

45

1

2

3

45

7

MEMDATA15

8

MEMDATA14

7

MEMDQS1

6

MEMDATA13

RP6 8P4RX68

MEMDATA43

8

MEMDATA42

7

MEMDATA47

6

MEMDATA46

RP42 8P4RX68

MEMBANKA0[5,8]

MEMWEA_L[5,8]

MEMBANKA1[5,8]

MEMRASA_L[5,8]

MEMCASA_L[5,8]

1

MEMWEA_L

2

3

MEMRASA_L

4 5

RP24 8P4RX47

MAA12

MEMCS_L0

1

MAA13

2

MEMCASA_L

3

MEMCS_L1

4 5

RP23 8P4RX47

MAA5

1

MAA3

2

MAA6

3

MAA4

4 5

RP27 8P4RX47

MAA9

1

MAA7

2

MAA11

3

MAA8

4 5

RP29 8P4RX47

MAA1

1

MAA10

2

MAA2

3

MAA0

4 5

RP26 8P4RX47

close CPU,500~1000mil

MEMCKEA[5,8]

close SO-DIMM

MEMCS_L3

RP18 8P4RX47

MAB6

MAB4

MAB2

MAB0

RP28 8P4RX47

MAB12

MAB9

MAB7

RP30 8P4RX47

MEMCS_L2

MAB13

RP20 8P4RX47

MAB5

MAB3

MAB1

MAB10

RP25 8P4RX47

MAB8

MAB11

RP32 8P4RX47

8

7

6

8

7

6

8

7

6

8

7

6

8

7

6

8

7

6

MEMBANKB1[5,8]

MEMRASB_L[5,8]

MEMCASB_L[5,8]

MEMCKEB[5,8]

MEMBANKB0[5,8]

MEMWEB_L[5,8]

MAB[0..13][5,8]

MAB[0..13]

close CPU,500~1000mil

R12447

1

2

3

45

1

2

3

45

8

7

6

8

7

6

8

7

6

8

7

6

8

7

6

R9847

6

+1.25V_DDR

1

2

3

45

1

2

3

45

1

2

3

45

1

2

3

45

1

2

3

45

1

2

3

45

+1.25V_DDR

5

+2.5V_DDR+1.25V_DDR

C467 0.1u

C466 0.1u

C438 0.1u

C417 0.1u

C182 0.1u

C340 0.1u

+

C164

+

330u/6.3V_LESR

6.3*7

+1.25V_DDR

1

2

3

45

1

2

3

45

C421

4.7u/10V_0805

MEMDATA18

8

RDQM2

7

MEMDATA17

6

MEMDATA16

RP8 8P4RX68

MEMDATA49

8

MEMDATA48

7

MEMDATA53

6

MEMDATA52

RP44 8P4RX68

+1.25V_DDR

C485

+

4.7u/10V_0805

+1.25V_DDR +2.5V_DDR

Layout: Place a Cap every 1 IN

. On +1.25v_DDR Trace between

CPU and DDR

4

C169

0.22u/6.3V_0603

+1.25V_DDR

+1.25V_DDR

C231

0.1u

C342

0.1u

C197

0.1u

C350

0.1u

+2.5V_DDR

C170

0.22u/6.3V_0603

+2.5V_DDR

C318

0.1u

C365

0.1u

+2.5V_DDR

C187

0.1u

C211

0.1u

+2.5V_DDR

MAA[0..13][5,8]

MEMCLK_L4[5,8]

MEMCLK_L5[5,8]

MEMCLK_L6[5,8]

MEMCLK_L7[5,8]

3

MEMCS_L[0..3][5,8]

PUT near CPU (<500 MIL)

C276

0.1u

C237

0.1u

C272

0.1u

C274

0.1u

R126 120

R127 120

R181 120

R182 120

C403

0.22u/6.3V_0603

C248

C241

0.1u

0.1u

C191

C200

0.1u

0.1u

C254

C239

0.1u

0.1u

C359

C369

0.1u

0.1u

C175

0.1u

C177

0.1u

C356

0.1u

C488

0.1u

MEMCLK_L4

MEMCLK_L5 MEMCLK_H5

MEMCLK_L6 MEMCLK_H6

MEMCLK_L7 MEMCLK_H7

C404

0.22u/6.3V_0603

DIMM DECOUPLING

LAYOUT: Place alternating cap s to GND a nd

+2.5V_DDR in a single along +1.25V_DDR

C307

C283

0.1u

0.1u

C293

C278

0.1u

0.1u

C161

C168

0.1u

0.1u

C376

C228

0.1u

0.1u

MEMCLK_H4

+2.5V_DDR

C316 0.1u

C8 *0.1u

C313 0.1u

C329 0.1u

C335 0.1u

C230 0.1u

2

C333

0.1u

C163

0.1u

C253

0.1u

C338

0.1u

MEMCLK_H4 [5,8]

MEMCLK_H5 [5,8]

MEMCLK_H6 [5,8]

MEMCLK_H7 [5,8]

C325

C246

0.1u

0.1u

C323

C383

0.1u

0.1u

C269

C367

0.1u

0.1u

C330

C260

0.1u

0.1u

DIMM DECOUPLING

C256 0.1u

C353 0.1u

C176 0.1u

C12 *0.1u

C192 0.1u

C212 0.1u

C375

0.1u

C171

0.1u

C229

0.1u

C490

0.1u

C362

0.1u

C352

0.1u

C348

0.1u

C491

0.1u

1

C14 *0.1u

C292 0.1u

C349 0.1u

C364 0.1u

C221 0.1u

C324 0.1u

C465

0.1u

C312

0.1u

C213

0.1u

C434

0.1u

C206

0.1u

C243

0.1u

C227

0.1u

C385

0.1u

01

C794

0.1u

UNIWILL COMPUTER CORP.

DDR Termination Resistors

255KIX

A

934Tuesday, August 10, 2004

01

of

1

0.22u/6.3V_0603

C232

5

C242

+

4.7u/10V_0805

C252

+

4.7u/10V_0805

C486

0.22u/6.3V_0603

C453

+

4.7u/10V_0805