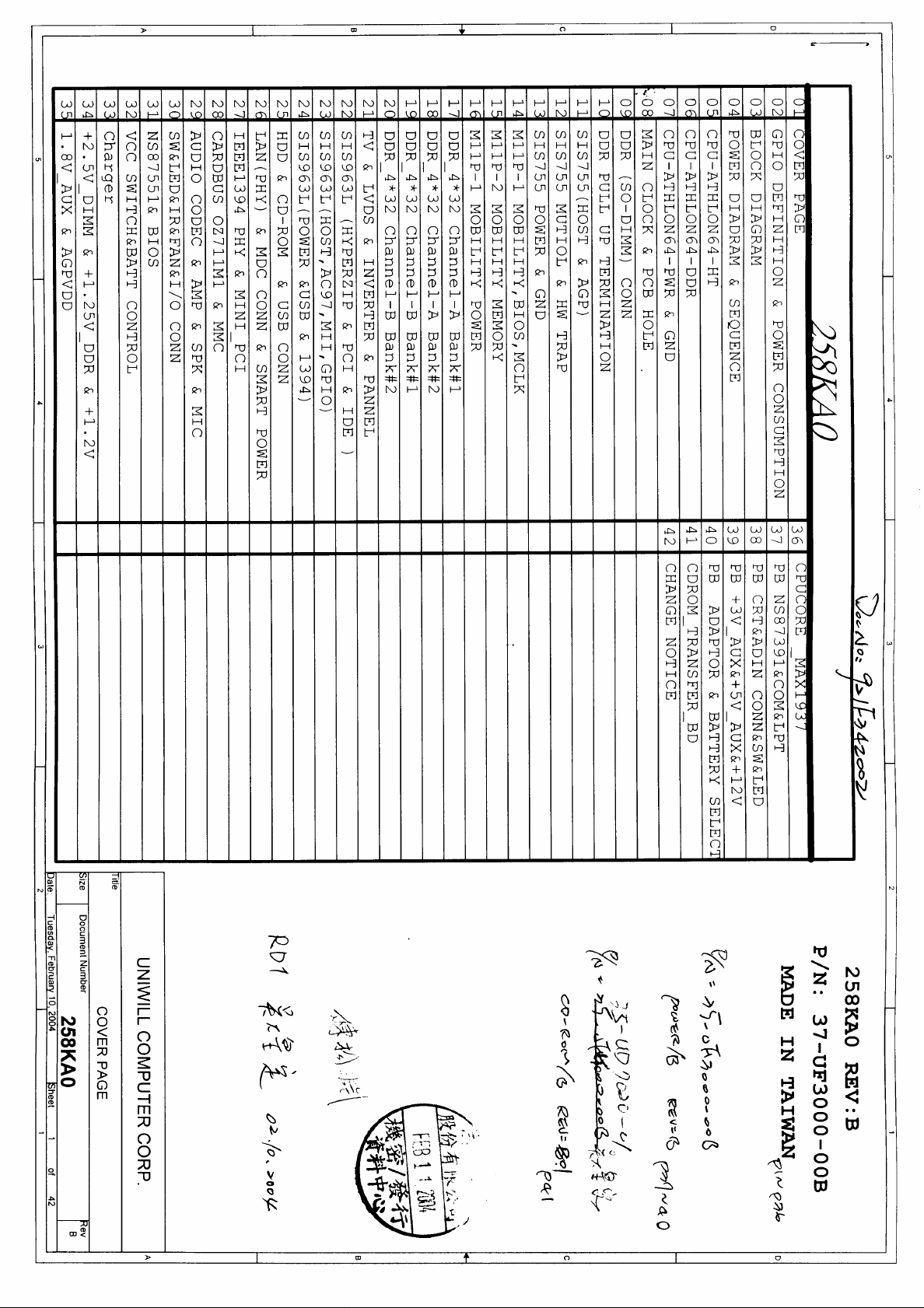

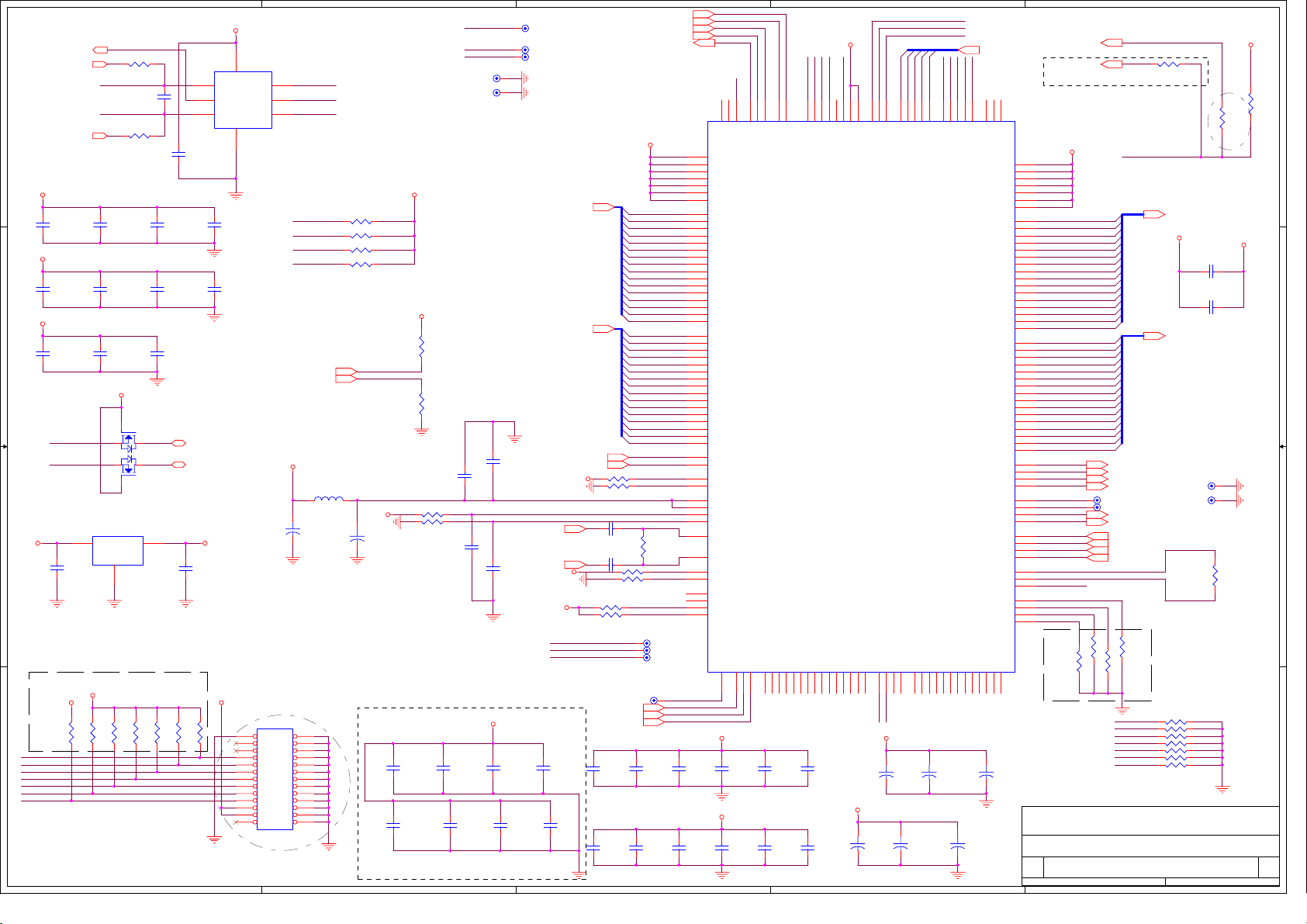

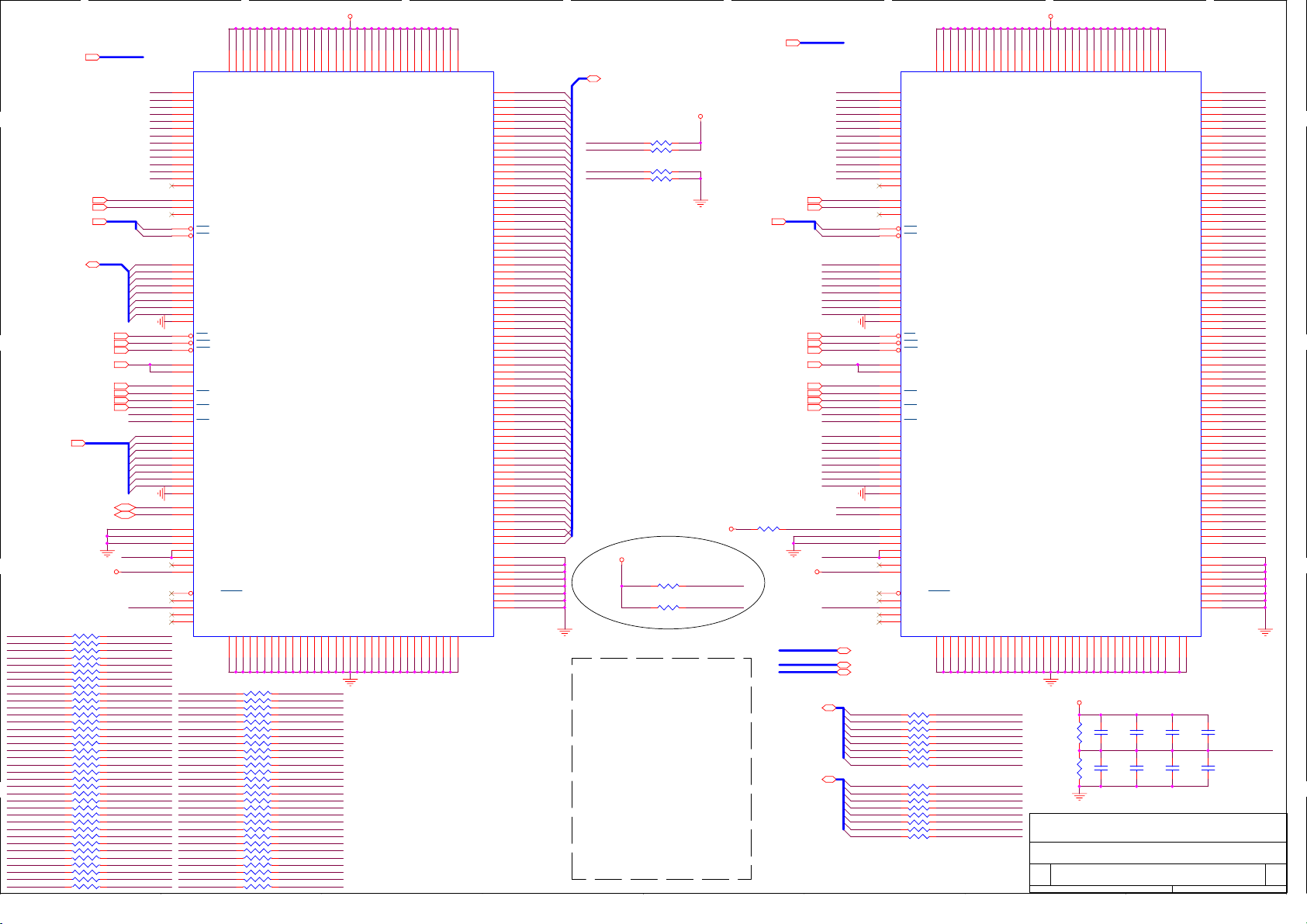

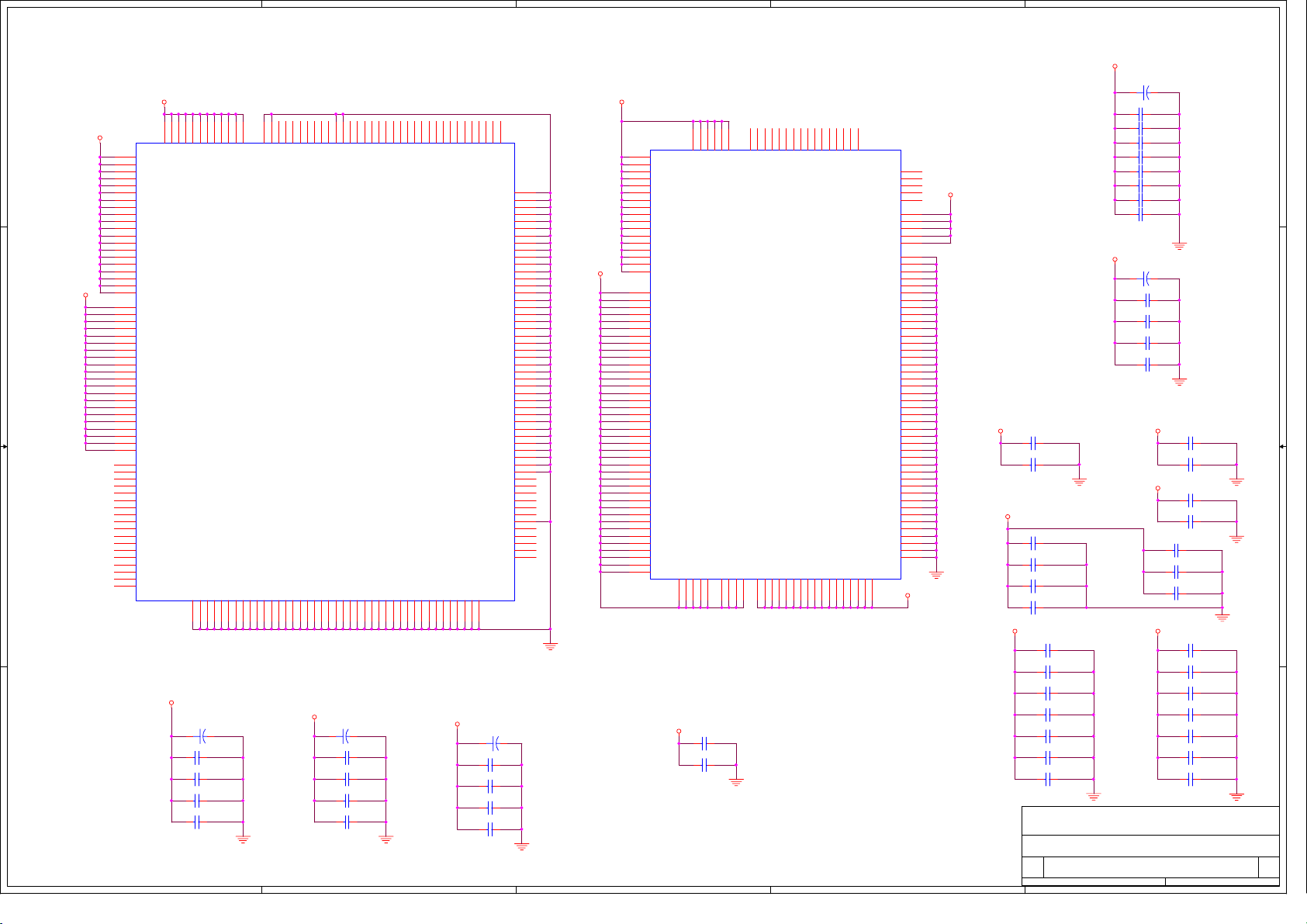

Page 1

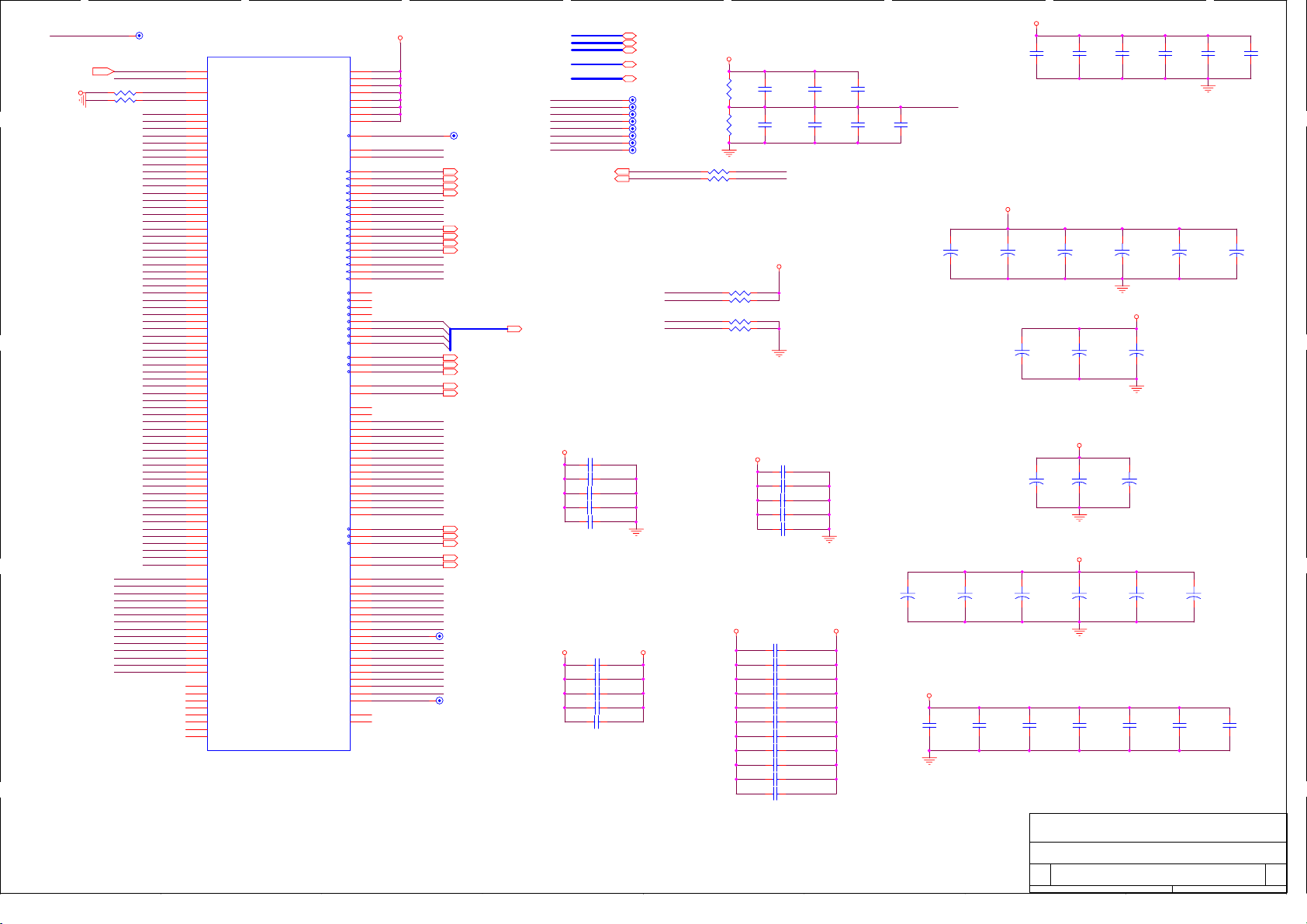

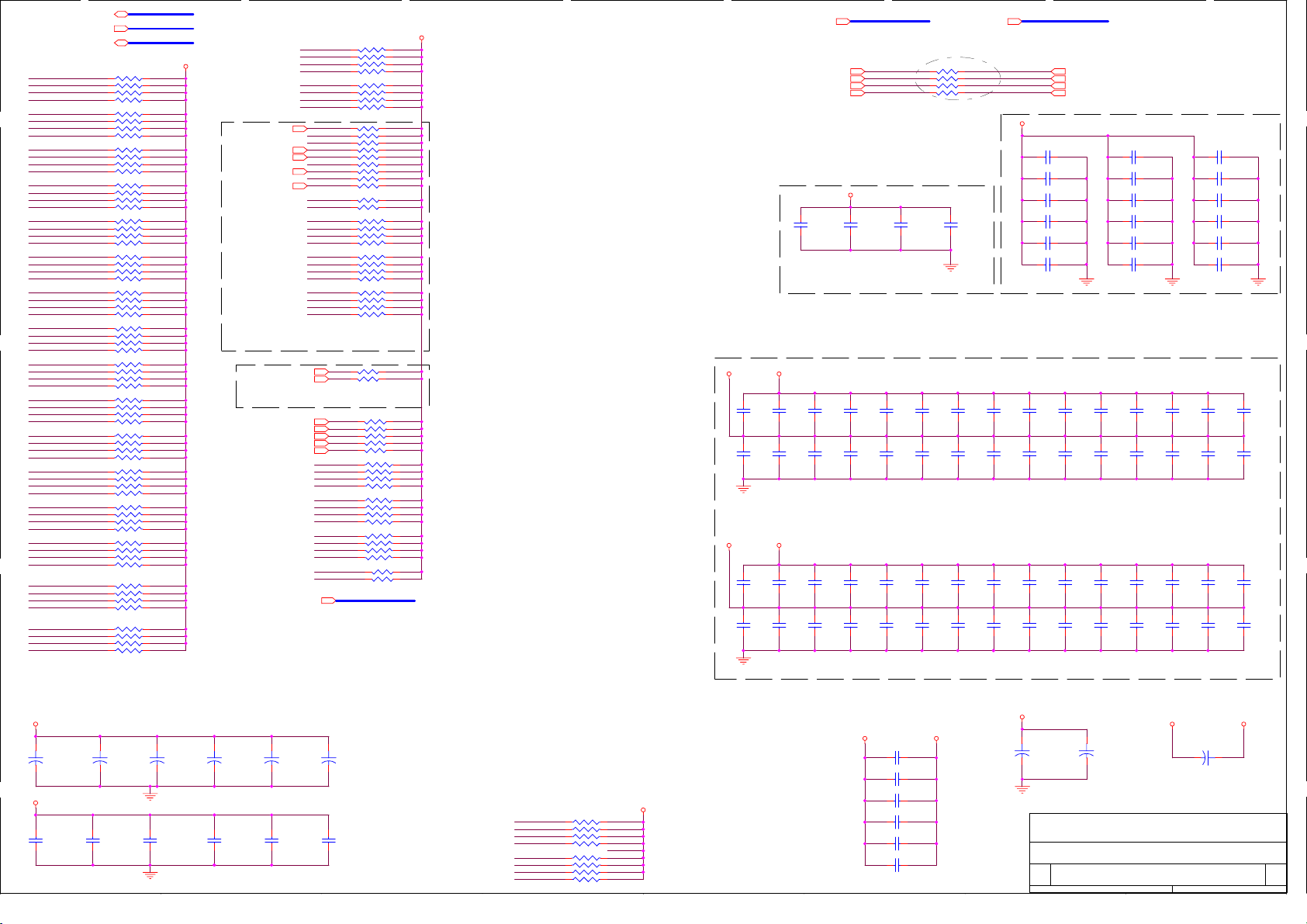

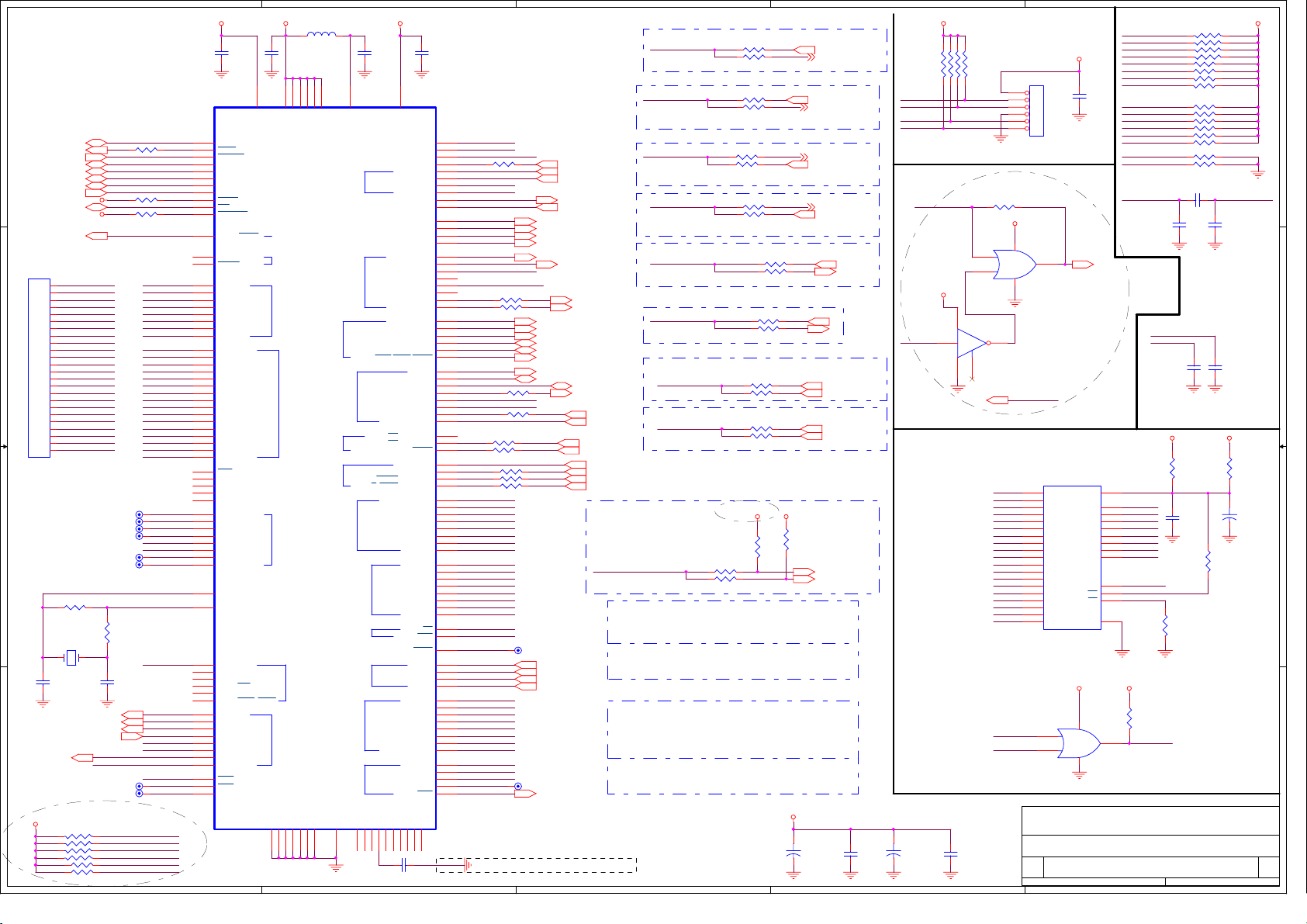

Page 2

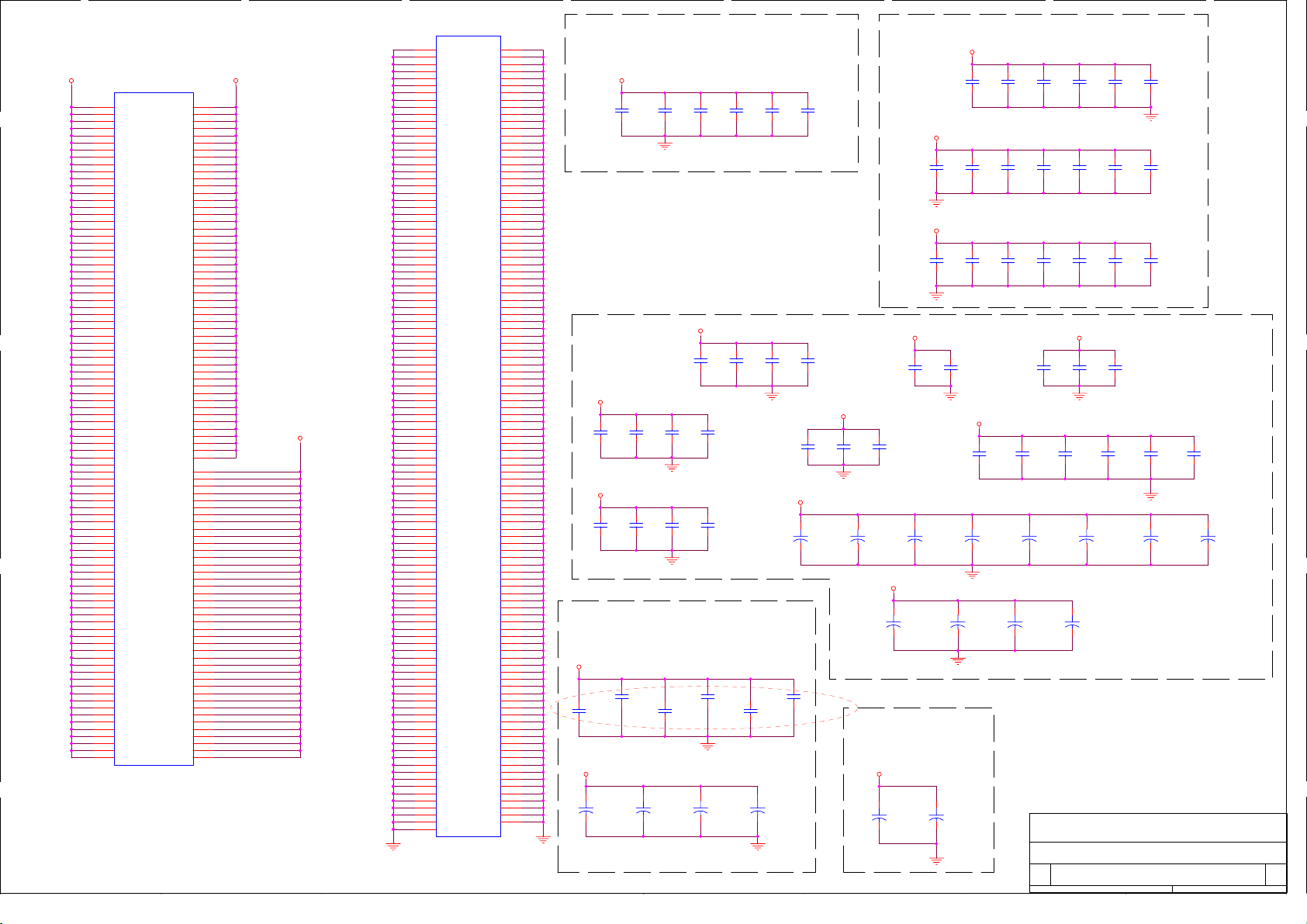

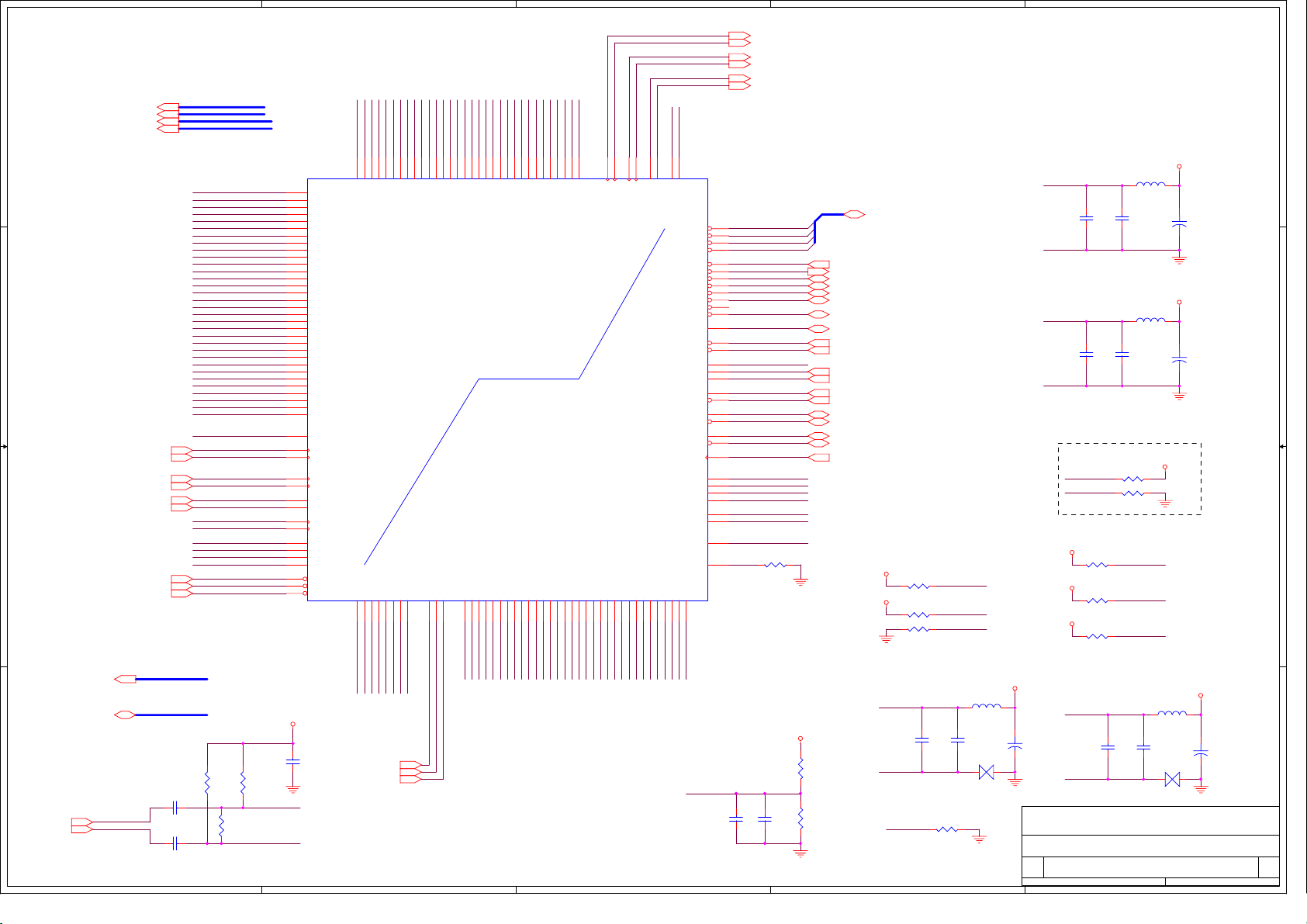

5

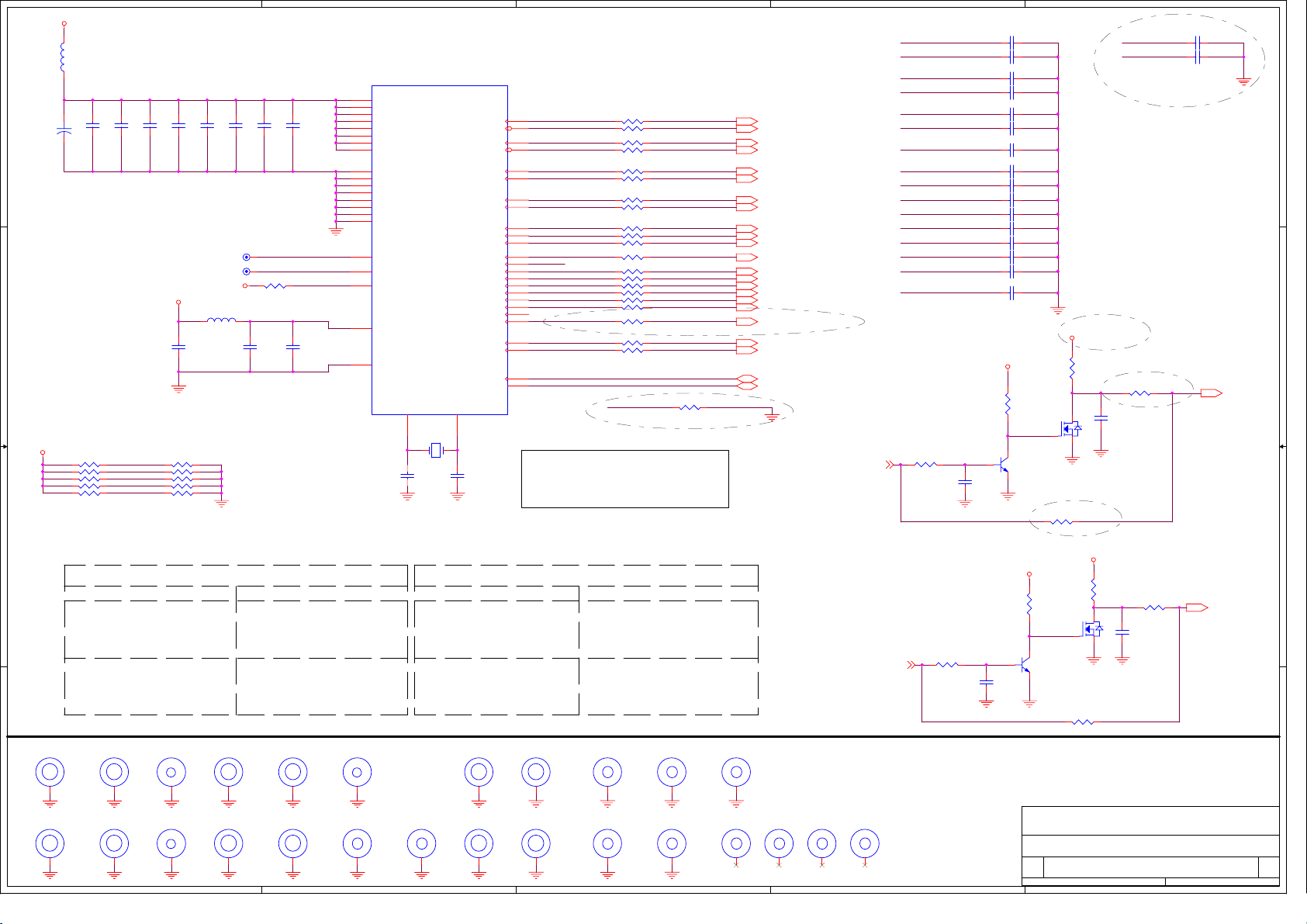

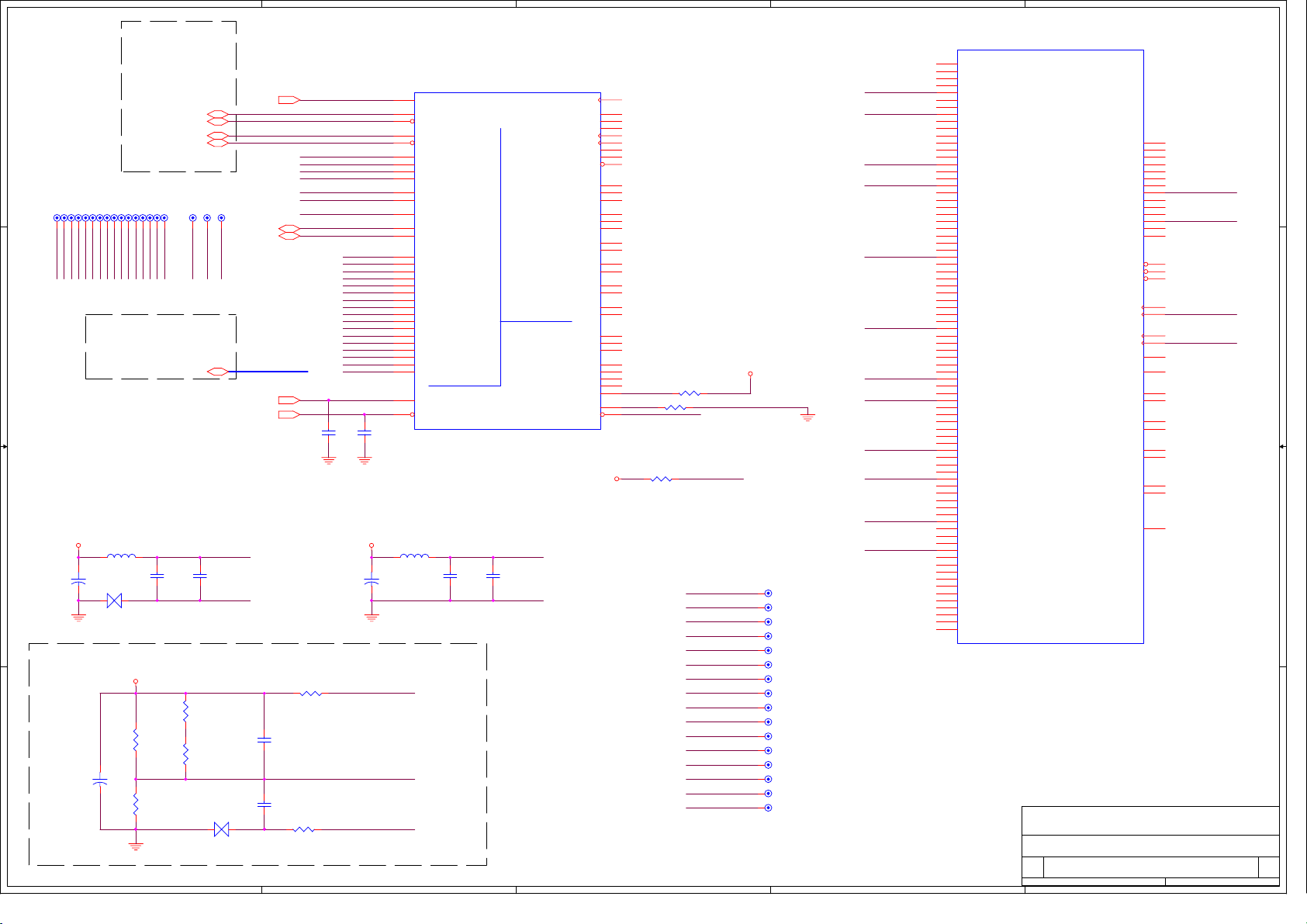

IOPA0

IOPA1

IOPA2

IOPA3

IOPA4

IOPA5

IOPA6

IOPA7

IOPB0

IOPB1

IOPB2

IOPB3

IOPB4

IOPB5

IOPB6

IOPB7

IOPC0

IOPC1

IOPC2

IOPC3

IOPC4

IOPC5

IOPC6

IOPC7

IOPD0

IOPD1

IOPD2

IOPD3

IOPD4

IOPD5

IOPD6

IOPD7

IOPE0

IOPE1

IOPE2

IOPE3

IOPE4

IOPE5

IOPE6

IOPE7

IOPF0

IOPF1

IOPF2

IOPF3

IOPF4

IOPF5

IOPF6

IOPF7

IOPH0

IOPH1

IOPH2

IOPH3

IOPH4

IOPH5

IOPH6

IOPH7

NS87551

GPIO

SUS_SKIP

BTL_BEEP

+1.8V_ON

NC

PWROK_CPUEC

NC

+3V_ON

S3_ON

PWRBTN#

PWROK1

MUTE#

SMBCLK_EC

SMBDAT_EC

NC

NC

M_DIS_BAT

LAN_DISABLE

SMBCLK_T

SMBDAT_T

S3AUXSW#

PSON#

CHG_LED#

SUS_LED#

LANLED#

NC

NC

PCIRST#

SCI#

PWR_LED#

CAPLED#

NUMLED#

SCROLED#

WWW#

E_MAIL#

LANSW#

PME#

PWRSW

ADAP_IN

TEMP

NC

NC

NC

NC

NC

TPCK

TPDAT

NC

NC

ROMA0

ROMA1

ROMA2

ROMA3

ROMA4

ROMA5

ROMA6

ROMA7

SIS963L

GPIO0

GPIO1

GPIO2

D D

GPIO3

GPIO4

GPIO5

GPIO6

GPIO7

GPIO8

GPIO9

GPIO10

GPIO11

GPIO12

GPIO13

GPIO14

GPIO15

GPIO16

GPIO17

GPIO18

C C

B B

A A

GPIO19

GPIO20

GPIO

NC

NC

THERMTRIP#

EXTSMI#

CLKRUN#

HDD/CDROM_RST#

NC

NC

PNLSW2

PNLSW0

PNLSW1

NC

NC

NC

S3AUXSW#

NC

NC

NC

32KHZ

SMBCLK

SMBDAT

5

4

NS87551

GPIO

IOPI0

IOPI1

IOPI2

IOPI3

IOPI4

IOPI5

IOPI6

IOPI7

IOPJ0

IOPJ1

IOPJ2

IOPJ3

IOPJ4

IOPJ5

IOPJ6

IOPJ7

IOPK0

IOPK1

IOPK2

IOPK3

IOPK4

IOPK5

IOPK6

IOPK7

IOPL0

IOPL1

IOPL2

IOPL3

IOPL4

IOPM0

IOPM1

IOPM2

IOPM3

IOPM4

IOPM5

IOPM6

IOPM7

AD0

AD1

AD2

AD3

ROMD0

ROMD1

ROMD2

ROMD3

ROMD4

ROMD5

ROMD6

ROMD7

ROMRD#

ROMWR0#

ROMWR1#

NC

NC

NC

NC

NC

ROMA8

ROMA9

ROMA10

ROMA11

ROMA12

ROMA13

ROMA14

ROMA15

ROMA16

ROMA17

ROMA18

NC

LCDSW

+1.2V_ON

+2.5V_DIMM_ON

CHG_ON

LID#

PAGE_UP#

PAGE_DN#

CORE_ON

NC

MB_ID

I_CPU

V_CPU

STOP_CHG#

3

CPU CORE(V)ICC(mA) TEMP( )

2.0G

1.525

1.5252.2G

2.26G

2.4G

2.5G

2.53G

2.6G

2.66G

2.8G

3.06G

VCC TEMP( )

1.525

1.525

1.525

1.525

1.525

1.525

1.525

1.525

ICC(mA)

+3V

+1.2V 88 0.1056

+1.8V

AGPVDD

VCC

ICC(mA)

+3V

+1.8V

+1.8V_AUX

+3V_AUX

RTCVDD

VTT(+1.8V)

ICC(mA)VCC

+3V

ICC(mA)VCC W

2

CPU

W

℃

+3V

SIS755

W

℃

+3V(DVDD) 70

+3V(AMPVDD) 36 0.118

100.2 0.4575

2208.2

401.7

2.1261

0.5107

70

VCC

SIS963L

TEMP( )

96

487

0.315

0.876

27

W

275 +3V

0.003

15

0.909

0.00001

0.027

℃

70

+3V

VCC0.049

PC87551

W

℃

TEMP( )

701300

PC87383

℃

50+3V

0.165

TEMP( )

70

1

RTL8201CL

ICC(mA)VCC

ALC655

ICC(mA)

71

ADM1032

0.56mW

OZ711MC1

ICC(mA)

30

W

WVCC

0.234

WICC

W

0.1

℃

TEMP( )

700.66200

TEMP( )

℃

TEMP( )

℃

150170uA

TEMP( )

℃

70

AD4

AD5

AD6

AD7

AD8

AD9

DA0

DA1

DA2

DA3

THERMDA_EC

THERMDC_EC

BRIGHTADJ

SET_I

FAN_CTRL1

FAN_CTRL0

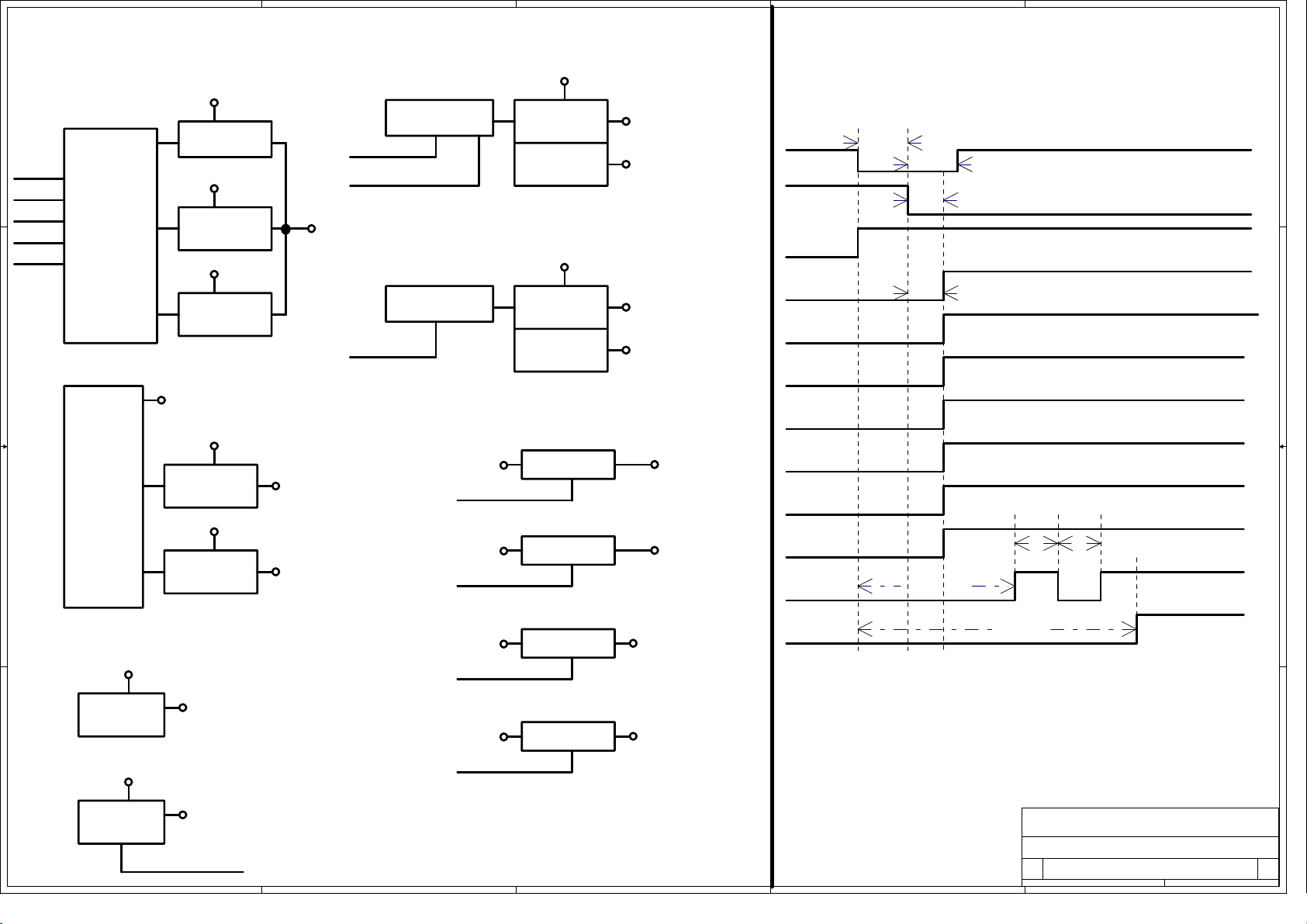

CLOCK GENERATOR

ICC(mA)VCC W

180+3V

0.594

TEMP( )

℃

70

UNIWILL COMPUTER CORP.

Title

GPIO DEFINITION & POWER CONSUMPTION

Size Document Number Rev

4

3

2

Date: Sheet

258KA0

1

242Tuesday, February 10, 2004

B

of

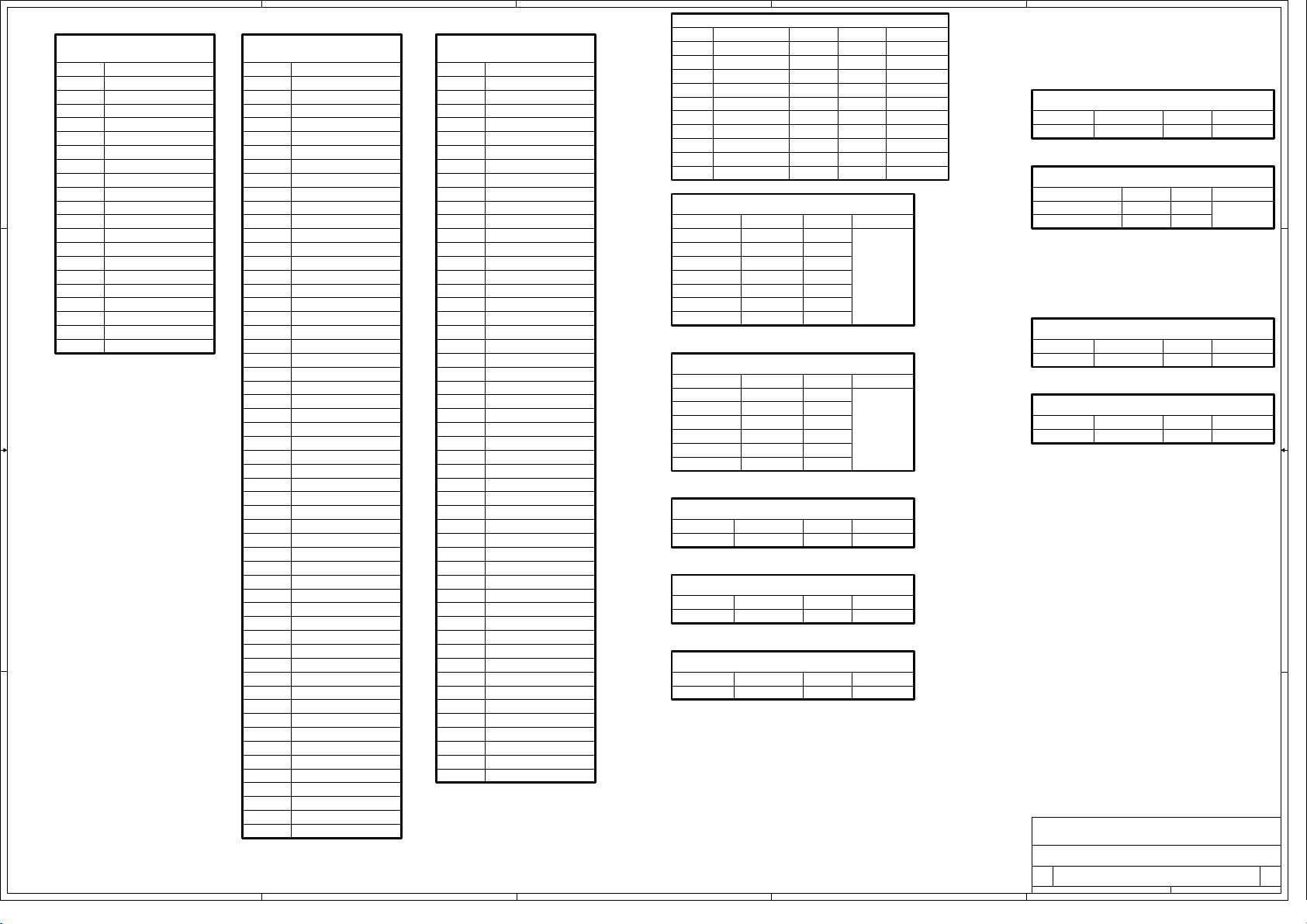

Page 3

5

4

3

2

1

DDR RAM BUS

CPUCLK

DDRCLK5

D D

DDR 1

DDRCLK5#

DDRCLK7#

DDRCLK4

DDRCLK6 DDRCLK6#DDRCLK7

DDR 2

DDRCLK4#

CPUCLK#

DDRCLK0

DDRCLK1

DDRCLK4

DDRCLK5

DDRCLK6

DDRCLK7

755CLK

755CLK#

AGPCLK0

755ZCLK

CPU

AMD ClawHammer

Socket 754

HyperTransport I/O BUS

North Bridge

SIS

755

DDRCLK0#

DDRCLK1#

DDRCLK4#

DDRCLK5#

DDRCLK6#

DDRCLK7#

AGP BUS

THERMAL

ADM 1032

VRAM x8

VRAM BUS

VGA

ATI

M11P

64M/128M/256M

VRAM

AGPCLK1

BLOCK DIAGRAM

258AA0

CRT

S-Video TV

LCD

15.0" XGA TFT

15.0" SXGA TFT

15.4" WXGA TFT

15.4" WSXGA TFT

Mutiol BUS

C C

AUDIO CODEC

Realtek

ALC655

MDC

RJ-11

AMPLIFIER

TI

TPA6011A4

AUDIO _CLK

LINE IN MICSPDIF

AC Link

PCI BUS

963ZCLK

963PCICLK

USB_48M

963OSCI

South Bridge

SIS

963L

RTC

L-SPKR R-SPKR

LAN(PHY)

REALTEK

RTL8201CL

CRYSTAL

25M HZ

CRYSTAL

32.768K

CRYSTAL

12M HZ

IDE BUS

RJ-45

HDD

2.5"

PRIMARY

MASTER

CD-ROM

DVD

CD-RW

COMBO

SECONDARY

MASTER

PCICLK_M

B B

Mini PCI

SCLK

CARDBUS

O2 MICRE

OZ711MC1

MMC/SD/MS

PCLK_CB

PCMCIA

CRYSTAL

24.576M HZ

READER

CRYSTAL

14.318MHz

CPUCLK

CPUCLK#

755CLK

755CLK#

A A

AGPCLK0

AGPCLK1

755ZCLK

963ZCLK

Clock Gen

ICS

ICS952802

USB_48M

383_48M

963PCICLK

PCICLK_CB

PCICLK_M

LPCCLK

PCICLK_EC

963OSCI

AUDIO _CLK

SCLK

5

383_48M

LPCCLK

4

LPC

NS

PC87383

PARALLEL

IEEE-1394

TI

TSB43AB22

1394

USB0 USB1

LPC BUS

CRYSTAL

32.768K

BIOS LED

INT K/BFIR

3

PCICLK_EC

USB2

K/B CONTROLLER

NS

PC87551

T/P

FAN

BATTERYCHARGER

DC/DC

UNIWILL COMPUTER CORP.

Title

Size Document Number Rev

2

Date: Sheet of

BLOCK DIAGRAM

258KA0

1

342Tuesday, February 10, 2004

B

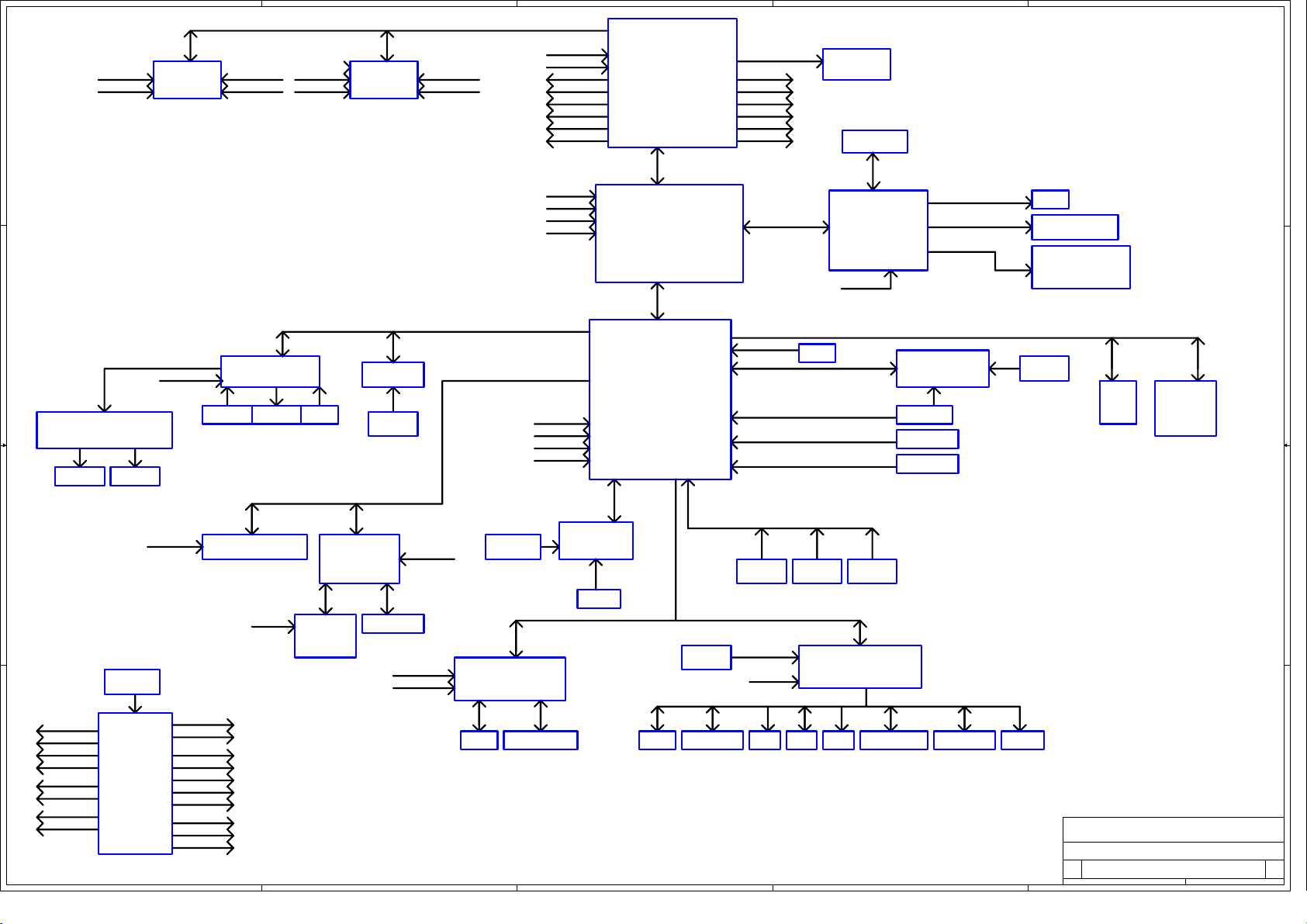

Page 4

5

4

3

2

1

POWER BLOCK DIAGRAM

VIN

POWER ON SEQUENCE

CORE_VIN

D D

VID0

VID1

RSS090N03

IRL7832

CORE_VIN

+3V_ON

+2.5V_DIMM_ON

VID2

VID3

MAX1937

RSS090N03

IRL7832

CPU_CORE/55A

VID4

CORE_VIN

RSS090N03

ISSL6225CA

IRL7832

C C

+3V_ON

RSS090N03ISSL6225CA +2.5V_DDR/6A

RSS090N03

AGP1.2V/7A

VIN

AOS4912

AOS4912

+1.8V_AUX/3.5A

AGPVDD/3.5A

PWRBTN#

PSON#

S3AUXSW#

+3V_ON

S3_ON

AGP_ON

68ms

66ms

44ms

44ms

44ms

44ms

+12V_AUX/100mA

CORE_ON

44ms

VINS_IO

MAX1902

RSS090N03

RSS090N03

+5V_AUX/6A

+5V_AUX

+3V_ON

RSS090N03

+5V

+1.2V_ON

+2.5V_DIMM_ON

44ms

44ms

VINS_IO

B B

RSS090N03

RSS090N03

+3V_AUX/6A

+3V_AUX

+3V_ON

RSS090N03

+3V

+1.8V_ON

PWROK_CPUEC

44ms

320ms

140ms 140ms

730ms

+2.5V_DDR

CM8562

+1.25V_DDR/2A

+1.8V_AUX

+3V_ON

+2.5V_DDR

RSS090N03

RSS090N03

+1.8V

+2.5V

PWROK1

+3V_ON

A A

+1.8V_AUX

CM8561

+1.2V_ON

5

+1.2V/0.8A

UNIWILL COMPUTER CORP.

Title

Size Document Number Rev

4

3

2

Date: Sheet of

POWER DIAGRAM & SEQUENCE

258KA0

1

442Tuesday, February 10, 2004

B

Page 5

5

+3V

THERM#30

THERMDA_EC14,31

D D

THERMDC_EC14,31

+1.2V

C952

0.22u/6.3V_0402

X7R

+1.25V_DDR

C956

0.22u/6.3V_0402

X7R

+2.5V_DDR

C C

B B

A A

+3V

DBREQ_L#

DBRDY

TCK

TMS

TDI

TRST_L

TDO

C960

0.22u/6.3V_0402

X7R

SMBCLK_ECC

SMBDAT_ECC

PC30

1u/10V_0603

+2.5V_DDR

R112 *680

R139 *0

THERMDA_CPU SMBDAT_ECC

C301

2200p X7R

THERMDC_CPU

R143 *0

C953

0.22u/6.3V_0402

X7R

C957

0.22u/6.3V_0402

X7R

C961

0.22u/6.3V_0402

X7R

+5V

Q7

G

2N7002

S

S

Q8

G

2N7002

PU3

AME8800DEFT

C E

VIN VOUT

GND

B

+2.5V_CPU

R102 *680

R89 *680

N.C.

R84 *680

5

C299

0.1u/10V

X7R

C954

0.22u/6.3V_0402

X7R

C958

0.22u/6.3V_0402

X7R

C962

0.22u/6.3V_0402

X7R

D

SMBCLK_T 31

D

SMBDAT_T 31

+2.5V/300mA

+2.5V_CPU

R81 *680

R77 *680

HDT Connectors

Change CN27 foot printer from M20-87616 to CN26-S

2

4

3

PC29

0.1u/16V

R75 *680

U7

D+

THERM#

D-

C955

0.22u/6.3V_0402

X7R

C959

0.22u/6.3V_0402

X7R

+2.5V_CPU

+2.5V

1

5

VDD

GND

ADATA

SCLK

ALERT

ADM1032

7

8

6

+2.5V_CPU

Ver:B

CN27

12

34

56

78

910

11 12

13 14

15 16

17 18

19 20

21 22

23 24

25 26

HDT CONNECTOR

SMBCLK_ECC

ALERT

ALERT

THERM#

SMBDAT_ECC

SMBCLK_ECC

VCORE_SENSE36

VSS_SENSE36

L14

QT1608RL060

C67

+

4.7u/10V_0805

Y5V

eight high frequncy cap. must close CPU side.

R151 4.7K

R150 4.7K

R145 4.7K

R141 4.7K

VCORE_SENSE

VSS_SENSE

+1.2V

C61

+

*100u/6.3V_TAN_B

0.22u/10V_0603

0.22u/10V_0603

4

+3V

CPU_CORE

R72 44.2_1%

R70 44.2_1%

C287

X7R

C292

X7R

4

PR55

10

PR56

10

C74

3300p

X7R

C135

1000p

X7R

C286

0.22u/10V_0603

X7R

C713

0.22u/10V_0603

LDTSTOP_L

PWROK_CPU

LDTREST#

TP86

TP87

NEAR 755

+1.2V

C77

0.22u/10V_0603

0.22u/10V_0603

X7R

C84

0.22u/10V_0603

X7R

C131

1000p

X7R

X7R

C76

X7R

TP83

TP84

TP85

L0_CADIN_H[0..15]11

L0_CADIN_L[0..15]11

CPUCLK8

CPUCLK#8

+2.5V_DDR

+2.5V

C75

0.22u/10V_0603

X7R

C712

0.22u/10V_0603

L0_CLKIN111

L0_CLKIN#111

+1.2V

VDDIOFB_H

VDDIOFB_L

VDD_2.5_SENSE

X7R

R130 49.9_1%

R131 49.9_1%

C68 3900p_0603

X7R

3900p_0603

X7R

C69

R69 820

R60 820

R430 680_1%

R429 680_1%

VDDIOFB_H34

VDDIOFB_L34

VDD_2.5_SENSE34

C687

0.1u/10V

X7R

C256

0.1u/10V

X7R

3

VCORE_SENSE36

VSS_SENSE36

LDTREST#11

PWROK_CPU8,36

LDTSTOP_L11,26

+1.2V

L0_CADIN_H15

L0_CADIN_H14

L0_CADIN_H13

L0_CADIN_H12

L0_CADIN_H11

L0_CADIN_H10

L0_CADIN_H9

L0_CADIN_H8

L0_CADIN_H7

L0_CADIN_H6

L0_CADIN_H5

L0_CADIN_H4

L0_CADIN_H3

L0_CADIN_H2

L0_CADIN_H1

L0_CADIN_H0

L0_CADIN_L15

L0_CADIN_L14

L0_CADIN_L13

L0_CADIN_L12

L0_CADIN_L11

L0_CADIN_L10

L0_CADIN_L9

L0_CADIN_L8

L0_CADIN_L7

L0_CADIN_L6

L0_CADIN_L5

L0_CADIN_L4

L0_CADIN_L3

L0_CADIN_L2

L0_CADIN_L1

L0_CADIN_L0

Z0501

Z0502

Z0503

Z0504

Z0505

Z0506

R49

169_1%_0603

Z0507

Z0508

Z0509

Z0510

Z0511 Z0514

TP92

TP93

TP94

TP95

CORE_SENSE

VDDIOFB_H

VDDIOFB_L

VDD_2.5_SENSE

C733

0.1u/10V

X7R

C708

0.1u/10V

X7R

3

U22A

D29

D27

D25

C28

C26

B29

B27

T25

U27

V25

W27

AA27

AB25

AC27

AD25

T27

V29

V27

Y29

AB29

AB27

AD29

AD27

R25

U26

U25

W26

AA26

AA25

AC26

AC25

T28

U29

V28

W29

AA29

AB28

AC29

AD28

Y25

W25

R27

R26

AH25

AJ25

AF27

AE26

AJ21

AH21

AJ23

AH23

AE24

AF24

C18

A19

C715

0.1u/10V

X7R

C710

0.1u/10V

X7R

VCORE_SENSE

VSS_SENSE

LDTREST#

PWROK_CPU

LDTSTOP_L

TDO

A28

AJ28

A22

TDO

KEY1

KEY0

VLDT0_A6

VLDT0_A5

VLDT0_A4

VLDT0_A3

VLDT0_A2

VLDT0_A1

VLDT0_A0

L0_CADIN_H15

L0_CADIN_H14

L0_CADIN_H13

L0_CADIN_H12

L0_CADIN_H11

L0_CADIN_H10

L0_CADIN_H9

L0_CADIN_H8

L0_CADIN_H7

L0_CADIN_H6

L0_CADIN_H5

L0_CADIN_H4

L0_CADIN_H3

L0_CADIN_H2

L0_CADIN_H1

L0_CADIN_H0

L0_CADIN_L15

L0_CADIN_L14

L0_CADIN_L13

L0_CADIN_L12

L0_CADIN_L11

L0_CADIN_L10

L0_CADIN_L9

L0_CADIN_L8

L0_CADIN_L7

L0_CADIN_L6

L0_CADIN_L5

L0_CADIN_L4

L0_CADIN_L3

L0_CADIN_L2

L0_CADIN_L1

L0_CADIN_L0

L0_CLKIN_H1

L0_CLKIN_L1

L0_CTLIN_H1

L0_CTLIN_L1

VDDA1

VDDA2

L0_REF1

L0_REF0

CLKIN_H

CLKIN_L

NC_AJ23

NC_AH23

NC_AE24

NC_AF24

NC_C18

NC_A19

CORE_SENSE

VDDIOFB_H

B23

AE12

AF12

+1.2V

C686

0.1u/10V

X7R

+1.2V

C709

0.1u/10V

X7R

VDDIOFB_L

AJ27

LDTSTOP_L

VDDIO_SENSE

AE11

AE18

+1.25V_DDR

TMS

TCK

TDI

TRST_L

AF20

A23

A24

PWROK

RESET_L

E20

E17

B21

A21

TDI

TCK

TRST_L

COREFB_L

COREFB_H

HYPER TRANSPORT - LINK0

FREE29

FREE31

FREE33

FREE35

FREE1

FREE37

FREE4

FREE38

FREE41

C1J3R3

AA2D3AG2

B18

AH1

AE21

C20

C689

C645

0.1u/10V

0.1u/10V

X7R

X7R

C676

C711

0.1u/10V

0.1u/10V

X7R

X7R

C15

TMS

NC_C15

FREE7

FREE11

AG4C6AG6

DBRDY

AG15

AH17

DBRDY

FREE12

+1.2V

+

C16

A20

VTT_A5

VTT_B5

FREE13

FREE14

FREE40

AE9

AG9

C261

220u/4V_KO

A26

A27

THERMDA

THERMDC

THERMTRIP_L

NC_AG17

NC_AJ18

AG17

AJ18

NC_AJ18

NC_AG17

+1.2V

+

220u/4V_KO

2

VID4

NC_AH18

AH18

C102

+

2

THERMTRIP_CPU_L

THERMDA_CPU

THERMDC_CPU

NC_D20

NC_C21

VID0

VID1

VID3

VID2

AG13

AF14

AG14

AF15

AE15

D20

C21

VID4

VID3

VID2

VID1

VID0

NC_D20

NC_AG18

FREE19

FREE42

FREE24

FREE25

FREE27

AG18

AG7

AE22

C24

A25

C9

C126

+

10u/6.3V_0805

X5R

C280

10u/6.3V_0805

X5R

VID[0..4] 36

NC_D18

NC_C19

NC_B19

D18

C19

B19

NC_B19

NC_C21

NC_D18

NC_C19

VLDT0_B6

VLDT0_B5

VLDT0_B4

VLDT0_B3

VLDT0_B2

VLDT0_B1

VLDT0_B0

L0_CADOUT_H15

L0_CADOUT_H14

L0_CADOUT_H13

L0_CADOUT_H12

L0_CADOUT_H11

L0_CADOUT_H10

L0_CADOUT_H9

L0_CADOUT_H8

L0_CADOUT_H7

L0_CADOUT_H6

L0_CADOUT_H5

L0_CADOUT_H4

L0_CADOUT_H3

L0_CADOUT_H2

L0_CADOUT_H1

L0_CADOUT_H0

L0_CADOUT_L15

L0_CADOUT_L14

L0_CADOUT_L13

L0_CADOUT_L12

L0_CADOUT_L11

L0_CADOUT_L10

L0_CADOUT_L9

L0_CADOUT_L8

L0_CADOUT_L7

L0_CADOUT_L6

L0_CADOUT_L5

L0_CADOUT_L4

L0_CADOUT_L3

L0_CADOUT_L2

L0_CADOUT_L1

L0_CADOUT_L0

L0_CLKOUT_H1

L0_CLKOUT_L1

L0_CLKOUT_H0

L0_CLKOUT_L0

L0_CTLOUT_H1

L0_CTLOUT_L1

L0_CTLOUT_H0

L0_CTLOUT_L0

L0_CTLIN_L0

L0_CTLIN_H0

L0_CLKIN_L0

L0_CLKIN_H0

G_FBCLKOUT_H

G_FBCLKOUT_L

DBREQ_L

NC_AF21

NC_AF22

NC_AF23

NC_AE23

FREE32

FREE34

FREE36

FREE10

FREE18

+

C240

+

4.7u/10V_0805

Y5V

AF18

D22

C22B13

NC_AF18

RSVD_SCL

RSVD_SDAFREE26

FREE28

FREE30

B7C3K1R2AA3F3C23

C83

4.7u/10V_0805

Y5V

1

Low active to short

down system.

THERMTRIP_CPU_L_S23

CORE_ON31,36

THERMTRIP_CPU_L_S

R427 *0

+2.5V

For debug only

R428

TP88

TP90

Ver: B

C276

39p

NPO

C657

39p

NPO

R55

80.6_1%

0

+1.2V

+1.2V

AH29

AH27

AG28

AG26

AF29

AE28

AF25

L0_CADOUT_H15

N26

L0_CADOUT_H14

L25

L0_CADOUT_H13

L26

L0_CADOUT_H12

J25

L0_CADOUT_H11

G25

L0_CADOUT_H10

G26

L0_CADOUT_H9

E25

L0_CADOUT_H8

E26

L0_CADOUT_H7

N29

L0_CADOUT_H6

M28

L0_CADOUT_H5

L29

L0_CADOUT_H4

K28

L0_CADOUT_H3

H28

L0_CADOUT_H2

G29

L0_CADOUT_H1

F28

L0_CADOUT_H0

E29

L0_CADOUT_L15

N27

L0_CADOUT_L14

M25

L0_CADOUT_L13

L27

L0_CADOUT_L12

K25

L0_CADOUT_L11

H25

L0_CADOUT_L10

G27

L0_CADOUT_L9

F25

L0_CADOUT_L8

E27

L0_CADOUT_L7

P29

L0_CADOUT_L6

M27

L0_CADOUT_L5

M29

L0_CADOUT_L4

K27

L0_CADOUT_L3

H27

L0_CADOUT_L2

H29

L0_CADOUT_L1

F27

L0_CADOUT_L0

F29

J26

J27

J29

K29

L0_CTLOUT1

N25

L0_CTLOUT#1

P25

P28

P27

L0_CTLIN#0

R29

L0_CTLIN0

T29

L0_CLKIN#0

Y28

L0_CLKIN0

Y27

AH19

AJ19

DBREQ_L#

AE19

Z0512 FBCLKOUT_L

AF21

Z0513

AF22

AF23

Z0515

AE23

R56 820

L0_CLKOUT1 11

L0_CLKOUT#1 11

L0_CLKOUT0 11

L0_CLKOUT#0 11

TP89

TP91

L0_CTLOUT0 11

L0_CTLOUT#0 11

L0_CTLIN#0 11

L0_CTLIN0 11

L0_CLKIN#0 11

L0_CLKIN0 11

R58 820

R64 820

NC_AJ18

NC_AG17

NC_D20

NC_C21

NC_D18

NC_C19

NC_B19

THERMTRIP_CPU_L

R62 820

L0_CADOUT_H[0..15] 11

CPU_CORE

L0_CADOUT_L[0..15] 11

NEAR CPU

FBCLKOUT_H

R48 680

R39 680

R420 680

R419 680

R124 680

R422 680

R421 680

UNIWILL COMPUTER CORP.

Title

Size Document Number Rev

Date: Sheet

2445

ATHLON64-HT

258KA0

542Tuesday, February 10, 2004

1

of

R426

680

B

Page 6

C234

39p

NPO

C89

+

10u/6.3V_0805

X5R

C452

+

*220u/4V_KO

C214

+

4.7u/16V_1206

Y5V

C133

X7R

EMI

C145

39p

NPO

C72

+

10u/6.3V_0805

X5R

+1.25V_DDR

C70

+

220u/4V_KO

C674

+

560u/4V_8*12.5

C118

+

4.7u/16V_1206

Y5V

C186

0.22u/10V_0603

X7R

C218

39p

NPO

C71

+

10u/6.3V_0805

X5R

C206

+

4.7u/16V_1206

Y5V

C142

X7R

0.22u/10V_0603

1

C212

39p

NPO

0.22u/10V_0603

C104

+

10u/6.3V_0805

X5R

C152

X7R

C366

39p

NPO

8

+1.25V_DDR_SENSE

+1.25V_DDR_SENSE34

+2.5V_DDR

D D

C C

B B

+1.25V_DDR_SENSE

DDRVREF_CPU

R123 34.8_1%

R122 34.8_1%

MAB0

MAB1

MAB2

MAB3

MAB4

MAB5

MAB6

MAB7

MAB8

MAB9

MAB10

MAB11

MAB12

MAB13

TP96

Z0601

Z0602

MMDATA63

MMDATA62

MMDATA61

MMDATA60

MMDATA59

MMDATA58

MMDATA57

MMDATA56

MMDATA55

MMDATA54

MMDATA53

MMDATA52

MMDATA51

MMDATA50

MMDATA49

MMDATA48

MMDATA47

MMDATA46

MMDATA45

MMDATA44

MMDATA43

MMDATA42

MMDATA41

MMDATA40

MMDATA39

MMDATA38

MMDATA37

MMDATA36

MMDATA35

MMDATA34

MMDATA33

MMDATA32

MMDATA31

MMDATA30

MMDATA29

MMDATA28

MMDATA27

MMDATA26

MMDATA25

MMDATA24

MMDATA23

MMDATA22

MMDATA21

MMDATA20

MMDATA19

MMDATA18

MMDATA17

MMDATA16

MMDATA15

MMDATA14

MMDATA13

MMDATA12

MMDATA11

MMDATA10

MMDATA9

MMDATA8

MMDATA7

MMDATA6

MMDATA5

MMDATA4

MMDATA3

MMDATA2

MMDATA1

MMDATA0

AE13

AG12

AG3

AE2

AH3

AH9

AG5

AH5

AJ10

AH11

AJ11

AH15

AJ15

AG11

AJ12

AJ14

AJ16

AB3

AA5

AD4

AC5

AD5

D14

C14

A16

B15

A12

B11

A17

A15

C13

A11

A10

C11

AC1

AC3

AC2

AD1

AE1

AE3

AJ4

AF1

AJ3

AJ5

AJ6

AJ7

AJ9

AF4

AF6

U22B

B9

C7

A6

A9

A5

B5

C5

A4

E2

E1

A3

B3

E3

F1

G2

G1

L3

L1

G3

J2

L2

M1

W1

W3

W2

Y1

M3

T4

U5

W5

Y4

M4

E9

U2

U1

P1

N2

V1

U3

N1

N3

A A

7

VTT_SENSE

MEMVREF1

MEMZN

MEMZP

MEMDATA63

MEMDATA62

MEMDATA61

MEMDATA60

MEMDATA59

MEMDATA58

MEMDATA57

MEMDATA56

MEMDATA55

MEMDATA54

MEMDATA53

MEMDATA52

MEMDATA51

MEMDATA50

MEMDATA49

MEMDATA48

MEMDATA47

MEMDATA46

MEMDATA45

MEMDATA44

MEMDATA43

MEMDATA42

MEMDATA41

MEMDATA40

MEMDATA39

MEMDATA38

MEMDATA37

MEMDATA36

MEMDATA35

MEMDATA34

MEMDATA33

MEMDATA32

MEMDATA31

MEMDATA30

MEMDATA29

MEMDATA28

MEMDATA27

MEMDATA26

MEMDATA25

MEMDATA24

MEMDATA23

MEMDATA22

MEMDATA21

MEMDATA20

MEMDATA19

MEMDATA18

MEMDATA17

MEMDATA16

MEMDATA15

MEMDATA14

MEMDATA13

MEMDATA12

MEMDATA11

MEMDATA10

MEMDATA9

MEMDATA8

MEMDATA7

MEMDATA6

MEMDATA5

MEMDATA4

MEMDATA3

MEMDATA2

MEMDATA1

MEMDATA0

MEMADDB0

MEMADDB1

MEMADDB2

MEMADDB3

MEMADDB4

MEMADDB5

MEMADDB6

MEMADDB7

MEMADDB8

MEMADDB9

MEMADDB10

MEMADDB11

MEMADDB12

MEMADDB13

MEMCHECK0

MEMCHECK1

MEMCHECK2

MEMCHECK3

MEMCHECK4

MEMCHECK5

MEMCHECK6

MEMCHECK7

MEMORY INTERFACE

VTT_A4

VTT_A1

VTT_A2

VTT_A3

VTT_B1

VTT_B2

VTT_B3

VTT_B4

MEMRESET_L

MEMCKEA

MEMCKEB

MEMCLK_H7

MEMCLK_H6

MEMCLK_H5

MEMCLK_H4

MEMCLK_H3

MEMCLK_H2

MEMCLK_H1

MEMCLK_H0

MEMCLK_L7

MEMCLK_L6

MEMCLK_L5

MEMCLK_L4

MEMCLK_L3

MEMCLK_L2

MEMCLK_L1

MEMCLK_L0

MEMCS_L7

MEMCS_L6

MEMCS_L5

MEMCS_L4

MEMCS_L3

MEMCS_L2

MEMCS_L1

MEMCS_L0

MEMRASA_L

MEMCASA_L

MEMWEA_L

MEMBANKA1

MEMBANKA0

RSVD_MEMADDA15

RSVD_MEMADDA14

MEMADDA13

MEMADDA12

MEMADDA11

MEMADDA10

MEMADDA9

MEMADDA8

MEMADDA7

MEMADDA6

MEMADDA5

MEMADDA4

MEMADDA3

MEMADDA2

MEMADDA1

MEMADDA0

MEMRASB_L

MEMCASB_L

MEMWEB_L

MEMBANKB1

MEMBANKB0

MEMDQS0

MEMDQS1

MEMDQS2

MEMDQS3

MEMDQS4

MEMDQS5

MEMDQS6

MEMDQS7

MEMDQS8

MEMDQS9

MEMDQS10

MEMDQS11

MEMDQS12

MEMDQS13

MEMDQS14

MEMDQS15

MEMDQS16

MEMDQS17

RSVD_MEMADDB15

RSVD_MEMADDB14

D17

A18

B17

C17

AF16

AG16

AH16

AJ17

AG10

AE8

AE7

D10

E12

AF8

AF10

V3

K5

R5

P3

C10

E11

AG8

AE10

V4

K4

P5

P4

D8

C8

E8

E7

D6

E6

C4

E5

H5

D4

G5

K3

H3

E13

C12

E10

AE6

AF3

M5

AE5

AB5

AD3

Y5

AB4

Y3

V5

T5

T3

N5

H4

F5

F4

L5

J5

AJ13

AJ8

AJ2

AB1

J1

D1

A8

A14

T1

AH13

AH7

AG1

AA1

H1

C2

A7

A13

R1

E14

D12

6

+1.25V_DDR

MEMRESET_L

MMCKEA

MMCKEB

MEMCLK_H7

MEMCLK_H6

MEMCLK_H5

MEMCLK_H4

MEMCLK_H3

MEMCLK_H2

MEMCLK_H1

MEMCLK_H0

MEMCLK_L7

MEMCLK_L6

MEMCLK_L5

MEMCLK_L4

MEMCLK_L3

MEMCLK_L2

MEMCLK_L1

MEMCLK_L0

MEMCS_L3

MEMCS_L2

MEMCS_L1

MEMCS_L0

MAA13

MAA12

MAA11

MAA10

MAA9

MAA8

MAA7

MAA6

MAA5

MAA4

MAA3

MAA2

MAA1

MAA0

MMDQS0

MMDQS1

MMDQS2

MMDQS3

MMDQS4

MMDQS5

MMDQS6

MMDQS7

Z0603

MEMDQS9

MEMDQS10

MEMDQS11

MEMDQS12

MEMDQS13

MEMDQS14

MEMDQS15

MEMDQS16

Z0604

TP102

MEMCLK_H7 9,10

MEMCLK_H6 9,10

MEMCLK_H5 9,10

MEMCLK_H4 9,10

MEMCLK_L7 9,10

MEMCLK_L6 9,10

MEMCLK_L5 9,10

MEMCLK_L4 9,10

MEMRASA_L 9,10

MEMCASA_L 9,10

MEMW EA_L 9,10

MEMBANKA1 9,10

MEMBANKA0 9,10

MEMRASB_L 9,10

MEMCASB_L 9,10

MEMW EB_L 9,10

MEMBANKB1 9,10

MEMBANKB0 9,10

TP106

TP107

5

MEMDQS[9..16]

MMDQS[0..7]

MMDATA[0..63]

MAA[0..13]

MAB[0..13]

MEMCLK_H0

MEMCLK_H1

MEMCLK_H3

MEMCLK_H2

MEMCLK_L3

MEMCLK_L2

MEMCLK_L1

MEMCLK_L0

MEMCS_L[0..3] 9,10

+1.25V_DDR

C78 1u/10V_0603

C726 1u/10V_0603

C438 1000p

C704 1000p

C702 100p

MEMCKEA9,10

MEMCKEB9,10

Y5V

Y5V

X7R

X7R

NPO

+2.5V_DDR+1.25V_DDR

C722 1u/10V_0603

Y5V

C651 1u/10V_0603

Y5V

C725 1u/10V_0603

Y5V

C723 1u/10V_0603

Y5V

C771 0.1u/10V

X7R

MEMDQS[9..16] 9

MMDQS[0..7] 9

MMDATA[0..63] 9

MAA[0..13] 9,10

MAB[0..13] 9,10

TP97

TP98

TP99

TP100

TP101

TP103

TP104

TP105

MEMCKEA

MEMCKEB

MEMCLK_L1

MEMCLK_L0

MEMCLK_H1

MEMCLK_H0

4

+2.5V_DDR

R45

75_1%

R37

75_1%

R66 10

R65 10

R87 10K_1%

R95 10K_1%

R86 10K_1%

R99 10K_1%

+1.25V_DDR +2.5V_DDR

C80

0.1u/10V

X7R

C65

0.1u/10V

X7R

MMCKEA

MMCKEB

+2.5V_DDR

+1.25V_DDR

C718 1u/10V_0603

Y5V

C717 1u/10V_0603

Y5V

C749 1000p

X7R

C460 1000p

X7R

C750 100p

NPO

C781 0.22u/10V_0603

X7R

C662 0.22u/10V_0603

X7R

C501 0.22u/10V_0603

X7R

C779 0.22u/10V_0603

X7R

C482 0.22u/10V_0603

X7R

C777 0.22u/10V_0603

X7R

C417 0.22u/10V_0603

X7R

C780 0.22u/10V_0603

X7R

C503 0.22u/10V_0603

X7R

C705 0.22u/10V_0603

X7R

C706 0.22u/10V_0603

X7R

C81

1000p

X7R

C66

1000p

X7R

C79

0.1u/10V

X7R

C63

0.1u/10V

X7R

3

DDRVREF_CPU

C64

0.1u/10V

X7R

+

0.22u/10V_0603

+

C156

4.7u/16V_1206

Y5V

+2.5V_DDR

C107

X7R

C105

10u/6.3V_0805

X5R

C138

+

4.7u/16V_1206

Y5V

X7R

0.22u/10V_0603

2

+2.5V_DDR

C233

39p

NPO

+2.5V_DDR

C73

+

10u/6.3V_0805

X5R

C275

+

10u/6.3V_0805

X5R

Put near Athlon 64

C185

+

220u/4V_KO

C198

+

4.7u/16V_1206

Y5V

C428

C100

0.22u/10V_0603

X7R

C431

+

10u/6.3V_0805

X5R

+2.5V_DDR

+2.5V_DDR

0.22u/10V_0603

UNIWILL COMPUTER CORP.

Title

Size Document Number Rev

8

7

6

5

4

3

Date: Sheet

2445

2

ATHLON64-DDR

258KA0

642Tuesday, February 10, 2004

B

of

1

Page 7

8

U22C

L7

VDD1

AC15

VDD2

AB14

AA15

AB16

AA17

AC17

AE17

AB18

AD18

AG19

AC19

AA19

AB20

AD20

AA21

AC21

AB22

AD22

AA23

AC23

AB24

AD24

AH24

AE25

G13

G15

G17

G19

M20

G21

W21

M22

G23

W23

M24

H18

VDD3

B20

VDD4

E21

VDD5

H22

VDD6

J23

VDD7

H24

VDD8

F26

VDD9

N7

VDD10

L9

VDD11

V10

VDD12

VDD13

K14

VDD14

Y14

VDD15

VDD16

VDD17

J15

VDD18

VDD19

H16

VDD20

K16

VDD21

Y16

VDD22

VDD23

VDD24

J17

VDD25

VDD26

VDD27

VDD28

F18

VDD29

K18

VDD30

Y18

VDD31

VDD32

VDD33

VDD34

E19

VDD35

VDD36

VDD39

VDD38

J19

VDD37

F20

VDD40

H20

VDD41

K20

VDD42

VDD43

P20

VDD44

T20

VDD45

V20

VDD46

Y20

VDD47

VDD48

VDD49

VDD50

J21

VDD51

L21

VDD52

N21

VDD53

R21

VDD54

U21

VDD55

VDD56

VDD57

VDD58

F22

VDD59

K22

VDD60

VDD61

P22

VDD62

T22

VDD63

V22

VDD64

Y22

VDD65

VDD66

VDD67

E23

VDD68

VDD69

L23

VDD70

N23

VDD71

R23

VDD72

U23

VDD73

VDD74

VDD75

VDD76

B24

VDD77

D24

VDD78

F24

VDD79

K24

VDD80

VDD81

P24

VDD82

T24

VDD83

V24

VDD84

Y24

VDD85

VDD86

VDD87

VDD88

VDD89

K26

VDD90

P26

VDD91

V26

VDD92

D D

C C

B B

VDDIO1

VDDIO2

VDDIO3

VDDIO4

VDDIO5

VDDIO7

VDDIO8

VDDIO9

VDDIO10

VDDIO11

VDDIO12

VDDIO13

VDDIO14

VDDIO15

VDDIO16

VDDIO17

VDDIO18

VDDIO19

VDDIO20

VDDIO21

VDDIO22

VDDIO23

VDDIO24

VDDIO25

VDDIO26

VDDIO27

VDDIO28

VDDIO29

VDDIO30

VDDIO31

VDDIO32

VDDIO33

VDDIO34

VDDIO35

VDDIO36

VDDIO37

VDDIO38

VDDIO39

VDDIO40

VDDIO41

VDDIO42

VDDIO43

VDDIO44

VDDIO45

VDDIO46

VDDIO47

VDDIO48

VDDIO49

VDDIO50

VDDIO6

VDD96

VDD97

VDD98

VDD99

VDD100

VDD101

VDD102

VDD103

VDD104

VDD105

VDD106

VDD107

VDD108

VDD109

VDD110

VDD111

VDD112

VDD113

VDD114

VDD115

VDD116

VDD117

VDD118

VDD119

VDD120

VDD121

VDD122

VDD123

VDD124

VDD125

VDD126

VDD127

VDD128

VDD129

VDD130

VDD131

VDD132

VDD133

VDD93

VDD94

VDD95

POWER

A A

8

E4

G4

J4

L4

N4

U4

W4

AA4

AC4

AE4

D5

AF5

F6

H6

K6

M6

P6

T6

V6

Y6

AB6

AD6

D7

G7

J7

AA7

AC7

AF7

F8

H8

AB8

AD8

D9

G9

AC9

AF9

F10

AD10

D11

AF11

F12

AD12

D13

AF13

F14

AD14

F16

AD16

D15

R4

N28

U28

AA28

AE27

R7

U7

W7

K8

M8

P8

T8

V8

Y8

J9

N9

R9

U9

W9

AA9

H10

K10

M10

P10

T10

Y10

AB10

G11

J11

AA11

AC11

H12

K12

Y12

AB12

J13

AA13

AC13

H14

AB26

E28

J28

7

+2.5V_DDRCPU_CORE

CPU_CORE

7

6

U22D

AH20

AB21

W22

M23

AG25

AG27

AF2

AA8

AB9

AA10

AE16

G20

R20

U20

W20

AA20

AC20

AE20

AG20

AJ20

D21

H21

M21

AD21

AG21

G22

N22

R22

U22

AG29

AA22

AC22

AG22

AH22

AJ22

D23

H23

AB23

AD23

AG23

G24

N24

R24

U24

W24

AA24

AC24

AG24

AJ24

C25

D26

H26

M26

AD26

AF26

AH26

C27

D28

G28

H15

AB17

AD17

G18

AA18

AC18

D19

H19

AB19

AD19

AF19

N20

B2

VSS1

VSS3

VSS4

VSS5

VSS6

L24

VSS7

VSS8

VSS9

D2

VSS10

VSS11

W6

VSS12

Y7

VSS13

VSS14

VSS15

VSS16

J12

VSS17

B14

VSS18

Y15

VSS19

VSS20

J18

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

F21

VSS32

VSS33

K21

VSS34

VSS35

P21

VSS36

T21

VSS37

V21

VSS38

Y21

VSS39

VSS40

VSS41

B22

VSS42

E22

VSS43

VSS44

J22

VSS45

L22

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

F23

VSS57

VSS58

K23

VSS59

P23

VSS60

T23

VSS61

V23

VSS62

Y23

VSS63

VSS64

VSS65

VSS66

E24

VSS67

VSS68

J24

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

B25

VSS78

VSS79

B26

VSS80

VSS81

VSS82

VSS83

T26

VSS84

Y26

VSS85

VSS86

VSS87

VSS88

VSS89

B28

VSS90

VSS91

VSS92

F15

VSS187

VSS188

VSS206

VSS207

B16

VSS208

VSS209

VSS210

VSS211

VSS212

F19

VSS213

VSS214

K19

VSS215

Y19

VSS216

VSS217

VSS218

VSS219

J20

VSS220

L20

VSS221

VSS222

GROUND

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

VSS161

VSS162

VSS163

VSS164

VSS165

VSS166

VSS167

VSS168

VSS169

VSS170

VSS171

VSS172

VSS173

VSS174

VSS175

VSS176

VSS177

VSS178

VSS179

VSS180

VSS181

VSS182

VSS183

VSS184

VSS185

VSS186

VSS189

VSS190

VSS191

VSS192

VSS194

VSS195

VSS196

VSS197

VSS198

VSS199

VSS223

VSS201

VSS202

VSS203

VSS204

VSS205

L28

R28

W28

AC28

AF28

AH28

C29

F2

H2

K2

M2

P2

T2

V2

Y2

AB2

AD2

AH2

B4

AH4

B6

G6

J6

L6

N6

R6

U6

AA6

AC6

AH6

F7

H7

K7

M7

P7

T7

V7

AB7

AD7

B8

G8

J8

L8

N8

R8

U8

W8

AC8

AH8

F9

H9

K9

M9

P9

T9

V9

Y9

AD9

B10

G10

J10

L10

N10

R10

U10

W10

AC10

AH10

F11

H11

K11

Y11

AB11

AD11

B12

G12

AA12

AC12

AH12

F13

H13

K13

Y13

AB13

AD13

AF17

G14

J14

AA14

AC14

AE14

D16

E15

K15

AB15

AD15

AH14

E16

G16

J16

AA16

AC16

AE29

AJ26

E18

F17

H17

K17

Y17

6

5

4

Put on in uPGA Socket cavity.

CPU_CORE

C211

0.1u/10V

X7R

C149

0.1u/10V

X7R

C217

0.1u/10V

X7R

Put near Socket

CPU_CORE

C167

0.1u/10V

X7R

CPU_CORE

C273

C169

0.1u/10V

0.1u/10V

X7R

X7R

CPU_CORE

C228

C241

0.1u/10V

0.1u/10V

X7R

X7R

Put near CPU Socket

cavity Bottom Side

CPU_CORE

0.22u/10V_0603

C137

C664

X7R

X7R

0.22u/10V_0603

CPU_CORE

+

C195

10u/6.3V_0805

X5R

0.22u/10V_0603

C208

+

10u/6.3V_0805

X5R

5

C204

0.1u/10V

X7R

C164

0.1u/10V

X7R

0.22u/10V_0603

C197

X7R

C200

+

10u/6.3V_0805

X5R

C224

0.1u/10V

X7R

C199

0.1u/10V

X7R

C170

X7R

10u/6.3V_0805

4

C247

0.1u/10V

X7R

C165

0.1u/10V

X7R

+

C658

X7R

C175

0.1u/10V

X7R

C210

0.1u/10V

X7R

CPU_CORE

+

0.22u/10V_0603

C187

10u/6.3V_0805

X5R

C239

0.1u/10V

X7R

C166

0.1u/10V

X7R

C365

0.1u/10V

X7R

C103

4.7u/16V_1206

Y5V

C150

X7R

3

0.22u/10V_0603

+1.25V_DDR

+2.5V_DDR

C144

C232

0.1u/10V

0.1u/10V

X7R

X7R

C202

4.7u/16V_1206

Y5V

CPU_CORE

+

CPU_CORE

C139

+

10u/6.3V_1206

X5R

+

C220

10u/6.3V_1206

X5R

+

Put near CPU Socket

cavity TOP Side

3

2

Put on the Backside of the Processor

CPU_CORE

10u/6.3V_0805

CPU_CORE

0.22u/10V_0603

C207

X7R

CPU_CORE

C188

0.1u/10V

X7R

C703

0.1u/10V

X7R

C153

4.7u/16V_1206

Y5V

+

C221

+

10u/6.3V_1206

X5R

C669

X7R

C237

X7R

C183

0.1u/10V

X7R

C488

0.1u/10V

X7R

CPU_CORE

C155

+

4.7u/16V_1206

Y5V

C154

10u/6.3V_1206

X5R

C663

10u/6.3V_0805

0.22u/10V_0603

0.22u/10V_0603

C192

39p

NPO

C668

X7R

C236

0.22u/10V_0603

C119

X7R

C194

0.1u/10V

X7R

C238

39p

NPO

C201

+

4.7u/16V_1206

Y5V

C203

+

10u/6.3V_1206

X5R

Title

Size Document Number Rev

Date: Sheet

0.22u/10V_0603

C666

0.22u/10V_0603

X7R

C213

0.22u/10V_0603

X7R

C209

0.1u/10V

X7R

C700

0.1u/10V

X7R

C226

39p

NPO

+

X7R

0.22u/10V_0603

X7R

C168

0.1u/10V

X7R

+1.2V

C279

0.1u/10V

X7R

C219

+

4.7u/16V_1206

Y5V

C120

10u/6.3V_1206

X5R

C661

C660

C225

39p

NPO

X7R

X7R

C229

0.1u/10V

X7R

C697

0.1u/10V

X7R

C659

10u/6.3V_0805

C136

0.22u/10V_0603

+

UNIWILL COMPUTER CORP.

ATHLON64-PWR&GND

2445

258KA0

X7R

X7R

0.1u/10V

X7R

C125

39p

NPO

C161

4.7u/16V_1206

Y5V

2

C227

1

C196

39p

NPO

C182

+

4.7u/16V_1206

Y5V

742Tuesday, February 10, 2004

1

B

of

Page 8

+3V

L73

QT1608RL060

VCC3_CLKGN

D D

C790

+

4.7u/10V_0805

Y5V

C C

+3V

R481 *2.7K

R470 *2.7K

R455 *2.7K

R452 *2.7K

R451 *2.7K

5

C786

C754

0.1u/10V

0.1u/10V

X7R

X7R

Frequency Selection

FS0

FS1

FS2

FS3

FS4

C743

C744

0.1u/10V

0.1u/10V

X7R

X7R

+3V

L72

QT1608RL060

C742

0.1u/10V

X7R

R482 2.7K

R471 *2.7K

R453 *2.7K

R466 *2.7K

R450 *2.7K

C740

0.1u/10V

X7R

C741

0.1u/10V

X7R

TP108

TP109

+3V

VCC3_CLKGN_VDDA

C755

0.1u/10V

X7R

R267

10K_1%

C737

0.1u/10V

X7R

Main Clock Generator

C787

0.1u/10V

X7R

Z0801

Z0802

PD#

C738

1000p

X7R

44

43

33

31

24

15

11

1

47

40

36

28

23

16

8

5

48

12

37

38

39

4

U12

VDDCPU

VDDCPU

VDDAGP

VDD48

VDDPCI

VDDPCI

VDDZ

VDDREF

VSSCPU

VSSCPU

VSSF

VSS48

VSSPCI

VSSPCI

VSSZ

VSSREF

*CPUSTOP#

*PCISTOP#

*PD#

VDDA

VSSA

X1

6

Z0818

14.318MHz

C756

10p

NPO

**FS3/PCICLK_F0

**FS4/PCICLK_F1

Y2

42

CPUCLK_0T

41

CPUCLK_0C

46

CPUCLK_1T

45

CPUCLK_1C

35

AGPCLK0

34

AGPCLK1

9

ZCLK0

10

ZCLK1

2

**FS0/REF0

3

**FS1/REF0

4

**FS2/REF0

13

14

17

PCICLK0

18

PCICLK1

19

PCICLK2

20

PCICLK3

21

PCICLK4

22

PCICLK5

25

PCICLK6

26

PCICLK7

30

48MHz

29

24_48MHz

32

SCLK

27

SDATA

X2

REALTEK RTM360-755R / ICS952802

7

Z0819

C739

10p

NPO

ICS 952802 Pin2 ( *FS0 ) is internal pull up

3

Damping Resistors

Place near to the

Clock Outputs

Z0803

Z0804

Z0805

Z0806

Z0807

Z0810

FS0

FS1

FS2

FS3

FS4

Z0811

Z0812

Z0813

Z0814

Z0815 PCICLK_1394

Z0823

USB12M-SEL

Z0816

Z0817

R265 15

R266 15

R263 10

R264 10

R268 22

R269 22

R467 22

R480 33

R469 33

R454 33

R465 33

R464 33

R463 33

R462 33

R461 33

R460 33

R459 33

R719 22

R270 22

R271 22

USB12M-SEL

Ver:B

CPUCLK

CPUCLK#

755CLK

755CLK#

AGPCLK0

AGPCLK1Z0808

755ZCLK

963ZCLK

PCM_SCLK

963OSCI

963PCICLK

PCICLK1

LPCCLK

PCICLK_M

PCICLK_EC

Ver:B

add R719 22 OHM

USB_48M

383_48M

R734 4.7K

add R734 4.7K OHM

* internal pull up

* * internal pull down

CPUCLK 5

CPUCLK# 5

755CLK 11

755CLK# 11

AGPCLK0 11

AGPCLK1 14

755ZCLK 12

963ZCLK 22

PCM_SCLK 28

963OSCI 23

AUDIO_CLK 26,29

963PCICLK 22

PCICLK1 28

LPCCLK 30

PCICLK_M 27

PCICLK_EC 31

PCICLK_1394 27

CLKPCI_ECTEST

USB12MHI 24

USB_48M 24

383_48M 30

SMBCLK 9,23

SMBDAT 9,23

2

By-Pass Capacitors

Place near to the Clock Outputs

755CLK

755CLK#

AGPCLK0

AGPCLK1

755ZCLK

963ZCLK

963OSCI

963PCICLK

PCICLK1

LPCCLKZ0809

PCICLK_M

PCICLK_EC

383_48M

USB_48M

PCICLK_1394

PCM_SCLK

PWROK131

R528

*4.7K

C446 10p NPO

C447 10p NPO

C440 10p NPO

C441 10p NPO

C805 10p NPO

C804 10p NPO

C794 10p NPO

C803 10p NPO

C802 10p NPO

C801 10p NPOR468 22

C800 10p NPO

C799 10p NPO

C443 10p NPO

C442 10p NPO

C798 10p NPO

C806 10p NPO

+5V_AUX

Z0821

B

C837

*0.1u

X5R

R522

*4.7K

Z0820

Q17

*2N3904

E C

ver:B

+3V

Change net. +3V from +2.5V

R510

*470

Z0826

D

Q18

*2N7002

G

S

add R721 0 OHM

ver:B

R721 0

1

CPUCLK

CPUCLK#

Add C966 ,C967 for EMI

C966 *10p NPO

C967 *10p NPO

Ver:B

add R720 0 OHM

R720 *0

ver:B

C829

*C

NPO

PWRGD TO CHIPSET

PWROK 12,23

B B

(FS0)

(FS1)

0

0

1

1

0

0

1

1

0

0

1

1160.00

0

0

1

1

H33

HOLEC314D181

H36

HOLEC314D181

SiS 755/760 CLOCK

0

1

0

1

0

1

0

1

0

1

1

0

1

0

133.33

H25

HOLEC314D106

H21

HOLEC314D106

CPU

(MHz)

206.00

210.00

202.00

202.00

240.331

245.00

235.661133.33

235.66

106.66

133.33

133.33

133.33

171.67

175.00

168.34

168.34

AGPCLK

ZCLK

(MHz)

(MHz)

137.33

140.00

134.66

161.60

137.33

140.00

134.67

157.11

106.66

133.33

133.33

177.77

137.33

140.00

134.66

168.33

H20

HOLEC314D106

H22

HOLEC314D106

3

68.67

70.00

67.33

67.33

68.67

70.00

67.33

67.33

53.33

66.67

66.67

66.67

68.67

70.00

67.33

67.33

PCI

(MHz)

34.33

35.00

33.66

33.66

34.33

35.00

33.66

33.66

26.66

33.33

33.33

33.33

34.33

35.00

33.66

33.66

H29

HOLEC217D106

H2

C158D158

H15

C158D158

H6

C158D158

PWROK_CPUEC31

H30

C158D158

R533 4.7K

2

H5

H14

(FS3)

0

0

0

0

0

0

0

1

1

1

1

1

1

1

(FS2)

0

0

0

1

1

1

0

0

0

0

1

1

1

1

HOLEC314D86

HOLEC314D86

5

(FS4)

0

0

0

0

0

0

0

0

0

0 0

0

0

0 133.33

0

0

H8

HOLEC314D157

A A

H11

HOLEC314D106

HOLEC314D157

HOLEC314D157

H26

H27

(FS1)

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

SiS 755/760 CLOCK

(FS0)

(MHz)

0

160.00

200

1

200

0

1

200

0

186.66

233.33

1

0

233.33

233.33

1

213.34

0

266.67

1

266.67

0

1

266.671

133.34

0

1

166.67

0

166.67

166.67

1

H16

HOLEC314D106

H23

HOLEC314D157

CPU

ZCLK

(MHz)

106.66

133.33

133.33

160.00

106.67

133.33

106.66

133.33

106.66

133.33

166.66

H19

HOLEC314D106

H24

HOLEC314D157

PCI

AGPCLK

(MHz)

(MHz)

26.66

53.33

66.67

33.33

33.33

66.67

66.67

33.330

53.33

26.66

33.33

66.67

33.33 0

66.67

33.33

66.67155.55

53.33

26.66

33.33

66.67

66.67

33.33

66.67

33.33

53.33

26.66

33.33

66.67

33.33

66.67

66.671

H28

HOLEC314D86

H17

HOLEC314D106

4

H18

HOLEC217D106

(FS4)

1

1

1

1

1

1

1

10

1

1133.33

1

1

1

1

1

(FS2)

(FS3)

0

0

0

0

0

0

1

10

1

1

1

1

1

1

H34

HOLEC314D181

H35

HOLEC314D181

00

0

0

0

1

1

1

10

0

0

0

1

1

1

1

+5V_AUX

Z0825

Z0827

B

C810

E C

*0.1u

X5R

Title

Size Document Number Rev

Date: Sheet

CLK Table for SiS755/760 ( For ICS-952801)

+2.5V

R523

R529

4.7K

Q15

2N3904

R534 *0

470

Z0822

R535 0

D

Q16

G

S

2N7002

C839

*0.1u

NPO

UNIWILL COMPUTER CORP.

CLOCK GENERATOR & PCB HOLE

2445

258KA0

PWROK_CPU 5,36

842Tuesday, February 10, 2004

1

B

of

Page 9

8

7

+2.5V_DDR

6

5

4

3

2

+2.5V_DDR

1

MEMCKEB6,10

MEMCLK_H46,10

MEMCLK_L46,10

MEMCLK_H66,10

MEMCLK_L66,10

+2.5V_DDR

MEMDQS[0..7]10

MAB[0..13]

MMDATA[0..63]

MMDQS[0..7]

MEMDQS[9..16]

RDQM[0..7]10

MAB0

MAB1

MAB2

MAB3

MAB4

MAB5

MAB6

MAB7

MAB8

MAB9

MAB10

MAB11

MAB12

MEMBANKB0

MEMBANKB1

MEMCS_L2

MEMCS_L3

RDQM0

RDQM1

RDQM2

RDQM3

RDQM4

RDQM5

RDQM6

RDQM7

MEMW EB_L

MEMCASB_L

MEMRASB_L

MEMCKEB

MEMCLK_H4

MEMCLK_L4

MEMCLK_H6

MEMCLK_L6

DCLK1

DCLK#1

MEMDQS0

MEMDQS1

MEMDQS2

MEMDQS3

MEMDQS4

MEMDQS5

MEMDQS6

MEMDQS7

SMBDAT

SMBCLK

Z0901

DDRVREF

MAB13

112

111

110

109

108

107

106

105

102

101

115

100

99

97

117

116

98

121

122

12

26

48

62

134

148

170

184

78

119

120

118

96

95

35

37

160

158

89

91

11

25

47

61

133

147

169

183

77

193

195

194

196

198

1

2

199

197

86

85

123

124

200

MMDATA[0..63] 6

MMDQS[0..7] 6

MEMDQS[9..16] 6

RDQM0

RDQM1

RDQM2

RDQM3

RDQM4

RDQM5

RDQM6

RDQM7

MEMDQS0

MEMDQS1

MEMDQS2

MEMDQS3

MEMDQS4

MEMDQS5

MEMDQS6

MEMDQS7

3

CN34

921334557698193113

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

GND

GND

GND

GND

GND

MEMDQS9

MEMDQS10

MEMDQS11

MEMDQS12

MEMDQS13

MEMDQS14

MEMDQS15

MEMDQS16

MMDQS0

MMDQS1

MMDQS2

MMDQS3

MMDQS4

MMDQS5

MMDQS6

MMDQS7

GND

VDDQ

GND

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10/AP

A11

A12

DU/A13

BA0

BA1

DU/BA2

CS0

CS1

DQM0

DQM1

DQM2

DQM3

DQM4

DQM5

DQM6

DQM7

DQM8

WE

CAS

RAS

CKE0

CKE1

CK0

CK0

CK1

CK1

CK2

CK2

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS8

SDA

SCL

SA0

SA1

SA2

VREF

VREF

VDDID

VDDSPD

NC//DU/RESET

NC/DU

NC/DU

NC/DU

NC/DU

GND

15273951637587

3

R218 10

R220 10

R222 10

R224 10

R238 10

R242 10

R243 10

R244 10 C745

R219 10

R221 10

R223 10

R225 10

R216 10

R217 10

R226 10

R227 10

179

131

143

155

157

167

VDDQ

GND

103

VDDQ

GND

125

137

VDDQ

GND

149

VDDQ

GND

159

1911022343646587082

VDD

VDD

VDD

VDDQ

VDDQ

VDDQ

GND

GND

GND

GND

GND

GND

161

173

1854162838405264768890

+2.5V_DDR

R202

75_1%

R252

75_1%

9294114

VDD

VDD

GND

VDD

VDD

VDD

VDD

VDD

VDD

GND

GND

GND

GND

GND

GND

GND

DDRVREF GEN. & DECOUPLING

C387

0.1u/10V

X7R

C379

0.1u/10V

X7R

UNIWILL COMPUTER CORP.

Title

Size Document Number Rev

2445

Date: Sheet

2

132

144

156

168

VDD

VDD

VDD

VDD

VDD

GND

GND

GND

GND

GND

104

138

150

162

126

C388

1000p

X7R

C381

1000p

X7R

DDR CONN

258KA0

180

VDD

GND

174

192

VDDQ

GND

186

D0

D1

D2

D3

D4

D5

D6

D7

D8

D9

D10

D11

D12

D13

D14

D15

D16

D17

D18

D19

D20

D21

D22

D23

D24

D25

D26

D27

D28

D29

D30

D31

D32

D33

D34

D35

D36

D37

D38

D39

D40

D41

D42

D43

D44

D45

D46

D47

D48

D49

D50

D51

D52

D53

D54

D55

D56

D57

D58

D59

D60

D61

D62

D63

CB0

CB1

CB2

CB3

CB4

CB5

CB6

CB7

GND

GND

201

202

DDR REV CONN

C390

1000p

X7R

C380

1000p

X7R

5

7

13

17

6

8

14

18

19

23

29

31

20

24

30

32

41

43

49

53

42

44

50

54

55

59

65

67

56

60

66

68

127

129

135

139

128

130

136

140

141

145

151

153

142

146

152

154

163

165

171

175

164

166

172

176

177

181

187

189

178

182

188

190

71

73

79

83

72

74

80

84

C389

1000p

X7R

1000p

X7R

942Tuesday, February 10, 2004

1

MEMDATA0

MEMDATA1

MEMDATA2

MEMDATA3

MEMDATA4

MEMDATA5

MEMDATA6

MEMDATA7

MEMDATA8

MEMDATA9

MEMDATA10

MEMDATA11

MEMDATA12

MEMDATA13

MEMDATA14

MEMDATA15

MEMDATA16

MEMDATA17

MEMDATA18

MEMDATA19

MEMDATA20

MEMDATA21

MEMDATA22

MEMDATA23

MEMDATA24

MEMDATA25

MEMDATA26

MEMDATA27

MEMDATA28

MEMDATA29

MEMDATA30

MEMDATA31

MEMDATA32

MEMDATA33

MEMDATA34

MEMDATA35

MEMDATA36

MEMDATA37

MEMDATA38

MEMDATA39

MEMDATA40

MEMDATA41

MEMDATA42

MEMDATA43

MEMDATA44

MEMDATA45

MEMDATA46

MEMDATA47

MEMDATA48

MEMDATA49

MEMDATA50

MEMDATA51

MEMDATA52

MEMDATA53

MEMDATA54

MEMDATA55

MEMDATA56

MEMDATA57

MEMDATA58

MEMDATA59

MEMDATA60

MEMDATA61

MEMDATA62

MEMDATA63

DDRVREF

of

B

MAB[0..13]6,10

MEMBANKB06,10

MEMBANKB16,10

MEMCS_L[0..3]6,10

MEMW EB_L6,10

MEMCASB_L6,10

MEMRASB_L6,10

R272

8.2K

4

MEMW EA_L6,10

MEMCASA_L6,10

MEMRASA_L6,10

MEMCKEA6,10

MEMCLK_H56,10

MEMCLK_L56,10

MEMCLK_H76,10

MEMCLK_L76,10

SMBDAT8,23

SMBCLK8,23

+2.5V_DDR

1

RP70

2

8P4RX10

3

4 5

4 5

RP26

3

8P4RX10

2

1

1

RP69

2

8P4RX10

3

4 5

4 5

RP27

3

8P4RX10

2

1

1

RP68

2

8P4RX10

3

4 5

1

RP67

2

8P4RX10

3

4 5

4 5

RP28

3

8P4RX10

2

1

4 5

RP29

3

8P4RX10

2

1

1

RP66

2

8P4RX10

3

4 5

8

MAA[0..13]

MEMBANKA0

MEMBANKA1

8

7

6

6

7

8

8

7

6

6

7

8

8

7

6

8

7

6

6

7

8

6

7

8

8

7

6

MEMCS_L0

MEMCS_L1

RDQM0

RDQM1

RDQM2

RDQM3

RDQM4

RDQM5

RDQM6

RDQM7

MEMWEA_L

MEMCASA_L

MEMRASA_L

MEMCKEA

MEMCLK_H5

MEMCLK_L5

MEMCLK_H7

MEMCLK_L7

DCLK0

DCLK#0

MEMDQS0

MEMDQS1

MEMDQS2

MEMDQS3

MEMDQS4

MEMDQS5

MEMDQS6

MEMDQS7

SMBDAT

SMBCLK

DDRVREF

MAA13

MMDATA26

MMDATA25

MMDATA24

MMDATA39

MMDATA38

MMDATA37

MMDATA36

MMDATA35

MMDATA34

MMDATA33

MMDATA32

MMDATA47

MMDATA46

MMDATA45

MMDATA44

MMDATA43

MMDATA42

MMDATA41

MMDATA40

MMDATA51

MMDATA50

MMDATA49

MMDATA48

MMDATA55

MMDATA54

MMDATA53

MMDATA63

MMDATA62

MMDATA61

MMDATA60

MMDATA59

MMDATA58

MMDATA57

MMDATA56MEMDATA56

921334557698193113

MAA0

MAA1

MAA2

MAA3

MAA4

MAA5

MAA6

MAA7

MAA8

MAA9

MAA10

MAA11

MAA12

112

111

110

109

108

107

106

105

102

101

115

100

99

97

117

116

98

121

122

12

26

48

62

134

148

170

184

78

119

120

118

96

95

35

37

160

158

89

91

11

25

47

61

133

147

169

183

77

193

195

194

196

198

1

2

199

197

86

85

123

124

200

VDDQ

VDDQ

VDDQ

VDDQ

GND

GND

GND

GND

15273951637587

3

4 5

RP22

3

8P4RX10

2

1

1

RP73

2

8P4RX10

3

4 5

4 5

RP23

3

8P4RX10

2

1

1

RP72

2

8P4RX10

3

4 5

4 5

RP24

3

8P4RX10

2

1

1

RP71

2

8P4RX10

3

4 5

4 5

RP25

3

8P4RX10

2

1

VDDQ

GND

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10/AP

A11

A12

DU/A13

BA0

BA1

DU/BA2

CS0

CS1

DQM0

DQM1

DQM2

DQM3

DQM4

DQM5

DQM6

DQM7

DQM8

WE

CAS

RAS

CKE0

CKE1

CK0

CK0

CK1

CK1

CK2

CK2

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS8

SDA

SCL

SA0

SA1

SA2

VREF

VREF

VDDID

VDDSPD

NC//DU/RESET

NC/DU

NC/DU

NC/DU

NC/DU

MEMDATA7

MEMDATA6

MEMDATA5

MEMDATA4

MEMDATA3

MEMDATA2

MEMDATA1

MEMDATA0

MEMDATA15

MEMDATA14

MEMDATA13

MEMDATA12

MEMDATA11

MEMDATA10

MEMDATA9

MEMDATA8

MEMDATA23

MEMDATA22

MEMDATA21

MEMDATA20

MEMDATA19

MEMDATA18

MEMDATA17

MEMDATA16

MEMDATA31

MEMDATA30

MEMDATA29

MEMDATA28 MMDATA28

7

VDDQ

GND

VDDQ

GND

6

7

8

8

7

6

6

7

8

8

7

6

6

7

8

8

7

6

6

7

8

CN31

179

131

143

155

157

167

1911022343646587082

VDD

VDD

VDD

VDDQ

GND

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

Address:0000h Address:0001h

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

103

125

137

149

159

161

173

1854162838405264768890

VDD

GND

VDD

GND

VDD

GND

VDD

GND

VDD

GND

9294114

VDD

VDD

GND

GND

VDD

GND

192

132

144

156

168

180

VDD

VDD

VDD

VDD

VDD

VDD

VDDQ

GND

GND

GND

GND

GND

GND

GND

104

138

150

162

174

126

186

5

D0

7

D1

13

D2

17

D3

6

D4

8

D5

14

D6

18

D7

19

D8

23

D9

29

D10

31

D11

20

D12

24

D13

30

D14

32

D15

41

D16

43

D17

49

D18

53

D19

42

D20

44

D21

50

D22

54

D23

55

D24

59

D25

65

D26

67

D27

56

D28

60

D29

66

D30

68

D31

127

D32

129

D33

135

D34

139

D35

128

D36

130

D37

136

D38

140

D39

141

D40

145

D41

151

D42

153

D43

142

D44

146

D45

152

D46

154

D47

163

D48

165

D49

171

D50

175

D51

164

D52

166

D53

172

D54

176

D55

177

D56

181

D57

187

D58

189

D59

178

D60

182

D61

188

D62

190

D63

71

CB0

73

CB1

79

CB2

83

CB3

72

CB4

74

CB5

80

CB6

84

CB7

DDR REV CONN

MEMDATA0

MEMDATA1

MEMDATA2

MEMDATA3

MEMDATA4

MEMDATA5

MEMDATA6

MEMDATA7

MEMDATA8

MEMDATA9

MEMDATA10

MEMDATA11

MEMDATA12

MEMDATA13

MEMDATA14

MEMDATA15

MEMDATA16

MEMDATA17

MEMDATA18

MEMDATA19

MEMDATA20

MEMDATA21

MEMDATA22

MEMDATA23

MEMDATA24

MEMDATA25

MEMDATA26

MEMDATA27

MEMDATA28

MEMDATA29

MEMDATA30

MEMDATA31

MEMDATA32

MEMDATA33

MEMDATA34

MEMDATA35

MEMDATA36

MEMDATA37

MEMDATA38

MEMDATA39

MEMDATA40

MEMDATA41

MEMDATA42

MEMDATA43

MEMDATA44

MEMDATA45

MEMDATA46

MEMDATA47

MEMDATA48

MEMDATA49

MEMDATA50

MEMDATA51

MEMDATA52

MEMDATA53

MEMDATA54

MEMDATA55

MEMDATA56

MEMDATA57

MEMDATA58

MEMDATA59

MEMDATA60

MEMDATA61

MEMDATA62

MEMDATA63

MEMDATA[63..0] 10

+2.5V_DDR

R273 10K_1%

DCLK#1

R434 10K_1%

DCLK#0

R262 10K_1%

DCLK1

R435 10K_1%

DCLK0

+2.5V_DDR

ver:B

+3V

R717 *10K

R718 *10K

SMBDAT

SMBCLK

must be put it neer to CN34 side

Routing

MMDATA7

MMDATA6

MMDATA5

MMDATA4

MMDATA3

MMDATA2

MMDATA1

MMDATA0

MMDATA15

MMDATA14

MMDATA13

MMDATA12

MMDATA11

MMDATA10

MMDATA9

MMDATA8

MMDATA23

MMDATA22

MMDATA21

MMDATA20

MMDATA19

MMDATA18

MMDATA17

MMDATA16

MMDATA31

MMDATA30

MMDATA29

6

5

in the top layer

MEMDATA[63:0] with 5/15

MEMDQS[8:0] with 5/20

MEMCHECK[7:0] with 5/15

DQM[8:0] with 5/20

in the bottom layer

MEMADDA[13:0] with 5/15

MEMADDB[13:0] with 5/15

MA COMMAND with 5/15

MB COMMAND with 5/15

MEMCLK_H/MEMCLK_L with

5/5/5, 20 mil spacing

Rout DDR nets 50 mil

sapcing to their own

net

MAA[0..13]6,10

D D

MEMBANKA06,10

MEMBANKA16,10

MEMCS_L[0..3]6,10

RDQM[0..7]10

C C

MEMDQS[0..7]10

B B

MEMDATA27 MMDATA27

MEMDATA26

MEMDATA25

MEMDATA24

MEMDATA39

MEMDATA38

MEMDATA37

MEMDATA36

MEMDATA35

MEMDATA34

MEMDATA33

MEMDATA32

MEMDATA47

MEMDATA46

MEMDATA45

MEMDATA44

MEMDATA43

MEMDATA42

MEMDATA41

MEMDATA40

MEMDATA51

MEMDATA50

MEMDATA49

A A

MEMDATA48

MEMDATA55

MEMDATA54

MEMDATA53

MEMDATA52 MMDATA52

MEMDATA63

MEMDATA62

MEMDATA61

MEMDATA60

MEMDATA59

MEMDATA58

MEMDATA57

Page 10

8

RDQM[0..7]9

MEMDQS[0..7]9

MEMDATA[63..0]9

MEMDATA0

MEMDATA1

RP34

MEMDQS0

8P4RX68

MEMDATA2

MEMDATA4

MEMDATA5

D D

RDQM0

MEMDATA6

MEMDATA8

MEMDATA3

MEMDATA9

MEMDQS1

MEMDATA7

MEMDATA12

MEMDATA13

RDQM1

MEMDQS2

MEMDATA18

MEMDATA19

MEMDATA24

RDQM2

MEMDATA22

MEMDATA23

MEMDATA28

MEMDATA29

RDQM3

MEMDATA30

MEMDATA31

MEMDATA25

MEMDQS3

MEMDATA26

C C

MEMDATA27

MEMDATA32

MEMDATA33

MEMDQS4

MEMDATA34

MEMDATA36

MEMDATA37

RDQM4

MEMDATA38

MEMDATA39

MEMDATA44

MEMDATA45

RDQM5

MEMDATA35

MEMDATA40

MEMDATA41

MEMDQS5

MEMDQS6

MEMDATA50

MEMDATA51

MEMDATA56

RDQM6

MEMDATA54

MEMDATA55

MEMDATA60

B B

MEMDATA57

MEMDQS7

MEMDATA58

MEMDATA59

MEMDATA61

RDQM7

MEMDATA62

MEMDATA63

RP84

8P4RX68

RP35

8P4RX68

RP83

8P4RX68

RP43

8P4RX68

RP81

8P4RX68

RP80

8P4RX68

RP44

8P4RX68

RP37

8P4RX68

RP76

8P4RX68

RP75

8P4RX68

RP38

8P4RX68

RP40

8P4RX68

RP78

8P4RX68

RP41

8P4RX68

RP77

8P4RX68

RDQM[0..7]

MEMDQS[0..7]

MEMDATA[63..0]

1

2

3

4 5

1

2

3

4 5

1

2

3

4 5

1

2

3

4 5

8

7

6

1

2

3

4 5

1

2

3

4 5

8

7

6

8

7

6

1

2

3

4 5

1

2

3

4 5

8

7

6

8

7

6

1

2

3

4 5

8

7

6

1

2

3

4 5

8

7

6

8

7

6

8

7

6

8

7

6

1

2

3

45

8

7

6

8

7

6

1

2

3

45

1

2

3

45

8

7

6

8

7

6

1

2

3

45

1

2

3

45

8

7

6

1

2

3

45

8

7

6

+1.25V_DDR

7

MEMDATA10

8

MEMDATA11

7

MEMDATA16

6

MEMDATA17

RP42 8P4RX68

MEMDATA42

8

MEMDATA43

7

MEMDATA48

6

MEMDATA49

RP39 8P4RX68

MEMBANKA16,9

MEMW EA_L6,9

MEMCASA_L6,9

MEMBANKA06,9

MEMRASA_L6,9

MEMCS_L0

MEMCS_L1

MEMW EA_L

MEMCASA_L

MEMCS_L2

MEMCS_L3

MEMRASA_L

MAA13

MAA10

MAA6

MAA8

MAA11

MAA0

RP32 8P4RX47

MAA9

MAA12

MAA1

MAA3

RP31 8P4RX47

MAA2

MAA4

MAA5

MAA7

RP33 8P4RX47

8

7

6

8

7

6

8

7

6

6

1

2

3

45

1

2

3

45

R24747

R21347

R25047

R21147

R24947

R25947

R21047

R44547

R24847

R21247

R25147

1

2

3

45

1

2

3

45

1

2

3

45

close CPU,500~1000mil

MEMCKEB6,9

MEMCKEA6,9

R44947

R24647

close SO-DIMM

MEMWEB_L6,9

MEMCASB_L6,9

MEMRASB_L6,9

MEMBANKB06,9

MEMBANKB16,9

MAB6

MAB4

MAB2

MAB0

MAB11

MAB8

MAB12

MAB9

MAB7

MAB5

MAB3

MAB1

MAB10