Page 1

FUJITSU SEMICONDUCTOR

MICROCONTROLLER MANUAL

HARDWARE MANUAL

CM25-10133-2E

F2MC-8L FAMILY

8-BIT MICROCONTROLLER

MB89990 Series

Page 2

Page 3

F2MC-8L FAMILY

8-BIT MICROCONTROLLER

MB89990 Series

HARDWARE MANUAL

FUJITSU LIMITED

Page 4

Page 5

PREFACE

Preface describes objectives and intended reader.

■

Objectives and Intended Reader

The MB89990 series of microcontrollers are mid-range of microcontroller. They are generalpurpose and high-speed products in the F

microcontrollers operating at low voltages. It has Timer, Remote-control transmission frequency

generator.

This manual covers the functions and operations of the MB89990 series of microcontrollers.

Refer to the

F2MC-8L Family Software Manual

2

MC-8L Family series of 8-bit single-chip

for instructions.

i

Page 6

1. The contents of this document are subject to change without notice. Customers are advised to consult

with FUJITSU sales representatives before ordering.

2. The information and circuit diagrams in this document are presented as examples of semiconductor

device applications, and are not intended to be incorporated in devices for actual use. Also, FUJITSU is

unable to assume responsibility for infringement of any patent rights or other rights of third parties

arising from the use of this information or circuit diagrams.

3. The contents of this document may not be reproduced or copied without the permission of FUJITSU

LIMITED.

4. FUJITSU semiconductor devices are intended for use in standard applications (computers, office

automation and other office equipments, industrial, communications, and measurement equipments,

personal or household devices, etc.).

CAUTION:

Customers considering the use of our products in special applications where failure or abnormal

operation may directly affect human lives or cause physical injury or property damage, or where

extremely high levels of reliability are demanded (such as aerospace systems, atomic energy controls,

sea floor repeaters, vehicle operating controls, medical devices for life support, etc.) are requested to

consult with FUJITSU sales representatives before such use. The company will not be responsible for

damages arising from such use witho ut prior approval.

5. Any sem iconductor device s have inherentl y a certain rate of failure. Y ou must protect against injury,

damage or loss from such failures by incorporating safety design measures into your facility and

equipment such as redundancy, fire protection, and prevention of over-current levels and other

abnormal operating conditions.

6. If any products described in this document represent goods or technologies subject to certain

restrictions on export under the Foreign Exchange and Foreign Trade Control Law of Japan, the prior

authorization by Japanese government should be required for export of those products from Japan.

©2000 FUJITSU LIMITED Printed in Japan

ii

Page 7

CONTENTS

CHAPTER 1 GENARAL ..................................................................................................... 1

1.1 Features ................................................................................................................................................ 2

1.2 Product Series ....................................................................................................................................... 3

1.3 Block Diagram ....................................................................................................................................... 5

1.4 Pin Assignment ...................................................................................................................................... 6

1.5 Pin Function Description ........................................................................................................................ 8

1.6 Handling Devices ................................................................................................................................. 12

CHAPTER 2 HARDWARE CONFIGRATION ................................................................... 13

2.1 CPU ..................................................................................................................................................... 14

2.2 Lock Control Block ............................................................................................................................... 19

2.3 Interrupt Controller ............................................................................................................................... 25

2.4 I/O Ports .............................................................................................................................................. 28

2.5 8/16-bit Timer (Timer 1 and Timer 2) ................................................................................................... 32

2.6 External Interrupt 1 .............................................................................................................................. 39

2.7 External Interrupt 2 (Wake Up) ............................................................................................................ 43

2.8 Remote-control Carrier Frequency Generator ..................................................................................... 45

2.9 Time-base Timer .................................................................................................................................. 48

2.10 Watchdog Timer Reset ........................................................................................................................ 51

CHAPTER 3 OPERATION ............................................................................................... 53

3.1 Clock Pulse Generator .................. ...... ....... ...... ....... ...... ....................................... ...... .......................... 54

3.2 Reset ................................................................................................................................................... 55

3.2.1 Reset Operation ............................................................................................................................. 56

3.2.2 Reset Source .................................................................................................................................. 57

3.3 Interrupt ............................................................................................................................................... 58

3.4 Low-power Consumption Modes ......................................................................................................... 60

3.5 Pin States for Sleep, Stop and Reset .................................................................................................. 61

CHAPTER 4 INSTRUCTIONS .......................................................................................... 63

4.1 Transfer Instructions ............................................................................................................................ 64

4.2 Operation Instruction ....................................... ....................................... ...... ....... ...... .......................... 66

4.3 Branch Instructions .............................................................................................................................. 68

4.4 Other Instructions ................................................................................................................................ 69

4.5 F2MC-8L Family Instruction Map ......................................................................................................... 70

CHAPTER 5 MASK OPTIONS ......................................................................................... 71

5.1 Mask Options ....................................................................................................................................... 72

APPENDIX ............................................................................................................................ 73

APPENDIX A I/O Map ................................................................................................................................ 74

APPENDIX B EPROM Setting for MB89P195 ............................................................................................ 76

iii

Page 8

FIGURES

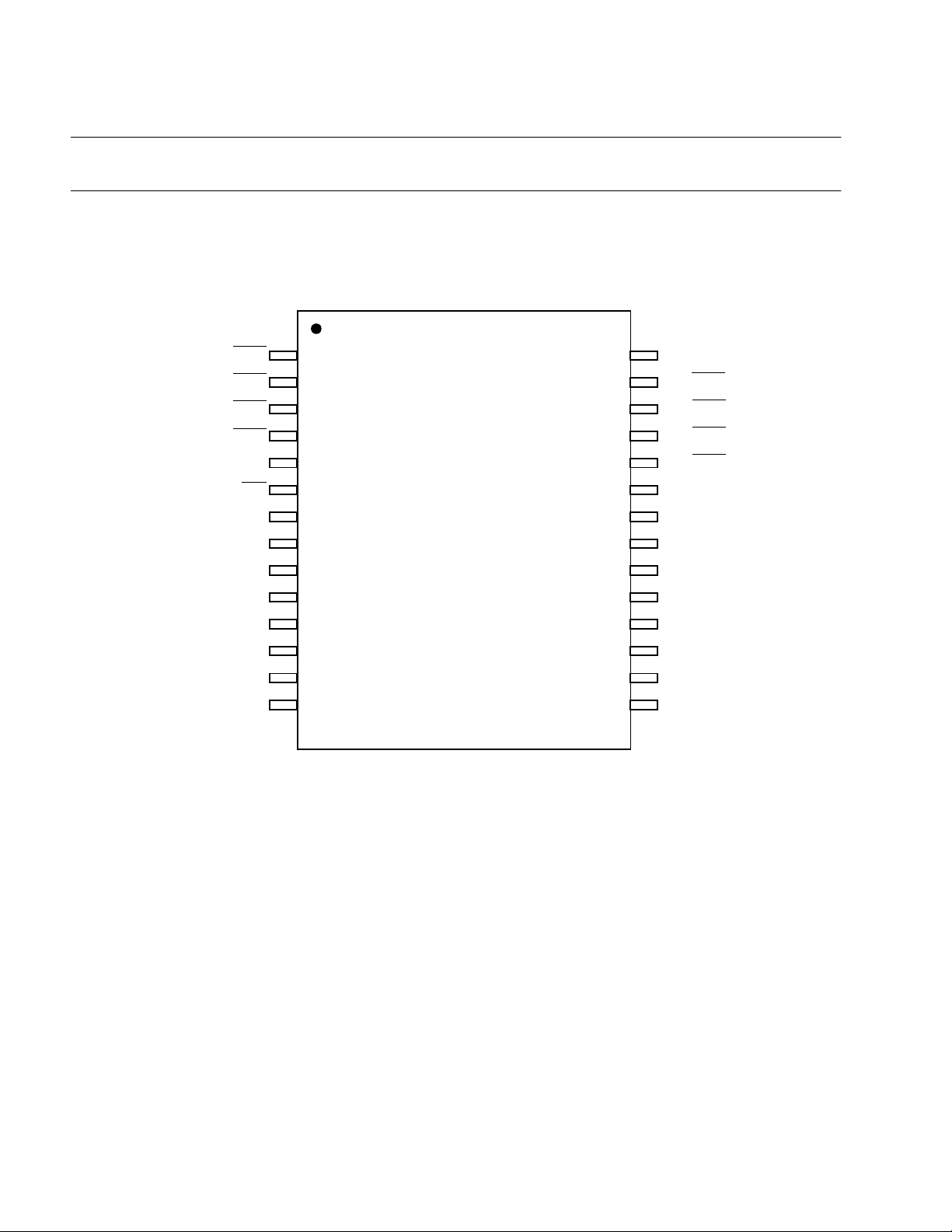

Figure 1.4-1 Pin Assignment (FPT-28P-M02, DIP-28P-M03) ........................................................................ 6

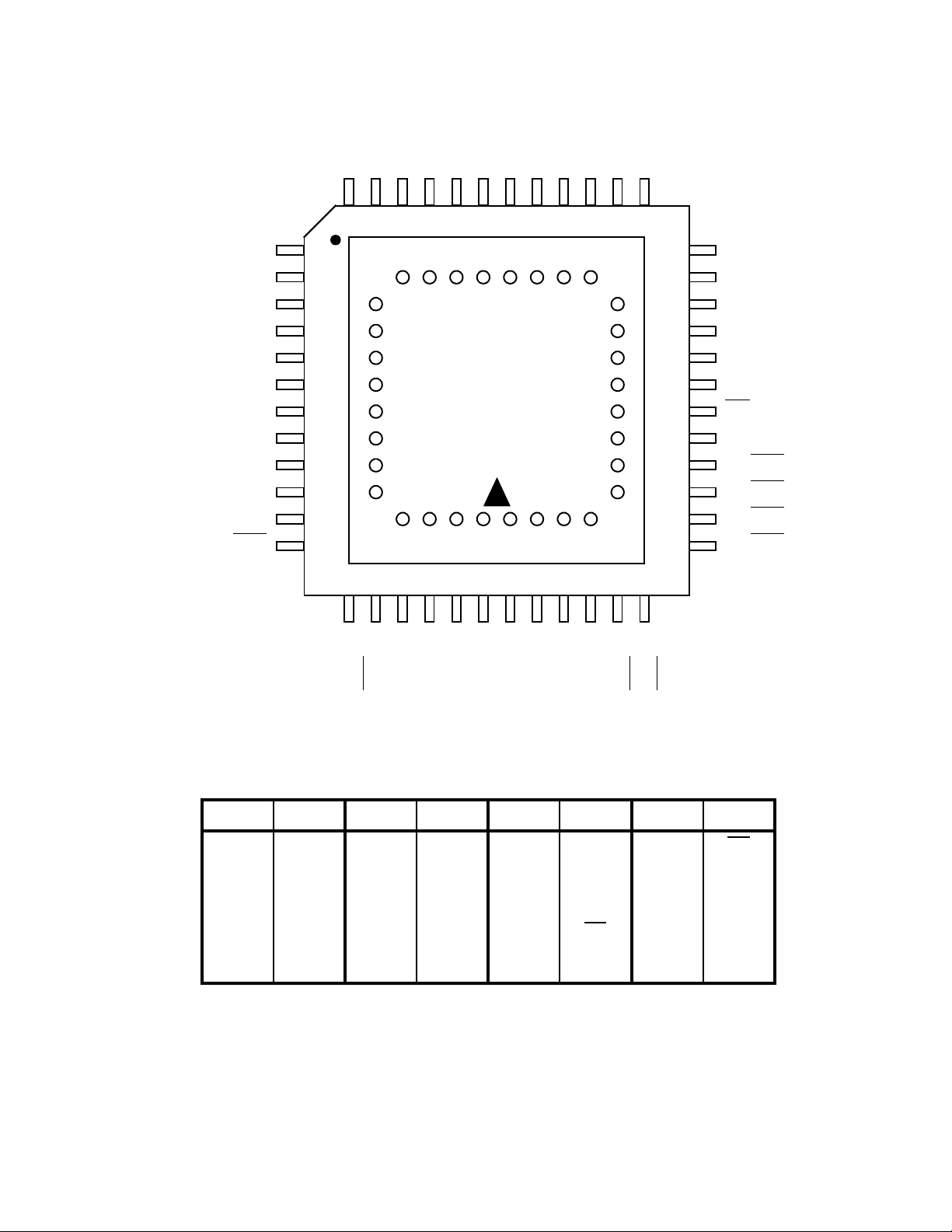

Figure 1.4-2 Pin Assignment (MQP-48C-P01) ................................................................................................ 7

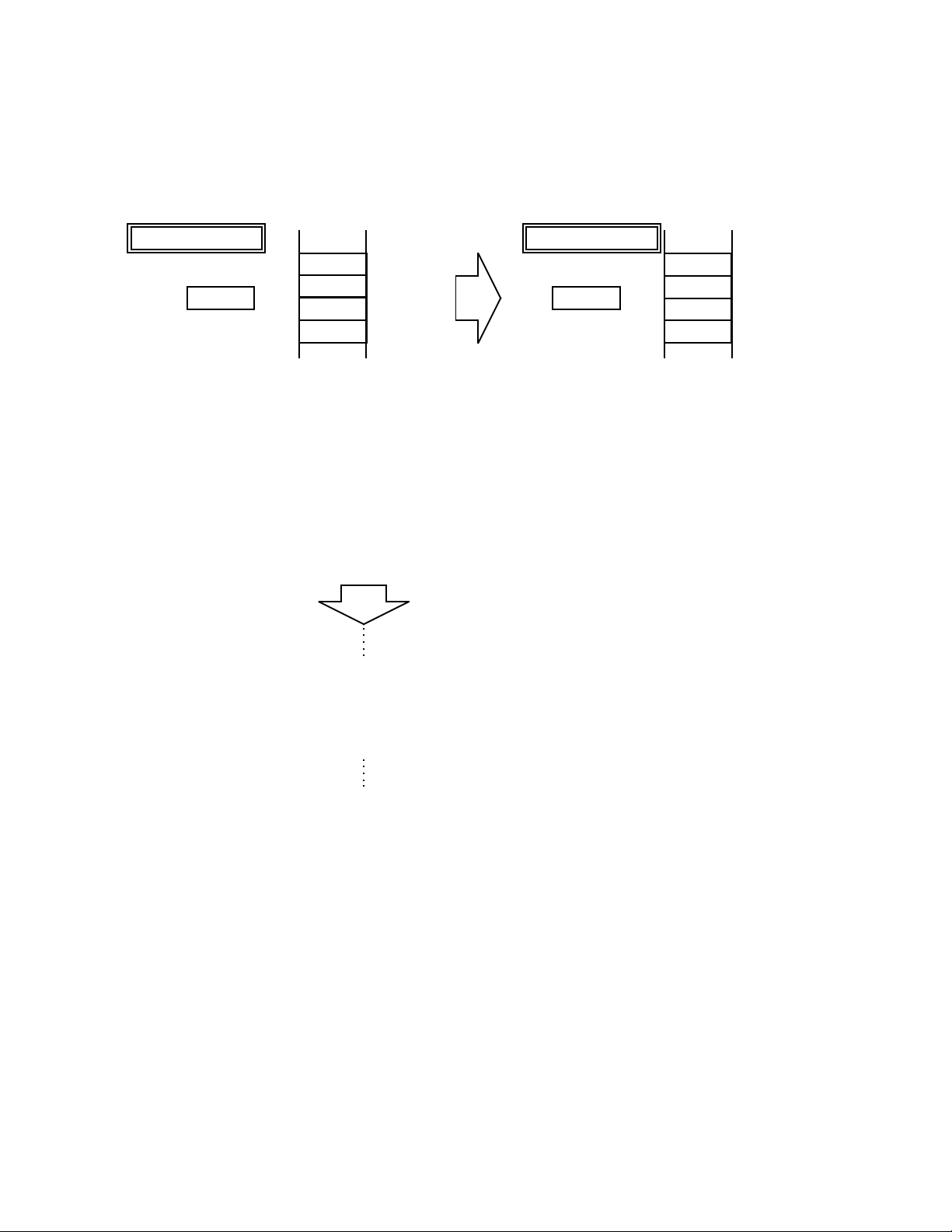

Figure 2.1-1 Memory Space of MB89990 Series of Microcontrollers ............................................................ 14

Figure 2.1-2 Arrangement of 16 bit Data in Memory ..................................................................................... 16

Figure 2.1-3 Arrangement of 16-bit Data during Execution of Instruction ..................................................... 16

Figure 2.1-4 Structure of Processor Status ...... ...... ....... ...... ....... ...... ....................................... ...... ................ 17

Figure 2.1-5 Rule for Translating Real Addresses at General-purpose Register Area ................................. 17

Figure 2.1-6 Register Bank Configuration ..................................................................................................... 18

Figure 2.3-1 Interrupt-processing Flowcha rt .......................................... ....... ...... ....... ...... ....... ...... ... ............. 27

Figure 2.4-1 Ports 00 to 07 and 30 to 37 ...................................................................................................... 30

Figure 2.4-2 Ports 40 to 45 ........................................................................................................................... 31

Figure 2.5-1 8/16-bit Timer Block Diagram ................................................................................................... 32

Figure 2.5-2 Description Diagram for Internal Clock Mode Operation .......................................................... 36

Figure 2.5-3 Flow Diagram for Timer Setting ................................................................................................ 36

Figure 2.5-4 Initialization of Equivalent Circuit .............................................................................................. 37

Figure 2.5-5 External Cock Mode Operation Description Diagram ............................................................... 37

Figure 2.5-6 Operation Diagram when Timer Stop Bit is Used ..................................................................... 38

Figure 3.1-1 Clock Pulse Generator .............................................................................................................. 54

Figure 3.2-1 Outline of Reset Operation ....................................................... ...... ....... ...... ....... ...................... 56

Figure 3.2-2 Reset Vector Structure ...................... ....... ...... ....... ...... ....................................... ...................... 56

Figure 3.3-1 Interrupt-processing Flowcha rt .......................................... ....... ...... ....... ...... ....... ...... ................ 58

iv

Page 9

TABLES

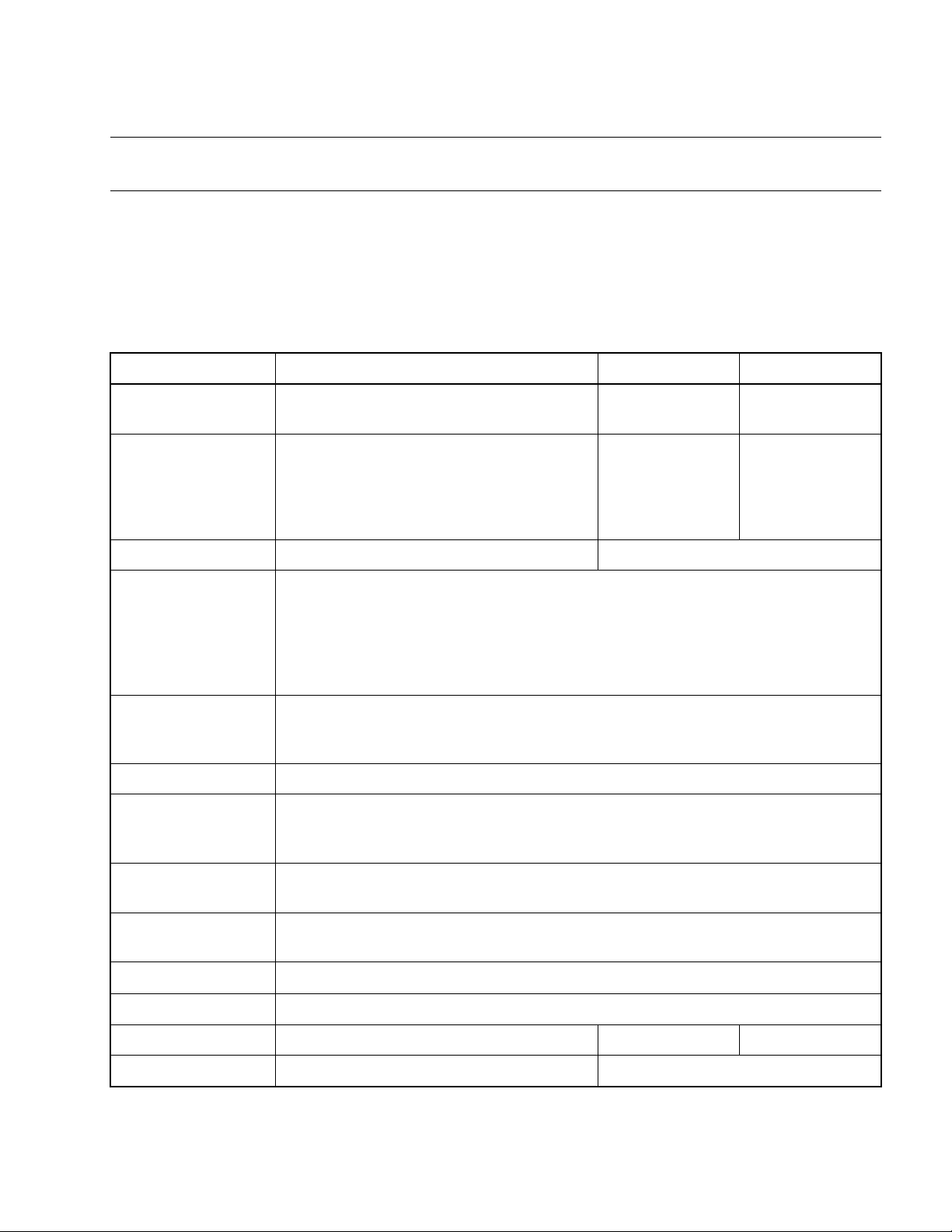

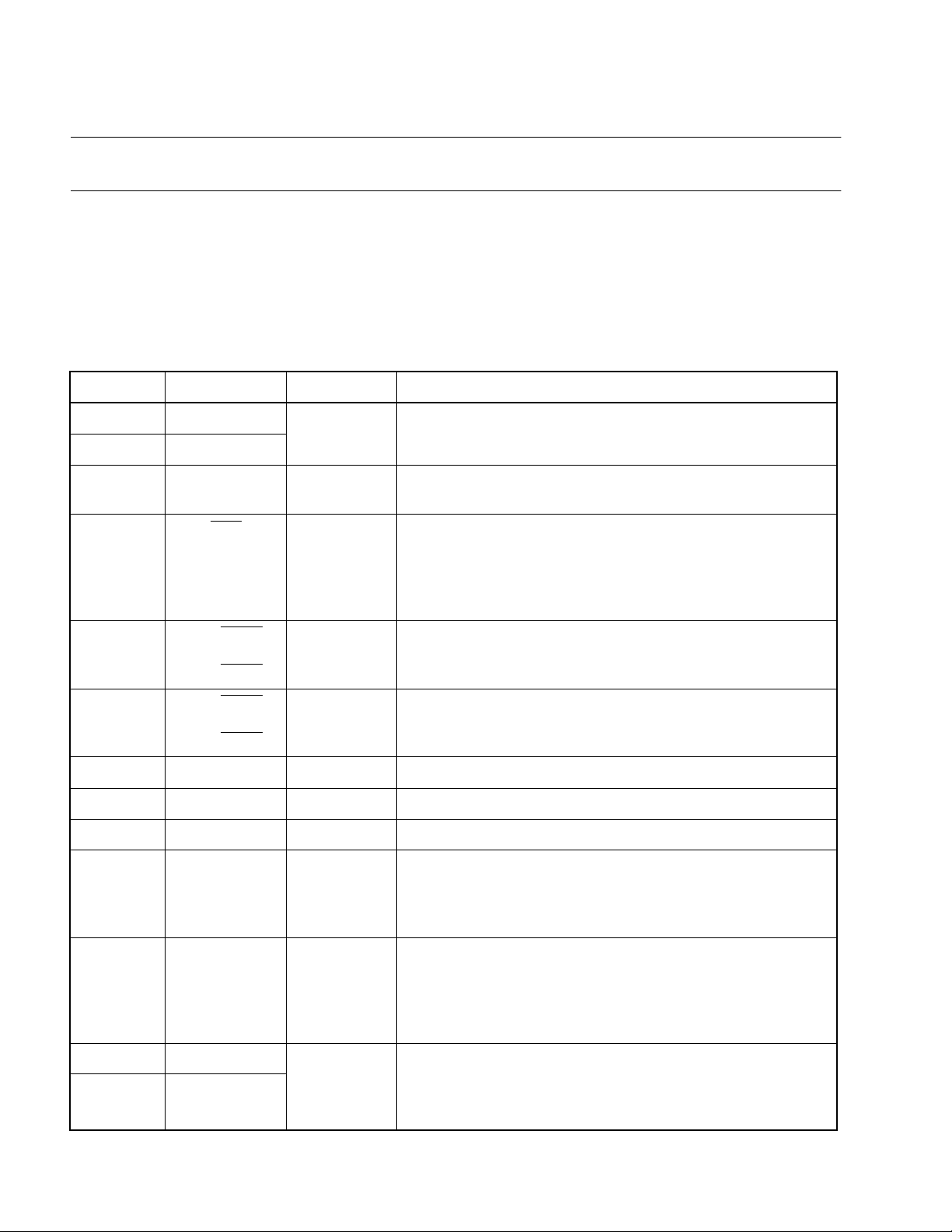

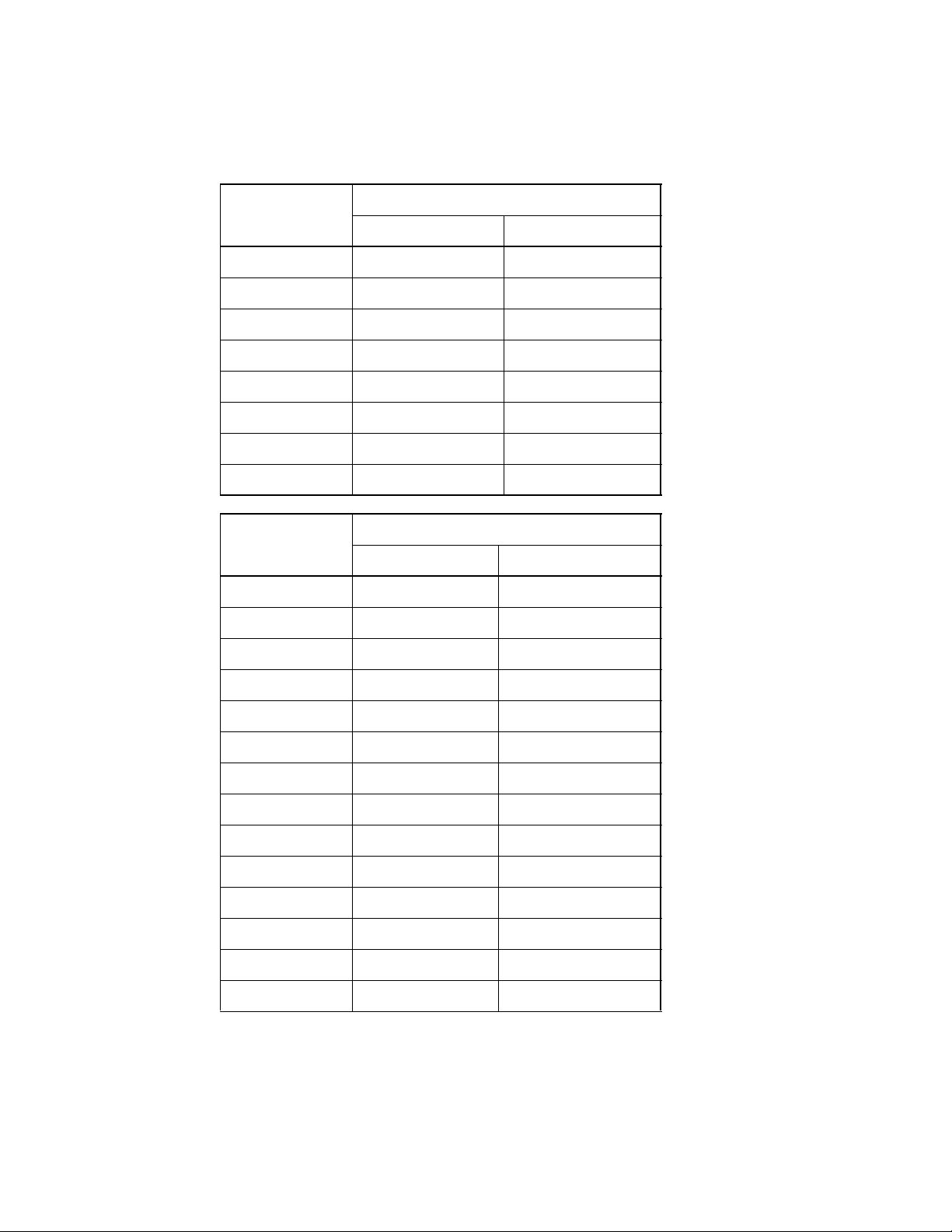

Table 1.2-1 Types and Functions of MB89990 Series of Microcontrollers ..................................................... 3

Table 1.5-1 Pin Function Description .............................................................................................................. 8

Table 1.5-2 Pins for External ROM ................................................................................................................. 9

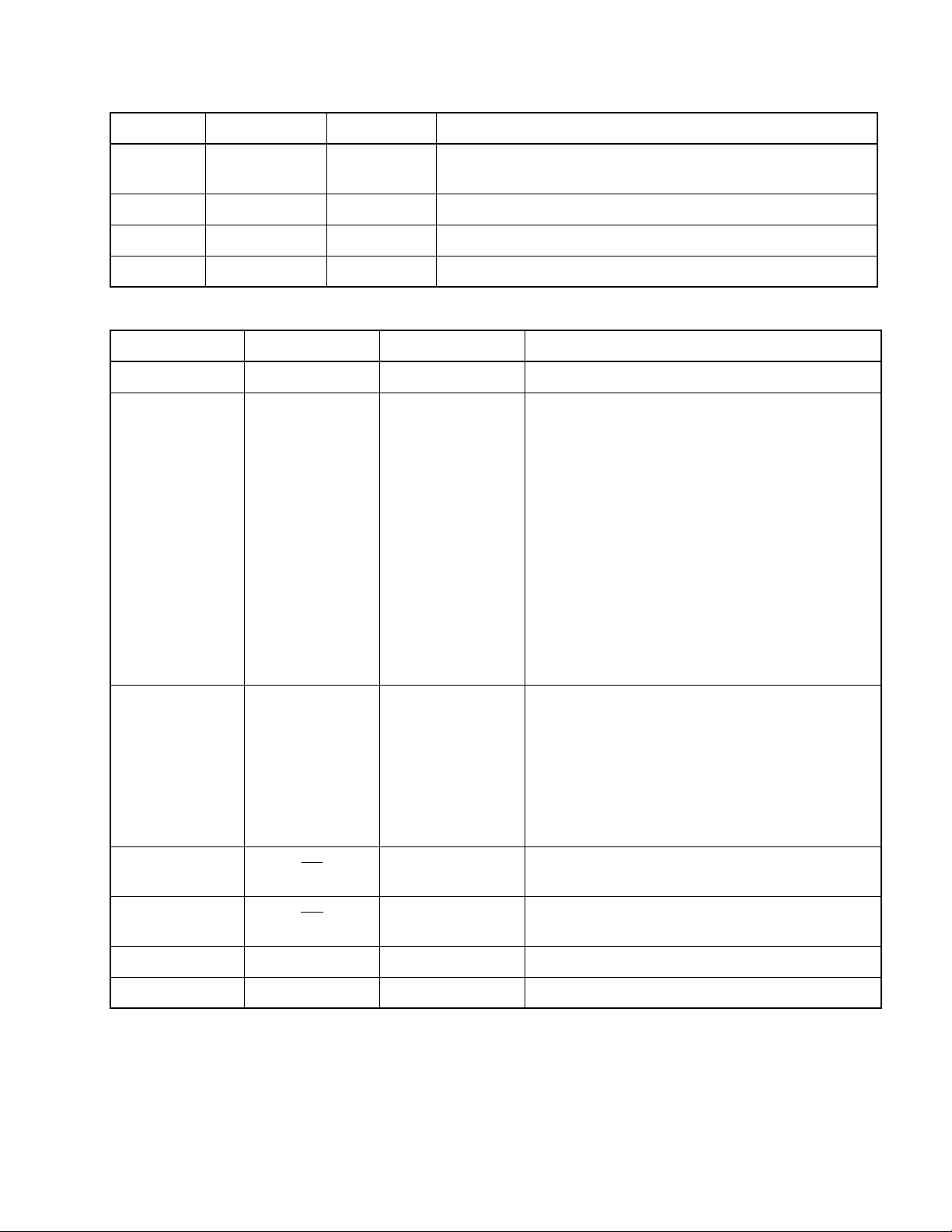

Table 1.5-3 Input/Output Circuit Configurations ........................................................................................... 10

Table 2.1-1 Table of Reset and Interrupt Vectors ......................................................................................... 15

Table 2.2-1 Opeating State of Low-power Consumption Modes .................................................................. 21

Table 2.2-2 Selection of Oscillation Stabilization Time ................................................................................. 22

Table 2.2-3 Sources of Reset ....................................................................................................................... 24

Table 2.4-1 List of Port Functions ................................................................................................................. 28

Table 3.3-1 Interrupt Sources and Interrupt Vectors .................................................................................... 59

Table 3.4-1 Low-power Consumption Mode at Each Clock Mode ................................................................ 60

Table 3.5-1 Pin State of MB89990 ............................................................................................................... 61

Table 5.1-1 Mask Options ............................................................................................................................ 72

v

Page 10

vi

Page 11

CHAPTER 1 GENARAL

The MB89990 series contains microcontrollers with a full range of resources such as

timers, external interrupts, and remote-control function, as well as the F2MC-8L CPU

core for low-voltage and high-speed operation. This single-chip microcontroller is

suitable for small devices such as remote controllers incorporating compact packages.

1.1 Features

1.2 Product Series

1.3 Block Diagram

1.4 Pin Assignment

1.5 Pin Function Description

1.6 Handling Devices

1

Page 12

CHAPTER 1 GENARAL

1.1 Features

This section describes the features .

■

Features

• Minimum instruction execution time: 0.95 µs at 4.2 MHz (V

2

• CPU core common to F

• Instruction set su itable for controlle r: - M ult ipl y /su btr ac tio n i ns truction, - 16-bit oper ati on,

- Instruction test and branch instruction, - Bit operation instruction

•Two timers

• 8/16-bit timer/counter

• 20-bit time-base counter

• External interrupts

• Edge detection: 3 pins (edge direction enabled)

• Low-level interrupt: 8 pins (wake-up)

• Built-in remote-control carrier frequency generator

• Low-power consumption modes

• Stop mode: Almost no power consumption because oscillation stopped

• Sleep mode: 33% of normal power consumption because CPU stopped

• Package: SOP-28, SH-DIP-28 (mask ROM only)

MC-8L CPU

CC

= 3 V)

2

Page 13

1.2 Product Series

1.2 Product Series

This section describes the product series.

■

Product Series

Table 1.2-1 "Types and Functions of MB89990 Series of Microcontrollers"lists the types and

functions of the MB89990 series of microcontrollers.

Table 1.2-1 Types and Functions of MB89990 Series of Microcontr ollers

Model Name MB89997 MB89P195* MB89PV190*

Classification Mass-produced product (mask ROM

product)

ROM capacity 32 K × 8 bits

(internal ROM)

RAM capacity 128 × 8 bits 256 × 8 bits

CPU functions Number of basic instructions

Instruction bit length

Instruction length

Data bit length

Minimum instruction execution time

Interrupt processing time

Port I/O port (N-ch open drain)

I/O port (CMOS)

Total

Timer counter 2 channels 8-bit counter or 1 channel 16-bit counte

External-interrupt 1 3 independent channels (edge selection, interrupt vector, interrupt source flag)

Interrupt mode selectable from rising edge, falling edge, or both edges

For releasing Stop/Sleep modes (edge detection in Stop mode enabled)

136 instructions

8 bits

1 to 3 bytes

1, 8, 16 bits

0.95 µs/4.2 MHz

8.6 µs/4.2 MHz

6 pins

16 pins (13 used as resource pins)

22 pins

One-time product For evaluation

and development

16 K × 8 bits

(internal ROM,

write enable by

general-purpose

writer)

32 K × 8 bits

(external ROM)

External-interrupt 2

(Wake-up)

Remote-control

carrier frequency

Standby mode Sleep and Stop modes

Process CMOS

Package FPT-28P-M02, DIP-28P-M03 FPT-28P-M02 MQP-48C-P01

Operating voltage 2.2 to 6.0 V** 2.7V to 6.0 V

8 channels (Low-level interrupt enabled)

Pulse width and cycle are programmable

3

Page 14

CHAPTER 1 GENARAL

* The MB89P195 microtroller is the one-time product for the MB89190 series which can be also be used

for the MB89990 series.

* The MB89PV190 microtroller is the evaluation and development product for the MB89190 series which

can be also be used for the MB89990 series.

** Operating voltage varies with conditions such as frequency or others. See the data sheet for details.

4

Page 15

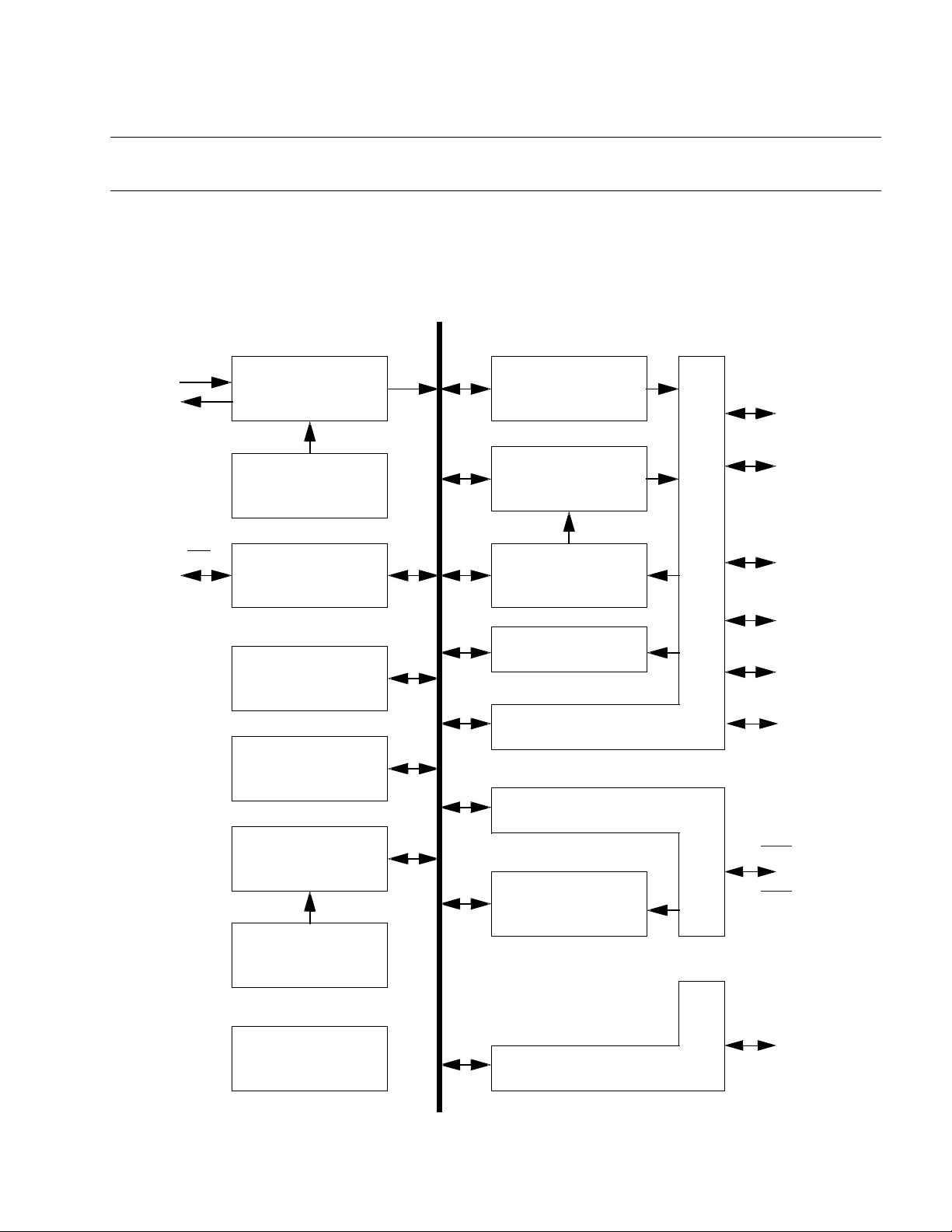

1.3 Block Diagram

This section describes the block diagram.

■

Block Diagram

Internal Bus

1.3 Block Diagram

X0

X1

RST

Main oscillator

circuit

Clock control

Reset circuit

(WDT)

Time-base timer

RAM

(128 x 8 bits)

Remote-control

carrier frequency

8-bit timer/counter

8-bit timer/counter

External Interrupt

CMOS I/O port

CMOS I/O port

P34/TO/INT10

P33 / EC

P30 ~ P32

Port 3

P35 / INT11

P36 / INT12

P37 / RCO

2

F

MC-8L

CPU

ROM

(32K x 8 bits)

TEST

Vcc, Vss

External Interrupt

(wake-up)

N-ch open drain I/O port

P00 / INT20 to

Port 0Port 4

P07 / INT27

P40 ~ P45

5

Page 16

CHAPTER 1 GENARAL

1.4 Pin Assignment

This section describes the pin assignment.

■

Pin Assignment

Figure 1.4-1 Pin Assignment (FPT-28P-M02, DIP-28P-M03)

P04/INT24

P05/INT25

P06/INT26

P07/INT27

TEST

RST

X0

X1

V

SS

P37/RCO

P36/INT12

P35/INT11

P34/TO/INT10

P33/EC

1

2

3

4

5

6

7

8

9

10

11

12

13

14

(TOP VIEW)

28

27

26

25

24

23

22

21

20

19

18

17

16

15

V

CC

P03/INT23

P02/INT22

P01/INT21

P00/INT20

P45

P44

P43

P42

P41

P40

P30

P31

P32

6

Page 17

Figure 1.4-2 Pin Assignment (MQP-48C-P01)

P35/INT11

N.C.

N.C.

N.C.

N.C.

N.C.

Vss

N.C.

N.C.

N.C.

N.C.

48 47 46 45 44 43 42 41 40 39 38 37

1.4 Pin Assignment

N.C.

P34/TO/INT10

P33/EC

P32

P31

P30

P40

P41

P42

P43

P44

P45

P00/INT20

1

2

3

4

5

6

7

8

9

10

11

12

*

68 67 66 65 64 63 62 61

69

70

71

72

73

74

75

76

77 78 79 80 49 50 51 52

13 14 15 16 17 18 19 20 21 22 23 24

N.C.

N.C.

P10/INT21

(TOP VIEW)

N.C.

N.C.

N.C.

N.C.

Vcc

60

59

58

57

56

55

54

53

N.C.

N.C.

P02/INT22

P30/INT23

36

35

34

33

32

31

30

29

28

27

26

25

N.C.

N.C.

P36/INT12

P37/RCO

X1

X0

RST

TEST

P07/INT27

P06/INT26

P05/INT25

P04/INT24

* Pin assignment on package top (only for piggyback/evaluation product)

Pin No. Symbol Pin No. Symbol Pin No. Symbol Pin No. Symbol

49 V

PP 57 NC 65 04 73 OE

50A1258A2660574NC

51 A7 59 A1 67 06 75 A11

52 A6 60 A0 68 07 76 A9

53 A5 61 01 69 08 77 A8

54 A4 62 02 70 CE

78 A13

55 A3 63 03 71 A10 79 A14

56 NC 64 GND 72 NC 80 V

CC

7

Page 18

CHAPTER 1 GENARAL

1.5 Pin Function Description

This section describes the pin functions.

■

Pin Function Description

Table 1.5-1 "Pin Function Description" and Table 1.5-2 "Pins for External ROM" list the pin

function and Table 1.5-3 "Input/Output Circuit Configurations" shows the input/output circuit

configurations.

Table 1.5-1 Pin Function Description

Pin No. Pin Name Circuit type Function

7X0

8X1

5TEST B

RST

6

P00/INT20

24 to 27

1 to 4

17 P30 E

16 P31 E

15 P32 E

14 P33/EC D

to

P03/INT23

P04/INT24

to

P07/INT27

A

C

D

D

Clock oscillator pins

Test input pin

These pins are connected directly to V

Reset I/O pin

This pin consists of an N-ch open-drain output with a pull-up

resistor and hysteresis input. A Low level is output from this

pin by internal source. The internal circuit is initialized at

input of a Low level.

General-purpose I/O port

These ports also serve as external interrupt input pin.

The external interrupt input is hysteresis type.

General-purpose I/O port

These ports also serve as external interrupt input pin.

The external interrupt input is hysteresis type.

General-purpose I/O port

General-purpose I/O port

General-purpose I/O port

General-purpose I/O port

This port also serves as an external clock input pin for the 8bit timer/counter. The external clock input is hysteresis type

with a built-in noise filter.

SS

.

13 P34/T0/INT10 D

12 P35/INT11

11 P36/INT12

8

General-purpose I/O port

This port also serves as an overflow output pin and an

external interrupt input pin for the 8-bit timer/counter. The

external interrupt input is hysteresis type with a built-in noise

filter.

General-purpose I/O port

D

This port also serves as an external interrupt input pin. The

external interrupt input is hysteresis type with a built-in noise

filter.

Page 19

Table 1.5-1 Pin Function Description (Continued)

Pin No. Pin Name Circuit type Function

1.5 Pin Function Description

10 P37/RCO E

18 to 23 P40 to P45 F

28 V

9V

CC

SS

—

—

General-purpose I/O port

This port also serves as remote-control output pin.

N-ch open-drain type I/O port

Power pin

Power (GND) pin

Table 1.5-2 Pins for External ROM

Pin No. Pin Name Circuit type Functinon

49 V

79

78

50

75

69

76

77

51

52

53

54

55

58

59

60

PP

A14

A13

A12

A11

A10

A9

A8

A7

A6

A5

A4

A3

A2

A1

A0

Output

Output

High-level output pin

Address-output pins

61

62

63

65

66

67

68

69

01

02

03

04

05

06

07

08

70 CE

73 OE

80 V

64 V

CC

SS

Intput

Output

Output

Output

Output

Data-input pins

Chip-enable pin for ROM

A High level is output in the standby mode.

Output-enable pin for ROM

A Low level is always output.

Power pin for EPROM

Power (GND) pin

9

Page 20

CHAPTER 1 GENARAL

Table 1.5-3 Input/Output Circuit Configurations

Classification Circuit Remarks

A • Crystal oscillator

X1

• Feedback resistor: About 1 MΩ/5V

(1 to 5MHz)

X0

Standby control signal

B • CMOS input

C • Output pull-up resistor (P-ch):

About 50 kΩ (5 V)

R

• Hysteresi s inp u t

Pch

Nch

D • CMOS input/output

• Hysteresis input (resorce input)

R

Pch

Pch

Nch

• The pull-up resistor is available.

10

Page 21

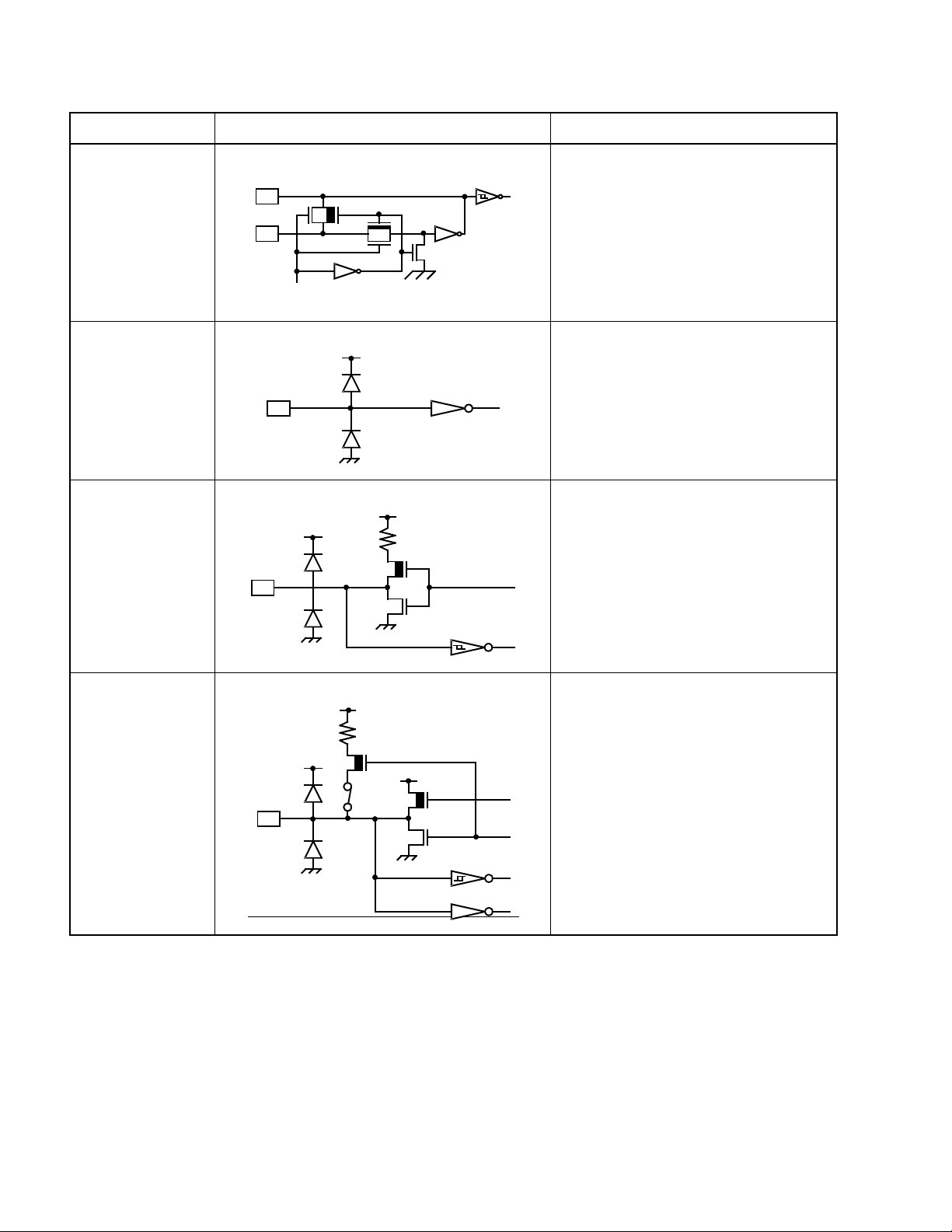

1.5 Pin Function Description

Table 1.5-3 Input/Output Circuit Configurations (Continued)

Classification Circuit Remarks

E • CMOS input/output

• The pull-up resistor is available.

R

Pch

Pch

Nch

F • N-ch open-drain output

• Analog input

R

Pch

• The pull-up resistor is available.

(MB89990 series only)

Nch

Analog input

11

Page 22

CHAPTER 1 GENARAL

1.6 Handling Devices

This section describes handling devices.

■

Handling Devices

(1) Preventing latch-up

Latch-up may occur if a voltage high er than V

or lower than VSS is applied to the input or

CC

output pins other than middle- and high-level-resistant pins, or if voltage exceeding the rated

value is applied between V

and VSS. When latch-up occurs, the supply current increases

CC

rapidly, sometimes r esulting in overheating and destruc tion. Therefore, no voltage exceeding

the maximum ratings should be used.

(2) Handling unused input pins

Leaving unused inp ut pin s open may cause a malfu nction. Therefore, t hese pin s shoul d be set

to pull-up or pull-down.

(3) Variations in supply voltage

Although the specif ied V

supply voltage op erating range is assured, a sud den change in the

CC

supply voltage within the specified range may cause a malfunction. Therefore, the voltage

supply to the IC should be kept as cons tant as possible. The V

supply frequency (50 to 60 Hz) should be less than 10% of the typical V

ripple (P-P value) at the

CC

value, or the

CC

coefficient of exces sive variati on should be less tha n 0.1 V/ms instantaneous change whe n the

power supply is switched.

(4) Precautions for external clocks

It takes some time for oscillation to stabilize after changing the mode from power-on reset

(option selection) and stop mode. Consequently, an external clock must be input.

(5) Recommended screening conditions

The OPTROM product should be screened by high-temperature aging before mounting.

12

Verify program

High-temperature aging (150°C, 48 H)

Read

Mount

The programming test can not be perform ed for all bi ts of the prep rogr ammed OPTROM product

due to its characteristics. Consequently, 100% programming yielding cannot be ensured.

Page 23

CHAPTER 2 HARDWARE CONFIGRATION

This chapter describes each block of the CPU hardware.

2.1 CPU

2.2 Clock Control Block

2.3 Interrupt Controller

2.4 I/O Ports

2.5 8/16-bit Timer (Timer 1 and Timer 2)

2.6 External Interrupt 1

2.7 External Interrupt 2 (Wake up)

2.8 Remote-control Carrier Frequency Generator

2.9 Time-base Timer

2.10 Watchdog Timer Reset

13

Page 24

CHAPTER 2 HARDWARE CONFIGRATION

2.1 CPU

• This section describes the memory space and register composing CPU hardware.

■

Memory Space

The MB89990 series of microc ontroller s have a memo ry area of 64K bytes . All I/O, data area s,

and program areas are located in this space. The I/O area is at the lowest address and the data

area is immediately above it. The data area may be divided into register, stack, and directaddress areas according to the applications. The program area is located near the highest

address and the tables of interrupt and reset vectors and vector-call instructions are at the

highest address. Figure 2.1-1 "Memory Space of MB89990 Series of Microc ontrollers" shows

the structure of the memory space for the MB89990 series of microcontrollers.

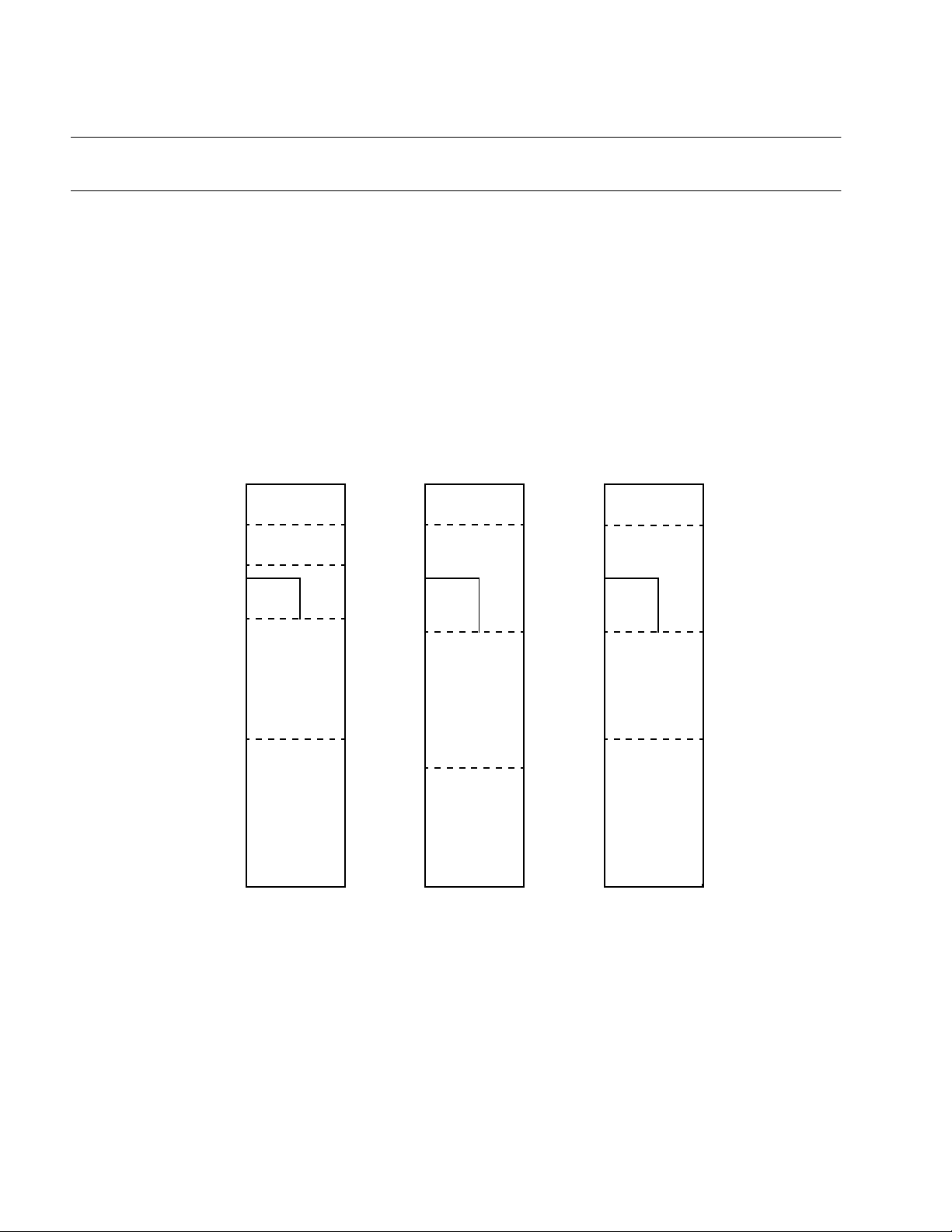

Figure 2.1-1 Memory Space of MB89990 Series of Microcontrollers

0000H

0080H

00C0H

0100H

0140H

8000H

FFFFH

MB89997

I/O

Vacant area

Register

Vacant area

Mask ROM

RAM

0000H

0080H

0100H

0180H

C000H

FFFFH

MB89P195

I/O

RAM

Register

Vacant area

Program PROM

(Mask ROM)

0000

0080H

0100H

0180H

8000H

FFFFH

MB89PV190

H

I/O

RAM

Register

Vacant area

External ROM

14

• I/O area

• This area is where various reso urce s such as contr ol and d ata reg ister s are loc ated. T he

memory map for the I/O area is given in APPENDIX A .

• RAM area

• This area is where the stati c RAM is lo cat ed. Ad dr es se s from

013F

for the MB89997) are also used as the general-purpose register area.

H

0100

H

to

017F

H

0100

(

• ROM area

• This area is whe re the in ter nal RO M is lo ca ted. Addresses fro m

FFC0

FFFF

to

H

H

to

H

are also

Page 25

used for the table o f reset and vector-c all instructions. T able 2.1-1 "Table of Reset and

Interrupt Vectors " shows the correspondence between each interrupt number or reset

and the table addresses to be referenced for the MB89990 series of microcontrollers.

Table 2.1-1 Table of Reset and Interrupt Vectors

Table address

Upper data Lower data

2.1 CPU

CALLV #0

CALLV #1

CALLV #2

CALLV #3

CALLV #4

CALLV #5

CALLV #6

CALLV #7

Interrupt #11

Interrupt #10

Interrupt #9

Interrupt #8

FFC0

FFC2

FFC4

FFC6

FFC8

FFCA

FFCC

FFCE

H

H

H

H

H

H

H

H

FFC1

FFC3

FFC5

FFC7

FFC9

FFCB

FFCD

FFCF

H

H

H

H

H

H

H

H

Table address

Upper data Lower data

FFE4

FFE6

FFE8

FFEA

H

H

H

H

FFE5

FFE7

FFE9

FFEB

H

H

H

H

Interrupt #7

Interrupt #6

Interrupt #5

Interrupt #4

Interrupt #3

Interrupt #2

Interrupt #1

Interrupt #0

Reset mode – – – –

Reset vector

Note:

FFFC

Set

is already reserved.

H

H

for

FFFD

in the Reset mode.

H

00

FFEC

FFFE

FFF0

FFF2

FFF4

FFF6

FFF8

FFFA

FFFE

H

H

H

H

H

H

H

H

H

FFED

FFEF

FFF1

FFF3

FFF5

FFF7

FFF9

FFFB

FFFD

FFFF

H

H

H

H

H

H

H

H

H

H

15

Page 26

CHAPTER 2 HARDWARE CONFIGRATION

■

Arrangement of 16-bit Data in Memory

When the MB89990 ser ies of microcontroller s handle 16-bit data, the data written at the lowe r

address is treated as the upper data and tha t written at th e next address is treated as the lower

data as shown in Figure 2.1-2 "Arrangement of 16 bit Data in Memory".

Figure 2.1-2 Arrangement of 16 bit Data in Memory

Before execution

1234H

A

Memory

ABCFH

ABCEH

ABCDH

ABCCH

MOVW ABCDH , A

After execution

1234H

A

Memory

34H

12H

ABCFH

ABCEH

ABCDH

ABCCH

This is the same as when 16 bits are specified by the operand during execution of an

instruction. Bits closer to the OP code are treated as the upper byte and those next to it are

treated as the lowe r byte. This is als o the same when the me mory a ddress or 1 6-bit i mmediate

data is specified by the operand.

Figure 2.1-3 Arrangement of 16-bit Data during Execution of Instruction

[Example]

MOV A, 5678

H ; Extended address

Assemble

XXXXH XX XX

Data saved in the stack by an interrupt is also treated in the same manner.

■

Internal Registers in CPU

The MB89990 serie s of microcontrollers have dedicated registers specifi ed applications in the

CPU and general-purpose registers in memory.

• Program counter (PC) 16-bit long register indicating location where instructions

• Accumulator (A) 16-bit long register where results of operations stored

• Temporary accumulator (T) 16-bit long register where the operations are performed

• Stack pointer (SP) 16-bit long register indicating stack area

XXXX

H 60 56 78 ; Extended address

H E4 12 34 ; 16-bit immediate data

XXXX

H XX

XXXX

stored

temporarily. The lower byte is used to execute 8-bit data

processing instructions.

between this register and the accumulator. The lower byte

is used to execute 8-bit data processing instructions.

16

Page 27

2.1 CPU

• Processor status (PS) 16-bit long register where register pointers and condition

codes stored

• Index register (IX) 16-bit long register for index modification

• Extra pointer (EP) 16-bit long register for memory addressing

16 bits

P C

A

T

IX

EP

SP

PS

Program counter

Accumulator

Temporary accumulator

Index register

Extra pointer

Stack pointer

Processor status

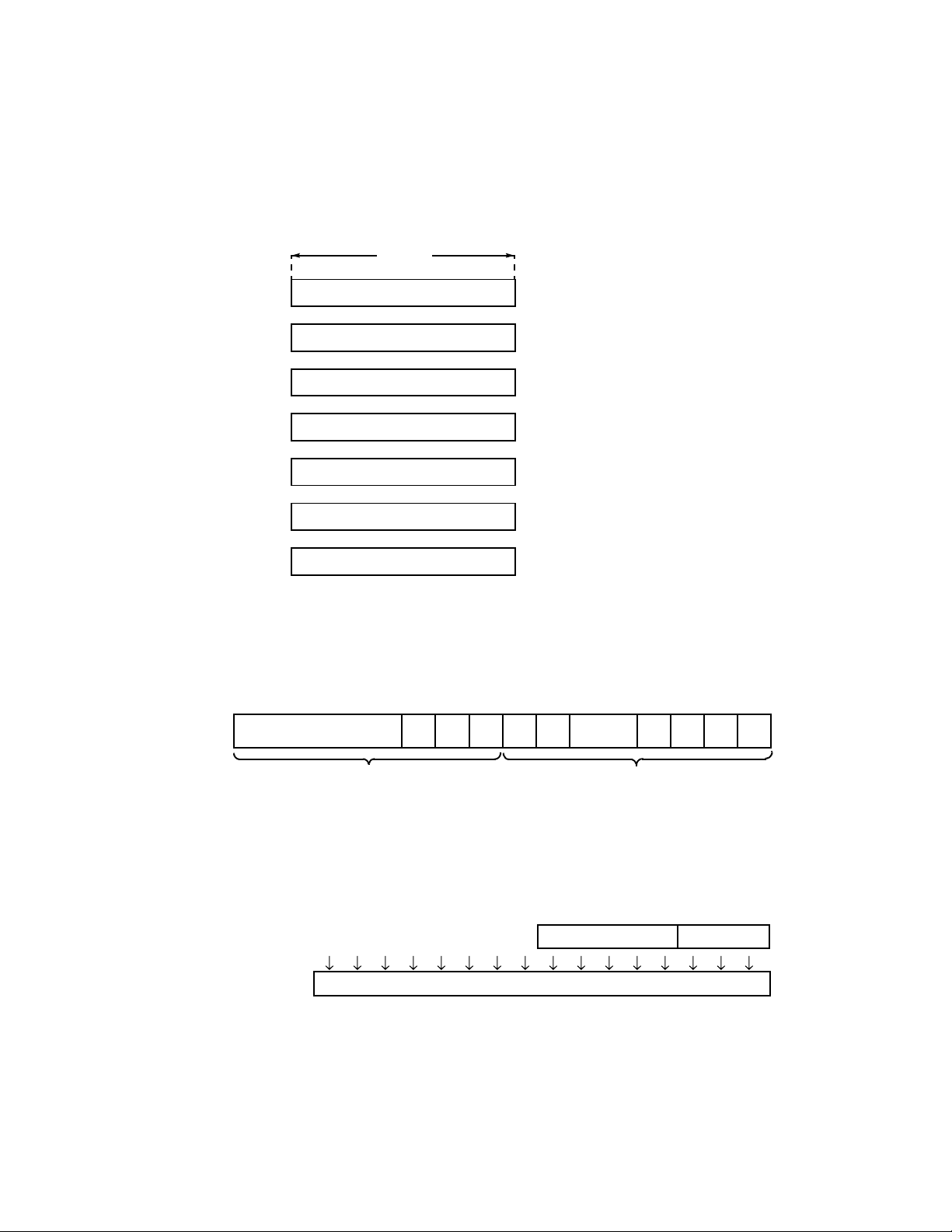

The 16 bits of the processor statu s (PS) can be divided into 8 upper bits for a register bank

pointer (RP) and 8 lower bits for a con dition code register (CCR ). (See Fig ure 2.1-4 "S tructure

of Processor Status".)

Figure 2.1-4 Structure of Processor Status

1514131211109876543210

PS

RP H I N Z V C

Vacant Vacant Vacant

IL1, 0

RP

CCR

The RP indicates the add ress of the cu rrent regi ster bank. T he contents of the RP and the re al

addresses are translated as shown in Figure 2.1-5 "Rule for Translating Real Addresses at

General-purpose Register Area" .

Figure 2.1-5 Rule for Translating Real Addresses at General-purpose Register Area

Lower bits of OP code

Source address

R P

'0' '0' '0' '0' '0' '0' '0' '1' R4 R3 R2 R1 R0 b2 b1 b0

A15 A14 A13 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0

The CCR has bits indicating the results of operations and transfer data contents, and bits

controlling the CPU operation when an interr upt oc curs .

- H-flag H-flag is set when a carry or a borrow out of bit 3 into bit 4 is generated

as a result of operations. It is cleared in other cases. This flag is used

for decimal-correction instructions.

17

Page 28

CHAPTER 2 HARDWARE CONFIGRATION

- I-flag An interrupt is enabled when this flag is 1 and is disabled when it is 0.

The I-flag is 0 at reset.

- IL1 and IL0 These bits indicate the level of the currently-enabled interrupt. The

Interrupt Processing executes interrupt processing only when an

interrupt with a value smaller than the value indicated by this bit is

requested.

IL1 IL0 Interrupt level High and low

0

0

1

1

- N-flag The N-flag is set when the most significant bit is 1 as a result of

operations. It is cleared when the MSB is 0.

- Z-flag Z-flag is set when the bit is 0 as a result of operations. It is cleared in

other cases.

0

1

0

1

1

2

3

High

Low = No interrupt

- V-flag V-flag is set when a twoís complement overflow occurs as a result of

operations. It is reset when an overflow does not occur.

- C-flag C-flag is set when a carry or a borrow out of bit 7 is generated as a

result of operations. It is cleared in other cases. When the shift

instruction is executed, the value of the C-flag is shifted out.

• General-purpose registers

General-purpose registers are 8-bit long registers for storing data.

The 8-bit long general- purpose registers are in the register ba nks in memory. One bank has

eight registers and up to 16 b anks are available for the MB89193 (8 banks for the MB89191).

The register bank pointer (RP) indicates the currently-used bank.

Figure 2.1-6 Register Bank Configuration

Address = 0100H + 8 (RP)

+

R0

R1

R2

R3

R4

R5

R6

R7

16 banks

18

Memory area

Page 29

2.2 Lock Control Block

• This block controls the standby operation and software reset.

■

Machine Clock Control Block Diagram

STP SLP SPL

2.2 Lock Control Block

Pin state

Stop

Sleep

Clock generator

From timebase timer

* f = oscillation

■

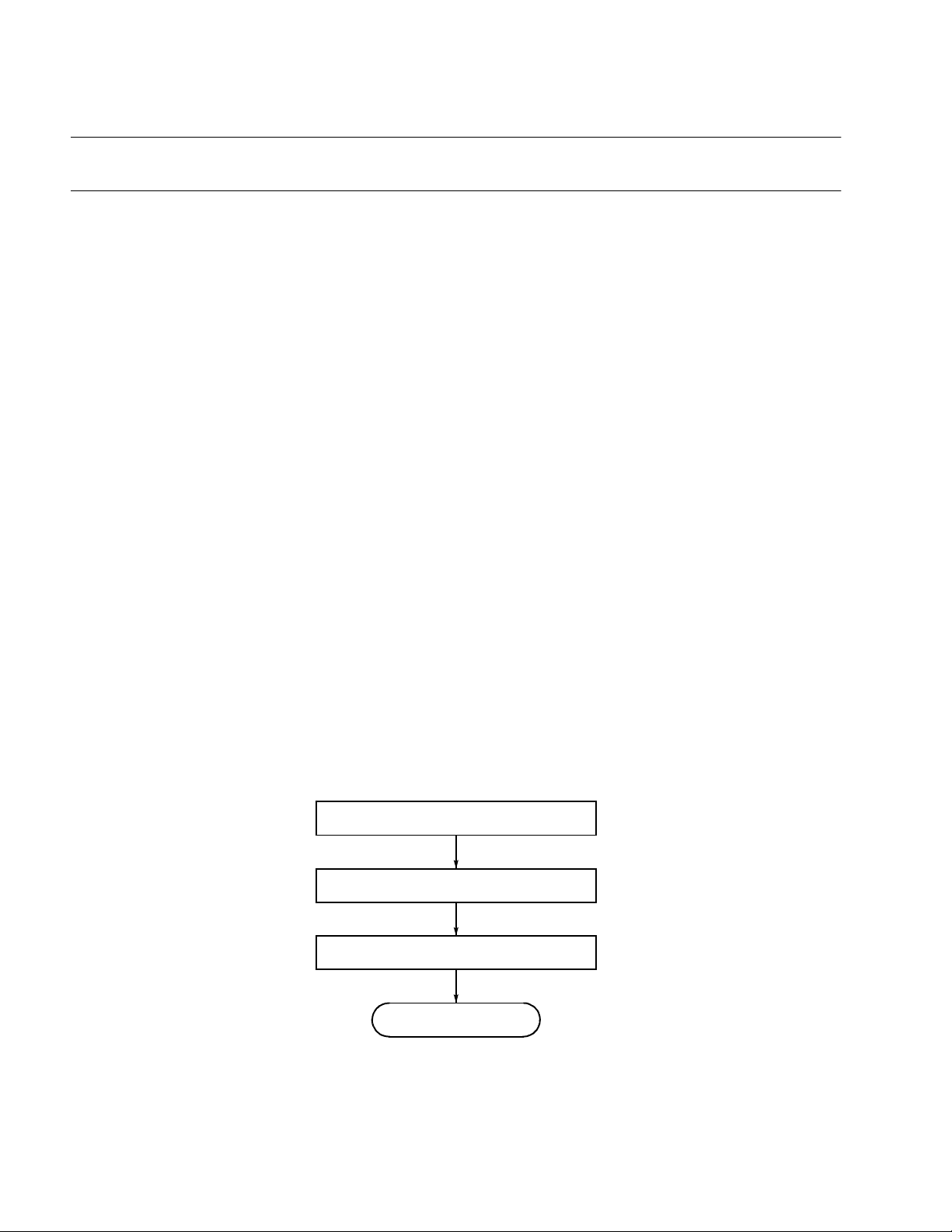

Register List

frequency

22/f*

12

/f

2

16

2

18

2

/f

/f

Selector

Stop release signal

Option

Address: 0008H STBC

8 bit

Clock control

R/W Stanby control register

CPU operation clock

Resource operation clock

19

Page 30

CHAPTER 2 HARDWARE CONFIGRATION

■

Description of Registers

The detail of each register is described below.

• Standby-control register (STBC)

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

Address: 0008

STP SLP SPL RST — — — —

H

(W) (W) (R/W) (W)

Intilial value

0001XXXX

B

[Bit 7] STP: Stop bit

This bit is used to specify switching CPU to the stop mode.

0 No operation

1 Stop mode

This bit is cleared at reset or stop cancellation.

0 is always read when this bit is read.

[Bit 6] SLP: Sleep bit

This bit is used to specify switching the CPU and resources to the sleep mode.

0 No operation

1 Sleep mode

This bit is cleared at reset, sleep or stop cancellation.

0 is always read when this bit is read.

[Bit 5] SPL: Pin state specifying bit

This bit is used to specify the external pin state in the stop mode.

0 Holds state and level immediately before stop mode

1 High impedance

This bit is cleared at resetting.

[Bit 4] RST: Software reset bit

This bit is used to specify the software reset.

0 Generates 4-cycle reset signal

1 No operation

1 is always read when this bit is read.

20

Page 31

■

Description of Operation

Main/sub clock block has normal and low-power consumption mode. The low-power

consumption mode are described below.

(1) Low-power consumption mode

This chip has three op eration m odes. T he slee p mode a nd stop mode i n the tabl e belo w reduce

the power consumption.

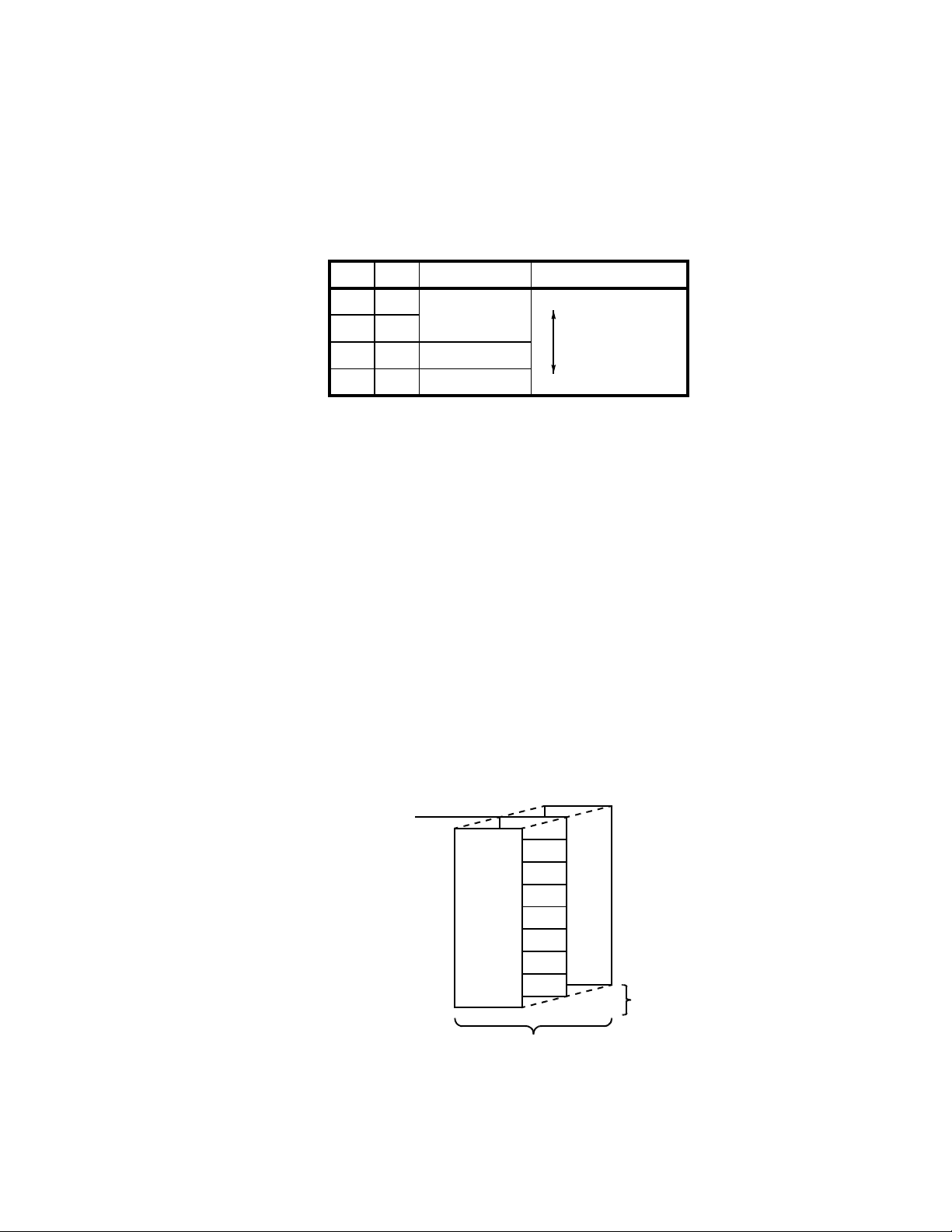

Table 2.2-1 Opeating State of Low-power Consumption Modes

Clock mode

of CPU

Clock pulse

Each operating clock pulse

(4 Mhz clock)

CPU

Time base

timer

resource

Each

2.2 Lock Control Block

Wake-up source

in each mode

RUN

Oscillates

Sleep

• The SLEEP mode stops only the operating clo ck pulse of the CPU. Other ope rations are

continued.

• The STOP mode stops the osci llation. Data c an be held with the lowest power consum ption

in this mode.

(a) SLEEP state

• Switching to Sleep State

• Writing 1 at the SLP bit (bit6) of the STBC register switches the mode to SLEEP state.

• The SLEEP state is the mode to stop clock pulse operating the CPU. Only the CPU

stops and the resources continue to operate.

• If an interrupt is requested when 1 is writte n at the SLP bit (bit 6), in struction execution

continues without switching to the SLEEP state.

• In the SLEEP state, the values of registers and RAM immediately before entering the

SLEEP state are held.

• Cancelling SLEEP state

2.0 MHz

Stops

2.0 MHz 2.0 MHz

Various interrupt

requests

• The SLEEP state is cancelled by inputting the reset signal and requesting an interrupt.

• When the reset sign al is input during the SLEEP state, the CPU is switched to t he reset

state and the SLEEP state is cancelled.

• When an interrupt l evel higher than 11 is reques ted from a resource during the SL EEP

state, the SLEEP state is cancelled.

• When the I flag and IL bit are enabled interrupt like an ordinary inte rrupt after cancelling,

the CPU executes th e interrupt processing. When they are disa bled, the CPU execute s

the interrupt proces sing from the instruction ne xt to the one before entering the SLEEP

state.

(b) STOP state

• Switching to STOP state

• Writing 1 at the STP bit (bit7) of the STBC register switches the mode to STOP state.

• In the STOP state, the clock oscillation, CPU, and all resources are stopped.

21

Page 32

CHAPTER 2 HARDWARE CONFIGRATION

• The input/output pins an d output pins during the STOP state can be controlled by the

SPL bit (bit5) of the STBC register so that they are held in the state immediately before

entering the STOP state, or so that they enter in the high-impedance state.

• If an interrupt is requ ested when 1 is written at the STP bi t (bit 7), instruction execution

continues without switching to the STOP state.

• In the STOP state, the values of registers and RAM immediately before entering the

STOP state are held.

• Cancelling STOP state

• The STOP state is cancelled either by inputting the reset signal or by requesting an

interrupt.

• When the reset signal is input during the STOP state, the CPU is switche d to the reset

state and the STOP state is cancelled.

• When an interrupt higher than level 11 is requested from the external interrupt circuit

during the STOP state, the STOP state is cancelled.

• When the I flag and IL bit a re enabled interrupt lik e an ordina ry interru pt after cancel ling,

the CPU executes the i nterrupt processing. When they are disabl ed, the CPU executes

the interrupt processing from the instruction next to the one before entering t he STOP

state.

• The oscillation st abilization ti me can be se lected by th e option from any of the four types

listed in Table 2.2-2 "Selection of Oscillation Stabilization Time".

• If the STOP state is cancelled by inpu tting the reset signal, the CPU is switched to the

oscillation stabiliz ation wait state. Therefore, the reset se quence is not executed unless

the oscillation s tabilizatio n time is elaps ed. The os cillation sta bilization time corresp onds

to the oscillation stabilization time of the main clock selected by the o ption. However,

when Power-on Reset is not s pecif ied by the mask option, the CP U is not s witch ed to the

oscillation stabilization wait state even if the STOP state is cancelled by inputting the

reset signal.

Table 2.2-2 Selection of Oscillation Stabilization Time

Ocillation stabilization time Ocillation stabilization time with 4 MHz source clock

18

2

/f* Approximate 65.5 ms

16

2

/f* Approximate 16.4 ms

12

2

/f* Approximate 1.2 ms

22/f* Approximate 0 ms

* f = source clock frequency

22

Page 33

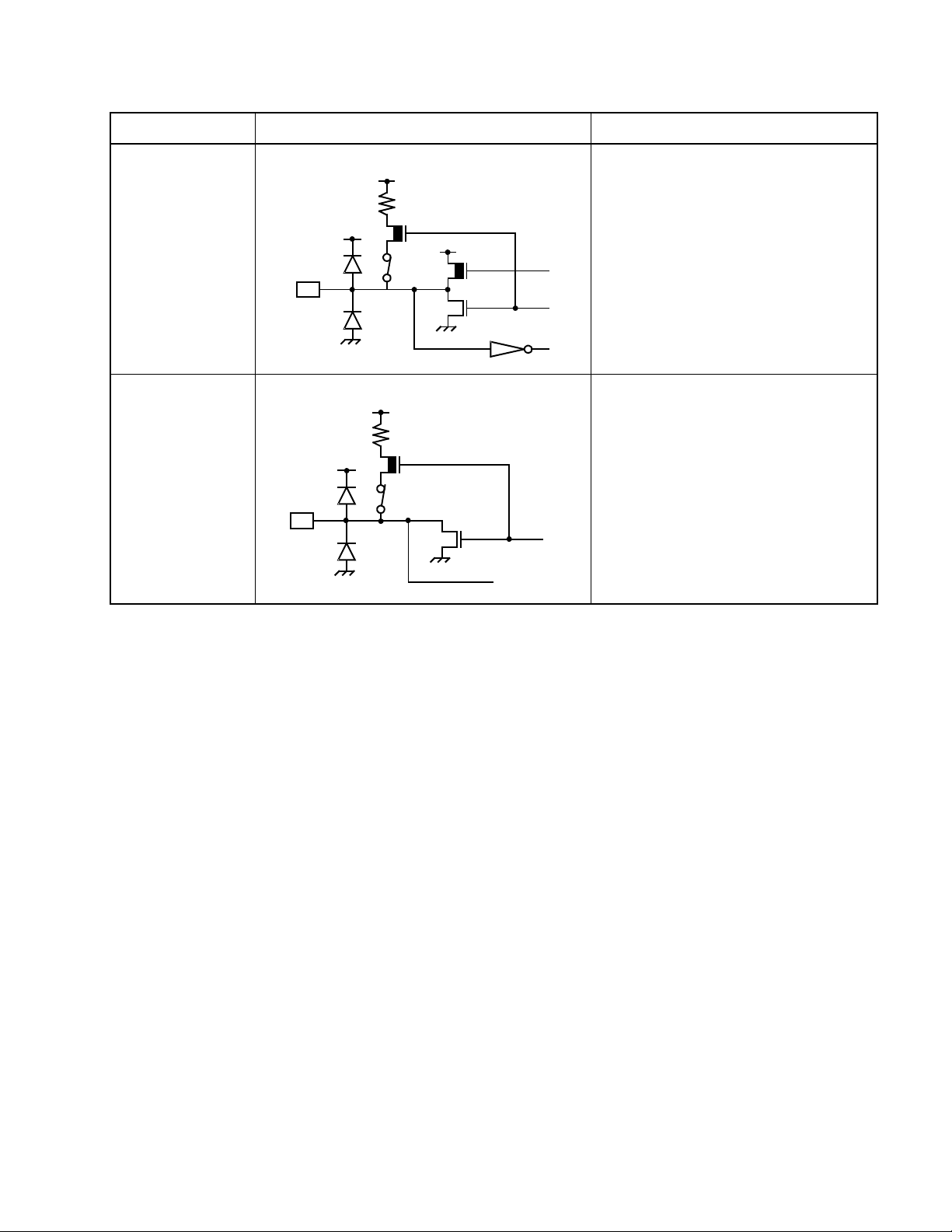

(2) State transition diagram at low power consumption mode

SLEEP

Clock oscillate

(h)

STOP

Clock stop

(f)

(e)

2.2 Lock Control Block

(g)

(c)

Oscillation

stabilization waiting

(a) (b)

Power-on

(a) When power-on reset option selected

(b) When power-on reset option not selected

(c) After oscillation stabilized

(d) Set STP bit to 1.

(d)

Clock oscillate

RUN

(e) Set SLP bit to 1.

(f) External reset when power-on reset option not selected

(g) External reset or interrupt when power-on reset option selected

(h) External reset or interrupt

23

Page 34

CHAPTER 2 HARDWARE CONFIGRATION

■

Reset Control Section

Power-on reset

Watchdog timer reset

External reset

Software reset

• Reset

• There are four types of resets as shown in Table 2.2-3 "Sources of Reset".

Table 2.2-3 Sources of Reset

Reset name Description

Power-on reset Turns power on

Watchdog reset Overflows watchdog timer

External-pin reset Sets external-reset pin to Low

Software reset Writes 0 at RST bit (bit 4) of STBC

Reset control

Internal reset signal

When the power-on reset and reset dur ing the stop state are used, the oscillat ion stabilization

time is needed after the oscillator operates be cause the oscillator stops. The time-base timer

controls this stabilization time. Consequently, the operation does not start immediately even

after cancelling the reset.

However, if the mas k option w ith out Powe r-on Res et is sele cted, n o oscil lation stabi liza tion ti me

is required in any state after external pins have been released from the reset.

Note:

When resetting a product without the power-on reset function, set a longer time than the

optional oscillation stabilization time. Otherwise, the reset timing matches the AC

characteristics.

24

Page 35

2.3 Interrupt Controller

2.3 Interrupt Controller

• The interrupt controller for the F2MC-8L family is located between the CPU and each

resource. This controller receives interrupt requests from the resources, assigns

priority to them, and transfers the priority to the CPU. It also decides the priority of

same-level interrupts.

■

Block Diagram

CPU

F2MC-8L bus

Resource #1

Resource #2

Resource #n

■

Register List

2

Test reg-

ister

G L

G

•

G

Address decorder

Level

L

L

Level

Level

Level

deciding

block

G

G

•

G

Same level

priority order

deciding block

Interrupt vector generation

•

block

•

•

Interrupt controller consi sts o f interr upt-lev el re giste rs (IL R1, 2, an d 3) and in terrupt- test re giste r

(ITR).

8 bit

Address: 007CH

Address: 007DH

Address: 007EH

Address: 007FH

ILR1

ILR2

ILR3

ITR

W Interrupt level register #1

W Interrupt level register #2

W Interrupt level register #3

— Interrupt test register

25

Page 36

CHAPTER 2 HARDWARE CONFIGRATION

■

Description of Registers

The detail of each register is described below.

(1) Interrupt levei setting register (ILR1 to ILR3)

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

Address: 007C

Address: 007D

Address: 007E

The ILRX sets the interrupt level of each resource. The digits in the center of each bit

correspond to the interrupt numbers.

[Example]

Interrupt requests

from resources

L3X

H

H

H

L31 L30 L21 L20 L11 L10 L01 L00

L71 L70 L61 L60 L51 L50 L41 L40

LB1 LB0 LA1 LA0 L91 L90 L81 L80

Intilial value

11111111

MB89990 hardware manual

Interrupt control module

IR0

IR1

IR2

IR3

IRB

Interrupt

number

#0

#1

#2

#3

#11

Table address

Upper Lower

FFFA

FFFB

FFF8

FFF9

FFF6

FFF7

FFF4

FFF5

FFE4

FFE5

When an interrupt is requested from each resource, the interrupt controller transfers the

interrupt level based o n the value set at the 2 bits of th e ILRX corresponding to the interrupt to

the CPU.

A relation between two bits of the ILRX and the interrupt level required is shown below.

Lx1 Lx0 Required interrupt level

0X 1

10 2

1 1 3 (None)

(2) Interrupt test register (ITR)

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

Address: 007F

H

——————* *

The ITR used for testing. Do not access it.

26

Page 37

■

Description

2.3 Interrupt Controller

The functions of interrupt controllers are described below.

• Interrupt functions

• The MB89990 series of microcontrollers have 4 inputs for interrupt requests from each

resource. The inte rrupt level can be set by 2-bit registers corresponding to eac h input.

When an interrupt c an be requested from a re source, the interrupt contr oller receives it

and transfers the contents of the corresponding level register to the CPU. The interrupt to

the device is processed as follows:

(a) An interrupt source is generated inside each resource.

(b) If an interrupt is enabled, an interrupt request is output from each resource to the

interrupt controller by referring to the interrupt-enable bit inside each resource.

(c) After receiving this interrupt request, the interrupt controller determines the priority of

simultaneously-requested interrupts and then transfers the interrupt level for the

applicable interrupt to the CPU.

(d) The CPU compares the interrupt level requested from the interrupt controller with the

IL bit in the processor status register.

(e) As a result of the comparison, if the priority of the interrupt level is higher than that of

the current interrupt processing level, the contents of the I-flag in the same processor

status register are checked.

(f) As a result of the check in step (e), if the I-flag is enabled for an interrupt, the

contents of the IL bit are set to the required level. As soon as the currently-executing

instruction is terminated, the CPU performs the interrupt processing and transfers

control to the interrupt-processing routine.

(g) When an interrupt source generated in step (a) is cleared by software in the userís

interrupt processing routine, the CPU terminates the interrupt processing.

Figure 2.3-1 "Interrup t-processing Flowchart" outlines the inte rrupt operation for the MB89990

series of microcontrollers.

Figure 2.3-1 Interrupt-processing Flowchart

Internal bus

Register file

IPLA IR

PS I IL

Check Comparator

(f)

(e)

(d)

MB89990

(c)

Resource

(g)

Enable FF

Source FF

(a)

AND

Resource

Level

comparator

(b)

Interrupt controller

27

Page 38

CHAPTER 2 HARDWARE CONFIGRATION

2.4 I/O Ports

• he MB89990 series of microcontrollers have three parallel ports and 22 pins. P00 to

P07 and P30 to P37 se rve as 8-bit I/O ports, P40 to P45 serve as 6-bit I/O ports.

• Port0 and Port3 are also used as the I/O pin for the resource.

■

List of port functions

Table 2.4-1 List of Port Functions

Pin

name

P00 to

P07

P30 to

P37

P30 to

P37

■

Register List

Input

type

Output

type

Function bit7 bit6 bit5 bit4 bit3 bit2 bit1 bit0

Parallel

port 00 to

07

External

CMOS

CMOS

push-

pull

interrupt 2

Parallel

CMOS

Cmos

port 30 to

37

push-

Hysteresis

pull

Timer,

External

interrupt 1

CMOS

N-ch

open-

drain

Parallel

port 40 to

45

I/O port consists of the following registers.

P07 P06 P05 P04 P03 P02 P01 P00

INT27

INT26 INT25 INT24 INT23 INT22 INT21 INT20

P37 P36 P35 P34 P3 P32 P31 P30

ROC INT12 INT11

TO/

INT10

EC———

— — P45 P44 P43 P42 P41 P40

28

Address: 0000

Address: 0001H

Address: 000CH

Address: 000DH

Address: 000EH

8 bit

H

PDR0

DDR0

PDR3

DDR3

PDR4

R/W Port 00 to 07 data register

W Port 00 to 07 data direction register

R/W Port 30 to 37 data register

W Port 30 to 37 data direction register

R/W Port 40 to 47 data register

Initial value = XXXXXXXXB

Initial value = 00000000B

Initial value = XXXXXXXXB

Initial value = 00000000B

Initial value = XX111111B

Page 39

■

Description of Functions

The function of each port is described below.

(1) P00 to P07: CMOS type I/O ports

P30 to P37: CMOS type I/O ports

• Switching input and output

• This port has a data-dir ection register (DDR ) and a port-data regi ster (PDR) for each bit.

• Operation for output port (DDR = 1)

• The value written at the PDR is output to t he pin when the DDR is set to 1. When the

2.4 I/O Ports

(also used as resource input and output)

(also used as resource input and output)

Input and output c an be set inde pendently fo r each bit . The pin wit h the DDR set to 1 is

set to output, and the pin with the DDR set to 0 i s set to i nput. W hen the re source out put

bit is enabled, these ports are set to output irrespective of the DDR setting conditions.

PDR is read, usually, the value of the pin is r ead instead of the contents of the output

latch. However, when the Read Modify Write instruct ion is execute d, the cont ents of the

output latch are read irrespective of the DDR setting conditions. Therefore, the bitprocessing instruc tion can be used even if input and output are mi xed with each other.

When data is writt en to t he PDR, the wr it ten data i s hel d i n t he outp ut l atc h irr es pecti ve of

the DDR setting conditions.

• Operation for input port (DDR = 0)

• When used as the input port, the output impedance goes High. Therefore, when the PDR

is read, the value of the pin is read.

• Resource output operation

• When using as the reso urce output, setting is performed by t he resource output enable

bit. (See the description of each resource.) Since the reso urce output enable bit has

priority in switch ing input and output, even if the D DR is set to 0, any bit is set as the

resource output when output is ena bled at each resource. Even if the output from each

resource is enable d, the read parallel port is effective, so the resource ou tput value can

be checked.

• Resource input operation

• The pin value at a p ort with the resource input fu nction is always input for the resource

input (irrespective of the settin g of the DDR and resource). Set the DDR to input when

using an external signal for the resource input.

• State when reset

• When reset, the DDR and the outp ut enable bit for each resource a re initialized t o 0 and

the output impedance goes High at all bits. When reset, the PDR is not defined.

Therefore, set the value of the PDR before setting the DDR to output.

• State when stop

• With the SPL bit of the standby-control register set to 1, in the stop mode, the output

impedance goes High irrespective of the value of the DDR.

29

Page 40

CHAPTER 2 HARDWARE CONFIGRATION

Figure 2.4-1 Ports 00 to 07 and 30 to 37

To external interrupt

To resource input

External interrupt enable

Stop mode SPL = 1

Stop mode SPL = 1

Internal data bus

Resource

output

Resource

output EN

PDR

PDR read

PDR read

(when Read Modify Write instruction executed)

Output latch

PDR write

DDR

DDR write

Stop mode SPL = 1

(2) P40 to P45: N-ch open-drain-type output ports

(also used as analog input)

Pull-up resistor (option)

Pch

Pch

Pin

Nch

30

• Operation for output port

• The value written at the PDR is outpu t to the pin. When the PDR i s read in this port, the

contents of the output latch is always read instead of the value of the pin.

• State when reset

• The PDR is initialized to 1 at reset, so the output register is turned off at all bits.

• State in stop mode

• When the SPL bit of the standb y-control registe r is set to 1, in the stop mode , the output

impedance goes High irrespective of the value of the PDR.

Page 41

Internal data bus

Figure 2.4-2 Ports 40 to 45

PDR

PDR read

PDR read

(when Read Modify Write instruction is executed )

Output latch

PDR write

Stop mode (SPL = 1)

Stop

Pull-up resistor

(option)

Pch

Pin

Nch

2.4 I/O Ports

31

Page 42

CHAPTER 2 HARDWARE CONFIGRATION

2.5 8/16-bit Timer (Timer 1 and Timer 2)

• Three internal clock pulses and one external clock pulse can be selected.

• Operation in 8-bit 2-ch mode or 16-bit 1-ch mode can be selected.

• A square-wave output function is included.

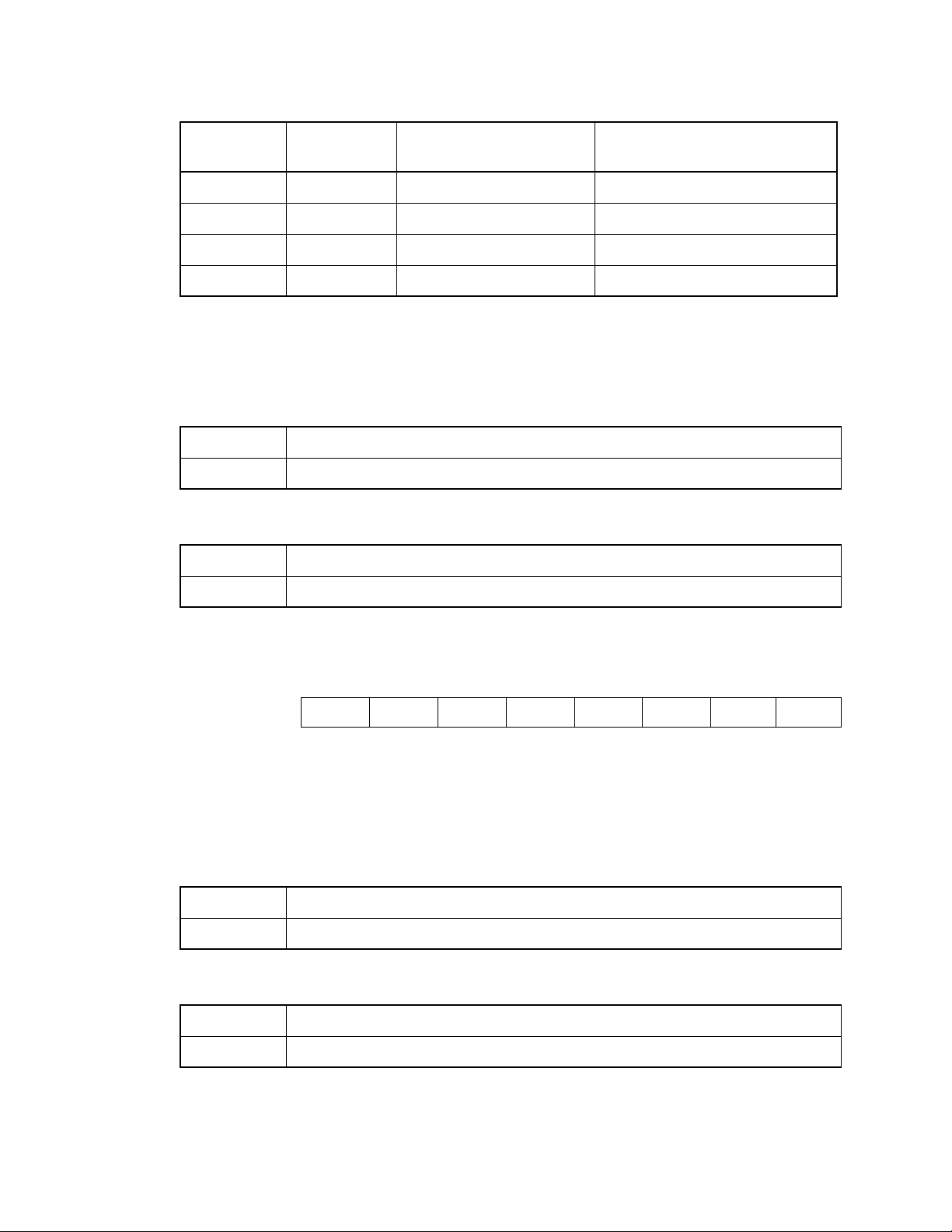

■

Block Diagram

Figure 2.5-1 8/16-bit Timer Block Diagram

Internal data bus

T1STR T1STP T1CS0 T1CS1 T1OS0 T1OS1 T1IE T1IF

CLR

1/64

1/1024

Prescaler

CPU clock

P33/EC

CPU clock

Prescaler

1/64

1/1024

CLR

Square-wave

output initialization

pin control

R.S

1/4

MPX

1/4

MPX

CK

8-bit counter

CLR

Comparator

LOAD

Compare data latch

Data register

Data register

LOAD

Compare data latch

Comparator

CLR

8-bit counter

CK

CO

EQ

EQ

Q

TFF

IRQ3

P34/TO

/INT00

IRQ4

■

Register List

32

T2STR T2STP T2CS0 T2CS1 — — T2IE T2IF

8 bit

Address: 0018H

Address: 0019H

Address: 001AH

Address: 001BH

T2CR

T1CR

T2DR

T1DR

R/W Timer-2 control register

R/W Timer-1 control register

R/W Timer-2 data register

R/W Timer-1 data register

Page 43

■

Description of Register Details

The detail of each register is described below.

(1) Timer 1 control register (T1CR)

2.5 8/16-bit Timer (Timer 1 and Timer 2)

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

Address: 0019

T1IF T1IE T1OS1 T1OS0 T1CS1 T1CS0 T1STP T1STR

H

(R/W) (R/W) (R/W) (R/W) (R/W) (R/W) (R/W) (R/W)

Intilial value

X00000X0

B

[Bit 7] T1IF: Interrupt request flag

(When write)

0 Interrupt request flag clearing

1 No operation

(When read)

0 No interrupt request

1 Interval interrupt request

1 is always read when the Read Modify Write instruction is executed.

[Bit 6] T1IE: Interrupt-enable bit

0 Interrupt disabled

1 Interrupt enabled

[Bit 5 and 4] T1OS1, T1OS0: Square-wave output control bit

T1OS1 T1OS0

0 0 Makes square-wave output port (P43) general-purpose port

0 1 Holds data setting square-wave output to Low level

1 0 Holds data setting square-wave output to High level

1 1 Sets square-wave output to held value

When the T1STR bit is 0, the square-wave output is set to the set value.

33

Page 44

CHAPTER 2 HARDWARE CONFIGRATION

[Bit 3 and 2] T1CS1, T1CS0: Clock source select bit

T1CS1 T1CS0

00 2.0 [

0 1 32.0 [µs]

1 0 512 [µs]

Clock cycle time

selected at 4 MHz

µ

s]

Clock cycle time

×

2 instruction cycle

×

32 instruction cycle

×

512 instruction cycle

1 1 External clock

Note:

When using Timer 1 in the 8- bit mode, the clock source sel ect io n bit s (T 1CS1 and T1CS0) of

the Timer 2 control register (T2CR) must be set to other than the 16-bit mode.

[Bit 1] T1STP: Timer-stop bit

0 Counting continued without clearing counter

1 Counting suspended

[Bit 0] T1STR: Timer-start bit)

0 Terminates operation

1 Clears counter and starts operation

(2) Timer 2 control register (T2CR)

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

Address: 0018

T21F T21E — — T2CS1 T2CS0 T2STP T2STR

H

(R/W) (R/W) (R/W) (R/W) (R/W) (R/W) (R/W) (R/W)

[Bit 7] T2IF: Interrupt request flag bit

(When write)

0 Interrupt request flag cleari ng

1 No operation

(When read)

0 No interrupt request

Intilial value

X00000X0

B

34

1 Interval interrupt request

1 is always read when the Read Modify Write instruction is executed.

Page 45

[Bit 6] T2IE: Interrupt-enable bit

0 Interrupt disabled

1 Interrupt enabled

[Bit 3 and 2]: T2CS1, T2CS0: Clock source select bit

2.5 8/16-bit Timer (Timer 1 and Timer 2)

T2CS1 T2CS0

00 2.0 [

Clock cycle time

selected at 4 MHz

µ

s]

0 1 32.0 [µs]

1 0 512 [µs]

1 1 16 bit mode

[Bit 1] T2STP: Timer stop bit

0 Operation continued without clearing counter

1 Count operation suspended

[Bit 0] T2STR: Timer start bit

0 Operation stopped

1 Operation started after clearing counter

(3) Timer 1 and 2 data registers (T1DR and T2DR)

Clock cycle time

×

2 instruction cycle

×

32 instruction cycle

×

512 instruction cycle

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

Address: 001B

Address: 001A

H

H

(R/W) (R/W) (R/W) (R/W) (R/W) (R/W) (R/W) (R/W)

Intilial value

XXXXXXXX

B

Write data is the set interval times and read data is the counted times.

35

Page 46

CHAPTER 2 HARDWARE CONFIGRATION

■

Description of Operation

(1) 8-bit internal clock mode

In the 8-bit internal clock mode, thr ee internal clock inputs can be selected by setti ng the clock

source select bits (T 1CS1 and T1 CS0, T2CS1 and T2CS0) of the ti mer control registers (T1CR

and T2CR). The timer data registers (T1DR and T2DR) serve as interval time setting registers.

To start the timer, set the inte rval time as the timer data registers, write 1 at the timer start bits

(T1STR and T2STR) of the timer control registers to clear the counter to 00

values of the timer data registers into the compare latch. Then, counting starts.

When the values of the counter agree wi th thos e of the time r data re gis ters , the in ter val in ter r upt

request flags (T1IF and T2IF) are set to 1. At this time, the counter is cleared to 00

of the timer data re giste rs a re r el oad ed into th e com par e lat ch , an d c ou nti ng is c ontinue d. If the

interrupt enable bits (T1IE and T2IE) are set to 1, an interrupt request is output to the CPU.

Assuming the se t value of the timer data register is n a nd the selected clock is φ, the interval

time (T) can be calculated as follows.

T = φ × (n + 1) [µs]

Figure 2.5-2 Description Diagram for Internal Clock Mode Operation

Matched Matched Matched

Counter clear

Set data value

, and load the

H

, the values

H

Compare latch

Count value

0000H

T1STR

T1IF

TO

T1IF = 0 (W) T1IF = 0 (W) T1IF = 0 (W)

Figure 2.5-3 Flow Diagram for Timer Setting

Operation mode specification

Interval time setting

T1STR = 1, T1IF = 0, T1IE = 1

Timer start

Main program

T1IF = 1

Interrupt processing

T1IF = 0 (W)

36

Page 47

2.5 8/16-bit Timer (Timer 1 and Timer 2)

(2) Initializing square-wave output

The square-wave output can be set to any value only when the timer stops (T1STR = 0 and

T2STR = 0).

To set, proceed as follows:

(a) Write the set values (01 and 10) at the initialize bits (T1OS1 and T1OS0, T2OS1 and

T2OS2, respectively) of the square wave output.

(b) Write 11 at the same bits. This initializes the square wave output to the set value. If

the T1STR bit is set to 0, the square wave output of the pin is set to the set value

during this write cycle.

Figure 2.5-4 Initialization of Equivalent Circuit

T1STR, T2STR

Level latch

D5

Q

D

QX

D

Q

QX

SET

(3) 8-bit external clock mode

In the 8-bit external clock mod e, the external clock input can be selected by setting the clock

source select bits (T1CS1 and T1CS0) of the timer 1 control register (T1CR).

To start the timer, write 1 at the ti mer start bit (T1S TR) of the T1 CR to clear the co unter. Then,

counting starts.

When the value of the cou nter agrees with that of the timer data regist er setting, the interval

interrupt request fla g bit (T1IF) is set to 1. At this time, i f an interrup t is enabled ( T1IE = 1), an

interrupt request is output to the CPU.

ECK

Counter clear

TSTR = 1

Count value

T1IF

T1DR

D4

Write

D

Q

QX

Q

D

QX

RST

Figure 2.5-5 External Cock Mode Operation Description Diagram

Undefined 00 00H 01H 02H 00H 01H

FEH FFH

FFHFFH

T1IF = 0 (W)

37

Page 48

CHAPTER 2 HARDWARE CONFIGRATION

(4) Precautions for use of timer stop bit

Since an input c lock pu ls e is fi xed to Hig h l ev el wh en the ti mer i s s topp ed by th e tim er s tar t bit s,

the count value differs depending on the state of the input clock pulse.

When writing 00 at the timer stop and timer start bits simultaneously after stopping the timer

with the timer stop bit, the count ma y be incr emented by 1. Theref ore, if the tim er is stop ped by

the timer stop bit, rea d the counter and then write 00 at the timer start bits (See Figure 2.5-6

"Operation Diagram when Timer Stop Bit is Used".).

Figure 2.5-6 Operation Diagram when Timer Stop Bit is Used

When input clock is High When input clock is Low

CK

CK'

TSTP

TSTR

TSTR'

Count value

(5) 16-bit mode

In the 16-bit mode, each bit of the timer control registers is as shown below.

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

Address: 0019

Address: 0018

T1IF T1IE T1OS1 T1OS0 T1CS1 T1CS0 T1STP T1STR

H

T2IF T2IF — — TECS1 TECS0 T2STP T2STR

H

No operation Set to 00 Set to 11 No operation

In the 16-bit mode, write 11 a t the T 2CS 1 a nd T2 CS0 bi ts of th e T 2CR and set 00 at the T2OS1

and T2OS0 bits.

When in the 16-b it mode, the ti mer is controll ed by the T1C R. The timer d ata registers T2DR

and T1DR use the upper and lower bytes, respectively.

The clock source is selec ted by the T1CS1 and T1CS0 bits of the T1CR. To start the ti mer,

write 1 at the T1STR bit of the T1CR to clear the counter.

If the value of th e counter a grees with that of th e timer data register , the T1IF b it is set to 1. At

this time, an interrupt request is output to the CPU if the T1IE bit is 1.

Note:

38

To read the valu e of the counter in the 16-bi t mode, always read the value twice to check

that it is valid, and then use the data.

See the 8-bit operation diagram for 16-bit mode operation.

Page 49

2.6 External Interrupt 1

2.6 External Interrupt 1

• The edges of three external-interrupt sources (INT10 to INT12) can be detected to

set the corresponding flag.

• An interrupt can be generated at the same time the flag is set.

• The three interrupts can release the STOP or SLEEP mode.

■

Block diagram

P35/INT11

MUX MUX

P34/TO/

INT 10

■

Registers

EIR1 SL11 SL10 EIE1 EIR0 SL01 SL00 EIE0 EIC1

IRQ0

IRQ1

P36/INT12

MUX

EIR2 SL21 SL20 EIE2 EIC2

IRQ2

Address: 0023H

Address: 0024H

8 bit

EIC1

EIC2

R/W External-interrupt control register 1

R/W External-interrupt control register 2

39

Page 50

CHAPTER 2 HARDWARE CONFIGRATION

■

Description of Registers

(1) External-interrupt control register 1 (EIC1)

The EIC1 controls interrupts by the INT10 and INT11 pins.

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

Address: 0023

EIR1 SL11 SL10 EIE1 EIR0 SL01 SL00 EIE0

H

(R/W) (R/W) (R/W) (R/W) (R/W) (R/W) (R/W) (R/W)

Intilial value

00000000

B

[Bit 7] EIR1: External-interrupt request flag

When the edge specified by the SL11 and SL10 bits is inp ut to the INT11 pin, bit 7 is set to 1.

When the EIE1 bit is 1, an interrupt request (IRQ1) is output if this bit is set.

The meaning of each bit to be read is as follows:

0 Specified edge not input to INT11 pin

1 Specified edge input to INT11 pin (IRQ1 is output.)

1 is always read when the Read Modify Write instruction is read.

The meaning of each bit to be written is as follows:

0 This bit is cleared.

1 This bit does not change nor affect other bits.

[Bit 6 and 5] SL11, SL10: Edge-polarity select bit

This bit is used to control the input edge polarity of the INT11 pin.

SL11 SL10

0 0 No edge detection

0 1 Rising edge

1 0 Falling edge

1 1 Both-edge mode

[Bit 4] EIE1: Interrupt-enable bit

This bit is used to enable an external-interrupt request by the INT11 pin.

0 Interrupt request disab led

1 Interrupt request enabled by EIR1 setting

40

Page 51

2.6 External Interrupt 1

[Bit 3] EIR0: External-interrupt request flag

When the edge specified by the SL01 and SL00 bits is inp ut to the INT10 pin, bit 3 is set to 1.

When the EIE0 is 1, an interrupt request (IRQ0) is output if this bit is set.

The meaning of each bit to be read is as follows:

0 Specified edge not input to INT10 pin

1 Specified edge input to INT10 pin (IRQ0 is output.)

1 is always read when the Read Modify Write instruction is read.

The meaning of each bit to be written is as follows:

0 This bit is cleared.

1 This bit does not change nor affect other bits.

[Bit 2 and 1] SL01, SL00: Edge-polarity select bit

This bit is used to control the input edge polarity of the INT10 pin.

SL01 SL00

0 0 No edge detection

0 1 Rising edge

1 0 Falling edge

1 1 Both-edge mode

[Bit 0] EIE0: Interrupt-enable bit

Bit 0 is used to enable an external-interrupt request by the INT10 pin.

0 Interrupt request disabled

1 Interrupt request enabled by EIR0 setting

(2) External-interrupt control register 2 (EIC2)

The EIC2 controls an interrupt by the INT12 pins.

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

Address: 0024

H

————EIR2SL21SL20EIE2

(R/W) (R/W) (R/W) (R/W)

Intilial value

----

0000

B

41

Page 52

CHAPTER 2 HARDWARE CONFIGRATION

[Bit 3] EIR2: External-interrupt request flag

When the edge specified by the SL21 and SL20 bit is input to the INT12 pin, bit 3 is set to 1.

When the EIE2 bit is 1, an interrupt request (IRQ2) is output if this bit is set.

The meaning of each bit to be read is as follows:

0 Specified edge not input to INT12 pin

1 Specified edge input to INT12 pin (IRQ2 is output.)

1 is always read when the Read Modify Write instruction is read.

The meaning of each bit to be written is as follows:

0 This bit is cleared.

1 This bit does not change nor affect other bits.

[Bit 2 and 1] SL21, SL20: Edge-polarity select bit

This bit is used to control the input edge polarity of the INT12 pin.

SL21 SL20

0 0 No edge detection

0 1 Rising edge

1 0 Falling edge

1 1 Both-edge mode

[Bit 0] EIE2: Interrupt-enable bit

This bit is used to enable an external-interrupt request by the INT12 pin.

0 Interrupt request disab led

1 Interrupt request enable d by setting of EIR2

■

Precautions for External-interrupt Circuit

• When enabling an interrupt after clearing reset, always clear the interrupt flag

simultaneously. A n interrupt request is output imme diately when the interrupt flag s (EIR2,

EIR1, EIR0) are set to 1.

• When no edge detection is specifie d by the edge-polari ty select b it, the cu rrent input is held

before the internal edge dete ction block. If an edge is speci fied in this state, edge detection

may be erroneous . Therefore, always clear the flag after an edge is specified.

42

Page 53

2.7 External Interrupt 2 (Wake Up)

• Eight external interrupt input pins

• An interrupt request is output by Low-level input signals.

• Also usable as wake-up input

■

Block Diagram

2.7 External Interrupt 2 (Wake Up)

P00/INT20

P01/INT21

P02/INT22

P03/INT23

P04/INT24

P05/INT25

P06/INT26

EIE2

765

43210

EIF2

IF20

Interrupt

IRQA

■

Register List

P07/INT27

This external interrupt 2 consists of external interrupt 2 control register (EIE2) and external

interrupt 2 flag register (EIF2).

8 bit

Address: 0032H

Address: 0033H

EIE2

EIF2

R/W External-interrupt control register 2

R/W External-interrupt flag register 2

43

Page 54

CHAPTER 2 HARDWARE CONFIGRATION

■

Description of Registers

The detail of each register is described below.

(1) External interrupt 2 control register (EIE2)

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

Address: 0032

H

IE27 IE26 IE25 IE24 IE23 IE22 IE21 IE20

(R/W) (R/W) (R/W) (R/W) (R/W) (R/W) (R/W) (R/W)

Intilial value

00000000

B

[Bit 7 to 0] IE27 to IE20: Operation-enable bit

These bits are used to operation-enable external interrupt of INT27

0 External interrupt operation-disabled

1 External interrupt operation-enabled

(2) External interrupt 2 control register (EIF2)

Bit 7Bit 6Bit 5Bit 4Bit 3Bit 2Bit 1Bit 0

Address: 0033

———————IF20

H

Intilial value

-------

0

B

to INT20.

(R/W)

[Bit 0] IF20: Low-level detect flag bit

This bit is used to detect LOW level of INT27

to INT20.

(When write)

0 Clears flag for detecting LOW level

1 No operation

(When read)

0 No LOW level input

1 LOW level input detected

If any of the interrupt en able b its (IE 27 to IE 20) of the exter nal inter rupt 2 c ontrol r egis ter (E IE2)

is 1, the Low-level de tect flag b it (IF20) i s set to 1 and an interrup t request is output to the CPU

when a Low level is input to the port corresponding to this bit.

Note:

Unlike other resources , even if the external interrupt 2 circuit is disabled for an inter rupt, it

keeps generating interr upts until the in terrupt source is cleared. Therefor e, always clear the

interrupt source (after disabling an interrupt).

44

Page 55

2.8 Remote-control Carrier Frequency Generator

2.8 Remote-control Carrier Frequency Generator

• This generator is a remote-control circuit for generating remote-control carrier

frequencies.

• The 6-bit binary counter is built in.

• Four internal clock pulses can be selected to set a duty (H width) and cycle.

■

Block Diagram

Internal data bus

RCK0 Compare register for dutyRCOERCK1

2/1

1/1

CPU clock Comparator

Internal data bus

■

Register List

0

1/32

1/128

CLEAR

CLK

6-bit counter

Compare register for cycle

8 bit

P30/BZ/RCO

CPU clock: Halved from source clock

Address: 0014

Address: 0015H

H

RCR1

RCR2

R/W Remote-control register 1

R/W Remote-control register 2

45

Page 56

CHAPTER 2 HARDWARE CONFIGRATION

■

Description of Registers

(1) Remote-control register 1 (RCR1)

This register is used to select the reference clock and set the duty of remote-control carrier

frequency.

Bit 7Bit 6Bit 5Bit 4Bit 3Bit 2Bit 1Bit 0

Address: 0014

RCK1 RCK0 HSC5 HSC4 HSC3 HSC2 HSC1 HSC0

H

(R/W) (R/W) (R/W) (R/W) (R/W) (R/W) (R/W) (R/W)

Intilial value

00000000

B