FUJITSU SEMICONDUCTOR

DATA SHEET

DS05-50202-2E

Stacked MCP (Multi-Chip Package) FLASH MEMORY & SRAM

CMOS

16M ( × 8/ × 16) FLASH MEMORY &

4M ( × 8/ × 16) STATIC RAM

MB84VD2118XA

FEATURES

■■■■

•

Power supply voltage of 2.7 to 3.6 V

•

High performance

85 ns maximum access time

•

Operating Temperature

−25 to +85 °C

• Package 69-ball FBGA, 56-pin TSOP(I)

PRODUCT LINE UP

■■■■

Ordering Part No. V

Max. Address Access Time (ns) 85 85

Max. CE

Max. OE

Access Time (ns) 85 85

Access Time (ns) 35 45

CCf, VCCs = 3.0 V MB84VD2118XA-85/MB84VD2119XA-85

+

−

0.6 V

0.3 V

-85

MB84VD2119XA

/

Flash Memory SRAM

-85

(Continued)

PACKAGES

■■■■

69-ball plastic FBGA 56-pin plastic TSOP(I)

(BGA-69P-M02) (FPT-56P-M04)

MB84VD2118XA

/MB84VD2119XA

-85

-85

(Continued)

1. FLASH MEMOR Y

•

Simultaneous Read/Write operations (dual bank)

Miltiple devices available with different bank sizes (Refer to “PIN DESCRIPTION”)

Host system can program or erase in one bank, then immediately and simultaneously read from the other bank

Zero latency between read and write operations

Read-while-erase

Read-while-program

•

Minimum 100,000 write/erase cycles

•

Sector erase architecture

Eight 4 K words and thirty one 32 K words.

Any combination of sectors can be concurrently erased. Also supports full chip erase.

•

Boot Code Sector Architecture

MB84VD2118XA : Top sector

MB84VD2119XA : Bottom sector

•

Embedded Erase

Automatically pre-programs and erases the chip or any sector

•

Embedded Program

Automatically writes and verifies data at specified address

•

Data Polling and Toggle Bit feature for detection of program or erase cycle completion

•

Ready-Busy output (RY/BY

Hardware method for detection of program or erase cycle completion

•

Automatic sleep mode

When addresses remain stable, automatically switch themselves to low power mode.

•

•

•

•

•

CC

Low V

Hidden ROM (Hi-ROM) region

64K byte of Hi-ROM, accessible through a new “Hi-ROM Enable” command sequence

Factory serialized and protected to provide a secure electronic serial number (ESN)

WP

At V

(MB84VD2118XA : SA37, SA38 MB84VD2119XA : SA0, SA1)

At VIH, allows removal of boot sector protection

At V

Erase Suspend/Resume

Suspends the erase operation to allow a read in another sector within the same device

Please refer to “MBM29DL16XTD/BD” data sheet in detailed function

f write inhibit

/ACC input pin

IL, allows protection of boot sectors, regardless of sector protection/unprotection status

ACC, program time will reduse by 40%.

TM

* Algorithms

TM

* Algorithms

≤

2.5 V

)

2. SRAM

•

Power dissipation

Operating : 40 mA max.

Standby : 7 µA max.

•

Power down features using CE1

•

Data retention supply voltage : 1.5 V to 3.6 V

•

CE1s

and CE2s Chip Select

• Byte data control : LBs (DQ

* :

Embedded Erase

2

TM

and Embedded ProgramTM are trademarks of Advanced Micro Devices, Inc.

s and CE2s

0 to DQ7

) , UBs (DQ8 to DQ15)

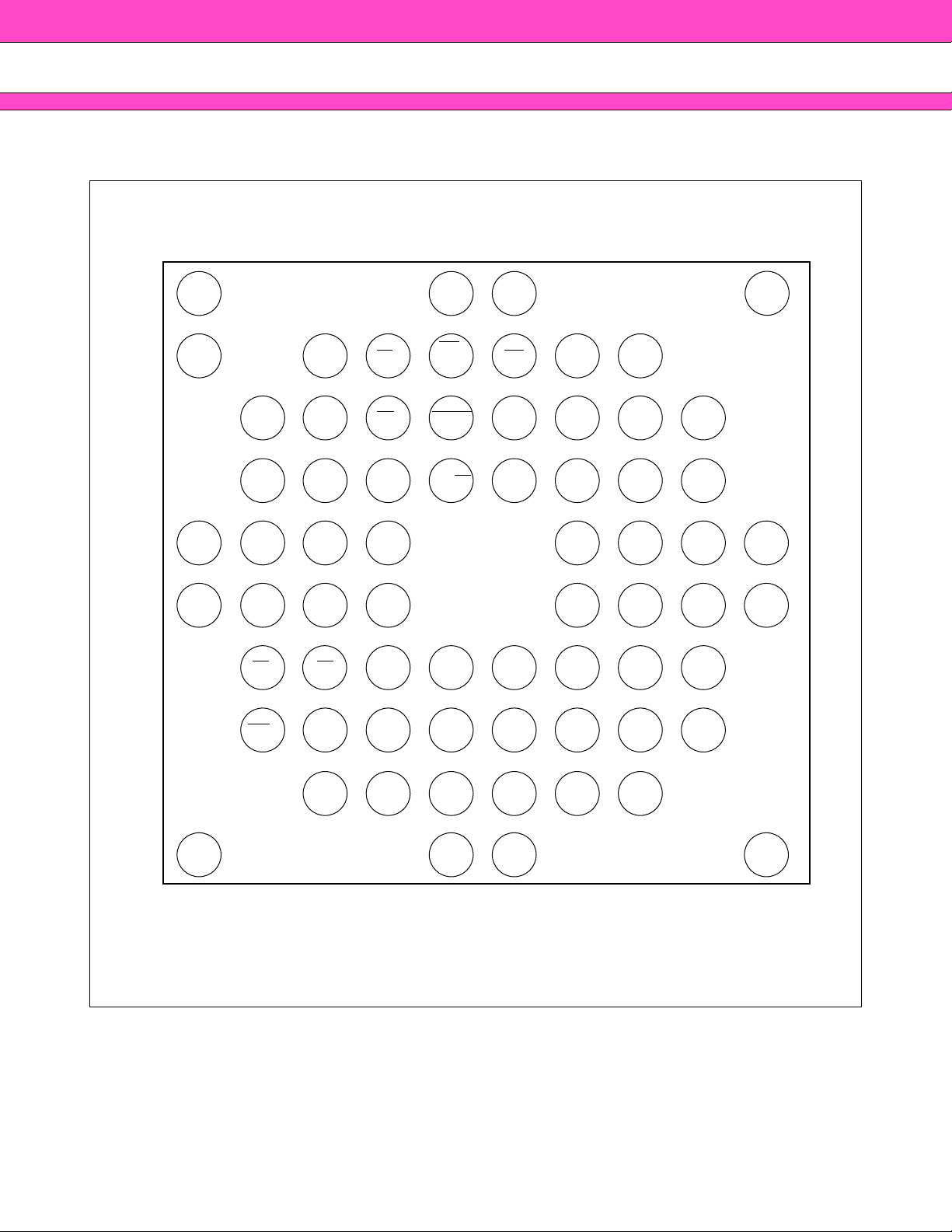

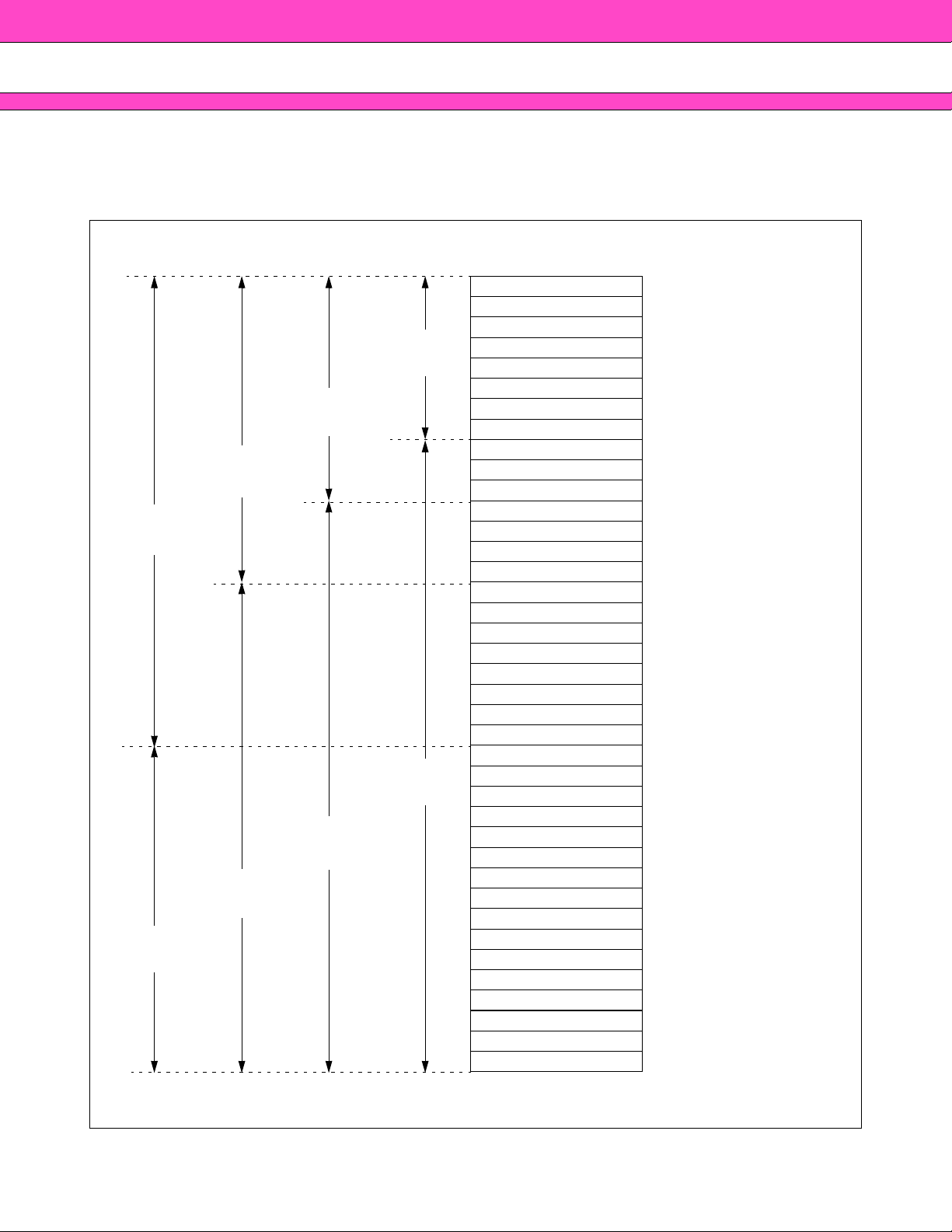

PIN ASSIGNMENTS

■■■■

MB84VD2118XA-85/MB84VD2119XA-

(Top View)

85

N.C.

A

B

N.C. A

C

D

E

N.C.

F

N.C.

G

H

A3

A2

A1

A0

CEf OE

S

CE1

7

A6

A5

A4

VSS

DQ

0 DQ10

N.C.

LBS

UBS RESET

A18

A17

DQ1

WP/

ACC

RY/BY

VCCfVCCs

N.C.

WE A

CE2S

N.C.

8

A19

A9

A10

DQ6

DQ13DQ4DQ3DQ9

DQ12

11

A

A12

A13

A14

SA A16

DQ15/

A−1

DQ

7

N.C.

A15

N.C.

N.C. N.C.

N.C.

CIOf

VSS

J

N.C. N.C.

K

1234567 9108

DQ8 DQ2

DQ

11

N.C. N.C.

DQ

14DQ5CIOS

69-ball FBGA

3

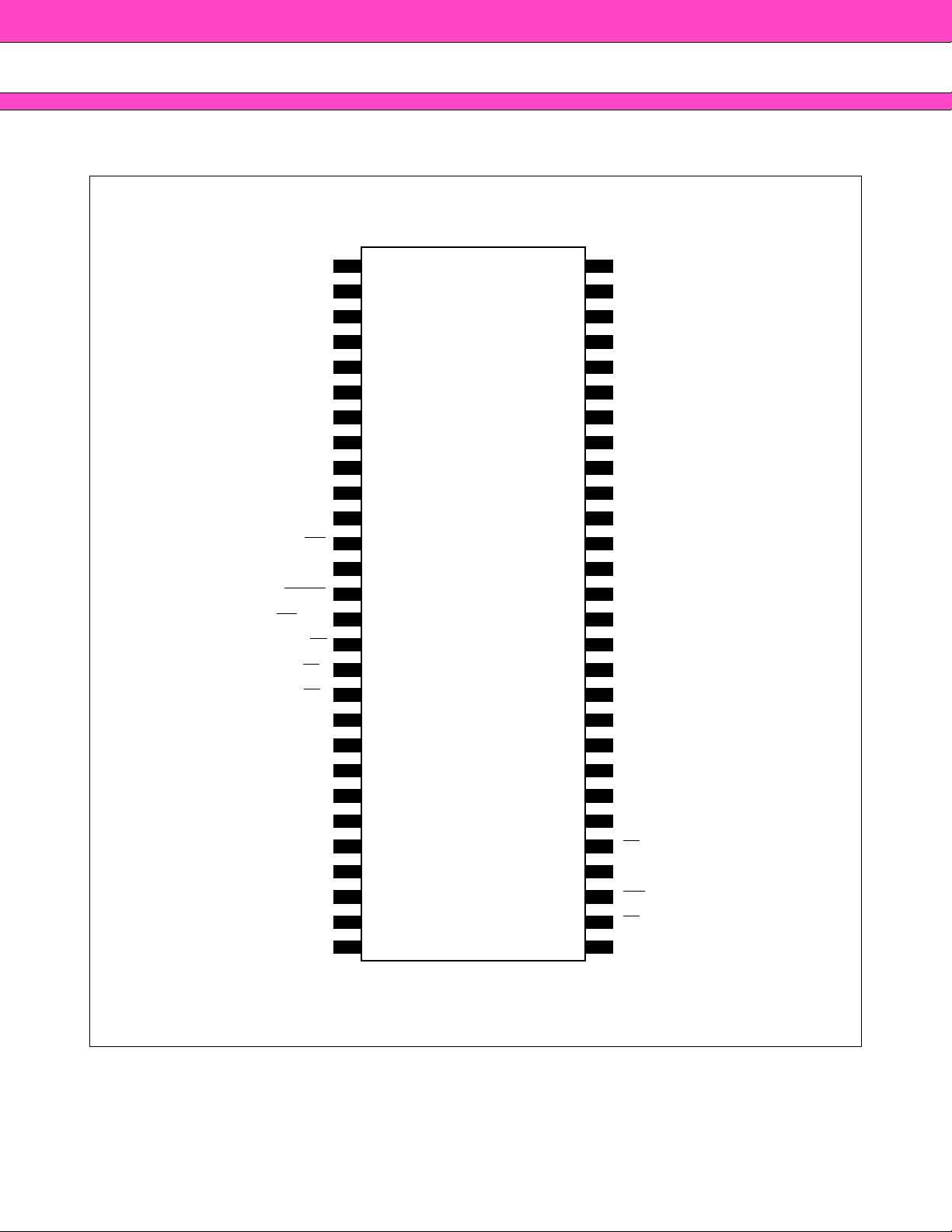

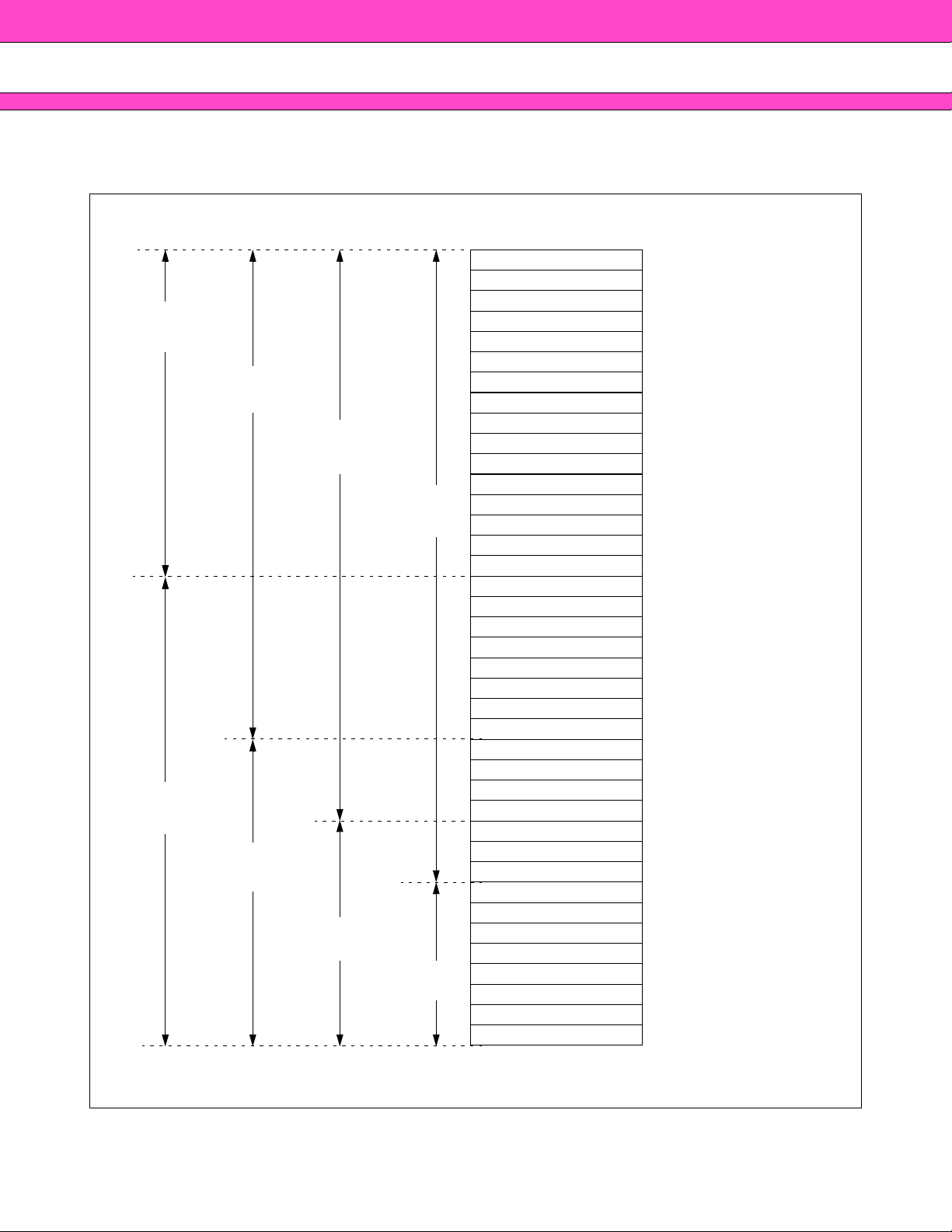

MB84VD2118XA

/MB84VD2119XA

-85

(Top View)

-85

N.C.

A15

A14

A13

A12

A11

A10

A9

A8

A19

N.C.

WE

CE2s

RESET

WP/ACC

RY/BY

UBs

LBs

A

A17

A7

A6

A5

A4

A3

A2

A1

N.C.

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

18

19

20

21

22

23

24

25

26

27

28

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

16

A

CIOf

V

SS

SA

DQ15/A-1

DQ7

DQ14

DQ6

DQ13

DQ5

DQ12

DQ4

CIOs

V

CCs

VCCf

DQ

11

DQ3

DQ10

DQ2

DQ9

DQ1

DQ8

DQ0

OE

V

SS

CE1s

CEf

A

0

56-pin TSOP(I)

4

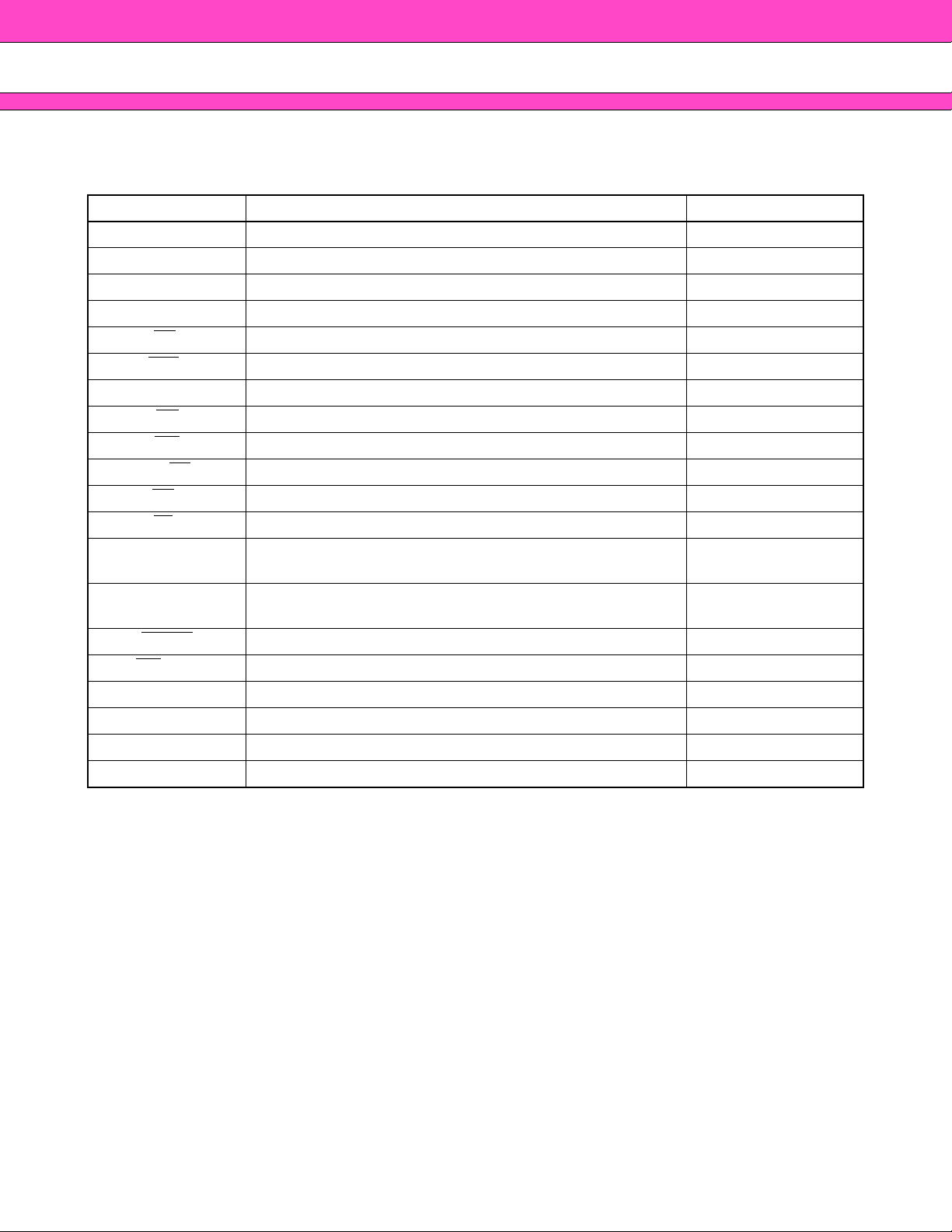

PIN DESCRIPTION

■■■■

Pin Function Input/Output

A

0 to A17 Address Inputs (Common) I

A

-1, A18, A19 Address Input (Flash) I

SA Address Input (SRAM) I

DQ

0 to DQ15 Data Inputs/Outputs (Common) I/O

CE

f Chip Enable (Flash) I

CE1s Chip Enable (SRAM) I

CE2s Chip Enable (SRAM) I

MB84VD2118XA-85/MB84VD2119XA-

85

OE

Output Enable (Common) I

WE Write Enable (Common) I

RY/BY

UB

s Upper Byte Control (SRAM) I

Ready/Busy Outputs (Flash) Open Drain Output O

LBs Lower Byte Control (SRAM) I

CIOf

CIOs

I/O Configuration (Flash)

CIOf = V

IH is Word mode ( × 16), CIOf = VIL is Byte mode ( × 8)

I/O Configuration (SRAM)

CIOs = V

IH is Word mode ( × 16), CIOs = VIL is Byte mode ( × 8)

RESET Hardware Reset Pin/Sector Protection Unlock (Flash) I

WP

/ACC Write Protect / Acceleration (Flash) I

N.C. No Internal Connection

V

SS Device Ground (Common) Power

VCCf Device Power Supply (Flash) Power

V

CCs Device Power Supply (SRAM) Power

I

I

5

MB84VD2118XA

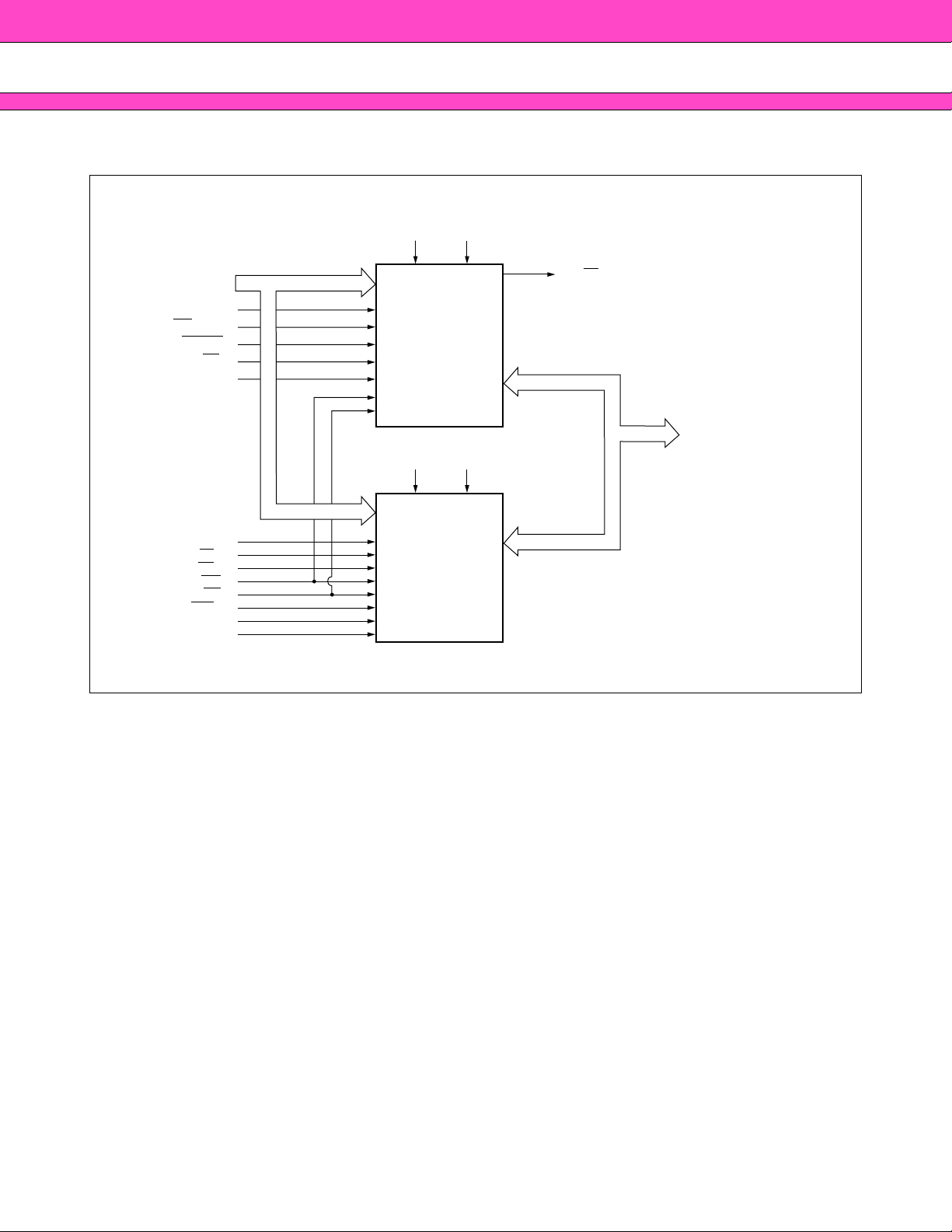

BLOCK DIAGRAM

■■■■

/MB84VD2119XA

-85

VCCfVSS

-85

A0 to A19

A-1

WP/ACC

RESET

CEf

CIOf

SA

LBs

UBs

WE

OE

CE1s

CE2s

CIOs

A0 to A19

A0 to A17

16 M bit

Flash Memory

VCCsVSS

4 M bit

Static RAM

RY/BY

DQ

0 to DQ15/A-1

DQ0 to DQ15/A-1

DQ0 to DQ15/A-1

6

MB84VD2118XA-85/MB84VD2119XA-

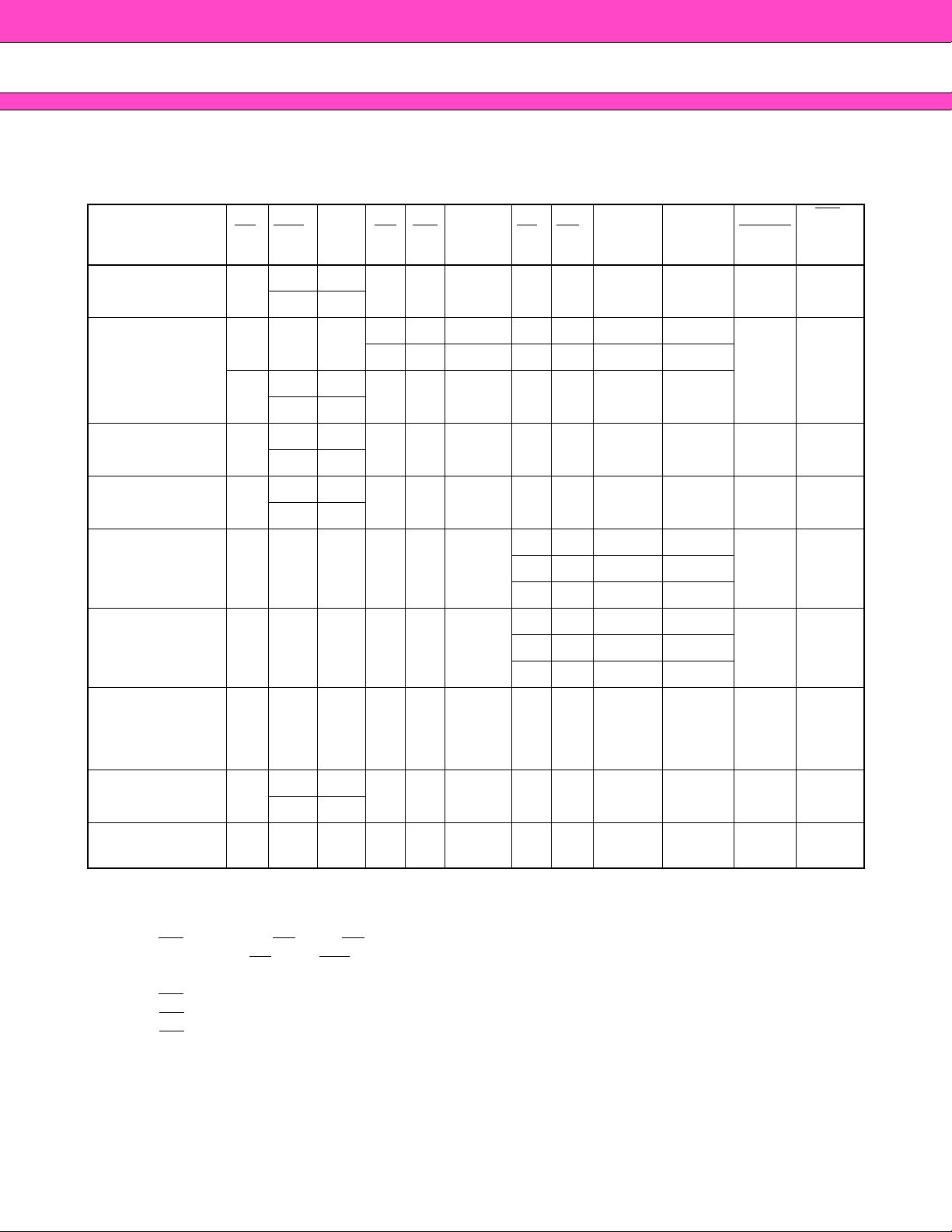

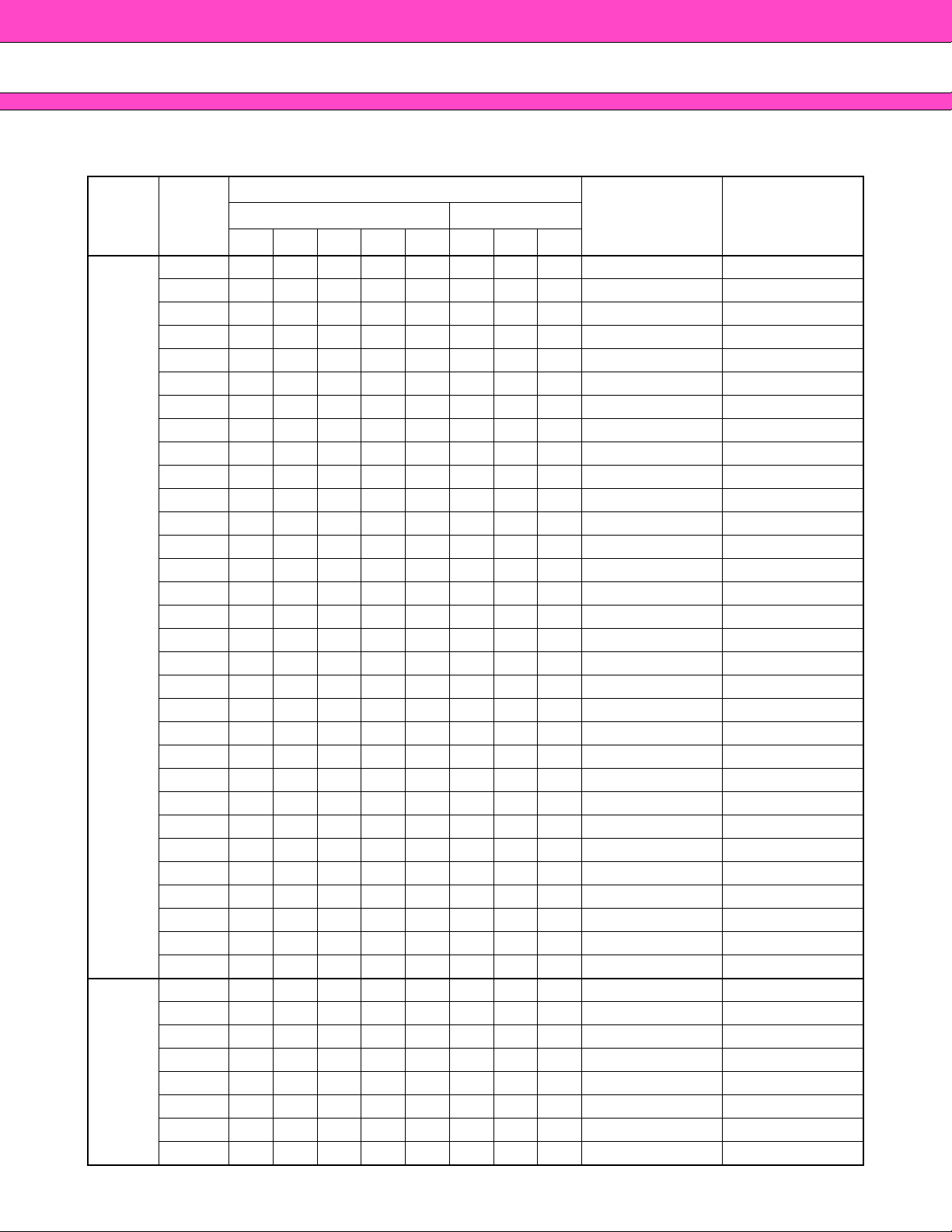

DEVICE BUS OPERATIONS

■■■■

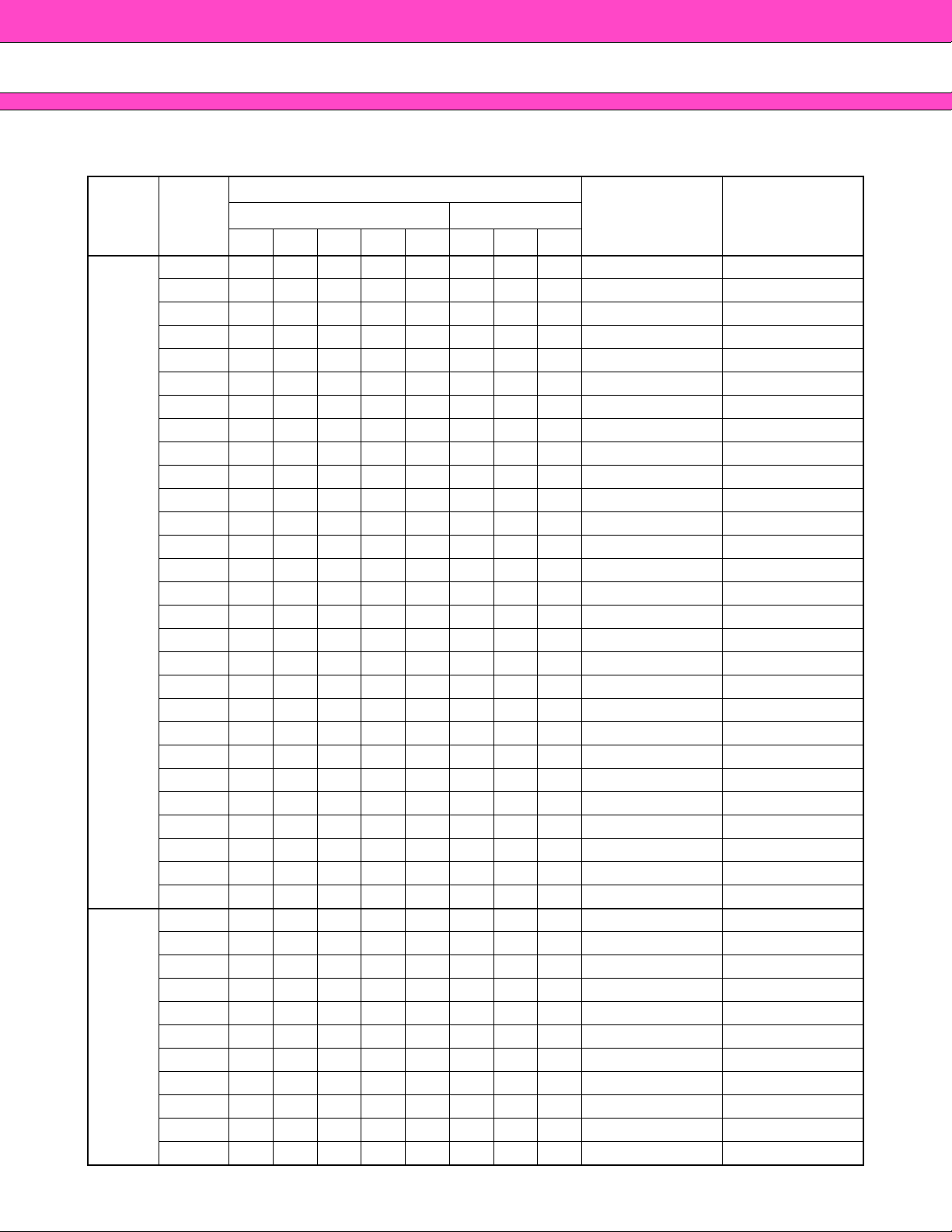

Table 2.1 User Bus Operations (Flash = Word mode; CIOf = VCCf, SRAM = Word mode; CIOs = VCCs)

85

Operation

(Note 1, 3)

fCE1sCE2s OE WE

CE

SA

(Note 6)

HX

Full Standby H

X X X X X HIGH-Z HIGH-Z H X

XL

H H X X X HIGH-Z HIGH-Z

HLH

X X X H H HIGH-Z HIGH-Z

Output Disable

HX

L

H H X X X HIGH-Z HIGH-Z

XL

Read from Flash

(Note 2)

L

HX

LH X XX D

XL

HX

Write to Flash L

HL X XX D

XL

Read from SRAM H L H L H X

Write to SRAM H L H X L X

0

DQ

to

sUBs

LB

DQ

LL D

OUT DOUT HX

OUT DOUT

DQ8 to

7

DQ

IN DIN HX

LH DOUT HIGH-Z

LL D

IN DIN

15

WP/

RESET

ACC

(Note 5)

HX

HXHLHIGH-ZDOUT

HXHLHIGH-ZDIN

LH DIN HIGH-Z

Temporary Sector

Group

Unprotection

XXXXXXXXX X V

(Note 4)

Flash Hardware

Reset

Boot Block Sector

Write Protection

Legend: L = V

IL, H = VIH, X = VIL or VIH. See “ELECTRICAL CHARACTERISTICS 1. DC Characteristics” for

HX

X

X X X X X HIGH-Z HIGH-Z L X

XL

XXXXXXXXX X X L

voltage levels.

Notes : 1. Other operations except for indicated this column are inhibited.

2. WE

can be VIL if OE is VIL, OE at VIH initiates the write operations.

3. Do not apply CE

f = VIL, CE1s = VIL and CE2s = VIH at a time.

4. It is also used for the extended sector group protections.

5. WP

/ACC = VIL ; protection of boot sectors.

WP/ACC = VIH ; removal of boot sectors protection.

WP/ACC = VACC (9V) ; Program time will reduce by 40%.

6. SA ; Don’t care or Open.

ID X

7

MB84VD2118XA

/MB84VD2119XA

-85

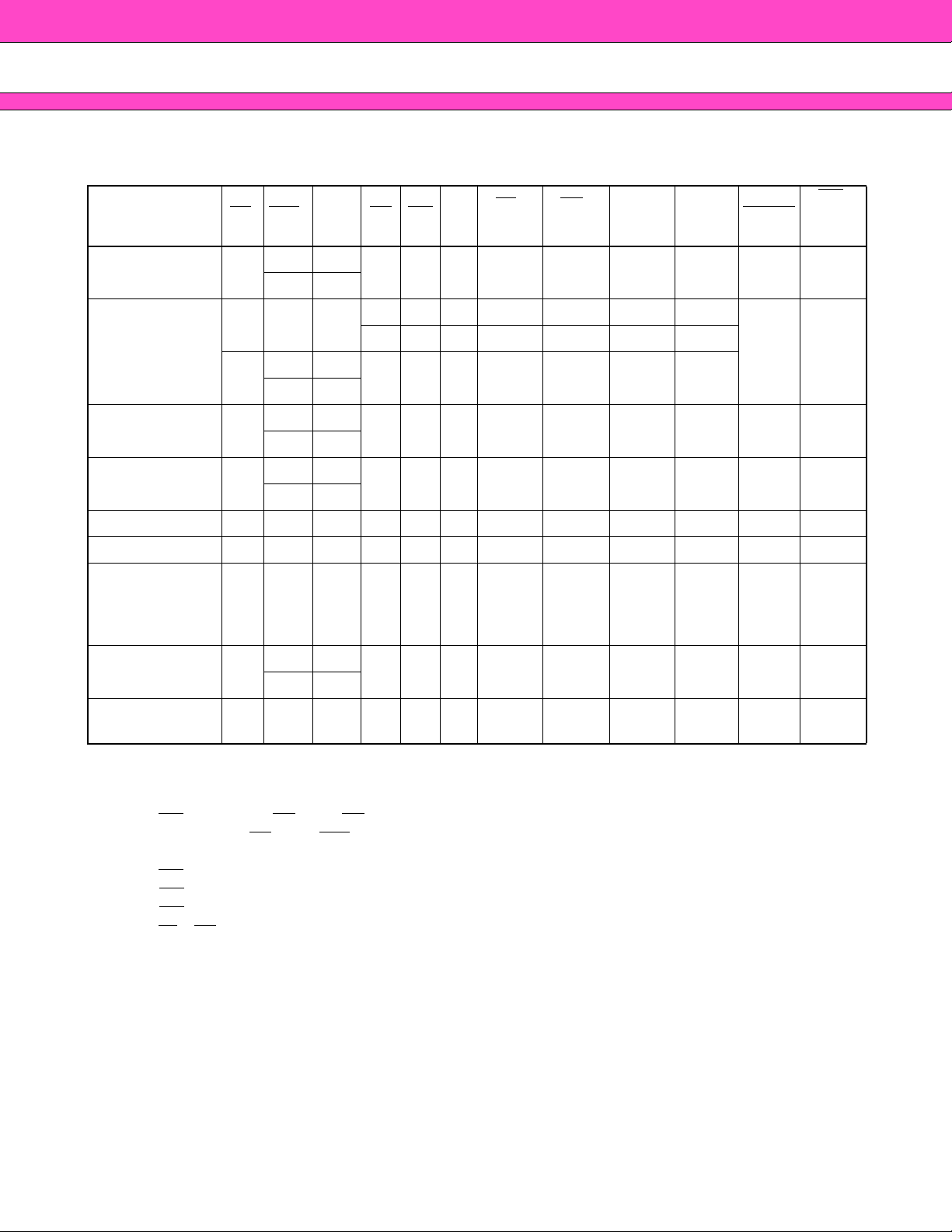

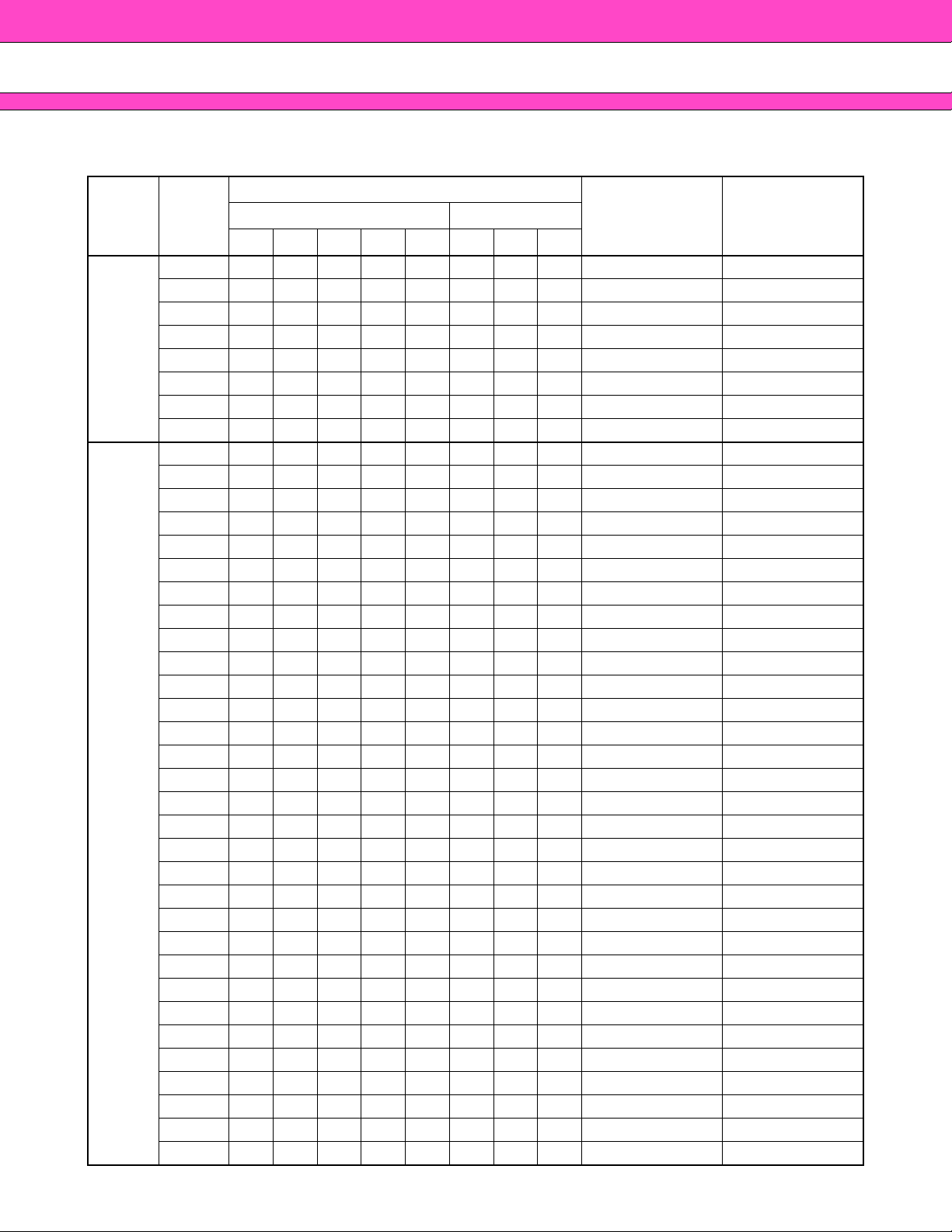

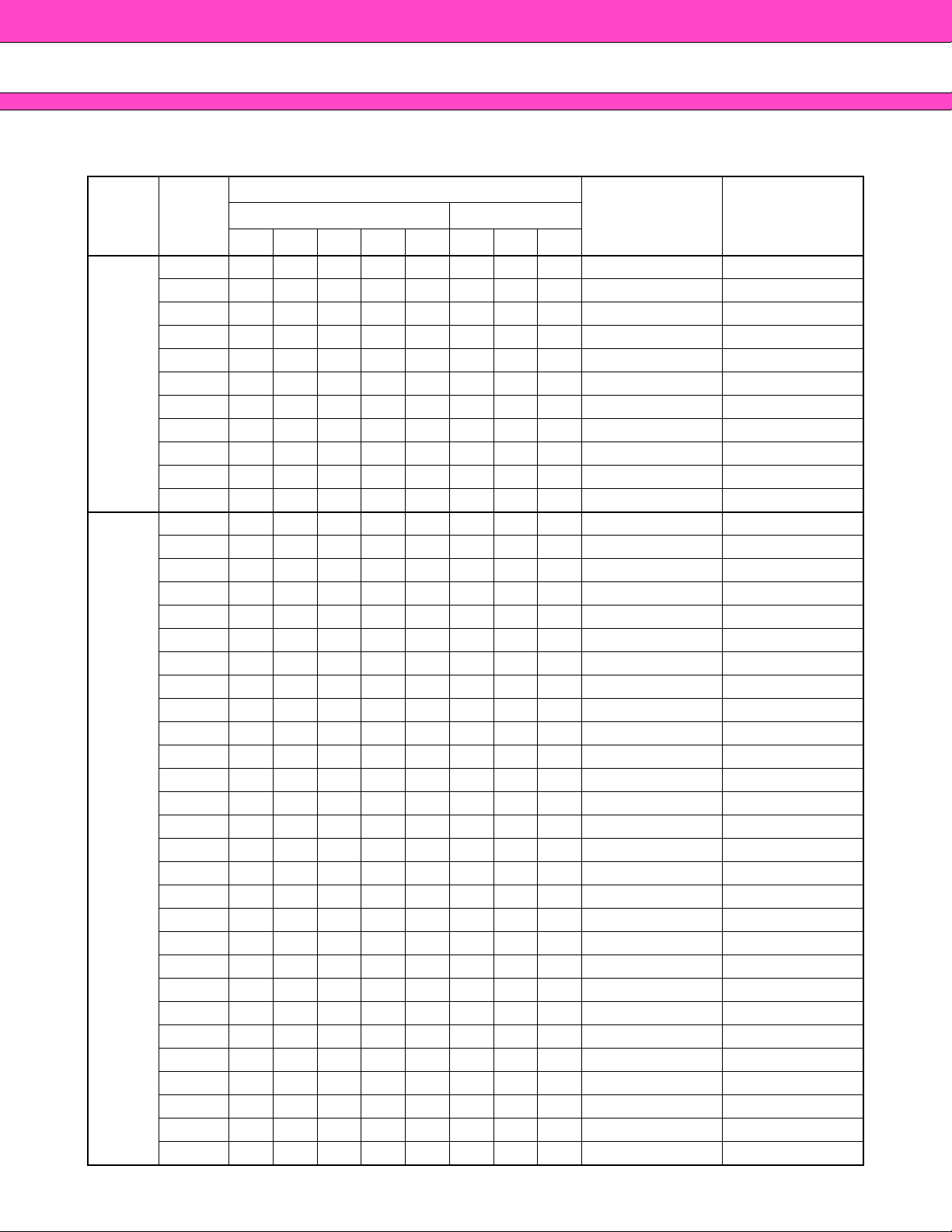

Table 2.2 User Bus Operations (Flash = Word mode ; CIOf = V

-85

CC

f, SRAM = Byte mode; CIOs = VSS)

Operation

(Note 1, 3)

fCE1sCE2s OE WE SA

CE

(Note 6)

UBs

(Note 6)

DQ0 to

DQ

LB

s

HX

Full Standby H

X X X X X HIGH-Z HIGH-Z H X

XL

H H X X X HIGH-Z HIGH-Z

HLH

X X X X X HIGH-Z HIGH-Z

Output Disable

HX

L

H H X X X HIGH-Z HIGH-Z

XL

Read from Flash

(Note 2)

L

HX

LHX X X D

XL

HX

Write to Flash L

HLX X X D

XL

Read from SRAM H L H L H SA X X D

Write to SRAM H L H X L SA X X D

Temporary Sector

Group

Unprotection

XX XXXX X X X X V

(Note 4)

WP/

ACC

(Note 5)

7

DQ8 to

15

DQ

RESET

HX

OUT DOUT HX

IN DIN HX

OUT HIGH-Z H X

IN HIGH-Z H X

ID X

Flash Hardware

Reset

Boot Block Sector

Write Protection

Legend: L = V

IL, H = VIH, X = VIL or VIH. See “ELECTRICAL CHARACTERISTICS 1. DC Characteristics” for

HX

X

X X X X X HIGH-Z HIGH-Z L X

XL

XX XXXX X X X X X L

voltage levels.

Notes : 1. Other operations except for indicated this column are inhibited.

2. WE

can be VIL if OE is VIL, OE at VIH initiates the write operations.

3. Do not apply CE

f = VIL, CE1s = VIL and CE2s = VIH at a time.

4. It is also used for the extended sector group protections.

5. WP

/ACC = VIL ; protection of boot sectors.

WP/ACC = VIH ; removal of boot sectors protection.

WP/ACC = VACC (9V) ; Program time will reduce by 40%.

6. LB

S , UBS ; Don’t care or Open.

8

MB84VD2118XA-85/MB84VD2119XA-

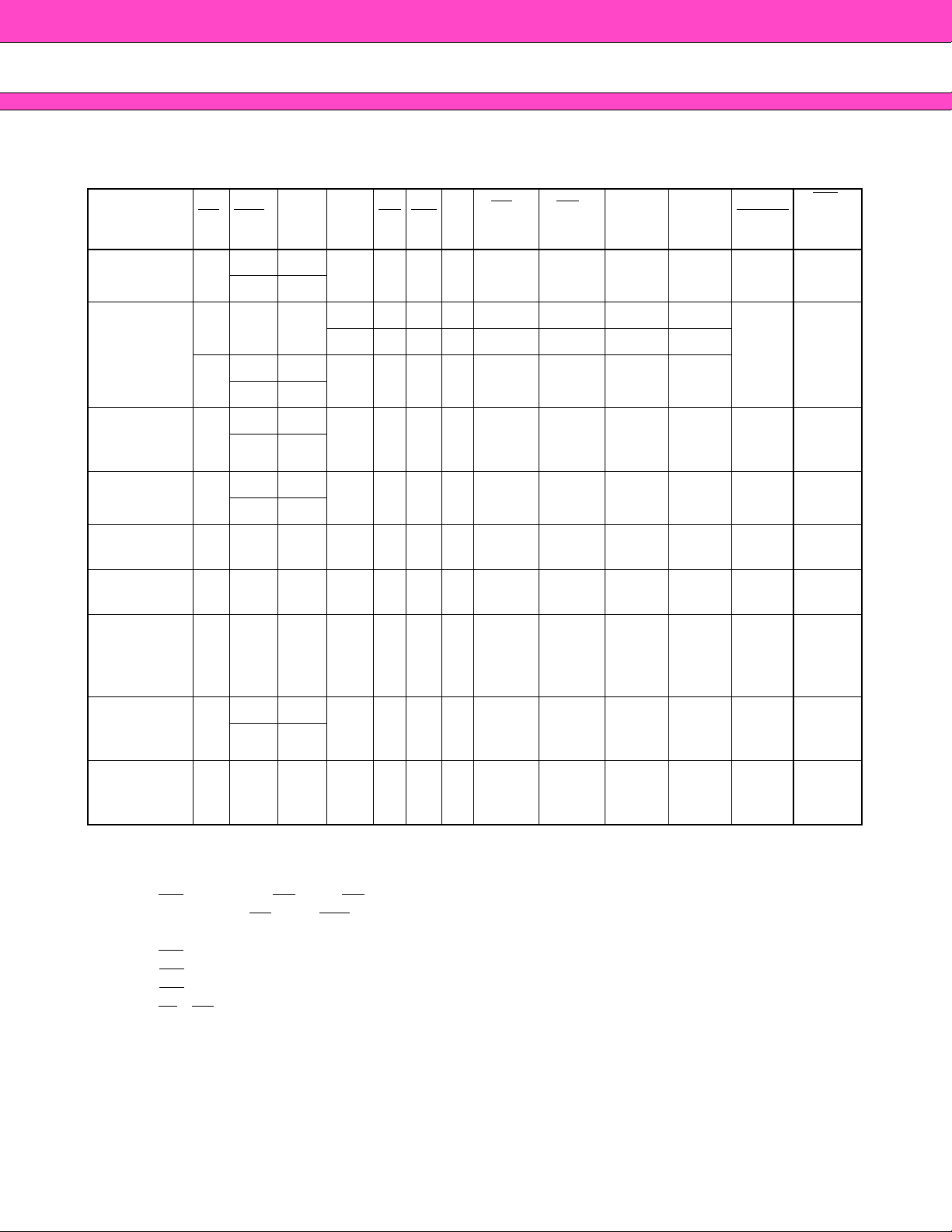

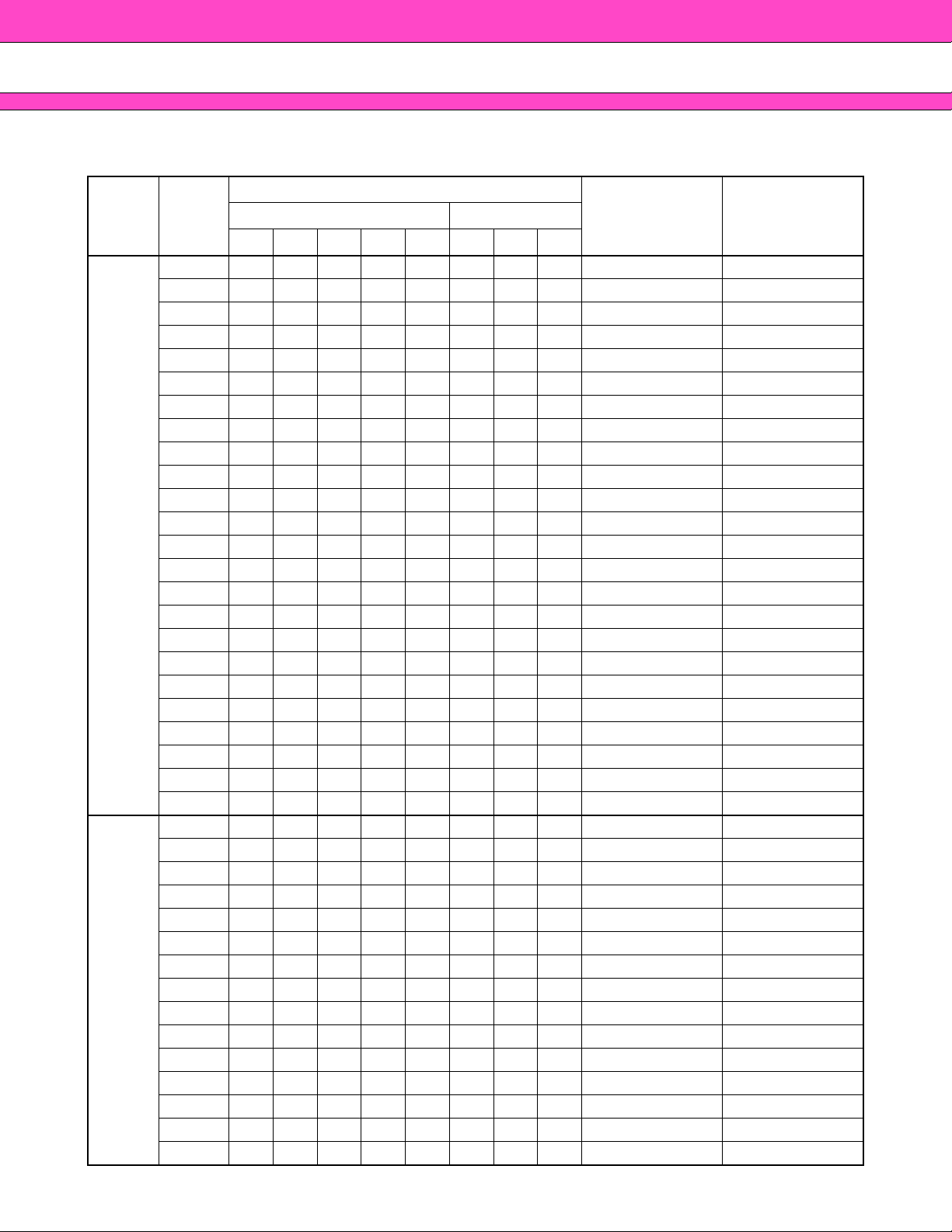

Table 2.3 User Bus Operations (Flash = Byte mode; CIOf = V

SS

, SRAM = Byte mode; CIOs = VSS)

85

Operation

(Note 1, 3)

CEfCE1sCE2s

Full Standby H

Output

Disable

Read from

Flash

(Note 2)

Write to

Flash

Read from

SRAM

Write to

SRAM

Temporary

Sector Group

Unprotection

(Note 4)

Flash

Hardware

Reset

1

DQ

A

/

-1

OE WE SA

LB

s

(Note 6)

UBs

(Note 6)

DQ0 to

7

DQ

DQ8 to

14

DQ

RESET

HX

X X X X X X HIGH-Z HIGH-Z H X

XL

X H H X X X HIGH-Z HIGH-Z

HL H

X X X X X X HIGH-Z HIGH-Z

HX

HX

L

-1 H H X X X HIGH-Z HIGH-Z

A

XL

HX

L

A

-1 LHX X X DOUT XHX

XL

HX

L

A

-1 HLX X X DIN XHX

XL

HL H XLHSAX X D

HL H XXLSAX X D

XX X XXXX X X X X V

OUT HIGH-Z H X

IN HIGH-Z H X

ID X

HX

X

X X X X X X HIGH-Z HIGH-Z L X

XL

WP/

ACC

(Note 5)

Boot Block

Sector Write

XX X XXXX X X X X X L

Protection

Legend: L = V

IL, H = VIH, X = VIL or VIH. See “ELECTRICAL CHARACTERISTICS 1. DC Characteristics” for

voltage levels.

Notes : 1. Other operations except for indicated this column are inhibited.

2. WE

can be VIL if OE is VIL, OE at VIH initiates the write operations.

3. Do not apply CE

f = VIL, CE1s = VIL and CE2s = VIH at a time.

4. It is also used for the extended sector group protections.

5. WP

/ACC = VIL ; protection of boot sectors.

WP/ACC = VIH ; removal of boot sectors protection.

WP/ACC = VACC (9V) ; Program time will reduce by 40%.

6. LB

S, UBS ; Don’t care or Open.

9

MB84VD2118XA

FLEXIBLE SECTOR-ERASE ARCHITECTURE on FLASH MEMORY

■■■■

• Eight 4 K words, and thirty one 32 K words.

• Individual-sector, multiple-sector, or bulk-erase capability.

/MB84VD2119XA

-85

-85

Word mode Byte mode

MB84VD21183A

Bank 1

MB84VD21184A

MB84VD21183A

Bank 2

MB84VD21184A

MB84VD21182A

Bank 1

MB84VD21182A

Bank 2

Bank 1

Bank 2

Bank 1

MB84VD21181A

Bank 2

MB84VD21181A

SA38 : 8KB (4KW)

SA37 : 8KB (4KW)

SA36 : 8KB (4KW)

SA35 : 8KB (4KW)

SA34 : 8KB (4KW)

SA33 : 8KB (4KW)

SA32 : 8KB (4KW)

SA31 : 8KB (4KW)

SA30 : 64KB (32KW)

SA29 : 64KB (32KW)

SA28 : 64KB (32KW)

SA27 : 64KB (32KW)

SA26 : 64KB (32KW)

SA25 : 64KB (32KW)

SA24 : 64KB (32KW)

SA23 : 64KB (32KW)

SA22 : 64KB (32KW)

SA21 : 64KB (32KW)

SA20 : 64KB (32KW)

SA19 : 64KB (32KW)

SA18 : 64KB (32KW)

SA17 : 64KB (32KW)

SA16 : 64KB (32KW)

SA15 : 64KB (32KW)

SA14 : 64KB (32KW)

SA13 : 64KB (32KW)

SA12 : 64KB (32KW)

SA11 : 64KB (32KW)

SA10 : 64KB (32KW)

SA9 : 64KB (32KW)

SA8 : 64KB (32KW)

SA7 : 64KB (32KW)

SA6 : 64KB (32KW)

SA5 : 64KB (32KW)

SA4 : 64KB (32KW)

SA3 : 64KB (32KW)

SA2 : 64KB (32KW)

SA1 : 64KB (32KW)

SA0 : 64KB (32KW)

0FFFFFH 1FFFFFH

0FF000H 1FE000H

0FE000H 1FC000H

0FD000H 1FA000H

0FC000H 1F8000H

0FB000H 1F6000H

0FA000H 1F4000H

0F9000H 1F2000H

0F8000H 1F0000H

0F0000H 1E0000H

0E8000H 1D0000H

0E0000H 1C0000H

0D8000H 1B0000H

0D0000H 1A0000H

0C8000H 190000H

0C0000H 180000H

0B8000H 170000H

0B0000H 160000H

0A8000H 150000H

0A0000H 140000H

098000H 130000H

090000H 120000H

088000H 110000H

080000H 100000H

078000H 0F0000H

070000H 0E0000H

068000H 0D0000H

060000H 0C0000H

058000H 0B0000H

050000H 0A0000H

048000H 090000H

040000H 080000H

038000H 070000H

030000H 060000H

028000H 050000H

020000H 040000H

018000H 030000H

010000H 020000H

008000H 010000H

000000H 000000H

10

MB84VD2118XA Sector Architecture (Top Boot Block)

MB84VD2118XA-85/MB84VD2119XA-

• Eight 4 K words, and thirty one 32 K words.

• Individual-sector, multiple-sector, or bulk-erase capability.

85

Word mode Byte mode

Bank 2

MB84VD21194A

MB84VD21193A

Bank 1

MB84VD21194A

MB84VD21193A

Bank 2

MB84VD21192A

Bank 1

MB84VD21192A

Bank 2

MB84VD21191A

Bank 1

MB84VD21191A

Bank 2

Bank 1

SA38 : 64KB (32KW)

SA37 : 64KB (32KW)

SA36 : 64KB (32KW)

SA35 : 64KB (32KW)

SA34 : 64KB (32KW)

SA33 : 64KB (32KW)

SA32 : 64KB (32KW)

SA31 : 64KB (32KW)

SA30 : 64KB (32KW)

SA29 : 64KB (32KW)

SA28 : 64KB (32KW)

SA27 : 64KB (32KW)

SA26 : 64KB (32KW)

SA25 : 64KB (32KW)

SA24 : 64KB (32KW)

SA23 : 64KB (32KW)

SA22 : 64KB (32KW)

SA21 : 64KB (32KW)

SA20 : 64KB (32KW)

SA19 : 64KB (32KW)

SA18 : 64KB (32KW)

SA17 : 64KB (32KW)

SA16 : 64KB (32KW)

SA15 : 64KB (32KW)

SA14 : 64KB (32KW)

SA13 : 64KB (32KW)

SA12 : 64KB (32KW)

SA11 : 64KB (32KW)

SA10 : 64KB (32KW)

SA9 : 64KB (32KW)

SA8 : 64KB (32KW)

SA7 : 8KB (4KW)

SA6 : 8KB (4KW)

SA5 : 8KB (4KW)

SA4 : 8KB (4KW)

SA3 : 8KB (4KW)

SA2 : 8KB (4KW)

SA1 : 8KB (4KW)

SA0 : 8KB (4KW)

0FFFFFH 1FFFFFH

0F8000H 1F0000H

0F0000H 1E0000H

0E8000H 1D0000H

0E0000H 1C0000H

0D8000H 1B0000H

0D0000H 1A0000H

0C8000H 190000H

0C0000H 180000H

0B8000H 170000H

0B0000H 160000H

0A8000H 150000H

0A0000H 140000H

098000H 130000H

090000H 120000H

088000H 110000H

080000H 100000H

078000H 0F0000H

070000H 0E0000H

068000H 0D0000H

060000H 0C0000H

058000H 0B0000H

050000H 0A0000H

048000H 090000H

040000H 080000H

038000H 070000H

030000H 060000H

028000H 050000H

020000H 040000H

018000H 030000H

010000H 020000H

008000H 010000H

007000H 00E000H

006000H 00C000H

005000H 00A000H

004000H 008000H

003000H 006000H

002000H 004000H

001000H 002000H

000000H 000000H

MB84VD2119XA Sector Architecture (Bottom Boot Block)

11

MB84VD2118XA

Bank Sector

19

A

SA0 00000XXX000000H to 00FFFFH 000000H to 007FFFH

SA1 00001XXX010000H to 01FFFFH 008000H to 00FFFFH

SA2 00010XXX020000H to 02FFFFH 010000H to 017FFFH

SA3 00011XXX030000H to 03FFFFH 018000H to 01FFFFH

SA4 00100XXX040000H to 04FFFFH 020000H to 027FFFH

SA5 00101XXX050000H to 05FFFFH 028000H to 02FFFFH

SA6 00110XXX060000H to 06FFFFH 030000H to 037FFFH

SA7 00111XXX070000H to 07FFFFH 038000H to 03FFFFH

SA8 01000XXX080000H to 08FFFFH 040000H to 047FFFH

SA9 01001XXX090000H to 09FFFFH 048000H to 04FFFFH

SA1001010XXX0A0000H to 0AFFFFH 050000H to 057FFFH

SA1101011XXX0B0000H to 0BFFFFH 058000H to 05FFFFH

SA1201100XXX0C0000H to 0CFFFFH 060000H to 067FFFH

SA1301101XXX0D0000H to 0DFFFFH 068000H to 06FFFFH

SA1401110XXX0E0000H to 0EFFFFH 070000H to 077FFFH

Bank 2

Bank 1

12

SA1501111XXX0F0000H to 0FFFFFH 078000H to 07FFFFH

SA1610000XXX100000H to 10FFFFH 080000H to 087FFFH

SA1710001XXX110000H to 11FFFFH 088000H to 08FFFFH

SA1810010XXX120000H to 12FFFFH 090000H to 097FFFH

SA1910011XXX130000H to 13FFFFH 098000H to 09FFFFH

SA2010100XXX140000H to 14FFFFH 0A0000H to 0A7FFFH

SA2110101XXX150000H to 15FFFFH 0A8000H to 0AFFFFH

SA2210110XXX160000H to 16FFFFH 0B0000H to 0B7FFFH

SA2310111XXX170000H to 17FFFFH 0B8000H to 0BFFFFH

SA2411000XXX180000H to 18FFFFH 0C0000H to 0C7FFFH

SA2511001XXX190000H to 19FFFFH 0C8000H to 0CFFFFH

SA2611010XXX1A0000H to 1AFFFFH 0D0000H to 0D7FFFH

SA2711011XXX1B0000H to 1BFFFFH 0D8000H to 0DFFFFH

SA2811100XXX1C0000H to 1CFFFFH 0E0000H to 0E7FFFH

SA2911101XXX1D0000H to 1DFFFFH 0E8000H to 0EFFFFH

SA3011110XXX1E0000H to 1EFFFFH 0F0000H to 0F7FFFH

SA31111110001F0000H to 1F1FFFH 0F8000H to 0F8FFFH

SA32111110011F2000H to 1F3FFFH 0F9000H to 0F9FFFH

SA33111110101F4000H to 1F5FFFH 0FA000H to 0FAFFFH

SA34111110111F6000H to 1F7FFFH 0FB000H to 0FBFFFH

SA35111111001F8000H to 1F9FFFH 0FC000H to 0FCFFFH

SA36111111011FA000H to 1FBFFFH0FD000H to 0FDFFFH

SA37111111101FC000H to 1FDFFFH 0FE000H to 0FEFFFH

SA38111111111FE000H to 1FFFFFH 0FF000H to 0FFFFFH

/MB84VD2119XA

-85

Table 3.1 Sector Address Tables (MB84VD21181)

Sector Address

Bank Address

18

A

17

A

16

15

14

A

A

A

13

A

Address Range

(Byte mode)

12

A

-85

Address Range

(Word mode)

Bank Sector

SA0 00000000000000H to 001FFFH 000000H to 000FFFH

SA1 00000001002000H to 003FFFH 001000H to 001FFFH

SA2 00000010004000H to 005FFFH 002000H to 002FFFH

Bank 1

Bank 2

SA3 00000011006000H to 007FFFH 003000H to 003FFFH

SA4 00000100008000H to 009FFFH 004000H to 004FFFH

SA5 0000010100A000H to 00BFFFH 005000H to 005FFFH

SA6 0000011000C000H to 00DFFFH006000H to 006FFFH

SA7 0000011100E000H to 00FFFFH 007000H to 007FFFH

SA8 00001XXX010000H to 01FFFFH 008000H to 00FFFFH

SA9 00010XXX020000H to 02FFFFH 010000H to 017FFFH

SA1000011XXX030000H to 03FFFFH 018000H to 01FFFFH

SA1100100XXX040000H to 04FFFFH 020000H to 027FFFH

SA1200101XXX050000H to 05FFFFH 028000H to 02FFFFH

SA1300110XXX060000H to 06FFFFH 030000H to 037FFFH

SA1400111XXX070000H to 07FFFFH 038000H to 03FFFFH

SA1501000XXX080000H to 08FFFFH 040000H to 047FFFH

SA1601001XXX090000H to 09FFFFH 048000H to 04FFFFH

SA1701010XXX0A0000H to 0AFFFFH 050000H to 057FFFH

SA1801011XXX0B0000H to 0BFFFFH 058000H to 05FFFFH

SA1901100XXX0C0000H to 0CFFFFH 060000H to 067FFFH

SA2001101XXX0D0000H to 0DFFFFH 068000H to 06FFFFH

SA2101110XXX0E0000H to 0EFFFFH 070000H to 077FFFH

SA2201111XXX0F0000H to 0FFFFFH 078000H to 07FFFFH

SA2310000XXX100000H to 10FFFFH 080000H to 087FFFH

SA2410001XXX110000H to 11FFFFH 088000H to 08FFFFH

SA2510010XXX120000H to 12FFFFH 090000H to 097FFFH

SA2610011XXX130000H to 13FFFFH 098000H to 09FFFFH

SA2710100XXX140000H to 14FFFFH 0A0000H to 0A7FFFH

SA2810101XXX150000H to 15FFFFH 0A8000H to 0AFFFFH

SA2910110XXX160000H to 16FFFFH 0B0000H to 0B7FFFH

SA3010111XXX170000H to 17FFFFH 0B8000H to 0BFFFFH

SA3111000XXX180000H to 18FFFFH 0C0000H to 0C7FFFH

SA3211001XXX190000H to 19FFFFH 0C8000H to 0CFFFFH

SA3311010XXX1A0000H to 1AFFFFH 0D0000H to 0D7FFFH

SA3411011XXX1B0000H to 1BFFFFH 0D8000H to 0DFFFFH

SA3511100XXX1C0000H to 1CFFFFH 0E0000H to 0E7FFFH

SA3611101XXX1D0000H to 1DFFFFH 0E8000H to 0EFFFFH

SA3711110XXX1E0000H to 1EFFFFH 0F0000H to 0F7FFFH

SA3811111XXX1F0000H to 1FFFFFH 0F8000H to 0FFFFFH

MB84VD2118XA-85/MB84VD2119XA-

85

Table 3.2 Sector Address Tables (MB84VD21191)

Sector Address

Bank Address

19

18

17

16

15

14

A

A

A

A

A

A

13

A

Address Range

(BYTE mode)

12

A

Address Range

(WORD mode)

13

MB84VD2118XA

Bank Sector

19

A

SA0 00000XXX000000H to 00FFFFH 000000H to 007FFFH

SA1 00001XXX010000H to 01FFFFH 008000H to 00FFFFH

SA2 00010XXX020000H to 02FFFFH 010000H to 017FFFH

SA3 00011XXX030000H to 03FFFFH 018000H to 01FFFFH

SA4 00100XXX040000H to 04FFFFH 020000H to 027FFFH

SA5 00101XXX050000H to 05FFFFH 028000H to 02FFFFH

SA6 00110XXX060000H to 06FFFFH 030000H to 037FFFH

SA7 00111XXX070000H to 07FFFFH 038000H to 03FFFFH

SA8 01000XXX080000H to 08FFFFH 040000H to 047FFFH

SA9 01001XXX090000H to 09FFFFH 048000H to 04FFFFH

SA1001010XXX0A0000H to 0AFFFFH 050000H to 057FFFH

SA1101011XXX0B0000H to 0BFFFFH 058000H to 05FFFFH

SA1201100XXX0C0000H to 0CFFFFH 060000H to 067FFFH

Bank 2

Bank 1

14

SA1301101XXX0D0000H to 0DFFFFH 068000H to 06FFFFH

SA1401110XXX0E0000H to 0EFFFFH 070000H to 077FFFH

SA1501111XXX0F0000H to 0FFFFFH 078000H to 07FFFFH

SA1610000XXX100000H to 10FFFFH 080000H to 087FFFH

SA1710001XXX110000H to 11FFFFH 088000H to 08FFFFH

SA1810010XXX120000H to 12FFFFH 090000H to 097FFFH

SA1910011XXX130000H to 13FFFFH 098000H to 09FFFFH

SA2010100XXX140000H to 14FFFFH 0A0000H to 0A7FFFH

SA2110101XXX150000H to 15FFFFH 0A8000H to 0AFFFFH

SA2210110XXX160000H to 16FFFFH 0B0000H to 0B7FFFH

SA2310111XXX170000H to 17FFFFH 0B8000H to 0BFFFFH

SA2411000XXX180000H to 18FFFFH 0C0000H to 0C7FFFH

SA2511001XXX190000H to 19FFFFH 0C8000H to 0CFFFFH

SA2611010XXX1A0000H to 1AFFFFH 0D0000H to 0D7FFFH

SA2711011XXX1B0000H to 1BFFFFH 0D8000H to 0DFFFFH

SA2811100XXX1C0000H to 1CFFFFH 0E0000H to 0E7FFFH

SA2911101XXX1D0000H to 1DFFFFH 0E8000H to 0EFFFFH

SA3011110XXX1E0000H to 1EFFFFH 0F0000H to 0F7FFFH

SA31111110001F0000H to 1F1FFFH 0F8000H to 0F8FFFH

SA32111110011F2000H to 1F3FFFH 0F9000H to 0F9FFFH

SA33111110101F4000H to 1F5FFFH 0FA000H to 0FAFFFH

SA34111110111F6000H to 1F7FFFH 0FB000H to 0FBFFFH

SA35111111001F8000H to 1F9FFFH 0FC000H to 0FCFFFH

SA36111111011FA000H to 1FBFFFH0FD000H to 0FDFFFH

SA37111111101FC000H to 1FDFFFH 0FE000H to 0FEFFFH

SA38111111111FE000H to 1FFFFFH 0FF000H to 0FFFFFH

/MB84VD2119XA

-85

Table 3.3 Sector Address Tables (MB84VD21182)

Sector Address

Bank Address

18

A

17

A

16

15

14

A

A

A

13

A

Address Range

(BYTE mode)

12

A

-85

Address Range

(WORD mode)

Bank Sector

SA0 00000000000000H to 001FFFH 000000H to 000FFFH

SA1 00000001002000H to 003FFFH 001000H to 001FFFH

SA2 00000010004000H to 005FFFH 002000H to 002FFFH

SA3 00000011006000H to 007FFFH 003000H to 003FFFH

SA4 00000100008000H to 009FFFH 004000H to 004FFFH

Bank 1

Bank 2

SA5 0000010100A000H to 00BFFFH 005000H to 005FFFH

SA6 0000011000C000H to 00DFFFH006000H to 006FFFH

SA7 0000011100E000H to 00FFFFH 007000H to 007FFFH

SA8 00001XXX010000H to 01FFFFH 008000H to 00FFFFH

SA9 00010XXX020000H to 02FFFFH 010000H to 017FFFH

SA1000011XXX030000H to 03FFFFH 018000H to 01FFFFH

SA1100100XXX040000H to 04FFFFH 020000H to 027FFFH

SA1200101XXX050000H to 05FFFFH 028000H to 02FFFFH

SA1300110XXX060000H to 06FFFFH 030000H to 037FFFH

SA1400111XXX070000H to 07FFFFH 038000H to 03FFFFH

SA1501000XXX080000H to 08FFFFH 040000H to 047FFFH

SA1601001XXX090000H to 09FFFFH 048000H to 04FFFFH

SA1701010XXX0A0000H to 0AFFFFH 050000H to 057FFFH

SA1801011XXX0B0000H to 0BFFFFH 058000H to 05FFFFH

SA1901100XXX0C0000H to 0CFFFFH 060000H to 067FFFH

SA2001101XXX0D0000H to 0DFFFFH 068000H to 06FFFFH

SA2101110XXX0E0000H to 0EFFFFH 070000H to 077FFFH

SA2201111XXX0F0000H to 0FFFFFH 078000H to 07FFFFH

SA2310000XXX100000H to 10FFFFH 080000H to 087FFFH

SA2410001XXX110000H to 11FFFFH 088000H to 08FFFFH

SA2510010XXX120000H to 12FFFFH 090000H to 097FFFH

SA2610011XXX130000H to 13FFFFH 098000H to 09FFFFH

SA2710100XXX140000H to 14FFFFH 0A0000H to 0A7FFFH

SA2810101XXX150000H to 15FFFFH 0A8000H to 0AFFFFH

SA2910110XXX160000H to 16FFFFH 0B0000H to 0B7FFFH

SA3010111XXX170000H to 17FFFFH 0B8000H to 0BFFFFH

SA3111000XXX180000H to 18FFFFH 0C0000H to 0C7FFFH

SA3211001XXX190000H to 19FFFFH 0C8000H to 0CFFFFH

SA3311010XXX1A0000H to 1AFFFFH 0D0000H to 0D7FFFH

SA3411011XXX1B0000H to 1BFFFFH 0D8000H to 0DFFFFH

SA3511100XXX1C0000H to 1CFFFFH 0E0000H to 0E7FFFH

SA3611101XXX1D0000H to 1DFFFFH 0E8000H to 0EFFFFH

SA3711110XXX1E0000H to 1EFFFFH 0F0000H to 0F7FFFH

SA3811111XXX1F0000H to 1FFFFFH 0F8000H to 0FFFFFH

MB84VD2118XA-85/MB84VD2119XA-

85

Table 3.4 Sector Address Tables (MB84VD21192)

Sector Address

Bank Address

19

18

17

16

15

14

A

A

A

A

A

A

13

A

Address Range

(BYTE mode)

12

A

Address Range

(WORD mode)

15

MB84VD2118XA

Bank Sector

19

A

SA0 00000XXX000000H to 00FFFFH 000000H to 007FFFH

SA1 00001XXX010000H to 01FFFFH 008000H to 00FFFFH

SA2 00010XXX020000H to 02FFFFH 010000H to 017FFFH

SA3 00011XXX030000H to 03FFFFH 018000H to 01FFFFH

SA4 00100XXX040000H to 04FFFFH 020000H to 027FFFH

SA5 00101XXX050000H to 05FFFFH 028000H to 02FFFFH

SA6 00110XXX060000H to 06FFFFH 030000H to 037FFFH

SA7 00111XXX070000H to 07FFFFH 038000H to 03FFFFH

SA8 01000XXX080000H to 08FFFFH 040000H to 047FFFH

SA9 01001XXX090000H to 09FFFFH 048000H to 04FFFFH

SA1001010XXX0A0000H to 0AFFFFH 050000H to 057FFFH

Bank 2

Bank 1

16

SA1101011XXX0B0000H to 0BFFFFH 058000H to 05FFFFH

SA1201100XXX0C0000H to 0CFFFFH 060000H to 067FFFH

SA1301101XXX0D0000H to 0DFFFFH 068000H to 06FFFFH

SA1401110XXX0E0000H to 0EFFFFH 070000H to 077FFFH

SA1501111XXX0F0000H to 0FFFFFH 078000H to 07FFFFH

SA1610000XXX100000H to 10FFFFH 080000H to 087FFFH

SA1710001XXX110000H to 11FFFFH 088000H to 08FFFFH

SA1810010XXX120000H to 12FFFFH 090000H to 097FFFH

SA1910011XXX130000H to 13FFFFH 098000H to 09FFFFH

SA2010100XXX140000H to 14FFFFH 0A0000H to 0A7FFFH

SA2110101XXX150000H to 15FFFFH 0A8000H to 0AFFFFH

SA2210110XXX160000H to 16FFFFH 0B0000H to 0B7FFFH

SA2310111XXX170000H to 17FFFFH 0B8000H to 0BFFFFH

SA2411000XXX180000H to 18FFFFH 0C0000H to 0C7FFFH

SA2511001XXX190000H to 19FFFFH 0C8000H to 0CFFFFH

SA2611010XXX1A0000H to 1AFFFFH 0D0000H to 0D7FFFH

SA2711011XXX1B0000H to 1BFFFFH 0D8000H to 0DFFFFH

SA2811100XXX1C0000H to 1CFFFFH 0E0000H to 0E7FFFH

SA2911101XXX1D0000H to 1DFFFFH 0E8000H to 0EFFFFH

SA3011110XXX1E0000H to 1EFFFFH 0F0000H to 0F7FFFH

SA31111110001F0000H to 1F1FFFH 0F8000H to 0F8FFFH

SA32111110011F2000H to 1F3FFFH 0F9000H to 0F9FFFH

SA33111110101F4000H to 1F5FFFH 0FA000H to 0FAFFFH

SA34111110111F6000H to 1F7FFFH 0FB000H to 0FBFFFH

SA35111111001F8000H to 1F9FFFH 0FC000H to 0FCFFFH

SA36111111011FA000H to 1FBFFFH0FD000H to 0FDFFFH

SA37111111101FC000H to 1FDFFFH 0FE000H to 0FEFFFH

SA38111111111FE000H to 1FFFFFH 0FF000H to 0FFFFFH

/MB84VD2119XA

-85

Table 3.5 Sector Address Tables (MB84VD21183)

Sector Address

Bank Address

18

A

17

A

16

15

14

A

A

A

13

A

Address Range

(BYTE mode)

12

A

-85

Address Range

(WORD mode)

Bank Sector

SA0 00000000000000H to 001FFFH 000000H to 000FFFH

SA1 00000001002000H to 003FFFH 001000H to 001FFFH

SA2 00000010004000H to 005FFFH 002000H to 002FFFH

SA3 00000011006000H to 007FFFH 003000H to 003FFFH

SA4 00000100008000H to 009FFFH 004000H to 004FFFH

SA5 0000010100A000H to 00BFFFH 005000H to 005FFFH

SA6 0000011000C000H to 00DFFFH006000H to 006FFFH

Bank 1

Bank 2

SA7 0000011100E000H to 00FFFFH 007000H to 007FFFH

SA8 00001XXX010000H to 01FFFFH 008000H to 00FFFFH

SA9 00010XXX020000H to 02FFFFH 010000H to 017FFFH

SA1000011XXX030000H to 03FFFFH 018000H to 01FFFFH

SA1100100XXX040000H to 04FFFFH 020000H to 027FFFH

SA1200101XXX050000H to 05FFFFH 028000H to 02FFFFH

SA1300110XXX060000H to 06FFFFH 030000H to 037FFFH

SA1400111XXX070000H to 07FFFFH 038000H to 03FFFFH

SA1501000XXX080000H to 08FFFFH 040000H to 047FFFH

SA1601001XXX090000H to 09FFFFH 048000H to 04FFFFH

SA1701010XXX0A0000H to 0AFFFFH 050000H to 057FFFH

SA1801011XXX0B0000H to 0BFFFFH 058000H to 05FFFFH

SA1901100XXX0C0000H to 0CFFFFH 060000H to 067FFFH

SA2001101XXX0D0000H to 0DFFFFH 068000H to 06FFFFH

SA2101110XXX0E0000H to 0EFFFFH 070000H to 077FFFH

SA2201111XXX0F0000H to 0FFFFFH 078000H to 07FFFFH

SA2310000XXX100000H to 10FFFFH 080000H to 087FFFH

SA2410001XXX110000H to 11FFFFH 088000H to 08FFFFH

SA2510010XXX120000H to 12FFFFH 090000H to 097FFFH

SA2610011XXX130000H to 13FFFFH 098000H to 09FFFFH

SA2710100XXX140000H to 14FFFFH 0A0000H to 0A7FFFH

SA2810101XXX150000H to 15FFFFH 0A8000H to 0AFFFFH

SA2910110XXX160000H to 16FFFFH 0B0000H to 0B7FFFH

SA3010111XXX170000H to 17FFFFH 0B8000H to 0BFFFFH

SA3111000XXX180000H to 18FFFFH 0C0000H to 0C7FFFH

SA3211001XXX190000H to 19FFFFH 0C8000H to 0CFFFFH

SA3311010XXX1A0000H to 1AFFFFH 0D0000H to 0D7FFFH

SA3411011XXX1B0000H to 1BFFFFH 0D8000H to 0DFFFFH

SA3511100XXX1C0000H to 1CFFFFH 0E0000H to 0E7FFFH

SA3611101XXX1D0000H to 1DFFFFH 0E8000H to 0EFFFFH

SA3711110XXX1E0000H to 1EFFFFH 0F0000H to 0F7FFFH

SA3811111XXX1F0000H to 1FFFFFH 0F8000H to 0FFFFFH

MB84VD2118XA-85/MB84VD2119XA-

85

Table 3.6 Sector Address Tables (MB84VD21193)

Sector Address

Bank Address

19

18

17

16

15

14

A

A

A

A

A

A

13

A

Address Range

(BYTE mode)

12

A

Address Range

(WORD mode)

17

MB84VD2118XA

Bank Sector

19

A

SA0 00000XXX000000H to 00FFFFH 000000H to 007FFFH

SA1 00001XXX010000H to 01FFFFH 008000H to 00FFFFH

SA2 00010XXX020000H to 02FFFFH 010000H to 017FFFH

SA3 00011XXX030000H to 03FFFFH 018000H to 01FFFFH

SA4 00100XXX040000H to 04FFFFH 020000H to 027FFFH

SA5 00101XXX050000H to 05FFFFH 028000H to 02FFFFH

SA6 00110XXX060000H to 06FFFFH 030000H to 037FFFH

Bank 2

Bank 1

18

SA7 00111XXX070000H to 07FFFFH 038000H to 03FFFFH

SA8 01000XXX080000H to 08FFFFH 040000H to 047FFFH

SA9 01001XXX090000H to 09FFFFH 048000H to 04FFFFH

SA1001010XXX0A0000H to 0AFFFFH 050000H to 057FFFH

SA1101011XXX0B0000H to 0BFFFFH 058000H to 05FFFFH

SA1201100XXX0C0000H to 0CFFFFH 060000H to 067FFFH

SA1301101XXX0D0000H to 0DFFFFH 068000H to 06FFFFH

SA1401110XXX0E0000H to 0EFFFFH 070000H to 077FFFH

SA1501111XXX0F0000H to 0FFFFFH 078000H to 07FFFFH

SA1610000XXX100000H to 10FFFFH 080000H to 087FFFH

SA1710001XXX110000H to 11FFFFH 088000H to 08FFFFH

SA1810010XXX120000H to 12FFFFH 090000H to 097FFFH

SA1910011XXX130000H to 13FFFFH 098000H to 09FFFFH

SA2010100XXX140000H to 14FFFFH 0A0000H to 0A7FFFH

SA2110101XXX150000H to 15FFFFH 0A8000H to 0AFFFFH

SA2210110XXX160000H to 16FFFFH 0B0000H to 0B7FFFH

SA2310111XXX170000H to 17FFFFH 0B8000H to 0BFFFFH

SA2411000XXX180000H to 18FFFFH 0C0000H to 0C7FFFH

SA2511001XXX190000H to 19FFFFH 0C8000H to 0CFFFFH

SA2611010XXX1A0000H to 1AFFFFH 0D0000H to 0D7FFFH

SA2711011XXX1B0000H to 1BFFFFH 0D8000H to 0DFFFFH

SA2811100XXX1C0000H to 1CFFFFH 0E0000H to 0E7FFFH

SA2911101XXX1D0000H to 1DFFFFH 0E8000H to 0EFFFFH

SA3011110XXX1E0000H to 1EFFFFH 0F0000H to 0F7FFFH

SA31111110001F0000H to 1F1FFFH 0F8000H to 0F8FFFH

SA32111110011F2000H to 1F3FFFH 0F9000H to 0F9FFFH

SA33111110101F4000H to 1F5FFFH 0FA000H to 0FAFFFH

SA34111110111F6000H to 1F7FFFH 0FB000H to 0FBFFFH

SA35111111001F8000H to 1F9FFFH 0FC000H to 0FCFFFH

SA36111111011FA000H to 1FBFFFH0FD000H to 0FDFFFH

SA37111111101FC000H to 1FDFFFH 0FE000H to 0FEFFFH

SA38111111111FE000H to 1FFFFFH 0FF000H to 0FFFFFH

/MB84VD2119XA

-85

Table 3.7 Sector Address Tables (MB84VD21184)

Sector Address

Bank Address

18

A

17

A

16

15

14

A

A

A

13

A

Address Range

(BYTE mode)

12

A

-85

Address Range

(WORD mode)

Bank Sector

SA0 00000000000000H to 001FFFH 000000H to 000FFFH

SA1 00000001002000H to 003FFFH 001000H to 001FFFH

SA2 00000010004000H to 005FFFH 002000H to 002FFFH

SA3 00000011006000H to 007FFFH 003000H to 003FFFH

SA4 00000100008000H to 009FFFH 004000H to 004FFFH

SA5 0000010100A000H to 00BFFFH 005000H to 005FFFH

SA6 0000011000C000H to 00DFFFH006000H to 006FFFH

SA7 0000011100E000H to 00FFFFH 007000H to 007FFFH

SA8 00001XXX010000H to 01FFFFH 008000H to 00FFFFH

SA9 00010XXX020000H to 02FFFFH 010000H to 017FFFH

SA1000011XXX030000H to 03FFFFH 018000H to 01FFFFH

Bank 1

Bank 2

SA1100100XXX040000H to 04FFFFH 020000H to 027FFFH

SA1200101XXX050000H to 05FFFFH 028000H to 02FFFFH

SA1300110XXX060000H to 06FFFFH 030000H to 037FFFH

SA1400111XXX070000H to 07FFFFH 038000H to 03FFFFH

SA1501000XXX080000H to 08FFFFH 040000H to 047FFFH

SA1601001XXX090000H to 09FFFFH 048000H to 04FFFFH

SA1701010XXX0A0000H to 0AFFFFH 050000H to 057FFFH

SA1801011XXX0B0000H to 0BFFFFH 058000H to 05FFFFH

SA1901100XXX0C0000H to 0CFFFFH 060000H to 067FFFH

SA2001101XXX0D0000H to 0DFFFFH 068000H to 06FFFFH

SA2101110XXX0E0000H to 0EFFFFH 070000H to 077FFFH

SA2201111XXX0F0000H to 0FFFFFH 078000H to 07FFFFH

SA2310000XXX100000H to 10FFFFH 080000H to 087FFFH

SA2410001XXX110000H to 11FFFFH 088000H to 08FFFFH

SA2510010XXX120000H to 12FFFFH 090000H to 097FFFH

SA2610011XXX130000H to 13FFFFH 098000H to 09FFFFH

SA2710100XXX140000H to 14FFFFH 0A0000H to 0A7FFFH

SA2810101XXX150000H to 15FFFFH 0A8000H to 0AFFFFH

SA2910110XXX160000H to 16FFFFH 0B0000H to 0B7FFFH

SA3010111XXX170000H to 17FFFFH 0B8000H to 0BFFFFH

SA3111000XXX180000H to 18FFFFH 0C0000H to 0C7FFFH

SA3211001XXX190000H to 19FFFFH 0C8000H to 0CFFFFH

SA3311010XXX1A0000H to 1AFFFFH 0D0000H to 0D7FFFH

SA3411011XXX1B0000H to 1BFFFFH 0D8000H to 0DFFFFH

SA3511100XXX1C0000H to 1CFFFFH 0E0000H to 0E7FFFH

SA3611101XXX1D0000H to 1DFFFFH 0E8000H to 0EFFFFH

SA3711110XXX1E0000H to 1EFFFFH 0F0000H to 0F7FFFH

SA3811111XXX1F0000H to 1FFFFFH 0F8000H to 0FFFFFH

MB84VD2118XA-85/MB84VD2119XA-

85

Table 3.8 Sector Address Tables (MB84VD21194)

Sector Address

Bank Address

19

18

17

16

15

14

A

A

A

A

A

A

13

A

Address Range

(BYTE mode)

12

A

Address Range

(WORD mode)

19

MB84VD2118XA

Table 4.1 Sector Group Addresses (MB84VD2118XA)

/MB84VD2119XA

-85

(Top Boot Block)

-85

Sector Group A

19

18

A

17

A

16

A

15

A

14

A

13

A

12

A

Sectors

SGA0 00000XXX SA0

00001XXX

SGA1

SA1 to SA300010XXX

00011XXX

SGA2 001XXXXXSA4 to SA7

SGA3 0 1 0 X X X X X SA8 to SA11

SGA4 0 1 1 X X X X X SA12 to SA15

SGA5 1 0 0 X X X X X SA16 to SA19

SGA6 1 0 1 X X X X X SA20 to SA23

SGA7 1 1 0 X X X X X SA24 to SA27

11100XXX

SGA8

SA28 to SA3011101XXX

11110XXX

SGA9 11111000 SA31

SGA1011111001 SA32

SGA1111111010 SA33

SGA1211111011 SA34

SGA1311111100 SA35

SGA1411111101 SA36

SGA1511111110 SA37

SGA1611111111 SA38

20

MB84VD2118XA-85/MB84VD2119XA-

Table 4.2 Sector Group Addresses (MB84VD2119XA)

(Bottom Boot Block)

85

Sector Group A

19

18

A

17

A

16

A

15

A

14

A

13

A

12

A

Sectors

SGA0 00000000 SA0

SGA1 00000001 SA1

SGA2 00000010 SA2

SGA3 00000011 SA3

SGA4 00000100 SA4

SGA5 00000101 SA5

SGA6 00000110 SA6

SGA7 00000111 SA7

00001XXX

SGA8

SA8 to SA1000010XXX

00011XXX

SGA9 0 0 1 X X X X X SA11 to SA14

SGA10 0 1 0 X X X X X SA15 to SA18

SGA11 0 1 1 X X X X X SA19 to SA22

SGA12 1 0 0 X X X X X SA23 to SA26

SGA13 1 0 1 X X X X X SA27 to SA30

SGA14 1 1 0 X X X X X SA31 to SA34

11100XXX

SGA15

SA35 to SA3711101XXX

11110XXX

SGA16 1 1 1 1 1 X X X SA38

21

MB84VD2118XA

Type A

/MB84VD2119XA

-85

Table 5 Flash Memory Autoselect Codes

12

to A

19

6

A

1

A

-85

A

A-1*

1

Code (HEX)

0

Manufacturer’s Code X V

Byte

MB84VD21181A

XV

Word X 2236H

Byte

MB84VD21191A

XV

Word X 2239H

Byte

MB84VD21182A

XV

Word X 222DH

Byte

Device

Code

MB84VD21192A

Word X 222EH

Byte

MB84VD21183A

XV

XV

Word X 2228H

Byte

MB84VD21193A

XV

Word X 222BH

Byte

MB84VD21184A

XV

Word X 2233H

Byte

MB84VD21194A

XV

Word X 2235H

Sector Group protect

Sector Group

Address

IL VIL VIL VIL 04H

VIL 36H

IL VIL VIH

VIL 39

IL VIL VIH

VIL 2D

IL VIL VIH

VIL 2E

IL VIL VIH

VIL 28H

IL VIL VIH

VIL 2BH

IL VIL VIH

VIL 33H

IL VIL VIH

VIL 35

IL VIL VIH

V

IL VIH VIL VIL 01H*

2

*1 : A

-1 is for Byte mode.

*2 : Output 01H at protected sector address and output 00H at unprotected sector address.

22

MB84VD2118XA-85/MB84VD2119XA-

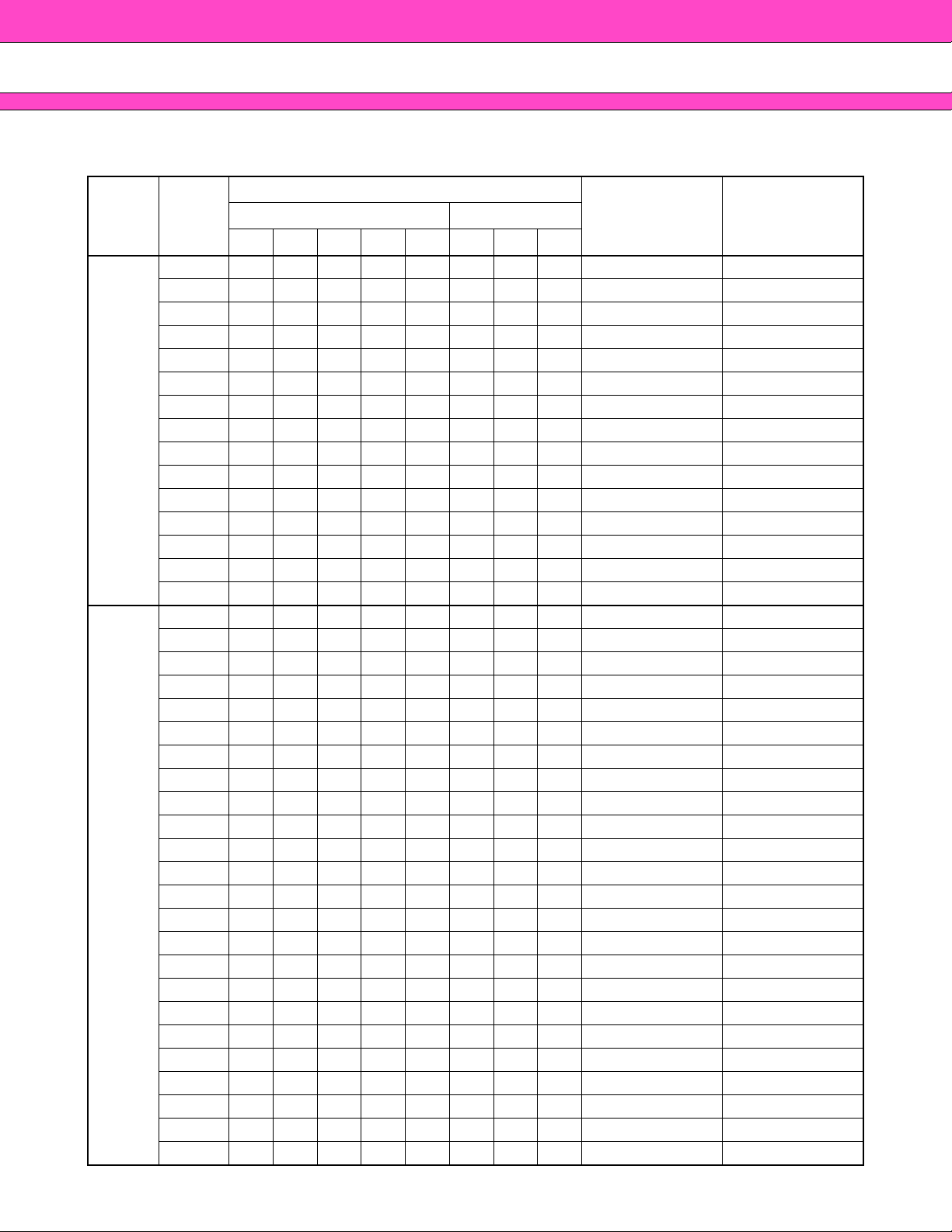

Table 6 Flash Memory Command Definitions

85

Command

Sequence

Read/Reset (Note 1) 1 XXXH F0H

Read/Reset

(Note 1)

Autoselect

Program

Chip Erase

Sector Erase

Sector Erase Suspend 1 BA B0H

Sector Erase Resume 1 BA 30H

Set to

Fast Mode

Fast Program

(Note 2)

Reset from

Fast Mode

(Note 2)

Extended

Sector Group

Protection

(Note 3)

Query

(Note 4)

Hi-ROM Entry

Hi-ROM

Program

(Note 5)

Hi-ROM Erase

(Note 5)

Hi-ROM Exit

(Note 5)

Word

Byte AAAH 555H AAAH

Word

Byte AAAH 555H

Word

Byte AAAH 555H AAAH

Word

Byte AAAH 555H AAAH AAAH 555H AAAH

Word

Byte AAAH 555H AAAH AAAH 555H

Word

Byte AAAH 555H AAAH

Word

Byte

Word

Byte

Word

Byte

Word

Byte AAH

Word

Byte AAAH 555H AAAH

Word

Byte AAAH 555H AAAH

Word

Byte AAAH 555H AAAH AAAH 555H

Word

Byte AAAH 555H

Bus

Write

Cycles

Req’d

First Bus

Write Cycle

Addr. Data Addr. Data Addr. Data Addr. Data Addr. Data Addr. Data

555H

3

555H

3

555H

4

555H

6

555H

6

555H

3

2 XXXH A0H PA PD

2 BA 90H XXXH

4 XXXH 60H SPA 60H SPA 40H SPA SD

1

555H

3

555H

4

555H

6

555H

4

AAH

AAH

AAH

AAH

AAH

AAH

55H

98H

AAH

AAH

AAH

AAH

Second Bus

Write Cycle

2AAH

2AAH

2AAH

2AAH

2AAH

2AAH

2AAH

2AAH

2AAH

2AAH

55H

55H

55H

55H

55H

55H

F0H

(Note6)

55H

55H

55H

55H

Third Bus

Write Cycle

555H

(BA)

555H

(BA)

AAAH

555H

555H

555H

555H

555H

555H

555H

(HRBA)

555H

(HRBA)

AAAH

Fourth Bus

Read/Write

Cycle

F0H RA RD

90H

A0H PA PD

80H

80H

20H

88H

A0H PA PD

80H

90H XXXH 00H

555H

AAH

555H

AAH

555H

AAH

Fifth Bus

Write Cycle

2AAH

2AAH

2AAH

Sixth Bus

Write Cycle

555H

55H

55H SA 30H

55H HRA 30H

10H

23

MB84VD2118XA

/MB84VD2119XA

-85

-85

Notes : 1 : Both Read/Reset commands are functionally equivalent, resetting the device to the read mode.

2 : This command is valid while Fast Mode.

3 : This command is valid while RESET

4 : The valid Address is A

0 to A6.

5 : This command is valid while Hi-ROM

= VID.

mode.

6 : The data “00H” is also acceptable.

Address bits A

12 to A19 = X = “H” or “L” for all address commands except for Program Address (PA) ,

Sector Address (SA) , and Bank Address (BA) .

Bus operations are defined in Table 2 “User Bus Operations”.

RA = Address of the memory location to be read.

PA = Address of the memory location to be programmed.

Addresses are latched on the falling edge of the write pulse.

SA = Address of the sector to be erased. The combination of A

19, A18, A17, A16, A15, A14, A13, and A12 will

uniquely select any sector.

BA = Bank address (A

SPA = Sector group address to be protected. Set sector group address (SGA) and (A

15 to A19)

6, A1, A0) = (0, 1, 0).

HRA = Address of the Hidden-ROM area.

SPA = Sector group address to be protected. Set sector group address (SGA) and (A

6, A1, A0) = (0, 1, 0).

HRA = Address of the Hidden-ROM area.

MB84VD2118XA (Top Boot Type) Word mode: 0F8000H to 0FFFFFH

Byte mode: 1F0000H to 1FFFFFH

MB84VD2119XA (Bottom Boot Type) Word mode: 000000H to 007FFFH

Byte mode: 000000H to 00FFFFH

HRBA = Bank addrss of the Hidden-ROM area.

MB84VD2118XA (Top Boot Type) : A

MB84VD2119XA (Bottom Boot Type) : A

15

= A16 = A17 = A18 = A

15

= A16 = A17 = A18 = A

19

= A20 = 1

19

= A20 = 0

RD = Data read from location RA during read operation.

PD = Data to be programmed at location PA.

SD = Sector protection verify data. Output 01H at protected sector addresses and output 00H

at unprotectedsector addresses.

The system should generate the following address patterns;

Word mode : 555H or 2AAH to addresses A

0 to A10

Byte mode : AAAH or 555H to addresses A -1 and A0 to A10

24

MB84VD2118XA-85/MB84VD2119XA-

ABSOLUTE MAXIMUM RATINGS

■■■■

85

Parameter Symbol

Unit

Min. Max.

Storage Temperature Tstg −55 +125 °C

Rating

Ambient Temperature with Power

Applied

Voltage with Respect to Ground All

pins except A

WP

/ACC (Note 1)

V

CCf/VCCs Supply (Note 1) VCCf, VCCs −0.3 +4.0 V

A

9 and OE (Note 2) VIN −0.3 +13.0 V

RESET

9, OE, RESET,

(Note 2) VIN −0.5 +13.0 V

T

A −25 +85 °C

CCf + 0.4

V

IN, VOUT −0.3

V

V

CCs + 0.4

V

WP/ACC (Note 3) VIN −0.5 +10.5 V

WARNING: Semiconductor devices can be permanently damaged by application of stress (voltage, current,

temperature, etc.) in excess of absolute maximum ratings. Do not exceed these ratings.

Notes 1. Minimum DC voltage on input or I/O pins is –0.3 V. During voltage transitions, input or I/O pins may

undershoot V

+0.4 V or V

SS to –2.0 V for periods of up to 20 ns. Maximum DC voltage on input or I/O pins is VCCf

CCs+0.4 V . During voltage tr ansitions, input or I/O pins may ov ershoot to VCCf+2.0 V or VCCs+2.0

V for periods of up to 20 ns.

2. Minimum DC input voltage on A

–0.5 V. During voltage transitions, A

9 and OE pin is –0.3 V. Minimum DC input voltage on RESET pin is

9, OE, and RESET pins may undershoot VSS to –2.0 V f or periods of

up to 20 ns.

Voltage difference between input and supply voltage (VIN-V

Maximum DC input voltage on A

9, OE, and RESET pins is +13.0 V which may overshoot to 14.0 V for

CCf or VCCs) does not exceed 9.0 V.

periods of up to 20 ns.

3. Minimum DC input voltage on WP

undershoot Vss to –2.0 V for periods of up to 20 ns. Maximum DC input v oltage on WP

V which may overshoot to 12.0 V for periods of up to 20 ns, when V

/ACC pin is –0.5 V. During voltage transitions, WP/ACC pin may

/ACC pin is +10.5

CCf is applied.

RECOMMENDED OPERATING CONDITIONS

■■■■

Value

Parameter Symbol

Unit

Min. Max.

Ambient Temperature T

V

CCf/VCCs Supply Voltages VCCf, VCCs +2.7 +3.6 V

A −25 +85 °C

Operating ranges define those limits between which the functionality of the device is guaranteed.

WARNING: The recommended operating conditions are required in order to ensure the normal operation of the

semiconductor device. All of the device’s electrical characteristics are warranted when the device is

operated within these ranges.

Always use semiconductor devices within their recommended operating condition ranges. Operation

outside these ranges may adversely affect reliability and could result in device failure.

No warranty is made with respect to uses, operating conditions, or combinations not represented on

the data sheet. Users considering application outside the listed conditions are advised to contact their

FUJITSU representatives beforehand.

25

MB84VD2118XA

ELECTRICAL CHARACTERISTICS

■■■■

/MB84VD2119XA

-85

-85

1. DC Characteristics

Parameter

Symbol

I

LI Input Leakage Current VIN = VSS to VCCf, VCCs −1.0 +1.0 µA

I

LO Output Leakage Current VOUT = VSS to VCCf, VCCs −1.0 +1.0 µA

ILIT

Parameter Description Test Conditions Min. Typ. Max. Unit

RESET Inputs Leakage

Current

VCCf = VCCf Max, VCCs = VCCs Max,

RESET

= 12.5V

35 µA

I

CC1f

I

LIA

ACC Input Leakage

Current

Flash V

CC Active Current

(Read)

(Note 1)

CC Active Current

ICC2f

Flash V

(Program/Erase)

(Note 2)

CC Active Current

I

CC3f

Flash V

(Read-While-Program)

(Note 5)

CC Active Current

I

CC4f

Flash V

(Read-While-Erase)

(Note 5)

CC Active Current

I

CC5f

Flash V

(Erase-Suspend-Program)

I

CC1sSRAM VCC Active Current

VCCf = VCCf Max, VCCs = VCCs Max,

WP

/ACC = VACC Max

20 mA

tCYCLE = 5 MHz Byte 13

t

CEf = VIL,

OE

= VIH

CE

f = VIL, OE = VIH 35 mA

CYCLE = 5 MHz Word 15

t

CYCLE = 1 MHz Byte 7

t

CYCLE = 1 MHz Word 7

Byte 48

CE

f = VIL, OE = VIH

Word 50

Byte 48

CE

f = VIL, OE = VIH

Word 50

CE

f = VIL, OE = VIH 35 mA

CCs = VCC Max.,

V

CE1

s = VIL,

CE2s = V

IH

tCYCLE = 10 MHz 40 mA

mA

mA

mA

mA

26

I

CC2sSRAM VCC Active Current

SB1f

I

ISB2f

I

SB3f

Flash VCC Standby Current

Flash VCC Standby Current (RESET

Flash V

)

CC Current

(Automatic Sleep Mode)

(Note 3)

I

SB1s

I

SB2s

SRAM VCC Standby

Current

SRAM VCC Standby

Current

s = 0.2 V,

CE1

CE2s = V

0.2 V,

CCs −

CYCLE = 10 MHz 40 mA

t

CYCLE = 1 MHz 8mA

t

VCCf = VCC Max., CEf = VCCf ± 0.3 V

RESET

WP

V

WP

= VCCf ± 0.3 V,

/ACC = VCCf ± 0.3 V

CCf = VCC Max., RESET = VSS ± 0.3 V

/ACC = VCCf ± 0.3 V

15µA

15µA

VCCf = VCC Max., CEf = VSS ± 0.3 V

RESET

WP

V

CE1s ≥ VCCs − 0.2V,

CE2s ≥ V

= VCCf ± 0.3 V,

/ACC = VCCf ± 0.3 V

IN = VCCf ± 0.3 V or VSS ± 0.3 V

CCs − 0.2V

15µA

0.2 7 µA

CE2s ≤ 0.2V 0.2 7 µA

(Continued)

Parameter

Symbol

V

IL Input Low Level −0.3 0.5 V

MB84VD2118XA-85/MB84VD2119XA-

(Continued)

Parameter Description Test Conditions Min. Typ. Max. Unit

85

V

IH Input High Level 2.4

VCC +

0.3*

V

Voltage for Sector

V

ID

Protection, and Temporary

Sector Unprotection

(RESET

) (Note 4)

11.5 12.5 V

Voltage for Program

V

ACC

Acceleration (WP

/ACC)

8.5 9.0 9.5 V

(Note4)

V

OL Output Low Voltage Level

VOH Output High Voltage Level

V

LKO

Flash Low VCCf Lock-Out

Voltage

VCCf = VCCf Min., VCCs = VCCs Min.,

OL

I

= 1.0 mA

VCCf = VCCf Min., VCCs = VCCs Min.,

OH

I

= −0.5 mA

2.3 2.5 V

0.4 V

2.4 V

*: VCC indicates lower of VCCf or VCCs.

Notes : 1. The ICC current listed includes both the DC operating current and the frequency dependent component.

2. I

CC active while Embedded Algorithm (program or erase) is in progress.

3. Automatic sleep mode enables the low power mode when address remain stable for 150ns.

4. Applicable for only V

CCf applying.

5. Embedded Alogorithm (program or erase) is in progress. (@5MHz)

27

MB84VD2118XA

2. AC Characteristics

•

Timing

CE

Parameter

Symbols

JEDEC Standard

/MB84VD2119XA

-85

Description Test Setup -85 Unit

-85

t

•

Timing Diagram for alternating SRAM to Flash

CCR CE Recover Time Min. 0 ns

CEf

CE1s

CE2s

tCCR

tCCR

tCCR

tCCR

28

MB84VD2118XA-85/MB84VD2119XA-

•

Read Only Operations Characteristics (Flash)

Parameter

Symbols

Description

Test

Setup

JEDEC Standard Min. Max.

t

AVAV tRC Read Cycle Time 85 ns

-85

(Note)

85

Unit

t

AVQV tACC Address to Output Delay

t

ELQV tCEf Chip Enable to Output Delay OE = VIL 85 ns

CEf = VIL

OE = VIL

85 ns

tGLQV tOE Output Enable to Output Delay 35 ns

t

EHQZ tDF Chip Enable to Output High-Z 30 ns

t

GHQZ tDF Output Enable to Output High-Z 30 ns

tAXQX tOH

t

READY RESET Pin Low to Read Mode 20 µs

Output Hold Time From Addresses,

CE

f or OE, Whichever Occurs First

0 ns

Note : Test Conditions − Output Load : 1 TTL gate and 30 pF

Input rise and fall times : 5 ns

Input pulse levels : 0.0 V to 3.0 V

Timing measurement reference level

Input : 1.5 V

Output : 1.5 V

29

MB84VD2118XA

/MB84VD2119XA

-85

-85

•

Read Cycle (Flash)

Addresses

CEf

OE

WE

tRC

Addresses Stable

tACC

tOE

tOEH

tCEf

tDF

DQ

Addresses

CEf

RESET

DQ

HIGH-Z HIGH-Z

tRC

Addresses Stable

tRH

HIGH-Z

tACC

tCEftRHtRP

Output Valid

tOH

Output Valid

30

MB84VD2118XA-85/MB84VD2119XA-

•

Erase/Program Operations (Flash)

Parameter Symbols

Description

JEDEC Standard Min. Typ. Max.

t

AVAV tWC Write Cycle Time 85 ns

t

AVWL tAS Address Setup Time (WE to Addr.) 0 ns

-85

85

Unit

t

ASO Address Setup Time to CEf Low During Toggle Bit Polling 15 ns

tWLAX tAH Address Hold Time (WE to Addr.) 45 ns

t

t

DVWH tDS Data Setup Time 35 ns

AHT

Address Hold Time from CEf or OE High During Toggle Bit

Polling

0 ns

tWHDX tDH Data Hold Time 0 ns

t

OES Output Enable Setup Time 0 ns

Read 0 ns

t

t

t

OEH Output Enable Hold Time

Toggle and Data

CEPH CEf High During Toggle Bit Polling 20 ns

OEPH OE High During Toggle Bit Polling 20 ns

Polling 10 ns

tGHEL tGHEL Read Recover Time Before Write (OE to CEf) 0 ns

t

GHWL tGHWL Read Recover Time Before Write (OE to WE) 0 ns

t

WLEL tWS WE Setup Time (CEf to WE) 0 ns

t

ELWL tCS CEf Setup Time (WE to CEf) 0 ns

tEHWH tWH WE Hold Time (CEf to WE) 0 ns

t

WHEH tCH CEf Hold Time (WE to CEf) 0 ns

t

WLWH tWP Write Pulse Width 35 ns

tELEH tCP CEf Pulse Width 35 ns

t

WHWL tWPH Write Pulse Width High 30 ns

t

EHEL tCPH CEf Pulse Width High 30 ns

Byte Programming Operation 8 µs

WHWH1 tWHWH1

t

Word Programming Operation 16 µs

t

WHWH2 tWHWH2 Sector Erase Operation (Note 1) 1 s

(Continued)

31

MB84VD2118XA

/MB84VD2119XA

-85

-85

(Continued)

Parameter Symbols

-85

Description

JEDEC Standard Min. Typ. Max.

t

VCS VCCf Setup Time 50 µs

Unit

t

t

t

VLHT Voltage Transition Time (Note 2) 4 µs

VIDR Rise Time to VID (Note 2) 500 ns

VACCR Rise Time to VACC 500 ns

tRB Recover Time from RY/BY 0 ns

t

t

RP RESET Pulse Width 500 ns

EOE Delay Time from Embedded Output Enable 85 ns

tRH RESET Hold Time Before Read 200 ns

t

t

BUSY Program/Erase Valid to RY/BY Delay 90 ns

TOW Erase Time-out Time (Note 3) 50 µs

tSPD Erase Suspend Transition Time (Note 4) 20 µs

Notes : 1. This does not include the preprogramming time.

2. This timing is for Sector Protection Operation.

3. The time between writes must be less than “t

erasure will start. A time-out or “t

TOW” from the rising edge of last CEf or WE whichever happens first will

TOW” otherwise that command will not be accepted and

initiate the execution of the Sector Erase command (s) .

4. When the Erase Suspend command is written during the Sector Erase operation, the device will take a

maximum of “t

SPD” to suspend the erase operation.

32

MB84VD2118XA-85/MB84VD2119XA-

•

Write Cycle (WE control) (Flash)

85

Addresses

3rd Bus Cycle

555H

tWC

PA PA

tAS tAH

Data Polling

CEf

tCS

tCH

OE

tGHWL

tWP

t

WPH

tWHWH1

WE

tDS

tDH

DQ

A0H PD DQ

7 DOUT DOUT

Notes : 1. PA is address of the memory location to be programmed.

2. PD is data to be programmed at byte address.

3. DQ

7 is the output of the complement of the data written to the device.

4. D

OUT is the output of the data written to the device.

5. Figure indicates last two bus cycles out of four bus cycle sequence.

6. These waveforms are for the × 16 mode. (The addresses differ from × 8 mode.)

tRC

tCEf

tOE

tOH

33

MB84VD2118XA

/MB84VD2119XA

-85

-85

•

Write Cycle (CE

f control) (Flash)

Addresses

WE

OE

CEf

DQ

3rd Bus Cycle

tWS

tGHEL

Data Polling

555H

tWC

tCP

tDS

A0H PD DQ

PA PA

tAS tAH

tWH

tCPH

tDH

tWHWH1

7 DOUT

Notes : 1. PA is address of the memory location to be programmed.

2. PD is data to be programmed at byte address.

3. DQ

7 is the output of the complement of the data written to the device.

4. D

OUT is the output of the data written to the device.

5. Figure indicates last two bus cycles out of four bus cycle sequence.

6. These waveforms are for the × 16 mode. (The addresses differ from × 8 mode.)

34

MB84VD2118XA-85/MB84VD2119XA-

•

AC Waveforms Chip/Sector Erase Operations (Flash)

Addresses

CEf

555H 2AAH 2AAH555H 555H

t

WC

tAS tAH

SA

85

*

tCS

tCH

OE

tGHWL

tWPHtWP

WE

tDS

tDH

AAH 55H 80H AAH 55H

DQ

tVCS

V

CCf

* : SA is the sector address for Sector Erase. Addresses = 555H for Chip Erase.

Note : These wav eforms are for the × 16 mode. (The addresses differ from × 8 mode .)

30H for Sector Erase

10H/

30H

35

MB84VD2118XA

/MB84VD2119XA

-85

-85

•

AC Waveforms for Data

CEf

OE

WE

DQ7

DQ

(DQ

0 to DQ6)

Polling during Embedded Algorithm Operations (Flash)

tCH tOE

tOEH

tCEf

*

Data In

Data In

DQ7

tWHWH1 or 2

DQ0 to DQ6 = Output Flag

DQ7 =

Valid Data

DQ0 to DQ6

Valid Data

tDF

High-Z

High-Z

tBUSY

RY/BY

* : DQ7 = Valid Data (The device has completed the Embedded operation.)

tEOE

36

MB84VD2118XA-85/MB84VD2119XA-

•

AC Waveforms for Toggle Bit during Embedded Algorithm Operations (Flash)

Addresses

tAHT

tAStAHT tASO

CEf

tCEPH

85

WE

OE

DQ6/DQ2

RY/BY

tOEH

tDH

Data

tBUSY

tOEPH

tOE tCEf*

Toggle

Data

Toggle

Data

Toggle

Data

tOEH

Toggling

* : DQ6 stops toggling (The device has completed the Embedded operation) .

Stop

Output

Valid

37

MB84VD2118XA

•

Back-to-back Read/Write Timing Diagram (Flash)

Read Command Read Command Read Read

tRC

/MB84VD2119XA

-85

tWC tRC tWC tRC

-85

tRC

Address

BA1

tAS

BA2

(555H)

tAH

BA1 BA1

tACC

tCEf

BA2

(PA)

BA2

(PA)

tAS

tAHT

CEf

t

OE

tCEPH

OE

tGHWL tOEH tDF

tWP

WE

DQ

Valid

Output

tDS

Valid

Input

(A0H)

tDH

Valid

Output

tDF

Valid

Input

(PD)

Valid

Output

Status

Note : This is example of Read for Bank 1 and Embedded Algorithm (program) for Bank 2.

BA1 : Address of Bank 1.

BA2 : Address of Bank 2.

38

MB84VD2118XA-85/MB84VD2119XA-

85

•

RY/BY

•

RESET

Timing Diagram during Write/Erase Operations (Flash)

CEf

The rising edge of the last write pulse

WE

RY/BY

, RY/BY Timing Diagram (Flash)

WE

Entire programming

or erase operations

t

BUSY

RESET

RY/BY

tRP

tRB

tREADY

39

MB84VD2118XA

•

Temporary Sector Unprotection (Flash)

/MB84VD2119XA

-85

-85

VCCf

V

3 V

RESET

CEf

WE

RY/BY

tVIDR

tVCS

ID

tVLHT

Program or Erase Command Sequence

Unprotection Period

tVLHT

3 V

tVLHT

40

MB84VD2118XA-85/MB84VD2119XA-

•

Extended Sector Protection (Flash)

VCCf

tVCS

85

RESET

Addresses

A

0

A1

A6

CEf

OE

tVIDR

tVLHT

tWC tWC

SGAx SGAx SGAy

TIME - OUT

tWP

WE

Data

60H 60H 40H 01H 60H

SGAx : Sector Group Address to be protected

SGAy : Next Group Sector Address to be protected

TIME-OUT : Time-Out window = 250 µs (min.)

t

OE

41

MB84VD2118XA

• Accelerated Program (Flash)

CC

V

VACC

3 V

WP/ACC

CE

WE

tVACCR

tVCS

/MB84VD2119XA

-85

-85

tVLHT

3 V

RY/BY

tVLHT

Program or Erase Command Sequence

Acceleration period

tVLHT

42

MB84VD2118XA-85/MB84VD2119XA-

85

•

Read Cycle (SRAM)

Parameter

Symbol

t

RC Read Cycle Time 85 ns

t

AA Address Access Time 85 ns

t

CO1 Chip Enable (CE1s) Access Time 85 ns

t

CO2 Chip Enable (CE2s) Access Time 85 ns

Parameter Description Min. Max. Unit

tOE Output Enable Access Time 45 ns

t

BA LBS, UBS to Output Valid 85 ns

t

COE Chip Enable (CE1s Low and CE2s High) to Output Active 5 ns

tOEE Output Enable Low to Output Active 0 ns

t

BE UBS, LBS Enable Low to Output Active 0 ns

t

OD Chip Enable (CE1s High or CE2s Low) to Output High-Z 35 ns

tODO Output Enable High to Output High-Z 35 ns

t

BD UBS, LBS Output Enable to Output High-Z 50 ns

t

OH Output Data Hold Time 10 ns

43

MB84VD2118XA

•

Read Cycle (Note) (SRAM)

ADDRESSES

CE1s

/MB84VD2119XA

-85

tRC

tAA

tCO1

-85

tOH

LBS, UBS

Note : WE

tCOE

CE2s

OE

tCOE

DQ

remains HIGH for the read cycle.

tCO2

tOEE

tBE

tOE

tBA

tOD

tOD

tODO

tBD

VALID DATA OUT

44

MB84VD2118XA-85/MB84VD2119XA-

•

Write Cycle (SRAM)

Parameter

Symbol

t

WC Write Cycle Time 85 ns

t

WP Write Pulse Width 55 ns

t

CW Chip Enable to End of Write 70 ns

t

AW Address valid to End of Write 70 ns

tBW UBS, LBS to End of Write 55 ns

t

AS Address Setup Time 0 ns

t

WR Write Recovery Time 0 ns

tODW WE Low to Output High-Z 35 ns

t

OEW WE High to Output Active 0 ns

t

DS Data Setup Time 35 ns

tDH Data Hold Time 0 ns

Parameter Description Min. Max. Unit

85

45

MB84VD2118XA

/MB84VD2119XA

-85

-85

•

Write Cycle (Note 3) (WE

Addresses

WE

CE1s

CE2s

LBS, UBS

control) (SRAM)

tAS

tWC

tAW

tCW

tCW

tBW

tWP

tWR

DOUT

DIN

tODW

Note 1 Note 2

tDS tDH

tOEW

Note 4Note 4 VALID DATA IN

Notes : 1. If CE1s goes LOW (or CE2s goes HIGH) coincident with or after WE goes LOW, the

output will remain at high impedance.

2. If CE1

s goes HIGH (or CE2s goes LOW) coincident with or bef ore WE goes HIGH, the

output will remain at high impedance.

3. If OE

is HIGH during the write cycle, the outputs will remain at high impedance.

4. Because I/O signals may be in the output state at this time, input signals of reverse

polarity must not be applied.

46

MB84VD2118XA-85/MB84VD2119XA-

85

• Write Cycle (Note 1) (CE1

Addresses

WE

CE1s

CE2s

s control) (SRAM)

tAS

tWC

tAW

tCW

tCW

tBW

tWP

tWR

LBS, UBS

tBE

tODW

tDS tDH

VALID DATA IN

DOUT

DIN

tCOE

Note 2

Notes : 1. If OE is HIGH during the write cycle, the outputs will remain at high impedance.

2. Because I/O signals may be in the output state at this time, input signals of reverse

polarity must not be applied.

47

MB84VD2118XA

•

Write Cycle (Note 1) (CE2s Control) (SRAM)

Addresses

/MB84VD2119XA

-85

-85

tWC

LB

WE

CE1s

CE2s

S, UBS

DOUT

tAS tWR

tBE

tWP

tCW

tAW

tCW

tBW

tODWtCOE

48

DIN

DS

t

Note 2 VALID DATA IN

tDH

Notes : 1. If OE is HIGH during the write cycle, the outputs will remain at high impedance.

2. Because I/O signals may be in the output state at this time, input signals of reverse

polarity must not be applied.

MB84VD2118XA-85/MB84VD2119XA-

85

• Write Cycle (Note 1) (LB

Addresses

WE

CE1s

CE2s

s, UBs Control) (SRAM)

tWC

tCW

tCW

tAW

tBWtAS

tWP

tWR

LBS, UBS

tBE

tCOE

D

OUT

DIN

Note 2

tODW

DS

t

VALID DATA IN

tDH

Notes : 1. If OE is HIGH during the write cycle, the outputs will remain at high impedance.

2. Because I/O signals may be in the output state at this time, input signals of reverse

polarity must not be applied.

49

MB84VD2118XA

/MB84VD2119XA

-85

-85

ERASE AND PROGRAMMING PERFORMANCE

■■■■

Parameter

Sector Erase Time 110s

Byte Programming Time 8 300 µs

Word Programming Time 16 360 µs

Chip Programming Time 50 s

Erase/Program Cycle 100,000 cycle

DATA RETENTION CHARACTERISTICS

■■■■

Parameter

Symbol

DH Data Retention Supply Voltage 1.5 3.6 V

V

IDDS2 Standby Current VDH = 3.0 V 0.2 7* µA

t

CDR Chip Deselect to Data Retention Mode Time 0 ns

Min. Typ. Max.

Parameter Description Min. Typ. Max. Unit

Limits

(SRAM)

(Flash)

Unit Comment

Excludes programming time

prior to erasure

Excludes system-level

overhead

Excludes system-level

overhead

Excludes system-level

overhead

t

R Recovery Time tRC ns

Note : t

* : 4 µA Max. at TA ≤ 60 °C, 1 µA Max. at TA ≤ 40 °C

RC : Read cycle time

•

s Controlled Data Retention Mode (Note 1)

CE1

VCCs

2.7 V

V

IH

VDH

CE1s

GND

DATA RETENTION MODE

VCCS −0.2 V

See Note 2See Note 2

t

RtCDR

50

MB84VD2118XA-85/MB84VD2119XA-

•

CE2s Controlled Data Retention Mode (Note 3)

85

VCCs

2.7 V

VDH

VIH

VIL

GND

Notes : 1. In CE1

to 0.2 V during data retention mode. Other input and input/output pins can be used between −0.3 V and

Vccs + 0.3 V.

2. When CE1

transition of V

3. In CE2s controlled data retention mode, input and input/output pins can be used between −0.3 V and

Vccs + 0.3 V.

DATA RETENTION MODE

CE2s

tCDR tR

0.2 V

s controlled data retention mode, input level of CE2s should be fixed Vccs to Vccs − 0.2 V or Vss

s is operating at the VIH min. level (2.2 V) , the standby current is given by ISB1s during the

CCs from 3.6 to 2.2 V.

PIN CAPACITANCE

■■■■

Parameter

Symbol

IN Input Capacitance VIN = 01114pF

C

C

OUT Output Capacitance VOUT = 01216pF

Parameter Description Test Setup Typ. Max. Unit

CIN2 Control Pin Capacitance VIN = 01416pF

C

IN3 WP/ACC Pin Capacitance VIN = 01720pF

Note : Test conditions TA = 25 °C, f = 1.0 MHz

HANDLING OF PACKAGE

■■■■

Please handle this package carefully since the sides of packages are right angle.

CAUTION

■■■■

1. The high voltage (VID) can not apply to address pins and control pins except RESET. Therefore, it can not

use autoselect and sector protect function by applying the high voltage (V

2. For the sector protection, since the high voltage (V

ID) can be applied to the RESET, it can be protected the

ID) to specific pins.

sector using “Extended sector protect” command.

51

MB84VD2118XA

ORDERING INFORMATION

■■■■

MB84VD2118 X A -85 -PBS

-85

/MB84VD2119XA

PACKAGE TYPE

PBS = 69-ball FBGA

PTS = 56-pin TSOP (I)

SPEED OPTION

See Product Selector Guide.

-85

Device Revision

Bank Size

1 = 0.5 Mbit / 15.5 Mbit

2 = 2 Mbit / 14 Mbit

3 = 4 Mbit / 12 Mbit

4 = 8 Mbit / 8 Mbit

DEVICE NUMBER/DESCRIPTION

16Mega-bit (2M × 8-bit or 1M × 16-bit) Dual Operation Flash Memory

3.0 V-only Read, Program, and Erase

4Mega-bit (512K × 8-bit) SRAM

BOOT CODE SECTOR ARCHITECTURE

84VD2118 = Top sector

84VD2119 = Bottom sector

52

PACKAGE DIMENSIONS

■■■■

69-ball plastic FBGA

(BGA-69P-M02)

11.00±0.10(.433±.004)

INDEX-MARK AREA

0.10(.004)

MB84VD2118XA-85/MB84VD2119XA-

7.20(.283)

+0.15

–0.10

8.00±0.10

(.315±.004)

1.25

.049 –.004

0.38±0.10

(.015±.004)

5.60(.220)

7.20(.283)

(Mounting height)

+.006

(Stand off)

0.80(.031)

REF

JK

5.60(.220)REF

0.80(.031)

+0.10

–0.05

69-Ø0.45

+.004

69-Ø0.18 –.002

ABCDEFGH

INDEX BALL

0.08(.003)

10

9

8

7

6

5

4

3

2

1

M

85

C

1999 FUJITSU LIMITED B69002S-1C-1

Dimension in mm (inches)

(Continued)

53

MB84VD2118XA

(Continued)

56-pin plastic TSOP (I)

(FPT-56P-M04)

14.00±0.20(.551±.008)

12.40±0.10(.488±.004)

INDEX

/MB84VD2119XA

-85

0.40(.016)

TYP

12.00±0.10

(.472±.004)

-85

+0.05

–0.03

0.145

+.002

–.001

.006

C

1998 FUJITSU LIMITED F56004S-1C-1

0.08(.003)

"A"

0.10±0.05

(.004±.002)

(Stand off)

0.18±0.035

(.007±.001)

1.15±0.05

(.045±.002)

(Mounting height)

0.10(.004)

M

Details of "A" part

0.25(.010)

0°~8°

0.45/0.75

(.018/.030)

Dimension in mm (inches)

54

MB84VD2118XA-85/MB84VD2119XA-

FUJITSU LIMITED

For further information please contact:

Japan

FUJITSU LIMITED

Corporate Global Business Support Division

Electronic Devices

KAWASAKI PLANT, 4-1-1, Kamikodanaka,

Nakahara-ku, Kawasaki-shi,

Kanagawa 211-8588, Japan

Tel: +81-44-754-3763

Fax: +81-44-754-3329

http://www.fujitsu.co.jp/

North and South America

FUJITSU MICROELECTRONICS, INC.

3545 North First Street,

San Jose, CA 95134-1804, U.S.A.

Tel: +1-408-922-9000

Fax: +1-408-922-9179

Customer Response Center

Mon. - Fri.: 7 am - 5 pm (PST)

Tel: +1-800-866-8608

Fax: +1-408-922-9179

http://www.fujitsumicro.com/

Europe

FUJITSU MICROELECTRONICS EUR OPE GmbH

Am Siebenstein 6-10,

D-63303 Dreieich-Buchschlag,

Germany

Tel: +49-6103-690-0

Fax: +49-6103-690-122

http://www.fujitsu-fme.com/

Asia Pacific

FUJITSU MICROELECTRONICS ASIA PTE. LTD.

#05-08, 151 Lorong Chuan,

New Tech Park,

Singapore 556741

Tel: +65-281-0770

Fax: +65-281-0220

http://www.fmap.com.sg/

Korea

FUJITSU MICROELECTRONICS K OREA LTD.

1702 KOSMO TOWER, 1002 Daechi-Dong,

Kangnam-Gu,Seoul 135-280

Korea

Tel: +82-2-3484-7100

Fax: +82-2-3484-7111

All Rights Reserved.

The contents of this document are subject to change without notice.

Customers are advised to consult with FUJITSU sales

representatives before ordering.

The information and circuit diagrams in this document are

presented as examples of semiconductor device applications, and

are not intended to be incorporated in devices for actual use. Also,

FUJITSU is unable to assume responsibility for infringement of

any patent rights or other rights of third parties arising from the use

of this information or circuit diagrams.

The contents of this document may not be reproduced or copied

without the permission of FUJITSU LIMITED.

FUJITSU semiconductor devices are intended for use in standard

applications (computers, office automation and other office

equipments, industrial, communications, and measurement

equipments, personal or household devices, etc.).

CAUTION:

Customers considering the use of our products in special

applications where failure or abnormal operation may directly

affect human lives or cause physical injury or property damage, or

where extremely high levels of reliability are demanded (such as

aerospace systems, atomic energy controls, sea floor repeaters,

vehicle operating controls, medical devices for life support, etc.)

are requested to consult with FUJITSU sales representatives before

such use. The company will not be responsible for damages arising

from such use without prior approval.

Any semiconductor devices have inherently a certain rate of failure.

You must protect against injury, damage or loss from such failures

by incorporating safety design measures into your facility and

equipment such as redundancy, fire protection, and prevention of

over-current levels and other abnormal operating conditions.

If any products described in this document represent goods or

technologies subject to certain restrictions on export under the

Foreign Exchange and Foreign Trade Control Law of Japan, the

prior authorization by Japanese government should be required for

export of those products from Japan.

85

F0007

FUJITSU LIMITED Printed in Japan

Loading...

Loading...