Page 1

FUJITSU SEMICONDUCTOR

CONTROLLER MANUAL

CM44-10136-1E

TM

F2MC

16-BIT MICROCONTROLLER

-16LX

MB90360 Series

HARDWARE MANUAL

Page 2

Page 3

TM

F2MC

16-BIT MICROCONTROLLER

-16LX

MB90360 Series

HARDWARE MANUAL

FUJITSU LIMITED

Page 4

Page 5

PREFACE

■ Objectives and intended reader

Thank you very much for your continued patronage of Fujitsu semiconductor products.

The MB90360 series has b een developed as a ge neral-purpose version of the F

which is an original 16-bit single-chip microcontroller compatible with the Application Specific IC

(ASIC).

This manual explains the functions and operation of the MB90360 series for engineers who actually

use the MB90360 series to design products. Please read this manual first.

■ Tr ademark

2

F

MC, an abbreviation of FUJIT SU Flexible Microco ntroller, is a registered trademark of FUJITSU

Ltd.

Embedded Algorithm is a registered trademark of Advanced Micro Devices Inc.

■ Structure of this preliminary manual

This manual contains the following 26 chapters and appendix.

2

MC-16LX family,

CHAPTER 1 OVERVIEW

2

The MB90360 Series is a family member of the F

CHAPTER 2 CPU

This chapter explains the CPU.

CHAPTER 3 INTERRUPTS

This chapter explains the interrupts and function and op eration of the extended intelligent I/O

service in the MB90360 series.

CHAPTER 4 DELAYED INTERRUPT GENERATION MODULE

This chapter explains the functions and operations of the delayed interrupt generation module.

CHAPTER 5 CLOCKS

This chapter explains the clocks used by MB90360 series microcontrollers.

CHAPTER 6 CLOCK SUPERVISOR

This chapter explain s the function and the operation of the cloc k supervisor. Only the product

with built-in clock supervisor of the MB90360 series is valid to this function.

CHAPTER 7 RESETS

This chapter describes resets for the MB90360-series microcontrollers.

CHAPTER 8 LOW-POWER CONSUMPTION MODE

MC-16LX micro controllers.

This chapter explains the low-power consumption mode of MB90360 series microcontrollers.

CHAPTER 9 MEMORY ACCESS MODES

This chapter explains the functions and operations of the memory access modes.

i

Page 6

CHAPTER 10 I/O PORTS

This chapter explains the functions and operations of the I/O ports.

CHAPTER 11 TIMEBASE TIMER

This chapter explains the functions and operations of the timebase timer.

CHAPTER 12 WATCHDOG TIMER

This chapter describes the function and operation of the watchdog timer.

CHAPTER 13 16-Bit I/O TIMER

This chapter explains the function and operation of the 16- bit I/O timer.

CHAPTER 14 16-BIT RELOAD TIMER

This chapter describes the functions and operation of the 16-bit reload timer.

CHAPTER 15 WATCH TIMER

This chapter describes the functions and operations of the watch timer.

CHAPTER 16 8-/16-BIT PPG TIMER

This chapter describes the functions and operations of the 8-/16-bit PPG timer.

CHAPTER 17 DTP/EXTERNAL INTERRUPTS

This chapter explains the functions and operations of DTP/external interrupt.

CHAPTER 18 8-/10-BIT A/D CONVERTER

This chapter explains the functions and operation of 8-/10-bit A/D converter.

CHAPTER 19 LOW VOLTAGE DETECTION/CPU OPERATING DETECTION RESET

This chapter explains the function and operating the low voltage detection/CPU operating

detection reset. This function can use only the product with "T" suffix of MB90360 series.

CHAPTER 20 LIN-UART

This chapter explains the functions and operation of LIN-UART.

CHAPTER 21 CAN CONTROLLER

This chapter explains the functions and operations of the CAN controller.

CHAPTER 22 ADDRESS MATCH DETECTION FUNCTION

This chapter explains the address match detection function and its operation.

CHAPTER 23 ROM MIRRORING MODULE

This chapter describes the functions and operations of the ROM mirroring function select

module.

CHAPTER 24 512K-BIT FLASH MEMORY

This chapter explains the functions and operation of the 512K-bit flash mem ory. The following

three methods are available for writing data to and erasing data from the flash memory:

• Parallel programmer

• Serial programmer

• Executing programs to write/erase data

This chapter explains “Executing programs to write/erase data”.

ii

Page 7

CHAPTER 25 EXAMPLES OF MB90F362/T(S), MB90F367/T(S) SERIAL PROGRAMMING

CONNECTION

This chapter shows an examp le of a serial programming connection using the AF220/AF210/

AF120/AF110 Flas h Micro-computer Programmer by Yo kogawa Digital Computer Corporation

when the AF220/AF210/AF120/AF110 flash serial microcontroller programer from Yokogawa

Digital Computer Corporation is used.

CHAPTER 26 ROM SECURITY FUNCTION

This chapter explains the ROM security function.

APPENDIX

The appendixes provide I/O maps, instructions, and other information.

iii

Page 8

• The contents of this document are subject to change without notice.

Customers are advised to consult with FUJITSU sales representatives before ordering.

• The information, such as descriptions of function and application circuit examples, in this document are

presented solely for the purpose of reference to show examples of operations and uses of Fujitsu

semiconductor device; Fujitsu does not warrant proper operation of the device with respect to use based

on such information. When you develop equipment incorporating the device based on such information,

you must assume any responsibility arising out of such use of the information. Fujitsu assumes no

liability for any damages whatsoever arising out of the use of the information.

• Any information in this document, including descriptions of function and schematic diagrams, shall not be

construed as license of the use or exercise of any intellectual property right, such as patent right or

copyright, or any other right of Fujitsu or any third party or does Fujitsu warrant non-infringement of any

third-party' s intellectual property right or other right by using such information. Fujitsu assumes no

liability for any infringement of the intellectual property rights or other rights of third parties which would

result from the use of information contained herein.

• The products described in this document are designed, developed and manufactured as contemplated

for general use, including without limitation, ordinary industrial use, general office use, personal use, and

household use, but are not designed, developed and manufactured as contemplated (1) for use

accompanying fatal risks or dangers that, unless extremely high safety is secured, could have a serious

effect to the public, and could lead directly to death, personal injury, severe physical damage or other

loss (i.e., nuclear reaction control in nuclear facility, aircraft flight control, air traffic control, mass

transport control, medical life support system, missile launch control in weapon system), or (2) for use

requiring extremely high reliability (i.e., submersible repeater and artificial satellite).

Please note that Fujitsu will not be liable against you and/or any third party for any claims or damages

arising in connection with above- mentioned uses of the products.

• Any semiconductor devices have an inherent chance of failure. You must protect against injury, damage

or loss from such failures by incorporating safety design measures into your facility and equipment such

as redundancy, fire protection, and prevention of over-current levels and other abnormal operating

conditions.

• If any products described in this document represent goods or technologies subject to certain restrictions

on export under the Foreign Exchange and Foreign Trade Law of Japan, the prior authorization by

Japanese government will be required for export of those products from Japan.

©2005 FUJITSU LIMITED Printed in Japan

iv

Page 9

CONTENTS

CHAPTER 1 OVERVIEW ................................................................................................... 1

1.1 Overview of MB90360 ........................................................................................................................ 2

1.2 Block Diagram of MB90360 series ..................................................................................................... 9

1.3 Package Dimensions ........................................................................................................................ 12

1.4 Pin Assignment ................................................................................................................................ . 13

1.5 Pin Functions ................................................................................................................ .................... 14

1.6 Input-Output Circuits ......................................................................................................................... 17

1.7 Handling Device .................................................. ....... ...... ...... ....... ...... ....... ...... ....... .......................... 21

CHAPTER 2 CPU ............................................................................................................ 27

2.1 Outline of the CPU ..................................................................................................................... ....... 28

2.2 Memory Space ..................................................................................................................... ...... ....... 29

2.3 Memory Map ..................................................................................................................................... 32

2.4 Linear Addressing ............................................................................................................................. 33

2.5 Bank Addressing Types .................................................................................................................... 34

2.6 Multi-byte Data in Memory Space ..................................................................................................... 36

2.7 Registers ................ ...... ....... ...... ....... ...... ....... ...... ....... ...... ...... ....................................... ....... ...... ....... 37

2.7.1 Accumulator (A) .................................................................................................................... ....... 40

2.7.2 User Stack Pointer (USP) and System Stack Pointer (SSP) ....................................................... 41

2.7.3 Processor Status (PS) ................................................................................................................. 42

2.7.4 Program Counter (PC) ................................................................................................................. 45

2.8 Register Bank ............................................................................................................... ....... ...... ....... 46

2.9 Prefix Codes ........................................................................................................................ ...... ....... 48

2.10 Interrupt Disable Instructions ............................................................................................................ 51

2.11 Precautions for Use of "DIV A, Ri" and "DIVW A, RWi" Instructions ................................................ 52

CHAPTER 3 INTERRUPTS ............................................................................................. 55

3.1 Outline of Interrupts .......................................................................................................................... 56

3.2 Interrupt Vector ................................................................................................................................. 59

3.3 Interrupt Control Registers (ICR) ...................................................................................................... 61

3.4 Interrupt Flow .................................................................................................................................... 65

3.5 Hardware Interrupts .......................................................................................................................... 67

3.5.1 Hardware Interrupt Operation ...................................................................................................... 68

3.5.2 Occurrence and Release of Hardware Interrupt .......................................................................... 69

3.5.3 Multiple interrupts ........................................................................................................................ 71

3.6 Software Interrupts ................... ....................................... ...... ....... ...... ....... ...... ....... ...... ....... ...... ....... 72

3.7 Extended Intelligent I/O Service (EI

3.7.1 Extended Intelligent I/O Service Descriptor (ISD) ....................................................................... 76

3.7.2 EI

3.8 Operation Flow of and Procedure for Using the Extended Intelligent I/O Service (EI

3.9 Exceptions ........................................................................................................................................ 82

2

OS Status Register (ISCS) ..................................................................................................... 78

2

OS) ............................... .............................................. ............. 74

2

OS) .............. 79

v

Page 10

CHAPTER 4 DELAYED INTERRUPT GENERATION MODULE .................................... 83

4.1 Overview of Delayed Interrupt Generation Module ........................................................................... 84

4.2 Block Diagram of Delayed Interrupt Generation Module .................................................................. 85

4.3 Configuration of Delayed Interrupt Generation Module .................................................................... 86

4.3.1 Delayed interrupt request generate/cancel register (DIRR) ........................................................ 87

4.4 Explanation of Operation of Delayed Interrupt Generation Module .................................................. 88

4.5 Precautions when Using Delayed Interrupt Generation Module ....................................................... 89

4.6 Program Example of Delayed Interrupt Generation Module ............................................................. 90

CHAPTER 5 CLOCKS ..................................................................................................... 91

5.1 Clocks .................... ....................................................................... .................................................... 92

5.2 Block Diagram of the Clock Generation Block .................................................................................. 95

5.2.1 Register of Clock Generation Block ............................................................................................. 97

5.3 Clock Selection Register (CKSCR) ................................................................................................... 98

5.4 PLL/Subclock Control Register (PSCCR) ....................................................................................... 101

5.5 Clock Mode ..................................................................................................................................... 103

5.6 Oscillation Stabilization Wait Interval .............................................................................................. 107

5.7 Connection of an Oscillator or an External Clock to the Microcontroller ......................................... 108

CHAPTER 6 CLOCK SUPERVISOR ............................................................................. 109

6.1 Overview of Clock Supervisor ......................................................................................................... 110

6.2 Block Diagram of Clock Supervisor ................................................................................................ 111

6.3 Clock Supervisor Control Register (CSVCR) .................................................................................. 113

6.4 Operating Mode of Clock Supervisor .............................................................................................. 115

CHAPTER 7 RESETS .................................................................................................... 119

7.1 Resets .......................... ............. ............. ............. ....... ............ ............. ............. ............................... 120

7.2 Reset Cause and Oscillation Stabilization Wait Times ................................................................... 123

7.3 External Reset Pin .......................................................................................................................... 125

7.4 Reset Operation .................. ...... ....... ...................................... ....... ...... ....... ...... ....... ........................ 126

7.5 Reset Cause Bits ... ...... ....... ....................................... ...... ...... ....... ...... ....... ...... ....... ...... .................. 128

7.6 Status of Pins in a Reset ................................................................................................................ 132

CHAPTER 8 LOW-POWER CONSUMPTION MODE ................................................... 133

8.1 Overview of Low-Power Consumption Mode .................................................................................. 134

8.2 Block Diagram of the Low-Power Consumption Control Circuit ..................................................... 137

8.3 Low-Power Consumption Mode Control Register (LPMCR) ........................................................... 139

8.4 CPU Intermittent Operation Mode .................................................................................................. 142

8.5 Standby Mode .............. ....... ...... ....... ...... ....... ...... ....... ...... ...... ....... .................................................. 143

8.5.1 Sleep Mode ............................................................................................................................... 145

8.5.2 Watch Mode .............................................................................................................................. 148

8.5.3 Timebase Timer Mode ............................................................................................................... 150

8.5.4 Stop Mode ................................................................................................................................. 152

8.6 Status Change Diagram ................................................................................................................. 155

8.7 Status of Pins in Standby Mode and during Hold and Reset .......................................................... 156

8.8 Usage Notes on Low-Power Consumption Mode ........................................................................... 157

vi

Page 11

CHAPTER 9 MEMORY ACCESS MODES .................................................................... 161

9.1 Outline of Memory Access Modes .................................................................................................. 162

9.1.1 Mode Pins .................................................................................................................................. 163

9.1.2 Mode Data ................................................................................................................................. 164

9.1.3 Memory Space in Each Bus Mode ............................................................................................ 165

CHAPTER 10 I/O PORTS ................................................................................................ 167

10.1 I/O Ports .......................................................................................................................................... 168

10.2 I/O Port Registers ........................................................................................................................... 169

10.2.1 Port Data Register (PDR) .......................................................................................................... 170

10.2.2 Port Direction Register (DDR) ................................................................................................... 172

10.2.3 Pull-up Control Register (PUCR) ............................................................................................... 174

10.2.4 Analog Input Enable Register (ADER) ...................................................................................... 175

10.2.5 Input Level Select Register ........................................................................................................ 176

CHAPTER 11 TIMEBASE TIMER ................................................................................... 179

11.1 Overview of Timebase Timer .......................................................................................................... 180

11.2 Block Diagram of Timebase Timer ................................................................................................. 182

11.3 Configuration of Timebase Timer ................................................................................................... 184

11.3.1 Timebase timer control register (TBTC) .................................................................................... 185

11.4 Interrupt of Timebase Timer ........................................................................................................... 187

11.5 Explanation of Operations of Timebase Timer Functions ............................................................... 188

11.6 Precautions when Using Timebase Timer ...................................................................................... 192

11.7 Program Example of Timebase Timer ............................................................................................ 193

CHAPTER 12 WATCHDOG TIMER ................................................................................ 195

12.1 Overview of Watchdog Timer ......................................................................................................... 196

12.2 Configuration of Watchdog Timer ................................................................................................... 199

12.3 Watchdog Timer Registers ............................................................................................................. 201

12.3.1 Watchdog timer control register (WDTC) .................................................................................. 202

12.4 Explanation of Operations of Watchdog Timer Functions .............................................................. 204

12.5 Precautions when Using Watchdog Timer ...................................................................................... 207

12.6 Program Examples of Watchdog Timer .......................................................................................... 208

CHAPTER 13 16-Bit I/O TIMER ............................................................ ..... ..... .... ............ 209

13.1 Overview of 16-bit I/O Timer ........................................................................................................... 210

13.2 Block Diagram of 16-bit I/O Timer .................................................................................................. 211

13.2.1 Block Diagram of 16-bit Free-run Timer .................................................................................... 213

13.2.2 Block Diagram of Input Capture ................................................................................................ 214

13.3 Configuration of 16-bit I/O Timer .................................................................................................... 216

13.3.1 Timer Control Status Register (Upper) (TCCSH) ...................................................................... 217

13.3.2 Timer Control Status Register (Lower) (TCCSL) ....................................................................... 218

13.3.3 Timer Data Register (TCDT) ..................................................................................................... 220

13.3.4 Input Capture Control Status Registers (ICS) ........................................................................... 221

13.3.5 Input Capture Register (IPCP) ................................................................................................... 223

13.3.6 Input Capture Edge Register (ICE) ............................................................................................ 224

13.4 Interrupts of 16-bit I/O Timer ........................................................................................................... 227

vii

Page 12

13.5 Explanation of Operation of 16-bit Free-run Timer ......................................................................... 229

13.6 Explanation of Operation of Input Capture ..................................................................................... 231

13.7 Precautions when Using 16-bit I/O Timer ....................................................................................... 233

13.8 Program Example of 16-bit I/O Timer ............................................................................................. 234

CHAPTER 14 16-BIT RELOAD TIMER ........................................................................... 237

14.1 Overview of the 16-bit Reload Timer .............................................................................................. 238

14.2 Block Diagram of 16-bit Reload Timer .......... ...... ....... ...... ...... ....................................... ....... ..... ...... 240

14.3 Configuration of 16-bit Reload Timer .............................................................................................. 242

14.3.1 Timer Control Status Registers (High) (TMCSR:H) ................................................................... 245

14.3.2 Timer Control Status Registers (Low) (TMCSR: L) ................................................................... 247

14.3.3 16-bit Timer Registers (TMR) .................................................................................................... 249

14.3.4 16-bit Reload Registers (TMRLR) ............................................................................................. 250

14.4 Interrupts of 16-bit Reload Timer .................................................................................................... 251

14.5 Explanation of Operation of 16-bit Reload Timer ............................................................................ 252

14.5.1 Operation in Internal Clock Mode .............................................................................................. 254

14.5.2 Operation in Event Count Mode ................................................................................................ 259

14.6 Precautions when Using 16-bit Reload Timer ................................................................................ 262

14.7 Sample Program of 16-bit Reload Timer ........................................................................................ 263

CHAPTER 15 WATCH TIMER ........................................................................................ 267

15.1 Overview of Watch Timer ............................................................................................................... 268

15.2 Block Diagram of Watch Timer ....................................................................................................... 270

15.3 Configuration of Watch Timer ......................................................................................................... 272

15.3.1 Watch Timer Control Register (WTC) ........................................................................................ 273

15.4 Watch Timer Interrupt ..................................................................................................................... 275

15.5 Explanation of Operation of Watch Timer ....................................................................................... 276

15.6 Program Example of Watch Timer .................................................................................................. 278

CHAPTER 16 8-/16-BIT PPG TIMER .............................................................................. 281

16.1 Overview of 8-/16-bit PPG Timer .................................................................................................... 282

16.2 Block Diagram of 8-/16-bit PPG Timer ........................................................................................... 285

16.2.1 Block Diagram for 8-/16-bit PPG Timer C ..................................... ....... ...... ....... ........................ 286

16.2.2 Block Diagram of 8-/16-bit PPG Timer D ................................................................................... 288

16.3 Configuration of 8-/16-bit PPG Timer ............................................................................................. 290

16.3.1 PPGC Operation Mode Control Register (PPGCC) .................................................................. 292

16.3.2 PPGD Operation Mode Control Register (PPGCD) .................................................................. 294

16.3.3 PPGC/D Count Clock Select Register (PPGCD) ....................................................................... 296

16.3.4 PPG Reload Registers (PRLLC/PRLHC, PRLLD/PRLHD) ........................................................ 298

16.4 Interrupts of 8-/16-bit PPG Timer .................................................................................................... 299

16.5 Explanation of Operation of 8-/16-bit PPG Timer ........................................................................... 300

16.5.1 8-bit PPG Output 2-channel Independent Operation Mode ....................................................... 301

16.5.2 16-bit PPG Output Operation Mode .......................................................................................... 304

16.5.3 8+8-bit PPG Output Operation Mode ........................................................................................ 307

16.6 Precautions when Using 8-/16-bit PPG Timer ................................................................................ 310

viii

Page 13

CHAPTER 17 DTP/EXTERNAL INTERRUPTS .............................................................. 313

17.1 Overview of DTP/External Interrupt ................................................................................................ 314

17.2 Block Diagram of DTP/External Interrupt ........................................................................................ 315

17.3 Configuration of DTP/External Interrupt .......................................................................................... 317

17.3.1 DTP/External Interrupt Factor Register (EIRR1) ....................................................................... 319

17.3.2 DTP/External Interrupt Enable Register (ENIR1) ...................................................................... 321

17.3.3 Detection Level Setting Register (ELVR1) ................................................................................ 323

17.3.4 External Interrupt Factor Select Register (EISSR) .................................................................... 325

17.4 Explanation of Operation of DTP/External Interrupt ....................................................................... 327

17.4.1 External Interrupt Function ...................... ...... ....... ...... ...... ....... ....................................... ........... 331

17.4.2 DTP Function .......... ....... ....................................... ...... ...... ....... ...... ....... ...... ....... ...... .................. 332

17.5 Precautions when Using DTP/External Interrupt ............................................................................ 333

17.6 Program Example of DTP/External Interrupt Function ................................................................... 335

CHAPTER 18 8-/10-BIT A/D CONVERTER .................................................................... 339

18.1 Overview of 8-/10-bit A/D Converter ............................................................................................... 340

18.2 Block Diagram of 8-/10-bit A/D Converter ...................................................................................... 341

18.3 Configuration of 8-/10-bit A/D Converter ........................................................................................ 344

18.3.1 A/D Control Status Register (High) (ADCS1) ............................................................................ 346

18.3.2 A/D Control Status Register (Low) (ADCS0) ............................................................................. 349

18.3.3 A/D Data Register (ADCR0/ADCR1) ......................................................................................... 351

18.3.4 A/D Setting Register (ADSR0/ADSR1) ...................................................................................... 352

18.3.5 Analog Input Enable Register (ADER5, ADER6) ...................................................................... 356

18.4 Interrupt of 8-/10-bit A/D Converter ................................................................................................ 358

18.5 Explanation of Operation of 8-/10-bit A/D Converter ...................................................................... 359

18.5.1 Single-shot Conversion Mode ................................................................................................... 360

18.5.2 Continuous Conversion Mode ................................................................................................... 362

18.5.3 Pause-conversion Mode ....................................... ...... ...... ....... ...... ....... ...... ............................... 364

18.5.4 Conversion Using EI

18.5.5 A/D-converted Data Protection Function ................................................................................... 367

18.6 Precautions when Using 8-/10-bit A/D Converter ........................................................................... 369

2

OS Function ................................... ....... ...... ....... ...... ............................... 366

CHAPTER 19 LOW VOLTAGE DETECTION/CPU OPERATING DETECTION RESET

371

19.1 Overview of Low Voltage/CPU Operating Detection Reset Circuit ................................................. 372

19.2 Configuration of Low Voltage/CPU Operating Detection Reset Circuit .......................................... 374

19.3 Low Voltage/CPU Operating Detection Reset Circuit Register ...................................................... 376

19.4 Operating of Low Voltage/CPU Operating Detection Reset Circuit ................................................ 378

19.5 Notes on Using Low Voltage/CPU Operating Detection Reset Circuit ........................................... 379

19.6 Sample Program for Low Voltage/CPU Operating Detection Reset Circuit .................................... 380

CHAPTER 20 LIN-UART ................................................................................................. 381

20.1 Overview of LIN-UART ................................................................................................................... 382

20.2 Configuration of LIN-UART ............................................................................................................. 386

20.3 LIN-UART Pins ............................................................................................................................... 391

20.4 LIN-UART Registers ....................................................................................................................... 392

20.4.1 Serial Control Register (SCR) ................................................................................................... 393

ix

Page 14

20.4.2 LIN-UART Serial Mode Register (SMR) .................................................................................... 395

20.4.3 Serial Status Register (SSR) ..................................................................................................... 397

20.4.4 Reception and Transmission Data Register (RDR/TDR) ........................................................... 399

20.4.5 Extended Status/Control Register (ESCR) ................................................................................ 401

20.4.6 Extended Communication Control Register (ECCR) ................................................................. 403

20.4.7 Baud Rate Generator Register 0 and 1 (BGR0/1) ..................................................................... 405

20.5 LIN-UART Interrupts ....................................................................................................................... 406

20.5.1 Reception Interrupt Generation and Flag Set Timing ................................................................ 409

20.5.2 Transmission Interrupt Generation and Flag Set Timing ........................................................... 411

20.6 LIN-UART Baud Rates ................................................................................................................... 413

20.6.1 Setting the Baud Rate ............................................................................................................... 415

20.6.2 Restarting the Reload Counter ................ ...... ....... ...................................... ....... ...... ....... .... ....... 418

20.7 Operation of LIN-UART .................................................................................................................. 420

20.7.1 Operation in Asynchronous Mode (Op. Modes 0 and 1) ........................................................... 422

20.7.2 Operation in Synchronous Mode (Operation Mode 2) ............................................................... 426

20.7.3 Operation with LIN Function (Operation Mode 3) ...................................................................... 429

20.7.4 Direct Access to Serial Pins ...................................................................................................... 432

20.7.5 Bidirectional Communication Function (Normal Mode) ............................................................. 433

20.7.6 Master-Slave Communication Function (Multiprocessor Mode) ................................................ 435

20.7.7 LIN Communication Function .................................................................................................... 438

20.7.8 Sample Flowcharts for LIN-UART in LIN communication (Operation Mode 3) .......................... 439

20.8 Notes on Using LIN-UART .............................................................................................................. 441

CHAPTER 21 CAN CONTROLLER ................................................................................ 443

21.1 Features of CAN Controller ............................................................................................................ 444

21.2 Block Diagram of CAN Controller ................................................................................................... 445

21.3 List of Overall Control Registers ..................................................................................................... 446

21.4 Classifying CAN Controller Registers ................. ....... ...... ...... ....... ...... ....... ...... ....... ........................ 452

21.4.1 Configuration of Control Status Register (CSR) ........................................................................ 453

21.4.2 Function of Control Status Register (CSR) ................................................................................ 454

21.4.3 Correspondence between Node Status Bit and Node Status .................................................... 456

21.4.4 Notes on Using Bus Operation Stop Bit (HALT = 1) .................................................................. 457

21.4.5 Last Event Indicator Register (LEIR) ......................................................................................... 458

21.4.6 Receive and Transmit Error Counters (RTEC) .......................................................................... 461

21.4.7 Bit Timing Register (BTR) .......................................................................................................... 462

21.4.8 Prescaler Setting by Bit Timing Register (BTR) ........................................................................ 463

21.4.9 Message Buffer Valid Register (BVALR) ................................................................................... 465

21.4.10 IDE Register (IDER) .................................................................................................................. 466

21.4.11 Transmission Request Register (TREQR) ................................................................................ 467

21.4.12 Transmission RTR Register (TRTRR) ....................................................................................... 468

21.4.13 Remote Frame Receiving Wait Register (RFWTR) ................................................................... 469

21.4.14 Transmission Cancel Register (TCANR) ................................................................................... 470

21.4.15 Transmission Complete Register (TCR) .................................................................................... 471

21.4.16 Transmission Interrupt Enable Register (TIER) ......................................................................... 472

21.4.17 Reception Complete Register (RCR) ........................................................................................ 473

21.4.18 Remote Request Receiving Register (RRTRR) ........................................................................ 474

21.4.19 Receive Overrun Register (ROVRR) ......................................................................................... 475

x

Page 15

21.4.20 Reception Interrupt Enable Register (RIER) ............................................................................. 476

21.4.21 Acceptance Mask Select Register (AMSR) ............................................................................... 477

21.4.22 Acceptance Mask Registers 0 and 1 (AMR0 and AMR1) .......................................................... 479

21.4.23 Message Buffers ........................................................................................................................ 481

21.4.24 ID Register x (x = 0 to 15) (IDRx) .............................................................................................. 483

21.4.25 DLC Register x (x = 0 to 15) (DLCRx) ....................................................................................... 485

21.4.26 Data Register x (x = 0 to 15) (DTRx) ......................................................................................... 486

21.5 Transmission of CAN Controller ..................................................................................................... 488

21.6 Reception of CAN Controller ................. ....... ...................................... ....... ...... ....... ...... .................. 490

21.7 Reception Flowchart of CAN Controller .......................................................................................... 493

21.8 How to Use CAN Controller ............................................................................................................ 494

21.9 Procedure for Transmission by Message Buffer (x) ....................................................................... 496

21.10 Procedure for Reception by Message Buffer (x) ............................................................................. 498

21.11 Setting Configuration of Multi-level Message Buffer ....................................................................... 500

21.12 Setting the CAN Direct Mode Register ........................................................................................... 502

21.13 Precautions when Using CAN Controller ........................................................................................ 503

CHAPTER 22 ADDRESS MATCH DETECTION FUNCTION ......................................... 505

22.1 Overview of Address Match Detection Function ............................................................................. 506

22.2 Block Diagram of Address Match Detection Function .................................................................... 507

22.3 Configuration of Address Match Detection Fu nctio n ................................. ...... ....... ...... ....... ........... 508

22.3.1 Address Detection Control Register (PACSR0/PACSR1) ......................................................... 509

22.3.2 Detect Address Setting Registers (PADR0 to PADR5) ............................................................. 513

22.4 Explanation of Operation of Address Match Detection Function .................................................... 516

22.4.1 Example of using Address Match Detection Function ............................................................... 517

22.5 Program Example of Address Match Detection Function ............................................................... 522

CHAPTER 23 ROM MIRRORING MODULE ................................................................... 525

23.1 Overview of ROM Mirroring Function Select Module ...................................................................... 526

23.2 ROM Mirroring Function Select Register (ROMM) ......................................................................... 528

CHAPTER 24 512K-BIT FLASH MEMORY .................................................................... 529

24.1 Overview of 512K-bit Flash Memory ............................................................................................... 530

24.2 Block Diagram of the Entire Flash Memory and Sector Configuration of the Flash Memory .......... 531

24.3 Write/Erase Modes ......................................................................................................................... 533

24.4 Flash Memory Control Status Register (FMCS) .................... ....... ...... ....... ..................................... 535

24.5 Starting the Flash Memory Automatic Algorithm ............................................................................ 538

24.6 Confirming the Automatic Algorithm Execution State ..................................................................... 539

24.6.1 Data Polling Flag (DQ7) ............................................................................................................ 541

24.6.2 Toggle Bit Flag (DQ6) ................................................................................................................ 542

24.6.3 Timing Limit Exceeded Flag (DQ5) ........................................................................................... 543

24.7 Detailed Explanation of Writing to and Erasing Flash Memory ....................................................... 544

24.7.1 Setting The Read/Reset State ................................................................................................... 545

24.7.2 Writing Data ............................................................................................................................... 546

24.7.3 Erasing All Data (Erasing Chips) ............................................................................................... 548

24.8 Notes on Using 512K-bit Flash Memory ......................................................................................... 550

24.9 Flash Security Feature ........ ...... ....................................... ...... ....... ...... ....... ...... ....... ...... .................. 551

xi

Page 16

CHAPTER 25 EXAMPLES OF MB90F362/T(S), MB90F367/T(S)SERIAL PROGRAMMING

CONNECTION .......................................................................................... 553

25.1 Basic Configuration of Serial Programming Connection with MB90F362/T(S), MB90F367/T(S) ... 554

25.2 Example of Serial Programming Connection (User Power Supply Used) ...................................... 557

25.3 Example of Serial Programming Connection (Power Supplied from Programmer) ........................ 559

25.4 Example of Minimum Connection to Flash Microcontroller Programmer

(User Power Supply Used) ............................................................................................................. 561

25.5 Example of Minimum Connection to Flash Microcontroller Programmer

(Power Supplied from Programmer) ............................................................................................... 563

CHAPTER 26 ROM SECURITY FUNCTION ................................................................... 565

26.1 Overview of ROM Security Function ............................................................................................... 566

APPENDIX ......................................................................................................................... 567

APPENDIX A I/O Maps .............................................................................................................................. 568

APPENDIX B Instructions ........................................................................................................................... 576

B.1 Instruction Types ............................................................................................................................ 577

B.2 Addressing ..................................................................................................................................... 578

B.3 Direct Addressing ........................................................................................................................... 580

B.4 Indirect Addressing ........................................................................................................................ 586

B.5 Execution Cycle Count ................................................................................................................... 593

B.6 Effective address field .................................................................................................................... 596

B.7 How to Read the Instruction List .................................................................................................... 597

B.8 F

B.9 Instruction Map ............................................................................................................................... 614

APPENDIX C Timing Diagrams in Flash Memory Mode ............................................................................ 636

APPENDIX D List of Interrupt Vectors ........................................................................................................ 644

2

MC-16LX Instruction List ............................................................................................................ 600

xii

Page 17

CHAPTER 1

OVERVIEW

The MB90360 Series is a family member of the F2MC16LX micro controllers.

1.1 Overview of MB90360

1.2 Block Diagram of MB90360 series

1.3 Package Dimensions

1.4 Pin Assignment

1.5 Pin Functions

1.6 Input-Output Circuits

1.7 Handling Device

1

Page 18

CHAPTER 1 OVERVIEW

1.1 Overview of MB90360

The MB90360 Series is a 16-bit micr ocont roller designed for automotive applications

and contains CAN function, capture, compare timer, A/D converter, and so on.

■ Features of MB9036 0 Seri es

MB90360 series has the following features:

Clock

●

• Built-in PLL clock multiplying circuit

• Machine clock (PLL clock) selectable from 1/2 frequency of oscillation clock or 1 to 6-multiplied

oscillation clock (4 MHz to 24 MHz when oscillation clock is 4 MHz)

• Subclock operation (8.192 kHz)

• Minimum instruction execution time: 42 ns (4-MHz oscillation clock and 6-multiplied PLL clock)

• Clock supervisor: monitors main clock or subclock independently

• Subclock mode: Clock source selectable from external oscillator or internal CR oscillator

16-MB CPU memory space

●

• Internal 24-bit addressing

Instruction system optimized for controllers

●

• Various data types (bit, byte, word, long word)

• 23 types of addr essing modes

• Enhanced signed instructio ns of multiplication/division and RETI

• High-accuracy operations enhanced by 32-bit accumulator

Instruction system for high-level language (C language)/multi-task

●

• System stack pointer

• Enhanced pointer indirect instructions

• Barrel shift instructions

Higher execution speed

●

4 bytes instruction queue

Powerful interrupt function

●

• Powerful interrupt function with 8 levels and 34 factors

• Corresponds to 8-channel external interrupts

2

Page 19

CPU-independent automatic data transfer function

●

CHAPTER 1 OVERVIEW

Extended intelligent I/O service (EI

Lower-power consumption (standby) modes

●

• Sleep mode (stops CPU cl ock)

• Timebase timer mode (operates only oscillation clock and subclock, timebase timer and watch timer)

• Watch mode (product without S-suffix operates only subclock and watch timer)

• Stop mode (stops oscillation clock and subclock)

• CPU intermittent operation mode

Process

●

CMOS Technology

I/O ports

●

• General-purpose I/O ports (CMOS output)

- 34 ports (product without S-suffix)

- 36 ports (product with S-suffix)

Subclock pin (X0A, X1A)

●

2

OS): Maximum 16 channels

• Yes (external oscillator used) ... products without S-suffix

• No (subclock mode is used with internal CR oscillation) ... product with S-suffix

Timers

●

• Timebase timer, watch timer (product without S-suffix), watchdog timer: 1 channel

• 8-/16-bit PPG timer: 8 bits × 4 channels or 16 bits × 2 channels

• 16-bit reload timer: 2 channels

• 16-bit I/O timer

- 16-bit free-run timer: 1 channel (FRT0: ICU0/1/2/3)

- 16-bit input capture (ICU): 4 channels

Full-CAN* CAN Controller: 1 channel

●

• Conforms to CAN Specification Ver. 2.0A and Ver. 2.0B.

• Built-in 16 message buffers

• CAN wake up

UART (LIN/SCI): Maximum 2 channels

●

• Full-duplex double buffer

• Clock asynchronous or clock synchronous serial transfer

DTP/external interrupt: 8 channels, CAN wake up: 1 channel

●

External input to start EI

2

OS and generate external interrupt

3

Page 20

CHAPTER 1 OVERVIEW

Delayed interrupt generation module

●

Generates interrupt request for task switchin g

8-/10-bit A/D converter: 16 channels

●

• 8-bit and 10-bit resolutions

• Start by external trigger input

• Conversion time: 3 µs (including sampling time at 24-MHz machine clock frequency)

Program patch function

●

Detects address match for six address pointers

Low voltage/CPU operation detection reset function (product with T-suffix)

●

• Detects low voltage (4.0 V ± 0.3 V) and reset automatically

• Automatic reset when program runs away and counter is not cleared within internal time (appro x. 262

ms @ 4 MHz external)

Clock supervisor (MB90x367x only)

●

Changeable port input voltage level

●

Automotive input level/CMOS Schmitt input level (initial value in single-chip mode is Automotive level)

ROM security function

●

Capable of protectin g t he content of ROM (MASK ROM product only)

*: Controller Area Network (CAN) - License of Robert Bosch GmbH

4

Page 21

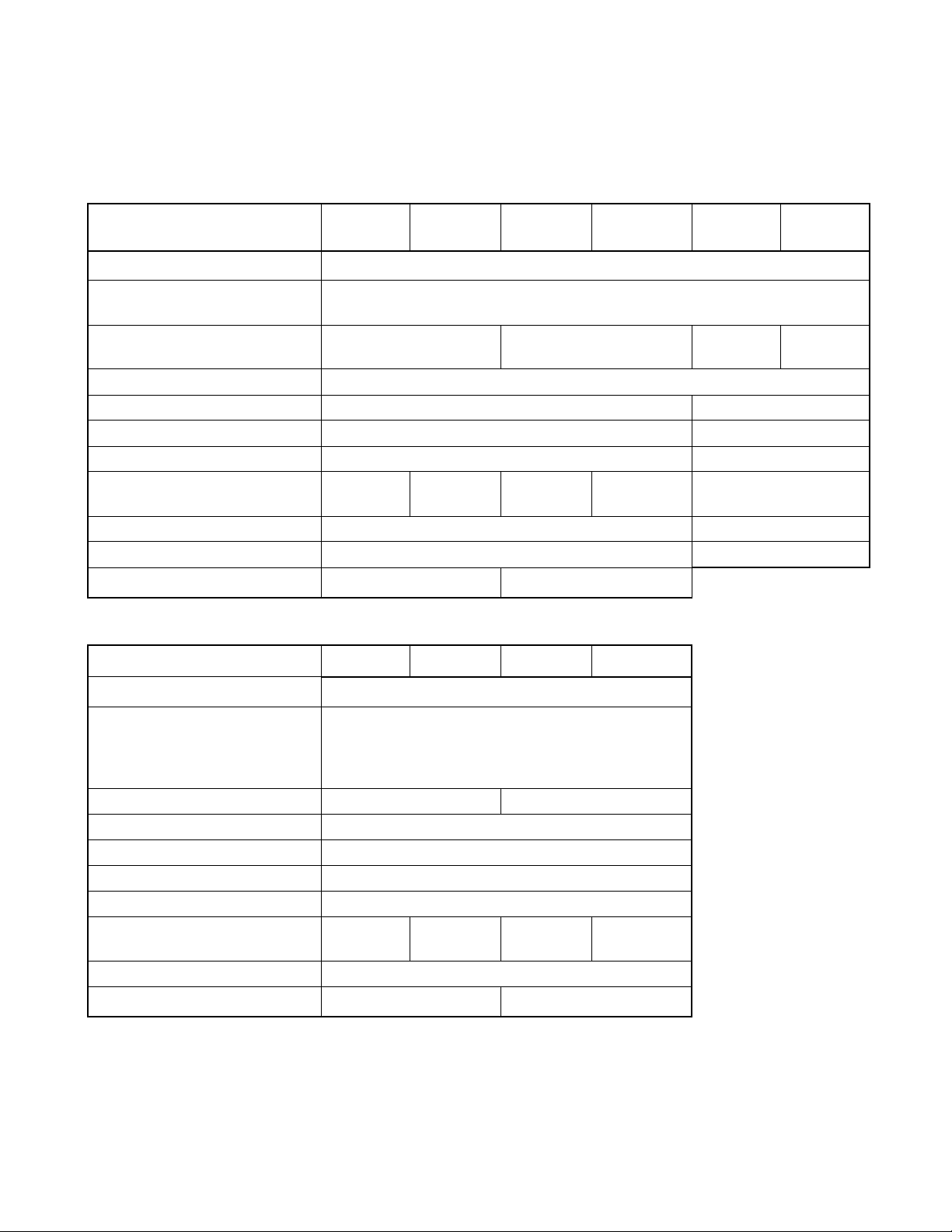

■ Product overview

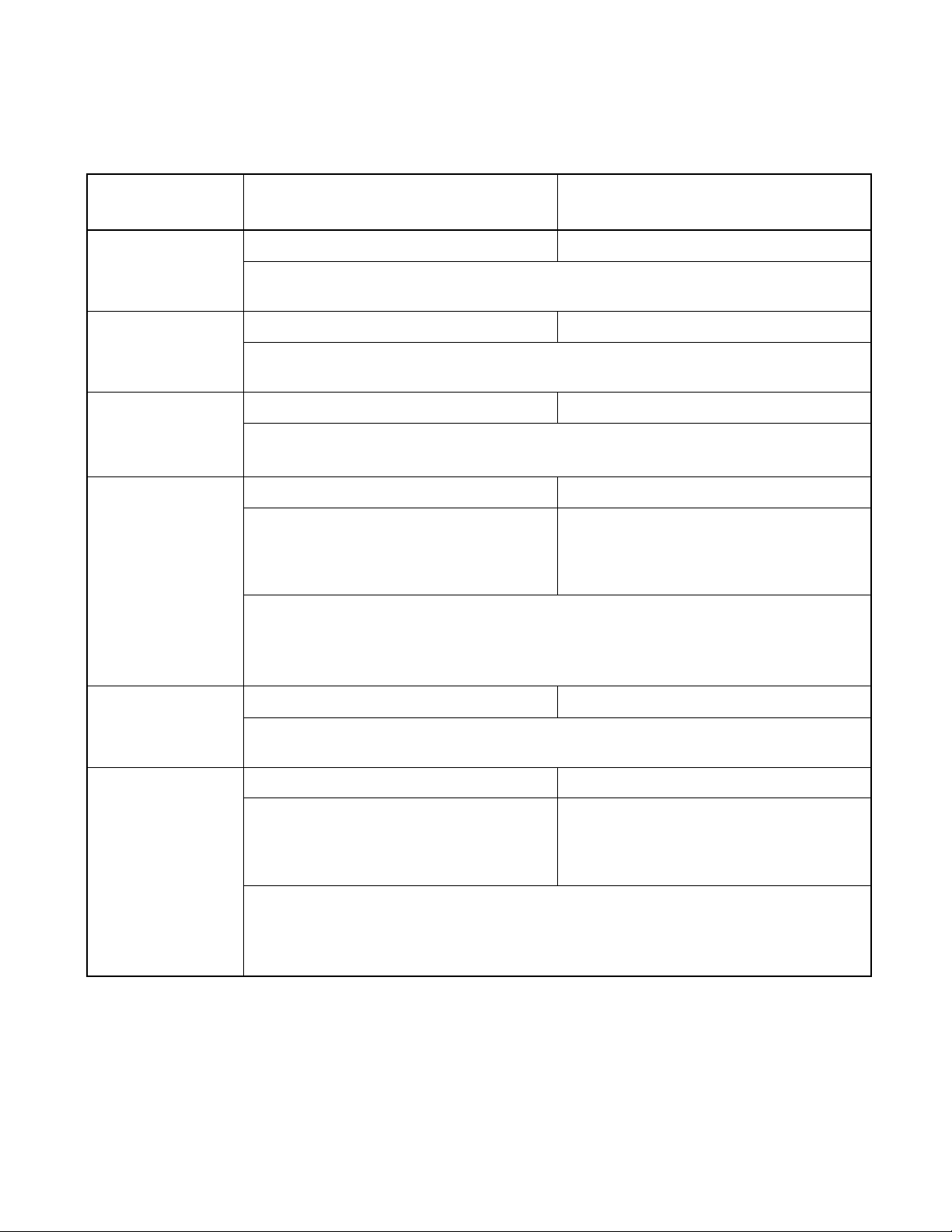

Table 1.1-1 Product Overview (1 /2)

CHAPTER 1 OVERVIEW

CPU

Features

MB90362 MB90362T MB90362S MB90362TS

2

F

MC-16LX CPU

MB90V340

A-101

MB90V340

A-102

System clock pin PLL clock multiplier (✕1, ✕2, ✕3, ✕4, ✕6, 1/2 when PLL stops)

Minimum instruction execution time: 42 ns (4 MHz osc. PLL ✕6)

Sub clock pin (X0A, X1A) Yes No No Yes

Clock supervisor No

ROM MASK ROM, 64K bytes External

RAM capac itance 3K bytes 30K bytes

CAN interface 1 channel 3 channels

Low voltage/CPU operation

No Yes No Yes No

detection reset

Package LQFP-48 PGA-299

Power supply for emulator* - Yes

Corresponding EVA product name

MB90V340A-102 MB90V340A-101

*: It is setting of Jumper switch (TOOL VCC) when Emulator (MB2147-01) is used. Please refer to Emulator hardware manual.

Features

MB90F362 MB90F362T MB90F362S MB90F362TS

CPU

2

MC-16LX CPU

F

System clock pin PLL clock multiplier (✕1, ✕2, ✕3, ✕4, ✕6, 1/2 when

PLL stops)

Minimum instruction execution time : 42 ns (4 MHz osc.

PLL ✕6)

Sub clock pin (X0A, X1A) Yes No

Clock supervisor No

ROM Flash memory, 64K bytes

RAM capacitance 3K bytes

CAN interface 1 channel

Low voltage/CPU operation

No Yes No Yes

detection reset

Package LQFP-48

Corresponding EVA product name

MB90V340A-102 MB90V340A-101

5

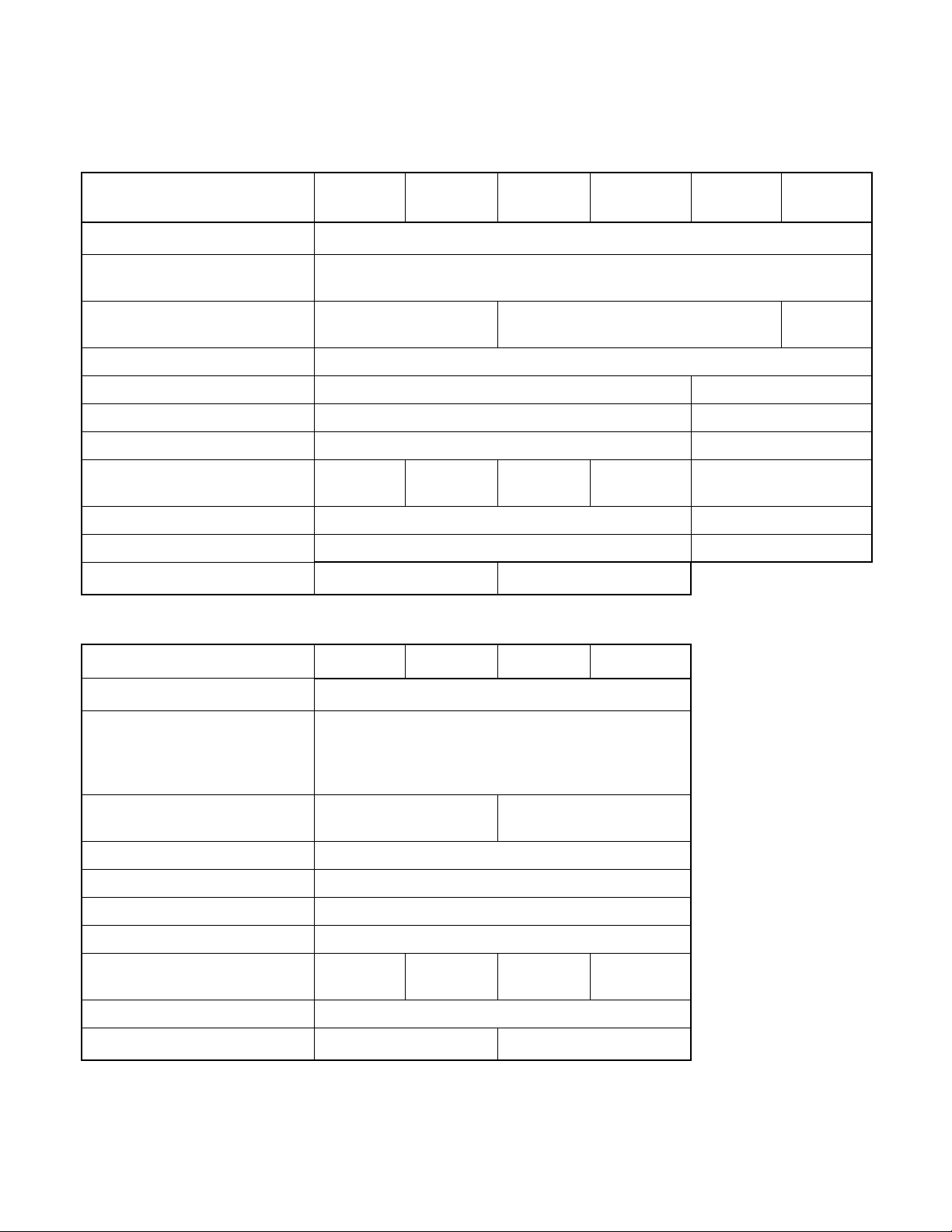

Page 22

CHAPTER 1 OVERVIEW

Table 1.1-2 Product Overview (2/2)

CPU

Features

MB90367 MB90367T MB90367S MB90367TS

2

F

MC-16LX CPU

MB90V340

A-103

MB90V340

A-104

System clock pin PLL clock multiplier (✕1, ✕2, ✕3, ✕4, ✕6, 1/2 when PLL stops)

Minimum instruction execution time: 42 ns (4 MHz osc. PLL ✕6)

Sub clock pin (X0A, X1A) Yes No (Internal CR oscillation can be used as

Yes

subclock)

Clock supervisor Yes

ROM MASK ROM, 64K bytes External

RAM capacitance 3K bytes 30K bytes

CAN interface 1 channel 3 channels

Low voltage/CPU operation

No Yes No Yes No

detection reset

Package LQFP-48 PGA-299

Power supply for emulator * - Yes

Corresponding EVA product name

MB90V340A-104 MB90V340A-103

*: It is setting of Jumper switch (TOOL VCC) when Emulator (MB2147-01) is used. Please refer to Emulator hardware manual.

Features

CPU

MB90F367 MB90F367T MB90F367S MB90F367TS

2

F

MC-16LX CPU

System clock pin PLL clock multiplier (✕1, ✕2, ✕3, ✕4, ✕6, 1/2 when

PLL stops)

Minimum instruction execution time: 42 ns (4 MHz osc.

PLL ✕6)

Sub clock pin (X0A, X1A) Yes No (Internal CR oscillation

can be used as subclock)

Clock supervisor Yes

ROM Flash memory, 64K bytes

RAM capacitance 3K bytes

CAN interface 1 channel

Low voltage/CPU operation

No Yes No Yes

detection reset

Package LQFP-48

Corresponding EVA product name

MB90V340A-104 MB90V340A-103

6

Page 23

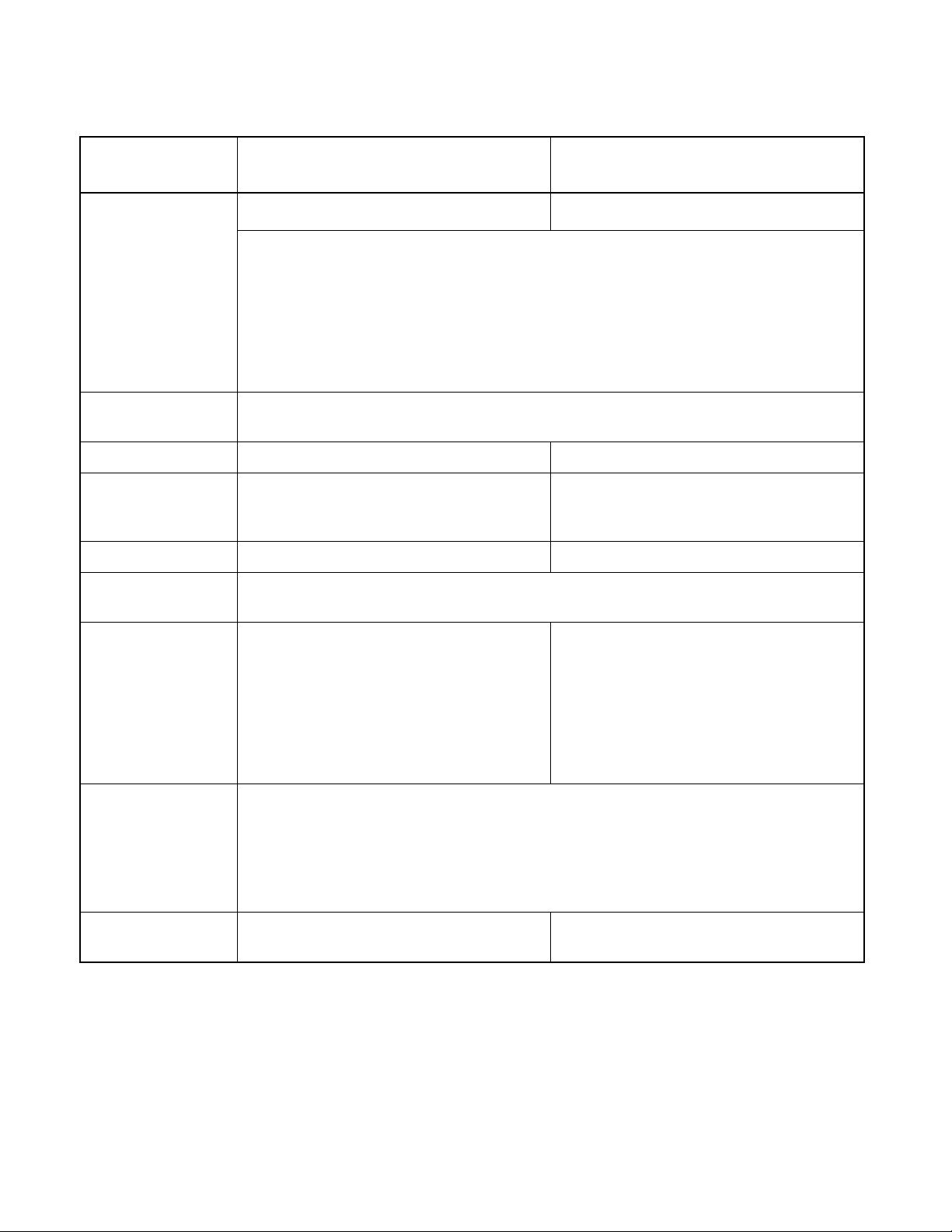

■ Features

Table 1.1-3 MB90360 Features (1/2)

CHAPTER 1 OVERVIEW

Features

MB90F362/T(S), MB90362/T(S)

MB90F367/T(S), MB90367/T(S)

MB90V340A-101, MB90V340A-102

MB90V340A-103, MB90V340A-104

UART 2 channels 5 channels

Wide range of baud rate settings using a dedicated reload timer

LIN functionality working either as LIN master or LIN slave device

A/D converter 16 channels 24 channels

10-bit or 8-bit resolution

Conversion ti me: Minimum 3 µs include sample time (per one channel)

2 channels 4 channels

16-bit reload timer

Operation clock frequency: fsys/2

1

, fsys/23, fsys/25(fsys=System cl ock freq.)

Support External Event Count function

1 channel 4 channels

16-bit I/O timer

I/O timer 0 (clock input FRCK0)

corresponding ICU 0/1/2/3.

I/O timer 0 (clock input FRCK0) corresponds

to ICU 0/1/2/3, OCU 0/1/2/3

I/O timer 1 (clock input FRCK1) corresponds

to ICU 4/5/6/7, OCU 4/5/6/7

Signal an interrupt when overflowing

Supports Timer Clear when a match with Output Compare (Channel 0, 4)

Operation clock freq.: fsys/2

1

, fsys/22, fsys/23, fsys/24, fsys/25, fsys/26, fsys/2

7

(fsys=System clock freq.)

16-bit input capture

8-/16-bit PPG

4 channels 8 channels

Maintains I/O timer value by pin input (rising edge, falling edge, or both edges) and generates

interrupt.

2 channels 8 channels

Supports 8-bit and 16-bit operation modes

Four 8-bit reload counter

Four 8-bit reload registers for L pulse width

Four 8-bit reload registers for H pulse width

Supports 8-bit and 16-bit operation modes

Sixteen 8-bit reload counter

Sixteen 8-bit reload registers for L pulse width

Sixteen 8-bit reload registers for H pulse width

A pair of 8-bit reload counters can be configured as one 16-bit reload coun ter or as 8-bit prescaler

plus 8-bit reload counter

Operation clock freq.: fsys, fsys/2

1

, fsys/22, fsys/23, fsys/24 or 102.4 µs fosc=@5MHz

(fsys=system clock frequency, fosc=oscillation clock frequency)

7

Page 24

CHAPTER 1 OVERVIEW

Table 1.1-3 MB90360 Features (2/2)

Features

CAN interface

MB90F362/T(S), MB90362/T (S)

MB90F367/T(S), MB90367/T (S)

1 channel

MB90V340A-101, MB90V340A-102

MB90V340A-103, MB90V340A-104

3 channels

Conforms to CAN Specification Version 2.0 Part A and B

Automatic re-transmission in case of error

Automatic transmission responding to Remote Frame

16 message buffers for transmission/reception

Supports multiple messages

Flexible configuration of acceptance filtering:

• Full bit compare/Full bit mask/2 partial bit masks

• Supports up to 1 Mbps communication

External interrupt (8

Can be programmed edge sensitive or level sensitive

channels)

D/A converter - 2 channels

Low voltage/CPU

Corresponds to product with T-suffix only operation detection

reset

Clock supervisor MB90F367/T(S), MB90367/T(S) only Subclock

(Maximum 100 kHz)

Corresponds to product without T-suffix only

Corresponds to MB90V340A-102/MB90V340A-104 only

I/O port Supports general-purpose I/O (CMOS output):

- 34 ports (product without S-suffix)

- 36 ports (product with S-suffix)

Input level setting:

- Port2, Port4, Port6, Port8: s electable from

CMOS/Automotive level

Supports general-purpose I/O (CMOS output):

- 80 ports (product without S-suffix)

- 82 ports (product with S-suffix)

Input level setting

- Port 0 to Port 3: selectable from CMOS/

Automotive/TTL level

- Port 4 to Port A: selectable from CMOS/

Automotive level

Flash memory

Supports automatic progr amming, Embedded Algorit hm

commands

A flag indicating completion of the algorithm

Number of erase cycles: 10,000 times

Data retention time: 20 years

Flash Security Feature for protecting the content of the Flash

ROM security Protects the content of ROM (MASK ROM

product only)

*:Embedded Algorithm is a registered trademark of Advanced Micro Device Inc.

TM*

, Write/Erase/Erase-Suspend/Resume

-

8

Page 25

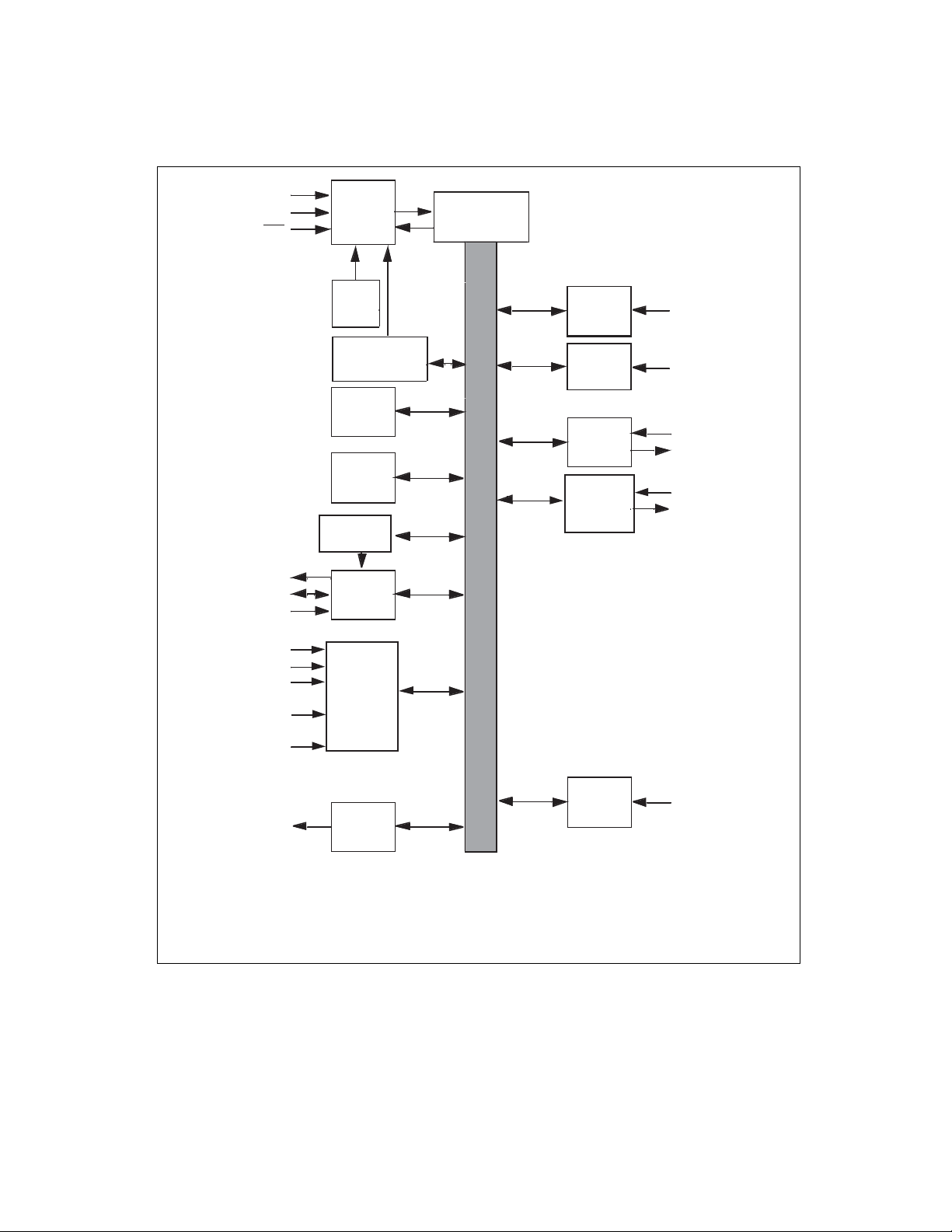

1.2 Block Diagram of MB90360 series

Figure 1.2-3 shows a block diagram of the MB90360.

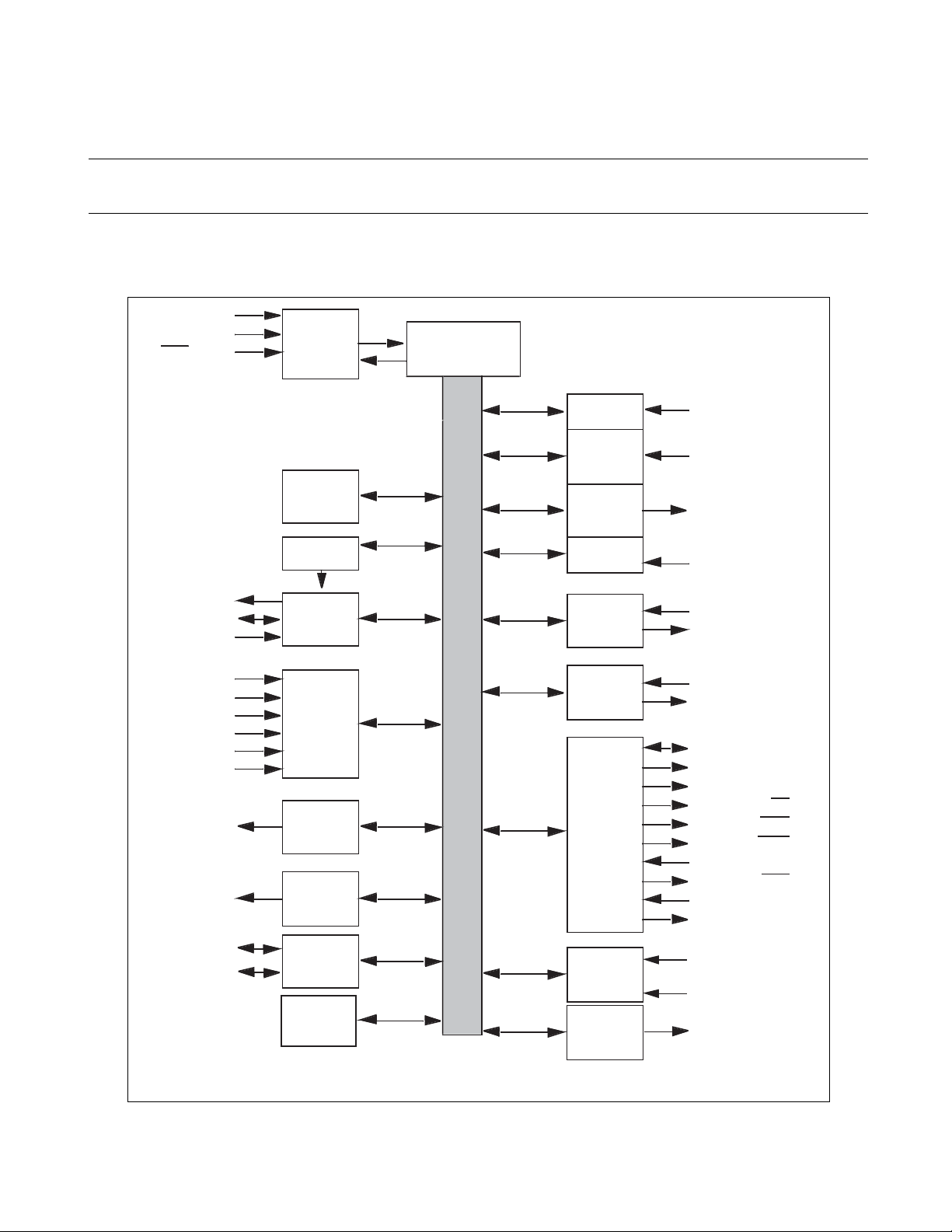

■ Block Diagram of Evaluation Chip

Figure 1.2-1 Block Diagram of Evaluation Chip (MB90V340A-101/102)

CHAPTER 1 OVERVIEW

X0, X1

X0A, X1A *

RST

SOT4 to SOT0

SCK4 to SCK0

SIN4 to SIN0

AV

CC

AV

SS

AN23 to AN0

AVRH

AVRL

ADTG

DA01, DA00

PPGF to PPG0

Clock

control

RAM 30KB

Prescaler

(5 channels)

UART

(5 channels)

8-/10-bit

A/D

converter

24 channels

10-bit

D/A

converter

2 channels

8-/16-bit

PPG

16 channels

2

MC-16LX core

F

Internal data bus

16-bit

I/O timer 0

Input

capture

8 channels

Output

compare

8 channels

16-bit

I/O timer 1

CAN

controller

3 channels

16-bit

reload

timer

4 channels

External

bus

FRCK0

IN7 to IN0

OUT7 to OUT0

FRCK1

RX2 to RX0

TX2 to TX0

TIN3 to TIN0

TOT3 to TOT0

AD15 to AD00

A23 to A16

ALE

RD

WRL

WRH

HRQ

HAK

RDY

CLK

SDA1, SDA0

SCL1, SCL0

I2C

interface

2channels

DMA

*: Support MB90V340A-102 only

DTP/

external

interrupt

Clock

monitor

INT15 to INT8

(INT15R to INT8R)

INT7 to INT0

CKOT

9

Page 26

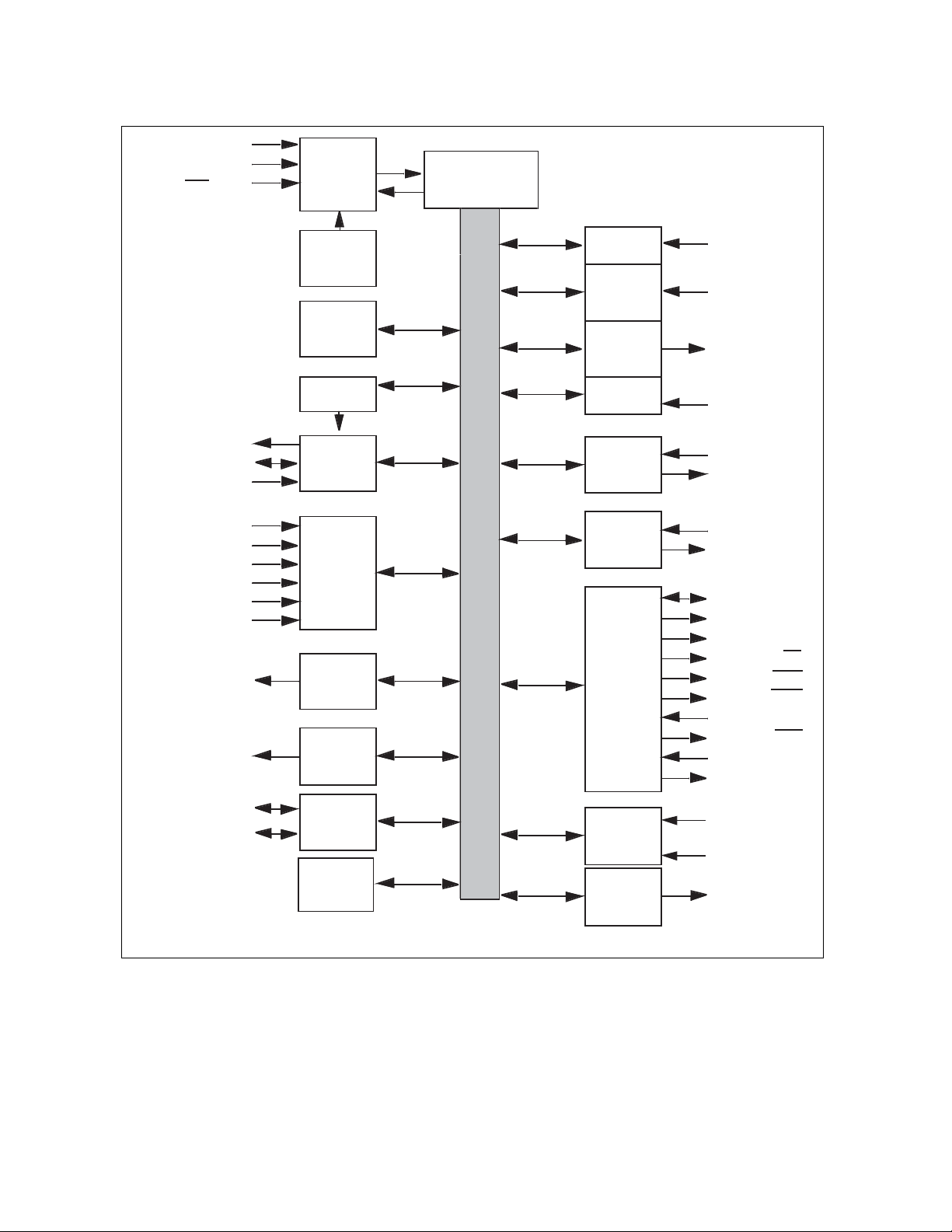

CHAPTER 1 OVERVIEW

Figure 1.2-2 Block Diagram of Evaluation Chip (MB90V340A-103/104)

X0,X1

X0A,X1A

RST

SOT4 to SOT0

SCK4 to SCK0

SIN4 to SIN0

AV

cc

AV

ss

AN23 to AN0

AVRH

AVRL

ADTG

DA01 , DA00

PPGF to PPG0

SDA1 , SDA0

SCL1 , SCL0

*

Clock

control

CR

oscillation

circuit

RAM 30KB

Prescaler

(5 channels)

UART

5 channels

8-/10-bit

A/D

converter

24 channels

F2MC-16LX core

16-bit

I/O timer 0

Input

capture

8 channels

Output

compare

8 channels

16-bit

I/O timer 1

CAN

controller

3 channels

16-bit

reload timer

4 channels

FRCK0

IN7 to IN0

OUT7 to OUT0

FRCK1

RX2 to RX0

TX2 to TX0

TIN3 to TIN0

TOT3 to TOT0

AD15 to AD00

Internal data bus

A23 to A16

ALE

10-bit D/A

converter

2 channels

External

bus

RD

WRL

WRH

HRQ

8-/16-bit

PPG

16 channels

2

I

C

Interface

2 channels

DTP/

external

interrupt

INT15 to INT8

(INT15R to INT8R)

INT7 to INT0

HAK

RDY

CLK

10

DMA

: Support MB90V340A-104 only

*

Clock

monitor

CKOT

Page 27

■ Block Diagram of Flash/Mask ROM Version

Figure 1.2-3 Block Diagram of Flash/Mask ROM Version

CHAPTER 1 OVERVIEW

X0A,X1A *

SOT0,SOT1

SCK0,SCK1

SIN0,SIN1

X0,X1

RST

1

Clock

control/

monitor *

CR

oscillation

circuit

Low voltage

detection*

CPU operation

detection*

RAM

3KB

ROM

64KB

Prescaler

(2 channels)

UART

2 channels

3

F2MC-16LX core

Input

capture

IN0 to IN3

4 channels

2

2

Internal data bus

16-bit

I/O

timer 0

CAN

controller

1 chnnal

16-bit

reload

timer

FRCK0

RX1

TX1

TIN2,TIN3

TOT2,TOT3

2 channels

AV

CC

AV

SS

AN15 to AN0

AVR

8/10-bit

A/D

converter

16 channels

ADTG

INT8,INT9R

INT10,INT11

INT12R,INT13

INT14R,INT15R

PPGF(E),PPGD(C),

PPGC(D),PPGE(F)

8/16bit

PPG

2 channels

DTP/

external

interrupt

*1: Product without S-suffix

*2: Product with T-suffix

*3: CR oscillation circuit/clock supervisor supports MB90367/T(S), MB90F367/T(S) only

11

Page 28

CHAPTER 1 OVERVIEW

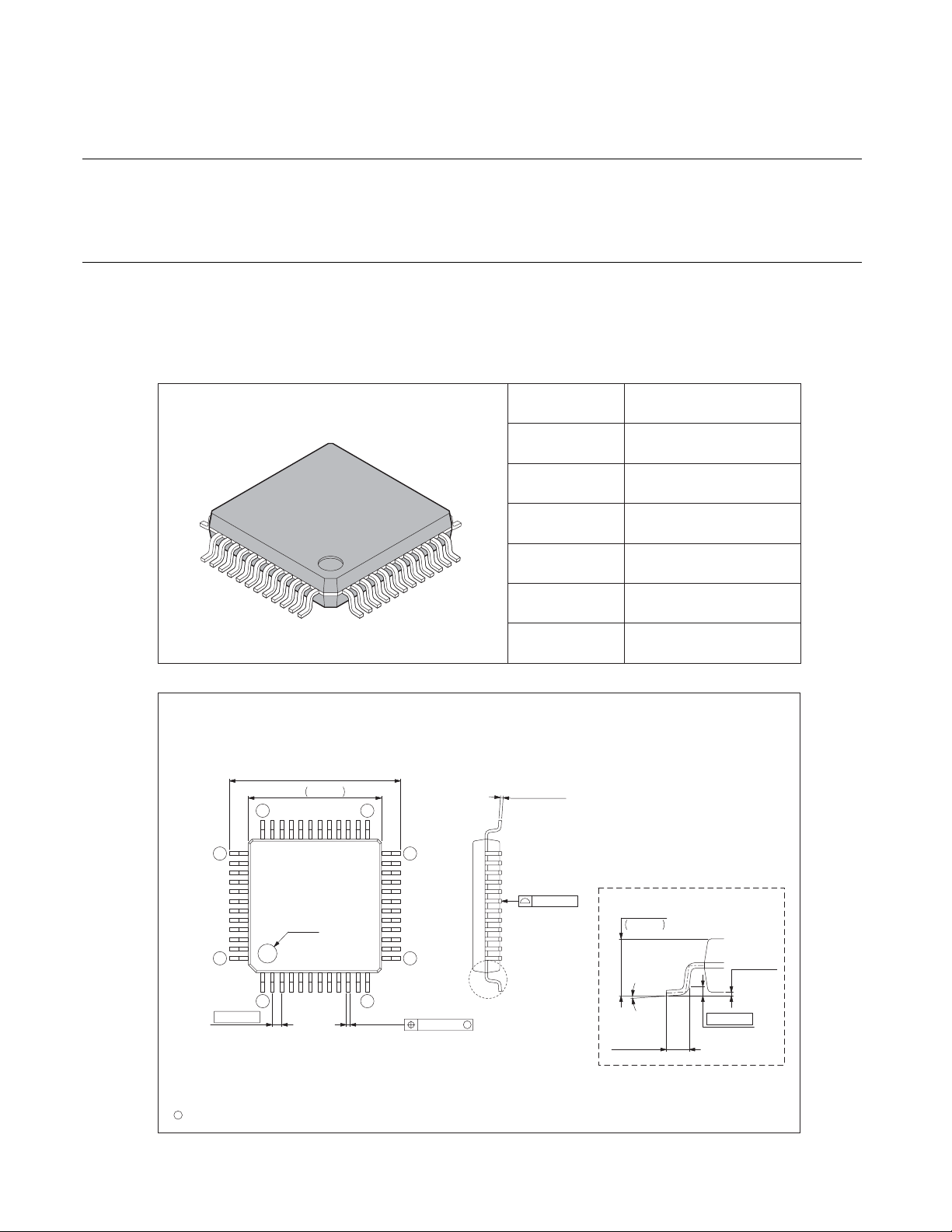

1.3 Package Dimensions

MB90360 series has a package.

Note that the dimensions show below are reference dimensions. For formal dimensions

of each package, contact us.

■ Package Dimensions

Figure 1.3-1 shows the package dimensions of LQFP-48 type.

Figure 1.3-1 Package Dimensions of LQFP-48 Type

48-pin plastic LQFP Lead pitch 0.50 mm

(FPT-48P-M26)

48-pin plastic LQFP

(FPT

-48P-M26)

9.00±0.20(.354±.008)SQ

+0.40

*

.276

7.00

–0.10

36

37

+.016

–.004

Package width ×

package length

7 × 7 mm

Lead shape Gullwing

Sealing method Plastic mold

Mounting height 1.70 mm MAX

Weight 0.17 g

Code

(Reference)

Note 1)* : These dimensions include resin protrusion.

Note 2) Pins width and pins thickness include plating thickness.

Note 3) Pins width do not include tie bar cutting remainder.

SQ

25

24

0.145±0.055

(.006±.002)

P-LFQFP48-7×7-0.50

12

INDEX

48

1

LEAD No.

0.50(.020)

C

2003 FUJITSU LIMITED F48040S-c-2-2

12

0.20±0.05

(.008±.002)

13

0.08(.003)

0.08(.003)

"A"

M

Details of "A" part

+0.20

1.50

–0.10

(Mounting height)

+.008

.059

–.004

0.10±0.10

0˚~8˚

0.60±0.15

(.024±.006)

Dimensions in mm (inches).

Note: The values in parentheses are reference values.

(.004±.004)

0.25(.010)

(Stand off)

Page 29

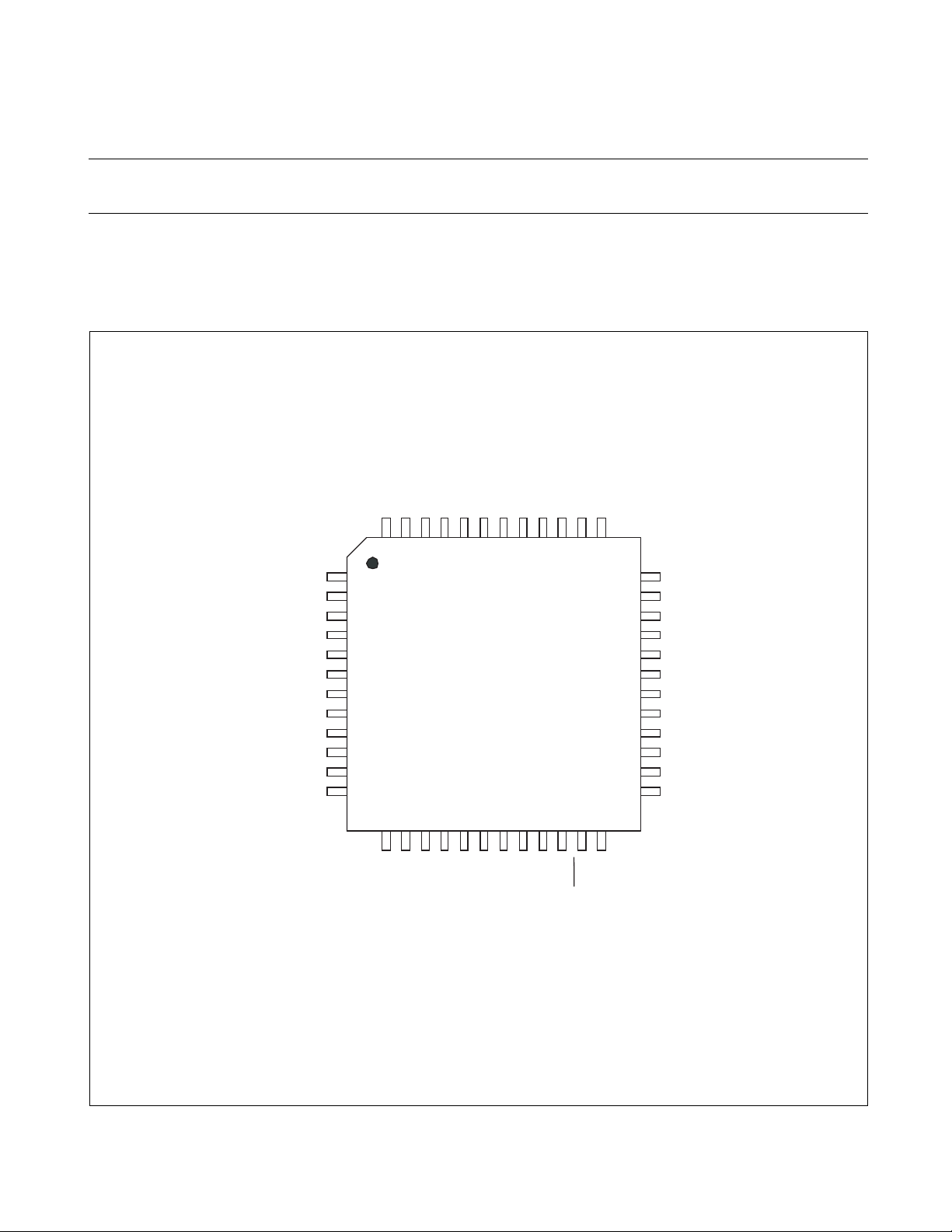

1.4 Pin Assignment

This section shows the pin assignments for the MB90360 series.

■ Pin assignment (LQFP-48)

Figure 1.4-1 shows the pin assignments of LQFP-48 type.

Figure 1.4-1 Pin Assignment (LQFP-48)

(TOP VIEW)

P84/SCK0/INT15R

P83/SOT0/TOT2

P42/RX1/INT9R

P43/TX1

P86/SOT1

P87/SCK1

AVss

X1A/P41 *1

X0A/P40 *1

P82/SIN0/INT14R/TIN2

P44/FRCK0

P85/SIN1

CHAPTER 1 OVERVIEW

AVcc

AVR

P60/AN0

P61/AN1

P62/AN2

P63/AN3

P64/AN4

P65/AN5

P66/AN6/PPGC(D)

P67/AN7/PPGE(F)

P80/ADTG/INT12R

P50/AN8

4847464544434241403938

1

2

3

4

5

6

7

8

9

10

11

12

1314151617181920212223

P51/AN9

P52/AN10

TOP VIEW

P53/AN11/TIN3

P55/AN13/INT10

P56/AN14/INT11

P57/AN15/INT13

P54/AN12/TOT3/INT8

(FPT-48P-M26)

MD2

MD1

MD0

RST

37

24

Vcc

36

35

34

33

32

31

30

29

28

27

26

25

P20

P21

P22/PPGD(C)

P23/PPGF(E)

P24/IN0

P25/IN1

P26/IN2

P27/IN3

X1

X0

C

Vss

*2

*2

*2

*2

*1: MB90F362/T, MB90362/T, MB90F367/T, MB90367/T : X0A, X1A

MB90F362S/TS, MB90362S/TS, MB90F367S/TS, MB90367S/TS : P40, P41

*2: High current port

13

Page 30

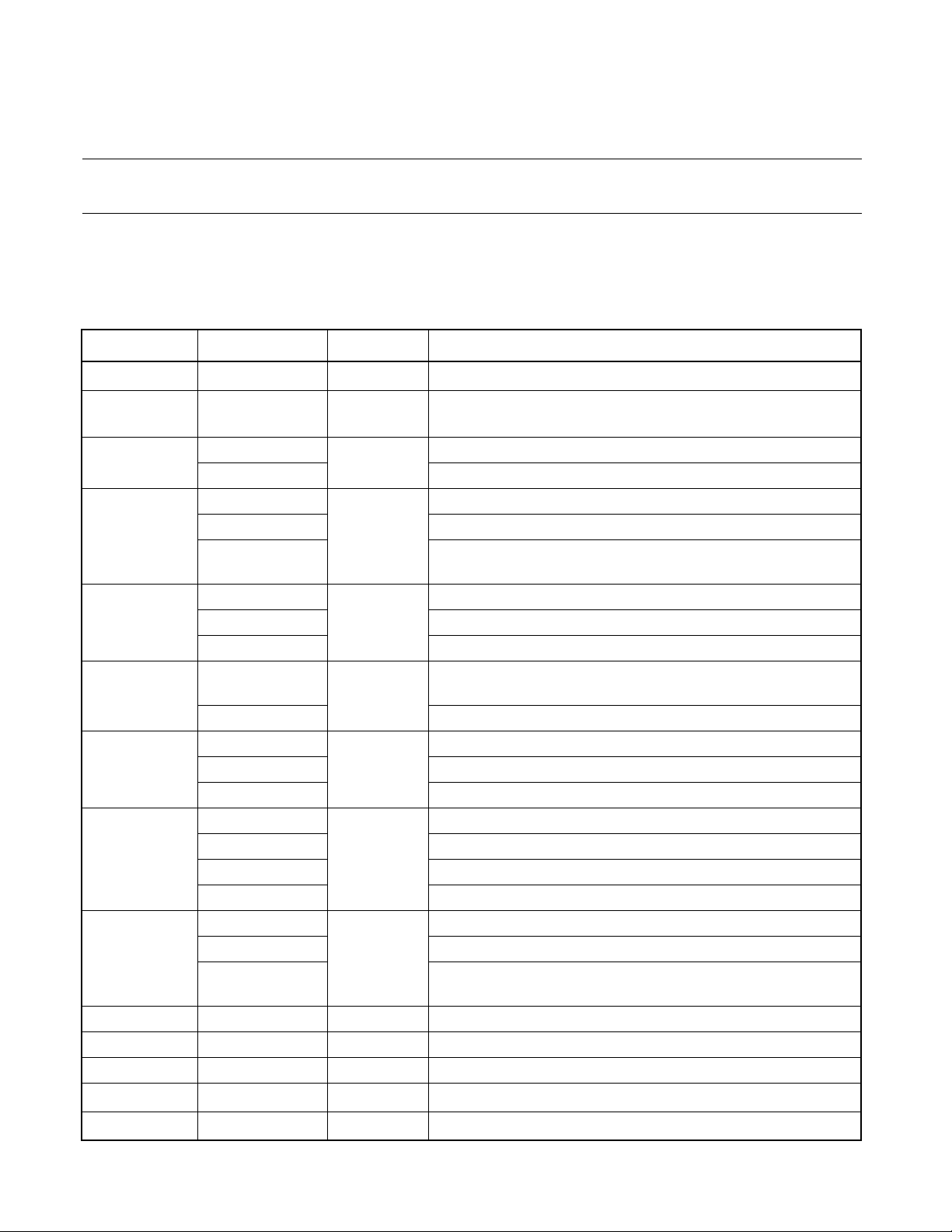

CHAPTER 1 OVERVIEW

1.5 Pin Functions

Table 1.5-1 describes the pin functions of the MB90360 series.

■ Pin Functions

Table 1.5-1 Pin Description (1/3)

Pin number Pin name Circuit type Functional description

1AV

CC

IV

power input pin for analog circuit

CC

2 AVR - Power (Vref+) input pin for A/D converter. The power supply

should not be input V

exceeding.

CC

3 to 8 P60 to P65 H General-purpose I/O port

AN0 to AN5 Analog input pin for A/D converter.

9 to 10 P66, P67 H General-purpose I/O port

AN6, AN7 Analog input pin for A/D converter

PPGC(D),

Output pin for PPG

PPGE(F)

11 P80 F General-purpose I/O port

ADTG Trigger input pin for A/D converter

INT12R External interrupt request input pin for INT12R.

12 to 14 P50 to P52 H General-purpose I/O port (I/O circuit type of P50 is different from

that of MB90V340A)

AN8 to AN10 Analog input pin for A/D converter

15 P53 H General-purpose I/O port

AN11 Analog input pin for A/D converter

TIN3 Event input pin for reload timer 3

16 P54 H General-purpose I/O port

AN12 Analog input pin for A/D converter

TOT3 Output pin for reload timer 3

INT8 External interrupt request input pin for INT8

17 to 19 P55 to P57 H General-purpose I/O port

AN13 to AN15 Analog input pin for A/D converter

INT10, INT11,

External interrupt request input pin for INT10, INT11 and INT13

INT13

20 MD2 D Input pin for selecting operation mode

21, 22 MD1,MD0 C Input pin for selecting operation mode

23 RST E Reset input

24 V

25 V

CC

SS

- Power input pin (3.5 V to 5.5 V)

- Power input pin (0 V)

14

Page 31

Table 1.5-1 Pin Description (2/3)

Pin number Pin name Circuit type Functional description

26 C I Capacity pin for stabilizing power supply.

It should be connected to higher than or equal to 0.1 µF ceramic

capacitor.

27 X0 A Oscillation input pin

28 X1 A Oscillation output pin

29 to 32 P24 to P27 G General-purpose I/O port

The register can be set to select whether to use pull-up register.

This function is enabled in single-chip mode.

IN0 to IN3 Event input pin for i nput captur e 0 to 3.

33, 34 P22 to P23 J General-purpose I/O port

The pull-up resistor ON/OFF can be set by setting the register.

This function becomes valid at shingle-chip mode.

High current output port

PPGF(E),

PPGD(C)

35, 36 P20, P21 J General-purpose I/O port

37 P85 K General-purpose I/O port

SIN1 Serial data input pin for UART1

38 P87 F General-purpose I/O port

SCK1 Clock I/O pin for UART1

39 P86 F General-purpose I/O port

SOT1 Serial data ou tput pin for UART1

40 P43 F General-purpose I/O port

TX1 TX output pin for CAN1 interface

41 P42 F General-purpose I/O port

RX1 RX input pin for CAN1 interface

INT9R External interrupt request input pin for INT9R (sub)

42 P83 F General-purpose I/O port

SOT0 Serial data ou tput pin for UART0

TOT2 Output pin for reload timer 2

43 P84 F General-purpose I/O port

SCK0 Clock I/O pin for UART0

INT15R External interrupt request input pin for INT15R

44 P82 K General-purpose I/O port

SIN0 Serial data input pin for UART0

INT14R External interrupt request input pin for INT14R

TIN2 Event input pin for reload timer 2

Output pin for PPG

The pull-up resistor ON/OFF can be set by setting the register.

This function becomes valid at shingle-chip mode.

High current output port

CHAPTER 1 OVERVIEW

15

Page 32

CHAPTER 1 OVERVIEW

Table 1.5-1 Pin Description (3/3)

Pin number Pin name Circuit type Functional description

45 P44 F General-purpose I/O port (I/O circuit t ype of P44 is different fr om

that of MB90V340A.)

FRCK0 Free-run timer 0 clock pin

46, 47 P40, P41 F General-purpose I/O port

(product with S-suffix and MB90V340A-101/103 only)

X1A, X0A B Oscillation input pin for subclock

(product without S-suffix and MB90V340A-102/104 only)

48 AV

SS

IV

power input pin for analog circuit

SS

16

Page 33

CHAPTER 1 OVERVIEW

1.6 Input-Output Circuits

Table 1.6-1 lists the input-output circuits.

■ Input-output Circuits

Table 1.6-1 I/O Circuit Types (1/4)

Type Circuit Remarks

A Oscillation circuit

X1

Xout

High-speed oscillation feedback resistor =

approx. 1 MΩ

X0

Standby control signal

B Oscillation circuit

X1A

Xout

Low-speed oscillation feedback resistor =

approx. 10 MΩ

X0A

Standby control signal

C Mask ROM device :

R

Hysteresis

input

CMOS hysteresis input pin

Flash device:

CMOS input