Page 1

130nm node CMOS Process (CS90A)

Technology Roadmap

Features

Technology Code CS90A

Transistor UHS HS ST LL

Physical Gate Length (nm) 110 110 110 110

Gate Oxide Thickness (nm) 2.9 2.9 2.9 2.9

Supply Voltage (V) 1.2 1.2 1.2 1.2

NMOS Ids (µA/µm) 780 678 570 390

PMOS Ids (µA/µm) -321 -276 -218 -150

NMOS Ioff (nA/µm) 36 4 0.18 0.005

PMOS Ioff (nA/µm) -18 -3.1 -0.22 -0.015

Gate Leak Current (nA/µm) 0.01 0.01 0.01 0.01

Basic Gate Delay (ps) 14 17 28 45

Number of Available Poly Layer 1

Number of Available Metal Layer 8Cu+1Al

Via Filling Cu Dual Damascene

ILD Structure Hybrid Low-k

SRAM Cell Size (µm2) 1.98

Dual Gate Oxide Options Available

Mixed Signal Options Available

RF Elements MIM cap., Poly Resistor, Inductor

Fuse RAM Redundancy

Mie plant

1000

500

200

100

Physical Gate Length (nm)

180-nm

Cu

CS80/80A

CS90

50

For COT

20

G: Generic, LL: Low Leakage

10

1998 2000

130-nm

Cu+Low+k

CS90A

CS100

2002 2004 2006 2008 2010 2012

90-nm

Cu+VLK

CS100A_LL

CS100A_G

CS200

65-nm

For ASIC & COT

CS200A_LL

CS200A_G

45-nm

32-nm

Year (Production Start)

Page 2

130nm node CMOS Process (CS90A)

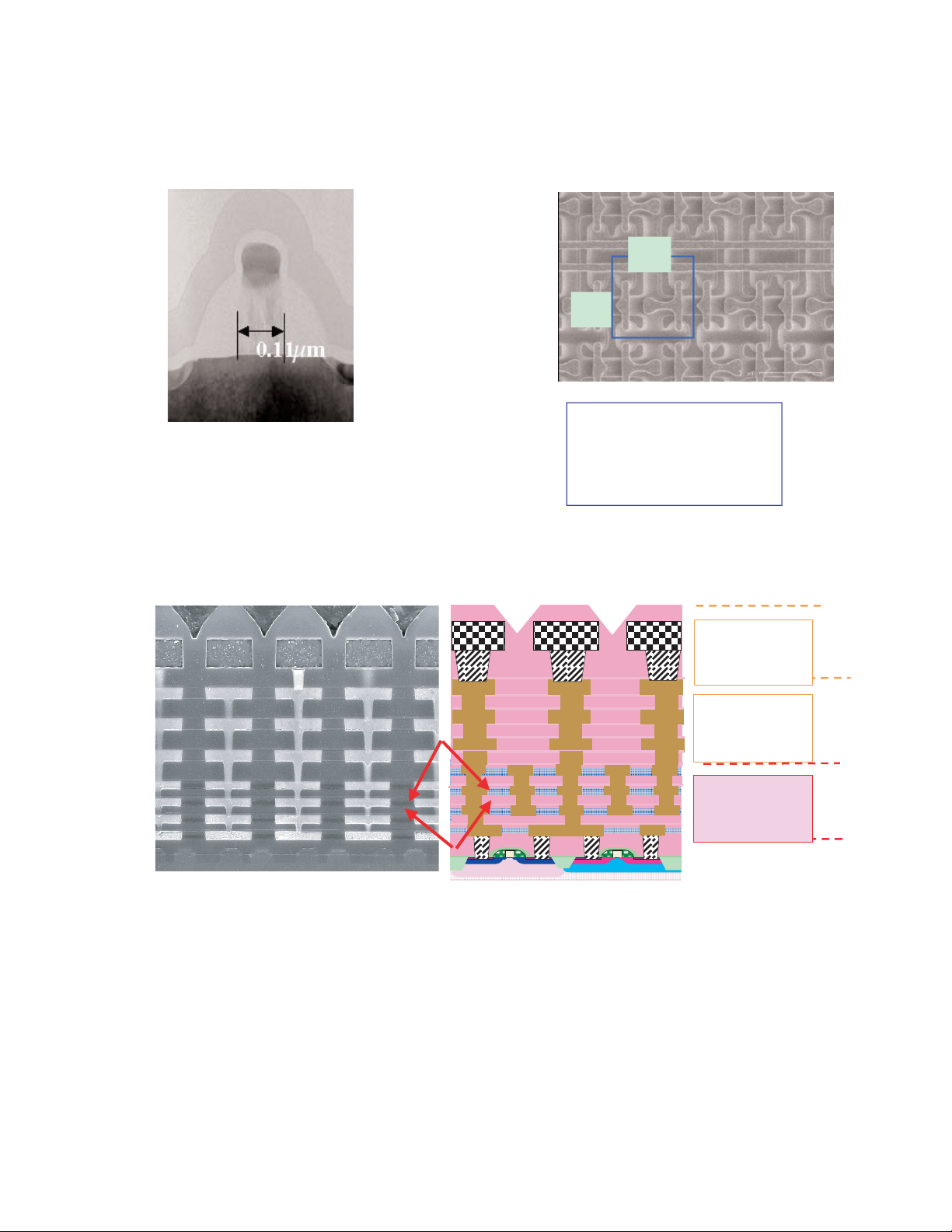

K

SRAM

Transistor

Interconnect

©2003 Fujitsu Microelectronics America, Inc.

All company and product names are trademarks or

registered trademarks of their respective owners.

Printed in the U.S.A. WFS-FS-20983-7/2003

FUJITSU MICROELECTRONICS AMERICA, INC.

Corporate Headquarters

1250 E. Arques Ave. Sunnyvale, CA 94088-3470

Tel: (800) 866-8608 Fax: (408) 737-5999

E-mail: inquiry@fma.fujitsu.com Web Site: http://www.fma.fujitsu.com

Cell Size = 1.98µm

2

(1.2µm x 1.65µm)

(2nd Generation SRAM)

1.65µm

Al

SiL

SiO2

Al

7-Cu

6-Cu

5-Cu

4-Cu

3-Cu

2-Cu

1-Cu

Global Metal:

AL (Fuse & Pad)

Pitch: 1.8µm

Semi Global Metal:

Thick Cu + SiO2

Pitch: 0.6µm

Intermediate Metal:

Thin Cu + SiLK

Pitch: 0.4µm

Loading...

Loading...