Page 1

FUJITSU SEMICONDUCTOR

CONTROLLER MANUAL

CM71-00101-5E

FR Family

32-BIT MICROCONTROLLER

INSTRUCTION MANUAL

Page 2

Page 3

FR Family

32-BIT MICROCONTROLLER

INSTRUCTION MANUAL

FUJITSU LIMITED

Page 4

Page 5

PREFACE

■ Objectives and intended reader

The FR* family CPU core features proprietary Fujitsu architecture and is designed for controller

applications using 32-bit RISC based comp uting. The architecture is optimized for use in mi crocontroller

CPU cores for built-in control applications where high-speed control is required.

This manual is written for engineers involved in the development of products using the FR family of

microcontrollers. It is designed specifically for programmers working in assembly lang uage for use with

FR family assemblers, and describes the various instructions used with FR family. Be sure to read the entire

manual carefully.

Note* that the use or non-use of coprocessors, as well as coprocessor specifications depends on the

functions of individual FR family products.

For information about coprocessor specifications, users should consult the coprocessor section of the

product documentation. Also, for the rules of assembly language grammar and the use of assembler

programs, refer to the "FR Family Assembler Manual".

* : FR, the abbreviation of FUJITSU RISC controller, is a line of products of FUJITSU Limited.

■ Trademark

The company names and brand names herein are the trademarks or registered trademarks of their respective

owners.

i

Page 6

■ Organization of this manual

This manual consists of the following 7 chapters and 1 appendix:

CHAPTER 1 FR FAMILY OVERVIEW

This chapter describes the features of the FR FAMILY CPU core, and provides sample configurations.

CHAPTER 2 MEMORY ARCHITECTURE

This chapter describes memory space in the FR family CPU.

CHAPTER 3 REGISTER DESCRIPTIONS

This chapter describes the registers used in the FR family CPU.

CHAPTER 4 RESET AND "EIT" PROCESSING

This chapter describes reset and "EIT" processing in the FR family CPU.

CHAPTER 5 PRECAUTIONARY INFORMATION FOR THE FR FAMILY CPU

This chapter presents precautionary information related to the use of the FR family CPU.

CHAPTER 6 INSTRUCTION OVERVIEW

This chapter presents an overview of the instructions used with the FR family CPU.

CHAPTER 7 DETAILED EXECUTION INSTRUCTIONS

This chapter presents each of the execution instructions used by the FR family assembler, in reference

format.

APPENDIX

The appendix section includes lists of CPU instruction s used in the FR family, as well as i nstruction map

diagrams.

ii

Page 7

• The contents of this document are subject to change without notice.

Customers are advised to consult with sales representatives before ordering.

• The information, such as descriptions of function and application circuit examples, in this document are presented solely for the

purpose of reference to show examples of operations and uses of FUJITSU semiconductor device; FUJITSU does not warrant

proper operation of the device with respect to use based on such information. When you develop equipment incorporating the

device based on such information, you must assume any responsibility arising out of such use of the information. FUJITSU

assumes no liability for any damages whatsoever arising out of the use of the information.

• Any information in this document, including descriptions of function and schematic diagrams, shall not be construed as license

of the use or exercise of any intellectual property right, such as patent right or copyright, or any other right of FUJITSU or any

third party or does FUJITSU warrant non-infringement of any third-party's intellectual property right or other right by using such

information. FUJITSU assumes no liability for any infringement of the intellectual property rights or other rights of third parties

which would result from the use of information contained herein.

• The products described in this document are designed, developed and manufactured as contemplated for general use, including

without limitation, ordinary industrial use, general office use, personal use, and household use, but are not designed, developed

and manufactured as contemplated (1) for use accompanying fatal risks or dangers that, unless extremely high safety is secured,

could have a serious effect to the public, and could lead directly to death, personal injury, severe physical damage or other loss

(i.e., nuclear reaction control in nuclear facility, aircraft flight control, air traffic control, mass transport control, medical life

support system, missile launch control in weapon system), or (2) for use requiring extremely high reliability (i.e., submersible

repeater and artificial satellite).

Please note that FUJITSU will not be liable against you and/or any third party for any claims or damages arising in connection

with above-mentioned uses of the products.

• Any semiconductor devices have an inherent chance of failure. You must protect against injury, damage or loss from such

failures by incorporating safety design measures into your facility and equipment such as redundancy, fire protection, and

prevention of over-current levels and other abnormal operating conditions.

• Exportation/release of any products described in this document may require necessary procedures in accordance with the

regulations of the Foreign Exchange and Foreign Trade Control Law of Japan and/or US export control laws.

• The company names and brand names herein are the trademarks or registered trademarks of their respective owners.

Copyright ©1997-2007 FUJITSU LIMITED All rights reserved.

iii

Page 8

iv v

Page 9

CONTENTS

CHAPTER 1 FR FAMILY OVERVIEW .............................................................................. 1

1.1 Features of the FR Family CPU Core ............... .......................................................................... ........ 2

1.2 Sample Configuration of an FR Family Device ................................................................................... 3

1.3 Sample Configuration of the FR Family CPU ..................................................................................... 4

CHAPTER 2 MEMORY ARCHITECTURE ........................................................................ 5

2.1 FR Family Memory Space .................................................................................................................. 6

2.1.1 Direct Address Area ...................................................................................................................... 7

2.1.2 Vector Table Area .......................................................................................................................... 8

2.2 Bit Order and Byte Order ..................................... ....................................... ... ... ... ............................. 10

2.3 Word Alignment ................................................................................................................................ 11

CHAPTER 3 REGISTER DESCRIPTIONS ...................................................................... 13

3.1 FR Family Register Configuration ..................................................................................................... 14

3.2 General-purpose Registers ............................................................................................................... 15

3.3 Dedicated Registers ......................................................................................................................... 17

3.3.1 Program Counter (PC) ................................................................................................................. 18

3.3.2 Program Status (PS) ................................................................................................................... 19

3.3.3 Table Base Register (TBR) ......................................................................................................... 23

3.3.4 Return Pointer (RP) ..................................................................................................................... 25

3.3.5 System Stack Pointer (SSP), User Stack Pointer (USP) ................................ .... ... ... ... ... .... ......... 27

3.3.6 Multiplication/Division Register (MD) ........................................................................................... 29

CHAPTER 4 RESET AND "EIT" PROCESSING ............................................................ 31

4.1 Reset Processing .............................................................................................................................. 33

4.2 Basic Operations in "EIT" Processing ............................................................................................... 34

4.3 Interrupts ....................... ............. ............. ............. ............. ............. ............. ............ .......................... 37

4.3.1 User Interrupts ............................................................................................................................. 38

4.3.2 Non-maskable Interrupts (NMI) ................................................................................................... 40

4.4 Exception Processing .......................................... ... ... .... ... ... ... ....................................... ... ................ 42

4.4.1 Undefined Instruction Exceptions ... ... ... ... ....................................... ... .... ... ... ................................ 43

4.5 Traps ............................. .......... .......... ...... .......... ......... .......... .......... ......... .......... ................................ 44

4.5.1 "INT" Instructions ......................................................................................................................... 45

4.5.2 "INTE" Instruction ........................................................................................................................ 46

4.5.3 Step Trace Traps ......................................................................................................................... 47

4.5.4 Coprocessor Not Found Traps .................... ... ... ... .... ...................................... .... ... ... ... ................ 48

4.5.5 Coprocessor Error Trap .. ...................................... .... ... ... ... .... ... ...................................... ............. 49

4.6 Priority Levels ................................................................................................................................... 51

Page 10

CHAPTER 5 PRECAUTIONARY INFORMATION FOR THE FR FAMILY CPU ............. 53

5.1 Pipeline Operation ........ ... .............................................................................. ... ... .... ... ... ................... 54

5.2 Pipeline Operation and Interrupt Processin g ................. ... ... ... .... ...................................................... 55

5.3 Register Hazards .............................................................................................................................. 56

5.4 Delayed Branching Processing ......................................................................................................... 58

5.4.1 Processing Non-delayed Branching Instructions ......................................................................... 60

5.4.2 Processing Delayed Branching Instructions ................................................................................ 61

CHAPTER 6 INSTRUCTION OVERVIEW ....................................................................... 63

6.1 Instruction Formats ................................. ....................................... ... ... ... .... ...................................... 64

6.2 Instruction Notation Formats ............................................................................. ... .... ... ... ... ................ 66

CHAPTER 7 DETAILED EXECUTION INSTRUCTIONS ................................................ 67

7.1 ADD (Add Word Data of Source Register to Destination Register) .................................................. 72

7.2 ADD (Add 4-bit Immediate Data to Destination Register) ................................................................. 73

7.3 ADD2 (Add 4-bit Immediate Data to Destination Register) ............................................................... 74

7.4 ADDC (Add Word Data of Source Register and Carry Bit to Destination Register) ......................... 75

7.5 ADDN (Add Word Data of Source Register to Destination Register) ............................................... 76

7.6 ADDN (Add Immediate Data to Destination Register) ...................................................................... 77

7.7 ADDN2 (Add Immediate Data to Destination Register) .................................................................... 78

7.8 SUB (Subtract Word Data in Source Register from Destination Register) ....................................... 79

7.9 SUBC (Subtract Word Data in Source Register and Carry Bit from Destination Register) ............... 80

7.10 SUBN (Subtract Word Data in Source Register from Destination Register) ..................................... 81

7.11 CMP (Compare Word Data in Source Register and Destination Register) ...................................... 82

7.12 CMP (Compare Immediate Data of Source Register and Destination Register) .............................. 83

7.13 CMP2 (Compare Immediate Data and Destination Register) ........................................................... 84

7.14 AND (And Word Data of Source Register to Destination Register) .................................................. 85

7.15 AND (And Word Data of Source Register to Data in Memory) ......................................................... 86

7.16 ANDH (And Half-word Data of Source Register to Data in Memory) ................................................ 88

7.17 ANDB (And Byte Data of Source Register to Data in Memory) ........................................................ 90

7.18 OR (Or Word Data of Source Register to Destination Register) ....................................................... 92

7.19 OR (Or Word Data of Source Register to Data in Memory) .............................................................. 93

7.20 ORH (Or Half-word Data of Source Register to Data in Memory) .................................................... 95

7.21 ORB (Or Byte Data of Source Register to Data in Memory) ............................................................. 97

7.22 EOR (Exclusive Or Word Data of Source Register to Destination Register) .................................... 99

7.23 EOR (Exclusive Or Word Data of Source Register to Data in Memory) ......................................... 100

7.24 EORH (Exclusive Or Half-word Data of Source Register to Data in Memory) ................................ 102

7.25 EORB (Exclusive Or Byte Data of Source Register to Data in Memory ) ................. ... ... ................. 104

7.26 BANDL (And 4-bit Immediate Data to Lower 4 Bits of Byte Data in Memory) ................................ 106

7.27 BANDH (And 4-bit Immediate Data to Higher 4 Bits of Byte Da ta in Mem or y) ............................... 108

7.28 BORL (Or 4-bit Immediate Data to Lower 4 Bits of Byte Data in Memory) ..................................... 110

7.29 BORH (Or 4-bit Immediate Data to Higher 4 Bits of Byte Data in Me m ory ) ............................... ... . 112

7.30 BEORL (Eor 4-bit Immediate Data to Lower 4 Bits of Byte Data in Memory) ................................. 114

7.31 BEORH (Eor 4-bit Immediate Data to Higher 4 Bits of Byte Data in Memory) ............................... 116

7.32 BTSTL (Test Lower 4 Bits of Byte Data in Memory) ....................................................................... 118

7.33 BTSTH (Test Higher 4 Bits of Byte Data in Memory) ..................................................................... 119

7.34 MUL (Multiply Word Data) .............................................................................................................. 120

vi

Page 11

7.35 MULU (Multiply Unsigned Word Data) ............................................................................................ 122

7.36 MULH (Multiply Half-word Data) ..................................................................................................... 124

7.37 MULUH (Multiply Unsigned Half-word Data) .......................... ....................................... ... ... .... ... ... . 126

7.38 DIV0S (Initial Setting Up for Signed Division) ................................................................................. 128

7.39 DIV0U (Initial Setting Up for Unsigned Division) ............................................................................. 130

7.40 DIV1 (Main Process of Division) ..................................................................................................... 132

7.41 DIV2 (Correction when Remainder is 0) ......................................................................................... 134

7.42 DIV3 (Correction when Remainder is 0) ......................................................................................... 136

7.43 DIV4S (Correction Answer for Signed Division) ............................................................................. 137

7.44 LSL (Logical Shift to the Left Direction) ...................................................................... ... ... ... ........... 138

7.45 LSL (Logical Shift to the Left Direction) ...................................................................... ... ... ... ........... 139

7.46 LSL2 (Logical Shift to the Left Direction) ........................................................................................ 140

7.47 LSR (Logical Shift to the Right Direction) ....................................................................................... 141

7.48 LSR (Logical Shift to the Right Direction) ....................................................................................... 142

7.49 LSR2 (Logical Shift to the Right Direction) ..................................................................................... 143

7.50 ASR (Arithmetic Shift to the Right Direction) ................................. ...................................... .... .. ..... 144

7.51 ASR (Arithmetic Shift to the Right Direction) ................................. ...................................... .... .. ..... 145

7.52 ASR2 (Arithmetic Shift to the Right Direction) ................................................................................ 146

7.53 LDI:32 (Load Immediate 32-bit Data to Destination Register) ........................................................ 147

7.54 LDI:20 (Load Immediate 20-bit Data to Destination Register) ........................................................ 148

7.55 LDI:8 (Load Immediate 8-bit Data to Destination Register) ............................................................ 149

7.56 LD (Load Word Data in Memory to Register) ................................... ....................................... ... ... . 150

7.57 LD (Load Word Data in Memory to Register) ................................... ....................................... ... ... . 151

7.58 LD (Load Word Data in Memory to Register) ................................... ....................................... ... ... . 152

7.59 LD (Load Word Data in Memory to Register) ................................... ....................................... ... ... . 153

7.60 LD (Load Word Data in Memory to Register) ................................... ....................................... ... ... . 154

7.61 LD (Load Word Data in Memory to Register) ................................... ....................................... ... ... . 155

7.62 LD (Load Word Data in Memory to Program Status Reg iste r) ................................ ... .................... 157

7.63 LDUH (Load Half-word Data in Memory to Register) ..................................................................... 159

7.64 LDUH (Load Half-word Data in Memory to Register) ..................................................................... 160

7.65 LDUH (Load Half-word Data in Memory to Register) ..................................................................... 161

7.66 LDUB (Load Byte Data in Memory to Register) .............................................................................. 162

7.67 LDUB (Load Byte Data in Memory to Register) .............................................................................. 163

7.68 LDUB (Load Byte Data in Memory to Register) .............................................................................. 164

7.69 ST (Store Word Data in Register to Memory) ................................................................................. 165

7.70 ST (Store Word Data in Register to Memory) ................................................................................. 166

7.71 ST (Store Word Data in Register to Memory) ................................................................................. 167

7.72 ST (Store Word Data in Register to Memory) ................................................................................. 168

7.73 ST (Store Word Data in Register to Memory) ................................................................................. 169

7.74 ST (Store Word Data in Register to Memory) ................................................................................. 170

7.75 ST (Store Word Data in Program Status Register to Memory) ....................................................... 171

7.76 STH (Store Half-word Data in Register to Memory) ....................................................................... 172

7.77 STH (Store Half-word Data in Register to Memory) ....................................................................... 173

7.78 STH (Store Half-word Data in Register to Memory) ....................................................................... 174

7.79 STB (Store Byte Data in Register to Memory) ................................................................................ 175

7.80 STB (Store Byte Data in Register to Memory) ................................................................................ 176

7.81 STB (Store Byte Data in Register to Memory) ................................................................................ 177

vii

Page 12

7.82 MOV (Move Word Data in Source Register to Destination Register) ............................................. 178

7.83 MOV (Move Word Data in Source Register to Destination Register) ............................................. 179

7.84 MOV (Move Word Data in Program Status Register to Destination Register) ................................ 180

7.85 MOV (Move Word Data in Source Register to Destination Register) ............................................. 181

7.86 MOV (Move Word Data in Source Register to Program Status Register) ...................................... 182

7.87 JMP (Jump) .................................................................................................................................... 184

7.88 CALL (Call Subroutine) .............. ... .... ... ... ....................................... ... ... ... .... .................................... 185

7.89 CALL (Call Subroutine) .............. ... .... ... ... ....................................... ... ... ... .... .................................... 186

7.90 RET (Return from Subroutine) ........................................................................................................ 187

7.91 INT (Software Interrupt) .................................................................... ... ... .... ... ................................. 188

7.92 INTE (Software Interrupt for Emulator) ................... ... ....................................... ... .... ... ... ................. 190

7.93 RETI (Return from Interrupt) ............. ... ....................................... ... ... ... ... ........................................ 192

7.94 Bcc (Branch Relative if Condition Satisfied) ................................................................................... 194

7.95 JMP:D (Jump) ................................................................................................................................. 196

7.96 CALL:D (Call Subroutine) ............................................................................................................... 197

7.97 CALL:D (Call Subroutine) ............................................................................................................... 199

7.98 RET:D (Return from Subroutine) .................................................................................................... 201

7.99 Bcc:D (Branch Relative if Condition Satisfied) ................................................................................ 203

7.100 DMOV (Move Word Data from Direct Address to Register) ........................................................... 205

7.101 DMOV (Move Word Data from Register to Direct Address) ........................................................... 206

7.102 DMOV (Move Word Data from Direct Address to Post Increment Register Indirect Address)

......................................................................................................................................................... 207

7.103 DMOV (Move Word Data from Post Increment Register Indirect Address to Direct Address)

......................................................................................................................................................... 209

7.104 DMOV (Move Word Data from Direct Add ress to Pre-decrement Register Indirect Address)

......................................................................................................................................................... 211

7.105 DMOV (Move Word Data from Post Increment Register Indirect Address to Direct Address)

......................................................................................................................................................... 213

7.106 DMOVH (Move Half-word Data from Direct Address to Register) .................................................. 215

7.107 DMOVH (Move Half-word Data from Register to Direct Address) .................................................. 216

7.108 DMOVH (Move Half-word Data from Direc t Address to Post Increment Register Indirect Address)

......................................................................................................................................................... 217

7.109 DMOVH (Move Half-word Data from Post Increment Register Indirect Address to Direct Address)

......................................................................................................................................................... 219

7.110 DMOVB (Move Byte Data from Direct Address to Register) .......................................................... 221

7.111 DMOVB (Move Byte Data from Register to Direct Address) .......................................................... 222

7.112 DMOVB (Move Byte Data from Direct Address to Post Increment Register Indirect Address)

......................................................................................................................................................... 223

7.113 DMOVB (Move Byte Data from Post Increment Register Indirect Address to Direct Address)

......................................................................................................................................................... 225

7.114 LDRES (Load Word Data in Memory to Resource) ........................................................................ 227

7.115 STRES (Store Word Data in Resource to Memory) ....................................................................... 228

7.116 COPOP (Coprocessor Operation) .................................................................................................. 229

7.117 COPLD (Load 32-bit Data from Register to Coprocessor Register) ............................................... 231

7.118 COPST (Store 32-bit Data from Coprocessor Register to Register) .............................................. 233

7.119 COPSV (Save 32-bit Data from Coprocessor Register to Register) ............................................... 235

7.120 NOP (No Operation) ....................................................................................................................... 237

7.121 ANDCCR (And Condition Code Register and Immediate Data) . ... ... ... ... .... ... ... ... .... ... ... ... ... .... ... ... . 238

7.122 ORCCR (Or Condition Code Register and Imm edi at e Da ta) ............................ .............................. 239

viii

Page 13

7.123 STILM (Set Immediate Data to Interrupt Level Mask Register) ...................................................... 240

7.124 ADDSP (Add Stack Pointer and Immediate Data) .......................................................................... 241

7.125 EXTSB (Sign Extend from Byte Data to Word Data) ...................................................................... 242

7.126 EXTUB (Unsign Extend from Byte Data to Word Data) .................................................................. 243

7.127 EXTSH (Sign Extend from Byte Data to Word Data) ........... ... .... ... ... .......................................... ... . 244

7.128 EXTUH (Unsigned Extend from Byte Data to Word Data) .............................................................. 245

7.129 LDM0 (Load Multiple Registers) ..................................................................................................... 246

7.130 LDM1 (Load Multiple Registers) ..................................................................................................... 248

7.131 STM0 (Store Multiple Registers) ..................................................................................................... 250

7.132 STM1 (Store Multiple Registers) ..................................................................................................... 252

7.133 ENTER (Enter Function) ................... ... ... ... ... ....................................... ... .... ... ... ... ........................... 254

7.134 LEAVE (Leave Function) ................................................................................................................ 256

7.135 XCHB (Exchange Byte Data) .......................................................................................................... 258

APPENDIX ......................................................................................................................... 261

APPENDIX A Instruction Lists .................................................................................................................... 262

A.1 Symbols Used in Instruction Lists .................................................................................................. 263

A.2 Instruction Lists ............................................................................ ... ... ... .... ... ... .............................. 265

APPENDIX B Instruction Maps ................................................................................................................... 274

B.1 Instruction Map ............................................................................................................................... 275

B.2 "E" Format ...................................................................................................................................... 276

INDEX...................................................................................................................................277

ix

Page 14

x

Page 15

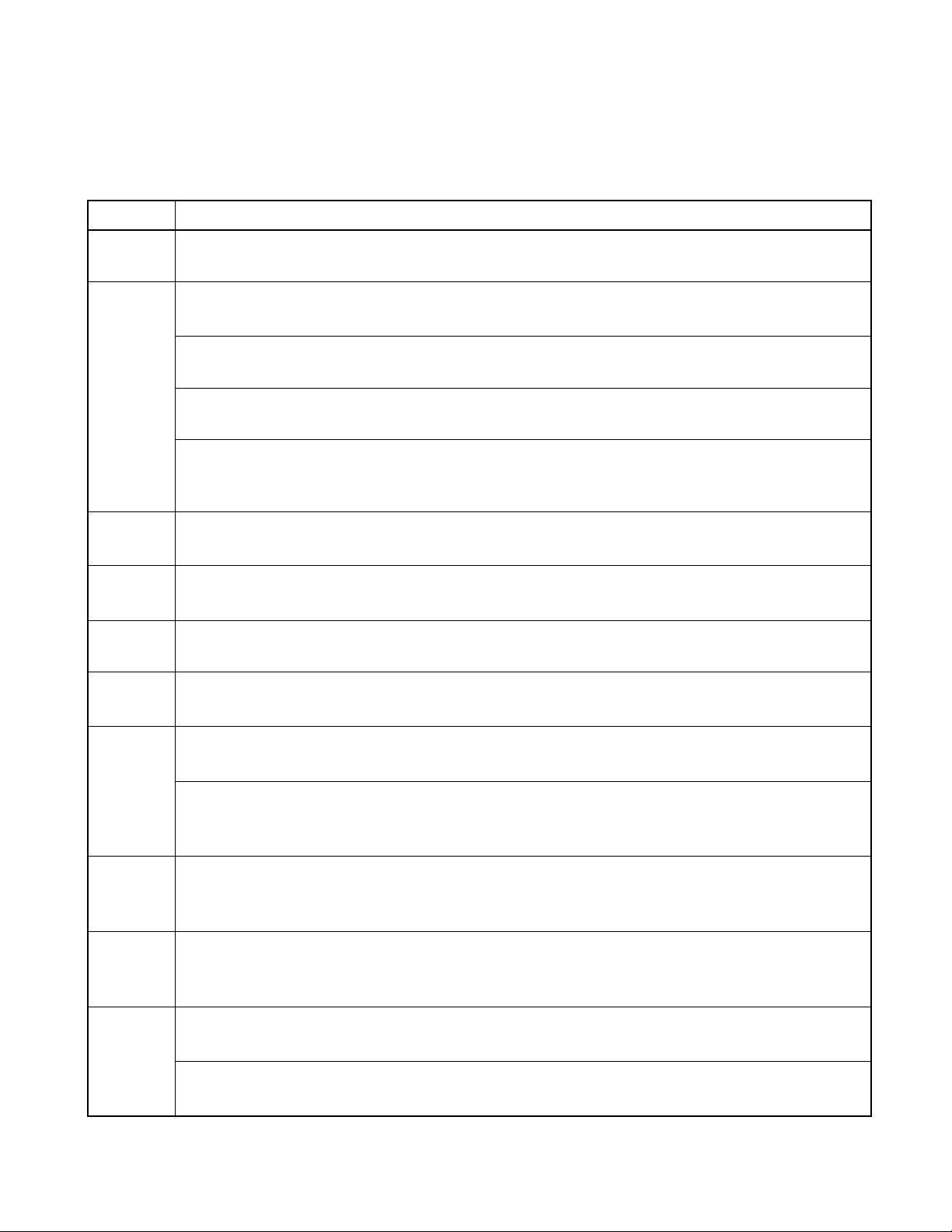

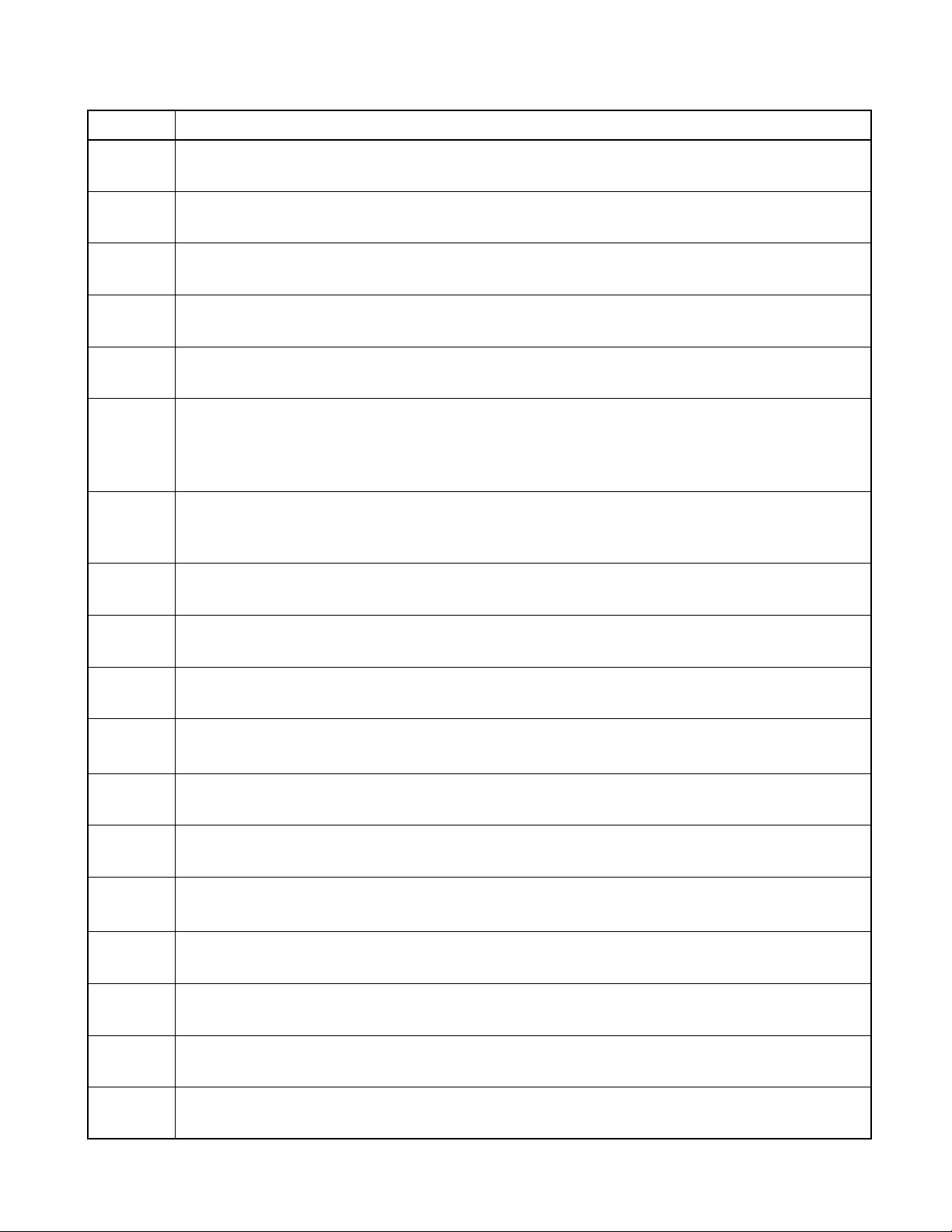

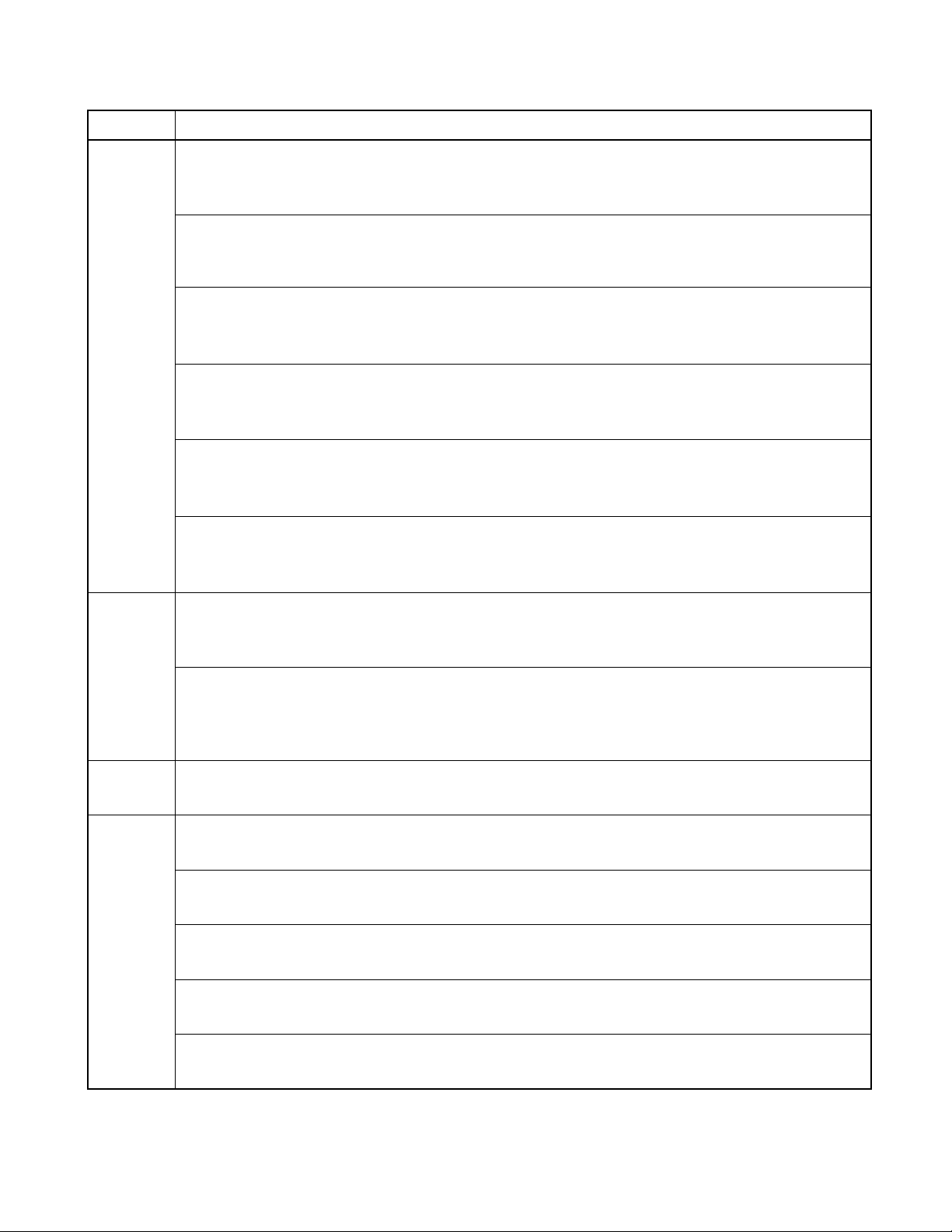

Main changes in this edition

Page Changes (For details, refer to main body.)

18

20

23

-

i

9

Be sure to refer to the "Check Sheet" for the latest cautions on development. is changed.

("Check Sheet" is seen at the following support page... is deleted.)

"■ Objectives and intended reader" is changed.

( "FR" → "FR*" )

"■ Objectives and intended reader" is changed.

( " *: " is added. )

"PREFACE" is changed.

( "■ Trademark" is added. )

"PREFACE" is changed.

( "The company names and brand names herein are the trademarks or registered trademarks of their

respective owners." is added. )

"Table 2.1-1 Structure of a Vector Table Area" is changed.

For 3F8H, ( "No" → "Yes" )

"● Lowest Bit Value of Program Counter" is changed.

( "incremented by one, and therefore" → "incremented and therefore" )

"Figure 3.3-4 "ILM" Register Functions" is changed.

( A line from ILM to COMP is added. )

"Figure 3.3-7 Sample of Table Base Register (TBR) Operation" is changed.

( "31" → "bit31" )

27

28

28

37

"■ System Stack Pointer (SSP), User Stack Pointer (USP)" is changed.

( "ST R13", "@-R15" → "ST R13, @-R15" )

The title of "Figure 3.3-12 Example of Stack Pointer Operation in Execution of Instruction "ST R13", "@R15" when "S" Flag = 0" is changed.

( "ST R13", "@-R15" → "ST R13, @-R15" )

The title of "Figure 3.3-13 Example of Stack Pointer Operation in Execution of Instruction "ST R13", "@R15" when "S" Flag = 1" is changed.

( "ST R13", "@-R15" → "ST R13, @-R15" )

"■ Recovery from EIT handler" is changed.

( "4.2 Basic Operations in "EIT" Processing ■ Recovery from EIT handler" →

"■ Recovery from EIT handler"of "4.2 Basic Operations in "EIT" Processing" )

"4.3 Interrupts" is changed.

( "External" → "User" )

"■ Sources of Interrupts" is changed.

( "External" → "User" )

xi

Page 16

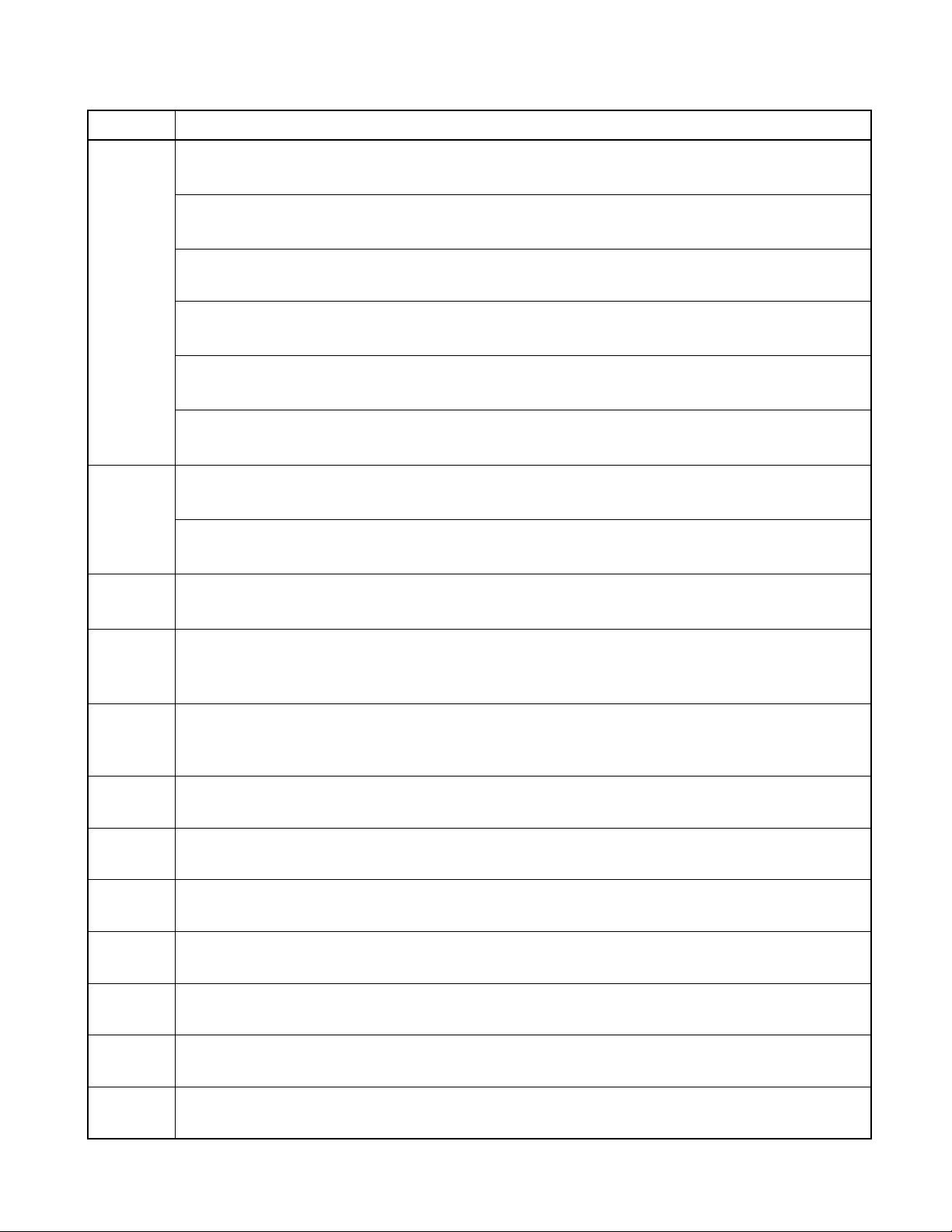

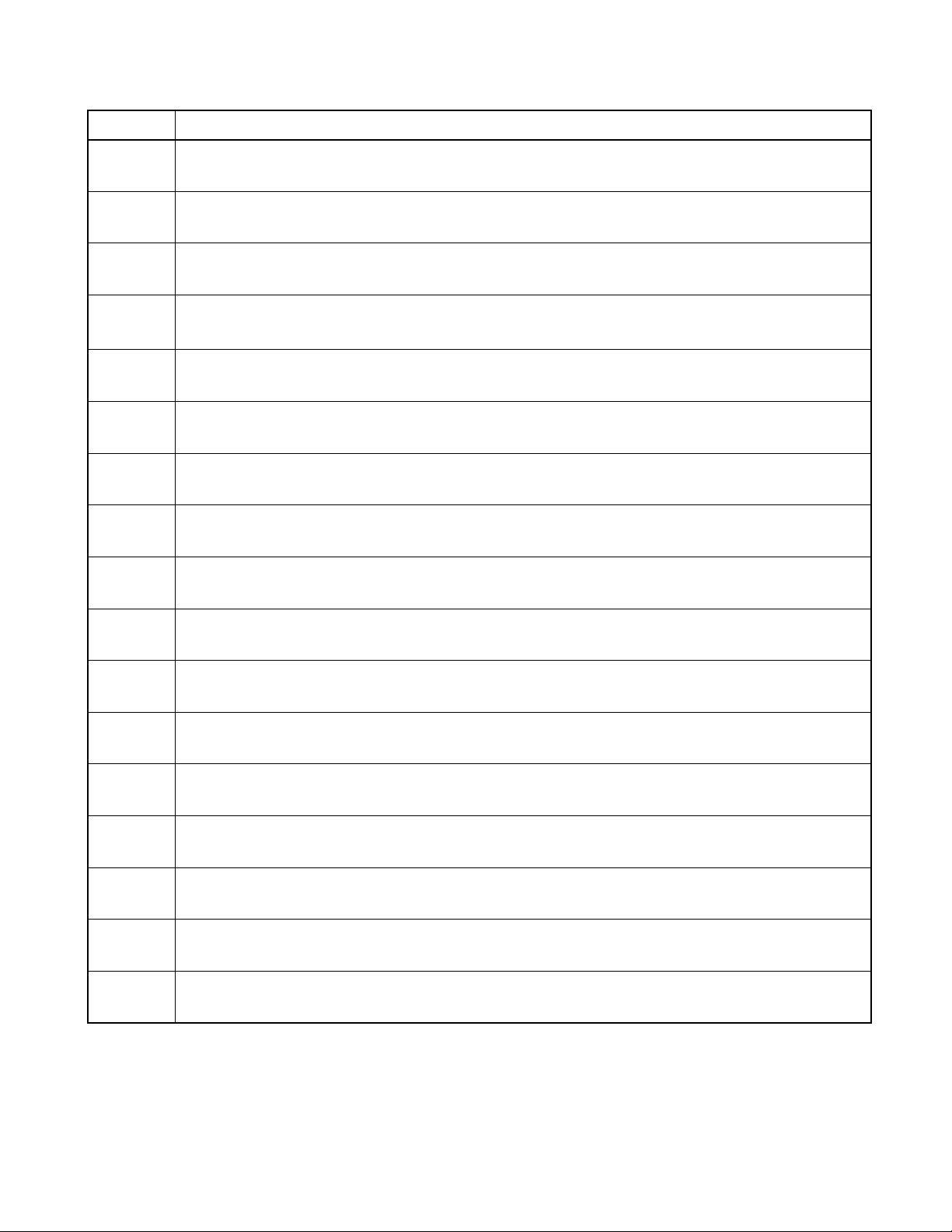

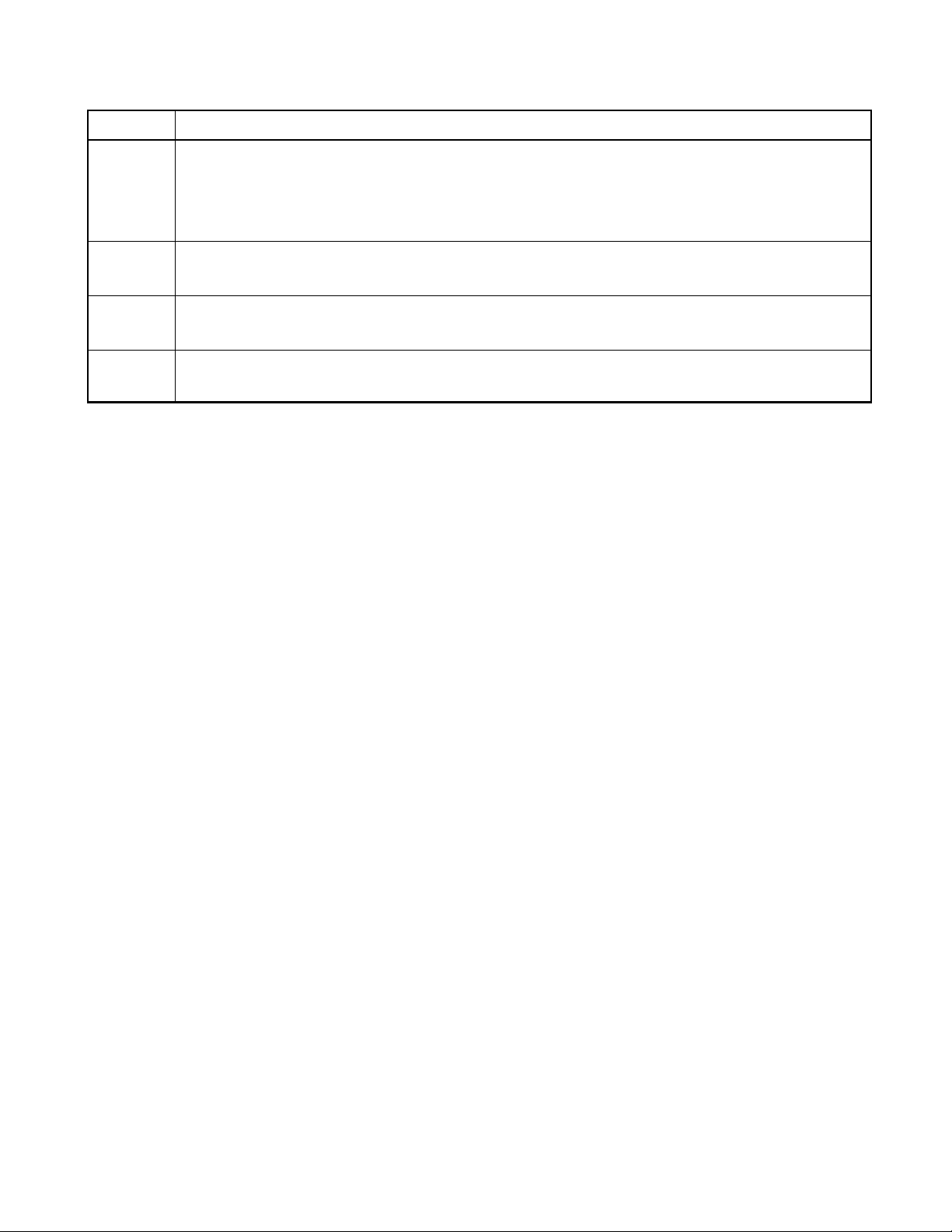

Page Changes (For details, refer to main body.)

"4.3.1 User Interrupts" is changed.

( "External" → "User" ), ( "external" → "user" )

"■ Overview of User Interrupts" is changed.

( "External" → "User" )

"■ Overview of User Interrupts" is changed.

( "Interrupts are referred to as "external" when they originate outside the CPU." is deleted. )

38

39

"■ Conditions for Acceptance of User Interrupt Requests" is changed.

( "External" → "User" )

"■ Conditions for Acceptance of User Interrupt Requests" is changed.

( "The CPU accepts interrupts" → "The CPU accepts user interrupts" )

"■ Operation Following Acceptance of an User Interrupt" is changed.

( "External" → "User" ), ( "external" → "user" )

"■ How to Use User Interrupts" is changed.

( "External" → "User" ), ( "external" → "user" )

"Figure 4.3-1 How to Use User Interrupts" is changed.

( "External" → "User" )

51

62

66

72

75

79

80

81

"Table 4.6-1 Priority of "EIT" Requests" is changed.

( "External" → "User"), ("INT" → "INTE")

"■ Examples of Programing Delayed Branching Instructions" is changed.

( The position of comment ";not satisfy" is changed. )

( R12 → R13)

"● Calculations are designated by a mnemonic placed between operand 1 and operand 2, with the results

stored at operand 2" is changed.

( The position of R2 is changed. )

"7.1 ADD (Add Word Data of Source Register to Destination Register)" is changed.

( "Instruction bit pattern : 1010 0110 0010 0011" is added. )

"7.4 ADDC (Add Word Data of Source Register and Carry Bit to Destination Register)" is changed.

( "Instruction bit pattern : 1010 0111 0010 0011" is added. )

"7.8 SUB (Subtract Word Data in Source Register from Destination Register)" is changed.

( "Instruction bit pattern : 1010 1100 0010 0011" is added. )

"7.9 SUBC (Subtract Word Data in Source Register and Carry Bit from Destination Register)" is changed.

( "Instruction bit pattern : 1010 1101 0010 0011" is added. )

"7.10 SUBN (Subtract Word Data in Source Register from Destination Register)" is changed.

( "Instruction bit pattern : 1010 1110 0010 0011" is added. )

82

85

"7.11 CMP (Compare Word Data in Source Register and Destination Register)" is changed.

( "Instruction bit pattern : 1010 1010 0010 0011" is added. )

"7.14 AND (And Word Data of Source Register to Destination Register)" is changed.

( "Instruction bit pattern : 1000 0010 0010 0011" is added. )

xii

Page 17

Page Changes (For details, refer to main body.)

87

89

91

92

94

96

98

99

101

"7.15 AND (And Word Data of Source Register to Data in Memory)" is changed.

( "Instruction bit pattern : 1000 0100 0010 0011" is added.)

"7.16 ANDH (And Half-word Data of Source Register to Data in Memory)" is changed.

( "Instruction bit pattern : 1000 0101 0010 0011" is added. )

"7.17 ANDB (And Byte Data of Source Register to Data in Memory)" is changed.

( "Instruction bit pattern : 1000 0110 0010 0011" is added. )

"7.18 OR (Or Word Data of Source Register to Destination Register)" is changed.

( "Instruction bit pattern : 1001 0010 0010 0011" is added.)

"7.19 OR (Or Word Data of Source Register to Data in Memory)" is changed.

( "Instruction bit pattern : 1001 0100 0010 0011" is added. )

"7.20 ORH (Or Half-word Data of Source Register to Data in Memory)" is changed.

( "Instruction bit pattern : 1001 0101 0010 0011" is added. )

"7.21 ORB (Or Byte Data of Source Register to Data in Memory)" is changed.

( "Instruction bit pattern : 1001 0110 0010 0011" is added. )

"7.22 EOR (Exclusive Or Word Data of Source Register to Destination Register)" is changed.

( "Instruction bit pattern : 1001 1010 0010 0011" is added. )

"7.23 EOR (Exclusive Or Word Data of Source Register to Data in Memory)" is changed.

( "Instruction bit pattern : 1001 1100 0010 0011" is added. )

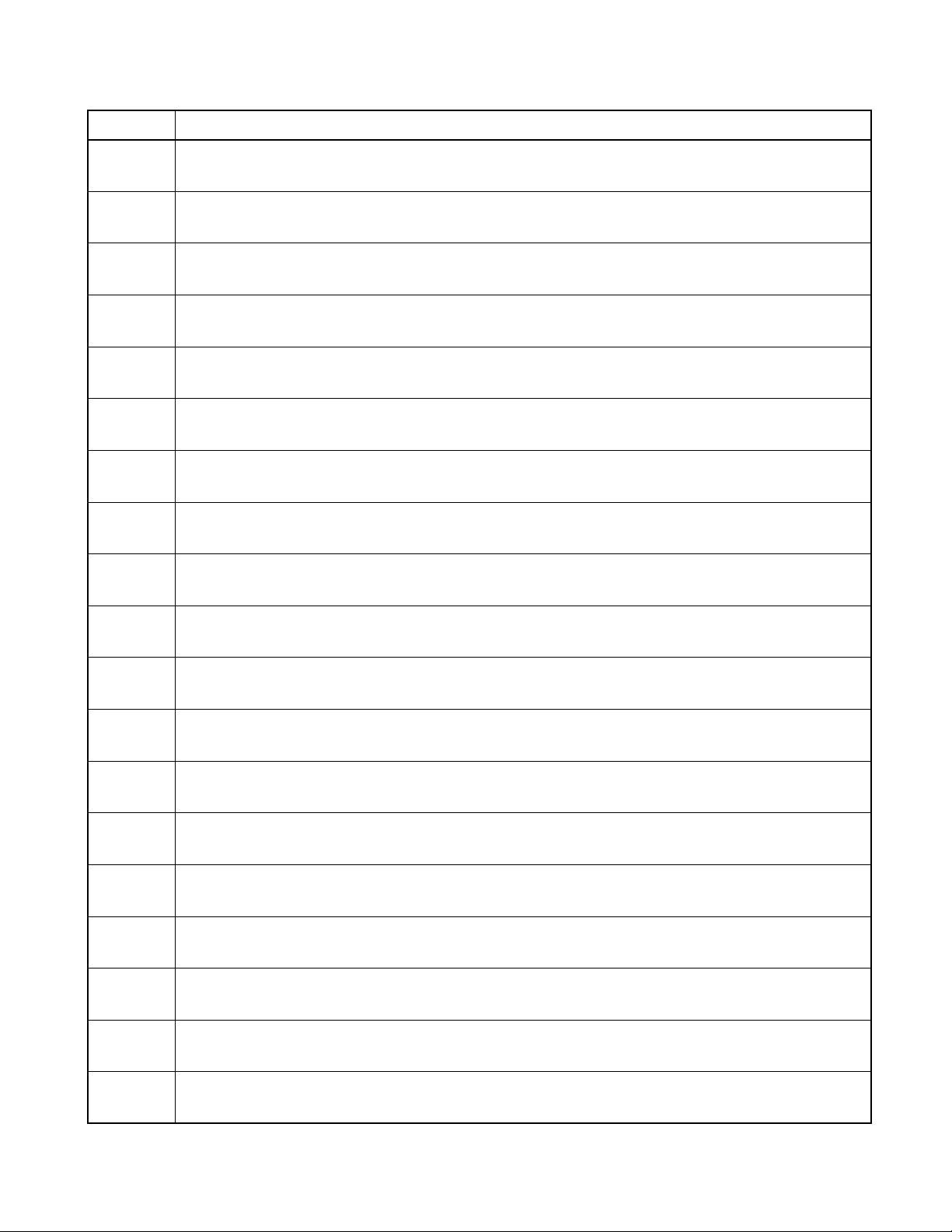

103

105

121

123

125

127

129

131

133

"7.24 EORH (Exclusive Or Half-word Data of Source Register to Data in Memory)" is changed.

( "Instruction bit pattern : 1001 1101 0010 0011" is added. )

"7.25 EORB (Exclusive Or Byte Data of Source Register to Data in Memory)" is changed.

( "Instruction bit pattern : 1001 1110 0010 0011" is added. )

"7.34 MUL (Multiply Word Data)" is changed.

( "Instruction bit pattern : 1010 1111 0010 0011" is added. )

"7.35 MULU (Multiply Unsigned Word Data)" is changed.

( "Instruction bit pattern : 1010 1011 0010 0011" is added. )

"7.36 MULH (Multiply Half-word Data)" is changed.

( "Instruction bit pattern : 1011 1111 0010 0011" is added. )

"7.37 MULUH (Multiply Unsigned Half-word Data)" is changed.

( "Instruction bit pattern : 1011 1011 0010 0011" is added. )

"7.38 DIV0S (Initial Setting Up for Signed Division)" is changed.

( "Instruction bit pattern : 1001 0111 0100 0010" is added. )

"7.39 DIV0U (Initial Setting Up for Unsigned Division)147/308" is changed.

( "Instruction bit pattern : 1001 0111 0101 0010" is added. )

"7.40 DIV1 (Main Process of Division)" is changed.

( "Instruction bit pattern : 1001 0111 0110 0010" is added. )

135

"7.41 DIV2 (Correction when Remainder is 0)" is changed.

( "Instruction bit pattern : 1001 0111 0111 0010" is added. )

xiii

Page 18

Page Changes (For details, refer to main body.)

136

137

138

141

144

147

148

149

"7.42 DIV3 (Correction when Remainder is 0)" is changed.

( "Instruction bit pattern : 1001 1111 0110 0000" is added. )

"7.43 DIV4S (Correction Answer for Signed Division)" is changed.

( "Instruction bit pattern : 1001 1111 0111 0000" is added. )

"7.44 LSL (Logical Shift to the Left Direction)" is changed.

( "Instruction bit pattern : 1011 0110 0010 0011" is added. )

"7.47 LSR (Logical Shift to the Right Direction)" is changed.

( "Instruction bit pattern : 1011 0010 0010 0011" is added. )

"7.50 ASR (Arithmetic Shift to the Right Direction)" is changed.

( "Instruction bit pattern : 1011 1010 0010 0011" is added. )

"7.53 LDI:32 (Load Immediate 32-bit Data to Destination Register)" is changed.

( "Instruction bit pattern : 1001 1111 1000 0011

: 1000 0111 0110 0101

: 0100 0011 0010 0001" is added. )

"7.54 LDI:20 (Load Immediate 20-bit Data to Destination Register)" is changed.

( "Instruction bit pattern : 1001 1011 0101 0011

: 0100 0011 0010 0001" is added. )

"7.55 LDI:8 (Load Immediate 8-bit Data to Destination Register)" is changed.

( "Instruction bit pattern : 1100 0010 0001 0011" is added. )

150

151

153

154

156

157

158

159

160

"7.56 LD (Load Word Data in Memory to Register)"is changed.

( "Instruction bit pattern : 0000 0100 0010 0011" is added. )

"7.57 LD (Load Word Data in Memory to Register)" is changed.

( "Instruction bit pattern : 0000 0000 0010 0011" is added. )

"7.59 LD (Load Word Data in Memory to Register)" is changed.

( "o4" → "u4" )

"7.60 LD (Load Word Data in Memory to Register)" is changed.

( "Instruction bit pattern : 0000 0111 0000 0011" is added. )

"7.61 LD (Load Word Data in Memory to Register)" is changed.

( "Instruction bit pattern : 0000 0111 1000 0100" is added. )

"7.62 LD (Load Word Data in Memory to Program Status Register)" is changed.

Flag change: ( "Ri" → "R15")

"7.62 LD (Load Word Data in Memory to Program Status Register)" is changed.

( "Instruction bit pattern : 0000 0111 1001 0000" is added. )

"7.63 LDUH (Load Half-word Data in Memory to Register)" is changed.

( "Instruction bit pattern : 0000 0101 0010 0011" is added. )

"7.64 LDUH (Load Half-word Data in Memory to Register)" is changed.

( "Instruction bit pattern : 0000 0001 0010 0011" is added. )

162

"7.66 LDUB (Load Byte Data in Memory to Register)" is changed.

( "Instruction bit pattern : 0000 0110 0010 0011" is added. )

xiv

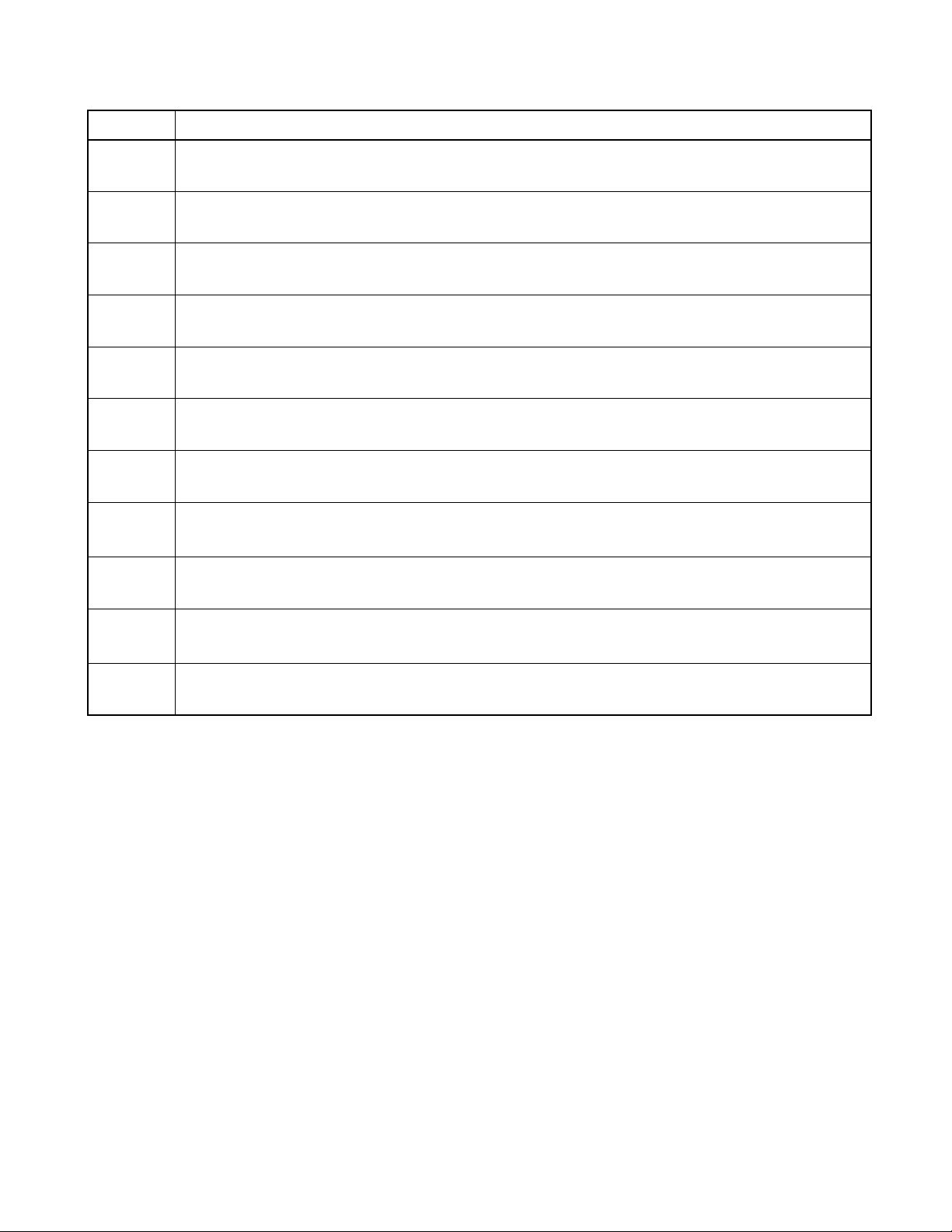

Page 19

Page Changes (For details, refer to main body.)

163

165

166

168

169

170

171

172

173

"7.67 LDUB (Load Byte Data in Memory to Register)" is changed.

( "Instruction bit pattern : 0000 0010 0010 0011" is added. )

"7.69 ST (Store Word Data in Register to Memory)" is changed.

( "Instruction bit pattern : 0001 0100 0010 0011" is added. )

"7.70 ST (Store Word Data in Register to Memory)" is changed.

( "Instruction bit pattern : 0001 0000 0010 0011" is added. )

"7.72 ST (Store Word Data in Register to Memory)" is changed.

( "o4" → "u4" )

"7.73 ST (Store Word Data in Register to Memory)" is changed.

( "Instruction bit pattern : 0001 0111 0000 0011" is added. )

"7.74 ST (Store Word Data in Register to Memory)" is changed.

( "Instruction bit pattern : 0001 0111 1000 0100" is added. )

"7.75 ST (Store Word Data in Program Status Register to Memory)" is changed.

( "Instruction bit pattern : 0001 0111 1001 0000" is added. )

"7.76 STH (Store Half-word Data in Register to Memory)" is changed.

( "Instruction bit pattern : 0001 0101 0010 0011" is added. )

"7.77 STH (Store Half-word Data in Register to Memory)" is changed.

( "Instruction bit pattern : 0001 0001 0010 0011" is added. )

175

176

178

179

180

181

183

184

"7.79 STB (Store Byte Data in Register to Memory)" is changed.

( "Instruction bit pattern : 0001 0110 0010 0011" is added. )

"7.80 STB (Store Byte Data in Register to Memory)" is changed.

( "Instruction bit pattern : 0001 0010 0010 0011" is added. )

"7.82 MOV (Move Word Data in Source Register to Destination Register)" is changed.

( "Instruction bit pattern : 1000 1011 0010 0011" is added. )

"7.83 MOV (Move Word Data in Source Register to Destination Register)" is changed.

( "Instruction bit pattern : 1011 0111 0101 0011" is added. )

"7.84 MOV (Move Word Data in Program Status Register to Destination Register)" is changed.

( "Instruction bit pattern : 0001 0111 0001 0011" is added. )

"7.85 MOV (Move Word Data in Source Register to Destination Register)" is changed.

( "Instruction bit pattern : 1011 0011 0101 0011" is added. )

"7.86 MOV (Move Word Data in Source Register to Program Status Register)" is changed.

( "Instruction bit pattern : 0000 0111 0001 0011" is added. )

"7.87 JMP (Jump)" is changed.

( "Instruction bit pattern : 1001 0111 0000 0001" is added. )

xv

Page 20

Page Changes (For details, refer to main body.)

"7.88 CALL (Call Subroutine)" is changed.

( "extension for use as the branch destination address" → "extension" )

"7.88 CALL (Call Subroutine)" is changed.

( "CALL 120H" →

185

" CALL label

...

label: ; CALL instruction address + 122

" )

H

"7.88 CALL (Call Subroutine)" is changed.

( "Instruction bit pattern : 1101 0000 1001 0000" is added. )

186

187

188

189

191

192

193

194

195

"7.89 CALL (Call Subroutine)" is changed.

( "Instruction bit pattern : 1001 0111 0001 0001" is added. )

"7.90 RET (Return from Subroutine)" is changed.

( "Instruction bit pattern : 1001 0111 0010 0000" is added. )

"7.91 INT (Software Interrupt)" is changed.

( "INT#9" to "#13", "#64", "#65" → "INT#9" to "INT#13", "INT#64", "INT#65" )

"7.91 INT (Software Interrupt)" is changed.

( "Instruction bit pattern : 0001 1111 0010 0000" is added. )

"7.92 INTE (Software Interrupt for Emulator)" is changed.

( "Instruction bit pattern : 1001 1111 0011 0000" ) is added.

"7.93 RETI (Return from Interrupt)" is changed.

( D2, D1, → S, )

"7.93 RETI (Return from Interrupt)" is changed.

( "Instruction bit pattern : 1001 0111 0011 0000" is added. )

"7.94 Bcc (Branch Relative if Condition Satisfied)" is changed.

( "extension, for use as the branch destination address." → "extension" )

"7.94 Bcc (Branch Relative if Condition Satisfied)" is changed.

( "BHI 50H" →

" BHI label

...

label: ; BHI instruction address + 50

" )

H

196

197

"7.95 JMP:D (Jump)" is changed.

( "Instruction bit pattern : 1001 1111 0000 0001" is added. )

"7.96 CALL:D (Call Subroutine)" is changed.

( "extension for use as the branch destination address" → "extension" )

xvi

Page 21

Page Changes (For details, refer to main body.)

"7.96 CALL:D (Call Subroutine)" is changed.

( "CALL : D 120H

LDI : 8 #0, R2 ; Instruction placed in delay slot" →

"CALL:D label

198

LDI : 8 #0, R2 ; Instruction placed in delay slot

...

label: ; CALL: D instruction address + 122

" )

H

"7.96 CALL:D (Call Subroutine)" is changed.

( "Instruction bit pattern : 1101 1000 1001 0000" is added. )

200

202

203

204

227

228

"7.97 CALL:D (Call Subroutine)" is changed.

( "Instruction bit pattern : 1001 1111 0001 0001" is added. )

"7.98 RET:D (Return from Subroutine)" is changed.

( "Instruction bit pattern : 1001 1111 0010 0000" is added. )

"7.99 Bcc:D (Branch Relative if Condition Satisfied)" is changed.

( "extension, for use as the branch destination address" → "extension" )

"7.99 Bcc:D (Branch Relative if Condition Satisfied)" is changed.

( "BHI :D 50H

LDI :8 #255, R1 ; Instruction placed in delay slot" →

"BHI:D label

...

LDI :8 #255, R1 ; Instruction placed in delay slot

label: ; BHI: D instruction address + 50

" )

H

"7.99 Bcc:D (Branch Relative if Condition Satisfied)" is changed.

( "Instruction bit pattern : 1111 1111 0010 1000" is changed. )

"7.114 LDRES (Load Word Data in Memory to Resource)" is changed.

( "Instruction bit pattern : 1011 1100 1000 0010" is added. )

"7.115 STRES (Store Word Data in Resource to Memory)" is changed.

( "Instruction bit pattern : 1011 1101 1000 0010" is added. )

229

231

233

235

237

"7.116 COPOP (Coprocessor Operation)" is changed.

( "Resource" → "Coprocessor" )

"7.117 COPLD (Load 32-bit Data from Register to Coprocessor Register)" is changed.

( "Resource" → "Coprocessor" )

"7.118 COPST (Store 32-bit Data from Coprocessor Register to Register)" is changed.

( "Resource" → "Coprocessor" )

"7.119 COPSV (Save 32-bit Data from Coprocessor Register to Register)" is changed.

( "Resource" → "Coprocessor" )

"7.120 NOP (No Operation)" is changed.

( "Instruction bit pattern : 1001 1111 1010 0000" is addded. )

xvii

Page 22

Page Changes (For details, refer to main body.)

238

239

240

242

243

244

245

255

257

"7.121 ANDCCR (And Condition Code Register and Immediate Data)" is changed.

( "Instruction bit pattern : 1000 0011 1111 1110" is added. )

"7.122 ORCCR (Or Condition Code Register and Immediate Data)" is changed.

( "Instruction bit pattern : 1001 0011 0001 0000" is added. )

"7.123 STILM (Set Immediate Data to Interrupt Level Mask Register)" is changed.

( "Instruction bit pattern : 1000 0111 0001 0100" is added. )

"7.125 EXTSB (Sign Extend from Byte Data to Word Data)" is changed.

( "Instruction bit pattern : 1001 0111 1000 0001" is added. )

"7.126 EXTUB (Unsign Extend from Byte Data to Word Data)" is changed.

( "Instruction bit pattern : 1001 0111 1001 0001" is changed. )

"7.127 EXTSH (Sign Extend from Byte Data to Word Data)" is changed.

( "Instruction bit pattern : 1001 0111 1010 0001" is added. )

"7.128 EXTUH (Unsigned Extend from Byte Data to Word Data)" is changed.

( "Instruction bit pattern : 1001 0111 1011 0001" is added. )

"7.133 ENTER (Enter Function)" is changed.

( "XXXX XXXX 0000 0011" → "0000 1111 0000 0011" )

"7.134 LEAVE (Leave Function)" is changed.

( "Instruction bit pattern : 1001 1111 1001 0000" is addded. )

258

259

"7.135 XCHB (Exchange Byte Data)" is chenged.

( "extu (Rj) → Ri" → "extu ((Rj)) → Ri" )

"7.135 XCHB (Exchange Byte Data)" is chenged.

( "Instruction bit pattern : 1000 1010 0001 0000" is added. )

xviii

Page 23

Page Changes (For details, refer to main body.)

"A.1 Symbols Used in Instruction Lists" is chenged.

● Symbols in Mnemonic and Operation Columns is changed.

i8 .............( "128 to 255" → "0 to 255" )

"A.1 Symbols Used in Instruction Lists" is chenged.

● Symbols in Mnemonic and Operation Columns is changed.

( "Note: Data from -128 to -1 is handled as data from 128 to 255." is deleted. )

"A.1 Symbols Used in Instruction Lists" is chenged.

● Symbols in Mnemonic and Operation Columns is changed.

i20 ...........( "0x80000

to 0xFFFFFH" → "00000H to FFFFFH" )

H

263

"A.1 Symbols Used in Instruction Lists" is chenged.

● Symbols in Mnemonic and Operation Columns is changed.

( "Note: Data from -0x80000

to -1 is handled as data from 0x80000H to 0xFFFFFH." is deleted. )

H

"A.1 Symbols Used in Instruction Lists" is chenged.

● Symbols in Mnemonic and Operation Columns is changed.

i32 ...........( "0x80000000

to 0xFFFFFFFFH" → "00000000H to FFFFFFFFH" )

H

"A.1 Symbols Used in Instruction Lists" is chenged.

● Symbols in Mnemonic and Operation Columns is changed.

( "Note: Data from -0x80000000

to -1 is handled as data from 0x80000000H to 0xFFFFFFFFH." is deleted. )

H

263

264

266

"A.1 Symbols Used in Instruction Lists" is changed.

● Symbols in Mnemonic and Operation Columns is changed.

• Ri" → "• Ri, Rj" )

( "

"● Symbols in Operation Column" is changed.

( "

• ( )............. indicates indirect addressing, which values reading or loading from/to the memory address

where the registers within ( ) or the formula indicate.

• { }............ indicates the calculation priority; ( ) is used for specifying indiiirect address" is added. )

"● Cycle (CYC) Column" is changed.

( "special" → "dedicated" )

"Table A.2-4 Bit Operation Instructions (8 Instructions)" is changed.

( "(Ri)&=(F0H+u4)" → "(Ri)&={F0H+u4}" )

"Table A.2-4 Bit Operation Instructions (8 Instructions)" is changed.

( "(Ri)&=((u4<<4)+FH)" → "(Ri)&={{u4<<4}+FH}" )

"Table A.2-4 Bit Operation Instructions (8 Instructions)" is changed.

( "(Ri) | = (u4<<4)" → "(Ri) | = {u4<<4}" )

"Table A.2-4 Bit Operation Instructions (8 Instructions)" is changed.

( "(Ri) ^ = (u4<<4)" → "(Ri) ^ = {u4<<4}" )

"Table A.2-4 Bit Operation Instructions (8 Instructions)" is changed.

( "(Ri) & (u4<<4)" → "(Ri) & {u4<<4}" )

xix

Page 24

Page Changes (For details, refer to main body.)

"Table A.2-6 Shift Instructions (9 Instructions)" is changed.

267

( "Ri <<(u4+16) → Ri" → "Ri <<{u4+16} → Ri" )

( "Ri >>(u4+16) → Ri" → "Ri >>{u4+16} → Ri" )

( "Ri >>(u4+16) → Ri" → "Ri >>{u4+16} → Ri" )

272

273

276

"Table A.2-13 Direct Addressing Instructions (14 Instructions)" is changed.

("disp8" → "dir8"), ("disp9" → "dir9"), ("disp10" → "dir10")

"Table A.2-16 Other Instructions (16 Instructions)" is changed.

("i8" → "u8")

"Table B.2-1 "E" Format" is changed.

( "- : Undefined" is added. )

xx

Page 25

CHAPTER 1

FR FAMILY OVERVIEW

This chapter describes the features of the FR FAMILY

CPU core, and provides sample configurations.

1.1 Features of the FR Family CPU Core

1.2 Sample Configuration of an FR Family Device

1.3 Sample Configuration of the FR Family CPU

1

Page 26

CHAPTER 1 FR FAMILY OVERVIEW

1.1 Features of the FR Family CPU Core

The FR family CPU core features proprietary Fujitsu ar chitecture and is designed for

controller applications using 32-bit "RISC" based computing. The architecture is

optimized for use in microcontroller CPU cores for built-in control applications where

high-speed control is required.

■ Features of the FR Family CPU Core

• General-purpose register architecture

• Linear space for 32-bit (4 Gbytes) addressing

• 16-bit fixed instruction length (excluding immediate data, coprocessor instructions)

• 5-stage pipeline configuration for basic instructions, one-instruction one-cycle execution

• 32-bit by 32-bit computation enables completion of multipl icati on instructions within five cycles

• Stepwise division instructions enable 32-bit/ 32-bit division

• Direct addressing instructions for peripheral circuit access

• Coprocessor instructions for direct designation of peripheral accelerator

• High speed interrupt processing complete within 6 cycles

2

Page 27

CHAPTER 1 FR FAMILY OVERVIEW

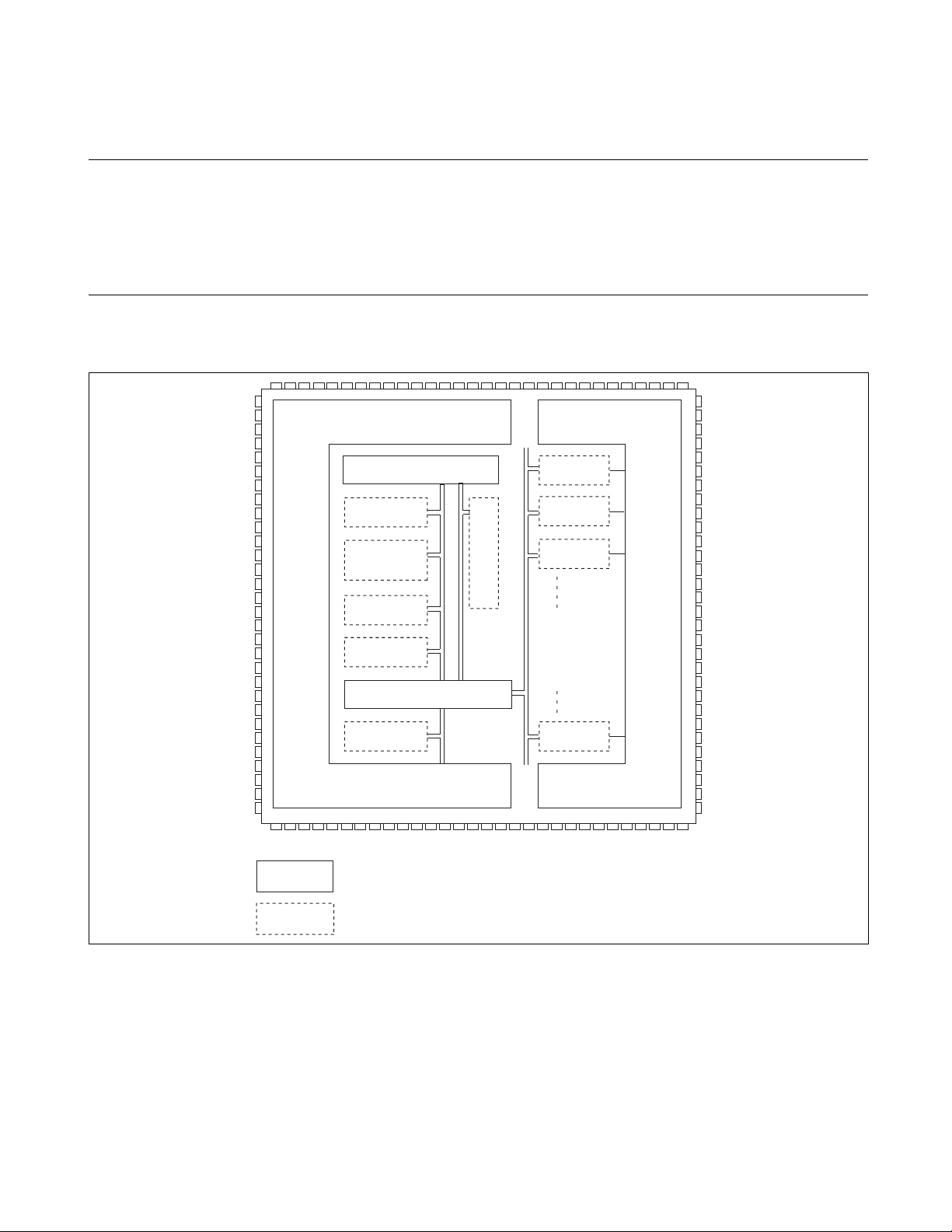

1.2 Sample Configuration of an FR Family Device

FR family devices have block configuration with bus connections between individual

modules. This enables module connections to be altered as necessary to accommodate

a wide variety of functional configurations.

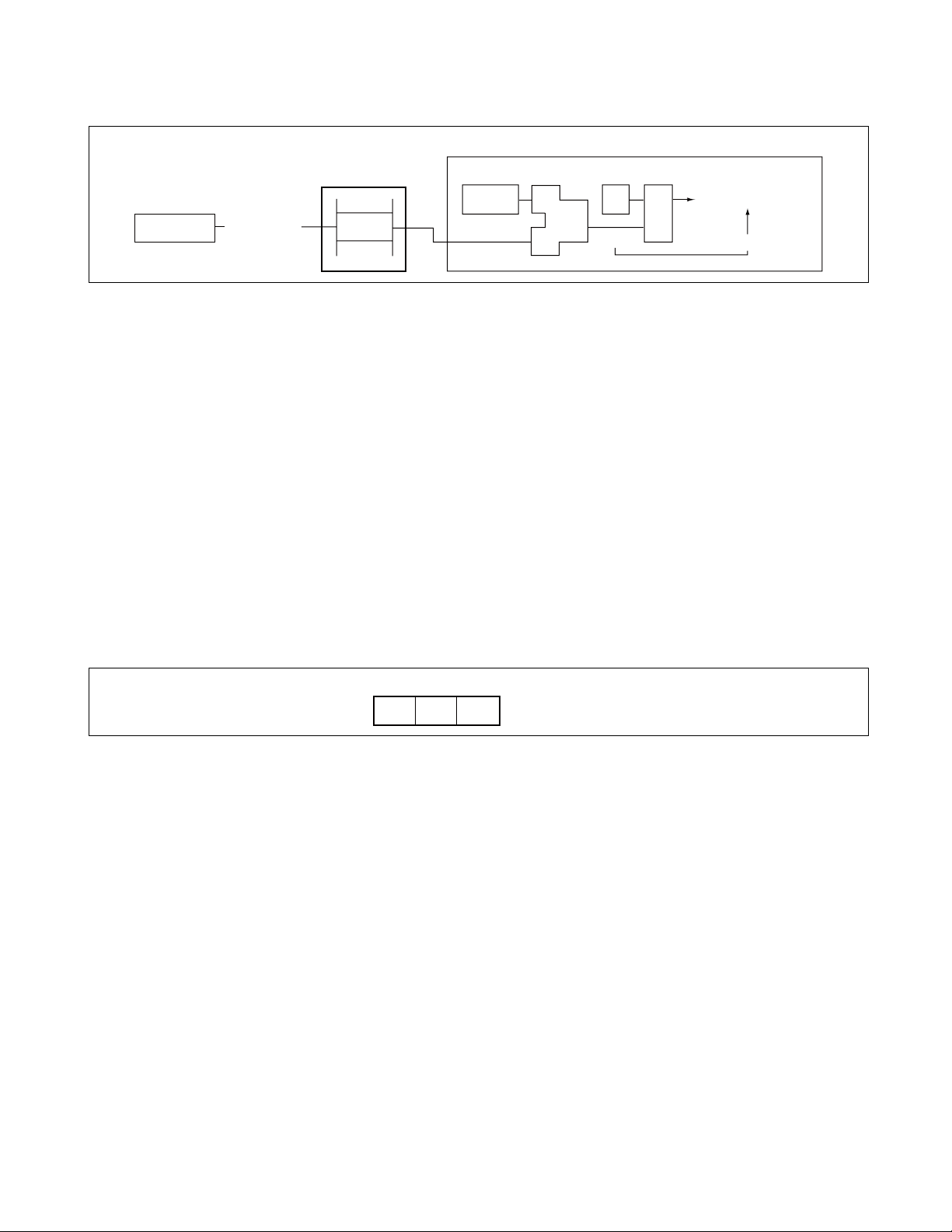

Figure 1.2-1 shows an example of the configuration of an FR family device.

■ Sample Configuration of an FR Family Device

Figure 1.2-1 Sample Configuration of an FR Family Device

FR family CPU

DMAC

Data cache

RAM

Data bus

High speed

peripherals

Internal bus interface

ROM

User bus interface General-purpose port

Mandatory: Standard in all models

Instruction cache

Instruction bus

Integrated bus

Low speed

peripherals

Low speed

peripherals

Low speed

peripherals

Peripheral bus

Low speed

peripherals

Option: Not included in some models

3

Page 28

CHAPTER 1 FR FAMILY OVERVIEW

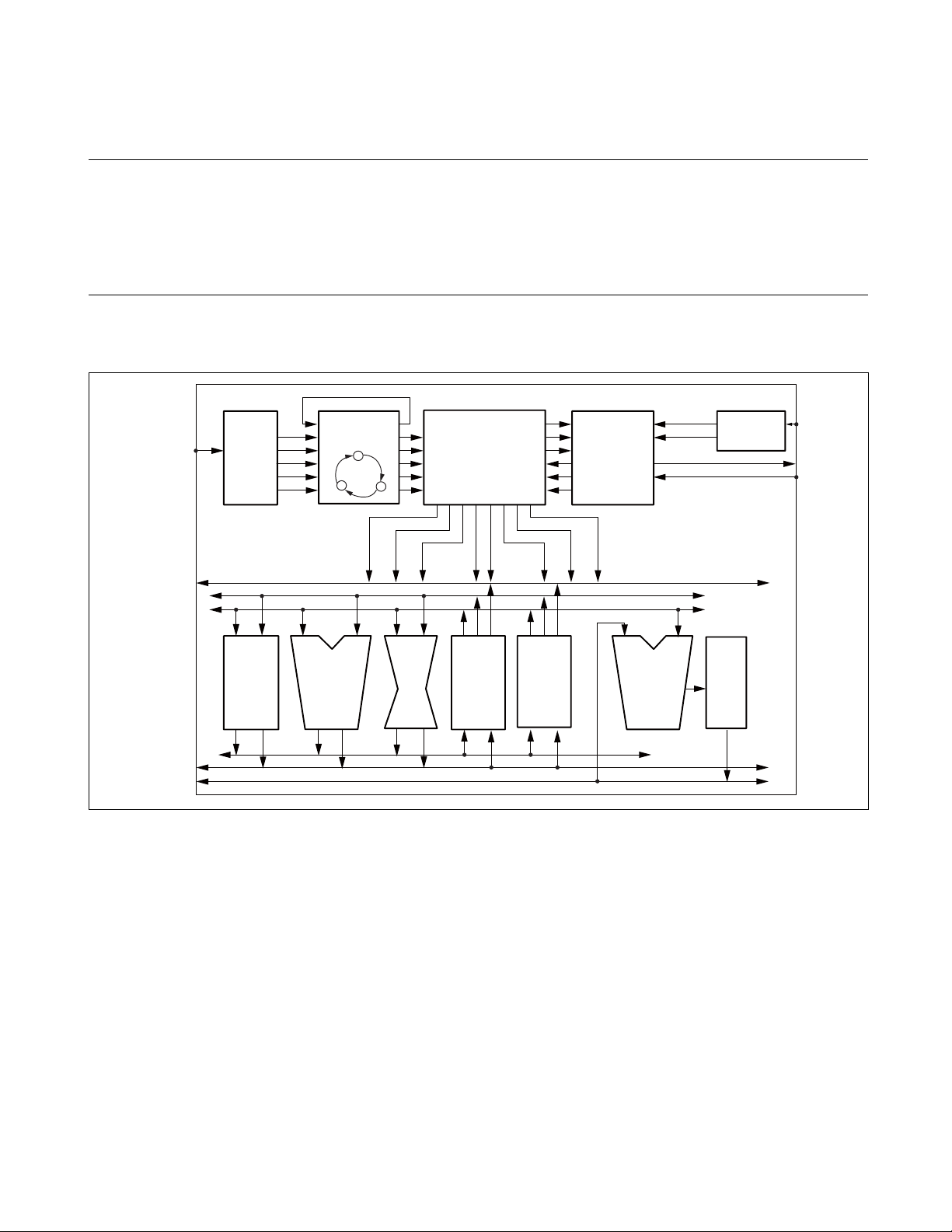

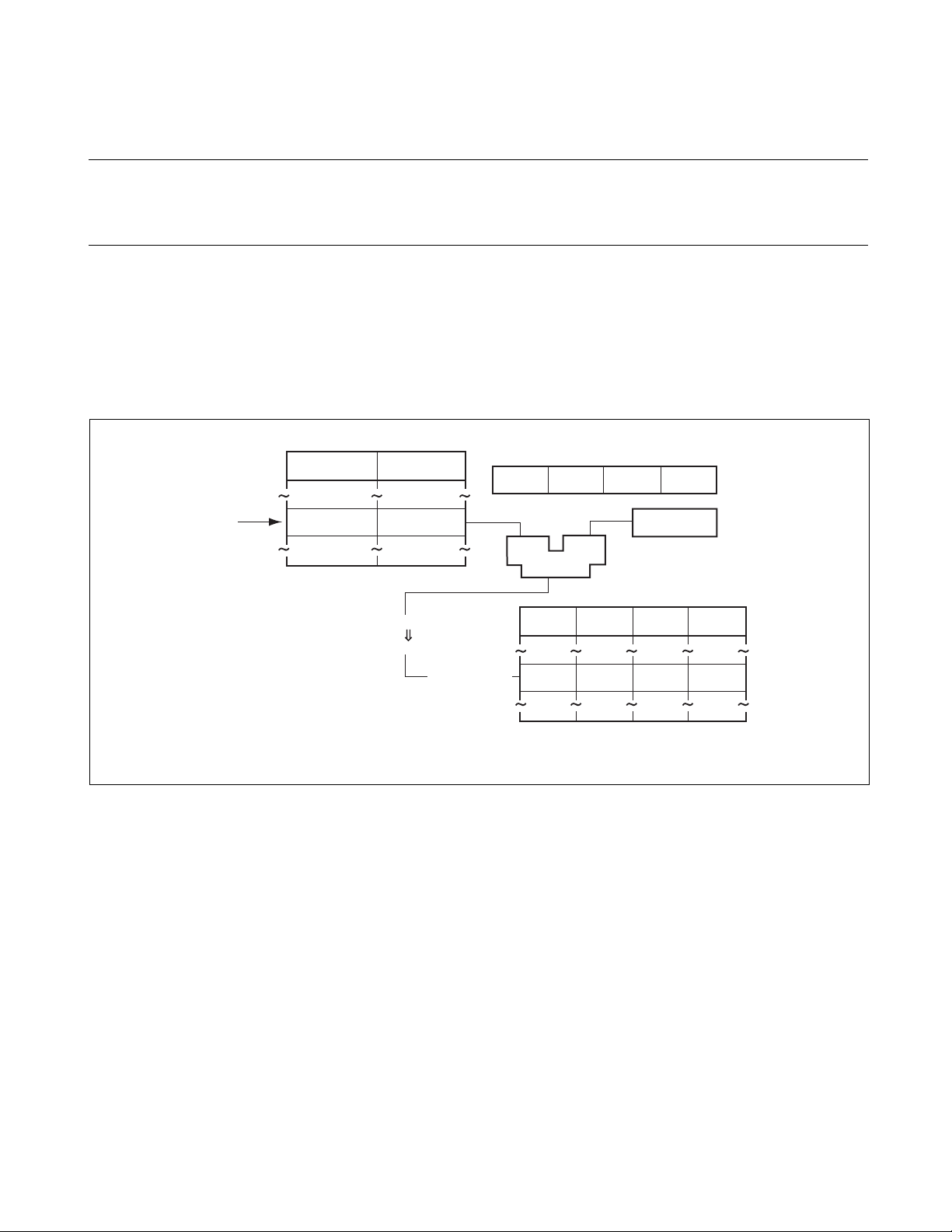

1.3 Sample Configuration of the FR Family CPU

The FR family CPU core features a block configuration organized around generalpurpose registers, with dedicated registers, "ALU" units, multipliers and other features

included for each specific application.

Figure 1.3-1 shows a sample configuration of an FR family CPU.

■ Sample Configuration of the FR Family CPU

Figure 1.3-1 Sample Configuration of the FR Family CPU

Instruction

data

Data

Data address

Instruction

address

Instruction

decoder

Multiplier

32 x 8

bits

Instruction

sequencer

ALU

Barrel

shifter

Pipeline

control

Bypass

Register

file

Bypass

interlock

Wait cancel

control

PC

adder

/inc

Internal bus

Exception

processing

Internal bus

Internal bus

PC

Interrupt

NMI

Wait bus

control

4

Page 29

CHAPTER 2

MEMORY ARCHITECTURE

This chapter describes memory space in the FR family

CPU.

Memory architecture includes the allocation of memory

space as well as methods used to access memory .

2.1 FR Family Memory Space

2.2 Bit Order and Byte Order

2.3 Word Alignment

5

Page 30

CHAPTER 2 MEMORY ARCHITECTURE

2.1 FR Family Memory Space

The FR family controls memory space in byte units, and provides linear designation of

32-bit spaces. Also, to enhance instruction efficiency, specific areas of memory are

allocated for use as direct address areas and vector table areas.

■ Memory Space

Figure 2.1-1 illustrates memory space in the FR family.

For a detailed description of the direct address area, see Section "2.1.1 Direct Address Area", and for the

vector table area, see Section "2.1.2 Vector Table Area".

Figure 2.1-1 FR Family Memory Space

Direct address area

General addressing

0000 0000H

0000 0100H

0000 0200H

0000 0400H

000F FC00H

0010 0000H

FFFF FFFFH

■ Unused V ector Table Area

Unused vector table area is available for use as program or data area.

Byte data

Half-word data

Word data

Vector table

initial area

Program or data area

000F FC00

TBR initial value

H TBR

6

Page 31

CHAPTER 2 MEMORY ARCHITECTURE

2.1.1 Direct Address Area

The lower portion of the address space is used for the direct address area. Instructions

that specify direct addresses allow you to access this area without the use of generalpurpose registers, using only the operand information in the instruction itself. The size

of the address area that can be specified by direct addressing varies according to the

length of the data being transferred.

■ Direct Address Area

The size of the address area that can be specified by direct addressing varies according to the length of the

data being transferred, as follows:

• Transfer of byte data: 0000 0000

• Transfer of half-word data: 0000 0000H to 0000 01FF

• Transfer of word data: 0000 0000H to 0000 03FF

to 0000 00FF

H

H

H

H

■ Use of Operand Information Contained in Instructions

The 8-bit address information contained in the instruction ha s the following significance.

• In byte data: Value represents the lower 8 bits of the address.

• In half-word data: Value is doubled and used as the lower 9 bits of the address.

• In word data: Value is multiplied by 4 and used as the lower 10 bits of the address.

Figure 2.1-2 shows the relationship between the length of the data that designates the direct address, and

the actual address in memory.

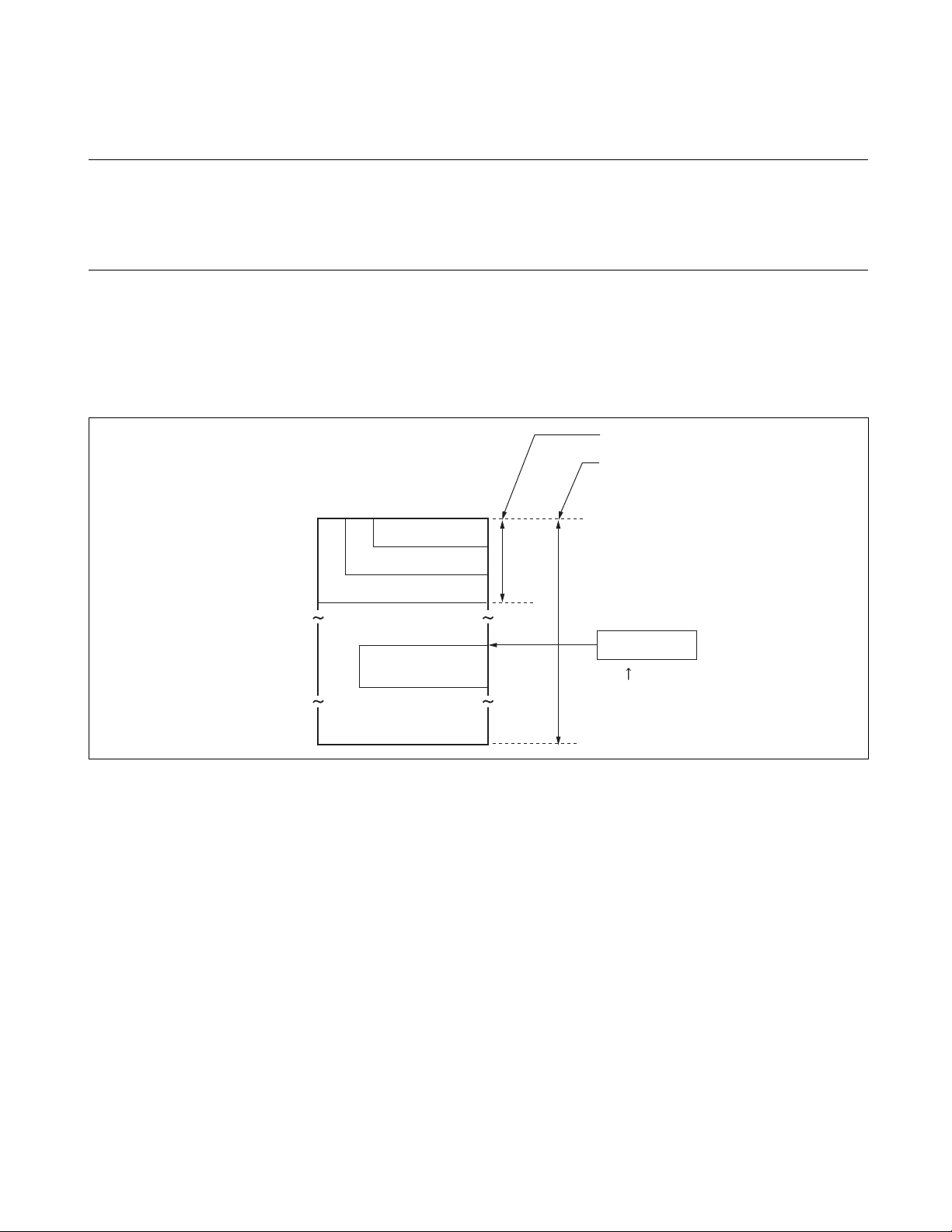

Figure 2.1-2 Relation between Direct Address Data and Memory Address Value

[Example 1] Byte data: DMOVB R13,@58H

58

Object code:1A58H

[Example 2] Half-word data: DMOVH R13,@58H

Object code:192C

No data shift

Right 1-bit shift

H 58HLeft 1-bit shift

0000 0058HR13 12345678

0000 0058

H

HR13 12345678

Memory space

78

Memory space

5678

[Example 3] Word data: DMOV R13,@58H

Object code:1816

Right 2-bit shift

H 58HLeft 2-bit shift

0000 0058

Memory space

HR13 12345678

1345678

7

Page 32

CHAPTER 2 MEMORY ARCHITECTURE

2.1.2 Vector Table Area

An area of 1 Kbyte beginning with the address shown in the table base register (TBR) is

used to store "EIT" vector addresses.

■ Overview of Vector Table Areas

An area of 1 Kbyte beginning with the address shown in the table base register (TBR) is used to store "EIT"

vector addresses. Data written to this area includes entry addresses for exception processing, interrupt

processing and trap processing.

The table base register (TBR) can be rewritten to allocate this area to any desired location within word

alignment limitations.

Figure 2.1-3 Relation between Table Base Register (TBR) and Vector Table Addresses

TBR

0000 0000H

1 Kbyte

FFFF FFFFH

Memory space

Vector

table

area

Number

FF

H

FEH

FDH

FCH

00H

Offset

from TBR

000H

004H

008H

00CH

3FCH

EIT source

Entry address for INT instruction

Entry address for INT instruction

Entry address for INT instruction

Entry address for INT instruction

Entry address for reset processing

8

Page 33

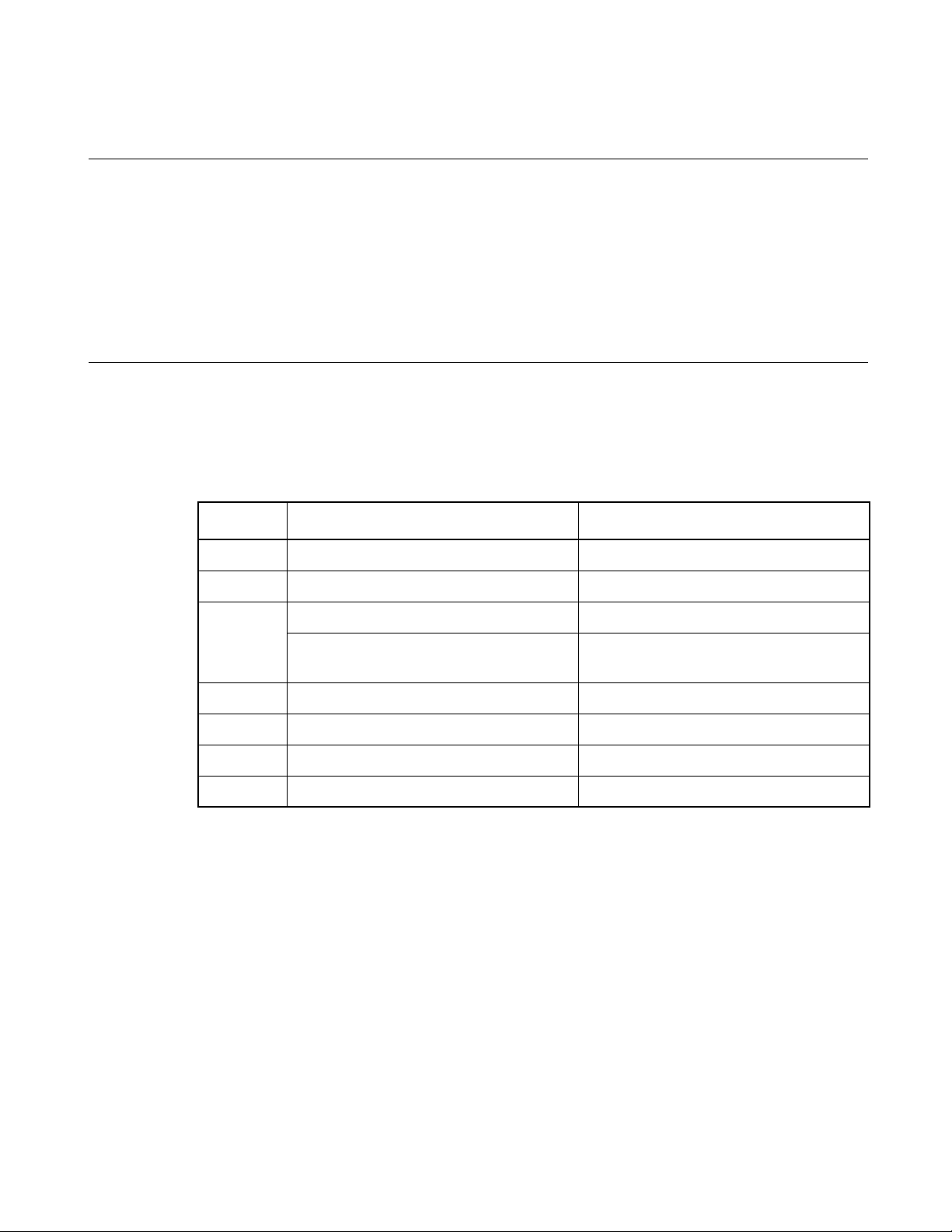

■ Contents of Vector Table Areas

A vector table is composed of entry addresses for each of the "EIT" processing programs. Each table

contains some values whose use is fixed according to the CPU architecture, and some that vary according

to the types of built-in peripheral circuits present. Table 2.1-1 shows the structure of a vector table area.

Table 2.1-1 Structure of a Vector Table Area

CHAPTER 2 MEMORY ARCHITECTURE

Offset from

TBR

000

004

~

2F8

2FC

~

33C

340

344

~

3BC

3C0

3C4

3C8

3CC

3D0

3D4

3D8

3DC

3E0

3E4

~

3F8

3FC

Number

(hex)

H

H

FF

FE

H

H

Model-

dependent

No

No

INT #0FF

INT #0FE

EIT value description Remarks

H

H

~ ~ ~ ~

H

H

41

40

H

H

No System reserved

No System reserved

~ ~ ~ ~

H

H

H

30

2F

2E

H

H

H

No

Yes

Yes

INT #030

INT #02F

INT #02E

H

or IR31

H

or IR30

H

~ ~ ~ ~

H

H

H

H

H

H

H

H

H

H

H

10

0F

0E

0D

0C

0B

0A

09

08

07

06

H

H

H

H

H

H

H

H

H

H

H

Yes INT #010H or IR00

No

No Undefined instruction exception

No Emulator exception

No Step trace break trap

No Operand break trap

No Instruction break trap

No Emulator exception

No

No

No System reserved

INT #00F

INT #008

INT #007

trap

or NMI

H

or coprocessor error trap

H

or coprocessor not-found

H

~ ~ ~ ~

H

H

01

00

H

H

Yes System reserved or Mode Vector

No Reset *

⎩

⎨

Do not use

⎧

⎩

Values will increase

⎪

towards higher limits

⎨

when using over 32source extension.

⎪

Refer to User’s Manual

⎧

for each model.

⎩

⎨

Do not use

⎧

Refer to User’s Manual for

each model.

~

~

~

~

*: Even when the "TBR" value is changed, the reset vector remains the fixed address "000FFFFC

■ Vector Table Area Initial Value

After a reset, the value of the table base register (TBR) is initialized to "000FF C00H", so that the vector

table area is between addresses "000FFC00

" and "000FFFFFH".

H

".

H

9

Page 34

CHAPTER 2 MEMORY ARCHITECTURE

2.2 Bit Order and Byte Order

This section describes the order in which three types of data, 8, 16, and 32 bits, are

placed in the memory in the FR family.

In the FR family, the bit number increases approaching the MSB, and the byte number

increases approaching the lowest address value.

■ Bit Order and Byte Order

Bit order in the general-purpose register is that the larger numbers are placed in the vicinity of the MSB

while the smaller numbers are near the LSB. Byte order configuration requires the upper data to be placed

in the smaller address memory, while the lower data are placed in the larger address memory.

Figure 2.2-1 illustrates the bit order and byte order in the FR family.

Figure 2.2-1 Bit Order and Byte Order

0000 0000H

1234 5678H

1234 5679H

1234 567AH

1234 567BH

FFFF FFFFH

Bit order

Memory space

H

12

34H

56H

78H

312423 1615 8 70

R0

R10

H 34H 56H 78H

12

12345678

H

LD @R10,R0

10

Page 35

CHAPTER 2 MEMORY ARCHITECTURE

2.3 Word Alignment

In the FR family, the type of data length used determines restrictions on the

designation of memory addresses (word alignment).

■ Program Restrictions on Word Alignment

When using half-word instruction length, memory addresses must be accessed in multiples of two. With

branching instructions and other instructions that may result in attempting to store odd numbered valu es to

the "PC", the lowest value in the "PC" will be read as "0". Thus an even numbered address will always be

generated by fetching a branching instruction.

■ Data Restrictions on Word Alignment

● Word data

Data must be assigned to addresses that are multiples of 4. Even if the operand value is not a m ultiple of 4,

the lower two bits of the memory address will explicitly be read as "0".

● Half-word data

Data must be assigned to addresses that are multiples of 2. Even if the operand value is not a m ultiple of 2,

the lowest bit of the memory address will explicitly be read as "0".

● Byte data

There are no restrictions on addresses.

The forced setting of some bits to "0" during memory access for word data and half-word data is applied

after the computation of the execution address, not at the source of the address information.

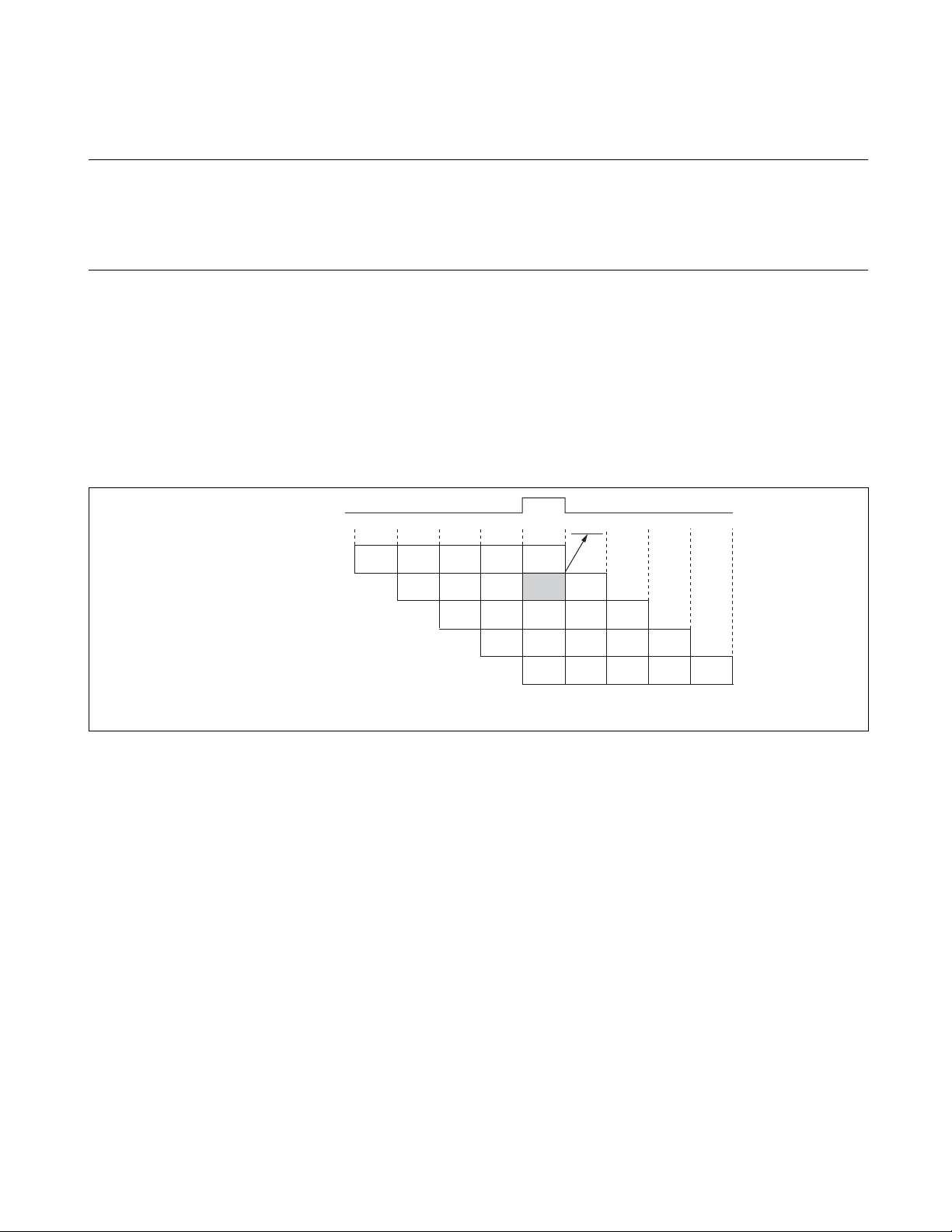

Figure 2.3-1 shows an example of the program-word boundary and data-word boundary.

Figure 2.3-1 Example of Program-word Boundary and Data-wor d Boundary

12345679

R10

JMP @R10 : Bit 0 = 0

12345678

PC

R1

43215679

R2

4321567B

H

H

H

H

Bit 0 = 0

as it is

0000 0000

1234 5678

1234 567A

1234 567C

4321 5678

4321 567A

4321 567C

4321 567E

Memory space

H

ST R13,@(R14,4)

H

STH R13,@R2

H

STB R13,@R1

H

H

EF

H

H

H

H

CDEF

89AB

CDEF

R14

R13

H

H

H

4321567B

89ABCDEF

H

H

4321567B

+

00000004

4321567F

Bits 1, 0 = 0

4321567C

H

H

H

H

FFFF FFFF

H

11

Page 36

CHAPTER 2 MEMORY ARCHITECTURE

12

Page 37

CHAPTER 3

REGISTER DESCRIPTIONS

This chapter describes the registers used in the FR

family CPU.

3.1 FR Family Register Configuration

3.2 General-purpose Registers

3.3 Dedicated Registers

13

Page 38

CHAPTER 3 REGISTER DESCRIPTIONS

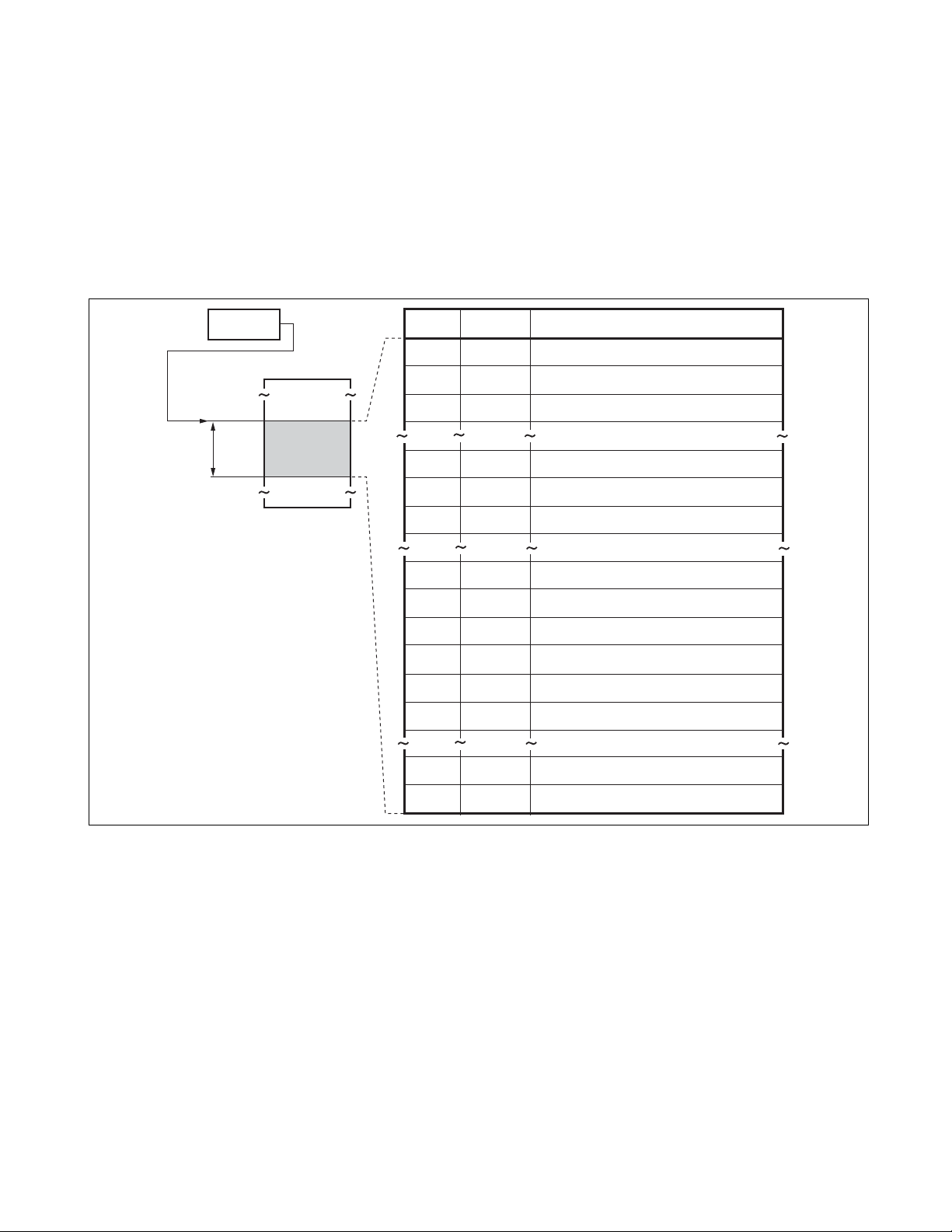

3.1 FR Family Register Configuration

FR family devices use two types of registers, general-purpose registers and dedicated

registers.

• General-purpose registers: Store computation data and address information

• Dedicated registers: Store information for specific applications

Figure 3.1-1 shows the configuration of registers in FR family devices.

■ FR Family Register Configuration

Figure 3.1-1 FR Family Register Configuration

Initial value

32 bits

General-purpose registers

Dedicated registers

R0

R1

R2

R3

R12

R13

R14

R15

PC

PS

TBR

RP

SSP

Accumulator(AC)

Frame pointer(FP)

SSP or USP

--

ILM SCR CCR

Undefined

Undefined

Undefined

Undefined

Undefined

Undefined

Undefined

00000000

Reset entry address

ILM=01111

SCR=XX0B

CCR=XX00XXXXB

000FFC00H

Undefined

00000000H

H

B

14

MD

USP

64 bits

Undefined

Undefined

Page 39

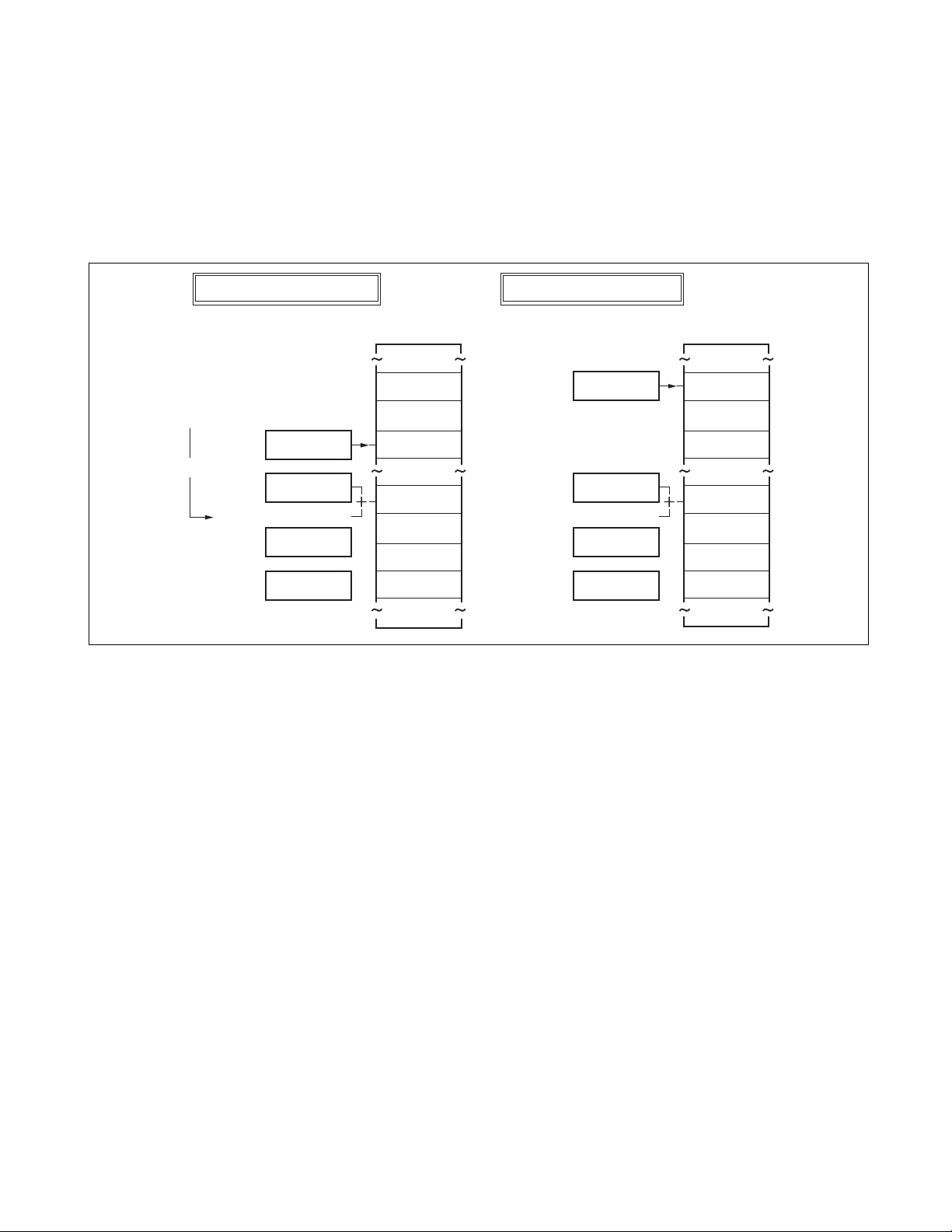

CHAPTER 3 REGISTER DESCRIPTIONS

3.2 General-purpose Registers

The FR family CPU uses general-purpose registers to hold the results of various

calculations, as well as information about addresses to be used as pointers for memory

access. These registers also have special functions with certain types of instructions.

■ Overview of General-purpose Registers

The FR family CPU has sixteen (16) general-purpose registers each 32 bits in length. Normal instructions

can use any of these sixteen registers without distinction.

Figure 3.2-1 shows the configuration of a general-purpose register.

Figure 3.2-1 General-purpose Register Configuration

Initial value

32 bits

R0

R1

R2

R3

R12

R13

R14

R15

Accumulator(AC)

Frame pointer(FP)

SSP or USP

■ Special Uses of General-purpose Registers

In addition to functioning as general-purpose registers, "R13", "R14", and "R15 " have the foll owing speci al

uses with certain types of instructions.

● R13 (Accumulator: AC)

• Base address register for load/store to memory instructions

[Example: LD @(R13, Rj), Ri]

• Accumulator for direct address designation

[Example: DMOV @dir10,R13]

• Memory pointer for direct address designation

[Example: DMOV @dir10, @R13+]

Undefined

Undefined

Undefined

Undefined

Undefined

Undefined

Undefined

00000000

H

15

Page 40

CHAPTER 3 REGISTER DESCRIPTIONS

● R14 (Frame P ointer: FP)

• Index register for load/store to memory inst ructions

[Example: LD @(R14, disp10), Ri]

• Frame pointer for reserve/release of dynamic memory area

[Example: ENTER #u10]

● R15 (Stack Pointer: SP)

• Index register for load/store to memory inst ructions

[Example: LD @(R15, udisp6), Ri]

• Stack pointer

[Example: LD @R15+, Ri]

• Stack pointer for reserve/release of dynamic memory area

[Example: ENTER #u10]

■ Relation between "R15" and Stack Pointer

The "R15" functions physically as either the system stack pointer (SSP) or user stack pointer (USP) for the

general-purpose registers. When the notation "R15" is used in an instruction, this register will function as

the "USP" if the "S" flag in the condition code register (CCR) section of the program status register (PS) is

set to "1". The R15 register will function as the "SSP" if the "S" flag is set to "0".

Ensure that the S flag value is set to "0" when R15 is recovered from the EIT handler with the RETI

instruction.

■ Initial Value of General-purpose Registers

After a reset, the value of registers "R00" through "R14" are undefined, and the value of "R15" is

"00000000

".

H

16

Page 41

CHAPTER 3 REGISTER DESCRIPTIONS

3.3 Dedicated Registers

The FR family has six 32-bit registers reserved for various special purposes, plus one

64-bit dedicated register for multiplication and division operations.

■ Dedicated Registers

The following seven dedicated registers are provided. For details, see the descriptions in Sect ions "3.3.1

Program Counter (PC)" through "3.3.6 Multiplication/Division Register (MD)".

● 32-bit Dedicated Registers

• Program counter (PC)

• Program status (PS)

• Table base register (TBR)

• Return pointer (RP)

• System stack pointer (SSP)

• User stack pointer (USP)

● 64-bit Dedicated Register

• Multiplication/Division Register (MD)

Figure 3.3-1 shows the configuration of the dedicated registers.

Figure 3.3-1 Dedicated Register Configuration

MD

PC

PS

TBR

RP

SSP

USP

64 bits

ILM SCR CCR

--

Reset entry address

ILM=01111

SCR=XX0B

CCR=XX00XXXXB

000FFC00H

Undefined

00000000

Undefined

Undefined

B

H

17

Page 42

CHAPTER 3 REGISTER DESCRIPTIONS

3.3.1 Program Counter (PC)

This register indicates the address containing the instruction that is currently

executing. Following a reset, the contents of the PC are set to the reset entry address

contained in the vector table.

■ Overview of the Program Counter

This register indicates the address containing the instruction that is currently executing. The value of the

lowest bit is always read as "0", and therefore all instructions must be written to addresses that are

multiples of 2.

■ Program Counter Functions

● Lowest Bit Value of Program Counter

The value of the lowest bit in the program counter is read as "0" by the internal circuits in the FR family

device. Even if "1" is written to this bit, it will be treated as "0" for addressing purposes. A physical cell

does exist for this bit, however, the lowest bit value remains "0" even wh en the program address value is

incremented and therefore the value of this bit is always "0" except following a branching operation.

Because the internal circuits in the FR family device are designed to read the value of the lowest bit as "0",

all instructions must be written to addresses that are multiples of 2.

● Program Counter Initial Value

Following a reset, the contents of the PC are set to the reset entry address contained in the vector table.

Because initialization is applied first to the table base register (TBR), the value of the reset vector address

will be "000FFFFC

".

H

18

Page 43

CHAPTER 3 REGISTER DESCRIPTIONS

3.3.2 Program Status (PS)

The program status (PS) indicates the status of program execution, and consists of the

following three parts:

• Interrupt level mask register (ILM)

• System condition code register (SCR)

• Condition code register (CCR)

■ Overview of Program Status Register

The program status register consists of sections that set the interrupt enable level, control the program trace

break function in the CPU, and indicate the status of instruction execution.

■ Program Status Register Configuration

Figure 3.3-2 shows the configuration of the program status register.

Figure 3.3-2 Program Status Register Configuration

Bit no.

31 2120 1615 1110 0807 00

PS Unused UnusedILM SCR CCR

■ Unused Bits in the Program Status Register

Unused bits are all reserved for future system expansion. Write values should always be "0". The read

value of these bits is always "0".

■ Interrupt Level Mask Register (ILM: Bit 20 to bit 16)

Bit Configuration of the ILM Register

●

Figure 3.3-3 Bit Configuration of the ILM Register

20 19 18 17 16

ILM ILM4 ILM3 ILM2 ILM1 ILM0 Initial value: 01111

● ILM Functions

B

The "ILM" determines the level of interrupt that will be accepted. Whenever the "I" flag in the "CCR"

register is "1", the contents of this register are compared to the level of the current interrupt request. If the