Page 1

SC140 DSP Core

Reference Manual

Revision 4.1, September 2005

This document contains information on a new product.

Specifications and information herein are subject to

change without notice.

(c) Freescale Semiconductor, Inc. 2005, All rights

Page 2

LICENSOR is defined as Freescale Semiconductor, Inc. LICENSOR reserves the right to make

changes without further notice to any products included and covered hereby. LICENSOR makes

no warranty, representation or guarantee regarding the suitability of its products for any particular

purpose, nor does LICENSOR assume any liability arising out of the application or use of any

product or circuit, and specifically disclaims any and all liability, including without limitation

incidental, consequential, reliance, exemplary, or any other similar such damages, by way of

illustration but not limitation, such as, loss of profits and loss of business opportunity. "Typical"

parameters which may be provided in LICENSOR data sheets and/or specifications can and do

vary in different applications and actual performance may vary over time. All operating

parameters, including "Typicals" must be validated for each customer application by customer’s

technical experts. LICENSOR does not convey any license under its patent rights nor the rights of

others. LICENSOR products are not designed, intended, or authorized for use as components in

systems intended for surgical implant into the body, or other applications intended to support life,

or for any other application in which the failure of the LICENSOR product could create a situation

where personal injury or death may occur. Should Buyer purchase or use LICENSOR products for

any such unintended or unauthorized application, Buyer shall indemnify and hold LICENSOR and

its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, cost,

damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim

of personal injury or death associated with such unintended or unauthorized use, even if such claim

alleges that LICENSOR was negligent regarding the design or manufacture of the part.

Freescale and are registered trademarks of Freescale Semiconductor, Inc. Freescale, Inc. is an

Equal Opportunity/Affirmative Action Employer.

All other tradenames, trademarks, and registered trademarks are the property of their respective

owners.

SC140 DSP Core Reference Manual

Page 3

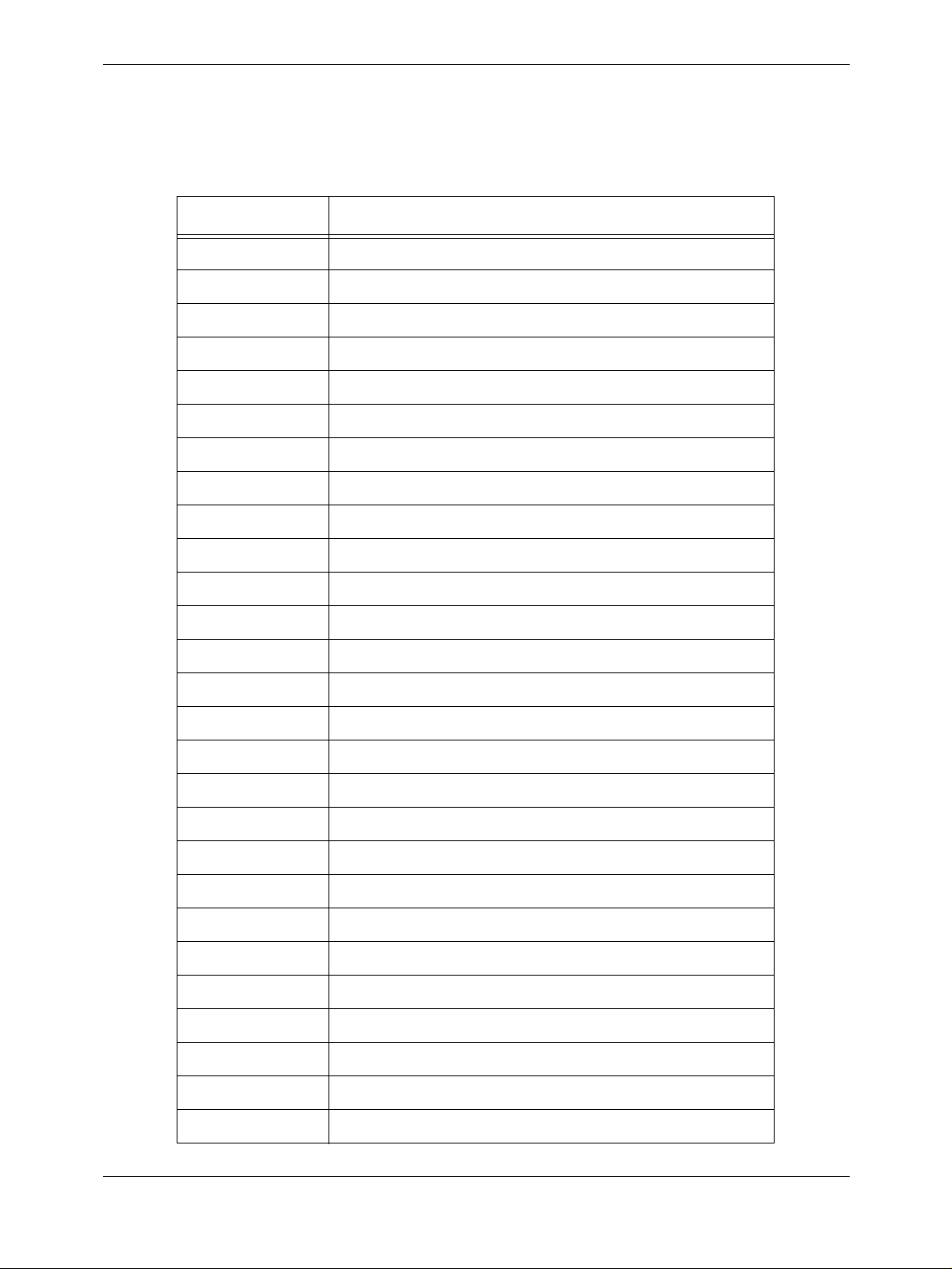

Table of Contents

About This Book

Audience. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .xxi

Organization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xxi

Abbreviations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xxii

Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xxiv

Chapter 1

Introduction

1.1 Target Markets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-1

1.2 Architectural Differentiation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-2

1.3 Core Architecture Features. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-3

1.3.1 Typical System-On-Chip Configuration. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-4

1.3.2 Variable Length Execution Set (VLES) Software Model . . . . . . . . . . . . . . . .1-5

Chapter 2

Core Architecture

2.1 Architecture Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-1

2.1.1 Data Arithmetic Logic Unit (DALU) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-2

2.1.1.1 Data Register File . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-3

2.1.1.2 Multiply-Accumulate (MAC) Unit. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-3

2.1.1.3 Bit-Field Unit (BFU) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-3

2.1.1.4 Shifter/Limiters. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-3

2.1.2 Address Generation Unit (AGU) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-3

2.1.2.1 Stack Pointer Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-4

2.1.2.2 Bit Mask Unit (BMU). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-4

2.1.3 Program Sequencer Unit (PSEQ) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-5

2.1.4 Enhanced On-Chip Emulator (EOnCE) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-5

2.1.5 Instruction Set Accelerator Plug-in (ISAP) Interface. . . . . . . . . . . . . . . . . . . .2-5

2.1.6 Memory Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-5

2.2 DALU . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-6

2.2.1 DALU Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-6

2.2.1.1 Data Registers (D0–D15) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-8

2.2.1.2 Multiply-Accumulate (MAC) Unit. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-10

2.2.1.3 Bit-Field Unit (BFU) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-12

2.2.1.4 Data Shifter/Limiter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-13

2.2.1.5 Scaling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-14

2.2.1.6 Limiting . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-14

2.2.1.7 Scaling and Arithmetic Saturation Mode Interactions . . . . . . . . . . . . . . .2-16

2.2.2 DALU Arithmetic and Rounding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-17

SC140 DSP Core Reference Manual iii

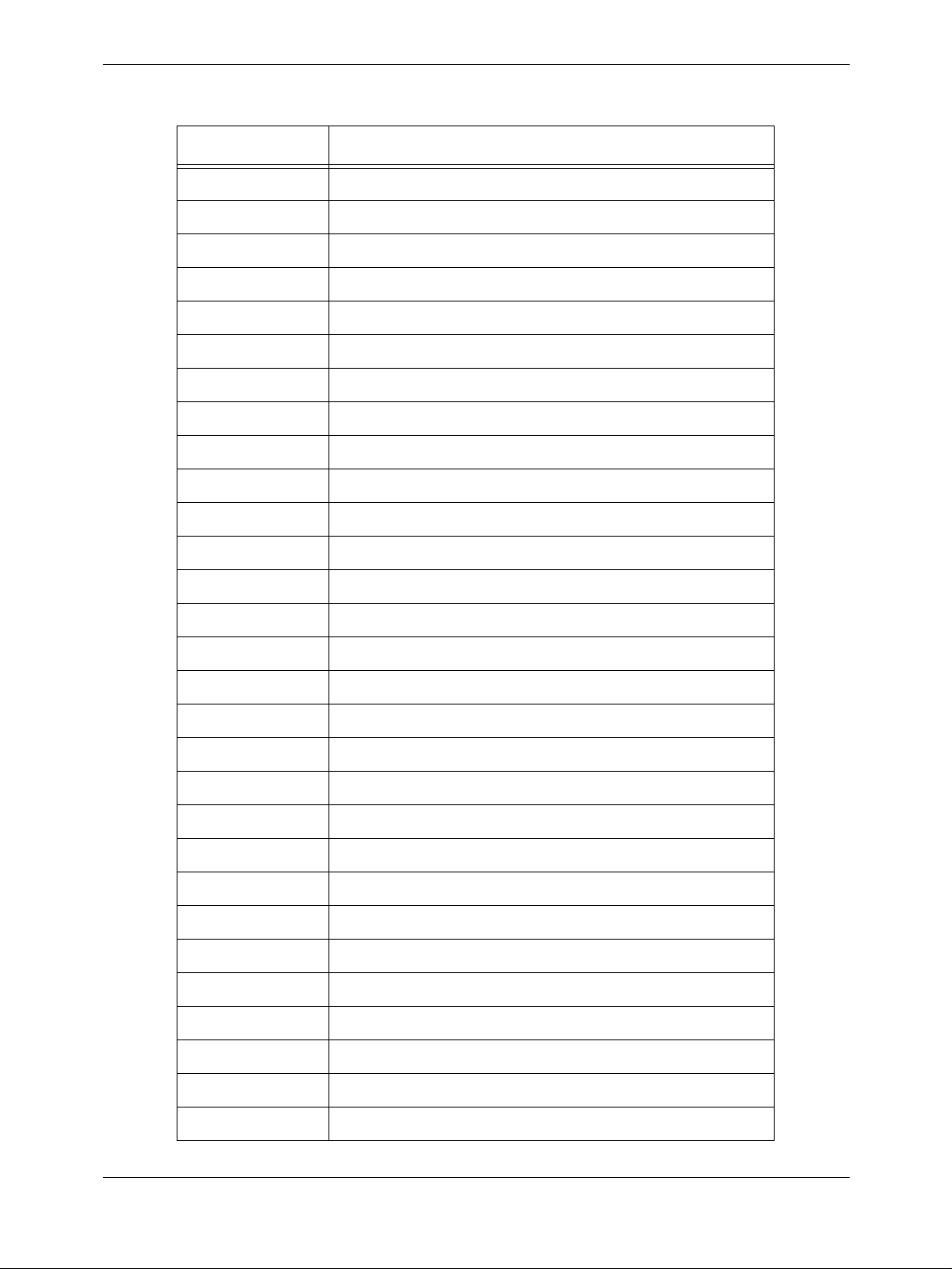

Page 4

2.2.2.1 Data Representation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-17

2.2.2.2 Data Formats. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-18

2.2.2.3 Multiplication . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-20

2.2.2.4 Division. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-20

2.2.2.5 Unsigned Arithmetic. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-20

2.2.2.6 Rounding Modes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-21

2.2.2.7 Arithmetic Saturation Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-25

2.2.2.8 Multi-Precision Arithmetic Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-26

2.2.2.9 Viterbi Decoding Support. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-30

2.3 Address Generation Unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-31

2.3.1 AGU Architecture. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-31

2.3.2 AGU Programming Model . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-34

2.3.2.1 Address Registers (R0–R15) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-35

2.3.2.2 Stack Pointer Registers (NSP, ESP) . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-35

2.3.2.3 Offset Registers (N0–N3). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-36

2.3.2.4 Base Address Registers (B0–B7) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-36

2.3.2.5 Modifier Registers (M0–M3) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-36

2.3.2.6 Modifier Control Register (MCTL) . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-37

2.3.3 Addressing Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-38

2.3.3.1 Register Direct Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-38

2.3.3.2 Address Register Indirect Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-38

2.3.3.3 PC Relative Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-40

2.3.3.4 Special Addressing Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-41

2.3.3.5 Memory Access Width . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-42

2.3.3.6 Memory Access Misalignment. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-42

2.3.3.7 Addressing Modes Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-43

2.3.4 Address Modifier Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-45

2.3.4.1 Linear Addressing Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-45

2.3.4.2 Reverse-carry Addressing Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-45

2.3.4.3 Modulo Addressing Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-45

2.3.4.4 Multiple Wrap-Around Modulo Addressing Mode . . . . . . . . . . . . . . . . .2-47

2.3.5 Arithmetic Instructions on Address Registers . . . . . . . . . . . . . . . . . . . . . . . .2-48

2.3.6 Bit Mask Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-49

2.3.6.1 Bit Mask Test and Set (Semaphore Support) Instruction . . . . . . . . . . . . .2-50

2.3.6.2 Semaphore Hardware Implementation . . . . . . . . . . . . . . . . . . . . . . . . . . .2-51

2.3.7 Move Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-51

2.4 Memory Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-55

2.4.1 SC140 Endian Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-56

2.4.1.1 SC140 Bus Structure. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-56

2.4.1.2 Memory Organization. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-57

2.4.1.3 Data Moves. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-58

2.4.1.4 Multi-Register Moves. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-60

2.4.1.5 Instruction Word Transfers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-62

2.4.1.6 Memory Access Behavior in Big/Little Endian Modes . . . . . . . . . . . . . .2-64

iv SC140 DSP Core Reference Manual

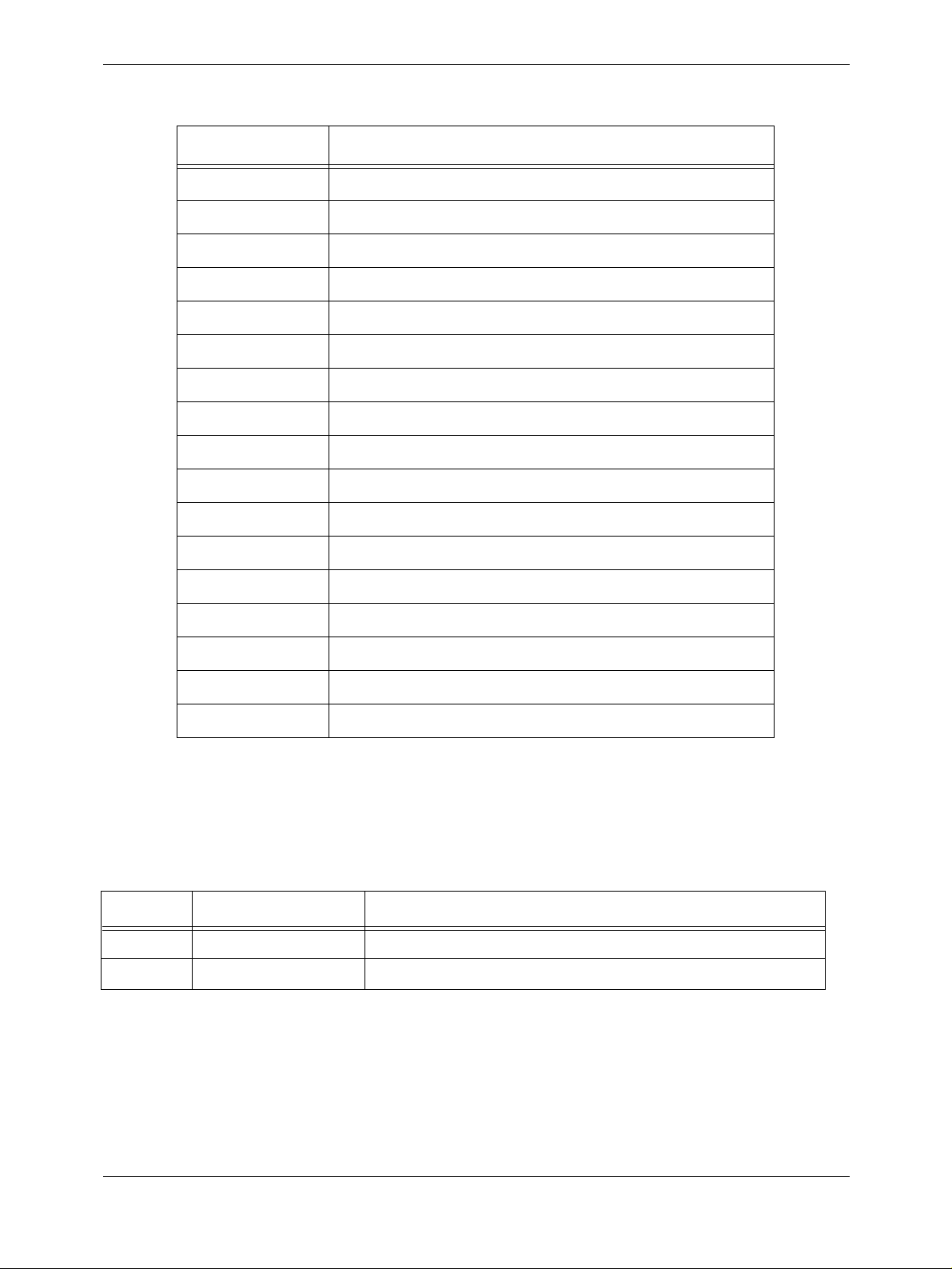

Page 5

Chapter 3

Control Registers

3.1 Core Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-1

3.1.1 Status Register (SR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-1

3.1.2 Exception and Mode Register (EMR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-7

3.1.2.1 Clearing EMR Bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-10

3.2 PLL and Clock Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-10

Chapter 4

Emulation and Debug (EOnCE)

4.1 Debugging System . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-1

4.2 Overview of the Combined JTAG and EOnCE Interface. . . . . . . . . . . . . . . . . . . .4-2

4.2.1 Cascading Multiple SC140 EOnCE Modules in a SoC . . . . . . . . . . . . . . . . . .4-2

4.2.2 JTAG Scan Paths . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-3

4.2.3 Activating the EOnCE Through the JTAG Port. . . . . . . . . . . . . . . . . . . . . . . .4-6

4.2.4 Enabling the EOnCE Module . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-6

4.2.5 DEBUG_REQUEST and ENABLE_EONCE Commands. . . . . . . . . . . . . . . .4-7

4.2.6 Reading/Writing EOnCE Registers Through JTAG. . . . . . . . . . . . . . . . . . . . .4-7

4.3 Main Capabilities of the EOnCE Module. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-10

4.3.1 EOnCE Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-10

4.3.2 EOnCE Dedicated Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-11

4.3.3 Debug State. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-11

4.3.4 Debug Exception. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-12

4.3.5 Executing an Instruction while in Debug State . . . . . . . . . . . . . . . . . . . . . . .4-12

4.3.6 Software Downloading . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-12

4.3.7 EOnCE Events . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-14

4.3.8 EOnCE Actions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-15

4.3.9 Event and Action Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-15

4.4 EOnCE Enabling and Power Considerations . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-16

4.5 EOnCE Module Internal Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-16

4.5.1 EOnCE Controller. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-16

4.5.2 Event Counter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-18

4.5.3 Event Detection Unit (EDU). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-20

4.5.3.1 Address Event Detection Channel (EDCA) . . . . . . . . . . . . . . . . . . . . . . .4-22

4.5.3.2 Data Event Detection Channel (EDCD). . . . . . . . . . . . . . . . . . . . . . . . . .4-24

4.5.3.3 Optional External Event Detection Address Channels. . . . . . . . . . . . . . .4-25

4.5.4 Event Selector (ES). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-25

4.5.5 Trace Unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-26

4.5.5.1 Change of Flow and Interrupt Tracing . . . . . . . . . . . . . . . . . . . . . . . . . . .4-28

4.5.5.2 Writing to the Trace Buffer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-29

4.5.5.3 Reading the Trace Buffer (TB_BUFF). . . . . . . . . . . . . . . . . . . . . . . . . . .4-29

4.5.5.4 Trace Unit Programming Model. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-29

4.6 EOnCE Register Addressing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-30

4.6.1 Reading or Writing EOnCE Registers Using Core Software . . . . . . . . . . . . .4-33

4.6.2 Real-Time JTAG Access . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-33

4.6.3 Real-Time Data Transfer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-34

SC140 DSP Core Reference Manual v

Page 6

4.6.4 General EOnCE Register Issues . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-34

4.7 EOnCE Controller Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-36

4.7.1 EOnCE Command Register (ECR). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-36

4.7.2 EOnCE Status Register (ESR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-37

4.7.3 EOnCE Monitor and Control Register (EMCR). . . . . . . . . . . . . . . . . . . . . . .4-41

4.7.4 EOnCE Receive Register (ERCV) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-43

4.7.5 EOnCE Transmit Register (ETRSMT). . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-43

4.7.6 EE Signals. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-44

4.7.6.1 EE Signals as Outputs. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-44

4.7.6.2 EE Signals as Inputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-45

4.7.6.3 EE Signals Control Register (EE_CTRL) . . . . . . . . . . . . . . . . . . . . . . . .4-45

4.7.7 Core Command Register (CORE_CMD) . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-48

4.7.8 PC of the Exception Execution Set (PC_EXCP) . . . . . . . . . . . . . . . . . . . . . .4-49

4.7.9 PC of the Next Execution Set (PC_NEXT) . . . . . . . . . . . . . . . . . . . . . . . . . .4-49

4.7.10 PC of Last Execution Set (PC_LAST) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-49

4.7.11 PC Breakpoint Detection Register (PC_DETECT) . . . . . . . . . . . . . . . . . . . .4-49

4.8 Event Counter Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-50

4.8.1 Event Counter Control Register (ECNT_CTRL) . . . . . . . . . . . . . . . . . . . . . .4-50

4.8.2 Event Counter Value Register (ECNT_VAL) . . . . . . . . . . . . . . . . . . . . . . . .4-52

4.8.3 Extension Counter Value Register (ECNT_EXT) . . . . . . . . . . . . . . . . . . . . .4-53

4.8.4 EC Signals. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-53

4.9 Event Detection Unit (EDU) Channels and Registers . . . . . . . . . . . . . . . . . . . . .4-54

4.9.1 Address Event Detection Channel (EDCA) . . . . . . . . . . . . . . . . . . . . . . . . . .4-54

4.9.1.1 EDCA Control Registers (EDCAi_CTRL). . . . . . . . . . . . . . . . . . . . . . . .4-54

4.9.1.2 EDCA Reference Value Registers A and B

(EDCAi_REFA, EDCAi_REFB) . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-57

4.9.1.3 EDCA Mask Register (EDCAi_MASK) . . . . . . . . . . . . . . . . . . . . . . . . .4-57

4.9.2 Data Event Detection Channel (EDCD). . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-58

4.9.2.1 EDCD Control Register (EDCD_CTRL) . . . . . . . . . . . . . . . . . . . . . . . . .4-58

4.9.2.2 EDCD Reference Value Register (EDCD_REF) . . . . . . . . . . . . . . . . . . .4-61

4.9.2.3 EDCD Mask Register (EDCD_MASK) . . . . . . . . . . . . . . . . . . . . . . . . . .4-61

4.10 Event Selector (ES) Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-61

4.10.1 Event Selector Control Register (ESEL_CTRL) . . . . . . . . . . . . . . . . . . . . . .4-61

4.10.2 Event Selector Mask Debug State Register (ESEL_DM) . . . . . . . . . . . . . . .4-63

4.10.3 Event Selector Mask Debug Exception

Register (ESEL_DI) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-64

4.10.4 Event Selector Mask Enable Trace Register (ESEL_ETB) . . . . . . . . . . . . . .4-64

4.10.5 Event Selector Mask Disable Trace Register (ESEL_DTB) . . . . . . . . . . . . .4-65

4.11 Trace Unit Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-65

4.11.1 Trace Buffer Control Register (TB_CTRL) . . . . . . . . . . . . . . . . . . . . . . . . . .4-65

4.11.2 Trace Buffer Read Pointer Register (TB_RD) . . . . . . . . . . . . . . . . . . . . . . . .4-69

4.11.3 Trace Buffer Write Pointer Register (TB_WR) . . . . . . . . . . . . . . . . . . . . . . .4-69

4.11.4 Trace Buffer Register (TB_BUFF). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-69

vi SC140 DSP Core Reference Manual

Page 7

Chapter 5

Program Control

5.1 Pipeline . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-1

5.1.1 Instruction Pipeline Stages . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-2

5.1.1.1 Instruction Pre-Fetch and Fetch . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-4

5.1.1.2 Instruction Dispatch . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-4

5.1.1.3 Address Generation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-4

5.1.1.4 Execution . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-5

5.2 Instruction Grouping. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-5

5.2.1 Grouping Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-6

5.2.1.1 Serial Grouping. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-7

5.2.1.2 Prefix Grouping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-7

5.2.2 Prefix Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-8

5.2.2.1 Two-Word Prefix . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-8

5.2.2.2 One-Word Low Register Prefix . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-9

5.2.3 Conditional Execution . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-9

5.2.4 Prefix Selection Algorithm. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-10

5.2.5 Instruction Reordering Within an Execution Set . . . . . . . . . . . . . . . . . . . . . .5-12

5.3 Instruction Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-14

5.3.1 Sequential Instruction Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-15

5.3.1.1 DALU Instruction Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-16

5.3.1.2 Move Instruction Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-16

5.3.1.3 Bit Mask Instruction Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-16

5.3.2 Change-Of-Flow Instruction Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-17

5.3.2.1 Direct, PC-Relative, and Conditional COF . . . . . . . . . . . . . . . . . . . . . . .5-18

5.3.2.2 Delayed COF . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-19

5.3.2.3 COF Execution Cycles . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-19

5.3.3 Memory Access Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-21

5.3.3.1 Memory Access Examples . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-22

5.3.3.2 Implicit Push/Pop Memory Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-24

5.3.3.3 Memory Stall Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-24

5.4 Hardware Loops . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-25

5.4.1 Loop Programming Model . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-25

5.4.1.1 Loop Start Address Registers (SAn). . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-25

5.4.1.2 Loop Counter Registers (LCn) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-26

5.4.1.3 Status Register (SR) Loop Flag Bits. . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-26

5.4.2 Loop Notation and Encoding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-26

5.4.3 Loop Initiation and Execution . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-27

5.4.4 Loop Nesting. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-28

5.4.5 Loop Iteration and Termination . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-28

5.4.6 Loop Control Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-29

5.4.7 Loop Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-32

5.5 Stack Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-32

5.5.1 SC140 Single Stack Memory Use . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-32

5.5.2 SC140 Dual Stack Memory Use. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-33

5.5.3 Stack Support Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-34

5.5.4 Shadow Stack Pointer Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-35

SC140 DSP Core Reference Manual vii

Page 8

5.5.5 Fast Return from Subroutines. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-36

5.6 Working Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-37

5.6.1 Normal Working Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-37

5.6.2 Exception Working Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-37

5.6.3 Typical Working Mode Usage Scenarios. . . . . . . . . . . . . . . . . . . . . . . . . . . .5-38

5.6.3.1 Dual-stack RTOS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-38

5.6.3.2 Single-stack RTOS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-39

5.6.4 Working Mode Transitions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-39

5.6.4.1 From Exception to Normal mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-39

5.6.4.2 From Normal to Exception mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-39

5.7 Processing States. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-41

5.7.1 Processing State Change Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-41

5.7.2 Processing State Transitions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-42

5.7.3 Execution State . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-43

5.7.4 Reset Processing State . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-43

5.7.5 Debug State. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-44

5.7.6 Wait Processing State . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-44

5.7.7 Stop Processing State . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-45

5.8 Exception Processing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-46

5.8.1 Interrupt Vector Address . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-48

5.8.1.1 Vector Base Address Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-48

5.8.1.2 Programming Exception Routine Addresses . . . . . . . . . . . . . . . . . . . . . .5-48

5.8.2 Return From Exception Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-49

5.8.3 Maskable Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-50

5.8.3.1 Interrupt Priority Level. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-50

5.8.3.2 Controlling All Interrupt Sources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-50

5.8.4 Non-Maskable Interrupts (NMI). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-50

5.8.5 Internal Exceptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-50

5.8.5.1 Illegal Exception. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-51

5.8.5.2 DALU Overflow. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-52

5.8.5.3 TRAP Exception. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-52

5.8.5.4 Debug Exception. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-52

5.8.6 Exception Interface to the Pipeline. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-52

5.8.6.1 Exception Routine Fetch. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-52

5.8.6.2 Exception Mode Execution. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-53

5.8.7 Exception Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-53

Chapter 6

Instruction Set Accelerator Plug-In

6.1 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-57

6.2 ISAP - SC140 Schematic Connection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-58

6.2.1 Single ISAP. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-58

6.2.2 Multiple ISAP. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-59

6.3 ISAP instructions and instruction encoding . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-60

6.4 ISAP Memory Access. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-60

6.5 ISAP-core register transfers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-61

6.6 Immediate Data Transfer to ISAP registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-62

viii SC140 DSP Core Reference Manual

Page 9

6.7 Core Assembly Syntax with an ISAP. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-63

6.7.1 Identification of ISAP instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-63

6.7.1.1 Working with One ISAP. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-63

6.7.1.2 Working with Multiple ISAPs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-64

6.7.2 An Example of the Definition Flexibility of an ISAP . . . . . . . . . . . . . . . . . .6-65

6.7.3 Conditional Execution . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-66

6.8 Programming Rules . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-67

6.8.1 ISAP Functions that Interact With the Core. . . . . . . . . . . . . . . . . . . . . . . . . .6-67

6.8.2 Grouping rules for explicit ISAP instructions . . . . . . . . . . . . . . . . . . . . . . . .6-68

6.8.3 Rules for implicit AGU instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-68

6.8.4 Sequencing rules for T bit update. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-69

Chapter 7

Programming Rules

7.1 VLES Sequencing Semantics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-1

7.2 VLES Grouping Semantics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-1

7.3 SC140 Pipeline Exposure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-3

7.4 Programming Rule Notation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-3

7.4.1 Grouping Rules. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-3

7.4.1.1 Prefix Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-3

7.4.1.2 Conditional Subgroups . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-3

7.4.1.3 Assembler Reordering . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-3

7.4.2 Sequencing Rules . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-4

7.4.2.1 Cycle Counts. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-4

7.4.2.2 Conditional Execution . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-4

7.4.2.3 Simulator Execution Counts. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-4

7.4.3 Register Read/Write . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-4

7.4.3.1 Register Names. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-4

7.4.3.2 B Register Aliasing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-5

7.4.4 Status Bit Updates. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-5

7.4.5 Instruction Words . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-5

7.4.6 MOVE-like Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-5

7.4.6.1 Address/Data Operands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-5

7.4.7 AGU Arithmetic Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-6

7.4.8 Change-Of-Flow Destinations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-6

7.4.8.1 COF Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-6

7.4.9 Delayed COF Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-6

7.4.9.1 Delay Slot . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-6

7.4.10 Hardware Loops . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-7

7.4.10.1 Enabled Loop . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-7

7.4.10.2 Enveloping Loop. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-7

7.5 Static Programming Rules . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-7

7.5.1 Hardware Loop Detection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-7

7.5.2 General Grouping Rules . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-8

7.5.3 Prefix Grouping Rules . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-11

7.5.4 AGU Rules . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-16

7.5.5 Delayed COF Rules . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-19

SC140 DSP Core Reference Manual ix

Page 10

7.5.6 Status Bit Rules. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-22

7.5.7 Loop Nesting Rules . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-28

7.5.8 Loop LA Rules . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-31

7.5.9 Loop Sequencing Rules . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-33

7.5.10 Loop COF Rules. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-36

7.5.11 General Looping Rules. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-40

7.6 Dynamic Programming Rules. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-41

7.6.1 AGU Dynamic Rules . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-41

7.6.2 Memory Access Rules . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-42

7.6.3 RAS Rules. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-43

7.6.4 Loop Rules . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-43

7.6.5 Rule Detection Across COF Boundaries . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-44

7.6.5.1 Cycle-Based COF Rules. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-44

7.6.5.2 VLES-Based COF Rules . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-45

7.6.6 Rule Detection Across Exception Boundaries . . . . . . . . . . . . . . . . . . . . . . . .7-46

7.7 Programming Guidelines . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-48

7.7.1 Rules Not Detected Across COF Boundaries. . . . . . . . . . . . . . . . . . . . . . . . .7-49

7.7.2 Good Programming Practices. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-49

7.7.2.1 Source Code Practices . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-49

7.7.2.2 Binary Code Practices. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-50

7.7.2.3 Software Development Practices . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-51

7.8 LPMARK Rules . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-51

7.8.1 LPMARK Instruction Type . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-51

7.8.2 Static Programming Rules . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-52

7.8.2.1 General Grouping Rules . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-52

7.8.2.2 Prefix Grouping Rules . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-52

7.8.3 Dynamic Programming Rules. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-52

7.8.3.1 LPMARK Notation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-52

7.8.3.2 Loop Nesting Rules . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-53

7.8.3.3 Loop LA Rules . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-53

7.8.3.4 Loop Sequencing Rules . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-55

7.8.3.5 Loop COF Rules. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-56

7.8.3.6 General Looping Rules. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-59

7.8.3.7 Rule Detection Across Exception Boundaries . . . . . . . . . . . . . . . . . . . . .7-59

7.8.4 LPMARK Programming Guidelines . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-59

7.9 NOP Definition. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-60

7.9.1 Grouping Examples . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-61

Appendix A

SC140 DSP Core Instruction Set

A.1 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-1

A.1.1 Conventions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-2

A.1.1.1 Brackets as ISAP indicators . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-4

A.1.1.2 Brackets as address indicators . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-4

A.1.2 Addressing Mode Notation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-5

A.1.3 Data Representation in Memory for the Examples. . . . . . . . . . . . . . . . . . . . . A-6

A.1.4 Encoding Notation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-6

x SC140 DSP Core Reference Manual

Page 11

A.1.5 Prefix Word Encoding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-7

A.1.5.1 One-Word Low Register Prefix . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-8

A.1.5.2 Two-Word Prefix . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-9

A.1.6 Instruction Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-12

A.1.6.1 Instruction Sub-types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-12

A.2 Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-19

A.2.1 Instruction Definition Layout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-19

Appendix B

StarCore Registry

B.1 Using the StarCore Registry . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-1

SC140 DSP Core Reference Manual xi

Page 12

xii SC140 DSP Core Reference Manual

Page 13

List of Figures

1-1 Block Diagram of a Typical SoC Configuration with the SC140 Core . . . . . . . 1-5

2-1 Block Diagram of the SC140 Core. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-2

2-2 DALU Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-6

2-3 DALU Data Representations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-18

2-4 Fractional and Integer Multiplication . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-20

2-5 Convergent Rounding (No Scaling) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-22

2-6 Two’s Complement Rounding (No Scaling) . . . . . . . . . . . . . . . . . . . . . . . . . . 2-24

2-7 DMAC Implementation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-26

2-8 Fractional Double-Precision Multiplication . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-27

2-9 Fractional Mixed-Precision Multiplication. . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-28

2-10 Signed Integer Double-Precision Multiplication . . . . . . . . . . . . . . . . . . . . . . . 2-29

2-11 Unsigned Integer Double-Precision Multiplication . . . . . . . . . . . . . . . . . . . . . 2-30

2-12 AGU Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-32

2-13 AGU Programming Model . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-34

2-14 Modifier Control Register (MCTL) Format . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-37

2-15 Modulo Addressing Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-46

2-16 Integer Move Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-53

2-17 Fractional Move Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-54

2-18 Bit Allocation in MOVE.L D0.e:D1.e . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-55

2-19 Endian Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-56

2-20 Basic Connection between SC140 Core and Memory . . . . . . . . . . . . . . . . . . . 2-57

2-21 Memory Organization of Big and Little Endian Mode. . . . . . . . . . . . . . . . . . . 2-57

2-22 Data Transfer in Big and Little Endian Modes. . . . . . . . . . . . . . . . . . . . . . . . . 2-59

2-23 Multi-Register Transfer in Big and Little Endian Modes. . . . . . . . . . . . . . . . . 2-61

2-24 Program Memory Organization in Big and Little Endian Modes . . . . . . . . . . 2-62

2-25 Instruction Moves in Big and Little Endian Modes . . . . . . . . . . . . . . . . . . . . . 2-63

3-1 Status Register -SR. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-2

3-2 Exception and Mode Register (EMR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-7

4-1 JTAG and EOnCE Multi-core Interconnection . . . . . . . . . . . . . . . . . . . . . . . . . 4-3

4-2 TAP Controller State Machine . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-5

4-3 Cascading Multiple EOnCE Modules. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-7

4-4 Reading and Writing EOnCE Registers Via JTAG . . . . . . . . . . . . . . . . . . . . . . 4-8

4-5 Accessing EOnCE registers through JTAG . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-9

4-6 Typical Debugging System. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-10

SC140 DSP Core Reference Manual xiii

Page 14

4-7 Software Downloading . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-13

4-8 EOnCE Controller Block Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-17

4-9 Event Counter Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-19

4-10 Event Detection Unit Block Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-21

4-11 EDCA Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-22

4-12 EDCD Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-24

4-13 Event Selector Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-26

4-14 Trace Unit Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-28

4-15 EOnCE Command Register (ECR). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-36

4-16 EOnCE Status Register (ESR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-38

4-17 EOnCE Monitor and Control Register (EMCR). . . . . . . . . . . . . . . . . . . . . . . . 4-41

4-18 EE Signals Control Register (EE_CTRL) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-45

4-19 Injected Instruction Format. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-48

4-20 Event Counter Register (ECNT_CTRL). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-51

4-21 EDCA Control Register (EDCAi_CTRL) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-54

4-22 EDCD Control Register (EDCD_CTRL). . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-58

4-23 Event Selector Control Register (ESEL_CTRL) . . . . . . . . . . . . . . . . . . . . . . . 4-62

4-24 Event Selector Mask Debug State (ESEL_DM). . . . . . . . . . . . . . . . . . . . . . . . 4-63

4-25 Event Selector Mask Debug Exception (ESEL_DI). . . . . . . . . . . . . . . . . . . . . 4-64

4-26 Event Selector Mask Enable Trace (ESEL_ETB) . . . . . . . . . . . . . . . . . . . . . . 4-64

4-27 Event Selector Mask Disable Trace (ESEL_DTB). . . . . . . . . . . . . . . . . . . . . . 4-65

4-28 Trace Buffer Control Register (TB_CTRL) . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-67

5-1 Instruction Pipeline Stages . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-2

5-2 Instruction Grouping Methods . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-6

5-3 Low Register Prefix Selection Algorithm . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-11

5-4 Hardware Loop Programming Model. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-25

5-5 Loop Nesting. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-28

5-6 SC140 Memory Use with a Single Stack Pointer. . . . . . . . . . . . . . . . . . . . . . . 5-32

5-7 SC140 Memory Use with Dual Stack Pointers. . . . . . . . . . . . . . . . . . . . . . . . . 5-33

5-8 Working mode Transitions - Unprotected Dual-stack RTOS. . . . . . . . . . . . . . 5-38

5-9 Working mode Transitions - Unprotected Single-stack RTOS . . . . . . . . . . . . 5-39

5-10 Core State Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-42

5-11 Core-PIC Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-47

5-12 Flowchart for Exception Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-55

6-1 Core to Single ISAP Connection Schematic. . . . . . . . . . . . . . . . . . . . . . . . . . . 6-58

6-2 Core to Multiple ISAP Connection Schematic. . . . . . . . . . . . . . . . . . . . . . . . . 6-59

xiv SC140 DSP Core Reference Manual

Page 15

List of Tables

2-1 DALU Programming Model. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-7

2-2 Write to Data Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-9

2-3 Read from Data Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-9

2-4 Data Registers Access Width . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-10

2-5 DALU Arithmetic Instructions (MAC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-10

2-6 DALU Logical Instructions (BFU). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-13

2-7 Scaling Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-14

2-8 Ln Bit Calculation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-15

2-9 Limiting Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-16

2-10 Scaling and Limiting Interactions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-16

2-11 Saturation and Rounding Interactions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-17

2-12 Two’s Complement Word Representations . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-19

2-13 Rounding Position in Relation to Scaling Mode . . . . . . . . . . . . . . . . . . . . . . . 2-21

2-14 Arithmetic Saturation Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-25

2-15 Fractional Signed and Unsigned Two’s Complement Multiplication . . . . . . . 2-26

2-16 Integer Signed and Unsigned Two’s Complement Multiplication. . . . . . . . . . 2-28

2-17 Address Modifier (AM) Bits. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-37

2-18 Access Width Support for Address and Register Update Calculations . . . . . . 2-42

2-19 Memory Address Alignment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-43

2-20 Addressing Modes Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-43

2-21 Modulo Register Values for Modulo Addressing Mode . . . . . . . . . . . . . . . . . 2-47

2-22 Modulo Register Values for Wrap-Around Modulo Addressing Mode. . . . . . 2-48

2-23 AGU Arithmetic Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-48

2-24 AGU Bit Mask Instructions (BMU) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-50

2-25 AGU Move Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-52

2-26 Data Representation in Memory. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-58

2-27 Move Instructions in Big and Little Endian Modes . . . . . . . . . . . . . . . . . . . . . 2-64

2-28 Stack Support Instructions in Big and Little Endian Modes . . . . . . . . . . . . . . 2-67

2-29 Bit Mask Instructions in Big and Little Endian Modes . . . . . . . . . . . . . . . . . . 2-67

2-31 Control Instructions in Big and Little Endian Modes. . . . . . . . . . . . . . . . . . . . 2-68

2-30 Non-Loop Change-of-Flow Instructions in Big and Little Endian Modes. . . . 2-68

3-1 Status Register Description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-2

3-2 EMR Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-8

4-1 JTAG Interface Signal Descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-2

SC140 DSP Core Reference Manual xv

Page 16

4-2 JTAG Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-3

4-3 JTAG Scan Paths . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-5

4-4 EOnCE Event Types. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-14

4-5 EOnCE Event and Action Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-15

4-6 EOnCE Controller Register Set . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-17

4-7 Event Counter Register Set. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-19

4-8 EDCA Register Set. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-23

4-9 EDCD Register Set. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-24

4-10 Event Selector Register Set. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-26

4-11 Trace Buffer Register Set . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-30

4-12 EOnCE Register Addressing Offsets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-31

4-13 ECR Description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-36

4-14 ESR Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-38

4-15 EMCR Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-41

4-16 EE_CTRL Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-46

4-17 Length Control Bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-48

4-18 ECNT_CTRL Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-51

4-19 EDCA_CTRL Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-54

4-20 EDCD_CTRL Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-58

4-21 ESEL_CTRL Description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-62

4-22 Allowed tracing mode combinations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-66

4-23 TB_CTRL Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-67

5-1 Pipeline Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-3

5-2 Pipeline Stages Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-3

5-3 Prefix Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-9

5-4 Conditional IFc Syntax. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-9

5-5 Instruction Categories Timing Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-15

5-6 Non-Loop Change-of-Flow Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-17

5-7 Loop Change-Of-Flow Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-18

5-8 Number of Cycles Needed by Change-of-Flow Instructions . . . . . . . . . . . . . . 5-20

5-9 LPMARKA and LPMARKB Bits in Short and Long Loops . . . . . . . . . . . . . . 5-27

5-10 Loop Control Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-29

5-11 Stack Push/Pop Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-34

5-12 Even and Odd Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-34

5-13 Stack Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-35

5-14 Stack Move Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-35

5-15 Working Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-37

5-16 Processing State Change Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-41

5-17 Processing State Transitions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-43

xvi SC140 DSP Core Reference Manual

Page 17

5-18 Exit Wait Processing State due to an Interrupt or NMI . . . . . . . . . . . . . . . . . . 5-45

5-19 Exception Vector Address Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-49

5-20 Exception Pipeline . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-53

5-21 Pipeline Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-56

6-1 ISAP Encoding Fields. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-60

A-1 Instruction Conventions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-2

A-2 Operations Syntax. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-3

A-3 Register Abbreviations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-3

A-4 Assembler Syntax . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-4

A-5 Addressing Mode Notation for the EA Operand . . . . . . . . . . . . . . . . . . . . . . . . A-5

A-6 Addressing Mode Notation for the ea Operand . . . . . . . . . . . . . . . . . . . . . . . . . A-5

A-7 DALU Arithmetic Instructions (MAC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-13

A-8 DALU Logical Instructions (BFU). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-14

A-9 AGU Arithmetic Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-15

A-10 AGU Move Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-15

A-11 AGU Stack Support Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-16

A-12 AGU Bit-Mask Instructions (BMU). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-17

A-13 AGU Non-Loop Change-of-Flow Instructions. . . . . . . . . . . . . . . . . . . . . . . . . A-17

A-14 AGU Loop Control (Including Loop COF) Instructions . . . . . . . . . . . . . . . . . A-18

A-15 AGU Program Control Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-18

A-16 Prefix Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-18

A-17 Combinations of LPMARKx Use. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-221

B-1 SCID Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-2

SC140 DSP Core Reference Manual xvii

Page 18

xviii SC140 DSP Core Reference Manual

Page 19

List of Examples

3-1 Clearing an EMR Bit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-10

5-1 Four SC140 Instructions in an Execution Set. . . . . . . . . . . . . . . . . . . . . . . . . . . 5-5

5-2 Grouping Six SC140 Instructions in an Execution Set. . . . . . . . . . . . . . . . . . . . 5-5

5-3 Execution Set with Three One-word and Two Two-word Instructions . . . . . . 5-13

5-4 Conditional VLES Having Two Subgroups . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-13

5-5 Set of 2 Two-word Instructions Requiring a NOP . . . . . . . . . . . . . . . . . . . . . . 5-13

5-6 Delayed Change-of-Flow and Its Delay Slot . . . . . . . . . . . . . . . . . . . . . . . . . . 5-17

5-7 Subroutine Call Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-20

5-8 Parallel Execution of Two Move Instructions . . . . . . . . . . . . . . . . . . . . . . . . . 5-23

5-9 Execution Set Containing a Bit Mask and a Move Instruction. . . . . . . . . . . . . 5-23

5-10 Execution Set Containing One Bit Mask Instruction . . . . . . . . . . . . . . . . . . . . 5-23

5-11 Execution Set Containing a Bit Mask and a Pop Instruction . . . . . . . . . . . . . . 5-24

5-12 Long Loop. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-30

5-13 Long Loop Disassembly. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-30

5-14 Short Loop, Two Execution Sets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-30

5-15 Short Loop, One Execution Set . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-31

5-16 Nested Loop . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-31

5-17 Basic Exception Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-53

6-1 ISAP memory access . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-61

6-2 ISAP-Core register transfers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-62

6-3 ISAP-Core register transfers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-62

6-4 Single ISAP coding. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-63

6-5 Multiple ISAP coding. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-65

6-6 Conditional Execution Example. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-66

6-7 Conditional Execution Example. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-66

6-8 MOVE rules with an implicit MOVE instruction from ISAP . . . . . . . . . . . . . 6-68

7-1 B Register Aliasing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-5

7-2 Delayed COF Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-6

7-3 VLES Word Count Exceeds Eight . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-8

7-4 Too Many AGU Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-8

7-5 Duplicate PC Destinations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-9

7-6 Duplicate Address Pointer Register Destinations. . . . . . . . . . . . . . . . . . . . . . . . 7-9

SC140 DSP Core Reference Manual xix

Page 20

7-7 Duplicate Stack Pointer Destinations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-9

7-8 Duplicate Register Destinations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-10

7-9 Duplicate SR/EMR Register Destinations . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-10

7-10 Duplicate Status Bit Destinations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-10

7-11 Dual Stack Pointer Destination Exception . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-10

7-12 Mutually Exclusive Register Destination Exception . . . . . . . . . . . . . . . . . . . . 7-11

7-13 Mutually Exclusive Status Bit Destination Exception . . . . . . . . . . . . . . . . . . . 7-11

7-14 Multiple C, S and DOVF Status Bit Destination Exception. . . . . . . . . . . . . . . 7-11

7-15 DALU Register Use Exceeds Four Times . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-11

7-16 VLES Extension Words Exceed Two. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-12

7-17 Two-Word Instructions Exceed Two . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-12

7-18 VLES Has Mutually Exclusive Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . 7-13

7-19 RTE Uses Both AAU . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-13

7-20 Data Source Use of Nn and Mn Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-14

7-21 IFc Having Two Subgroups . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-14

7-22 IFA Subgroup Must Be Last Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-14

7-23 Core AGU instructions on same VLES as ISAP instructions . . . . . . . . . . . . . 7-15

7-24 ISAP instructions in same IFc group . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-15

7-25 MCTL Write to R0-R7 Use . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-16

7-26 Rn, Nn, Mn Write to AGU Use . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-17

7-27 Rn or Nn Write to MOVE-like Use . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-18

7-28 LCn Write to MOVE-like Use . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-18

7-29 NMID Update to EMR Read . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-19

7-30 Instructions in a Delay Slot. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-19

7-31 Instructions in a RTED Delay Slot . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-20

7-32 RTE/D with SR Updates . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-20

7-33 PC Read in a Return Delay Slot . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-21

7-34 SR Write with a Subroutine Call . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-21

7-35 SR Write in BSRD or JSRD Delay Slot . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-21

7-36 SP Use in Return Delay Slots . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-21

7-37 SR Read in a CONTD Delay Slot. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-22

7-38 EMR Use in Return Delay Slots. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-22

7-39 T Bit Update to IFT/IFF AGU Use. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-22

7-40 T Bit Update by ISAP and COF . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-23

7-41 T Bit Update by ISAP and MOVET/MOVEF . . . . . . . . . . . . . . . . . . . . . . . . . 7-23

7-42 T Bit Update by ISAP and IFT/IFF . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-23

7-43 SR Write to SR Status Bit Use . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-25

xx SC140 DSP Core Reference Manual

Page 21

7-44 SR Write to SR Status Bit Update . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-26

7-45 DOVF Update to SR Read or Write . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-27

7-46 DOVF Update grouped with Move-like SR updates . . . . . . . . . . . . . . . . . . . . 7-27

7-47 Status Bit Update with SR Read. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-28

7-48 Nested Loops with the Same LA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-28

7-49 Nested Loops with Ordered Index . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-29

7-50 Nested DOENn/DOENSHn Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-29

7-51 DOENn instruction following DOENSHn Instruction. . . . . . . . . . . . . . . . . . . 7-30

7-52 LOOPEND between DOEN and LOOPEND. . . . . . . . . . . . . . . . . . . . . . . . . . 7-30

7-53 Changing a loop type . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-30

7-54 Instructions at the End of Long Loops . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-31

7-55 LCn Write at the End of Long Loop n . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-31

7-56 Instructions in Short Loops. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-32

7-57 Short Loop LA at the End of a Long Loop. . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-32

7-58 LCn Write to SKIPLS Instruction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-33

7-59 LCn Write at the End of Long Loop n . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-33

7-60 LCn Write at the Start of Short Loop n . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-34

7-61 LCn Write to CONT/D Instruction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-34

7-62 SAn Write at the End of Long Loop n . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-35

7-63 SAn Write to CONT/D Instruction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-35

7-64 LCn Read at the Start of Short Loop n . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-35

7-65 COF Destination to Loop Delay Slots . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-36

7-66 COF Instructions at LA-2 of a Long Loop . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-36

7-67 Bc/Jc at SA-1 of a Short Loop . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-36

7-68 Bc/Jc at LA-3 of a Long Loop . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-37

7-69 Loop COF Destination in the Same Loop . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-38

7-70 Loop COF at End of Nested Long Loops. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-39

7-71 Subroutine Call to End of Loops . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-39

7-72 Delayed COF at LA-3 of a Long Loop. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-40

7-73 Delayed COF at SA-1 of a Short Loop. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-40

7-74 SR Read to LA of Any Long Loop. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-40

7-75 SR Read to SA of Any Short Loop. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-40

7-76 Enabling Short and Long Loops. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-41

7-77 Bn, Mn Write to AGU Use. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-41

7-78 Multiple Memory Writes to the Same Location. . . . . . . . . . . . . . . . . . . . . . . . 7-42

7-79 Pre-Calculated Memory Accesses to the Same Location. . . . . . . . . . . . . . . . . 7-42

7-80 Memory Write to Stack in a Return Delay Slot . . . . . . . . . . . . . . . . . . . . . . . . 7-42

SC140 DSP Core Reference Manual xxi

Page 22

7-81 Illegal use of RAS value. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-43

7-82 SR.2 Across a COF Boundary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-44

7-83 A.2 from a Delay Slot to a COF Destination . . . . . . . . . . . . . . . . . . . . . . . . . . 7-44

7-84 Set condition during a COF, and use it at the destination (T.1) . . . . . . . . . . . . 7-45

7-85 EMR access at the start of an exception . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-46

7-86 MCTL Write to R0-R7 Use . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-47

7-87 Invalid COF Destination Cannot be Detected . . . . . . . . . . . . . . . . . . . . . . . . . 7-48

7-88 COF Destination in the Middle of a VLES. . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-48

7-89 COF Destination in a Delay Slot . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-48

7-90 LFn Enabled During Loop Body n . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-49

7-91 LFn Enabled at LPA or LPB. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-53

7-92 Instructions at the End of Long Loops . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-53

7-93 Active LCn Write at the End of Long Loops . . . . . . . . . . . . . . . . . . . . . . . . . . 7-54

7-94 Instructions in Short Loops. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-54

7-95 Active LCn Write at the Start of a Loop. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-55

7-96 Active SAn Write at the End of Long Loops . . . . . . . . . . . . . . . . . . . . . . . . . . 7-55

7-97 Active LCn Read at the Start of a Loop . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-56

7-98 COF Instructions at LPB of a Long Loop. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-57

7-99 Bc/Jc at the Start of a Loop. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-57

7-100 Loop COF at End of Nested Long Loops. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-58

7-101 Subroutine Call to End of Loops . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-58

7-102 Delay Slot at LPA or LPB of a Loop . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-59

7-103 SR Read to LPA or LPB of a Loop . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-59

7-104 COF Destination to Loop Delay Slots . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-60

xxii SC140 DSP Core Reference Manual

Page 23

About This Book

This manual provides reference information for the StarCore SC140 digital signal processor (DSP) core.

Specifically, this book describes the instruction set architecture and programming model for the SC140

core as well as corresponding register details, debug capabilities, and programming rules.

An appendix provides a detailed instruction reference for the SC140 instruction set, describing the

operation, mnemonics, instruction fields, and encoding for each instruction. Instruction examples are also

provided.

The resulting system-on-chip devices designed around the SC140 core will usually include additional

functional blocks such as on-chip memory, an external memory interface, peripheral accelerators, and

coprocessor devices. The specification of these functional blocks is customer-specific as well as

application-specific. Therefore, this information is not covered in this manual.

Audience

This manual is intended for systems software developers, hardware designers, and application developers.

Organization

This book is organized into six chapters and one appendix as follows:

• Chapter 1, “Introduction”, describes key features of the SC140 architecture. This chapter also

illustrates a typical system using the SC140 core.

• Chapter 2, “Core Architecture”, describes the main functional blo cks and data paths of the SC140

core.