Page 1

QE128 Quick Reference User Guide

Devices Supported:

MCF51QE128

MC9S08QE128

Document Number: QE128QRUG

Rev. 1.0

10/2007

Page 2

How to Reach Us:

Home Page:

www.freescale.com

E-mail:

support@freescale.com

USA/Europe or Locations Not Listed:

Freescale Semiconductor

Technical Information Center, CH370

1300 N. Alma School Road

Chandler, Arizona 85224

+1-800-521-6274 or +1-480-768-2130

support@freescale.com

Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH

Technical Information Center

Schatzbogen 7

81829 Muenchen, Germany

+44 1296 380 456 (English)

+46 8 52200080 (English)

+49 89 92103 559 (German)

+33 1 69 35 48 48 (French)

support@freescale.com

Japan:

Freescale Semiconductor Japan Ltd.

Headquarters

ARCO Tower 15F

1-8-1, Shimo-Meguro, Meguro-ku,

Tokyo 153-0064, Japan

0120 191014 or +81 3 5437 9125

support.japan@freescale.com

Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd.

Technical Information Center

2 Dai King Street

Tai Po Industrial Estate

Tai Po, N.T., Hong Kong

+800 26668334

support.asia@freescale.com

For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center

P.O. Box 5405

Denver, Colorado 80217

1-800-441-2447 or 303-675-2140

Fax: 303-675-2150

LDCForFreescaleSemiconductor@hibbertgroup.com

Information in this document is provided solely to enable system and

software implementers to use Freescale Semiconductor products. There are

no express or implied copyright licenses granted hereunder to design or

fabricate any integrated circuits or integrated circuits based on the

information in this document.

Freescale Semiconductor reserves the right to make changes without further

notice to any products herein. Freescale Semiconductor makes no warranty,

representation or guarantee regarding the suitability of its products for any

particular pur pose, nor does Freescale Semiconductor assume any liability

arising out of the application or use of any product or circuit, and specifically

disclaims any and all liability, including without limitation consequential or

incidental damages. “Typical” parameters that may be provided in Freescale

Semiconductor data sheets and/or specifications can and do vary in different

applications and actual performance may vary over time. All operating

parameters, including “Typicals”, must be validated for each customer

application by customer’s technical exper ts. Freescale Semiconductor does

not convey any license under its patent rights nor the rights of others.

Freescale Semiconductor products are not designed, intended, or authorized

for use as components in systems intended for surgical implant into the body,

or other applications intended to support or sustain life, or for any other

application in which the failure of the Freescale Semico nductor product could

create a situation where personal injury or death may occur. Should Buyer

purchase or use Freescale Semicondu ctor products for any such unintended

or unauthorized application, Buyer shall indemnify and hold Freescale

Semiconductor and its officers, employees, subsidiaries, affiliates, and

distributors harmless against all claims, costs, damages, and expenses, and

reasonable attorney fees arising out of, directly or indirectly, any claim of

personal injury or death associated with such unintended or unauthorized

use, even if such claim alleges that Freescale Semiconductor was negligent

regarding the design or manufacture of the part.

Freescale™ and the Freescale logo are trademarks of Freescale

Semiconductor, Inc. All other product or service names are the property of their

respective owners.

© Freescale Semiconductor, Inc. 2007. All rights reserved.

QE128QRUG

Rev. 1.0

10/2007

Page 3

Chapter 1

QE Peripheral Module Quick Reference User Guide

Chapter 2

QE MCUs 8-bit and 32-bit Comparison

2.1 Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1

2.2 Cores Comparison . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1

2.2.1 V1 core . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1

2.2.2 QE S08 core . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-10

2.2.3 ColdFire V1 or 9S08QE. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-12

2.3 Features Comparison . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-18

2.3.1 On-Chip Memory Comparison . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-18

2.3.2 Power-Saving Modes and Power-Saving Features Comparison . . . . . . . . . . 1-18

2.3.3 Package Comparison . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-18

2.3.4 Clock Comparison . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-19

2.3.5 System Comparison . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-19

2.3.6 Input/Output Comparison. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-19

2.3.7 Development Support Comparison . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-20

2.3.8 Peripherals Comparison . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-20

Chapter 3

How to Load the QRUG Examples?

3.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1

3.2 Steps to programming the MCU using Multilink . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1

3.3 Steps to programming the MCU Using In-Circuit BDM. . . . . . . . . . . . . . . . . . . . . . . . . . 1-6

Chapter 4

Using the Keyboard Interrupt (KBI) for the QE Microcontrollers

4.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1

4.2 KBI project for EVB. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1

4.2.1 Code example and explanation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1

4.2.2 Hardware Implementation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-3

4.3 KBI project for Demo board . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-5

4.3.1 Code example and explanation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-5

4.3.2 Hardware Implementation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-6

Chapter 5

Using the Internal Clock Source (ICS) for the QE Microcontrollers

5.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1

5.2 Code Example and Explanation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1

5.3 Hardware Implementation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-4

Freescale Semiconductor -1

QE128 Quick Reference User Guide, Rev. 1.0

Page 4

Chapter 6

Using the Inter-Integrated Circuit (IIC) for the QE Microcontrollers

6.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1

6.2 Code Example and Explanation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1

6.2.1 IIC Master Project . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-2

6.2.2 IIC Slave Project . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-6

6.3 Hardware Implementation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-7

Chapter 7

Using the Analog Comparator (ACMP) for the QE Microcontrollers

7.1 Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1

7.2 ACMP project for EVB . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-2

7.2.1 Code Example and Explanation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-2

7.2.2 Hardware Implementation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-4

7.3 ACMP project for Demo board . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-5

7.3.1 Code Example and Explanation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-5

7.3.2 Hardware Inplementation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-6

Chapter 8

Using the Analog to Digital Converter (ADC) for the QE Microcontrollers

8.1 Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1

8.2 ADC project for EVB . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-2

8.2.1 Code Example and Explanation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-2

8.2.2 Hardware Implementation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-4

8.3 ADC project for Demo board . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-5

8.3.1 Code Example and Explanation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-5

8.3.2 Hardware Implementation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-6

Using the Real Time Counter (RTC) for the QE Microcontrollers

9.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1

9.2 RTC project for EVB . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1

9.2.1 Code Example and Explanation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1

9.2.2 Hardware Implementation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-3

9.3 RTC project for Demo board . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-4

9.3.1 Code Example and Explanation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-4

9.3.2 Hardware Implementation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-5

Using the Serial Communications Interface (SCI) for the QE Microcontrollers

10.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1

10.2 SCI project for EVB . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1

Chapter 9

Chapter 10

QE128 Quick Reference User Guide, Rev. 1.0

Freescale Semiconductor-2

Page 5

10.2.1 Code Example and Explanation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1

10.2.2 Hardware Implementation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-3

10.3 SCI project for Demo board . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-4

10.3.1 Code Example and Explanation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-4

10.3.2 Hardware Implementation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-5

Chapter 11

Using the Serial Peripheral Interface (SPI) for the QE Microcontrollers

11.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1

11.2 SPI project for EVB. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1

11.2.1 Code Example and Explanation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1

11.2.2 Hardware Implementation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-5

11.3 SPI project for Demo board . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-6

11.3.1 Code Example and Explanation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-6

11.3.2 Hardware Implementation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-9

Chapter 12

Generating PWM Signals Using Timer/Pulse-Width Modulator (TPM) Module

for the QE Microcontrollers

12.1 Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1

12.2 PWM project for EVB . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-2

12.2.1 Code Example and Explanation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-2

12.2.2 Hardware Implementation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-4

12.3 PWM project for Demo board . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-5

12.3.1 Code Example and Explanation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-5

12.3.2 Hardware Implementation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-6

Chapter 13

Using the Output Compare function with the Timer/Pulse-Width Modulator

(TPM) module for the QE Microcontrollers

13.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1

13.2 TPM Project for EVB . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-2

13.2.1 Code Example and Explanation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-2

13.2.2 Hardware Implementation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-4

13.3 TPM project for Demo board . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-5

13.3.1 Code Example and Explanation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-5

13.3.2 Hardware Implementation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-6

Chapter 14

Using the Rapid General Purpose I/O (RGPIO) for the MCF51QE128 Micro-

controllers

14.1 Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1

QE128 Quick Reference User Guide, Rev. 1.0

Freescale Semiconductor -3

Page 6

14.2 Code Example and Explanation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1

14.3 Simulation steps . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-2

14.4 Hardware Implementation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-7

QE128 Quick Reference User Guide, Rev. 1.0

Freescale Semiconductor-4

Page 7

Chapter 1

QE Peripheral Module Quick Reference User Guide

A Compilation of Demonstration Firmware for QE Modules

This document is a brief description of the QE128 microcontroller unit (MCU) in an 8-bit version and

32-bit version. There is also useful information about core differences.

This document is a compilation of code examples and quick reference materials that have been created to

help users speed the development of their applications. Each section in this document contains an example

that works with an evaluation board (EVB) and Demo board with both 8-bit and 32-bit cores versions.

These examples were developed using CodeWarriorTM 6.0 version. Consult the device reference manual

for specific part information.

NOTE

• The provided examples were made to be used with the MC9S08QE128

and MCF51QE128 in an 80-pin and 64-bit package, but could be easily

migrated to a different QE device, pay attention to the used pins.

• All the example projects were developed in two different boards:

EVBQE128 STARTER KIT and DEMO board, no extra hardware is

needed except for the ACMP module, SPI, and IIC.

Revision History

Date

25-Jun-07 0 Initial public release. N/A

19-Oct-07 1.0 Changes in template, function names and other minor corrections. N/A

Revision

Level

Description

QE128 Quick Reference User Guide, Rev. 1.0

Number(s)

Page

Freescale Semiconductor 1-1

Page 8

QE Peripheral Module Quick Reference User Guide

1-2 Freescale Semiconductor

QE128 Quick Reference User Guide, Rev. 1.0

Page 9

Chapter 2

QE MCUs 8-bit and 32-bit Comparison

2.1 Overview

This is a brief explanation of MCU architectures. It has helpful information about cores, addressing modes

and exception processing. The intention of this section is to provide an overview of the S08 and V1 Core.

Further information can be found in reference manuals at www.freescale.com.

2.2 Cores Comparison

2.2.1 V1 core

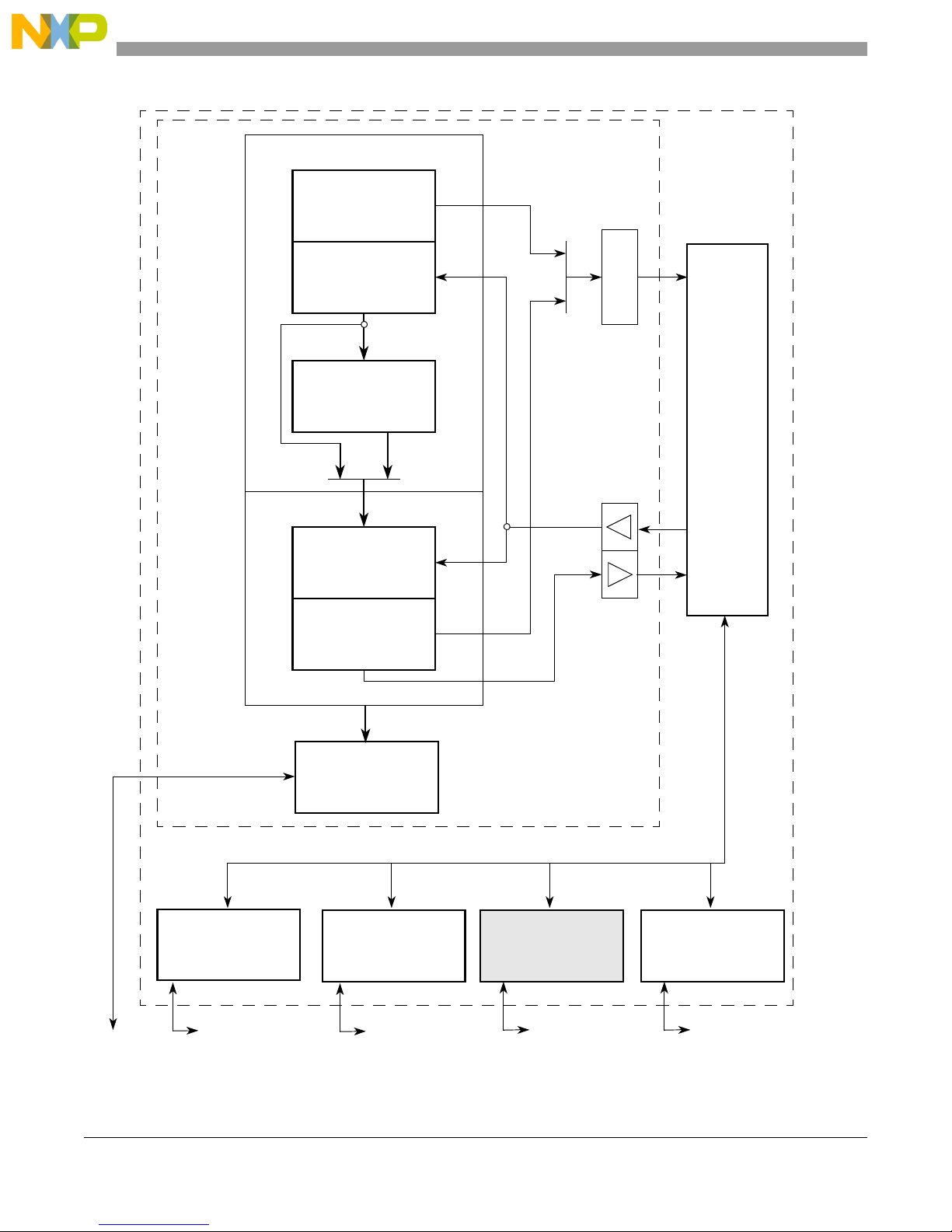

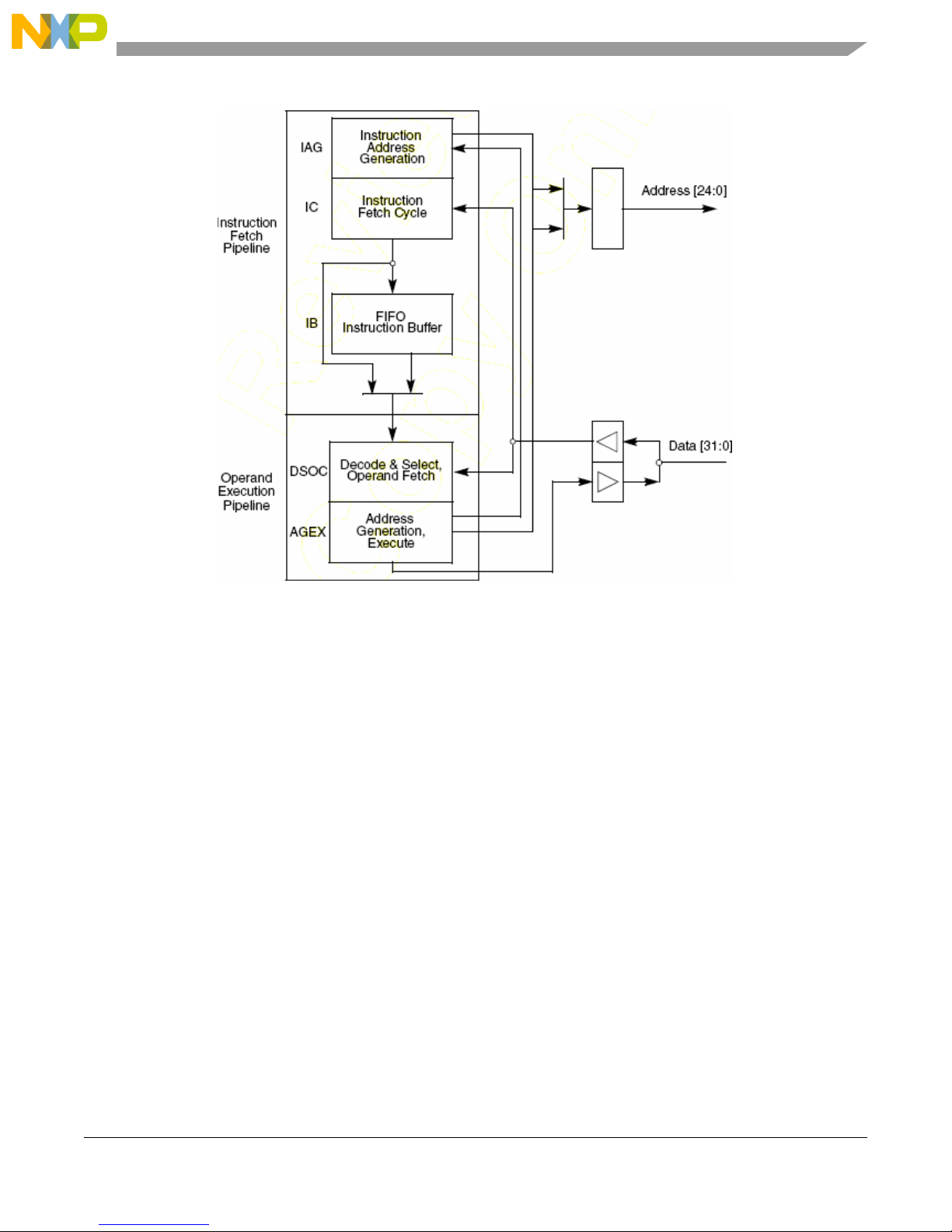

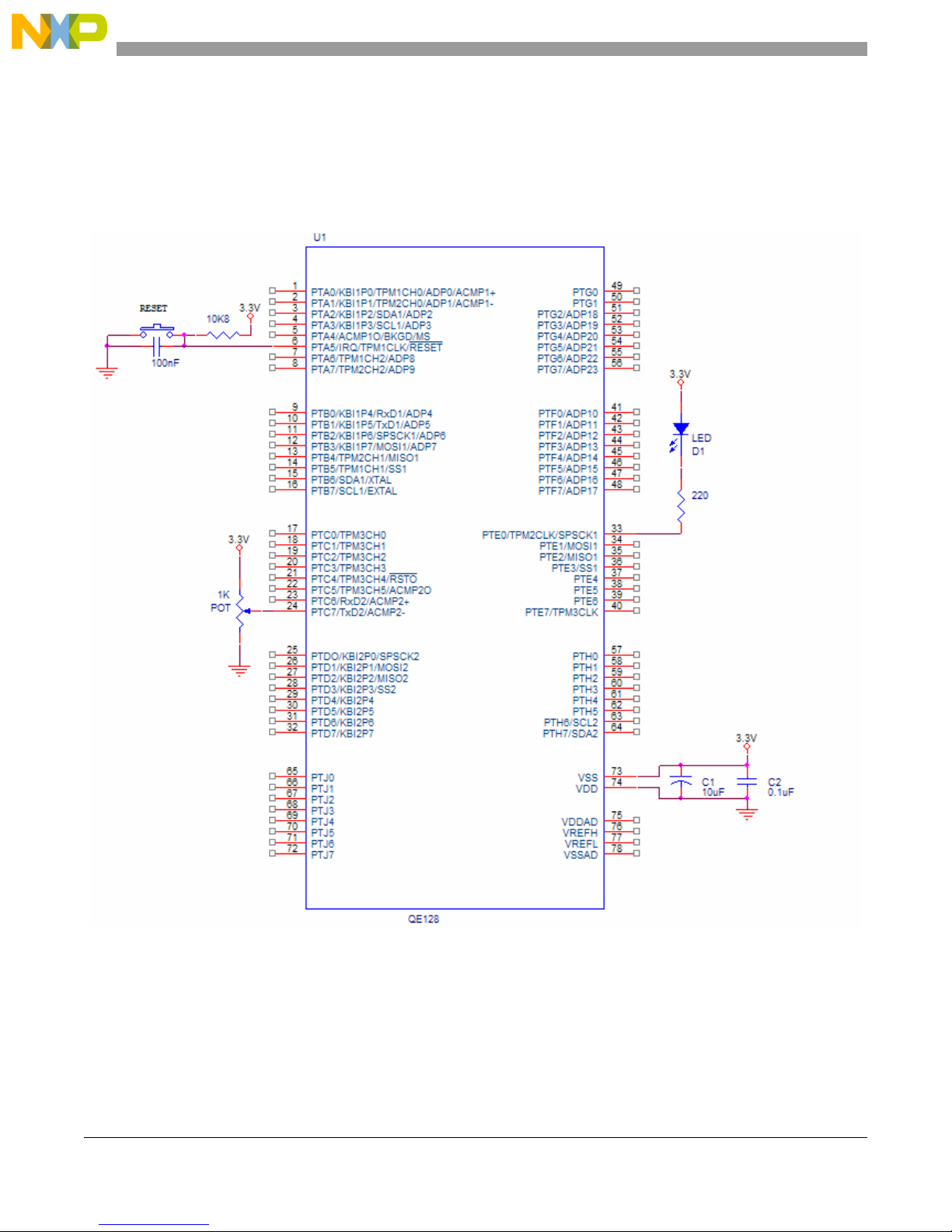

The MCF51QE128, MCF51QE96, MCF51QE64 are members of the low-cost, low-power, high

performance ColdFire® V1 core (version 1) family of 32-bit MCUs. Figure 2-1 shows the ColdFire V1

core platform block diagram.

The ColdFire V1 core features are:

• Implements Instruction Set Revision C (ISA_C).

• Supports up to 30 peripheral interrupts and seven software interrupts.

• Built upon lowest-cost ColdFire V2 core microarchitecture.

• Two independent decoupled 2-stage pipelines.

• Debug architecture remapped into S08's single-pin BDM interface.

QE128 Quick Reference User Guide, Rev. 1.0

Freescale Semiconductor 2-1

Page 10

QE MCUs 8-bit and 32-bit Comparison

IA Generation

Instruction

Fetch Cycle

FIFO

Instruction

Buffer

Decode & Select,

Operand Fetch

Address

Generation,

Execute

IFP

OEP

IAG

IC

IB

DSOC

AGEX

BDC/Debug

Flash Array

SRAM Array

Local

Controller

RGPIO

Controller

RGPIO

Pins

BKGD

Bus

Platform

V1 ColdFire

core

On-Platform Bus

Flash

Controller

RAM

Controller

Peripheral

Bridge

Write Data

Read Data

Address,

Attributes

Peripheral Bus

Off-Platform

Off-Platform

Figure 2-1. ColdFire V1 Core Platform Block Diagram

2-2 Freescale Semiconductor

QE128 Quick Reference User Guide, Rev. 1.0

Page 11

QE MCUs 8-bit and 32-bit Comparison

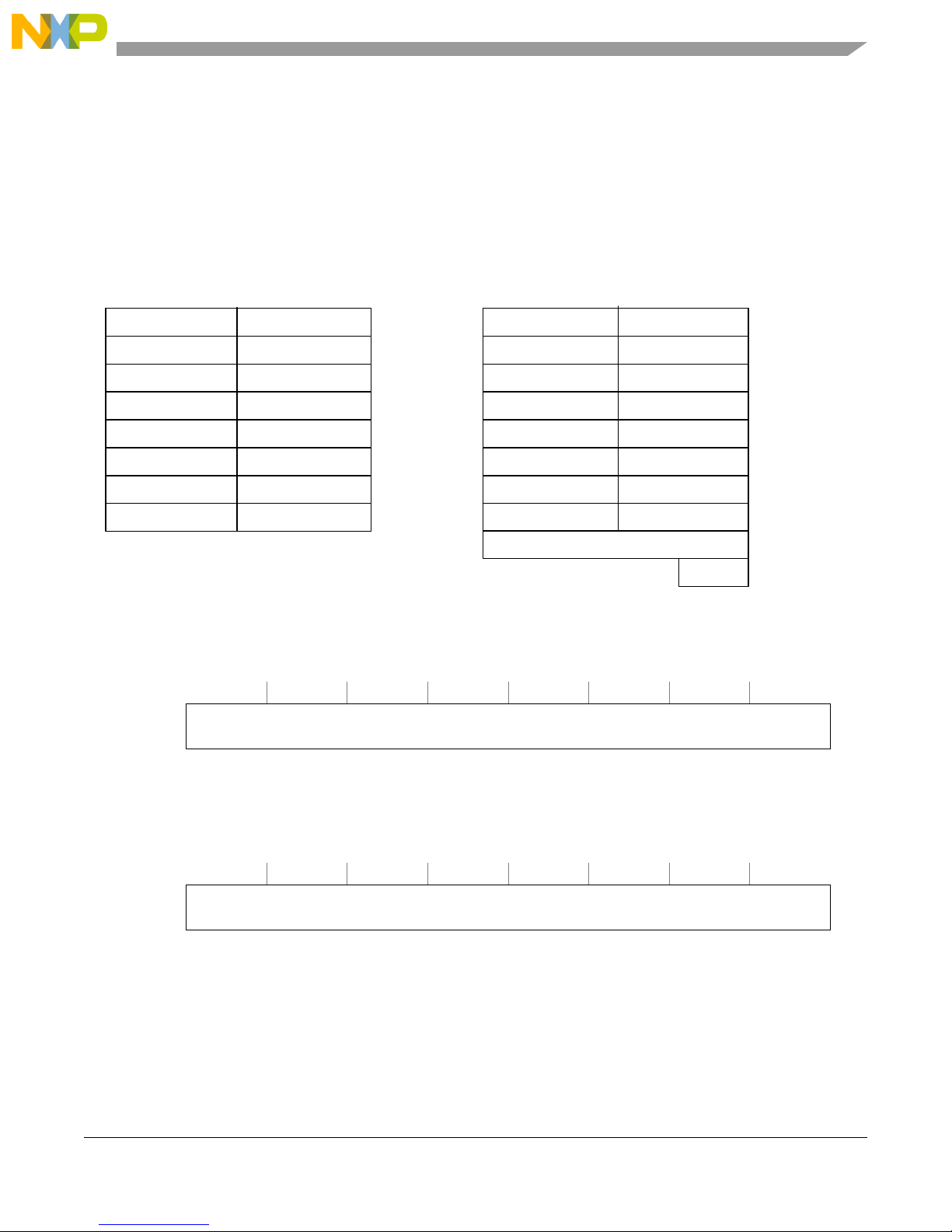

0

Data Registers

3

5D7

31 0

0

Address Register s

3

5A7

310 S

C

CC

The ColdFire V1 core has two programming models, the user and supervisor. First, is the user

programming model which is the same as the M68000 family microprocessors and consists of the

following registers:

• 16 general-purpose 32-bit registers (D0-D7, A0-A7)

• 32-bit program counter (PC)

• 8-bit condition code register (CCR)

D

A

D1

D2

D

D4

D

A1

A2

A

A4

A

P

P

R

Figure 2-2. User Programming Model Registers

Data registers (D0-D7) -- These registers are used for bit, byte, word or longword operations. It can also

be used as index registers for effective address (<ea>) calculations.

313029282726252423222120191817161514131211109876543210

R

W

Figure 2-3. Data Registers (D0–D7)

Data

Address registers (A0-A6) -- These registers can be used as software stack pointers, index registers or

based address registers. They can also be used as data operation

storage,word and longword operations.

313029282726252423222120191817161514131211109876543210

R

W

A7 -- Is a user stack pointer and is treated specifically by CPU.

Program counter (PC) -- This register contains the address of the currently executing instruction. The

PC increments its value or can be loaded with a new one when an instruction

is executing or when an exception occurs.

Freescale Semiconductor 2-3

Address

Figure 2-4. Address Registers (A0–A6)

QE128 Quick Reference User Guide, Rev. 1.0

Page 12

QE MCUs 8-bit and 32-bit Comparison

313029282726252423222120191817161514131211109876543210

R

W

Address

Figure 2-5. Program Counter Register (PC)

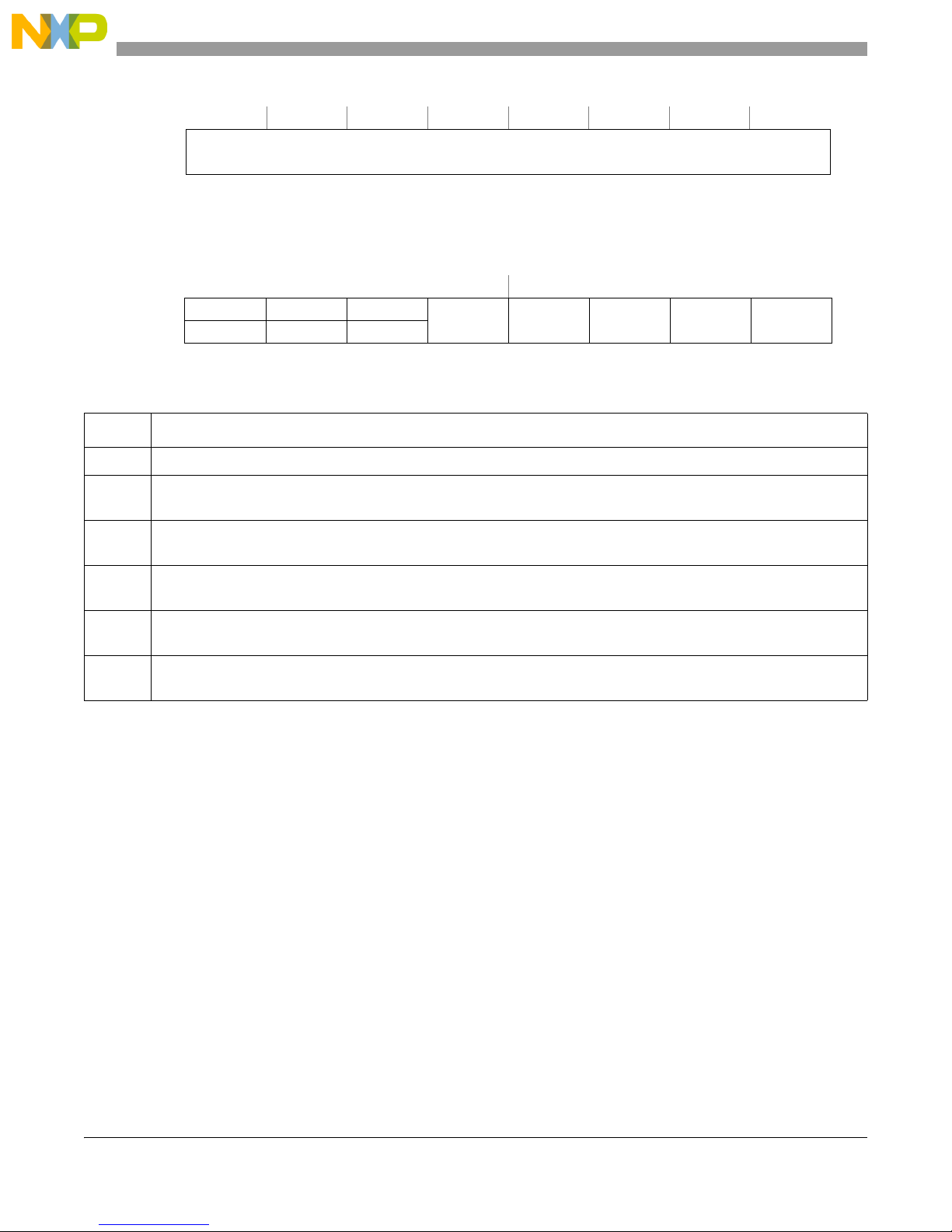

Condition code register (CCR) -- This register reflects the result of most instruction flags. It is used to

evaluate the instructions of the conditional branches.

76543210

R000

W

Figure 2-6. Condition Code Register (CCR)

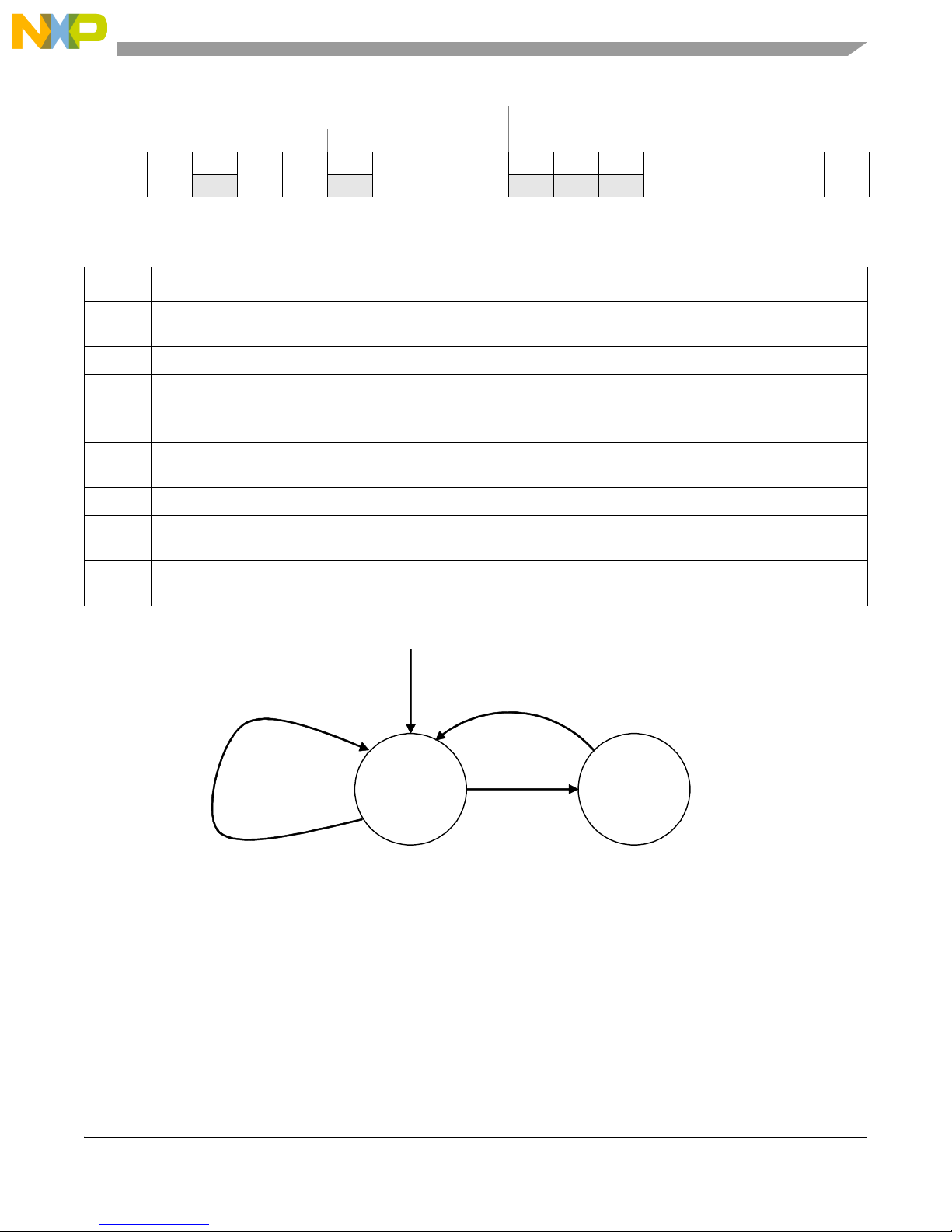

Table 2-1. CCR Field Descriptions

Field Description

7–5 Reserved, must be cleared.

4

Extend condition code bit. Set to the C-bit value for arithmetic operations; otherwise not affected or set to a specified

X

result.

XNZVC

3

Negative condition code bit. Set if most significant bit of the result is set; otherwise cleared.

N

2

Zero condition code bit. Set if result equals zero; otherwise cleared.

Z

1

Overflow condition code bit. Set if an arithmetic overflow occurs implying the result cannot be represented in operand

V

size; otherwise cleared.

0

Carry condition code bit. Set if a carry out of the operand msb occurs for an addition, or if a borrow occurs in a

C

subtraction; otherwise cleared.

Second, is the supervisor programming model. This is intended to be used only by system control software

to implement restricted operating system functions: I/O control, and memory management. In the

supervisor programming model all registers and features of the ColdFire processors can be accessed and

modified. This consists of registers available in user mode and the following control registers:

• 16-bit status register (SR).

• 32-bit supervisor stack pointer (SSP).

• 32-bit vector base register (VBR).

• 32-bit CPU configuration register (CPUCR).

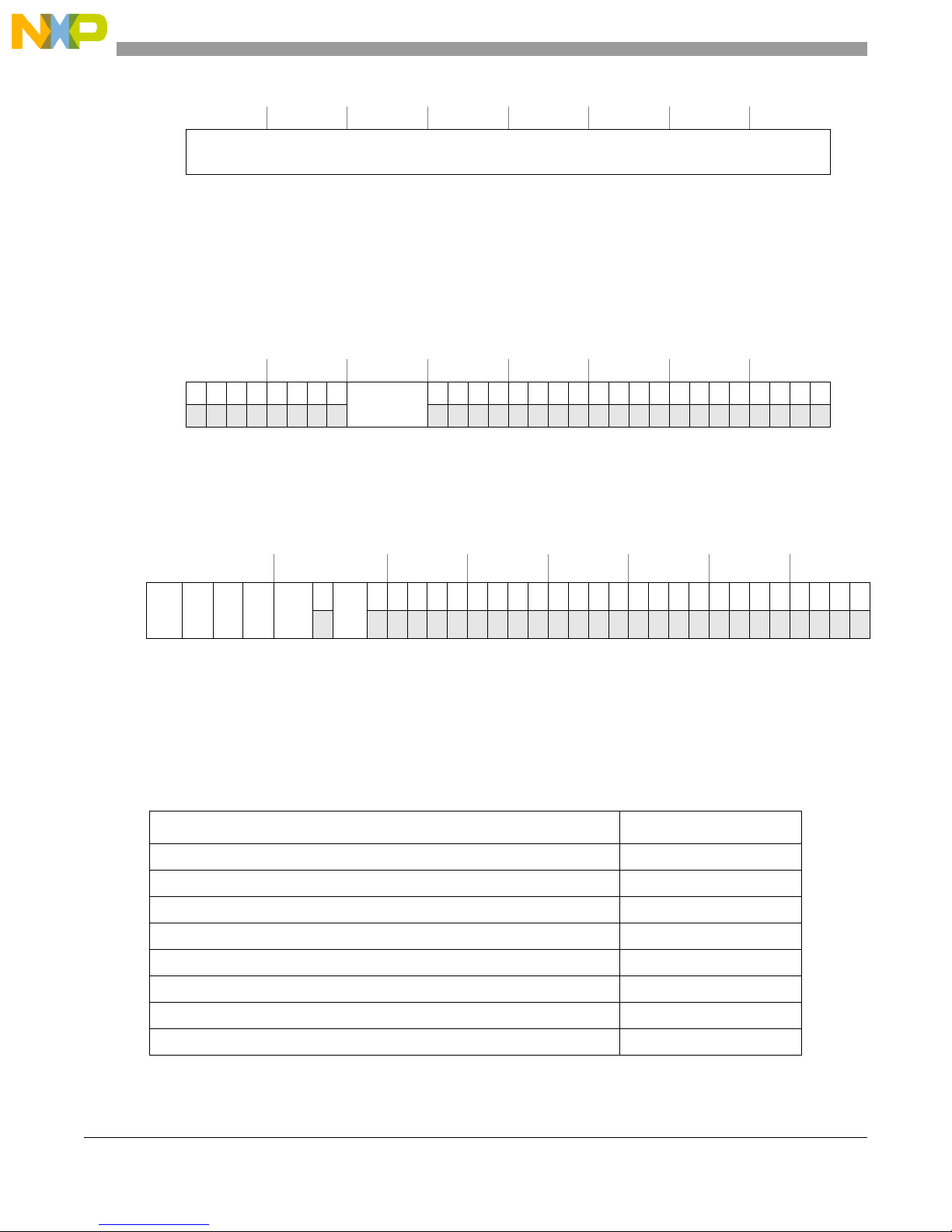

Status register (SR) — This is a 16-bit register. It stores the processor status and includes the condition

code register (CCR). When it is used in user mode only the lower 8-bit can

be accessed. When used in supervisor mode the registers can be accessed.

If a supervisor instruction is executed in user mode it generates a privilege

violation exception. Figure 2-8 shows the SR behavior in a state machine.

2-4 Freescale Semiconductor

QE128 Quick Reference User Guide, Rev. 1.0

Page 13

System Byte Condition Code Register (CCR)

SR[S] = 1

SR[S] = 0

Reset

Supervisor

Mode

User Mode

Exception

Rte, move-t o- sr with

sr_operand[13] = 1

Rte, move-t o- sr with

sr_operand[13] = 0

1514131211109876543210

000

W

R

0

T

S M

0

I

Figure 2-7. Status Register (SR)

Table 2-2. SR Field Descriptions

Field Description

QE MCUs 8-bit and 32-bit Comparison

X N ZVC

15

Trace enable. When set, the processor performs a trace exception after every instruction.

T

14 Reserved, must be cleared.

13

Supervisor/user state.

S

0User mode

1 Supervisor mode

12

Master/interrupt state. Bit is cleared by an interrupt exception and software can set it during execution of the RTE or

M

move to SR instructions.

11 Reserved, must be cleared.

10–8IInterrupt level mask. Defines current interrupt level. Interrupt requests are inhibited for all priority levels less than or

7–0

CCR

equal to current level, except edge-sensitive level 7 requests, which cannot be masked.

Refer to MCF51QE128 Reference Manual.

Supervisor stack pointer (SSP) -- This ColdFire architecture supports two independent stack pointers,

A7 registers. Each operating mode has its own stack pointer, SSP and user

stack pointer (USP). The hardware implementation of these two registers do

not identify one as SSP and the other as USP . Instead, the hardware uses one

32-bit register as the active A7 and the other as, OTHER_A7.

Freescale Semiconductor 2-5

Figure 2-8. Processor Status State Machine

QE128 Quick Reference User Guide, Rev. 1.0

Page 14

QE MCUs 8-bit and 32-bit Comparison

313029282726252423222120191817161514131211109876543210

R

W

Address

Figure 2-9. Stack Pointer Registers (A7 and OTHER_A7)

Vector base register (VBR) -- This register defines the base addres s of the exception vector table in the

memory. It has two different possible values: 0x(00)00_0000 exception

vector table based on the flash, and 0x(00)80_0000 exception vector table

based on the RAM. At reset the VBR is cleared. The VBR is located at the

base of the exception table at the address 0x(00)00_0000 in the flash.

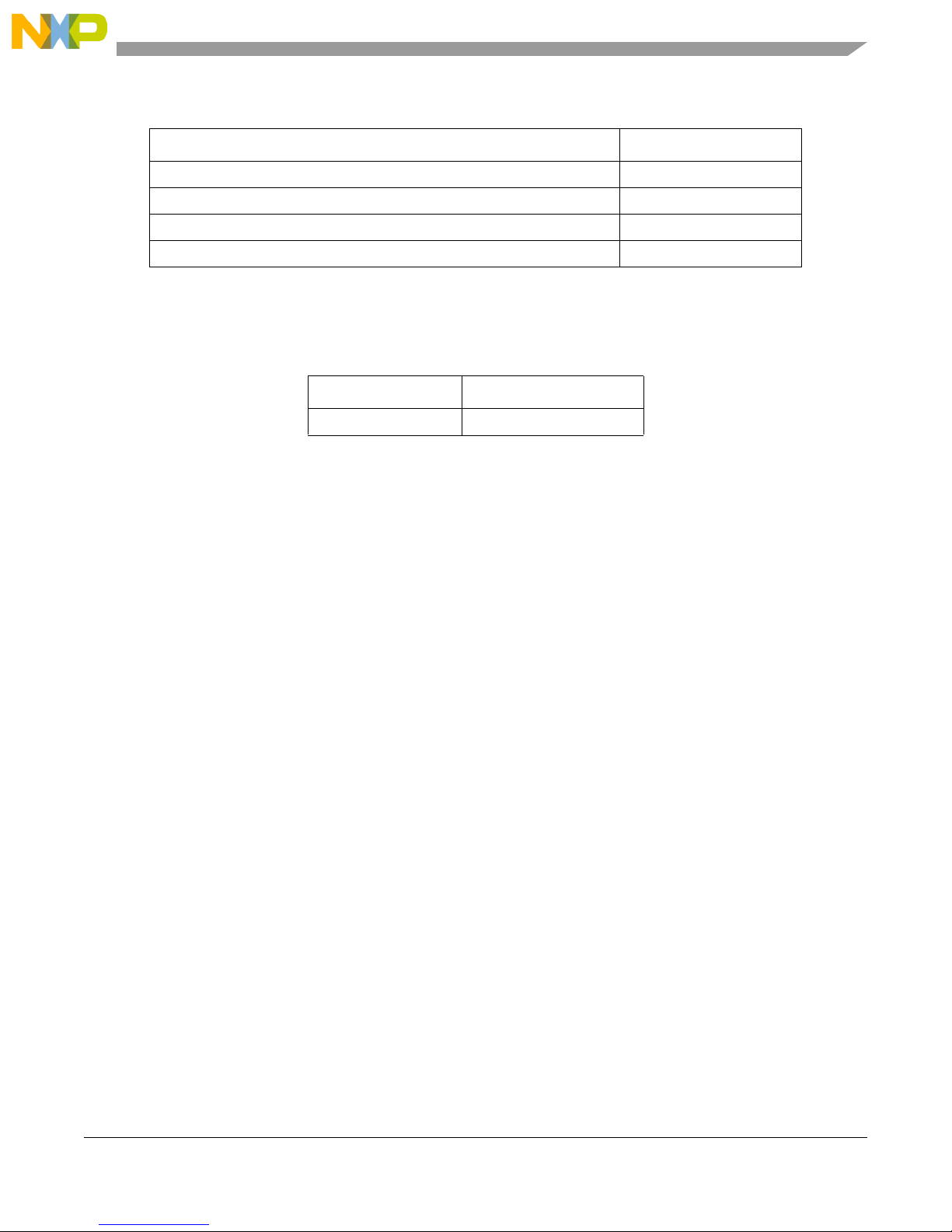

313029282726252423222120191817161514131211109876543210

R 0 0 0 0 0 000

W

Base

Address

0 0 0 0 0 000000000 000 0 00

Figure 2-10. Vector Base Register (VBR)

CPU configuration register (CPUCR) -- With this register you can configure some cores into supervisor

mode. Certain hardware features can be enabled or disabled based on the

state of the CPUCR.

31 30 29 28 27 26252423222120191817161514131211109876543210

R

ARD IRD IAE IME BWD0FSD

W

0000000 0 0 0 000000000 000 0 00

Figure 2-11. CPU Configuration Register

2.2.1.1 Addressing Modes

The ColdFire V1 core counts with 12 different addressing modes. The addressing modes and syntax are

shown in Table 2-3:

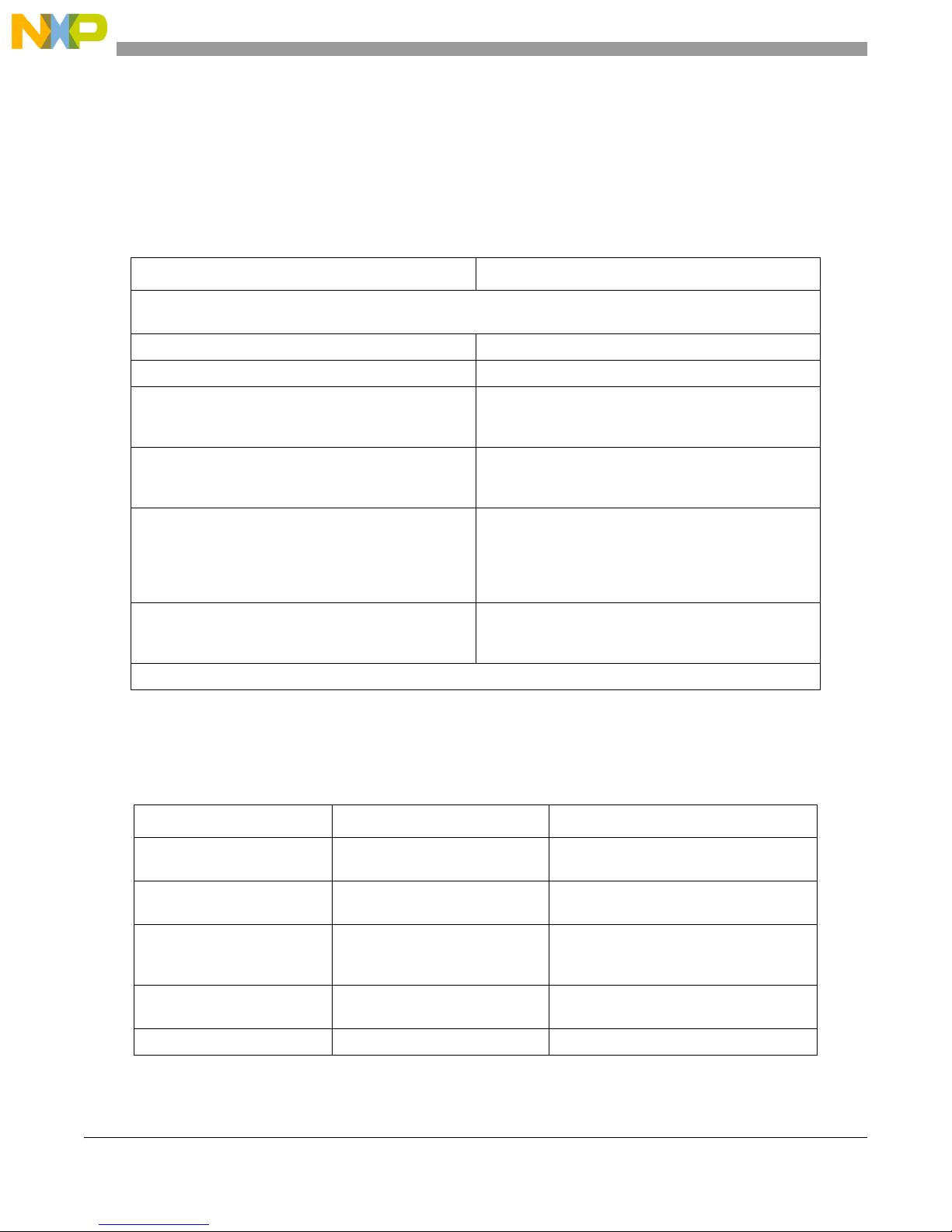

Table 2-3. Addressing Modes and Syntax

Addressing modes Syntax

Register Direct. op.sz

Address Register Indirect. op.sz (Ax),Rx

Address Register Indirect with Post-increment. op.sz (Ax)+,Rx

Address Register Indirect Pre-decrement. op.sz -(Ay),Rx

Address Register Indirect with Displacement. op.sz d16(Ay),Rx

Address Register Indirect with Scaled Index and Displacement. op.sz d8(Ay,Xi*SF),Rx

Program Counter Indirect with Displacement. op.sz d16(PC),Rx

1

Ry,Rx

Program Counter Indirect with Scaled Index and Displacement. op.sz d8(PC,Xi*SF),Rx)

2-6 Freescale Semiconductor

QE128 Quick Reference User Guide, Rev. 1.0

Page 15

QE MCUs 8-bit and 32-bit Comparison

Table 2-3. Addressing Modes and Syntax

Addressing modes Syntax

Absolute Short Addressing. op.sz xxx.w,Rx

Absolute Long Addressing. op.sz xxx.{l},Rx

Immediate Byte, Word. op.{b,w}2 #imm,Rx

3

Immediate Long. op.l#imm

1

op.sz - operand size(size is 1 for byte, 2 for word, 4 for long).

2

op.{b,w} - operand {byte,word}.

3

op.l - operand long.

,Rx

This is a syntax for a V1 core example:

Source Destination

#0x55 Rx

2.2.1.2 Exception Processing

Exception processing is defined as processor-detected conditions that force an instruction stream

discontinuity because of a program or system error: a system call, a debug, or an I/O interrupt. The

ColdFire V1 core uses a reduced version of the interrupt controller from other ColdFire processors. This

hardware implementation is available only for a 32-bit MCU.

Freescale Semiconductor 2-7

QE128 Quick Reference User Guide, Rev. 1.0

Page 16

QE MCUs 8-bit and 32-bit Comparison

Saves a copy of the SR.

Forces:

SR[S]=1

SR[T]=0

If an interrupt forces

the interrupt

SR[M]=0

then sets

SR[I]=to the level of

Calculates the vector for

all internal exceptions.

For interrupts, the CPU

uses the vector number

supplied by the interrupt

controller or performs an

interrupt acknowledge

(IACK) cycle to retrieve

the I/O vector number.

Init

Saves the content at the

time of the exception by

storing a 64-bit

exception stack frame

(including the saved SR)

on the top of the

supervisor stack.

The processor fetches a

32-bit vector address

from the exception

vector table @ (VBR +

vector_number x 4). The

address defines the first

instruction of the

exception handler or

interrupts service routine

(ISR). Control is then

passed to the exception

handler at this address.

1

End

1

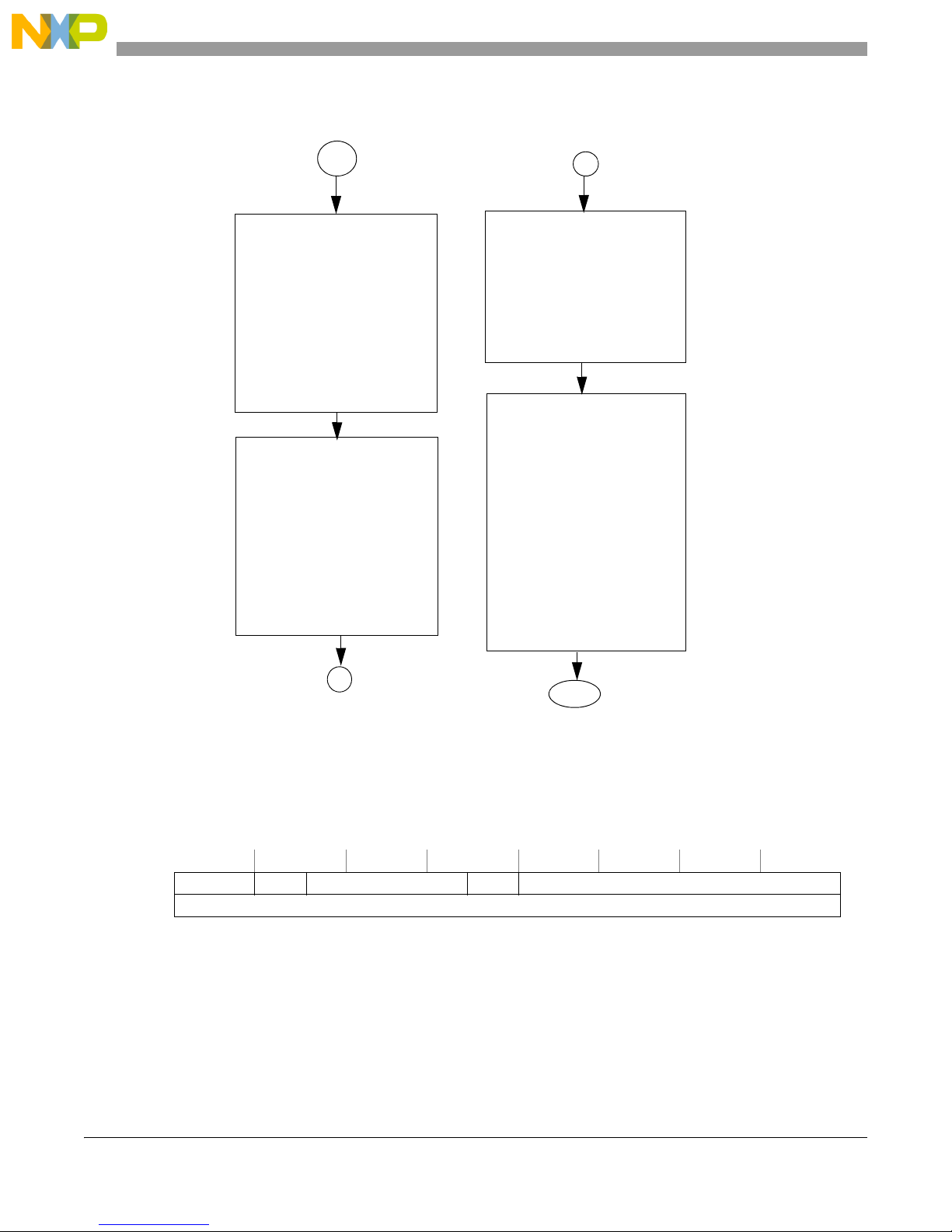

The processor performs the following operations to process an exception:

Interrupts are treated as lowest-priority exception type. CPU samples for halts and interrupts once per

instruction. The first instruction in ISR does not sample. Interrupts are guaranteed to be recoverable

exceptions.

313029282726252423222120191817161514131211109876543210

Format FS[3:2] Vector FS[1:0] Status Register

Figure 2-12. Processor Operations Process

Figure 2-13. Exception Stack Frame Form

ColdFire architecture reserves 64 entries for processor exceptions and the remaining 192 entries for I/O

interrupts. The ColdFire V1 core architecture only uses a relatively small number of the I/O interrupt

vector. Table 2-4 shows the ColdFire V1 core processor with the exception of the vector table.

QE128 Quick Reference User Guide, Rev. 1.0

Program Counter

2-8 Freescale Semiconductor

Page 17

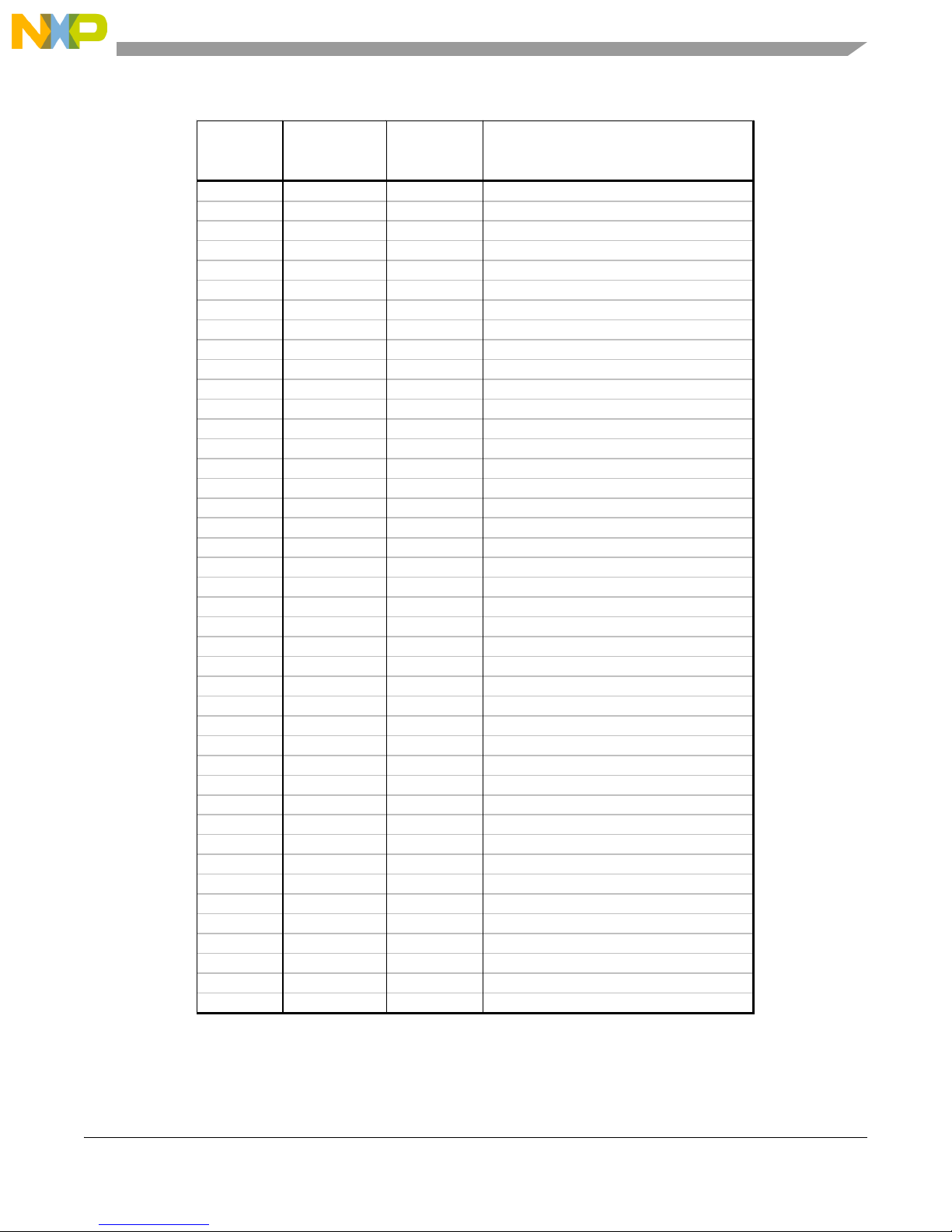

Table 2 -4. Ve cto r Ta b l e

Vector

Number(s)

Vector

Offset(Hex)

Stacked

Program

Counter

Assignment

0 0x000 - Initial supervisor stack pointer

1 0x004 - Initial program counter

2-63 0x008-0x0FC - Reserved for internal CPU Ex ceptions

64 0x100 Next IRQ_pin

65 0x104 Next Low_voltage

66 0x108 Next TPM1_ch0

67 0x10C Next TPM1_ch1

68 0x110 Next TPM1_ch2

69 0x114 Next TPM1_ovfl

70 0x118 Next TPM2_ch0

71 0x11C Next TPM2_ch1

72 0x120 Next TPM2_ch2

73 0x124 Next TPM2_ovfl

74 0x128 Next SPI2

75 0x12C Next SPI1

76 0x130 Next SCI1_err

77 0x134 Next SCI1_rx

78 0x138 Next SCI1_tx

79 0x13C Next IICx

80 0x140 Next KBIx

81 0x144 Next ADC

82 0x148 Next ACMPx

83 0x14C Next SCI2_err

84 0x150 Next SCI2_rx

85 0x154 Next SCI2_tx

86 0x158 Next RTC

87 0x15C Next TPM3_ch0

88 0x160 Next TPM3_ch1

89 0x164 Next TPM3_ch2

90 0x168 Next TPM3_ch3

91 0x16C Next TPM3_ch4

92 0x170 Next TPM3_ch5

93 0x174 Next TPM3_ovfl

94-95 0x178-0x17C - Reserved; unused for V1

96 0x180 Next Level 7 Software Interrupt

97 0x184 Next Level 6 Software Interrupt

98 0x188 Next Level 5 Software Interrupt

99 0x18C Next Level 4 Software Interrupt

100 0x190 Next Level 3 Software Interrupt

101 0x194 Next Level 2 Software Interrupt

102 0x198 Next Level 1 Software Interrupt

103-255 0x 19C-0x3FC - Reserved; unused for V1

QE MCUs 8-bit and 32-bit Comparison

Freescale Semiconductor 2-9

QE128 Quick Reference User Guide, Rev. 1.0

Page 18

QE MCUs 8-bit and 32-bit Comparison

2.2.2 QE S08 core

This section provides summary information about the registers, addressing modes and core features. The

generated source and object-code is compatible with the M68HC08 CPU.

The S08 MCU supports only the user programming model. Figure 2-14 shows five CPU registers. These

registers are not part of the memory map.

Figure 2-14. CPU Registers

Accumulator -- The accumulator is a general-purpose 8-bit register . One operand input to the arithmetic

logic unit (ALU) is connected to the accumulator and the ALU results are

often stored in the accumulator after arithmetic and logical operations.

Index Register (H:X) -- This is a two separate 8-bit register, which often works together as a 16-bit

address pointer where H holds the upper byte of an address and X the lower

byte. All the indexing addressing mode instructions use the 16-bit register.

Stack pointer (SP) -- This 16-bit address pointer register points to the next available location on the

automatic last-in-first-out (LIFO). The stack is used to automatically store

the return address from subroutine calls or return from interrupts. It stores

the context in the interrupt service routine (ISR) and it stores the local

variables and parameters in function calls.

Program counter (PC) -- This register contains the next instruction or operand to be retrieved. This

register automatically increments to the next memory location during a

normal program execution.

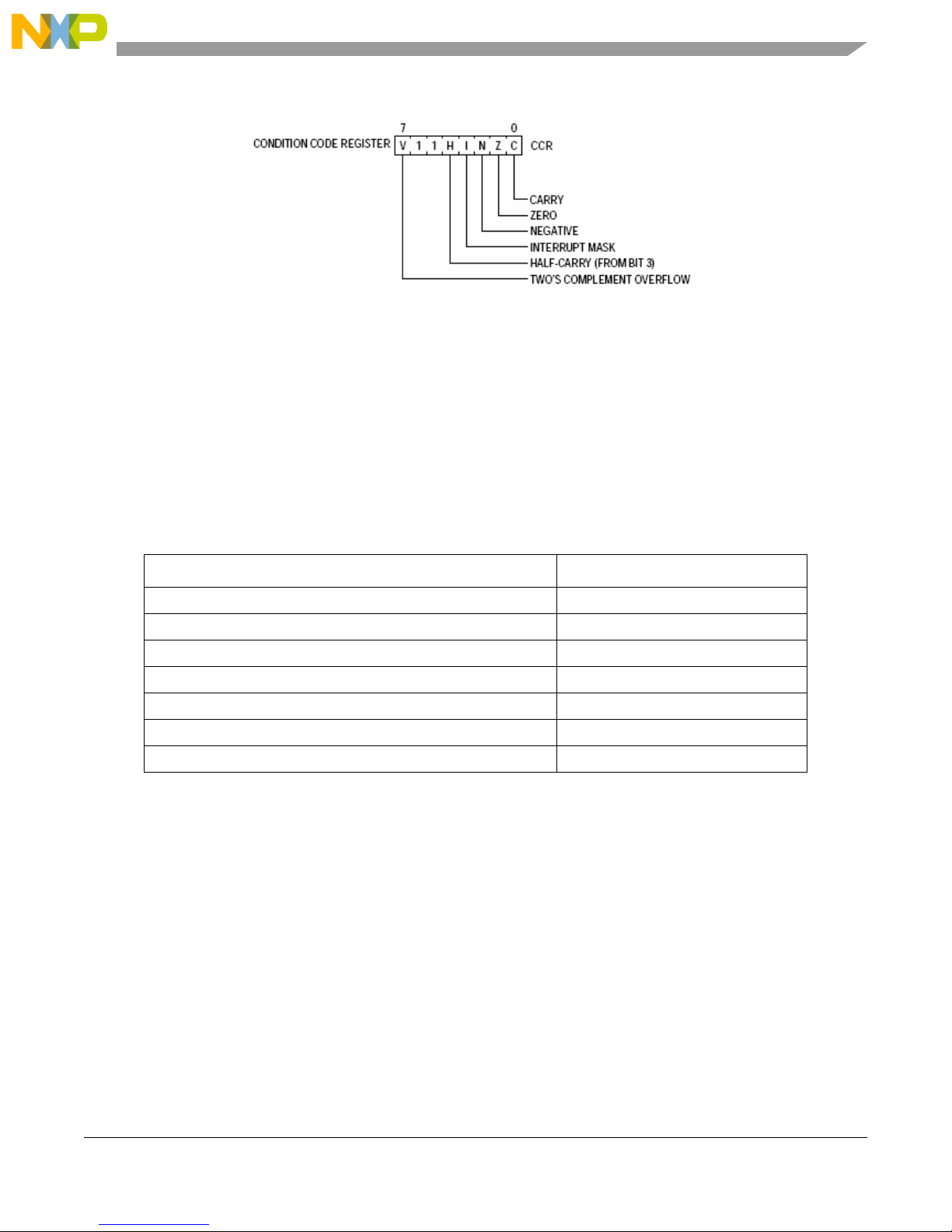

Condition code register (CCR) -- This 8-bit condition code register contains the interrupt mask (I) and

five flags that indicate the results of the instruction just executed. Bits 5 and

6 are permanently set to 1.

2-10 Freescale Semiconductor

QE128 Quick Reference User Guide, Rev. 1.0

Page 19

QE MCUs 8-bit and 32-bit Comparison

Figure 2-15. Condition Code Register

V - Two's complement Overflow Flag N - Negative flag

H - Half Carry Flag Z - Zero Flag

I - Interrupt Mask Bit C - Carry/Borrow flag

2.2.2.1 Addressing Modes

Addressing modes define the way the CPU accesses operand and data. The S08 core supports seven

different addressing modes:

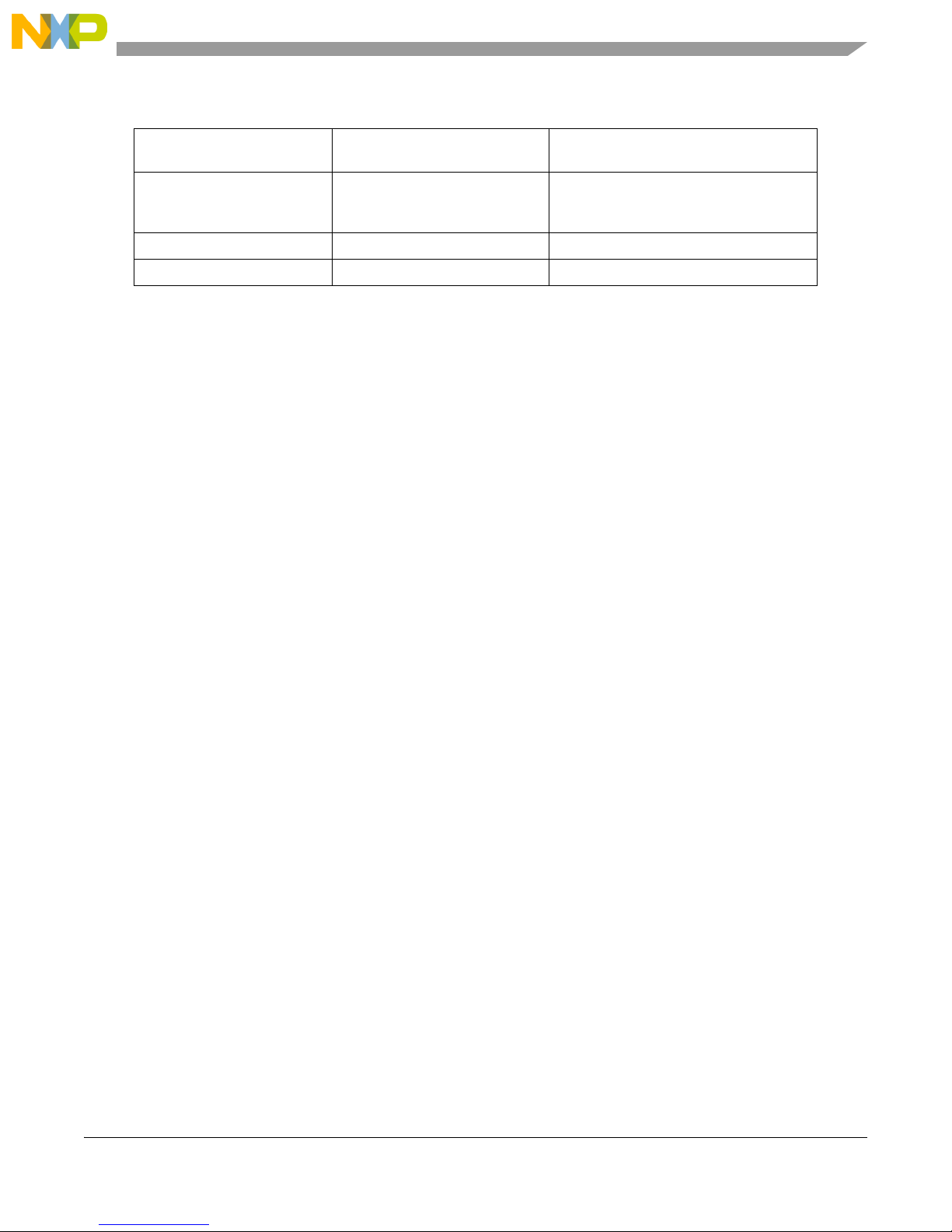

Table 2-5. Addressing Modes and Examples

Addressing Modes Example

Inherent --Operands in internal registers. ASLA – Arithmetic Shift Left A.

Relative -- 8-bit offset to branch destination. BEQ rel – Branch if equal

Immediate -- Operand in next object code byte. ADC #opr8i – Add with carry

Direct -- Operand in memory at 0x0000-0x00FF. ADC opr8a – Add with carry

Extended -- Operand within 64 Kbyte address space. ADC opr16a – Add with carry

Indexed relative to H:X. ADC oprx8,X – Add with carry

Indexed relative to SP. ADC oprx8,SP – Add with carry

n -- Any label or expression that evaluates to a single integer in the range 0-7

opr8i -- Any label or expression that evaluates to an 8-bit immediate value

opr16i -- Any label or expression that evaluates to a 16-bit immediate value

opr8a -- Any label or expression that evaluates to an 8-bit value

opr16a -- Any label or expression that evaluates to a 16-bit value

oprx8 -- Any label or expression that evaluates to an unsigned 8-bit value, used for indexed addressing

oprx16 -- Any label or expression that evaluates to a 16-bit value

page -- Any label or expression that evaluates to a valid bank number for PPAGE register. Any value

between 0 and 7 is valid.

rel -- Any label or expression that refers to an address that is within -128 to +127 locations from the next

address after the last byte of object code for the current instruction.

A -- Accumulator

Freescale Semiconductor 2-11

QE128 Quick Reference User Guide, Rev. 1.0

Page 20

QE MCUs 8-bit and 32-bit Comparison

Store PCL in SP

Store X in SP

Store PCH in SP

Store A in SP

Store PCL in SP

Store CCR in SP

Sets the | bit in the CCR

Fetches the high-order

half of the interrupt

vector

Fetches the low-order

half of the interrupt

vector

Delays for one free bus

cycle

Init

1

Fetches three bytes of

program information

starting at the address

indicated by the interrupt

vector

Fills the instruction

queue, preparing for

execution of the first

instruction in the

interrupt service routine

1

2

2

End

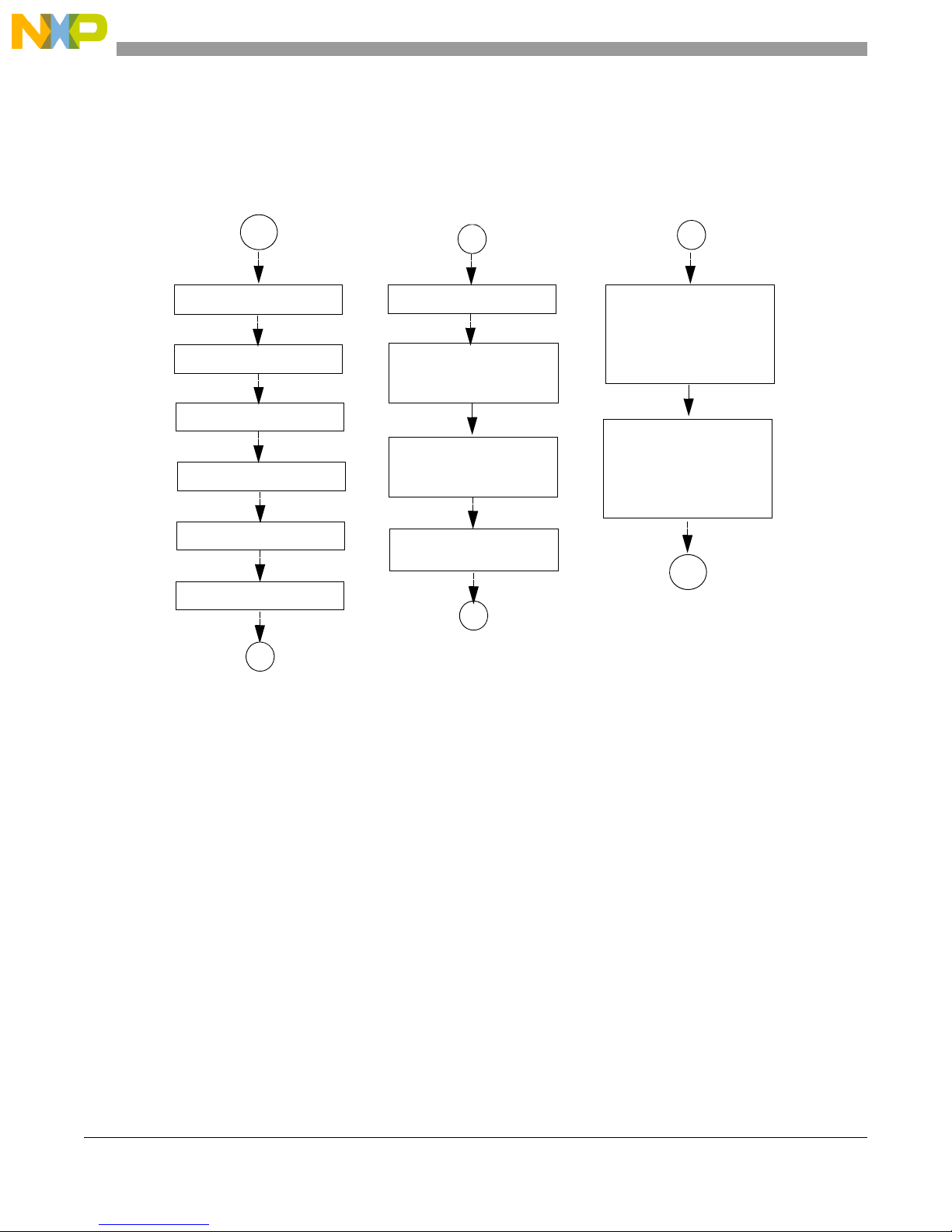

2.2.2.2 Interrupt Sequence

The S08 core interrupt sequence first completes the current instruction then attends the requested interrupt.

The CPU responds to an interrupt with the same sequence operation as in a software interrupt (SWI), and

it differs from the address used for the vector retrieved.

Figure 2-16. The CPU Interrupt Sequence

2.2.3 ColdFire V1 or 9S08QE

The ColdFire V1 and S08 cores have significant differences, even though the 32 bit ColdFire V1 core

presents improvements in performance. These differences are highlighted in the following section.

The ColdFire V1 architecture features, staged pipelining allows the core to process multiple instructions

at the same time.

2-12 Freescale Semiconductor

QE128 Quick Reference User Guide, Rev. 1.0

Page 21

QE MCUs 8-bit and 32-bit Comparison

Figure 2-17. V1 Core Pipelines

• The V1 Coldfire core pipeline stages include the following:

— Two-stage instruction fetch pipeline (IPF) (plus instruction buffer stage)

— Instruction address generation (IAG) – Calculates the next prefetch address

— Instruction fetch cycle (IC) – Initiates prefetch on the processor’s local bus

— Instruction buffer (IB) – Buffer stage minimizes effects of fetch latency using fifo queue

• Two-stage operand execution pipeline (OEP)

— Decode and select/operand fetch cycle (DSOC) – Decodes instruction and fetches the required

components for effective address calculation, or the operand fetch cycle

— Address generation/execute cycle (AGEX) – Calculates operand address or executes the

instruction

ColdFire V1 core architecture -- Is an orthogonal architecture that has an advantage. It has 16 different

registers for operation that can be used instead of one. The ColdFire V1 core

processes more effectively the 32-bit length operations than the 8-bit core

version.

S08 core architecture -- Is accumulator based, almost all arithmetic and logical instructions use the

accumulator. The S08 can handle 32-bit length operations but requires more

cycles because it executes more instructions, taking more time.

The ColdFire MCU has two programming models with different privileges to control the system. These

programming models are similar to the administrator and user in windows. When the MCU is on the

Freescale Semiconductor 2-13

QE128 Quick Reference User Guide, Rev. 1.0

Page 22

QE MCUs 8-bit and 32-bit Comparison

administrator level it can access all the registers and change values. The 8-bit core version does not count

with this feature.

Table 2-6 shows a global view of the core differences. Detailed information is explained in the beginning

of this chapter. Refer to review Reference Manual MCF51QE128 and MC9S08QE128 at the

www.freescale.com site.

Table 2-6. Comparison of Cores

MC9S08QE128 MCF51QE128

Up to 50 MHz CPU from 3.6 V 2.1 V, and 20 MHz CPU from 2.1 V to 1.8 V across temperature ranged of -40°C

to 85°C.

8-bit HCS08 core. 32-bit ColdFire V1 core.

8-bit data bus, 16-bit address bus. 32-bit data bus, 24-bit address bus.

64 Kb memory map, 16 Kb paging window for

addressing memory beyond 64 Kb. Linear address

pointer for accessing data across entire memory range.

HC08 instruction set with added BGND, CALL and RTC

instructions.

Support for up to 32 interrupt/reset exceptions.

Exception priorities are fixed. One level of interrupt

grouping. No hardware support for nesting.

16 Mb memory map, entire memory map addressed

directly.

ColdFire Instruction Set Revision C (ISA_C), and

additional instructions for efficient handling of 8-bit and

16-bit data.

Support for up to 256 interrupt/reset exceptions (39 are

used on MCF51QE128). Exception priorities are fixed

except for two interrupts that can be remapped. Seven

levels of interrupt grouping and hardware support for

nesting.

Resets: one vector for all reset sources. Vector must

point to address within pages 0-3. No illegal address

reset. Entire memory map is legal.

System reset status (SRS) registers set flags for most recent reset source.

Resets: vectors for up to 64 reset sources. Vector can

point to any valid address. Illegal address reset is

supported.

2.2.3.1 Exception Comparison

Table 2-7 shows the exception differences between 8-bit core and 32-bit core.

Table 2-7. Exception Differences

Attribute S08 V1 ColdFire

Exception Vector Table. 32, 2-byte entries, fixed location at

upper end of memory.

More on Vectors. 2 for CPU + 30 for IRQs (interrupt

requests), reset at upper address.

Exception Stack Frame. 5-byte frame: CCR, A, X, PC. 8-byte frame: F/V, SR, PC;

Interrupt Levels. 1 = f(CCR[I]). 7 = f(SR[I]) with automatic hardware

Non-Maskable IRQ Support. No Yes with level 7 interrupts.

103, 4-byte entries, located at lower end of

memory at reset, relocatable with the VBR.

64 for CPU + 39 for IRQs, reset at lowest

address.

General-purpose registers (An, Dn) must

be saved/restored by the ISR.

support for nesting.

2-14 Freescale Semiconductor

QE128 Quick Reference User Guide, Rev. 1.0

Page 23

QE MCUs 8-bit and 32-bit Comparison

Table 2-7. Exception Differences

Core-enforced IRQ Sensitivity. No Level 7 is edge sensitive, and others level

sensitive.

INTC (interrupt controller)

Vectoring.

Software IACK. No Yes

Exit Instruction from ISR. RTI (real time interrupt). RTE (real time exception).

Fixed priorities and vector

assignments.

Fixed priorities and vector assignments,

plus any 2 IRQs can be remapped as the

highest priority level 6 requests.

2.2.3.2 Code Example Comparison

This example is a code made in C and is compiled and executed for both MCUs,V1 and S08. Both results

present a difference in execution time. The generated assembly lines are similar.

There are two four loop cycles that nest within this endless loop.The inner loop cycle counts from 0 to 100

and stores the k variable value in the buffer k array. The outer loop counts from 0 to 60000. The i variable

counter increments every time the k variable counter reaches the 101 value.

void main(void) {

unsigned int i,k;

unsigned int buffer[100];

SOPT1 = 0x23; // Watchdog disable. Stop Mode Enable. Background Pin

// enable. RESET pin enable

for(;;) {

for (i=0; i<=60000; i++) { // This rutine is executed 60001

for (k=0; k<=100; k++) {

buffer[k] = k;

}

}

} // loop forever

// please make sure that you never leave main

}

Assembly code lines generated for the S08 MCU; observe the difference between this assembly code and

the assembly code generated from the ColdFire V1 core.

10: SOPT1 = 0x23; // Watchdog disable. Stop Mode Enable. Background Pin enable. RESET pin

enable

0004 a623 [2] LDA #35

0006 c70000 [4] STA _SOPT1

0009 L9:

11: for(;;) {

12:

13: for (i=0; i<=60000; i++) {

0009 95 [2] TSX

000a 6f03 [5] CLR 3,X

000c 6f02 [5] CLR 2,X

000e LE:

14: for (k=0; k<=100; k++) {

000e 95 [2] TSX

000f 6f01 [5] CLR 1,X

Freescale Semiconductor 2-15

QE128 Quick Reference User Guide, Rev. 1.0

Page 24

QE MCUs 8-bit and 32-bit Comparison

0011 7f [4] CLR ,X

0012 L12:

15: buffer[k] = k;

0012 95 [2] TSX

0013 e601 [3] LDA 1,X

0015 48 [1] LSLA

0016 af04 [2] AIX #4

0018 87 [2] PSHA

0019 9f [1] TXA

001a 8b [2] PSHH

001b 95 [2] TSX

001c eb01 [3] ADD 1,X

001e e701 [3] STA 1,X

0020 86 [3] PULA

0021 a900 [2] ADC #0

0023 87 [2] PSHA

0024 e602 [3] LDA 2,X

0026 8a [3] PULH

0027 88 [3] PULX

0028 f7 [2] STA ,X

0029 9ee602 [4] LDA 2,SP

002c e701 [3] STA 1,X

002e 95 [2] TSX

002f 6c01 [5] INC 1,X

0031 2601 [3] BNE L34 ;abs = 0034

0033 7c [4] INC ,X

0034 L34:

0034 9efe01 [5] LDHX 1,SP

0037 650064 [3] CPHX #100

003a 23d6 [3] BLS L12 ;abs = 0012

003c 95 [2] TSX

003d 6c03 [5] INC 3,X

003f 2602 [3] BNE L43 ;abs = 0043

0041 6c02 [5] INC 2,X

0043 L43:

0043 9efe03 [5] LDHX 3,SP

0046 65ea60 [3] CPHX #-5536

0049 23c3 [3] BLS LE ;abs = 000e

16: }

17: }

18:

19: PTED = 0xFF;

004b 6eff00 [4] MOV #-1,_PTED

004e 20b9 [3] BRA L9 ;abs = 0009

20: } // loop forever

21: // please make sure that you never leave main

22: }

23:

Assembly lines generated for the MCF51QE128 MCU.

; 10: SOPT1 = 0x23; // Watchdog disable. Stop Mode Enable. Background Pin enable.

RESET pin enable

; 11: for(;;) {

; 12:

;

0x00000004 0x7023 moveq #35,d0

0x00000006 0x11C09802 move.b d0,0xffff9802

2-16 Freescale Semiconductor

QE128 Quick Reference User Guide, Rev. 1.0

Page 25

QE MCUs 8-bit and 32-bit Comparison

;

; 13: for (i=0; i<=60000; i++) {

;

0x0000000A 0x4280 clr.l d0

0x0000000C 0x6016 bra.s *+24 ; 0x00000024

;

; 14: for (k=0; k<=100; k++) {

;

0x0000000E 0x4281 clr.l d1

0x00000010 0x6008 bra.s *+10 ; 0x0000001a

;

; 15: buffer[k] = k;

;

0x00000012 0x41D7 lea (a7),a0

0x00000014 0x21811C00 move.l d1,(a0,d1.l*4)

;

; 16: }

;

0x00000018 0x5281 addq.l #1,d1

0x0000001A 0x0C8100000064 cmpi.l #100,d1 ; '...d'

0x00000020 0x63F0 bls.s *-14 ; 0x00000012

;

; 17: }

; 18:

;

0x00000022 0x5280 addq.l #1,d0

0x00000024 0x0C800000EA60 cmpi.l #60000,d0 ; '...`'

0x0000002A 0x63E2 bls.s *-28 ; 0x0000000e

;

; 19: PTED = 0xFF;

;

0x0000002C 0x103C00FF move.b #-1,d0 ; '.'

0x00000030 0x11C08008 move.b d0,0xffff8008

;

; 20: } /* loop forever */

;

0x00000034 0x60D4 bra.s *-42 ; 0x0000000a

0x00000036 0x51FC trapf

Table 2-8 shows the CPU cycles needed and the assembly lines code generated to complete the execution

of the program described above. The used compiler for this test was CW 6.0 version and no optimization

tool was used.

This example is just a particular comparison and the performance between

cores is not reflected with this example. The performance is application

dependant.

Table 2-8. Comparison of CPU Cycles and Assembly Code Lines

Assembly lines code 18 43

CPU Cycles 49,201,507 407,947,991

Freescale Semiconductor 2-17

NOTE

MCF51QE128 MC9S08QE128

QE128 Quick Reference User Guide, Rev. 1.0

Page 26

QE MCUs 8-bit and 32-bit Comparison

2.3 Features Comparison

2.3.1 On-Chip Memory Comparison

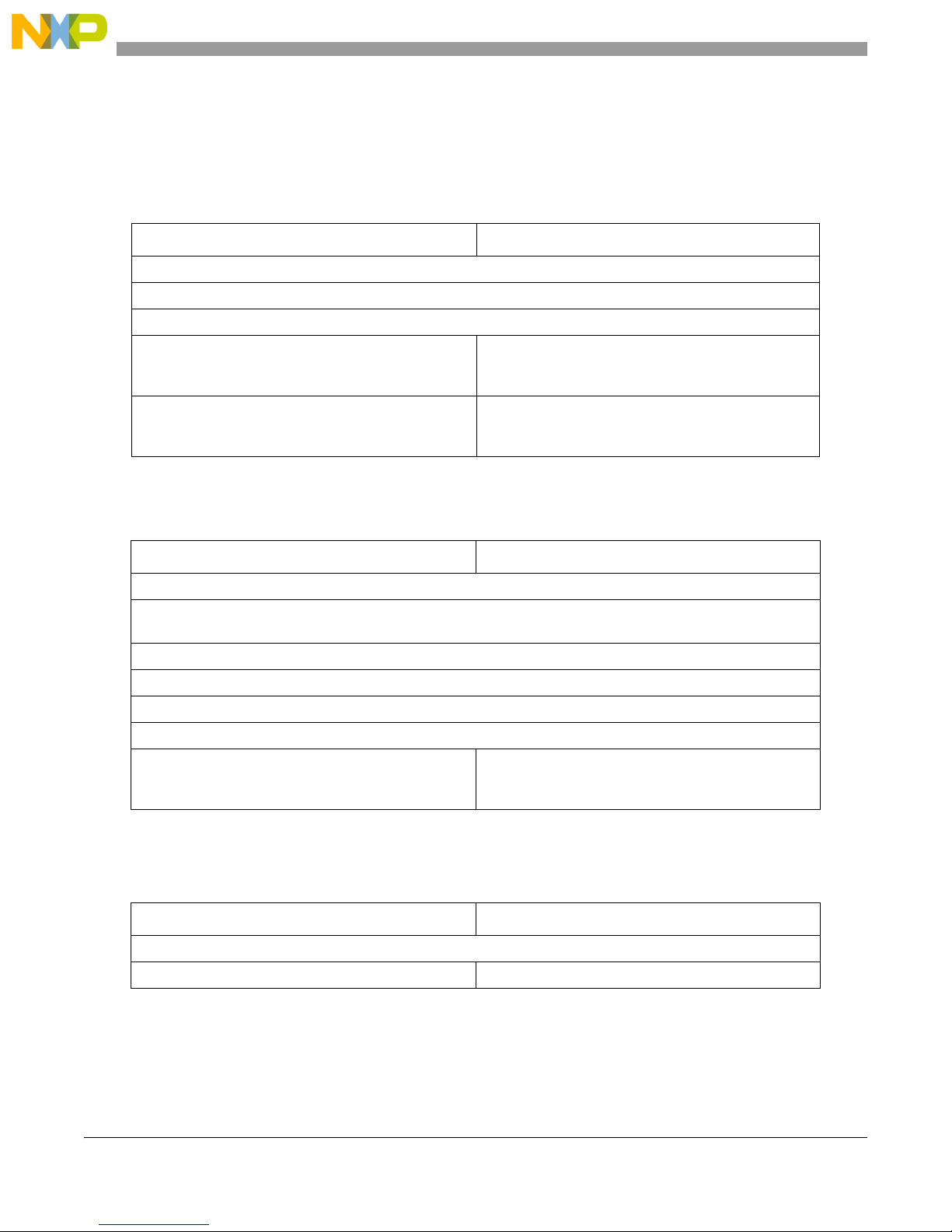

Table 2-9. On-Chip Memory Comparison

MC9S08QE128 MCF51QE128

Peripheral register maps maintain relative addresses.

Up to 8 Kb of random-access memory (RAM).

FLASH read/program/erase over full operating voltage and temperature.

Up to 128KB of FLASH, two FLASH arrays of 64Kb x

8-bits arranged in series. Two flash arrays allow for

“read while write” programming.

Security circuitry to prevent unauthorized access to

RAM and FLASH contents, default is secured when

blank

2.3.2 Power-Saving Modes and Power-Saving Features Comparison

Table 2-10. Power-Saving mode Comparison

Up to 128 KB of FLASH. Two FLASH arrays of 64 Kb x

8-bits arranged in parallel. FLASH “read while write” not

supported.

Security circuitry to prevent unauthorized access to

RAM and FLASH contents, default is unsecured when

blank

MC9S08QE128 MCF51QE128

Two very low power stop modes (Stop2 and Stop3).

Low Power run (LPRun) and wait (LPWait) modes allow for use of peripherals in reduced-current and

reduced-speed mode.

Peripheral clock enable register can disable clocks to unused modules, thereby reducing currents.

Very low power external oscillator that can be used in stop modes to provide accurate clock source RTC module.

Very low power real time counter for use in run, wait, and stop modes with internal and external clock sources.

6µs typical wake up time from stop modes.

Reduced power wait mode (enabled by WAIT

instruction).

2.3.3 Package Comparison

Table 2-11. Package Comparison

MC9S08QE128 MCF51QE128

Pin-to-pin compatible in 80-LQFP and 64-LQFP packages.

Additional 48-QFN, 44-QFP and 32-LQFP packages. No additional packages.

Reduced power wait mode (enabled by setting WAIT bit

in the SOPT1 register then executing STOP

instruction).

2-18 Freescale Semiconductor

QE128 Quick Reference User Guide, Rev. 1.0

Page 27

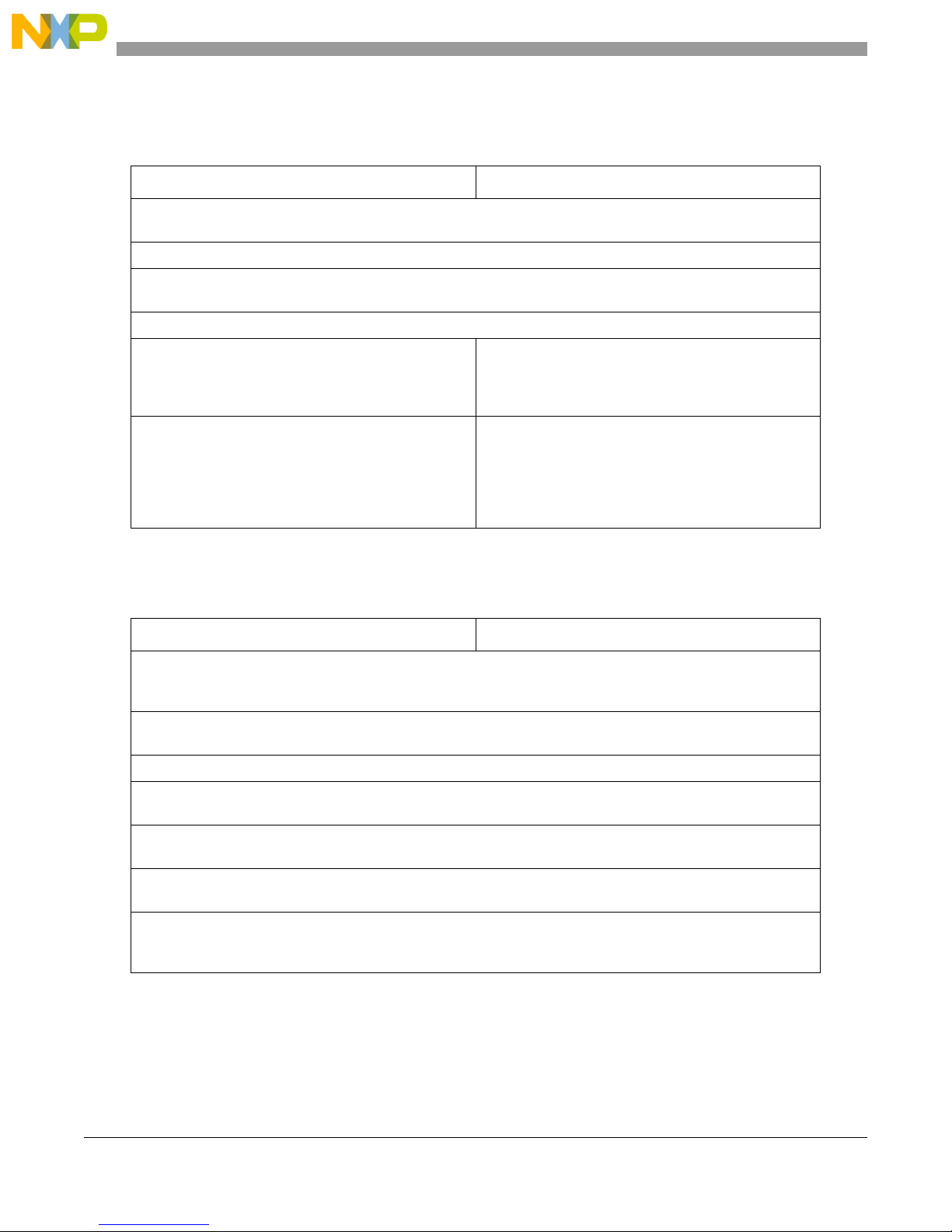

2.3.4 Clock Comparison

Table 2-12. Clock Comparison

MC9S08QE128 MCF51QE128

Oscillator (XOSC) – Loop-control pierce oscillator, crystal or ceramic resonator range of 31.25 kHz to 38.4 kHz

or 1 MHz to 16 MHz

Internal clock source (ICS) – Internal clock source module containing a frequency-locked-loop (FLL) controlled

by internal or external reference. Precision trimming of internal reference allows 0.2% resolution and 2%

deviation over temperature and voltage. Supports CPU frequencies from 2 MHz to 50 MHz

2.3.5 System Comparison

Table 2-13. System Comparison

MC9S08QE128 MCF51QE128

Watchdog computer operating properly (COP) reset with option to run from dedicated 1 kHz internal clock source

or bus clock.

Low-voltage detection with reset or interrupt. Selectable trip points.

Illegal opcode detection with reset.

No illegal address reset, all addresses in maps are

legal.

QE MCUs 8-bit and 32-bit Comparison

Illegal address detection with reset.

FLASH Block protection: protects in 1k increments.

Protects array 0 first (from 0x0FFFF - 0x00000), then

array 1 (from 0x1FFFF – 0x10000).

2.3.6 Input/Output Comparison

Table 2-14. Input/Output Comparison

MC9S08QE128 MCF51QE128

70 GPIOs (general purpose input/output) and 1 input-only and 1 output-only pin.

16 KBI (keyboard interrupts) with selectable polarity.

Hysteresis and configurable pull up device on all input pins, configurable slew rate and drive strength on all output

pins.

SET/CLR registers on 16 pins (PTC and PTE).

Rapid I/O not featured. Selectable Rapid I/O supported on PTC and PTE ports.

FLASH Block protection: protects in 2 k increments.

Protects array from 0x00000 to 0x1FFFF.

Freescale Semiconductor 2-19

QE128 Quick Reference User Guide, Rev. 1.0

Page 28

QE MCUs 8-bit and 32-bit Comparison

2.3.7 Development Support Comparison

Table 2-15. Development Support Comparison

MC9S08QE128 MCF51QE128

Single-wire background debug interface. Same hardware Background Debug Mode (BDM) cable supports both

devices.

One version of CodeWarrior integrated development environment (IDE) and debugger supports both devices.

CodeWarrior stationary, project wizard, initialization wizard and Processor Expert make C-code migration

between devices easy.

SET/CLR registers on 16 pins (PTC and PTE).

Break point capability to allow single breakpoint setting

during in-circuit debugging, plus three more

breakpoints in on-chip debug module.

Integrated ColdFire DEBUG_Rev_B+ interface with

single wire BDM connection supports the same

electrical interface used by the S08 family debug

modules.

On-chip in-circuit emulator (ICE) debug module

containing three comparators and nine trigger modes.

Eight deep FIFO for tracing change-of-flow addresses

and event-only data. Debug module supports both tag

and force breakpoints.

2.3.8 Peripherals Comparison

Table 2-16. Peripherals Comparison

MC9S08QE128 MCF51QE128

ADC – 24-Channel, 12-bit resolution, 2.5 µs conversion time, automatic compare function, 1.7 mV/°C

temperature sensor, internal bandgap reference channel, operation in stop3, and fully functional from 3.6 V to

1.8 V.

ACMPx – Two analog comparators with selectable interrupt on rising, falling, or either edge of comparator output,

compare option to fixed internal bandgap reference voltage, and operation in stop3.

SCIx – Two serial communications interface modules with optional 13-bit break.

SPIx – Two serial peripheral interfaces with Full-duplex or single-wire bidirectional, double-buffered transmit and

receive, Master or Slave mode, MSB-first or LSB-first shifting.

IICx – Two IICs with up to 100 kbps with maximum bus loading, multi-master operation, programmable slave

address, Interrupt driven byte-by-byte data transfer, supports broadcast mode and 10-bit addressing.

Classic ColdFire Debug B+ functionality mapped into

the single-pin BDM interface. 64 deep FIFO for tracing

processor status (PST) and debug data (DDATA). Real

time debug support, with 6 hardware breakpoints, four

PC, one address and one data, that can be configured

into a 1 or 2 level trigger with a programmable response.

TPMx – One 6-channel (TPM3) and two 3-channel (TPM1 and TPM2), selectable input capture, output compare,

or buffered edge- aligned or center-aligned PWM on each channel, and operation in stop3.

RTC – (Real time counter) 8-bit modules counter with binary or decimal based prescaler; external clock source

for precise time base, time-of-day, calendar or task scheduling functions; Free running on-chip low power

oscillator (1 kHz) for periodical wake-up without external components; runs in all MCU modes

2-20 Freescale Semiconductor

QE128 Quick Reference User Guide, Rev. 1.0

Page 29

Chapter 3

How to Load the QRUG Examples?

3.1 Overview

This section describes the steps needed to download the firmware to flash. This shows the modules

working in the hardware.

All the examples described in this document are developed using Code Warrior 6.0 version and can be

changed in order to fit the application. T o run these examples a Code W arrior version 6.0 and an Evaluation

Board or a Demo board are needed in order to run these examples satisfactorily.

3.2 Steps to programming the MCU using Multilink

Follow these simple steps in order to load the QRUG examples and download it to the device. The

explanation works for the EVB and Demo board.

1. Open CodeWarrior 6.0.

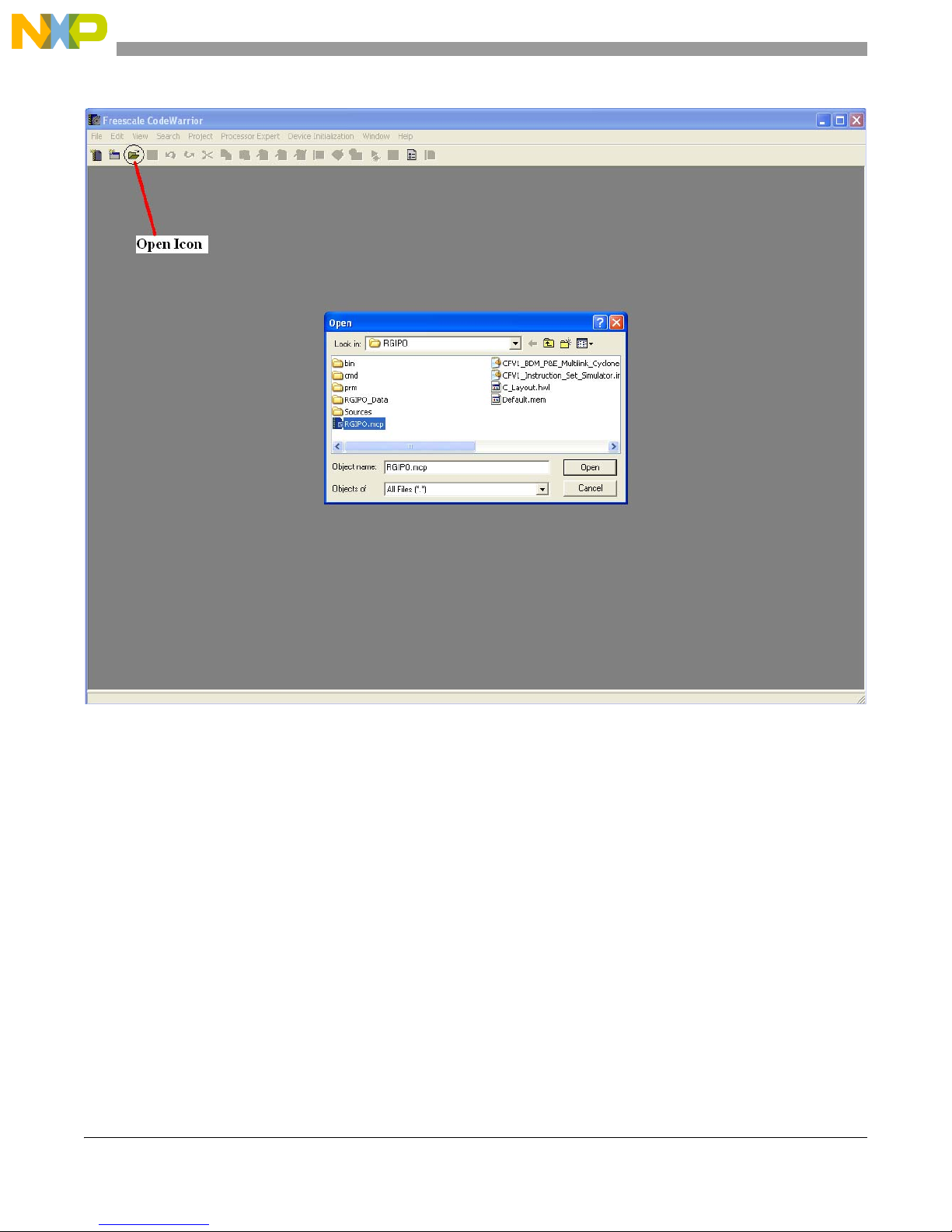

2. File -> Open, or click on the Open Icon as shown in Figure 3-1.

Freescale Semiconductor 3-1

QE128 Quick Reference User Guide, Rev. 1.0

Page 30

How to Load the QRUG Examples?

Figure 3-1. Open the Desired Project

3. Browse the desired project.

4. Double click on the .mcp extension file, in this case RGPIO.mcp.

5. To open the file double click on .c extension file (main.c).

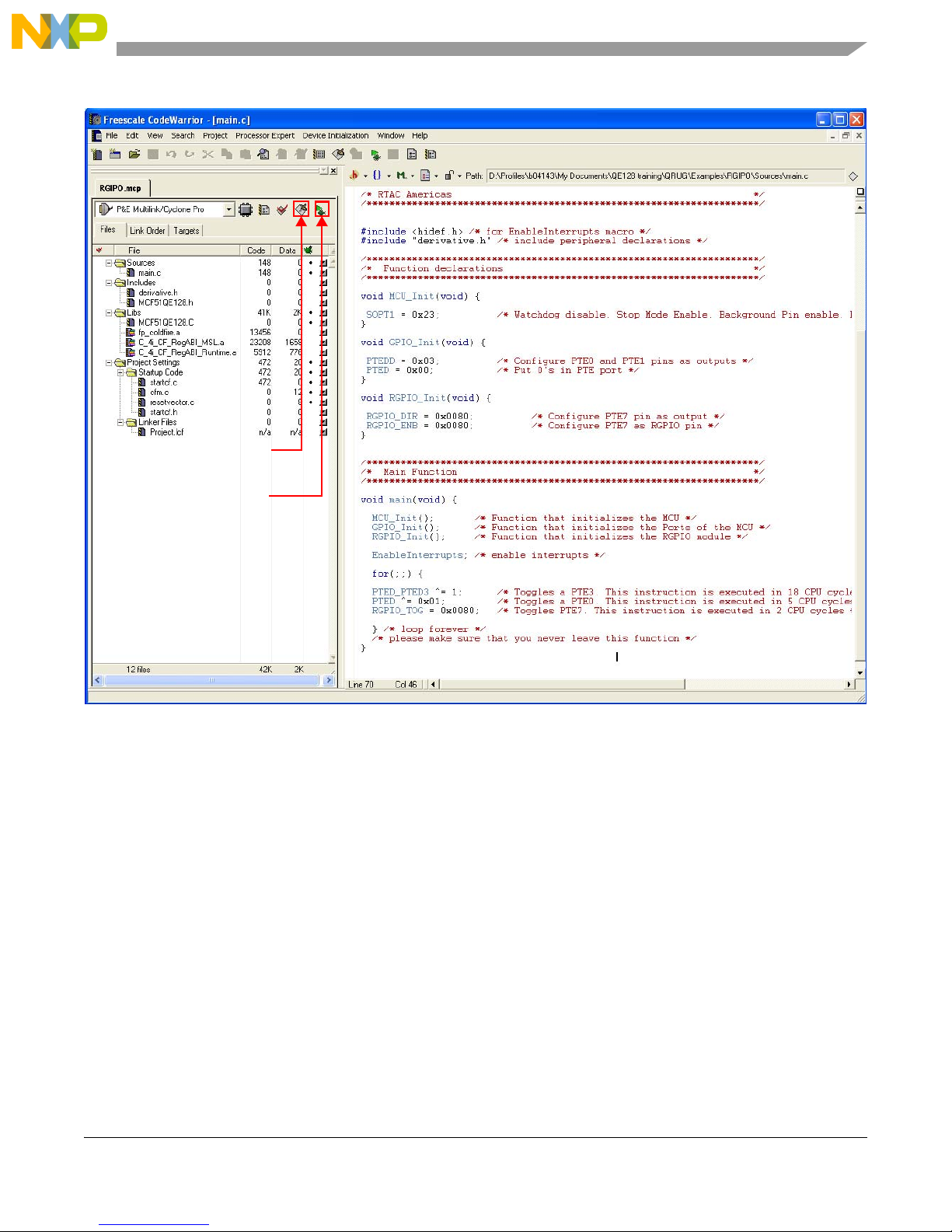

6. On the left side of the window is a combo box. Select the P&E Multilink/Cyclone Pro option as

shown in Figure 3-2. The BDM multilink hardware for programming the MCU is needed when an

EVB is used. This device is developed by PEmicro. If a demo board is used do not buy a multilink.

QE128 Quick Reference User Guide, Rev. 1.0

3-2 Freescale Semiconductor

Page 31

How to Load the QRUG Examples?

Figure 3-2. Select the Correct Option in the Combo Box

7. There are three different ways to compile the project. Click on the make icon, beside the combo

box, as shown in Figure 3-3. The make command can be accessed from the Project menu, -> Make,

or just press F7 key on your keyboard.

8. No errors should show up.

9. Project –> Debug. Click on the debug icon beside the make icon, or just press F5 on the keyboard.

Doing this launches the debugger and downloads the program to the MCU flash.

QE128 Quick Reference User Guide, Rev. 1.0

Freescale Semiconductor 3-3

Page 32

How to Load the QRUG Examples?

Make Icon

Debug Icon

Figure 3-3. Make Icon and Debug Icon

10. After the debug command is executed a window pops up (see Figure 3-4). Click on the Connect

option.

QE128 Quick Reference User Guide, Rev. 1.0

3-4 Freescale Semiconductor

Page 33

How to Load the QRUG Examples?

Figure 3-4. Connect Option

11. If a window appears asking to erase and program flash, click Yes.

12. The True-time simulator window appears on your screen. In this window debug the projects,

review the registers and memory in real time.

13. Click on the run button as shown in Figure 3-5. This figure shows the true-time simulator window

or debugger window. This makes the MCU start to execute the project.

QE128 Quick Reference User Guide, Rev. 1.0

Freescale Semiconductor 3-5

Page 34

How to Load the QRUG Examples?

Start/Continue Button

Figure 3-5. Run/Continue Icon

3.3 Steps to programming the MCU Using In-Circuit BDM

Follow these simple steps in order to load the QRUG examples and download it to the device. The

explanation works for EVB only.

1. Open CodeWarrior 6.0.

2. File -> Open, or click on the Open Icon as shown in Figure 3-6.

QE128 Quick Reference User Guide, Rev. 1.0

3-6 Freescale Semiconductor

Page 35

How to Load the QRUG Examples?

Figure 3-6. Open the Desired Project

3. Browse the desired project.

4. Double click on the .mcp extension file, in this case RGPIO.mcp.

5. To open the file, double click on .c extension file (main.c).

6. On the left side of the window is a combo box. Select the SofTec option as shown in Figure 3-7.

QE128 Quick Reference User Guide, Rev. 1.0

Freescale Semiconductor 3-7

Page 36

How to Load the QRUG Examples?

Figure 3-7. Select the Correct Option in the Combo Box

7. There are three different ways to compile the project.

8. Click on the make icon, beside the combo box, as shown in Figure 3-8. The make command can

be accessed from the Project menu, -> Make, or just press F7 key on your keyboard.

9. No errors show up.

10. Project –> Debug. Also click on the debug icon beside the make icon, or just press F5 on the

keyboard. Doing this launches the debugger and downloads the program to the MCU flash.

QE128 Quick Reference User Guide, Rev. 1.0

3-8 Freescale Semiconductor

Page 37

How to Load the QRUG Examples?

Make Icon

Debug Icon

Figure 3-8. Make Icon and Debug Icon

11. After the debug command is executed a window pops up (see Figure 3-9), select the EVBQE128

hardware model and then click on the Connect option.

QE128 Quick Reference User Guide, Rev. 1.0

Freescale Semiconductor 3-9

Page 38

How to Load the QRUG Examples?

F

Figure 3-9. Connect Option

12. A new window may appear asking to erase and program flash, click Yes.

13. The True-time simulator window appears on the screen. In this window debug the projects, review

the registers and memory in real time.

14. Click on the run button as shown in Figure 3-10. This figure shows the true-time simulator window

or debugger window. This makes the MCU start to execute the project.

QE128 Quick Reference User Guide, Rev. 1.0

3-10 Freescale Semiconductor

Page 39

How to Load the QRUG Examples?

Start/Continue button

Figure 3-10. Run/Continue Icon

QE128 Quick Reference User Guide, Rev. 1.0

Freescale Semiconductor 3-11

Page 40

How to Load the QRUG Examples?

3-12 Freescale Semiconductor

QE128 Quick Reference User Guide, Rev. 1.0

Page 41

Chapter 4

KBIxSC KBF KBACK KBIE KBMOD

Module Configuration

KBF – set when event occurs

KBACK – clears KBF

KBI Quick Reference

KBIxPE KBIPE7 KBIPE6 KBIPE5 KBIPE4 KBIPE3 KBIPE2 KBIPE1 KBIPE0

KBI Pin Enable

KBIPE[7:0] — enables and disables each port pin to operate as a keyboard interrupt pin.

KBIxES KBEDG7 KBEDG6 KBEDG5 KBEDG4 KBEDG3 KBEDG2 KBEDG1 KBEDG0

KBI Pin Enable

KBEDG[7:0] – determines the polarity edge that is recognized as a trigger event for the

KBIE – interrupt enable

KBMOD – mode select

corresponding pin.

Because there is more than one KBI module on this device, there may be more than one full

set of registers on your device. In the register name below, where there's a small x, there

would be a 1 or a 2 in your software to distinguish the register that is on KBI1 from KBI2 .

Using the Keyboard Interrupt (KBI) for the QE

Microcontrollers

4.1 Overview

This is a quick reference for using the keyboard interrupt (KBI) module for the QE family

microcontrollers (MCUs). Basic information about the functional description and configuration options

are provided.

The following example may be modified to suit an application. The KBI project is made for the

MC9S08QE128 and MCF51QE128 MCUs.

4.2 KBI project for EVB

4.2.1 Code example and explanation

This example code is available from the Freescale Web site www.freescale.com

Freescale Semiconductor 4-1

QE128 Quick Reference User Guide, Rev. 1.0

Page 42

Using the Keyboard Interrupt (KBI) for the QE Microcontrollers

In this application, four of the KBI pins are used to trigger an interrupt routine that toggles an LED every

time a keyboard event is detected. The MCU is programmed to:

• Have four KBI pins (PTD4, PTD5, PTD6 and PTD7), as the interrupt trigger.

• Detect falling edges only on the selected pins

• Generate a hardware interrupt where the LED toggle routine is serviced.

The functions for KBI.mcp project are:

• main – Endless loop waiting for a KBI interrupt.

• MCU_Init – MCU initialization, watchdog disable and the KBI clock module enabled.

• GPIO_Init – Configure PTE0 pin as output.

• KBI_Init – KBI module configuration.

• KBI_ISR – routine that toggles an LED every time an interrupt is generated.

The code below executes the instructions to disable the watchdog, enable the Reset option and background

pin. The System Option Register 1 (SOPT1) is used to configure the MCU. The SCGC1 and SCGC2 are

registers used for power saving consumption, here the bus clock to peripherals can be enabled or disabled.

In this example only the bus clock to the KBI module is active. The clocks to the other peripherals are

disabled.

void MCU_Init(void) {

SOPT1 = 0x23; // Watchdog disable. Stop Mode Enable. Background Pin

// enable. RESET pin enable

SCGC1 = 0x00; // Disable Bus clock to unused peripherals

SCGC2 = 0x10; // Bus Clock to the KBI module is enabled

}

This is the General Purpose Input/Output configuration. These code lines configure the direction for the

PTE port. Eight LEDs from the EVB are connected to the PTE port. The PTE0 is configured as output in

order to drive a LED.

void GPIO_Init(void) {

PTEDD = 0x01; // Configure PTE0 pin as output

PTED = 0x00; // Put 0's in PTE port

}

This is the initialization code for the keyboard interrupt using the QE128 MCU. For this example, both

KBI registers (KBIxSC and KBIxPE) are used to configure the module to detect only falling edges and

enable P T D4 to PTD7 as KBI. During the initialization phase the interrupts are masked. It takes time for

the internal pull up to reach a ‘1’ logic value. After the false interrupts are cleared, the keyboard interrupt

is unmasked.

void KBI_Init(void) {

KBI2SC = 0x06; // KBI interrupt request enabled. Detects edges only

KBI2PE = 0xF0; // PTD4, PTD5, PTD6 and PTD7 enabled as Keyboard interrupts

KBI2ES = 0x00; // Pins detects falling edge

}

This is the main function, above are the described called functions, and all the interrupts are enabled. After

this the keyboard interrupt can be serviced.

void main(void) {

MCU_Init(); // Function that initializes the MCU

4-2 Freescale Semiconductor

QE128 Quick Reference User Guide, Rev. 1.0

Page 43

Using the Keyboard Interrupt (KBI) for the QE Microcontrollers

GPIO_Init(); // Function that initializes the Ports of the MCU

KBI_Init(); // Function that initializes the KBI module

EnableInterrupts; // enable interrupts

for(;;) {

} // loop forever

// please make sure that you never leave this function

}

NOTE

This is the KBI service routine. Every time an interrupt is detected this

routine toggles a LED. The VectorNumber_Vkeyboard can be replaced by

the interrupt vector number. This depends, if the MCU is a 9S08 or V1.

Using this example makes the code fully compatible for either MCU.

void interrupt VectorNumber_keyboard KBI_ISR(void) {

// KBI interrupt vector number = 18 (S08)

// KBI interrupt vector number = 80 (V1)

KBI2SC_KBACK = 1; // Clear the KBI interrupt flag

PTED_PTED0 ^= 1; // Toggles PTE0

}

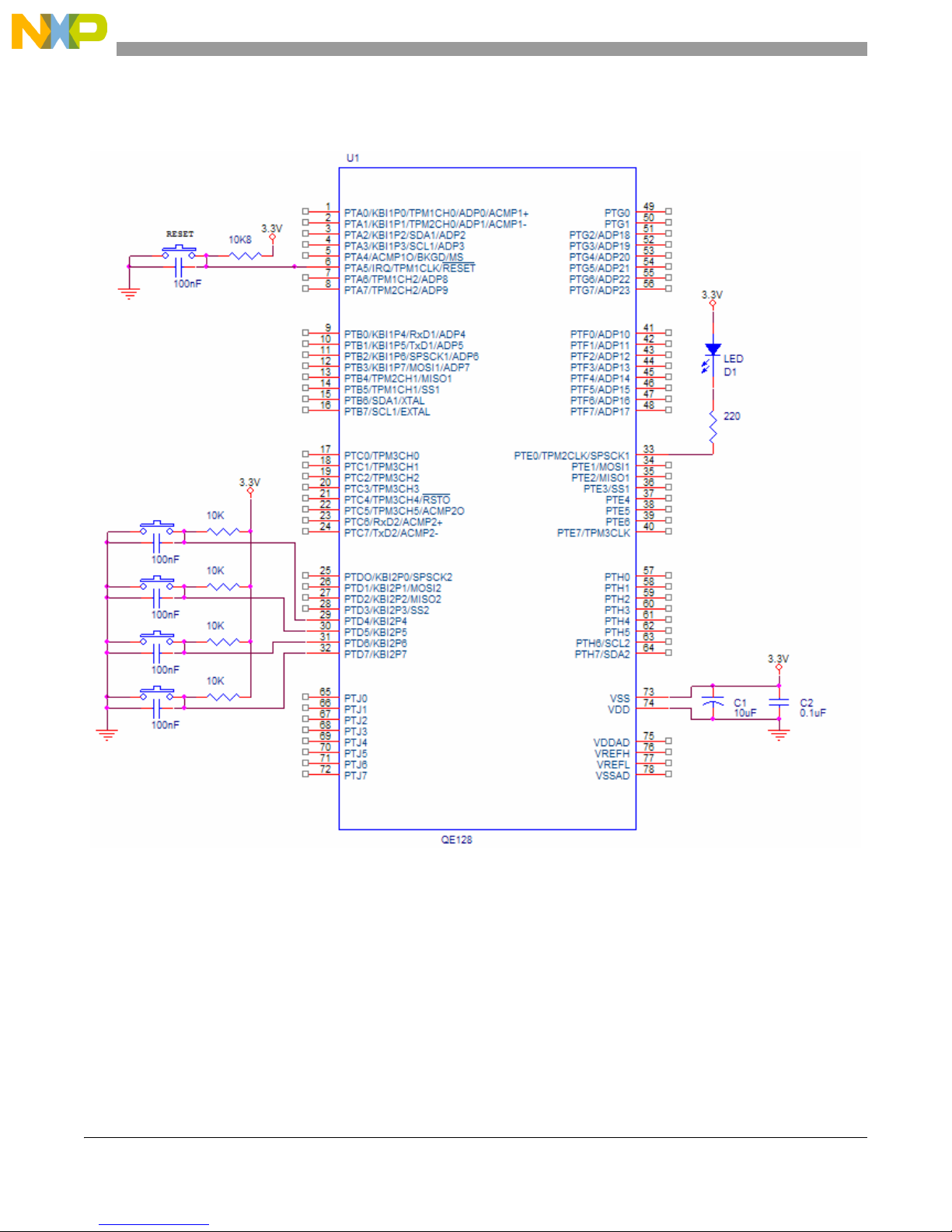

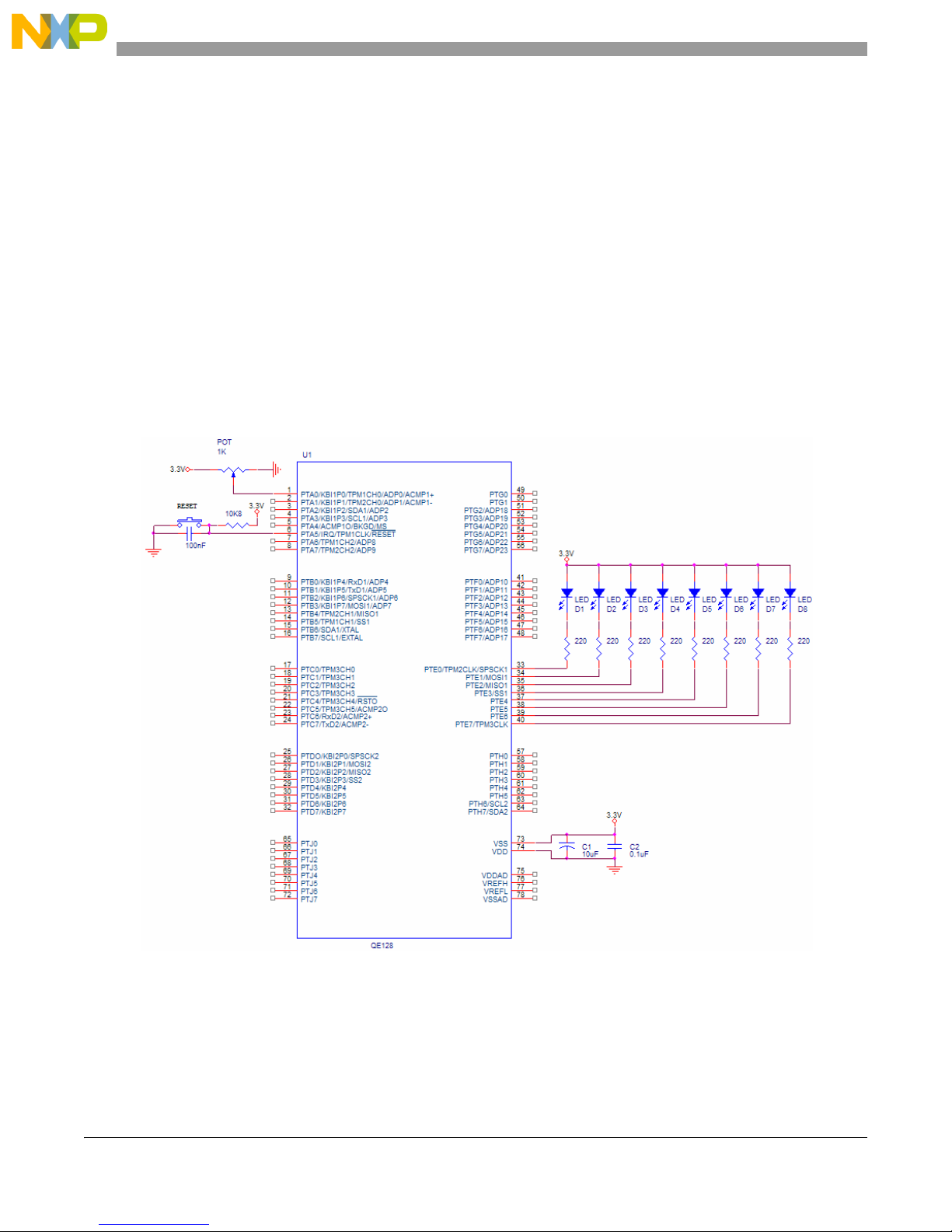

4.2.2 Hardware Implementation

This project is developed using the EVBQE128 STARTER KIT and can be downloaded at

www.freescale.com. No extra hardware is needed.

Freescale Semiconductor 4-3

QE128 Quick Reference User Guide, Rev. 1.0

Page 44

Using the Keyboard Interrupt (KBI) for the QE Microcontrollers

If the use of other KBI pins are required, extra hardware is easy to install. A push button, a resistor and a

capacitor are used to build the circuit. Figure 4-1 shows the hardware configuration.

Figure 4-1. EVB KBI Hardware Implementation

This example is developed using the CodeWarrior IDE version 6.0 for the

HCS08 and V1 families. It is expressly made for the MCF51QE128 and

MC9S08QE128 (80-pin package). There may be changes needed in the

code to initialize another MCU.

4-4 Freescale Semiconductor

NOTE

QE128 Quick Reference User Guide, Rev. 1.0

Page 45

Using the Keyboard Interrupt (KBI) for the QE Microcontrollers

Figure 4-1, shows hardware connections used for the KBI project. For

detailed information about the MCU supply voltages needed, please refer to

the Pins and Connections chapter in the Reference Manual (MC9S08QE128

or MCF51QE128). It can also be found at www.freescale.com.

4.3 KBI project for Demo board

4.3.1 Code example and explanation

This example code is available from the Freescale Web site www.freescale.com.

This section explains the differences of the codes used in EVB and the Demo board. The codes are the

same.

The functions for KBI.mcp project are:

• main – Endless loop waiting for a KBI interrupt.

• MCU_Init – MCU initialization, watchdog disable and the KBI clock module enabled.

• GPIO_Init – Enables internal pull-ups. Configures PTC0 pin as output.

• KBI_Init – KBI module configuration.

• KBI_ISR – routine that toggles a LED every time an interrupt is generated.

This is the General Purpose Input/Output configuration These code lines configure the direction for the

PTC port. Only six LEDs from the demo board are connected to the PTC port. The other two LEDs are

connected to the E port. In this example only PTC0 is configured as output in order to drive a LED. The

demo board does not count with any pull-ups; therefore the internal pull-up is enabled for the PTA2 and

PTA3 pins.

void GPIO_Init(void) {

PTAPE = 0x0C; // Enable PTA2 and PTA3 pins Internal Pullups

PTCDD = 0x01; // Configure PTC0 pin as output

PTCD = 0x01; // Put 0's in PTC0 pin

}

This is the initialization code for the keyboard interrupt using the QE128 MCU. For this example, both

KBI registers (KBIxSC and KBIxPE) are used to configure the module to detect only falling edges and

enable P TA2 and PTA3 as KBI. During the initialization phase, the interrupts are masked. It takes time for

the internal pull up to reach a ‘1’ logic value. After the false interrupts are cleared, the keyboard interrupt

is unmasked.

void KBI_Init(void) {

KBI1SC = 0x06; // KBI interrupt request enabled. Detects edges only

KBI1PE = 0x0C; // PTA2 and PTA3 enabled as Keyboard interrupts

KBI1ES = 0x00; // Pins detects falling edge

}

Freescale Semiconductor 4-5

QE128 Quick Reference User Guide, Rev. 1.0

Page 46

Using the Keyboard Interrupt (KBI) for the QE Microcontrollers

NOTE

This is the keyboard interrupt service routine. Every time an interrupt is

detected this routine toggles a LED. The VectorNumber_Vkeyboard can be

replaced by the interrupt vector number, this depends if the MCU is a 9S08

or V1. Using this example makes the code fully compatible for either MCU.

void interrupt VectorNumber_Vkeyboard KBI_ISR(void) {

KBI1SC_KBACK = 1; // Clear the KBI interrupt flag

PTCD_PTCD0 ^= 1; // Toggles PTC0

}

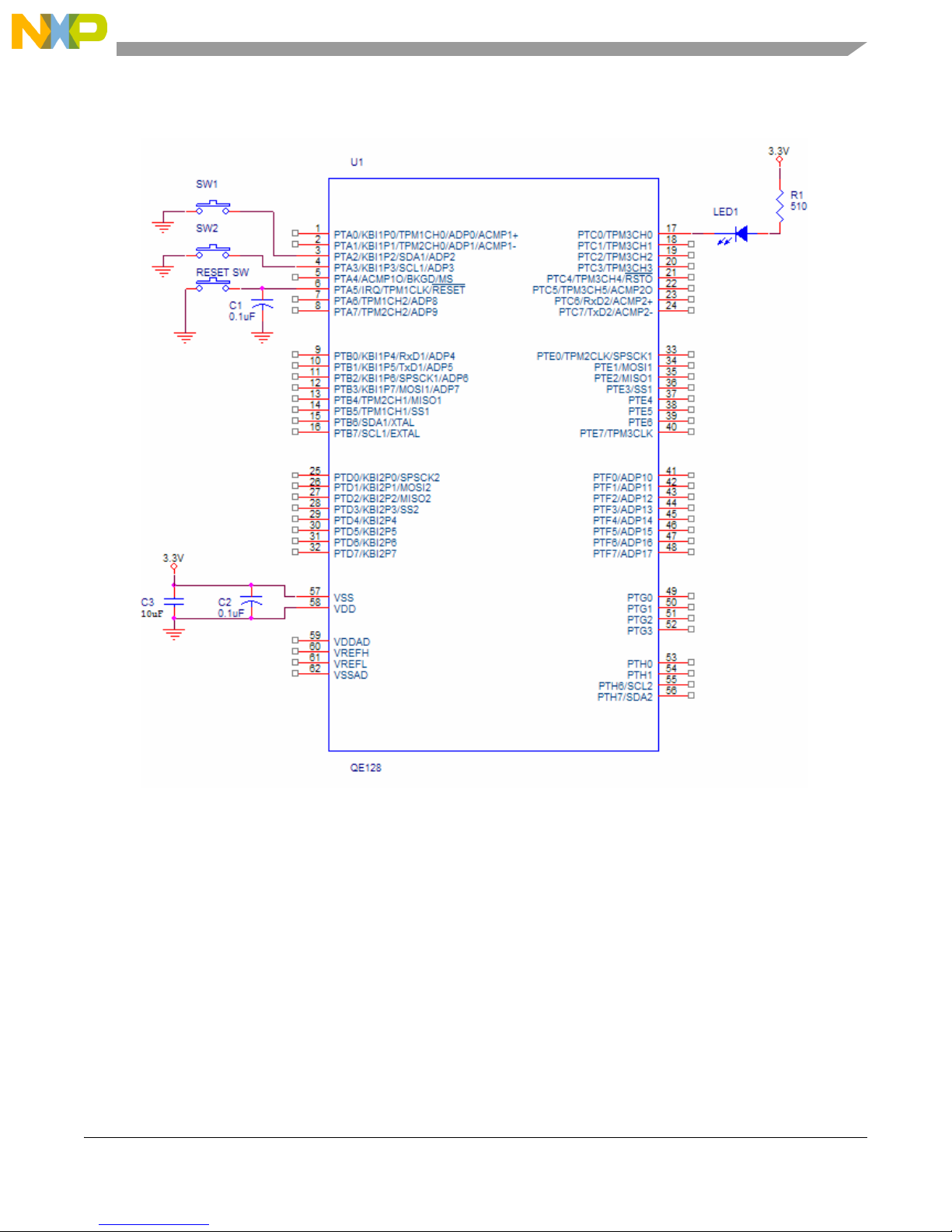

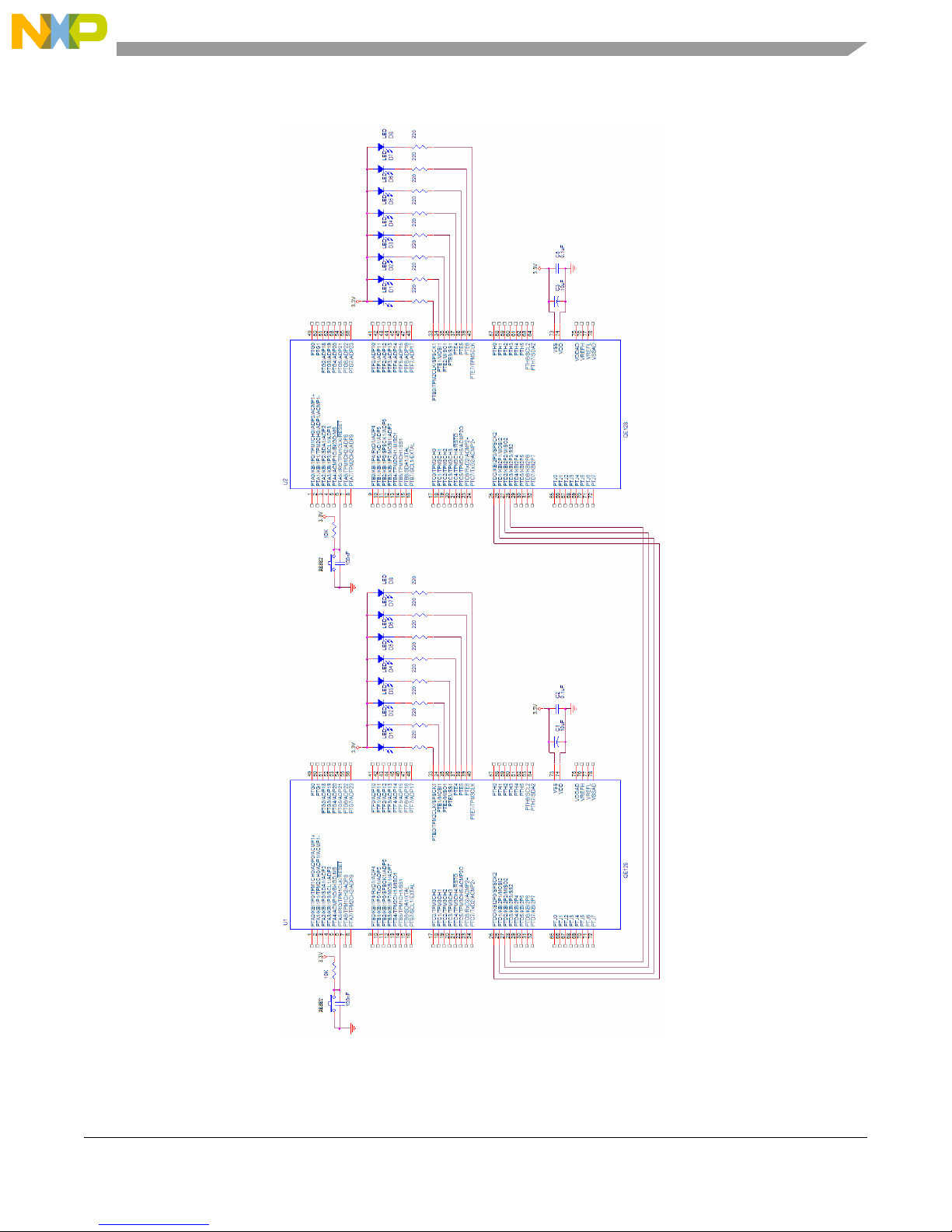

4.3.2 Hardware Implementation

This project was developed using the DEMOQE board. No extra hardware is needed.

4-6 Freescale Semiconductor

QE128 Quick Reference User Guide, Rev. 1.0

Page 47

Using the Keyboard Interrupt (KBI) for the QE Microcontrollers

Figure 4-2. Demo Board KBI Hardware Implementation.

This example is developed using the CodeWarrior IDE version 6.0 for the

HCS08 and V1 families. It is expressly made for the MCF51QE128 and

MC9S08QE128 (64-pin package). There may be changes needed in the

code to initialize another MCU.

Figure 4-2, shows the hardware connections used for the KBI project, for

detailed information about the MCU supply voltages needed, please refer to

the Pins and Connections chapter in the Reference Manual (MC9S08QE128

or MCF51QE128). It can also be found at www.freescale.com.

Freescale Semiconductor 4-7

NOTE

QE128 Quick Reference User Guide, Rev. 1.0

Page 48

Using the Keyboard Interrupt (KBI) for the QE Microcontrollers

4-8 Freescale Semiconductor

QE128 Quick Reference User Guide, Rev. 1.0

Page 49

Chapter 5

Using the Internal Clock Source (ICS) for the QE

Microcontrollers

5.1 Overview

This is a quick reference for using the internal source clock (ICS) module for the QE family

microcontrollers (MCUs). Basic information about the functional description and configuration options

are provided. The following example may be modified to suit an application. The ICS project is made for

the MC9S08QE128 and MCF51QE128 MCUs.

ICS Quick Reference

ICS1 CLKS RDIV IREFS IRCLKEN IREFSTEN

Module Configuration:

CLKS - Clock Source Select IRCLKEN - Internal Reference Clock Enable

RDIV - Reference Divider IREFSTEN - Internal Reference Stop Enable

IREFS - Internal Reference Select

ICS2 BDIV RANGE HGO LP EREFS ERCLKEN EREFSTEN

Module Configuration:

BDIV - Bus Frequency Divider EREFS - External Reference Select

RANGE - Frequency Range Select ERCLKEN - External Reference Enable

HGO - High Gain Oscillator Select EREFSTEN - External Reference Stop Enable

LP - Low Power Select

ICSRM TRIM

Internal oscillator trim value: higher value = slower frequency

ICSSC DRST/DRS DMX32 IREFST CLKST OSCINIT FTRIM

Module Status:

DRST - DCO Range Status / DRS - DCO Range Select CLKST - Clock Mode Status

DMX32 - DCO Maximum frequency with 32.768 kHz reference OSCINIT - OSC Initialization

IREFST - Internal Reference Status FTRIM - ICS Fine Trim

5.2 Code Example and Explanation

The project ICS.mcp shows how to configure the ICS module for the QE family MCUs. The main

functions are:

• main — Endless loop toggling a LED.

• MCU_Init – MCU initialization, watchdog disable.

• GPIO_Init – Configure PTE0 pin as output.

QE128 Quick Reference User Guide, Rev. 1.0

Freescale Semiconductor 5-1

Page 50

Using the Internal Clock Source (ICS) for the QE Microcontrollers

• ICS_Init – ICS module configuration

This example configures one of six modes of operation for the ICS module.

These are the four definitions used in the ICS code source. You need to uncomment the desired mode and

compile the project. This makes the MCU work with the selected clock source. For example to configure

the ICS in FEE mode just delete the two slashes at the beginning of the define.

//#define FEI // Configure bus clock to run at 25 MHz in FEI mode.

//#define FEE // Configure bus clock to run at 2 MHz in FEE mode.

//#define FBI // Configure bus clock to run at low frequency in FBI mode.

//#define FBE // Configure bus clock to run at low frequency in FBE mode.

The code below executes the instructions to disable the watchdog, enable the Reset option and background

pin. The System Option Register 1 (SOPT1) is used to configure the MCU. The SCGC1 and SCGC2 are

registers used for power saving consumption, here the bus clock to peripherals can be enabled or disabled.

The clocks to the other peripherals are disabled.

void MCU_Init(void) {

SOPT1 = 0x23; // Watchdog disabled. Stop Mode Enabled. Background Pin

// enabled. RESET pin enabled.

SCGC1 = 0x20; // Bus to TPM1 peripheral is enabled.

SCGC2 = 0x00; // All clocks to peripherals are disabled.

}

This is the General Purpose Input/Output configuration. These code lines configure the directions for the

PTE port. Only one LED is connected to the PTE port; therefore the PTE0 pin is configured as output.

void GPIO_Init(void) {

PTEDD = 0x01; // Configure PTE port as output

PTED = 0x00; // Put 0's in PTE port

}

This is the initialization code for the internal source clock used for the QE MCU. This application

configures the MCU in one of six modes of the ICS module.

void ICS_Init(void) {

#ifdef FEI

ICSC1 = 0x04; // Output of FLL is selected and Internal Reference Selected

ICSC2 = 0x00; // Bus frequency divided by 1

ICSTRM = *(unsigned char*far)0xFFAF; // Initialize ICSTRM register from a non volatile memory

ICSSC = (*(unsigned char*far)0xFFAE) | 0xA0; /* Initialize ICSSC register from a non volatile

memory */

#endif

#ifdef FEE

ICSC1 = 0x00; // Output of FLL is selected

ICSC2 = 0x87; // Divides slected clock by 4. External reference is selected

ICSSC = 0x00; // Initialize ICSSC register from a non volatile memory

#endif

#ifdef FBE

ICSC1 = 0xB8; // External reference clock selected. External reference divided by 5

ICSC2 = 0x00; // Bus frequency divided by 1

ICSSC = 0x00; // Initialize ICSSC register from a non volatile memory

#endif

#ifdef FBI

ICSC1 = 0x40; // Internal reference clock is selected

ICSC2 = 0x00; // Divides selected clock by 1

5-2 Freescale Semiconductor

QE128 Quick Reference User Guide, Rev. 1.0

Page 51

Using the Internal Clock Source (ICS) for the QE Microcontrollers

ICSSC = (*(unsigned char*far)0xFFAE) | 0x00; /* Initialize ICSSC register from a non volatile

memory */

ICSTRM = *(unsigned char*far)0xFFAF; // Initialize ICSTRM register from a non volatile memory

#endif FBI

}

This is the main function, above are the described called functions, and the interrupts are all enabled. The

ICS_configuration function configures the MCU in the selected clock mode. The clock frequency can be

seen on the PTE0 pin.

void main(void) {

MCU_Init(); // Function that initializes the MCU

GPIO_Init(); // Function that initializes the Ports of the MCU

ICS_Init(); // Function that initializes the ICS module

EnableInterrupts; // interrupts are enabled

for(;;) {

PTED_PTED0 ^= 1; // Toggle PTE0

Delay ();

} // loop forever

// please make sure that you never leave this function

}

The Bus frequency can be checked in the True-T ime Simulator window of CodeW arrior . Once the program