Page 1

MPC8308 PowerQUICC II Pro

Processor Reference Manual

MPC8308RM

Rev. 1

09/2013

Page 2

How to Reach Us:

Home Page:

www.freescale.com

Web Support:

http://www.freescale.com/support

Information in this document is provided solely to enable system and software

implementers to use Freescale products. There are no express or implied copyright

licenses granted hereunder to design or fabricate any integrated circuits based on the

information in this document.

Freescale reserves the right to make changes without further notice to any products

herein. Freescale makes no warranty, representation, or guarantee regarding the

suitability of its products for any pa rticular purpose, nor does Freescale assume any

liability arising out of the application or use of any product or circuit, and specifically

disclaims any and all liability, including without limitation consequential or incidental

damages. “Typical” parameters that may be provided in Freescale data sheets and/or

specifications can and do vary in different applications, and actua l performance may v ary

over time. All operat i ng parameters, including “typicals,” must be validated for each

customer application by customer’s technical experts. Freescale does not convey any

license under its patent rights nor the rights of othe rs. Freescale sells products pursuant

to standard terms and conditions of sale, which can be found at the following address:

freescale.com/SalesTermsandConditions.

Freescale, the Freescale logo, CodeWarrior, ColdFire, PowerQUICC,QorIQ,StarCore,

Symphony ,and VortiQa are trademarks of Freescale Semiconductor, Inc., Reg. U .S. P at.

& Tm. Off. CoreNet,and QUICC Engine are trademarks of F reescale Semicon ductor , Inc.

All other product or service names are the property of their respective owners. The P ower

Architecture and Po wer.org word marks and the Power and P ow er.org logos and related

marks are trademarks and service marks licensed by Power.org.

© 2010 and 2013 Freescale Semiconductor, Inc.

Document Number: MPC8308RM

Rev. 1, 09/2013

Page 3

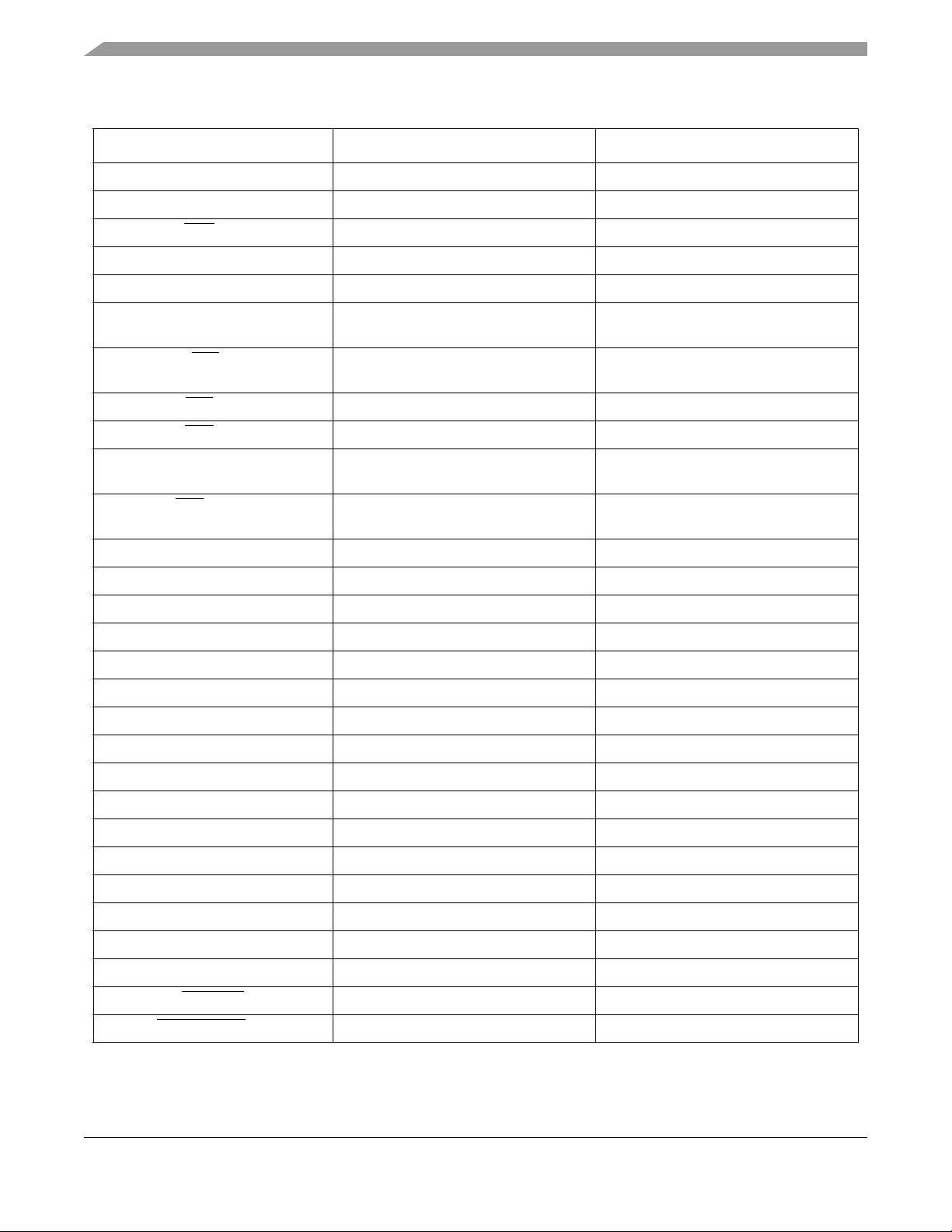

Contents

Paragraph

Number Title

Page

Number

About This Book

Audience...................................................................................................................... lvii

Organization................................................................................................................. lvii

Suggested Reading........................................................................................................ lix

General Information.................................................................................................. lix

Related Documentation ............................................................................................ lix

Conventions................................................................................................................... lx

Signal Conventions....................................................................................................... lxi

Acronyms and Abbreviations ....................................................................................... lxi

Chapter 1

Overview

1.1 MPC8308 Overview ........................................................................................................ 1-1

1.2 MPC8308 Architecture Overview ................................................................................... 1-7

1.2.1 e300 Core.....................................................................................................................1-7

1.2.2 DDR2 Memory Controller......................................................................................... 1-10

1.2.3 Dual Enhanced Three-Speed Ethernet Controllers.................................................... 1-10

1.2.4 SerDes PHY............................................................................................................... 1-11

1.2.5 PCI Express Interface ................................................................................................ 1-11

1.2.6 Universal Serial Bus (USB) 2.0................................................................................. 1-11

1.2.7 Enhanced Local Bus Controller (eLBC).................................................................... 1-12

1.2.8 Integrated Programmable Interrupt Controller (IPIC)............................................... 1-14

2

1.2.9 I

C Interface............................................................................................................... 1-15

1.2.10 General Purpose DMA Controller............................................................................. 1-15

1.2.11 Dual Universal Asynchronous Receiver/Transmitter (DUART)............................... 1-16

1.2.12 Enhanced Secure Digital Host Controller (eSDHC).................................................. 1-16

1.2.13 System Timers ........................................................................................................... 1-17

Chapter 2

Signal Descriptions

2.1 Signals Overview.............................................................................................................2-1

2.2 Output Signal States During Reset ................................................................................ 2-13

MPC8308 PowerQUICC II Pro Processor Reference Manual, Rev. 1

Freescale Semiconductor iii

Page 4

Figures

Figure

Number Title

Page

Number

Chapter 3

Memory Map

3.1 Internal Memory-Mapped Registers................................................................................ 3-1

3.2 Accessing IMMR Memory from the Local Processor..................................................... 3-1

3.3 IMMR Address Map........................................................................................................ 3-1

Chapter 4

Reset, Clocking, and Initialization

4.1 External Signals............................................................................................................... 4-1

4.1.1 Reset Signals................................................................................................................ 4-1

4.1.2 Clock Signals............................................................................................................... 4-2

4.2 Functional Description..................................................................................................... 4-3

4.2.1 Reset Operations..........................................................................................................4-3

4.2.2 Power-On Reset Flow.................................................................................................. 4-5

4.2.3 Hard Reset Flow .......................................................................................................... 4-6

4.3 Reset Configuration......................................................................................................... 4-7

4.3.1 Reset Configuration Signals ........................................................................................ 4-7

4.3.2 Reset Configuration Words.......................................................................................... 4-9

4.3.3 Loading the Reset Configuration Words ................................................................... 4-16

4.4 Clocking ........................................................................................................................ 4-22

4.4.1 System Clock Domains.............................................................................................. 4-23

4.4.2 USB Clocking............................................................................................................ 4-24

4.4.3 Ethernet Clocking...................................................................................................... 4-25

4.5 Memory Map/Register Definitions................................................................................ 4-25

4.5.1 Reset Configuration Register Descriptions................................................................ 4-25

4.5.2 Clock Configuration Registers................................................................................... 4-29

Chapter 5

System Configuration

5.1 Local Memory Map Overview and Example .................................................................. 5-1

5.1.1 Address Translation and Mapping............................................................................... 5-3

5.1.2 Window into Configuration Space...............................................................................5-3

5.1.3 Local Access Windows................................................................................................ 5-4

5.1.4 Local Access Register Descriptions ............................................................................ 5-5

5.1.5 Precedence of Local Access Windows...................................................................... 5-13

5.1.6 Configuring Local Access Windows......................................................................... 5-13

5.1.7 Distinguishing Local Access Windows from Other Mapping Functions..................5-13

5.1.8 Outbound Address Translation and Mapping Windows............................................ 5-14

MPC8308 PowerQUICC II Pro Processor Reference Manual, Rev. 1

iv Freescale Semiconductor

Page 5

Figures

Figure

Number Title

Page

Number

5.1.9 Inbound Address Translation and Mapping Windows .............................................. 5-14

5.1.10 Internal Memory Map................................................................................................ 5-14

5.1.11 Accessing Internal Memory from External Masters.................................................. 5-15

5.2 System Configuration .................................................................................................... 5-15

5.2.1 System Configuration Register Memory Map........................................................... 5-15

5.2.2 System Configuration Registers ................................................................................ 5-16

5.3 Software Watchdog Timer (WDT)................................................................................. 5-32

5.3.1 WDT Overview.......................................................................................................... 5-32

5.3.2 WDT Features............................................................................................................ 5-33

5.3.3 WDT Modes of Operation......................................................................................... 5-33

5.3.4 WDT Memory Map/Register Definition ................................................................... 5-34

5.3.5 Functional Description............................................................................................... 5-37

5.3.6 Initialization/Application Information (WDT Programming Guidelines)................. 5-39

5.4 Real Time Clock (RTC) Module.................................................................................... 5-39

5.4.1 Overview.................................................................................................................... 5-39

5.4.2 Features...................................................................................................................... 5-40

5.4.3 Assumptions............................................................................................................... 5-40

5.4.4 Modes of operation.................................................................................................... 5-40

5.4.5 External Signal Description....................................................................................... 5-41

5.4.6 RTC Memory Map/Register Definition..................................................................... 5-41

5.4.7 Functional Description............................................................................................... 5-45

5.4.8 RTC Reset Sequence.................................................................................................. 5-47

5.4.9 RTC Initialization Sequence ...................................................................................... 5-47

5.5 Periodic Interval Timer (PIT) ........................................................................................ 5-47

5.5.1 PIT Overview............................................................................................................. 5-47

5.5.2 PIT Features...............................................................................................................5-48

5.5.3 PIT Modes of Operation............................................................................................ 5-48

5.5.4 PIT External Signal Description................................................................................ 5-48

5.5.5 PIT Memory Map/Register Definition ...................................................................... 5-49

5.5.6 Functional Description............................................................................................... 5-52

5.5.7 PIT Programming Guidelines.................................................................................... 5-53

5.6 General-Purpose Timers (GTMs)................................................................................... 5-53

5.6.1 GTM Overview.......................................................................................................... 5-53

5.6.2 GTM Features ............................................................................................................ 5-54

5.6.3 GTM Modes of Operation.......................................................................................... 5-55

5.6.4 GTM External Signal Description ............................................................................. 5-56

5.6.5 GTM Memory Map/Register Definition.................................................................... 5-57

5.6.6 Functional Description............................................................................................... 5-66

5.6.7 Initialization/Application Information (Programming Guidelines for GTM Registers)....

5-69

5.7 Power Management Control (PMC)..............................................................................5-69

MPC8308 PowerQUICC II Pro Processor Reference Manual, Rev. 1

Freescale Semiconductor v

Page 6

Figures

Figure

Number Title

Page

Number

5.7.1 External Signal Description....................................................................................... 5-70

5.7.2 PMC Memory Map/Register Definition.................................................................... 5-70

5.7.3 Functional Description............................................................................................... 5-71

Chapter 6

Arbiter and Bus Monitor

6.1 Overview.......................................................................................................................... 6-1

6.1.1 Coherent System Bus Overview.................................................................................. 6-1

6.2 Arbiter Memory Map/Register Definition....................................................................... 6-2

6.2.1 Arbiter Configuration Register (ACR)........................................................................ 6-3

6.2.2 Arbiter Timers Register (ATR) .................................................................................... 6-4

6.2.3 Arbiter Event Enable Register (AEER).......................................................................6-5

6.2.4 Arbiter Event Register (AER)...................................................................................... 6-6

6.2.5 Arbiter Interrupt Definition Register (AIDR).............................................................. 6-7

6.2.6 Arbiter Mask Register (AMR)..................................................................................... 6-8

6.2.7 Arbiter Event Attributes Register (AEATR)................................................................ 6-9

6.2.8 Arbiter Event Address Register (AEADR)................................................................ 6-10

6.2.9 Arbiter Event Response Register (AERR)................................................................. 6-11

6.3 Functional Description................................................................................................... 6-12

6.3.1 Arbitration Policy ...................................................................................................... 6-12

6.3.2 Bus Error Detection................................................................................................... 6-15

6.4 Initialization/Applications Information ......................................................................... 6-18

6.4.1 Initialization Sequence............................................................................................... 6-18

6.4.2 Error Handling Sequence........................................................................................... 6-18

Chapter 7

e300 Processor Core Overview

7.1 Overview.......................................................................................................................... 7-1

7.1.1 Features........................................................................................................................ 7-3

7.1.2 Instruction Unit............................................................................................................ 7-6

7.1.3 Independent Execution Units....................................................................................... 7-7

7.1.4 Completion Unit .......................................................................................................... 7-8

7.1.5 Memory Subsystem Support........................................................................................ 7-8

7.1.6 Bus Interface Unit (BIU) ........................................................................................... 7-10

7.1.7 System Support Functions......................................................................................... 7-11

7.2 e300 Processor and System Version Numbers............................................................... 7-13

7.3 PowerPC Architecture Implementation......................................................................... 7-13

7.4 Implementation-Specific Information............................................................................ 7-14

7.4.1 Register Model........................................................................................................... 7-14

MPC8308 PowerQUICC II Pro Processor Reference Manual, Rev. 1

vi Freescale Semiconductor

Page 7

Figures

Figure

Number Title

Page

Number

7.4.2 Instruction Set and Addressing Modes...................................................................... 7-26

7.4.3 Cache Implementation............................................................................................... 7-29

7.4.4 Interrupt Model.......................................................................................................... 7-31

7.4.5 Memory Management................................................................................................ 7-35

7.4.6 Instruction Timing ..................................................................................................... 7-36

7.4.7 Core Interface ............................................................................................................ 7-37

7.4.8 Debug Features ......................................................................................................... 7-39

7.5 Differences Between Cores........................................................................................... 7-40

Chapter 8

Integrated Programmable Interrupt Controller (IPIC)

8.1 Introduction...................................................................................................................... 8-1

8.2 Features............................................................................................................................ 8-4

8.3 Modes of Operation ......................................................................................................... 8-4

8.3.1 Core Enable Mode....................................................................................................... 8-4

8.3.2 Core Disable Mode...................................................................................................... 8-4

8.4 External Signal Description............................................................................................. 8-5

8.4.1 Overview...................................................................................................................... 8-5

8.4.2 Detailed Signal Descriptions ....................................................................................... 8-5

8.5 Memory Map/Register Definition ................................................................................... 8-6

8.5.1 System Global Interrupt Configuration Register (SICFR).......................................... 8-8

8.5.2 System Global Interrupt Vector Register (SIVCR)...................................................... 8-9

8.5.3 System Internal Interrupt Pending Registers (SIPNR_H and SIPNR_L).................. 8-12

8.5.4 System Internal Interrupt Group A Priority Register (SIPRR_A)............................. 8-14

8.5.5 System Internal Interrupt Group B Priority Register (SIPRR_B) ............................. 8-15

8.5.6 System Internal Interrupt Group C Priority Register (SIPRR_C) ............................. 8-16

8.5.7 System Internal Interrupt Group D Priority Register (SIPRR_D)............................. 8-16

8.5.8 System Internal Interrupt Mask Register (SIMSR_H and SIMSR_L)...................... 8-17

8.5.9 System Internal Interrupt Control Register (SICNR)................................................ 8-18

8.5.10 System External Interrupt Pending Register (SEPNR).............................................. 8-20

8.5.11 System Mixed Interrupt Group A Priority Register (SMPRR_A)............................. 8-21

8.5.12 System Mixed Interrupt Group B Priority Register (SMPRR_B)............................. 8-22

8.5.13 System External Interrupt Mask Register (SEMSR)................................................. 8-22

8.5.14 System External Interrupt Control Register (SECNR).............................................. 8-23

8.5.15 System Error Status Register (SERSR)..................................................................... 8-25

8.5.16 System Error Mask Register (SERMR)..................................................................... 8-25

8.5.17 System Error Control Register (SERCR) .................................................................. 8-26

8.5.18 System External interrupt Polarity Control Register (SEPCR)................................. 8-26

8.5.19 System Internal Interrupt Force Registers (SIFCR_H and SIFCR_L)...................... 8-27

8.5.20 System External Interrupt Force Register (SEFCR).................................................. 8-29

MPC8308 PowerQUICC II Pro Processor Reference Manual, Rev. 1

Freescale Semiconductor vii

Page 8

Figures

Figure

Number Title

Page

Number

8.5.21 System Error Force Register (SERFR)...................................................................... 8-29

8.5.22 System Critical Interrupt Vector Register (SCVCR)................................................. 8-30

8.5.23 System Management Interrupt Vector Register (SMVCR) ....................................... 8-30

8.6 Functional Description................................................................................................... 8-31

8.6.1 Interrupt Types........................................................................................................... 8-31

8.6.2 Interrupt Configuration.............................................................................................. 8-32

8.6.3 Internal Interrupts Group Relative Priority................................................................ 8-33

8.6.4 Mixed Interrupts Group Relative Priority.................................................................. 8-33

8.6.5 Highest Priority Interrupt........................................................................................... 8-34

8.6.6 Interrupt Source Priorities.......................................................................................... 8-34

8.6.7 Masking Interrupt Sources......................................................................................... 8-38

8.6.8 Interrupt Vector Generation and Calculation............................................................. 8-39

8.6.9 Machine Check Interrupts.......................................................................................... 8-39

8.7 Message Shared Interrupts............................................................................................. 8-40

8.7.1 Memory Map/Register Definition ............................................................................. 8-40

8.7.2 Message Shared Registers ......................................................................................... 8-40

Chapter 9

DDR Memory Controller

9.1 Introduction...................................................................................................................... 9-1

9.2 Features............................................................................................................................ 9-2

9.2.1 Modes of Operation..................................................................................................... 9-3

9.3 External Signal Descriptions ........................................................................................... 9-3

9.3.1 Signals Overview......................................................................................................... 9-3

9.3.2 Detailed Signal Descriptions ....................................................................................... 9-6

9.4 Memory Map/Register Definition ................................................................................... 9-9

9.4.1 Register Descriptions................................................................................................. 9-10

9.5 Functional Description................................................................................................... 9-38

9.5.1 DDR SDRAM Interface Operation............................................................................ 9-42

9.5.2 DDR SDRAM Address Multiplexing........................................................................ 9-43

9.5.3 JEDEC Standard DDR SDRAM Interface Commands............................................. 9-45

9.5.4 DDR SDRAM Interface Timing................................................................................ 9-47

9.5.5 DDR SDRAM Mode-Set Command Timing............................................................. 9-51

9.5.6 DDR SDRAM Registered DIMM Mode................................................................... 9-51

9.5.7 DDR SDRAM Write Timing Adjustments................................................................ 9-52

9.5.8 DDR SDRAM Refresh .............................................................................................. 9-53

9.5.9 DDR Data Beat Ordering........................................................................................... 9-56

9.5.10 Page Mode and Logical Bank Retention ................................................................... 9-57

9.5.11 Error Checking and Correcting (ECC) ...................................................................... 9-58

9.5.12 Error Management..................................................................................................... 9-60

MPC8308 PowerQUICC II Pro Processor Reference Manual, Rev. 1

viii Freescale Semiconductor

Page 9

Figures

Figure

Number Title

Page

Number

9.6 Initialization/Application Information........................................................................... 9-60

9.6.1 DDR SDRAM Initialization Sequence...................................................................... 9-62

Chapter 10

Enhanced Local Bus Controller

10.1 Introduction.................................................................................................................... 10-1

10.1.1 Overview.................................................................................................................... 10-2

10.1.2 Features...................................................................................................................... 10-2

10.1.3 Modes of Operation................................................................................................... 10-3

10.2 External Signal Descriptions ......................................................................................... 10-4

10.3 Memory Map/Register Definition ................................................................................. 10-7

10.3.1 Register Descriptions................................................................................................. 10-9

10.4 Functional Description................................................................................................. 10-39

10.4.1 Basic Architecture.................................................................................................... 10-40

10.4.2 General-Purpose Chip-Select Machine (GPCM)..................................................... 10-42

10.4.3 Flash Control Machine (FCM) ................................................................................ 10-53

10.4.4 User-Programmable Machines (UPMs)................................................................... 10-68

10.5 Initialization/Application Information......................................................................... 10-84

10.5.1 Interfacing to Peripherals in Different Address Modes........................................... 10-84

10.5.2 Interface to Different Port-Size Devices.................................................................. 10-85

10.5.3 Command Sequence Examples for NAND Flash EEPROM................................... 10-86

10.5.4 Interfacing to Fast-Page Mode DRAM Using UPM ............................................... 10-90

10.5.5 Interfacing to ZBT SRAM Using UPM................................................................. 10-100

Chapter 11

Enhanced Secure Digital Host Controller

11.1 Overview........................................................................................................................ 11-1

11.2 Features.......................................................................................................................... 11-3

11.2.1 Data Transfer Modes.................................................................................................. 11-4

11.3 External Signal Description........................................................................................... 11-4

11.4 Memory Map/Register Definition ................................................................................. 11-5

11.4.1 DMA System Address Register (DSADDR)............................................................. 11-7

11.4.2 Block Attributes Register (BLKATTR)..................................................................... 11-7

11.4.3 Command Argument Register (CMDARG).............................................................. 11-8

11.4.4 Transfer Type Register (XFERTYP).......................................................................... 11-9

11.4.5 Command Response 0–3 (CMDRSP0–3)................................................................ 11-12

11.4.6 Buffer Data Port Register (DATPORT)................................................................... 11-14

11.4.7 Present State Register (PRSSTAT) .......................................................................... 11-15

11.4.8 Protocol Control Register (PROCTL) ..................................................................... 11-19

MPC8308 PowerQUICC II Pro Processor Reference Manual, Rev. 1

Freescale Semiconductor ix

Page 10

Figures

Figure

Number Title

Page

Number

11.4.9 System Control Register (SYSCTL)........................................................................ 11-22

11.4.10 Interrupt Status Register (IRQSTAT)....................................................................... 11-24

11.4.11 Interrupt Status Enable Register (IRQSTATEN)..................................................... 11-28

11.4.12 Interrupt Signal Enable Register (IRQSIGEN) ....................................................... 11-31

11.4.13 Auto CMD12 Error Status Register (AUTOC12ERR)............................................ 11-33

11.4.14 Host Controller Capabilities (HOSTCAPBLT) ....................................................... 11-35

11.4.15 Watermark Level Register (WML).......................................................................... 11-36

11.4.16 Force Event Register (FEVT).................................................................................. 11-36

11.4.17 Host Controller Version Register (HOSTVER)....................................................... 11-38

11.4.18 DMA Control Register (DCR)................................................................................. 11-38

11.5 Functional Description................................................................................................. 11-38

11.5.1 Data Buffer .............................................................................................................. 11-39

11.5.2 DMA CSB Interface ................................................................................................ 11-41

11.5.3 SD Protocol Unit...................................................................................................... 11-42

11.5.4 Clock & Reset Manager........................................................................................... 11-44

11.5.5 Clock Generator....................................................................................................... 11-44

11.5.6 SDIO Card Interrupt ................................................................................................ 11-44

11.5.7 Card Insertion and Removal Detection.................................................................... 11-46

11.5.8 Power Management ................................................................................................. 11-46

11.6 Initialization/Application Information......................................................................... 11-47

11.6.1 Command Send and Response Receive Basic Operation........................................ 11-47

11.6.2 Card Identification Mode......................................................................................... 11-48

11.6.3 Card Access ............................................................................................................. 11-52

11.6.4 Switch Function....................................................................................................... 11-57

11.6.5 Commands for MMC/SD/SDIO.............................................................................. 11-60

11.7 Software Restrictions................................................................................................... 11-65

11.7.1 Initialization Active ................................................................................................. 11-65

11.7.2 Software Polling Procedure..................................................................................... 11-65

11.7.3 Suspend Operation................................................................................................... 11-65

11.7.4 Data Port Access...................................................................................................... 11-65

11.7.5 Multi-block Read..................................................................................................... 11-65

Chapter 12

DMA Controller (DMAC)

12.1 Overview........................................................................................................................ 12-1

12.1.1 Features...................................................................................................................... 12-2

12.2 DMAC Memory Map/Register Definition .................................................................... 12-2

12.2.1 DMA Control Register (DMACR)............................................................................ 12-3

12.3 DMA Error Status (DMAES) ........................................................................................ 12-6

12.3.1 DMA Enable Error Interrupt Register (DMAEEI)....................................................12-8

MPC8308 PowerQUICC II Pro Processor Reference Manual, Rev. 1

x Freescale Semiconductor

Page 11

Figures

Figure

Number Title

Page

Number

12.3.2 DMA Set Enable Error Interrupt (DMASEEI).......................................................... 12-9

12.3.3 DMA Clear Enable Error Interrupt (DMACEEI)...................................................... 12-9

12.3.4 DMA Clear Interrupt Request (DMACINT)........................................................... 12-10

12.3.5 DMA Clear Error (DMACERR).............................................................................. 12-11

12.3.6 DMA Set START Bit (DMASSRT)......................................................................... 12-11

12.3.7 DMA Clear DONE Status (DMACDNE)................................................................ 12-12

12.3.8 DMA Interrupt Request Register (DMAINT)......................................................... 12-12

12.3.9 DMA Error Register (DMAERR)............................................................................ 12-13

12.3.10 DMA General Purpose Output Register (DMAGPOR) .......................................... 12-14

12.3.11 DMA Channel n Priority (DCHPRIn), n = 0–15..................................................... 12-15

12.3.12 Transfer Control Descriptor (TCD)......................................................................... 12-16

12.4 Functional Description................................................................................................. 12-24

12.4.1 DMA Microarchitecture .......................................................................................... 12-24

12.4.2 DMA Basic Data Flow ............................................................................................ 12-25

12.5 Initialization/Application Information......................................................................... 12-28

12.5.1 DMA Initialization................................................................................................... 12-28

12.5.2 DMA Programming Errors...................................................................................... 12-29

12.6 DMA Transfer.............................................................................................................. 12-29

12.6.1 Single Request ......................................................................................................... 12-29

12.6.2 Multiple Requests.................................................................................................... 12-30

12.7 TCD Status................................................................................................................... 12-32

12.7.1 Minor Loop Complete ............................................................................................. 12-32

12.7.2 Active Channel TCD Reads..................................................................................... 12-32

12.7.3 Preemption status..................................................................................................... 12-32

12.8 Channel Linking .......................................................................................................... 12-33

12.9 Programming during channel execution...................................................................... 12-33

12.9.1 Dynamic priority changing...................................................................................... 12-33

12.9.2 Dynamic channel linking and dynamic scatter/gather............................................. 12-34

Chapter 13

Universal Serial Bus Interface

13.1 Introduction.................................................................................................................... 13-1

13.1.1 Overview.................................................................................................................... 13-2

13.1.2 Features...................................................................................................................... 13-2

13.1.3 Modes of Operation................................................................................................... 13-2

13.2 External Signals............................................................................................................. 13-3

13.2.1 ULPI Interface ........................................................................................................... 13-3

13.3 Memory Map/Register Definitions................................................................................ 13-4

13.3.1 Capability Registers................................................................................................... 13-6

13.3.2 Operational Registers............................................................................................... 13-10

MPC8308 PowerQUICC II Pro Processor Reference Manual, Rev. 1

Freescale Semiconductor xi

Page 12

Figures

Figure

Number Title

Page

Number

13.4 Functional Description................................................................................................. 13-44

13.4.1 System Interface ...................................................................................................... 13-44

13.4.2 DMA Engine............................................................................................................ 13-45

13.4.3 FIFO RAM Controller............................................................................................. 13-45

13.4.4 PHY Interface.......................................................................................................... 13-45

13.5 Host Data Structures.................................................................................................... 13-45

13.5.1 Periodic Frame List.................................................................................................. 13-46

13.5.2 Asynchronous List Queue Head Pointer.................................................................. 13-47

13.5.3 Isochronous (High-Speed) Transfer Descriptor (iTD)............................................. 13-48

13.5.4 Split Transaction Isochronous Transfer Descriptor (siTD)...................................... 13-52

13.5.5 Queue Element Transfer Descriptor (qTD)............................................................. 13-56

13.5.6 Queue Head.............................................................................................................. 13-62

13.5.7 Periodic Frame Span Traversal Node (FSTN)......................................................... 13-66

13.6 Host Operations ........................................................................................................... 13-68

13.6.1 Host Controller Initialization................................................................................... 13-68

13.6.2 Power Port................................................................................................................ 13-69

13.6.3 Reporting Over-Current........................................................................................... 13-69

13.6.4 Suspend/Resume...................................................................................................... 13-69

13.6.5 Schedule Traversal Rules......................................................................................... 13-72

13.6.6 Periodic Schedule Frame Boundaries vs. Bus Frame Boundaries........................... 13-73

13.6.7 Periodic Schedule .................................................................................................... 13-75

13.6.8 Managing Isochronous Transfers Using iTDs.........................................................13-76

13.6.9 Asynchronous Schedule........................................................................................... 13-81

13.6.10 Managing Control/Bulk/Interrupt Transfers via Queue Heads................................ 13-85

13.6.11 Ping Control............................................................................................................. 13-89

13.6.12 Split Transactions.....................................................................................................13-90

13.6.13 Port Test Modes ..................................................................................................... 13-118

13.6.14 Interrupts................................................................................................................ 13-119

13.7 Device Data Structures .............................................................................................. 13-123

13.7.1 Endpoint Queue Head............................................................................................ 13-124

13.7.2 Endpoint Transfer Descriptor (dTD) ..................................................................... 13-127

13.8 Device Operational Model......................................................................................... 13-129

13.8.1 Device Controller Initialization............................................................................. 13-129

13.8.2 Port State and Control............................................................................................ 13-130

13.8.3 Managing Endpoints..............................................................................................13-133

13.8.4 Managing Queue Heads......................................................................................... 13-143

13.8.5 Managing Transfers with Transfer Descriptors ..................................................... 13-145

13.8.6 Servicing Interrupts................................................................................................ 13-148

13.9 Deviations from the EHCI Specifications ................................................................. 13-149

13.9.1 Embedded Transaction Translator Function.......................................................... 13-150

13.9.2 Device Operation................................................................................................... 13-153

MPC8308 PowerQUICC II Pro Processor Reference Manual, Rev. 1

xii Freescale Semiconductor

Page 13

Figures

Figure

Number Title

Page

Number

13.9.3 Non-Zero Fields the Register File ......................................................................... 13-154

13.9.4 SOF Interrupt......................................................................................................... 13-154

13.9.5 Embedded Design.................................................................................................. 13-154

13.9.6 Miscellaneous Variations from EHCI.................................................................... 13-154

13.10 Timing Diagrams....................................................................................................... 13-156

Chapter 14

PCI Express Interface Controller

14.1 Introduction.................................................................................................................... 14-1

14.1.1 MPC8308 as a PCI Express Initiator......................................................................... 14-3

14.1.2 MPC8308 as a PCI Express Target............................................................................ 14-3

14.1.3 Features...................................................................................................................... 14-4

14.1.4 Modes of Operation................................................................................................... 14-4

14.2 External Signal Descriptions ......................................................................................... 14-5

14.3 Memory Map/Register Definitions................................................................................ 14-5

14.3.1 PCI Express Memory Map ........................................................................................ 14-5

14.4 PCI Express Core Configuration Header Registers..................................................... 14-14

14.4.1 Common PCI Express-Compatible Configuration Header Registers...................... 14-14

14.4.2 Type 0 PCI Express-Compatible Configuration Header Registers.......................... 14-21

14.4.3 Type 1 PCI-Compatible Configuration Header Registers ....................................... 14-27

14.4.4 PCI Express-Compatible Device-Specific Configuration Space Registers............. 14-36

14.4.5 PCI Express Extended Configuration Space ........................................................... 14-52

14.4.6 PCI Express Controller Internal Control and Status Registers (CSRs)................... 14-62

14.4.7 PCI Express BAR Configuration Registers (EP Mode) .......................................... 14-72

14.4.8 PCI Express Extended Status and Control Registers............................................... 14-74

14.5 PCI Express CSB Bridge............................................................................................. 14-76

14.5.1 PCI Express CSB Bridge Configuration Space....................................................... 14-77

14.5.2 Global Registers....................................................................................................... 14-77

14.5.3 PCI Express Outbound PIO Registers..................................................................... 14-80

14.5.4 PCI Express Inbound PIO Registers........................................................................ 14-82

14.5.5 DMA Registers........................................................................................................ 14-83

14.5.6 Mailbox Registers.................................................................................................... 14-88

14.5.7 PCI Express Host Interrupt Registers...................................................................... 14-90

14.5.8 CSB System Interrupt Registers.............................................................................. 14-94

14.5.9 PCI Express Power Management Registers........................................................... 14-103

14.5.10 PCI Express Outbound Address Mapping Registers............................................. 14-104

14.5.11 PCI Express EP Inbound Address Translation Registers ...................................... 14-107

14.5.12 PCI Express RC Inbound Address Mapping Registers ......................................... 14-108

14.6 Functional Description................................................................................................14-111

14.6.1 Architecture ........................................................................................................... 14-112

MPC8308 PowerQUICC II Pro Processor Reference Manual, Rev. 1

Freescale Semiconductor xiii

Page 14

Figures

Figure

Number Title

Page

Number

14.6.2 Interrupts............................................................................................................... 14-122

14.6.3 Mailbox.................................................................................................................. 14-124

14.6.4 Power Management ............................................................................................... 14-126

14.6.5 Hot Reset................................................................................................................ 14-127

14.7 Initialization/Application Information....................................................................... 14-127

14.7.1 Initialization Sequence........................................................................................... 14-127

14.8 DMA Functional Operation....................................................................................... 14-128

14.8.1 DMA Descriptor Format........................................................................................ 14-128

14.8.2 Write DMA............................................................................................................ 14-130

14.8.3 Read DMA............................................................................................................. 14-131

14.8.4 Descriptor-Based DMA......................................................................................... 14-132

Chapter 15

SerDes PHY

15.1 Introduction.................................................................................................................... 15-1

15.1.1 Overview.................................................................................................................... 15-1

15.1.2 Features...................................................................................................................... 15-1

15.1.3 Mode of Operation..................................................................................................... 15-2

15.1.4 Clock.......................................................................................................................... 15-2

15.2 External Signals............................................................................................................. 15-2

15.3 Memory Map/Registers ................................................................................................. 15-3

15.3.1 SerDes Control Register 0 (SRDSCR0) .................................................................... 15-4

15.3.2 SerDes Control Register 1 (SRDSCR1) .................................................................... 15-6

15.3.3 SerDes Control Register 2 (SRDSCR2) .................................................................... 15-7

15.3.4 SerDes Control Register 3 (SRDSCR3) .................................................................... 15-8

15.3.5 SerDes Control Register 4 (SRDSCR4) .................................................................... 15-9

15.3.6 SerDesn Reset Control Register (SRDSRSTCTL).................................................. 15-10

15.4 Initialization Sequence and Reset................................................................................ 15-10

15.5 Power Management: Power Down .............................................................................. 15-11

Chapter 16

Enhanced Three-Speed Ethernet Controllers

16.1 Overview........................................................................................................................ 16-1

16.2 Features.......................................................................................................................... 16-2

16.3 Modes of Operation ....................................................................................................... 16-4

16.4 External Signals Description ......................................................................................... 16-5

16.4.1 Detailed Signal Descriptions ..................................................................................... 16-7

16.5 Memory Map/Register Definition ................................................................................. 16-9

16.5.1 Top-Level Module Memory Map ............................................................................ 16-10

MPC8308 PowerQUICC II Pro Processor Reference Manual, Rev. 1

xiv Freescale Semiconductor

Page 15

Figures

Figure

Number Title

Page

Number

16.5.2 Detailed Memory Map............................................................................................. 16-10

16.5.3 Memory-Mapped Register Descriptions.................................................................. 16-21

16.6 Functional Description............................................................................................... 16-120

16.6.1 Connecting to Physical Interfaces on Ethernet...................................................... 16-121

16.6.2 Gigabit Ethernet Controller Channel Operation.................................................... 16-124

16.6.3 TCP/IP Off-Load ................................................................................................... 16-139

16.6.4 Quality of Service (QoS) Provision....................................................................... 16-144

16.6.5 Lossless Flow Control ........................................................................................... 16-154

16.6.6 Hardware Assist for IEEE Std. 1588 Compliant Ti mestamping ........................... 16-157

16.6.7 Buffer Descriptors.................................................................................................. 16-164

16.7 Initialization/Application Information....................................................................... 16-171

16.7.1 Interface Mode Configuration ............................................................................... 16-172

16.7.2 MAC: Half-Duplex Collision on FCS of Short Frame.......................................... 16-178

Chapter 17

I2C Interface

17.1 Introduction.................................................................................................................... 17-1

17.1.1 Features...................................................................................................................... 17-2

17.1.2 Modes of Operation................................................................................................... 17-2

17.2 External Signal Descriptions ......................................................................................... 17-3

17.2.1 Signal Overview ........................................................................................................ 17-3

17.2.2 Detailed Signal Descriptions ..................................................................................... 17-3

17.3 Memory Map/Register Definition ................................................................................. 17-4

17.3.1 Register Descriptions................................................................................................. 17-5

17.4 Functional Description................................................................................................. 17-10

17.4.1 Transaction Protocol................................................................................................17-10

17.4.2 Arbitration Procedure .............................................................................................. 17-14

17.4.3 Handshaking ............................................................................................................ 17-15

17.4.4 Clock Control........................................................................................................... 17-15

17.4.5 Boot Sequencer Mode.............................................................................................. 17-16

17.5 Initialization/Application Information......................................................................... 17-21

17.5.1 Interrupt Service Routine Flowchart........................................................................ 17-21

17.5.2 Initialization Sequence............................................................................................. 17-23

17.5.3 Generation of START.............................................................................................. 17-23

17.5.4 Post-Transfer Software Response............................................................................ 17-23

17.5.5 Generation of STOP................................................................................................. 17-24

17.5.6 Generation of Repeated START.............................................................................. 17-24

17.5.7 Generation of SCL When SDA is Negated ............................................................. 17-24

17.5.8 Slave Mode Interrupt Service Routine..................................................................... 17-24

MPC8308 PowerQUICC II Pro Processor Reference Manual, Rev. 1

Freescale Semiconductor xv

Page 16

Figures

Figure

Number Title

Page

Number

Chapter 18

DUART

18.1 Overview........................................................................................................................ 18-1

18.1.1 Features...................................................................................................................... 18-2

18.1.2 Modes of Operation................................................................................................... 18-2

18.2 External Signal Descriptions ......................................................................................... 18-3

18.2.1 Signal Overview ........................................................................................................ 18-3

18.2.2 Detailed Signal Descriptions ..................................................................................... 18-3

18.3 Memory Map/Register Definition ................................................................................. 18-3

18.3.1 Register Descriptions................................................................................................. 18-5

18.4 Functional Description................................................................................................. 18-16

18.4.1 Serial Interface......................................................................................................... 18-17

18.4.2 Baud-Rate Generator Logic..................................................................................... 18-18

18.4.3 Local Loopback Mode............................................................................................. 18-19

18.4.4 Errors ....................................................................................................................... 18-19

18.4.5 FIFO Mode .............................................................................................................. 18-19

18.5 DUART Initialization/Application Information .......................................................... 18-21

Chapter 19

Serial Peripheral Interface

19.1 Overview........................................................................................................................ 19-1

19.1.1 Features...................................................................................................................... 19-2

19.1.2 SPI Transmission and Reception Process.................................................................. 19-2

19.1.3 Modes of Operation................................................................................................... 19-3

19.2 External Signal Descriptions ......................................................................................... 19-6

19.2.1 Overview.................................................................................................................... 19-6

19.2.2 Detailed Signal Descriptions ..................................................................................... 19-6

19.3 Memory Map/Register Definition ................................................................................. 19-7

19.3.1 Register Descriptions................................................................................................. 19-8

19.4 Initialization/Application Information......................................................................... 19-15

19.4.1 SPI Master Programming Example ......................................................................... 19-15

19.4.2 SPI Slave Programming Example............................................................................ 19-15

Chapter 20

JTAG/Testing Support

20.1 Overview........................................................................................................................ 20-1

20.2 JTAG Signals ................................................................................................................. 20-1

20.2.1 External Signal Descriptions ..................................................................................... 20-2

MPC8308 PowerQUICC II Pro Processor Reference Manual, Rev. 1

xvi Freescale Semiconductor

Page 17

Figures

Figure

Number Title

Page

Number

20.3 JTAG Registers and Scan Chains .................................................................................. 20-3

Chapter 21

General Purpose I/O (GPIO)

21.1 Introduction.................................................................................................................... 21-1

21.1.1 Overview.................................................................................................................... 21-1

21.1.2 Features...................................................................................................................... 21-1

21.2 External Signal Description........................................................................................... 21-2

21.2.1 Signals Overview....................................................................................................... 21-2

21.3 Memory Map/Register Definition ................................................................................. 21-2

21.3.1 GPIO Direction Register (GPDIR)............................................................................ 21-3

21.3.2 GPIO Open Drain Register (GPODR)....................................................................... 21-3

21.3.3 GPIO Data Register (GPDAT)................................................................................... 21-4

21.3.4 GPIO Interrupt Event Register (GPIER)................................................................... 21-4

21.3.5 GPIO Interrupt Mask Register (GPIMR)................................................................... 21-4

21.3.6 GPIO Interrupt Control Register (GPICR)................................................................ 21-5

Appendix A

Complete List of Configuration, Control, and Status Registers

A.1 Local Access Windows................................................................................................... A-1

A.2 System Configuration Registers ..................................................................................... A-2

A.3 Watchdog Timer (WDT)................................................................................................. A-3

A.4 Real Time Clock (RTC).................................................................................................. A-3

A.5 Periodic Interval Timer (PIT) ......................................................................................... A-3

A.6 General Purpose (Global) Timers (GTMs) ..................................................................... A-4

A.7 Integrated Programmable Interrupt Controller (IPIC).................................................... A-5

A.8 System Arbiter................................................................................................................ A-6

A.9 Reset Configuration........................................................................................................ A-6

A.10 Clock Configuration ....................................................................................................... A-7

A.11 Power Management Controller (PMC)........................................................................... A-7

A.12 General Purpose I/O (GPIO)........................................................................................... A-8

A.13 DDR Memory Controller................................................................................................ A-8

A.14 I2C Controller ................................................................................................................. A-9

A.15 DUART......................................................................................................................... A-10

A.16 Enhanced Local Bus Controller (eLBC)........................................................................A-11

A.17 Serial Peripheral Interface (SPI)................................................................................... A-12

A.18 DMA Controller............................................................................................................ A-13

A.19 PCI Express Controller................................................................................................. A-14

A.20 Enhanced Three-Speed Ethernet Controllers (eTSECs)............................................... A-21

MPC8308 PowerQUICC II Pro Processor Reference Manual, Rev. 1

Freescale Semiconductor xvii

Page 18

Figures

Figure

Number Title

Page

Number

A.21 SerDes PHY..................................................................................................................A-31

A.22 Enhanced Secure Digital Host Controller (eSDHC)..................................................... A-32

A.23 Universal Serial Bus (USB) Interface........................................................................... A-32

Appendix B

Revision History

MPC8308 PowerQUICC II Pro Processor Reference Manual, Rev. 1

xviii Freescale Semiconductor

Page 19

Figures

Figure

Number Title

Figures

Page

Number

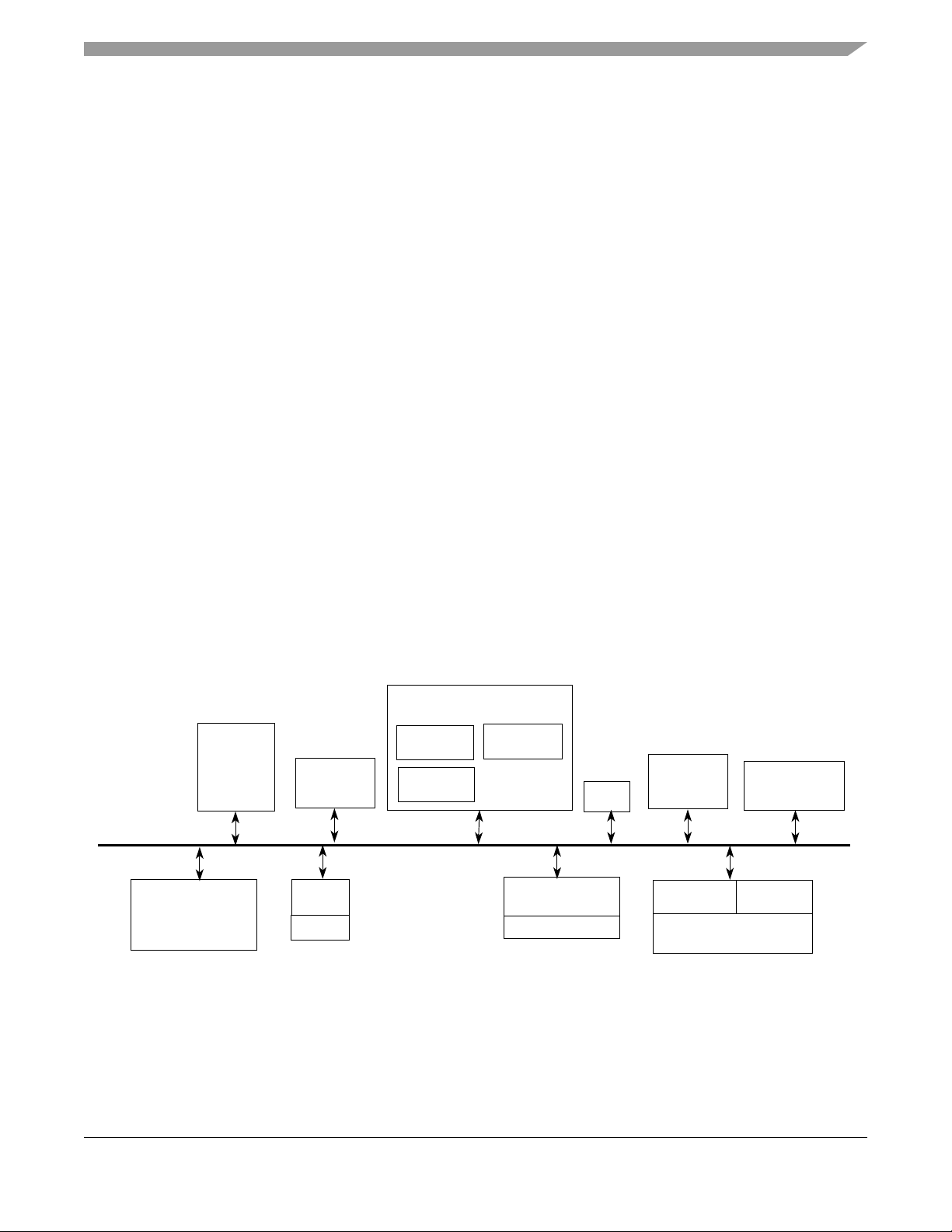

1-1 MPC8308 Block Diagram....................................................................................................... 1-1

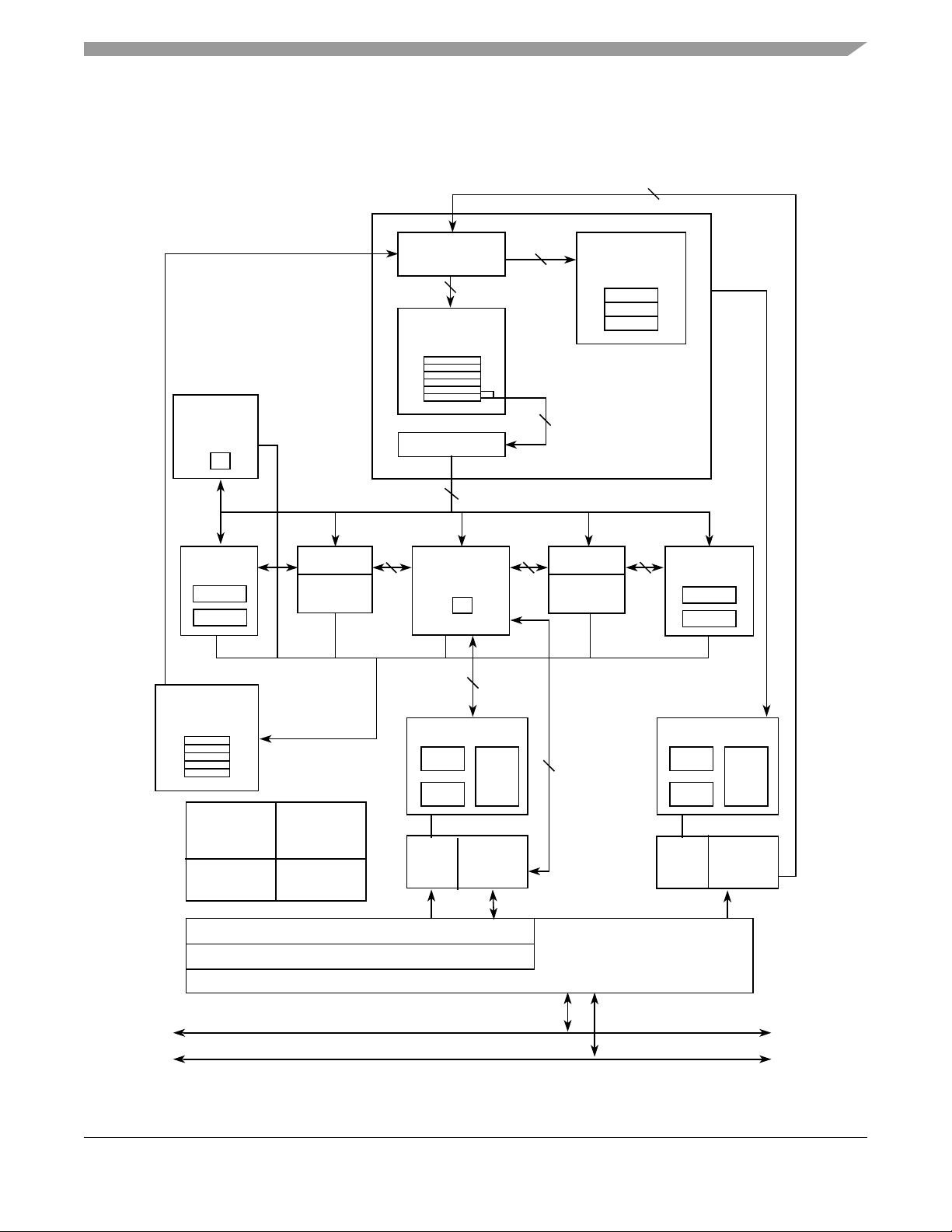

1-2 MPC8308 Integrated e300c3 Core Block Diagram................................................................ 1-9

1-3 USB Controllers Port Configuration..................................................................................... 1-12

2-1 MPC8308 Signal Groupings (1 of 2)...................................................................................... 2-2

2-2 MPC8308 Signal Groupings (2 of 2)...................................................................................... 2-3

4-1 Power-On Reset Flow............................................................................................................. 4-6

4-2 Hard Reset Flow...................................................................................................................... 4-7

4-3 Reset Configuration Word Low Register (RCWLR)............................................................ 4-10

4-4 Reset Configuration Word High Register (RCWHR)........................................................... 4-12

4-5 EEPROM Data Format for Reset Configuration Words Preload Command........................ 4-19

4-6 EEPROM Contents............................................................................................................... 4-20

4-7 Clock Subsystem Block Diagram ......................................................................................... 4-23

4-8 Reset Status Register (RSR)..................................................................................................4-26

4-9 Reset Mode Register (RMR)................................................................................................. 4-27

4-10 Reset Protection Register (RPR)........................................................................................... 4-28

4-11 Reset Control Register (RCR)............................................................................................... 4-28

4-12 Reset Control Enable Register (RCER)................................................................................4-29

4-13 System PLL Mode Register.................................................................................................. 4-30

4-14 Output Clock Control Register (OCCR)............................................................................... 4-31

4-15 System Clock Control Register (SCCR)............................................................................... 4-32

5-1 Local Memory Map Example ................................................................................................. 5-2

5-2 Internal Memory Map Registers’ Base Address Register (IMMRBAR)................................ 5-6

5-3 Alternate Configuration Base Address Register (ALTCBAR)............................................... 5-7

5-4 LBC Local Access Window n Base Address Registers (LBLAWBAR0–LBLAWBAR3).... 5-7

5-5 LBC Local Access Window n Attributes Registers (LBLAWAR0–LBLAWAR3) ................ 5-8

5-6 PCI Express 1 Local Access Window Base Address Register (PCIEXP1LAWBAR) ........... 5-9

5-7 PCI Express 1 Local Access Window Attributes Register (PCIEXP1LAWAR) .................. 5-10

5-8 DDR Local Access Window n Base Address Registers (DDRLAWBAR0–DDRLAWBAR1)...

5-11

5-9 DDR Local Access Window n Attributes Registers (DDRLAWAR0–DDRLAWAR1)....... 5-12

5-10 System General Purpose Register Low (SGPRL)................................................................. 5-16

5-11 System General Purpose Register High (SGPRH) ............................................................... 5-16

5-12 System Part and Revision ID Register (SPRIDR) ................................................................ 5-17

5-13 System Priority Configuration Register (SPCR) .................................................................. 5-18

5-14 System I/O Configuration Register Low (SICRL) ............................................................... 5-20

5-15 System I/O Configuration Register High (SICRH) .............................................................. 5-22

5-16 DDR Control Driver Register (DDRCDR)........................................................................... 5-27

5-17 DDR Debug Status Register (DDRDSR).............................................................................. 5-28

MPC8308 PowerQUICC II Pro Processor Reference Manual, Rev. 1

Freescale Semiconductor xix

Page 20

Figures

Figure

Number Title

Page

Number

5-18 PCI Express Controller Registers (PECR1).......................................................................... 5-29

5-19 eSDHC Control Register (SDHCCR)...................................................................................5-30

5-20 RTC Control Register (RTCCR)...........................................................................................5-32

5-21 Software Watchdog Timer High-Level Block Diagram ....................................................... 5-33

5-22 System Watchdog Control Register (SWCRR)..................................................................... 5-34

5-23 System Watchdog Count Register (SWCNR)....................................................................... 5-35

5-24 System Watchdog Service Register (SWSRR) ..................................................................... 5-36

5-25 Software Watchdog Timer Service State Diagram................................................................ 5-37