Page 1

Freescale Semiconductor, Inc.

M68HC12A4EVBUM/D

October 1999

..

.

nc

M68HC12A4EVB

T

O

R

,

A

R

EVALUATION BOARD

USER’S MANUAL

M

E SE

L

A

C

S

E

E

R

F

Y

B

D

E

V

I

H

C

C

U

D

N

O

C

I

.

C

N

I

Freescale Semiconductor, I

For More Information On This Product,

Go to: www.freescale.com

Page 2

Freescale Semiconductor, Inc.

Important Notice to Users

..

.

nc

While every effort has been made to ensure the accuracy of all information in

this document, Motorola assumes no liability to any party for any loss or

damage caused by errors or omissions or by statements of any kind in this

document, its updates, supplements, or special editions, whether such errors are

omissions orstatementsresultingfromnegligence, accident, or any other cause.

M

O

C

I

Motorola further assumes no liability arising out of the application or use of any

information,product, or system described herein: nor any liability for incidental

or consequential damages arising from the use of this document. Motorola

disclaims all warranties regarding the information contained herein, whether

R

E

E

S

expressed, implied, or statutory, including implied warranties of

merchantability or fitness for a particular purpose. Motorola makes no

representation that the interconnection of products in the manner described

herein will not infringe on existing or future patent rights, nor do the

descriptions contained herein imply the granting or license to make, use or sell

H

C

equipment constructed in accordance with this description.

R

A

Trademarks

D

E

V

I

This document includes these trademarks:

Motorola and the Motorola logo are registered trademarks

of Motorola, Inc.

MCUez is a trademark of Motorola, Inc.

F

Y

B

C

A

E SE

L

N

D

U

C

T

O

R

,

.

C

N

I

Freescale Semiconductor, I

© Motorola, Inc., 1999; All Rights Reserved

Apple, Macintosh, MacTerminal, and System 7 are registered

trademarks of Apple Computer, Inc.

Windows and Windows 95 are registered trademarks of Microsoft

Corporation in the U.S. and other countries.

Intel is a registered trademark of Intel Corporation.

Motorola, Inc., is an Equal Opportunity / Affirmative Action Employer.

For More Information On This Product,

Go to: www.freescale.com

Page 3

..

.

nc

Freescale Semiconductor, Inc.

User’s Manual — M68HC12A4EVB Evaluation Board

Section 1. General Information . . . . . . . . . . . . . . . . . . . .15

Section 2. Configuration and Setup . . . . . . . . . . . . . . . .27

Section 3. Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . .37

Section 4. Hardware Reference . . . . . . . . . . . . . . . . . . . .77

R

E

E

S

Appendix A. S-Record Format . . . . . . . . . . . . . . . . . . . .117

F

Appendix B. Communications Program Examples . . .123

D

E

Appendix C. D-Bug12 Startup Code . . . . . . . . . . . . . . .131

V

I

H

C

R

Appendix D. D-Bug12 Customization Data. . . . . . . . . .135

A

Y

B

C

A

E SE

L

M

C

I

O

N

D

U

Appendix E. Customizing the EPROMs . . . . . . . . . . . .141

Appendix F. SDI Configuration . . . . . . . . . . . . . . . . . . .143

Glossary. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .145

Index. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .149

List of Sections

.

C

N

I

,

R

O

T

C

Freescale Semiconductor, I

M68HC12A4EVB Evaluation Board — Rev. 1 User’s Manual

MOTOROLA List of Sections 3

For More Information On This Product,

Go to: www.freescale.com

Page 4

List of Sections

..

.

nc

A

R

Freescale Semiconductor, Inc.

E

V

I

H

C

D

O

C

I

M

E SE

L

A

C

S

E

E

R

F

Y

B

N

D

U

C

T

O

R

,

.

C

N

I

Freescale Semiconductor, I

User’s Manual M68HC12A4EVB Evaluation Board — Rev. 1

4 List of Sections MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Page 5

..

.

nc

Freescale Semiconductor, Inc.

User’s Manual — M68HC12A4EVB Evaluation Board

Section 1. General Information

1.1 Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

U

C

O

N

D

1.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

I

1.3 General Description and Features. . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

1.4 Performance Notes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

1.5 Functional Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

1.6 External Equipment Requirements. . . . . . . . . . . . . . . . . . . . . . . . . . . 22

E

1.7 EVB Specifications. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

V

I

H

C

1.8 Typographic Conventions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

R

A

1.9 Customer Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

D

Y

B

E

E

R

F

S

C

A

L

M

E SE

Section 2. Configuration and Setup

2.1 Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

2.2 Unpacking and Preparation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

2.3 EVB Configuration. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

Table of Contents

.

C

N

I

,

R

O

T

C

Freescale Semiconductor, I

M68HC12A4EVB Evaluation Board — Rev. 1 User’s Manual

MOTOROLA Table of Contents 5

2.4 EVB to Power Supply Connection . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

2.5 EVB to Terminal Connection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

2.6 Terminal Communications Setup . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

2.6.1 Communication Parameters. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

2.6.2 Dumb-Terminal Setup . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

2.6.3 Host-Computer Setup. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

2.6.4 Changing the Baud Rate . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

For More Information On This Product,

Go to: www.freescale.com

Page 6

Table of Contents

Freescale Semiconductor, Inc.

2.7 Using Fast External RAM. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

2.7.1 Selecting and Replacing the RAM Chips . . . . . . . . . . . . . . . . . . . 32

2.7.2 Reprogramming the RAM Chip Select . . . . . . . . . . . . . . . . . . . . . 33

Section 3. Operation

..

.

nc

Freescale Semiconductor, I

3.1 Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

3.2 Startup. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

3.3 Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

3.4 Program Abort . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

3.5 Using D-Bug12 Commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

E SE

S

C

A

L

3.6 D-Bug12 Command Set . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

A

R

C

H

ASM Assemble Instructions . . . . . . . . . . . . . . . . . . . . . 44

BAUD Set Baud Rate . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

Y

BF Block Fill. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

B

D

BR Breakpoint Set . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

E

V

I

BULK Bulk Erase On-Chip EEPROM . . . . . . . . . . . . . . 51

CALL Call Subroutine . . . . . . . . . . . . . . . . . . . . . . . . . . 52

G Go Execute a User Program . . . . . . . . . . . . . . . . 53

GT Go Till . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

HELP Onscreen Help Summary. . . . . . . . . . . . . . . . . . . 55

LOAD Load S-Record File . . . . . . . . . . . . . . . . . . . . . . . 56

MD Memory Display . . . . . . . . . . . . . . . . . . . . . . . . . 57

MDW Display Memory as 16-Bit Word . . . . . . . . . . . . 58

MM Memory Modify. . . . . . . . . . . . . . . . . . . . . . . . . . 59

MMW Modify 16-Bit Memory Word. . . . . . . . . . . . . . . 60

MOVE Move Memory Block. . . . . . . . . . . . . . . . . . . . . . 61

NOBR Remove Breakpoints . . . . . . . . . . . . . . . . . . . . . . 62

RD Register Display. . . . . . . . . . . . . . . . . . . . . . . . . . 63

RM Register Modify. . . . . . . . . . . . . . . . . . . . . . . . . . 64

T Trace . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

UPLOAD Display Memory in S-Record Format . . . . . . . . . 67

VERF Verify S-Record File Against Memory . . . . . . . . 68

<RegisterName> Modify Register Value . . . . . . . . . . . . . . . . . . . . 70

E

E

R

F

M

O

C

I

N

D

U

C

T

O

R

,

.

C

N

I

3.7 Alternate Execution from EEPROM . . . . . . . . . . . . . . . . . . . . . . . . . 72

User’s Manual M68HC12A4EVB Evaluation Board — Rev. 1

6 Table of Contents MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Page 7

..

.

nc

Freescale Semiconductor, Inc.

3.8 Off-Board Code Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

3.9 Memory Usage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

3.9.1 Description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

3.9.2 Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

3.10 Operational Limitations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

3.10.1 On-Chip RAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

3.10.2 SCI Port Usage. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

3.10.3 Dedicated MCU Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

3.10.4 Terminal Communications. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

4.1 Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

4.2 Printed Circuit Board (PCB) Description. . . . . . . . . . . . . . . . . . . . . . 78

4.3 Configuration Headers and Jumper Settings. . . . . . . . . . . . . . . . . . . . 78

4.4 Power Input Circuitry . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

E

V

I

4.5 Terminal Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

H

C

R

4.6 Microcontroller. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

A

4.7 Memory. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86

4.7.1 Memory Types and Sockets. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86

4.7.2 Chip Selects . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88

4.7.3 Glue Logic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

4.8 Clock Circuitry . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

4.9 Phase-Locked Loop (PLL) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

D

Table of Contents

.

C

N

I

,

R

O

T

C

U

D

N

M

O

C

I

Section 4. Hardware Reference

E SE

L

A

C

S

E

E

R

F

Y

B

Freescale Semiconductor, I

M68HC12A4EVB Evaluation Board — Rev. 1 User’s Manual

MOTOROLA Table of Contents 7

4.10 Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

4.11 Low-Voltage Inhibit (LVI). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

4.12 Analog-to-Digital (A/D) Converter . . . . . . . . . . . . . . . . . . . . . . . . . . 91

4.13 Background Debug Mode (BDM) Interface. . . . . . . . . . . . . . . . . . . . 91

4.14 Prototype Area . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

4.15 MCU Connectors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

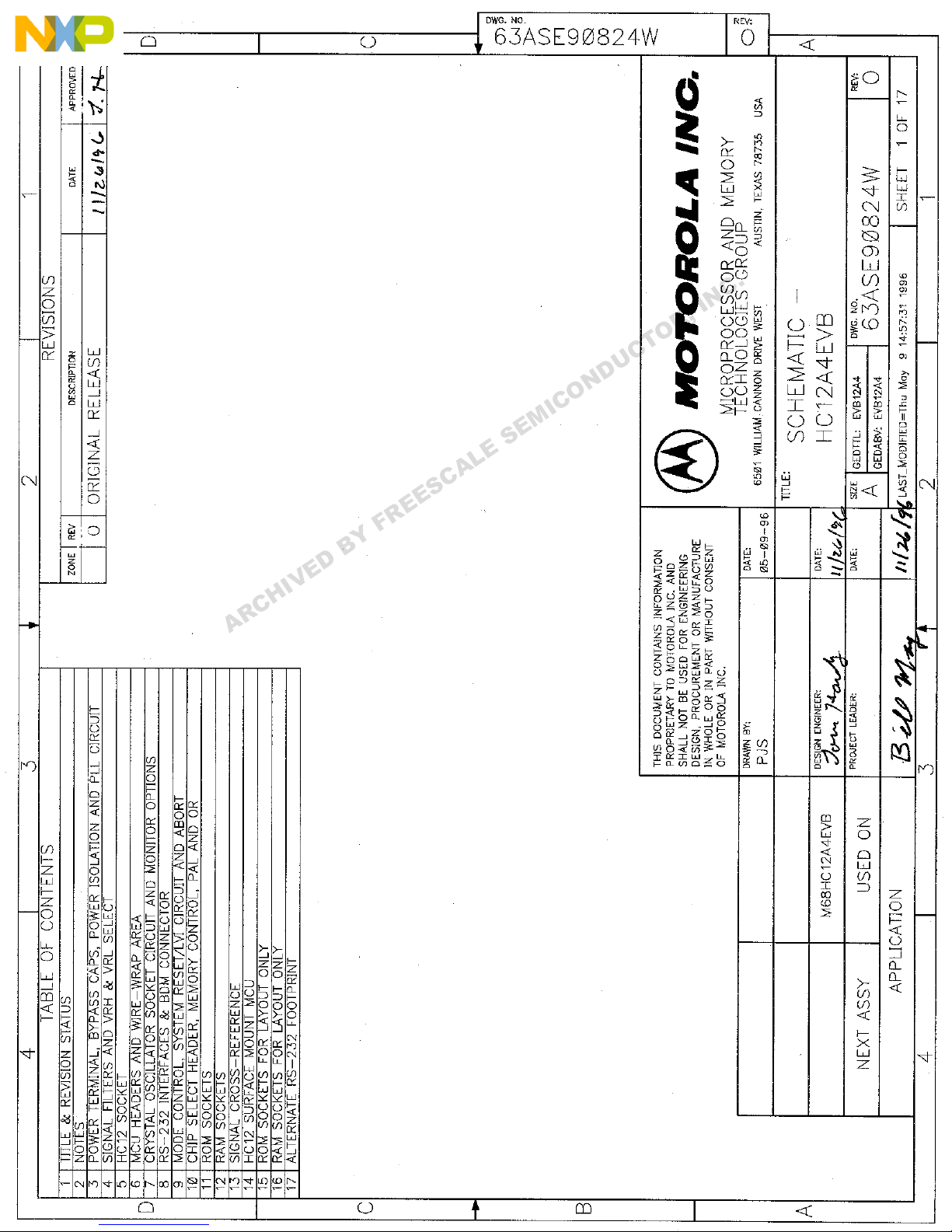

4.16 Schematics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

For More Information On This Product,

Go to: www.freescale.com

Page 8

Table of Contents

Freescale Semiconductor, Inc.

Appendix A. S-Record Format

A.1 Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 117

A.2 Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 117

A.3 S-Record Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 117

..

.

nc

Freescale Semiconductor, I

A.4 S-Record Types. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 119

,

C

T

O

R

A.5 S Record Creation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 120

O

N

D

U

A.6 S-Record Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 120

A.6.1 S0 Header Record . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 120

A.6.2 First S1 Record. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 121

A.6.3 S9 Termination Record . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 122

A.6.4 ASCII Characters. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 122

S

E

E

B

Y

R

F

Appendix B. Communications Program Examples

V

E

D

B.1 Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123

I

H

B.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124

C

R

A

B.3 Procomm for DOS — IBM PC. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124

B.3.1 Setup. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124

B.3.2 S-Record Transfers to EVB Memory. . . . . . . . . . . . . . . . . . . . . . 126

B.4 Kermit for DOS — IBM PC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 126

B.4.1 Setup. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 126

B.4.2 S-Record Transfers to EVB Memory. . . . . . . . . . . . . . . . . . . . . . 127

B.5 Kermit — Sun Workstation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 127

B.5.1 Setup. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 127

B.5.2 S-Record Transfers to EVB Memory. . . . . . . . . . . . . . . . . . . . . . 128

C

A

E SE

L

M

C

I

.

C

N

I

B.6 MacTerminal — Apple Macintosh . . . . . . . . . . . . . . . . . . . . . . . . . . 128

B.6.1 Setup. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 128

B.6.2 S-Record Transfers to EVB Memory. . . . . . . . . . . . . . . . . . . . . . 129

B.7 Red Ryder — Apple Macintosh . . . . . . . . . . . . . . . . . . . . . . . . . . . . 130

B.7.1 Setup. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 130

B.7.2 S-Record Transfers to EVB Memory. . . . . . . . . . . . . . . . . . . . . . 130

User’s Manual M68HC12A4EVB Evaluation Board — Rev. 1

8 Table of Contents MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Page 9

..

.

nc

Freescale Semiconductor, Inc.

Table of Contents

Appendix C. D-Bug12 Startup Code

Appendix D. D-Bug12 Customization Data

D.1 Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 135

D.2 Customization Data Area . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 135

D.2.1 C Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 136

T

O

R

,

D.2.2 Assembly Format. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 136

D.2.3 Initial User CPU Register Values . . . . . . . . . . . . . . . . . . . . . . . . 136

D.2.4 SysClk Field. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 137

D.2.5 IOBase Field . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 137

D.2.6 SCIBaudRegVal Field . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 137

D.2.7 EEBase and EESize Fields. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 138

D.2.8 EEPROM Erase/Program Delay Function Pointer Field. . . . . . . 138

D.2.9 Auxiliary Command Table Entries . . . . . . . . . . . . . . . . . . . . . . . 138

F

Y

B

Appendix E. Customizing the EPROMs

D

E

V

I

H

C

R

A

S

E

E

R

Appendix F. SDI Configuration

C

A

E SE

L

M

O

C

I

N

D

U

C

.

C

N

I

Glossary

Index

Freescale Semiconductor, I

M68HC12A4EVB Evaluation Board — Rev. 1 User’s Manual

MOTOROLA Table of Contents 9

For More Information On This Product,

Go to: www.freescale.com

Page 10

Table of Contents

..

.

nc

A

R

Freescale Semiconductor, Inc.

E

V

I

H

C

D

O

C

I

M

E SE

L

A

C

S

E

E

R

F

Y

B

N

D

U

C

T

O

R

,

.

C

N

I

Freescale Semiconductor, I

User’s Manual M68HC12A4EVB Evaluation Board — Rev. 1

10 Table of Contents MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Page 11

..

.

nc

Freescale Semiconductor, Inc.

User’s Manual — M68HC12A4EVB Evaluation Board

Figure Title Page

1-1 EVB Layout and Component Placement . . . . . . . . . . . . . . . . . . . . . . 18

1-2 System Block Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

C

I

2-1 EVB Power Connector J6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

L

A

E

E

S

C

4-1 Memory Sockets Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

4-2 Chip Select Header . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88

4-3 RAM/ROM Logic Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

V

E

D

4-4 Prototype Area (Component Side View) . . . . . . . . . . . . . . . . . . . . . . 93

4-5 MCU Connector J8 (Component-Side View). . . . . . . . . . . . . . . . . . . 94

I

H

C

4-6 MCU Connector J9 (Component-Side View). . . . . . . . . . . . . . . . . . . 95

R

A

B

Y

R

F

M

E SE

O

N

D

U

List of Figures

.

C

N

I

,

R

O

T

C

Freescale Semiconductor, I

M68HC12A4EVB Evaluation Board — Rev. 1 User’s Manual

MOTOROLA List of Figures 11

For More Information On This Product,

Go to: www.freescale.com

Page 12

List of Figures

..

.

nc

A

R

Freescale Semiconductor, Inc.

E

V

I

H

C

D

O

C

I

M

E SE

L

A

C

S

E

E

R

F

Y

B

N

D

U

C

T

O

R

,

.

C

N

I

Freescale Semiconductor, I

User’s Manual M68HC12A4EVB Evaluation Board — Rev. 1

12 List of Figures MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Page 13

..

.

nc

Freescale Semiconductor, I

Freescale Semiconductor, Inc.

User’s Manual — M68HC12A4EVB Evaluation Board

Table Title Page

1-1 EVB Specifications. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

2-1 RS-232C Interface Cabling. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

2-2 Communication Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

E SE

L

A

E

E

S

C

3-1 D-Bug12 Command-Set Summary . . . . . . . . . . . . . . . . . . . . . . . . . . 42

3-2 M68HC11 to CPU12 Instruction Translation. . . . . . . . . . . . . . . . . . . 45

3-3 CPU12 Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

V

E

D

3-4 Condition Code Register Bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

3-5 Factory-Configuration Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . 74

I

H

C

R

A

4-1 Jumper-Selectable Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

4-2 CPU Mode Selection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

4-3 EVB Memories Supplied . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88

4-4 BDM Connector J5 Pin Assignments. . . . . . . . . . . . . . . . . . . . . . . . . 92

4-5 MCU Connector J8 Pin Assignments . . . . . . . . . . . . . . . . . . . . . . . . 96

4-6 MCU Connector J9 Pin Assignments . . . . . . . . . . . . . . . . . . . . . . . . 98

A-1 S-Record Fields. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 118

A-2 S-Record Field Contents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 118

A-3 S-Record Types. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 119

A-4 S0 Header Record . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 120

A-5 S1 Header Record. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 121

A-6 S9 Header Record. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 122

B

Y

R

F

M

C

I

O

N

D

U

C

List of Tables

.

C

N

I

,

R

O

T

E-1 Physical EPROM Addresses. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 142

F-1 SDI Memory Map. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 144

M68HC12A4EVB Evaluation Board — Rev. 1 User’s Manual

MOTOROLA List of Tables 13

For More Information On This Product,

Go to: www.freescale.com

Page 14

List of Tables

..

.

nc

A

R

Freescale Semiconductor, Inc.

E

V

I

H

C

D

O

C

I

M

E SE

L

A

C

S

E

E

R

F

Y

B

N

D

U

C

T

O

R

,

.

C

N

I

Freescale Semiconductor, I

User’s Manual M68HC12A4EVB Evaluation Board — Rev. 1

14 List of Tables MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Page 15

User’s Manual — M68HC12A4EVB Evaluation Board

1.1 Contents

..

.

nc

1.2 Introduction

Freescale Semiconductor, I

Freescale Semiconductor, Inc.

Section 1. General Information

.

C

N

I

,

R

O

D

U

C

T

1.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

1.3 General Description and Features. . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

1.4 Performance Notes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

S

C

A

L

1.5 Functional Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

1.6 External Equipment Requirements. . . . . . . . . . . . . . . . . . . . . . . . . . . 22

D

Y

B

1.7 EVB Specifications. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

E

1.8 Typographic Conventions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

V

I

H

C

R

1.9 Customer Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

A

This user’s manual provides the necessary information for using the

M68HC12A4EVB evaluation board (EVB), an evaluation, debugging, and

code-generation tool for the MC68HC812A4 microcontroller units (MCU).

Reference items, such as schematic diagrams and parts lists, are shipped as part

of the EVB package.

E

E

R

F

M

E SE

N

O

C

I

1.3 General Description and Features

The EVB is an economical tool for designing and debugging code for and

evaluating the operation of the M68HC12 MCU Family. By providing the

essential MCU timing and input/output (I/O) circuitry, the EVB simplifies user

evaluation of prototype hardware and software.

M68HC12A4EVB Evaluation Board — Rev. 1 User’s Manual

MOTOROLA General Information 15

For More Information On This Product,

Go to: www.freescale.com

Page 16

General Information

..

.

nc

Freescale Semiconductor, I

Freescale Semiconductor, Inc.

The board consists of an 8-inch by 8-inch multi-layer printed circuit board

(PCB) that provides the platform for interface and power connections to the

MC68HC812A4 MCU chip, which is installed in a production socket.

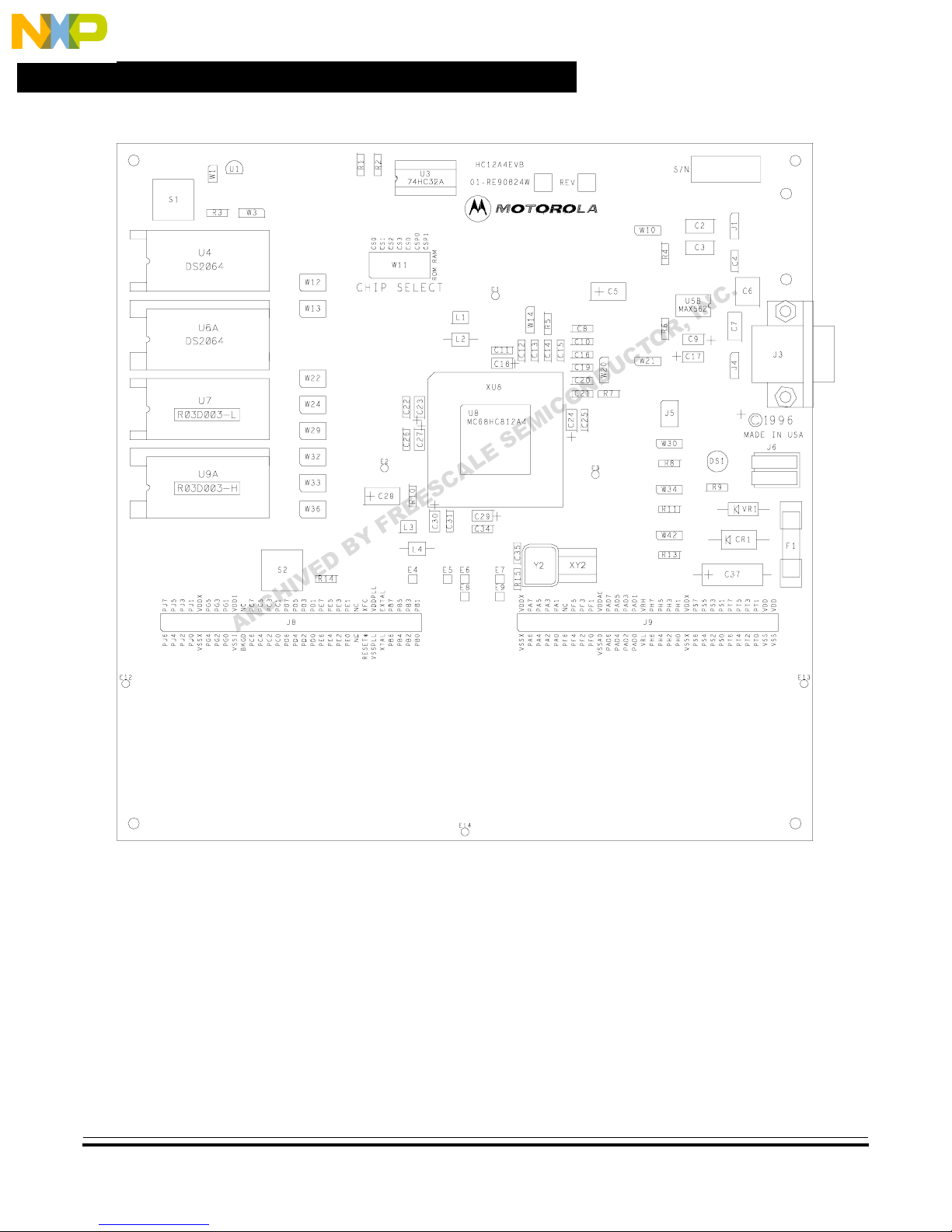

Figure 1-1 shows the EVB’s layout and locations of the major components, as

viewed from the component side of the board.

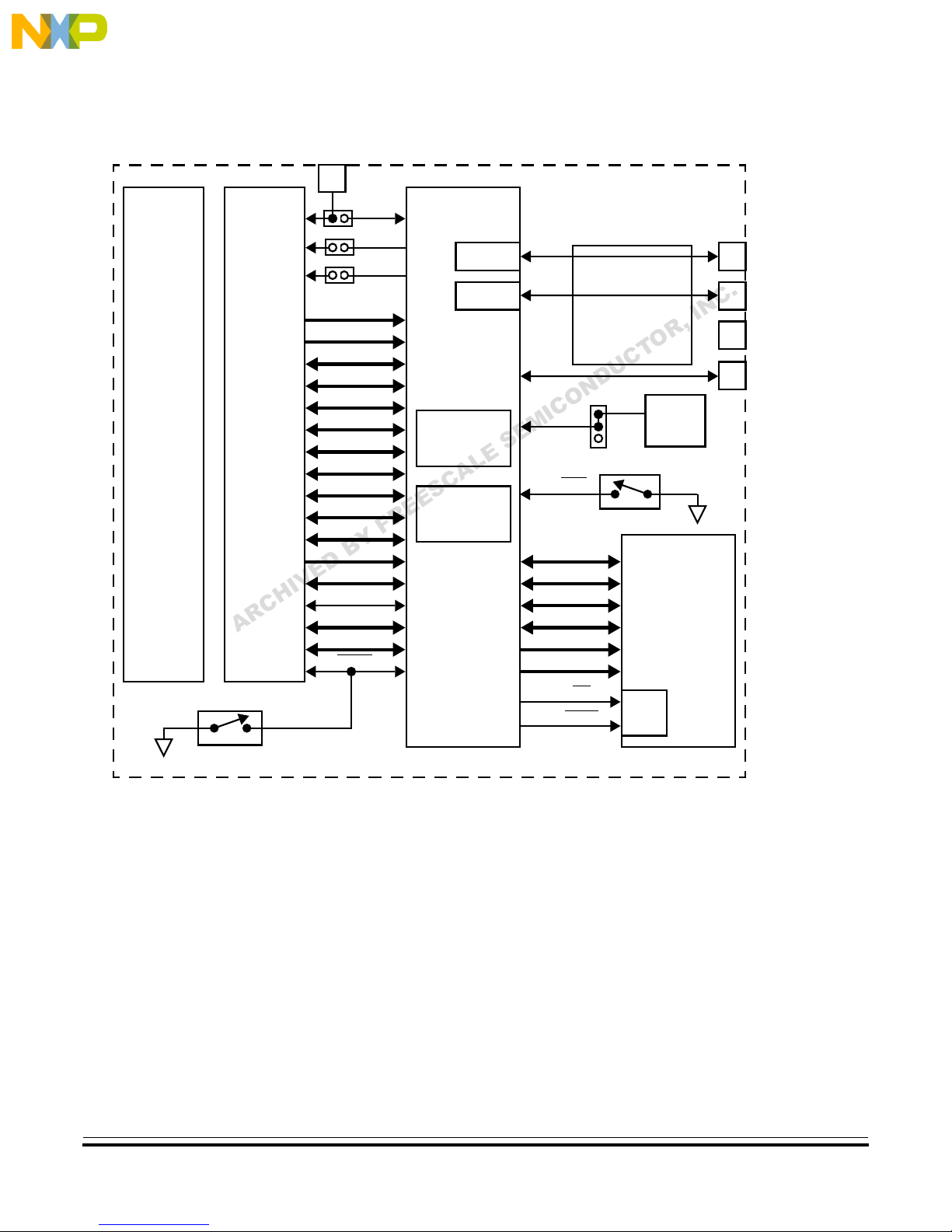

The block diagram in Figure 1-2 depicts the logical relationships and

interconnections within the EVB and with external equipment.

Hardware features of the EVB include:

• Power, ground, and four signal planes

• Single-supply +3- to +5-Vdc power input (J6)

• Two RS-232C interfaces

• Two memory sockets populated with two 32-Kbyte x 8-bit EPROMs

• Two memory sockets populated with two 8-Kbyte x 8-bit SRAMs

E

V

I

H

C

A

R

• Support for up to 1 MByte of program space and 512 Kbytes of data

• 16-MHz crystal-controlled clock oscillator (Y2) in a socket that can

• Headers for jumper selection of hardware options (for full details of the

.

C

N

I

,

R

O

T

C

U

D

N

O

C

I

M

E SE

L

A

C

S

E

E

B

Y

R

F

(U7 and U9A), containing the D-Bug12 monitor program

D

(U4 and U6A)

space using optional memory configurations

accommodate optional 8- or 14-pin oscillator chips (XY2)

jumper settings, refer to Table 4-1):

– Low-voltage inhibit (LVI) (W1)

– RAM (random-access memory) write-protection (W3)

– MCU chip selects for memory devices (W11)

User’s Manual M68HC12A4EVB Evaluation Board — Rev. 1

16 General Information MOTOROLA

– RAM function select (W12 and W13)

– ROM (read-only memory) function select (W22, W24, W29, W32,

W33, and W36)

– MCU mode control (W30, W34, and W42)

– Alternate execution from on-chip EEPROM (W20)

– Serial communications interface (SCI) configuration (W10, W14,

and W21)

For More Information On This Product,

Go to: www.freescale.com

Page 17

..

.

nc

Freescale Semiconductor, Inc.

• Two 2-row x 30-pin header connectors for access to the MCU’s I/O and

• Prototype expansion area for customized interfacing with the MCU

• Low-profile reset (S1) and program-abort (S2) push-button switches

• LVI protection (U1)

• Light-emitting diode (LED) power-on indicator (DS1)

• Test points for ground connections around the board (E1, E2, E3, E12,

• 2-row x 3-pin header (J5) provides a connector for using background

• Phase-locked loop (PLL) biasing circuitry for altering the MCU’s

Firmware features include:

• D-Bug12 monitor/debugger program, resident in external EPROM

E

V

I

H

C

A

R

• Full support for either dumb-terminal or host-computer terminal

• Single-line assembler/disassembler

• File transfer capability from a host computer, allowing off-board code

bus lines (J8 and J9)

E13, and E14)

debug development tools such as the serial debug interface (SDI)

timebase

F

Y

B

D

(erasable programmable read-only memory)

interface

generation

R

E

E

S

C

A

E SE

L

M

General Information

General Description and Features

.

C

N

I

,

R

O

T

C

U

D

N

O

C

I

Freescale Semiconductor, I

M68HC12A4EVB Evaluation Board — Rev. 1 User’s Manual

MOTOROLA General Information 17

For More Information On This Product,

Go to: www.freescale.com

Page 18

General Information

..

.

nc

A

R

Freescale Semiconductor, Inc.

E

V

I

H

C

D

O

C

I

M

E SE

L

A

C

S

E

E

R

F

Y

B

PROTOTYPE AREA

N

D

U

C

T

O

R

,

.

C

N

I

Freescale Semiconductor, I

Figure 1-1. EVB Layout and Component Placement

User’s Manual M68HC12A4EVB Evaluation Board — Rev. 1

18 General Information MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Page 19

..

.

nc

PROTO-

TYPE

AREA

EXTERNAL CLOCK

J8 / J9

H

C

R

A

S1 RESET

Freescale Semiconductor, Inc.

J7

E

V

I

EXTAL

XTAL

XFC

/6

V

DD

VSS/6

PA [7:0]

PB [7:0]

PC [7:0]

PD [7:0]

PE [7:0]

PF [6:0]

PG [5:0]

PH [7:0]

PJ [7:0]

Y

PAD [7:0]

B

D

, V

V

RH

BKGD

PS [7:0]

PT [7:0]

RESET

RL

F

MC68HC812A4

E

E

R

MCU

ON-CHIP

EEPROM

A

C

S

ON-CHIP

RAM

112 PINS

TOTAL

SCI0

SCI1

E SE

L

BKGD

O

C

EXTAL

I

M

PE0/XIRQ

PA [7:0]

PB [7:0]

PC [7:0]

PD [7:0]

PE [6:0]

PG [5:0]

PE2/RW

PE3/LSTRB

M68HC12A4EVB

RS-232C

TRANSCEIVER

C

U

D

N

S2 – PROGRAM ABORT

GLUE

LOGIC

Figure 1-2. System Block Diagram

,

R

O

T

CLOCK

EXTERNAL

ROM

AND

RAM

General Information

Performance Notes

J3

TERMINAL

.

J2

SPARE

C

N

I

J6

POWER

J5

BDM INTERFACE

Freescale Semiconductor, I

1.4 Performance Notes

The M68HC12A4EVB’s external RAM memory chips, U4 and U6A, were

chosen to emphasize the EVB’s low-voltage and low-power operational

capability over the range of +3.5 to +5.0 Vdc.

However, these parts are not fast enough to operate at the 16-MHz speed of the

factory-supplied clock oscillator. To use them at this external clock speed, the

D-Bug12 startup code programs the MCU’s RAM chip select to insert one wait

state into each access of external RAM. Thus, when programs are run from

M68HC12A4EVB Evaluation Board — Rev. 1 User’s Manual

MOTOROLA General Information 19

For More Information On This Product,

Go to: www.freescale.com

Page 20

General Information

..

.

nc

NOTE:

1.5 Functional Overview

Freescale Semiconductor, I

Freescale Semiconductor, Inc.

external RAM, performance is approximately 40 percent slower than it would

be if the RAM chips were fast enough to run without wait states. Typical

software performance improvements of 80 to 95 percent can be realized with

faster external RAM.

For high-speed performance, the factory-supplied RAM devices may be

replaced with faster parts that allow programs to execute at the full external

clock speed. Two steps are required for this:

1. Replace the RAM devices, U4 and U6A, with faster parts.

2. Modify the RAM chip select to eliminate the wait state (E-clock stretch).

Detailed instructions for these procedures are found in 2.7 Using Fast External

RAM.

Programsthat execute exclusively from theMCU’s on-chip RAM and EEPROM

alwaysrun at the fullclock speed. No wait states are introduced when accessing

these areas.

Table 3-5. Factory-Configuration Memory Map, the default memory map,

E

V

I

depicts the addresses of the EVB’s different memory areas.

H

C

R

A

The EVB is factory-configured to execute D-Bug12, the EPROM-resident

monitor program, without further configuration by the user. It is ready for use

with an RS-232C terminal for writing and debugging user code. Follow the

setup instructions in Section 2. Configuration and Setup to prepare for

operation.

Optionally, the EVB can accommodate various types and configurations of

external memory to suit a particular application’s requirements. These custom

configurations are made by installing the appropriate memory chips in the

EVB’s memory sockets and by setting jumpers on the EVB to correctly

establish the MC68HC812A4’s memory-access operations. Table 1-1 lists the

allowable sizes and types of memory. For the correct jumper settings, refer to

4.3 Configuration Headers and Jumper Settings.

D

.

C

N

I

,

R

O

T

C

U

D

N

O

C

I

M

E SE

L

A

C

S

E

E

R

F

Y

B

NOTE:

User’s Manual M68HC12A4EVB Evaluation Board — Rev. 1

20 General Information MOTOROLA

The D-Bug12 operating instructions in this manual presume the factory-default

memory configuration. Other configurations require different

operating-software arrangements.

For More Information On This Product,

Go to: www.freescale.com

Page 21

..

.

nc

NOTE:

A

Freescale Semiconductor, Inc.

The MC68HC812A4’s two serial communications interface (SCI) ports are

associated with separate RS-232C interfaces. D-Bug12 uses one of the SCIs for

communications with the user terminal (jumper-selectable, SCI0 by default).

The second SCI port is available for user applications. For information on the

ports and their connectors, refer to 2.5 EVB to Terminal Connection and 4.5

Terminal Interface.

If the MCU’s single-wire background debug mode (BDM) interface serves as

the user interface, both of the SCI ports become available for user applications.

This mode requires a background debug development tool, such as Motorola’s

serial debug interface (SDI), and a host computer with the appropriate interface

software. For more information, refer to Appendix F. SDI Configuration and

tothe Serial Debug Interface User’s Manual, Motoroladocument order number

SDIUM/D.

D-Bug12 does not use the BDM interface.

Two methods may be used to generate EVB user code:

E

• For small programs or subroutines, D-Bug12’s single-line

V

I

H

C

R

• For larger programs, the Motorola MCUez assembler may be used on

The EVB features a prototype area, which allows custom interfacing with the

MCU’s I/O and bus lines. These connections are broken out via headers J8 and

J9, which are immediately adjacent to the prototype area as shown in

Figure 1-1.

General Information

Functional Overview

.

C

N

I

,

R

O

T

C

U

D

N

O

C

I

M

E SE

L

A

C

S

E

E

R

F

Y

B

D

assembler/disassembler may be used to place object code directly into

the EVB’s memory.

a host computer to generate S-record object files, which then can be

loaded into the EVB’s memory using D-Bug12’s LOAD command.

Freescale Semiconductor, I

M68HC12A4EVB Evaluation Board — Rev. 1 User’s Manual

MOTOROLA General Information 21

An on-board push-button switch, S1, provides for resetting the EVB hardware

and restarting D-Bug12. Another on-board switch, S2, allows aborting the

execution of a user program, useful in regaining control of a runaway program.

Both of these switch functions are available for customized use in the prototype

area.

The EVB can begin operation in either of two jumper-selectable (W20) modes

at reset. In normal mode, D-Bug12 immediately issues its command prompt on

the terminal display and waits for a user entry. In the alternate mode, execution

For More Information On This Product,

Go to: www.freescale.com

Page 22

General Information

Freescale Semiconductor, Inc.

begins directly with the user code in on-chip EEPROM. This hardware function

is also available for customized use in the prototype area.

D-Bug12 allows programming of the MC68HC812A4’s on-chip EEPROM

through commands that directly alter memory. For full details of all the

commands, refer to 3.6 D-Bug12 Command Set.

Because the MCU must manage the EVB hardware and execute D-Bug12 in

addition to serving as the user-application processor, there are a few restrictions

on its use. For more information, refer to 3.10 Operational Limitations.

1.6 External Equipment Requirements

..

.

nc

NOTE:

Freescale Semiconductor, I

In addition to the EVB, the following user-supplied external equipment is

required:

• Power supply — See Table 1-1 for voltage and current requirements.

Table 1-1 indicates that EVB operation at +3.0 Vdc requires the slower clock

speed of 8 MHz. This limitation applies to programs (including the operating

firmware, D-Bug12) that use external memory.

If an application program uses on-chip RAM and EEPROM exclusively — for

H

C

instance, if external memory is not used — the clock speed can remain at

R

A

16 MHz with a supply voltage of +3.0 Vdc.

D

E

V

I

• User terminal — Options:

Y

B

– RS-232C dumb terminal — Allows single-line on-board code

assembly and disassembly

– Host computer with RS-232C serial port — Allows off-board code

assembly that can be loaded into the EVB’s memory. Requires a

user-supplied communications program capable of emulating a

dumb terminal. Examples of acceptable communications programs

are given in Appendix B. Communications Program Examples.

F

R

E

E

S

C

A

E SE

L

M

.

C

N

I

,

R

O

T

C

U

D

N

O

C

I

• Power-supply and terminal interconnection cables as required

For full details of equipment setup, cabling, and special requirements, refer to

Section 2. Configuration and Setup.

User’s Manual M68HC12A4EVB Evaluation Board — Rev. 1

22 General Information MOTOROLA

– Host computer using the MCU’s BDM (background debug mode)

interface — Frees both of the MCU’s SCI ports for user applications.

Requires a background debug development tool, such as the

Motorola serial debug interface (SDI), and the appropriate interface

software

For More Information On This Product,

Go to: www.freescale.com

Page 23

Freescale Semiconductor, Inc.

1.7 EVB Specifications

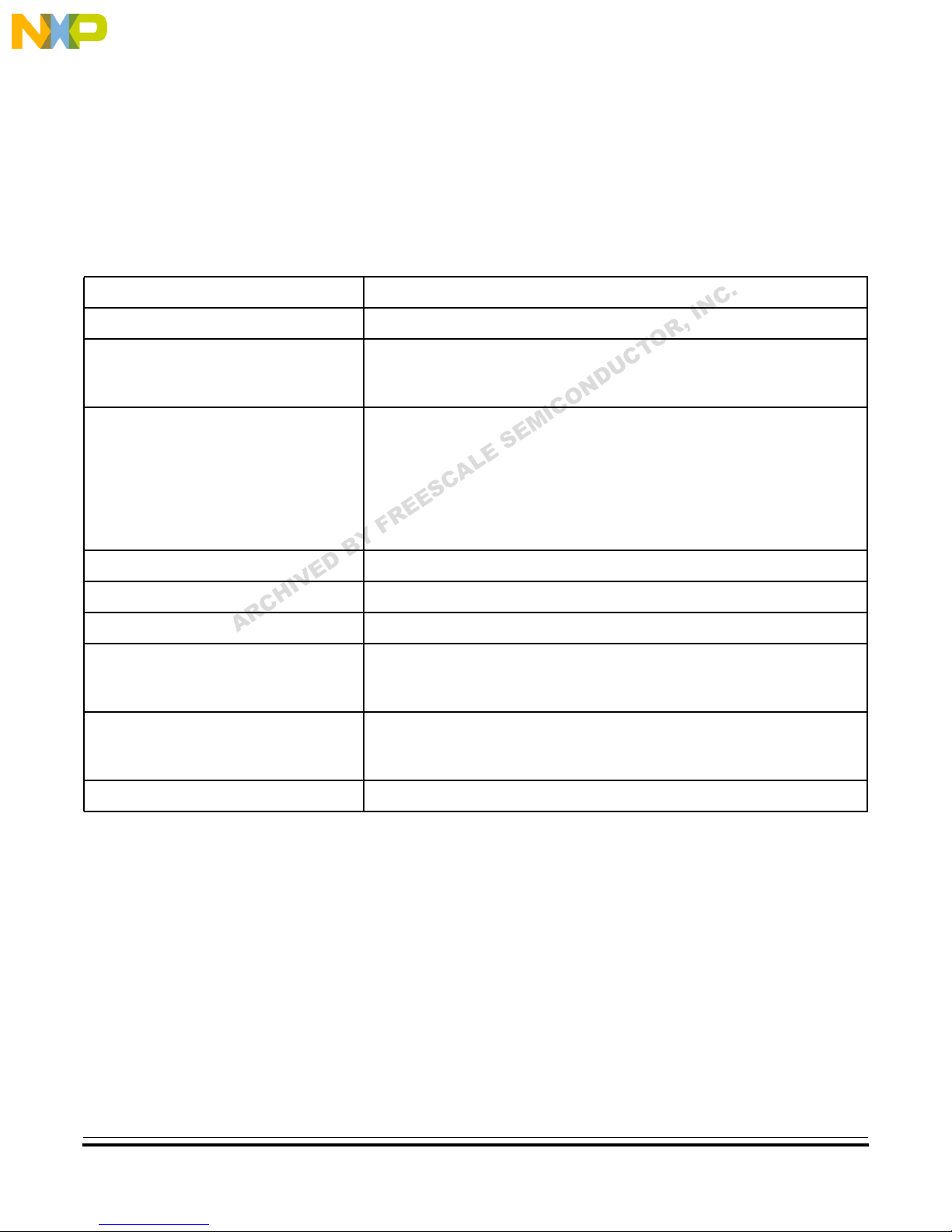

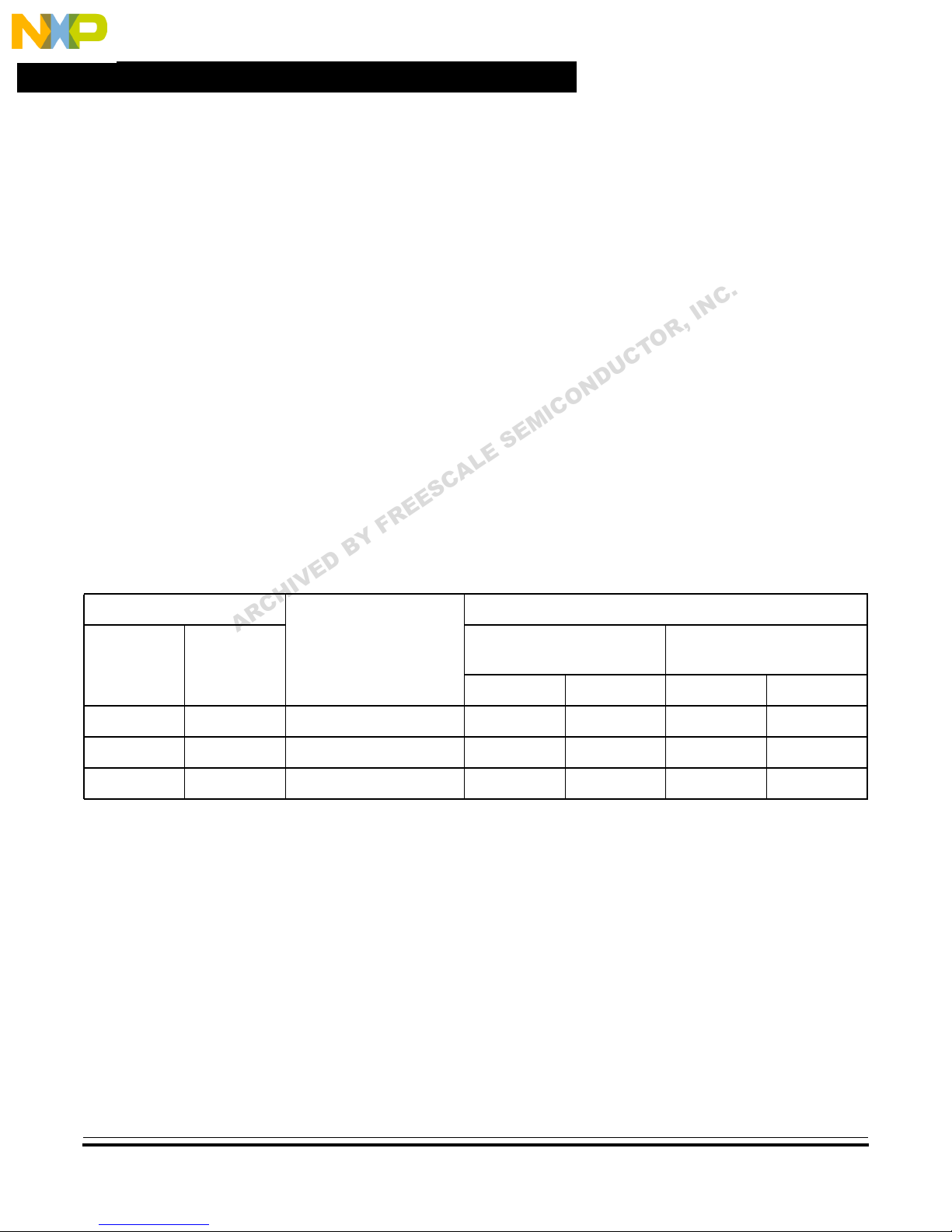

Table 1-1 lists the EVB specifications.

General Information

EVB Specifications

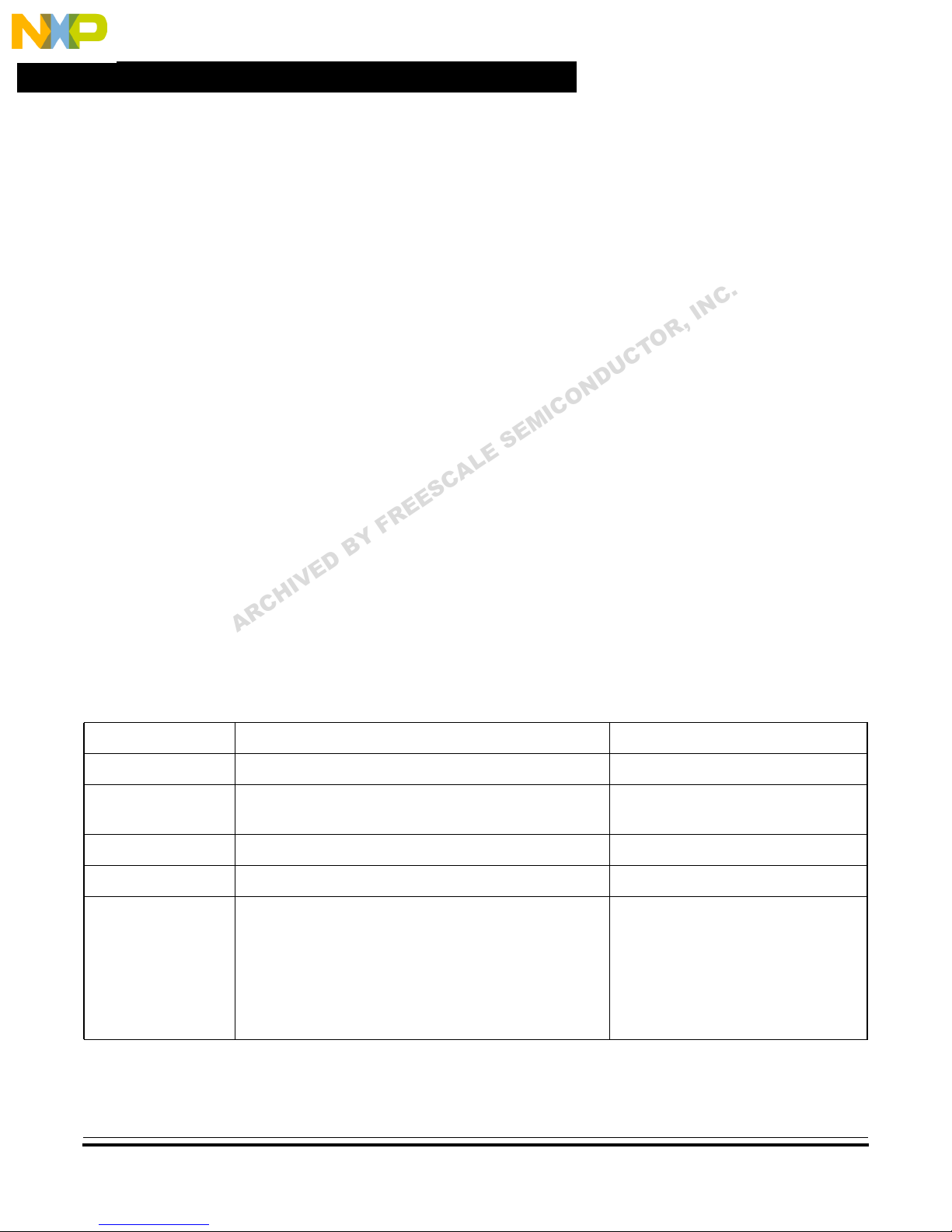

Table 1-1. EVB Specifications

..

.

nc

Characteristic Specifications

MCU MC68HC812A4

SRAM maximum memory:

Wide mode

Narrow mode

ROM maximum memory:

EPROM:

Wide mode

Narrow mode

EEPROM:

Wide mode

Narrow mode

MCU I/O ports HCMOS compatible

Background debug mode interface 2-row x 3-pin header

Communications ports Two RS-232C DCE ports

Power requirements:

16-MHz clock source

8-MHz clock source

Prototype area:

Area

Holes

Board dimensions 8 inches x 8 inches

A

R

C

H

E

V

I

16, 64, 256, or 1024 Kbytes

8, 32, 128, or 512 Kbytes

M

C

A

E SE

L

64, 128, 256, 512, or 1024 Kbytes

32, 64, 128, 256, or 512 Kbytes

S

E

E

64, 128, 256, or 512 Kbytes

R

F

32, 64, 128, or 256 Kbytes

Y

B

D

+3.5 to +5.0 Vdc @ 150 mA (max.), fuse-protected @ 1.5 A

+3.0 to +5.0 Vdc @ 150 mA (max.), fuse-protected @ 1.5 A

2 inches x 8 inches, approximately

79 wide x 20 high (0.1-inch centers)

.

C

N

I

,

R

O

T

C

U

D

N

O

C

I

Freescale Semiconductor, I

M68HC12A4EVB Evaluation Board — Rev. 1 User’s Manual

MOTOROLA General Information 23

For More Information On This Product,

Go to: www.freescale.com

Page 24

General Information

1.8 Typographic Conventions

This user’s manual uses special typographical conventions to enhance

readability. They are:

..

.

nc

H

C

R

A

Freescale Semiconductor, I

Freescale Semiconductor, Inc.

• Code, statements, confirmations, data entry, field text, parameters, and

• When arguments in code are italicized, they are placeholders for values

E

V

• In code, the user’s entry is underlined. This underlining does not actually

I

• Window names and parts of windows are indicated in initial caps, unless

strings are indicated in regular Courier:

.

,

C

N

I

$INCLUDE

“INIT.AS”

This option displays an Exit Application confirmation message.

This new filename replaces the [NONAME#1] in the title bar.

%FILE%

E SE

L

A

C

R

E

E

S

to be entered by the user:

<

n

>

F

Y

B

<argument>

D

appear onscreen.

A typical example looks like this:

>

baud 9600 User’s entry

Change Terminal BR, D-Bug12’s response

Press Return

> D-Bug12 prompt for next entry

the name of the window is capitalized in a unique way:

Memory and Code windows

M

C

I

O

N

D

U

C

T

O

R

• For usage in this manual, filenames are not case sensitive. But for

User’s Manual M68HC12A4EVB Evaluation Board — Rev. 1

24 General Information MOTOROLA

CASM08W window

WinIDE main window

consistency, they will always appear in all capital letters:

SETUP.EXE

MAP file

For More Information On This Product,

Go to: www.freescale.com

Page 25

Freescale Semiconductor, Inc.

• Buttons, icons, functions, and keyboard keys are indicated in small caps:

General Information

Customer Support

..

.

nc

1.9 Customer Support

Press the

Type

The

• Commands are not case sensitive. But for consistency, they will always

appear in all capital letters, unless they contain some peculiarity:

INPUTx

UNDO

LOADMAP

• Menu names, options, and tabs, and dialog, edit, text, and lists boxes are

indicated in Times bold:

Do this by checking the Main File option in the Environment

Settings dialog’s General Options tab.

F

Y

Open the Open File dialog.

B

D

E

V

I

H

C

R

A

To obtain information about technical support or ordering parts, call the

Motorola help desk at 800-521-6274.

Select the filename in the File Name list, and use the filename in the

Main filename edit box.

ENTER key.

CTRL + N or click on the NEW toolbar button.

RESET function is an input and output.

I

,

R

O

T

C

U

D

N

O

C

I

M

E SE

L

A

C

S

E

E

R

N

C

.

Freescale Semiconductor, I

M68HC12A4EVB Evaluation Board — Rev. 1 User’s Manual

MOTOROLA General Information 25

For More Information On This Product,

Go to: www.freescale.com

Page 26

General Information

..

.

nc

A

R

Freescale Semiconductor, Inc.

E

V

I

H

C

D

O

C

I

M

E SE

L

A

C

S

E

E

R

F

Y

B

N

D

U

C

T

O

R

,

.

C

N

I

Freescale Semiconductor, I

User’s Manual M68HC12A4EVB Evaluation Board — Rev. 1

26 General Information MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Page 27

Freescale Semiconductor, Inc.

User’s Manual — M68HC12A4EVB Evaluation Board

2.1 Contents

2.2 Unpacking and Preparation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

..

.

nc

2.3 EVB Configuration. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

2.4 EVB to Power Supply Connection . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

2.5 EVB to Terminal Connection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

2.6 Terminal Communications Setup . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

2.6.1 Communication Parameters. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

2.6.2 Dumb-Terminal Setup . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

2.6.3 Host-Computer Setup. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

V

I

H

2.6.4 Changing the Baud Rate . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

C

R

A

2.7 Using Fast External RAM. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

2.7.1 Selecting and Replacing the RAM Chips . . . . . . . . . . . . . . . . . . . 32

2.7.2 Reprogramming the RAM Chip Select . . . . . . . . . . . . . . . . . . . . . 33

2.2 Unpacking and Preparation

Before beginning configuration and setup of the EVB:

Freescale Semiconductor, I

1. Verify that these items are present in the EVB package:

Section 2. Configuration and Setup

C

I

M

E SE

L

A

C

S

E

E

R

F

Y

B

D

E

• M68HC12A4EVB board assembly

O

N

D

U

C

T

O

R

,

.

C

N

I

M68HC12A4EVB Evaluation Board — Rev. 1 User’s Manual

MOTOROLA Configuration and Setup 27

• Warranty and registration cards

• EVB schematic diagram and parts list

• M68HC12A4EVB User’s Manual

• MC68HC812A4 Technical Summary

• CPU12 Reference Manual

For More Information On This Product,

Go to: www.freescale.com

Page 28

Freescale Semiconductor, Inc.

Configuration and Setup

• MC68HC12 Family Brochure

• Using D-Bug12 Callable Routines

• Demo software

• Assembly language development toolset

..

.

nc

2.3 EVB Configuration

Freescale Semiconductor, I

2. Remove the EVB from its anti-static shipping bag.

3. Carefully remove the protective case and conductive foam that cover the

MCU and its socket during shipment.

C

U

C

O

N

D

4. Save all packing materials for storing and shipping the EVB.

5. Inspect the alignment of the MCU’s pins within its socket. If it appears

necessary to reseat the MCU:

E SE

L

E

S

C

A

a. Press down on two opposite sides of the MCU socket.

b. Gently press the MCU chip into place.

c. Release the MCU socket.

B

D

E

6. Verify that all other socketed parts are correctly seated.

V

I

H

C

R

A

Becausethe EVB has been factory-configuredto operate withD-Bug12, it is not

necessary to change any of the jumper settings to begin operating immediately.

Only one jumper (header W20) should be changed during the course of

factory-default EVB operation with D-Bug12:

• Pins 2 and 3 jumpered (default) — Normal execution mode. D-Bug12 is

executed from external EPROM upon reset. The D-Bug12 prompt

appears immediately on the terminal display.

Y

E

R

F

M

I

T

O

R

,

.

C

N

I

• Pins 1 and 2 jumpered — Alternate execution mode. User code is

Other jumper settings affect the hardware setup and/or MCU operational

modes. For an overview of all jumper-selectable functions, refer to 1.3 General

Description and Features. For details of the settings, see Table 4-1.

Jumper-Selectable Functions.

User’s Manual M68HC12A4EVB Evaluation Board — Rev. 1

28 Configuration and Setup MOTOROLA

executedfrom on-chip EEPROMupon reset. For more information, refer

to 3.7 Alternate Execution from EEPROM.

For More Information On This Product,

Go to: www.freescale.com

Page 29

Freescale Semiconductor, Inc.

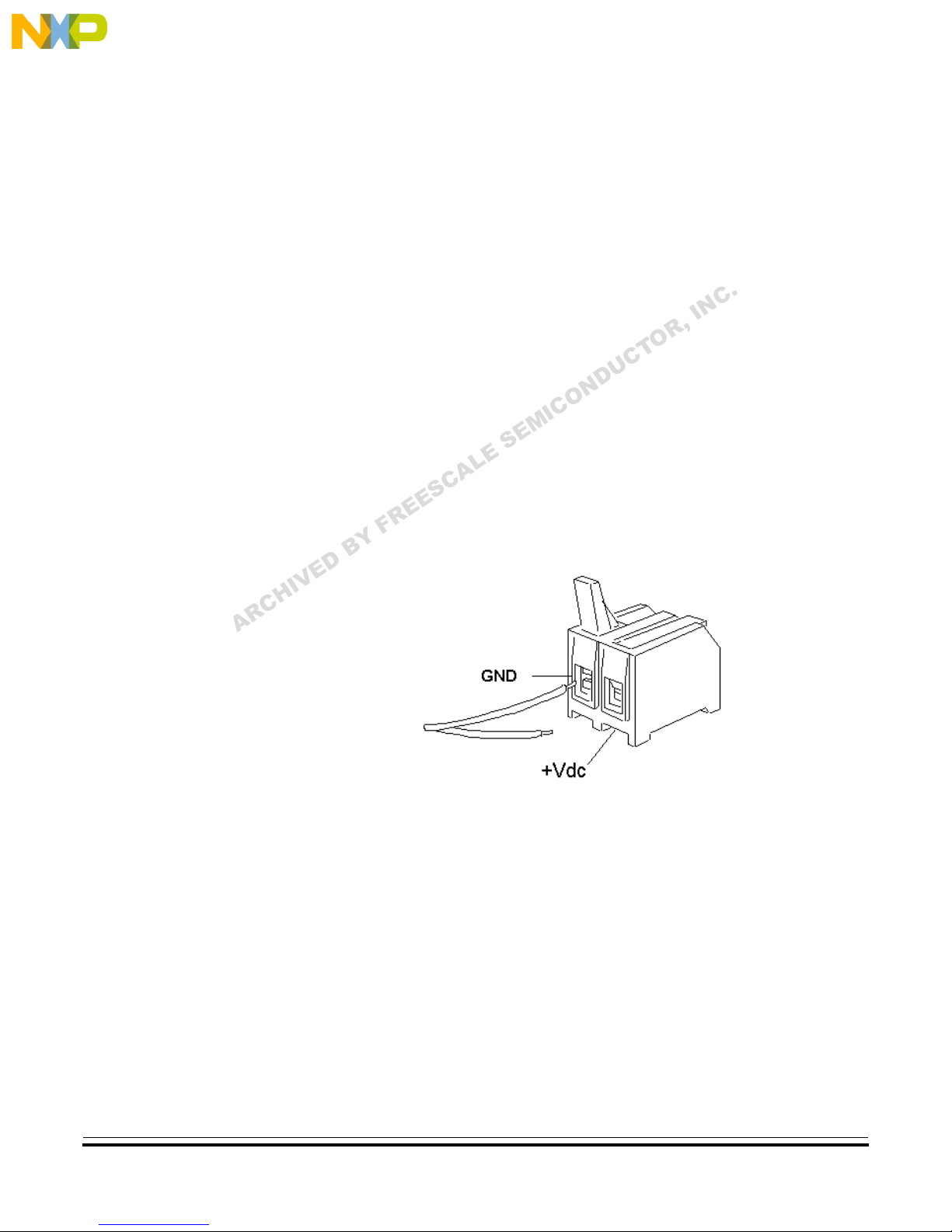

2.4 EVB to Power Supply Connection

The EVB requires a user-provided external power supply. See Table 1-1. EVB

Specifications for the voltage and current specifications. For full details of the

EVB’s power-input circuitry, refer to 4.4 Power Input Circuitry.

Configuration and Setup

EVB to Power Supply Connection

..

.

nc

CAUTION:

A

Although fuse protection is built into the EVB, a power supply with

current-limiting capability is desirable. If this feature is available on the power

T

O

R

,

supply, set it to 200 mA.

N

D

U

C

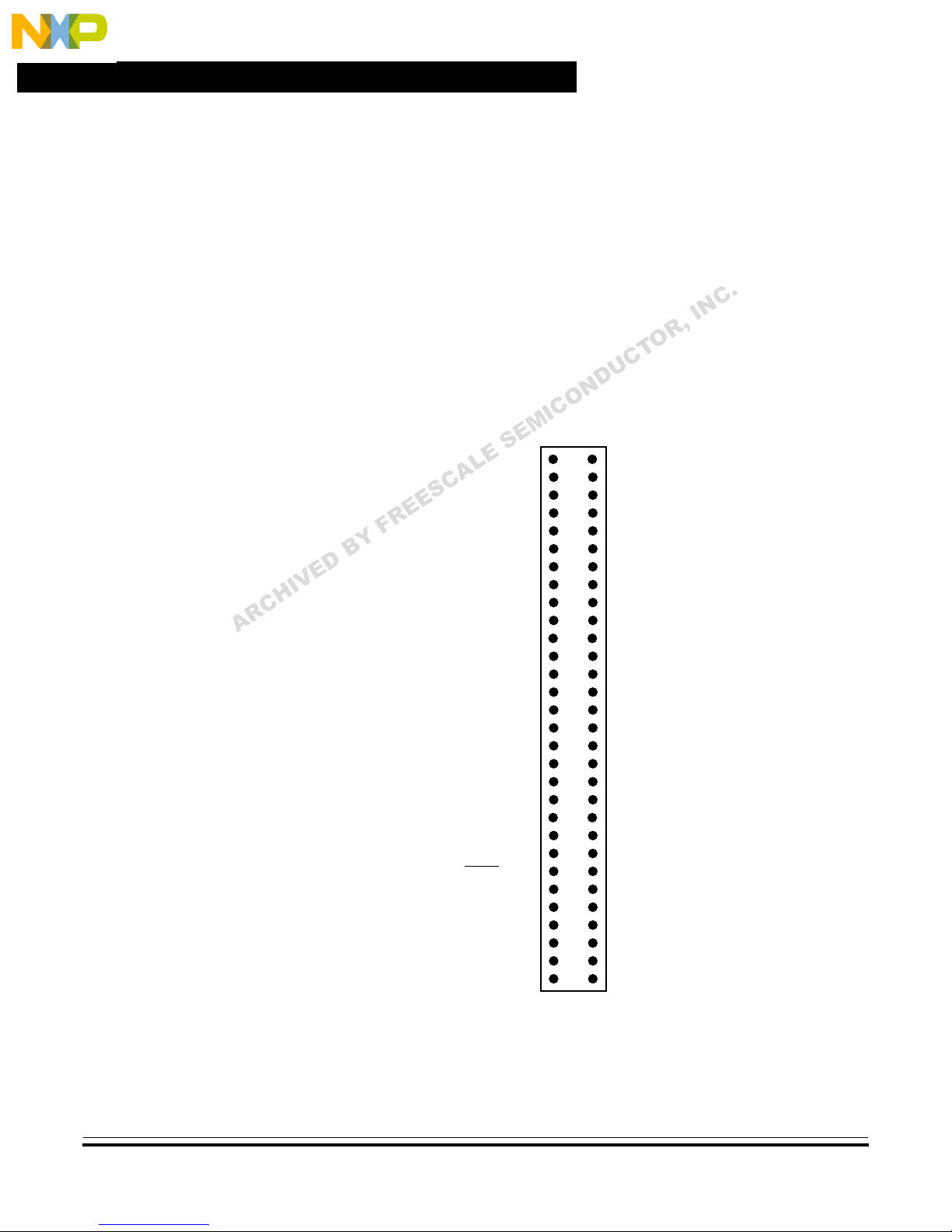

Connect the external power supply to connector J6 on the EVB as shown in

Figure 2-1, using 20 AWG or smaller insulated wire. Strip each wire’s

insulation 1/4 inch from the end, lift the J6 contact lever to release tension on

the contact, insert the bare end of the wire into J6, and close the lever to secure

the wire. Observe the polarity carefully.

S

Do not use wire larger than 20 AWG in connector J6. Larger wire could

damage the connector.

E

V

I

H

C

R

D

Y

B

E

E

R

F

Figure 2-1. EVB Power Connector J6

C

A

E SE

L

M

O

C

I

.

C

N

I

Freescale Semiconductor, I

2.5 EVB to Terminal Connection

For factory-default operation, connect the terminal to J3 or J4 on the EVB, as

shown in Table 2-1. This setup uses the MCU’s SCI port 0 (SCI0) and its

associated RS-232C interface for communications with the terminal device.

To use SCI1 and the second RS-232C interface for the terminal, the EVB’s

hardware setup must be modified. For details, refer to 4.5 Terminal Interface.

M68HC12A4EVB Evaluation Board — Rev. 1 User’s Manual

MOTOROLA Configuration and Setup 29

For More Information On This Product,

Go to: www.freescale.com

Page 30

Configuration and Setup

..

.

nc

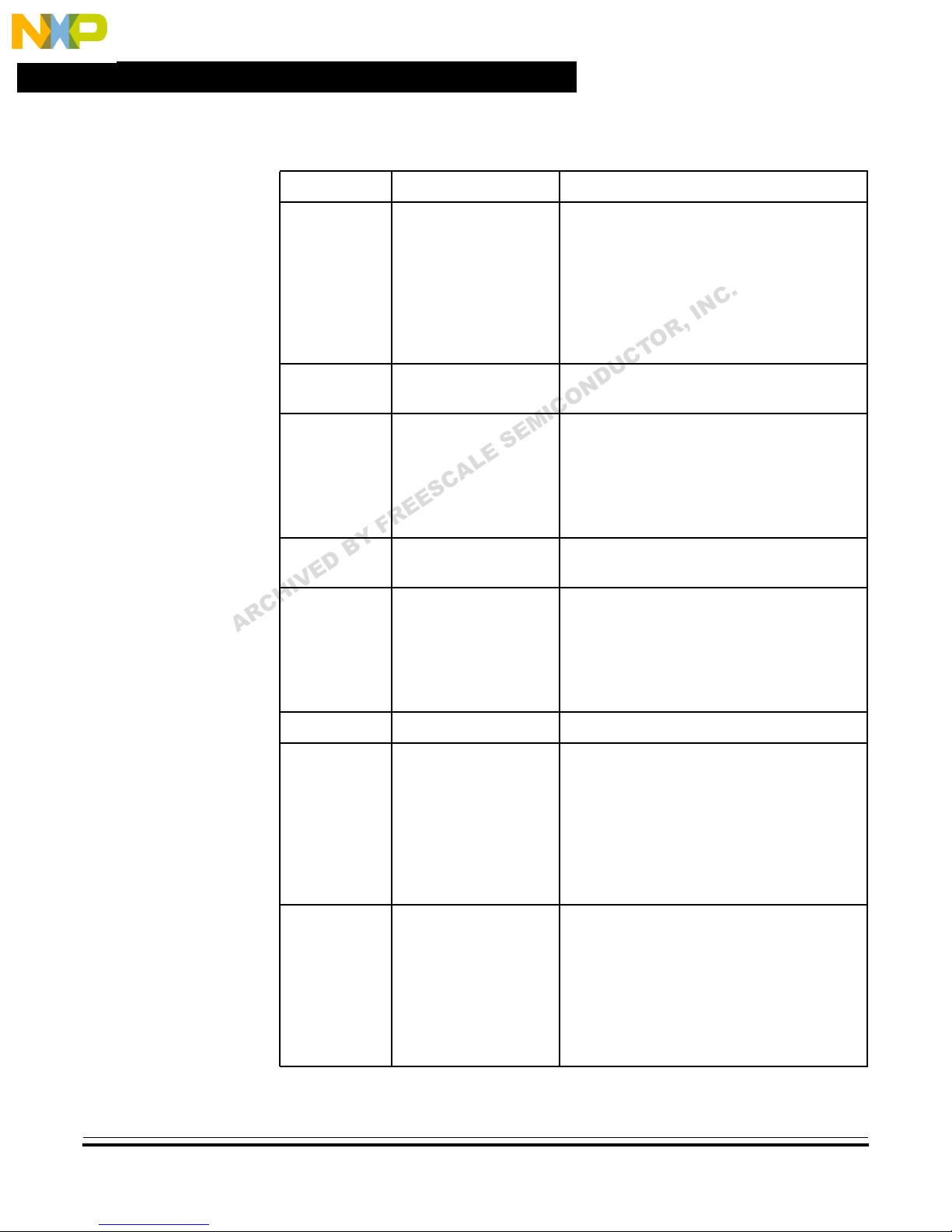

EVB Pins, Always DCE

(1)

J3

Receptacle

(1)

(2)

Freescale Semiconductor, I

(3)

(4)

(2)

/ J2

DB-9

2 2 Receive data (RXD) 2233

3 3 Transmit data (TXD) 3322

5 1 Ground (GND) 5757

Factory default. Terminal interface uses SCI0.

Optional. Terminal interface uses SCI1. Hardware modifications are required. For details, refer to 4.5 Terminal

Interface.

Normal (DCE-to-DTE) cable connections

Null modem (DCE-to-DCE) cable connections

(1)

J4

3-Pin

Header

A

/ J1

Freescale Semiconductor, Inc.

Standard, commercially available cables may be used in most cases. Note that

the EVB uses only three of the RS-232C signals. Table 2-1 lists these signals

and their pin assignments.

The EVB’s RS-232C connectors, J2 (default) and J3 (unpopulated footprint),

are wired as data circuit-terminating equipment (DCE) and employ 9-pin

subminiature D (DB-9) receptacles. The equivalent 3-pin headers, J1 and J4,

serve the same purposes and may be used for customized cabling.

,

R

U

C

T

O

Most terminal devices — whether dumb terminals or the serial ports on host

computers — are wired as data terminal equipment (DTE) and employ 9- or

25-pin subminiature D (DB-9 or DB-25) plugs. In these cases, normal

straight-through cabling is used between the EVB and the terminal. Adapters

M

I

C

O

N

D

.

C

N

I

are readily available for connecting 9-pin cables to 25-pin terminal connectors.

E SE

L

E

S

C

A

Terminal Pins

(3)

DTE

Plug

DB-9 DB-25 DB-9 DB-25

DCE

Receptacle

(4)

If the terminal device is wired as DCE, the RXD and TXD lines must be

cross-connected, as shown in Table 2-1. Commercial null modem adapter

cables are available for this purpose.

B

D

Table 2-1. RS-232C Interface Cabling

E

V

I

H

C

R

(2)

DTE Signal

Y

E

R

F

Optionally, the MCU’s background debug mode (BDM) interface can serve as

the user interface. This setup makes both of the SCI ports available for user

applications. Additional hardware and software are required. For more

information, refer to the documentation for the background debug development

tool being used, such as Motorola’s serial debug interface.

NOTE:

User’s Manual M68HC12A4EVB Evaluation Board — Rev. 1

30 Configuration and Setup MOTOROLA

D-Bug12 does not use the BDM interface.

For More Information On This Product,

Go to: www.freescale.com

Page 31

Freescale Semiconductor, Inc.

2.6 Terminal Communications Setup

This section describes how to set up the terminal communications.

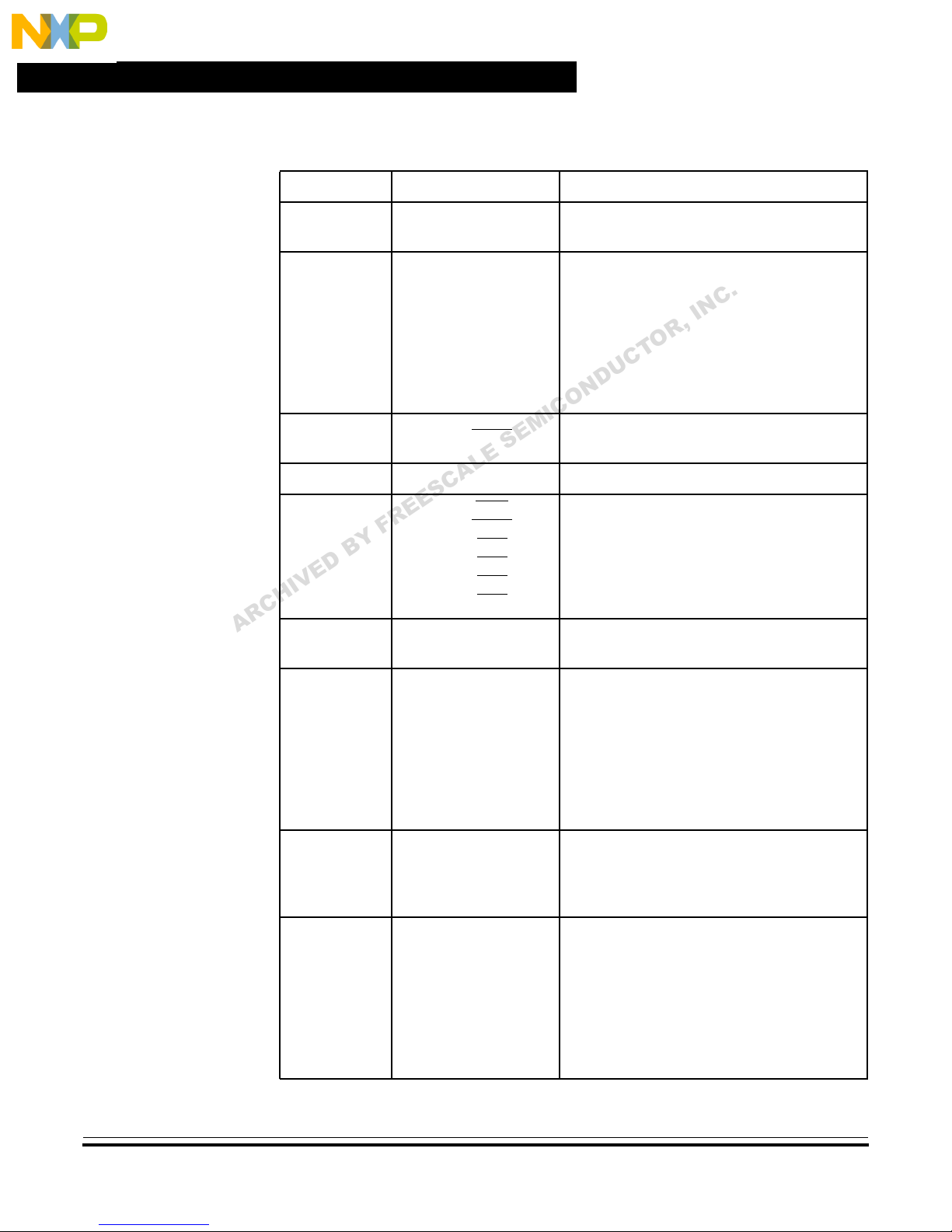

2.6.1 Communication Parameters

The EVB’s serial communications ports use the communication parameters

listedin Table 2-2. Of these, only thebaud rate canbe changed. For instructions

on changing it, refer to 2.6.4 Changing the Baud Rate.

..

.

nc

2.6.2 Dumb-Terminal Setup

2.6.3 Host-Computer Setup

Freescale Semiconductor, I

Configuring a dumb terminal for use with the EVB consists of setting its

V

I

H

parameters as shown in Table 2-2. Many terminals are configurable with

C

R

externally accessible switches, but the procedure differs between brands and

A

models. Consult the manufacturer’s instructions for the terminal being used.

One advantage of using a host computer as the EVB’s terminal is the ability to

generate code off-board, for subsequent loading into the EVB’s memory. It is

thus desirable for the host to be capable of runningprograms such as Motorola’s

MCUez assembler. For more information, see 3.8 Off-Board Code

Generation.

To serve as the EVB’s terminal, the host computer must have an RS-232C serial

port and an installed communications program capable of operating with the

parameters listed in Table 2-2.

E

D

B

Terminal Communications Setup

N

D

U

C

Table 2-2. Communication Parameters

M

O

C

I

Y

Baud Rate 9600

Data Bits 8

E SE

Stop Bits 1

L

A

C

S

E

E

R

F

Parity None

T

Configuration and Setup

.

C

N

I

,

R

O

Setting up the parameters is normally done within the communications

program, after it has been started on the host. Usually, the setup can be saved in

a configuration file so that it does not have to be repeated. Because procedures

vary between programs, consult the user’s guide for the specific program.

Appendix B. Communications Program Examples provides examples of

using some of the commonly available communications programs.

M68HC12A4EVB Evaluation Board — Rev. 1 User’s Manual

MOTOROLA Configuration and Setup 31

For More Information On This Product,

Go to: www.freescale.com

Page 32

Freescale Semiconductor, Inc.

Configuration and Setup

2.6.4 Changing the Baud Rate

The EVB’s default baud rate for the RS-232C ports is 9600. This can be

changed in two ways:

• For temporary changes, use the D-Bug12 BAUD command. This change

remains in effect only until the next reset or power-up, when the baud

rate returns to 9600.

• For permanent changes, the D-Bug12 baud-rate initialization value

stored in EPROM must be modified. For instructions, refer to

..

.

Appendix D. D-Bug12 Customization Data and Appendix E.

Customizing the EPROMs.

nc

2.7 Using Fast External RAM

To replace the two factory-supplied SRAM chips with parts capable of

F

operation at the full 16-MHz external clock speed (8-MHz E-clock) with no

wait states, two operations are required:

H

C

R

A

2.7.1 Selecting and Replacing the RAM Chips

The replacement 8-Kbyte x 8-bit SRAM devices should have a chip-select

access time of less than 60 nanoseconds. An example of a device that has been

used successfully is the Integrated Device Technologies part number

Freescale Semiconductor, I

IDT7164L25P (8 Kbytes x 8 bits, 25 ns).

D

E

V

I

1. Replace the SRAM chips with suitably fast parts. See 2.7.1 Selecting

2. Reprogram the SRAM chip select,

Y

B

and Replacing the RAM Chips.

See 2.7.2 Reprogramming the RAM Chip Select.

R

E

E

S

C

A

E SE

L

M

.

C

N

I

,

R

O

T

C

U

D

N

O

C

I

CSD, for zero-wait-state operation.

When installing the replacement SRAM devices, make sure that their pins align

with the rightmost ends of sockets U4 and U6A, as viewed in Figure 1-1. EVB

Layout and Component Placement.

User’s Manual M68HC12A4EVB Evaluation Board — Rev. 1

32 Configuration and Setup MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Page 33

Freescale Semiconductor, Inc.

2.7.2 Reprogramming the RAM Chip Select

Configuration and Setup

Using Fast External RAM

..

.

nc

NOTE:

A

NOTE:

Either of two methods may be used to reprogram the RAM chip select,

eliminate the wait state.

Before attempting either of the following methods, ensure that the EVB is

operating properly by following the startup instructions in 3.2 Startup.

Method A — Modifying the CSSTR0 register in memory (temporary)

This method may be used without altering the D-Bug12 startup code in

EPROM. However, it must be repeated each time the EVB is powered up or

M

O

C

I

reset.

Using D-Bug12’s MM (MEMORY MODIFY) command, change the value at

memory location $003E from $05 to $04.

S

E

Y

E

R

F

Method B — Modifying the D-Bug12 startup code in EPROM (permanent)

E

D

B

This method is accomplished by reprogramming a single byte in the

factory-supplied, one-time-programmable (OTP) EPROM, U7. An EPROM

V

I

H

programmer is required.

C

R

Method B does not work in reverse. If U7 has already been reprogrammed

using this technique, it cannot be restored to its original state.

If the EPROMs are to be customized in some other way — for example, to add

a user program or to modify another aspect of D-Bug12 — the change to

registerCSSTR0 can be made in the startupsource code. For more information,

refer to Appendix C. D-Bug12 Startup Code and Appendix E. Customizing

the EPROMs.

C

A

E SE

L

N

D

U

C

T

O

R

,

.

C

N

I

CSD, to

Freescale Semiconductor, I

M68HC12A4EVB Evaluation Board — Rev. 1 User’s Manual

MOTOROLA Configuration and Setup 33

To permanently reprogram U7 for zero RAM wait states, follow these steps:

1. Remove power from the EVB.

2. Being careful not to bend any pins, remove U7 from its socket on the

3. Following the instructions and using the software for the EPROM

EVB and install it in the appropriate socket on the EPROM programmer.

programmer, perform the steps in procedure 1 or procedure 2, as

described here.

For More Information On This Product,

Go to: www.freescale.com

Page 34

Configuration and Setup

Procedure 1 1. Select the Atmel Corporation’s device type AT27LV256R.

..

.

nc

A

Freescale Semiconductor, Inc.

Some EPROM programmers do not have an editable RAM buffer capable of

holding the entire contents of U7. Instead, they program EPROMs directly from

the contents of a disk file.

If the programmer being used has an editable RAM buffer large enough to hold

the contents of U7, use procedure 1. Otherwise, to reprogram U7 from a disk

file, use procedure 2.

2. Read the contents of U7 into the EPROM programmer’s editable RAM

3. Before modifying U7, save a copy of its contents to a disk file for backup

4. Change the contents of the programmer’s editable RAM buffer at

5. Reprogram U7 with the edited contents of the programmer’s RAM

E

V

I

H

6. Reinstall U7 in its socket on the EVB. Be sure that its pins align with the

C

R

7. Apply power to the EVB and press S1, the reset switch. The D-Bug12

8. Ensure that the modification was performed properly by using

.

C

N

I

,

R

O

T

C

U

D

buffer.

M

purposes.

S

E

Y

E

R

F

location $7ED6 from $05 to $04.

B

D

buffer.

rightmost end of its socket, as viewed in Figure 1-1. EVB Layout and

Component Placement.

prompt should appear on the terminal display.

D-Bug12’s MD command to examine the CSSTR0 register at memory

location $003E. It should contain the value $04.

C

A

E SE

L

N

O

C

I

Freescale Semiconductor, I

User’s Manual M68HC12A4EVB Evaluation Board — Rev. 1

34 Configuration and Setup MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Page 35

..

.

nc

Freescale Semiconductor, Inc.

Procedure 2 1. Create a text file containing these two lines:

2. Select the Atmel Corporation’s device type AT27LV256R.

3. Before modifying U7, save a copy of its contents to a disk file for backup

4. Reprogram U7 with the contents of the text file created in step 1.

5. Reinstall U7 in its socket on the EVB. Be sure that its pins align with the

6. Apply power to the EVB and press S1, the reset switch. The D-Bug12

7. Ensure that the modification was performed properly by using

E

V

I

H

C

R

A

S1047E6D040C

S9030000FC

purposes.

T

C

U

C

O

N

D

rightmost end of its socket, as viewed in Figure 1-1. EVB Layout and

Component Placement.

E SE

S

C

A

L

prompt should appear on the terminal display.

E

E

B

Y

R

F

D-Bug12’s MD (MEMORY DISPLAY) command to examine the

CSSTR0 register at memory location $003E. It should contain the

D

value $04.

M

I

Configuration and Setup

Using Fast External RAM

.

C

N

I

,

R

O

Freescale Semiconductor, I

M68HC12A4EVB Evaluation Board — Rev. 1 User’s Manual

MOTOROLA Configuration and Setup 35

For More Information On This Product,

Go to: www.freescale.com

Page 36

Configuration and Setup

..

.

nc

A

R

Freescale Semiconductor, Inc.

E

V

I

H

C

D

O

C

I

M

E SE

L

A

C

S

E

E

R

F

Y

B

N

D

U

C

T

O

R

,

.

C

N

I

Freescale Semiconductor, I

User’s Manual M68HC12A4EVB Evaluation Board — Rev. 1

36 Configuration and Setup MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Page 37

User’s Manual — M68HC12A4EVB Evaluation Board

3.1 Contents

..

.

nc

Freescale Semiconductor, I

Freescale Semiconductor, Inc.

Section 3. Operation

.

C

N

I

,

R

O

D

U

C

T

3.2 Startup. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

3.3 Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

3.4 Program Abort . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

S

C

A

L

3.5 Using D-Bug12 Commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

3.6 D-Bug12 Command Set . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

ASM Assemble Instructions . . . . . . . . . . . . . . . . . . . . . 44

Y

B

BAUD Set Baud Rate . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

D

E

BF Block Fill. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

V

I

A

R

C

H

BR Breakpoint Set . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

BULK Bulk Erase On-Chip EEPROM . . . . . . . . . . . . . . 51

CALL Call Subroutine . . . . . . . . . . . . . . . . . . . . . . . . . . 52

G Go Execute a User Program . . . . . . . . . . . . . . . . 53

GT Go Till . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

HELP Onscreen Help Summary. . . . . . . . . . . . . . . . . . . 55

LOAD Load S-Record File . . . . . . . . . . . . . . . . . . . . . . . 56

MD Memory Display . . . . . . . . . . . . . . . . . . . . . . . . . 57

MDW Display Memory as 16-Bit Word . . . . . . . . . . . . 58

MM Memory Modify. . . . . . . . . . . . . . . . . . . . . . . . . . 59

MMW Modify Memory in 16-Bit Word. . . . . . . . . . . . . 60

MOVE Move Memory Block. . . . . . . . . . . . . . . . . . . . . . 61

NOBR Remove Breakpoints . . . . . . . . . . . . . . . . . . . . . . 62

RD Register Display. . . . . . . . . . . . . . . . . . . . . . . . . . 63

RM Register Modify. . . . . . . . . . . . . . . . . . . . . . . . . . 64

T Trace . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

UPLOAD Display Memory in S-Record Format . . . . . . . . . 67

VERF Verify S-Record File Against Memory . . . . . . . . 68

<RegisterName> Modify Register Value . . . . . . . . . . . . . . . . . . . . 70

E

E

R

F

M

E SE

N

O

C

I

M68HC12A4EVB Evaluation Board — Rev. 1 User’s Manual

MOTOROLA Operation 37

For More Information On This Product,

Go to: www.freescale.com

Page 38

Operation

..

.

nc

3.2 Startup

Freescale Semiconductor, I

Freescale Semiconductor, Inc.

3.7 Alternate Execution from EEPROM . . . . . . . . . . . . . . . . . . . . . . . . . 72

3.8 Off-Board Code Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

3.9 Memory Usage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

3.9.1 Description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

3.9.2 Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

3.10 Operational Limitations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

3.10.1 On-Chip RAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

3.10.2 SCI Port Usage. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

3.10.3 Dedicated MCU Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

3.10.4 Terminal Communications. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

The following startup procedure includes a checklist of configuration and setup

items from Section 2. Configuration and Setup. To begin operating the

M68HC12A4EVB, follow these steps:

E

V

1. Configure the EVB if required. See 2.3 EVB Configuration.

I

H

C

A

R

2. Determine whether execution should begin with the D-Bug12 monitor

3. Connect the EVB to the external power supply. See 2.4 EVB to Power

4. Connect the EVB to the terminal. See 2.5 EVB to Terminal

5. Configure the terminal communications interface. See 2.6 Terminal

.

C

N

I

,

R

O

T

C

U

D

N

O

C

I

M

E SE

L

A

C

S

E

E

R

F

Y

B

D

program (factory default) or with user code in on-chip EEPROM. Set the

jumper on header W20 accordingly. See 2.3 EVB Configuration and

3.7 Alternate Execution from EEPROM.

Supply Connection.

Connection.

Communications Setup.

6. Apply power to the EVB and to the terminal. If the terminal is a host

7. Reset the EVB by pressing and releasing the on-board reset switch (S1).

User’s Manual M68HC12A4EVB Evaluation Board — Rev. 1

38 Operation MOTOROLA

computer:

a. Verify that it has booted correctly.

b. Start the communications program for terminal emulation. See

2.6.3 Host-Computer Setup and Appendix B. Communications

Program Examples.

For More Information On This Product,

Go to: www.freescale.com

Page 39

..

.

nc

3.3 Reset

Freescale Semiconductor, Inc.

If the EVB is configured to execute D-Bug12 upon reset (factory default —

startup step 2), the D-Bug12 sign-on banner and prompt should appear on the

terminal’s display like this:

If the prompt does not appear, check all connections and verify that startup

steps 1 through 7 have been performed correctly.

When the prompt appears, D-Bug12 is ready to accept commands from the

terminal as described in 3.5 Using D-Bug12 Commands and 3.6 D-Bug12

Command Set.

If the EVB is configured to execute user code upon reset (startup step 2), the

codein on-chip EEPROMis executed immediately.For more information, refer

to 3.7 Alternate Execution from EEPROM.

E

V

I

Control can be returned to the D-Bug12 terminal prompt by doing one of these:

H

C

A

R

1. Terminating the user code with appropriate instructions; see

2. Activating the program-abort function; see 3.4 Program Abort

EVB operation can be restarted at any time by activating the hardware reset

function. Do this in one of two ways:

D-Bug12 v1.0.2

Copyright 1995 - 1996 Motorola Semiconductor

For Commands type “Help”

>

C

U

D

N

O

C

I

M

E SE

L

A

C

S

E

E

R

F

Y

B

D

3.7 Alternate Execution from EEPROM

T

O

R

,

.

C

N

I

Operation

Reset

Freescale Semiconductor, I

M68HC12A4EVB Evaluation Board — Rev. 1 User’s Manual

MOTOROLA Operation 39

1. Press and release the on-board reset switch, S1 (always applicable).

2. If the hardware reset input has been customized in the prototype area,

Note that the EVB’s reset circuitry is associated with the low-voltage inhibit

(LVI) protection. For more information, refer to 4.10 Reset and

4.11 Low-Voltage Inhibit (LVI).

activate it in accordance with the custom circuitry.

For More Information On This Product,

Go to: www.freescale.com

Page 40

Operation

3.4 Program Abort