Page 1

i.MX 6SoloLite Linux Reference

Manual

Document Number: IMXL6SLRM

Rev L3.0.35_4.1.0, 09/2013

Page 2

i.MX 6SoloLite Linux Reference Manual, Rev. L3.0.35_4.1.0, 09/2013

2 Freescale Semiconductor, Inc.

Page 3

Contents

Section number Title Page

Chapter 1

About This Book

1.1 Audience.........................................................................................................................................................................17

1.1.1 Conventions.......................................................................................................................................................17

1.1.2 Definitions, Acronyms, and Abbreviations........................................................................................................17

Chapter 2

Introduction

2.1 Overview.........................................................................................................................................................................21

2.1.1 Software Base....................................................................................................................................................21

2.1.2 Features..............................................................................................................................................................22

Chapter 3

Machine Specific Layer (MSL)

3.1 Introduction.....................................................................................................................................................................27

3.2 Interrupts (Operation).....................................................................................................................................................28

3.2.1 Interrupt Hardware Operation............................................................................................................................28

3.2.2 Interrupt Software Operation.............................................................................................................................28

3.2.3 Interrupt Features...............................................................................................................................................29

3.2.4 Interrupt Source Code Structure........................................................................................................................29

3.2.5 Interrupt Programming Interface.......................................................................................................................29

3.3 Timer...............................................................................................................................................................................30

3.3.1 Timer Software Operation.................................................................................................................................30

3.3.2 Timer Features...................................................................................................................................................30

3.3.3 Timer Source Code Structure.............................................................................................................................31

3.3.4 Timer Programming Interface............................................................................................................................31

3.4 Memory Map..................................................................................................................................................................31

3.4.1 Memory Map Hardware Operation....................................................................................................................31

3.4.2 Memory Map Software Operation.....................................................................................................................31

3.4.3 Memory Map Features.......................................................................................................................................31

i.MX 6SoloLite Linux Reference Manual, Rev. L3.0.35_4.1.0, 09/2013

Freescale Semiconductor, Inc. 3

Page 4

Section number Title Page

3.4.4 Memory Map Source Code Structure................................................................................................................32

3.4.5 Memory Map Programming Interface...............................................................................................................32

3.5 IOMUX...........................................................................................................................................................................32

3.5.1 IOMUX Hardware Operation............................................................................................................................33

3.5.2 IOMUX Software Operation..............................................................................................................................33

3.5.3 IOMUX Features................................................................................................................................................34

3.5.4 IOMUX Source Code Structure.........................................................................................................................34

3.5.5 IOMUX Programming Interface........................................................................................................................34

3.5.6 IOMUX Control Through GPIO Module..........................................................................................................34

3.5.6.1 GPIO Hardware Operation.................................................................................................................35

3.5.6.1.1 Muxing Control.................................................................................................................35

3.5.6.1.2 PULLUP Control..............................................................................................................35

3.5.6.2 GPIO Software Operation (general)..................................................................................................35

3.5.6.3 GPIO Implementation........................................................................................................................35

3.5.6.4 GPIO Source Code Structure.............................................................................................................36

3.5.6.5 GPIO Programming Interface............................................................................................................36

3.6 General Purpose Input/Output(GPIO)............................................................................................................................36

3.6.1 GPIO Software Operation..................................................................................................................................36

3.6.1.1 API for GPIO.....................................................................................................................................37

3.6.2 GPIO Features....................................................................................................................................................37

3.6.3 GPIO Module Source Code Structure................................................................................................................37

3.6.4 GPIO Programming Interface 2.........................................................................................................................38

Chapter 4

Smart Direct Memory Access (SDMA) API

4.1 Overview.........................................................................................................................................................................39

4.1.1 Hardware Operation...........................................................................................................................................39

4.1.2 Software Operation............................................................................................................................................39

4.1.3 Source Code Structure.......................................................................................................................................40

4.1.4 Menu Configuration Options.............................................................................................................................41

i.MX 6SoloLite Linux Reference Manual, Rev. L3.0.35_4.1.0, 09/2013

4 Freescale Semiconductor, Inc.

Page 5

Section number Title Page

4.1.5 Programming Interface......................................................................................................................................41

4.1.6 Usage Example..................................................................................................................................................41

Chapter 5

Electrophoretic Display Controller (EPDC) Frame Buffer Driver

5.1 Introduction.....................................................................................................................................................................43

5.2 Hardware Operation........................................................................................................................................................44

5.3 Software Operation.........................................................................................................................................................44

5.3.1 EPDC Frame Buffer Driver Overview...............................................................................................................44

5.3.2 EPDC Frame Buffer Driver Extensions.............................................................................................................45

5.3.3 EPDC Panel Configuration................................................................................................................................45

5.3.3.1 Boot Command Line Parameters.......................................................................................................46

5.3.4 EPDC Waveform Loading.................................................................................................................................47

5.3.4.1 Using a Default Waveform File.........................................................................................................47

5.3.4.2 Using a Custom Waveform File.........................................................................................................48

5.3.5 EPDC Panel Initialization..................................................................................................................................48

5.3.6 Grayscale Framebuffer Selection.......................................................................................................................49

5.3.7 Enabling An EPDC Splash Screen.....................................................................................................................49

5.4 Source Code Structure ...................................................................................................................................................50

5.5 Menu Configuration Options..........................................................................................................................................51

5.6 Programming Interface...................................................................................................................................................51

5.6.1 IOCTLs/Functions.............................................................................................................................................52

5.6.2 Structures and Defines.......................................................................................................................................55

Chapter 6

Sipix Display Controller (SPDC) Frame Buffer Driver

6.1 Introduction.....................................................................................................................................................................57

6.2 Hardware Operation........................................................................................................................................................58

6.3 Software Operation.........................................................................................................................................................58

6.3.1 SPDC Frame Buffer Driver Overview...............................................................................................................58

6.3.2 SPDC Frame Buffer Driver Extensions.............................................................................................................59

i.MX 6SoloLite Linux Reference Manual, Rev. L3.0.35_4.1.0, 09/2013

Freescale Semiconductor, Inc. 5

Page 6

Section number Title Page

6.3.3 SPDC Panel Configuration................................................................................................................................59

6.3.3.1 Boot Command Line Parameters.......................................................................................................60

6.3.4 SPDC Waveform Loading.................................................................................................................................60

6.3.4.1 Using a Default Waveform File.........................................................................................................61

6.3.4.2 Using a Custom Waveform File.........................................................................................................61

6.3.5 SPDC Panel Initialization..................................................................................................................................62

6.3.6 Grayscale Framebuffer Selection.......................................................................................................................62

6.4 Source Code Structure ...................................................................................................................................................63

6.5 Menu Configuration Options..........................................................................................................................................64

6.6 Programming Interface...................................................................................................................................................64

6.6.1 IOCTLs/Functions.............................................................................................................................................65

6.6.2 Structures and Defines.......................................................................................................................................68

Chapter 7

Pixel Pipeline (PxP) DMA-ENGINE Driver

7.1 Introduction.....................................................................................................................................................................71

7.2 Hardware Operation........................................................................................................................................................71

7.3 Software Operation.........................................................................................................................................................71

7.3.1 Key Data Structs................................................................................................................................................71

7.3.2 Channel Management........................................................................................................................................72

7.3.3 Descriptor Management.....................................................................................................................................72

7.3.4 Completion Notification....................................................................................................................................72

7.3.5 Limitations.........................................................................................................................................................73

7.4 Menu Configuration Options..........................................................................................................................................73

7.5 Source Code Structure....................................................................................................................................................73

Chapter 8

ELCDIF Frame Buffer Driver

8.1 Introduction.....................................................................................................................................................................75

8.2 Hardware Operation........................................................................................................................................................75

8.3 Software Operation.........................................................................................................................................................75

i.MX 6SoloLite Linux Reference Manual, Rev. L3.0.35_4.1.0, 09/2013

6 Freescale Semiconductor, Inc.

Page 7

Section number Title Page

8.4 Menu Configuration Options..........................................................................................................................................76

8.5 Source Code Structure....................................................................................................................................................76

Chapter 9

Graphics Processing Unit (GPU)

9.1 Introduction.....................................................................................................................................................................77

9.1.1 Driver Features...................................................................................................................................................77

9.1.1.1 Hardware Operation...........................................................................................................................77

9.1.1.2 Software Operation............................................................................................................................78

9.1.1.3 Source Code Structure ......................................................................................................................78

9.1.1.4 Library Structure ...............................................................................................................................78

9.1.1.5 API References..................................................................................................................................80

9.1.1.6 Menu Configuration Options.............................................................................................................80

Chapter 10

High-Definition Multimedia Interface (HDMI)

10.1 Introduction.....................................................................................................................................................................81

10.2 Software Operation.........................................................................................................................................................81

10.2.1 Hotplug Handling and Video Mode Changes....................................................................................................81

10.3 Source Code Structure....................................................................................................................................................82

10.3.1 Linux Menu Configuration Options...................................................................................................................83

10.4 Unit Test..........................................................................................................................................................................83

10.4.1 Video..................................................................................................................................................................83

10.4.2 Audio..................................................................................................................................................................84

Chapter 11

X Windows Acceleration

11.1 Introduction.....................................................................................................................................................................85

11.2 Hardware Operation........................................................................................................................................................85

11.3 Software Operation.........................................................................................................................................................85

11.3.1 X Windows Acceleration Architecture..............................................................................................................86

11.3.2 i.MX 6 Driver for X-Windows System..............................................................................................................87

11.3.3 xorg.conf for i.MX 6..........................................................................................................................................89

i.MX 6SoloLite Linux Reference Manual, Rev. L3.0.35_4.1.0, 09/2013

Freescale Semiconductor, Inc. 7

Page 8

Section number Title Page

11.3.4 Setup X-Windows System Acceleration............................................................................................................90

Chapter 12

Camera Sensor Interface (CSI) Driver

12.1 Hardware Operation........................................................................................................................................................93

12.2 Software Operation.........................................................................................................................................................93

12.2.1 CSI Software Operation.....................................................................................................................................94

12.2.2 Video for Linux 2 (V4L2) APIs.........................................................................................................................94

12.2.2.1 V4L2 Capture Device........................................................................................................................94

12.2.2.2 Use of the V4L2 Capture APIs..........................................................................................................95

12.3 Source Code Structure....................................................................................................................................................95

12.4 Linux Menu Configuration Options................................................................................................................................96

12.5 Programming Interface...................................................................................................................................................96

Chapter 13

OV5640 Using parallel interface

13.1 Hardware Operation........................................................................................................................................................97

13.2 Software Operation.........................................................................................................................................................97

13.3 Source Code Structure....................................................................................................................................................98

13.4 Linux Menu Configuration Options................................................................................................................................98

Chapter 14

Low-level Power Management (PM) Driver

14.1 Hardware Operation........................................................................................................................................................99

14.1.1 Software Operation............................................................................................................................................99

14.1.2 Source Code Structure.......................................................................................................................................100

14.1.3 Menu Configuration Options.............................................................................................................................100

14.1.4 Programming Interface......................................................................................................................................101

14.1.5 Unit Test.............................................................................................................................................................101

Chapter 15

PF100 Regulator Driver

15.1 Introduction.....................................................................................................................................................................103

i.MX 6SoloLite Linux Reference Manual, Rev. L3.0.35_4.1.0, 09/2013

8 Freescale Semiconductor, Inc.

Page 9

Section number Title Page

15.2 Hardware Operation........................................................................................................................................................103

15.2.1 Driver Features...................................................................................................................................................104

15.3 Software Operation.........................................................................................................................................................104

15.3.1 Regulator APIs...................................................................................................................................................104

15.4 Driver Architecture.........................................................................................................................................................106

15.4.1 Driver Interface Details......................................................................................................................................107

15.4.2 Source Code Structure.......................................................................................................................................107

15.4.3 Menu Configuration Options.............................................................................................................................107

Chapter 16

CPU Frequency Scaling (CPUFREQ) Driver

16.1 Introduction.....................................................................................................................................................................109

16.1.1 Software Operation............................................................................................................................................109

16.1.2 Source Code Structure.......................................................................................................................................110

16.2 Menu Configuration Options..........................................................................................................................................110

16.2.1 Board Configuration Options.............................................................................................................................111

Chapter 17

Dynamic Voltage Frequency Scaling (DVFS) Driver

17.1 Introduction.....................................................................................................................................................................113

17.1.1 Operation............................................................................................................................................................113

17.1.2 Software Operation............................................................................................................................................113

17.1.3 Source Code Structure.......................................................................................................................................114

17.2 Menu Configuration Options..........................................................................................................................................114

17.2.1 Board Configuration Options.............................................................................................................................114

Chapter 18

Thermal Driver

18.1 Introduction.....................................................................................................................................................................115

18.1.1 Thermal Driver Overview..................................................................................................................................115

18.2 Hardware Operation........................................................................................................................................................115

18.2.1 Thermal Driver Software Operation..................................................................................................................116

i.MX 6SoloLite Linux Reference Manual, Rev. L3.0.35_4.1.0, 09/2013

Freescale Semiconductor, Inc. 9

Page 10

Section number Title Page

18.3 Driver Features................................................................................................................................................................116

18.3.1 Source Code Structure.......................................................................................................................................116

18.3.2 Menu Configuration Options.............................................................................................................................116

18.3.3 Programming Interface......................................................................................................................................116

18.3.4 Interrupt Requirements......................................................................................................................................117

18.4 Unit Test..........................................................................................................................................................................117

Chapter 19

Anatop Regulator Driver

19.1 Introduction.....................................................................................................................................................................119

19.1.1 Hardware Operation...........................................................................................................................................119

19.2 Driver Features................................................................................................................................................................120

19.2.1 Software Operation............................................................................................................................................120

19.2.2 Regulator APIs...................................................................................................................................................120

19.2.3 Driver Interface Details......................................................................................................................................121

19.2.4 Source Code Structure.......................................................................................................................................121

19.2.5 Menu Configuration Options.............................................................................................................................121

Chapter 20

SNVS Real Time Clock (SRTC) Driver

20.1 Introduction.....................................................................................................................................................................123

20.1.1 Hardware Operation...........................................................................................................................................123

20.2 Software Operation.........................................................................................................................................................123

20.2.1 IOCTL................................................................................................................................................................123

20.2.2 Keeping Alive in the Power Off State...............................................................................................................124

20.3 Driver Features................................................................................................................................................................124

20.3.1 Source Code Structure.......................................................................................................................................125

20.3.2 Menu Configuration Options.............................................................................................................................125

Chapter 21

Advanced Linux Sound Architecture (ALSA) System on a Chip (ASoC) Sound Driver

21.1 ALSA Sound Driver Introduction...................................................................................................................................127

i.MX 6SoloLite Linux Reference Manual, Rev. L3.0.35_4.1.0, 09/2013

10 Freescale Semiconductor, Inc.

Page 11

Section number Title Page

21.2 SoC Sound Card .............................................................................................................................................................130

21.2.1 Stereo CODEC Features....................................................................................................................................130

21.2.2 Sound Card Information.....................................................................................................................................130

21.3 Hardware Operation........................................................................................................................................................131

21.3.1 Stereo Audio CODEC........................................................................................................................................131

21.4 Software Operation.........................................................................................................................................................132

21.4.1 ASoC Driver Source Architecture.....................................................................................................................132

21.4.2 Sound Card Registration....................................................................................................................................132

21.4.3 Device Open.......................................................................................................................................................133

21.4.4 Platform Data.....................................................................................................................................................133

21.4.5 Menu Configuration Options.............................................................................................................................134

21.5 Unit Test..........................................................................................................................................................................134

21.5.1 Stereo CODEC Unit Test...................................................................................................................................134

Chapter 22

SPI NOR Flash Memory Technology Device (MTD) Driver

22.1 Introduction.....................................................................................................................................................................137

22.1.1 Hardware Operation...........................................................................................................................................137

22.1.2 Software Operation............................................................................................................................................138

22.1.3 Driver Features...................................................................................................................................................138

22.1.4 Source Code Structure.......................................................................................................................................138

22.1.5 Menu Configuration Options.............................................................................................................................139

Chapter 23

MMC/SD/SDIO Host Driver

23.1 Introduction.....................................................................................................................................................................141

23.1.1 Hardware Operation...........................................................................................................................................141

23.1.2 Software Operation............................................................................................................................................142

23.2 Driver Features................................................................................................................................................................144

23.2.1 Source Code Structure.......................................................................................................................................145

23.2.2 Menu Configuration Options.............................................................................................................................145

i.MX 6SoloLite Linux Reference Manual, Rev. L3.0.35_4.1.0, 09/2013

Freescale Semiconductor, Inc. 11

Page 12

Section number Title Page

23.2.3 Platform Data.....................................................................................................................................................146

23.2.4 Programming Interface......................................................................................................................................146

23.2.5 Loadable Module Operations.............................................................................................................................147

Chapter 24

Inter-IC (I2C) Driver

24.1 Introduction.....................................................................................................................................................................149

24.1.1 I2C Bus Driver Overview..................................................................................................................................149

24.1.2 I2C Device Driver Overview.............................................................................................................................150

24.1.3 Hardware Operation...........................................................................................................................................150

24.2 Software Operation.........................................................................................................................................................150

24.2.1 I2C Bus Driver Software Operation...................................................................................................................150

24.2.2 I2C Device Driver Software Operation.............................................................................................................151

24.3 Driver Features................................................................................................................................................................151

24.3.1 Source Code Structure.......................................................................................................................................152

24.3.2 Menu Configuration Options.............................................................................................................................152

24.3.3 Programming Interface......................................................................................................................................152

24.3.4 Interrupt Requirements......................................................................................................................................152

Chapter 25

Enhanced Configurable Serial Peripheral Interface (ECSPI) Driver

25.1 Introduction.....................................................................................................................................................................155

25.1.1 Hardware Operation...........................................................................................................................................155

25.2 Software Operation.........................................................................................................................................................156

25.2.1 SPI Sub-System in Linux...................................................................................................................................156

25.2.2 Software Limitations..........................................................................................................................................157

25.2.3 Standard Operations...........................................................................................................................................157

25.2.4 ECSPI Synchronous Operation..........................................................................................................................158

25.3 Driver Features................................................................................................................................................................160

25.3.1 Source Code Structure.......................................................................................................................................160

25.3.2 Menu Configuration Options.............................................................................................................................160

i.MX 6SoloLite Linux Reference Manual, Rev. L3.0.35_4.1.0, 09/2013

12 Freescale Semiconductor, Inc.

Page 13

Section number Title Page

25.3.3 Programming Interface......................................................................................................................................160

25.3.4 Interrupt Requirements......................................................................................................................................161

Chapter 26

ARC USB Driver

26.1 Introduction.....................................................................................................................................................................163

26.1.1 Architectural Overview......................................................................................................................................163

26.2 Hardware Operation........................................................................................................................................................164

26.2.1 Software Operation............................................................................................................................................164

26.2.2 Source Code Structure.......................................................................................................................................165

26.2.3 Menu Configuration Options.............................................................................................................................166

26.2.4 Programming Interface......................................................................................................................................169

26.3 System WakeUp..............................................................................................................................................................169

26.3.1 USB Wakeup usage...........................................................................................................................................169

26.3.2 How to Enable USB WakeUp System Ability...................................................................................................169

26.3.3 WakeUp Events Supported by USB..................................................................................................................170

26.3.4 How to Close the USB Child Device Power......................................................................................................171

Chapter 27

Fast Ethernet Controller (FEC) Driver

27.1 Introduction.....................................................................................................................................................................173

27.2 Hardware Operation........................................................................................................................................................173

27.2.1 Software Operation............................................................................................................................................176

27.2.2 Source Code Structure.......................................................................................................................................176

27.2.3 Menu Configuration Options.............................................................................................................................176

27.3 Programming Interface...................................................................................................................................................177

27.3.1 Device-Specific Defines....................................................................................................................................177

27.3.2 Getting a MAC Address.....................................................................................................................................178

Chapter 28

Universal Asynchronous Receiver/Transmitter (UART) Driver

28.1 Introduction.....................................................................................................................................................................179

i.MX 6SoloLite Linux Reference Manual, Rev. L3.0.35_4.1.0, 09/2013

Freescale Semiconductor, Inc. 13

Page 14

Section number Title Page

28.2 Hardware Operation........................................................................................................................................................180

28.2.1 Software Operation............................................................................................................................................180

28.2.2 Driver Features...................................................................................................................................................181

28.2.3 Source Code Structure.......................................................................................................................................181

28.3 Configuration..................................................................................................................................................................182

28.3.1 Menu Configuration Options.............................................................................................................................182

28.3.2 Source Code Configuration Options..................................................................................................................183

28.3.3 Chip Configuration Options...............................................................................................................................183

28.3.4 Board Configuration Options.............................................................................................................................183

28.4 Programming Interface...................................................................................................................................................183

28.4.1 Interrupt Requirements......................................................................................................................................183

Chapter 29

Pulse-Width Modulator (PWM) Driver

29.1 Introduction.....................................................................................................................................................................185

29.1.1 Hardware Operation...........................................................................................................................................185

29.1.2 Clocks.................................................................................................................................................................186

29.1.3 Software Operation............................................................................................................................................187

29.1.4 Driver Features...................................................................................................................................................187

29.1.5 Source Code Structure.......................................................................................................................................187

29.1.6 Menu Configuration Options.............................................................................................................................188

Chapter 30

Watchdog (WDOG) Driver

30.1 Introduction.....................................................................................................................................................................189

30.1.1 Hardware Operation...........................................................................................................................................189

30.1.2 Software Operation............................................................................................................................................189

30.2 Generic WDOG Driver...................................................................................................................................................190

30.2.1 Driver Features...................................................................................................................................................190

30.2.2 Menu Configuration Options.............................................................................................................................190

30.2.3 Source Code Structure.......................................................................................................................................190

i.MX 6SoloLite Linux Reference Manual, Rev. L3.0.35_4.1.0, 09/2013

14 Freescale Semiconductor, Inc.

Page 15

Section number Title Page

30.2.4 Programming Interface......................................................................................................................................191

Chapter 31

OProfile

31.1 Introduction.....................................................................................................................................................................193

31.1.1 Overview............................................................................................................................................................193

31.1.2 Features..............................................................................................................................................................193

31.1.3 Hardware Operation...........................................................................................................................................194

31.2 Software Operation.........................................................................................................................................................194

31.2.1 Architecture Specific Components....................................................................................................................194

31.2.2 oprofilefs Pseudo Filesystem.............................................................................................................................195

31.2.3 Generic Kernel Driver........................................................................................................................................195

31.2.4 OProfile Daemon...............................................................................................................................................195

31.2.5 Post Profiling Tools...........................................................................................................................................196

31.3 Requirements..................................................................................................................................................................196

31.3.1 Source Code Structure.......................................................................................................................................196

31.3.2 Menu Configuration Options.............................................................................................................................196

31.3.3 Programming Interface......................................................................................................................................197

31.3.4 Interrupt Requirements......................................................................................................................................197

i.MX 6SoloLite Linux Reference Manual, Rev. L3.0.35_4.1.0, 09/2013

Freescale Semiconductor, Inc. 15

Page 16

i.MX 6SoloLite Linux Reference Manual, Rev. L3.0.35_4.1.0, 09/2013

16 Freescale Semiconductor, Inc.

Page 17

Chapter 1

About This Book

1.1 Audience

This document is targeted to individuals who will port the i.MX Linux BSP to customerspecific products.

The audience is expected to have a working knowledge of the Linux 3.0 kernel internals,

driver models, and i.MX processors.

1.1.1 Conventions

This document uses the following notational conventions:

• Courier monospaced type indicate commands, command parameters, code examples,

and file and directory names.

• Italic type indicates replaceable command or function parameters.

• Bold type indicates function names.

1.1.2 Definitions, Acronyms, and Abbreviations

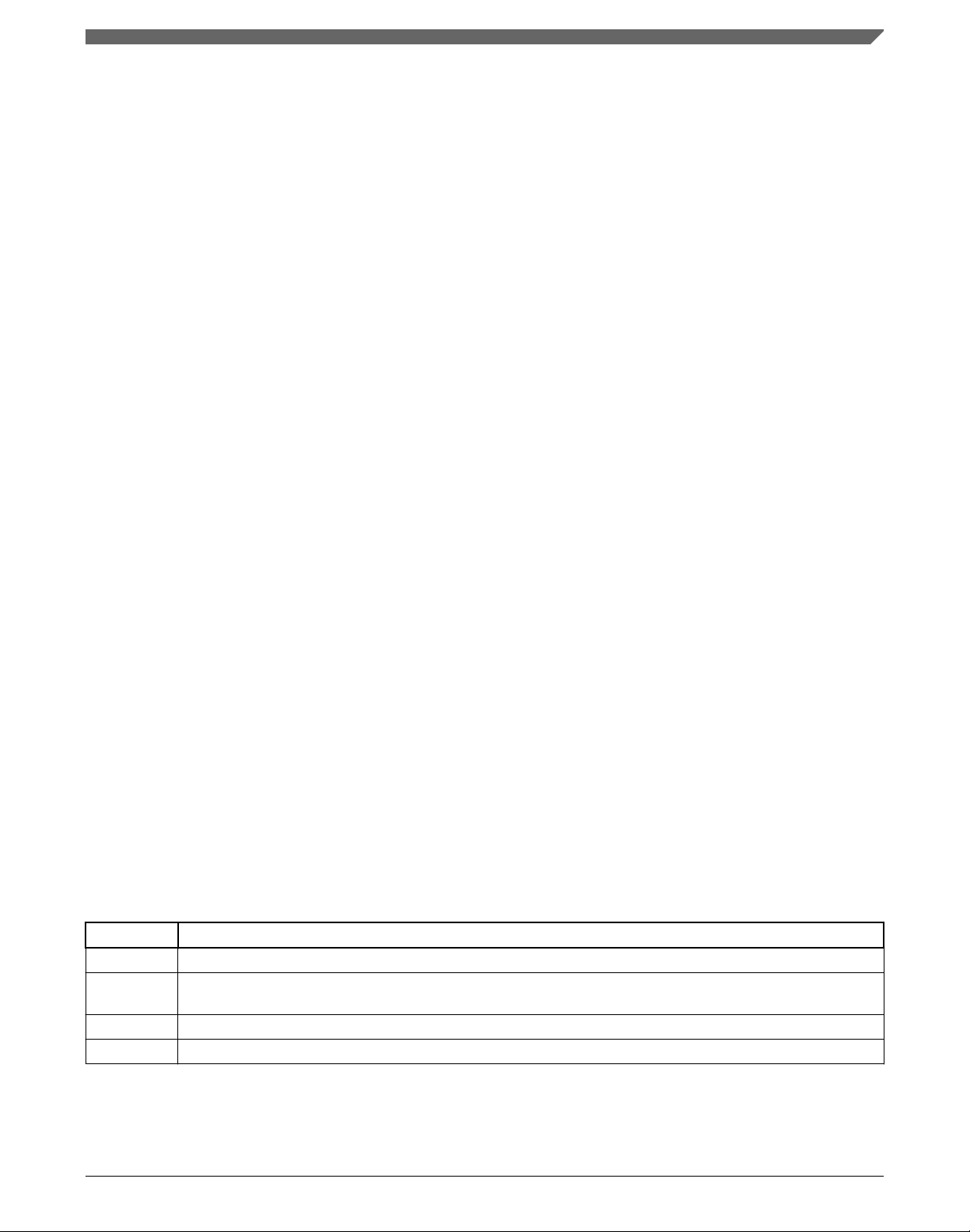

The following table defines the acronyms and abbreviations used in this document.

Definitions and Acronyms

Term Definition

ADC Asynchronous Display Controller

address

translation

API Application Programming Interface

®

ARM

Freescale Semiconductor, Inc. 17

Address conversion from virtual domain to physical domain

Advanced RISC Machines processor architecture

Table continues on the next page...

i.MX 6SoloLite Linux Reference Manual, Rev. L3.0.35_4.1.0, 09/2013

Page 18

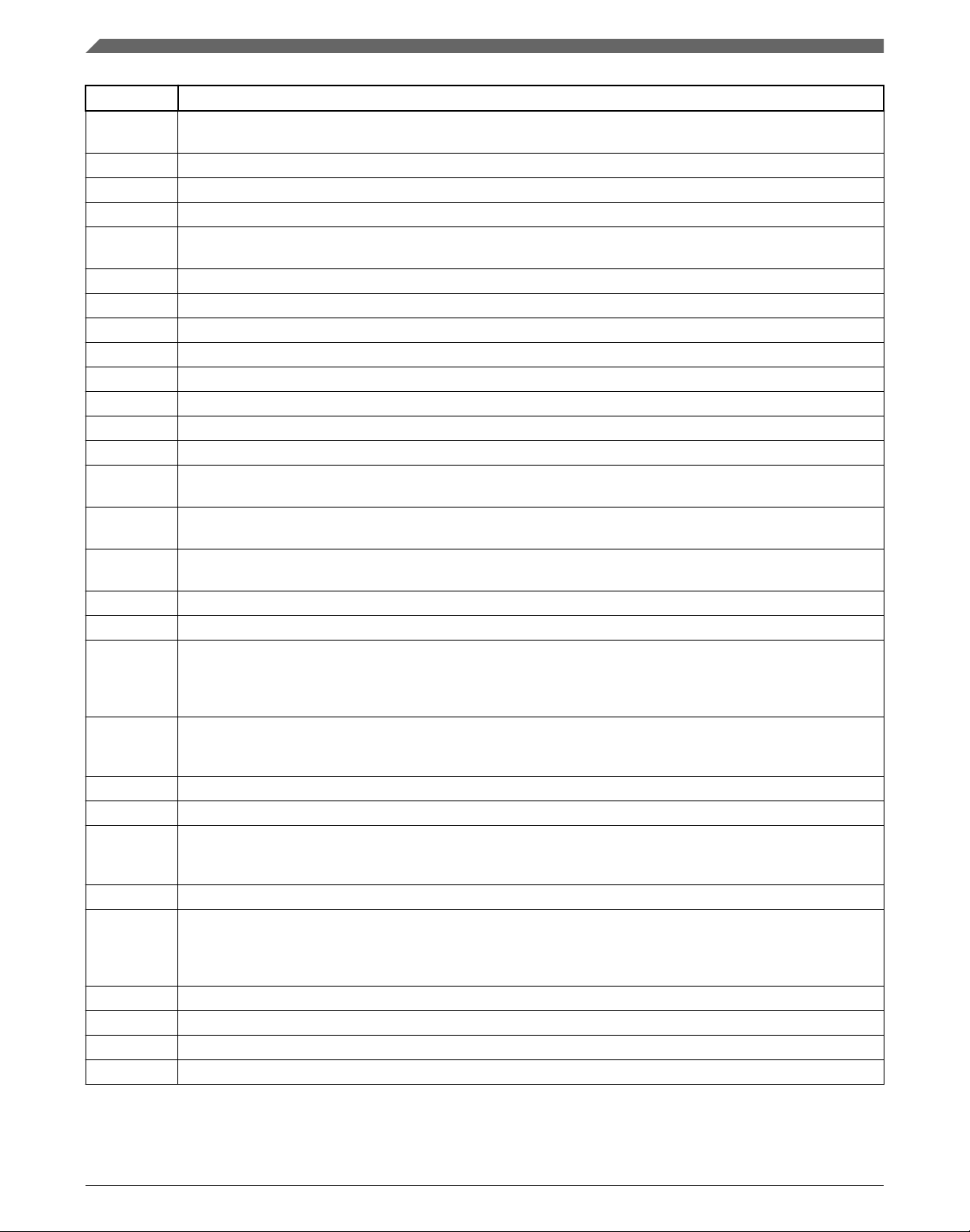

Audience

Term Definition

AUDMUX Digital audio MUX-provides a programmable interconnection for voice, audio, and synchronous data routing

between host serial interfaces and peripheral serial interfaces

BCD Binary Coded Decimal

bus A path between several devices through data lines

bus load The percentage of time a bus is busy

CODEC Coder/decoder or compression/decompression algorithm-used to encode and decode (or compress and

decompress) various types of data

CPU Central Processing Unit-generic term used to describe a processing core

CRC Cyclic Redundancy Check-Bit error protection method for data communication

CSI Camera Sensor Interface

DFS Dynamic Frequency Scaling

DMA Direct Memory Access-an independent block that can initiate memory-to-memory data transfers

DPM Dynamic Power Management

DRAM Dynamic Random Access Memory

DVFS Dynamic Voltage Frequency Scaling

EMI External Memory Interface-controls all IC external memory accesses (read/write/erase/program) from all the

masters in the system

Endian Refers to byte ordering of data in memory. Little endian means that the least significant byte of the data is

stored in a lower address than the most significant byte. In big endian, the order of the bytes is reversed

EPIT Enhanced Periodic Interrupt Timer-a 32-bit set and forget timer capable of providing precise interrupts at

regular intervals with minimal processor intervention

FCS Frame Checker Sequence

FIFO First In First Out

FIPS Federal Information Processing Standards-United States Government technical standards published by the

National Institute of Standards and Technology (NIST). NIST develops FIPS when there are compelling

Federal government requirements such as for security and interoperability but no acceptable industry

standards

FIPS-140 Security requirements for cryptographic modules-Federal Information Processing Standard 140-2(FIPS 140-2)

is a standard that describes US Federal government requirements that IT products should meet for Sensitive,

but Unclassified (SBU) use

Flash A non-volatile storage device similar to EEPROM, where erasing can be done only in blocks or the entire chip.

Flash path Path within ROM bootstrap pointing to an executable Flash application

Flush Procedure to reach cache coherency. Refers to removing a data line from cache. This process includes

cleaning the line, invalidating its VBR and resetting the tag valid indicator. The flush is triggered by a software

command

GPIO General Purpose Input/Output

hash Hash values are produced to access secure data. A hash value (or simply hash), also called a message

digest, is a number generated from a string of text. The hash is substantially smaller than the text itself, and is

generated by a formula in such a way that it is extremely unlikely that some other text produces the same hash

value.

I/O Input/Output

ICE In-Circuit Emulation

IP Intellectual Property

ISR Interrupt Service Routine

Table continues on the next page...

i.MX 6SoloLite Linux Reference Manual, Rev. L3.0.35_4.1.0, 09/2013

18 Freescale Semiconductor, Inc.

Page 19

Chapter 1 About This Book

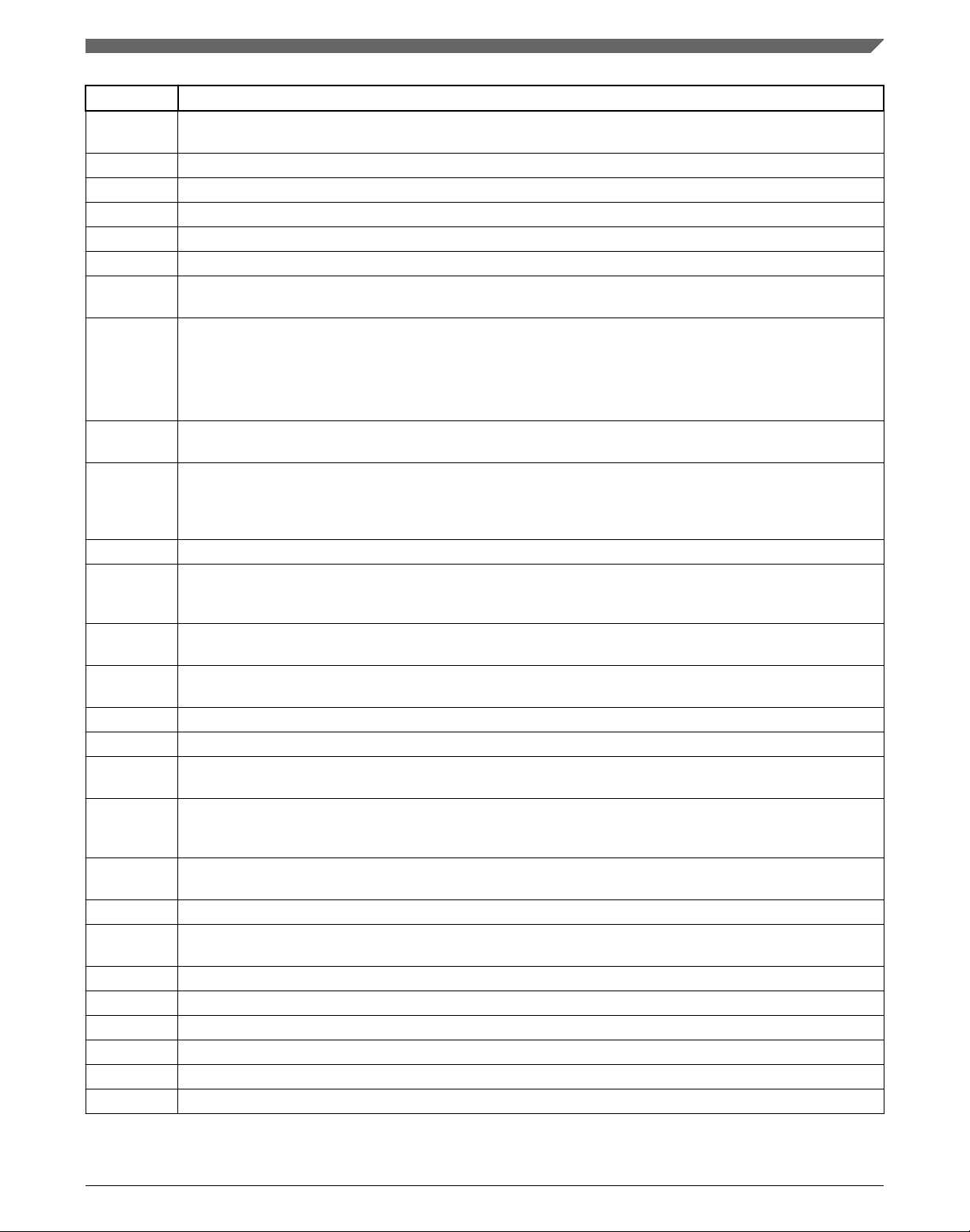

Term Definition

JTAG JTAG (IEEE Standard 1149.1) A standard specifying how to control and monitor the pins of compliant devices

on a printed circuit board

Kill Abort a memory access

KPP KeyPad Port-16-bit peripheral used as a keypad matrix interface or as general purpose input/output (I/O)

line Refers to a unit of information in the cache that is associated with a tag

LRU Least Recently Used-a policy for line replacement in the cache

MMU Memory Management Unit-a component responsible for memory protection and address translation

MPEG Moving Picture Experts Group-an ISO committee that generates standards for digital video compression and

audio. It is also the name of the algorithms used to compress moving pictures and video

MPEG

standards

MQSPI Multiple Queue Serial Peripheral Interface-used to perform serial programming operations necessary to

NAND Flash Flash ROM technology-NAND Flash architecture is one of two flash technologies (the other being NOR) used

NOR Flash See NAND Flash

PCMCIA Personal Computer Memory Card International Association-a multi-company organization that has developed

physical

address

PLL Phase Locked Loop-an electronic circuit controlling an oscillator so that it maintains a constant phase angle (a

RAM Random Access Memory

RAM path Path within ROM bootstrap leading to the downloading and the execution of a RAM application

RGB The RGB color model is based on the additive model in which Red, Green, and Blue light are combined to

RGBA RGBA color space stands for Red Green Blue Alpha. The alpha channel is the transparency channel, and is

RNGA Random Number Generator Accelerator-a security hardware module that produces 32-bit pseudo random

ROM Read Only Memory

ROM

bootstrap

RTIC Real-Time Integrity Checker-a security hardware module

SCC SeCurity Controller-a security hardware module

SDMA Smart Direct Memory Access

SDRAM Synchronous Dynamic Random Access Memory

SoC System on a Chip

SPBA Shared Peripheral Bus Arbiter-a three-to-one IP-Bus arbiter, with a resource-locking mechanism

Several standards of compression for moving pictures and video:

• MPEG-1 is optimized for CD-ROM and is the basis for MP3

• MPEG-2 is defined for broadcast video in applications such as digital television set-top boxes and DVD

• MPEG-3 was merged into MPEG-2

• MPEG-4 is a standard for low-bandwidth video telephony and multimedia on the World-Wide Web

configure radio subsystems and selected peripherals

in memory cards such as the Compact Flash cards. NAND is best suited to flash devices requiring high

capacity data storage. NAND flash devices offer storage space up to 512-Mbyte and offers faster erase, write,

and read capabilities over NOR architecture

a standard for small, credit card-sized devices, called PC Cards. There are three types of PCMCIA cards that

have the same rectangular size (85.6 by 54 millimeters), but different widths

The address by which the memory in the system is physically accessed

lock) on the frequency of an input, or reference, signal

create other colors. The abbreviation RGB comes from the three primary colors in additive light models

unique to this color space. RGBA, like RGB, is an additive color space, so the more of a color placed, the

lighter the picture gets. PNG is the best known image format that uses the RGBA color space

numbers as part of the security module

Internal boot code encompassing the main boot flow as well as exception vectors

Table continues on the next page...

i.MX 6SoloLite Linux Reference Manual, Rev. L3.0.35_4.1.0, 09/2013

Freescale Semiconductor, Inc. 19

Page 20

Audience

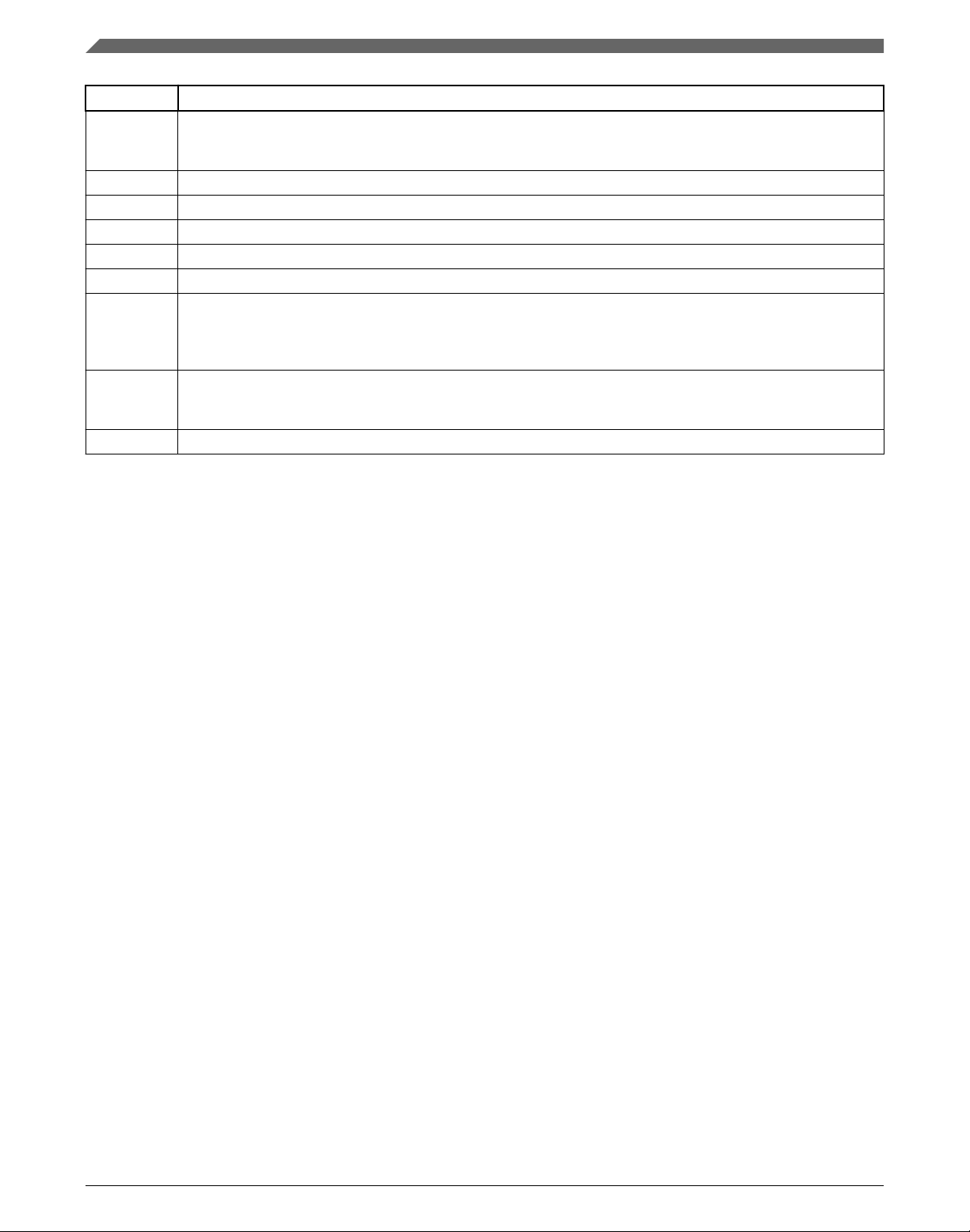

Term Definition

SPI Serial Peripheral Interface-a full-duplex synchronous serial interface for connecting low-/medium-bandwidth

external devices using four wires. SPI devices communicate using a master/slave relationship over two data

lines and two control lines: Also see SS, SCLK, MISO, and MOSI

SRAM Static Random Access Memory

SSI Synchronous-Serial Interface-standardized interface for serial data transfer

TBD To Be Determined

UART Universal Asynchronous Receiver/Transmitter-asynchronous serial communication to external devices

UID Unique ID-a field in the processor and CSF identifying a device or group of devices

USB Universal Serial Bus-an external bus standard that supports high speed data transfers. The USB 1.1

specification supports data transfer rates of up to 12 Mb/s and USB 2.0 has a maximum transfer rate of 480

Mbps. A single USB port can be used to connect up to 127 peripheral devices, such as mice, modems, and

keyboards. USB also supports Plug-and-Play installation and hot plugging

USBOTG USB On The Go-an extension of the USB 2.0 specification for connecting peripheral devices to each other.

USBOTG devices, also known as dual-role peripherals, can act as limited hosts or peripherals themselves

depending on how the cables are connected to the devices, and they also can connect to a host PC

word A group of bits comprising 32-bits

i.MX 6SoloLite Linux Reference Manual, Rev. L3.0.35_4.1.0, 09/2013

20 Freescale Semiconductor, Inc.

Page 21

Chapter 2

Introduction

2.1 Overview

The i.MX family Linux Board Support Package (BSP) supports the Linux Operating

System (OS) on the following processor:

• i.MX 6SoloLite Applications Processor

The purpose of this software package is to support Linux on the i.MX 6SoloLite family

of Integrated Circuits (ICs) and their associated platforms. It provides the necessary

software to interface the standard open-source Linux kernel to the i.MX hardware. The

goal is to enable Freescale customers to rapidly build products based on i.MX devices

that use the Linux OS.

The BSP is not a platform or product reference implementation. It does not contain all of

the product-specific drivers, hardware-independent software stacks, Graphical User

Interface (GUI) components, Java Virtual Machine (JVM), and applications required for

a product. Some of these are made available in their original open-source form as part of

the base kernel.

The BSP is not intended to be used for silicon verification. While it can play a role in

this, the BSP functionality and the tests run on the BSP do not have sufficient coverage to

replace traditional silicon verification test suites.

2.1.1 Software Base

The i.MX BSP is based on version 3.0.35 of the Linux kernel from the official Linux

kernel web site (http://www.kernel.org ). It is enhanced with the features provided by

Freescale.

i.MX 6SoloLite Linux Reference Manual, Rev. L3.0.35_4.1.0, 09/2013

Freescale Semiconductor, Inc. 21

Page 22

Overview

2.1.2 Features

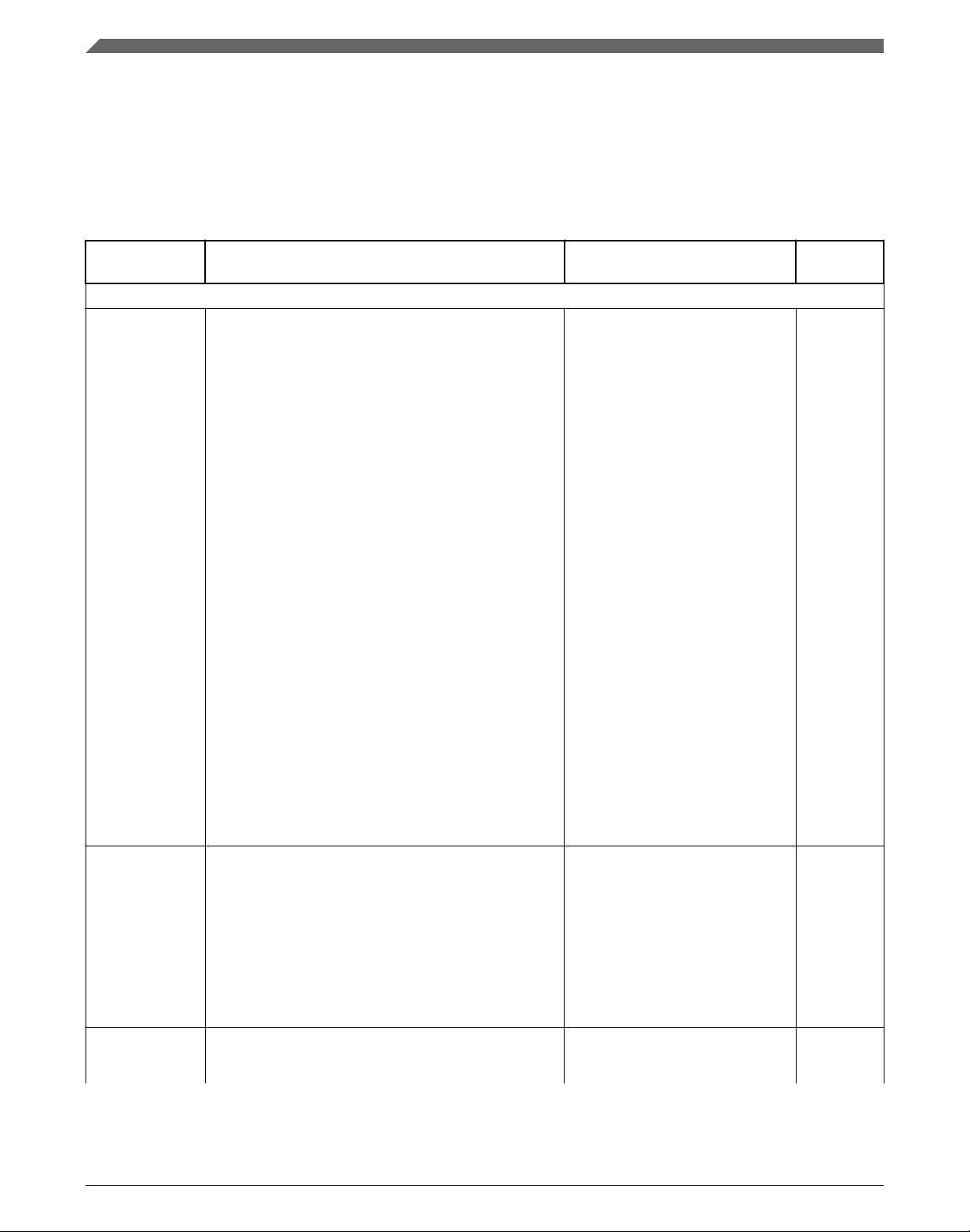

Table below describes the features supported by the Linux BSP for specific platforms.

Table 2-1. Linux BSP Supported Features

Feature Description Chapter Source Applicable

Platform

Machine Specific Layer

MSL Machine Specific Layer (MSL) supports interrupts,

Timer, Memory Map, GPIO/IOMUX, SPBA, SDMA.

• Interrupts GIC: The linux kernel contains common

ARM GIC interrupts handling code.

• Timer (GPT): The General Purpose Timer (GPT)

is set up to generate an interrupt as programmed

to provide OS ticks. Linux facilitates timer use

through various functions for timing delays,

measurement, events, alarms, high resolution

timer features, and so on. Linux defines the MSL

timer API required for the OS-tick timer and does

not expose it beyond the kernel tick

implementation.

• GPIO/EDIO/IOMUX: The GPIO and EDIO

components in the MSL provide an abstraction

layer between the various drivers and the

configuration and utilization of the system,

including GPIO, IOMUX, and external board I/O.

The IO software module is board-specific, and

resides in the MSL layer as a self-contained set

of files. I/O configuration changes are centralized

in the GPIO module so that changes are not

required in the various drivers.

• SPBA: The Shared Peripheral Bus Arbiter

(SPBA) provides an arbitration mechanism

among multiple masters to allow access to the

shared peripherals. The SPBA implementation

under MSL defines the API to allow different

masters to take or release ownership of a shared

peripheral.

SDMA API The Smart Direct Memory Access (SDMA) API driver

controls the SDMA hardware. It provides an API to

other drivers for transferring data between MCU, DSP

and peripherals. . The SDMA controller is responsible

for transferring data between the MCU memory space,

peripherals, and the DSP memory space. The SDMA

API allows other drivers to initialize the scripts, pass

parameters and control their execution. SDMA is based

on a microRISC engine that runs channel-specific

scripts.

Low-level PM

Drivers

The low-level power management driver is responsible

for implementing hardware-specific operations to meet

power requirements and also to conserve power on the

Table continues on the next page...

Machine Specific Layer (MSL) All

Smart Direct Memory Access

(SDMA) API

Low-level Power Management

(PM) Driver

i.MX

6SoloLite

i.MX

6SoloLite

i.MX 6SoloLite Linux Reference Manual, Rev. L3.0.35_4.1.0, 09/2013

22 Freescale Semiconductor, Inc.

Page 23

Chapter 2 Introduction

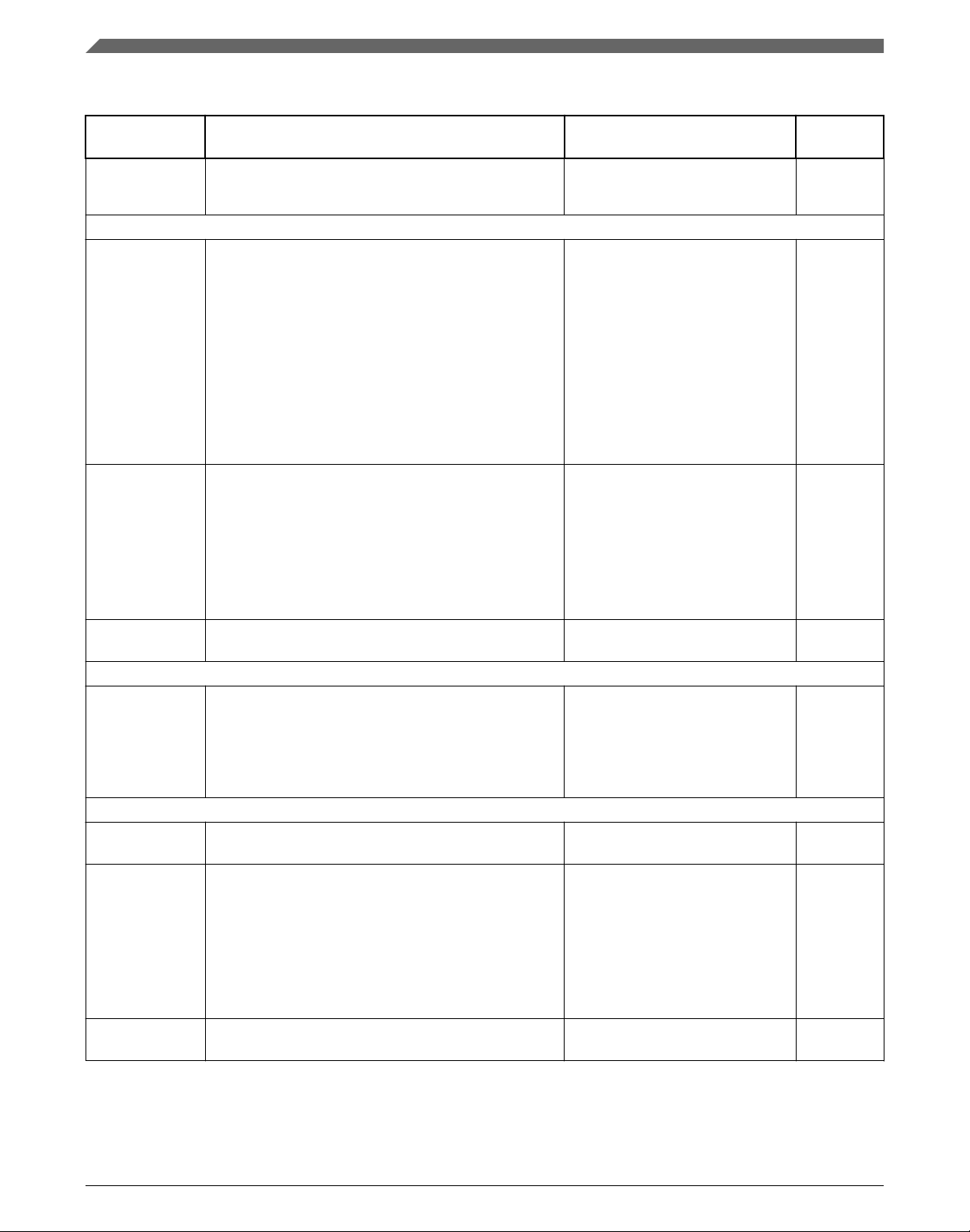

Table 2-1. Linux BSP Supported Features (continued)

Feature Description Chapter Source Applicable

development platforms. Driver implementations are

often different for different platforms. It is used by the

DPM layer.

CPU Frequency

Scaling

DVFS The Dynamic Voltage Frequency Scaling (DVFS)

Multimedia Drivers

LCD The LCD interface driver supports the Samsung

EPDC The Electrophoretic Display Controller (EPDC) is a

SPDC SPDC is a direct-drive active matrix EPD controller

PxP The Pixel Pipeline (PxP) DMA-ENGINE driver provides

Sound Drivers

ALSA Sound The Advanced Linux Sound Architecture (ALSA) is a

Memory Drivers

SPI NOR MTD The SPI NOR MTD driver provides the support to the

Input Device Drivers

Networking Drivers

ENET The ENET Driver performs the full set of IEEE 802.3/

The CPU frequency scaling device driver allows the

clock speed of the CPUs to be changed on the fly.

device driver allows simple dynamic voltage frequency

scaling. The frequency of the core clock domain and

the voltage of the core power domain can be changed

on the fly with all modules continuing their normal

operations.

LMS430xx 4.3" WQVGA LCD panel.

direct-drive active matrix EPD controller designed to

drive E Ink EPD panels supporting a wide variety of

TFT backplanes.

designed to drive Sipix panel for E-Book application.

The SPDC provides control signals for the source driver

and gate drivers. This IP provides a high performance,

low cost solution for SiPix EPDs (Electronic Paper

Display).

a unique API, which are implemented as a dmaengine

client that smooths over the details of different

hardware offload engine implementations.

sound driver that provides ALSA and OSS compatible

applications with the means to perform audio playback

and recording functions. ALSA has a user-space

component called ALSAlib that can extend the features

of audio hardware by emulating the same in software

(user space), such as resampling, software mixing,

snooping, and so on. The ASoC Sound driver supports

stereo CODEC playback and capture through SSI.

Atmel data Flash using the SPI interface.

Ethernet CSMA/CD media access control and channel

interface functions. The FEC requires an external

interface adaptor and transceiver function to complete

Table continues on the next page...

CPU Frequency Scaling

(CPUFREQ) Driver

Dynamic Voltage Frequency

Scaling (DVFS) Driver

ELCDIF Frame Buffer Driver i.MX

Electrophoretic Display Controller

(EPDC) Frame Buffer

Sipix Display Controller (SPDC)

Frame Buffer

PXP DMA-ENGINE Driver i.MX

ALSA Sound Driver i.MX

SPI NOR Flash Memory

Technology Device (MTD) Driver

Fast Ethernet Controller (FEC)

Driver

i.MX

6SoloLite

i.MX

6SoloLite

6SoloLite

i.MX

6SoloLite

i.MX

6SoloLite

6SoloLite

6SoloLite

i.MX

6SoloLite

i.MX

6SoloLite

Platform

i.MX 6SoloLite Linux Reference Manual, Rev. L3.0.35_4.1.0, 09/2013

Freescale Semiconductor, Inc. 23

Page 24

Overview

Table 2-1. Linux BSP Supported Features (continued)

Feature Description Chapter Source Applicable

the interface to the Ethernet media. It supports half or

full-duplex operation on 10M\100M related Ethernet

networks.

Bus Drivers

I2C The I2C bus driver is a low-level interface that is used

to interface with the I2C bus. This driver is invoked by

the I2C chip driver; it is not exposed to the user space.

The standard Linux kernel contains a core I2C module

that is used by the chip driver to access the bus driver

to transfer data over the I2C bus. This bus driver

supports:

• Compatibility with the I2C bus standard

• Bit rates up to 400 Kbps

• Standard I2C master mode

• Power management features by suspending and

resuming I2C.

CSPI The low-level Enhanced Configurable Serial Peripheral

Interface (ECSPI) driver interfaces a custom, kernelspace API to both ECSPI modules. It supports the

following features:

• Interrupt-driven transmit/receive of SPI frames

• Multi-client management

• Priority management between clients

• SPI device configuration per client

MMC/SD/SDIO uSDHC

UART Drivers

MXC UART The Universal Asynchronous Receiver/Transmitter

General Drivers

USB The USB driver implements a standard Linux driver

WatchDog The Watchdog Timer module protects against system

MXC PWM driver The MXC PWM driver provides the interfaces to access

The MMC/SD/SDIO Host driver implements the

standard Linux driver interface to eSDHC.

(UART) driver interfaces the Linux serial driver API to

all of the UART ports. A kernel configuration parameter

gives the user the ability to choose the UART driver

and also to choose whether the UART should be used

as the system console.

interface to the ARC USB-OTG controller.

failures by providing an escape from unexpected hang

or infinite loop situations or programming errors. This

WDOG implements the following features:

• Generates a reset signal if it is enabled but not

serviced within a predefined time-out value

• Does not generate a reset signal if it is serviced

within a predefined time-out value

MXC PWM signals

Inter-IC (I2C) Driver i.MX

Enhanced Configurable Serial

Peripheral Interface (ECSPI) Driver

MMC/SD/SDIO Host Driver i.MX

Universal Asynchronous Receiver/

Transmitter (UART) Driver

ARC USB Driver i.MX

Watchdog (WDOG) Driver i.MX

Pulse-Width Modulator (PWM)

Driver

Platform

6SoloLite

i.MX

6SoloLite

6SoloLite

i.MX

6SoloLite

6SoloLite

6SoloLite

i.MX

6SoloLite

Table continues on the next page...

i.MX 6SoloLite Linux Reference Manual, Rev. L3.0.35_4.1.0, 09/2013

24 Freescale Semiconductor, Inc.

Page 25

Chapter 2 Introduction

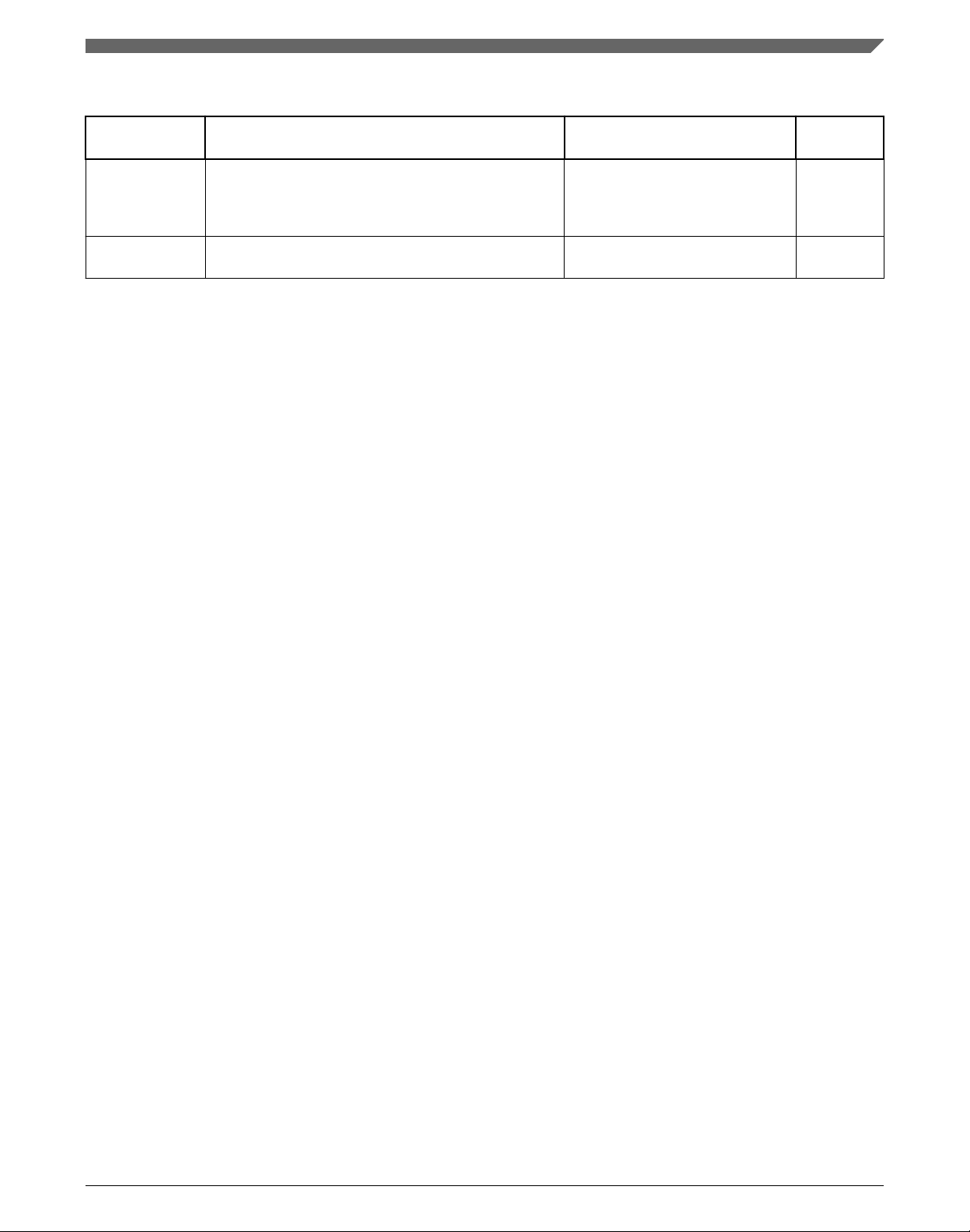

Table 2-1. Linux BSP Supported Features (continued)

Feature Description Chapter Source Applicable

Thermal Driver Thermal driver is a necessary driver for monitoring and

protecting the SoC. The thermal driver will monitor the

SoC's temperature in a certain frequency. It defines

three trip points: critical, hot, and active.

OProfile OProfile is a system-wide profiler for Linux systems,

capable of profiling all running code at low overhead.

Thermal Driver i.MX

6SoloLite

OProfile i.MX

6SoloLite

Platform

i.MX 6SoloLite Linux Reference Manual, Rev. L3.0.35_4.1.0, 09/2013

Freescale Semiconductor, Inc. 25

Page 26

Overview

i.MX 6SoloLite Linux Reference Manual, Rev. L3.0.35_4.1.0, 09/2013

26 Freescale Semiconductor, Inc.

Page 27

Chapter 3

Machine Specific Layer (MSL)

3.1 Introduction

The Machine Specific Layer (MSL) provides the Linux kernel with the following

machine-dependent components:

• Interrupts including GPIO and EDIO (only on certain platforms)

• Timer

• Memory map

• General Purpose Input/Output (GPIO) including IOMUX on certain platforms

• Shared Peripheral Bus Arbiter (SPBA)

• Smart Direct Memory Access (SDMA)

These modules are normally available in the following directory:

<ltib_dir>/rpm/BUILD/linux/arch/arm/mach-mx6 for i.MX 6 platform

The header files are implemented under the following directory:

<ltib_dir>/rpm/BUILD/linux/arch/arm/plat-mxc/include/mach

The MSL layer contains not only the modules common to all the boards using the same

processor, such as the interrupts and timer, but it also contains modules specific to each