Page 1

S12CPUV2

Reference Manual

HCS12

Microcontrollers

S12CPUV2

Rev. 4.0

03/2006

freescale.com

Page 2

Page 3

S12CPUV2

Reference Manual

To provide the most up-to-date information, the revision of our documents on the World Wide Web will be

the most current. Your printed copy may be an earlier revision. To verify you have the latest information

available, refer to:

http://www.freescale.com

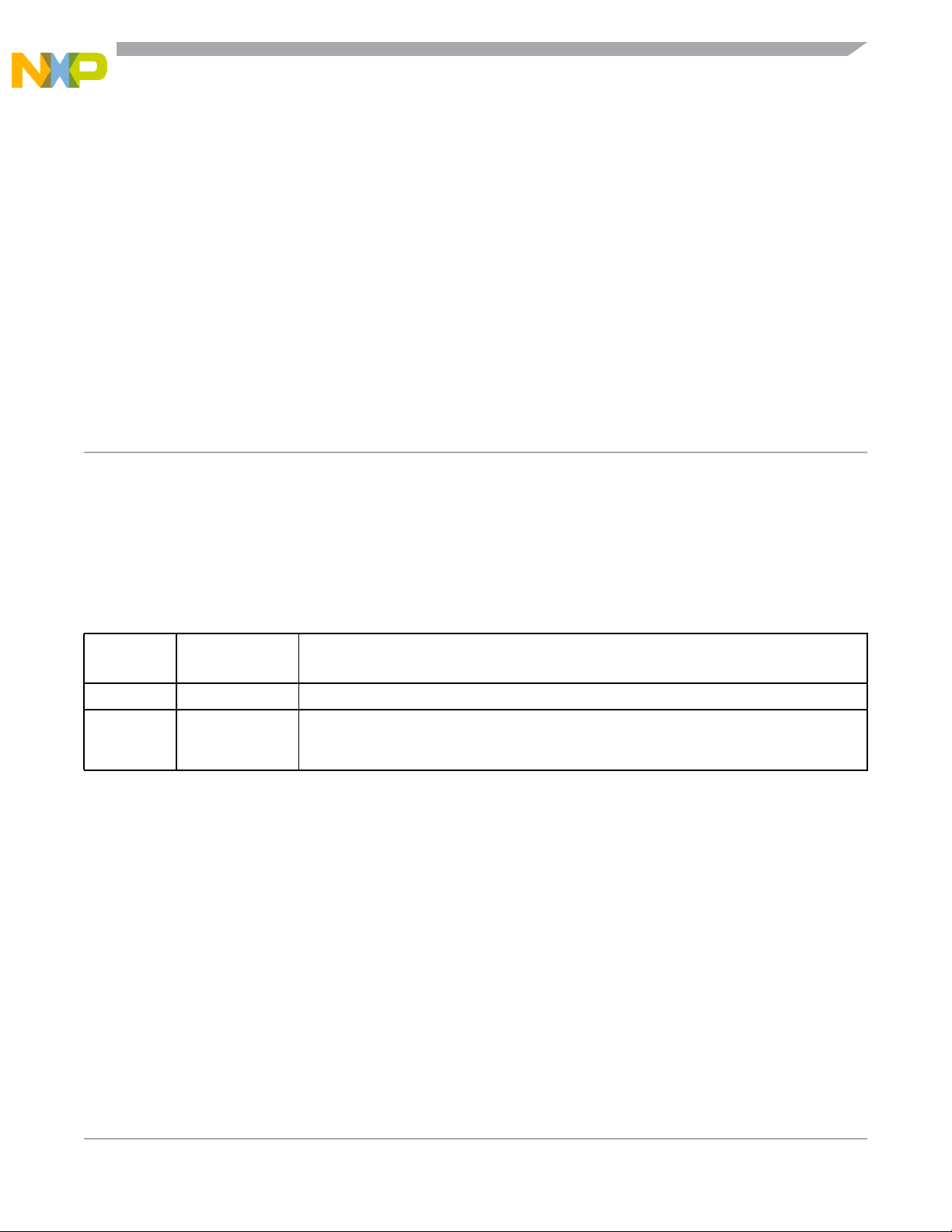

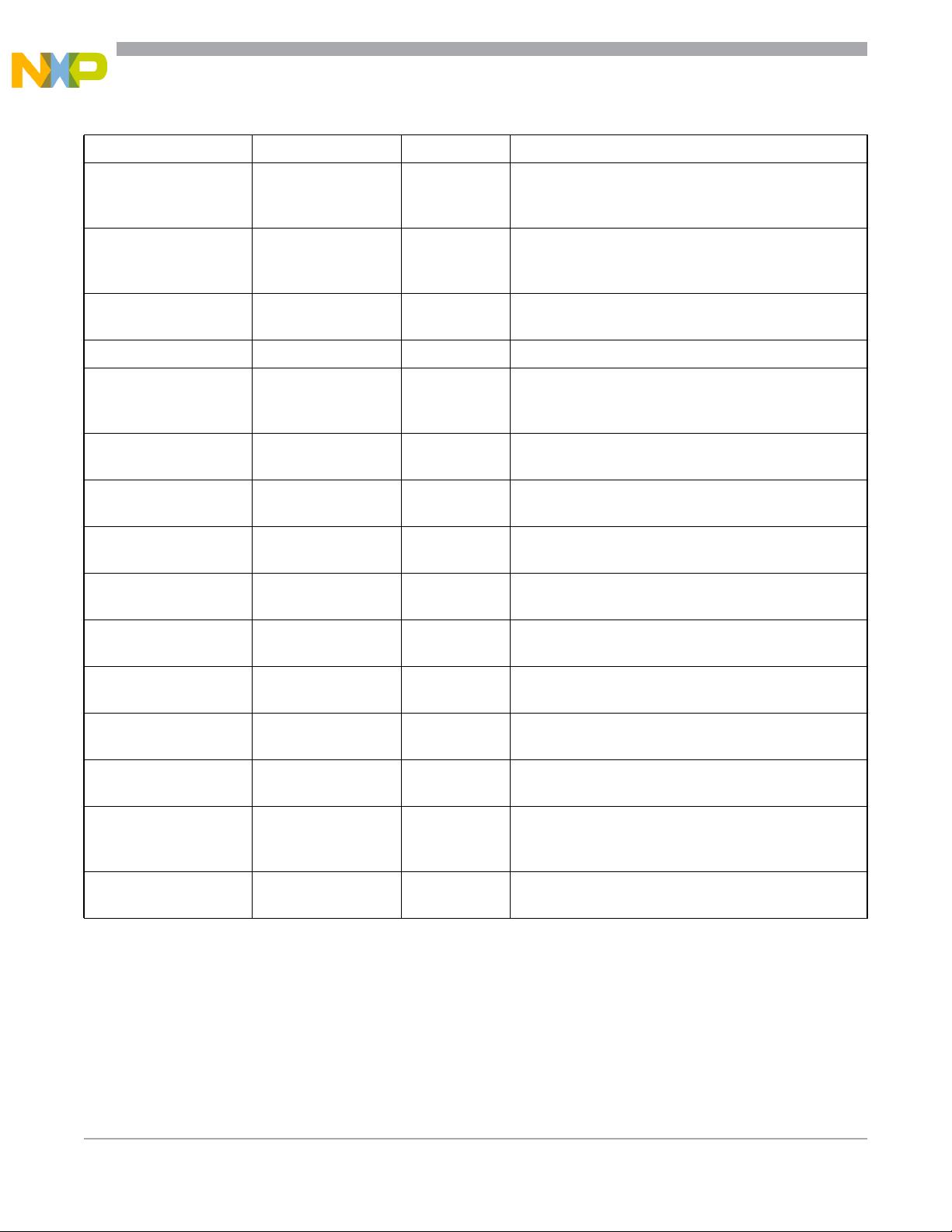

The following revision history table summarizes changes contained in this document.

Revision History

Revision

Number

3.0 April, 2002 Incorporated information covering HCS12 Family of 16-bit MCUs throughout the book.

4.0 March, 2006 Reformatted to Freescale publication standards.

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc.

© Freescale Semiconductor, Inc., 2005. All rights reserved.

Date Summary of Changes

Corrected mistake in ANDCC/TAP descriptions (Instruction Glossary).

Corrected mistake in MEM description (Instruction Glossary).

S12CPUV2 Reference Manual, Rev. 4.0

Freescale Semiconductor 3

Page 4

S12CPUV2 Reference Manual, Rev. 4.0

4 Freescale Semiconductor

Page 5

Reference Manual — S12CPUV2

Table of Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7

Section 1. Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15

Section 2. Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21

Section 3. Addressing Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . .29

Section 4. Instruction Queue . . . . . . . . . . . . . . . . . . . . . . . . . . . . .47

Section 5. Instruction Set Overview . . . . . . . . . . . . . . . . . . . . . . .55

Section 6. Instruction Glossary. . . . . . . . . . . . . . . . . . . . . . . . . . .87

List of Sections

Section 7. Exception Processing. . . . . . . . . . . . . . . . . . . . . . . . .311

Section 8. Instruction Queue . . . . . . . . . . . . . . . . . . . . . . . . . . .323

Section 9. Fuzzy Logic Support. . . . . . . . . . . . . . . . . . . . . . . . . .337

Appendix A. Instruction Reference. . . . . . . . . . . . . . . . . . . . . . .375

Appendix B. M68HC11 to CPU12 Upgrade Path. . . . . . . . . . . . .403

Appendix C. High-Level Language Support. . . . . . . . . . . . . . . .425

Index . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .433

S12CPUV2 Reference Manual, Rev. 4.0

Freescale Semiconductor 5

Page 6

S12CPUV2 Reference Manual, Rev. 4.0

6 Freescale Semiconductor

Page 7

Reference Manual — S12CPUV2

1.1 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15

1.2 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15

1.3 Symbols and Notation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .16

1.3.1 Abbreviations for System Resources . . . . . . . . . . . . . . . . . . . . . . . . . .16

1.3.2 Memory and Addressing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17

1.3.3 Operators . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18

1.3.4 Definitions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .19

2.1 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21

2.2 Programming Model . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21

2.2.1 Accumulators . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22

2.2.2 Index Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22

2.2.3 Stack Pointer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22

2.2.4 Program Counter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .23

2.2.5 Condition Code Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .23

2.2.5.1 S Control Bit. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24

2.2.5.2 X Mask Bit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25

2.2.5.3 H Status Bit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25

2.2.5.4 I Mask Bit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25

2.2.5.5 N Status Bit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .26

2.2.5.6 Z Status Bit. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .26

2.2.5.7 V Status Bit. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .26

2.2.5.8 C Status Bit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .26

Table of Contents

Section 1. Introduction

Section 2. Overview

2.3 Data Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .27

2.4 Memory Organization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .27

2.5 Instruction Queue . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .28

S12CPUV2 Reference Manual, Rev. 4.0

Freescale Semiconductor 7

Page 8

Section 3. Addressing Modes

3.1 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .29

3.2 Mode Summary. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .29

3.3 Effective Address . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .29

3.4 Inherent Addressing Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .31

3.5 Immediate Addressing Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .31

3.6 Direct Addressing Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .32

3.7 Extended Addressing Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .33

3.8 Relative Addressing Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .33

3.9 Indexed Addressing Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .34

3.9.1 5-Bit Constant Offset Indexed Addressing . . . . . . . . . . . . . . . . . . . . . .37

3.9.2 9-Bit Constant Offset Indexed Addressing . . . . . . . . . . . . . . . . . . . . . .37

3.9.3 16-Bit Constant Offset Indexed Addressing . . . . . . . . . . . . . . . . . . . . .38

3.9.4 16-Bit Constant Indirect Indexed Addressing. . . . . . . . . . . . . . . . . . . .38

3.9.5 Auto Pre/Post Decrement/Increment Indexed Addressing. . . . . . . . . .39

3.9.6 Accumulator Offset Indexed Addressing . . . . . . . . . . . . . . . . . . . . . . .40

3.9.7 Accumulator D Indirect Indexed Addressing . . . . . . . . . . . . . . . . . . . .41

3.10 Instructions Using Multiple Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .41

3.10.1 Move Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .41

3.10.2 Bit Manipulation Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .43

3.11 Addressing More than 64 Kbytes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .44

Section 4. Instruction Queue

4.1 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .47

4.2 Queue Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .47

4.2.1 Original M68HC12 Queue Implementation. . . . . . . . . . . . . . . . . . . . . .48

4.2.2 HCS12 Queue Implementation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .48

4.3 Data Movement in the Queue. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .48

4.3.1 No Movement. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .49

4.3.2 Latch Data from Bus (Applies Only to the M68HC12 Queue) . . . . . . .49

4.3.3 Advance and Load from Data Bus . . . . . . . . . . . . . . . . . . . . . . . . . . . .49

4.3.4 Advance and Load from Buffer (Applies Only to M68HC12 Queue) . .49

4.4 Changes in Execution Flow . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .49

4.4.1 Exceptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .50

4.4.2 Subroutines . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .50

4.4.3 Branches . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .51

S12CPUV2 Reference Manual, Rev. 4.0

8 Freescale Semiconductor

Page 9

4.4.3.1 Short Branches. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .52

4.4.3.2 Long Branches. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .52

4.4.3.3 Bit Condition Branches. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .53

4.4.3.4 Loop Primitives. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .53

4.4.4 Jumps. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .53

Section 5. Instruction Set Overview

5.1 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .55

5.2 Instruction Set Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .55

5.3 Load and Store Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .56

5.4 Transfer and Exchange Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . .57

5.5 Move Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .58

5.6 Addition and Subtraction Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . .59

5.7 Binary-Coded Decimal Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .60

5.8 Decrement and Increment Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . .61

5.9 Compare and Test Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .62

5.10 Boolean Logic Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .63

5.11 Clear, Complement, and Negate Instructions. . . . . . . . . . . . . . . . . . . . . .63

5.12 Multiplication and Division Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . .64

5.13 Bit Test and Manipulation Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . .65

5.14 Shift and Rotate Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .66

5.15 Fuzzy Logic Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .67

5.15.1 Fuzzy Logic Membership Instruction . . . . . . . . . . . . . . . . . . . . . . . . . .67

5.15.2 Fuzzy Logic Rule Evaluation Instructions. . . . . . . . . . . . . . . . . . . . . . .67

5.15.3 Fuzzy Logic Weighted Average Instruction . . . . . . . . . . . . . . . . . . . . .68

5.16 Maximum and Minimum Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . .70

5.17 Multiply and Accumulate Instruction . . . . . . . . . . . . . . . . . . . . . . . . . . . . .71

5.18 Table Interpolation Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .72

5.19 Branch Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .73

5.19.1 Short Branch Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .74

5.19.2 Long Branch Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .75

5.19.3 Bit Condition Branch Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . .76

5.20 Loop Primitive Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .77

5.21 Jump and Subroutine Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .78

S12CPUV2 Reference Manual, Rev. 4.0

Freescale Semiconductor 9

Page 10

5.22 Interrupt Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .79

5.23 Index Manipulation Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .81

5.24 Stacking Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .82

5.25 Pointer and Index Calculation Instructions . . . . . . . . . . . . . . . . . . . . . . . .83

5.26 Condition Code Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .84

5.27 Stop and Wait Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .85

5.28 Background Mode and Null Operations . . . . . . . . . . . . . . . . . . . . . . . . . .86

Section 6. Instruction Glossary

6.1 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .87

6.2 Glossary Information. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .88

6.3 Condition Code Changes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .89

6.4 Object Code Notation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .90

6.5 Source Forms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .91

6.6 Cycle-by-Cycle Execution. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .94

6.7 Glossary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .99

Section 7. Exception Processing

7.1 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .311

7.2 Types of Exceptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .311

7.3 Exception Priority . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .312

7.4 Resets. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .313

7.4.1 Power-On Reset. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .314

7.4.2 External Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .314

7.4.3 COP Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .314

7.4.4 Clock Monitor Reset. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .314

7.5 Interrupts. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .315

7.5.1 Non-Maskable Interrupt Request (

7.5.2 Maskable Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .315

7.5.3 Interrupt Recognition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .316

7.5.4 External Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .317

7.5.5 Return-from-Interrupt Instruction (RTI). . . . . . . . . . . . . . . . . . . . . . . .317

XIRQ) . . . . . . . . . . . . . . . . . . . . . .315

7.6 Unimplemented Opcode Trap. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .317

7.7 Software Interrupt Instruction (SWI) . . . . . . . . . . . . . . . . . . . . . . . . . . . .318

S12CPUV2 Reference Manual, Rev. 4.0

10 Freescale Semiconductor

Page 11

7.8 Exception Processing Flow. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .318

7.8.1 Vector Fetch. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .318

7.8.2 Reset Exception Processing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .320

7.8.3 Interrupt and Unimplemented Opcode Trap Exception Processing . .320

Section 8. Instruction Queue

8.1 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .323

8.2 External Reconstruction of the Queue . . . . . . . . . . . . . . . . . . . . . . . . . .323

8.3 Instruction Queue Status Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .324

8.3.1 HCS12 Timing Detail . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .324

8.3.2 M68HC12 Timing Detail . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .325

8.3.3 Null (Code 0:0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .327

8.3.4 LAT — Latch Data from Bus (Code 0:1). . . . . . . . . . . . . . . . . . . . . . .327

8.3.5 ALD — Advance and Load from Data Bus (Code 1:0). . . . . . . . . . . .327

8.3.6 ALL — Advance and Load from Latch (Code 1:1) . . . . . . . . . . . . . . .327

8.3.7 INT — Interrupt Sequence Start (Code 0:1). . . . . . . . . . . . . . . . . . . .327

8.3.8 SEV — Start Instruction on Even Address (Code 1:0). . . . . . . . . . . .328

8.3.9 SOD — Start Instruction on Odd Address (Code 1:1) . . . . . . . . . . . .328

8.4 Queue Reconstruction (for HCS12) . . . . . . . . . . . . . . . . . . . . . . . . . . . .328

8.4.1 Queue Reconstruction Registers (for HCS12) . . . . . . . . . . . . . . . . . .329

8.4.1.1 fetch_add Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .329

8.4.1.2 st1_add, st1_dat Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .329

8.4.1.3 st2_add, st2_dat Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .329

8.4.1.4 st3_add, st3_dat Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .329

8.4.2 Reconstruction Algorithm (for HCS12). . . . . . . . . . . . . . . . . . . . . . . .330

8.5 Queue Reconstruction (for M68HC12) . . . . . . . . . . . . . . . . . . . . . . . . . .331

8.5.1 Queue Reconstruction Registers (for M68HC12). . . . . . . . . . . . . . . .331

8.5.1.1 in_add, in_dat Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .332

8.5.1.2 fetch_add, fetch_dat Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . .332

8.5.1.3 st1_add, st1_dat Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .332

8.5.1.4 st2_add, st2_dat Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .332

8.5.2 Reconstruction Algorithm (for M68HC12). . . . . . . . . . . . . . . . . . . . . .332

8.5.2.1 LAT Decoding. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .333

8.5.2.2 ALD Decoding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .333

8.5.2.3 ALL Decoding. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .333

8.6 Instruction Tagging . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .335

Section 9. Fuzzy Logic Support

S12CPUV2 Reference Manual, Rev. 4.0

Freescale Semiconductor 11

Page 12

9.1 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .337

9.2 Fuzzy Logic Basics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .338

9.2.1 Fuzzification (MEM) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .340

9.2.2 Rule Evaluation (REV and REVW). . . . . . . . . . . . . . . . . . . . . . . . . . .342

9.2.3 Defuzzification (WAV). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .344

9.3 Example Inference Kernel. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .345

9.4 MEM Instruction Details . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .347

9.4.1 Membership Function Definitions. . . . . . . . . . . . . . . . . . . . . . . . . . . .347

9.4.2 Abnormal Membership Function Definitions. . . . . . . . . . . . . . . . . . . .349

9.4.2.1 Abnormal Membership Function Case 1 . . . . . . . . . . . . . . . . . . . .351

9.4.2.2 Abnormal Membership Function Case 2 . . . . . . . . . . . . . . . . . . . .352

9.4.2.3 Abnormal Membership Function Case 3 . . . . . . . . . . . . . . . . . . . .352

9.5 REV and REVW Instruction Details . . . . . . . . . . . . . . . . . . . . . . . . . . . .353

9.5.1 Unweighted Rule Evaluation (REV) . . . . . . . . . . . . . . . . . . . . . . . . . .353

9.5.1.1 Set Up Prior to Executing REV. . . . . . . . . . . . . . . . . . . . . . . . . . . .353

9.5.1.2 Interrupt Details . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .355

9.5.1.3 Cycle-by-Cycle Details for REV . . . . . . . . . . . . . . . . . . . . . . . . . . .355

9.5.2 Weighted Rule Evaluation (REVW) . . . . . . . . . . . . . . . . . . . . . . . . . .359

9.5.2.1 Set Up Prior to Executing REVW. . . . . . . . . . . . . . . . . . . . . . . . . .359

9.5.2.2 Interrupt Details . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .361

9.5.2.3 Cycle-by-Cycle Details for REVW . . . . . . . . . . . . . . . . . . . . . . . . .361

9.6 WAV Instruction Details . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .364

9.6.1 Set Up Prior to Executing WAV . . . . . . . . . . . . . . . . . . . . . . . . . . . . .364

9.6.2 WAV Interrupt Details. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .365

9.6.3 Cycle-by-Cycle Details for WAV and wavr . . . . . . . . . . . . . . . . . . . . .365

9.7 Custom Fuzzy Logic Programming. . . . . . . . . . . . . . . . . . . . . . . . . . . . .369

9.7.1 Fuzzification Variations. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .369

9.7.2 Rule Evaluation Variations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .372

9.7.3 Defuzzification Variations. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .373

Appendix A. Instruction Reference

A.1 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .375

A.2 Stack and Memory Layout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .376

A.3 Interrupt Vector Locations. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .376

A.4 Notation Used in Instruction Set Summary. . . . . . . . . . . . . . . . . . . . . . .377

A.5 Hexadecimal to Decimal Conversion . . . . . . . . . . . . . . . . . . . . . . . . . . .402

S12CPUV2 Reference Manual, Rev. 4.0

12 Freescale Semiconductor

Page 13

A.6 Decimal to Hexadecimal Conversion . . . . . . . . . . . . . . . . . . . . . . . . . . .402

Appendix B. M68HC11 to CPU12 Upgrade Path

B.1 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .403

B.2 CPU12 Design Goals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .403

B.3 Source Code Compatibility . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .404

B.4 Programmer’s Model and Stacking. . . . . . . . . . . . . . . . . . . . . . . . . . . . .407

B.5 True 16-Bit Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .407

B.5.1 Bus Structures . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .407

B.5.2 Instruction Queue. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .408

B.5.3 Stack Function . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .409

B.6 Improved Indexing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .410

B.6.1 Constant Offset Indexing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .412

B.6.2 Auto-Increment Indexing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .413

B.6.3 Accumulator Offset Indexing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .414

B.6.4 Indirect Indexing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .414

B.7 Improved Performance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .415

B.7.1 Reduced Cycle Counts. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .415

B.7.2 Fast Math . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .415

B.7.3 Code Size Reduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .416

B.8 Additional Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .417

B.8.1 Memory-to-Memory Moves. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .420

B.8.2 Universal Transfer and Exchange . . . . . . . . . . . . . . . . . . . . . . . . . . .420

B.8.3 Loop Construct. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .420

B.8.4 Long Branches . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .421

B.8.5 Minimum and Maximum Instructions . . . . . . . . . . . . . . . . . . . . . . . . .421

B.8.6 Fuzzy Logic Support. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .422

B.8.7 Table Lookup and Interpolation . . . . . . . . . . . . . . . . . . . . . . . . . . . . .422

B.8.8 Extended Bit Manipulation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .423

B.8.9 Push and Pull D and CCR . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .423

B.8.10 Compare SP. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .423

B.8.11 Support for Memory Expansion . . . . . . . . . . . . . . . . . . . . . . . . . . . . .424

Appendix C. High-Level Language Support

C.1 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .425

C.2 Data Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .425

S12CPUV2 Reference Manual, Rev. 4.0

Freescale Semiconductor 13

Page 14

C.3 Parameters and Variables . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .426

C.3.1 Register Pushes and Pulls. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .426

C.3.2 Allocating and Deallocating Stack Space. . . . . . . . . . . . . . . . . . . . . .427

C.3.3 Frame Pointer. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .427

C.4 Increment and Decrement Operators . . . . . . . . . . . . . . . . . . . . . . . . . . .428

C.5 Higher Math Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .428

C.6 Conditional If Constructs. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .429

C.7 Case and Switch Statements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .429

C.8 Pointers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .429

C.9 Function Calls. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .430

C.10 Instruction Set Orthogonality. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .431

S12CPUV2 Reference Manual, Rev. 4.0

14 Freescale Semiconductor

Page 15

Reference Manual — S12CPUV2

1.1 Introduction

This manual describes the features and operation of the core (central

processing unit, or CPU, and development support functions) used in all

HCS12 microcontrollers. For reference, information is provided for the

M68HC12.

1.2 Features

The CPU12 is a high-speed, 16-bit processing unit that has a programming

model identical tothat of theindustry standard M68HC11central processor

unit (CPU). The CPU12 instruction set is a proper superset of the M68HC11

instruction set, and M68HC11 source code is accepted by CPU12

assemblers with no changes.

Section 1. Introduction

• Full 16-bit data paths supports efficient arithmetic operation and

high-speed math execution

• Supports instructions with odd byte counts, including many

single-byte instructions. This allows much more efficient use of ROM

space.

• An instruction queue buffers program information so the CPU has

immediate access to at least three bytes of machine code at the start

of every instruction.

• Extensive set of indexed addressing capabilities, including:

– Using the stack pointer as an indexing register in all indexed

operations

– Using the program counter as an indexing register in all but auto

increment/decrement mode

– Accumulator offsets using A, B, or D accumulators

– Automatic index predecrement, preincrement, postdecrement,

and postincrement (by –8 to +8)

S12CPUV2 Reference Manual, Rev. 4.0

Freescale Semiconductor 15

Page 16

1.3 Symbols and Notation

The symbols and notation shown here are used throughout the manual.

More specialized notation that applies only to the instruction glossary or

instruction set summary are described at the beginning of those sections.

1.3.1 Abbreviations for System Resources

A — Accumulator A

B — Accumulator B

D — Double accumulator D (A : B)

X — Index register X

Y — Index register Y

SP — Stack pointer

PC — Program counter

CCR — Condition code register

S — STOP instruction control bit

X — Non-maskable interrupt control bit

H — Half-carry status bit

I — Maskable interrupt control bit

N — Negative status bit

Z — Zero status bit

V — Two’s complement overflow status bit

C — Carry/Borrow status bit

S12CPUV2 Reference Manual, Rev. 4.0

16 Freescale Semiconductor

Page 17

1.3.2 Memory and Addressing

M — 8-bit memory location pointed to by the effective

M : M+1 — 16-bit memory location. Consists of the contents of the

M~M+3

M

(Y)~M(Y+3)

M

(X)

M

(SP)

M

(Y+3)

PPAGE — Program overlay page (bank) number for extended

Page — Program overlay page

X

H

X

L

( ) — Content of register or memory location

$ — Hexadecimal value

% — Binary value

address of the instruction

location pointed to by the effective address

concatenated with the contents of the location at the

nexthighermemoryaddress. The most significant byte

is at location M.

— 32-bit memory location. Consists of the contents of the

effective address of the instruction concatenated with

thecontentsofthenextthreehighermemorylocations.

The most significant byte is at location M or M

(Y)

.

— Memory locations pointed to by index register X

— Memory locations pointed to by the stack pointer

— Memory locations pointed to by index register Y plus 3

memory (>64 Kbytes).

— High-order byte

— Low-order byte

S12CPUV2 Reference Manual, Rev. 4.0

Freescale Semiconductor 17

Page 18

1.3.3 Operators

+

–

•

+

⊕

×

÷

M

⇒

⇔

—

Addition

—

Subtraction

—

Logical AND

—

Logical OR (inclusive)

—

Logical exclusive OR

—

Multiplication

—

Division

—

Negation. One’s complement (invert each bit of M)

—

:

Concatenate

Example: A : B means the 16-bit valueformedbyconcatenating 8-bit accumulator A with 8-bit accumulator B.

A is in the high-order position.

—

Transfer

Example: (A) ⇒ M means the content of accumulator A is

transferred to memory location M.

—

Exchange

Example: D ⇔ X means exchange the contents of D with

those of X.

S12CPUV2 Reference Manual, Rev. 4.0

18 Freescale Semiconductor

Page 19

1.3.4 Definitions

Logic level 1 is the voltage that corresponds to the true (1) state.

Logic level 0 is the voltage that corresponds to the false (0) state.

Set refers specifically to establishing logic level 1 on a bit or bits.

Cleared refers specifically to establishing logic level 0 on a bit or bits.

Asserted means that a signal is in active logic state. An active low signal

changes from logic level 1 to logic level 0 when asserted, and an active

high signal changes from logic level 0 to logic level 1.

Negated means that an asserted signal changes logic state. An active low

signal changes from logic level 0 to logic level 1 when negated, and an

active high signal changes from logic level 1 to logic level 0.

ADDR is the mnemonic for address bus.

DATA is the mnemonic for data bus.

LSB means least significant bit or bits.

MSB means most significant bit or bits.

LSW means least significant word or words.

MSW means most significant word or words.

A specific bit location within a range is referred to by mnemonic and

number. For example, A7 is bit 7 of accumulator A.

A range of bit locations is referred to by mnemonic and the numbers that

definetherange. For example,DATA[15:8]formthehigh byte ofthedata

bus.

S12CPUV2 Reference Manual, Rev. 4.0

Freescale Semiconductor 19

Page 20

S12CPUV2 Reference Manual, Rev. 4.0

20 Freescale Semiconductor

Page 21

Reference Manual — S12CPUV2

2.1 Introduction

This section describes the CPU12 programming model, register set, the

data types used, and basic memory organization.

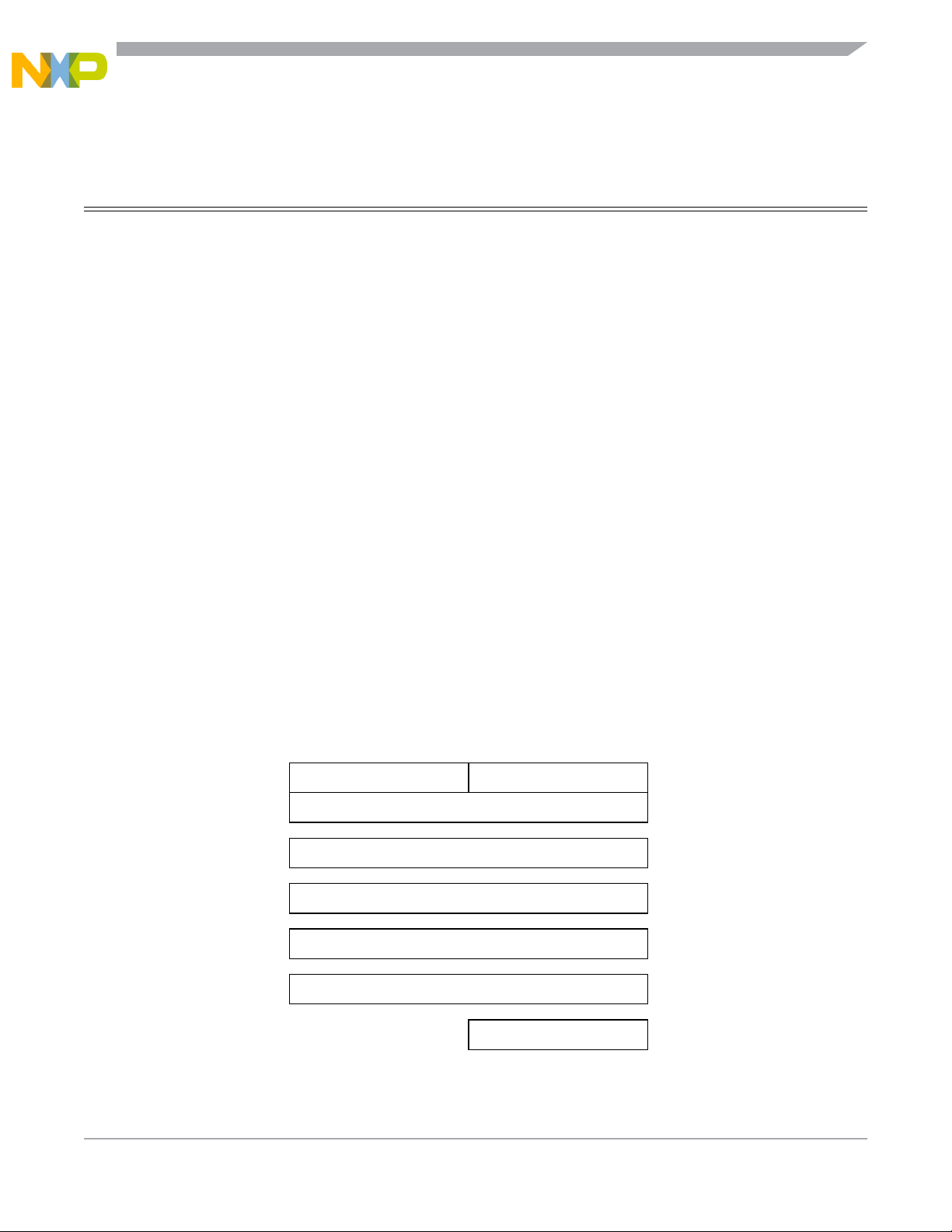

2.2 Programming Model

The CPU12 programming model, shown in Figure 2-1, is the same as that

of the M68HC11 CPU. The CPU has two 8-bit general-purpose

accumulators (A and B) that can be concatenated into a single 16-bit

accumulator (D) for certain instructions. It also has:

• Two index registers (X and Y)

Section 2. Overview

• 16-bit stack pointer (SP)

• 16-bit program counter (PC)

• 8-bit condition code register (CCR)

7

15

15

15

15

15

AB

70

D

IX

IY

SP

PC

NSXH I ZVC

Figure 2-1. Programming Model

0

8-BIT ACCUMULATORS A AND B

OR

0

16-BIT DOUBLE ACCUMULATOR D

0

INDEX REGISTER X

0

INDEX REGISTER Y

0

STACK POINTER

0

PROGRAM COUNTER

CONDITION CODE REGISTER

S12CPUV2 Reference Manual, Rev. 4.0

Freescale Semiconductor 21

Page 22

2.2.1 Accumulators

General-purpose8-bitaccumulatorsAandBare used to hold operands and

results of operations. Some instructions treat the combination of these two

8-bit accumulators (A : B) as a 16-bit double accumulator (D).

Most operations can use accumulator A or B interchangeably. However,

there are a few exceptions. Add, subtract, and compare instructions

involving both A and B (ABA, SBA, and CBA) only operate in one direction,

so it is important to make certain the correct operand is in the correct

accumulator. The decimal adjust accumulator A (DAA) instruction is used

after binary-coded decimal (BCD) arithmetic operations. There is no

equivalent instruction to adjust accumulator B.

2.2.2 Index Registers

16-bit index registers X and Y are used for indexed addressing. In the

indexed addressing modes, the contents of an index register are added to

5-bit, 9-bit, or 16-bit constants or to the content of an accumulator to form

the effective address of the instruction operand. The second index register

is especially useful for moves and in cases where operands from two

separate tables are used in a calculation.

2.2.3 Stack Pointer

TheCPU12supportsan automatic program stack.Thestackisused to save

system context during subroutine calls and interrupts and can also be used

for temporary data storage. The stack can be located anywhere in the

standard 64-Kbyte address space and can grow to any size up to the total

amount of memory available in the system.

The stack pointer (SP) holds the 16-bit address of the last stack location

used. Normally, the SP is initialized by one of the first instructions in an

application program. The stack grows downward from the address pointed

to by the SP. Each time a byte is pushed onto the stack, the stack pointer is

automatically decremented, and each time a byte is pulled from the stack,

the stack pointer is automatically incremented.

When a subroutine is called, the address of the instruction following the

calling instruction is automatically calculated and pushed onto the stack.

Normally, a return-from-subroutine (RTS) or a return-from-call (RTC)

instruction is executed at the end of a subroutine. The return instruction

S12CPUV2 Reference Manual, Rev. 4.0

22 Freescale Semiconductor

Page 23

loads the program counter with the previously stacked return address and

execution continues at that address.

When an interrupt occurs, the current instruction finishes execution. The

address of the next instruction is calculated and pushed onto the stack, all

the CPU registers are pushed onto the stack,theprogramcounter is loaded

with the address pointed to by the interrupt vector, and execution continues

at that address. The stacked registers are referred to as an interrupt stack

frame. The CPU12 stack frame is the same as that of the M68HC11.

NOTE: These instructions can be interrupted, and they resume execution once the

interrupt has been serviced:

2.2.4 Program Counter

The program counter (PC) is a 16-bit register that holds the address of the

nextinstructiontobeexecuted.Itisautomaticallyincrementedeachtimean

instruction is fetched.

• REV (fuzzy logic rule evaluation)

• REVW (fuzzy logic rule evaluation (weighted))

• WAV (weighted average)

2.2.5 Condition Code Register

The condition code register (CCR), named for its five status indicators,

contains:

• Five status indicators

• Two interrupt masking bits

• STOP instruction control bit

S12CPUV2 Reference Manual, Rev. 4.0

Freescale Semiconductor 23

Page 24

The status bits reflect the results of CPU operation as it executes

instructions. The five flags are:

• Half carry (H)

• Negative (N)

• Zero (Z)

• Overflow (V)

• Carry/borrow (C)

The half-carry flag is used only for BCD arithmetic operations. The N, Z, V,

and C status bits allow for branching based on the results of a previous

operation.

In some architectures, only a few instructions affectconditioncodes,so that

multiple instructions must be executed in order to load and test a variable.

Since most CPU12 instructions automatically update condition codes, it is

rarely necessary to execute an extra instruction for this purpose. The

challenge in using the CPU12lies in finding instructions thatdo not alter the

condition codes. The most important of these instructions arepushes,pulls,

transfers, and exchanges.

2.2.5.1 S Control Bit

It is always a good idea to refer to an instruction set summary (see

Appendix A. Instruction Reference) to check which condition codes are

affected by a particular instruction.

The following paragraphs describe normal uses of the condition codes.

There are other, more specialized uses. For instance, the C status bit is

usedto enable weighted fuzzy logic rule evaluation. Specialized usages are

described in the relevant portions of this manual and in Section 6.

Instruction Glossary.

Clearing the S bit enables the STOP instruction. Execution of a STOP

instruction normally causes the on-chip oscillator to stop. This may be

undesirableinsomeapplications.Ifthe CPU encounters a STOP instruction

while the S bit is set, it is treated like a no-operation (NOP) instruction and

continues to the next instruction. Reset sets the S bit.

S12CPUV2 Reference Manual, Rev. 4.0

24 Freescale Semiconductor

Page 25

2.2.5.2 X Mask Bit

XIRQ input is an updated version of the NMI input found on earlier

The

generations of MCUs. Non-maskable interrupts are typically used to deal

with major system failures, such as loss of power. However, enabling

non-maskableinterruptsbeforeasystemisfullypoweredandinitializedcan

lead to spurious interrupts. The X bit provides a mechanism for enabling

non-maskable interrupts after a system is stable.

By default, the Xbit is set to 1 during reset. As longas the X bitremains set,

interrupt service requests made via the

XIRQ pin are not recognized. An

instruction must clear the X bit to enable non-maskable interrupt service

requests made via the

XIRQ pin. Once the X bit has been cleared to 0,

software cannot reset it to 1 by writing to the CCR. The X bit is not affected

by maskable interrupts.

2.2.5.3 H Status Bit

When an

XIRQ interrupt occurs after non-maskable interrupts are enabled,

both the X bit and the I bit are set automatically to prevent other interrupts

from being recognized during the interrupt service routine. The mask bits

are set after the registers are stacked, but before the interrupt vector is

fetched.

Normally, a return-from-interrupt (RTI) instruction at the end of the interrupt

service routine restores register values that were present before the

interrupt occurred. Since the CCR is stacked before the X bit is set, the RTI

normally clears the X bit, and thus re-enables non-maskable interrupts.

While it is possible to manipulate thestackedvalue of X so that X issetafter

an RTI, there is no software method to reset X (and disable

XIRQ) once X

has been cleared.

The H bit indicates a carry from accumulator A bit 3 during an addition

operation. The DAA instruction uses the value of the H bit to adjust a result

in accumulator A to correct BCD format. H is updated only by the add

accumulator A to accumulator B (ABA), add without carry (ADD), and add

with carry (ADC) instructions.

2.2.5.4 I Mask Bit

The I bit enables and disables maskable interrupt sources. By default, the I

bit is set to 1 during reset. An instruction must clear the I bit to enable

maskable interrupts. While the I bit is set, maskable interrupts can become

S12CPUV2 Reference Manual, Rev. 4.0

Freescale Semiconductor 25

Page 26

2.2.5.5 N Status Bit

pending and are remembered, but operation continues uninterrupted until

the I bit is cleared.

When an interrupt occurs after interrupts are enabled, the I bit is

automatically set to prevent other maskable interrupts during the interrupt

service routine. The I bitis set after the registersare stacked, but before the

first instruction in the interrupt service routine is executed.

Normally, an RTI instruction at the end of the interrupt service routine

restores register values that were present before the interrupt occurred.

Since the CCR is stacked before the I bit is set, the RTI normally clears the

Ibit,andthusre-enables interrupts. Interrupts can bere-enabledbyclearing

the I bit within the service routine.

TheNbitshowsthestateof the MSB of the result. N ismostcommonlyused

in two’s complement arithmetic, where the MSB of a negative number is 1

and the MSB of a positive number is 0, but it has other uses. For instance,

if the MSB ofa register or memory location is used as a status flag, the user

can test status by loading an accumulator.

2.2.5.6 Z Status Bit

2.2.5.7 V Status Bit

2.2.5.8 C Status Bit

The Z bit is set when all the bits of the result are 0s. Compare instructions

perform an internal implied subtraction, and the condition codes, including

Z, reflect the results of that subtraction. The increment index register X

(INX), decrement index register X (DEX), increment index register Y (INY),

and decrement index register Y (DEY) instructions affect the Z bit and no

other condition flags. These operations can only determine = (equal) and ≠

(not equal).

The V bit is set when two’s complement overflow occurs as a result of an

operation.

The C bit is set when a carry occurs during addition or a borrow occurs

duringsubtraction. The C bit also acts as an error flag for multiply and divide

S12CPUV2 Reference Manual, Rev. 4.0

26 Freescale Semiconductor

Page 27

2.3 Data Types

operations.Shiftandrotate instructions operatethroughtheCbit to facilitate

multiple-word shifts.

The CPU12 uses these types of data:

• Bits

• 5-bit signed integers

• 8-bit signed and unsigned integers

• 8-bit, 2-digit binary-coded decimal numbers

• 9-bit signed integers

• 16-bit signed and unsigned integers

• 16-bit effective addresses

• 32-bit signed and unsigned integers

Negative integers are represented in two’s complement form.

Five-bit and 9-bit signed integers are used only as offsets for indexed

addressing modes.

Sixteen-bit effective addresses are formed during addressing mode

computations.

Thirty-two-bit integer dividends are used by extended division instructions.

Extended multiply and extended multiply-and-accumulate instructions

produce 32-bit products.

2.4 Memory Organization

ThestandardCPU12addressspaceis64Kbytes.SomeM68HC12devices

support a paged memory expansion scheme that increases the standard

space by means of predefined windows in address space. The CPU12 has

special instructions that support use of expanded memory.

Eight-bit values can be stored at any odd or even byte address in available

memory.

S12CPUV2 Reference Manual, Rev. 4.0

Freescale Semiconductor 27

Page 28

Sixteen-bit values are stored in memory as two consecutive bytes; the high

byte occupies the lowest address, but need not be aligned to an even

boundary.

Thirty-two-bit values are stored in memory as four consecutive bytes; the

high byte occupies the lowest address, but need not be aligned to an even

boundary.

All input/output (I/O) and all on-chip peripherals are memory-mapped. No

special instruction syntax is required to access these addresses. On-chip

registers and memory typically are grouped in blocks which can be

relocated within the standard 64-Kbyte address space. Refer to device

documentation for specific information.

2.5 Instruction Queue

The CPU12 uses an instruction queue to buffer program information. The

mechanism is called a queue rather than a pipeline because a typical

pipelined CPU executes more than one instruction at the same time, while

the CPU12 always finishes executing an instruction before beginning to

execute another. Refer to Section 4. Instruction Queue for more

information.

S12CPUV2 Reference Manual, Rev. 4.0

28 Freescale Semiconductor

Page 29

Reference Manual — S12CPUV2

3.1 Introduction

Addressing modes determine how the central processor unit (CPU)

accesses memory locations to be operated upon. This section discusses

the various modes and how they are used.

3.2 Mode Summary

Addressing modes are an implicit part of CPU12 instructions. Refer to

Appendix A. Instruction Reference for the modes used by each

instruction. All CPU12 addressing modes are shown in Table 3-1.

The CPU12 uses all M68HC11 modes as well as new forms of indexed

addressing. Differences between M68HC11and M68HC12 indexed modes

are described in 3.9 Indexed Addressing Modes. Instructions that use

more than one mode are discussed in 3.10 Instructions Using Multiple

Modes.

Section 3. Addressing Modes

3.3 Effective Address

Each addressing mode except inherent mode generates a 16-bit effective

address which is used during the memory reference portion of the

instruction. Effective address computations do not require extra execution

cycles.

S12CPUV2 Reference Manual, Rev. 4.0

Freescale Semiconductor 29

Page 30

Table 3-1. M68HC12 Addressing Mode Summary

Addressing Mode Source Format Abbreviation Description

INST

Inherent

(no externally

supplied operands)

INH Operands (if any) are in CPU registers

INST #opr8i

Immediate

Direct INST opr8a DIR

Extended INST opr16a EXT Operand is a 16-bit address

Relative

Indexed

(5-bit offset)

Indexed

(pre-decrement)

Indexed

(pre-increment)

Indexed

(post-decrement)

Indexed

(post-increment)

Indexed

(accumulator offset)

INST oprx5,xysp IDX

INST oprx3,–xys IDX Auto pre-decrement x, y, or sp by 1 ~ 8

INST oprx3,+xys IDX Auto pre-increment x, y, or sp by 1 ~ 8

INST oprx3,xys– IDX Auto post-decrement x, y, or sp by 1 ~ 8

INST oprx3,xys+ IDX Auto post-increment x, y, or sp by 1 ~ 8

or

INST #opr16i

INST rel8

or

INST rel16

INST abd,xysp IDX

IMM

REL

Operand is included in instruction stream

8- or 16-bit size implied by context

Operand is the lower 8 bits of an address

in the range $0000–$00FF

An 8-bit or 16-bit relative offset from the current pc

is supplied in the instruction

5-bit signed constant offset

from X, Y, SP, or PC

Indexed with 8-bit (A or B) or 16-bit (D)

accumulator offset from X, Y, SP, or PC

Indexed

(9-bit offset)

Indexed

(16-bit offset)

Indexed-Indirect

(16-bit offset)

Indexed-Indirect

(D accumulator offset)

30 Freescale Semiconductor

INST oprx9,xysp IDX1

INST oprx16,xysp IDX2

INST [oprx16,xysp] [IDX2]

INST [D,xysp] [D,IDX]

S12CPUV2 Reference Manual, Rev. 4.0

9-bit signed constant offset from X, Y, SP, or PC

(lower 8 bits of offset in one extension byte)

16-bit constant offset from X, Y, SP, or PC

(16-bit offset in two extension bytes)

Pointer to operand is found at...

16-bit constant offset from X, Y, SP, or PC

(16-bit offset in two extension bytes)

Pointer to operand is found at...

X, Y, SP, or PC plus the value in D

Page 31

3.4 Inherent Addressing Mode

Instructions that use this addressing mode either have no operands or all

operands are in internal CPU registers. In either case, the CPU does not

need to access any memory locations to complete the instruction.

Examples:

NOP ;this instruction has no operands

INX ;operand is a CPU register

3.5 Immediate Addressing Mode

Operands for immediate mode instructions are included in the instruction

stream and are fetched into the instruction queue one 16-bit word at a time

during normal program fetch cycles. Since program data is read into the

instruction queue several cycles before it is needed, when an immediate

addressingmodeoperandiscalled for by an instruction, it isalreadypresent

in the instruction queue.

The pound symbol (#) is used to indicate an immediate addressing mode

operand. One common programming error is to accidentally omit the #

symbol. This causes the assembler to misinterpret the expression that

follows it as an address rather than explicitly provided data. For example,

LDAA #$55 means toload the immediate value$55 into the A accumulator,

while LDAA $55 means to load the value from address $0055 into the A

accumulator. Without the # symbol, the instruction is erroneously

interpreted as a direct addressing mode instruction.

Examples:

LDAA #$55

LDX #$1234

LDY #$67

These are common examples of 8-bit and 16-bit immediate addressing

modes. The size of the immediate operand is implied by the instruction

context. In the third example, the instruction implies a 16-bit immediate

value but only an 8-bit value is supplied. In this case the assembler will

generate the 16-bit value $0067 because the CPU expects a16-bit value in

the instruction stream.

Example:

BRSET FOO,#$03,THERE

S12CPUV2 Reference Manual, Rev. 4.0

Freescale Semiconductor 31

Page 32

In this example, extended addressing mode is used to access the operand

FOO, immediate addressing mode is used to access the mask value $03,

and relative addressing mode is used to identify the destination address of

a branch in case the branch-taken conditions are met. BRSET is listed as

an extended mode instruction even though immediate and relative modes

are also used.

3.6 Direct Addressing Mode

This addressing mode is sometimes called zero-page addressing because

it is used to access operands in the address range $0000 through $00FF.

Since these addresses always begin with $00, only the eight low-order bits

of the address need to be included in the instruction, which saves program

space and execution time. A system can be optimized by placing the most

commonly accessed data in this area of memory. The eight low-order bits of

the operand address are supplied with the instruction, and the eight

high-order bits of the address are assumed to be 0.

Example:

LDAA $55

This is a basic example of direct addressing. The value $55 is taken to be

the low-order half of an address in the range $0000 through $00FF. The

high order half of the address is assumed to be 0. During execution of this

instruction, the CPU combines the value $55 from the instruction with the

assumed value of $00 to form the address $0055, which is then used to

access the data to be loaded into accumulator A.

Example:

LDX $20

In this example, the value $20 is combined with the assumed value of $00

to form the address $0020. Since the LDX instruction requires a 16-bit

value, a 16-bit word of data is read from addresses $0020 and $0021. After

execution of this instruction, the X index register will have the value from

address $0020 in its high-orderhalf and the value fromaddress $0021 in its

low-order half.

S12CPUV2 Reference Manual, Rev. 4.0

32 Freescale Semiconductor

Page 33

3.7 Extended Addressing Mode

In this addressing mode, the full 16-bit address of the memory locationtobe

operated on is provided in the instruction. This addressing mode can be

used to access any location in the 64-Kbyte memory map.

Example:

LDAA $F03B

This is a basic example of extended addressing. The value from address

$F03B is loaded into the A accumulator.

3.8 Relative Addressing Mode

Therelativeaddressingmodeisusedonly by branch instructions. Short and

long conditional branch instructions use relative addressing mode

exclusively, but branching versions of bit manipulation instructions (branch

if bits set (BRSET) and branch if bits cleared (BRCLR)) use multiple

addressing modes, including relative mode. Refer to

3.10 Instructions Using Multiple Modes for more information.

Shortbranchinstructionsconsistofan8-bitopcodeand a signed 8-bit offset

contained in the byte that follows the opcode. Long branch instructions

consist of an 8-bit prebyte, an 8-bit opcode, and a signed 16-bit offset

contained in the two bytes that follow the opcode.

Each conditional branch instruction tests certain status bits in the condition

code register. If the bits are in a specified state, the offset is added to the

address of the next memory location after the offset to form an effective

address, and execution continues at that address. If the bits are not in the

specified state, execution continues with the instruction immediately

following the branch instruction.

Bit-condition branches test whether bits in a memory byte are in a specific

state. Various addressing modes can be used to access the memory

location.An8-bitmaskoperandisusedtotestthebits.Ifeachbitinmemory

that corresponds to a 1in the mask is either set (BRSET) or clear(BRCLR),

an 8-bit offset is added to the address of the next memory location after the

offsettoformaneffectiveaddress,andexecutioncontinuesatthataddress.

If all the bits in memory that correspond to a 1 in the mask are not in the

specified state, execution continues with the instruction immediately

following the branch instruction.

S12CPUV2 Reference Manual, Rev. 4.0

Freescale Semiconductor 33

Page 34

8-bit, 9-bit, and 16-bit offsets are signed two’s complement numbers to

support branching upward and downward inmemory. The numeric range of

short branch offset values is $80 (–128) to $7F (127). Loop primitive

instructions support a 9-bit offset which allows a range of $100 (–256) to

$0FF (255). The numeric range of long branch offset values is $8000

(–32,768) to $7FFF (32,767). If the offset is 0, the CPU executes the

instruction immediately following the branch instruction, regardless of the

test involved.

Since the offset is at the end of a branch instruction, using a negative offset

valuecancausetheprogram counter (PC) topointtotheopcodeand initiate

a loop. For instance, a branch always (BRA) instruction consists of two

bytes, so using an offset of $FE sets up an infinite loop; the same is true of

a long branch always (LBRA) instruction with an offset of $FFFC.

An offset that points to the opcode can cause a bit-condition branch to

repeat execution until the specified bit condition is satisfied. Since

bit-condition branches can consist of four, five, or six bytes depending on

the addressing mode used to access the byte in memory, the offset value

that sets up a loop can vary. For instance, using an offset of $FC with a

BRCLR that accesses memory using an 8-bit indexed postbyte sets up a

loop that executes until all the bits in the specified memory byte that

correspond to 1s in the mask byte are cleared.

3.9 Indexed Addressing Modes

The CPU12 uses redefined versions of M68HC11 indexed modes that

reduce execution time and eliminate code size penalties for using the Y

indexregister.In most cases, CPU12codesizefor indexed operationsisthe

same or is smaller than that for the M68HC11. Execution time is shorter in

all cases. Execution time improvements are due to both a reduced number

of cycles for all indexed instructions and to faster system clock speed.

The indexed addressing scheme uses a postbyte plus zero, one, or two

extension bytes after the instruction opcode. The postbyte and extensions

do the following tasks:

1. Specify which index register is used

2. Determine whether a value in an accumulator is used as an offset

3. Enable automatic pre- or post-increment or pre- or post-decrement

4. Specify size of increment or decrement

5. Specify use of 5-, 9-, or 16-bit signed offsets

S12CPUV2 Reference Manual, Rev. 4.0

34 Freescale Semiconductor

Page 35

This approach eliminates the differences between X and Y register use

while dramatically enhancing the indexed addressing capabilities.

Major advantages of the CPU12 indexed addressing scheme are:

• The stack pointer can be used as an index register in all indexed

operations.

• The program counter can be used as an index register in all but

autoincrement and autodecrement modes.

• A, B, or D accumulators can be used for accumulator offsets.

• Automatic pre- or post-increment or pre- or post-decrement by –8 to

+8

• A choice of 5-, 9-, or 16-bit signed constant offsets

• Use of two new indexed-indirect modes:

– Indexed-indirect mode with 16-bit offset

– Indexed-indirect mode with accumulator D offset

Table 3-2 is a summary of indexed addressing mode capabilities and a

description of postbyte encoding. The postbyte is noted as xb in instruction

descriptions. Detailed descriptions of the indexed addressing mode

variations follow the table.

All indexed addressing modes use a 16-bit CPU register and additional

information to create an effective address. In most cases the effective

address specifies the memory location affected by the operation. In some

variations of indexed addressing, the effective address specifies the

location of a value that points to the memory location affected by the

operation.

S12CPUV2 Reference Manual, Rev. 4.0

Freescale Semiconductor 35

Page 36

Table 3-2. Summary of Indexed Operations

Postbyte

Code (xb)

rr0nnnnn

111rr0zs

111rr011 [n,r]

rr1pnnnn

Source

Code

Syntax

–n,r

–n,r

n,–r n,+r

n,r–

n,r+

,r

n,r

n,r

Comments

rr; 00 = X, 01 = Y, 10 = SP, 11 = PC

5-bit constant offset n = –16 to +15

r can specify X, Y, SP, or PC

Constant offset (9- or 16-bit signed)

z- 0 = 9-bit with sign in LSB of postbyte(s) –256 ≤ n ≤ 255

1 = 16-bit –32,768 ≤ n ≤ 65,535

if z = s = 1, 16-bit offset indexed-indirect (see below)

r can specify X, Y, SP, or PC

16-bit offset indexed-indirect

rr can specify X, Y, SP, or PC –32,768 ≤ n ≤ 65,535

Auto predecrement, preincrement, postdecrement,or postincrement;

p = pre-(0) or post-(1), n = –8 to –1, +1 to +8

r can specify X, Y, or SP (PC not a valid choice)

+8 = 0111

…

+1 = 0000

–1 = 1111

…

–8 = 1000

A,r

111rr1aa

111rr111 [D,r]

B,r

D,r

Accumulator offset (unsigned 8-bit or 16-bit)

aa-00 = A

01 = B

10 = D (16-bit)

11 = see accumulator D offset indexed-indirect

r can specify X, Y, SP, or PC

Accumulator D offset indexed-indirect

r can specify X, Y, SP, or PC

Indexed addressing mode instructions use a postbyte to specify index

registers(Xand Y), stack pointer (SP), or program counter (PC) as the base

indexregisterandtofurtherclassifythewaytheeffective address is formed.

A special group of instructions cause this calculated effective address to be

loaded into an index register for further calculations:

• Load stack pointer with effective address (LEAS)

• Load X with effective address (LEAX)

• Load Y with effective address (LEAY)

S12CPUV2 Reference Manual, Rev. 4.0

36 Freescale Semiconductor

Page 37

3.9.1 5-Bit Constant Offset Indexed Addressing

This indexed addressing mode uses a 5-bit signed offset which is included

in the instruction postbyte. This short offset is added to the base index

register (X, Y, SP, or PC) to form the effective address of the memory

location that will be affected by the instruction. This gives a range of –16

through +15 from the value in the base index register. Although other

indexed addressing modes allow 9- or 16-bit offsets, those modes also

require additional extension bytes in the instruction for this extra

information. The majority of indexed instructions in real programs use

offsets that fit in the shortest 5-bit form of indexed addressing.

Examples:

LDAA 0,X

STAB

–8,Y

For these examples, assume X has a value of $1000 and Y has a value of

$2000 before execution. The 5-bit constant offset mode does not change

thevalueinthe index register, so Xwillstillbe$1000 and Y will stillbe$2000

after execution of these instructions. In the first example, A will be loaded

with the value from address $1000. In the second example, the value from

the B accumulator will be stored at address $1FF8 ($2000 –$8).

3.9.2 9-Bit Constant Offset Indexed Addressing

This indexed addressing mode uses a 9-bit signed offset which is added to

the base index register (X, Y,SP, or PC) to form theeffective address of the

memory location affected by the instruction. This gives a range of

through +255 from the valuein the base index register. Themost significant

bit (sign bit) of the offset is included in the instruction postbyte and the

remaining eight bits are provided as an extension byte after the instruction

postbyte in the instruction flow.

Examples:

LDAA $FF,X

LDAB

–20,Y

For these examples, assume X is $1000 andYis $2000 before execution of

these instructions.

NOTE: These instructions do not alter the index registers so they will still be $1000

and $2000, respectively, after the instructions.

The first instruction will load A with the value from address $10FF and the

second instruction will load B with the value from address $1FEC.

–256

S12CPUV2 Reference Manual, Rev. 4.0

Freescale Semiconductor 37

Page 38

This variation of the indexed addressing mode in the CPU12 is similartothe

M68HC11 indexed addressing mode, but is functionally enhanced. The

M68HC11 CPU provides for unsigned 8-bit constant offset indexing from X

or Y, and use of Y requires an extra instruction byte and thus, an extra

execution cycle. The 9-bit signed offset used in the CPU12 covers the same

range of positive offsets as the M68HC11, and adds negative offset

capability. The CPU12 can use X, Y, SP, or PC as the base index register.

3.9.3 16-Bit Constant Offset Indexed Addressing

This indexed addressing mode uses a 16-bit offset which is added to the

base index register (X, Y, SP, or PC) to form the effective address of the

memory location affected by the instruction. This allows access to any

address in the 64-Kbyte address space. Since the address bus and the

offset are both 16 bits, it does not matter whether the offset value is

considered to be a signed or an unsigned value ($FFFF may be thought of

as +65,535 or as –1). The 16-bit offset is provided as two extension bytes

after the instruction postbyte in the instruction flow.

3.9.4 16-Bit Constant Indirect Indexed Addressing

This indexed addressing mode adds a 16-bit instruction-supplied offset to

the base index register to form the address of a memory location that

contains a pointer to the memory location affected by the instruction. The

instruction itself does not point to the address of the memory location to be

acted upon, but rather to the location of a pointer to the address to be acted

on. The square brackets distinguish this addressing mode from 16-bit

constant offset indexing.

Example:

LDAA [10,X]

In this example, X holds the base address of a table of pointers. Assume

that X has an initial value of $1000, and that the value $2000 is stored at

addresses $100A and $100B. The instruction first adds the value 10 to the

value in X to form the address $100A. Next, an address pointer ($2000) is

fetched from memory at $100A. Then, the value stored in location $2000 is

read and loaded into the A accumulator.

S12CPUV2 Reference Manual, Rev. 4.0

38 Freescale Semiconductor

Page 39

3.9.5 Auto Pre/Post Decrement/Increment Indexed Addressing

This indexed addressing mode provides four ways to automatically change

the value in a base index register as a part of instruction execution. The

index register can be incremented or decremented by an integer value

either before or after indexing takes place. The base index register may be

X, Y, or SP. (Auto-modify modes would not make sense on PC.)

Pre-decrement and pre-increment versions of the addressing mode adjust

the value of the index register before accessing the memory location

affected by the instruction — the index register retains the changed value

after the instruction executes. Post-decrement and post-increment versions

of the addressing mode use the initial value in the index register to access

thememorylocation affected bytheinstruction,thenchange the valueofthe

index register.

The CPU12 allows the index register to be incremented or decremented by

any integer value in the ranges –8 through –1 or 1 through 8. The value

need not be related to the size of the operand for the current instruction.

These instructions can be used to incorporate an index adjustment into an

existinginstructionratherthan using anadditionalinstructionandincreasing

executiontime.Thisaddressingmodeisalsousedtoperformoperationson

a series of data structures in memory.

When an LEAS, LEAX, or LEAY instruction is executed using this

addressingmode,andtheoperationmodifiesthe index register that is being

loaded, the final value in the registeristhevalue that would have been used

to access a memory operand. (Premodification is seen in the result but

postmodification is not.)

Examples:

STAA 1,

STX 2,

–SP ;equivalent to PSHA

–SP ;equivalent to PSHX

LDX 2,SP+ ;equivalent to PULX

LDAA 1,SP+ ;equivalent to PULA

For a “last-used” type of stack like the CPU12 stack, these four examples

are equivalent to common push and pull instructions.

For a “next-available” stack like the M68HC11 stack, push A onto stack

(PSHA) is equivalent to store accumulator A (STAA) 1,SP– and pull A from

stack (PULA) is equivalent to load accumulator A (LDAA) 1,+SP. However,

in the M68HC11, 16-bit operations like push register X onto stack (PSHX)

and pull register X from stack (PULX) require multiple instructions to

decrement the SP by one, then store X, then decrement SP by one again.

S12CPUV2 Reference Manual, Rev. 4.0

Freescale Semiconductor 39

Page 40

In the STAA 1,–SP example, the stack pointer is pre-decremented by one

and then A is stored to the address contained in the stack pointer. Similarly

the LDX 2,SP+ first loads X from the address in the stack pointer, then

post-increments SP by two.

Example:

MOVW 2,X+,4,+Y

This example demonstrates how to work with data structures larger than

bytes and words. With this instruction in a program loop, it is possible to

movewordsofdatafromalisthavingonewordperentryintoasecondtable

that has four bytes per table element. In this example the source pointer is

updated after the data is read from memory (post-increment) while the

destination pointer is updated before it is used to access memory

(pre-increment).

3.9.6 Accumulator Offset Indexed Addressing

In this indexed addressing mode, the effective address is the sum of the

values in the base index register and an unsigned offset in one of the

accumulators. The value in the index register itself is not changed. The

index register can be X, Y, SP, or PC and the accumulator can be either of

the 8-bit accumulators (A or B) or the 16-bit D accumulator.

Example:

LDAA B,X

This instruction internally adds B to X to form the address from which A will

be loaded. B and X are not changed by this instruction. This example is

similar to the following 2-instruction combination in an M68HC11.

Examples:

ABX

LDAA 0,X

However, this 2-instruction sequence alters the index register. If this

sequence was part of a loop where B changed on each pass, the index

register would have to be reloaded with the reference value on each loop

pass. The use of LDAA B,X is more efficient in the CPU12.

S12CPUV2 Reference Manual, Rev. 4.0

40 Freescale Semiconductor

Page 41

3.9.7 Accumulator D Indirect Indexed Addressing

This indexed addressing mode adds the value in the D accumulator to the

value in the base index register to form the address of a memory location

that contains a pointer to the memory location affected by the instruction.

The instruction operand does not point to the address of the memory

location to be acted upon, but rather to the location of a pointer to the

address to be acted upon. The square brackets distinguish this addressing

mode from D accumulator offset indexing.

Examples:

JMP [D,PC]

GO1 DC.W PLACE1

GO2 DC.W PLACE2

GO3 DC.W PLACE3

This example is a computed GOTO. The values beginning at GO1 are

addressesofpotentialdestinations of thejump(JMP)instruction.At the time

the JMP [D,PC] instruction is executed, PC points to the address GO1, and

D holds one of the values $0000, $0002, or $0004 (determined by the

program some time before the JMP).

Assume that the value in D is $0002. The JMP instruction adds the values

in D and PC to form the address of GO2. Next the CPU reads the address

PLACE2 from memory at GO2 and jumps to PLACE2. The locations of

PLACE1 through PLACE3 were known at the timeofprogramassembly but

the destination of the JMP depends upon the value in D computed during

program execution.

3.10 Instructions Using Multiple Modes

Several CPU12 instructions use more than one addressing mode in the

course of execution.

3.10.1 Move Instructions

Moveinstructionsuse separate addressingmodestoaccess the sourceand

destination of a move. There are move variations for all practical

combinations of immediate, extended, and indexed addressing modes.

The only combinations of addressing modes that are not allowed are those

with an immediate mode destination (the operand of an immediate mode

instruction is data, not an address). For indexedmoves,thereference index

register may be X, Y, SP, or PC.

S12CPUV2 Reference Manual, Rev. 4.0

Freescale Semiconductor 41

Page 42

Move instructions do not support indirect modes, 9-bit, or 16-bit offset

modes requiring extra extension bytes. There are special considerations

when using PC-relative addressing with move instructions. The original

M68HC12 implemented the instruction queue slightly differently than the

newer HCS12. In the older M68HC12 implementation, the CPU did not

maintain a pointer to the start of the instruction after the current instruction

(what the user thinks of as the PC value during execution). This caused an

offset for PC-relative move instructions.

PC-relative addressing uses the address of the location immediately

following the last byte of object code for the current instruction as a

reference point. The CPU12 normally corrects for queue offset and for

instruction alignment so that queue operation is transparent to the user.

However, in the original M68HC12, move instructions pose three special

problems:

• Some moves use an indexed source and an indexed destination.

• Some moves have object code that is too long to fit in the queue all at

one time, so the PC value changes during execution.

• All moves do not have the indexed postbyte as the last byte of object

code.

These cases are not handled by automatic queue pointer maintenance, but

it is still possible to use PC-relative indexing with move instructions by

providing for PC offsets in source code.

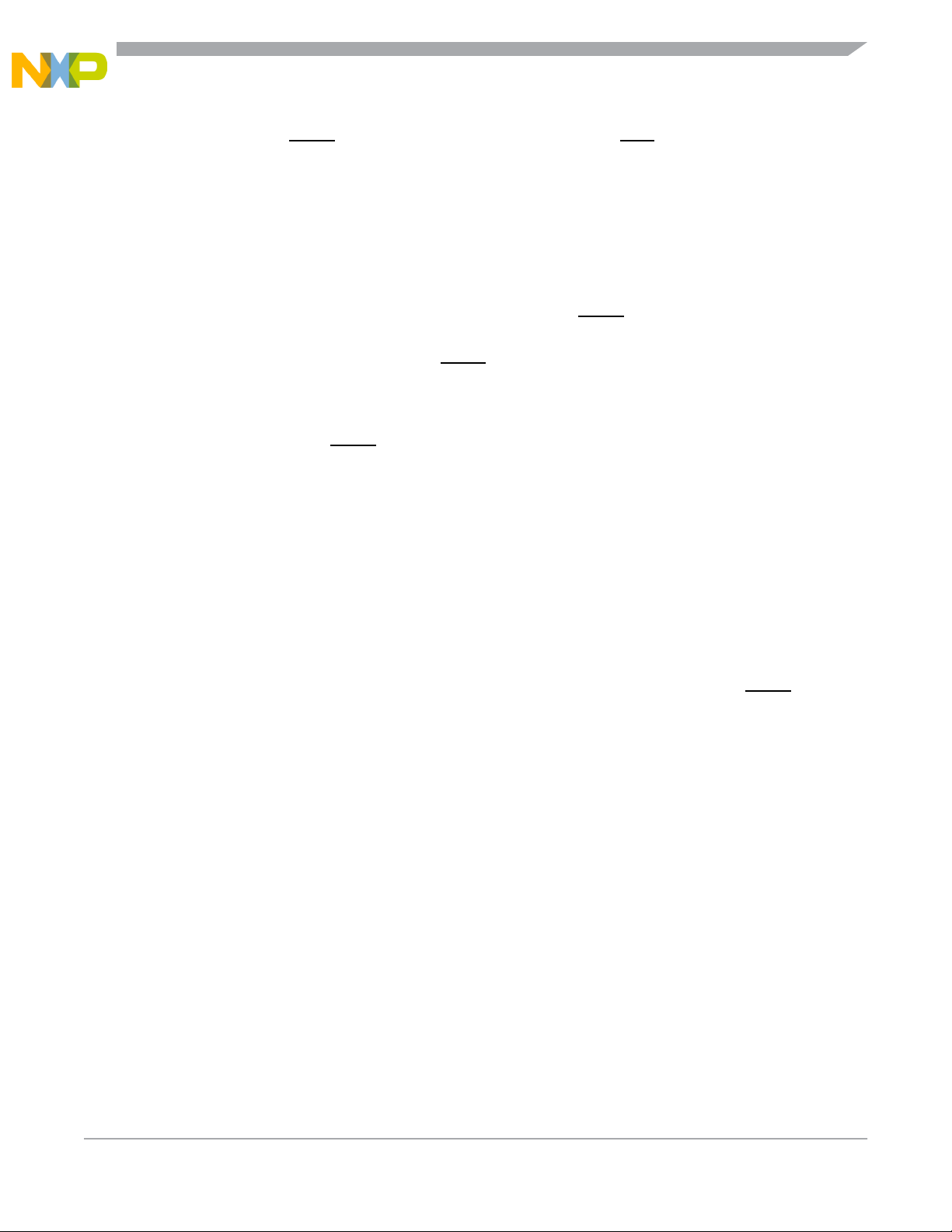

Table 3-3 shows PC offsets from the location immediately following the

current instruction by addressing mode.

Table 3-3. PC Offsets for MOVE Instructions (M68HC12 Only)

MOVE Instruction Addressing Modes Offset Value

IMM ⇒ IDX +1

EXT ⇒ IDX +2

MOVB

MOVW

IDX ⇒ EXT –2

IDX ⇒ IDX

IMM ⇒ IDX +2

EXT ⇒ IDX +2

IDX ⇒ EXT –2

IDX ⇒ IDX

–1 for first operand

+1 for second operand

–1 for first operand

+1 for second operand

S12CPUV2 Reference Manual, Rev. 4.0

42 Freescale Semiconductor

Page 43

Example:

1000 18 09 C2 20 00 MOVB $2000 2,PC

Moves a byte of data from $2000 to $1009

The expected location of the PC = $1005. The offset = +2.

[1005 + 2 (for 2,PC) + 2 (for correction) = 1009]

$18 is the page pre-byte, 09 is the MOVB opcode for ext-idx, C2 is the

indexed postbyte for 2,PC (without correction).

The Freescale MCUasm assembler produces corrected object code for

PC-relative moves (18 09 C0 20 00 for the example shown).

NOTE: Instead of assembling the 2,PC as C2, the correction has been applied to