Page 1

FlexRay

Communication

freescale.com

Controllers

MFR4310RM

Rev. 2

03/2008

MFR4310

Reference Manual

Page 2

Page 3

MFR4310 Reference Manual

MFR4310RM

Rev. 2

03/2008

Page 4

To provide the most up-to-date information, the revision of our documents on the World Wide Web will

be the most current. Your printed copy may be an earlier revision. To verify that you have the latest

information available, refer to http://www.freescale.com/flexray.

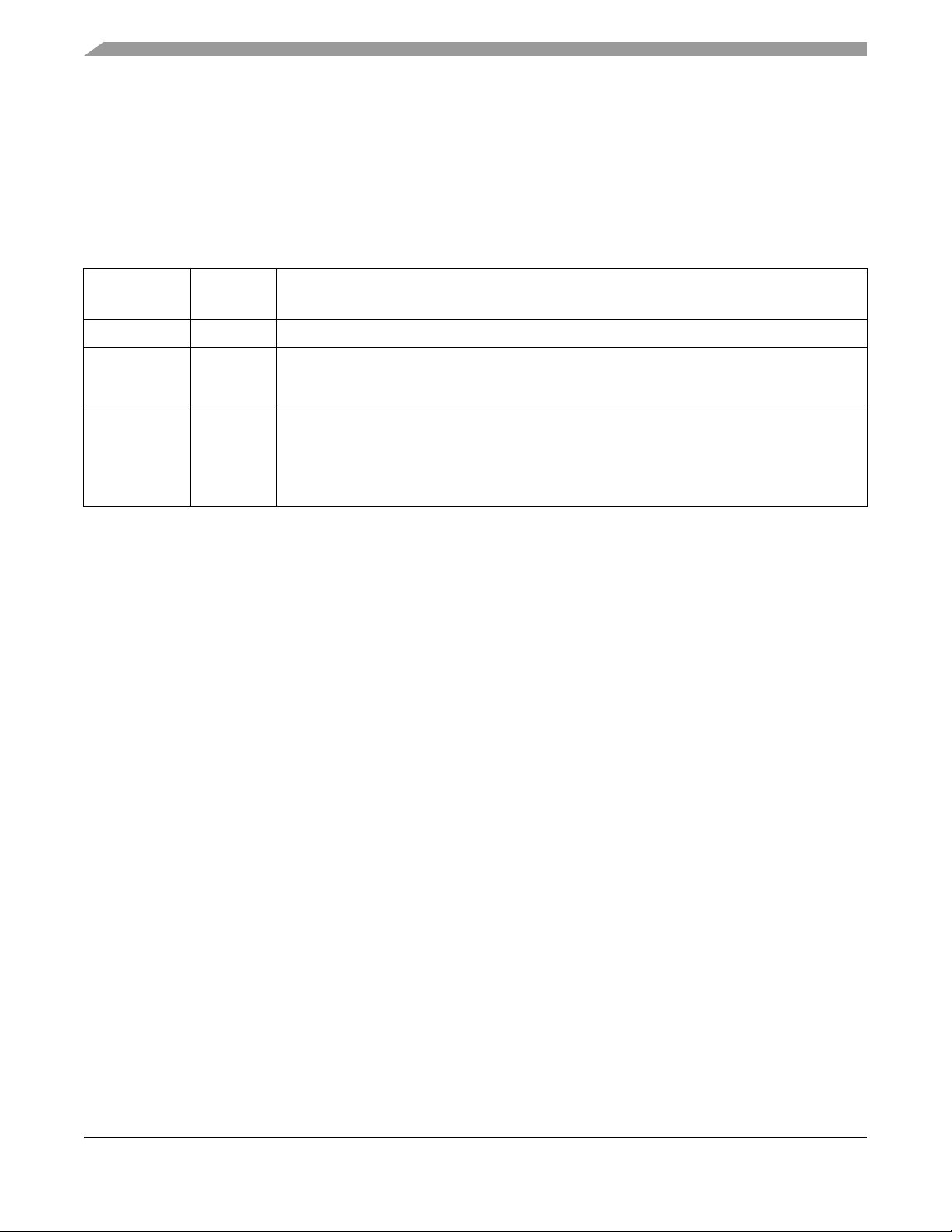

The following revision history table summarizes changes made to this document.

Revision History

Date

9 May 2007 0 First public release.

20 Jun 2007 1 Added row for 1M63J maskset to Table 2-2.

21 Mar 2008 2 Revised Figure 1-1.

Revision

Level

Description

Changed Figure 4-2 read and reset values and following paragraph to reflect 1M63J maskset

as an example .

Updated Table A-1 (maximum junction temperature changed from +150C to +140C).

Updated Table A-5. Thermal Characteristics

Updated Table A-8. Supply Current Characteristics (50mA max for -40 C, 25C & 140 C).

Updated Table A-12. Oscillator Characteristics (VDCbias TYP = 2.5).

MFR4310 Reference Manual, Rev. 2

4 Freescale Semiconductor

Page 5

Introduction

Device Overview

FlexRay Module (FLEXRAYV4)

Port Integration Module (PIM)

Dual Output Voltage Regulator (VREG3V3V2)

Clocks and Reset Generator (CRG)

Oscillator (OSCV2)

Electrical Characteristics

Package Information

Printed Circuit Board Layout Recommendations

Index of Registers

MFR4310 Reference Manual, Rev. 2

Freescale Semiconductor 5

Page 6

MFR4310 Reference Manual, Rev. 2

6 Freescale Semiconductor

Page 7

Contents

Section Number Title Page

Chapter 1

Introduction

1.1 Audience . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

1.2 Additional Reading . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

1.3 Terminology . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

1.4 Part Number Coding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Chapter 2

Device Overview

2.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

2.2 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

2.3 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

2.3.1 Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

2.3.2 Part ID and Module Version Number Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

2.4 Signal Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

2.4.1 System Pinout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

2.4.2 Pin Functions and Signal Properties . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

2.4.3 Detailed Signal Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

2.4.4 Power Supply Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

2.5 Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

2.6 External Clock and Host Interface Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

2.6.1 External 4/10/40 MHz Output Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

2.6.2 External Host Interface Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

2.6.3 Recommended Pullup/pulldown Resistor Values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

2.7 External Host Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

2.7.1 Asynchronous Memory Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

2.7.2 MPC Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

2.7.3 HCS12 Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

2.8 Resets and Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

2.8.1 Resets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

2.8.2 Interrupt Sources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

Chapter 3

FlexRay Module (FLEXRAYV4)

3.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

3.1.1 Reference . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

3.1.2 Glossary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

3.1.3 Color Coding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

MFR4310 Reference Manual, Rev. 2

Freescale Semiconductor 7

Page 8

Section Number Title Page

3.1.4 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

3.1.5 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

3.1.6 Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

3.2 External Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

3.2.1 Detailed Signal Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

3.3 Memory Map and Register Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

3.3.1 Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

3.3.2 Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

3.4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 134

3.4.1 Message Buffer Concept . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 134

3.4.2 Physical Message Buffer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 134

3.4.3 Message Buffer Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 135

3.4.4 FlexRay Memory Layout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 140

3.4.5 Physical Message Buffer Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 142

3.4.6 Individual Message Buffer Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . 151

3.4.7 Individual Message Buffer Search . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 176

3.4.8 Individual Message Buffer Reconfiguration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 178

3.4.9 Receive FIFO . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 179

3.4.10 Channel Device Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 184

3.4.11 External Clock Synchronization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 186

3.4.12 Sync Frame ID and Sync Frame Deviation Tables . . . . . . . . . . . . . . . . . . . . . . . . . . . . 186

3.4.13 MTS Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 189

3.4.14 Sync Frame and Startup Frame Transmission . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 190

3.4.15 Sync Frame Filtering . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 191

3.4.16 Strobe Signal Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 192

3.4.17 Timer Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 193

3.4.18 Slot Status Monitoring . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 194

3.4.19 Interrupt Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 197

3.4.20 Clock Domain Crossing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 202

3.5 Lower FlexRay Bit Rate Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 202

3.6 Initialization Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 202

3.6.1 FlexRay Initialization Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 203

3.6.2 Number of Usable Message Buffers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 203

3.7 Application Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 204

3.7.1 Shut Down Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 204

3.7.2 Protocol Control Command Execution . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 205

3.7.3 Protocol Reset Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 206

Chapter 4

Port Integration Module (PIM)

4.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 207

4.1.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 207

MFR4310 Reference Manual, Rev. 2

8 Freescale Semiconductor

Page 9

Section Number Title Page

4.1.2 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 207

4.1.3 Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 207

4.2 External Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 207

4.2.1 Functional Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 208

4.2.2 Reset Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 209

4.3 PIM Memory Map and Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 209

4.3.1 Port Integration Module Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 210

4.4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 215

4.4.1 Functional Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 215

4.4.2 Reset Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 216

Chapter 5

Dual Output Voltage Regulator (VREG3V3V2)

5.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 217

5.1.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 217

5.1.2 Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 217

5.1.3 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 217

5.2 External Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 219

5.2.1 V

5.2.2 V

5.2.3 V

5.2.4 V

5.3 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 220

5.3.1 REG — Regulator Core . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 220

5.3.2 Full-performance Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 220

5.3.3 POR — Power On Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 220

5.3.4 LVR — Low Voltage Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 221

5.3.5 CTRL — Regulator Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 221

5.4 Resets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 221

5.4.1 Power On Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 221

5.4.2 Low Voltage Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 221

, V

DDR

, V

DDA

DD2_5

DDOSC

— Regulator Power Input . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 219

SSR

— Regulator Reference Supply . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 219

SSA

, V

, V

— Regulator Output1 (Core Logic) . . . . . . . . . . . . . . . . . . . . . . . . . . 220

SS2_5

— Regulator Output2 (OSC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 220

SSOSC

Chapter 6

Clocks and Reset Generator (CRG)

6.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 223

6.1.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 223

6.1.2 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 223

6.2 MFR4310 Relevant Pins for the CRG . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 224

6.3 CRG Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 224

6.3.1 Detection Enable Register (DER) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 224

6.3.2 Clock and Reset Status Register (CRSR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 225

6.4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 226

MFR4310 Reference Manual, Rev. 2

Freescale Semiconductor 9

Page 10

Section Number Title Page

6.4.1 Reset Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 226

6.4.2 Interface Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 229

6.4.3 CLKOUT Mode Selection and Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 230

Chapter 7

Oscillator (OSCV2)

7.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 235

7.1.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 235

7.1.2 Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 235

7.2 External Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 235

7.2.1 V

DDOSC

and V

SSOSC

— OSC Operating Voltage, OSC Ground . . . . . . . . . . . . . . . . . . 235

7.2.2 EXTAL and XTAL — Clock/Crystal Source Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . 235

7.3 Memory Map and Register Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 236

7.4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 236

7.4.1 Clock Monitor (CM) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 236

7.5 Resets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 236

Appendix A

Electrical Characteristics

A.1 General . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 237

A.1.1 Parameter Classification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 237

A.1.2 Power Supply . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 238

A.1.3 Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 238

A.1.4 Current Injection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 238

A.1.5 Absolute Maximum Ratings. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 239

A.1.6 ESD Protection and Latch-up Immunity . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 240

A.1.7 Operating Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 241

A.1.8 Power Dissipation and Thermal Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 241

A.1.9 I/O Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 244

A.1.10 Supply Currents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 246

A.2 Voltage Regulator (VREG). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 247

A.2.1 Operating Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 247

A.2.2 Chip Power-up and Voltage Drops. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 248

A.2.3 Output Loads. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 248

A.3 Reset and Oscillator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 249

A.3.1 Startup. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 249

A.3.2 Oscillator. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 250

A.4 Asynchronous Memory Interface Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 250

A.5 MPC Interface Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 252

A.6 HCS12 Interface Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 255

MFR4310 Reference Manual, Rev. 2

10 Freescale Semiconductor

Page 11

Section Number Title Page

Appendix B

Package Information

B.1 64-pin LQFP package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 257

Appendix C

Printed Circuit Board Layout Recommendations

Appendix D

Index of Registers

MFR4310 Reference Manual, Rev. 2

Freescale Semiconductor 11

Page 12

Section Number Title Page

MFR4310 Reference Manual, Rev. 2

12 Freescale Semiconductor

Page 13

List of Figures

Figure Number Title Page

Figure 1-1. Order Part Number Coding. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Figure 2-1. MFR4310 Functional Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

Figure 2-2. MFR4310 Pin Assignment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

Figure 2-3. Oscillator Connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

Figure 2-4. External Square Wave Clock Generator Connection . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

Figure 2-5. AMI Interface with S12X Family. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

Figure 2-6. AMI Interface with DSP 56F83 (Hawk) Family . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

Figure 2-7. MPC EBI Interface with MPC5xx and MPC55xx Families. . . . . . . . . . . . . . . . . . . . . . . 52

Figure 2-8. HCS12 Interface Address Decoding and Internal Chip Select Generation . . . . . . . . . . . 54

Figure 2-9. HCS12 interface with HCS12 Page Mode Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

Figure 2-10. HCS12 interface with HCS12 Unpaged Mode Support. . . . . . . . . . . . . . . . . . . . . . . . . . 56

Figure 3-1. FlexRay Module Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

Figure 3-2. Module Version Register (MVR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

Figure 3-3. Module Configuration Register (MCR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

Figure 3-4. Strobe Signal Control Register (STBSCR). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

Figure 3-5. Message Buffer Data Size Register (MBDSR). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

Figure 3-6. Message Buffer Segment Size and Utilization Register (MBSSUTR). . . . . . . . . . . . . . . 76

Figure 3-7. Protocol Operation Control Register (POCR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

Figure 3-8. Global Interrupt Flag and Enable Register (GIFER) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

Figure 3-9. Protocol Interrupt Flag Register 0 (PIFR0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

Figure 3-10. Protocol Interrupt Flag Register 1 (PIFR1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

Figure 3-11. Protocol Interrupt Enable Register 0 (PIER0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

Figure 3-12. Protocol Interrupt Enable Register 1 (PIER1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

Figure 3-13. CHI Error Flag Register (CHIERFR). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86

Figure 3-14. Message Buffer Interrupt Vector Register (MBIVEC). . . . . . . . . . . . . . . . . . . . . . . . . . . 88

Figure 3-15. Channel A Status Error Counter Register (CASERCR). . . . . . . . . . . . . . . . . . . . . . . . . . 89

Figure 3-16. Channel B Status Error Counter Register (CBSERCR). . . . . . . . . . . . . . . . . . . . . . . . . . 89

Figure 3-17. Protocol Status Register 0 (PSR0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

Figure 3-18. Protocol Status Register 1 (PSR1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

Figure 3-19. Protocol Status Register 2 (PSR2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

Figure 3-20. Protocol Status Register 3 (PSR3) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

Figure 3-21. Macrotick Counter Register (MTCTR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

MFR4310 Reference Manual, Rev. 2

Freescale Semiconductor 13

Page 14

Figure Number Title Page

Figure 3-22. Cycle Counter Register (CYCTR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

Figure 3-23. Slot Counter Channel A Register (SLTCTAR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

Figure 3-24. Slot Counter Channel B Register (SLTCTBR). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

Figure 3-25. Rate Correction Value Register (RTCORVR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

Figure 3-26. Offset Correction Value Register (OFCORVR). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

Figure 3-27. Combined Interrupt Flag Register (CIFRR). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

Figure 3-28. Sync Frame Counter Register (SFCNTR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100

Figure 3-29. Sync Frame Table Offset Register (SFTOR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100

Figure 3-30. Sync Frame Table Configuration, Control, Status Register (SFTCCSR). . . . . . . . . . . . 101

Figure 3-31. Sync Frame ID Rejection Filter Register (SFIDRFR) . . . . . . . . . . . . . . . . . . . . . . . . . . 102

Figure 3-32. Sync Frame ID Acceptance Filter Value Register (SFIDAFVR). . . . . . . . . . . . . . . . . . 103

Figure 3-33. Sync Frame ID Acceptance Filter Mask Register (SFIDAFMR). . . . . . . . . . . . . . . . . . 103

Figure 3-34. Network Management Vector Registers (NMVR0–NMVR5). . . . . . . . . . . . . . . . . . . . 103

Figure 3-35. Network Management Vector Length Register (NMVLR) . . . . . . . . . . . . . . . . . . . . . . 104

Figure 3-36. Timer Configuration and Control Register (TICCR) . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

Figure 3-37. Timer 1 Cycle Set Register (TI1CYSR). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 106

Figure 3-38. Timer 1 Macrotick Offset Register (TI1MTOR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 106

Figure 3-39. Timer 2 Configuration Register 0 (TI2CR0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 107

Figure 3-40. Timer 2 Configuration Register 1 (TI2CR1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 107

Figure 3-41. Slot Status Selection Register (SSSR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 108

Figure 3-42. Slot Status Counter Condition Register (SSCCR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109

Figure 3-43. Slot Status Registers (SSR0–SSR7) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

Figure 3-44. Slow Status Counter Registers (SSCR0–SSCR3) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 112

Figure 3-45. MTS A Configuration Register (MTSACFR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

Figure 3-46. MTS B Configuration Register (MTSBCFR). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

Figure 3-47. Receive Shadow Buffer Index Register (RSBIR). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 114

Figure 3-48. Receive FIFO Selection Register (RFSR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 115

Figure 3-49. Receive FIFO Start Index Register (RFSIR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 115

Figure 3-50. Receive FIFO Depth and Size Register (RFDSR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 116

Figure 3-51. Receive FIFO A Read Index Register (RFARIR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 116

Figure 3-52. Receive FIFO B Read Index Register (RFBRIR). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 117

Figure 3-53. Receive FIFO Message ID Acceptance Filter Value Register (RFMIDAFVR). . . . . . . 117

Figure 3-54. Receive FIFO Message ID Acceptance Filter Mask Register (RFMIAFMR). . . . . . . . 118

Figure 3-55. Receive FIFO Frame ID Rejection Filter Value Register (RFFIDRFVR). . . . . . . . . . . 118

Figure 3-56. Receive FIFO Frame ID Rejection Filter Mask Register (RFFIDRFMR). . . . . . . . . . . 118

MFR4310 Reference Manual, Rev. 2

14 Freescale Semiconductor

Page 15

Figure Number Title Page

Figure 3-57. Receive FIFO Range Filter Configuration Register (RFRFCFR) . . . . . . . . . . . . . . . . . 119

Figure 3-58. Receive FIFO Range Filter Control Register (RFRFCTR) . . . . . . . . . . . . . . . . . . . . . . 119

Figure 3-59. Last Dynamic Slot Channel A Register (LDTXSLAR). . . . . . . . . . . . . . . . . . . . . . . . . 120

Figure 3-60. Last Dynamic Slot Channel B Register (LDTXSLBR) . . . . . . . . . . . . . . . . . . . . . . . . . 121

Figure 3-61. Protocol Configuration Register 0 (PCR0). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123

Figure 3-62. Protocol Configuration Register 1 (PCR1). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123

Figure 3-63. Protocol Configuration Register 2 (PCR2). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123

Figure 3-64. Protocol Configuration Register 3 (PCR3). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124

Figure 3-65. Protocol Configuration Register 4 (PCR4). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124

Figure 3-66. Protocol Configuration Register 5 (PCR5). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124

Figure 3-67. Protocol Configuration Register 6 (PCR6). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124

Figure 3-68. Protocol Configuration Register 7 (PCR7). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124

Figure 3-69. Protocol Configuration Register 8 (PCR8). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 125

Figure 3-70. Protocol Configuration Register 9 (PCR9). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 125

Figure 3-71. Protocol Configuration Register 10 (PCR10). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 125

Figure 3-72. Protocol Configuration Register 11 (PCR11). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 125

Figure 3-73. Protocol Configuration Register 12 (PCR12). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 126

Figure 3-74. Protocol Configuration Register 13 (PCR13). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 126

Figure 3-75. Protocol Configuration Register 14 (PCR14). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 126

Figure 3-76. Protocol Configuration Register 15 (PCR15). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 126

Figure 3-77. Protocol Configuration Register 16 (PCR16). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 126

Figure 3-78. Protocol Configuration Register 17 (PCR17). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 127

Figure 3-79. Protocol Configuration Register 18 (PCR18). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 127

Figure 3-80. Protocol Configuration Register 19 (PCR19). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 127

Figure 3-81. Protocol Configuration Register 20 (PCR20). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 127

Figure 3-82. Protocol Configuration Register 21 (PCR21). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 127

Figure 3-83. Protocol Configuration Register 22 (PCR22). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 128

Figure 3-84. Protocol Configuration Register 23 (PCR23). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 128

Figure 3-85. Protocol Configuration Register 24 (PCR24). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 128

Figure 3-86. Protocol Configuration Register 25 (PCR25). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 128

Figure 3-87. Protocol Configuration Register 26 (PCR26). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 128

Figure 3-88. Protocol Configuration Register 27 (PCR27). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 129

Figure 3-89. Protocol Configuration Register 28 (PCR28). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 129

Figure 3-90. Protocol Configuration Register 29 (PCR29). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 129

Figure 3-91. Protocol Configuration Register 30 (PCR30). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 129

MFR4310 Reference Manual, Rev. 2

Freescale Semiconductor 15

Page 16

Figure Number Title Page

Figure 3-92. Message Buffer Configuration, Control, Status Registers (MBCCSRn) . . . . . . . . . . . . 130

Figure 3-93. Message Buffer Cycle Counter Filter Registers (MBCCFRn). . . . . . . . . . . . . . . . . . . . 132

Figure 3-94. Message Buffer Frame ID Registers (MBFIDRn) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 133

Figure 3-95. Message Buffer Index Registers (MBIDXRn). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 133

Figure 3-96. Physical Message Buffer Structure. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 134

Figure 3-97. Individual Message Buffer Structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 136

Figure 3-98. Receive Shadow Buffer Structure. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 137

Figure 3-99. Receive FIFO Structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 138

Figure 3-100. Example of FRM Layout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 141

Figure 3-101. Frame Header Structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 143

Figure 3-102. Receive Message Buffer Slot Status Structure (ChAB) . . . . . . . . . . . . . . . . . . . . . . . . . 146

Figure 3-103. Receive Message Buffer Slot Status Structure (ChA) . . . . . . . . . . . . . . . . . . . . . . . . . . 146

Figure 3-104. Receive Message Buffer Slot Status Structure (ChB) . . . . . . . . . . . . . . . . . . . . . . . . . . 146

Figure 3-105. Transmit Message Buffer Slot Status Structure (ChAB) . . . . . . . . . . . . . . . . . . . . . . . . 148

Figure 3-106. Transmit Message Buffer Slot Status Structure (ChA) . . . . . . . . . . . . . . . . . . . . . . . . . 148

Figure 3-107. Transmit Message Buffer Slot Status Structure (ChB). . . . . . . . . . . . . . . . . . . . . . . . . . 148

Figure 3-108. Message Buffer Data Field Structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 150

Figure 3-109. Single Transmit Message Buffer Access Regions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 153

Figure 3-110. Single Transmit Message Buffer States . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 154

Figure 3-111. Message Transmission Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 158

Figure 3-112. Message Transmission from HLck state with unlock. . . . . . . . . . . . . . . . . . . . . . . . . . . 158

Figure 3-113. Null Frame Transmission from Idle state . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 159

Figure 3-114. Null Frame Transmission from HLck state . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 159

Figure 3-115. Null Frame Transmission from HLck state with unlock . . . . . . . . . . . . . . . . . . . . . . . . 159

Figure 3-116. Null Frame Transmission from Idle State with locking . . . . . . . . . . . . . . . . . . . . . . . . . 160

Figure 3-117. Receive Message Buffer Access Regions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 161

Figure 3-118. Receive Message Buffer States. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 162

Figure 3-119. Message Reception Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 166

Figure 3-120. Double Transmit Buffer Structure and Data Flow . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 168

Figure 3-121. Double Transmit Message Buffer Access Regions Layout . . . . . . . . . . . . . . . . . . . . . . 168

Figure 3-122. Double Transmit Message Buffer State Diagram (Commit Side) . . . . . . . . . . . . . . . . . 170

Figure 3-123. Double Transmit Message Buffer State Diagram (Transmit Side). . . . . . . . . . . . . . . . . 171

Figure 3-124. Internal Message Transfer in Streaming Commit Mode . . . . . . . . . . . . . . . . . . . . . . . . 175

Figure 3-125. Internal Message Transfer in Immediate Commit Mode . . . . . . . . . . . . . . . . . . . . . . . . 175

Figure 3-126. Inconsistent Channel Assignment. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 178

MFR4310 Reference Manual, Rev. 2

16 Freescale Semiconductor

Page 17

Figure Number Title Page

Figure 3-127. Message Buffer Reconfiguration Scheme . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 179

Figure 3-128. Received Frame FIFO Filter Path. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 182

Figure 3-129. Dual Channel Device Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 184

Figure 3-130. Single Channel Device Mode (Channel A) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 185

Figure 3-131. Single Channel Device Mode (Channel B). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 185

Figure 3-132. External Offset Correction Write and Application Timing . . . . . . . . . . . . . . . . . . . . . . 186

Figure 3-133. External Rate Correction Write and Application Timing. . . . . . . . . . . . . . . . . . . . . . . . 186

Figure 3-134. Sync Table Memory Layout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 187

Figure 3-135. Sync Frame Table Trigger and Generation Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . 189

Figure 3-136. Strobe Signal Timing (type = pulse, clk_offset = -2). . . . . . . . . . . . . . . . . . . . . . . . . . . 192

Figure 3-137. Strobe Signal Timing (type = pulse, clk_offset = +4) . . . . . . . . . . . . . . . . . . . . . . . . . . 192

Figure 3-138. Slot Status Vector Update. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 194

Figure 3-139. Slot Status Counting and SSCRn Update. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 196

Figure 3-140. Scheme of cascaded interrupt request. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 200

Figure 3-141. INT_CC# generation scheme . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 201

Figure 3-142. Scheme of combined interrupt flags. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 201

Figure 4-1. Part ID Register (PIDR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 210

Figure 4-2. ASIC Version Number Register (AVNR) (for Maskset 1M63J) . . . . . . . . . . . . . . . . . . 210

Figure 4-3. Host Interface Pins Drive Strength Register (HIPDSR). . . . . . . . . . . . . . . . . . . . . . . . . 210

Figure 4-4. Physical Layer Pins Drive Strength Register (PLPDSR) . . . . . . . . . . . . . . . . . . . . . . . . 211

Figure 4-5. Host Interface Pins Pullup/pulldown Enable Register (HIPPER) . . . . . . . . . . . . . . . . . 212

Figure 4-6. Host Interface Pins Pullup/pulldown Control Register (HIPPCR). . . . . . . . . . . . . . . . . 213

Figure 4-7. Physical Layer Pins Pullup/pulldown Enable Register (PLPPER). . . . . . . . . . . . . . . . . 214

Figure 4-8. Physical Layer Pins Pullup/pulldown Control Register (PLPPCR) . . . . . . . . . . . . . . . . 215

Figure 5-1. VREG3V3 Block Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 218

Figure 6-1. Detection Enable Register (DER). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 224

Figure 6-2. Clock and Reset Status Register (CRSR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 225

Figure 6-3. CRG Power On Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 227

Figure 6-4. Low Voltage Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 228

Figure 6-5. Clock Monitor Failure Reset. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 228

Figure 6-6. External Reset. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 229

Figure 6-7. Interface Selection during Power-on or Low Voltage Reset or Clock Monitor Failure. 230

Figure 6-8. Interface Selection during External Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 230

Figure 6-9. CLKOUT Mode Selection and Control during Low-voltage Reset or

Clock Monitor Failure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 231

MFR4310 Reference Manual, Rev. 2

Freescale Semiconductor 17

Page 18

Figure Number Title Page

Figure 6-10. CLKOUT Mode Selection and Control during External Reset . . . . . . . . . . . . . . . . . . . 232

Figure 6-11. CLKOUT Mode Selection and Control during Power-on Reset . . . . . . . . . . . . . . . . . . 233

Figure A-1. Voltage Regulator — Chip Power-up and Voltage Drops (not scaled) . . . . . . . . . . . . . 248

Figure A-2. AMI Interface Read Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 251

Figure A-3. AMI Interface Write Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 251

Figure A-4. MPC Interface Read Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 253

Figure A-5. MPC Interface Write Timing Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 253

Figure A-6. HCS12 Interface Read Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 255

Figure A-7. HCS12 Interface Write Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 255

Figure B-1. 64-pin LQFP Mechanical Dimensions (Case N 840F-02) (Page 1) . . . . . . . . . . . . . . . . 257

Figure B-2. 64-pin LQFP Mechanical Dimensions (Case N 840F-02) (Page 2) . . . . . . . . . . . . . . . . 258

Figure B-3. 64-pin LQFP Mechanical Dimensions (Case N 840F-02) (Page 3) . . . . . . . . . . . . . . . . 259

Figure C-1. Recommended PCB Layout (64-pin LQFP) for Standard Pierce Oscillator Mode . . . . 262

MFR4310 Reference Manual, Rev. 2

18 Freescale Semiconductor

Page 19

List of Tables

Table Number Title Page

Table 1-1. Acronyms and Abbreviations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

Table 1-2. Notational Conventions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Table 2-1. MFR4310 Device Memory Map After Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Table 2-2. Part ID and Module Version Numbers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

Table 2-3. Pin Functions and Signal Properties . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

Table 2-4. MFR4310 Power and Ground Connection Summary. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

Table 2-5. CLKOUT Frequency Selection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

Table 2-6. Interface Selection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

Table 2-7. Recommended Pullup and Pulldown Resistor Values for IF_SEL[1:0] Inputs . . . . . . . . . 47

Table 2-8. AMI Access Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

Table 2-9. MPC Interface Access Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

Table 2-10. HCS12 Access Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

Table 3-1. List of Terms. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

Table 3-2. External Signal Properties. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

Table 3-3. FlexRay Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

Table 3-4. Register Access Conventions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

Table 3-5. Additional Register Reset Conditions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

Table 3-6. Register Write Access Restrictions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

Table 3-7. MVR Field Descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

Table 3-8. MCR Field Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

Table 3-9. FlexRay Channel Selection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

Table 3-10. FlexRay Channel Bit Rate Selection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

Table 3-11. STBSCR Field Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

Table 3-12. Strobe Signal Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

Table 3-13. MBDSR Field Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

Table 3-14. MBSSUTR Field Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

Table 3-15. POCR Field Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

Table 3-16. GIFER Field Descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

Table 3-17. PIFR0 Field Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

Table 3-18. PIFR1 Field Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

Table 3-19. PIER0 Field Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

Table 3-20. PIER1 Field Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

MFR4310 Reference Manual, Rev. 2

Freescale Semiconductor 19

Page 20

Table Number Title Page

Table 3-21. CHIERFR Field Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86

Table 3-22. MBIVEC Field Descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88

Table 3-23. CASERCR Field Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

Table 3-24. CBSERCR Field Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

Table 3-25. PSR0 Field Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

Table 3-26. PSR1 Field Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

Table 3-27. PSR2 Field Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

Table 3-28. PSR3 Field Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

Table 3-29. MTCTR Field Descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

Table 3-30. CYCTR Field Descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

Table 3-31. SLTCTAR Field Descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

Table 3-32. SLTCTBR Field Descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

Table 3-33. RTCORVR Field Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

Table 3-34. OFCORVR Field Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

Table 3-35. CIFRR Field Descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

Table 3-36. SFCNTR Field Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100

Table 3-37. SFTOR Field Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

Table 3-38. SFTCCSR Field Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

Table 3-39. SFIDRFR Field Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

Table 3-40. SFIDAFVR Field Descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103

Table 3-41. SFIDAFMR Field Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103

Table 3-42. NMVR[0:5] Field Descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104

Table 3-43. Mapping of NMVRn to the Received Payload Bytes NMVn. . . . . . . . . . . . . . . . . . . . . . 104

Table 3-44. NMVLR Field Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104

Table 3-45. TICCR Field Descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

Table 3-46. TI1CYSR Field Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 106

Table 3-47. TI1MTOR Field Descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 106

Table 3-48. TI2CR0 Field Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 107

Table 3-49. TI2CR1 Field Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 108

Table 3-50. SSSR Field Descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109

Table 3-51. Mapping Between SSSRn and SSRn . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109

Table 3-52. SSCCR Field Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 110

Table 3-53. Mapping between internal SSCCRn and SSCRn . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 110

Table 3-54. SSR0–SSR7 Field Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

Table 3-55. SSCR0–SSCR3 Field Descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

MFR4310 Reference Manual, Rev. 2

20 Freescale Semiconductor

Page 21

Table Number Title Page

Table 3-56. MTSACFR Field Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

Table 3-57. MTSBCFR Field Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 114

Table 3-58. RSBIR Field Descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 114

Table 3-59. SEL Controlled Receiver FIFO Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 115

Table 3-60. RFSR Field Descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 115

Table 3-61. RFSIR Field Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 115

Table 3-62. RFDSR Field Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 116

Table 3-63. RFARIR Field Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 116

Table 3-64. RFBRIR Field Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 117

Table 3-65. RFMIDAFVR Field Descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 117

Table 3-66. RFMIAFMR Field Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 118

Table 3-67. RFFIDRFVR Field Descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 118

Table 3-68. RFFIDRFMR Field Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 119

Table 3-69. RFRFCFR Field Descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 119

Table 3-70. RFRFCTR Field Descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 120

Table 3-71. LDTXSLAR Field Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 120

Table 3-72. LDTXSLBR Field Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 121

Table 3-73. Protocol Configuration Register Fields. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 121

Table 3-74. Wakeup Channel Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123

Table 3-75. MBCCSRn Field Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 130

Table 3-76. MBCCFRn Field Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 132

Table 3-77. Channel Assignment Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 132

Table 3-78. MBFIDRn Field Descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 133

Table 3-79. MBIDXRn Field Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 133

Table 3-80. Frame Header Write Access Constraints . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 143

Table 3-81. Frame Header Field Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 144

Table 3-82. Receive Message Buffer Slot Status Content . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 146

Table 3-83. Receive Message Buffer Slot Status Field Descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . 146

Table 3-84. Transmit Message Buffer Slot Status Content . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 148

Table 3-85. Transmit Message Buffer Slot Status Structure Field Descriptions . . . . . . . . . . . . . . . . . 148

Table 3-86. Message Buffer Data Field Minimum Length . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 149

Table 3-87. Frame Data Write Access Constraints . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 151

Table 3-88. Frame Data Field Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 151

Table 3-89. Individual Message Buffer Types. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 152

Table 3-90. Single Transmit Message Buffer Access Regions Description. . . . . . . . . . . . . . . . . . . . . 153

MFR4310 Reference Manual, Rev. 2

Freescale Semiconductor 21

Page 22

Table Number Title Page

Table 3-91. Single Transmit Message Buffer State Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 154

Table 3-92. Single Transmit Message Buffer Application Transitions . . . . . . . . . . . . . . . . . . . . . . . . 155

Table 3-93. Single Transmit Message Buffer Module Transitions . . . . . . . . . . . . . . . . . . . . . . . . . . . 156

Table 3-94. Single Transmit Message Buffer Transition Priorities . . . . . . . . . . . . . . . . . . . . . . . . . . . 156

Table 3-95. Receive Message Buffer Access Region Description. . . . . . . . . . . . . . . . . . . . . . . . . . . . 162

Table 3-96. Receive Message Buffer States and Access . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 162

Table 3-97. Receive Message Buffer Application Transitions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 163

Table 3-98. Receive Message Buffer Module Transitions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 164

Table 3-99. Receive Message Buffer Transition Priorities . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 164

Table 3-100. Receive Message Buffer Update. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 165

Table 3-101. Double Transmit Message Buffer Access Regions Description . . . . . . . . . . . . . . . . . . . . 169

Table 3-102. Double Transmit Message Buffer State Description (Commit Side) . . . . . . . . . . . . . . . . 170

Table 3-103. Double Transmit Message Buffer State Description (Transmit Side) . . . . . . . . . . . . . . . 171

Table 3-104. Double Transmit Message Buffer Host Transitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 172

Table 3-105. Double Transmit Message Buffer Module Transitions. . . . . . . . . . . . . . . . . . . . . . . . . . . 173

Table 3-106. Double Transmit Message Buffer Transition Priorities . . . . . . . . . . . . . . . . . . . . . . . . . . 173

Table 3-107. Message Buffer Search Priority . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 177

Table 3 -108. Sync Frame Table Generation Modes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 188

Table 3-109. Slot Status Content . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 195

Table 3-110. FlexRay Channel Bit Rate Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 202

Table 3-111. Minimum f

[MHz] examples (128 message buffers) . . . . . . . . . . . . . . . . . . . . . . . . . . 204

chi

Table 3-112. Protocol Control Command Priorities. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 205

Table 4-1. Pin Functions (Functional Mode) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 208

Table 4-2. Pin Functions (Reset Mode) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 209

Table 4-3. Port Integration Module Memory Map. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 209

Table 4-4. HIPDSR Field Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 211

Table 4-5. PLPDSR Field Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 211

Table 4-6. HIPPER Field Descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 212

Table 4-7. HIPPCR Field Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 213

Table 4-8. PLPPER Field Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 215

Table 4-9. PLPPCR Field Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 215

Table 4-10. Reset Mode Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 216

Table 5-1. VREG3V3V2 — Signal Properties. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 219

Table 5-2. VREG3V3V2 — Reset Sources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 221

Table 6-1. MFR4310 Relevant Pins for the CRG. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 224

MFR4310 Reference Manual, Rev. 2

22 Freescale Semiconductor

Page 23

Table Number Title Page

Table 6-2. DER Field Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 225

Table 6-3. CRSR Field Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 225

Table 6-4. CRG Reset Sources Priorities . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 226

Table 6-5. IF_SEL[1:0] Encoding by CRSR.ECS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 230

Table A-1. Absolute Maximum Ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 239

Table A-2. ESD and Latch-up Test Conditions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 240

Table A-3. ESD and Latch-up Protection Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 240

Table A-4. Operating Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 241

Table A-5. Thermal Package Simulation Details . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 243

Table A-6. 5V I/O Characteristics (VDD5 = 5V) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 244

Table A-7. 3.3V I/O Characteristics (VDD5 = 3.3V) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 245

Table A-8. Supply Current Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 246

Table A-9. Voltage Regulator — Operating Conditions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 247

Table A-10. Voltage Regulator Recommended Capacitive Loads . . . . . . . . . . . . . . . . . . . . . . . . . . . . 248

Table A-11. Startup Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 249

Table A-12. Oscillator Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 250

Table A-13. AMI Interface AC Switching Characteristics Over the Operating Range . . . . . . . . . . . . 252

Table A-14. MPC Interface AC Switching Characteristics Over the Operating Range . . . . . . . . . . . . 254

Table A-15. HCS12 Interface AC Switching Characteristics Over the Operating Range . . . . . . . . . . 256

Table C-1. Suggested External Component Values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 261

MFR4310 Reference Manual, Rev. 2

Freescale Semiconductor 23

Page 24

Table Number Title Page

MFR4310 Reference Manual, Rev. 2

24 Freescale Semiconductor

Page 25

Chapter 1 Introduction

This reference manual provides information on a system that includes the MFR4310 FlexRay

Communication Controller Module.

1.1 Audience

This reference manual is intended for application and system hardware developers who wish to develop

products for the FlexRay MFR4310. It is assumed that the reader understands FlexRay protocol

functionality and microcontroller system design.

1.2 Additional Reading

For additional reading that provides background to, or supplements, the information in this manual:

• For more information about the FlexRay protocol, refer to the following document:

— FlexRay Communications System Protocol Specification V2.1A

— FlexRay Communications System Electrical Physical Layer Specification V2.1A

• For more information about M9HCS12, MPC5xx and MPC55xx Family devices and how to

program them, refer to the Freescale Products section at www.freescale.com.

MFR4310 Reference Manual, Rev. 2

Freescale Semiconductor 25

Page 26

Introduction

1.3 Terminology

Table 1-1. Acronyms and Abbreviations

Term Meaning

AMI Asynchronous Memory Interface

BCU Buffer Control Unit

CC Communication Controller

CDC Clock Domain Crosser

CHI Controller Host Interface

ID Identification

EBI External Bus Interface

FRM FlexRay Memory

FSS Frame Start Sequence

HCS12 Freescale’s HCS12 family of microcontrollers

HIF Host Interface

LUT Look Up Table

MBIDX Message Buffer Index

MBNum Message Buffer Number

MCU Microcontroller Unit

MPC Device title prefix for Freescale’s MPC5xx and MPC55xx family microcontrollers

μT Microtick. A microtick is one CLK_CC period long, and starts on the rising edge of CLK_ CC.

MT Macrotick

MTS Media Access Test Symbol

NIT Network Idle Time

PE Protocol Engine

PHY Physical Layer Interface

PL Physical Layer

POC Protocol Operation Control

SEQ Sequencer Engine

Rx Reception

TCU Time Control Unit

Tx Transmission

MFR4310 Reference Manual, Rev. 2

26 Freescale Semiconductor

Page 27

Introduction

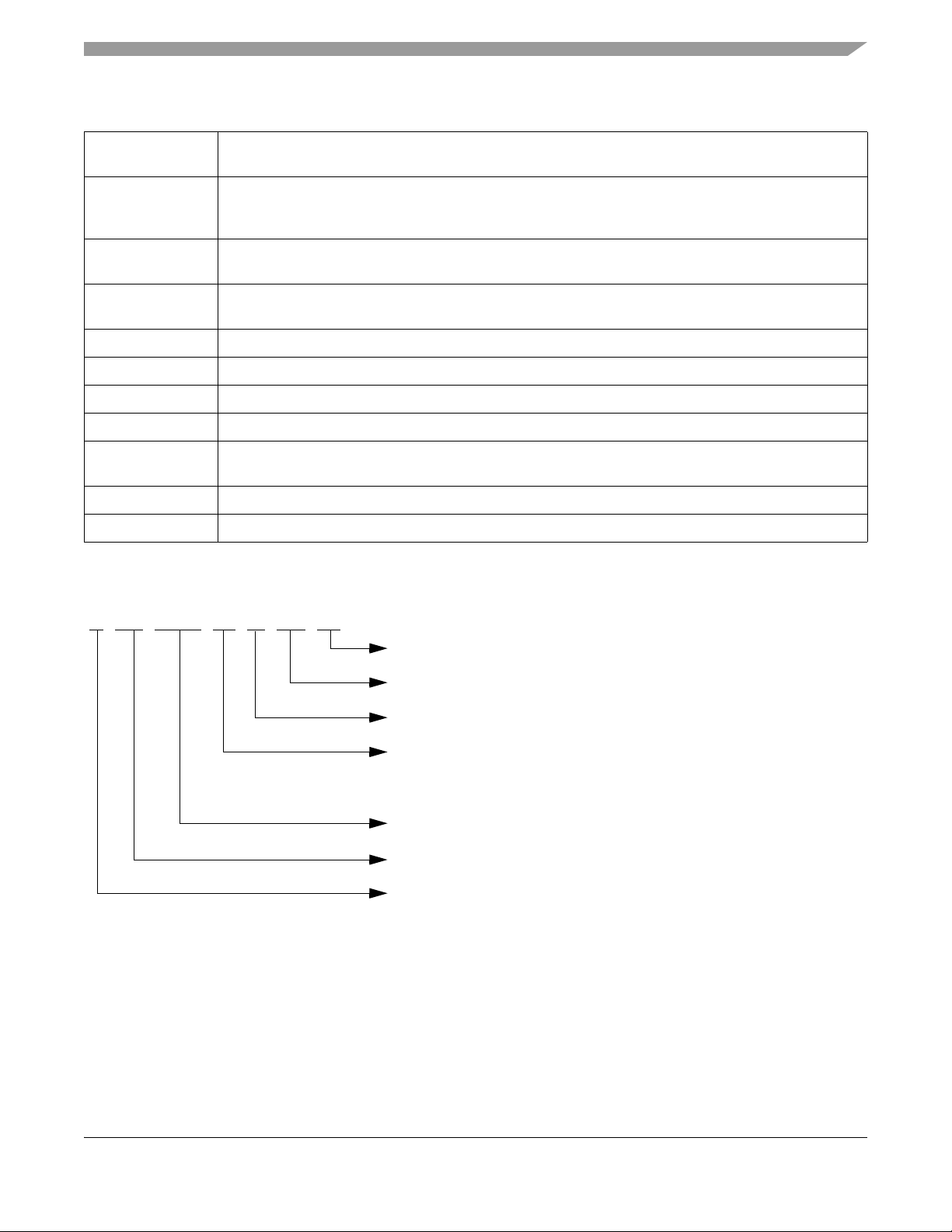

S FR 4310 J1 M AE 40

Speed Option

Temperature Option

Device Title

Controller Family

Qualification

Package Option

40 = 40 MHz

AE = 64-pin Lead Free/Halide Free LQFP

M = -40

o

C to +125oC

S = Maskset specific part number

Maskset Identifier First character usually identifies wafer fab

Second character usually identifiesSuffix

mask revision

active-high Names of signals that are active-high are shown in upper case text, without a # symbol at the end.

Active-high signals are asserted (active) when they are high and deasserted when they are low.

active-low An active-low signal is asserted (active) when it is at the logic low level and is deasserted when it is at the

logic high level.

Note: A # symbol at the end of a signal name indicates that the signal is active-low.

asserted A signal that is asserted is in its active logic state. An active-low signal changes from high to low when

asserted; an active-high signal changes from low to high when asserted.

deasserted A signal that is deasserted is in its inactive logic state. An active-low signal changes from low to high when

deasserted; an active-high signal changes from high to low when deasserted.

set To set a bit means to establish logic level one on the bit.

clear To clear a bit means to establish logic level zero on the bit.

0x0F The prefix 0x denotes a hexadecimal number.

0b0011 The prefix 0b denotes a binary number.

x In certain contexts, such as a signal encoding, this indicates don’t care. For example, if a field is binary

encoded 0bx001, the state of the most significant bit is don’t care.

== Used in equations, this symbol signifies comparison.

# A # symbol at the end of a signal name indicates that the signal is active-low.

Table 1-2. Notational Conventions

1.4 Part Number Coding

Figure 1-1. Order Part Number Coding

MFR4310 Reference Manual, Rev. 2

Freescale Semiconductor 27

Page 28

Introduction

MFR4310 Reference Manual, Rev. 2

28 Freescale Semiconductor

Page 29

Chapter 2 Device Overview

2.1 Introduction

The MFR4310 FlexRay Communication Controller implements the FlexRay protocol according to the

FlexRay Communications System Protocol Specification V2.1A.

The controller host interface (CHI) of the MFR4310 FlexRay Communication Controller is implemented

in accordance with Chapter 3, “FlexRay Module (FLEXRAYV4)” of this reference manual.

2.2 Features

The MFR4310 FlexRay controller provides the following features:

• Single channel support

— Internal channel A and FlexRay Port A can be configured to be connected to physical FlexRay

channel A or physical FlexRay channel B

• Variable bit rate support: 2.5, 5, 8, or 10 Mb/s

• 128 configurable message buffers with

— Individual frame ID filtering

— Individual channel ID filtering

— Individual cycle counter filtering

• Message buffer header, status and payload data are stored in FlexRay memory

— Consistent data access ensured by means of buffer locking scheme

— Host can lock multiple buffers at the same time

• Size of message buffer data section configurable from 0 up to 254 bytes

• Two independent message buffer segments with configurable size of payload data section

— Each segment can contain message buffers assigned to the static segment and message buffers

assigned to the dynamic segment at the same time

• Zero padding for transmit message buffers in static segment

— Applied when the frame payload length exceeds the size of the message buffer data section

• Transmit message buffers configurable with state/event semantics

• Message buffers can be configured as

— Receive message buffers

— Single buffered transmit message buffer

— Double buffered transmit message buffer (combines two single buffered message buffer)

• Individual message buffer reconfiguration supported

— Means provided to safely disable individual message buffers

— Disabled message buffers can be reconfigured

MFR4310 Reference Manual, Rev. 2

Freescale Semiconductor 29

Page 30

Device Overview

• Two independent receive FIFOs

— One receive FIFO per channel

— Up to 256 entries for each FIFO

— Global frame ID filtering, based on both value/mask filters and range filters

— Global channel ID filtering

— Global message ID filtering for the dynamic segment

• Four configurable slot error counters

• Four dedicated slot status indicators

— Used to observe slots without using receive message buffers

• Provides measured value indicators for clock synchronization

— PE internal synchronization frame ID and measurement tables can be copied into the FlexRay

memory

• Fractional macroticks are supported for clock correction

• Maskable interrupt sources provided through individual and combined interrupt lines

• One absolute timer

• One timer that can be configured to absolute or relative

Features specific to the MFR4310 include the following:

• Identical pinout to MFR4300; pin functionality compatible with MFR4300

• Three hardware selectable host interfaces:

— HCS12 Interface for direct connection to Freescale’ s HCS12 family of microcontrollers, with

interface clock signal to synchronize the data transfer (the maximum frequency of this clock

signal can be calculated from the ECLK_CC pulse width low and high times, t

LEC

and t

given in Table A-15.)

— Asynchronous Memory Interface (AMI) for asynchronous connection to microcontrollers —

minimum read access time of 56 ns (with CHICLK_CC running at 76 MHz)

— MPC Interface for asynchronous connection to Freescale’s MPC5xx and MPC55xx family

microcontrollers — minimum read access time of 56 ns (with CHICLK_CC running at

76 MHz)

• 8K bytes addressable for byte or word accesses

• Internal quartz oscillator of 40 MHz

• CHI and AMI/MPC clock selectable between 40 MHz oscillator clock used for PE and 20 MHz to

76 MHz separate CHI/AMI/MPC-only clock

• Internal voltage regulator for the digital logic and the oscillator

• Hardware selectable clock output to drive external host devices: disabled, 4, 10, or 40 MHz

• Maskable interrupt sources available over one interrupt output line

HEC

• RESET# glitch filter

• Electrical physical layer interface compatible with dedicated FlexRay physical layer

• Four multiplexed debug strobe pins

MFR4310 Reference Manual, Rev. 2

30 Freescale Semiconductor

Page 31

2.3 Block Diagram

Voltage Regulator

VSSR

VDDA

VSSA

VDDR

VSS2_5

VDD2_5

Oscillator

Clock and Reset

Gen. Module

RESET#

External

Clock Interface

CLKOUT/TM0

D0/PA7

D1/PA6

D2/PA5

D3/PA4

D4/PA3

D5/PA2

D6/PA1

D7/PA0

D8/PB7

D9/PB6

D10/PB5

D11/PB4

D12/PB3

D13/PB2

D14/PB1

D15/PB0

External

Bus Interface

AMI

HCS12

Interface

A1/XADDR19

A2/XADDR18

A3/XADDR17

A4/XADDR16

A5/XADDR15

A6/XADDR14

A7

A8

A9

OE#/ACS0

A11/ACS1

A12/ACS2

WE#/RW_CC#

CE#/LSTRB

A10/ECLK_CC

INT_CC#

Receiver A

Receiver B

RXD_BG2

RXD_BG1

Transmitter A Transmitter B

TXD_BG1/IF_SEL1

TXEN1#

TXD_BG2/IF_SEL0

TXEN2#

DBG3/CLK_S1

TCU Debug

TEST

VDDX[1:4]

VSSX[1:4]

XTAL

EXTAL/CLK_CC