Page 1

e200z3 Power Architecture™

Core Reference Manual

Supports

e200z3

e200z335

e200z3coreRM

Rev. 2

06/2008

Page 2

How to Reach Us:

Home Page:

www.freescale.com

Web Support:

http://www.freescale.com/support

USA/Europe or Locations Not Listed:

Freescale Semiconductor, Inc.

Technical Infor mation Center, EL516

2100 East Elliot Road

Tempe, Arizona 85284

+1-800-521-6274 or

+1-480-768-2130

www.freescale.com/support

Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH

Technical Information Center

Schatzbogen 7

81829 Muenchen, Germany

+44 1296 380 456 (English)

+46 8 52200080 (English)

+49 89 92103 559 (German)

+33 1 69 35 48 48 (French)

www.freescale.com/support

Japan:

Freescale Semiconductor Japan Ltd.

Headquarters

ARCO Tower 15F

1-8-1, Shimo-Meguro, Meguro-ku

Tokyo 153-0064

Japan

0120 191014 or

+81 3 5437 9125

support.japan@freescale.com

Asia/Pacific:

Freescale Semiconductor China Ltd.

Exchange Building 23F

No. 118 Jianguo Road

Chaoyang District

Beijing 100022

China

+86 010 5879 8000

support.asia@freescale.com

For Literature Requests Only:

Freescale Semiconductor

Literature Distribution Center

P.O. Box 5405

Denver, Colorado 80217

+1-800 441-2447 or

+1-303-675-2140

Fax: +1-303-675-2150

LDCForFreescaleSemiconductor

@hibbertgroup.com

Information in this document is provided solely to enable system and software

implementers to use Freescale Semiconductor products. There are no express or

implied copyright licenses granted hereunder to design or fabricate any integrated

circuits or integrated circuits based on the informat ion in this document.

Freescale Semiconductor reserves the right to make changes without further notice to

any products herein. Freescale Semiconductor makes no warranty, representation or

guarantee regarding the suitability of its products for any particular purpose, nor does

Freescale Semiconductor assume any liability arising out of the application or use of

any product or circuit, and specifically disclaims any and all liability, including without

limitation consequential or incidental damages. “Typical” parameters which may be

provided in Freescale Semiconductor data sheets and/or specifications can and do

vary in different applications and actual performance may vary over time. All operating

parameters, including “Typicals” must be validated for each customer application by

customer’s technical experts. Freescale Semiconductor does not convey any license

under its patent rights nor the rights of others. Freescale Semiconductor products are

not designed, intended, or authorized for use as components in systems intended for

surgical implant into the body, or other applications intended to support or sustain life,

or for any other application in which the failure of the Freescale Semiconductor product

could create a situation where personal injury or death may occur. Should Buyer

purchase or use Freescale Semiconductor products for any such unintended or

unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor

and its officers, employees, subsidiaries, affiliates, and distributors har mless against all

claims, costs, damages, and expenses, and reasonable attorney fees arising out of,

directly or indirectly, any claim of personal injury or death associated with such

unintended or unauthorized use, even if such claim alleges that Freescale

Semiconductor was negligent regarding the design or manufacture of the part.

Freescale, the Freescale logo, and StarCore and the Freescale logo are

trademarks or registered trademarks of Freescale Semiconductor, Inc. in

the U.S. and other countries. All other product or service names are the

property of their respective owners. HyperTransport is a trademark of the

HyperTransport Technology Consortium. The Power Architecture and

Power.org word marks and the Power and Power.org logos and related

marks are trademarks and ser vice marks licensed by Power.org. The

PowerPC name is a trademark of IBM Corp. and is used under license.

RapidIO is a registered trademark of the RapidIO Trade Association. IEEE

nnn, nnn, and nnn are trademarks or registered trademarks of the Institute

of Electrical and Electronics Engineers, Inc. (IEEE). This product is not

endorsed or approved by the IEEE.

© Freescale Semiconductor, Inc., 2007. All rights reserved.

Document Number: e200z3coreRM

Rev. 2, 06/2008

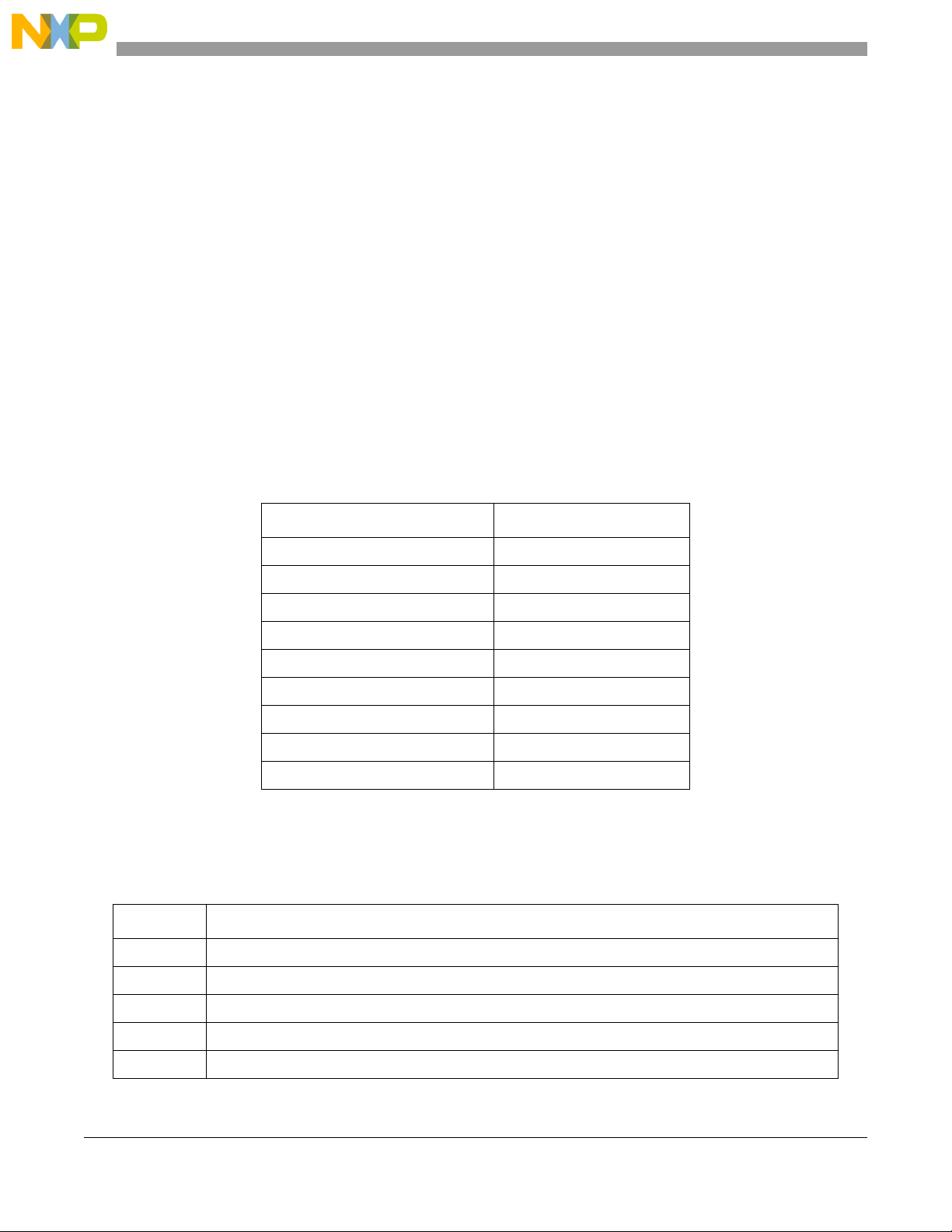

Page 3

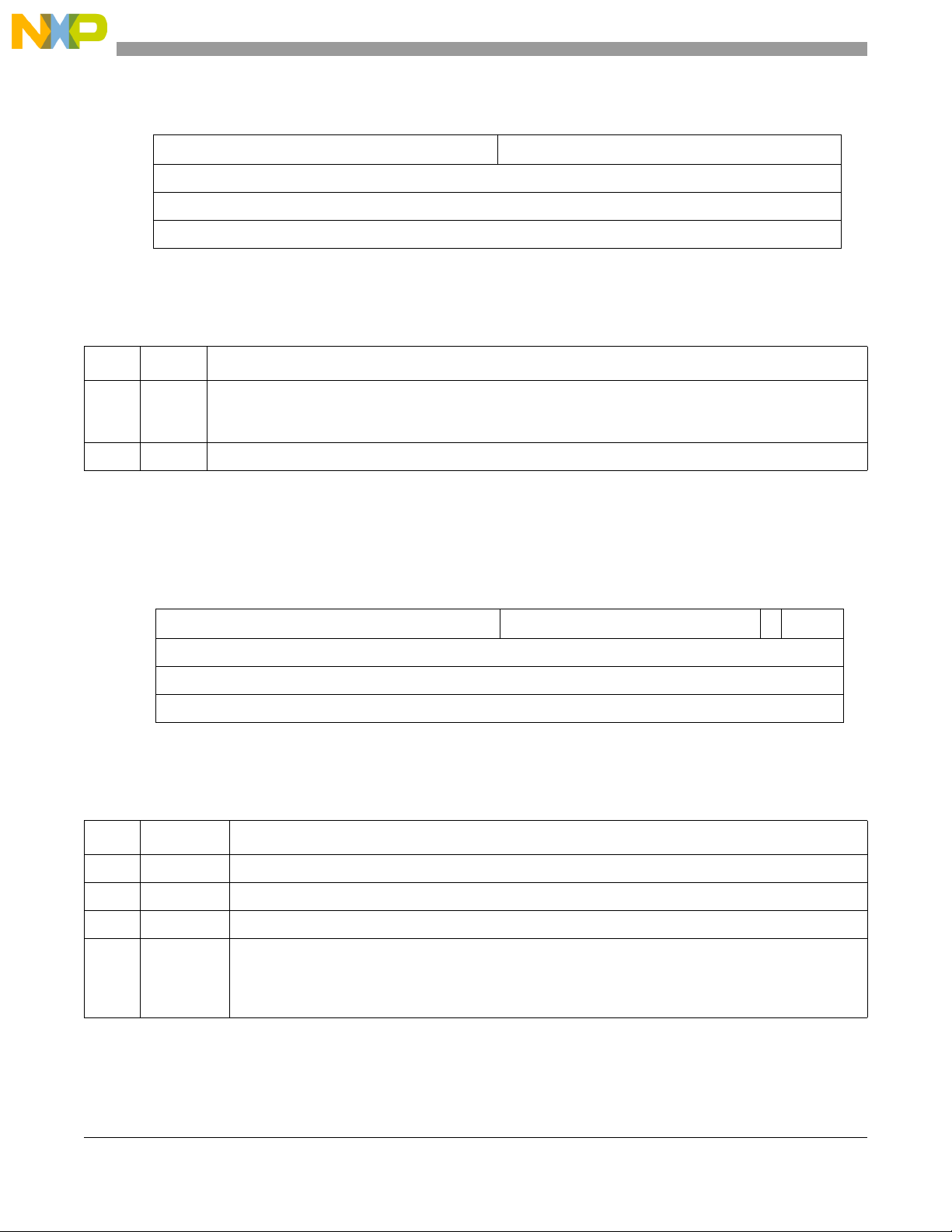

Contents

Paragraph

Number Title

Page

Number

General Information......................................................................................................... viii

Related D o cu mentatio n..... ................ ......................... ........................ ................................ i x

Terminology Conventions....................................................................................................x

Acronyms and Abbreviations ..............................................................................................x

Chapter 1

e200z335 Core Complex Overview

1.1 Overview of the e200z3 and e200z335............................................................................1-1

1.1.1 Features........................................................................................................................1-4

1.2 Programming Model........................................................................................................ 1-5

1.2.1 Regist e r S e t ..... ........ ................ ......................... ................ ........................ ....................1-5

1.3 Ins t ruction Set ... ........ ........................ ......................... ........................ ................ ..............1-7

1.4 VLE Category..................................................................................................................1-8

1.5 Interrupts and Exception Handling.................................................................................. 1-8

1.5.1 Interrupt Handling........................................................................................................ 1-9

1.5.2 Interrupt Classes ..........................................................................................................1-9

1.5.3 Interrupt Types........................................................................................................... 1-10

1.5.4 Interrupt Registers...................................................................................................... 1-10

1.6 Microarchitecture Summary .......................................................................................... 1-12

1.6.1 Instruction Unit Fea t u res ...................... ......................... ................ ........................ .... 1-13

1.6.2 Intege r Un it Features ................ ......................... ........................ ........................ ........ 1 -13

1.6.3 Load/Store Unit (LS U ) F e at u res................... ................. ........................ ................ .... 1-13

1.6.4 Memory Management Uni t (M MU) Features...... .................... .............................. ... 1-14

1.6.5 System Bus (Core Complex Interface) Features...................... .... .... .... .... .... ...... .... .... 1-14

1.6.6 Nexus 32+ Module Features...................................................................................... 1-14

1.7 Legacy Support of PowerPC Architecture.....................................................................1-14

1.7.1 Instruction Set Compatibility..................................................................................... 1-15

1.7.1.1 User Ins t ru c t i o n Set .......... ................ ......................... ................ ........................ .... 1-15

1.7.1.2 Supervi sor Instru ction Set ............... ......................... ................ ................ .............. 1- 1 5

1.7.2 Memory Subsystem ................................................................................................... 1-15

1.7.3 Interrupt Handling...................................................................................................... 1-15

1.7.4 Memory Management................................................................................................ 1-16

1.7.5 Reset........................................................................................................................... 1-16

1.7.6 Little-Endian Mode. ...................................................................................................1-16

e200z3 Power Architecture Core Reference Manual, Rev. 2

Freescale Semiconductor iii

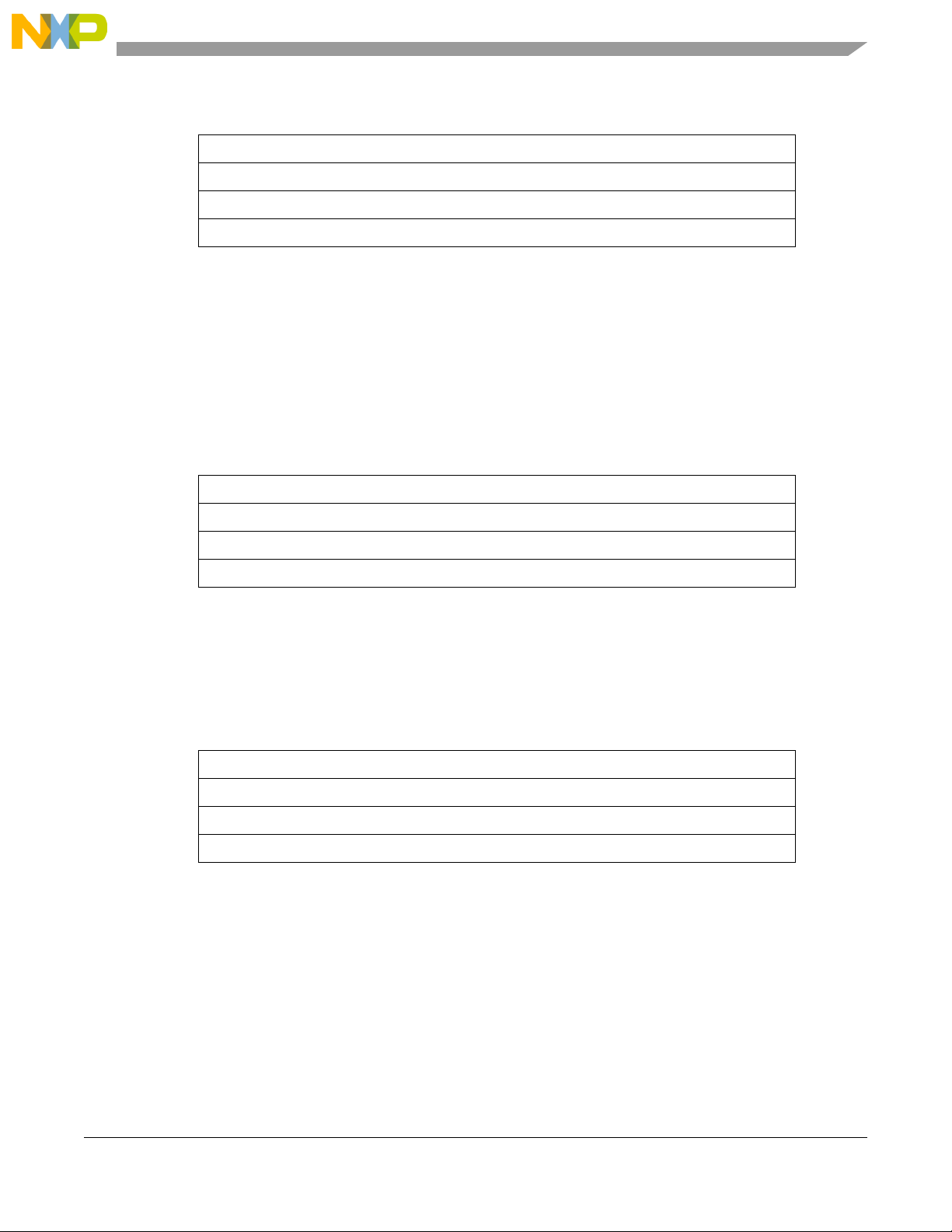

Page 4

Contents

Paragraph

Number Title

Page

Number

Chapter 2

Register Model

2.1 PowerPC Book E Registers ............................................................................................. 2-4

2.2 e200z3-Specific Registers................................................................................................ 2-6

2.3 e200z3-Specific Device Control Registers...................................................................... 2-7

2.4 Proc essor Cont ro l Reg isters................ ......................... ........................ ................ ............ 2-7

2.4.1 Machine State Register (MSR)..................... ......................... ........................ .............. 2- 7

2.4.2 Proce sso r ID Re g i ster (PIR) ......... ................ ......................... ................ ...................... 2-9

2.4.3 Processo r Version Regi ster (PVR )................................. ........................ ................ .... 2-10

2.4.4 System Ver si o n Re g i st er (SVR)............................. ........................ ........................ .... 2-10

2.5 Registers for Integer Operations.................................................................................... 2-11

2.5.1 General-Purpose Registers (GPRs)............................................................................ 2-11

2.5.2 Intege r Ex ception Regi ster (XER )................ ......................... ........................ ............ 2-11

2.6 Registers for Branch Operations.................................................................................... 2-12

2.6.1 Condition Register (CR)............................................................................................ 2-12

2.6.1.1 CR Setti n g fo r In t eger Inst ru ctions......... ................. ........................ ................ ...... 2- 1 4

2.6.1.2 CR Setting for Store Conditional Instructions .......................................................2-14

2.6.1.3 CR Settin g fo r Co m p a re Instruct ions ..... ......... ................ ........................ .............. 2- 1 4

2.6.2 Count Register (CTR)................................................................................................ 2-15

2.6.3 Link Regi ster (LR).... ........ ........................ ......................... ........................ ................ 2 -15

2.7 SPE and SPFP APU Registers....................................................................................... 2-16

2.7.1 Signal Processing/Embedded Floating-Point Status and Control

Regist e r (S P EFSCR) ............... ......................... ........................ .............................. 2-16

2.7.2 Accumulator (ACC)................................................................................................... 2-19

2.8 Interrupt Registers..........................................................................................................2-19

2.8.1 Interrupt Registers Defined by Book E...................................................................... 2-19

2.8.1.1 Save/Restore Register 0 (SRR0 )............................ ........................ ........................ 2-20

2.8.1.2 Save/Restore Register 1 (SRR1 )............................ ........................ ........................ 2-20

2.8.1.3 C ri t ical Save/Restore Regis t e r 0 (CS R R0). .......... .................... .. .......... .................2-20

2.8.1.4 C ri t ical Save/Restore Regis t e r 1 (CS R R1). .......... .................... .. .......... .................2-21

2.8.1.5 Data Exception Add ress Regist er (DEAR)........................ ........................ ............ 2-21

2.8.1.6 Interrupt Vector Prefix Register (IVPR)................................................................ 2-21

2.8.1.7 Interrupt Vector Offset Registers (IVORs) ............................................................ 2-22

2.9 Exception Syndrome Register (ESR) ............................................................................ 2-23

2.9.1 VLE Mode Instruction Syndrome.............................................................................. 2- 25

2.9.2 Misaligned Instruction Fetch Syndrome.................................................................... 2-25

2.9.3 Precise External Termination Error Syndrome.......................................................... 2-25

2.9.4 e200z3-Specific Interrupt Registers........................................................................... 2-26

2.9.4.1 Debug Save/Restore Register 0 (DSRR0) ............................................................. 2-26

2.9.4.2 Debug Save/Restore Register 1 (DSRR1) ............................................................. 2-26

e200z3 Power Architecture Core Reference Manual, Rev. 2

iv Freescale Semiconductor

Page 5

Contents

Paragraph

Number Title

Page

Number

2.9.4.3 Machine Check Syndrome Register (MCSR)........................................................ 2-26

2.10 Software-Use SPR s ( SP R G0 – SPRG7 and U SP RG0) ... ........ ........................ ................ 2- 2 7

2.11 Timer Registers......... ................ ........................ ......................... ........................ ............2-28

2.11.1 Timer Control Re g i ster (TCR)................ ......................... ........................ .................. 2-29

2.11.2 Timer Status Register (TSR)...................................................................................... 2-30

2.11.3 Time Base (TBU an d TBL) .. ................................. ........................ ........................ .... 2-31

2.11.4 Decrementer Register ................................................................................................ 2-33

2.11.5 Dec rementer Auto -Reload Regist er (DECAR)............................... ...........................2-33

2.12 Debug Registers.............................................................................................................2-34

2.12.1 Debug Address and Value Registers.......................................................................... 2-34

2.12.1.1 Instruction Address Compare Registers (IAC1–IAC4)......................................... 2-34

2.12.1 .2 Data Add ress Compare Re g i st ers (DAC1–D A C2).... ........................ .................... 2-35

2.12.1.3 Data Value Compare Registers (DVC1–DVC2) (e200z335 only)........................ 2-35

2.12.2 Debug Counter Register (DBCNT) ........................................................................... 2-36

2.12.3 Debug Control and Status Registers (DBCR0–DBCR3)........................................... 2-36

2.12.3.1 Debug Control Register 0 (DBCR0)......................................................................2-36

2.12.3.2 Debug Control Register 1 (DBCR1)......................................................................2-39

2.12.3.3 Debug Control Register 2 (DBCR2)......................................................................2-41

2.12.3.4 Debug Control Register 3 (DBCR3)......................................................................2-43

2.12.3.5 Debug Control Register 4 (DBCR4) (e200z335 only)..........................................2-48

2.12.4 Debug Status Register (DBSR)..................................................................................2-49

2.12.5 Debug External Resource Control Register (DBERC0)............................................ 2-50

2.13 Hardware Implementation-Dependent Registers........................................................... 2-57

2.13.1 Hardwa r e Im p l e m e n t a t i o n -Dependent Register 0 (HI D 0 )............ .............................2-57

2.13.2 Hardwa r e Im p l e m e n t a t i o n -Dependent Register 1 (HI D 1 )............ .............................2-59

2.14 Branch Target Buffer (BTB) Registers.......................................................................... 2-61

2.14.1 Branch Unit Control and Status Register (BUCSR).................................................. 2-61

2.15 L1 Cache Configuration Registers................................................................................. 2-61

2.15.1 L1 Cac h e Configuratio n Register 0 (L1CFG0) ........ .......... .................... ...................2-61

2.16 MMU Registers.............................................................................................................. 2-62

2.16.1 MMU Control and Sta t u s Register 0 (M MU C S R0)..... .......... .............................. ..... 2-62

2.16.2 MMU Configuration Register (MMUCFG) .............................................................. 2-62

2.16.3 TLB Configuration Registers (TLBnCFG)................................................................ 2-63

2.16.3.1 TLB Configuration Register 0 (TLB0CFG).......................................................... 2-63

2.16.3.2 TLB Configuration Register 1 (TLB1CFG).......................................................... 2-64

2.16.4 MMU Assist Registers (MAS0–MAS4, MAS6) ....................................................... 2-65

2.16.5 Process ID Register (PID0)........................................................................................ 2-69

2.17 Support for Fast Context Switching...............................................................................2-69

2.17.1 Context Co n trol Regis ter (CTXCR) ........................ ................ ........................ .......... 2-70

2.18 SPR Register Access...................................................................................................... 2-70

2.18.1 Invalid S PR References...... ........ ................ ......................... ........................ .............. 2-70

e200z3 Power Architecture Core Reference Manual, Rev. 2

Freescale Semiconductor v

Page 6

Contents

Paragraph

Number Title

Page

Number

2.18.2 Synchro n i zation Requirements for SPRs...... ................. ........................ .................... 2-7 0

2.18.3 Special-Purpose Register Summary........................................................................... 2-71

2.18.4 Reset Settings.............................................................................................................2-74

2.19 Parallel Signat u re U n i t Register s...................... ................. ........................ ................ .... 2-76

2.19.1 Parallel Signatu re Co n t r o l Register (PSCR).......................... ........................ .. ........ .. 2-77

2.19.2 P arallel Signature Status Register (PSSR)................................................................. 2-78

2.19.3 Parallel Signatu re H i g h Re g i st e r (P SHR)... ................. ........................ ................ ...... 2- 7 8

2.19.4 Parallel Signatu re L o w Re g is t e r (PSLR)................. .. ........ ........................ ................ 2-79

2.19.5 Parallel Signature Counter Register (PSCTR)........................................................... 2-79

2.19.6 Parallel Signature Update High Register (PSUHR) .................................................. 2-80

2.19.7 Parallel Signature Update Low Register (PSULR)....................................................2-80

Chapter 3

Instruction Model

3.1 Operand Conventions ...................................................................................................... 3-1

3.1.1 Data Organization in Memory and Data Transfers......................................................3-1

3.1.2 Alignment and Misaligned Accesses........................................................................... 3-1

3.1.3 e200z3 Floating-Point Implementation .......................................................................3-2

3.2 Unsupported Instructions and Instruction Forms.............................................................3-2

3.3 Optionally Supported Instructions and Instruction Forms...............................................3-2

3.4 Implementation-Specific Instructions.............................................................................. 3-3

3.5 BookE Instruction Extensions ......................................................................................... 3-3

3.6 Memory Access Alignment Support................................................................................ 3-4

3.7 Memory Synchronization and Reservation Instructions.................................................. 3-4

3.8 Bran c h Pr e d i ction ... ........................ ......................... ........................ ........................ ........3-5

3.9 Interruption of Instructions by Interrupt Requests........................................................... 3-5

3.10 e200z3-Specific Instructions............................................................................................ 3-6

3.10.1 Intege r S e l e ct A PU ........................... ......................... ................ ........................ .......... 3-6

3.10.2 Debug APU.................................................................................................................. 3-6

3.10.3 Wait APU (e200z335 only).......................................................................................... 3-6

3.10.4 Volatile Context Save/Restore APU (e200z335 only)....................................... .......... 3-7

3.10.5 SPE APU Instructions.................................................................................................. 3-7

3.10.6 Embedded Vector and Scalar Single-Precision Floating-Point APU

Instructions ............................................................................................................ 3-15

3.10.6.1 Options for Embedded Floating-Point APU Implementations..............................3-16

3.11 Unimplemented SPRs and Read-Only SPRs................................................................. 3-16

3.12 Invalid In struct ion Forms........ ........ ................ ................. ................ ................ .............. 3- 1 7

3.13 Instruction Summ ary... ........ ........................ ................. ........................ ................ .......... 3-17

3.13.1 Instruction Index Sorted by Mnemonic ..................................................................... 3-18

3.13.2 Instruction Index Sorted by Opcode.......................................................................... 3-29

e200z3 Power Architecture Core Reference Manual, Rev. 2

vi Freescale Semiconductor

Page 7

Contents

Paragraph

Number Title

Page

Number

Chapter 4

Interrupts and Exceptions

4.1 Overview..........................................................................................................................4-1

4.2 e200z3 Interrupts .......................................... ....................................... .................... ........ 4-2

4.3 Exception Syndrome Register (ESR) .............................................................................. 4-4

4.4 Mac h ine State Regis ter (MSR) ............................ ........................ ................ .................... 4-5

4.4.1 Machine Check Syndrome Register (MCSR).............................................................. 4-7

4.4.1.1 Interrupt Vector Prefix Register (IVPR).................................................................. 4-8

4.5 Interrupt Vector Offset Registers (IVORn)...................................................................... 4-8

4.6 Interrupt Definitions ...................................................................................................... 4-10

4.6.1 Critical Input Interrupt (IVOR0)................................................................................4-10

4.6.2 Machine Check Interrupt (IVOR1)............................................................................ 4-11

4.6.2.1 Machine Ch ec k In t e rrupt Enable d (MSR[ME]=1)......................... ....................... 4-1 1

4.6.2.2 Checkstop State ..................................................................................................... 4-12

4.6.2.3 Non-Maskable Interrupts (NMI) (e200z335 only) ................................................ 4-13

4.6.3 Data Storag e I n terrupt (I V O R2 ) ..... ........ ......................... ................ ........................ .. 4-13

4.6.4 Instruction Storage Interrupt (IVOR3) ...................................................................... 4-14

4.6.5 External Input Interrupt (IVOR4)..............................................................................4-15

4.6.6 Alignment Interrupt (IVOR5).................................................................................... 4-16

4.6.7 Program Interrupt (IVOR6) ....................................................................................... 4-16

4.6.8 Floating-Point Unavailable Interrupt (IVOR7).......................................................... 4-17

4.6.9 System Call Interrupt (IVOR8).................................................................................. 4-18

4.6.10 Auxiliary Processor Unavailable Interrupt (IVOR9)................................................. 4-18

4.6.11 Decrementer Interrupt (IVOR10) .............................................................................. 4-19

4.6.12 Fixed-Interval Timer Interrupt (IVOR11)..................................................................4-19

4.6.13 Watchdog Timer Interrupt (IVOR12) ................................................ ........................ 4- 20

4.6.14 Data TLB Error Inter ru p t (IVOR13) .. ........ ......................... ................ ...................... 4-21

4.6.15 Instru ction TLB Er r o r In terrupt (IV O R14)........ ........................ ................ ................ 4-21

4.6.16 Debug Interrupt (IVOR15) ........................................................................................4-22

4.6.17 System Reset..............................................................................................................4-25

4.6.18 SPE APU Una v a i l a b l e In terrupt (IVOR32)........................... ........................ ............ 4-26

4.6.19 SPE Floating-Point Data Interrupt (IVOR33) ........................................................... 4-27

4.6.20 SPE Floating-Point Round Interrupt (IVOR34) ........................................................ 4-27

4.7 Exception Recognition and Priorities . ........................................................................... 4-28

4.7.1 Interrupt Priorities........................................ ... .. .... .... .... .... .... ...... .... .... .... .... .... .... .... ...4-29

4.8 Interrupt Processing....................................................................................................... 4-32

4.8.1 Enabling and Disabling Exceptions........................................................................... 4-33

4.8.2 Returning from an Interrupt Handler......................................................................... 4-33

4.9 Proc ess Switch i n g..... ........ ........................ ......................... ................ ........................ .... 4-34

e200z3 Power Architecture Core Reference Manual, Rev. 2

Freescale Semiconductor vii

Page 8

Contents

Paragraph

Number Title

Page

Number

Chapter 5

Memory Management Unit

5.1 Overview..........................................................................................................................5-1

5.1.1 MMU Features............................................................................................................. 5-1

5.1.2 TLB Entr y Ma i n t e n an c e Features Summary ... ........................ ........................ ............ 5-1

5.2 Effective-to-Real Address Translation............................................................................. 5-2

5.2.1 Effectiv e A d d resses ...... ........................ ................. ........................ ................ .............. 5-4

5.2.2 Address Spaces............................................................................................................5-4

5.2.3 Virtual Addresses and Proce ss ID. ................ ......................... ........................ .............. 5- 4

5.2.4 Translation Flow ..........................................................................................................5-5

5.2.5 Permissions..................................................................................................................5-6

5.3 Translation Lookaside Buffer ..........................................................................................5-7

5.3.1 IPROT Inv a l i d a t i o n Pr o t e ction in TLB1 ......................... ........................ .................... 5-8

5.3.2 Replac e m e n t Alg o r ithm for TLB1.... ........ ......................... ........................ ................ .. 5-8

5.3.3 The G Bit (of W IMGE) ............................ ......................... ................ ........................ .. 5-9

5.3.4 TLB Entry Field Summary.......................................................................................... 5-9

5.4 Software Interface and TLB Instructions................................. ...... .... .... .... ...... .... .... ...... 5-10

5.5 TLB O p erations .... ................ ........................ ......................... ........................ ................ 5-11

5.5.1 Translation Reload ..................................................................................................... 5-11

5.5.2 Reading t h e TLB... ................ ........................ ......................... ........................ ............ 5-12

5.5.3 Writing the TLB.................. ........................ ......................... ................ ...................... 5-12

5.5.4 Searching the TLB..................................................................................................... 5-12

5.5.5 TLB Coher e n cy Co n trol . ........................ ......................... ........................ .................. 5-12

5.5.6 TLB Miss Ex c ep tion Upda t e ............................. ........................ ................ ................ 5-12

5.5.7 TLB Load o n Rese t....................... ......................... ........................ ................ ............ 5-13

5.6 MMU Configuration and Control Registers.................................................................. 5-13

5.6.1 MMU Configuration Register (MMUCFG) .............................................................. 5-13

5.6.2 TLB0 and TLB1 Configuration Registers ................................................................. 5-14

5.6.3 Data Exception Add ress Regist er (DEAR)...................... ........................ ................ .. 5-14

5.6.4 MMU Control and Sta t u s Register 0 (MMUCSR0). .................... .................... .........5-14

5.6.5 MMU Assist Registers (MAS) .................................................................................. 5-14

5.6.5.1 MAS Regist e r s Summary ....................... ......................... ........................ .............. 5- 1 4

5.6.5.2 MAS Regist e r U p d a t es ............................. ......................... ........................ ............ 5-14

5.7 Effect of Hardware Debug on MMU Operation............................................................ 5-15

Chapter 6

Instruction Pipeline and Execution Timing

6.1 Overview of Operation .................................................................................................... 6-1

6.1.1 Contro l Un i t .......................... ................ ......................... ........................ ......................6-2

e200z3 Power Architecture Core Reference Manual, Rev. 2

viii Freescale Semiconductor

Page 9

Contents

Paragraph

Number Title

Page

Number

6.1.2 Instruction Unit....... ........ ........................ ................. ........................ ........................ ....6-2

6.1.3 Branch U n i t....................... ........................ ......................... ................ ..........................6-3

6.1.4 Instruction Decod e Un it ................ ......................... ................ ........................ .............. 6- 3

6.1.5 Except ion H a n d l i n g .... ........................ ......................... ........................ ........................ 6-3

6.2 Execution Uni t s........... ........................ ......................... ........................ ........................ .... 6-3

6.2.1 Intege r Ex ecution Unit ........ ........................ ......................... ........................ ................ 6-3

6.2.2 Load/Store Unit............................................................................................................6-3

6.3 Ins t ruction Pipeline....... ........................ ......................... ........................ ................ .......... 6-4

6.3.1 Descrip t i o n of Pi p el ine Stages........ ......................... ........................ ................ ............ 6-4

6.3.2 Instruction Buffers ........ ........................ ......................... ........................ ................ ...... 6-5

6.3.3 Single-Cycle Instruction Pipeline Operation............................................................... 6-7

6.3.4 Basic Lo a d and Store Instru ction Pipeli n e Ope ration..................................... .. .......... .6-8

6.3.5 Change-of-Flow Instruction Pipeline Operation.......................................................... 6-9

6.3.6 Basic Multi-Cycle Instruction Pipeline Operation..................................................... 6-10

6.3.7 Additional Examples of Instruction Pipeline Operation for Load and Store.............6-10

6.3.8 Move to/from SPR Instruction Pipeline Operation.................................................... 6-11

6.4 Stalls Caused by Accessing SPRs.................................................................................. 6-13

6.5 Ins t ru ction Serialization ............................ ................. ........................ ................ ............ 6-13

6.6 Interrupt Recognition and Exception Processing...........................................................6-14

6.7 Ins t ruction Timings............................. ......................... ........................ ................ .......... 6-16

6.7.1 SPE and Embedded Floating-Point Instruction Timing.............................................6-21

6.7.1.1 SPE Integer Simple Instructions Timing ............................................................... 6-22

6.7.1.2 SPE Load and Store Instruction Timing......................... ...... ........ ........ ...... ........ ...6-23

6.7.1.3 SPE Complex Integer Instruction Timing ................................ ...... ...... ...... ...... .... .6-24

6.7.1.4 Vector Floating-Point APU Instruction Timing.....................................................6-27

6.7.1.5 SPE Scalar Floating-Point Instruction Timing ............................................. ...... ...6-28

6.8 Operand Placement on Performance.............................................................................. 6-29

Chapter 7

External Core Complex Interfaces

7.1 Overview..........................................................................................................................7-1

7.2 Signal Index.....................................................................................................................7-2

7.3 Signal Descriptions ..........................................................................................................7-7

7.3.1 Processo r State Signa l s ......... ........................ ......................... ........................ ............ 7-20

7.3.2 JT AG ID Signals........................................................................................................ 7-29

7.4 Internal Signals ......... ........................ ......................... ........................ ........................ ....7-30

7.5 Timing Di a g rams .. ........................ ................ ......................... ........................ ................ 7-30

7.5.1 Proce sso r In structio n / D a t a Trans fers.. ........ ......................... ................ ................ ...... 7- 3 0

7.5.1.1 Basic Rea d Trans fe r Cy c l e s...................... ................................. ........................ .... 7-32

7.5.1.2 Read Transfe r with Wait State...... ................. ........................ ........................ ........ 7 -33

e200z3 Power Architecture Core Reference Manual, Rev. 2

Freescale Semiconductor ix

Page 10

Contents

Paragraph

Number Title

Page

Number

7.5.1.3 Basic Write Transfer Cycles ................. ......................... ................................ ........ 7 -34

7.5.1.4 Write Transfer with Wait States............................................................................. 7-35

7.5.1.5 Read and Write Transfers ............. ......................... ........................ ........................ 7-36

7.5.1.6 Misaligned Accesses.............................................................................................. 7-39

7.5.2 Burst Accesses.............................. .. .... .. .... .. ....... .. .... .. .... .. .... .. .... .. .... .. .... .. .... .. .... .. .... .. 7-43

7.5.3 Address Retraction..................................................................................................... 7-49

7.5.3.1 Error Terminatio n O p eration .... ................ ................. ........................ ................ .... 7-51

7.5.4 Address Retraction..................................................................................................... 7-55

7.5.5 Power Ma n a g em e n t .... ........................ ......................... ........................ ...................... 7-57

7.5.6 Interrupt Interface ...................................................................................................... 7-58

Chapter 8

Power Management

8.1 Overview..........................................................................................................................8-1

8.1.1 Power Ma n a g em e n t Si g n als.................... ......................... ........................ ................ .... 8-2

8.1.2 Power Ma n a g em e n t Co n trol Bits...... ................. ........................ ................ .................. 8-3

8.1.3 Software Considerations for Power Management.......................................................8-3

8.1.4 Debug Considerations for Power Management...........................................................8-3

Chapter 9

Debug Support

9.1 Introduction...................................................................................................................... 9-2

9.2 Overview..........................................................................................................................9-2

9.2.1 S oftware Debug Facilities. .... .............. ............................. .............. .............. .............. .. 9- 2

9.2.1.1 PowerPC Book E Compatibility.............................................................................. 9-3

9.2.2 Additional Debug Facilities.........................................................................................9-3

9.2.3 Hardware Debug Facilities............................. ........ ............ ............ .......... ............ .......9-3

9.2.4 S haring Debug Resources by Software/Hardware in e200z335.............. ........ .......... .. 9- 4

9.2.4.1 Simultaneous Hardware and Software Debug Event Handing in e200z335........... 9-4

9.3 Debug Registers...............................................................................................................9-5

9.4 Software Debug Events and Exceptions.................................................... .......... ............ 9-6

9.5 External Debug Support................................................................................................. 9-11

9.5.1 OnCE Introduction.....................................................................................................9-12

9.5.2 JT AG/OnCE Signals.................................................................................................. 9-15

9.5.3 OnCE Internal Interface Signals................................................................................ 9-16

9.5.3.1 CPU Address and Attributes.................................................................................. 9-16

9.5.3.2 CPU Data............................................................................................................... 9-16

9.5.4 OnCE Interface Signals ............................................................................................. 9-16

9.5.5 OnCE Controller and Serial Interface........................................................................ 9-18

e200z3 Power Architecture Core Reference Manual, Rev. 2

x Freescale Semiconductor

Page 11

Contents

Paragraph

Number Title

Page

Number

9.5.5.1 OnCE Status Register (OSR)................................................................................. 9-19

9.5.5.2 OnCE Command Register (OCMD)...................................................................... 9-19

9.5.5.3 OnCE Control Register (OCR).............................................................................. 9-22

9.5.6 Acces s to Debug Resources....................................................................................... 9- 23

9.5.7 Methods for Entering Debug Mode........................................................................... 9- 25

9.5.8 CPU Status and Co n t rol Scan Chain Re g i st er (CPUSC R) ...... ........................ .......... 9-26

9.5.8.1 Instruction Regis ter (IR)......... ................ ................................. ........................ ...... 9- 2 7

9.5.8.2 Contro l State Register (CTL)........ ......................... ........................ ........................ 9-27

9.5.8.3 Program Counter Register (PC).... ............................. .............. .............. .............. .. 9- 30

9.5.8.4 Write-Back Bus Registe r (WBBR (lower) and WBBR (upper)) (should we consider

making this shorter i.e. WBBRL and WBBRU) ...............................................9-30

9.5.8.5 Machine State Register (MSR)........................ ........................ ........................ ...... 9- 3 1

9.5.9 Instruction Addr e ss FIFO Buffer ( PC FI FO )......................... ........................ ............ 9-31

9.5.10 Reserved Registers..................................................................................................... 9-33

9.6 Watchpoint Support .......................................................................................................9-33

9.7 MMU and Ca che Operati o n d u ri n g D e b u g..... ................. ................................ .............. 9- 3 4

9.8 Cache Array Access During Debug............................................................................... 9-34

9.9 Enabling, Using, and Exiting External Debug Mode: Example.................................... 9-34

Chapter 10

Nexus3/Nexus2+ Module

10.1 Introduction.................................................................................................................... 10-2

10.1.1 General Description................................................................................................... 10-2

10.1.2 T erms and Definitions................................................................................................ 10-2

10.1.3 Feature List ................................................................................................................10-3

10.2 Enablin g N ex u s3 O p e r a t i o n................................. ........................ ................ .................. 10-6

10.3 TCODEs Supported.......................................................................................................10-7

10.4 Nexus3/Nexus2+ Programmer’ s Model ..................................................................... 10-11

10.4.1 Client Select Control Register (CSC)...................................................................... 10-12

10.4.2 Port Configuratio n Re g i st e r (PCR)............................ ................................ .............. 10 - 1 3

10.4.3 Development Control Register 1, 2 (DC1, DC2).....................................................10-14

10.4.4 Development Status Register (DS) .......................................................................... 10-16

10.4.5 Read/Write Access Control/Status Register (RW CS)........................ .... .... .... .... .... .. 10- 16

10.4.6 Read/Write Access Data Register (RWD)..................................... .... .... .. .... .... .. .... .. 10-18

10.4.7 Read/Write Access Address Register (RWA).................... .... .... .... .. .... .... .... .... .. .... .. 10- 20

10.4.8 Watchpoint Trigger Register (WT).......................................................................... 10-20

10.4.9 Data Trace Control Register (DTC)......................................................................... 10-21

10.4.10 Data Trace Start Address 1 and 2 Registers (DTSA1 and DTSA2) ........................10-23

10.4.11 Data Trace End Address Registers 1 and 2 (DTEA1 and DTEA2).........................10-23

10.5 Nexus3/Nexus2+ Register Access Through JTAG/OnCE..... .......... ........ .......... ........ .. 10-24

e200z3 Power Architecture Core Reference Manual, Rev. 2

Freescale Semiconductor xi

Page 12

Contents

Paragraph

Number Title

Page

Number

10.6 Ownersh i p Trace ........................... ......................... ................ ........................ .............. 10-24

10.6.1 Overview.................................................................................................................. 10-24

10.6.2 Ownership Trace Messaging (OTM)....................................................................... 10-25

10.6.3 OTM Error Messages............................................................................................... 10-25

10.6.4 OTM Flow ............................................................................................................... 10-26

10.7 Program Trace.............................................................................................................. 10-27

10.7.1 Branch Trace Messaging (BTM) ............................................................................. 10-27

10.7.1.1 e200z6e200z3 I ndirect Branch Message Instructions (Book E).......................... 10-27

10.7.1.2 e200z6e200z3 Direct Branch Message Instructions (Book E)............................ 10-27

10.7.1.3 BTM Using Branch History Messages................................................................ 10-28

10.7.1.4 BTM Using Traditional Program Trace Messages.............................................. 10-28

10.7.2 BTM Messa g e Formats............. ......................... ................ ........................ .............. 10 - 2 8

10.7.2 .1 Indirec t Branch Messa g es (History ) .................. ........................ ........................ .. 10-29

10.7.2 .2 Indirec t Branch Messa g es (Traditional ) ........ ................ ................ ...................... 10 -29

10.7.2 .3 Direct Bran c h Messages (Tradi tional)......... ........................ ........................ ........ 1 0 -29

10.7.2.4 Resource Full Messages ...................................................................................... 10-29

10.7.2.5 Debug Status Messages ....................................................................................... 10- 30

10.7.2.6 Program Correlation Messages............................................................................10-30

10.7.2 .7 BTM Overf low Error Me ssages ............. ......................... ................ .................... 10- 3 1

10.7.2.8 Program Trace Synchronization Messages..........................................................10-32

10.7.3 BTM Operation..... ................ ........................ ......................... ................ .................. 10-34

10.7.3 .1 Enablin g P ro g ram Trace.............................. ........................ ........................ ........ 1 0 -34

10.7.3 .2 Relativ e A d d r e ssing.................... ......................... ................ ........................ ........ 1 0 -34

10.7.3 .3 Execut io n Mo d e Indicati o n ............... ................. ........................ ........................ .. 10-35

10.7.3.4 Branch/Predicate Instruction History (HIST)...................................................... 10-35

10.7.3.5 Sequential Instruction Count (I-CNT)................................................................. 10-35

10.7.3.6 Program Trace Queueing ..................................................................................... 10-36

10.7.4 Program Trace Timing Diagrams (2 MDO/1 MSEO Configuration)............ ...... .... 10-36

10.8 Data Trace...................................................................................................................10-37

10.8.1 Data Trace Messaging (DTM) ................................................................................. 10-37

10.8.2 DTM Message Formats ........................................................................................... 10-38

10.8.2 .1 Data Write Messages .. ................ ................................. ........................ ................ 10-38

10.8.2 .2 Data Read Me ssages....... ................ ................................. ........................ ............ 10-3 8

10.8.2.3 DTM Overflow Error Messages.......................................................................... 10-39

10.8.2.4 Data Trace Synchronization Messages................................................................ 10-39

10.8.3 DTM Operation........................................................................................................ 10-41

10.8.3.1 DTM Queueing.................................................................................................... 10-41

10.8.3 .2 Relativ e A d d r e ssing.................... ......................... ................ ........................ ........ 1 0 -41

10.8.3.3 Data Trace Windowing............................. ....................... .......... ............ ............ .. 10- 41

10.8.3.4 Data Access/Instruction Access Data Tracing..................................................... 10-41

10.8.3.5 e200z6e200z3 Bus Cycle Special Cases.............................................................. 10-41

e200z3 Power Architecture Core Reference Manual, Rev. 2

xii Freescale Semiconductor

Page 13

Contents

Paragraph

Number Title

Page

Number

10.8.4 Data Trace Timing Dia g rams (8 MDO /2 MS EO Configuration) ............................ 10-42

10.9 Watchpoint Support ..................................................................................................... 10-43

10.9.1 Overview.................................................................................................................. 10-43

10.9.2 Watchpoint Messaging............................................................................................. 10-43

10.9.3 Watchpoint Error Message....................................................................................... 10-44

10.9.4 Watchpoint Timing Diagram (2 MDO/1 MSEO Configuration) . ............................ 10-45

10.10 Nexus3/Nexus2+ Read/Write Access to Memory-Mapped Resources ...................... 10-45

10.10.1 Single Write Access................................................................................................. 10-46

10.10. 2 Block Write Access (Non-Burst Mode )........... ........................ ........................ ........ 1 0 -46

10.10. 3 Block Write Access (Burst Mo d e )........ ........ ......................... ........................ .......... 10-47

10.10.4 Single Read Access.................................................................................................. 10-47

10.10.5 Block Read Access (Non-Burst Mode) ....................... .... ...... .... .... ...... .... .... ...... .... .. 10- 48

10.10.6 Block Read Access (Burst Mode). .... .... ...... ......... ...... .... ...... .... ...... .... ...... .... ...... .... .. 10- 48

10.10. 7 Error Ha n d l i n g .......................... ................ ......................... ................ ...................... 10-49

10.10. 7 .1 AHB Read/Writ e Error..... ................ ................. ........................ ................ .......... 10-49

10.10.7.2 Access Termination .......... ...... ...... ...... .... ........... ...... ...... ...... ...... .... ...... ...... ...... .... 10-49

10.10.7.3 Read/Write Access Error Message ......... ......... .... ...... .... .... .... .... .... ...... .... .... .... .... 10-50

10.11 N ex u s 3 / N exus2+ Pin In t erface ... ........ ................. ........................ ................ ................ 10-50

10.11.1 Pins Implemented .................................................................................................... 10-50

10.11.2 Pin Prot o co l................... ........................ ......................... ................ ........................ .. 10-52

10.12 Rules for Output Messages .......................................................................................... 10-55

10.13 Auxiliary Port Arbitration............................................................................................10-55

10.14 Examples...................................................................................................................... 10-55

10.15 El e ctrical Characteristics ...... ................ ......................... ........................ ...................... 10 - 58

10.16 IEEE 1149.1 (JTAG) RD/WR Sequences......... ......................... ............ ............ .......... 10-58

10.16 .1 JTAG Seq uen c e for Accessing In ternal Nexus R eg isters....... .. .......... .....................10-58

10.16 .2 JTAG Seq uen c e for Read Access of Memory-Ma p p e d Re sources ........ .................10-59

10.16.3 JTAG Sequence for Write Access of Memory-Mapped Resources......................... 10-59

e200z3 Power Architecture Core Reference Manual, Rev. 2

Freescale Semiconductor xiii

Page 14

Contents

Paragraph

Number Title

Page

Number

e200z3 Power Architecture Core Reference Manual, Rev. 2

xiv Freescale Semiconductor

Page 15

Figures

Figure

Number Title

Page

Number

1-1 e200z3 Block Diagram.................................................................................. .............. .......... 1-34

1-2 e200z335 Block Diagram.................................................................................................. .... 1-35

1-3 e200z3 Programmer’s Model. .... .................... ....................................... .................... ............ 1- 39

2-1 e200z3 Programmer’s Model. .... .................... ....................................... .................... .............. 2-2

2-2 Mac h ine State Regis ter (MSR) ...... ................ ......................... ........................ ........................ 2-6

2-3 Proc essor ID Regi ster (PIR)......................... ................. ........................ ................ .................. 2-8

2-4 Proc essor Version Re g i ster (PVR ) ......................... ......................... ........................ ................ 2-9

2-5 System Version Reg i ster (SVR )............................... ......................... ................ ...................... 2-9

2-6 Integ er Except io n Reg i ster (XER ) ................. ......................... ................ ........................ ...... 2- 1 0

2-7 Condition Register (CR) ....................................................................................................... 2-11

2-8 Count Register (CTR)........................................................................................................... 2-14

2-9 Link Reg ister (LR) ... ........ ................................ ......................... ........................ .. ........ .......... 2-15

2-10 Signal Processing and Embedded Floating-Point Status and Control

Regist e r (S P EFSCR) ... ........ ........................ ................................. ........................ ............ 2-15

2-11 Sa v e / Re store Register 0 (SRR0 ) ............ ......................... ........................ ........................ ...... 2-19

2-12 Sa v e / Re store Register 1 (SRR1 ) ............ ......................... ........................ ........................ ...... 2- 19

2-13 Critical Save/Restore Register 0 (CSRR0) ........................................................................... 2-20

2-14 Critical Save/Restore Register 1 (CSRR1) ........................................................................... 2-20

2-15 Data Exceptio n A d d ress Regist er (DEAR)......................... ........................ ................ .......... 2-20

2-16 Interrupt Vector Prefix Register (IVPR) ............................................................................... 2-21

2-17 Interrupt Vector Offset Registers (IVOR)............................................................................. 2-21

2-18 Exception Syndrome Register (ESR).................................................................................... 2-23

2-19 Debug Save/Restore Register 0 (DSRR0) ............................................................................ 2-25

2-20 Debug Save/Restore Register 1 (DSRR1) ............................................................................ 2-25

2-21 Machine Check Syndrome Register (MCSR).......................................................................2-26

2-22 So ftware-Use SPRs (SPRG0 – S PRG7 and USPRG0)..... ........................ ........................ ...... 2-27

2-23 Relationship of Timer Facilities to the Time Base................................................................ 2-27

2-24 Timer Co n t ro l Re g i ster (TCR) ................... ......................... ........................ ........................ .. 2-28

2-25 Timer Status Register (TSR).................................................................................................2-30

2-26 Time Base Upper/Lower Registers (TBU/TBL)................................................................... 2-31

2-27 Decrementer Register (DEC) ................................................................................................ 2-32

2-28 Decrementer Auto-Reload Register (DECAR)..................................................................... 2-32

2-29 Instructio n Ad d ress Compar e Re g i sters (IAC1 – IAC4) .......... ........................ ................ ...... 2- 3 3

2-30 Dat a A d d ress Compare Re g i st e rs (DAC1–DA C2)......................... ................................ ...... 2- 3 4

2-31 Dat a Valu e Co m p are Registers (DVC1–DV C2).. ......... ................................ ........................ 2-34

2-32 DBCNT Register.............. ........................ ......................... ........................ ............................ 2-35

2-33 DBCR0 Register ................................................................................................................... 2-36

2-34 Debug Control Register 1 (DBCR1)..................................................................................... 2- 38

e200z3 Power Architecture Core Reference Manual, Rev. 2

Freescale Semiconductor 1

Page 16

Figures

Figure

Number Title

Page

Number

2-35 DBCR2 Register ................................................................................................................... 2-40

2-36 DBCR3 Register ................................................................................................................... 2-43

2-37 DBSR Register......................................................................................................................2-47

2-38 Hardware Implementation-Dependent Register 0 (HID0).................................................... 2-49

2-39 Hardware Implementation-Dependent Register 1 (HID1).................................................... 2-51

2-40 Br an c h Un it Control and Sta t u s Re g i st er (BUCSR) ....... ................................ ...................... 2- 5 2

2-41 MMU Control and Status Register 0 (MMUCSR0) ............................................................. 2-53

2-42 MMU Configuration Register 1 (MMUCFG) ...................................................................... 2-53

2-43 TL B Co n f iguration Re g i st e r 0 (TLB0CFG) .. ................. ................................ ...................... 2- 5 4

2-44 TL B Co n f iguration Re g i st e r 1 (TLB1CFG) .. ................. ................................ ...................... 2- 5 5

2-45 MAS Re g i st e r 0 (MA S 0 ) Format......................... ................................. ........................ ........ 2 -56

2-46 MM U As si st Re g i ster 1 (MAS1 ) ....... ......................................... ........................ .................. 2-56

2-47 MM U As si st Re g i ster 2 (MAS2) ............. ................................. ................................ ............ 2-57

2-48 MM U As si st Re g i ster 3 (MAS3) ............. ................................. ................................ ............ 2-58

2-49 MM U As si st Re g i ster 4 (MAS4) ............. ................................. ................................ ............ 2-59

2-50 MM U As si st Re g i ster 6 (MAS6) )............................... ................................ .......................... 2-60

2-51 Process ID Register (PID0)................................................................................................... 2-60

2-52 Con t e x t Co n t ro l Re g i ster (CTXCR) ...... ........ ......................... ........................ ...................... 2-61

2-53 Pa rallel Sig n ature Contro l Register (P SC R) ........ ......................... ........................ ................ 2-68

2-54 Parallel Signature Status Register (PSSR)............................................................................2-69

2-55 Pa rallel Sig n ature High Reg ister (PSH R) ......................... ........................ ........................ .... 2-70

2-56 Pa rallel Sig n ature Low Reg is t e r (PSLR) ......... ......................... ........................ .................... 2-7 0

2-57 Parallel Signature Counter Register (PSCTR)......................................................................2-70

2-58 Pa rallel Sig n ature Update H i g h Re g i st e r (PSUHR).... ........................ ........................ .......... 2-71

2-59 Pa rallel Sig n ature Update Lo w Reg ister (PSU LR)..... ........................ ................ .................. 2-71

4-1 Exception Syndrome Register (ESR)......................................................................................4-4

4-2 Mac h ine State Regis ter (MSR) ...... ................ ......................... ........................ ........................ 4-5

4-3 Machine Check Syndrome register (MCSR) .......................................................................... 4-7

4-4 Interrupt Vector Prefix Register (IVPR) ................................................................................. 4-8

4-5 Interrupt Vector Offset Registers (IVOR)............................................................................... 4-9

5-1 Effec t i v e - to-Real Add r e ss Translation F low................... ........................ ........................ ........ 5-3

5-2 Virtual Address and TLB-Entry Compare Process................................................................. 5-5

5-3 Granting of Access Permission............................................................................................... 5-7

5-4 e200z3 TLB1 Organization.....................................................................................................5-8

5-5 Victim Selection...................................................... ... .. ...... .... ...... .... ...... ...... .... ...... ...... ........... 5-9

5-6 MMU Assist Registers Summary ......................................................................................... 5-14

6-1 e200z3 Block Diagram.................................................................................. .............. ............ 6-2

6-2 Pi p el ine Diagram..................... .............................. ............................. .................... .................6-4

6-3 Ins t ru ction Buffers ....... ................ ........................ ......................... ........................ ..................6-6

6-4 Bran c h Target Buffer.... ................ ........................ ................. ........................ ................ .......... 6-7

6-5 Basic Pipeline Flow, Single-Cycle Instructions...................................................................... 6-8

e200z3 Power Architecture Core Reference Manual, Rev. 2

2 Freescale Semiconductor

Page 17

Figures

Figure

Number Title

Page

Number

6-6 A Load Fo l l o w ed b y a De p en d ent Add Ins tr u c t i o n ........................ ........................ ................ 6-8

6-7 Back-to-Back Lo ad Instru c t i o n s .... ........ ................ ......................... ........................ ................ 6-9

6-8 A Load Fo l l o w ed b y a Dep e n d ent Store Inst ruction............. ........................ ........................ .. 6-9

6-9 Basic Pipeline Flow, Branch Instructions ............................................................................. 6-10

6-10 Basic Pipeline Flow, Branch Speculation ............................................................................. 6-10

6-11 Basic Pipeline Flow, Multi-Cycle Instructions ..................................................................... 6-10

6-12 Pipelined Load/Store Instructions......................................................................................... 6-11

6-13 Pipelined Load/Store Instructions with Wait-State ............................................................... 6-11

6-14 mtspr, mfspr Instruction Execution—(1)..............................................................................6-12

6-15 mtmysr, wrtee, wrteei Instruction Execution...................................................................... 6-12

6-16 DCR, MMU mtspr, mfspr, and MMU Manageme n t In structio n Ex ecution ................. ...... 6- 1 3

6-17 I n t e rru p t R ec o g n i t ion and Handle r In struction Exe c u t i o n................... ................................. 6-14

6-18 Interrupt Recognition and Handler Instruction Execution—Load/Store in Progress ........... 6-15

6-19 Interrupt Recognition and Handler Instruction Execution—Multi-Cycle

Instruction Abo r t ..... ................ ........................ ................. ........................ ................ ........ 6-16

7-1 Core Signal Groups................................................................................................................. 7-3

7-2 Exam p l e Ex ternal JTAG Register D e si g n.......... ......... ........................ ........................ .......... 7-28

7-3 Basic Read Transfer—Single-Cycle Reads, Full Pipelining................................................. 7-32

7-4 Read with Wait-State, Single-Cycle Reads, Full Pipelining................................................. 7-33

7-5 Ba si c Write Transfer s— Single-Cy c l e Writes, Fu l l Pi p e l i n i n g. .................... .................... ..... 7-34

7-6 Write with Wait-state, Si n g le-Cycle Writes, Full Pi p e l i n i n g................... .............................7-35

7-7 Singl e-Cycle R ea d s, Single-Cy c l e Write, Full Pipe lin i n g .... ................................ ................ 7 -36

7-8 Single-Cycl e Rea d , Writ e, Re ad — Full Pipel i n i n g ........ .. ........ ........................ ...................... 7-37

7-9 Multiple-Cycle Reads with Wait-State, Single-Cyc le Writes, Full Pipelining ..................... 7-38

7-10 Multi-Cycle Read with Wait-State, Single-Cycle Write, Read with Wait-State, Single-Cycle

Write, Full Pip el ining.............. ................ ......................... ........................ ........................ 7-39

7-11 Misaligned Re ad , Re ad, Full Pipelining .... ................................. ................................ .......... 7-40

7-12 Misaligned Write, Write , Ful l Pipelini n g....... ................. ........................ ........................ ...... 7- 4 1

7-13 Misaligned Write, Single Cycle Read Transfer, Full Pipelining...........................................7-42

7-14 Burst Read Transfe r . ................................ ................................. .. ........ ........................ .......... 7-43

7-15 Burst Read wit h Wait-state Transf e r ........................ ......................... ........................ ............ 7-44

7-16 Burst Write Transfer................... ................................. ........................ ........................ .......... 7-45

7-17 Burst Write with Wa it - St a t e Transfer........... ................................. ........................ ................ 7-46

7-18 Burst Read Transfe rs................................................ ................................. ............................ 7-47

7-19 Burst Read with Wait-State Transfer, Retr a ct ion........................ ................................ .......... 7-48

7-20 Burst Write Transfers, S ing l e-Beat bur st ............. .. ......... ........................ .............................. 7-49

7-21 Read Transfer with Wait-State, Address Retraction ............................................................. 7-50

7-22 Burst Read with Wait-State Transfer, Retr a ct ion........................ ................................ .......... 7-51

7-23 Read and Write Transfers: Instruction Read with Error, Data Read, Write,

Full Pipelining..... ........ ........................ ......................... ........................ ........................ ....7-52

7-24 Data Read with Error, Data Write Retracted, Instruction Read, Full Pipelining .................. 7-53

e200z3 Power Architecture Core Reference Manual, Rev. 2

Freescale Semiconductor 3

Page 18

Figures

Figure

Number Title

Page

Number

7-25 Misaligned W rite wi th Error, Data Write Retracted, Burst Read

Substituted, Full Pipelining.............................................................................................. 7-54

7-26 Burst Read with Error Termination , Bu rst Write........ ................................ .......................... 7-55

7-27 Read Transfer with Wait-State, Address Retraction ............................................................. 7-56

7-28 Burst Read with Wait-State Transfer, Retr a ct ion........................ ................................ .......... 7-57

7-29 Wakeup Control Signal (p_wakeup) ..................................................................................... 7-57

7-30 Interrupt Interface Input Signals ...........................................................................................7-58

7-31 Interrupt Pending Operation..................................................................................................7-58

7-32 Interrupt Acknowledge Operation Case 1............................................................................. 7-59

7-33 Interrupt Acknowledge Operation Case 2............................................................................. 7-60

8-1 Pow e r Management Stat e D i a g ram................ ......................... ........................ ........................ 8-2

9-1 Core Debug Resources............................................................................................................ 9-3

9-2 OnCE TAP Controller and Registers .................................................................................... 9-11

9-3 OnCE Controller as an FSM ................................................................................................. 9-12

9-4 OnCE Controller and Serial Interface................................................................................... 9-16

9-5 OnCE Status Register (OSR) ................................................................................................ 9-17

9-6 OnCE Command Register (OCMD)..................................................................................... 9-18

9-7 OnCE Control Register.........................................................................................................9-20

9-8 CPU Scan Chain Register (CPUSCR) .................................................................................. 9-25

9-9 Cont rol State Register (CTL)............. ......................... ........................ ................ .................. 9-26

9-10 OnCE PC FIFO..................................................................................................................... 9-30

10-1 Nexus3 Functional Block Diagram....................................................................................... 10-4

10-2 Client Select Control Register............................................................................................. 10-10

10-3 Po rt Co n figuratio n Re g i st e r ..... ........................ ......................... ........................ .................. 10-11

10-4 Dev e l o p m e n t Co n t ro l Re g i ster 1 (DC1) ................................... ........................ .................. 10-12

10-5 Dev e l o p m e n t Co n t ro l Re g i ster 2 (DC2) ................................... ........................ .................. 10-13

10-6 Development Status Register (DS) ..................................................................................... 10-14

10-7 Read/Write Access Control/Status Register (RWCS)................. .... .... .... .... .... .... .... .... .... .... 10-15

10-8 Read/Write Access Data Register (RWD) ......... .. .... ..... .... .... .. .... .... .. .... .. .... .... .. .... .. .... .... .. .. 10-16