Page 1

DSP56364 24-Bit Digital Signal

Processor

Users Manual

Document Number: DSP56364UM

Rev. 2

08/2006

Page 2

How to Reach Us:

Home Page:

www.freescale.com

E-mail:

support@freescale.com

USA/Europe or Locations Not Listed:

Freescale Semiconductor

Technical Information Center, CH370

1300 N. Alma School Road

Chandler, Arizona 85224

+1-800-521-6274 or +1-480-768-2130

support@freescale.com

Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH

Technical Information Center

Schatzbogen 7

81829 Muenchen, Germany

+44 1296 380 456 (English)

+46 8 52200080 (English)

+49 89 92103 559 (German)

+33 1 69 35 48 48 (French)

support@freescale.com

Japan:

Freescale Semiconductor Japan Ltd.

Headquarters

ARCO Tower 15F

1-8-1, Shimo-Meguro, Meguro-ku,

Tokyo 153-0064, Japan

0120 191014 or +81 3 5437 9125

support.japan@freescale.com

Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd.

Technical Information Center

2 Dai King Street

Tai Po Industrial Estate

Tai Po, N.T., Hong Kong

+800 2666 8080

support.asia@freescale.com

For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center

P.O. Box 5405

Denver, Colorado 80217

1-800-521-6274 or 303-675-2140

Fax: 303-675-2150

LDCForFreescaleSemiconductor@hibbertgroup.com

Information in this document is provided solely to enable system and software implementers to use

Freescale Semiconductor products. There are no express or implied copyright licenses granted

hereunder to design or fabricate any integrated circuits or integrated circuits based on the information

in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products

herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the

suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any

liability arising out of the application or use of any product or circuit, and specifically disclaims any

and all liability, including without limitation consequential or incidental damages. “Typical” parameters

that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary

in different applications and actual performance may vary over time. All operating parameters,

including “Typicals”, must be validated for each customer application by customer’s technical experts.

Freescale Semiconductor does not convey any license under its patent rights nor the rights of others.

Freescale Semiconductor products are not designed, intended, or authorized for use as components

in systems intended for surgical implant into the body, or other applications intended to support or

sustain life, or for any other application in which the failure of the Freescale Semiconductor product

could create a situation where personal injury or death may occur. Should Buyer purchase or use

Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall

indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and

distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney

fees arising out of, directly or indirectly, any claim of personal injury or death associated with such

unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was

negligent regarding the design or manufacture of the part.

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other

product or service names are the property of their respective owners.

© Freescale Semiconductor, Inc. 2006. All rights reserved.

Page 3

Contents

Manual Conventions

1 Overview

1.1 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1

1.2 Features. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-2

1.3 Audio Processor Architecture. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-3

1.4 Core Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-4

1.5 DSP56300 Core Functional Blocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-4

1.5.1 Data ALU . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-4

1.5.1.1 Data ALU Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-5

1.5.1.2 Multiplier-Accumulator (MAC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-5

1.5.2 Address Generation Unit (AGU) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-5

1.5.3 Program Control Unit (PCU) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-6

1.5.4 Internal Buses . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-6

1.5.5 Direct Memory Access (DMA) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-7

1.5.6 PLL-based Clock Oscillator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-7

1.5.7 JTAG TAP and OnCE Module. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-8

1.6 Data and Program memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-8

1.6.1 Reserved Memory Spaces. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-8

1.6.2 Program ROM Area Reserved for Freescale Use. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-8

1.6.3 Bootstrap ROM. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-8

1.6.4 Dynamic Memory Configuration Switching . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-8

1.6.5 External Memory Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-9

1.7 Internal I/O Memory Map. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-9

1.8 Status Register (SR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-10

2 Signal/Connection Descriptions

2.1 Signal Groupings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-1

2.2 Power . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-3

2.3 Ground . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-3

2.4 Clock and PLL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-4

2.5 External Memory Expansion Port (Port A) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-4

2.5.1 External Address Bus . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-4

2.5.2 External Data Bus . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-5

2.5.3 External Bus Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-5

2.6 Interrupt and Mode Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-6

2.7 Serial Host Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-7

2.8 Enhanced Serial Audio Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-10

2.9 JTAG/OnCE Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-13

2.10 GPIO Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-14

BookTitle, Rev. #

Freescale Semiconductor iii

Page 4

3 Memory Configuration

3.1 Memory Spaces. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-1

3.1.1 Program Memory Space . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-1

3.1.1.1 Program RAM. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-1

3.1.1.2 Program ROM. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-1

3.1.1.3 Bootstrap ROM. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-2

3.1.1.4 Reserved Program Memory Locations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-2

3.1.2 Data Memory Spaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-2

3.1.2.1 X Data Memory Space . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-2

3.1.2.2 X Data RAM. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-3

3.1.2.3 Y Data Memory Space . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-3

3.1.2.4 Y Data RAM. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-3

3.2 Memory Space Configuration. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-3

3.3 Internal Memory Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-3

3.3.1 RAM Locations. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-4

3.3.2 ROM Locations. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-4

3.3.3 Dynamic Memory Configuration Switching . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-5

3.4 Memory Maps. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-6

3.5 External Memory Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-8

3.6 Internal I/O Memory Map. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-8

4 Core Configuration

4.1 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-1

4.2 Operating Mode Register (OMR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-1

4.2.1 Mode C (MC) - Bit 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-2

4.2.2 Address Attribute Priority Disable (APD) - Bit 14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-2

4.2.3 Address Tracing Enable (ATE) - Bit 15 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-2

4.3 Operating Modes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-3

4.4 Bootstrap Program . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-4

4.5 Interrupt Priority Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-4

4.6 DMA Request Sources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-7

4.7 PLL and Clock Generator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-7

4.7.1 PLL Multiplication Factor (MF0-MF11) - Bits 0-11 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-7

4.7.2 Crystal Range Bit (XTLR) - Bit 15 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-8

4.7.3 XTAL Disable Bit (XTLD) - Bit 16 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-8

4.7.4 Clock Output Disable Bit (COD) - Bit 19 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-8

4.7.5 PLL Pre-Divider Factor (PD0-PD3) - Bits 20-23. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-8

4.8 Device Identification (ID) Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-8

4.9 JTAG Identification (ID) Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-8

4.10 JTAG Boundary Scan Register (BSR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-9

BookTitle, Rev. #

iv Freescale Semiconductor

Page 5

5 General Purpose Input/Output Port (GPIO)

5.1 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-1

5.2 GPIO Programming Model. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-1

5.2.1 Port B Control Register (PCRB). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-2

5.2.1.1 PCRB Control Bits (PC[3:0]) - Bits 3-0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-2

5.2.1.2 PCRB Reserved Bits - Bits 23-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-2

5.2.1.3 PRRB Direction Bits (PDC[3:0]) - Bits 3-0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-3

5.2.1.4 PRRB Reserved Bits - Bits 23-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-3

5.2.2 Port B GPIO Data Register (PDRB). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-3

5.2.2.1 PDRB Data Bits (PD[3:0]) - Bits 3-0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-3

5.2.2.2 PDRB Reserved Bits - Bits 23-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-3

6 Enhanced Serial AUDIO Interface (ESAI)

6.1 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-1

6.2 ESAI Data and Control Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-3

6.2.1 Serial Transmit 0 Data Pin (SDO0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-3

6.2.2 Serial Transmit 1 Data Pin (SDO1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-3

6.2.3 Serial Transmit 2/Receive 3 Data Pin (SDO2/SDI3) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-3

6.2.4 Serial Transmit 3/Receive 2 Data Pin (SDO3/SDI2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-4

6.2.5 Serial Transmit 4/Receive 1 Data Pin (SDO4/SDI1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-4

6.2.6 Serial Transmit 5/Receive 0 Data Pin (SDO5/SDI0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-4

6.2.7 Receiver Serial Clock (SCKR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-4

6.2.8 Transmitter Serial Clock (SCKT) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-5

6.2.9 Frame Sync for Receiver (FSR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-6

6.2.10 Frame Sync for Transmitter (FST) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-7

6.2.11 High Frequency Clock for Transmitter (HCKT) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-7

6.2.12 High Frequency Clock for Receiver (HCKR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-7

6.3 ESAI Programming Model . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-7

6.3.1 ESAI Transmitter Clock Control Register (TCCR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-8

6.3.1.1 TCCR Transmit Prescale Modulus Select (TPM7–TPM0) - Bits 0–7 . . . . . . . . . . . . . . 6-8

6.3.1.2 TCCR Transmit Prescaler Range (TPSR) - Bit 8 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-9

6.3.1.3 TCCR Tx Frame Rate Divider Control (TDC4–TDC0) - Bits 9–13 . . . . . . . . . . . . . . 6-10

6.3.1.4 TCCR Tx High Frequency Clock Divider (TFP3-TFP0) - Bits 14–17 . . . . . . . . . . . . 6-11

6.3.1.5 TCCR Transmit Clock Polarity (TCKP) - Bit 18 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-12

6.3.1.6 TCCR Transmit Frame Sync Polarity (TFSP) - Bit 19. . . . . . . . . . . . . . . . . . . . . . . . . 6-12

6.3.1.7 TCCR Transmit High Frequency Clock Polarity (THCKP) - Bit 20 . . . . . . . . . . . . . . 6-12

6.3.1.8 TCCR Transmit Clock Source Direction (TCKD) - Bit 21 . . . . . . . . . . . . . . . . . . . . . 6-12

6.3.1.9 TCCR Transmit Frame Sync Signal Direction (TFSD) - Bit 22 . . . . . . . . . . . . . . . . . 6-12

6.3.1.10 TCCR Transmit High Frequency Clock Direction (THCKD) - Bit 23 . . . . . . . . . . . . 6-12

6.3.2 ESAI Transmit Control Register (TCR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-13

6.3.2.1 TCR ESAI Transmit 0 Enable (TE0) - Bit 0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-13

6.3.2.2 TCR ESAI Transmit 1 Enable (TE1) - Bit 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-13

6.3.2.3 TCR ESAI Transmit 2 Enable (TE2) - Bit 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-14

BookTitle, Rev. #

Freescale Semiconductor v

Page 6

6.3.2.4 TCR ESAI Transmit 3 Enable (TE3) - Bit 3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-14

6.3.2.5 TCR ESAI Transmit 4 Enable (TE4) - Bit 4 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-14

6.3.2.6 TCR ESAI Transmit 5 Enable (TE5) - Bit 5 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-15

6.3.2.7 TCR Transmit Shift Direction (TSHFD) - Bit 6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-15

6.3.2.8 TCR Transmit Word Alignment Control (TWA) - Bit 7 . . . . . . . . . . . . . . . . . . . . . . . 6-15

6.3.2.9 TCR Transmit Network Mode Control (TMOD1-TMOD0) - Bits 8-9 . . . . . . . . . . . . 6-16

6.3.2.10 TCR Tx Slot and Word Length Select (TSWS4-TSWS0) - Bits 10-14 . . . . . . . . . . . . 6-18

6.3.2.11 TCR Transmit Frame Sync Length (TFSL) - Bit 15 . . . . . . . . . . . . . . . . . . . . . . . . . . 6-19

6.3.2.12 TCR Transmit Frame Sync Relative Timing (TFSR) - Bit 16 . . . . . . . . . . . . . . . . . . . 6-21

6.3.2.13 TCR Transmit Zero Padding Control (PADC) - Bit 17 . . . . . . . . . . . . . . . . . . . . . . . . 6-21

6.3.2.14 TCR Reserved Bit - Bits 18 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-21

6.3.2.15 TCR Transmit Section Personal Reset (TPR) - Bit 19 . . . . . . . . . . . . . . . . . . . . . . . . . 6-21

6.3.2.16 TCR Transmit Exception Interrupt Enable (TEIE) - Bit 20 . . . . . . . . . . . . . . . . . . . . . 6-21

6.3.2.17 TCR Transmit Even Slot Data Interrupt Enable (TEDIE) - Bit 21 . . . . . . . . . . . . . . . 6-22

6.3.2.18 TCR Transmit Interrupt Enable (TIE) - Bit 22 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-22

6.3.2.19 TCR Transmit Last Slot Interrupt Enable (TLIE) - Bit 23 . . . . . . . . . . . . . . . . . . . . . . 6-22

6.3.3 ESAI Receive Clock Control Register (RCCR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-22

6.3.3.1 RCCR Receiver Prescale Modulus Select (RPM7–RPM0) - Bits 7–0. . . . . . . . . . . . . 6-23

6.3.3.2 RCCR Receiver Prescaler Range (RPSR) - Bit 8 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-23

6.3.3.3 RCCR Rx Frame Rate Divider Control (RDC4–RDC0) - Bits 9–13 . . . . . . . . . . . . . . 6-23

6.3.3.4 RCCR Rx High Frequency Clock Divider (RFP3-RFP0) - Bits 14-17 . . . . . . . . . . . . 6-24

6.3.3.5 RCCR Receiver Clock Polarity (RCKP) - Bit 18 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-24

6.3.3.6 RCCR Receiver Frame Sync Polarity (RFSP) - Bit 19 . . . . . . . . . . . . . . . . . . . . . . . . 6-24

6.3.3.7 RCCR Receiver High Frequency Clock Polarity (RHCKP) - Bit 20 . . . . . . . . . . . . . . 6-24

6.3.3.8 RCCR Receiver Clock Source Direction (RCKD) - Bit 21 . . . . . . . . . . . . . . . . . . . . . 6-25

6.3.3.9 RCCR Receiver Frame Sync Signal Direction (RFSD) - Bit 22 . . . . . . . . . . . . . . . . . 6-25

6.3.3.10 RCCR Receiver High Frequency Clock Direction (RHCKD) - Bit 23 . . . . . . . . . . . . 6-26

6.3.4 ESAI Receive Control Register (RCR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-26

6.3.4.1 RCR ESAI Receiver 0 Enable (RE0) - Bit 0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-27

6.3.4.2 RCR ESAI Receiver 1 Enable (RE1) - Bit 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-27

6.3.4.3 RCR ESAI Receiver 2 Enable (RE2) - Bit 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-27

6.3.4.4 RCR ESAI Receiver 3 Enable (RE3) - Bit 3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-28

6.3.4.5 RCR Reserved Bits - Bits 4-5, 17-18 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-28

6.3.4.6 RCR Receiver Shift Direction (RSHFD) - Bit 6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-28

6.3.4.7 RCR Receiver Word Alignment Control (RWA) - Bit 7 . . . . . . . . . . . . . . . . . . . . . . . 6-28

6.3.4.8 RCR Receiver Network Mode Control (RMOD1-RMOD0) - Bits 8-9 . . . . . . . . . . . . 6-28

6.3.4.9 RCR Receiver Slot and Word Select (RSWS4-RSWS0) - Bits 10-14 . . . . . . . . . . . . . 6-29

6.3.4.10 RCR Receiver Frame Sync Length (RFSL) - Bit 15 . . . . . . . . . . . . . . . . . . . . . . . . . . 6-30

6.3.4.11 RCR Receiver Frame Sync Relative Timing (RFSR) - Bit 16 . . . . . . . . . . . . . . . . . . . 6-30

6.3.4.12 RCR Receiver Section Personal Reset (RPR) - Bit 19 . . . . . . . . . . . . . . . . . . . . . . . . . 6-31

6.3.4.13 RCR Receive Exception Interrupt Enable (REIE) - Bit 20 . . . . . . . . . . . . . . . . . . . . . 6-31

6.3.4.14 RCR Receive Even Slot Data Interrupt Enable (REDIE) - Bit 21 . . . . . . . . . . . . . . . . 6-31

6.3.4.15 RCR Receive Interrupt Enable (RIE) - Bit 22 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-31

6.3.4.16 RCR Receive Last Slot Interrupt Enable (RLIE) - Bit 23 . . . . . . . . . . . . . . . . . . . . . . 6-31

6.3.5 ESAI Common Control Register (SAICR). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-32

BookTitle, Rev. #

vi Freescale Semiconductor

Page 7

6.3.5.1 SAICR Serial Output Flag 0 (OF0) - Bit 0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-32

6.3.5.2 SAICR Serial Output Flag 1 (OF1) - Bit 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-32

6.3.5.3 SAICR Serial Output Flag 2 (OF2) - Bit 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-32

6.3.5.4 SAICR Reserved Bits - Bits 3-5, 9-23 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-32

6.3.5.5 SAICR Synchronous Mode Selection (SYN) - Bit 6 . . . . . . . . . . . . . . . . . . . . . . . . . . 6-33

6.3.5.6 SAICR Transmit External Buffer Enable (TEBE) - Bit 7 . . . . . . . . . . . . . . . . . . . . . . 6-33

6.3.5.7 SAICR Alignment Control (ALC) - Bit 8 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-33

6.3.6 ESAI Status Register (SAISR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-34

6.3.6.1 SAISR Serial Input Flag 0 (IF0) - Bit 0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-35

6.3.6.2 SAISR Serial Input Flag 1 (IF1) - Bit 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-35

6.3.6.3 SAISR Serial Input Flag 2 (IF2) - Bit 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-35

6.3.6.4 SAISR Reserved Bits - Bits 3-5, 11-12, 18-23 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-35

6.3.6.5 SAISR Receive Frame Sync Flag (RFS) - Bit 6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-36

6.3.6.6 SAISR Receiver Overrun Error Flag (ROE) - Bit 7 . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-36

6.3.6.7 SAISR Receive Data Register Full (RDF) - Bit 8 . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-36

6.3.6.8 SAISR Receive Even-Data Register Full (REDF) - Bit 9 . . . . . . . . . . . . . . . . . . . . . . 6-36

6.3.6.9 SAISR Receive Odd-Data Register Full (RODF) - Bit 10 . . . . . . . . . . . . . . . . . . . . . . 6-36

6.3.6.10 SAISR Transmit Frame Sync Flag (TFS) - Bit 13 . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-37

6.3.6.11 SAISR Transmit Underrun Error Flag (TUE) - Bit 14 . . . . . . . . . . . . . . . . . . . . . . . . . 6-37

6.3.6.12 SAISR Transmit Data Register Empty (TDE) - Bit 15 . . . . . . . . . . . . . . . . . . . . . . . . 6-37

6.3.6.13 SAISR Transmit Even-Data Register Empty (TEDE) - Bit 16 . . . . . . . . . . . . . . . . . . 6-37

6.3.6.14 SAISR Transmit Odd-Data Register Empty (TODE) - Bit 17 . . . . . . . . . . . . . . . . . . . 6-38

6.3.7 ESAI Receive Shift Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-41

6.3.8 ESAI Receive Data Registers (RX3, RX2, RX1, RX0) . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-41

6.3.9 ESAI Transmit Shift Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-41

6.3.10 ESAI Transmit Data Registers (TX5, TX4, TX3, TX2,TX1,TX0) . . . . . . . . . . . . . . . . . . 6-41

6.3.11 ESAI Time Slot Register (TSR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-41

6.3.12 Transmit Slot Mask Registers (TSMA, TSMB) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-41

6.3.13 Receive Slot Mask Registers (RSMA, RSMB) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-43

6.4 Operating Modes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-44

6.4.1 ESAI After Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-44

6.4.2 ESAI Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-44

6.4.3 ESAI Interrupt Requests . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-45

6.4.4 Operating Modes – Normal, Network, and On-Demand . . . . . . . . . . . . . . . . . . . . . . . . . . 6-46

6.4.4.1 Normal/Network/On-Demand Mode Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-46

6.4.4.2 Synchronous/Asynchronous Operating Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-46

6.4.4.3 Frame Sync Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-47

6.4.4.4 Shift Direction Selection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-47

6.4.5 Serial I/O Flags . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-48

6.5 GPIO - Pins and Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-48

6.5.1 Port C Control Register (PCRC). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-48

6.5.2 Port C Direction Register (PRRC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-49

6.5.3 Port C Data register (PDRC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-49

6.6 ESAI Initialization Examples . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-50

6.6.1 Initializing the ESAI Using Individual Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-50

BookTitle, Rev. #

Freescale Semiconductor vii

Page 8

6.6.2 Initializing Just the ESAI Transmitter Section . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-51

6.6.3 Initializing Just the ESAI Receiver Section . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-51

7 Serial Host Interface

7.1 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-1

7.2 Serial Host Interface Internal Architecture. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-2

7.3 SHI Clock Generator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-3

7.4 Serial Host Interface Programming Model. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-3

7.4.1 SHI Input/Output Shift Register (IOSR)—Host Side. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-5

7.4.2 SHI Host Transmit Data Register (HTX)—DSP Side . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-6

7.4.3 SHI Host Receive Data FIFO (HRX)—DSP Side . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-6

7.4.4 SHI Slave Address Register (HSAR)—DSP Side . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-6

7.4.4.1 HSAR Reserved Bits—Bits 17–0,19 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-7

7.4.4.2 HSAR I2C Slave Address (HA[6:3], HA1)—Bits 23–20,18 . . . . . . . . . . . . . . . . . . . . . 7-7

7.4.5 SHI Clock Control Register (HCKR)—DSP Side . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-7

7.4.5.1 Clock Phase and Polarity (CPHA and CPOL)—Bits 1–0 . . . . . . . . . . . . . . . . . . . . . . . 7-7

7.4.5.2 HCKR Prescaler Rate Select (HRS)—Bit 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-9

7.4.5.3 HCKR Divider Modulus Select (HDM[7:0])—Bits 10–3 . . . . . . . . . . . . . . . . . . . . . . . 7-9

7.4.5.4 HCKR Reserved Bits—Bits 23–14, 11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-9

7.4.5.5 HCKR Filter Mode (HFM[1:0]) — Bits 13–12 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-9

7.4.6 SHI Control/Status Register (HCSR)—DSP Side . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-10

7.4.6.1 HCSR Host Enable (HEN)—Bit 0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-10

7.4.6.1.1 SHI Individual Reset. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-11

7.4.6.2 HCSR I2C/SPI Selection (HI2C)—Bit 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-11

7.4.6.3 HCSR Serial Host Interface Mode (HM[1:0])—Bits 3–2 . . . . . . . . . . . . . . . . . . . . . . 7-11

7.4.6.4 HCSR I2C Clock Freeze (HCKFR) - Bit 4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-11

7.4.6.5 HCSR Reserved Bits—Bits 23, 18 and 16 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-12

7.4.6.6 HCSR FIFO-Enable Control (HFIFO)—Bit 5 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-12

7.4.6.7 HCSR Master Mode (HMST)—Bit 6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-12

7.4.6.8 HCSR Host-Request Enable (HRQE[1:0])—Bits 8–7 . . . . . . . . . . . . . . . . . . . . . . . . . 7-12

7.4.6.9 HCSR Idle (HIDLE)—Bit 9 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-13

7.4.6.10 HCSR Bus-Error Interrupt Enable (HBIE)—Bit 10 . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-13

7.4.6.11 HCSR Transmit-Interrupt Enable (HTIE)—Bit 11 . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-14

7.4.6.12 HCSR Receive Interrupt Enable (HRIE[1:0])—Bits 13–12. . . . . . . . . . . . . . . . . . . . . 7-14

7.4.6.13 HCSR Host Transmit Underrun Error (HTUE)—Bit 14 . . . . . . . . . . . . . . . . . . . . . . . 7-15

7.4.6.14 HCSR Host Transmit Data Empty (HTDE)—Bit 15 . . . . . . . . . . . . . . . . . . . . . . . . . . 7-15

7.4.6.15 Host Receive FIFO Not Empty (HRNE)—Bit 17 . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-15

7.4.6.16 Host Receive FIFO Full (HRFF)—Bit 19 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-16

7.4.6.17 Host Receive Overrun Error (HROE)—Bit 20. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-16

7.4.6.18 Host Bus Error (HBER)—Bit 21 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-16

7.4.6.19 HCSR Host Busy (HBUSY)—Bit 22 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-16

7.5 SPI Bus Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-16

7.6 I

7.6.1 Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-17

2

C Bus Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-17

BookTitle, Rev. #

viii Freescale Semiconductor

Page 9

7.6.2 I2C Data Transfer Formats . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-19

7.7 SHI Programming Considerations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-20

7.7.1 SPI Slave Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-20

7.7.2 SPI Master Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-21

2

7.7.3 I

7.7.3.1 Receive Data in I

C Slave Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-21

2

C Slave Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-22

7.7.3.2 Transmit Data In I2C Slave Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-23

7.7.4 I2C Master Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-23

7.7.4.1 Receive Data in I2C Master Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-24

7.7.4.2 Transmit Data In I2C Master Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-25

7.7.5 SHI Operation During DSP Stop . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-25

Appendix A Bootstrap ROM

A.1 DSP56364 Bootstrap Program . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .A-1

Appendix B BDSL File

B.1 BSDL FILE. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-1

Appendix C Programmer’s Reference

C.1 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . C-1

C.1.1 Peripheral Addresses. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . C-1

C.1.2 Interrupt Addresses . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . C-1

C.1.3 Interrupt Priorities. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . C-1

C.2 Programming Sheets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . C-8

BookTitle, Rev. #

Freescale Semiconductor ix

Page 10

BookTitle, Rev. #

x Freescale Semiconductor

Page 11

List of Figures

Figure 1-1 DSP56364 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-2

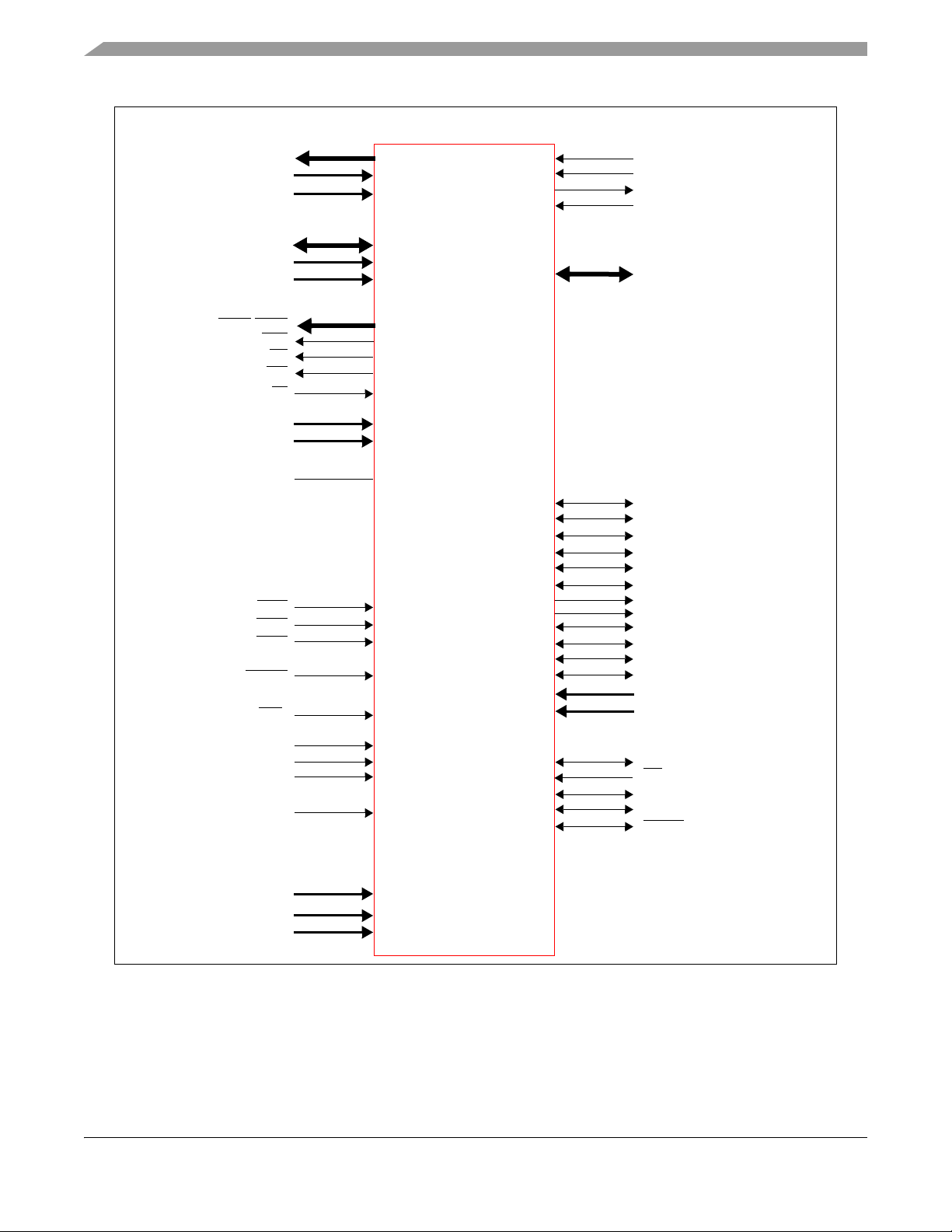

Figure 2-1 Signals Identified by Functional Group . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-2

Figure 3-1 Memory Maps for MS=0, SC=0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-6

Figure 3-2 Memory Maps for MS=1, SC=0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-6

Figure 3-3 Memory Maps for MS=0, SC=1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-7

Figure 3-4 Memory Maps for MS=1, SC=1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-7

Figure 4-1 Operating Mode Register (OMR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-2

Figure 4-2 Interrupt Priority Register P . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-6

Figure 4-3 Interrupt Priority Register C . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-6

Figure 5-1 GPIO Port B Control Register (PCRB) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-1

Figure 5-2 GPIO Port B Direction Register (PRRB) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-2

Figure 5-3 GPIO Port B Data Register (PDRB) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-2

Figure 6-1 ESAI Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-2

Figure 6-2 TCCR Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-8

Figure 6-3 ESAI Clock Generator Functional Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-9

Figure 6-4 ESAI Frame Sync Generator Functional Block Diagram . . . . . . . . . . . . . . . . . . . . . . 6-11

Figure 6-5 TCR Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-13

Figure 6-6 Normal and Network Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-17

Figure 6-7 Frame Length Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-20

Figure 6-8 RCCR Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-23

Figure 6-9 RCR Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-27

Figure 6-10 SAICR Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-32

Figure 6-11 SAICR SYN Bit Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-34

Figure 6-12 SAISR Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-35

Figure 6-13 ESAI Data Path Programming Model ([R/T]SHFD=0) . . . . . . . . . . . . . . . . . . . . . . . 6-39

Figure 6-14 ESAI Data Path Programming Model ([R/T]SHFD=1) . . . . . . . . . . . . . . . . . . . . . . . 6-40

Figure 6-15 TSMA Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-42

Figure 6-16 TSMB Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-42

Figure 6-17 RSMA Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-43

Figure 6-18 RSMB Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-43

Figure 6-19 PCRC Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-49

Figure 6-20 PRRC Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-49

Figure 6-21 PDRC Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-50

Figure 7-1 Serial Host Interface Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-2

Figure 7-2 SHI Clock Generator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-3

Figure 7-3 SHI Programming Model—Host Side . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-3

Figure 7-4 SHI Programming Model—DSP Side . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-4

Figure 7-5 SHI I/O Shift Register (IOSR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-6

Figure 7-6 SPI Data-To-Clock Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-8

Figure 7-7 I2C Bit Transfer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-17

Figure 7-8 I2C Start and Stop Events . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-18

Figure 7-9 Acknowledgment on the I

Figure 7-10 I

2

C Bus Protocol For Host Write Cycle . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-19

Figure 7-11 I2C Bus Protocol For Host Read Cycle . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-19

Figure C-1 Status Register (SR). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . C-9

2

C Bus . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-18

DSP56364 24-Bit Digital Signal Processor Users Manual, Rev. 2

Freescale Semiconductor xi

Page 12

Figure C-2 Operating Mode Register (OMR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . C-10

Figure C-3 Interrupt Priority Register-Core (IPR-C). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . C-11

Figure C-4 Interrupt Priority Register- Peripherals (IPR-P) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . C-12

Figure C-5 Phase Lock Loop Control Register (PCTL) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . C-13

Figure C-6 SHI Slave Address (HSAR) and Clock Control Register (HCKR) . . . . . . . . . . . . . . . C-14

Figure C-7 SHI Host Transmit Data Register (HTX) and Host Receive Data Register (HRX) (FIFO)

C-15

Figure C-8 SHI Host Control/Status Register (HCSR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . C-16

Figure C-9 ESAI Transmit Clock Control Register (TCCR). . . . . . . . . . . . . . . . . . . . . . . . . . . . . C-17

Figure C-10 ESAI Transmit Clock Control Register (TCR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . C-18

Figure C-11 ESAI Receive Clock Control Register (RCCR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . C-19

Figure C-12 ESAI Receive Clock Control Register (RCR). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . C-20

Figure C-13 ESAI Common Control Register (SAICR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . C-21

Figure C-14 ESAI Status Register (SAISR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . C-22

Figure C-15 Port B Registers (PCRB, PRRB, PDRB). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . C-23

Figure C-16 Port C Registers (PCRC, PRRC, PDRC). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . C-24

DSP56364 24-Bit Digital Signal Processor Users Manual, Rev. 2

xii Freescale Semiconductor

Page 13

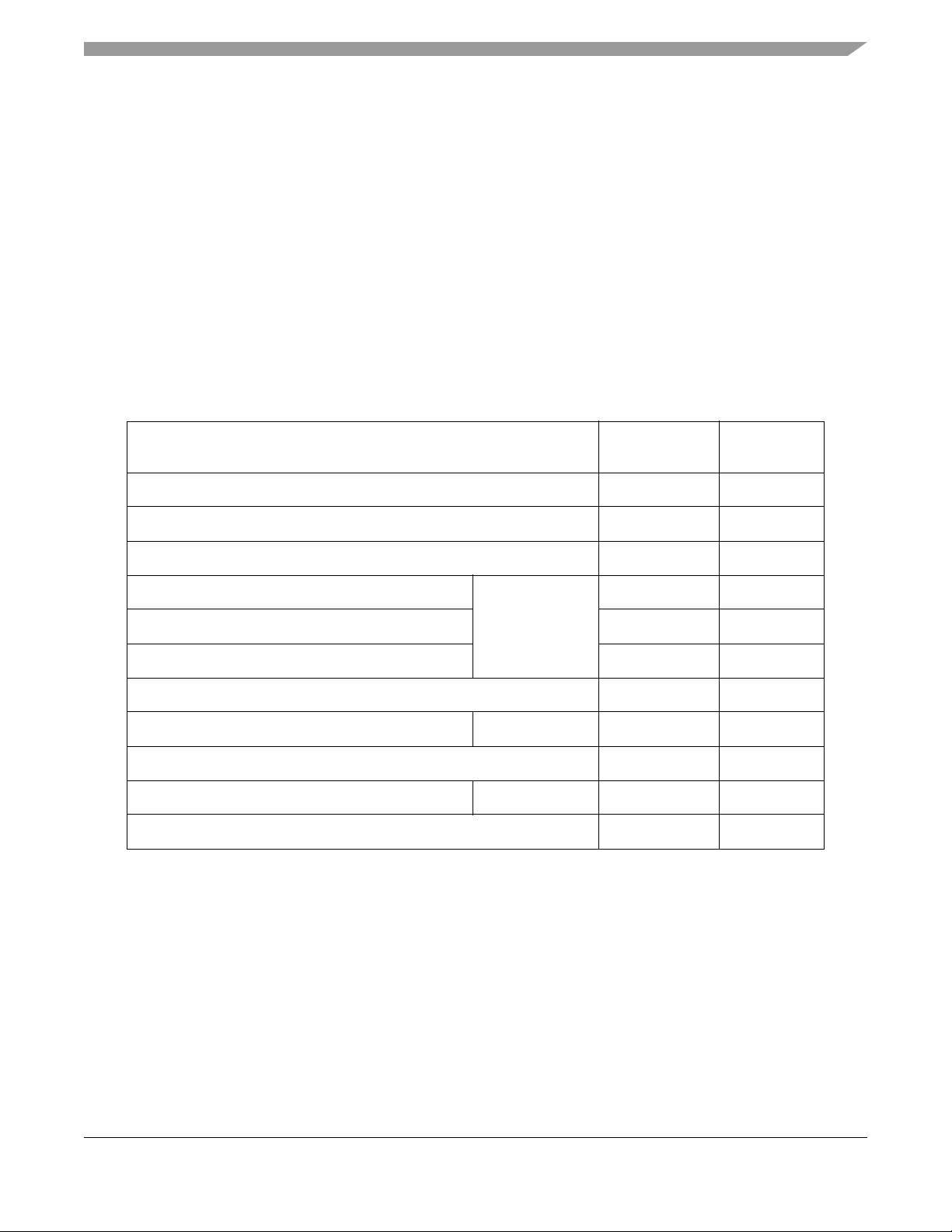

List of Tables

Table 2-1 DSP56364 Functional Signal Groupings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-1

Table 2-2 Power Inputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-3

Table 2-3 Grounds . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-3

Table 2-4 Clock and PLL Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-4

Table 2-5 External Address Bus Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-4

Table 2-6 External Data Bus Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-5

Table 2-7 External Bus Control Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-5

Table 2-8 Interrupt and Mode Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-7

Table 2-9 Serial Host Interface Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-8

Table 2-10 Enhanced Serial Audio Interface Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-10

Table 2-11 JTAG/OnCE Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-13

Table 2-12 GPIO Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-14

Table 3-1 Memory Space Configuration Bit Settings for the DSP56364 . . . . . . . . . . . . . . . . . . . 3-3

Table 3-2 Internal Memory Configurations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-4

Table 3-3 On-chip RAM Memory Locations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-4

Table 3-4 On-chip ROM Memory Locations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-4

Table 4-1 DSP56364 Operating Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-3

Table 4-2 Interrupt Priority Level Bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-5

Table 4-3 DMA Request Sources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-7

Table 4-4 Identification Register Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-8

Table 4-5 JTAG Identification Register Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-8

Table 4-6 DSP56364 BSR Bit Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-9

Table 5-1 GPIO Pin Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-3

Table 6-1 Receiver Clock Sources (asynchronous mode only) . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-5

Table 6-2 Transmitter Clock Sources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-6

Table 6-3 Transmitter High Frequency Clock Divider . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-11

Table 6-4 Transmit Network Mode Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-16

Table 6-5 ESAI Transmit Slot and Word Length Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-18

Table 6-6 Receiver High Frequency Clock Divider . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-24

Table 6-7 SCKR Pin Definition Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-25

Table 6-8 FSR Pin Definition Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-26

Table 6-9 HCKR Pin Definition Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-26

Table 6-10 ESAI Receive Network Mode Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-29

Table 6-11 ESAI Receive Slot and Word Length Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-29

Table 6-12 PCRC and PRRC Bits Functionality . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-49

Table 7-1 SHI Interrupt Vectors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-5

Table 7-2 SHI Internal Interrupt Priorities . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-5

Table 7-3 SHI Noise Reduction Filter Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-10

Table 7-4 SHI Data Size . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-11

Table 7-5 HREQ Function In SHI Slave Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-12

Table 7-6 HCSR Receive Interrupt Enable Bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-14

Table C-1 Internal I/O Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . C-1

Table C-2 DSP56364 Interrupt Vectors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . C-5

Table C-3 Interrupt Sources Priorities Within an IP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . C-6

DSP56364 24-Bit Digital Signal Processor Users Manual, Rev. 2

Freescale Semiconductor xiii

Page 14

DSP56364 24-Bit Digital Signal Processor Users Manual, Rev. 2

xiv Freescale Semiconductor

Page 15

Preface

This manual contains the following sections and appendices.

SECTION 1—DSP56364 OVERVIEW

• Provides a brief description of the DSP56364, including a features list and block diagram. Lists

related documentation needed to use this chip and describes the organization of this manual.

SECTION 2—SIGNAL/CONNECTION DESCRIPTIONS

• Describes the signals on the DSP56364 pins and how these signals are grouped into interfaces.

SECTION 3—MEMORY CONFIGURATION

• Describes the DSP56364 memory spaces, RAM and ROM configuration, memory configurations

and their bit settings, and memory maps.

SECTION 4—CORE CONFIGURATION

• Describes the registers used to configure the DSP56300 core when programming the DSP56364,

in particular the interrupt vector locations and the operation of the interrupt priority registers.

Explains the operating modes and how they affect the processor’s program and data memories.

SECTION 5—GENERAL PURPOSE INPUT/OUTPUT (GPIO)

• Describes the DSP56364 GPIO capability and the programming model for the GPIO signals

(operation, registers, and control).

SECTION 6—ENHANCED SERIAL AUDIO INTERFACE (ESAI)

• Describes the full-duplex serial port for serial communication with a variety of serial devices.

SECTION 7—SERIAL HOST INTERFACE (SHI)

• Describes the serial input/output interface providing a path for communication and

program/coefficient data transfers between the DSP and an external host processor. The SHI can

also communicate with other serial peripheral devices.

APPENDIX A—BOOTSTRAP PROGRAM

• Lists the bootstrap code used for the DSP56364.

APPENDIX B—BSDL LISTING

• Provides the BSDL listing for the DSP56364.

APPENDIX C—PROGRAMMING REFERENCE

• Lists peripheral addresses, interrupt addresses, and interrupt priorities for the DSP56364. Contains

programming sheets listing the contents of the major DSP56364 registers for programmer

reference.

DSP56364 24-Bit Digital Signal Processor Users Manual, Rev. 2

Freescale Semiconductor xv

Page 16

Manual Conventions

The following conventions are used in this manual:

• Bits within registers are always listed from most significant bit (MSB) to least significant bit

(LSB).

• When several related bits are discussed, they are referenced as AA[n:m], where n>m. For purposes

of description, the bits are presented as if they are contiguous within a register. However, this is not

always the case. Refer to the programming model diagrams or to the programmer’s sheets to see

the exact location of bits within a register.

• When a bit is described as “set”, its value is 1. When a bit is described as “cleared”, its value is 0.

• The word “assert” means that a high true (active high) signal is pulled high to VCC or that a low

true (active low) signal is pulled low to ground. The word “deassert” means that a high true signal

is pulled low to ground or that a low true signal is pulled high to VCC.

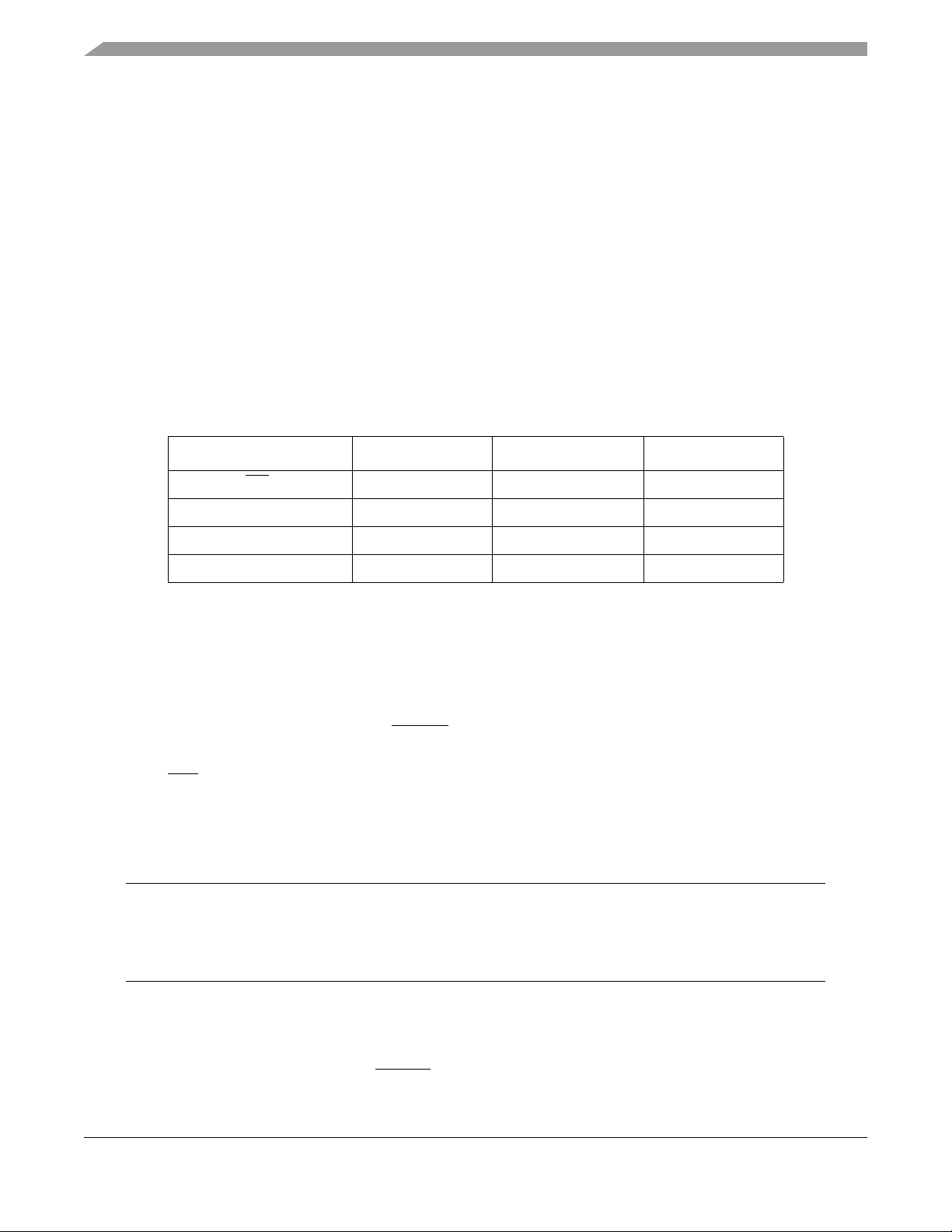

Signal/Symbol Logic State Signal State Voltage

1

PIN

PIN False Deasserted V

PIN True Asserted V

PIN False Deasserted Ground

1

PIN is a generic term for any pin on the chip.

2

Ground is an acceptable low voltage level. See the appropriate data sheet for the range of

acceptable low voltage levels (typically a TTL logic low).

3

VCC is an acceptable high voltage level. See the appropriate data sheet for the range of acceptable

high voltage levels (typically a TTL logic high).

High True/Low True Signal Conventions

True Asserted Ground

CC

CC

2

3

• Pins or signals that are asserted low (made active when pulled to ground)

— In text, have an overbar (e.g., RESET is asserted low).

— In code examples, have a tilde in front of their names. In example below, line 3 refers to the

SS0 pin (shown as ~SS0).

• Sets of pins or signals are indicated by the first and last pins or signals in the set (e.g., HA1–HA8).

• Code examples are displayed in a monospaced font, as shown below:

.

BFSET #$0007,X:PCC; Configure: line 1

; MISO0, MOSI0, SCK0 for SPI master line 2

; ~SS0 as PC3 for GPIO line 3

Example Sample Code Listing

• Hex values are indicated with a dollar sign ($) preceding the hex value, as follows: $FFFFFF is the

X memory address for the core interrupt priority register (IPR-C).

• The word “reset” is used in four different contexts in this manual:

— the reset signal, written as “RESET,”

DSP56364 24-Bit Digital Signal Processor Users Manual, Rev. 2

xvi Freescale Semiconductor

Page 17

— the reset instruction, written as “RESET,”

— the reset operating state, written as “Reset,” and

— the reset function, written as “reset.”

DSP56364 24-Bit Digital Signal Processor Users Manual, Rev. 2

Freescale Semiconductor xvii

Page 18

DSP56364 24-Bit Digital Signal Processor Users Manual, Rev. 2

xviii Freescale Semiconductor

Page 19

1 Overview

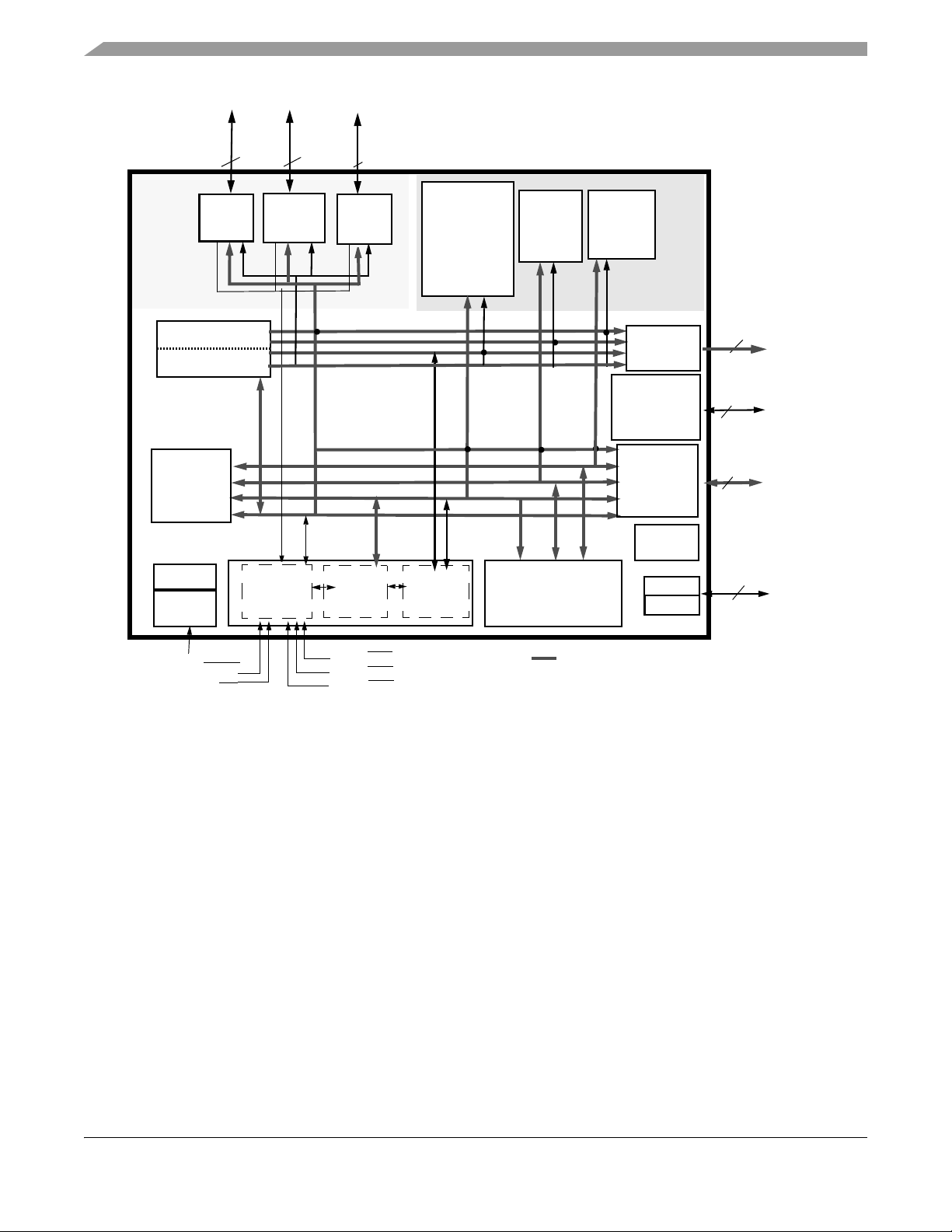

1.1 Introduction

The DSP56364 24-Bit Digital Signal Processor, a new audio digital signal processor based on the 24-bit

DSP56300 architecture, is targeted to applications that require digital audio signal processing such as

sound field processing, acoustic equalization and other digital audio algorithms.

The DSP56364 supports digital audio applications requiring sound field processing, acoustic equalization,

and other digital audio algorithms. The DSP56364 uses the high performance, single-clock-per-cycle

DSP56300 core family of programmable CMOS digital signal processors (DSPs) combined with the audio

signal processing capability of the Freescale Symphony™ DSP family, as shown in Figure 1-1. This

design provides a two-fold performance increase over Freescale’s popular Symphony family of DSPs

while retaining code compatibility. Significant architectural enhancements include a barrel shifter, 24-bit

addressing, instruction cache, and direct memory access (DMA).

This document is intended to be used with the following Freescale publications:

• DSP56300 24-Bit Digital Signal Processor Family Manual, Freescale publication DSP56300FM.

• DSP56364 24-Bit Digital Signal Processor Technical Data Sheet, Freescale publication

DSP56364.

The DSP56300 24-Bit Digital Signal Processor Family Manual, Freescale publication DSP56300FM

provides a description of the components of the DSP56300 modular chassis which is common to all

DSP56300 family processors and includes a detailed description of the instruction set. This document

provides a detailed description of the core configuration, memory, and peripherals that are specific to the

DSP56364. The electrical specifications, timings and packaging information can be found in the

DSP56364 Technical Data Sheet.

DSP56364 24-Bit Digital Signal Processor Users Manual, Rev. 2

Freescale Semiconductor 1-1

Page 20

Features

PERIPHERAL

EXPANSION

AREA

GENERATION UNIT

INTERNAL

DATA BU S

SWITCH

CLOCK

GEN

GPIO

ADDRESS

SIX CHANNELS

DMA UNIT

PLL

4

PROGRAM

INTERRUPT

CONT

ESAI

12

PIO_EB

5

SHI

24-BIT

DSP56300

CORE

PROGRAM

DECODE

CONT

PROGRAM

RAM

0.5K x 24

PR O GR A M R O M

8K x 24

Bootstrap ROM

192 x 24

PROGRAM

ADDRESS

GEN

X

MEMORY

RAM

1K X 24

XM_EB

YA B

PM_EB

XAB

PA B

DAB

DDB

YDB

XDB

PDB

GDB

DATA A L U

24 X 24+56

TWO 56-BIT ACCUMULATORS

56-BIT MAC

→

BARREL SHIFTER

Y MEMORY

RAM

1.5K X 24

MEMORY

EXPANSION

AREA

YM_EB

ADDRESS BUS

DRAM & SRAM

INTERFACE

EXTERNAL

EXTERNAL

SWITCH

BUS

DATA BUS

SWITCH

POWER

MGMT

JTAG

OnCE™

ADDRESS

18

CONTROL

6

8

4

DATA

EXTAL

RESET

PINIT/NMI

1.2 Features

• DSP56300 modular chassis

— 100 Million Instructions Per Second (MIPS) with an 100 MHz clock at 3.3V.

— Object Code Compatible with the 56K core.

— Data ALU with a 24 × 24 bit multiplier-accumulator and a 56-bit barrel shifter. 16-bit

arithmetic support.

— Program Control with position independent code support and instruction cache support.

— Six-channel DMA controller.

— PLL based clocking with a wide range of frequency multiplications (1 to 4096), predivider

factors (1 to 16) and power saving clock divider (2i: i = 0 to 7). Reduces clock noise.

— Internal address tracing support and OnCE‰ for Hardware/Software debugging.

— JTAG port.

MODA/IRQA

MODB/IRQB

MODD/IRQD

24 BITS BUS

Figure 1-1 DSP56364 Block Diagram

DSP56364 24-Bit Digital Signal Processor Users Manual, Rev. 2

1-2 Freescale Semiconductor

Page 21

Audio Processor Architecture

— Very low-power CMOS design, fully static design with operating frequencies down to DC.

— STOP and WAIT low-power standby modes.

• On-chip Memory Configuration

— 1.5K × 24 Bit Y-Data RAM.

—1K × 24 Bit X-Data RAM.

—8K × 24 Bit Program ROM.

— 0.5K × 24 Bit Program RAM and 192 × 24 Bit Bootstrap ROM.

— 0.75K × 24 Bit from Y Data RAM can be switched to Program RAM resulting in up to

1.25K × 24 Bit of Program RAM.

• Off-chip memory expansion

— External Memory Expansion Port with 8-bit data bus.

— Off-chip expansion up to 2 × 16M x 8-bit word of Data memory when using DRAM.

— Off-chip expansion up to 2 × 256K x 8-bit word of Data memory when using SRAM.

— Simultaneous glueless interface to SRAM and DRAM.

• Peripheral modules

— Serial Audio Interface (ESAI): up to 4 receivers and up to 6 transmitters, master or slave. I2S,

Sony, AC97, network and other programmable protocols. Unused pins of ESAI may be used

as GPIO lines.

— Serial Host Interface (SHI): SPI and I2C protocols, multi master capability, 10-word receive

FIFO, support for 8, 16 and 24-bit words.

— Four dedicated GPIO lines.

• 100-pin plastic TQFP package.

1.3 Audio Processor Architecture

This section defines the DSP56364 audio processor architecture. The audio processor is composed of the

following units:

• The DSP56300 core is composed of the Data ALU, Address Generation Unit, Program Controller,

Instruction-Cache Controller, DMA Controller, PLL-based clock oscillator, Memory Module

Interface, Peripheral Module Interface and the On-Chip Emulator (OnCE). The DSP56300 core is

described in the document DSP56300 24-Bit Digital Signal Processor Family Manual, Motorola

publication DSP56300FM.

• Memory modules.

• Peripheral modules. The SHI, ESAI and GPIO peripheral are described in this document.

See Figure 1-1 for the block diagram of the DSP56364.

DSP56364 24-Bit Digital Signal Processor Users Manual, Rev. 2

Freescale Semiconductor 1-3

Page 22

Core Description

1.4 Core Description

The DSP56364 uses the DSP56300 core, a high-performance, single clock cycle per instruction engine that

provides up to twice the performance of Freescale's popular DSP56000 core family while retaining code

compatibility with it.

The DSP56300 core provides the following functional blocks:

• Data arithmetic logic unit (Data ALU)

• Address generation unit (AGU)

• Program control unit (PCU)

• Bus interface unit (BIU)

• DMA controller (with six channels)

• Instruction cache controller

• PLL-based clock oscillator

• OnCE module

• JTAG TAP

• Memory

The DSP56300 core family offers a new level of performance in speed and power, provided by its rich

instruction set and low power dissipation, thus enabling a new generation of wireless, telecommunications,

and multimedia products. Significant architectural enhancements to the DSP56300 core family include a

barrel shifter, 24-bit addressing, an instruction cache, and direct memory access (DMA).

Core features are described fully in the DSP56300 Family Manual. Pinout, memory, and peripheral

features are described in this manual.

1.5 DSP56300 Core Functional Blocks

1.5.1 Data ALU

The Data ALU performs all the arithmetic and logical operations on data operands in the DSP56300 core.

The components of the Data ALU are as follows:

• Fully pipelined 24-bit × 24-bit parallel multiplier-accumulator (MAC)

• Bit field unit, comprising a 56-bit parallel barrel shifter (fast shift and normalization; bit stream

generation and parsing)

• Conditional ALU instructions

• 24-bit or 16-bit arithmetic support under software control

• Four 24-bit input general purpose registers: X1, X0, Y1, and Y0

• Six Data ALU registers (A2, A1, A0, B2, B1, and B0) that are concatenated into two general

purpose, 56-bit accumulators (A and B), accumulator shifters

• Two data bus shifter/limiter circuits

DSP56364 24-Bit Digital Signal Processor Users Manual, Rev. 2

1-4 Freescale Semiconductor

Page 23

DSP56300 Core Functional Blocks

1.5.1.1 Data ALU Registers

The Data ALU registers can be read or written over the X memory data bus (XDB) and the Y memory data

bus (YDB) as 24- or 48-bit operands (or as 16- or 32-bit operands in 16-bit arithmetic mode). The source

operands for the Data ALU, which can be 24, 48, or 56 bits (16, 32, or 40 bits in 16-bit arithmetic mode),

always originate from Data ALU registers. The results of all Data ALU operations are stored in an

accumulator.

All the Data ALU operations are performed in two clock cycles in pipeline fashion so that a new

instruction can be initiated in every clock, yielding an effective execution rate of one instruction per clock

cycle. The destination of every arithmetic operation can be used as a source operand for the immediately

following arithmetic operation without a time penalty (in other words, without a pipeline stall).

1.5.1.2 Multiplier-Accumulator (MAC)

The MAC unit comprises the main arithmetic processing unit of the DSP56300 core and performs all of

the calculations on data operands. In the case of arithmetic instructions, the unit accepts as many as three

input operands and outputs one 56-bit result of the following form- Extension:Most Significant

Product:Least Significant Product (EXT:MSP:LSP).

The multiplier executes 24-bit × 24-bit, parallel, fractional multiplies, between two’s-complement signed,

unsigned, or mixed operands. The 48-bit product is right-justified and added to the 56-bit contents of either

the A or B accumulator. A 56-bit result can be stored as a 24-bit operand. The LSP can either be truncated

or rounded into the MSP. Rounding is performed if specified.

1.5.2 Address Generation Unit (AGU)

The AGU performs the effective address calculations using integer arithmetic necessary to address data

operands in memory and contains the registers used to generate the addresses. It implements four types of

arithmetic: linear, modulo, multiple wrap-around modulo, and reverse-carry. The AGU operates in parallel

with other chip resources to minimize address-generation overhead.

The AGU is divided into two halves, each with its own Address ALU. Each Address ALU has four sets of

register triplets, and each register triplet is composed of an address register, an offset register, and a

modifier register. The two Address ALUs are identical. Each contains a 24-bit full adder (called an offset

adder).

A second full adder (called a modulo adder) adds the summed result of the first full adder to a modulo

value that is stored in its respective modifier register. A third full adder (called a reverse-carry adder) is

also provided.

The offset adder and the reverse-carry adder are in parallel and share common inputs. The only difference

between them is that the carry propagates in opposite directions. Test logic determines which of the three

summed results of the full adders is output.

Each Address ALU can update one address register from its respective address register file during one

instruction cycle. The contents of the associated modifier register specifies the type of arithmetic to be used

in the address register update calculation. The modifier value is decoded in the Address ALU.

DSP56364 24-Bit Digital Signal Processor Users Manual, Rev. 2

Freescale Semiconductor 1-5

Page 24

DSP56300 Core Functional Blocks

1.5.3 Program Control Unit (PCU)

The PCU performs instruction prefetch, instruction decoding, hardware DO loop control, and exception

processing. The PCU implements a seven-stage pipeline and controls the different processing states of the

DSP56300 core. The PCU consists of the following three hardware blocks:

• Program decode controller (PDC)

• Program address generator (PAG)

• Program interrupt controller (PIC)

The PDC decodes the 24-bit instruction loaded into the instruction latch and generates all signals necessary

for pipeline control. The PAG contains all the hardware needed for program address generation, system

stack, and loop control. The PIC arbitrates among all interrupt requests (internal interrupts, as well as the

five external requests: IRQA, IRQB, IRQD, and NMI), and generates the appropriate interrupt vector

address.

PCU features include the following:

• Position independent code support

• Addressing modes optimized for DSP applications (including immediate offsets)

• On-chip instruction cache controller

• On-chip memory-expandable hardware stack

• Nested hardware DO loops

• Fast auto-return interrupts

The PCU implements its functions using the following registers:

• PC—program counter register

• SR—Status register

• LA—loop address register

• LC—loop counter register

• VBA—vector base address register

• SZ—stack size register

• SP—stack pointer

• OMR—operating mode register

• SC—stack counter register

The PCU also includes a hardware system stack (SS).

1.5.4 Internal Buses

To provide data exchange between blocks, the following buses are implemented:

• Peripheral input/output expansion bus (PIO_EB) to peripherals

• Program memory expansion bus (PM_EB) to program memory

• X memory expansion bus (XM_EB) to X memory

DSP56364 24-Bit Digital Signal Processor Users Manual, Rev. 2

1-6 Freescale Semiconductor

Page 25

DSP56300 Core Functional Blocks

• Y memory expansion bus (YM_EB) to Y memory

• Global data bus (GDB) between registers in the DMA, AGU, OnCE, PLL, BIU, and PCU as well

as the memory-mapped registers in the peripherals

• DMA data bus (DDB) for carrying DMA data between memories and/or peripherals

• DMA address bus (DAB) for carrying DMA addresses to memories and peripherals

• Program Data Bus (PDB) for carrying program data throughout the core

• X memory Data Bus (XDB) for carrying X data throughout the core

• Y memory Data Bus (YDB) for carrying Y data throughout the core

• Program address bus (PAB) for carrying program memory addresses throughout the core

• X memory address bus (XAB) for carrying X memory addresses throughout the core

• Y memory address bus (YAB) for carrying Y memory addresses throughout the core

All internal buses on the DSP56300 family members are 24-bit buses. See Figure 1-1, DSP56364 block

diagram.

1.5.5 Direct Memory Access (DMA)

The DMA block has the following features:

• Six DMA channels supporting internal and external accesses

• One-, two-, and three-dimensional transfers (including circular buffering)

• End-of-block-transfer interrupts

• Triggering from interrupt lines and all peripherals

1.5.6 PLL-based Clock Oscillator

The clock generator in the DSP56300 core is composed of two main blocks: the PLL, which performs

clock input division, frequency multiplication, and skew elimination; and the clock generator (CLKGEN),

which performs low-power division and clock pulse generation. PLL-based clocking:

• Allows change of low-power divide factor (DF) without loss of lock

• Provides output clock with skew elimination

• Provides a wide range of frequency multiplications (1 to 4096), predivider factors (1 to 16), and a

power-saving clock divider (2

The PLL allows the processor to operate at a high internal clock frequency using a low frequency clock

input. This feature offers two immediate benefits:

• A lower frequency clock input reduces the overall electromagnetic interference generated by a

system.

• The ability to oscillate at different frequencies reduces costs by eliminating the need to add

additional oscillators to a system.

i

: i = 0 to 7) to reduce clock noise

DSP56364 24-Bit Digital Signal Processor Users Manual, Rev. 2

Freescale Semiconductor 1-7

Page 26

Data and Program memory

1.5.7 JTAG TAP and OnCE Module

The DSP56300 core provides a dedicated user-accessible TAP fully compatible with the IEEE 1149.1

Standard Test Access Port and Boundary Scan Architecture. Problems associated with testing high-density

circuit boards led to developing this standard under the sponsorship of the Test Technology Committee of

IEEE and JTAG. The DSP56300 core implementation supports circuit-board test strategies based on this

standard.

The test logic includes a TAP consisting of four dedicated signals, a 16-state controller, and three test data

registers. A boundary scan register links all device signals into a single shift register. The test logic,

implemented utilizing static logic design, is independent of the device system logic.

The OnCE module provides a nonintrusive means of interacting with the DSP56300 core and its

peripherals so a user can examine registers, memory, or on-chip peripherals. This facilitates hardware and

software development on the DSP56300 core processor. OnCE module functions are provided through the

JTAG TAP signals.

1.6 Data and Program memory

The on-chip memory configuration of the DSP56364 is affected by the state of the MS (Memory Switch)

control bit in the OMR register, and by the SC bit in the Status Register. Refer to Section 3, "Memory

Configuration".

1.6.1 Reserved Memory Spaces

The reserved memory spaces should not be accessed by the user. They are reserved for future expansion.

1.6.2 Program ROM Area Reserved for Freescale Use

The last 128 words ($FF2F80-$FF2FFF) of the Program ROM are reserved for Freescale use. This

memory area is reserved for use as expansion area for the bootstrap ROM as well as for testing purposes.

Customer code should not use this area. The contents of this Program ROM segment is defined by the

Bootstrap ROM source code in Appendix A, "Bootstrap ROM".

1.6.3 Bootstrap ROM

The 192-word Bootstrap ROM occupies locations $FF0000-$FF00BF. The bootstrap ROM is

factory-programmed to perform the bootstrap operation following hardware reset. The contents of the

Bootstrap ROM are defined by the Bootstrap ROM source code in Appendix A, "Bootstrap ROM".

1.6.4 Dynamic Memory Configuration Switching

The internal memory configuration is altered by re-mapping RAM modules from Y data memory into

program memory space and vice-versa. The contents of the switched RAM modules are preserved.

The memory can be dynamically switched from one configuration to another by changing the MS bit in

OMR. The address ranges that are directly affected by the switch operation are specified in Tab le 3-1 The

DSP56364 24-Bit Digital Signal Processor Users Manual, Rev. 2

1-8 Freescale Semiconductor

Page 27

Internal I/O Memory Map

memory switch can be accomplished provided that the affected address ranges are not being accessed

during the instruction cycle in which the switch operation takes place. Accordingly, the following

condition must be observed for trouble-free dynamic switching:

NOTE

No accesses (including instruction fetches) to or from the affected address

ranges in program and data memories are allowed during the switch cycle.

NOTE

The switch cycle actually occurs 3 instruction cycles after the instruction

that modifies the MS bit.

Any sequence that complies with the switch condition is valid. For example, if the program flow executes

in the address range that is not affected by the switch, the switch condition can be met very easily. In this

case a switch can be accomplished by just changing the MS bit in OMR in the regular program flow,

assuming no accesses to the affected address ranges of the data memory occur up to 3 instructions after the