Page 1

Freescale Semiconductor, Inc.

DSP56002

24-BIT

nc...

I

cale Semiconductor,

Frees

DIGITAL SIGNAL PROCESSOR

USER’S MANUAL

Motorola, Inc.

Semiconductor Products Sector

DSP Division

6501 William Cannon Drive, West

Austin, Texas 78735-8598

For More Information On This Product,

Go to: www.freescale.com

Page 2

Freescale Semiconductor, Inc.

TABLE OF CONTENTS

Paragraph Page

Number Title Number

SECTION 1

INTRODUCTION TO THE DSP56002

nc...

I

cale Semiconductor,

Frees

1.1 INTRODUCTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-3

1.2 FEATURES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-4

1.3 DSP56K CENTRAL PROCESSING UNIT OVERVIEW. . . . . . . . . . . . . . . . 1-4

1.4 MANUAL ORGANIZATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-5

SECTION 2

DSP56002 PIN DESCRIPTIONS

2.1 INTRODUCTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-3

2.2 SIGNAL DESCRIPTIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-3

2.2.1 Port A Address and Data Bus. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-3

2.2.1.1 Address (A0–A15) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-4

2.2.1.2 Data Bus (D0–D23) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-4

2.2.2 Port A Bus Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-4

2.2.2.1 Program Memory Select (PS

2.2.2.2 Data Memory Select (DS) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-5

2.2.2.3 X/Y Select (X/Y) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-5

2.2.2.4 Read Enable (RD) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-5

2.2.2.5 Write Enable (WR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-5

2.2.2.6 Bus Needed (BN) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-5

2.2.2.7 Bus Request (BR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-5

2.2.2.8 Bus Grant (BG) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-6

2.2.2.9 Bus Strobe (BS) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-6

2.2.2.10 Bus Wait (WT) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-6

2.2.3 Interrupt and Mode Control. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-6

2.2.3.1 Mode Select A/External Interrupt Request A

(MODA/IRQA)/STOP Recovery . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-6

2.2.3.2 Mode Select B/External Interrupt Request B (MODB/IRQB) . . . . . . .2-7

2.2.3.3 Mode Select C/Non-Maskable Interrupt Request (MODC/NMI) . . . .2-7

) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-4

MOTOROLA

For More Information On This Product,

TABLE OF CONTENTS

Go to: www.freescale.com

iii

Page 3

nc...

I

cale Semiconductor,

Frees

iv

Freescale Semiconductor, Inc.

Table of Contents (Continued)

Paragraph Page

Number Title Number

2.2.3.4 Reset (RESET) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-7

2.2.4 Power and Clock. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-8

2.2.4.1 Power (Vcc), Ground (GND) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-8

2.2.4.2 External Clock/Crystal Input (EXTAL) . . . . . . . . . . . . . . . . . . . . . . . .2-8

2.2.4.3 Crystal Output (XTAL) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-8

2.2.5 Host Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-8

2.2.5.1 Host Data Bus (H0–H7) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-8

2.2.5.2 Host Address (HA0–HA2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-9

2.2.5.3 Host Read/Write (HR/W) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-9

2.2.5.4 Host Enable (HEN) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-9

2.2.5.5 Host Request (HREQ) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-9

2.2.5.6 Host Acknowledge (HACK

2.2.6 Serial Communication Interface (SCI) . . . . . . . . . . . . . . . . . . . . . . . . . . 2-10

2.2.6.1 Receive Data (RXD) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-10

2.2.6.2 Transmit Data (TXD) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-10

2.2.6.3 SCI Serial Clock (SCLK) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-10

2.2.7 Synchronous Serial Interface (SSI) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-10

2.2.7.1 Serial Clock Zero (SC0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-10

2.2.7.2 Serial Control One (SC1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-11

2.2.7.3 Serial Control Two (SC2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-11

2.2.7.4 SSI Serial Clock (SCK) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-11

2.2.7.5 SSI Receive Data (SRD) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-11

2.2.7.6 SSI Transmit Data (STD) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-11

2.3 ON-CHIP EMULATION (OnCE) PINS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-11

2.3.1 Debug Serial Input/Chip Status 0 (DSI/OS0) . . . . . . . . . . . . . . . . . . . . . 2-11

2.3.2 Debug Serial Clock/Chip Status 1 (DSCK/OS1). . . . . . . . . . . . . . . . . . . 2-12

2.3.3 Debug Serial Output (DSO) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-12

2.3.4 Debug Request Input (DR). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-13

2.4 PLL PINS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-13

2.5 TIMER/EVENT COUNTER MODULE PIN. . . . . . . . . . . . . . . . . . . . . . . . . . 2-14

) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-9

SECTION 3

MEMORY MODULES

AND OPERATING MODES

3.1 MEMORY MODULES AND OPERATING MODES. . . . . . . . . . . . . . . . . . . 3-3

3.2 DSP56002 DATA AND PROGRAM MEMORY . . . . . . . . . . . . . . . . . . . . . . 3-3

3.2.1 Program Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-3

3.2.2 X Data Memory. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-4

For More Information On This Product,

TABLE OF CONTENTS MOTOROLA

Go to: www.freescale.com

Page 4

nc...

I

cale Semiconductor,

Frees

Freescale Semiconductor, Inc.

Table of Contents (Continued)

Paragraph Page

Number Title Number

3.2.3 Y Data Memory. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-4

3.3 DSP56002 OPERATING MODE REGISTER (OMR). . . . . . . . . . . . . . . . . . 3-4

3.3.1 Chip Operating Mode (Bits 0 and 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-6

3.3.2 Data ROM Enable (Bit 2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-6

3.3.3 Internal Y Memory Disable Bit (Bit 3) . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-6

3.3.4 Chip Operating Mode (Bit 4). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-7

3.3.5 Reserved (Bit 5) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-7

3.3.6 Stop Delay (Bit 6) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-7

3.3.7 Reserved OMR Bits (Bits 7–23) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-7

3.4 DSP56002 OPERATING MODES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-7

3.4.1 Single Chip Mode (Mode 0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-8

3.4.2 Bootstrap From EPROM (Mode 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-8

3.4.3 Normal Expanded Mode (Mode 2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-11

3.4.4 Development Mode (Mode 3). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-11

3.4.5 Reserved (Mode 4). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-11

3.4.6 Bootstrap From Host (Mode 5). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-11

3.4.7 Bootstrap From SCI (Mode 6). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-12

3.4.8 Reserved (Mode 7). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-12

3.5 DSP56002 INTERRUPT PRIORITY REGISTER. . . . . . . . . . . . . . . . . . . . . 3-12

3.6 DSP56002 PHASE-LOCKED LOOP (PLL) MULTIPLICATION FACTOR. . 3-13

SECTION 4

PORT A

4.1 INTRODUCTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-3

4.2 PORT A INTERFACE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-3

4.3 PORT A TIMING . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-9

4.4 PORT A WAIT STATES. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-13

4.5 BUS CONTROL REGISTER (BCR). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-13

4.6 BUS STROBE AND WAIT PINS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-15

4.7 BUS ARBITRATION AND SHARED MEMORY. . . . . . . . . . . . . . . . . . . . . . 4-16

4.7.1 Bus Arbitration Using Only BR and BG With Internal Control. . . . . . . . . 4-18

4.7.2 Bus Arbitration Using BN, BR, and BG With External Control . . . . . . . . 4-18

4.7.3 Bus Arbitration Using BR and BG, and WT and BS With No Overhead. 4-20

4.7.4 Signaling Using Semaphores . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-22

MOTOROLA

For More Information On This Product,

TABLE OF CONTENTS

Go to: www.freescale.com

v

Page 5

nc...

I

cale Semiconductor,

Frees

vi

Freescale Semiconductor, Inc.

Table of Contents (Continued)

Paragraph Page

Number Title Number

SECTION 5

PORT B

5.1 INTRODUCTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-3

5.2 GENERAL PURPOSE I/O CONFIGURATION . . . . . . . . . . . . . . . . . . . . . . 5-4

5.2.1 Programming General Purpose I/O . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-5

5.2.2 Port B General Purpose I/O Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-8

5.3 HOST INTERFACE (HI). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-10

5.3.1 Host Interface – DSP CPU Viewpoint. . . . . . . . . . . . . . . . . . . . . . . . . . . 5-11

5.3.2 Programming Model – DSP CPU Viewpoint. . . . . . . . . . . . . . . . . . . . . . 5-12

5.3.2.1 Host Control Register (HCR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-14

5.3.2.1.1 HCR Host Receive Interrupt Enable (HRIE) Bit 0 . . . . . . . . . . . .5-14

5.3.2.1.2 HCR Host Transmit Interrupt Enable (HTIE) Bit 1 . . . . . . . . . . . .5-14

5.3.2.1.3 HCR Host Command Interrupt Enable (HCIE) Bit 2 . . . . . . . . . .5-14

5.3.2.1.4 HCR Host Flag 2 (HF2) Bit 3 . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-14

5.3.2.1.5 HCR Host Flag 3 (HF3) Bit 4 . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-15

5.3.2.1.6 HCR Reserved Control (Bits 5, 6, and 7) . . . . . . . . . . . . . . . . . . .5-15

5.3.2.2 Host Status Register (HSR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-15

5.3.2.2.1 HSR Host Receive Data Full (HRDF) Bit 0 . . . . . . . . . . . . . . . . .5-15

5.3.2.2.2 HSR Host Transmit Data Empty (HTDE) Bit 1 . . . . . . . . . . . . . . .5-15

5.3.2.2.3 HSR Host Command Pending (HCP) Bit 2 . . . . . . . . . . . . . . . . .5-16

5.3.2.2.4 HSR Host Flag 0 (HF0) Bit 3 . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-16

5.3.2.2.5 HSR Host Flag 1 (HF1) Bit 4 . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-16

5.3.2.2.6 HSR Reserved Status (Bits 5 and 6) . . . . . . . . . . . . . . . . . . . . . .5-17

5.3.2.2.7 HSR DMA Status (DMA) Bit 7 . . . . . . . . . . . . . . . . . . . . . . . . . . .5-17

5.3.2.3 Host Receive Data Register (HRX) . . . . . . . . . . . . . . . . . . . . . . . . . .5-17

5.3.2.4 Host Transmit Data Register (HTX) . . . . . . . . . . . . . . . . . . . . . . . . .5-17

5.3.2.5 Register Contents After Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-17

5.3.2.6 Host Interface DSP CPU Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . .5-18

5.3.2.7 Host Port Usage Considerations – DSP Side . . . . . . . . . . . . . . . . . .5-18

5.3.3 Host Interface – Host Processor Viewpoint . . . . . . . . . . . . . . . . . . . . . . 5-19

5.3.3.1 Programming Model – Host Processor Viewpoint . . . . . . . . . . . . . . .5-20

5.3.3.2 Interrupt Control Register (ICR) . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-20

5.3.3.2.1 ICR Receive Request Enable (RREQ) Bit 0 . . . . . . . . . . . . . . . .5-22

5.3.3.2.2 ICR Transmit Request Enable (TREQ) Bit 1 . . . . . . . . . . . . . . . .5-22

5.3.3.2.3 ICR Reserved Bit (Bit 2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-23

5.3.3.2.4 ICR Host Flag 0 (HF0) Bit 3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-23

5.3.3.2.5 ICR Host Flag 1 (HF1) Bit 4 . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-23

5.3.3.2.6 ICR Host Mode Control (HM1 and HM0 bits) Bits 5 and 6 . . . . . .5-23

5.3.3.2.7 ICR Initialize Bit (INIT) Bit 7 . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-24

5.3.3.3 Command Vector Register (CVR) . . . . . . . . . . . . . . . . . . . . . . . . . . .5-26

For More Information On This Product,

TABLE OF CONTENTS MOTOROLA

Go to: www.freescale.com

Page 6

nc...

I

cale Semiconductor,

Frees

Freescale Semiconductor, Inc.

Table of Contents (Continued)

Paragraph Page

Number Title Number

5.3.3.3.1 CVR Host Vector (HV) Bits 0–5 . . . . . . . . . . . . . . . . . . . . . . . . . .5-26

5.3.3.3.2 CVR Reserved Bit (Bit 6) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-27

5.3.3.3.3 CVR Host Command Bit (HC) Bit 7 . . . . . . . . . . . . . . . . . . . . . . .5-27

5.3.3.4 Interrupt Status Register (ISR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-27

5.3.3.4.1 ISR Receive Data Register Full (RXDF) Bit 0 . . . . . . . . . . . . . . .5-27

5.3.3.4.2 ISR Transmit Data Register Empty (TXDE) Bit 1 . . . . . . . . . . . . .5-28

5.3.3.4.3 ISR Transmitter Ready (TRDY) Bit 2 . . . . . . . . . . . . . . . . . . . . . .5-28

5.3.3.4.4 ISR Host Flag 2 (HF2) Bit 3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-28

5.3.3.4.5 ISR Host Flag 3 (HF3) Bit 4 . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-28

5.3.3.4.6 ISR Reserved Bit (Bit 5) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-28

5.3.3.4.7 ISR DMA Status (DMA) Bit 6 . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-29

5.3.3.4.8 ISR Host Request (HREQ) Bit 7 . . . . . . . . . . . . . . . . . . . . . . . . .5-29

5.3.3.5 Interrupt Vector Register (IVR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-29

5.3.3.6 Receive Byte Registers (RXH, RXM, RXL) . . . . . . . . . . . . . . . . . . . .5-29

5.3.3.7 Transmit Byte Registers (TXH, TXM, TXL) . . . . . . . . . . . . . . . . . . . .5-30

5.3.3.8 Registers After Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-30

5.3.4 Host Interface Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-30

5.3.4.1 Host Data Bus(H0-H7) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-30

5.3.4.2 Host Address (HA0–HA2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-31

5.3.4.3 Host Read/Write (HR/W) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-32

5.3.4.4 Host Enable (HEN) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-32

5.3.4.5 Host Request (HREQ) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-32

5.3.4.6 Host Acknowledge (HACK) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-32

5.3.5 Servicing the Host Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-33

5.3.5.1 HI Host Processor Data Transfer . . . . . . . . . . . . . . . . . . . . . . . . . . .5-34

5.3.5.2 HI Interrupts Host Request (HREQ) . . . . . . . . . . . . . . . . . . . . . . . . .5-34

5.3.5.3 Polling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-35

5.3.5.4 Servicing Non-DMA Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-36

5.3.5.5 Servicing DMA Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-37

5.3.6 HI Application Examples . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-37

5.3.6.1 HI Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-38

5.3.6.2 Polling/Interrupt Controlled Data Transfer . . . . . . . . . . . . . . . . . . . . .5-38

5.3.6.2.1 Host to DSP - Data Transfer . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-40

5.3.6.2.2 Host to DSP – Command Vector . . . . . . . . . . . . . . . . . . . . . . . . .5-43

5.3.6.2.3 Host to DSP - Bootstrap Loading Using the HI . . . . . . . . . . . . . .5-50

5.3.6.2.4 DSP to Host Data Transfer . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-51

5.3.6.3 DMA Data Transfer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-54

5.3.6.3.1 Host To DSP Internal Processing . . . . . . . . . . . . . . . . . . . . . . . .5-56

5.3.6.3.2 Host to DSP DMA Procedure . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-57

5.3.6.3.3 DSP to Host Internal Processing . . . . . . . . . . . . . . . . . . . . . . . . .5-59

5.3.6.3.4 DSP to Host DMA Procedure . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-60

5.3.6.4 Example Circuits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-62

5.3.6.5 Host Port Usage Considerations – Host Side . . . . . . . . . . . . . . . . . .5-65

MOTOROLA

For More Information On This Product,

TABLE OF CONTENTS

Go to: www.freescale.com

vii

Page 7

nc...

I

cale Semiconductor,

Frees

Freescale Semiconductor, Inc.

Table of Contents (Continued)

Paragraph Page

Number Title Number

SECTION 6

PORT C

6.1 INTRODUCTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-3

6.2 GENERAL-PURPOSE I/O (PORT C) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-4

6.2.1 Programming General Purpose I/O . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-6

6.2.2 Port C General Purpose I/O Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-9

6.3 SERIAL COMMUNICATION INTERFACE (SCI) . . . . . . . . . . . . . . . . . . . . . 6-11

6.3.1 SCI I/O Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-11

6.3.1.1 Receive Data (RXD) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-12

6.3.1.2 Transmit Data (TXD) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-12

6.3.1.3 SCI Serial Clock (SCLK) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-12

6.3.2 SCI Programming Model . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-12

6.3.2.1 SCI Control Register (SCR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-14

6.3.2.1.1 SCR Word Select (WDS0, WDS1, WDS2) Bits 0, 1, and 2 . . . . .6-14

6.3.2.1.2 SCR SCI Shift Direction (SSFTD) Bit 3 . . . . . . . . . . . . . . . . . . . .6-18

6.3.2.1.3 SCR Send Break (SBK) Bit 4 . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-18

6.3.2.1.4 SCR Wakeup Mode Select (WAKE) Bit 5 . . . . . . . . . . . . . . . . . .6-18

6.3.2.1.5 SCR Receiver Wakeup Enable (RWU) Bit 6 . . . . . . . . . . . . . . . .6-18

6.3.2.1.6 SCR Wired-OR Mode Select (WOMS) Bit 7 . . . . . . . . . . . . . . . .6-19

6.3.2.1.7 SCR Receiver Enable (RE) Bit 8 . . . . . . . . . . . . . . . . . . . . . . . . .6-19

6.3.2.1.8 SCR Transmitter Enable (TE) Bit 9 . . . . . . . . . . . . . . . . . . . . . . .6-19

6.3.2.1.9 SCR Idle Line Interrupt Enable (ILIE) Bit 10 . . . . . . . . . . . . . . . .6-20

6.3.2.1.10 SCR SCI Receive Interrupt Enable (RIE) Bit 11 . . . . . . . . . . . . .6-21

6.3.2.1.11 SCR SCI Transmit Interrupt Enable (TIE) Bit 12 . . . . . . . . . . . . .6-21

6.3.2.1.12 SCR Timer Interrupt Enable (TMIE) Bit 13 . . . . . . . . . . . . . . . . .6-21

6.3.2.1.13 SCR SCI Timer Interrupt Rate (STIR) Bit 14 . . . . . . . . . . . . . . . .6-21

6.3.2.1.14 SCR SCI Clock Polarity (SCKP) Bit 15 . . . . . . . . . . . . . . . . . . . .6-22

6.3.2.2 SCI Status Register (SSR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-22

6.3.2.2.1 SSR Transmitter Empty (TRNE) Bit 0 . . . . . . . . . . . . . . . . . . . . .6-22

6.3.2.2.2 SSR Transmit Data Register Empty (TDRE) Bit 1 . . . . . . . . . . . .6-22

6.3.2.2.3 SSR Receive Data Register Full (RDRF) Bit 2 . . . . . . . . . . . . . .6-23

6.3.2.2.4 SSR Idle Line Flag (IDLE) Bit 3 . . . . . . . . . . . . . . . . . . . . . . . . . .6-23

6.3.2.2.5 SSR Overrun Error Flag (OR) Bit 4 . . . . . . . . . . . . . . . . . . . . . . .6-23

6.3.2.2.6 SSR Parity Error (PE) Bit 5 . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-23

6.3.2.2.7 SSR Framing Error Flag (FE) Bit 6 . . . . . . . . . . . . . . . . . . . . . . .6-24

6.3.2.2.8 SSR Received Bit 8 Address (R8) Bit 7 . . . . . . . . . . . . . . . . . . . .6-24

6.3.2.3 SCI Clock Control Register (SCCR) . . . . . . . . . . . . . . . . . . . . . . . . .6-24

6.3.2.3.1 SCCR Clock Divider (CD11–CD0) Bits 11–0 . . . . . . . . . . . . . . . .6-25

6.3.2.3.2 SCCR Clock Out Divider (COD) Bit 12 . . . . . . . . . . . . . . . . . . . .6-26

6.3.2.3.3 SCCR SCI Clock Prescaler (SCP) Bit 13 . . . . . . . . . . . . . . . . . . .6-26

viii

For More Information On This Product,

TABLE OF CONTENTS MOTOROLA

Go to: www.freescale.com

Page 8

nc...

I

cale Semiconductor,

Frees

Freescale Semiconductor, Inc.

Table of Contents (Continued)

Paragraph Page

Number Title Number

6.3.2.3.4 SCCR Receive Clock Mode Source Bit (RCM) Bit 14 . . . . . . . . .6-26

6.3.2.3.5 SCCR Transmit Clock Source Bit (TCM) Bit 15 . . . . . . . . . . . . . .6-26

6.3.2.4 SCI Data Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-26

6.3.2.4.1 SCI Receive Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-26

6.3.2.4.2 SCI Transmit Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-28

6.3.2.5 Preamble, Break, and Data Transmission Priority . . . . . . . . . . . . . .6-30

6.3.3 Register Contents After Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-31

6.3.4 SCI Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-31

6.3.5 SCI Exceptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-37

6.3.6 Synchronous Data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-39

6.3.7 Asynchronous Data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-44

6.3.7.1 Asynchronous Data Reception . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-45

6.3.7.2 Asynchronous Data Transmission . . . . . . . . . . . . . . . . . . . . . . . . . . .6-48

6.3.8 Multidrop. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-55

6.3.8.1 Transmitting Data and Address Characters . . . . . . . . . . . . . . . . . . .6-57

6.3.8.2 Wired-OR Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-57

6.3.8.3 Idle Line Wakeup . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-57

6.3.8.4 Address Mode Wakeup . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-61

6.3.8.5 Multidrop Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-61

6.3.9 SCI Timer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-68

6.3.10 Bootstrap Loading Through the SCI (Operating Mode 6). . . . . . . . . . . . 6-71

6.3.11 Example Circuits. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-74

6.4 SYNCHRONOUS SERIAL INTERFACE (SSI) . . . . . . . . . . . . . . . . . . . . . . 6-76

6.4.1 SSI Data and Control Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-78

6.4.1.1 Serial Transmit Data Pin (STD) . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-78

6.4.1.2 Serial Receive Data Pin (SRD) . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-80

6.4.1.3 Serial Clock (SCK) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-80

6.4.1.4 Serial Control Pin (SC0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-82

6.4.1.5 Serial Control Pin (SC1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-82

6.4.1.6 Serial Control Pin (SC2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-83

6.4.2 SSI Programming Model. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-83

6.4.2.1 SSI Control Register A (CRA) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-87

6.4.2.1.1 CRA Prescale Modulus Select (PM7–PM0) Bits 0–7 . . . . . . . . . .6-87

6.4.2.1.2 CRA Frame Rate Divider Control (DC4–DC0) Bits 8–12 . . . . . . .6-87

6.4.2.1.3 CRA Word Length Control (WL0, WL1) Bits 13 and 14 . . . . . . . .6-87

6.4.2.1.4 CRA Prescaler Range (PSR) Bit 15 . . . . . . . . . . . . . . . . . . . . . . .6-88

6.4.2.2 SSI Control Register B (CRB) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-88

6.4.2.2.1 CRB Serial Output Flag 0 (OF0) Bit 0 . . . . . . . . . . . . . . . . . . . . .6-88

6.4.2.2.2 CRB Serial Output Flag 1 (OF1) Bit 1 . . . . . . . . . . . . . . . . . . . . .6-88

6.4.2.2.3 CRB Serial Control 0 Direction (SCD0) Bit 2 . . . . . . . . . . . . . . . .6-89

6.4.2.2.4 CRB Serial Control 1 Direction (SCD1) Bit 3 . . . . . . . . . . . . . . . .6-89

6.4.2.2.5 CRB Serial Control 2 Direction (SCD2) Bit 4 . . . . . . . . . . . . . . . .6-89

MOTOROLA

For More Information On This Product,

TABLE OF CONTENTS

Go to: www.freescale.com

ix

Page 9

nc...

I

cale Semiconductor,

Frees

x

Freescale Semiconductor, Inc.

Table of Contents (Continued)

Paragraph Page

Number Title Number

6.4.2.2.6 CRB Clock Source Direction (SCKD) Bit 5 . . . . . . . . . . . . . . . . .6-89

6.4.2.2.7 CRB Shift Direction (SHFD) Bit 6 . . . . . . . . . . . . . . . . . . . . . . . . .6-91

6.4.2.2.8 CRB Frame Sync Length (FSL0 and FSL1) Bits 7 and 8 . . . . . .6-91

6.4.2.2.9 CRB Sync/Async (SYN) Bit 9 . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-91

6.4.2.2.10 CRB Gated Clock Control (GCK) Bit 10 . . . . . . . . . . . . . . . . . . . .6-91

6.4.2.2.11 CRB SSI Mode Select (MOD) Bit 11 . . . . . . . . . . . . . . . . . . . . . .6-92

6.4.2.2.12 CRB SSI Transmit Enable (TE) Bit 12 . . . . . . . . . . . . . . . . . . . . .6-92

6.4.2.2.13 CRB SSI Receive Enable (RE) Bit 13 . . . . . . . . . . . . . . . . . . . . .6-92

6.4.2.2.14 CRB SSI Transmit Interrupt Enable (TIE) Bit 14 . . . . . . . . . . . . .6-93

6.4.2.2.15 CRB SSI Receive Interrupt Enable (RIE) Bit 15 . . . . . . . . . . . . .6-93

6.4.2.3 SSI Status Register (SSISR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-94

6.4.2.3.1 SSISR Serial Input Flag 0 (IF0) Bit 0 . . . . . . . . . . . . . . . . . . . . . .6-94

6.4.2.3.2 SSISR Serial Input Flag 1 (IF1) Bit 1 . . . . . . . . . . . . . . . . . . . . . .6-94

6.4.2.3.3 SSISR Transmit Frame Sync Flag (TFS) Bit 2 . . . . . . . . . . . . . .6-94

6.4.2.3.4 SSISR Receive Frame Sync Flag (RFS) Bit 3 . . . . . . . . . . . . . . .6-95

6.4.2.3.5 SSISR Transmitter Underrun Error Flag (TUE) Bit 4 . . . . . . . . . .6-96

6.4.2.3.6 SSISR Receiver Overrun Error Flag (ROE) Bit 5 . . . . . . . . . . . . .6-96

6.4.2.3.7 SSISR SSI Transmit Data Register Empty (TDE) Bit 6 . . . . . . . .6-97

6.4.2.3.8 SSISR SSI Receive Data Register Full (RDF) Bit 7 . . . . . . . . . . .6-97

6.4.2.3.9 SSI Receive Shift Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-97

6.4.2.3.10 SSI Receive Data Register (RX) . . . . . . . . . . . . . . . . . . . . . . . . .6-97

6.4.2.3.11 SSI Transmit Shift Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-97

6.4.2.3.12 SSI Transmit Data Register (TX) . . . . . . . . . . . . . . . . . . . . . . . . .6-100

6.4.2.3.13 Time Slot Register (TSR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-100

6.4.3 Operational Modes and Pin Definitions . . . . . . . . . . . . . . . . . . . . . . . . . 6-100

6.4.4 Registers After Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-100

6.4.5 SSI Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-104

6.4.6 SSI Exceptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-109

6.4.7 Operating Modes – Normal, Network, and On-Demand. . . . . . . . . . . . . 6-112

6.4.7.1 Data/Operation Formats . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-112

6.4.7.1.1 Normal/Network Mode Selection . . . . . . . . . . . . . . . . . . . . . . . . .6-112

6.4.7.1.2 Continuous/Gated Clock Selection . . . . . . . . . . . . . . . . . . . . . . .6-113

6.4.7.1.3 Synchronous/Asynchronous Operating Modes . . . . . . . . . . . . . .6-113

6.4.7.1.4 Frame Sync Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-123

6.4.7.1.5 Shift Direction Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-127

6.4.7.2 Normal Mode Examples . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-127

6.4.7.2.1 Normal Mode Transmit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-130

6.4.7.2.2 Normal Mode Receive . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-133

6.4.7.3 Network Mode Examples . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-135

6.4.7.3.1 Network Mode Transmit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-140

6.4.7.3.2 Network Mode Receive . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-144

6.4.7.4 On-Demand Mode Examples . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-145

For More Information On This Product,

TABLE OF CONTENTS MOTOROLA

Go to: www.freescale.com

Page 10

Freescale Semiconductor, Inc.

Table of Contents (Continued)

Paragraph Page

Number Title Number

6.4.7.4.1 On-Demand Mode – Continuous Clock . . . . . . . . . . . . . . . . . . . .6-148

6.4.7.4.2 On-Demand Mode – Gated Clock . . . . . . . . . . . . . . . . . . . . . . . .6-148

6.4.8 Flags. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-153

6.4.9 Example Circuits. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-157

SECTION 7

DSP56002 TIMER AND

EVENT COUNTER

nc...

I

cale Semiconductor,

Frees

7.1 INTRODUCTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-3

7.2 TIMER/EVENT COUNTER BLOCK DIAGRAM. . . . . . . . . . . . . . . . . . . . . . 7-3

7.3 TIMER COUNT REGISTER (TCR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-4

7.4 TIMER CONTROL/STATUS REGISTER (TCSR) . . . . . . . . . . . . . . . . . . . . 7-5

7.4.1 Timer Enable (TE) Bit 0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-5

7.4.2 Timer Interrupt Enable (TIE) Bit 1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-5

7.4.3 Inverter (INV) Bit 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-5

7.4.4 Timer Control (TC0-TC2) Bits 3-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-6

7.4.5 General Purpose I/O (GPIO) Bit 6 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-6

7.4.6 Timer Status (TS) Bit 7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-7

7.4.7 Direction (DIR) Bit 8 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-7

7.4.8 Data Input (DI) Bit 9 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-7

7.4.9 Data Output (DO) Bit 10 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-7

7.4.10 TCSR Reserved bits (Bits 11-23) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-7

7.5 TIMER/EVENT COUNTER MODES OF OPERATION . . . . . . . . . . . . . . . . 7-7

7.5.1 Timer Mode 0

(Standard Timer Mode, Internal Clock, No Timer Output) . . . . . . . . . . . 7-7

7.5.2 Timer Mode 1

(Standard Timer Mode, Internal Clock, Output Pulse Enabled) . . . . . . . 7-8

7.5.3 Timer Mode 2

(Standard Timer Mode, Internal Clock, Output Toggle Enabled) . . . . . . 7-10

7.5.4 Timer Mode 4 (Pulse Width Measurement Mode) . . . . . . . . . . . . . . . . . 7-11

7.5.5 Timer Mode 5 (Period Measurement Mode). . . . . . . . . . . . . . . . . . . . . . 7-12

7.5.6 Timer Mode 6 (Standard Time Counter Mode, External Clock) . . . . . . . 7-13

7.5.7 Timer Mode 7 (Standard Timer Mode, External Clock) . . . . . . . . . . . . . 7-15

7.6 TIMER/EVENT COUNTER BEHAVIOR DURING WAIT and STOP . . . . . . 7-16

7.7 OPERATING CONSIDERATIONS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-17

7.8 SOFTWARE EXAMPLES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-18

7.8.1 General Purpose I/O Input . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-18

7.8.2 General Purpose I/O Output. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-19

MOTOROLA

For More Information On This Product,

TABLE OF CONTENTS

Go to: www.freescale.com

xi

Page 11

Freescale Semiconductor, Inc.

Table of Contents (Continued)

Paragraph Page

Number Title Number

7.8.3 Timer Mode 0, Input Clock, GPIO Output, and No Timer Output. . . . . . 7-20

7.8.4 Pulse Width Measurement Mode (Timer Mode 4) . . . . . . . . . . . . . . . . . 7-21

7.8.5 Period Measurement Mode (Timer Mode 5). . . . . . . . . . . . . . . . . . . . . . 7-22

APPENDIX A

BOOTSTRAP

AND

ROM CODE

nc...

I

cale Semiconductor,

Frees

A.1 INTRODUCTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-3

APPENDIX B

PROGRAMMING SHEETS

B.1 PERIPHERAL ADDRESSES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-3

B.2 INTERRUPT VECTOR ADDRESSES . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-4

B.3 INSTRUCTIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-5

B.4 CENTRAL PROCESSOR . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-10

B.5 GP I/O . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-14

B.6 HOST . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-16

B.7 SCI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-21

B.8 SSI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-24

B.9 TIMER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-27

xii

For More Information On This Product,

TABLE OF CONTENTS MOTOROLA

Go to: www.freescale.com

Page 12

Freescale Semiconductor, Inc.

LIST of FIGURES

Figure Page

Number Title Number

nc...

I

cale Semiconductor,

Frees

1-1 DSP56002 Technical Literature . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-3

SECTION 1

1-2 DSP56002 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-6

SECTION 2

2-1 DSP56002 Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-3

SECTION 3

3-1 DSP56002 Memory Maps . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-5

3-2 OMR Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-6

3-3 Port A Bootstrap Circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-9

3-4 DSP56002 Interrupt Priority Register (IPR) . . . . . . . . . . . . . . . . . . . . . . . . . 3-13

SECTION 4

4-1 Port A Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-4

4-2 External Program Space . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-5

4-3 External X and Y Data Space . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-6

4-4 Memory Segmentation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-7

4-5 Port A Bootstrap ROM with X and Y RAM . . . . . . . . . . . . . . . . . . . . . . . . . . 4-8

4-6 Port A Bus Operation with No Wait States . . . . . . . . . . . . . . . . . . . . . . . . . . 4-9

4-7 Port A Bus Operation with Two Wait States . . . . . . . . . . . . . . . . . . . . . . . . . 4-10

4-8 Mixed-Speed Expanded System . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-12

4-9 Bus Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-14

4-10 Bus Strobe/Wait Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-15

4-11 Bus Request/Bus Grant Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-17

4-12 Bus Arbitration Using Only BR and BG with Internal Control . . . . . . . . . . . . 4-19

4-13 Two DSPs with External Bus Arbitration Timing . . . . . . . . . . . . . . . . . . . . . . 4-19

4-14 Bus Arbitration Using BN, BR, and BG with External Control . . . . . . . . . . . . 4-20

4-15 Bus Arbitration Using BR and BG,

and WT and BS with No Overhead . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-21

4-16 Two DSPs with External Bus Arbitration Timing . . . . . . . . . . . . . . . . . . . . . . 4-22

4-17 Signaling Using Semaphores . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-23

SECTION 5

5-1 Port B Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-3

5-2 Parallel Port B Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-4

5-3 Parallel Port B Pinout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-5

5-4 Port B I/O Pin Control Logic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-6

5-5 On-Chip Peripheral Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-7

5-6 Instructions to Write/Read Parallel Data with Port B . . . . . . . . . . . . . . . . . . . 5-8

MOTOROLA

Revision 2.1 DSP56004 DESIGN SPECIFICATION xiii

For More Information On This Product,

LIST of FIGURES

Go to: www.freescale.com

xiii

Page 13

nc...

I

cale Semiconductor,

Frees

Freescale Semiconductor, Inc.

List of Figures (Continued)

Figure Page

Number Title Number

5-7 I/O Port B Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-9

5-8 HI Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-12

5-9 Host Interface Programming Model – DSP Viewpoint . . . . . . . . . . . . . . . . . 5-13

5-10 Host Flag Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-16

5-11 HSR–HCR Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-19

5-12 Host Processor Programming Model – Host Side . . . . . . . . . . . . . . . . . . . . . 5-21

5-13 HI Register Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-22

5-14 Command Vector Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-26

5-15 Host Processor Transfer Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-33

5-16 Interrupt Vector Register Read Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-34

5-17 HI Interrupt Structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-36

5-18 DMA Transfer Logic and Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-37

5-19 HI Initialization Flowchart . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-38

5-20 HI Initialization–DSP Side . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-39

5-21a HI Configuration–Host Side . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-40

5-21b HI Initialization–Host Side, Polling Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-40

5-21c HI Initialization–Host Side, Interrupt Mode . . . . . . . . . . . . . . . . . . . . . . . . . . 5-41

5-21d HI Initialization–Host Side, DMA Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-42

5-22 Host Mode and INIT Bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-43

5-23 Bits Used for Host-to-DSP Transfer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-44

5-24 Data Transfer from Host to DSP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-45

5-25 Receive Data from Host–Main Program . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-46

5-26 Receive Data from Host Interrupt Routine . . . . . . . . . . . . . . . . . . . . . . . . . . 5-46

5-27 HI Exception Vector Locations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-47

5-28 Host Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-48

5-29 Bootstrap Using the HI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-49

5-30 Transmit/Receive Byte Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-50

5-31 Bootstrap Code Fragment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-51

5-32 Bits Used for DSP to Host Transfer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-52

5-33 Data Transfer from DSP to Host . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-53

5-34 Main Program - Transmit 24-Bit Data to Host . . . . . . . . . . . . . . . . . . . . . . . . 5-54

5-35 Transmit to HI Routine . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-54

5-36 HI Hardware–DMA Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-55

5-37 DMA Transfer and Host Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-56

5-38 Host Bits with TREQ and RREQ . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-57

5-39 Host-to-DSP DMA Procedure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-58

5-40 DSP to Host DMA Procedure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-61

5-41 MC68HC11 to DSP56002 Host Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-62

5-42 MC68000 to DSP56002 Host Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-63

5-43 Multi-DSP Network Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-64

xiv

For More Information On This Product,

LIST of FIGURES MOTOROLA

Go to: www.freescale.com

Page 14

Freescale Semiconductor, Inc.

List of Figures (Continued)

Figure Page

Number Title Number

nc...

I

cale Semiconductor,

Frees

6-1 Port C Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-3

SECTION 6

6-2 Port C GPIO Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-4

6-3 Port C GPIO Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-5

6-4 Port C I/O Pin Control Logic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-6

6-5 On-Chip Peripheral Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-7

6-6 Write/Read Parallel Data with Port C . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-8

6-7 I/O Port C Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-9

6-8 SCI Programming Model – Control and Status Registers . . . . . . . . . . . . . . . 6-13

6-9 SCI Programming Model . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-14

6-10 Serial Formats (Sheet 1 of 2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-16

6-11 16 x Serial Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-25

6-12 SCI Baud Rate Generator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-27

6-13 Data Packing and Unpacking . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-29

6-14 SCI Initialization Procedure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-33

6-15 SCI General Initialization Detail – Step 2 (Sheet 1 of 2) . . . . . . . . . . . . . . . . 6-34

6-16 SCI Exception Vector Locations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-38

6-17 Synchronous Master . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-40

6-18 Synchronous Slave . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-42

6-19 Synchronous Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-43

6-20 SCI Synchronous Transmit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-44

6-21 SCI Synchronous Receive . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-45

6-22 Asynchronous SCI Receiver Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-46

6-23 SCI Character Reception . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-47

6-24 SCI Character Reception with Exception . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-49

6-25 Asynchronous SCI Transmitter Initialization . . . . . . . . . . . . . . . . . . . . . . . . . 6-50

6-26 Asynchronous SCI Character Transmission . . . . . . . . . . . . . . . . . . . . . . . . . 6-51

6-27 Transmitting Marks and Spaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-52

6-28 SCI Asynchronous Transmit/Receive Example (Sheet 1 of 3) . . . . . . . . . . . 6-53

6-29 11-Bit Multidrop Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-56

6-30 Transmitting Data and Address Characters . . . . . . . . . . . . . . . . . . . . . . . . . 6-58

6-31 Wired-OR Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-59

6-32 Idle Line Wakeup . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-60

6-33 Address Mode Wakeup . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-62

6-34 Multidrop Transmit Receive Example (Sheet 1 of 4) . . . . . . . . . . . . . . . . . . . 6-64

6-35 SCI Timer Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-69

6-36 SCI Timer Example (Sheet 1 of 2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-70

6-37 DSP56002 Bootstrap Example - Mode 6 . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-72

6-38 Bootstrap Code Fragment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-73

6-39 Synchronous Mode Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-74

MOTOROLA

For More Information On This Product,

LIST of FIGURES

Go to: www.freescale.com

xv

Page 15

nc...

I

cale Semiconductor,

Frees

Freescale Semiconductor, Inc.

List of Figures (Continued)

Figure Page

Number Title Number

6-40 Master-Slave System Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-75

6-41 Multimaster System Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-75

6-42 SSI Clock Generator Functional Block Diagram . . . . . . . . . . . . . . . . . . . . . . 6-80

6-43 SSI Frame Sync Generator Functional Block Diagram . . . . . . . . . . . . . . . . . 6-81

6-44 SSI Programming Model — Control and Status Registers . . . . . . . . . . . . . . 6-84

6-45 SSI Programming Model (Sheet 1 of 2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-85

6-46 Serial Control, Direction Bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-90

6-47 Receive Data Path . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-98

6-48 Transmit Data Path . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-99

6-49 SSI Initialization Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-104

6-50 SSI CRA Initialization Procedure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-105

6-51 SSI CRB Initialization Procedure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-106

6-52 SSI Initialization Procedure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-107

6-53 SSI Exception Vector Locations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-110

6-54 SSI Exceptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-111

6-55 CRB MOD Bit Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-114

6-56 Normal Mode, External Frame Sync (8 Bit, 1 Word in Frame) . . . . . . . . . . . 6-115

6-57 Network Mode, External Frame Sync (8 Bit, 2 Words in Frame) . . . . . . . . . 6-115

6-58 CRB GCK Bit Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-116

6-59 Continuous Clock Timing Diagram (8-Bit Example) . . . . . . . . . . . . . . . . . . . 6-117

6-60 Internally Generated Clock Timing (8-Bit Example) . . . . . . . . . . . . . . . . . . . 6-118

6-61 Externally Generated Gated Clock Timing (8-Bit Example) . . . . . . . . . . . . . 6-119

6-62 Synchronous Communication . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-120

6-63 CRB SYN Bit Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-121

6-64 Gated Clock — Synchronous Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-122

6-65 Gated Clock — Asynchronous Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-122

6-66 Continuous Clock — Synchronous Operation . . . . . . . . . . . . . . . . . . . . . . . . 6-122

6-67 Continuous Clock — Asynchronous Operation . . . . . . . . . . . . . . . . . . . . . . . 6-122

6-68 CRB FSL0 and FSL1 Bit Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-124

6-69 Normal Mode Initialization for FLS1=0 and FSL0=0 . . . . . . . . . . . . . . . . . . . 6-125

6-70 Normal Mode Initialization for FSL1=1 and FSL0=0 . . . . . . . . . . . . . . . . . . . 6-126

6-71 CRB SHFD Bit Operation (Sheet 1 of 2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-128

6-72 Normal Mode Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-130

6-73 Normal Mode Transmit Example (Sheet 1 of 2) . . . . . . . . . . . . . . . . . . . . . . 6-132

6-74 Normal Mode Receive Example (Sheet 1 of 2) . . . . . . . . . . . . . . . . . . . . . . . 6-134

6-75 Network Mode Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-136

6-76 TDM Network Software Flowchart . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-137

6-77 Network Mode Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-139

6-78 Network Mode Transmit Example Program (Sheet 1 of 2) . . . . . . . . . . . . . . 6-141

6-79 Network Mode Receive Example Program (Sheet 1 of 2) . . . . . . . . . . . . . . 6-143

xvi

For More Information On This Product,

LIST of FIGURES MOTOROLA

Go to: www.freescale.com

Page 16

nc...

I

cale Semiconductor,

Frees

Freescale Semiconductor, Inc.

List of Figures (Continued)

Figure Page

Number Title Number

6-80 On Demand Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-146

6-81 On-Demand Data-Driven Network Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-147

6-82 Clock Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-148

6-83 SPI Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-149

6-84 On-Demand Mode Example — Hardware Configuration . . . . . . . . . . . . . . . 6-150

6-85 On-Demand Mode Transmit Example Program (Sheet 1 of 2) . . . . . . . . . . . 6-150

6-86 On-Demand Mode Receive Example Program . . . . . . . . . . . . . . . . . . . . . . . 6-152

6-87 Output Flag Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-154

6-88 Output Flag Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-155

6-89 Output Flag Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-156

6-90 Input Flags . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-157

6-91 SSI Cascaded Multi-DSP System . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-157

6-92 SSI TDM Parallel DSP Network . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-159

6-93 SSI TDM Connected Parallel Processing Array . . . . . . . . . . . . . . . . . . . . . . 6-160

6-94 SSI TDM Serial/Parallel Processing Array . . . . . . . . . . . . . . . . . . . . . . . . . . 6-161

6-95 SSI Parallel Processing — Nearest Neighbor Array . . . . . . . . . . . . . . . . . . . 6-162

6-96 SSI TDM Bus DSP Network . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-163

6-97 SSI TDM Master-Slave DSP Network . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-164

7-1 Timer/Event Counter Module Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . 7-3

7-2 Timer/Event Counter Programming Model . . . . . . . . . . . . . . . . . . . . . . . . . . 7-4

7-3 Standard Timer Mode (Mode 0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-8

7-4 Timer/Event Counter Disable . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-9

7-5 Standard Timer Mode, Internal Clock, Output Pulse Enabled (INV=0) . . . . . 7-10

7-6 Standard Timer Mode, Internal Clock, Output Pulse Enabled (INV=1) . . . . . 7-11

7-7 Standard Timer Mode, Internal Clock, Output Toggle Enable . . . . . . . . . . . 7-12

7-8 Pulse Width Measurement Mode (INV=0) . . . . . . . . . . . . . . . . . . . . . . . . . . 7-13

7-9 Pulse Width Measurement Mode (INV=1) . . . . . . . . . . . . . . . . . . . . . . . . . . 7-14

7-10 Period Measurement Mode (INV=0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-15

7-11 Period Measurement Mode (INV=1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-16

7-12 Standard Time Counter Mode, External Clock (INV=0) . . . . . . . . . . . . . . . . 7-17

7-13 Standard Timer Mode, External Clock (INV=1) . . . . . . . . . . . . . . . . . . . . . . . 7-18

7-14 Standard Timer Mode, External Clock (INV=0) . . . . . . . . . . . . . . . . . . . . . . . 7-19

7-15 Standard Timer Mode, External Clock (INV=1) . . . . . . . . . . . . . . . . . . . . . . . 7-20

A-1 DSP56002 Bootstrap Program (Sheet 1 of 3) . . . . . . . . . . . . . . . . . . . . . . . . A-4

B-1 On-chip Peripheral Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-3

B-2 Status Register (SR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-10

B-3 Bus Control Register (BCR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-10

B-4 Interrupt Priority Register (IPR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-11

SECTION 7

AAPPENDIX A

BAPPENDIX B

MOTOROLA

For More Information On This Product,

LIST of FIGURES

Go to: www.freescale.com

xvii

Page 17

nc...

I

cale Semiconductor,

Frees

Freescale Semiconductor, Inc.

List of Figures (Continued)

Figure Page

Number Title Number

B-5 Operating Mode Register (OMR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-12

B-6 PLL Control Register (PCTL) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-13

B-7 Port B Control Register (PBC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-14

B-8 Port B Data Direction Register (PBDDR) . . . . . . . . . . . . . . . . . . . . . . . . . . . B-14

B-9 Port B Data Register (PBD) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-14

B-10 Port C Control Register (PCC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-15

B-11 Port C Data Direction Register (PCDDR) . . . . . . . . . . . . . . . . . . . . . . . . . . . B-15

B-12 Port C Data Register (PCD) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-15

B-13 Port B Control Register (PBC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-16

B-14 Host Control Register (HCR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-16

B-15 Host Transmit Data Register (HTX) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-17

B-16 Host Receive Data Register (HRX) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-17

B-17 Host Status Register (HSR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-17

B-18 Command Vector Register (CVR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-18

B-19 Interrupt Control Register (ICR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-18

B-20 Interrupt Status Register (ISR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-19

B-21 Interrupt Vector Register (IVR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-19

B-22 Receive Byte Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-20

B-23 Transmit Byte Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-20

B-24 Port C Control Register (PCC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-21

B-25 SCI Control Register (SCR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-21

B-26 SCI Clock Control Register (SCCR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-22

B-27 SCI Status Register (SSR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-22

B-28 SCI Receive Data Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-23

B-29 SCI Transmit Data Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-23

B-30 SSI Control Register (PCC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-24

B-31 SSI Control Register A (CRA) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-24

B-32 SSI Control Register B (CRB) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-25

B-33 SSI Status Register (SSISR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-26

B-34 Timer Control and Status Register (TCSR) . . . . . . . . . . . . . . . . . . . . . . . . . . B-27

B-35 Timer Count Register (TCR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-27

xviii

For More Information On This Product,

LIST of FIGURES MOTOROLA

Go to: www.freescale.com

Page 18

Freescale Semiconductor, Inc.

List of Figures (Continued)

Figure Page

Number Title Number

nc...

I

cale Semiconductor,

Frees

MOTOROLA

For More Information On This Product,

LIST of FIGURES

Go to: www.freescale.com

xix

Page 19

Freescale Semiconductor, Inc.

List of Tables (Continued)

Table Page

Number Title Number

SECTION 1SECTION 1

SECTION 2SECTION 2

SECTION 3SECTION 3

SECTION 4SECTION 4

SECTION 5SECTION 5

SECTION 6SECTION 6

SECTION 7SECTION 7

APPENDIX A A-1

nc...

I

cale Semiconductor,

Frees

2-1 Program and Data Memory Select Encoding . . . . . . . . . . . . . . . . . . . . . . . .2-4

3-1 Memory Mode Bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-7

3-2 DSP56002 Operating Mode Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-8

3-3 Organization of EPROM Data Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-10

3-4 Interrupt Vectors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-14

3-5 Exception Priorities Within an IPL. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-15

4-1 Program and Data Memory Select Encoding . . . . . . . . . . . . . . . . . . . . . . . .4-7

4-2 Wait State Control. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-13

4-3 BR and BG During WAIT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-17

5-1 Host Registers after Reset–DSP CPU Side . . . . . . . . . . . . . . . . . . . . . . . . .5-18

5-2 HREQ Pin Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-23

5-3 Host Mode Bit Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-24

5-4 HREQ Pin Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-25

5-5 Host Registers after Reset (Host Side). . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-31

5-6 Port B Pin Definitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-32

6-1 Word Formats. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-15

6-2 SCI Registers after Reset. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-32

6-3a Asynchronous SCI Bit Rates for a 40-MHz Crystal. . . . . . . . . . . . . . . . . . . .6-36

6-3b Frequencies for Exact Asynchronous SCI Bit Rates. . . . . . . . . . . . . . . . . . .6-36

6-4a Synchronous SCI Bit Rates for a 32.768-MHz Crystal . . . . . . . . . . . . . . . . .6-37

6-4b Frequencies for Exact Synchronous SCI Bit Rates . . . . . . . . . . . . . . . . . . .6-37

6-5 Definition of SC0, SC1, SC2, and SCK. . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-79

6-6 SSI Clock Sources, Inputs, and Outputs. . . . . . . . . . . . . . . . . . . . . . . . . . . .6-79

6-7 SSI Operation: Flag 0 and Rx Clock. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-82

6-8 SSI Operation: Flag 1 and Rx Frame Sync. . . . . . . . . . . . . . . . . . . . . . . . . .6-83

6-9 SSI Operation: Tx and Rx Frame Sync. . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-83

6-10 Number of Bits/Word. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-87

6-11 Frame Sync Length. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-91

6-12 Mode and Pin Definition Table – Continuous Clock . . . . . . . . . . . . . . . . . . .6-101

6-13 Mode and Pin Definition Table – Gated Clock . . . . . . . . . . . . . . . . . . . . . . .6-102

6-14 SSI Registers After Reset. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-103

6-15aSSI Bit Rates for a 40-MHz Crystal. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-108

6-15bSSI Bit Rates for a 39.936-MHz Crystal . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-108

6-16 Crystal Frequencies Required for Codecs . . . . . . . . . . . . . . . . . . . . . . . . . .6-108

6-17 SSI Operating Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-112

7-1 Timer/Event Counter Control Bits. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-6

MOTOROLA

For More Information On This Product,

LIST of TABLES

Go to: www.freescale.com

xix

Page 20

xx

Freescale Semiconductor, Inc.

List of Tables (Continued)

Table Page

Number Title Number

APPENDIX B B-1

B-1 Interrupts Starting Addresses and Sources . . . . . . . . . . . . . . . . . . . . . . . . .B-4

B-2 Instruction Set Summary — Sheet 1 of 5 . . . . . . . . . . . . . . . . . . . . . . . . . . .B-5

nc...

I

cale Semiconductor,

Frees

For More Information On This Product,

LIST of TABLES MOTOROLA

Go to: www.freescale.com

Page 21

Freescale Semiconductor, Inc.

DSP56002 User’s Manual Trouble Report

DSP Applications Fax Number — (512) 891-4665

Dr. BuB Bulletin Board —891-DSP3 (8 data bits, no parity, 1 stop)

We welcome your comments and suggestions. They help us provide you with better product documentation. Please send your suggestions/corrections to the Fax number or Email

address above or mail this completed form to:

Motorola Inc.

6501 Wm. Cannon Drive West

Austin, Texas 78735-8598

Attn: DSP Applications/Documentation

Mail Drop: OE314

nc...

I

cale Semiconductor,

Frees

1. Did you find errors in the manual? Please give page number and a description of

each error.

For More Information On This Product,

Go to: www.freescale.com

Page 22

Freescale Semiconductor, Inc.

DSP56002 User’s Manual Trouble Report

2. Did you find the manual clear and easy to use? Please comment on specific

sections that you feel need improvement.

nc...

I

cale Semiconductor,

Frees

3. What sections of this manual do you consider most important/least important?

For More Information On This Product,

Go to: www.freescale.com

Page 23

MOTOROLA

Freescale Semiconductor, Inc.

Order this document by

DSP56002UMAD/AD

SEMICONDUCTOR

TECHNICAL DATA

DSP56002

Addendum to

24-bit Digital Signal Processor

User’s Manual

This document, containing changes, additional features, further explanations, and clarifications, is

a supplement to the original document:

DSP56002UM/AD Rev. 1 User’s Manual DSP56002

24-bit Digital Signal Processor

Change the following:

nc...

I

Page 1-4, Section 1.2 - Insert after first group of bullets “PLL based clocking with wide input frequency range, wide range frequency multiplication (1 to 4096) and power saving clock divider

(2i, i=0,...,15) to reduce clock noise”

Page 1-4, Section 1.2 - Replace “24 General Purpose I/O Pins” with “25 General Purpose I/O pins”

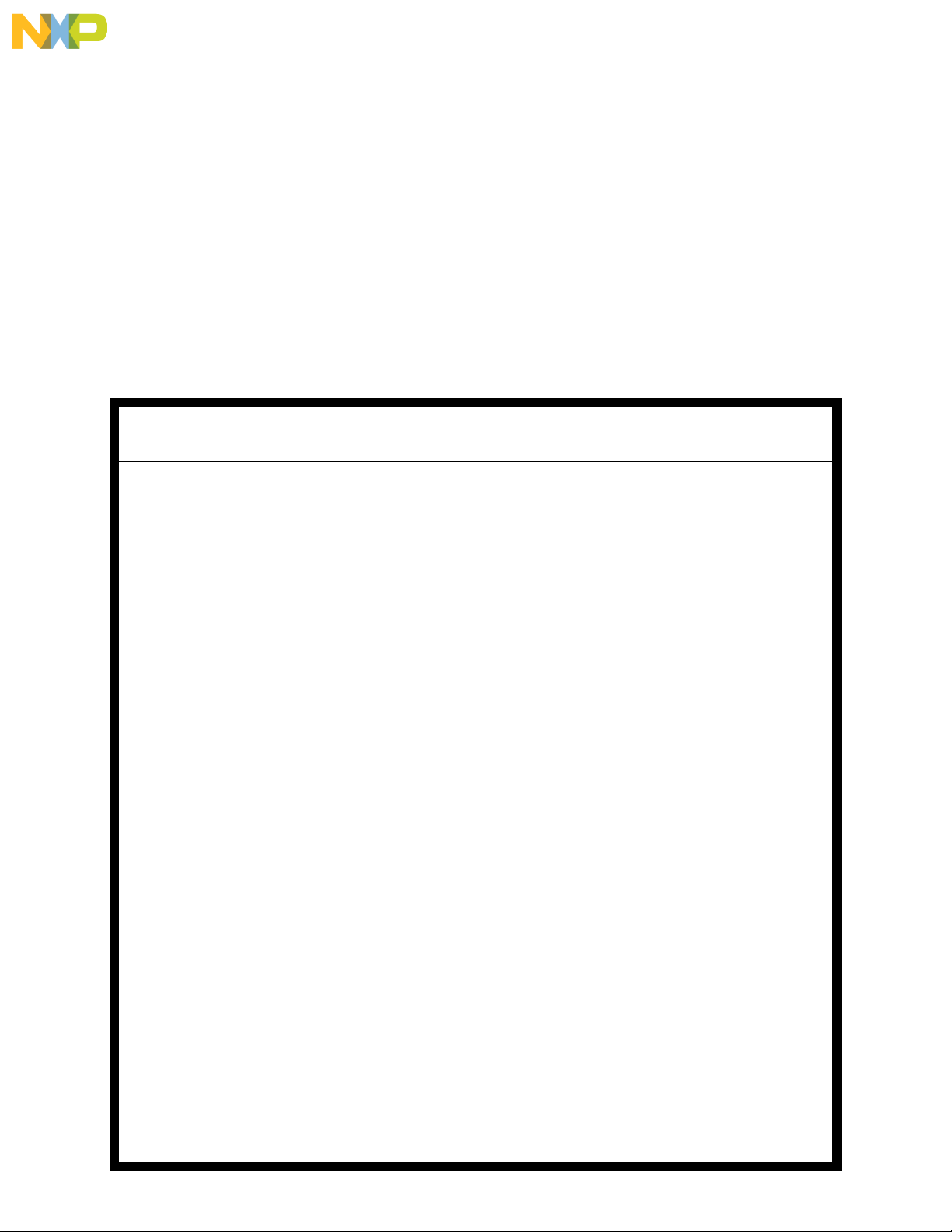

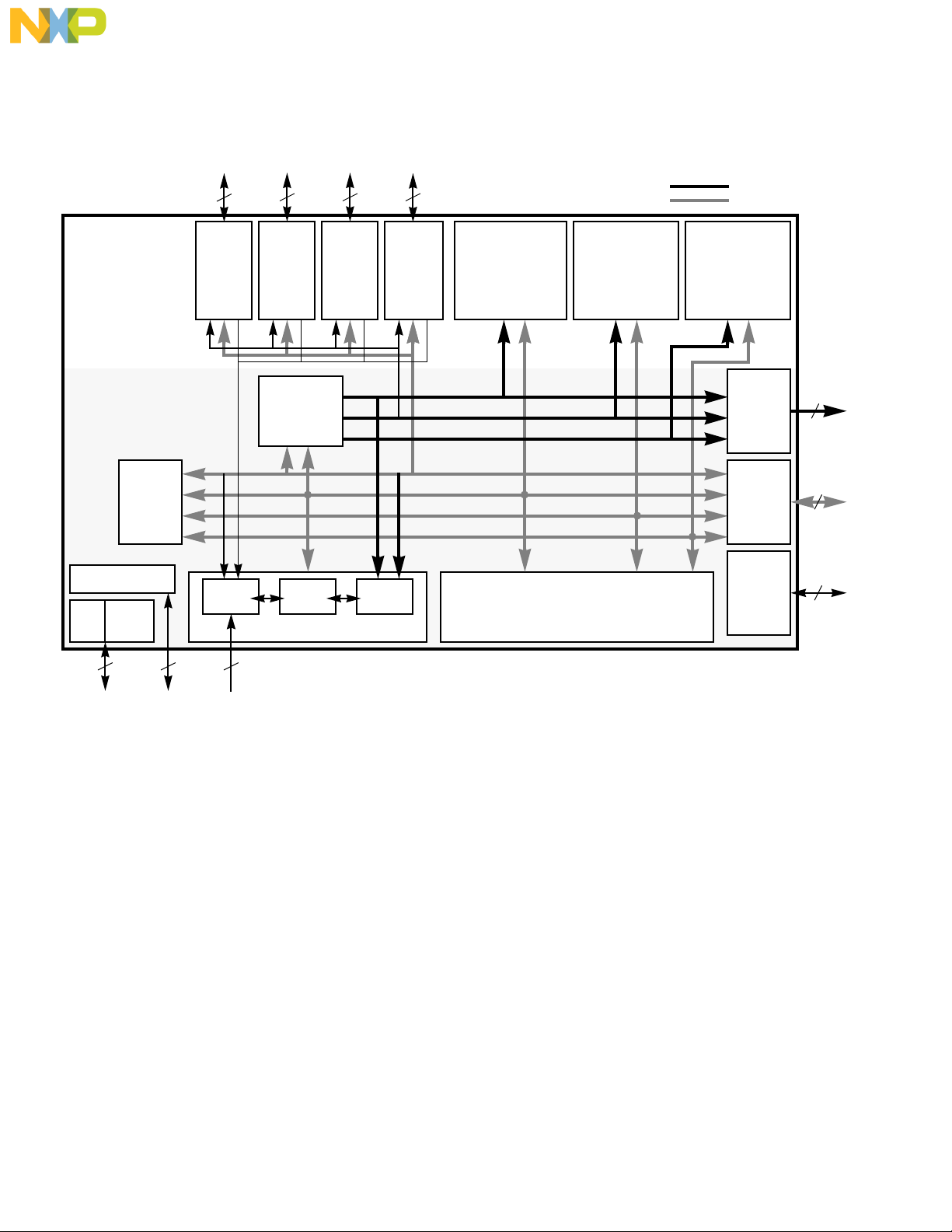

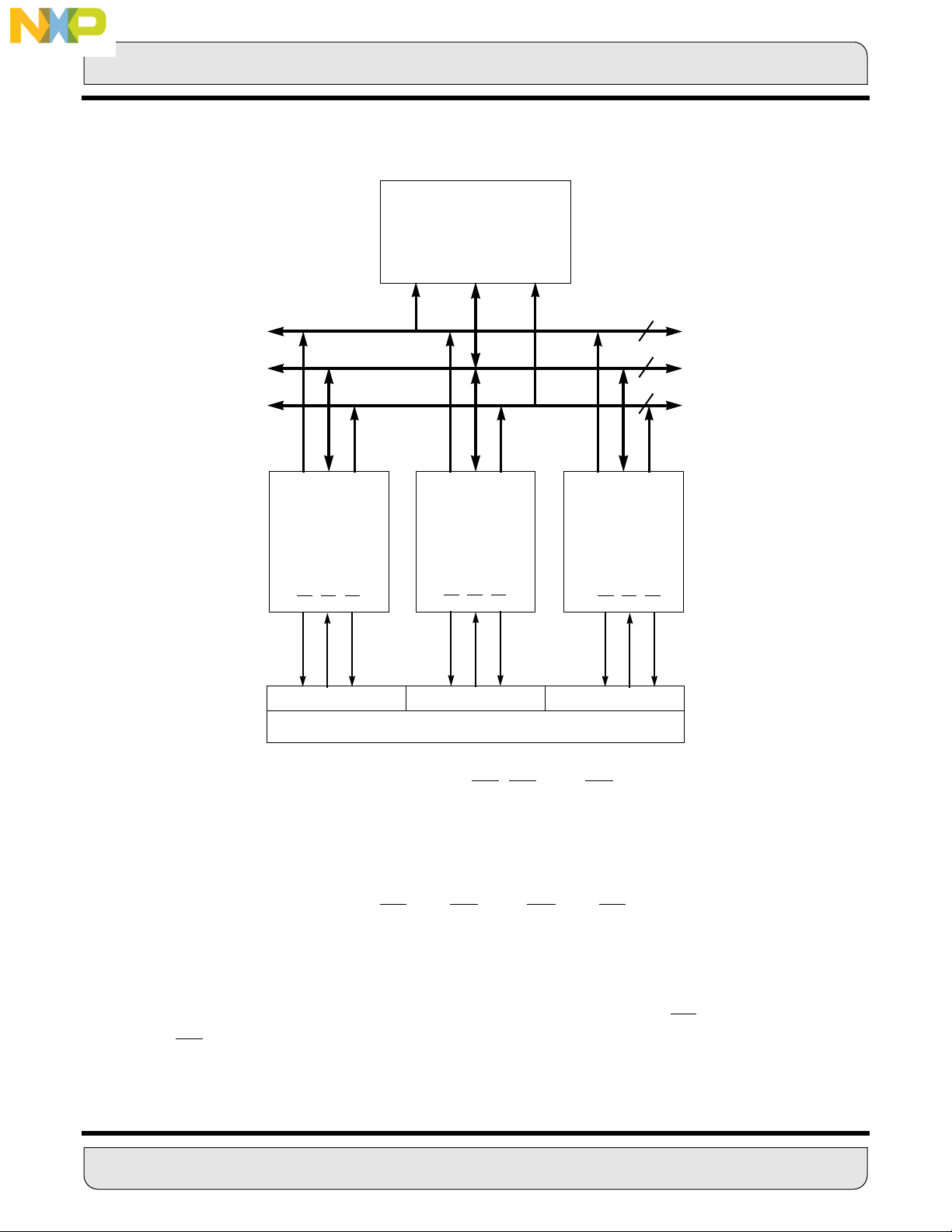

Page 1-6 - Replace with the following Figure 1-2.

cale Semiconductor,

Frees

Page 2-14, Section 2.5 - Insert “Reset disables the TIO pin and causes it to be three-stated.”

Page 3-11, Section 3.4.3, third sentence - Replace “Mode 0” with “Mode 2”.

Page 5-19, Figure 5-11 - Replace “X:FFE” in two places with “X:$FFE8” on top and “X:FFE9” on

bottom.

Page 6-28, Program listing - Move: “MOVE (R0)+ ;and increment the packing pointer”

to after the JCS instruction.

Replace “RTI”

with “RTI X:”

Replace “FLAG MOVE A,(R3)+”

with “FLAG MOVE A,X:(R3)+”

Page 6-68, Section 6.3.9, third sentence - Replace “Bits CD11–CD0, SCP, and STIR in the SCCR work

together to determine the time base.” with “Bits CD11–CD0 and SCP in the SCCR and the STIR bit

in the SCR work together to determine the time base.”

Page 6-127, Section 6.4.7.2, second paragraph - Replace “MC15500” with “MC145500”.

Page 6-130, Figure 6-72 - Replace “MC1550x” with “MC14550x”.

Page 6-155, Figure 6-88 - Replace “MC15500” with “MC145500”.

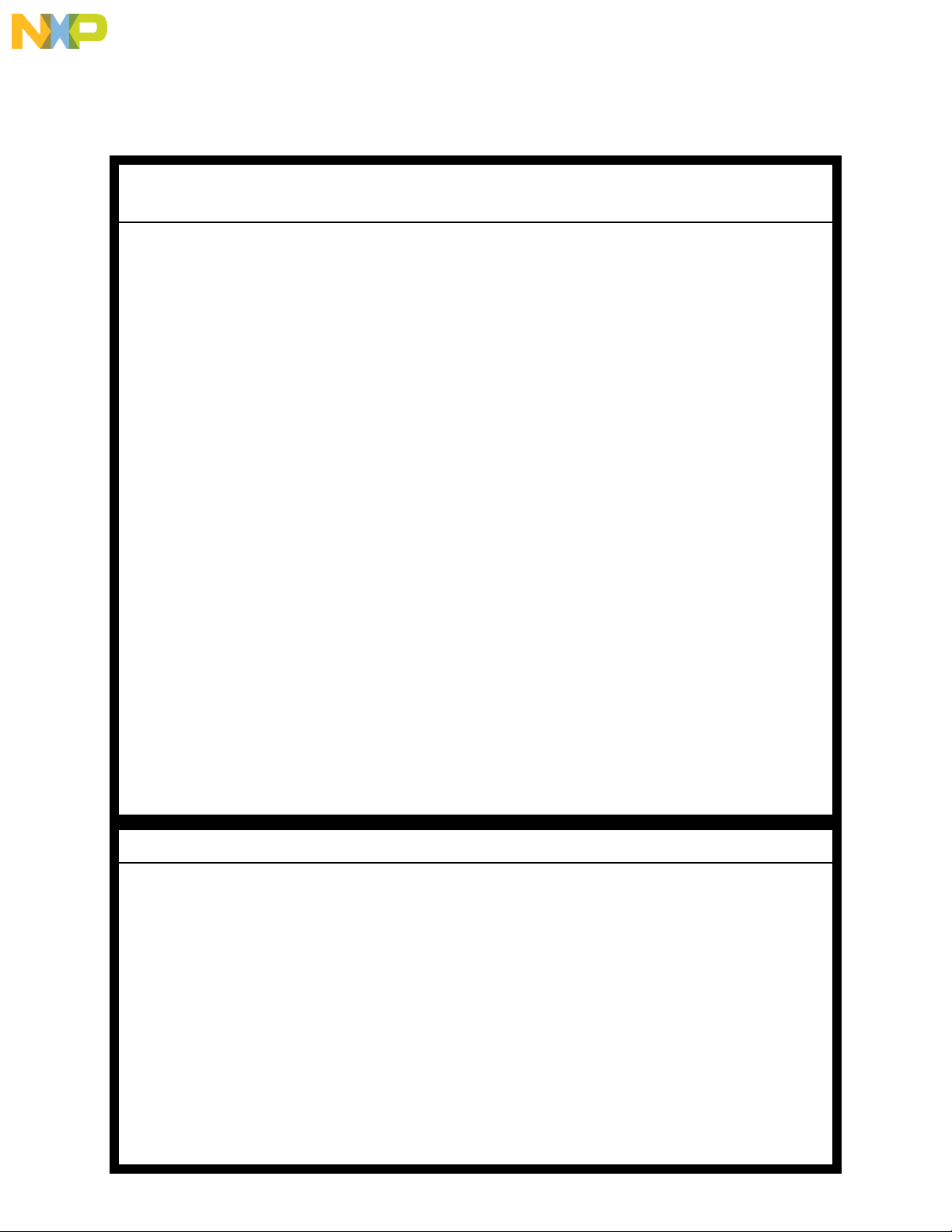

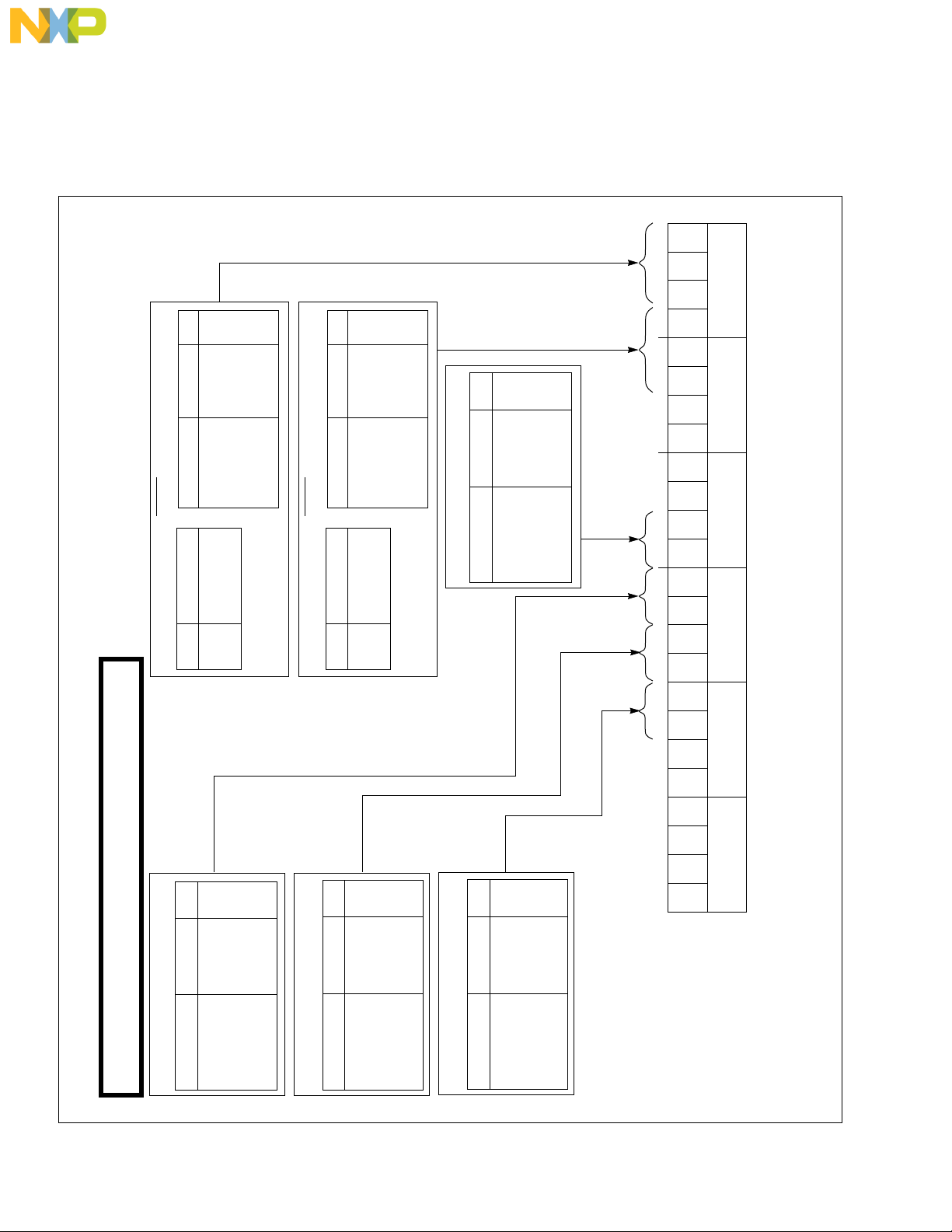

Page B-11, Figure B-4 - Add programming description for IPR bits 16 and 17 (see Figure B-4

below).

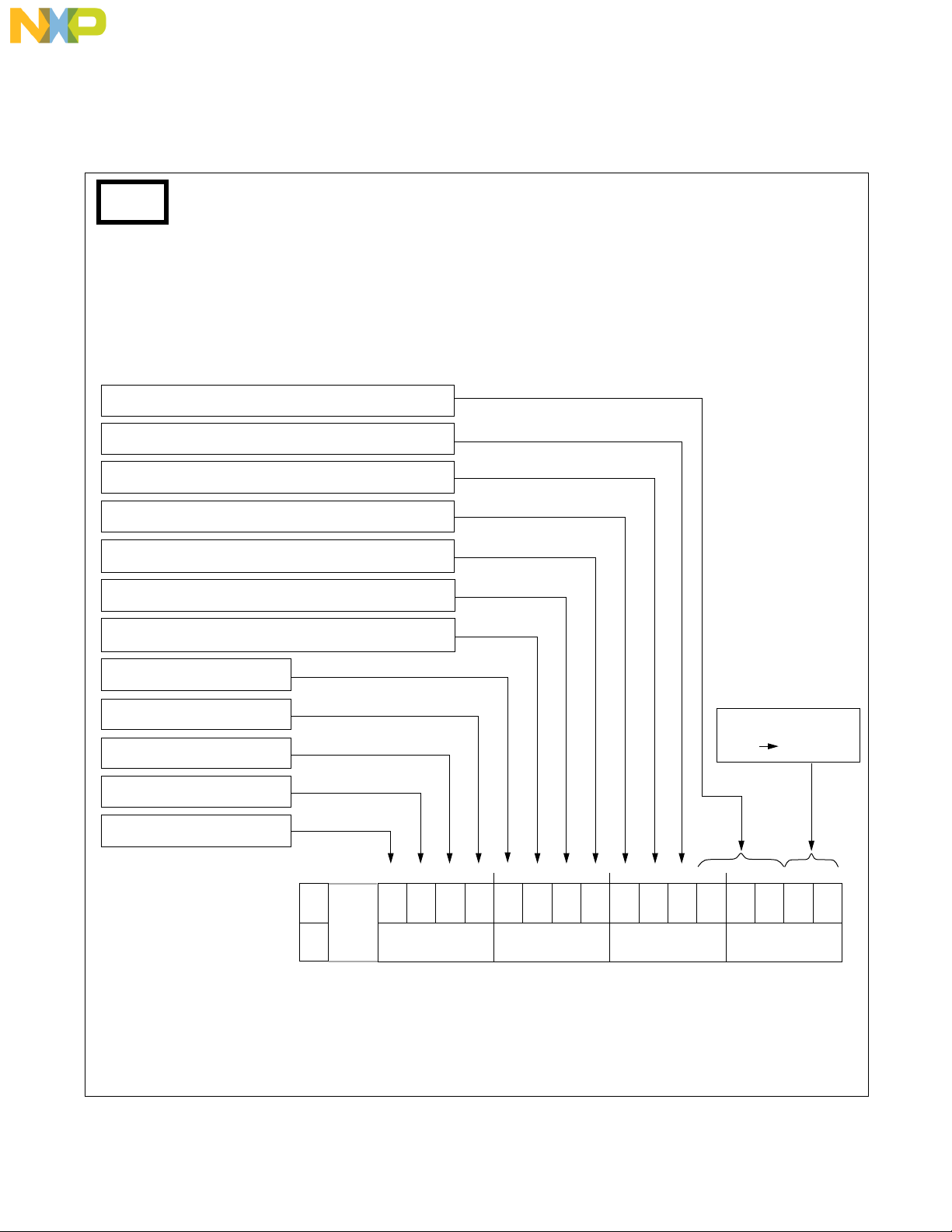

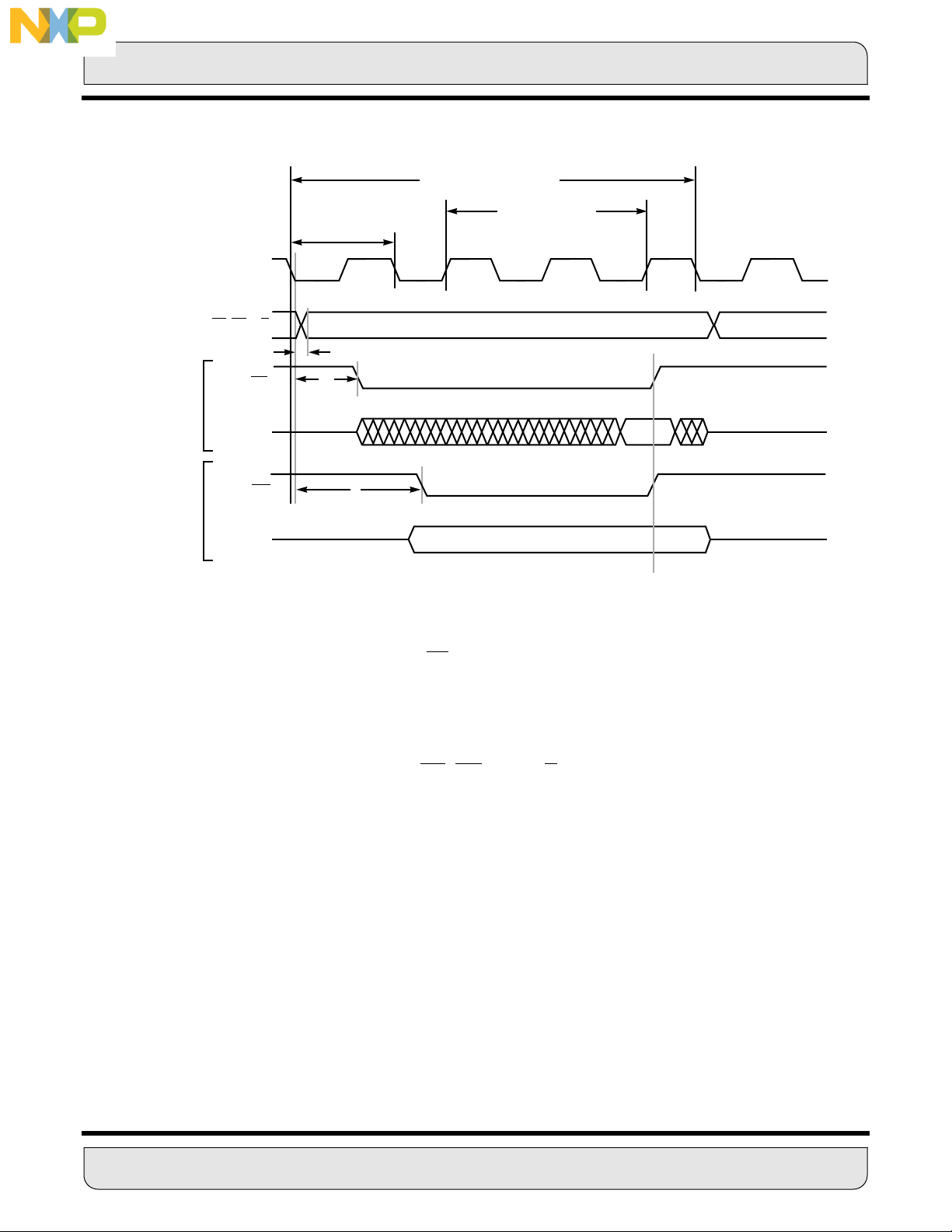

Page B-25, Figure B-32 - Change CRB bits 2-4 description (see Figure B-32 below).

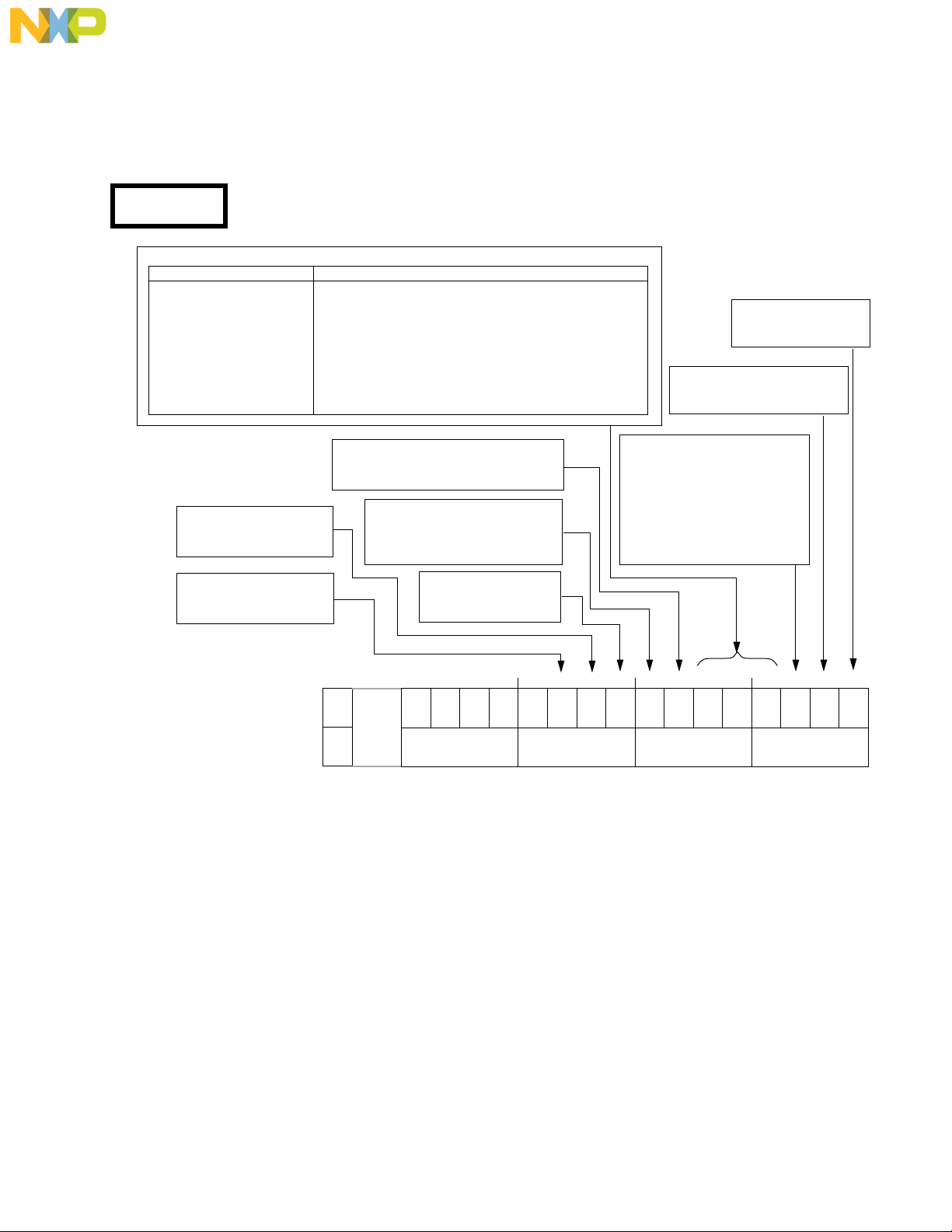

Page B-27, Figure B-34 - Change arrows pointing to Timer Enable bits 1 and 0 as shown in

Figure B-34 below.

MOTOROLA INC., 1995

For More Information On This Product,

Go to: www.freescale.com

Page 24

2

Freescale Semiconductor, Inc.

nc...

I

cale Semiconductor,

24-bit

56000 DSP

Core

Internal

Data

Bus

Switch

OnCETM Port

Clock

PLL

Gen.

Counter

47

1

24-bit

Timer /

Event

Interrupt

Control

IRQ

Sync.

Serial

(SSI)

or I/O

Address

Generation

Program Control Unit

3

6

Unit

Program

Decode

Controller

Serial

Comm.

(SCI)

or I/O

Generator

3

Interface

Program

Address

Host

(HI)

or I/O

15

PAB

XAB

YAB

GDB

PDB

XDB

YDB

Program

Memory

512 × 24 RAM

64 × 24 ROM

(boot) (A-law / µ-law) (sine)

Data ALU

24 × 24 + 56 → 56-bit MAC

Two 56-bit Accumulators

Figure 1-2 DSP56002 Block Diagram

X Data

Memory

256 × 24 RAM

256 × 24 ROM

16-bit Bus

24-bit Bus

Y Data

Memory

256 × 24 RAM

256 × 24 ROM

External

Address

Bus

Switch

External

Data

Bus

Switch

Bus

Control

Address

16

Data

24

Control

10

Frees

DSP56002 User’s Manual Addendum

For More Information On This Product,

Go to: www.freescale.com

MOTOROLA

Page 25

Freescale Semiconductor, Inc.

nc...

I

cale Semiconductor,

Frees

MOTOROLA

For More Information On This Product,

DSP56002 User’s Manual Addendum

Go to: www.freescale.com

3

Page 26

4

Freescale Semiconductor, Inc.

nc...

I

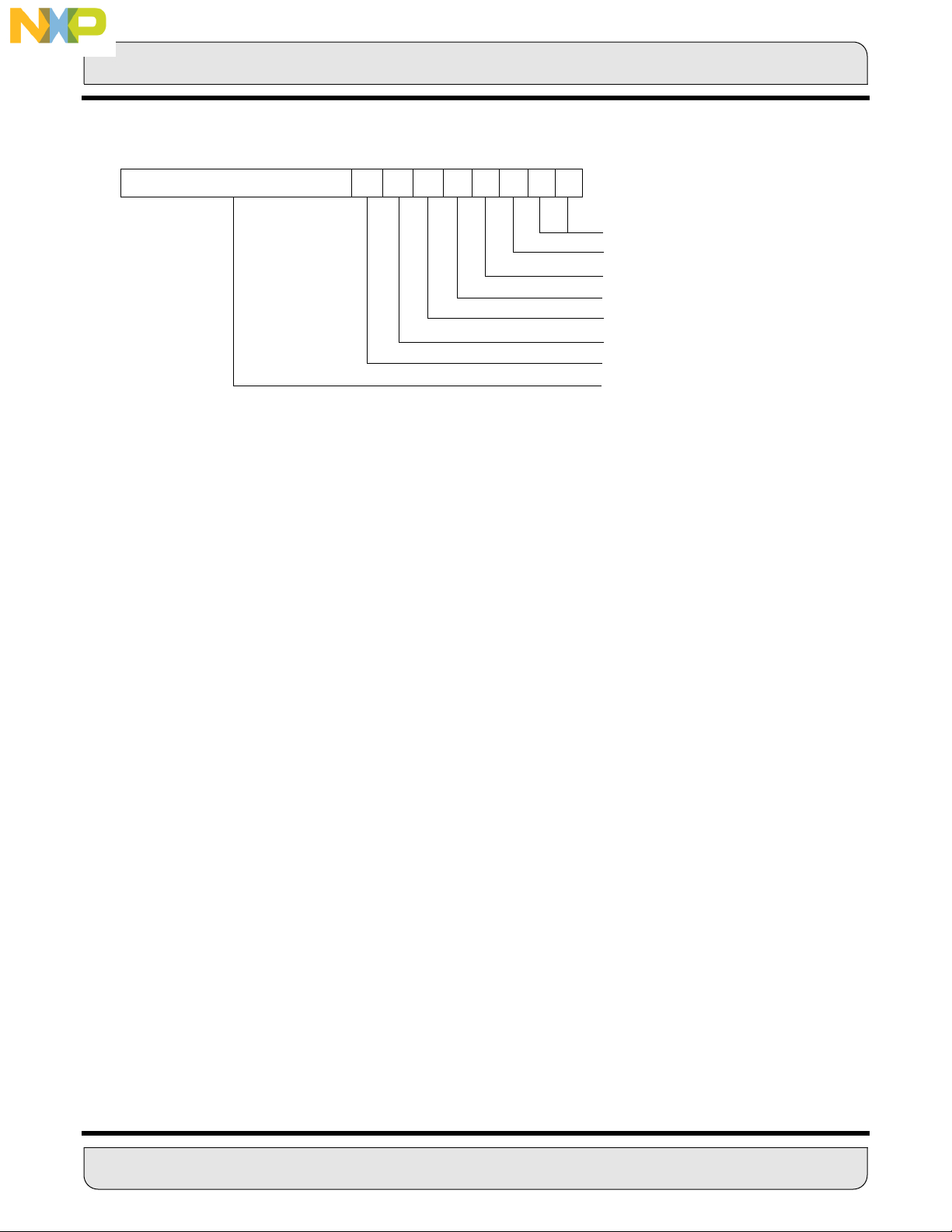

1 0 Yes 1

1 1 Yes 2

IRQA Mode

IRQB Mode

0

*

0

*

0

1 0 Yes 1

1 1 Yes 2

Host IPL

*

*

0

= Reserved, Program as zero

*

cale Semiconductor,

Frees

IAL2 Trigger IAL1 IAL0 Enabled IPL

0 Level 0 0 No —

0 0 No —

0 1 Yes 0

1 0 Yes 1

1 1 Yes 2

HPL1 HPL0 Enabled IPL

SSL1SSL0

1 Neg. Edge 0 1 Yes 0

IBL2 Trigger IBL1 IBL0 Enabled IPL

0 Level 0 0 No —

1 Neg. Edge 0 1 Yes 0

SCL0 HPL1 HPL0 IBL2 IBL1 IBL0 IAL2 IAL1 IAL0

1514131211109876543210

SCL1

TIL0

TIL1

0

*

0

*

0

*

*

0

Figure B-4 Interrupt Priority Register (IPR)

$0

0

*

0

*

23 22 21 20 19 18 1617

SSI IPL

SSL1 SSL0 Enabled IPL

0 0 No —

0 1 Yes 0

1 0 Yes 1

SCI IPL

1 1 Yes 2

SCL1 SCL0 Enabled IPL

0 0 No —

0 1 Yes 0

1 0 Yes 1

1 1 Yes 2

TIMER IPL

0 0 No —

TIL1 TIL0 Enabled IPL

0 1 Yes 0

1 0 Yes 1

CENTRAL PROCESSOR

DSP56002 User’s Manual Addendum

For More Information On This Product,

Go to: www.freescale.com

1 1 Yes 2

Register (IPR)

Interrupt Priority

X:$FFFF Read/Write

Reset = $000000

MOTOROLA

Page 27

Freescale Semiconductor, Inc.

nc...

I

cale Semiconductor,

Frees

MOTOROLA

For More Information On This Product,

DSP56002 User’s Manual Addendum

Go to: www.freescale.com

5

Page 28

nc...

I

cale Semiconductor,

Frees

Freescale Semiconductor, Inc.

SSI

Serial Control Direction Bits

0 = Input 1 = Output

Clock Source Direction

0 = External Clock 1 = Internal Clock

Shift Direction

0 = MSB First 1 = LSB First

Frame Sync Length 0

0 = Rx and Tx Same Length 1 = Rx and Tx Different Length

Frame Sync Length 1

0 = Rx is Word Length 1 = Rx is Bit Length

Sync/Async Control

0 = Asynchronous 1 = Synchronous

Gated Clock Control

0 = Continuous Clock 1 = Gated Clock

SSI Mode Select

0 = Normal 1 = Network

Transmit Enable

0 = Disable 1 = Enable

Receive Enable

0 = Disable 1 = Enable

Transmit Interrupt Enable

0 = Disable 1 = Enable

Receive Interrupt Enable

0 = Disable 1 = Enable

SSI

Control Register B (CRB)

X:$FFED Read/Write

Reset = $000000

23

*

0

•••

1514131211109876543210

RIE TIE RE TE MOD GCK SYN FSL1 FSL0SHFDSCKDSCD2SCD1SCD0 OF1 OF0

6

Output Flag x

If SYN = 1 and SCD1=1

OFx SCx Pin

= Reserved, Program as zero

*

Figure B-32 SSI Control Register B (CRB)

DSP56002 User’s Manual Addendum

For More Information On This Product,

Go to: www.freescale.com

MOTOROLA

Page 29

Freescale Semiconductor, Inc.

TIMER

Timer Control Bits 3-5 (TC0 - TC2)