MC9S08AC16

MC9S08AC8

S9S08AW16A

S9S08AW8A

Data Sheet: Advanced Information

HCS08

Microcontrollers

MC9S08AC16

Rev. 0

12/2007

freescale.com

PRELIMINARY

MC9S08AC16 Series Features

MC9S08AC16 Series Devices

• Consumer & Industrial

— MC9S08AC16

— MC9S08AC8

• Automotive

— S9S08AW16A

— S9S08AW8A

8-Bit HCS08 Central Processor Unit (CPU)

• 40-MHz HCS08 CPU (central processor unit)

• 20-MHz internal bus frequency

• HC08 instruction set with added BGND

instruction

• Background debugging system

• Breakpoint capability to allow single breakpoint

setting during in-circuit debugging (plus two

more breakpoints in on-chip debug module)

• Debugmodulecontainingtwo comparatorsand

nine trigger modes. Eightdeep FIFO for storing

change-of-flowaddresses and event-onlydata.

Debug module supports both tag and force

breakpoints.

• Support for up to 32 interrupt/reset sources

Memory Options

• Up to 16 KB of on-chip in-circuit programmable

FLASH memory with block protection and

security options

• Up to 1 KB of on-chip RAM

Clock Source Options

• Clocksource optionsinclude crystal, resonator,

external clock, or internally generated clock

with precision NVM trimming

System Protection

• Optional computer operating properly (COP)

reset with option to run from independent

internal clock source or bus clock

• Low-voltage detection with reset or interrupt

• Illegal opcode detection with reset

• Illegal address detection with reset

Peripherals

• ADC — 8-channel, 10-bit analog-to-digital

converter with automatic compare function

• SCI — Two serial communications interface

modules with optional 13-bit break

• SPI — Serial peripheral interface module

• IIC — Inter-integrated circuit bus module to

operate at up to 100 kbps with maximum bus

loading; capable of higher baud rates with

reduced loading

• Timers — Three1 16-bit timer/pulse-width

modulator (TPM) modules — Two1 2-channel

and one 4-channel; each has selectable input

capture, output compare, and edge-aligned

PWM capability on each channel. Each timer

module may be configured for buffered,

centered PWM (CPWM) on all channels

• KBI — 7-pin keyboard interrupt module

Input/Output

• Up to 38 general-purpose input/output (I/O)

pins

• Software selectable pullups on ports when

used as inputs

• Software selectable slew rate control on ports

when used as outputs

• Software selectable drive strength on ports

when used as outputs

• Master reset pin and power-on reset (POR)

• Internal pullup on RESET,IRQ, and BKGD/MS

pins to reduce customer system cost

Package Options

• 48-pin quad flat no-lead package (QFN)

• 44-pin low-profile quad flat package (LQFP)

• 32-pin low-profile quad flat package (LQFP)

Power-Saving Modes

• Wait plus two stops

1. MC9S08AC16 and MC9S08AC8 devices only.

MC9S08AC16 Series Data Sheet

Covers MC9S08AC16

MC9S08AC8

S9S08AW16A

S9S08AW8A

MC9S08AC16

Rev. 0

12/2007

PRELIMINARY

Revision History

To provide the most up-to-date information, the revision of our documents on the WorldWide Web will be

the most current. Your printed copy may be an earlier revision. To verify you have the latest information

available, refer to:

http://freescale.com/

The following revision history table summarizes changes contained in this document. For your

convenience, the page number designators have been linked to the appropriate location.

Revision

Number

0 12/2007 Initial Release.

Revision

Date

Description of Changes

This product incorporates SuperFlash® technology licensed from SST.

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc.

© Freescale Semiconductor, Inc., 2006. All rights reserved.

MC9S08AC16 Series Data Sheet, Rev. 0

6 PRELIMINARY Freescale Semiconductor

List of Chapters

Chapter Title Page

Chapter 1 Introduction..............................................................................19

Chapter 2 Pins and Connections.............................................................25

Chapter 3 Modes of Operation.................................................................35

Chapter 4 Memory.....................................................................................41

Chapter 5 Resets, Interrupts, and System Configuration .....................63

Chapter 6 Parallel Input/Output ...............................................................81

Chapter 7 Central Processor Unit (S08CPUV2)....................................111

Chapter 8 Internal Clock Generator (S08ICGV4)..................................131

Chapter 9 Keyboard Interrupt (S08KBIV1)............................................159

Chapter 10 Timer/PWM (S08TPMV3) .......................................................165

Chapter 11 Serial Communications Interface (S08SCIV4).....................193

Chapter 12 Serial Peripheral Interface (S08SPIV3) ................................213

Chapter 13 Inter-Integrated Circuit (S08IICV2).......................................229

Chapter 14 Analog-to-Digital Converter (S08ADC10V1)........................249

Chapter 15 Development Support ...........................................................277

Appendix A Electrical Characteristics and Timing Specifications.......299

Appendix B Ordering Information and Mechanical Drawings...............325

MC9S08AC16 Series Data Sheet, Rev. 0

Freescale Semiconductor PRELIMINARY 7

Contents

Section Number Title Page

Chapter 1

Introduction

1.1 Overview .........................................................................................................................................19

1.2 MCU Block Diagrams .....................................................................................................................20

1.3 System Clock Distribution ..............................................................................................................22

Chapter 2

Pins and Connections

2.1 Introduction .....................................................................................................................................25

2.2 Device Pin Assignment ...................................................................................................................25

2.3 Recommended System Connections ...............................................................................................29

2.3.1 Power (V

2.3.2 Oscillator (XTAL, EXTAL) ..............................................................................................31

2.3.3

2.3.4 Background/Mode Select (BKGD/MS) ............................................................................32

2.3.5 ADC Reference Pins (V

2.3.6 External Interrupt Pin (IRQ) .............................................................................................32

2.3.7 General-Purpose I/O and Peripheral Ports ........................................................................33

RESET ..............................................................................................................................31

, 2 x VSS, V

DD

DDAD

REFH

, V

, V

) ............................................................................31

SSAD

) ..............................................................................32

REFL

Chapter 3

Modes of Operation

3.1 Introduction .....................................................................................................................................35

3.2 Features ...........................................................................................................................................35

3.3 Run Mode ........................................................................................................................................35

3.4 Active Background Mode ................................................................................................................35

3.5 Wait Mode .......................................................................................................................................36

3.6 Stop Modes ......................................................................................................................................36

3.6.1 Stop2 Mode .......................................................................................................................37

3.6.2 Stop3 Mode .......................................................................................................................38

3.6.3 Active BDM Enabled in Stop Mode .................................................................................38

3.6.4 LVD Enabled in Stop Mode ..............................................................................................39

3.6.5 On-Chip Peripheral Modules in Stop Modes ....................................................................39

Chapter 4

Memory

4.1 MC9S08AC16 Series Memory Map ...............................................................................................41

4.1.1 Reset and Interrupt Vector Assignments ...........................................................................42

MC9S08AC16 Series Data Sheet, Rev. 0

Freescale Semiconductor PRELIMINARY 9

Section Number Title Page

4.2 Register Addresses and Bit Assignments ........................................................................................43

4.3 RAM ................................................................................................................................................49

4.4 FLASH ............................................................................................................................................50

4.4.1 Features .............................................................................................................................50

4.4.2 Program and Erase Times .................................................................................................50

4.4.3 Program and Erase Command Execution .........................................................................51

4.4.4 Burst Program Execution ..................................................................................................52

4.4.5 Access Errors ....................................................................................................................54

4.4.6 FLASH Block Protection ..................................................................................................54

4.4.7 Vector Redirection ............................................................................................................55

4.5 Security ............................................................................................................................................55

4.6 FLASH Registers and Control Bits .................................................................................................57

4.6.1 FLASH Clock Divider Register (FCDIV) ........................................................................57

4.6.2 FLASH Options Register (FOPT and NVOPT) ................................................................58

4.6.3 FLASH Configuration Register (FCNFG) ........................................................................59

4.6.4 FLASH Protection Register (FPROT and NVPROT) .......................................................60

4.6.5 FLASH Status Register (FSTAT) ......................................................................................60

4.6.6 FLASH Command Register (FCMD) ...............................................................................62

Chapter 5

Resets, Interrupts, and System Configuration

5.1 Introduction .....................................................................................................................................63

5.2 Features ...........................................................................................................................................63

5.3 MCU Reset ......................................................................................................................................63

5.4 Computer Operating Properly (COP) Watchdog .............................................................................64

5.5 Interrupts .........................................................................................................................................65

5.5.1 Interrupt Stack Frame .......................................................................................................66

5.5.2 External Interrupt Request (IRQ) Pin ...............................................................................66

5.5.3 Interrupt Vectors, Sources, and Local Masks ....................................................................67

5.6 Low-Voltage Detect (LVD) System ................................................................................................69

5.6.1 Power-On Reset Operation ...............................................................................................69

5.6.2 LVD Reset Operation ........................................................................................................69

5.6.3 LVD Interrupt Operation ...................................................................................................69

5.6.4 Low-Voltage Warning (LVW) ...........................................................................................69

5.7 Real-Time Interrupt (RTI) ...............................................................................................................69

5.8 MCLK Output .................................................................................................................................70

5.9 Reset, Interrupt, and System Control Registers and Control Bits ...................................................70

5.9.1 Interrupt Pin Request Status and Control Register (IRQSC) ............................................71

5.9.2 System Reset Status Register (SRS) .................................................................................72

5.9.3 System Background Debug Force Reset Register (SBDFR) ............................................73

5.9.4 System Options Register (SOPT) .....................................................................................74

5.9.5 System MCLK Control Register (SMCLK) .....................................................................75

MC9S08AC16 Series Data Sheet, Rev. 0

10 PRELIMINARY Freescale Semiconductor

Section Number Title Page

5.9.6 System Device Identification Register (SDIDH, SDIDL) ................................................76

5.9.7 System Real-Time Interrupt Status and Control Register (SRTISC) ................................77

5.9.8 System Power Management Status and Control 1 Register (SPMSC1) ...........................78

5.9.9 System Power Management Status and Control 2 Register (SPMSC2) ...........................79

5.9.10 System Options Register 2 (SOPT2) ................................................................................80

Chapter 6

Parallel Input/Output

6.1 Introduction .....................................................................................................................................81

6.2 Features ...........................................................................................................................................83

6.3 Pin Descriptions ..............................................................................................................................83

6.3.1 Port A ................................................................................................................................83

6.3.2 Port B ................................................................................................................................84

6.3.3 Port C ................................................................................................................................84

6.3.4 Port D ................................................................................................................................85

6.3.5 Port E ................................................................................................................................85

6.3.6 Port F .................................................................................................................................86

6.3.7 Port G ................................................................................................................................86

6.4 Parallel I/O Control .........................................................................................................................87

6.5 Pin Control ......................................................................................................................................88

6.5.1 Internal Pullup Enable .......................................................................................................88

6.5.2 Output Slew Rate Control Enable .....................................................................................88

6.5.3 Output Drive Strength Select ............................................................................................88

6.6 Pin Behavior in Stop Modes ............................................................................................................89

6.7 Parallel I/O and Pin Control Registers ............................................................................................89

6.7.1 Port A I/O Registers (PTAD and PTADD) .......................................................................89

6.7.2 Port A Pin Control Registers (PTAPE, PTASE, PTADS) .................................................90

6.7.3 Port B I/O Registers (PTBD and PTBDD) .......................................................................92

6.7.4 Port B Pin Control Registers (PTBPE, PTBSE, PTBDS) .................................................93

6.7.5 Port C I/O Registers (PTCD and PTCDD) .......................................................................95

6.7.6 Port C Pin Control Registers (PTCPE, PTCSE, PTCDS) .................................................96

6.7.7 Port D I/O Registers (PTDD and PTDDD) .......................................................................98

6.7.8 Port D Pin Control Registers (PTDPE, PTDSE, PTDDS) ................................................99

6.7.9 Port E I/O Registers (PTED and PTEDD) ......................................................................101

6.7.10 Port E Pin Control Registers (PTEPE, PTESE, PTEDS) ................................................102

6.7.11 Port F I/O Registers (PTFD and PTFDD) .......................................................................104

6.7.12 Port F Pin Control Registers (PTFPE, PTFSE, PTFDS) ................................................105

6.7.13 Port G I/O Registers (PTGD and PTGDD) .....................................................................107

6.7.14 Port G Pin Control Registers (PTGPE, PTGSE, PTGDS) ..............................................108

MC9S08AC16 Series Data Sheet, Rev. 0

Freescale Semiconductor PRELIMINARY 11

Section Number Title Page

Chapter 7

Central Processor Unit (S08CPUV2)

7.1 Introduction ...................................................................................................................................111

7.1.1 Features ...........................................................................................................................111

7.2 Programmer’s Model and CPU Registers .....................................................................................112

7.2.1 Accumulator (A) .............................................................................................................112

7.2.2 Index Register (H:X) .......................................................................................................112

7.2.3 Stack Pointer (SP) ...........................................................................................................113

7.2.4 Program Counter (PC) ....................................................................................................113

7.2.5 Condition Code Register (CCR) .....................................................................................113

7.3 Addressing Modes .........................................................................................................................115

7.3.1 Inherent Addressing Mode (INH) ...................................................................................115

7.3.2 Relative Addressing Mode (REL) ...................................................................................115

7.3.3 Immediate Addressing Mode (IMM) ..............................................................................115

7.3.4 Direct Addressing Mode (DIR) ......................................................................................115

7.3.5 Extended Addressing Mode (EXT) ................................................................................116

7.3.6 Indexed Addressing Mode ..............................................................................................116

7.4 Special Operations .........................................................................................................................117

7.4.1 Reset Sequence ...............................................................................................................117

7.4.2 Interrupt Sequence ..........................................................................................................117

7.4.3 Wait Mode Operation ......................................................................................................118

7.4.4 Stop Mode Operation ......................................................................................................118

7.4.5 BGND Instruction ...........................................................................................................119

7.5 HCS08 Instruction Set Summary ..................................................................................................120

Chapter 8

Internal Clock Generator (S08ICGV4)

8.1 Introduction ...................................................................................................................................133

8.1.1 Features ...........................................................................................................................133

8.1.2 Modes of Operation ........................................................................................................134

8.1.3 Block Diagram ................................................................................................................135

8.2 External Signal Description ..........................................................................................................135

8.2.1 EXTAL — External Reference Clock / Oscillator Input ................................................135

8.2.2 XTAL — Oscillator Output ............................................................................................135

8.2.3 External Clock Connections ...........................................................................................136

8.2.4 External Crystal/Resonator Connections ........................................................................136

8.3 Register Definition ........................................................................................................................137

8.3.1 ICG Control Register 1 (ICGC1) ....................................................................................137

8.3.2 ICG Control Register 2 (ICGC2) ....................................................................................139

8.3.3 ICG Status Register 1 (ICGS1) .......................................................................................140

8.3.4 ICG Status Register 2 (ICGS2) .......................................................................................141

8.3.5 ICG Filter Registers (ICGFLTU, ICGFLTL) ..................................................................141

MC9S08AC16 Series Data Sheet, Rev. 0

12 PRELIMINARY Freescale Semiconductor

Section Number Title Page

8.3.6 ICG Trim Register (ICGTRM) .......................................................................................142

8.4 Functional Description ..................................................................................................................142

8.4.1 Off Mode (Off) ................................................................................................................143

8.4.2 Self-Clocked Mode (SCM) .............................................................................................143

8.4.3 FLL Engaged, Internal Clock (FEI) Mode .....................................................................144

8.4.4 FLL Engaged Internal Unlocked ....................................................................................145

8.4.5 FLL Engaged Internal Locked ........................................................................................145

8.4.6 FLL Bypassed, External Clock (FBE) Mode ..................................................................145

8.4.7 FLL Engaged, External Clock (FEE) Mode ...................................................................145

8.4.8 FLL Lock and Loss-of-Lock Detection ..........................................................................146

8.4.9 FLL Loss-of-Clock Detection .........................................................................................147

8.4.10 Clock Mode Requirements .............................................................................................148

8.4.11 Fixed Frequency Clock ...................................................................................................149

8.4.12 High Gain Oscillator .......................................................................................................149

8.5 Initialization/Application Information ..........................................................................................149

8.5.1 Introduction .....................................................................................................................149

8.5.2 Example #1: External Crystal = 32 kHz, Bus Frequency = 4.19 MHz ...........................151

8.5.3 Example #2: External Crystal = 4 MHz, Bus Frequency = 20 MHz ..............................153

8.5.4 Example #3: No External Crystal Connection, 5.4 MHz Bus Frequency ......................155

8.5.5 Example #4: Internal Clock Generator Trim ..................................................................157

Chapter 9

Keyboard Interrupt (S08KBIV1)

9.1 Introduction ...................................................................................................................................159

9.2 Keyboard Pin Sharing ....................................................................................................................159

9.3 Features .........................................................................................................................................159

9.3.1 KBI Block Diagram ........................................................................................................161

9.4 Register Definition ........................................................................................................................161

9.4.1 KBI Status and Control Register (KBISC) .....................................................................162

9.4.2 KBI Pin Enable Register (KBIPE) ..................................................................................163

9.5 Functional Description ..................................................................................................................163

9.5.1 Pin Enables ......................................................................................................................163

9.5.2 Edge and Level Sensitivity ..............................................................................................163

9.5.3 KBI Interrupt Controls ....................................................................................................164

Chapter 10

Timer/PWM (S08TPMV3)

10.1 Introduction ...................................................................................................................................165

10.2 Features .........................................................................................................................................165

10.3 TPMV3 Differences from Previous Versions ................................................................................168

10.3.1 Migrating from TPMV1 ..................................................................................................170

10.3.2 Features ...........................................................................................................................171

MC9S08AC16 Series Data Sheet, Rev. 0

Freescale Semiconductor PRELIMINARY 13

Section Number Title Page

10.3.3 Modes of Operation ........................................................................................................171

10.3.4 Block Diagram ................................................................................................................172

10.4 Signal Description .........................................................................................................................174

10.4.1 Detailed Signal Descriptions ...........................................................................................174

10.5 Register Definition ........................................................................................................................178

10.5.1 TPM Status and Control Register (TPMxSC) ................................................................178

10.5.2 TPM-Counter Registers (TPMxCNTH:TPMxCNTL) ....................................................179

10.5.3 TPM Counter Modulo Registers (TPMxMODH:TPMxMODL) ....................................180

10.5.4 TPM Channel n Status and Control Register (TPMxCnSC) ..........................................181

10.5.5 TPM Channel Value Registers (TPMxCnVH:TPMxCnVL) ..........................................183

10.6 Functional Description ..................................................................................................................184

10.6.1 Counter ............................................................................................................................185

10.6.2 Channel Mode Selection .................................................................................................187

10.7 Reset Overview .............................................................................................................................190

10.7.1 General ............................................................................................................................190

10.7.2 Description of Reset Operation .......................................................................................190

10.8 Interrupts .......................................................................................................................................190

10.8.1 General ............................................................................................................................190

10.8.2 Description of Interrupt Operation ..................................................................................191

Chapter 11

Serial Communications Interface (S08SCIV4)

11.1 Introduction ...................................................................................................................................193

11.1.1 Features ...........................................................................................................................195

11.1.2 Modes of Operation ........................................................................................................195

11.1.3 Block Diagram ................................................................................................................196

11.2 Register Definition ........................................................................................................................198

11.2.1 SCI Baud Rate Registers (SCIxBDH, SCIxBDL) ..........................................................198

11.2.2 SCI Control Register 1 (SCIxC1) ...................................................................................199

11.2.3 SCI Control Register 2 (SCIxC2) ...................................................................................200

11.2.4 SCI Status Register 1 (SCIxS1) ......................................................................................201

11.2.5 SCI Status Register 2 (SCIxS2) ......................................................................................203

11.2.6 SCI Control Register 3 (SCIxC3) ...................................................................................204

11.2.7 SCI Data Register (SCIxD) .............................................................................................205

11.3 Functional Description ..................................................................................................................205

11.3.1 Baud Rate Generation .....................................................................................................205

11.3.2 Transmitter Functional Description ................................................................................206

11.3.3 Receiver Functional Description .....................................................................................207

11.3.4 Interrupts and Status Flags ..............................................................................................209

11.3.5 Additional SCI Functions ...............................................................................................210

MC9S08AC16 Series Data Sheet, Rev. 0

14 PRELIMINARY Freescale Semiconductor

Section Number Title Page

Chapter 12

Serial Peripheral Interface (S08SPIV3)

12.1 Introduction ...................................................................................................................................213

12.1.1 Features ...........................................................................................................................215

12.1.2 Block Diagrams ..............................................................................................................215

12.1.3 SPI Baud Rate Generation ..............................................................................................217

12.2 External Signal Description ..........................................................................................................218

12.2.1 SPSCK — SPI Serial Clock ............................................................................................218

12.2.2 MOSI — Master Data Out, Slave Data In ......................................................................218

12.2.3 MISO — Master Data In, Slave Data Out ......................................................................218

12.2.4

12.3 Modes of Operation .......................................................................................................................219

12.3.1 SPI in Stop Modes ..........................................................................................................219

12.4 Register Definition ........................................................................................................................219

12.4.1 SPI Control Register 1 (SPI1C1) ....................................................................................219

12.4.2 SPI Control Register 2 (SPI1C2) ....................................................................................220

12.4.3 SPI Baud Rate Register (SPI1BR) ..................................................................................221

12.4.4 SPI Status Register (SPI1S) ............................................................................................222

12.4.5 SPI Data Register (SPI1D) ..............................................................................................223

12.5 Functional Description ..................................................................................................................224

12.5.1 SPI Clock Formats ..........................................................................................................224

12.5.2 SPI Interrupts ..................................................................................................................227

12.5.3 Mode Fault Detection .....................................................................................................227

SS — Slave Select ...........................................................................................................218

Chapter 13

Inter-Integrated Circuit (S08IICV2)

13.1 Introduction ...................................................................................................................................229

13.1.1 Features ...........................................................................................................................231

13.1.2 Modes of Operation ........................................................................................................231

13.1.3 Block Diagram ................................................................................................................232

13.2 External Signal Description ..........................................................................................................232

13.2.1 SCL — Serial Clock Line ...............................................................................................232

13.2.2 SDA — Serial Data Line ................................................................................................232

13.3 Register Definition ........................................................................................................................232

13.3.1 IIC Address Register (IIC1A) .........................................................................................233

13.3.2 IIC Frequency Divider Register (IIC1F) .........................................................................233

13.3.3 IIC Control Register (IIC1C1) ........................................................................................236

13.3.4 IIC Status Register (IIC1S) .............................................................................................237

13.3.5 IIC Data I/O Register (IIC1D) ........................................................................................238

13.3.6 IIC Control Register 2 (IIC1C2) .....................................................................................238

13.4 Functional Description ..................................................................................................................239

13.4.1 IIC Protocol .....................................................................................................................239

MC9S08AC16 Series Data Sheet, Rev. 0

Freescale Semiconductor PRELIMINARY 15

Section Number Title Page

13.4.2 10-bit Address .................................................................................................................243

13.4.3 General Call Address ......................................................................................................244

13.5 Resets ............................................................................................................................................244

13.6 Interrupts .......................................................................................................................................244

13.6.1 Byte Transfer Interrupt ....................................................................................................244

13.6.2 Address Detect Interrupt .................................................................................................244

13.6.3 Arbitration Lost Interrupt ................................................................................................244

13.7 Initialization/Application Information ..........................................................................................246

Chapter 14

Analog-to-Digital Converter (S08ADC10V1)

14.1 Overview .......................................................................................................................................249

14.2 Channel Assignments ....................................................................................................................249

14.2.1 Alternate Clock ...............................................................................................................250

14.2.2 Hardware Trigger ............................................................................................................250

14.2.3 Temperature Sensor ........................................................................................................252

14.2.4 Features ...........................................................................................................................253

14.2.5 Block Diagram ................................................................................................................253

14.3 External Signal Description ..........................................................................................................254

14.3.1 Analog Power (V

14.3.2 Analog Ground (V

14.3.3 Voltage Reference High (V

14.3.4 Voltage Reference Low (V

14.3.5 Analog Channel Inputs (ADx) ........................................................................................255

14.4 Register Definition ........................................................................................................................255

14.4.1 Status and Control Register 1 (ADC1SC1) ....................................................................255

14.4.2 Status and Control Register 2 (ADC1SC2) ....................................................................257

14.4.3 Data Result High Register (ADC1RH) ...........................................................................258

14.4.4 Data Result Low Register (ADC1RL) ............................................................................258

14.4.5 Compare Value High Register (ADC1CVH) ..................................................................259

14.4.6 Compare Value Low Register (ADC1CVL) ...................................................................259

14.4.7 Configuration Register (ADC1CFG) ..............................................................................259

14.4.8 Pin Control 1 Register (APCTL1) ..................................................................................261

14.4.9 Pin Control 2 Register (APCTL2) ..................................................................................262

14.4.10Pin Control 3 Register (APCTL3) ..................................................................................263

14.5 Functional Description ..................................................................................................................264

14.5.1 Clock Select and Divide Control ....................................................................................264

14.5.2 Input Select and Pin Control ...........................................................................................265

14.5.3 Hardware Trigger ............................................................................................................265

14.5.4 Conversion Control .........................................................................................................265

14.5.5 Automatic Compare Function .........................................................................................268

14.5.6 MCU Wait Mode Operation ............................................................................................268

) ..................................................................................................255

DDAD

) .................................................................................................255

SSAD

) ...................................................................................255

REFH

) .....................................................................................255

REFL

MC9S08AC16 Series Data Sheet, Rev. 0

16 PRELIMINARY Freescale Semiconductor

Section Number Title Page

14.5.7 MCU Stop3 Mode Operation ..........................................................................................268

14.5.8 MCU Stop1 and Stop2 Mode Operation .........................................................................269

14.6 Initialization Information ..............................................................................................................269

14.6.1 ADC Module Initialization Example .............................................................................269

14.7 Application Information ................................................................................................................271

14.7.1 External Pins and Routing ..............................................................................................271

14.7.2 Sources of Error ..............................................................................................................273

Chapter 15

Development Support

15.1 Introduction ...................................................................................................................................277

15.1.1 Features ...........................................................................................................................278

15.2 Background Debug Controller (BDC) ..........................................................................................278

15.2.1 BKGD Pin Description ...................................................................................................279

15.2.2 Communication Details ..................................................................................................280

15.2.3 BDC Commands .............................................................................................................284

15.2.4 BDC Hardware Breakpoint .............................................................................................286

15.3 On-Chip Debug System (DBG) ....................................................................................................287

15.3.1 Comparators A and B ......................................................................................................287

15.3.2 Bus Capture Information and FIFO Operation ...............................................................287

15.3.3 Change-of-Flow Information ..........................................................................................288

15.3.4 Tag vs. Force Breakpoints and Triggers .........................................................................288

15.3.5 Trigger Modes .................................................................................................................289

15.3.6 Hardware Breakpoints ....................................................................................................291

15.4 Register Definition ........................................................................................................................291

15.4.1 BDC Registers and Control Bits .....................................................................................291

15.4.2 System Background Debug Force Reset Register (SBDFR) ..........................................293

15.4.3 DBG Registers and Control Bits .....................................................................................294

Appendix A

Electrical Characteristics and Timing Specifications

A.1 Introduction....................................................................................................................................299

A.2 Parameter Classification.................................................................................................................299

A.3 Absolute Maximum Ratings...........................................................................................................299

A.4 Thermal Characteristics..................................................................................................................301

A.5 ESD Protection and Latch-Up Immunity.......................................................................................302

A.6 DC Characteristics..........................................................................................................................303

A.7 Supply Current Characteristics.......................................................................................................306

A.8 ADC Characteristics.......................................................................................................................309

A.9 Internal Clock Generation Module Characteristics........................................................................312

A.9.1 ICG Frequency Specifications.........................................................................................313

A.10 AC Characteristics..........................................................................................................................316

MC9S08AC16 Series Data Sheet, Rev. 0

Freescale Semiconductor PRELIMINARY 17

Section Number Title Page

A.10.1 Control Timing ................................................................................................................316

A.10.2 Timer/PWM (TPM) Module Timing...............................................................................317

A.11 SPI Characteristics .........................................................................................................................319

A.12 FLASH Specifications....................................................................................................................322

A.13 EMC Performance..........................................................................................................................323

Appendix B

Ordering Information and Mechanical Drawings

B.1 Ordering Information .....................................................................................................................325

B.2 Mechanical Drawings.....................................................................................................................326

MC9S08AC16 Series Data Sheet, Rev. 0

18 PRELIMINARY Freescale Semiconductor

Chapter 1 Introduction

1.1 Overview

The MC9S08AC16Series devicesare members of thelow-cost,high-performance HCS08 Familyof 8-bit

microcontroller units (MCUs). All MCUs in the family use the enhanced HCS08 core and are available

with a variety of modules, memory sizes, memory types, and package types. Refer to Table 1-1 for

memory sizes and package types.

NOTE

• The MC9S08AC16and MC9S08AC8 devices are qualified for, and are

intended to be used in, consumer and industrial applications.

• The S9S08AW16A and S9S08AW8A devices are qualified for, and are

intended to be used in, automotive applications.

Table 1-1 summarizes the feature set available in the MCUs.

MC9S08AC16 Series Data Sheet, Rev. 0

Freescale Semiconductor PRELIMINARY 19

Chapter 1 Introduction

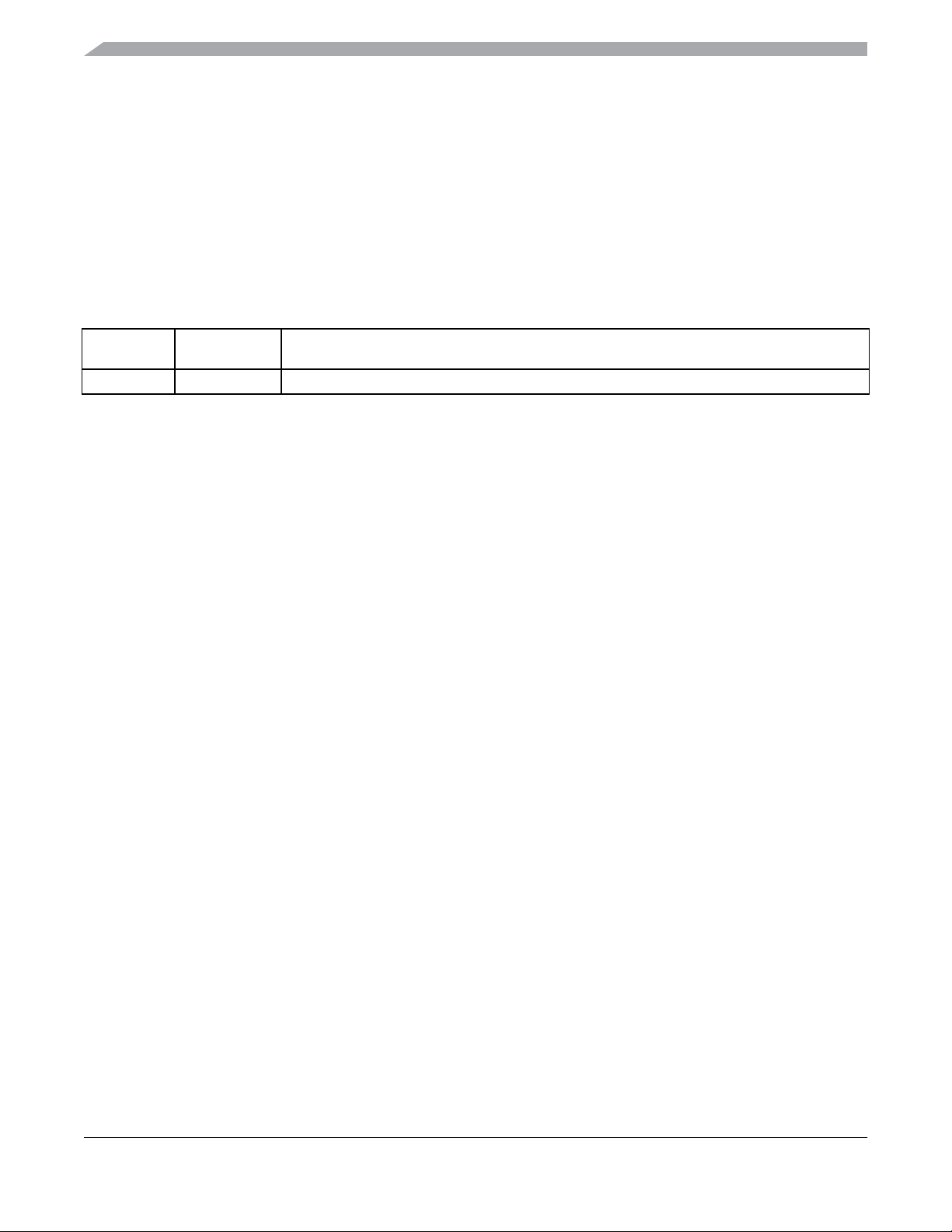

Table 1-1. Features by MCU and Package

Consumer and Industrial “AC” Devices

Feature MC9S08AC16 MC9S08AC8

FLASH size (bytes) 16K 8K

RAM size (bytes) 1024 768

Pin quantity

ADC channels 8 8 6 8 8 6

TPM1 channels 4 4 2 4 4 2

TPM2 channels 2 2 2 2 2 2

TPM3 channels 2 2 2 2 2 2

KBI pins 7 6 4 7 6 4

GPIO pins 38 34 22 38 34 22

Consumer & Industrial

Qualified

Automotive Qualified no no

48 44 32 48 44 32

yes yes

Automotive “AW” Devices

Feature S9S08AW16A S9S08AW8A

FLASH size (bytes) 16K 8K

RAM size (bytes) 1024 768

Pin quantity

ADC channels 8 8 6 8 8 6

TPM1 channels 4 4 2 4 4 2

TPM2 channels 2 2 2 2 2 2

TPM3 channels — — — — — —

KBI pins 7 6 4 7 6 4

GPIO pins 38 34 22 38 34 22

Consumer & Industrial

Qualified

Automotive Qualified yes yes

48 44 32 48 44 32

no no

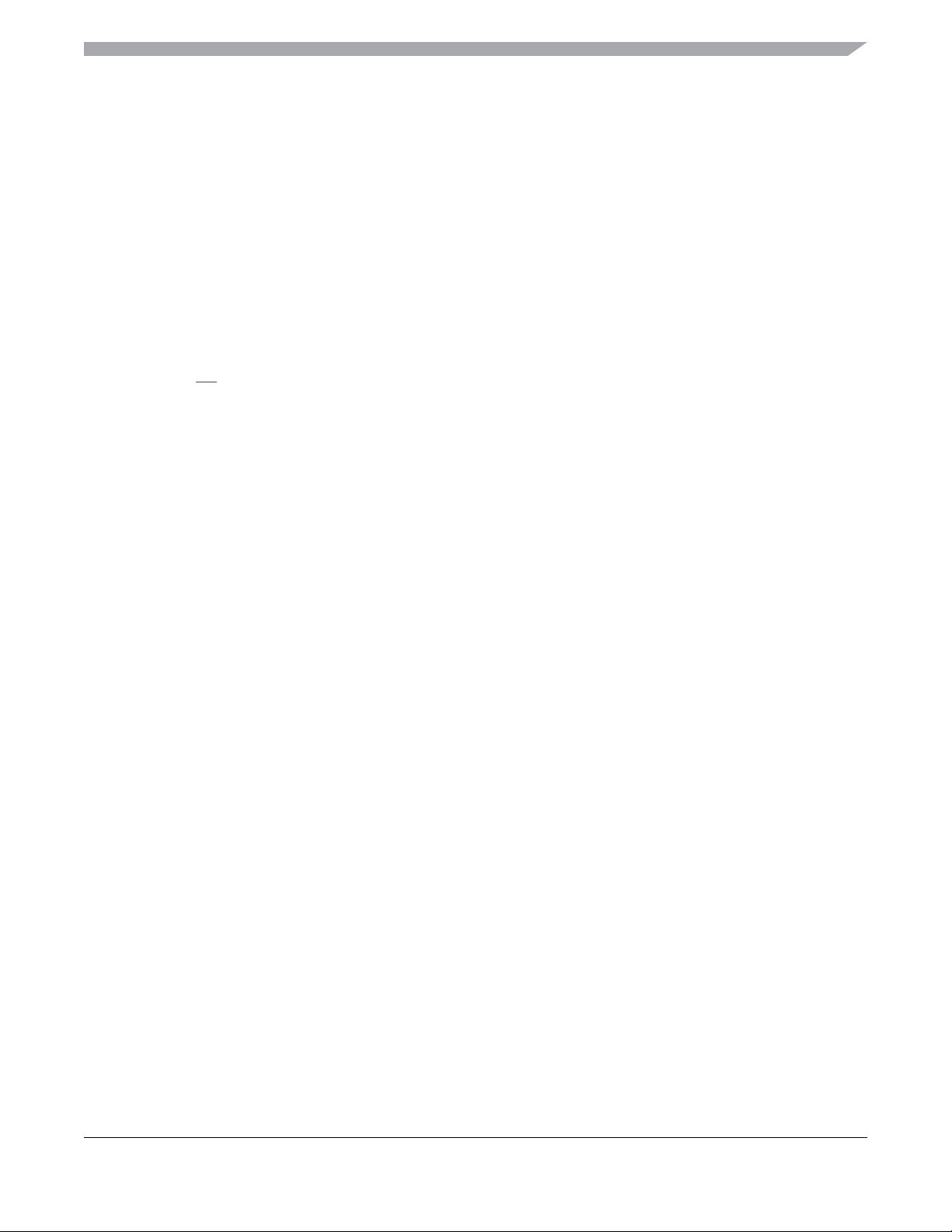

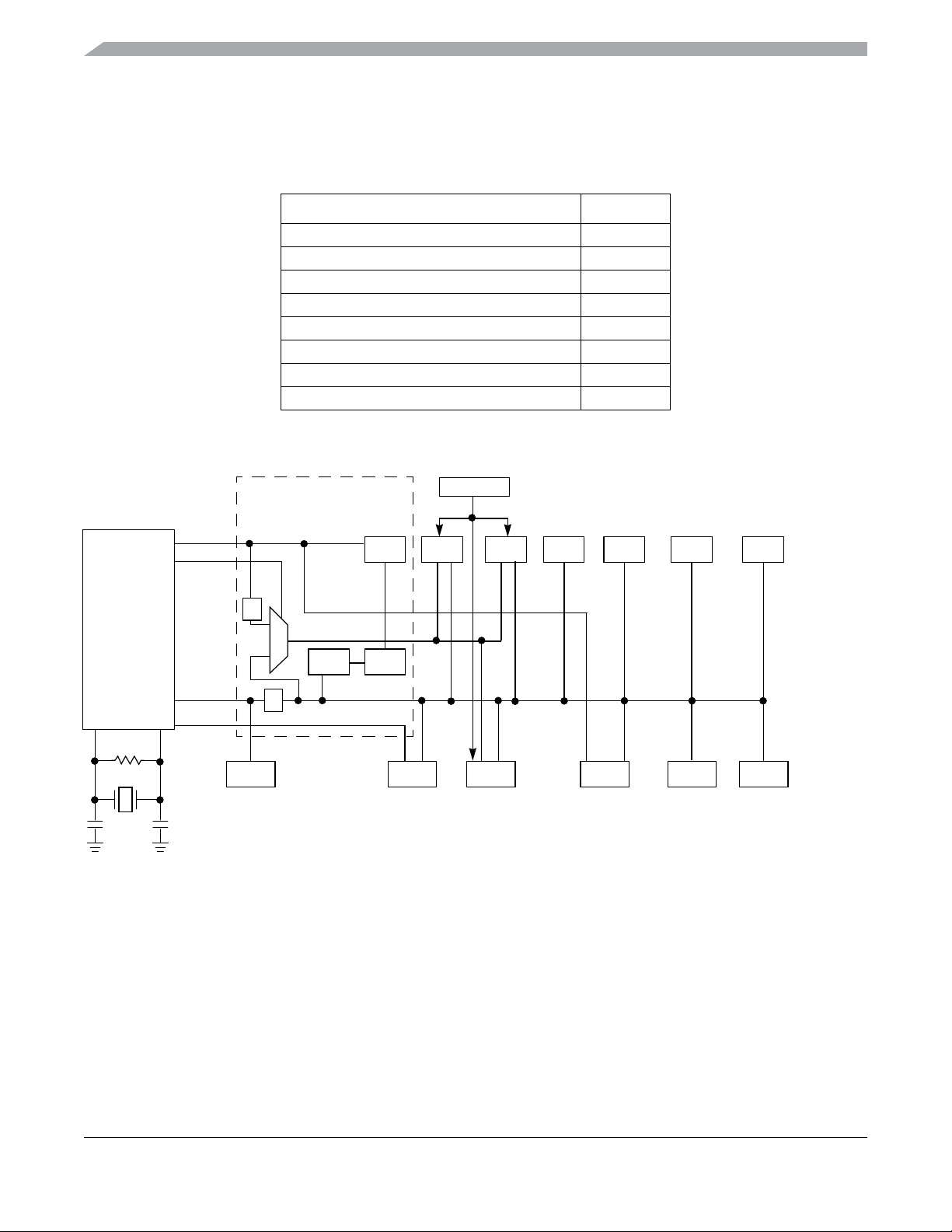

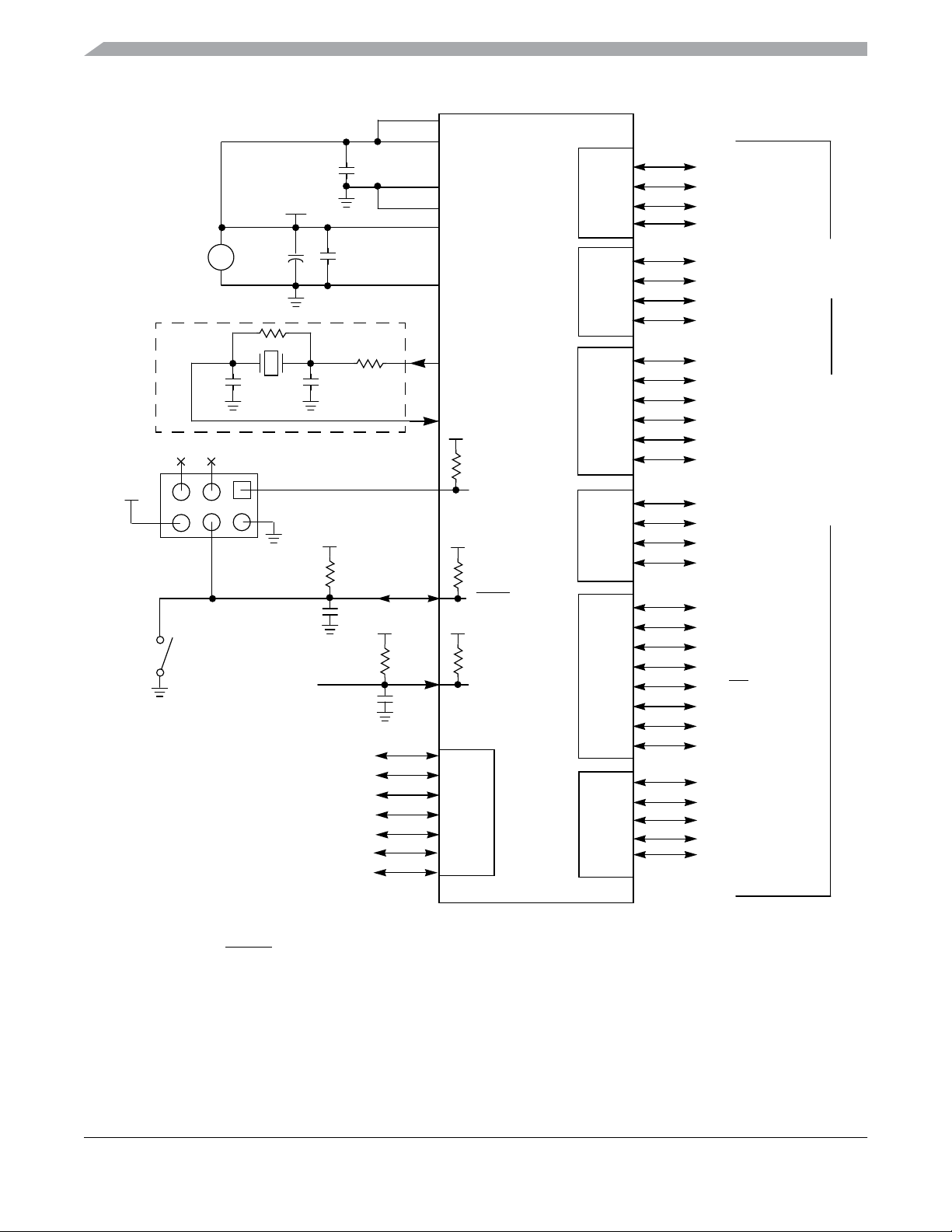

1.2 MCU Block Diagrams

The block diagram shows the structure of the MC9S08AC16 Series MCU.

MC9S08AC16 Series Data Sheet, Rev. 0

20 PRELIMINARY Freescale Semiconductor

Chapter 1 Introduction

0

V

DDAD

V

SSAD

V

REFL

V

REFH

BKGD/MS

RESET

IRQ/TPMCLK

HCS08 CORE

CPUBDC

HCS08 SYSTEM CONTROL

RESET

S AND INTERRUPTS

MODES OF OPERATION

POWER MANAGEMENT

RTI COP

IRQ LVD

USER FLASH

16,384 BYTES

OR 8192 BYTES

USER RAM

1024 BYTES

OR 768 BYTES

TPMCLK

10-BIT

ANALOG-TO-DIGITAL

CONVERTER (ADC1)

DEBUG

MODULE (DBG)

IIC MODULE (IIC1)

INTERNAL CLOCK

GENERATOR (ICG)

LOW-POWER OSCILLATOR

7-BIT KEYBOARD

INTERRUPT MODULE (KBI)

SERIAL COMMUNICATIONS

INTERFACE MODULE (SCI1)

SERIAL COMMUNICATIONS

INTERFACE MODULE (SCI2)

SERIAL PERIPHERAL

INTERFACE MODULE (SPI1)

4-CHANNEL TIMER/PWM

MODULE (TPM1)

2-CHANNEL TIMER/PWM

MODULE (TPM2)

AD1P3–AD1P0

4

4

AD1P11–AD1P8

SDA1

SCL1

EXTAL

XTAL

KBIP6–KBIP5

2

KBIP4–KBIP0

5

RxD1

TxD1

RxD2

TxD2

SPSCK1

MOSI1

MISO1

SS1

TPM1CH1

TPM1CH0

TPM1CH3

TPM1CH2

TPM2CH1

TPM2CH0

PORT A

PORT B

PORT C

PORT D

PORT E

PORT F

PTA7

PTA2

PTA1

PTA0

PTB3/AD1P3

PTB2/AD1P2

PTB1/TPM3CH1 /AD1P1

PTB0/TPM3CH0 /AD1P

PTC5/RxD2

PTC4

PTC3/TxD2

PTC2/MCLK

PTC1/SDA1

PTC0/SCL1

PTD3/KBIP6/AD1P11

PTD2/KBIP5/AD1P10

PTD1/AD1P9

PTD0/AD1P8

PTE7/SPSCK1

PTE6/MOSI1

PTE5/MISO1

PTE4/

SS1

PTE3/TPM1CH1

PTE2/TPM1CH0

PTE1/RxD1

PTE0/TxD1

PTF6

PTF5/TPM2CH1

PTF4/TPM2CH0

PTF1/TPM1CH3

PTF0/TPM1CH2

V

DD

V

SS

VOLTAGE

REGULATOR

= Not available on 32-, or 44-pin packages

= Not available on 32-pin packages

= Not available on 32-pin packages

2-CHANNEL TIMER/PWM

MODULE (TPM3)

TPM3CH1

TPM3CH0

PORT G

PTG6/EXTAL

PTG5/XTAL

PTG4/KBIP4

PTG3/KBIP3

PTG2/KBIP2

PTG1/KBIP1

PTG0/KBIP0

= Not available on S9S08AWxxA devices

Notes:

1. Port pins are software configurable with pullup device if input port.

2. Pin contains software configurable pullup/pulldown device if IRQ is enabled (IRQPE = 1). Pulldown is enabled

if rising edge detect is selected (IRQEDG = 1)

3. IRQ does not have a clamp diode to V

. IRQ should not be driven above VDD.

DD

4. Pin contains integrated pullup device.

5. PTD3, PTD2, and PTG4 contain both pullup and pulldown devices. Pulldown enabled when KBI is enabled

(KBIPEn = 1) and rising edge is selected (KBEDGn = 1).

MC9S08AC16 Series Data Sheet, Rev. 0

Freescale Semiconductor PRELIMINARY 21

Chapter 1 Introduction

Figure 1-1. MC9S08AC16 Block Diagram

Table 1-2 lists the functional versions of the on-chip modules.

Table 1-2. Versions of On-Chip Modules

Module Version

Analog-to-Digital Converter (ADC) 1

Internal Clock Generator (ICG) 4

Inter-Integrated Circuit (IIC) 2

Keyboard Interrupt (KBI) 1

Serial Communications Interface (SCI) 4

Serial Peripheral Interface (SPI) 3

Timer Pulse-Width Modulator (TPM) 3

Central Processing Unit (CPU) 2

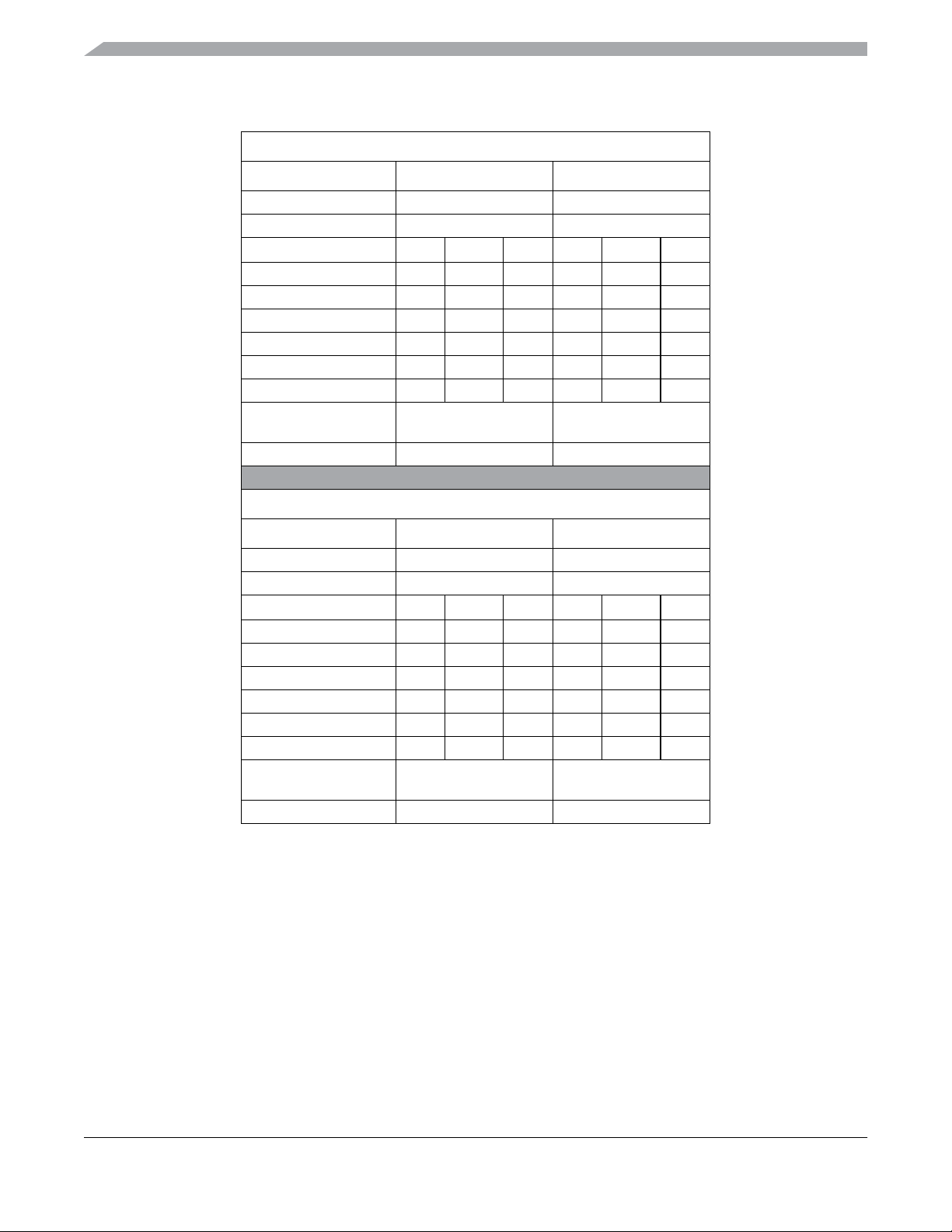

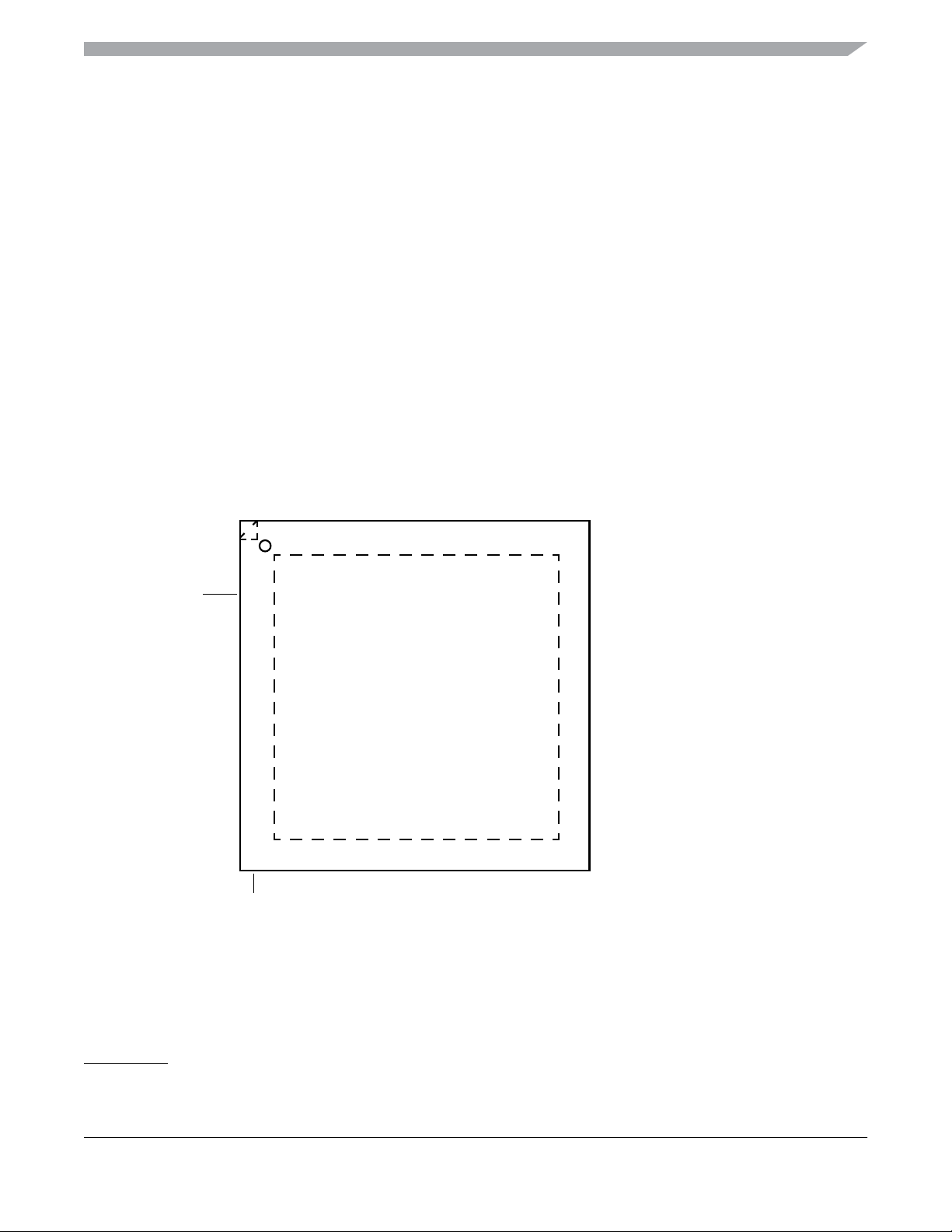

1.3 System Clock Distribution

ICG

SYSTEM

CONTROL

2

LOGIC

2

XCLK**

COP

BUSCLK

RTI

1 kHz

BDCCPU ADC1 RAM FLASH

ICGERCLK

FFE

ICGOUT

ICGLCLK*

* ICGLCLK is the alternate BDC clock source for the MC9S08AC16 Series.

** XCLK is the fixed-frequency clock.

*** TPM3 is not available on S9S08AWxxA devices.

TPMCLK

TPM1 TPM2 IIC1 SCI1 SCI2 SPI1

TPM3***

Figure 1-2. System Clock Distribution Diagram

ADC has min and max

frequency requirements.

See the Electricals appendix

and the ADC chapter.

FLASH has frequency

requirements for program

and erase operation.

See the Electricals

appendix.

Some of the modules inside the MCU have clock source choices. Figure 1-2 shows a simplified clock

connection diagram. The ICG supplies the clock sources:

• ICGOUT is an output of the ICG module. It is one of the following:

— The external crystal oscillator

— An external clock source

MC9S08AC16 Series Data Sheet, Rev. 0

22 PRELIMINARY Freescale Semiconductor

Chapter 1 Introduction

— The output of the digitally-controlled oscillator (DCO) in the frequency-locked loop

sub-module

— Control bits inside the ICG determine which source is connected.

• FFE is a control signal generated inside the ICG. If the frequency of ICGOUT > 4 × the frequency

of ICGERCLK, this signal is a logic 1 and the fixed-frequency clock will be ICGERCLK/2.

Otherwise the fixed-frequency clock will be BUSCLK.

• ICGLCLK — Development tools can select this internal self-clocked source (~ 8 MHz) to speed

up BDC communications in systems where the bus clock is slow.

• ICGERCLK — External reference clock can be selected as the real-time interrupt clock source.

Can also be used as the ALTCLK input to the ADC module.

MC9S08AC16 Series Data Sheet, Rev. 0

Freescale Semiconductor PRELIMINARY 23

Chapter 1 Introduction

MC9S08AC16 Series Data Sheet, Rev. 0

24 PRELIMINARY Freescale Semiconductor

Chapter 2 Pins and Connections

2.1 Introduction

This chapter describes signals that connect to package pins. It includes a pinout diagram, a table of signal

properties, and detailed discussion of signals.

2.2 Device Pin Assignment

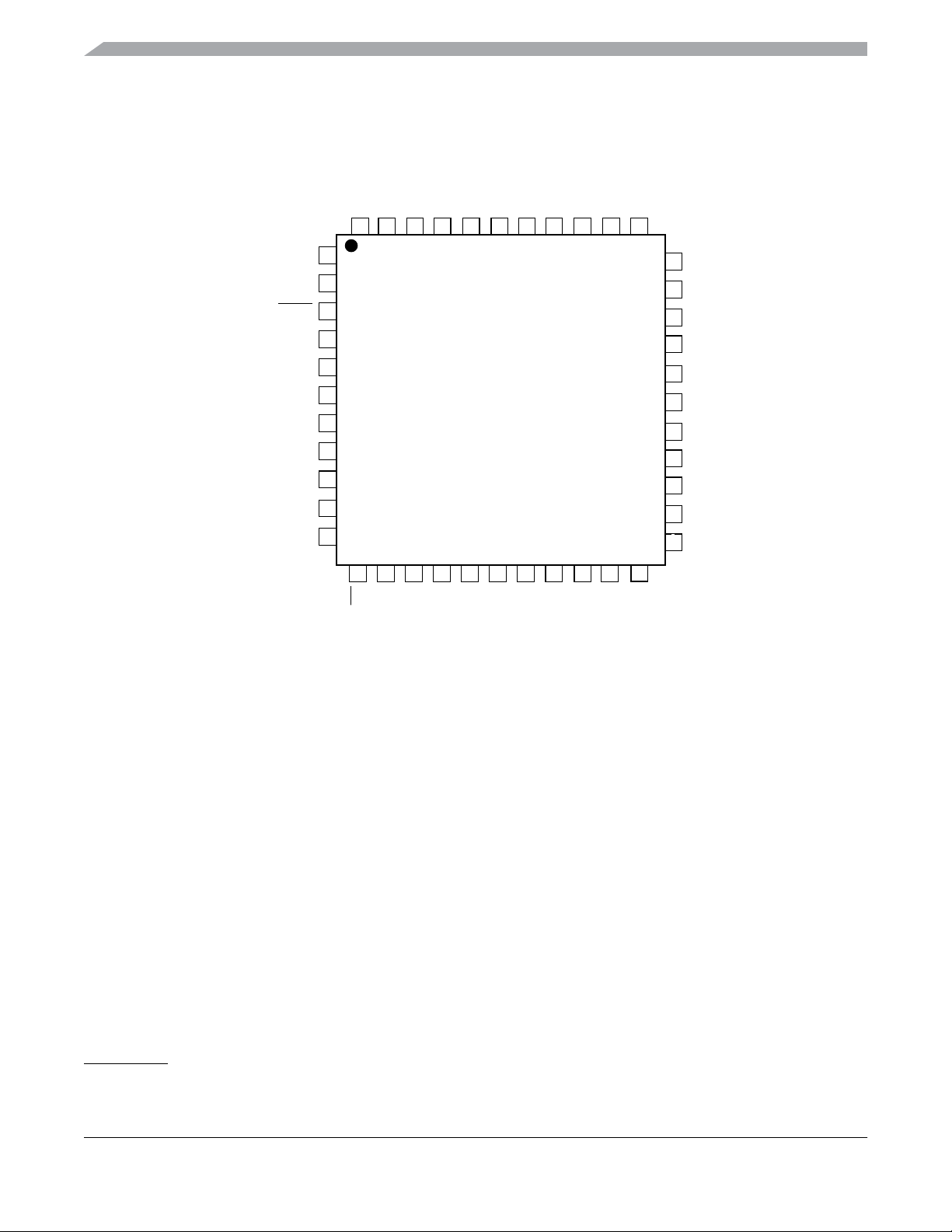

Figure 2-1 shows the 48-pin QFN pin assignments for the MC9S08AC16 Series device.

REFH

REFL

BKGD/MS

V

40

39

V

38

PTG4/KB1IP4

37

PTG3/KBIP3

36

PTD3/KBIP6/AD1P11

35

PTD2/KBIP5/AD1P10

34

V

33

SSAD

V

32

DDAD

PTD1/AD1P9

31

PTD0/AD1P8

30

PTC4

IRQ/TPMCLK

RESET

PTF0/TPM1CH2

PTF1/TPM1CH3

PTF4/TPM2CH0

PTF5/TPM2CH1

1

2

3

4

5

6

7

PTC5/RxD2

PTC3/TxD2

47

48

PTC1/SDA1

PTC2/MCLK

46

45

SS

PTG6/EXTAL

V

PTC0/SCL1

44

43

42

48-Pin QFN

PTG5/XTAL

41

8

PTF6

PTE0/TxD1

PTE1/RxD1

PTE2/TPM1CH0

PTE3/TPM1CH1

9

10

11

12

14

15

16

17

18

19

20

21

13

PTE4/SS1

PTE6/MOSI1

PTE5/MISO1

SS

V

V

PTE7/SPSCK1

DD

PTG1/KBIP1

PTG0/KBIP0

22

PTA0

PTG2/KBIP2

23

PTA1

Figure 2-1. MC9S08AC16 Series in 48-Pin QFN Package

PTB3/AD1P3

29

PTB2/AD1P2

28

27

PTB1/TPM3CH1/AD1P1

PTB0/TPM3CH0/AD1P0

26

PTA7

25

24

PTA2

1

1

1

1. TPM3 not available on the S9S08AWxxA.

MC9S08AC16 Series Data Sheet, Rev. 0

Freescale Semiconductor PRELIMINARY 25

Chapter 2 Pins and Connections

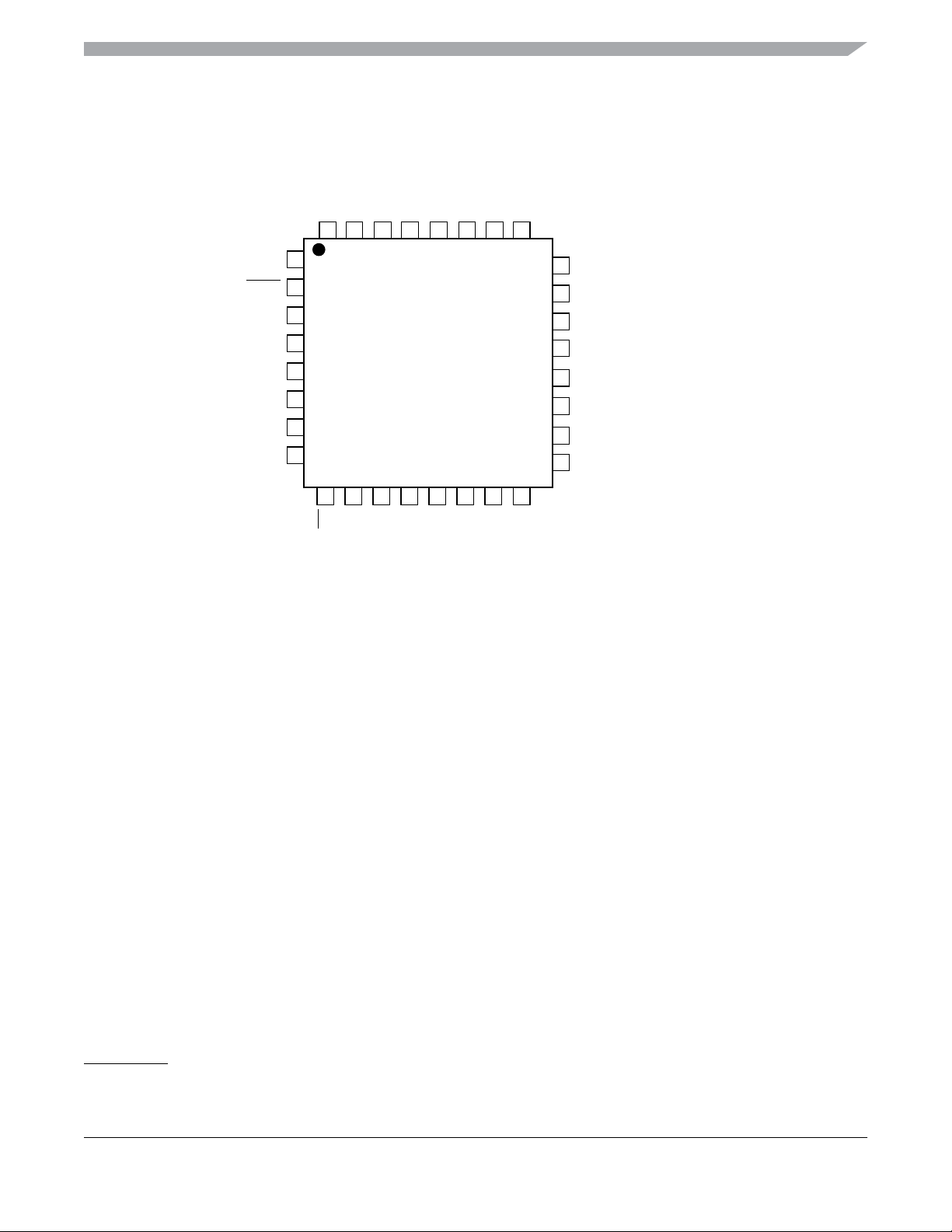

Figure 2-2. shows the 44-pin LQFP pin assignments for the MC9S08AC16 Series device.

PTC4

IRQ/TPMCLK

RESET

PTF0/TPM1CH2

PTF1/TPM1CH3

PTF4/TPM2CH0

PTF5/TPM2CH1

PTE0/TxD1

PTE1/RxD1

PTE2/TPM1CH0

PTE3/TPM1CH1

11

1

PTC5/RxD2

44

2

3

4

5

6

7

8

9

10

12

PTE4/SS1

PTC3/TxD2

PTC2/MCLK

43 42 41

14

13

PTE6/MOSI1

PTE5/MISO1

PTC0/SCL1

PTC1/SDA1

40

44-Pin LQFP

15 16 17

SS

V

PTE7/SPSCK1

SS

V

39

DD

V

PTG6/EXTAL

37

38

18

PTG0/KBIP0

BKGD/MS

PTG5/XTAL

36

20 21

PTG2/KBIP2

PTG1/KBIP1

REFL

V

35

PTA019PTA1

REFH

V

34

PTG3/KBIP3

33

32

PTD3/KBIP6/AD1P11

PTD2/KBIP5/AD1P10

31

V

30

29

28

27

26

25

24

22

SSAD

V

DDAD

PTD1/AD1P9

PTD0/AD1P8

PTB3/AD1P3

PTB2/AD1P2

PTB1/TPM3CH1/AD1P1

PTB0/TPM3CH0/AD1P0

23

1

1

Figure 2-2. MC9S08AC16 Series in 44-Pin LQFP Package

1

1. TPM3 not available on the S9S08AWxxA.

MC9S08AC16 Series Data Sheet, Rev. 0

26 PRELIMINARY Freescale Semiconductor

Chapter 2 Pins and Connections

Figure 2-3. shows the 32-pin LQFP pin assignments for the MC9S08AC16 Series device.

IRQ/TPMCLK

RESET

PTF4/TPM2CH0

PTF5/TPM2CH1

PTE0/TxD1

PTE1/RxD1

PTE2/TPM1CH0

PTE3/TPM1CH1

Figure 2-3. MC9S08AC16 Series in 32-Pin LQFP Package

PTC1/SDA1

SS

V

PTC0/SCL1

PTG6/EXTAL

PTG5/XTAL

BKGD/MS

REFL

V

REFH

V

32

1

31 30 29 28

2

3

4

32-Pin LQFP

5

6

7

8

11

10

12 13 14

27

PTD3/AD1P11/KBIP6

24

23

PTD2/AD1P10/KBIP5

22

V

SSAD

21

V

DDAD

20

PTB3/AD1P3

PTB2/AD1P2

19

18

PTB1/TPM3CH1/AD1P1

17

PTB0/TPM3CH0/AD1P0

16

15

1

1

25

26

9

SS

DD

V

V

PTE4/SS1

PTE6/MOSI1

PTE5/MISO1

PTE7/SPSCK1

PTG1/KBIP1

PTG0/KBIP0

1

1. TPM3 not available on the S9S08AWxxA.

MC9S08AC16 Series Data Sheet, Rev. 0

Freescale Semiconductor PRELIMINARY 27

Chapter 2 Pins and Connections

Table 2-1. Pin Availability by Package Pin-Count

Pin Number <-- Lowest Priority --> Highest

48 44 32 Port Pin Alt 1 Alt 2

1 1 — PTC4

2 2 1 IRQ TPMCLK

332

RESET

4 4 — PTF0 TPM1CH2

5 5 — PTF1 TPM1CH3

6 6 3 PTF4 TPM2CH0

7 7 4 PTF5 TPM2CH1

8 — — PTF6

9 8 5 PTE0 TxD1

10 9 6 PTE1 RxD1

11 10 7 PTE2 TPM1CH0

12 11 8 PTE3 TPM1CH1

13 12 9 PTE4

SS1

14 13 10 PTE5 MISO1

15 14 11 PTE6 MOSI1

16 15 12 PTE7 SPSCK1

17 16 13 V

18 17 14 V

SS

DD

19 18 15 PTG0 KBIP0

20 19 16 PTG1 KBIP1

21 20 — PTG2 KBIP2

22 21 — PTA0

23 22 — PTA1

24 — — PTA2

Pin Number <-- Lowest Priority --> Highest

48 44 32 Port Pin Alt 1 Alt 2

25 — — PTA7

1

1

AD1P0

AD1P1

26 23 17 PTB0 TPM3CH0

27 24 18 PTB1 TPM3CH1

28 25 19 PTB2 AD1P2

29 26 20 PTB3 AD1P3

30 27 — PTD0 AD1P8

31 28 — PTD1 AD1P9

32 29 21 V

33 30 22 V

DDAD

SSAD

34 31 23 PTD2 AD1P10 KBIP5

35 32 24 PTD3 AD1P11 KBIP6

36 33 — PTG3 KBIP3

37 — — PTG4 KBIP4

38 34 25 V

39 35 26 V

REFH

REFL

40 36 27 BKGD MS

41 37 28 PTG5 XTAL

42 38 29 PTG6 EXTAL

43 39 30 V

SS

44 40 31 PTC0 SCL1

45 41 32 PTC1 SDA1

46 42 — PTC2 MCLK

47 43 — PTC3 TxD2

48 44 — PTC5 RxD2

1

TPM3 not available on S9S08AWxxA.

Table 2-2. Pin Function Reference

Signal Function Example(s) Reference

Port Pins PTAx, PTBx Chapter 6, “Parallel Input/Output”

Serial peripheral interface

Keyboard interrupts KBIPx Chapter 9, “Keyboard Interrupt (S08KBIV1)”

Timer/PWM TCLK, TPMCHx Chapter 10, “Timer/PWM (S08TPMV3)”

Inter-integrated circuit SCL, SDA Chapter 13, “Inter-Integrated Circuit (S08IICV2)”

Serial communications interface TxD, RxD Chapter 11, “Serial Communications Interface (S08SCIV4)”

Oscillator/clocking EXTAL, XTAL Chapter 8, “Internal Clock Generator (S08ICGV4)”

Analog-to-digital ADPx Chapter 14, “Analog-to-Digital Converter (S08ADC10V1)”

Power/core BKGD/MS, V

Reset and interrupts

28 PRELIMINARY Freescale Semiconductor

SS, MISO, MOSI, SPSCK Chapter 12, “Serial Peripheral Interface (S08SPIV3)”

DD

, V

SS

Chapter 2, “Pins and Connections”

RESET, IRQ Chapter 5, “Resets, Interrupts, and System Configuration”

MC9S08AC16 Series Data Sheet, Rev. 0

Chapter 2 Pins and Connections

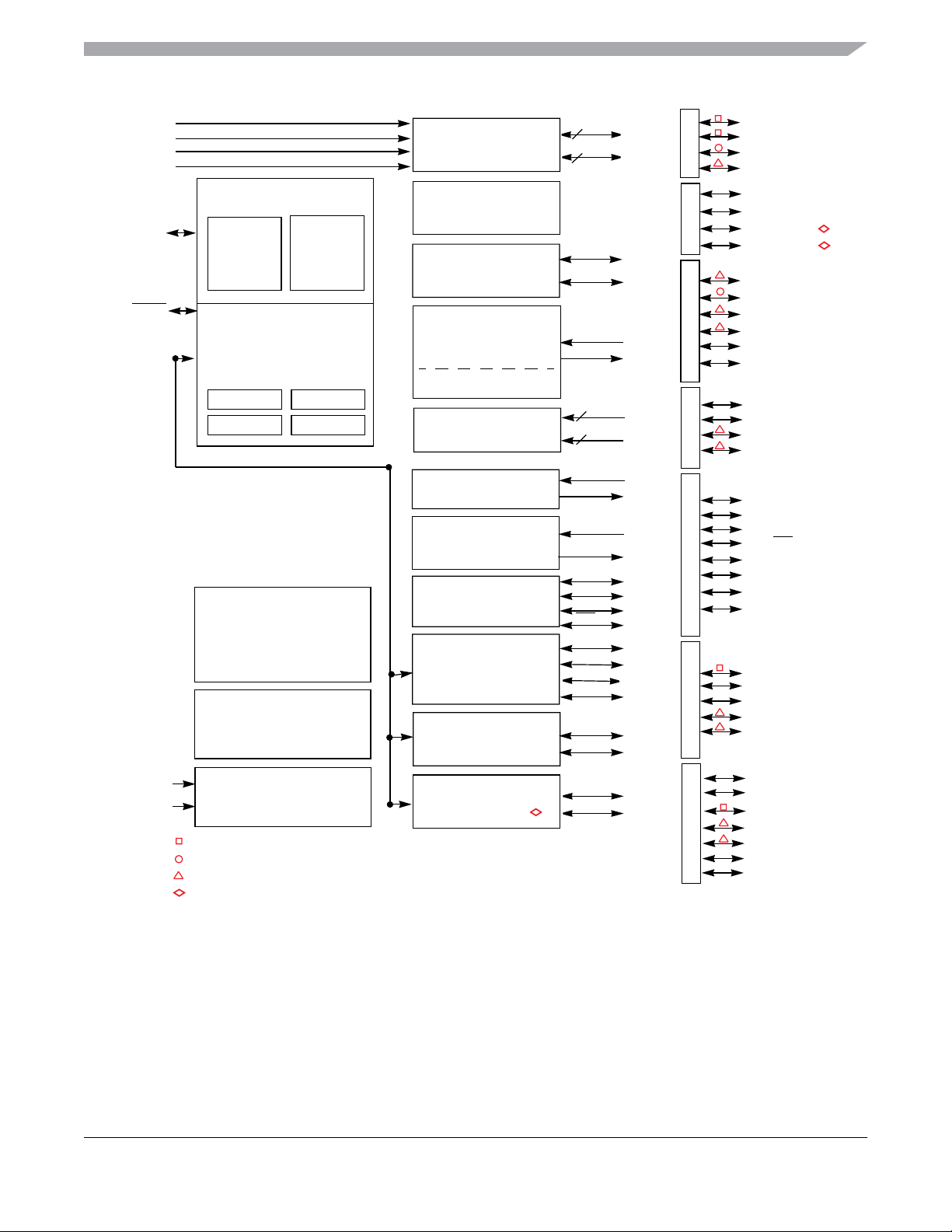

2.3 Recommended System Connections

Figure 2-4 shows pin connections that are common to almost all MC9S08AC16 Series application

systems.

MC9S08AC16 Series Data Sheet, Rev. 0

Freescale Semiconductor PRELIMINARY 29

Chapter 2 Pins and Connections

SYSTEM

POWER

+

C

5 V

10 μF

NOTE 1

C1

BACKGROUND HEADER

V

DD

OPTIONAL

MANUAL

RESET

ASYNCHRONOUS

INTERRUPT

BLK

X1

INPUT

V

DD

+

R

F

PTG4/KBIP4

C

BY

0.1 μF

C2

V

DD

4.7 kΩ–10 kΩ

0.1 μF

PTG0/KBIP0

PTG1/KBIP1

PTG2/KBIP2

PTG3/KBIP3

PTG5/XTAL

PTG6/EXTAL

C

BYAD

0.1 μF

R

S

V

DD

4.7 kΩ–

10 kΩ

0.1 μF

V

REFH

V

DDAD

V

SSAD

V

REFL

V

DD

VSS(x2)

XTAL

NOTE 2

EXTAL

NOTE 2

PORT

G

MC9S08AC16

BKGD/MS

RESET

NOTE 3

TPMCLK/IRQ

NOTE 3

PORT

A

PORT

B

PORT

C

PORT

D

PORT

E

PORT

F

PTA0

PTA1

PTA2

PTA7

PTB0/AD1P0/TPM3CH0 NOTE 4

PTB1/AD1P1/TPM3CH1 NOTE 4

PTB2/AD1P2

PTB3/AD1P3

PTC0/SCL1

PTC1/SDA1

PTC2/MCLK

PTC3/TxD2

PTC4

PTC5/RxD2

I/O AND

PERIPHERAL

INTERFACE TO

APPLICATION

PTD0/AD1P8

SYSTEM

PTD1/AD1P9

PTD2/AD1P10/KBIP5

PTD3/AD1P11/KBIP6

PTE0/TxD1

PTE1/RxD1

PTE2/TPM1CH0

PTE3/TPM1CH1

PTE4/

SS1

PTE5/MISO1

PTE6/MOSI1

PTE7/SPSCK1

PTF0/TPM1CH2

PTF1/TPM1CH3

PTF4/TPM2CH0

PTF5/TPM2CH1

PTF6

NOTES:

1. Not required if using the internal clock option.

2. XTAL and EXTAL are PTG5 and PTG6 respectively.

3. RC filters on

RESET and IRQ are recommended for EMC-sensitive applications.

4. TPM3 is not available on S9S08AWxxA.

Figure 2-4. Basic System Connections

MC9S08AC16 Series Data Sheet, Rev. 0

30 PRELIMINARY Freescale Semiconductor

Loading...

Loading...