Freescale Semiconductor

Technical Data

MPC866/MPC859 Hardware Specifications

MPC866EC

Rev. 2, 2/2006

This document contains detailed information on power

considerations, DC/AC electrical characteristics, and AC timing

specifications for the MPC866/859 family (refer to Table 1 for a

list of devices). The MPC866P is the superset device of the

MPC866/859 family.This document describe s pertinent electrical

and physical characteristics of the MPC8245. For functional

characteristics of the processor, refer to the MPC866

PowerQUICC Family Users Manual (MPC866UM/D).

1Overview

The MPC866/859 is a derivative of Freesca le’s MPC860

PowerQUICC™ family of devices. It is a versatile single-chip

integrated mic roprocessor and per ipher al combin ation th at can be

used in a variety of controller applications and communications

and networking systems. The MPC866/859/859DSL provides

enhanced ATM func tionality over that of other ATM- enable d

members of the MPC860 family.

Contents

1. Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

2. Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

3. Maximum Tolerated Ratings . . . . . . . . . . . . . . . . . . . 8

4. Thermal Characteristics . . . . . . . . . . . . . . . . . . . . . . . 9

5. Power Dissipation . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

6. DC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . 10

7. Thermal Calculation and Measurement . . . . . . . . . . 12

8. Power Supply and Power Sequencing . . . . . . . . . . . 15

9. Layout Practices . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

10. Bus Signal Timing . . . . . . . . . . . . . . . . . . . . . . . . . . 16

11. IEEE 1149.1 Electrical Specifications . . . . . . . . . . . 46

12. CPM Electrical Characteristics . . . . . . . . . . . . . . . . . 48

13. UTOPIA AC Electrical Specifications . . . . . . . . . . . 72

14. FEC Electrical Characteristics . . . . . . . . . . . . . . . . . 74

15. Mechanical Data and Ordering Information . . . . . . . 78

16. Document Revision History . . . . . . . . . . . . . . . . . . . 93

© Freescale Semiconductor, Inc., 2006. All rights reserved.

Features

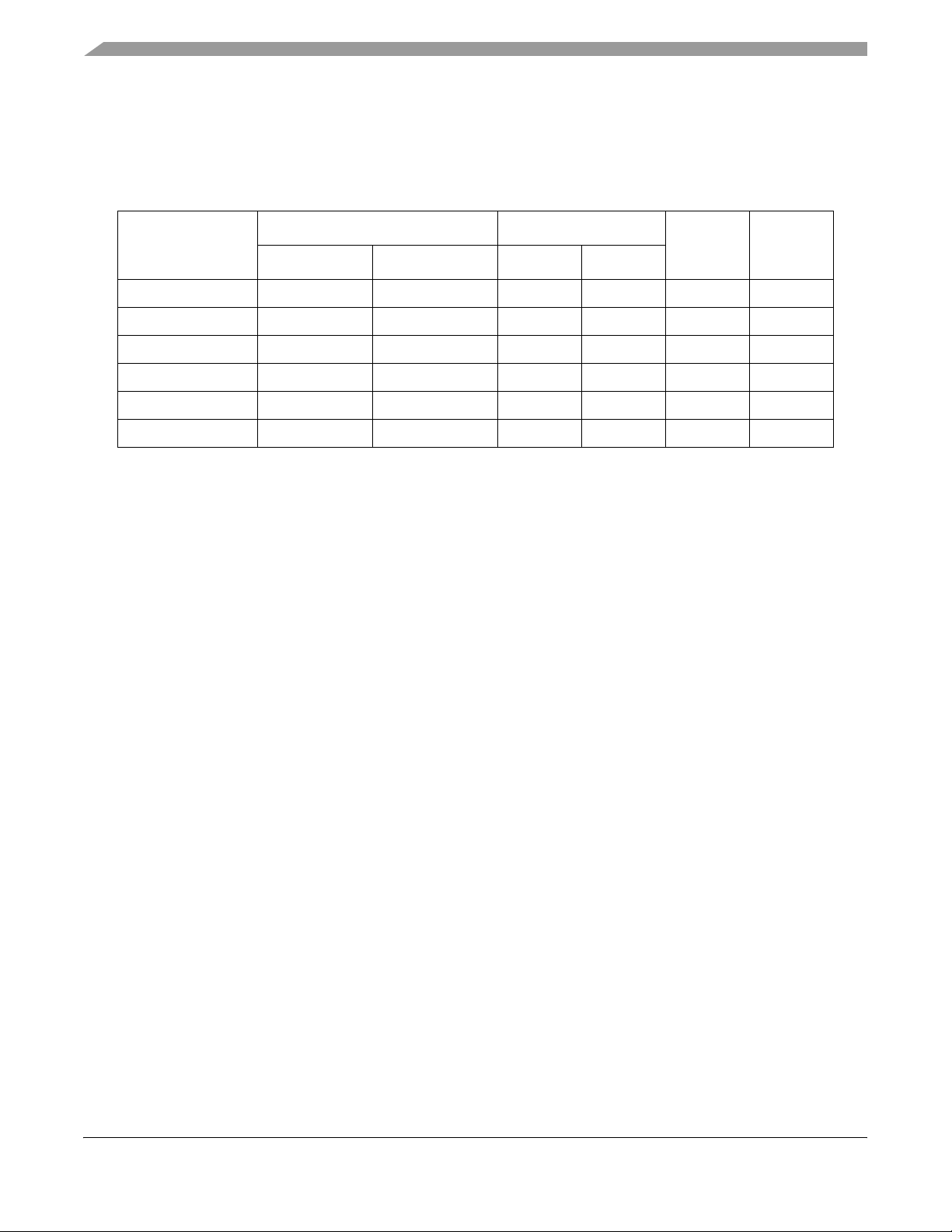

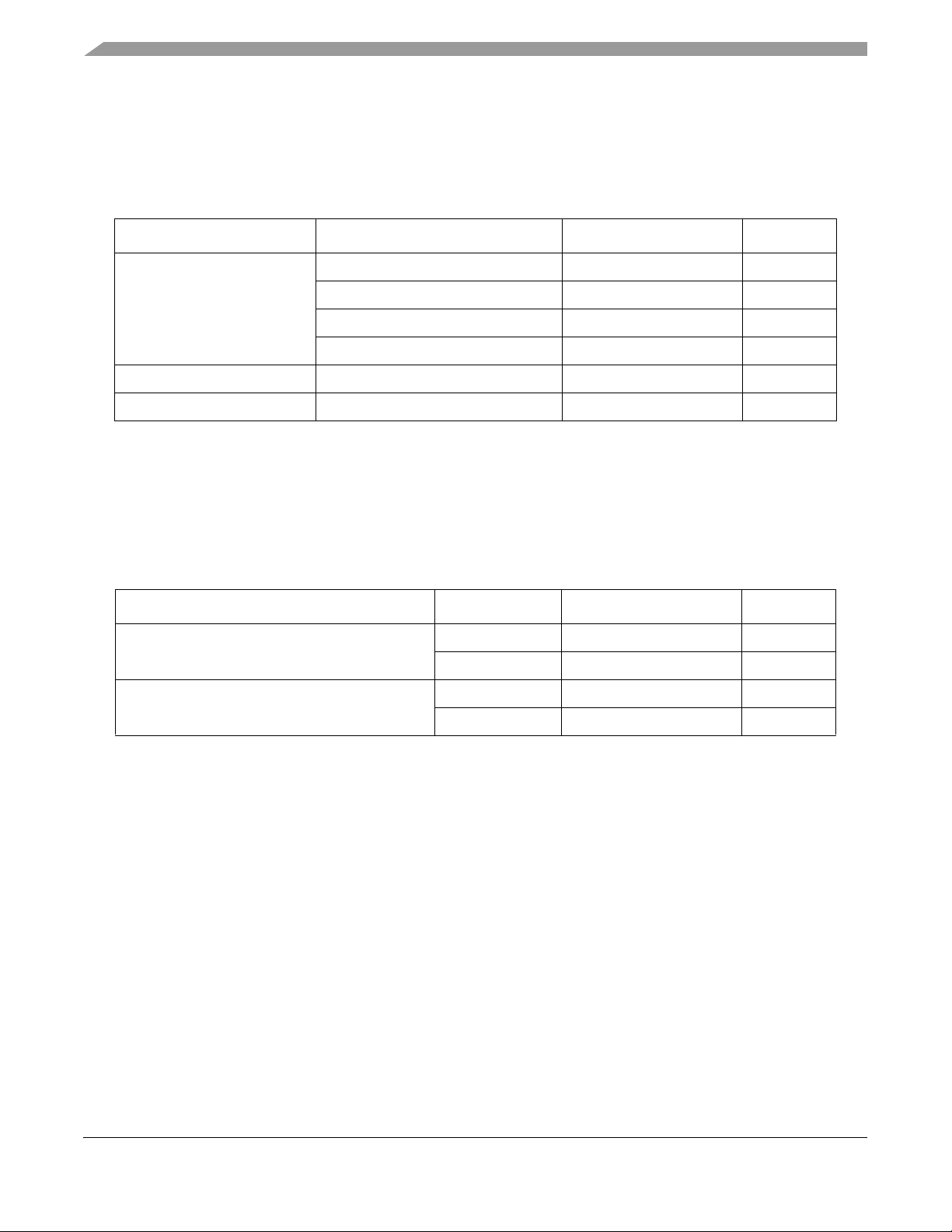

Table 1 shows the functionality supported by the members of the MPC866/859 family.

2Features

Table 1. MPC866 Family Functionality

Cache Ethernet

Par t

Instruction Data 10T 10/100

MPC866P 16 Kbytes 8 Kbytes Up to 4 1 4 2

MPC866T 4 Kbytes 4 Kbytes Up to 4 1 4 2

MPC859P 16 Kbytes 8 Kbytes 1112

MPC859T 4 Kbytes 4 Kbytes 1112

MPC859DSL 4 Kbytes 4 Kbytes 1 1 1

MPC852T

1

On the MPC859DSL, the SCC (SCC1) is for ethernet only. Also, the MPC859DSL does not support the Time Slot

Assigner (TSA).

2

On the MPC859DSL, the SMC (SMC1) is for UART only.

3

For more details on the MPC852T, please refer to the

3

4 KBytes4 Kbytes2121

MPC852T Hardware Specifications.

SCC SMC

1

1

2

The following list summarize s the key MPC866/859 features:

• Embedded single-issue , 32- bit PowerPC™ core (implementing the PowerPC architecture) with

thirty-two 32-bit general-purpose registers (GPRs)

— The core performs branch predi ct ion with conditional prefetch, without conditional execution

— 4- or 8-Kbyte data cache and 4- or 16-Kbyte instruction cache (see Table 1)

– 16-Kbyte instruction cache (MPC866P and MPC859P) is four-way, set-associative with 256 sets;

4-Kbyte instruction cache (MPC866T, MPC859T, and MPC859DSL) is two-wa y, set- associative

with 128 sets.

– 8-Kbyte data cache (MPC866P and MPC859P) is two-way, set-associative with 256 sets; 4-Kbyte

data cache(MPC866T, MPC859T, and MPC859DSL) is two-way, set-associative with 128 sets.

– Cache coherency for both instruction and data caches is maintained on 128-bit (4-word) cache

blocks

– Caches are physic ally addresse d, implement a least rec ently used (LRU) replacement a lgorithm, and

are lockable on a cache block basis.

— MMUs with 32-entry TLB, fully associative instruction and data TLBs

— MMUs support multiple page sizes of 4, 16, and 512 Kbytes, and 8 Mbytes; 16 virtual address spaces

and 16 protection groups.

— Advanced on-chip-emulation debug mode

• The MPC866/859 provides enhanced ATM functionality over that of the MPC860 SAR. The MPC866/859

adds major new features avail able in 'enhanced SAR' (ESAR) mode, including the following:

— Improved operation, administration, and maintenance (OAM) support

— OAM performance monitoring (PM) support

— Multiple APC priority leve ls available to support a range of traff ic pace requirements

MPC866/MPC859 Hardware Specifications, Rev. 2

2 Freescale Semiconductor

— ATM port-to-port switching capability without the need for RAM-based microcode

— Simultaneous MII (10/100Ba se-T) and UTOPIA (half-duplex) capability

— Optional statistical cell counters per PHY

— UTOPIA level 2 compliant inte rface with added FIFO buffering to reduce the total cell transmission

time. (The earlier UTOPIA level 1 specification is also supported.)

– Multi-PHY support on the MPC866, MPC859P, and MPC859T

– Four PHY support on the MPC866/859

2

— Parameter RAM for both SPI and I

C can be relocated without RAM-based microcode

— Supports full- duplex UTOPI A both master (ATM side) and slave ( PHY side) oper ation using a 'split ' bus

— AAL2/VBR functionality is ROM-res ident.

• Up to 32-bit data bus (dynamic bus sizing for 8, 16, and 32 bits)

• Thirty-two address lines

• Memory controller (eight banks)

— Contains complete dynamic RAM (DRAM) controller

— Each bank can be a chi p select or RAS

to support a DRAM bank

— Up to 30 wait states programmable per memory bank

— Glueless interfa ce to page mode/EDO/S DRAM, SRAM, EPROMs, flash EPROMs, and other memory

devices.

— DRAM controller programmable to support most size and speed memory interfaces

— Four CAS

lines, four WE lines, and one OE line

— Boot chip-select avai lable at reset (options for 8-, 16-, or 32-bit memory)

— Variable block sizes (32 Kbytes–256 Mbytes)

— Selectable write protection

— On-chip bus arbitrat ion logic

• General-purpose timers

— Four 16-bit timers casca dable to be two 32-bit timers

— Gate mode can enab l e/d isa b le coun t ing

— Interrupt can be masked on reference match and event capture

• Fast Ethernet controller (FEC)

— Simultaneous MII (10/100Ba se-T) and UTOPIA operation when using the UTOPIA multip lexed bus

• System integration unit (SIU)

— Bus monitor

— Software watchdog

— Periodic interrupt timer (PIT)

— Low-power stop mode

— Clock synthesizer

— Decrementer and time base from the PowerPC architecture

— Reset controller

— IEEE 1149.1 test access port (JTAG)

Features

MPC866/MPC859 Hardware Specifications, Rev. 2

Freescale Semiconductor 3

Features

• Interrupts

— Seven external interrupt request (IRQ) l ines

— T welve port pins with interrupt capability

— The MPC866P and MPC866T have 23 internal interrupt sour ces; the MPC859P, MPC859T, and

MPC859DSL have 20 internal interru pt sources.

— Programmable priority between SCCs (MPC866P and MPC866T)

— Programmable highest pri ority request

• Communications processor module (CPM)

— RISC controller

— Communication-spec ific commands (for example ,

RESTART TRANSMIT)

GRACEFUL STOP TRANSMIT, ENTER HUNT MODE, and

— Supports continuous mode tr ansmission and reception on all serial channe ls

— Up to 8-Kbytes of dual-port RAM

— MPC866P and MPC866T have 16 serial DMA (SDMA) channels; MPC859P, MPC859T, and

MPC859DSL have 10 serial DMA (SDMA) channels.

— Three para lle l I/O regist ers with ope n -drai n capab i lity

• Four baud rate generators

— Independent (can be connected to any SCC or SMC)

— Allow changes during operation

— Autobaud support option

• MPC866P and MPC866T have four SCCs (serial communication controller); MPC859P, MPC859T, and

MPC859DSL have one SCC; and SCC1 on MPC859DSL supports Ethernet only.

— Serial ATM capability on all SCCs

— Optional UTOPIA port on SCC4

— Ethernet/IEEE 802.3 optional on SCC1–4, supporting full 10-Mbps operation

— HDLC/SDLC

— HDLC bus (implements an HDLC-based local area network (LAN))

— Asynchronous HDLC to support PPP (point-to-point protocol)

— AppleTalk

— Universal asynchro nous receiver transmitter (UART)

— Synchronous UART

— Serial infrared (Ir DA)

— Binary synchronous communication (BISYNC)

— T otally transparent (bit str eams)

— T otally transparent (fra me based with optional cyclic redundancy check (CRC)

• Two SMCs (serial management channels) (MPC859DSL has one SMC (SMC1) for UART.)

— UART

— Transparent

— General circuit interface (GCI) controller

— Can be connected to the time-division multiplexed (TDM) channels

MPC866/MPC859 Hardware Specifications, Rev. 2

4 Freescale Semiconductor

Features

• One serial peripheral interface (SPI)

— Supports master and slave modes

— Supports multiple-m aster operation on the same bus

2

• One inter-i ntegrated circuit (I

C) port

— Supports master and slave modes

— Multiple-master en vironment support

• Time slot assigner (TSA) (MPC859DSL does not have TSA.)

— Allows SCCs and SMCs to run in multiplexed and/or non-multiplexed operation

— Supports T1, CEPT, PCM highway, ISDN basic rate, ISDN primary rate, user -defined

— 1- or 8-bit resolution

— Allows independent transm it and receive routing, frame synchronization, and clocking

— Allows dynamic changes

— On MPC866P and MPC866T , can be internally connected to six serial channels (four SCCs and two

SMCs); on MPC859P and MPC859T, can be connected to three serial channe ls (one SCC and two

SMCs).

• Parallel interface port (PIP)

— Centronics interface support

— Supports fast connection between compatible ports on MPC866/859 or MC68360

• PCMCIA interface

— Master (socket) interface, compliant with PCI Local Bus Specification (Rev 2.1)

— Supports one or two PCMCIA sockets whether ESAR functio nality is enabled

— Eight memory or I/O windows supported

• Debug interface

— Eight comparators : four operate on instr uction add ress, two operate on data address, and two ope rate on

data.

— Supports conditions: = ≠ < >

— Each watchpoint can generate a breakpoint internally

• Normal high and normal low power modes to conserve power

• 1.8 V core and 3.3 V I/O operation with 5-V TTL compatibility; refer to Table 6 for a listing of the 5-V

tolerant pins.

• 357-pin plastic ball grid array (PBGA) package

• Operation up to 133 MHz

MPC866/MPC859 Hardware Specifications, Rev. 2

Freescale Semiconductor 5

Features

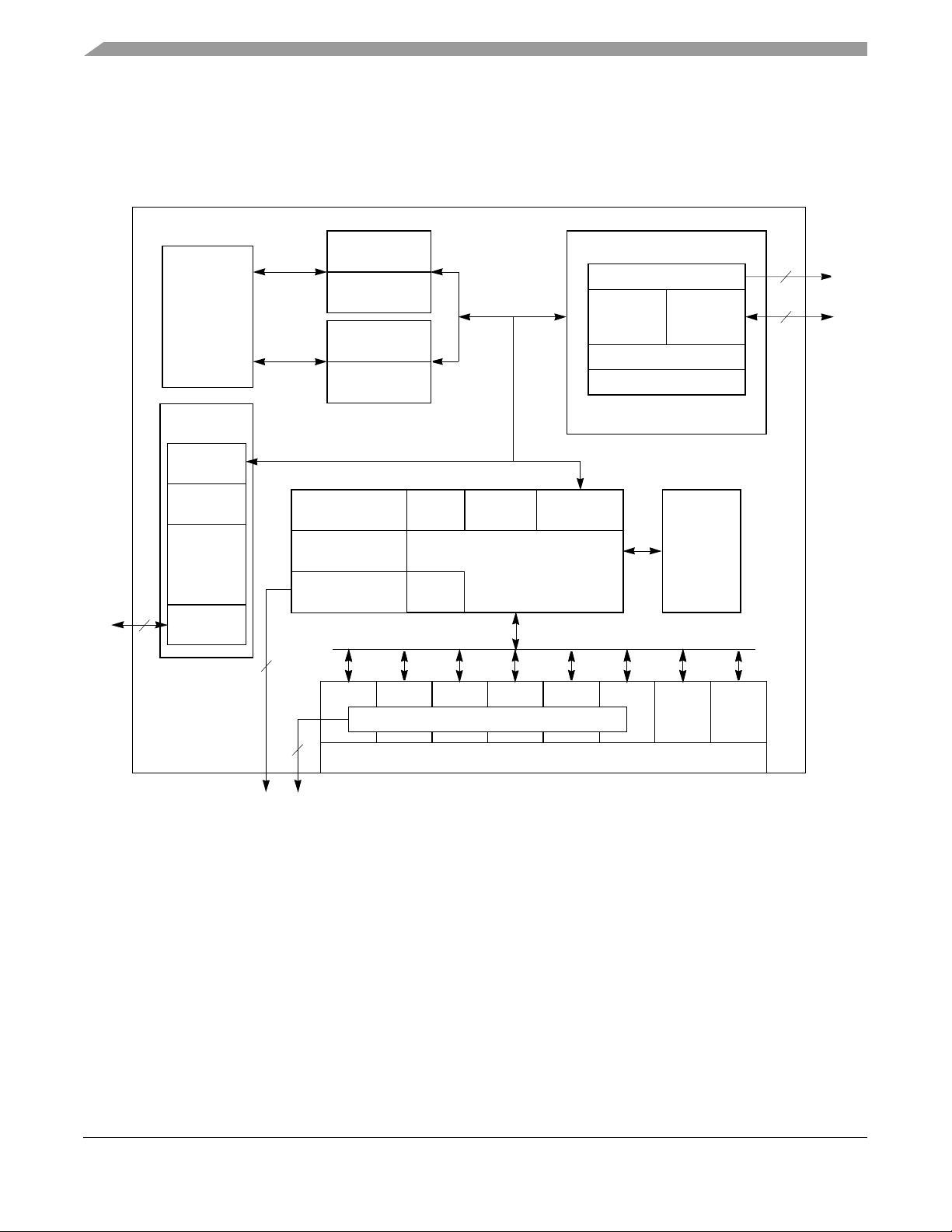

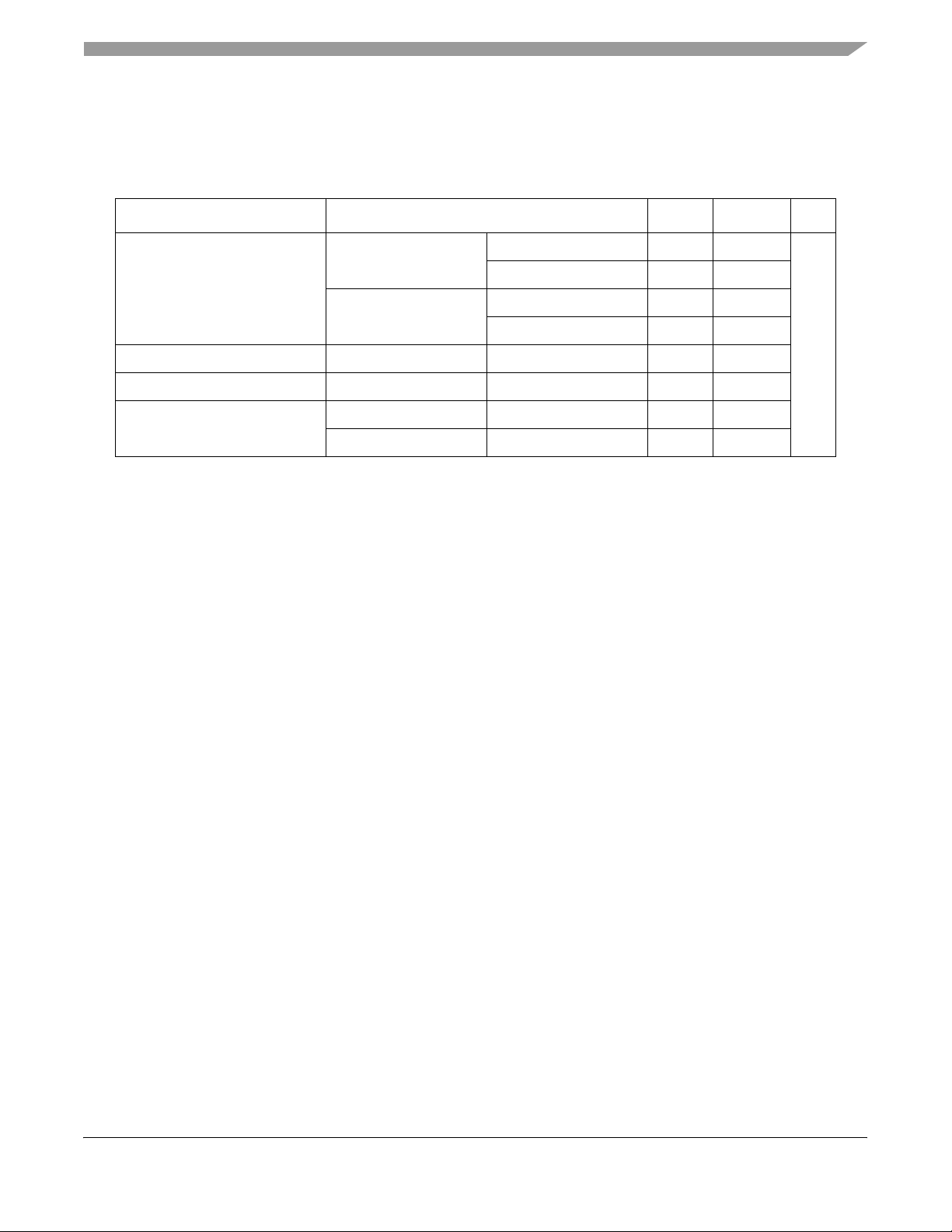

The MPC866/859 is comprised of three modules that each use a 32-bit internal bus: MPC8xx core, system

integration unit (SIU), and communication processor module (CPM). The MPC866P block diagram is shown in

Figure 1. The MPC859P/859T/859DSL block diagram is shown in Figure 2.

Embedded

MPC8xx

Processor

Core

Fast Ethernet

Controller

DMAs

FIFOs

10/100

Base-T

Media Access

Control

MII

Instruction

Bus

Load/Store

Bus

Parallel I/O

4 Baud Rate

Generators

Parallel Interface Port

and UTOPIA

16-Kbyte

Instruction Cache

Instruction MMU

32-Entry ITLB

8-Kbyte

Data Cache

Data MMU

32-Entry DTLB

SCC1

Unified

Bus

4

Interrupt

Timers

Timers

Controllers

32-Bit RISC Controller

and Program

ROM

SCC3 SCC4

Time Slot Assigner

Time Slot Assigner

System Interface Unit (SIU)

Bus Interface

8-Kbyte

Dual-Port RAM

Memory Controller

Internal

Unit

System Functions

PCMCIA/ATA Interface

External

Bus Interface

Unit

16 Virtual

Serial

and

2

Independent

DMA

Channels

I2CSPISMC2SMC1SCC2

Serial Interface

Figure 1. MPC866P Block Diagram

MPC866/MPC859 Hardware Specifications, Rev. 2

6 Freescale Semiconductor

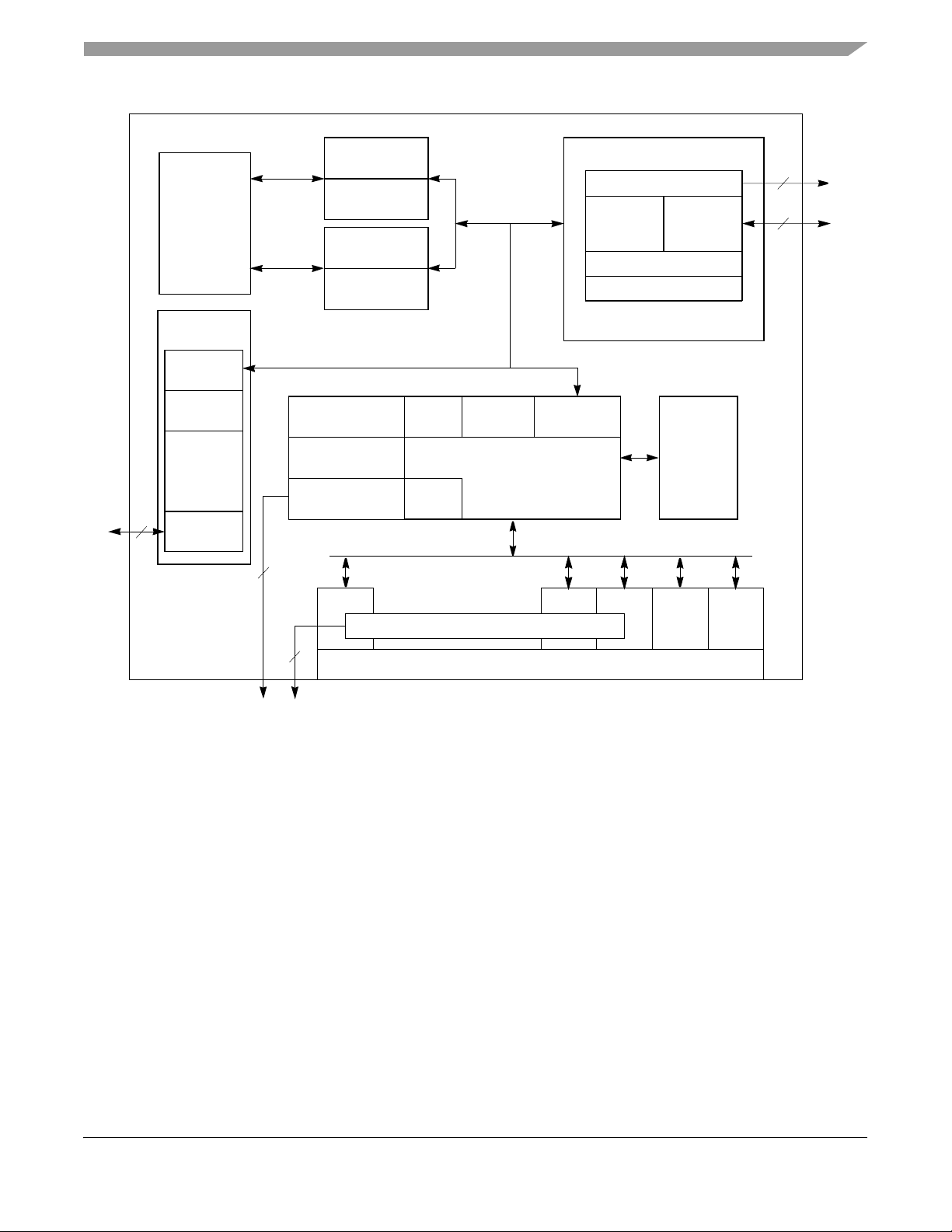

Embedded

MPC8xx

Processor

Core

Fast Ethernet

Controller

DMAs

FIFOs

10/100

Base-T

Media Access

Control

MII

Instruction

Bus

Load/Store

Bus

Parallel I/O

4 Baud Rate

Generators

Parallel Interface Port

and UTOPIA

†

4-Kbyte

Instruction Cache

Instruction MMU

32-Entry ITLB

†

4-Kbyte

Data Cache

Data MMU

32-Entry DTLB

4

Timers

Controllers

32-Bit RISC Controller

Timers

Unified

Bus

Interrupt

and Program

ROM

System Interface Unit (SIU)

Bus Interface

8-Kbyte

Dual-Port RAM

Memory Controller

Internal

External

Bus Interface

Unit

Unit

System Functions

PCMCIA/ATA Interface

10 Virtual

Serial

and

2

Independent

DMA

Channels

Features

SCC1

Time Slot Assigner

Time Slot Assigner*

I2CSPISMC2*SMC1

Serial Interface

†

The MPC859P has a 16-Kbyte instruction cache and a 8-Kbyte data cache.

* The MPC859DSL does not contain SMC2 nor the time slot assigner, and provides eight SDMA

controllers.

Figure 2. MPC859P/859T/MPC859DSL Block Diagram

MPC866/MPC859 Hardware Specifications, Rev. 2

Freescale Semiconductor 7

Maximum Tolerated Ratings

3 Maximum Tolerated Ratings

This section provides the maximum tolerated voltage and temperature ranges for the MPC866/859. Table 2 shows

the maximum tolerated ratings, and Table 3 shows the operating temperatures.

Table 2. Maximum Tolerated Ratings

Rating Symbol Value Unit

Supply voltage

Input voltage

Storage temperature range T

1

The power supply of the device must start its ramp from 0.0 V.

2

Functional operating conditions are provided with the DC electrical specifications in Tab l e 6 . Absolute maximum

ratings are stress ratings only; functional operation at the maxima is not guaranteed. Stress beyond those listed may

affect device reliability or cause permanent damage to the device. See page 15.

Caution: All inputs that tolerate 5 V cannot be more than 2.5 V greater than VDDH. This restriction applies to

power-up and normal operation (that is, if the MPC866/859 is unpowered, a voltage greater than 2.5 V must not be

applied to its inputs).

1

2

VDDH – 0.3 to 4.0 V

VDDL – 0.3 to 2.0 V

VDDSYN – 0.3 to 2.0 V

Difference between VDDL to VDDSYN 100 mV

V

in

stg

GND – 0.3 to VDDH V

–55 to +150 °C

Table 3. Operating Temperatures

Rating Symbol Value Unit

Temperature

Temperature (extended) T

1

Minimum temperatures are guaranteed as ambient temperature, TA. Maximum temperatures are guaranteed as

junction temperature, T

1

(standard)

T

A(min)

T

j(max)

A(min)

T

j(max)

.

j

0°C

95 °C

–40 °C

100 °C

This device contains circ uitry protecting against damage due to high- sta tic voltage or electrical fiel ds; however, it

is advised that nor mal precautions be taken to avoid a pplication of any voltages highe r than maximum-rated voltag es

to this high -impedance circuit. Reliability of operation is enhanced if unused inputs are tied to an appropriate logic

voltage level (for exampl e, either GND or VDD).

MPC866/MPC859 Hardware Specifications, Rev. 2

8 Freescale Semiconductor

Thermal Characteristics

4 Thermal Characteristics

Table 4 shows the thermal characteristics for the MPC866/859.

Table 4. MPC866/859 Thermal Resistance Data

Rating Environment Symbol Value Unit

Junction-to-ambient

1

Natural Convection Single-layer board (1s) R

Four-layer board (2s2p) R

Airflow (200 ft/min) Single-layer board (1s) R

Four-layer board (2s2p) R

Junction-to-board

Junction-to-case

Junction-to-package top

4

5

6

Natural Convection Ψ

Airflow (200 ft/min) Ψ

1

Junction temperature is a function of on-chip power dissipation, package thermal resistance, mounting site (board)

temperature, ambient temperature, airflow, power dissipation of other components on the board, and board thermal

resistance.

2

Per SEMI G38-87 and JEDEC JESD51-2 with the single-layer board horizontal.

3

Per JEDEC JESD51-6 with the board horizontal.

4

Thermal resistance between the die and the printed-circuit board per JEDEC JESD51-8. Board temperature is

measured on the top surface of the board near the package.

5

Indicates the average thermal resistance between the die and the case top surface as measured by the cold plate

method (MIL SPEC-883 Method 1012.1) with the cold plate temperature used for the case temperature. For exposed

pad packages where the pad would be expected to be soldered, junction-to-case thermal resistance is a simulated

value from the junction to the exposed pad without contact resistance.

6

Thermal characterization parameter indicating the temperature difference between package top and junction

temperature per JEDEC JESD51-2.

θJA

θJMA

θJMA

θJMA

R

θJB

R

θJC

JT

JT

2

3

3

3

37 °C/W

23

30

19

13

6

2

2

MPC866/MPC859 Hardware Specifications, Rev. 2

Freescale Semiconductor 9

Power Dissipation

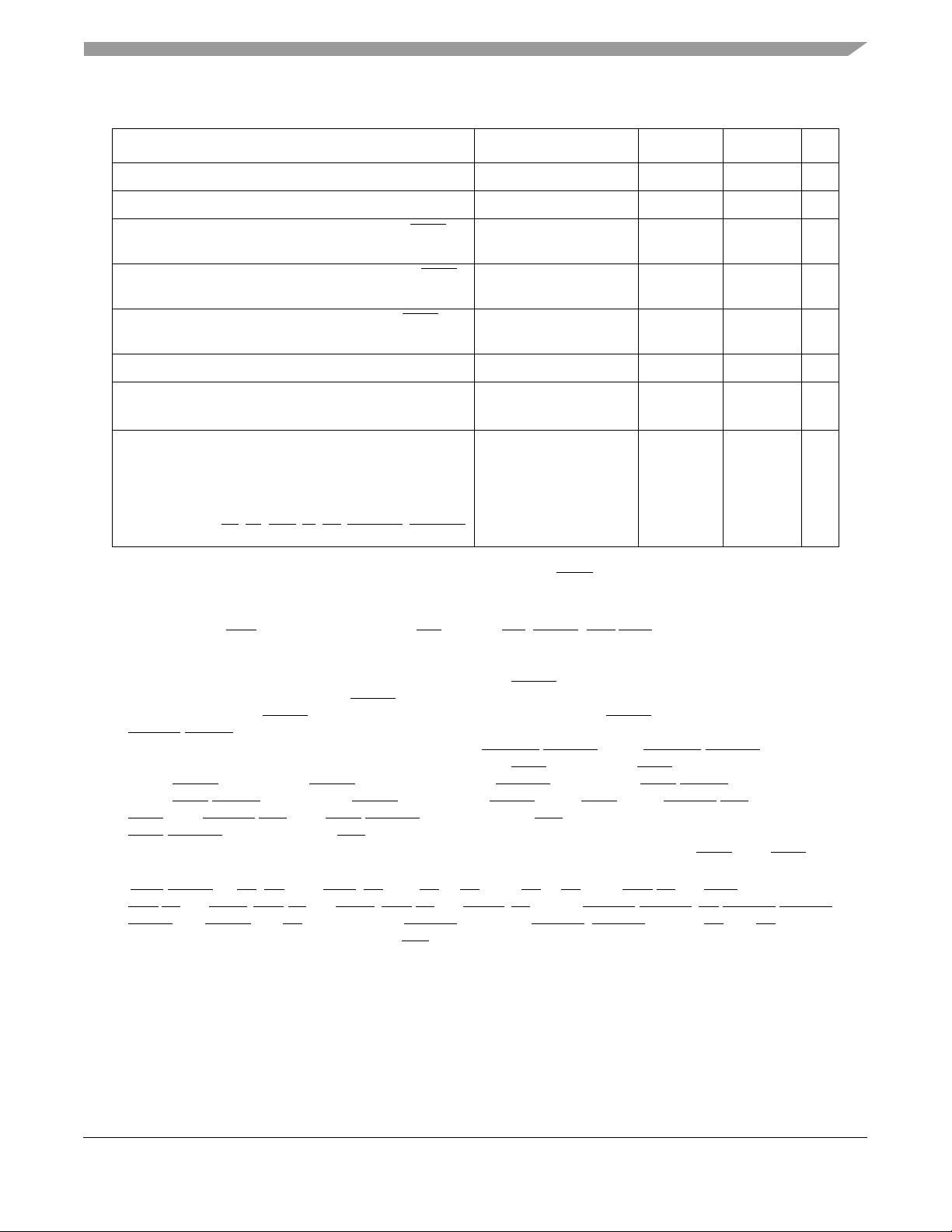

5 Power Dissipation

Table 5 shows power dissipation information. The modes are 1:1, where CPU and bus speeds are equal, and 2:1

mode, where CPU frequency is twice the bus speed.

Table 5. Power Dissipation (PD)

Die Revision Bus Mode

0 1:1 50 MHz 110 140 mW

2:1 66 MHz 140 160 mW

1

Typical power dissipation at VDDL and VDDSYN is at 1.8 V. and VDDH is at 3.3 V.

2

Maximum power dissipation at VDDL and VDDSYN is at 1.9 V, and VDDH is at 3.465 V.

Values in Table 5 represent VDDL based powe r di ssipati on a nd

do not include I/O power dissipation over VDDH. I/O power

dissipation varies widely by application due to buffer current,

depending on external circuitry. The VDDSYN power

dissipation is negligi ble.

6 DC Characteristics

CPU

Frequency

66 MHz 150 180 mW

80 MHz 170 200 mW

100 MHz 210 250 mW

133 MHz 260 320 mW

Typical

1

Maximum

2

NOTE

Unit

Table 6 shows the DC electrical characteristics for the MPC866/859.

Table 6. DC Electrical Specifications

Characteristic Symbol Min Max Unit

Operating voltage VDDL (core) 1.7 1.9 V

VDDH (I/O) 3.135 3.465 V

1

1.7 1.9 V

— 100 mV

Input high voltage (all inputs except EXTAL and

EXTCLK)

2

MPC866/MPC859 Hardware Specifications, Rev. 2

VDDSYN

Difference between

VDDL to VDDSYN

VIH 2.0 3.465 V

10 Freescale Semiconductor

DC Characteristics

Table 6. DC Electrical Specifications (continued)

Characteristic Symbol Min Max Unit

Input low voltage VIL GND 0.8 V

EXTAL, EXTCLK input high voltage VIHC 0.7*(VDDH) VDDH V

Input leakage current, Vin = 5.5V (except TMS, TRST

DSCK and DSDI pins) for 5 Volts Tolerant Pins

Input leakage current, Vin = VDDH (except TMS, TRST

,

I

2

in

,

I

In

— 100 µA

—10µA

DSCK, and DSDI)

Input leakage current, Vin = 0 V (except TMS, TRST

I

In

—10µA

,

DSCK and DSDI pins)

Input capacitance

3

Output high voltage, IOH = – 2.0 mA,

C

in

—20pF

VOH 2.4 — V

except XTAL, and Open drain pins

Output low voltage

• IOL = 2.0 mA (CLKOUT)

• IOL = 3.2 mA

• IOL = 5.3 mA

4

5

VOL — 0. 5 V

• IOL = 7.0 mA (TXD1/PA14, TXD2/PA12)

• IOL = 8.9 mA (TS

1

The difference between VDDL and VDDSYN can not be more than 100 m V.

2

The signals PA[0:15], PB[14:31], PC[4:15], PD[3:15], TDI, TDO, TCK, TRST_B, TMS, MII_TXEN, MII_MDIO are 5 V

, TA, TEA, BI, BB, HRESET, SRESET)

tolerant.

3

Input capacitance is periodically sampled.

4

A(0:31), TSIZ0/REG, TSIZ1, D(0:31), DP(0:3)/IRQ(3:6), RD/WR, BURST, RSV/IRQ2,

IP_B(0:1)/IWP(0:1)/VFLS(0:1), IP_B2/IOIS16_B/AT2, IP_B3/IWP2/VF2, IP_B4/LWP0/VF0, IP_B5/LWP1/VF1,

IP_B6/DSDI/AT0, IP_B7/PTR/AT3, RXD1 /PA15, RXD2/PA13, L1TXDB/PA11, L1RXDB/PA10, L1TXDA/PA9,

L1RXDA/PA8, TIN1/L1RCLKA/BRGO1/CLK1/PA7, BRGCLK1/TOUT1

TIN2/L1TCLKA/BRGO2/CLK3/PA5, TOUT2

BRGCLK2/L1RCLKB/TOUT3

REJCT1

/SPISEL/PB31, SPICLK/PB30, SPIMOSI/PB29, BRGO4/SPIMISO/PB28, BRGO1/I2CSDA/PB27,

/CLK6/PA2, TIN4/BRGO4/CLK7/PA1, L1TCLKB/TOUT4/CLK8/PA0,

/CLK4/PA4, TIN3/BRGO3/CLK5/PA3,

BRGO2/I2CSCL/PB26, SMTXD1/PB25, SMRXD1/PB24, SMSYN1

SMTXD2/L1CLKOB/PB21, SMRXD2/L1CLKOA/PB20, L1ST1/RTS1

L1ST3/L1RQB

L1ST2/RTS2

CTS2

/PC9, TGATE2/CD2/PC8, CTS3/SDACK2/L1TSYNCB/PC7, CD3/L1RSYNCB/PC6,

CTS4

/SDACK1/L1TSYNCA/PC5, CD4/L1RSYNCA/PC4, PD15/L1TSYNCA, PD14/L1RSYNCA, PD13/L1TSYNCB,

/PB17, L1ST4/L1RQA/PB16, BRGO3/PB15, RSTRT1/PB14, L1ST1/RTS1/DREQ0/PC15,

/DREQ1/PC14, L1ST3/L1RQB/PC13, L1ST4/L1RQA/PC12, CTS1/PC11, TGATE1/CD1/PC10,

PD12/L1RSYNCB, PD11/RXD3, PD10/TXD3, PD9/RXD4, PD8/TXD4, PD5/REJECT2, PD6/RTS4

/CLK2/PA6,

/SDACK1/PB23, SMSYN2/SDACK2/PB22,

/PB19, L1ST2/RTS2/PB18,

, PD7/RTS3,

PD4/REJECT3, PD3, MII_MDC, MII_TX_ER, MII_EN, MII_MDIO, MII_TXD[0:3].

5

BDIP/GPL_B(5), BR, BG, FRZ/IRQ6, CS(0:5), CS(6)/CE(1)_B, CS(7)/CE(2)_B, WE0/BS_B0/IORD,

WE1

/BS_B1/IOWR, WE2/BS_B2/PCOE, WE3/BS_B3/PCWE, BS_A(0:3), GPL_A0/GPL_B0, OE/GPL_A1/GPL_B1,

GPL_A

(2:3)/GPL_B(2:3)/CS(2:3), UPWAITA/GPL_A4, UPWAITB/GPL_B4, GPL_A5, ALE_A, CE1_A, CE2_A,

ALE_B/DSCK/AT1, OP(0:1), OP2/MODCK1/STS

, OP3/MODCK2/DSDO, BADDR(28:30).

MPC866/MPC859 Hardware Specifications, Rev. 2

Freescale Semiconductor 11

Thermal Calculation and Measurement

7 Thermal Calculation and Measurement

For the fol lowing disc uss ions, PD = (VDDL x IDDL) + P I/O, where PI/ O is the po wer di ssipati on of the I /O driv ers.

The VDDSYN power dissipation is negligi ble.

7.1 Estimation with Junction-to-Ambient Thermal Resistance

An estimation of the chip junction te mperature, TJ, in °C can be obtained from the equation:

= TA +(R

T

J

θJA

x PD)

where:

= ambient tem perat u re (ºC)

T

A

= package junction-to-a mbient thermal resistance (ºC/W)

R

θJA

= power dissipation in package

P

D

The junction-to- ambient thermal resistance is an industry standard value that provides a quick and easy estimation

of thermal performance. However, the answer is only an estimate; test cases have demonstrated that errors of a factor

of two (in the quantity T

) are possible.

J-TA

7.2 Estimation with Junction-to-Case Thermal Resistance

Historically, the thermal resi stance has f requently bee n expressed as the sum of a junction-to -case the rmal resist ance

and a case-to-ambient thermal resistance:

= R

R

θJA

where:

R

θJA

R

θJC

R

θCA

is device related and cannot be influenced by the user. The user adjusts the thermal environment to affec t the

R

θJC

case-to-am bient thermal resi s tan ce, R

heat sink, change the mounting arra ngement on the printed-circuit board, or change the thermal dissipation on the

printed-circ uit board surrounding the devic e. This thermal model is most useful fo r ceramic packages with heat sinks

where some 90% of the heat flows through the case and the heat sink to the ambient environment. For most

packages, a better model is required.

+ R

θJC

θCA

= junctio n - t o-am b ient th ermal res i s tanc e ( º C/W )

= junction-to-case thermal resistance (ºC/W)

= case-to-am bient ther mal resistance (ºC/W)

. For instance, the user can change the airflow around the device, add a

θCA

7.3 Estimation with Junction-to-Board Thermal Resistance

A simple package thermal model that has demonstrated reasonable accuracy (about 20%) is a two-res istor model

consisting of a junction-t o-board and a junction-to -case thermal r esistance. Th e junction-to- case covers t he situ ation

where a heat sink is used or where a substantial amount of heat is dissipated from the top of the package. The

junction-to-board thermal resistance describes the thermal performance when most of the heat is conducted to the

printed-circ uit board. It has been observed that the thermal perfor mance of most plastic packages and especially

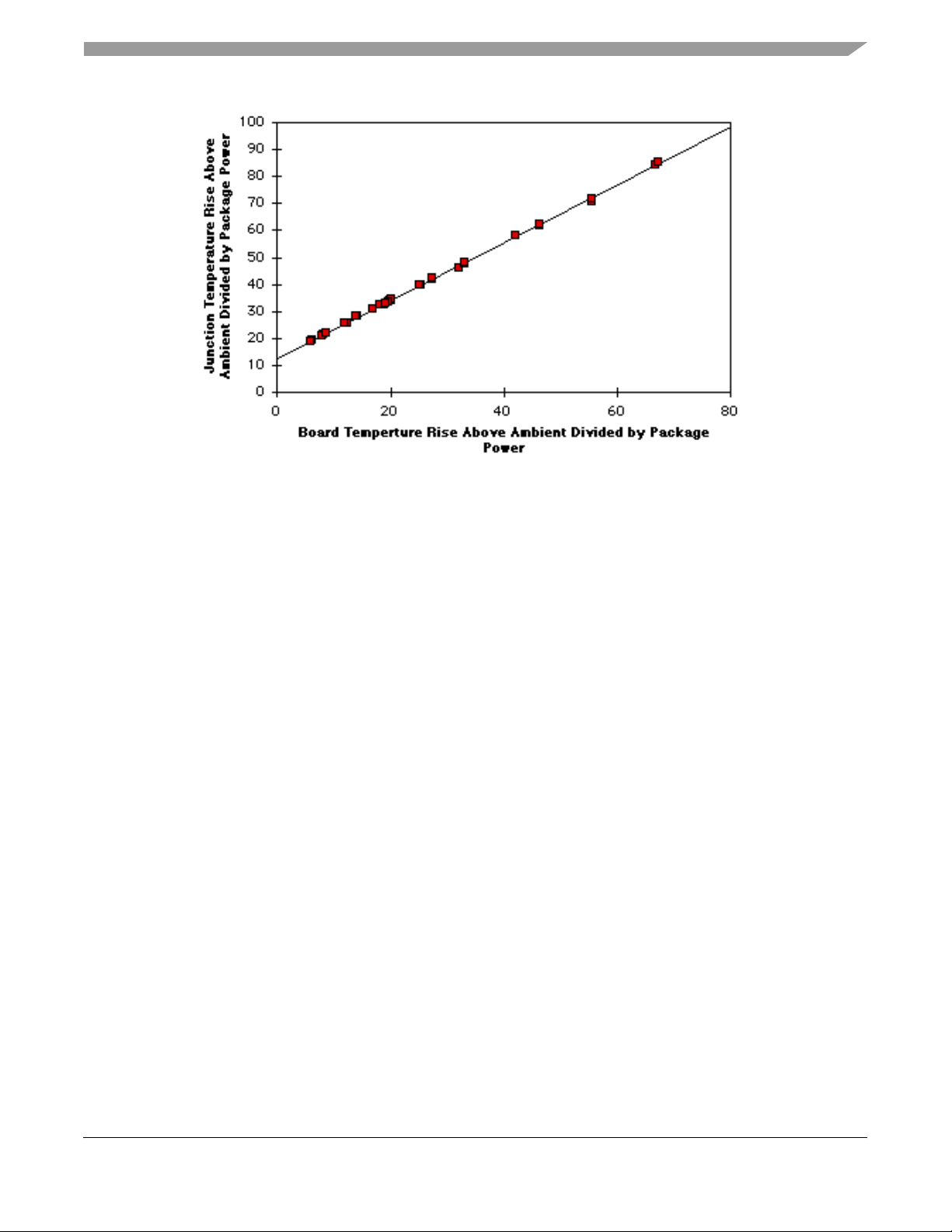

PBGA packages is strongly dependent on the board temperature; see Figure 3.

MPC866/MPC859 Hardware Specifications, Rev. 2

12 Freescale Semiconductor

Thermal Calculation and Measurement

Figure 3. Effect of Board Temperature Rise on Thermal Behavior

If the board temperature is known, an estimate of the junction temperature in the environment can be made using

the following equatio n:

= TB +(R

T

J

θJB

x PD)

where:

= junction-to-board the rmal resistance (ºC/W)

R

θJB

= board temper atu re ºC

T

B

= power dissipation in package

P

D

If the board temperature is known and the heat loss from the package case to the air can be ignored, acceptable

predictions of junction temperature can be made. For this method to work, the board and board mounting must be

similar to the test board used to deter mine the junction-to-board thermal res istance, namely a 2s2p (board with a

power and a ground plane) and vias attaching the thermal balls to the ground plane.

7.4 Estimation Using Simulation

When the boar d temperature is not known, a the rmal sim ulation of t he applic ation is needed. T he simple t wo-resistor

model can be use d with the thermal sim ulation of the application [2], or a more accurate and c omplex model of the

package can be used in the thermal simulation.

MPC866/MPC859 Hardware Specifications, Rev. 2

Freescale Semiconductor 13

Thermal Calculation and Measurement

7.5 Experimental Determination

To determine the junction temperature of the device in the application after prototypes are available, the thermal

characteriz at ion parameter (ΨJT) can be used to determine the junction temperature with a measurement of the

temperature at the top center of the package case using the following equation:

= TT +(ΨJT x PD)

T

J

where:

= thermal characteriz ation parameter

Ψ

JT

= thermocouple temperature on top of package

T

T

= power dissipation in package

P

D

The thermal characterization parameter is measured per JESD51-2 specification published by JEDEC using a 40

gauge type T thermocouple epoxie d to the top center of the package case. The thermocouple should be positi oned

so that the thermocouple junc tion rests on the package. A small amount of epoxy is placed over the thermocoup le

junction and over about 1 mm of wir e ext ending fr om the j unction. The thermoc ouple wire is pl aced flat again st the

package case to avoid measurement errors caused by cooling effects of the ther mocouple wire.

7.6 References

Semiconductor Equipment and Materials International(415 ) 964-5111

805 East Middlefield Rd.

Mountain View, CA 94043

MIL-SPEC and EIA/JESD (JEDEC) specifications800-854-7179 or

(Available from Global Engine ering Documents)303-397-7956

JED E C Spec ifica t io ns h t t p://www.jedec.o r g

1. C.E. Triplett and B. Joiner, “An Experimental Characterization of a 272 PBGA Within an Automotive Engine

Controller Module,” Proceedings of SemiTherm, San Diego, 1998, pp. 47-54.

2. B. Joiner and V. Adams, “Measurement and Simulation of Junction to Board Thermal Resistance and Its

Application in Thermal Model ing,” Proceedings of SemiTherm, San Diego, 1999, pp. 212-220.

MPC866/MPC859 Hardware Specifications, Rev. 2

14 Freescale Semiconductor

Power Supply and Power Sequencing

8 Power Supply and Power Sequencing

This section provide s design considerations for the MPC866/ 859 power supply . The MPC866/859 has a core voltage

(VDDL) and PLL voltage (VDDSYN) that ope rates a t a lower voltage tha n th e I/O volta ge VDDH. The I /O sect ion

of the MPC866/859 is supplied with 3.3 V across VDDH and V

Signals PA[0:15], PB[14:31], PC[4:15], PD[3:15], TDI, TDO, TC K, TRST_B, TMS, MII_TXEN, and MII_MDIO

are 5-V tolerant. All inputs cannot be more than 2.5 V greater than VDDH. In addition, 5-V tolerant pins cann ot

exceed 5.5 V and the remaining input pins cannot exceed 3.465 V. This restriction applies to power up/down and

normal operation.

One consequence of multiple power supplies is that when power is initially applied the voltage rails ramp up at

different r ates. The rates depend on the nature of the power supply, the type of load on each power supply, and the

manner in which diffe rent voltages are derived. The following restrictions apply:

• VDDL must not exceed VDDH during power up and power down.

• VDDL must not exceed 1.9 V and VDDH must not exceed 3.465 V.

These cautio ns are necessary for the long term reliability of the part. If they are viol ated, the electrostatic discharge

(ESD) protection diodes are forward-biased and excessive current can flow through these diodes. If the system

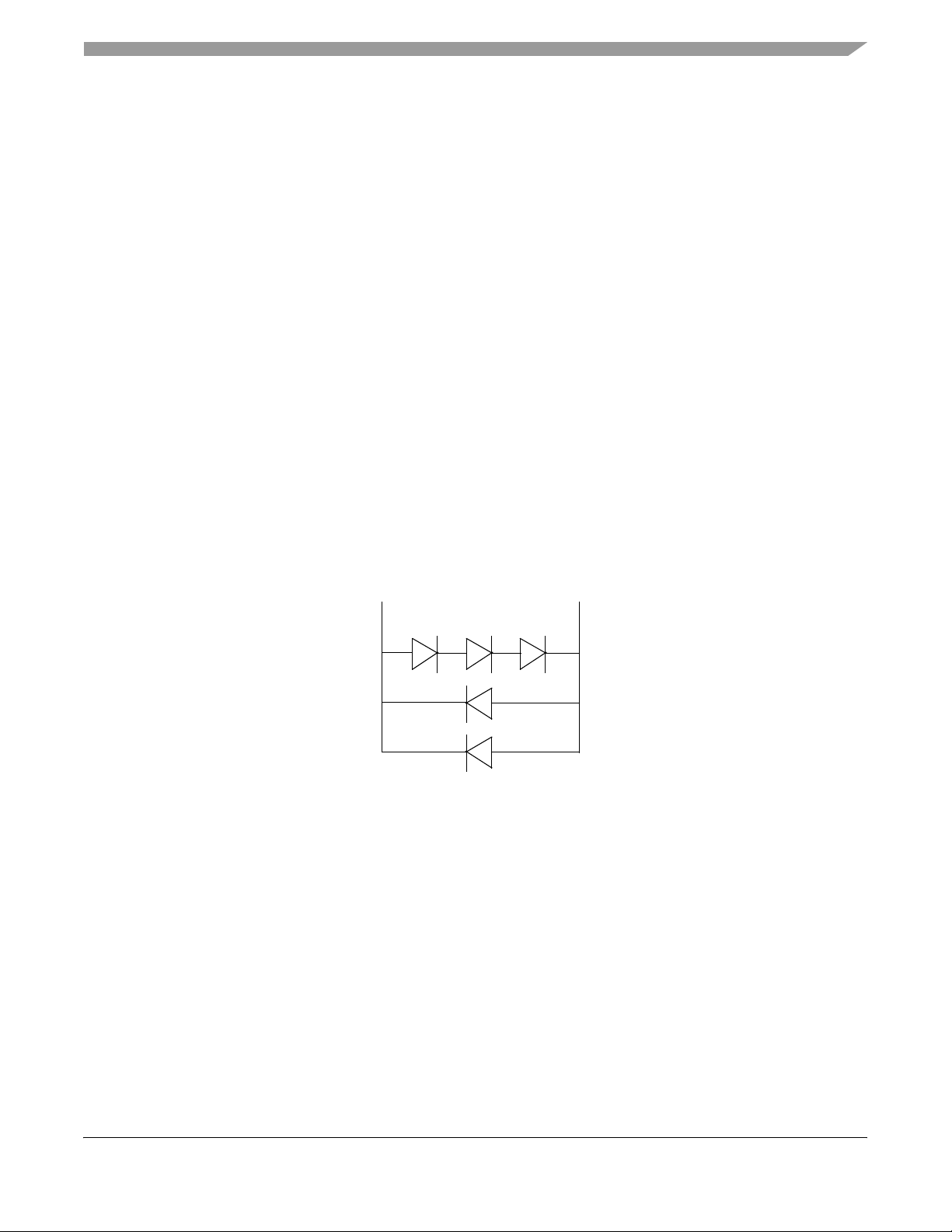

power supply design does not contr ol the voltage sequencing, the circuit shown in Figure 4 can be added to meet

these requirement s. The MUR420 Schottky diodes control the maximum potential differen ce between the external

bus and core power supplies on powerup and the 1N5820 diodes regulate the maximum potential difference on

powerdown.

(GND).

SS

VDDH VDDL

MUR420

1N5820

Figure 4. Example Voltage Sequencing Circuit

9 Layout Practices

Each VDD pin on the MPC866/859 should be provided with a low-impedan ce path to the board’s supply.

Furthermore, ea ch GND pi n shou ld be provide d wit h a l ow-impeda nce pat h to gr ound. The p ower supply pins drive

distinct groups of logic on chip. The VDD power supply should be bypassed to ground using at least four 0.1 µF

bypass capacitors located as close as possible to the four sides of the package. Each board designed should be

characterized and additional appropriate decoupling capacitors should be used if required. The capacitor leads and

associated printed-circuit traces connecting to chip V

At a minimum, a four-layer board employing two inner layers as V

All output pins on the MPC866/859 have fast rise and fall times. Printed-circuit (PC) trace interconnection length

should be minimized in order to minimize undershoot and reflections caused by these fast output switching times.

and GND should be kept to less than 1/2” per capacito r lead.

DD

and GND planes should be used.

DD

MPC866/MPC859 Hardware Specifications, Rev. 2

Freescale Semiconductor 15

Bus Signal Timing

This recommendation partic ularly applies to the address and data buses. Maximum PC trace le ngths of 6” are

recommended. Capacitance calculations should consider all device loads as well as parasitic capacitances due to the

PC traces. Attention to proper PCB layout and bypassing becomes especially crit ic al in systems with higher

capacitive loads because these loads create higher transient currents in the V

and GND circuits . Pull up all unused

DD

inputs or signals that will be inputs during reset. Special care should be taken to minimize the noise levels on the

PLL supply pins. For more information, please refer to Section 14.4.3, Clock Synthesizer Power (VDDSYN,

VSSSYN, VSSSYN1), in the MPC866 User’s Manual.

10 Bus Signal Timing

The maximum bus speed supported by the MPC866/859 is 66 MHz. Higher-speed parts must be operated in

half-speed bus mode (for example , an MPC866/859 use d at 100 MHz must be configured for a 50-MHz bus).

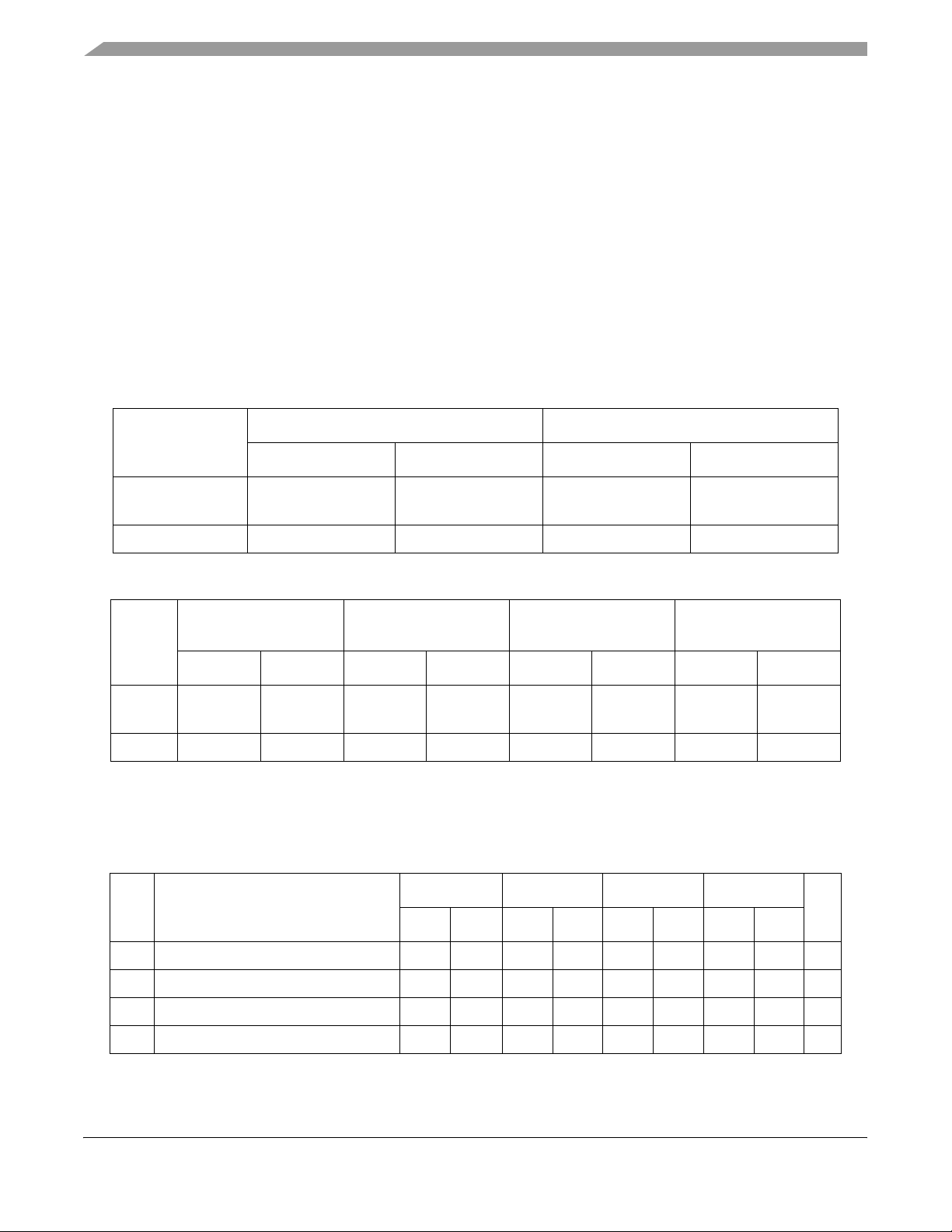

Table 7 and Table 8 show the frequency ranges for standard part frequencies.

Table 7. Frequency Ranges for Standard Part Frequencies (1:1 Bus Mode)

Part Freq 50 MHz 66 MHz

Min Max Min Max

Core 40 50 40 66.67

Bus 40 50 40 66.67

Table 8. Frequency Ranges for Standard Part Frequencies (2:1 Bus Mode)

Par t

Freq

Core 40 50 40 66.67 40 100 40 133.34

Bus 20 25 20 33.33 20 50 20 66.67

50 MHz 66 MHz 100 MHz 133 MHz

Min Max Min Max Min Max Min Max

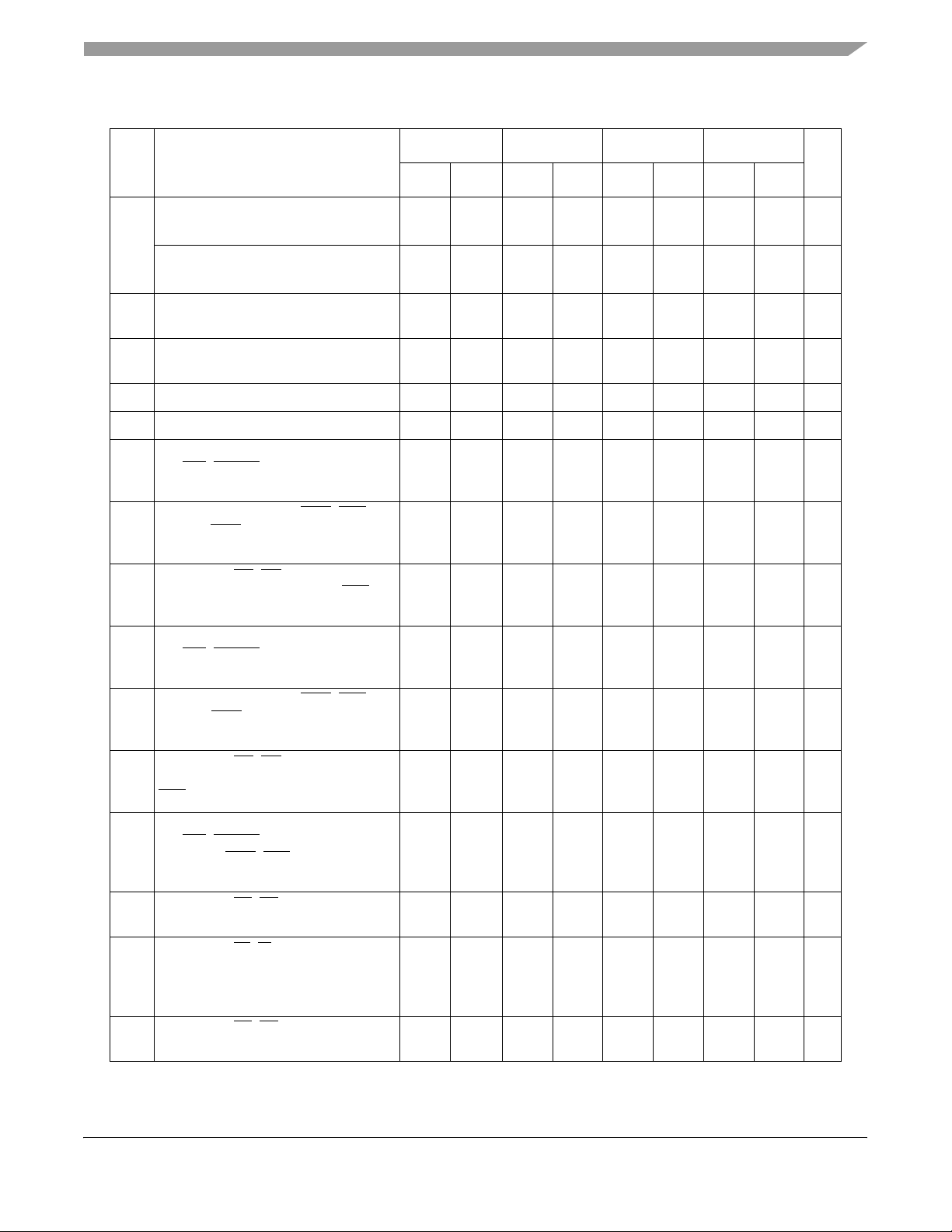

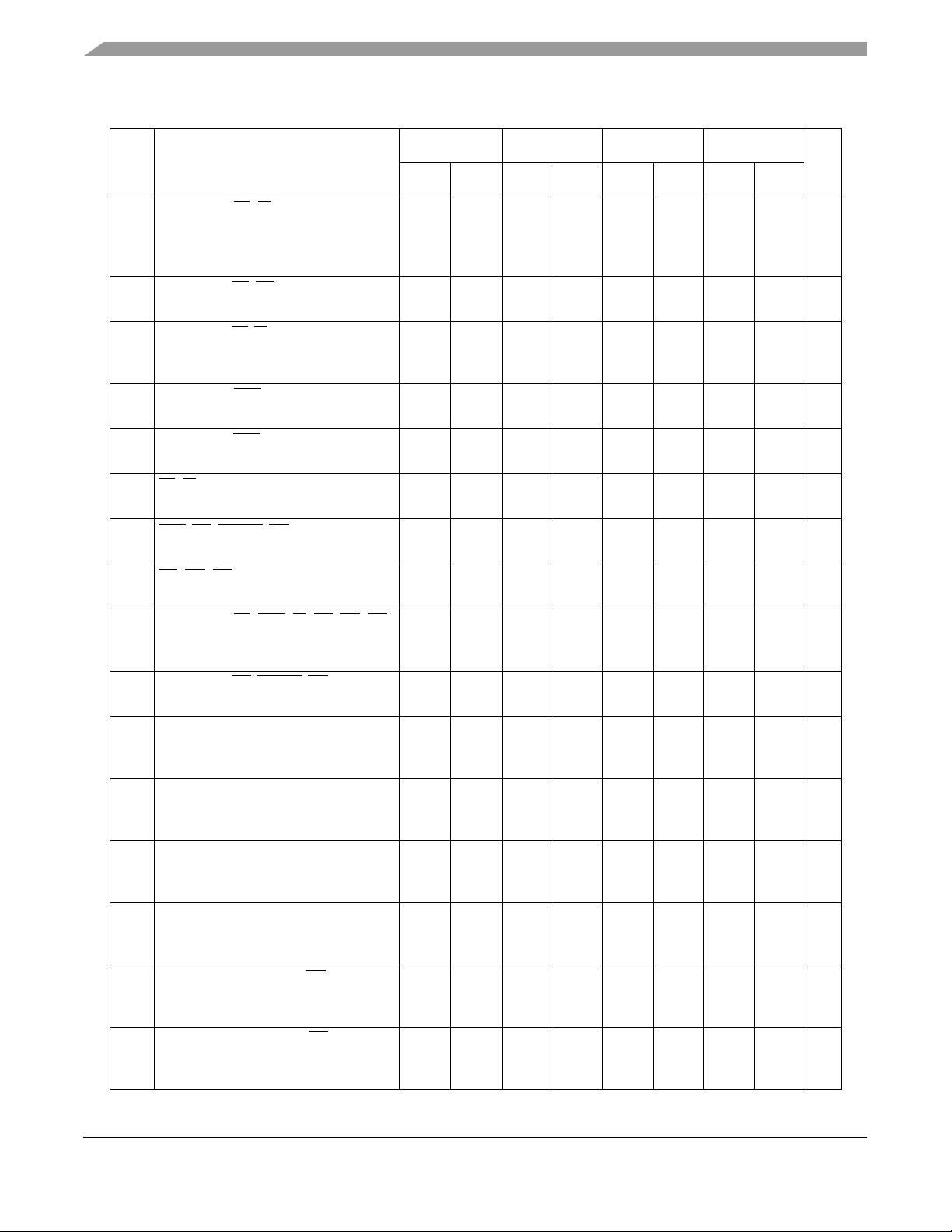

Table 9 shows the timings for the MPC866/859 at 33, 40, 50, and 66 MHz bus operation. The timing for the

MPC866/859 bus shown in this table assumes a 50-pF load for maximum delays and a 0-pF load for minimum

delays. CLKOUT assumes a 100-pF load maximum delay.

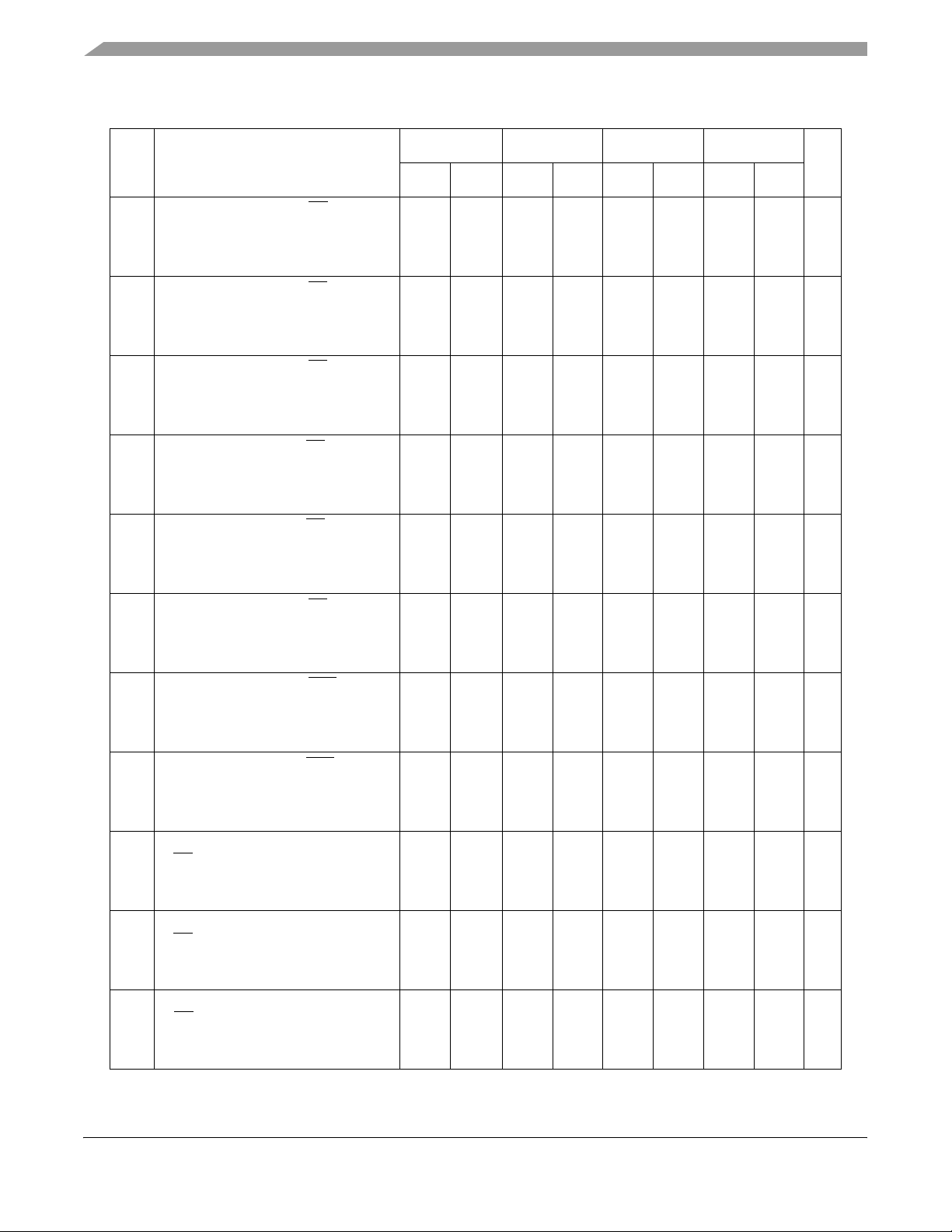

Table 9. Bus Operation Timings

33 MHz 40 MHz 50 MHz 66 MHz

Num Characteristic

Min Max Min Max Min Max Min Max

B1 Bus Period (CLKOUT) See Ta b le 7 ————————ns

B1a EXTCLK to CLKOUT phase skew – 2 +2 – 2 +2 – 2 +2 – 2 +2 ns

Unit

B1b CLKOUT frequency jitter peak-to-peak — 1 — 1 — 1 — 1 ns

B1c Frequency jitter on EXTCLK — 0.50 — 0.50 — 0.50 — 0.50 %

MPC866/MPC859 Hardware Specifications, Rev. 2

16 Freescale Semiconductor

Num Characteristic

Bus Signal Timing

Table 9. Bus Operation Timings (continued)

33 MHz 40 MHz 50 MHz 66 MHz

Unit

Min Max Min Max Min Max Min Max

B1d CLKOUT phase jitter peak-to-peak

—4—4—4—4ns

for OSCLK ≥ 15 MHz

CLKOUT phase jitter peak-to-peak

—5—5—5—5ns

for OSCLK < 15 MHz

B2 CLKOUT pulse width low (MIN = 0.4 x

12.1 18.2 10.0 15.0 8.0 12.0 6.1 9.1 ns

B1, MAX = 0.6 x B1)

B3 CLKOUT pulse width high (MIN = 0.4 x

12.1 18.2 10.0 15.0 8.0 12.0 6.1 9.1 ns

B1, MAX = 0.6 x B1)

B4 CLKOUT rise time — 4.00 — 4.00 — 4.00 — 4.00 ns

B5 CLKOUT fall time

B7 CLKOUT to A(0:31), BADDR(28:30),

RD/WR

, BURST, D(0:31), DP(0:3)

— 4.00 — 4.00 — 4.00 — 4.00 ns

7.60 — 6.30 — 5.00 — 3.80 — ns

output hold (MIN = 0.25 x B1)

B7a CLKOUT to TSIZ(0:1), REG

AT ( 0: 3 ), B DI P

, PTR output hold (MIN =

, RSV,

7.60 — 6.30 — 5.00 — 3.80 — ns

0.25 x B1)

B7b CLKOUT to BR

, BG, FRZ, VFLS(0:1),

VF(0:2), IWP(0:2), LWP(0:1), STS

7.60 — 6.30 — 5.00 — 3.80 — ns

output hold (MIN = 0.25 x B1)

B8 CLKOUT to A(0:31), BADDR(28:30)

RD/WR

, BURST, D(0:31), DP(0:3),

— 13.80 — 12.50 — 11.30 — 10.00 ns

valid (MAX = 0.25 x B1 + 6.3)

B8a CLKOUT to TSIZ(0:1), REG

AT(0:3), BDIP

, PTR valid (MAX = 0.25

, RSV,

— 13.80 — 12.50 — 11.30 — 10.00 ns

x B1 + 6.3)

B8b CLKOUT to BR

, BG, VFLS(0:1),

— 13.80 — 12.50 — 11.30 — 10.00 ns

VF(0:2), IWP(0:2), FRZ, LWP(0:1),

STS

valid 4 (MAX = 0.25 x B1 + 6.3)

B9 CLKOUT to A(0:31), BADDR(28:30),

RD/WR

TSIZ(0:1), REG

, BURST, D(0:31), DP(0:3),

, RSV, AT(0:3), PTR

7.60 13.80 6.30 12.50 5.00 11.30 3.80 10.00 ns

High-Z (MAX = 0.25 x B1 + 6.3)

B11 CLKOUT to TS

, BB assertion (MAX =

7.60 13.60 6.30 12.30 5.00 11.00 3.80 9.80 ns

0.25 x B1 + 6.0)

B11a CLKOUT to TA

, BI assertion (when

2.50 9.30 2.50 9.30 2.50 9.30 2.50 9.80 ns

driven by the memory controller or

PCMCIA interface) (MAX = 0.00 x B1 +

1

9.30

)

B12 CLKOUT to TS

, BB negation (MAX =

7.60 12.30 6.30 11.00 5.00 9.80 3.80 8.50 ns

0.25 x B1 + 4.8)

MPC866/MPC859 Hardware Specifications, Rev. 2

Freescale Semiconductor 17

Bus Signal Timing

Num Characteristic

Table 9. Bus Operation Timings (continued)

33 MHz 40 MHz 50 MHz 66 MHz

Unit

Min Max Min Max Min Max Min Max

B12a CLKOUT to TA, BI negation (when

driven by the memory controller or

PCMCIA interface) (MAX = 0.00 x B1 +

9.00)

B13 CLKOUT to TS

, BB High-Z (MIN = 0.25

x B1)

B13a CLKOUT to TA

, BI High-Z (when driven

by the memory controller or PCMCIA

interface) (MIN = 0.00 x B1 + 2.5)

B14 CLKOUT to TEA

assertion (MAX =

0.00 x B1 + 9.00)

B15 CLKOUT to TEA

High-Z (MIN = 0.00 x

B1 + 2.50)

B16 TA

, BI valid to CLKOUT (setup time)

(MIN = 0.00 x B1 + 6.00)

B16a TEA

, KR, RETRY, CR valid to CLKOUT

(setup time) (MIN = 0.00 x B1 + 4.5)

B16b BB

B17 CLKOUT to TA

, BG, BR, valid to CLKOUT (setup

2

time)

(4 MIN = 0.00 x B1 + 0.00 )

, TEA, BI, BB, BG, BR

valid (hold time) (MIN = 0.00 x B1 +

3

1.00

)

2.50 9.00 2.50 9.00 2.50 9.00 2.50 9.00 ns

7.60 21.60 6.30 20.30 5.00 19.00 3.80 14.00 ns

2.50 15.00 2.50 15.00 2.50 15.00 2.50 15.00 ns

2.50 9.00 2.50 9.00 2.50 9.00 2.50 9.00 ns

2.50 15.00 2.50 15.00 2.50 15.00 2.50 15.00 ns

6.00 — 6.00 — 6.00 — 6.00 — ns

4.50 — 4.50 — 4.50 — 4.50 — ns

4.00 — 4.00 — 4.00 — 4.00 — ns

1.00 — 1.00 — 1.00 — 2.00 — ns

B17a CLKOUT to KR

, RETRY, CR valid (hold

time) (MIN = 0.00 x B1 + 2.00)

B18 D(0:31), DP(0:3) valid to CLKOUT

rising edge (setup time)

4

(MIN = 0.00

x B1 + 6.00)

B19 CLKOUT rising edge to D(0:31),

DP(0:3) valid (hold time)

x B1 + 1.00

5

)

B20 D(0:31), DP(0:3) valid to CLKOUT

falling edge (setup time)

4

(MIN = 0.00

6

(MIN = 0.00

x B1 + 4.00)

B21 CLKOUT falling edge to D(0:31),

DP(0:3) valid (hold Time)

6

(MIN = 0.00

x B1 + 2.00)

B22 CLKOUT rising edge to CS

asserted

GPCM ACS = 00 (MAX = 0.25 x B1 +

6.3)

B22a CLKOUT falling edge to CS

asserted

GPCM ACS = 10, TRLX = 0 (MAX =

0.00 x B1 + 8.00)

MPC866/MPC859 Hardware Specifications, Rev. 2

2.00 — 2.00 — 2.00 — 2.00 — ns

6.00 — 6.00 — 6.00 — 6.00 — ns

1.00 — 1.00 — 1.00 — 2.00 — ns

4.00 — 4.00 — 4.00 — 4.00 — ns

2.00 — 2.00 — 2.00 — 2.00 — ns

7.60 13.80 6.30 12.50 5.00 11.30 3.80 10.00 ns

— 8.00 — 8.00 — 8.00 — 8.00 ns

18 Freescale Semiconductor

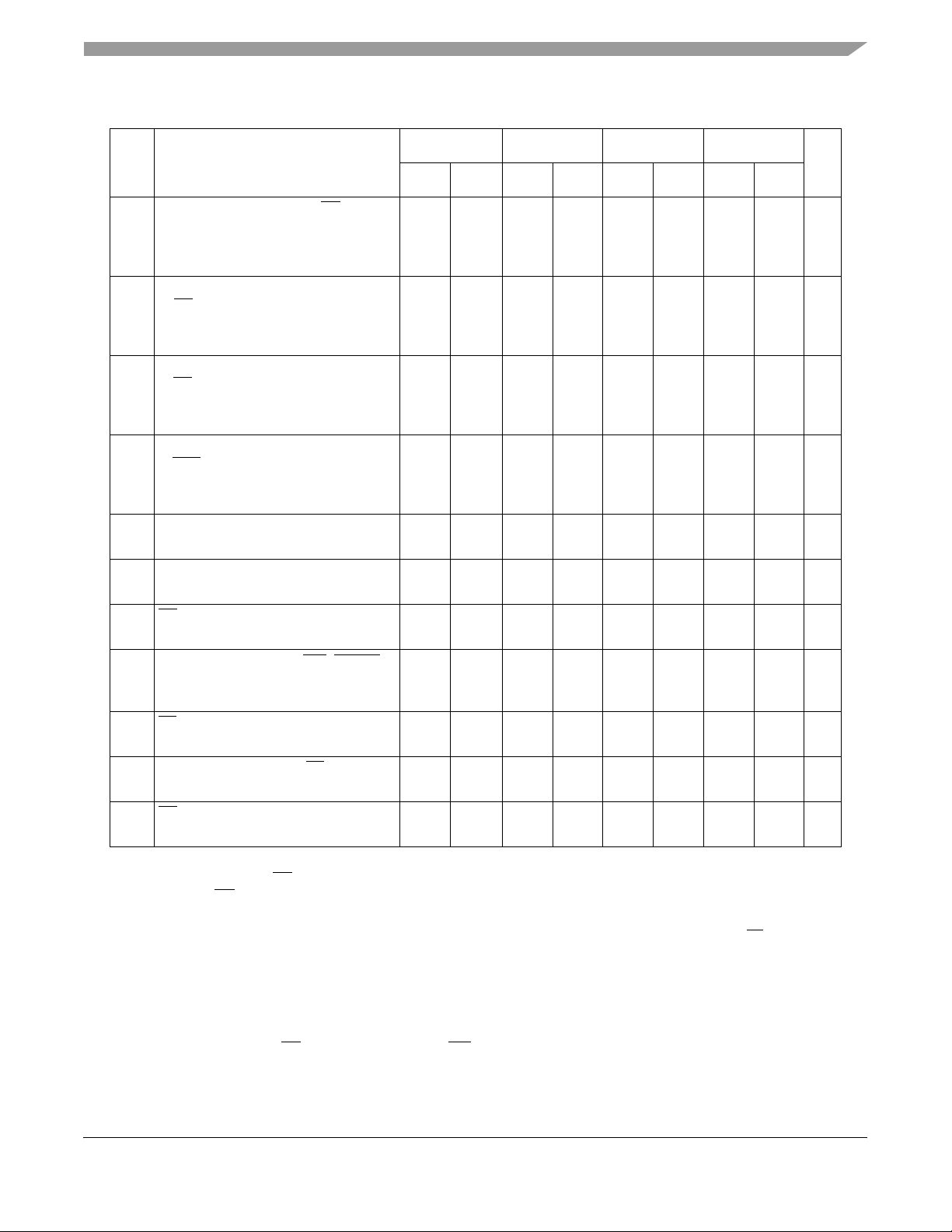

Num Characteristic

Bus Signal Timing

Table 9. Bus Operation Timings (continued)

33 MHz 40 MHz 50 MHz 66 MHz

Unit

Min Max Min Max Min Max Min Max

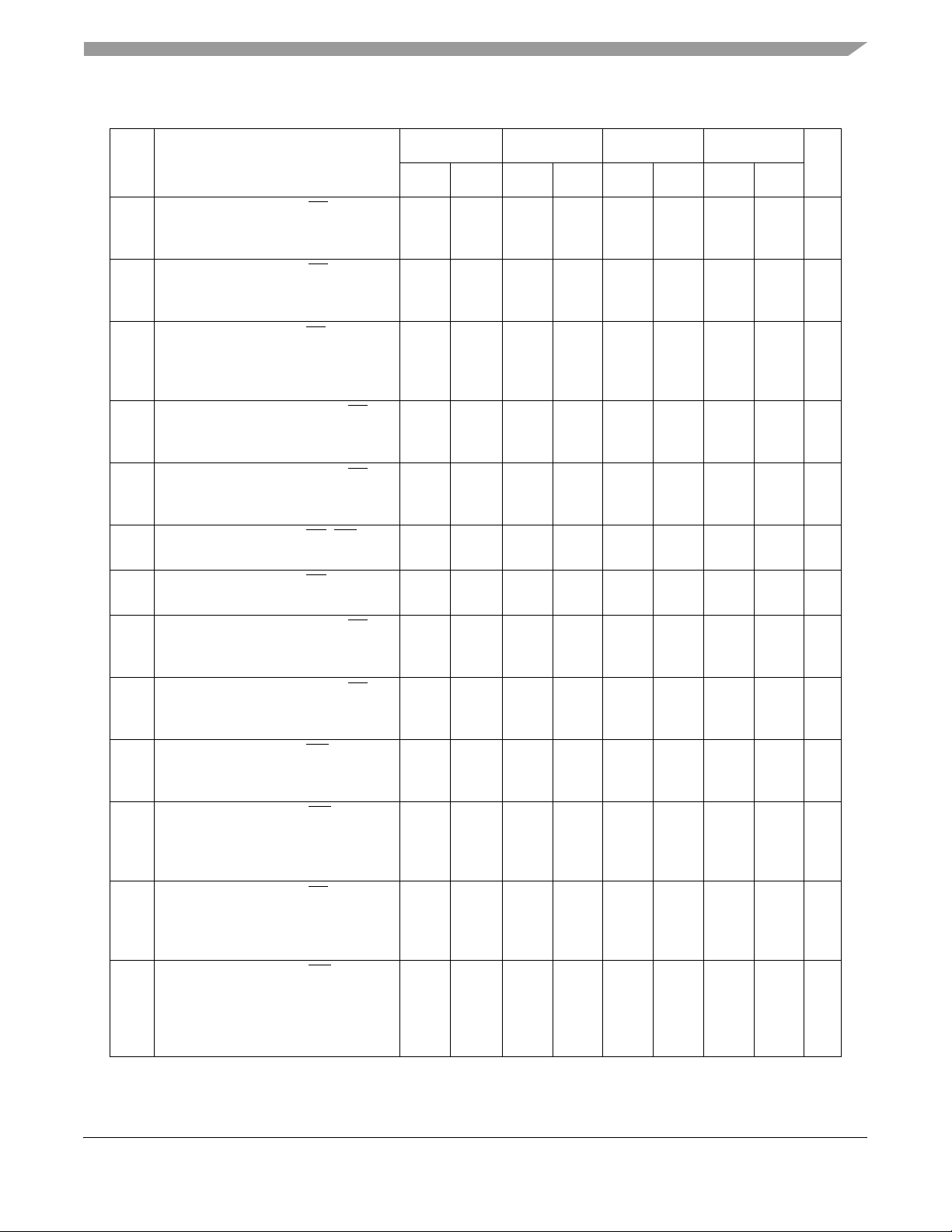

B22b CLKOUT falling edge to CS asserted

GPCM ACS = 11, TRLX = 0, EBDF = 0

(MAX = 0.25 x B1 + 6.3)

B22c CLKOUT falling edge to CS

GPCM ACS = 11, TRLX = 0, EBDF = 1

(MAX = 0.375 x B1 + 6.6)

B23 CLKOUT rising edge to CS

GPCM read access, GPCM write

access ACS = 00, TRLX = 0 & CSNT =

0 (MAX = 0.00 x B1 + 8.00)

B24 A(0:31) and BADDR(28:30) to CS

asserted GPCM ACS = 10, TRLX = 0

(MIN = 0.25 x B1 - 2.00)

B24a A(0:31) and BADDR(28:30) to CS

asserted GPCM ACS = 11, TRLX = 0

(MIN = 0.50 x B1 - 2.00)

B25 CLKOUT rising edge to OE

asserted (MAX = 0.00 x B1 + 9.00)

B26 CLKOUT rising edge to OE

(MAX = 0.00 x B1 + 9.00)

B27 A(0:31) and BADDR(28:30) to CS

asserted GPCM ACS = 10, TRLX = 1

(MIN = 1.25 x B1 - 2.00)

asserted

negated

, WE(0:3)

negated

7.60 13.80 6.30 12.50 5.00 11.30 3.80 10.00 ns

10.90 18.00 10.90 16.00 7.00 14.10 5.20 12.30 ns

2.00 8.00 2.00 8.00 2.00 8.00 2.00 8.00 ns

5.60 — 4.30 — 3.00 — 1.80 — ns

13.20 — 10.50 — 8.00 — 5.60 — ns

— 9.00 — 9.00 — 9.00 — 9.00 ns

2.00 9.00 2.00 9.00 2.00 9.00 2.00 9.00 ns

35.90 — 29.30 — 23.00 — 16.90 — ns

B27a A(0:31) and BADDR(28:30) to CS

asserted GPCM ACS = 11, TRLX = 1

(MIN = 1.50 x B1 - 2.00)

B28 CLKOUT rising edge to WE

negated GPCM write access CSNT =

0 (MAX = 0.00 x B1 + 9.00)

B28a CLKOUT falling edge to WE

negated GPCM write access TRLX =

0,1, CSNT = 1, EBDF = 0 (MAX = 0.25

x B1 + 6.80)

B28b CLKOUT falling edge to CS

GPCM write access TRLX = 0,1,

CSNT = 1, ACS = 10 or ACS = 11,

EBDF = 0 (MAX = 0.25 x B1 + 6.80)

B28c CLKOUT falling edge to WE

negated GPCM write access TRLX =

0, CSNT = 1 write access TRLX = 0,1,

CSNT = 1, EBDF = 1 (MAX = 0.375 x

B1 + 6.6)

(0:3)

(0:3)

negated

(0:3)

MPC866/MPC859 Hardware Specifications, Rev. 2

43.50 — 35.50 — 28.00 — 20.70 — ns

— 9.00 — 9.00 — 9.00 — 9.00 ns

7.60 14.30 6.30 13.00 5.00 11.80 3.80 10.50 ns

— 14.30 — 13.00 — 11.80 — 10.50 ns

10.90 18.00 10.90 18.00 7.00 14.30 5.20 12.30 ns

Freescale Semiconductor 19

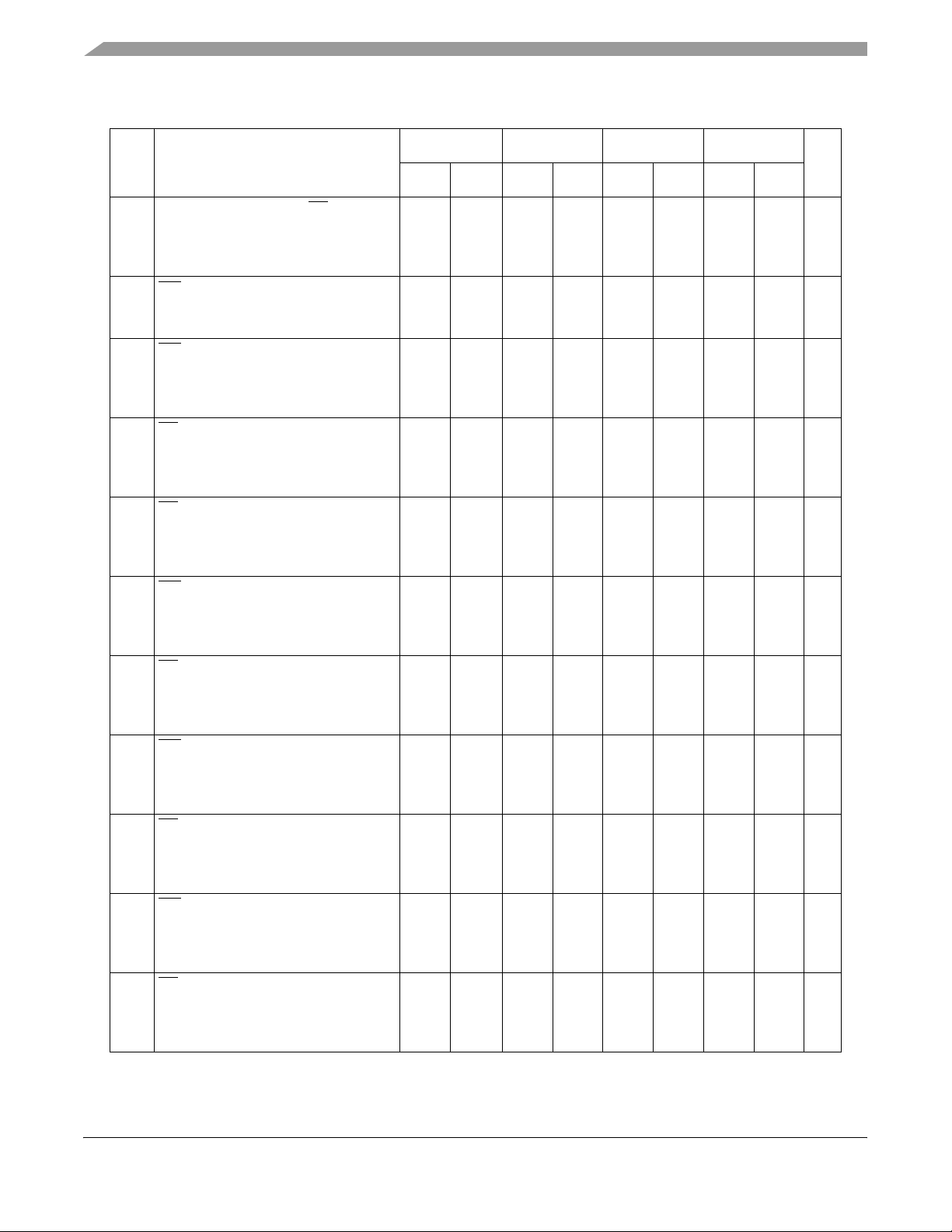

Bus Signal Timing

Num Characteristic

Table 9. Bus Operation Timings (continued)

33 MHz 40 MHz 50 MHz 66 MHz

Unit

Min Max Min Max Min Max Min Max

B28d CLKOUT falling edge to CS negated

GPCM write access TRLX = 0,1,

CSNT = 1, ACS = 10, or ACS = 11,

EBDF = 1 (MAX = 0.375 x B1 + 6.6)

B29 WE

B29a WE

B29b CS

B29c CS

B29d WE

(0:3) negated to D(0:31), DP(0:3)

High-Z GPCM write access, CSNT = 0,

EBDF = 0 (MIN = 0.25 x B1 - 2.00)

(0:3) negated to D(0:31), DP(0:3)

High-Z GPCM write access, TRLX = 0,

CSNT = 1, EBDF = 0 (MIN = 0.50 x B1

– 2.00)

negated to D(0:31), DP(0:3), High

Z GPCM write access, ACS = 00,

TRLX = 0,1 & CSNT = 0 (MIN = 0.25 x

B1– 2.00)

negated to D(0:31), DP(0:3) High-Z

GPCM write access, TRLX = 0, CSNT

= 1, ACS = 10, or ACS = 11, EBDF = 0

(MIN = 0.50 x B1 – 2.00)

(0:3) negated to D(0:31), DP(0:3)

High-Z GPCM write access, TRLX = 1,

CSNT = 1, EBDF = 0 (MIN = 1.50 x B1

– 2.00)

— 18.00 — 18.00 — 14.30 — 12.30 ns

5.60 — 4.30 — 3.00 — 1.80 — ns

13.20 — 10.50 — 8.00 — 5.60 — ns

5.60 — 4.30 — 3.00 — 1.80 — ns

13.20 — 10.50 — 8.00 — 5.60 — ns

43.50 — 35.50 — 28.00 — 20.70 — ns

B29e CS

B29f WE

B29g CS

B29h WE

B29i CS

negated to D(0:31), DP(0:3) High-Z

GPCM write access, TRLX = 1, CSNT

= 1, ACS = 10, or ACS = 11, EBDF = 0

(MIN = 1.50 x B1 – 2.00)

(0:3) negated to D(0:31), DP(0:3)

High Z GPCM write access, TRLX = 0,

CSNT = 1, EBDF = 1 (MIN = 0.375 x

B1 – 6.30)

negated to D(0:31), DP(0:3) High-Z

GPCM write access, TRLX = 0, CSNT

= 1 ACS = 10 or ACS = 11, EBDF = 1

(MIN = 0.375 x B1 – 6.30)

(0:3) negated to D(0:31), DP(0:3)

High Z GPCM write access, TRLX = 1,

CSNT = 1, EBDF = 1 (MIN = 0.375 x

B1 – 3.30)

negated to D(0:31), DP(0:3) High-Z

GPCM write access, TRLX = 1, CSNT

= 1, ACS = 10 or ACS = 11, EBDF = 1

(MIN = 0.375 x B1 – 3.30)

43.50 — 35.50 — 28.00 — 20.70 — ns

5.00 — 3.00 — 1.10 — 0.00 — ns

5.00 — 3.00 — 1.10 — 0.00 — ns

38.40 — 31.10 — 24.20 — 17.50 — ns

38.40 — 31.10 — 24.20 — 17.50 — ns

MPC866/MPC859 Hardware Specifications, Rev. 2

20 Freescale Semiconductor

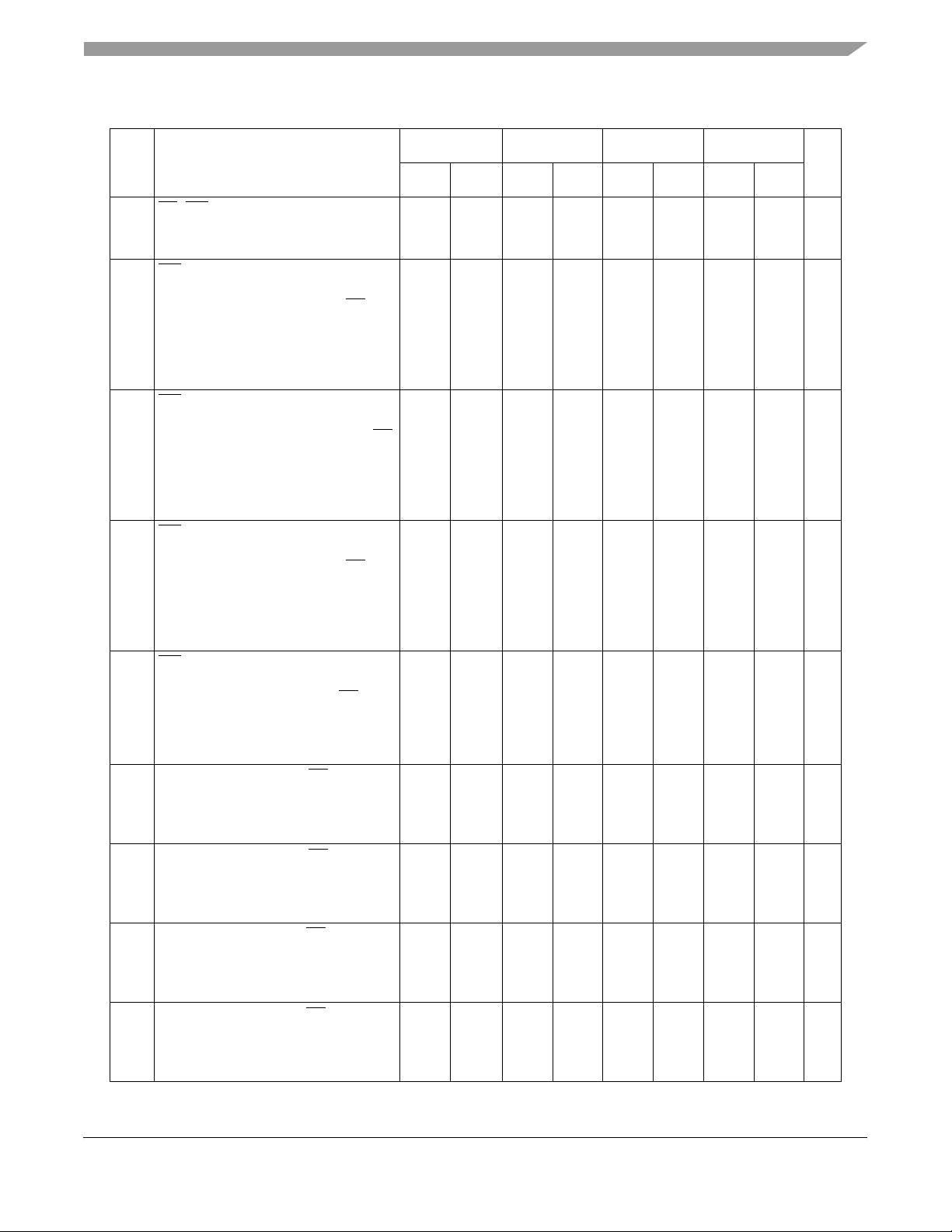

Num Characteristic

Bus Signal Timing

Table 9. Bus Operation Timings (continued)

33 MHz 40 MHz 50 MHz 66 MHz

Unit

Min Max Min Max Min Max Min Max

B30 CS, WE(0:3) negated to A(0:31),

BADDR(28:30) invalid GPCM write

access

B30a WE

7

(MIN = 0.25 x B1 – 2.00)

(0:3) negated to A(0:31),

BADDR(28:30) invalid GPCM, write

access, TRLX = 0, CSNT = 1, CS

negated to A(0:31) invalid GPCM write

access TRLX = 0, CSNT =1 ACS = 10,

or ACS == 11, EBDF = 0 (MIN = 0.50 x

B1 – 2.00)

B30b WE

(0:3) negated to A(0:31) invalid

GPCM BADDR(28:30) invalid GPCM

write access, TRLX = 1, CSNT = 1. CS

negated to A(0:31) invalid GPCM write

access TRLX = 1, CSNT = 1, ACS =

10, or ACS == 11 EBDF = 0 (MIN =

1.50 x B1 – 2.00)

B30c WE

(0:3) negated to A(0:31),

BADDR(28:30) invalid GPCM write

access, TRLX = 0, CSNT = 1. CS

negated to A(0:31) invalid GPCM write

access, TRLX = 0, CSNT = 1 ACS =

10, ACS == 11, EBDF = 1 (MIN = 0.375

x B1 – 3.00)

5.60 — 4.30 — 3.00 — 1.80 — ns

13.20 — 10.50 — 8.00 — 5.60 — ns

43.50 — 35.50 — 28.00 — 20.70 — ns

8.40 — 6.40 — 4.50 — 2.70 — ns

B30d WE

(0:3) negated to A(0:31),

BADDR(28:30) invalid GPCM write

access TRLX = 1, CSNT =1, CS

negated to A(0:31) invalid GPCM write

access TRLX = 1, CSNT = 1, ACS = 10

or 11, EBDF = 1

B31 CLKOUT falling edge to CS

requested by control bit CST4 in the

corresponding word in the UPM (MAX

= 0.00 X B1 + 6.00)

B31a CLKOUT falling edge to CS

requested by control bit CST1 in the

corresponding word in the UPM (MAX

= 0.25 x B1 + 6.80)

B31b CLKOUT rising edge to CS

requested by control bit CST2 in the

corresponding word in the UPM (MAX

= 0.00 x B1 + 8.00)

B31c CLKOUT rising edge to CS

requested by control bit CST3 in the

corresponding word in the UPM (MAX

= 0.25 x B1 + 6.30)

valid, as

valid, as

valid , as

valid , as

38.67 — 31.38 — 24.50 — 17.83 — ns

1.50 6.00 1.50 6.00 1.50 6.00 1.50 6.00 ns

7.60 14.30 6.30 13.00 5.00 11.80 3.80 10.50 ns

1.50 8.00 1.50 8.00 1.50 8.00 1.50 8.00 ns

7.60 13.80 6.30 12.50 5.00 11.30 3.80 10.00 ns

MPC866/MPC859 Hardware Specifications, Rev. 2

Freescale Semiconductor 21

Bus Signal Timing

Num Characteristic

Table 9. Bus Operation Timings (continued)

33 MHz 40 MHz 50 MHz 66 MHz

Unit

Min Max Min Max Min Max Min Max

B31d CLKOUT falling edge to CS valid, as

requested by control bit CST1 in the

corresponding word in the UPM EBDF

= 1 (MAX = 0.375 x B1 + 6.6)

B32 CLKOUT falling edge to BS

requested by control bit BST4 in the

corresponding word in the UPM (MAX

= 0.00 x B1 + 6.00)

B32a CLKOUT falling edge to BS

requested by control bit BST1 in the

corresponding word in the UPM, EBDF

= 0 (MAX = 0.25 x B1 + 6.80)

B32b CLKOUT rising edge to BS

requested by control bit BST2 in the

corresponding word in the UPM (MAX

= 0.00 x B1 + 8.00)

B32c CLKOUT rising edge to BS

requested by control bit BST3 in the

corresponding word in the UPM (MAX

= 0.25 x B1 + 6.80)

B32d CLKOUT falling edge to BS

requested by control bit BST1 in the

corresponding word in the UPM, EBDF

= 1 (MAX = 0.375 x B1 + 6.60)

valid, as

valid, as

valid, as

valid, as

valid- as

13.30 18.00 11.30 16.00 9.40 14.10 7.60 12.30 ns

1.50 6.00 1.50 6.00 1.50 6.00 1.50 6.00 ns

7.60 14.30 6.30 13.00 5.00 11.80 3.80 10.50 ns

1.50 8.00 1.50 8.00 1.50 8.00 1.50 8.00 ns

7.60 14.30 6.30 13.00 5.00 11.80 3.80 10.50 ns

13.30 18.00 11.30 16.00 9.40 14.10 7.60 12.30 ns

B33 CLKOUT falling edge to GPL

requested by control bit GxT4 in the

corresponding word in the UPM (MAX

= 0.00 x B1 + 6.00)

B33a CLKOUT rising edge to GPL

requested by control bit GxT3 in the

corresponding word in the UPM (MAX

= 0.25 x B1 + 6.80)

B34 A(0:31), BADDR(28:30), and D(0:31)

to CS

valid, as requested by control bit

CST4 in the corresponding word in the

UPM (MIN = 0.25 x B1 - 2.00)

B34a A(0:31), BADDR(28:30), and D(0:31)

to CS

valid, as requested by control bit

CST1 in the corresponding word in the

UPM (MIN = 0.50 x B1 – 2.00)

B34b A(0:31), BADDR(28:30), and D(0:31)

to CS

valid, as requested by CST2 in

the corresponding word in UPM (MIN =

0.75 x B1 – 2.00)

valid, as

valid, as

MPC866/MPC859 Hardware Specifications, Rev. 2

1.50 6.00 1.50 6.00 1.50 6.00 1.50 6.00 ns

7.60 14.30 6.30 13.00 5.00 11.80 3.80 10.50 ns

5.60 — 4.30 — 3.00 — 1.80 — ns

13.20 — 10.50 — 8.00 — 5.60 — ns

20.70 — 16.70 — 13.00 — 9.40 — ns

22 Freescale Semiconductor

Num Characteristic

Bus Signal Timing

Table 9. Bus Operation Timings (continued)

33 MHz 40 MHz 50 MHz 66 MHz

Unit

Min Max Min Max Min Max Min Max

B35 A(0:31), BADDR(28:30) to CS valid, as

requested by control bit BST4 in the

corresponding word in the UPM (MIN =

0.25 x B1 – 2.00)

B35a A(0:31), BADDR(28:30), and D(0:31)

to BS

valid, as Requested by BST1 in

the corresponding word in the UPM

(MIN = 0.50 x B1 – 2.00)

B35b A(0:31), BADDR(28:30), and D(0:31)

to BS

valid, as requested by control bit

BST2 in the corresponding word in the

UPM (MIN = 0.75 x B1 – 2.00)

B36 A(0:31), BADDR(28:30), and D(0:31)

to GPL

valid as requested by control bit

GxT4 in the corresponding word in the

UPM (MIN = 0.25 x B1 – 2.00)

B37 UPWAIT valid to CLKOUT falling

B38 CLKOUT falling edge to UPWAIT

B39 AS

8

edge

(MIN = 0.00 x B1 + 6.00)

8

(MIN = 0.00 x B1 + 1.00)

valid

valid to CLKOUT rising edge 9 (MIN

= 0.00 x B1 + 7.00)

5.60 — 4.30 — 3.00 — 1.80 — ns

13.20 — 10.50 — 8.00 — 5.60 — ns

20.70 — 16.70 — 13.00 — 9.40 — ns

5.60 — 4.30 — 3.00 — 1.80 — ns

6.00 — 6.00 — 6.00 — 6.00 — ns

1.00 — 1.00 — 1.00 — 1.00 — ns

7.00 — 7.00 — 7.00 — 7.00 — ns

B40 A(0:31), TSIZ(0:1), RD/WR

, BURST,

7.00 — 7.00 — 7.00 — 7.00 — ns

valid to CLKOUT rising edge (MIN =

0.00 x B1 + 7.00)

B41 TS

valid to CLKOUT rising edge (setup

7.00 — 7.00 — 7.00 — 7.00 — ns

time) (MIN = 0.00 x B1 + 7.00)

B42 CLKOUT rising edge to TS

valid (hold

2.00 — 2.00 — 2.00 — 2.00 — ns

time) (MIN = 0.00 x B1 + 2.00)

B43 AS

negation to memory controller

— TBD — TBD — TBD — TBD ns

signals negation (MAX = TBD)

1

For part speeds above 50 MHz, use 9.80 ns for B11a.

2

The timing required for BR input is relevant when the MPC866/859 is selected to work with the internal bus arbiter.

The timing for BG

3

For part speeds above 50 MHz, use 2 ns for B17.

4

The D(0:31) and DP(0:3) input timings B18 and B19 refer to the rising edge of CLKOUT, in which the TA input signal

input is relevant when the MPC866/859 is selected to work with the external bus arbiter.

is asserted.

5

For part speeds above 50 MHz, use 2 ns for B19.

6

The D(0:31) and DP(0:3) input timings B20 and B21 refer to the falling edge of CLKOUT. This timing is valid only for

read accesses controlled by chip-selects under control of the UPM in the memory controller, for data beats, where

DLT3 = 1 in the UPM RAM words. (This is only the case where data is latched on the falling edge of CLKOUT.)

7

The timing B30 refers to CS when ACS = 00 and to WE(0:3) when CSNT = 0.

MPC866/MPC859 Hardware Specifications, Rev. 2

Freescale Semiconductor 23

Bus Signal Timing

8

The signal UPWAIT is considered asynchronous to CLKOUT and synchronized internally. The timings specified in

B37 and B38 are specified to enable the freeze of the UPM output signals as described in Figure 20.

9

The AS signal is considered asynchronous to CLKOUT. The timing B39 is specified in order to allow the behavior

specified in Figure 23.

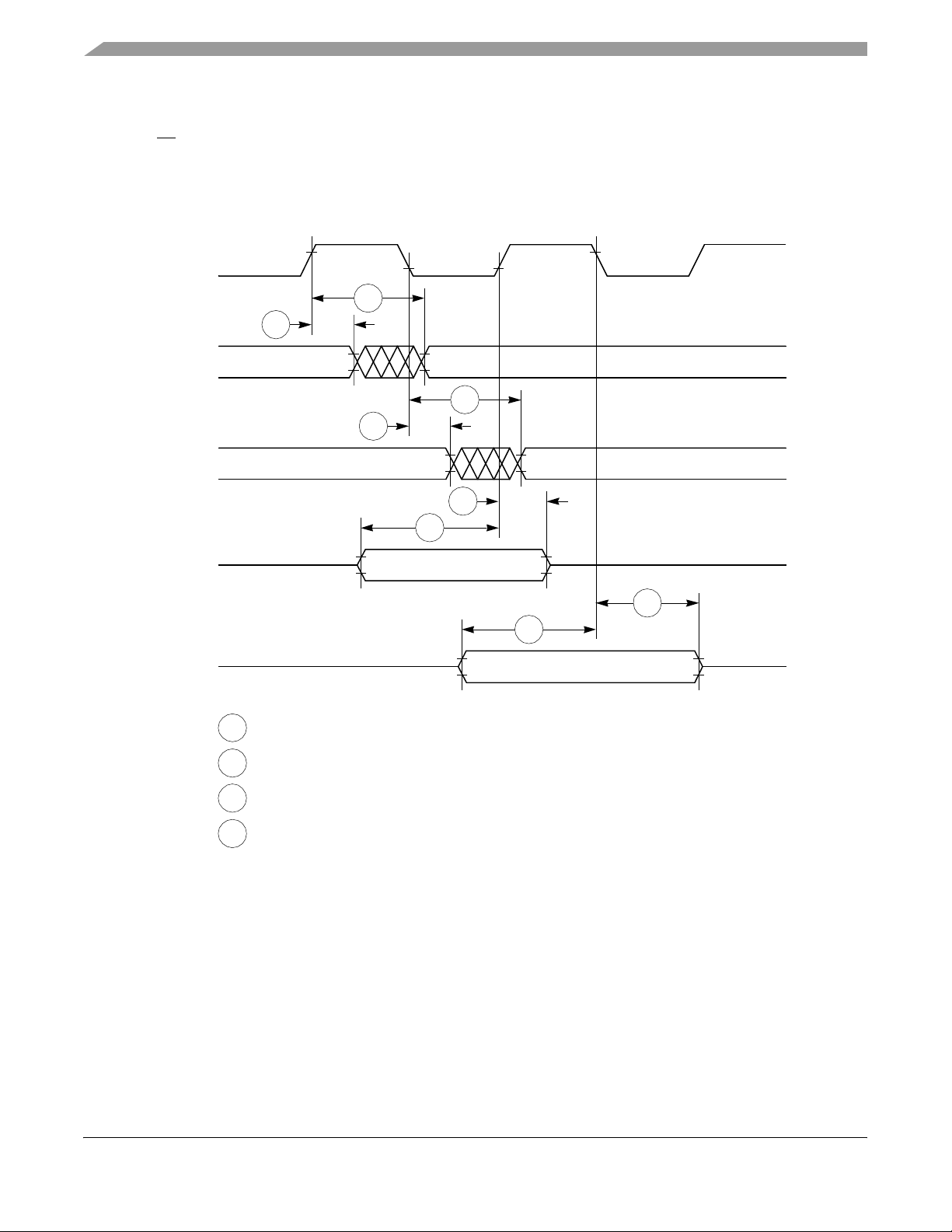

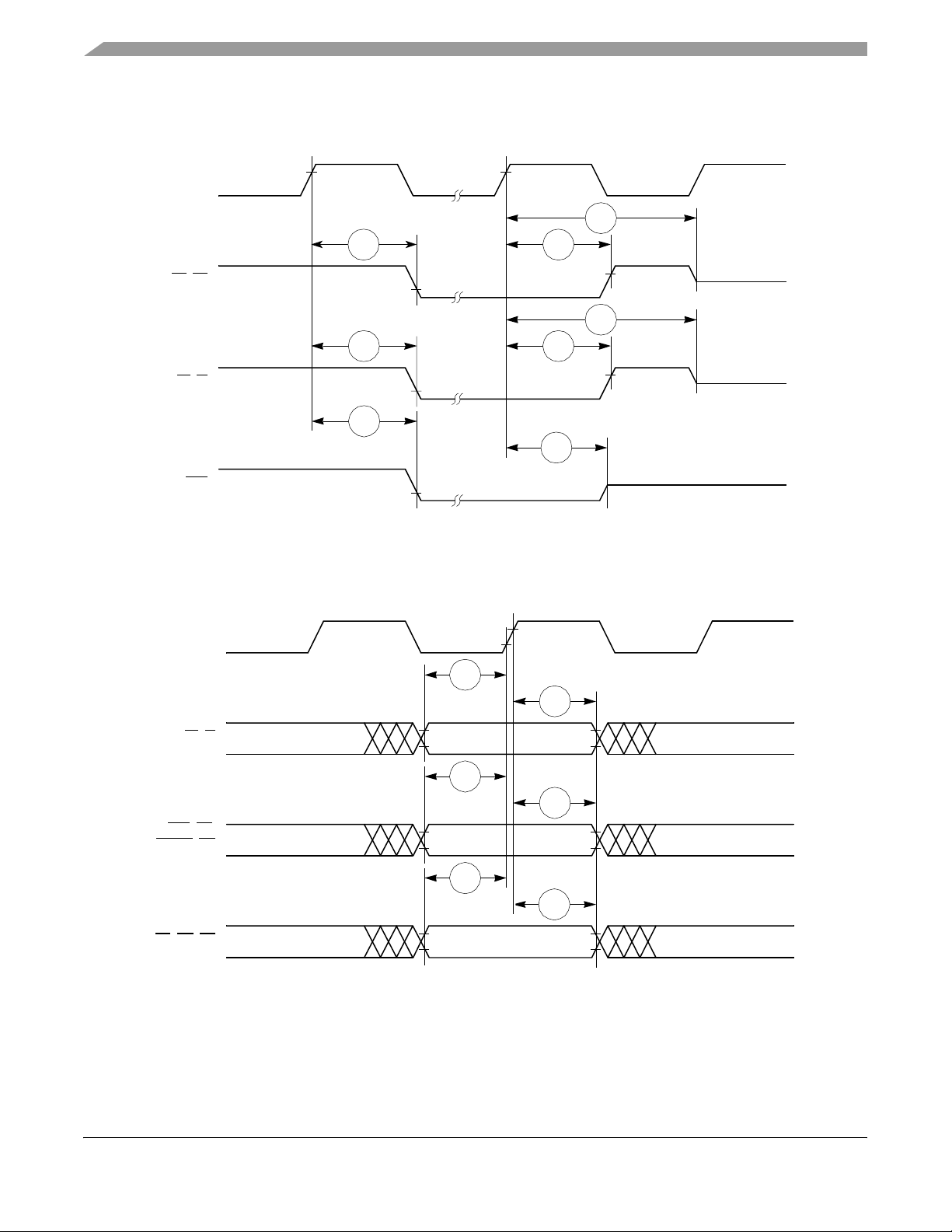

Figure 5 shows the control timing diagram.

CLKOUT

Outputs

Outputs

Inputs

Inputs

2.0 V

B

2.0 V

0.8 V

A

B

2.0 V

0.8 V

0.8 V

2.0 V

0.8 V

C

2.0 V

0.8 V

0.8 V

A

D

2.0 V

0.8 V

2.0 V

2.0 V

0.8 V

2.0 V

0.8 V

D

C

2.0 V

0.8 V

A Maximum output delay specification

B Minimum output hold time

C Minimum input setup time specification

D Minimum input hold time specification

Figure 5. Control Timing

MPC866/MPC859 Hardware Specifications, Rev. 2

24 Freescale Semiconductor

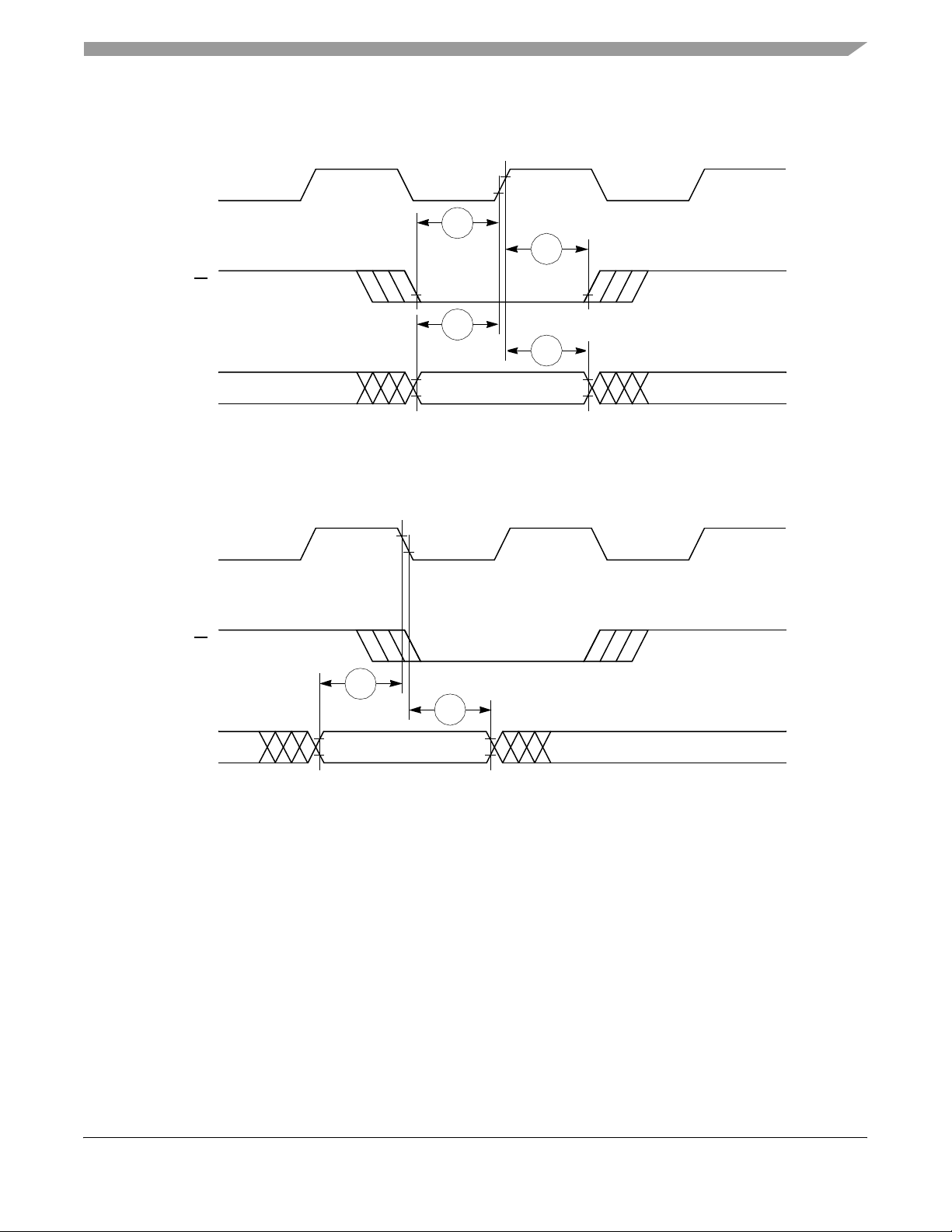

Figure 6 shows the timing for the external clock.

CLKOUT

Bus Signal Timing

B1

B1

B4

B5

Figure 6. External Clock Timing

Figure 7 shows the timing for the synchronous output signals.

CLKOUT

B8

B7 B9

Output

Signals

B8a

Output

Signals

B8b

B3

B2

B9B7a

Output

Signals

B7b

Figure 7. Synchronous Output Signals Timing

MPC866/MPC859 Hardware Specifications, Rev. 2

Freescale Semiconductor 25

Bus Signal Timing

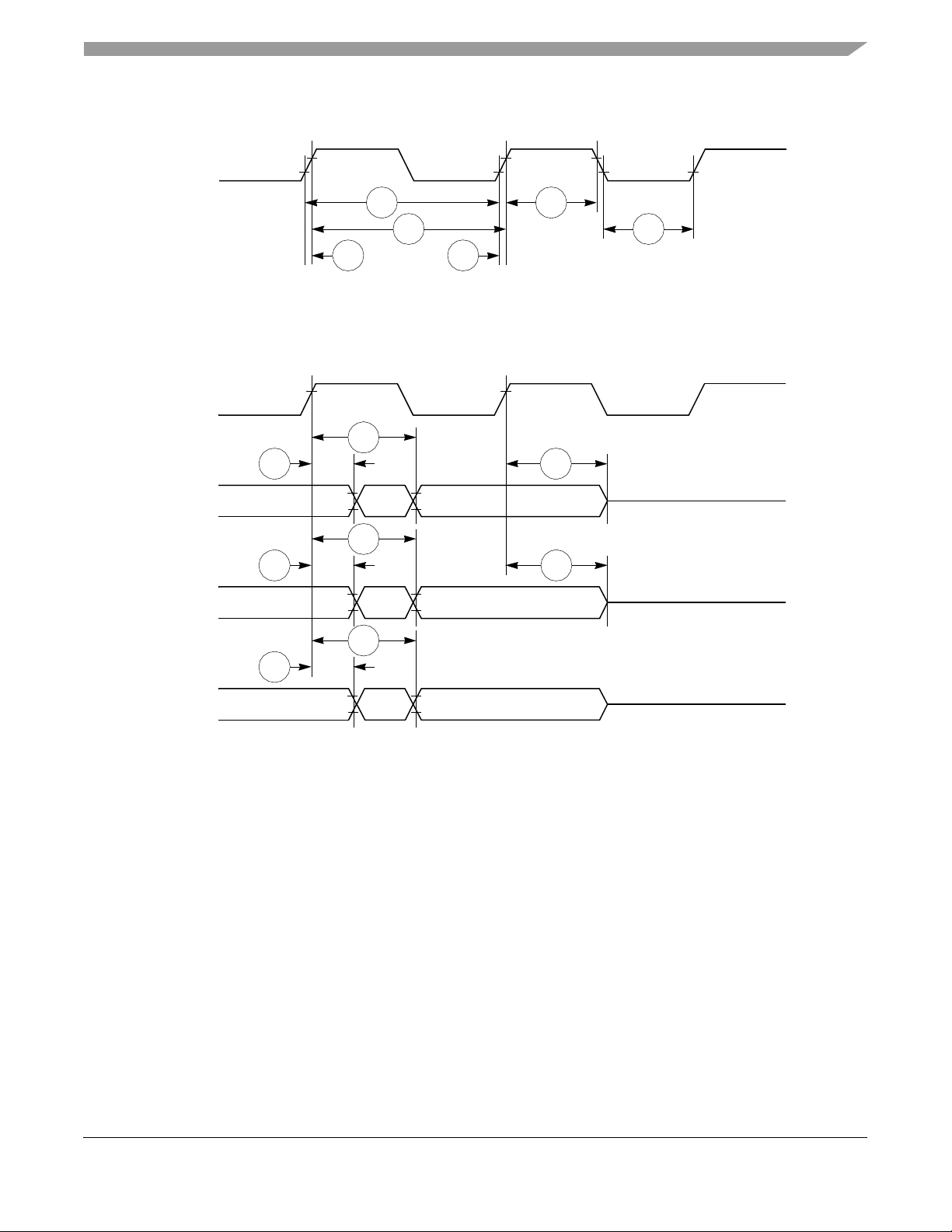

Figure 8 shows the timing for the synchronous active pull-up and open-drain output signals.

CLKOUT

B13

B12B11

TS

, BB

B13a

B11a B12a

TA , BI

B14

B15

TEA

Figure 8. Synchronous Active Pull-Up Resistor and Open-Drain Output Signals Timing

Figure 9 shows the timing for the synchronous input signals.

CLKOUT

B16

, BI

TA

B16a

TEA, KR,

RETRY

, CR

B16b

BB, BG, BR

B17

B17a

B17

Figure 9. Synchronous Input Signals Timing

MPC866/MPC859 Hardware Specifications, Rev. 2

26 Freescale Semiconductor

Bus Signal Timing

Figure 10 shows normal case timing for input data. It also applies to normal read accesses under the control of the

UPM in the memory controller.

CLKOUT

B16

B17

TA

B18

B19

D[0:31],

DP[0:3]

Figure 10. Input Data Timing in Normal Case

Figure 11 shows the timing for the input data controlled by the UPM for data beats where DLT3 = 1 in the UPM

RAM words. (This is only the case where data is latched on the fal ling edge of CLKOUT. )

CLKOUT

TA

B20

B21

D[0:31],

DP[0:3]

Figure 11. Input Data Timing when Controlled by UPM in the Memory Controller and DLT3 = 1

MPC866/MPC859 Hardware Specifications, Rev. 2

Freescale Semiconductor 27

Bus Signal Timing

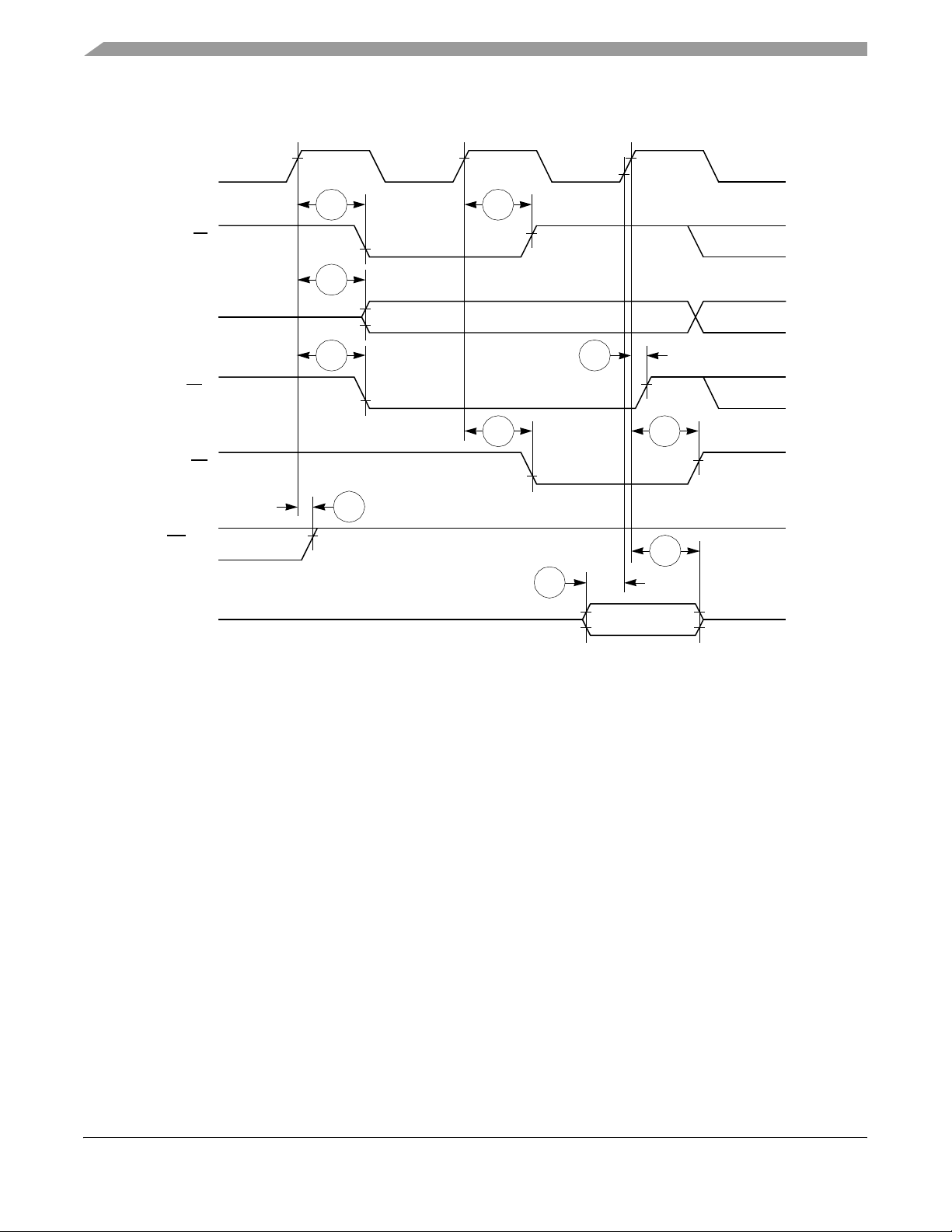

Figure 12 through Figure 15 show the timing for the external bus read controlled by various GPCM factors.

CLKOUT

B11 B12

TS

B8

A[0:31]

CSx

OE

WE[0:3]

D[0:31],

DP[0:3]

B22

B25

B28

B23

B26

B19

B18

Figure 12. External Bus Read Timing (GPCM Controlled—ACS = 00)

MPC866/MPC859 Hardware Specifications, Rev. 2

28 Freescale Semiconductor

CLKOUT

TS

A[0:31]

Bus Signal Timing

B11 B12

B8

B22a

CSx

B25B24

OE

D[0:31],

DP[0:3]

B23

B26

B19B18

Figure 13. External Bus Read Timing (GPCM Controlled—TRLX = 0 or 1, ACS = 10)

CLKOUT

B11 B12

TS

B22bB8

A[0:31]

B22c B23

CSx

B24a B25 B26

OE

B19B18

D[0:31],

DP[0:3]

Figure 14. External Bus Read Timing (GPCM Controlled—TRLX = 0 or 1, ACS = 11)

MPC866/MPC859 Hardware Specifications, Rev. 2

Freescale Semiconductor 29

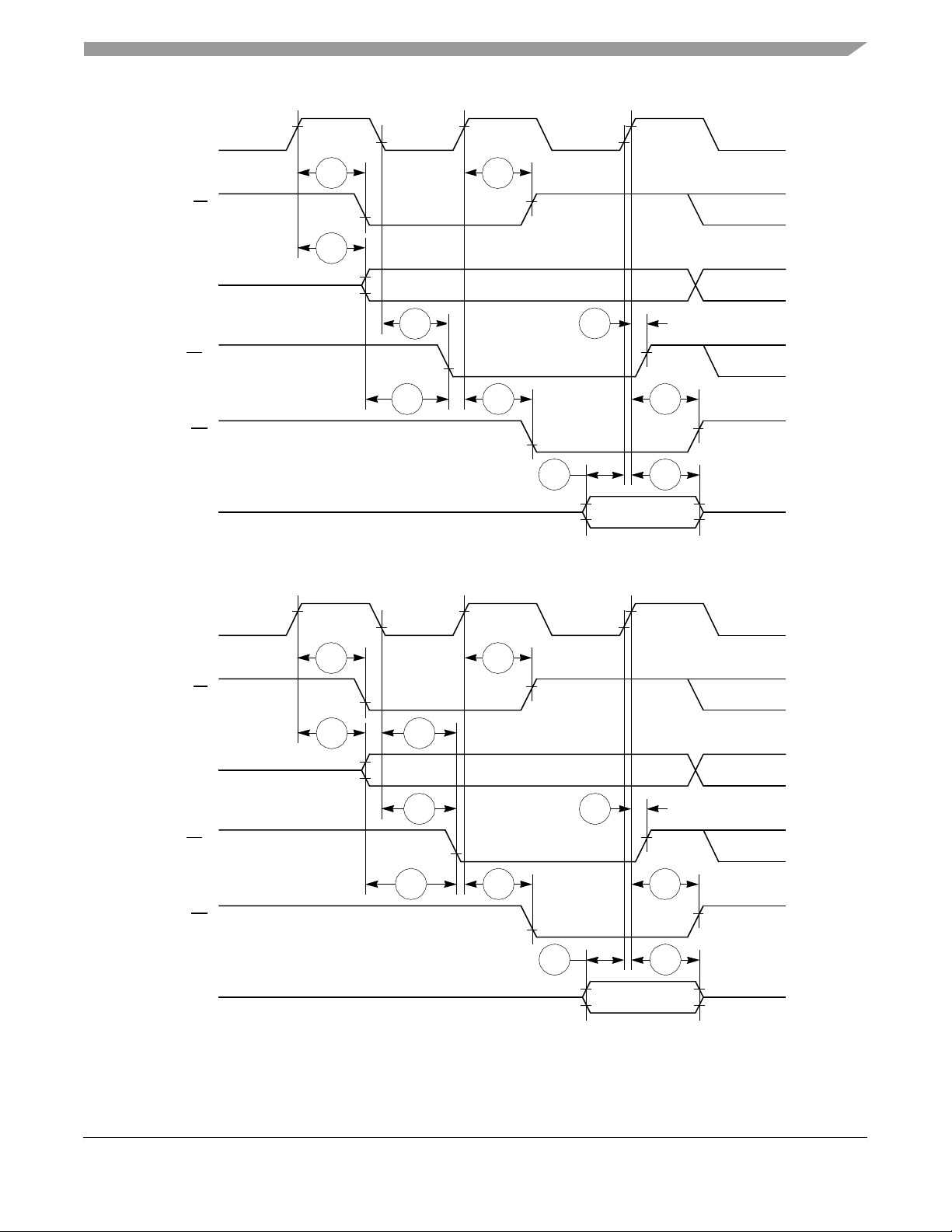

Loading...

Loading...