Page 1

集成的通信處理器

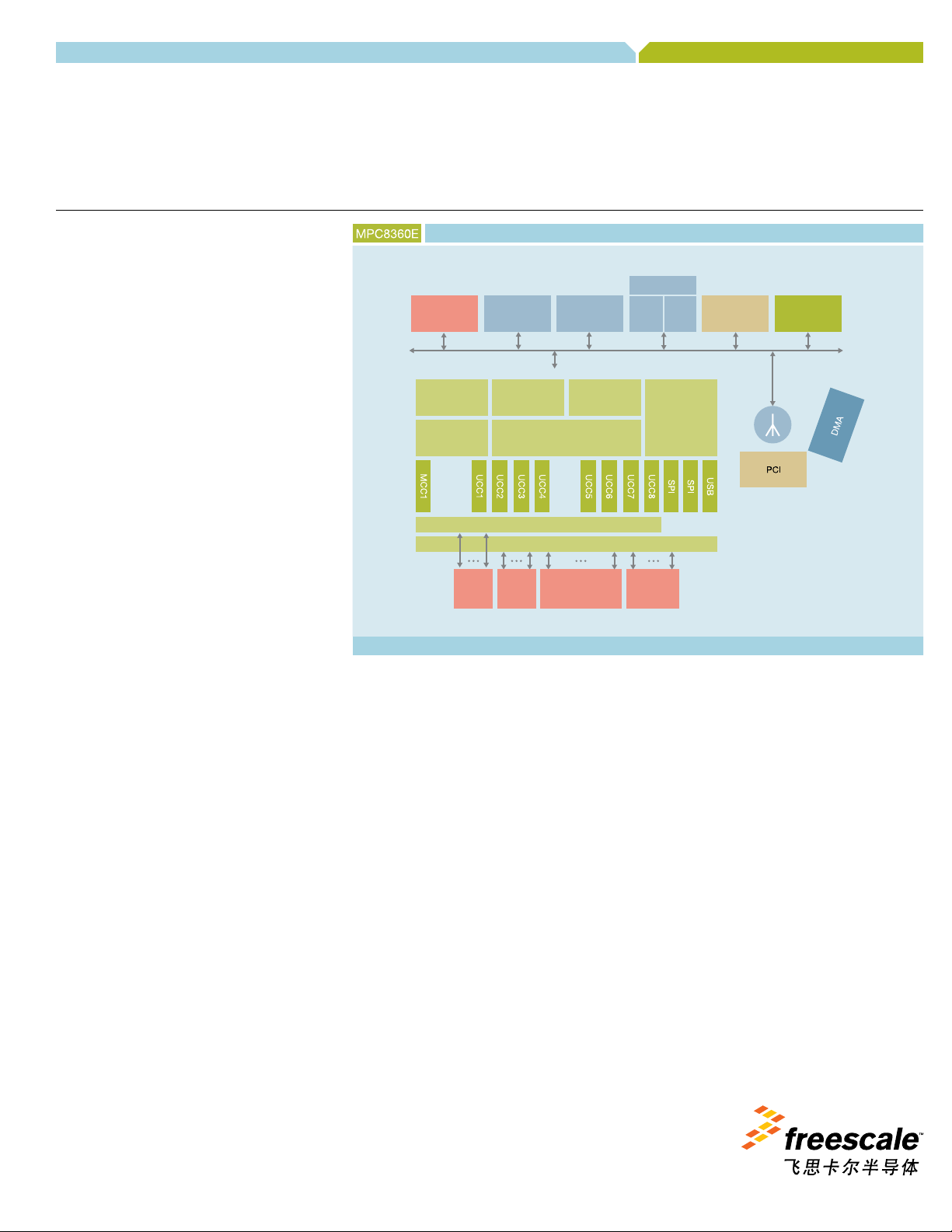

එιؿ

ΪͲʵᎽ

DUARTd

ᔶI2Cdցࣂኂd

GPIOdSPI

ɻᒾ

ઁԹኂ

e300ʑ࣏

2 KB

ᅕኣ

ᇅΦ

.%

ܞ˥

ᇅΦ

Δᐢᇃ

DDRઁԹኂ

QUICC Engine™Ҍ

ؐଅೕኂd

ցࣂኂ

ኂ༦ᓎኂ

෬ˤᆦ

Λʸ

RAM

ϷI/O

32ϽRISC෬ઁԹኂೡѵ

5205$0ࣂʗኂ

ϻϷ

DAM

2മᏃ

DAM

ࣂʗኂ

ϻϷઅɟ

TDM

ဲɟ

0,,50,,

ဲɟ

8723,$326

ဲɟc128MPHY

2GMII/RGMII

2TBI/RTBI

2

UTOPIA/POS

(128MPHY)

MPC8360E PowerQUICC™ II Pro系列

概述

飛思卡爾半導體的MPC8360E PowerQUICC

II Pro集成通信處理器系列是廣受歡迎的

PowerQUICC II的下一代產品,內置Power

Architecture技術。MPC8360E系列結合下一

代通信引擎QUICC Engine,支持一系列不同

協議,包括千兆以太網和QC-12异步傳輸模

式(ATM)/ Packet over Sonet (POS)。其他增

強功能還包括構建在Power Architecture技術

(603e內核增強版本,高速緩存容量更大)上

的e300內核,最高可擴展到667 MHz、2個

DDR內存控制器和集成的安全引擎。

MPC8360E PowerQUICC II Pro通信處理器

的先進功能使它非常適合當今和未來有線、

無線接入設備以及中小型企業聯網設備。目

標應用包括多租戶單元(MTU)、數字用戶線

路接入多路複用器(DSLAM)、無線基站、多

用戶和固定用戶接入節點、分插複用器和路

由器。

作為MPC8360E PowerQUICC II Pro系列中

的成員,MPC8358E處理器與MPC8360E

是管腳兼容的。MPC8358E是一款經濟高

效、低功率的處理解決方案,能滿足寬帶接

入應用的性能要求,如中小型企業(SME)路

由器、低端DSLAM和IP專用自動小交換機

(PABX)系統。

e300片上系統平臺

MPC8360E PowerQUICC II Pro系列基于

e300片上系統(SoC)平臺。這使得添加或刪除

功能塊既簡單又快速,同時為新興市場開發

基于SoC的其他系列成員。e300 SoC平臺

的中央是構建在Power Architecture技術上

的飛思卡爾e300內核。e300內核是上一代

PowerQUICC II 處理器中使用的603e內核

的增強版本。e300的增強包括兩倍于後者的

L1緩存(32 KB數據緩存和32 KB指令緩存),

集成的奇偶校驗及其他一些性能增強特性。

e300內核與現有的基于603e內核的產品能夠

軟件兼容。

Page 2

連通性

MPC8360E處理器能夠支持大量通信接

口,如MII、RMII、GMII、TBI、RTBI、

NMSI、UTOPIA、POS和TDM。雙32位

DDR內存控制器有助于確保高速內存接

入和速率高達133MHz的本地系統總線。

其他系統連通性通過雙UART、雙I2C、

雙串行接口(SPI)、PCI接口和通用串行

總線(USB)接口(兼容USB 2.0全速/低速)

來實現。

集成的安全

MPC8360E 和 MPC8358E處理器通過

源自于飛思卡爾安全協處理器產品線的

強大集成安全引擎實現了集成安全。

集成安全支持DES、3DES、MD-5、

SHA-1、AES 和ARC-4加密算法,

以及公共密鑰加速器和片上隨機號碼

發生器。集成的安全引擎能夠實現

single-pass加密和鑒權,符合IPsec、

IEEE® 802.11i標準和其他安全協議的

要求。

QUICC Engine

飛思卡爾QUICC Engine技術包括2個優化的

RISC處理器,不但可以支持大量協議,同時

還能提供高達1.2 Gbps的數據吞吐量。8個

統一通信控制器 (UCC)提供了靈活性,能夠

以高達OC-12的速率支持快速以太網、千兆

以太網、高級數據鏈路控制 (HDLC)和ATM/

POS。MPC8360E和MPC8358E支持最多8

個T1/E1連通性。MPC8360E支持8個TDM,

MPC8358E支持4個TDM,每個TDM都能支

持一個純通道T3/E3。MPC8360E上的一個

多通道通信控制器 (MCC)最多支持256條

64 kbps 的HDLC或透明通道。

為了簡化從當前PowerQUICC設計中的過

渡,先進的QUICC Engine引擎技術保持了與

基于PowerQUICC的上一代處理器設計很高

的軟件兼容性。這有助于減少移植問題,降

低開發成本,加快產品上市步伐。

QUICC Engine技術基于PowerQUICC

shrink-wrapped 軟件協議支持,提供互通、

解析、交換和前轉等增強功能。同時還提供

了一整套可配置驅動軟件和初始化支持。

關鍵優勢

高性能、低功率、經濟高效的通信處理器

•

解決方案

與基于分組的網絡融合

兼容當前的PowerQUICC產品

經濟高效的芯片和系統層解決方案

• 先進的QUICC Engine技術,支持大量協議

和相關的互通

• DDR內存支持 — 1個64位或2個32位接口

• 當從原有系統移植到IP系統上時風險低

• 軟件兼容性實現了產品快速上市

• 低材料單(BOM)成本

產品系列亮點

• 基于Power Architecture技術構建的e300

內核 (603e內核增強版本,更大緩存)

• DDR內存控制器,1個32/64位或2個

32位,速率高達333 MHz

• QUICC Engine技術,8個通信接口支持

快速以太網、千兆以太網、ATM、POS、

HDLC、异步HDLC、UART和透明性

• 32位PCI接口

• 32位本地總線接口

• 可選的集成安全

典型應用

• DSL基礎設施

DSLAMs

MTU

•

無線基礎設施

基站收發站(BTS)

基站控制器(BSC)

無線網絡控制器(RNC)

節點B

•

中小型企業(SME)路由器

入侵檢測/保護系統(IDS/IPS)

安全VPN

防火墙

• 分插複用器和數字交叉連接

• 集成語音路由器和數字IP專用自動小

交換機(PABX)

•

多業務接入節點(MSAN)

•

工業和通用聯網

互通

由于話音、視頻和數據的三重播放業務具備

從一個IP分組網絡中提供3股收入流的潛力,

因此它成為所有電信運營商的目標。IP是關

鍵的支持因素,而且過不了多長時間,它就

會成為普遍現象。到那時,設備必須在電路

和分組交換網絡之間,以及眾多標準和協議

之間進行互操作。標準協議間的互操作性被

稱為互通。

QUICC Engine塊支持ATM和以太網間的互

通,無需任何CPU干預,就能支持行業標準

RFC2684技術規範。此外,它還支持MC/

MLPPP和以太網間的互通。

它能夠執行強大的表格查看功能,包括從L2

到L4的多個字段,而無需CPU干預。

Page 3

技術規範

• e300 Power Architecture 內核,運行在

266 MHz至667 MHz之間

32位高性能超標量內核

667 MHz時為1261個MIPS,266 MHz時

為503個MIPS

雙精浮點、整數、負載/存儲、系統寄存

器和分支處理器單元

32 KB 數據和32 KB指令高速緩存,帶

線路鎖支持

• QUICC Engine技術,初始運行速率高達

500 MHz

2個32位RISC控制器,靈活支持通信

外設

串行DMA通道,用于所有串行通道上

的接收和發送

QUICC Engine外設請求接口,實現集成

的安全、PCI和IEEE Std 1588

8個UCC支持下列協議和接口:

·· 10/100/1000 Mbps以太網

·· 支持IEEE Std 1588協議

·· ATM SAR,支持AAL5、AAL2、

AAL1、AAL0、TM 4.0 CBR、VBR

和UBR流量類型,高達64 KB的外部

連接

·· ATM 反向複用(IMA)

·· 高達622 Mbps的POS

·· 透明

·· HDLC

··

多鏈路多級PPP

·· HDLC總線

·· UART

·· BISYNC

1個多信道通信控制器(MCC),支持:

··

256條TDM信道

·· 每信道的透明和HDLC模式

·· 支持信令系統編號(SS7)

·· 子組的幾乎任何組合都可以複用到

一個或多個TDM接口

2個UTOPIA/POS接口,每個接口最多

支持128個multi-PHY

2個串行外設接口(SPI)

8個TDM接口,支持:

·· 64 kbps的總帶寬和256條通道

·· 一條TDM鏈路上最高16 Mbps和

最多256條通道

·· 2048字節的SI RAM (1024個條目)

·· 8個可編程閃控

·· 位或字節分辨率

·· 獨立的發送和接收路由、幀同步

·· T1、CEPT、T1/E1、T3/E3、脈衝 -

代碼調製總線、ISDN首要/基本速率,

飛思卡爾芯片間數字鏈路 (IDL)和用戶

定義的TDM串行接口

16個獨立的波特率發生器

4個獨立的16位定時器,可以作為2個

32位定時器互連

2個SPI端口,可以配置成以太網管理端

口,用來管理數據輸入/輸出 (MDIO);

同時另外一個可以配置為經濟高效的串

行外設。SPI還包含CPU模式,由CPU進

行配置,而非QUICC Engine

• USB接口 (兼容USB 2.0全/低速率)

• DDR內存控制器

可編程定時,支持DDR-1/2 SDRAM

2個32位 (僅MPC8360E)或

1個32/64位數據接口;高達333 MHz

數據速率

4個內存庫,每個容量都高達1GB

全ECC支持

• PCI接口

1個32位 PCI 2.3總線控制器(3.3V I/O,

高達66 MHz)

• 集成的安全(僅MPC8360E和MPC8358E)

公共密鑰執行

(RSA和Diffie-Hellman)

數據加密標準執行

(DES和3DES)

先進的加密標準(AES)執行

ARC-4 執行(兼容RC4的算法)

信息摘要執行(SHA,MD5, HMAC)

隨機號碼生成(RNG)

• 本地總線控制器

複用的32位地址和數據操作,速率

高達133 MHz

32、16和8位端口規模,由片上內存

控制器控制

• 雙UART (DUART)

2

• 雙I

C接口 (主從模式)

• 4通道DMA控制器

• 通用平行I/O

• IEEE 1149.1 JTAG測試接入端口

• 封裝選項:37.5 mm X 37.5 mm 740

TBGA (MPC8360E, MPC8358E); 29 mm

x 29 mm 668 PBGA (僅MPC8358)

• 處理技術:130 nm CMOS

• 電壓:1.2V內核電壓,3.3V、2.5V和

1.8V I/O

Page 4

MPC8360e系列功能對比

MPC8358E MPC8360E

CPU e300 e300

•

指令高速緩存/數據高速緩存 (KB)

可用時鐘頻率 最高400 MHz 最高667 MHz

•

QUICC Engine™

•

可用時鐘頻率 最高400 MHz 最高400 MHz

•

以太網

最多2個10/100/1000 最多2個10/100/1000

32/32 32/32

2個RISC內核 2個RISC內核

最多6個10/100 最多8個10/100

•

ATM

MPHY

POS

•

•

TDM

內存控制器

本地總線

PCI

集成安全引擎*

DUART

I2C控制器

SPI

USB

中斷控制器

封裝選項

*產品名稱中的“E”表示通過集成安全引擎的加密加速度。不帶集成安全引擎的MPC8360和MPC8358處理器版本現已上市。

1個UTOPIA L2 2個UTOPIA L2

一個

31/128

端口 每個

UTOPIA

端口128個

是 是

最多4個TDM接口

速率為16Mbps時一個接口上

最多有256條通道

最多4個純通道T3/E3

1個32/64位DDR-1/2

1個32/64位或2個32/64位

最多8個TDM接口

速率為16Mbps時一個接口上

最多有256條通道

最多8個純通道T3/E3

是 是

1個32位 (最高66 MHz) 1個32位 (最高66 MHz)

是 是

是 是

2 2

2 2

是 是

是 是

740 TBGA

668 PBGA

740 TBGA

DDR-1/2

飛思卡爾TM及飛思卡爾標識都是飛思卡爾半導體的商標。所有其他產品或業務名稱為各自所有者的財產。

Architecture和Power.org

©

飛思卡爾半導體

文件編號:

REV 4

2008

MPC8360EFS

字樣標記,

Power 和 Power.org

標識及相關標記都是

Power.org

授權的注冊商標和服務商標。

瞭解更多:

Power

如需瞭解飛思卡爾產品及文獻的最新信息,

請訪問:www.freescale.com/powerquicc.

Loading...

Loading...