Page 1

Freescale Semiconductor

© Freescale Semiconductor, Inc., 2004. All rights reserved.

MPC750UM/D

12/2001

Rev. 1

nc...

MPC750 RISC Microprocessor

Family User’s Manual

Freescale Semiconductor, I

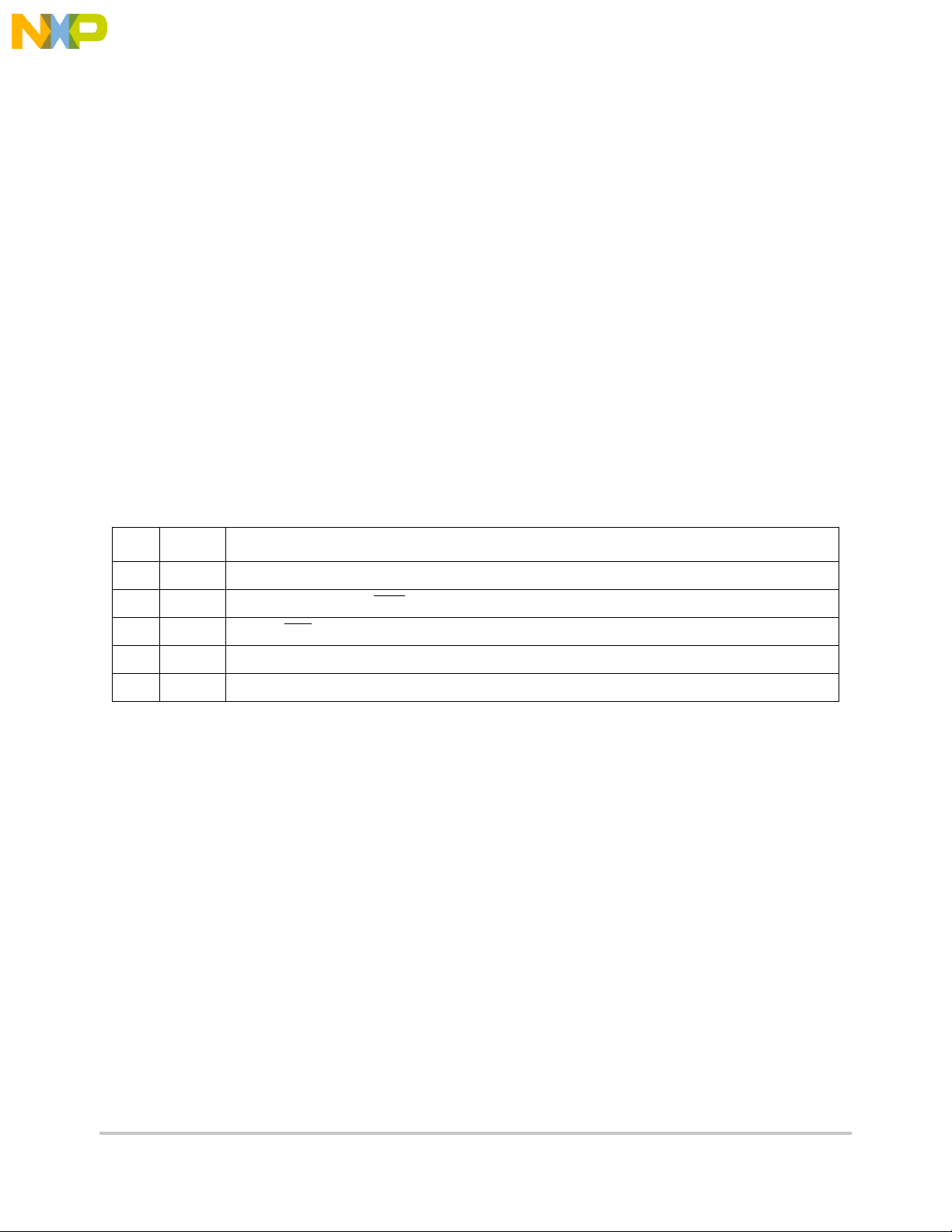

Devices Supported:

MPC755

MPC750

MPC745

MPC740

Page 2

Home Page:

www.freescale.com

email:

support@freescale.com

USA/Europe or Locations Not Listed:

Freescale Semiconductor

Technical Information Center, CH370

1300 N. Alma School Road

Chandler, Arizona 85224

(800) 521-6274

480-768-2130

support@freescale.com

Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH

Technical Information Center

Schatzbogen 7

81829 Muenchen, Germany

+44 1296 380 456 (English)

+46 8 52200080 (English)

+49 89 92103 559 (German)

+33 1 69 35 48 48 (French)

support@freescale.com

Japan:

Freescale Semiconductor Japan Ltd.

Headquarters

ARCO Tower 15F

1-8-1, Shimo-Meguro, Meguro-ku

Tokyo 153-0064, Japan

0120 191014

+81 2666 8080

support.japan@freescale.com

Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd.

Technical Information Center

2 Dai King Street

Tai Po Industrial Estate,

Tai Po, N.T., Hong Kong

+800 2666 8080

support.asia@freescale.com

For Literature Requests Only:

Freescale Semiconductor

Literature Distribution Center

P.O. Box 5405

Denver, Colorado 80217

(800) 441-2447

303-675-2140

Fax: 303-675-2150

LDCForFreescaleSemiconductor

@hibbertgroup.com

Information in this document is provided solely to enable system and software

implementers to use Freescale Semiconductor products. There are no express or

implied copyright licenses granted hereunder to design or fabricate any integrated

circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to

any products herein. Freescale Semiconductor makes no warranty, representation or

guarantee regarding the suitability of its products for any particular purpose, nor does

Freescale Semiconductor assume any liability arising out of the application or use of

any product or circuit, and specifically disclaims any and all liability, including without

limitation consequential or incidental damages. “Typical” parameters which may be

provided in Freescale Semiconductor data sheets and/or specifications can and do

vary in different applications and actual performance may vary over time. All operating

parameters, including “Typicals” must be validated for each customer application by

customer’s technical experts. Freescale Semiconductor does not convey any license

under its patent rights nor the rights of others. Freescale Semiconductor pro ducts are

not designed, intended, or authorized for use as components in systems intended for

surgical implant into the body, or other applications intended to support or sustain life,

or for any other application in which the failure of the Freescale Semiconductor product

could create a situation where personal injury or death may occur. Should Buyer

purchase or use Freescale Semiconductor products for any such unintended or

unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor

and its officers, employees, subsidiaries, affiliates, and distributors harmless against all

claims, costs, damages, and expenses, and reasonable attorney fees arising out of,

directly or indirectly, any claim of personal injury or death associated with such

unintended or unauthorized use, even if such claim alleges that Freescale

Semiconductor was negligent regarding the design or manufacture of the part.

..

.

nc

Freescale Semiconductor, Inc.

Freescale Semiconductor, I

For More Information On This Product,

Go to: www.freescale.com

Page 3

Freescale Semiconductor, Inc.

..

.

nc

Overview

Programming Model

Cache

Exceptions

Memory Management Unit

Instruction Timing

Signals

System Interface

L2 Cache Interface

Power Management

Performance Monitor

Instruction Set Listings

1

2

3

4

5

6

7

8

9

10

11

A

Freescale Semiconductor, I

Invalid Instructions

MPC755 Microprocessor

User’s Manual Revision History

Glossary

Index

For More Information On This Product,

Go to: www.freescale.com

B

C

D

GLO

IND

Page 4

Freescale Semiconductor, Inc.

..

.

nc

1

2

3

4

5

6

7

8

Overview

Programming Model

Cache

Exceptions

Memory Management Unit

Instruction Timing

Signals

System Interface

9

10

11

A

B

Freescale Semiconductor, I

C

D

LO

L2 Cache Interface

Power Management

Performance Monitor

Instruction Set Listings

Invalid Instructions

MPC755 Microprocessor

User’s Manual Revision History

Glossary

IND

Index

For More Information On This Product,

Go to: www.freescale.com

Page 5

Freescale Semiconductor, Inc.

Contents

Contents

..

.

nc

Freescale Semiconductor, I

Section

Paragraph

Number Title

Number Title

Page

Page

Number

Number

About This Book

Audience........................................................................................................... xxxii

Organization..................................................................................................... xxxiii

Suggested Reading........................................................................................... xxxiv

General Information ........................................................................... xxxiv

Related Documentation ...................................................................... xxxiv

Conventions .......................................................................................................xxxv

Acronyms and Abbreviations...........................................................................xxxvi

Terminology Conventions................................................................................ xxxix

Chapter 1

Overview

1.1 MPC750 Microprocessor Overview....................................................................1-1

1.2 MPC750 Microprocessor Features ......................................................................1-4

1.2.1 Overview of the MPC750 Microprocessor Features ....................................... 1-4

1.2.2 Instruction Flow...............................................................................................1-7

1.2.2.1 Instruction Queue and Dispatch Unit ..........................................................1-8

1.2.2.2 Branch Processing Unit (BPU)....................................................................1-8

1.2.2.3 Completion Unit .......................................................................................... 1-9

1.2.2.4 Independent Execution Units..................................................................... 1-10

1.2.2.4.1 Integer Units (IUs).................................................................................1-10

1.2.2.4.2 Floating-Point Unit (FPU)..................................................................... 1-10

1.2.2.4.3 Load/Store Unit (LSU)..........................................................................1-11

1.2.2.4.4 System Register Unit (SRU).................................................................. 1-11

1.2.3 Memory Management Units (MMUs)...........................................................1-12

1.2.4 On-Chip Instruction and Data Caches...........................................................1-13

1.2.5 L2 Cache Implementation (Not Supported in the MPC740)......................... 1-14

1.2.6 System Interface/Bus Interface Unit (BIU)...................................................1-15

1.2.7 Signals............................................................................................................ 1-16

1.2.8 Signal Configuration......................................................................................1-17

1.2.9 Clocking.........................................................................................................1-18

1.3 MPC750 Microprocessor Implementation......................................................... 1-19

1.4 PowerPC Registers and Programming Model ................................................... 1-21

Contents

For More Information On This Product,

Go to: www.freescale.com

v

Page 6

Freescale Semiconductor, Inc.

Contents

..

.

nc

Freescale Semiconductor, I

Paragraph

Number Title

1.5 Instruction Set.................................................................................................... 1-25

1.5.1 PowerPC Instruction Set................................................................................1-25

1.5.2 MPC750 Microprocessor Instruction Set ......................................................1-27

1.6 On-Chip Cache Implementation........................................................................1-27

1.6.1 PowerPC Cache Model..................................................................................1-28

1.6.2 MPC750 Microprocessor Cache Implementation..........................................1-28

1.7 Exception Model................................................................................................1-28

1.7.1 PowerPC Exception Model............................................................................ 1-28

1.7.2 MPC750 Microprocessor Exception Implementation ................................... 1-30

1.8 Memory Management........................................................................................1-31

1.8.1 PowerPC Memory Management Model........................................................1-32

1.8.2 MPC750 Microprocessor Memory Management Implementation................1-32

1.9 Instruction Timing..............................................................................................1-33

1.10 Power Management ...........................................................................................1-35

1.11 Thermal Management........................................................................................ 1-36

1.12 Performance Monitor.........................................................................................1-37

Page

Number

Chapter 2

Programming Model

2.1 The MPC750 Processor Register Set...................................................................2-1

2.1.1 Register Set......................................................................................................2-2

2.1.2 MPC750-Specific Registers.............................................................................2-9

2.1.2.1 Instruction Address Breakpoint Register (IABR)........................................2-9

2.1.2.2 Hardware Implementation-Dependent Register 0 ..................................... 2-10

2.1.2.3 Hardware Implementation-Dependent Register 1 ..................................... 2-14

2.1.2.4 Performance Monitor Registers.................................................................2-14

2.1.2.4.1 Monitor Mode Control Register 0 (MMCR0)....................................... 2-15

2.1.2.4.2 User Monitor Mode Control Register 0 (UMMCR0)............................ 2-16

2.1.2.4.3 Monitor Mode Control Register 1 (MMCR1)....................................... 2-17

2.1.2.4.4 User Monitor Mode Control Register 1 (UMMCR1)............................ 2-17

2.1.2.4.5 Performance Monitor Counter Registers (PMC1–PMC4) .................... 2-17

2.1.2.4.6 User Performance Monitor Counter Registers (UPMC1–UPMC4)...... 2-21

2.1.2.4.7 Sampled Instruction Address Register (SIA)......................................... 2-21

2.1.2.4.8 User Sampled Instruction Address Register (USIA) ............................. 2-21

2.1.2.4.9 Sampled Data Address Register (SDA) and User Sampled

Data Address Register (USDA)............................................................. 2-21

2.1.3 Instruction Cache Throttling Control Register (ICTC)..................................2-22

2.1.4 Thermal Management Registers (THRM1–THRM3) ................................... 2-22

2.1.5 L2 Cache Control Register (L2CR)...............................................................2-25

2.1.6 Reset Settings................................................................................................. 2-27

MPC750 RISC Microprocessor Family User’s Manual

For More Information On This Product,

Go to: www.freescale.com

Page 7

Freescale Semiconductor, Inc.

Contents

..

.

nc

Freescale Semiconductor, I

Paragraph

Number Title

2.2 Operand Conventions.........................................................................................2-28

2.2.1 Floating-Point Execution Models—UISA.....................................................2-28

2.2.2 Data Organization in Memory and Data Transfers........................................ 2-29

2.2.3 Alignment and Misaligned Accesses.............................................................2-29

2.2.4 Floating-Point Operand..................................................................................2-30

2.3 Instruction Set Summary....................................................................................2-31

2.3.1 Classes of Instructions...................................................................................2-33

2.3.1.1 Definition of Boundedly Undefined........................................................... 2-33

2.3.1.2 Defined Instruction Class........................................................................... 2-33

2.3.1.3 Illegal Instruction Class............................................................................. 2-34

2.3.1.4 Reserved Instruction Class.........................................................................2-35

2.3.2 Addressing Modes ......................................................................................... 2-35

2.3.2.1 Memory Addressing................................................................................... 2-35

2.3.2.2 Memory Operands ..................................................................................... 2-35

2.3.2.3 Effectiv e Address Calculation....................................................................2-36

2.3.2.4 Synchronization......................................................................................... 2-36

2.3.2.4.1 Context Synchronization ....................................................................... 2-36

2.3.2.4.2 Execution Synchronization....................................................................2-37

2.3.2.4.3 Instruction-Related Exceptions.............................................................. 2-37

2.3.3 Instruction Set Overview...............................................................................2-38

2.3.4 PowerPC UISA Instructions.......................................................................... 2-38

2.3.4.1 Integer Instructions.................................................................................... 2-38

2.3.4.1.1 Integer Arithmetic Instructions..............................................................2-38

2.3.4.1.2 Integer Compare Instructions ................................................................ 2-40

2.3.4.1.3 Integer Logical Instructions...................................................................2-40

2.3.4.1.4 Integer Rotate and Shift Instructions..................................................... 2-41

2.3.4.2 Floating-Point Instructions ........................................................................ 2-42

2.3.4.2.1 Floating-Point Arithmetic Instructions .................................................. 2-42

2.3.4.2.2 Floating-Point Multiply-Add Instructions............................................. 2-43

2.3.4.2.3 Floating-Point Rounding and Conversion Instructions ......................... 2-43

2.3.4.2.4 Floating-Point Compare Instructions..................................................... 2-44

2.3.4.2.5 Floating-Point Status and Control Register Instructions....................... 2-44

2.3.4.2.6 Floating-Point Move Instructions..........................................................2-45

2.3.4.3 Load and Store Instructions....................................................................... 2-45

2.3.4.3.1 Self-Modifying Code.............................................................................2-46

2.3.4.3.2 Integer Load and Store Address Generation..........................................2-46

2.3.4.3.3 Register Indirect Integer Load Instructions........................................... 2-46

2.3.4.3.4 Integer Store Instructions....................................................................... 2-48

2.3.4.3.5 Integer Store Gathering..........................................................................2-49

2.3.4.3.6 Integer Load and Store with Byte-Reverse Instructions........................2-49

2.3.4.3.7 Integer Load and Store Multiple Instructions........................................2-49

Page

Number

Contents

For More Information On This Product,

Go to: www.freescale.com

vii

Page 8

Freescale Semiconductor, Inc.

Contents

..

.

nc

Freescale Semiconductor, I

Paragraph

Number Title

2.3.4.3.8 Integer Load and Store String Instructions............................................2-50

2.3.4.3.9 Floating-Point Load and Store Address Generation..............................2-51

2.3.4.3.10 Floating-Point Store Instructions...........................................................2-52

2.3.4.4 Branch and Flow Control Instructions....................................................... 2-54

2.3.4.4.1 Branch Instruction Address Calculation................................................2-54

2.3.4.4.2 Branch Instructions................................................................................2-54

2.3.4.4.3 Condition Register Logical Instructions................................................2-55

2.3.4.4.4 Trap Instructions....................................................................................2-55

2.3.4.5 System Linkage Instruction—UISA..........................................................2-56

2.3.4.6 Processor Control Instructions—UISA ..................................................... 2-56

2.3.4.6.1 Move to/from Condition Register Instructions...................................... 2-56

2.3.4.6.2 Move to/from Special-Purpose Register Instructions (UISA)...............2-56

2.3.4.7 Memory Synchronization Instructions—UISA......................................... 2-59

2.3.5 PowerPC VEA Instructions............................................................................ 2-60

2.3.5.1 Processor Control Instructions—VEA ......................................................2-60

2.3.5.2 Memory Synchronization Instructions—VEA .......................................... 2-61

2.3.5.3 Memory Control Instructions—VEA ........................................................ 2-62

2.3.5.3.1 User-Level Cache Instructions—VEA ..................................................2-62

2.3.5.4 Optional External Control Instructions...................................................... 2-64

2.3.6 PowerPC OEA Instructions...........................................................................2-65

2.3.6.1 System Linkage Instructions—OEA ......................................................... 2-65

2.3.6.2 Processor Control Instructions—OEA ......................................................2-65

2.3.6.3 Memory Control Instructions—OEA ........................................................ 2-66

2.3.6.3.1 Supervisor-Level Cache Management Instruction—(OEA)..................2-66

2.3.6.3.2 Segment Register Manipulation Instructions (OEA)............................. 2-67

2.3.6.3.3 Translation Lookaside Buffer Management Instructions—(OEA)........ 2-67

2.3.7 Recommended Simplified Mnemonics..........................................................2-68

Page

Number

Chapter 3

L1 Instruction and Data Cache Operation

3.1 Data Cache Organization..................................................................................... 3-3

3.2 Instruction Cache Organization ........................................................................... 3-4

3.3 Memory and Cache Coherency............................................................................ 3-5

3.3.1 Memory/Cache Access Attributes (WIMG Bits)............................................. 3-6

3.3.2 MEI Protocol....................................................................................................3-7

3.3.2.1 MEI Hardware Considerations .................................................................... 3-9

3.3.3 Coherency Precautions in Single Processor Systems....................................3-10

3.3.4 Coherency Precautions in Multiprocessor Systems.......................................3-10

3.3.5 MPC750-Initiated Load/Store Operations.....................................................3-10

3.3.5.1 Performed Loads and Stores......................................................................3-11

MPC750 RISC Microprocessor Family User’s Manual

For More Information On This Product,

Go to: www.freescale.com

Page 9

Freescale Semiconductor, Inc.

Contents

..

.

nc

Freescale Semiconductor, I

Paragraph

Number Title

3.3.5.2 Sequential Consistency of Memory Accesses ...........................................3-11

3.3.5.3 Atomic Memory References......................................................................3-11

3.4 Cache Control .................................................................................................... 3-13

3.4.1 Cache Control Parameters in HID0...............................................................3-13

3.4.1.1 Data Cache Flash Invalidation................................................................... 3-13

3.4.1.2 Data Cache Enabling/Disabling................................................................. 3-13

3.4.1.3 Data Cache Locking ..................................................................................3-14

3.4.1.4 Instruction Cache Flash Invalidation ......................................................... 3-14

3.4.1.5 Instruction Cache Enabling/Disabling.......................................................3-14

3.4.1.6 Instruction Cache Locking......................................................................... 3-15

3.4.2 Cache Control Instructions ............................................................................ 3-15

3.4.2.1 Data Cache Block Touch (dcbt) and

Data Cache Block Touch for Store (dcbtst)...........................................3-15

3.4.2.2 Data Cache Block Zero (

3.4.2.3 Data Cache Block Store (

3.4.2.4 Data Cache Block Flush (

3.4.2.5 Data Cache Block Invalidate (

3.4.2.6 Instruction Cache Block Invalidate (

3.5 Cache Operations...............................................................................................3-18

3.5.1 Cache Block Replacement/Castout Operations............................................. 3-18

3.5.2 Cache Flush Operations.................................................................................3-21

3.5.3 Data Cache-Block-Fill Operations.................................................................3-21

3.5.4 Instruction Cache-Block-Fill Operations.......................................................3-21

3.5.5 Data Cache-Block-Push Operation................................................................3-22

3.5.5.1 Enveloped High-Priority Cache-Block-Push Operation............................ 3-22

3.6 L1 Caches and 60x Bus Transactions................................................................ 3-22

3.6.1 Read Operations and the MEI Protocol......................................................... 3-23

3.6.2 Bus Operations Caused by Cache Control Instructions.................................3-23

3.6.3 Snooping........................................................................................................ 3-25

3.6.4 Snoop Response to 60x Bus Transactions..................................................... 3-26

3.6.5 Transfer Attributes......................................................................................... 3-28

3.7 Bus Interface...................................................................................................... 3-30

3.8 MEI State Transactions......................................................................................3-31

dcbz ).................................................................. 3-16

dcbst )................................................................ 3-17

dcbf )................................................................. 3-17

dcbi )...........................................................3-17

icbi )..................................................3-18

Page

Number

Chapter 4

Exceptions

4.1 MPC750 Microprocessor Exceptions..................................................................4-2

4.2 Exception Recognition and Priorities .................................................................. 4-4

4.3 Exception Processing...........................................................................................4-7

4.3.1 Enabling and Disabling Exceptions...............................................................4-10

Contents

For More Information On This Product,

Go to: www.freescale.com

ix

Page 10

Freescale Semiconductor, Inc.

Contents

..

.

nc

Freescale Semiconductor, I

Paragraph

Number Title

4.3.2 Steps for Exception Processing......................................................................4-10

4.3.3 Setting MSR[RI]............................................................................................4-11

4.3.4 Returning from an Exception Handler...........................................................4-11

4.4 Process Switching.............................................................................................. 4-12

4.5 Exception Definitions.........................................................................................4-12

4.5.1 System Reset Exception (0x00100)...............................................................4-13

4.5.2 Machine Check Exception (0x00200) ........................................................... 4-14

4.5.2.1 Machine Check Exception Enabled (MSR[ME] = 1)................................4-16

4.5.2.2 Checkstop State (MSR[ME] = 0) ..............................................................4-16

4.5.3 DSI Exception (0x00300).............................................................................. 4-17

4.5.4 ISI Exception (0x00400)................................................................................ 4-17

4.5.5 External Interrupt Exception (0x00500)........................................................ 4-17

4.5.6 Alignment Exception (0x00600) ...................................................................4-18

4.5.7 Program Exception (0x00700).......................................................................4-18

4.5.8 Floating-Point Unavailable Exception (0x00800)......................................... 4-19

4.5.9 Decrementer Exception (0x00900)................................................................4-19

4.5.10 System Call Exception (0x00C00) ................................................................4-19

4.5.11 Trace Exception (0x00D00)...........................................................................4-19

4.5.12 Floating-Point Assist Exception (0x00E00)..................................................4-20

4.5.13 Performance Monitor Interrupt (0x00F00)....................................................4-20

4.5.14 Instruction Address Breakpoint Exception (0x01300)...................................4-21

4.5.15 System Management Interrupt (0x01400)..................................................... 4-22

4.5.16 Thermal Management Interrupt Exception (0x01700).................................. 4-23

Page

Number

Chapter 5

Memory Management

5.1 MMU Overview...................................................................................................5-2

5.1.1 Memory Addressing......................................................................................... 5-3

5.1.2 MMU Organization..........................................................................................5-4

5.1.3 Address Translation Mechanisms.................................................................... 5-7

5.1.4 Memory Protection Facilities...........................................................................5-9

5.1.5 Page History Information...............................................................................5-10

5.1.6 General Flow of MMU Address Translation.................................................5-11

5.1.6.1 Real Addressing Mode and Block Address

Translation Selection.............................................................................5-11

5.1.6.2 Page Address Translation Selection........................................................... 5-12

5.1.7 MMU Exceptions Summary.......................................................................... 5-14

5.1.8 MMU Instructions and Register Summary....................................................5-16

5.2 Real Addressing Mode....................................................................................... 5-18

5.3 Block Address Translation................................................................................. 5-18

MPC750 RISC Microprocessor Family User’s Manual

For More Information On This Product,

Go to: www.freescale.com

Page 11

Freescale Semiconductor, Inc.

Contents

..

.

nc

Freescale Semiconductor, I

Paragraph

Number Title

5.4 Memory Segment Model ................................................................................... 5-19

5.4.1 Page History Recording.................................................................................5-19

5.4.1.1 Referenced Bit ........................................................................................... 5-20

5.4.1.2 Changed Bit ...............................................................................................5-21

5.4.1.3 Scenarios for Referenced and Changed Bit Recording ............................. 5-21

5.4.2 Page Memory Protection ...............................................................................5-23

5.4.3 TLB Description............................................................................................5-23

5.4.3.1 TLB Organization......................................................................................5-23

5.4.3.2 TLB Invalidation........................................................................................5-25

5.4.4 Page Address Translation Summary ..............................................................5-26

5.4.5 Page Table Search Operation.........................................................................5-27

5.4.6 Page Table Updates........................................................................................ 5-31

5.4.7 Segment Register Updates.............................................................................5-32

Page

Number

Chapter 6

Instruction Timing

6.1 Terminology and Conventions.............................................................................6-1

6.2 Instruction Timing Overvie w...............................................................................6-3

6.3 Timing Considerations.........................................................................................6-7

6.3.1 General Instruction Flow.................................................................................6-8

6.3.2 Instruction Fetch Timing................................................................................6-10

6.3.2.1 Cache Arbitration.......................................................................................6-11

6.3.2.2 Cache Hit ................................................................................................... 6-11

6.3.2.3 Cache Miss................................................................................................. 6-14

6.3.2.4 L2 Cache Access Timing Considerations ................................................. 6-15

6.3.3 Instruction Dispatch and Completion Considerations...................................6-16

6.3.3.1 Rename Register Operation.......................................................................6-17

6.3.3.2 Instruction Serialization.............................................................................6-17

6.4 Execution Unit Timings.....................................................................................6-18

6.4.1 Branch Processing Unit Execution Timing....................................................6-18

6.4.1.1 Branch Folding and Removal of Fall-Through Branch Instructions ......... 6-18

6.4.1.2 Branch Instructions and Completion ......................................................... 6-20

6.4.1.3 Branch Prediction and Resolution ............................................................. 6-21

6.4.1.3.1 Static Branch Prediction........................................................................6-22

6.4.1.3.2 Predicted Branch Timing Examples...................................................... 6-22

6.4.2 Integer Unit Execution Timing ...................................................................... 6-24

6.4.3 Floating-Point Unit Execution Timing ..........................................................6-24

6.4.4 Effect of Floating-Point Exceptions on Performance.................................... 6-25

6.4.5 Load/Store Unit Execution Timing................................................................6-25

6.4.6 Effect of Operand Placement on Performance...............................................6-25

Contents

For More Information On This Product,

Go to: www.freescale.com

xi

Page 12

Freescale Semiconductor, Inc.

Contents

..

.

nc

Freescale Semiconductor, I

Paragraph

Number Title

6.4.7 Integer Store Gathering.................................................................................. 6-26

6.4.8 System Register Unit Execution Timing........................................................6-27

6.5 Memory Performance Considerations ............................................................... 6-27

6.5.1 Caching and Memory Coherency..................................................................6-27

6.5.2 Effect of TLB Miss........................................................................................6-28

6.6 Instruction Scheduling Guidelines.....................................................................6-28

6.6.1 Branch, Dispatch, and Completion Unit Resource Requirements.................6-29

6.6.1.1 Branch Resolution Resource Requirements .............................................. 6-29

6.6.1.2 Dispatch Unit Resource Requirements......................................................6-30

6.6.1.3 Completion Unit Resource Requirements ................................................. 6-30

6.7 Instruction Latency Summary............................................................................6-31

Page

Number

Chapter 7

Signal Descriptions

7.1 Signal Configuration............................................................................................ 7-2

7.2 Signal Descriptions.............................................................................................. 7-3

7.2.1 Address Bus Arbitration Signals......................................................................7-4

7.2.1.1 Bus Request (BR

7.2.1.2 Bus Grant (BG

7.2.1.3 Address Bus Busy (ABB

7.2.1.3.1 Address Bus Busy (ABB

7.2.1.3.2 Address Bus Busy (ABB

7.2.2 Address Transfer Start Signals.........................................................................7-6

7.2.2.1 Transfer Start (TS

7.2.2.1.1 Transfer Start (TS

7.2.2.1.2 Transfer Start (TS

7.2.3 Address Transfer Signals................................................................................. 7-7

7.2.3.1 Address Bus (A[0–31])................................................................................7-7

7.2.3.1.1 Address Bus (A[0–31])—Output............................................................. 7-7

7.2.3.1.2 Address Bus (A[0–31])—Input ............................................................... 7-7

7.2.3.2 Address Bus Parity (AP[0–3])..................................................................... 7-7

7.2.3.2.1 Address Bus Parity (AP[0–3])—Output..................................................7-8

7.2.3.2.2 Address Bus Parity (AP[0–3])—Input.....................................................7-8

7.2.4 Address Transfer Attribute Signals..................................................................7-8

7.2.4.1 Transfer Type (TT[0–4]).............................................................................. 7-8

7.2.4.1.1 Transfer Type (TT[0–4])—Output...........................................................7-9

7.2.4.1.2 Transfer Type (TT[0–4])—Input .............................................................7-9

7.2.4.2 Transfer Size (TSIZ[0–2])—Output.......................................................... 7-11

7.2.4.3 Transfer Burst (TBST

7.2.4.3.1 Transfer Burst (TBST

)—Output......................................................................... 7-4

)—Input ............................................................................... 7-4

)............................................................................7-5

)—Output......................................................... 7-5

)—Input ........................................................... 7-5

)....................................................................................... 7-6

)—Output....................................................................7-6

)—Input.......................................................................7-6

)...............................................................................7-12

)—Output............................................................ 7-12

MPC750 RISC Microprocessor Family User’s Manual

For More Information On This Product,

Go to: www.freescale.com

Page 13

Freescale Semiconductor, Inc.

Contents

..

.

nc

Freescale Semiconductor, I

Paragraph

Number Title

7.2.4.3.2 Transfer Burst (TBST)—Input..............................................................7-12

7.2.4.4 Cache Inhibit (CI

7.2.4.5 Write-Through (WT

7.2.4.6 Global (GBL

7.2.4.6.1 Global (GBL

7.2.4.6.2 Global (GBL

7.2.5 Address Transfer Termination Signals...........................................................7-14

7.2.5.1 Address Acknowledge (AA

7.2.5.2 Address Retry (ARTRY

7.2.5.2.1 Address Retry (AR

7.2.5.2.2 Address Retry (AR

7.2.6 Data Bus Arbitration Signals......................................................................... 7-16

7.2.6.1 Data Bus Grant (DBG

7.2.6.2 Data Bus Write Only (DBW

7.2.6.3 Data Bus Busy (DBB

7.2.6.3.1 Data Bus Busy (DBB

7.2.6.3.2 Data Bus Busy (DBB

7.2.7 Data Transfer Signals..................................................................................... 7-17

7.2.7.1 Data Bus (DH[0–31], DL[0–31]) ..............................................................7-18

7.2.7.1.1 Data Bus (DH[0–31], DL[0–31])—Output ........................................... 7-18

7.2.7.1.2 Data Bus (DH[0–31], DL[0–31])—Input..............................................7-18

7.2.7.2 Data Bus Parity (DP[0–7])......................................................................... 7-19

7.2.7.2.1 Data Bus Parity (DP[0–7])—Output ..................................................... 7-19

7.2.7.2.2 Data Bus Parity (DP[0–7])—Input........................................................ 7-19

7.2.7.3 Data Bus Disable (DBDIS

7.2.8 Data Transfer Termination Signals ................................................................7-20

7.2.8.1 Transfer Acknowledge (T

7.2.8.2 Data Retry (DR

7.2.8.3 Transfer Error Acknowledge (TEA

7.2.9 System Status Signals.................................................................................... 7-22

7.2.9.1 Interrupt (INT

7.2.9.2 System Management Interrupt (SMI

7.2.9.3 Machine Check Interrupt (MCP

7.2.9.4 Checkstop Input (CKSTP_IN

7.2.9.5 Checkstop Output (CKSTP_OUT

7.2.9.6 Reset Signals.............................................................................................. 7-24

7.2.9.6.1 Hard Reset (HRESET

7.2.9.6.2 Soft Reset (SRESET

7.2.9.7 Processor Status Signals............................................................................7-25

7.2.9.7.1 Quiescent Request (QREQ

7.2.9.7.2 Quiescent Acknowledge (QACK

)—Output.......................................................................7-13

)—Output.................................................................. 7-13

).............................................................................................7-13

)—Output.......................................................................... 7-13

)—Input ............................................................................ 7-14

CK)—Input....................................................7-14

)........................................................................... 7-14

TRY)—Output ........................................................7-14

TRY)—Input...........................................................7-15

)—Input..................................................................7-16

O)—Input ..................................................... 7-16

) ...............................................................................7-17

)—Output ............................................................ 7-17

)—Input...............................................................7-17

)—Input ........................................................... 7-19

A)—Input..........................................................7-20

TRY)—Input.....................................................................7-21

)—Input.............................................. 7-21

)—Input............................................................................... 7-22

)—Input ...........................................7-22

)—Input................................................... 7-22

)—Input ......................................................7-23

)—Output.............................................7-23

)—Input..............................................................7-24

)—Input................................................................ 7-24

)—Output.................................................... 7-25

)—Input.............................................7-25

Page

Number

Contents

For More Information On This Product,

Go to: www.freescale.com

xiii

Page 14

Freescale Semiconductor, Inc.

Contents

..

.

nc

Freescale Semiconductor, I

Paragraph

Number Title

7.2.9.7.3 Reservation (RSRV)—Output...............................................................7-25

7.2.9.7.4 Time Base Enable (TBEN)—Input........................................................7-26

7.2.9.7.5 TLBI Sync (TLBISYNC

7.2.9.7.6 L2 Cache Interface................................................................................. 7-26

7.2.9.8 L2 Address (L2ADDR[16–0])—Output.................................................... 7-26

7.2.9.9 L2 Data (L2DATA[0–63]) ......................................................................... 7-27

7.2.9.9.1 L2 Data (L2DATA[0–63])—Output ...................................................... 7-27

7.2.9.9.2 L2 Data (L2DATA[0–63])—Input......................................................... 7-27

7.2.9.10 L2 Data Parity (L2DP[0–7])...................................................................... 7-27

7.2.9.10.1 L2 Data Parity (L2DP[0–7])—Output...................................................7-27

7.2.9.10.2 L2 Data Parity (L2DP[0–7])—Input .....................................................7-27

7.2.9.11 L2 Chip Enable (L2CE)—Output..............................................................7-28

7.2.9.12 L2 Write Enable (L2WE)—Output ...........................................................7-28

7.2.9.13 L2 Clock Out A (L2CLK_OUTA)—Output..............................................7-28

7.2.9.14 L2 Clock Out B (L2CLK_OUTB)—Output..............................................7-28

7.2.9.15 L2 Sync Out (L2SYNC_OUT)—Output...................................................7-29

7.2.9.16 L2 Sync In (L2SYNC_IN)—Input ............................................................ 7-29

7.2.9.17 L2 Low-Power Mode Enable (L2ZZ)—Output......................................... 7-29

7.2.10 IEEE 1149.1a-1993 Interface Description.....................................................7-30

7.2.11 Clock Signals................................................................................................. 7-30

7.2.11.1 System Clock (SYSCLK)—Input.............................................................. 7-30

7.2.11.2 Clock Out (CLK_OUT)—Output..............................................................7-31

7.2.11.3 PLL Configuration (PLL_CFG[0–3])—Input ...........................................7-31

7.2.12 Power and Ground Signals.............................................................................7-31

)—Input.......................................................... 7-26

Page

Number

Chapter 8

System Interface Operation

8.1 MPC750 System Interface Overview .................................................................. 8-1

8.1.1 Operation of the Instruction and Data L1 Caches............................................8-2

8.1.2 Operation of the L2 Cache...............................................................................8-4

8.1.3 Operation of the System Interface...................................................................8-4

8.1.4 Direct-Store Accesses......................................................................................8-6

8.2 Memory Access Protocol ..................................................................................... 8-6

8.2.1 Arbitration Signals...........................................................................................8-7

8.2.2 Address Pipelining and Split-Bus Transactions...............................................8-8

8.3 Address Bus Tenure .............................................................................................8-9

8.3.1 Address Bus Arbitration...................................................................................8-9

8.3.2 Address Transfer............................................................................................8-12

8.3.2.1 Address Bus Parity.....................................................................................8-13

8.3.2.2 Address Transfer Attribute Signals............................................................ 8-13

MPC750 RISC Microprocessor Family User’s Manual

For More Information On This Product,

Go to: www.freescale.com

Page 15

Freescale Semiconductor, Inc.

Contents

..

.

nc

Freescale Semiconductor, I

Paragraph

Number Title

8.3.2.2.1 Transfer Type (TT[0–4]) Signals........................................................... 8-13

8.3.2.2.2 Transfer Size (TSIZ[0–2]) Signals ........................................................ 8-14

8.3.2.2.3 Write-Through (WT) Signal..................................................................8-14

8.3.2.2.4 Cache Inhibit (CI) Signal....................................................................... 8-15

8.3.2.3 Burst Ordering During Data Transfers ...................................................... 8-15

8.3.2.4 Effect of Alignment in Data Transfers....................................................... 8-15

8.3.2.4.1 Alignment of External Control Instructions..........................................8-17

8.3.3 Address Transfer Termination........................................................................ 8-17

8.4 Data Bus Tenure.................................................................................................8-19

8.4.1 Data Bus Arbitration......................................................................................8-19

8.4.1.1 Using the DBB

8.4.2 Data Bus Write Only......................................................................................8-21

8.4.3 Data Transfer..................................................................................................8-21

8.4.4 Data Transfer Termination ............................................................................. 8-22

8.4.4.1 Normal Single-Beat Termination............................................................... 8-22

8.4.4.2 Normal Burst Termination ......................................................................... 8-24

8.4.4.3 Data Transfer Termination Due to a Bus Error..........................................8-26

8.4.5 Memory Coherency—MEI Protocol .............................................................8-26

8.5 Timing Examples...............................................................................................8-28

8.6 No-DRTRY

8.7 Interrupt, Checkstop, and Reset Signal Operation.............................................8-34

8.7.1 External Interrupts ......................................................................................... 8-34

8.7.2 Checkstops.....................................................................................................8-35

8.7.3 Reset Inputs....................................................................................................8-35

8.7.4 System Quiesce Control Signals....................................................................8-35

8.8 Processor State Signals......................................................................................8-35

8.8.1 Support for the

8.8.2 TLBISYNC

8.9 IEEE 1149.1a-1993 Compliant Interface........................................................... 8-36

8.9.1 JTAG/COP Interface...................................................................................... 8-36

8.10 Using Data Bus Write Only............................................................................... 8-37

Mode ............................................................................................. 8-33

Signal ...............................................................................8-20

lwarx/stwcx. Instruction Pair...............................................8-36

Input ..........................................................................................8-36

Page

Number

Chapter 9

L2 Cache Interface Operation

9.1 L2 Cache Interface Overview.............................................................................. 9-1

9.1.1 L2 Cache Operation.........................................................................................9-2

9.1.2 L2 Cache Flushing...........................................................................................9-4

9.1.3 L2 Cache Control Register (L2CR).................................................................9-4

9.1.4 L2 Cache Initialization.....................................................................................9-6

9.1.5 L2 Cache Global Invalidation.......................................................................... 9-7

Contents

For More Information On This Product,

Go to: www.freescale.com

xv

Page 16

Freescale Semiconductor, Inc.

Contents

..

.

nc

Paragraph

Number Title

9.1.6 L2 Cache Test Features and Methods .............................................................. 9-8

9.1.6.1 L2CR Support for L2 Cache Testing ........................................................... 9-8

9.1.6.2 L2 Cache Testing .........................................................................................9-9

9.1.7 L2 Clock Configuration.................................................................................9-10

9.1.8 L2 Cache SRAM Timing Examples.............................................................. 9-10

9.1.8.1 Flow-Through Burst SRAM...................................................................... 9-10

9.1.8.2 Pipelined Burst SRAM..............................................................................9-12

9.1.8.3 Late-Write SRAM .....................................................................................9-13

Page

Number

Chapter 10

Power and Thermal Management

10.1 Dynamic Power Management............................................................................10-1

10.2 Programmable Power Modes.............................................................................10-1

10.2.1 Power Management Modes............................................................................10-2

10.2.1.1 Full-Power Mode with DPM Disabled......................................................10-2

10.2.1.2 Full-Power Mode with DPM Enabled ....................................................... 10-2

10.2.1.3 Doze Mode.................................................................................................10-3

10.2.1.4 Nap Mode ..................................................................................................10-3

10.2.1.5 Sleep Mode ................................................................................................ 10-4

10.2.2 Power Management Software Considerations...............................................10-5

10.3 Thermal Assist Unit ...........................................................................................10-5

10.3.1 Thermal Assist Unit Overview.......................................................................10-6

10.3.2 Thermal Assist Unit Operation......................................................................10-7

10.3.2.1 TAU Single Threshold Mode..................................................................... 10-8

10.3.2.2 TAU Dual-Threshold Mode.......................................................................10-9

10.3.2.3 MPC750 Junction Temperature Determination.........................................10-9

10.3.2.4 Power Saving Modes and TAU Operation...............................................10-10

10.4 Instruction Cache Throttling............................................................................10-10

Freescale Semiconductor, I

Chapter 11

Performance Monitor

11.1 Performance Monitor Interrupt..........................................................................11-2

11.2 Special-Purpose Registers Used by Performance Monitor................................11-2

11.2.1 Performance Monitor Registers.....................................................................11-3

11.2.1.1 Monitor Mode Control Register 0 (MMCR0) ........................................... 11-3

11.2.1.2 User Monitor Mode Control Register 0 (UMMCR0)................................11-5

11.2.1.3 Monitor Mode Control Register 1 (MMCR1) ........................................... 11-5

11.2.1.4 User Monitor Mode Control Register 1 (UMMCR1)................................11-6

11.2.1.5 Performance Monitor Counter Registers (PMC1–PMC4)......................... 11-6

MPC750 RISC Microprocessor Family User’s Manual

For More Information On This Product,

Go to: www.freescale.com

Page 17

Freescale Semiconductor, Inc.

Contents

..

.

nc

Freescale Semiconductor, I

Paragraph

Number Title

11.2.1.6 User Performance Monitor Counter Registers (UPMC1–UPMC4) .......... 11-9

11.2.1.7 Sampled Instruction Address Register (SIA)........................................... 11-10

11.2.1.8 User Sampled Instruction Address Register (USIA)...............................11-10

11.3 Event Counting ................................................................................................ 11-10

11.4 Event Selection ................................................................................................ 11-11

11.5 Warnings .......................................................................................................... 11-12

Page

Number

Appendix A

PowerPC Instruction Set Listings

A.1 Instructions Sorted by Mnemonic.......................................................................A-1

A.2 Instructions Sorted by Opcode............................................................................A-7

A.3 Instructions Grouped by Functional Categories ...............................................A-13

A.4 Instructions Sorted by Form.............................................................................. A-22

A.5 Instruction Set Legend...................................................................................... A-31

Appendix B

Instructions Not Implemented

Appendix C

MPC755 Embedded G3 Microprocessor

C.1 MPC755 Overview ..............................................................................................C-2

C.2 MPC755 Functional Description .........................................................................C-3

C.3 MPC755 Features.................................................................................................C-6

C.4 The MPC755 Programming Model (Chapter 2)................................................C-10

C.4.1 MPC755-Specific Registers...........................................................................C-12

C.4.1.1 The MPC755 Additional SPR Encodings........................................C-13

C.4.1.2 Processor Version Register (PVR)...................................................C-14

C.4.1.3 Hardware Implementation-Dependent Register 2 (HID2)...............C-15

C.4.2 MPC750 and MPC755 Instruction Use.........................................................C-16

C.4.2.1

C.4.2.2

C.4.3

C.5 MPC755 L1 Instruction and Data Cache Operation (Chapter 3).......................C-19

C.5.1 L1 Cache Coherency......................................................................................C-20

stfd Instruction Use..........................................................................C-16

isync Instruction Use with mtsr and mtsrin.....................................C-16

tlbld and tlbli Instructions.............................................................................C-17

C.5.1.1 Coherency Precautions in Single Processor Systems ......................C-20

C.5.1.2

C.5.2 Cache Locking...............................................................................................C-21

dcbz and L1 Cache Coherency........................................................C-21

C.5.2.1 Cache Locking Terminology ...........................................................C-21

Contents

For More Information On This Product,

Go to: www.freescale.com

xvii

Page 18

Freescale Semiconductor, Inc.

Contents

..

.

nc

Freescale Semiconductor, I

Paragraph

Number Title

Page

Number

C.5.2.2 Cache Locking Register Summary ..................................................C-22

C.5.2.3 Performing Data and Instruction Cache Locking ............................C-23

C.5.2.3.1 Enabling the Data Cache..............................................................C-23

C.5.2.3.2 Address Translation for Data Cache Locking..............................C-24

C.5.2.3.3 Disabling Exceptions for Data Cache Locking............................C-24

C.5.2.3.4 Invalidating the Data Cache.........................................................C-25

C.5.2.3.5 Loading the Data Cache...............................................................C-26

C.5.2.3.6 Entire Data Cache Locking ..........................................................C-26

C.5.2.3.7 Data Cache Way Locking ............................................................C-27

C.5.2.3.8 Invalidating the Data Cache (Even if Locked).............................C-27

C.5.2.3.9 Enabling the Instruction Cache ....................................................C-28

C.5.2.3.10 Address Translation for Instruction Cache Locking ....................C-28

C.5.2.3.11 Disabling Exceptions for Instruction Cache Locking ..................C-29

C.5.2.3.12 Preloading Instructions into the Instruction Cache ......................C-29

C.5.2.3.13 MPC755 Prefetching Considerations...........................................C-31

C.5.2.3.14 Entire Instruction Cache Locking ................................................C-31

C.5.2.3.15 Instruction Cache Way Locking...................................................C-31

C.5.2.3.16 Invalidating the Instruction Cache (Even if Locked)...................C-32

C.6 MPC755 Exceptions (Chapter 4).......................................................................C-32

C.6.1 Instruction TLB Miss Exception (0x01000)..................................................C-34

C.6.2 Data TLB Miss for Load Exception (0x01100).............................................C-34

C.6.3 Data TLB Miss for Store Exception (0x01200).............................................C-35

C.7 MPC755 Memory Management (Chapter 5).....................................................C-35

C.7.1 Software Table Search Resources..................................................................C-36

C.7.2 Software Table Search Registers...................................................................C-37

C.7.2.1 Data and Instruction TLB Miss Address Registers

(DMISS, IMISS)..............................................................................C-37

C.7.2.2 Data and Instruction TLB Compare Registers (DCMP, ICMP)......C-38

C.7.2.3 Primary and Secondary Hash Address Registers

(HASH1, HASH2)...........................................................................C-38

C.7.2.4 Required Physical Address Register (RPA).....................................C-39

C.7.3 Software Table Search Operation..................................................................C-39

C.7.3.1 Flow for Example Exception Handlers............................................C-40

C.7.3.2 Code for Example Exception Handlers............................................C-44

C.8 MPC755 Instruction Timing (Chapter 6)...........................................................C-51

C.9 MPC755 Signal Descriptions (Chapter 7) .........................................................C-51

C.10 MPC755 System Interface Operation (Chapter 8).............................................C-51

C.10.1 MPC755 System Interface Overview............................................................C-51

C.10.2 Address Bus Pipelining..................................................................................C-52

C.10.3 Bus Clocking..................................................................................................C-53

MPC750 RISC Microprocessor Family User’s Manual

For More Information On This Product,

Go to: www.freescale.com

Page 19

Freescale Semiconductor, Inc.

Contents

..

.

nc

Freescale Semiconductor, I

Paragraph

Number Title

C.10.4 32-Bit Data Bus Mode...................................................................................C-53

Page

Number

C.10.4.1 Burst Ordering..................................................................................C-54

C.10.4.2 Aligned Transfers.............................................................................C-54

C.10.4.3 Misaligned Data Transfers...............................................................C-55

C.10.4.4 Selecting D32 Mode.........................................................................C-56

C.10.4.5 Signal Relationships.........................................................................C-56

C.11 MPC755 L2 Cache Interface Operation (Chapter 9).........................................C-58

C.11.1 MPC755 L2 Cache Interface Overview.........................................................C-58

C.11.1.1 L2 Cache Organization ....................................................................C-59

C.11.1.2 L2 Cache Control.............................................................................C-60

C.11.1.3 L2 Private Memory..........................................................................C-60

C.11.2 L2 Interface Operation...................................................................................C-60

C.11.2.1 L2 Cache Operation.........................................................................C-61

C.11.2.1.1 L2 Cache Access Priorities ..........................................................C-61

C.11.2.1.2 L2 Cache Services........................................................................C-61

C.11.2.1.3 L2 Cache Coherency and WIMG Bits .........................................C-62

C.11.2.1.4 Single-Beat Accesses to L2 Interface...........................................C-62

C.11.2.2 L2 Private Memory Operation.........................................................C-62

C.11.3 L2 Clocking ...................................................................................................C-64

C.11.4 L2 Registers...................................................................................................C-65

C.11.4.1 L2 Cache Control Register (L2CR).................................................C-65

C.11.4.2 L2 Private Memory Control Register (L2PM).................................C-68

C.11.5 L2 Address and Data Parity Signals..............................................................C-69

C.11.6 L2 Cache Programming Considerations........................................................C-70

C.11.6.1 Enabling and Disabling the L2 Cache..............................................C-70

C.11.6.2 L2 Cache Global Invalidation..........................................................C-71

C.11.6.3 L2 Cache Flushing...........................................................................C-72

C.11.6.4 Other Cache Control Instructions and Effect on L2 Cache .............C-72

C.11.6.5 Cache Control Instructions and Effect on Private Memory

Operation..........................................................................................C-73

C.11.6.6 L2 Cache Testing.............................................................................C-73

C.11.7 L2 Cache SRAM Timing Examples..............................................................C-76

C.11.7.1 Pipelined PB3 Burst SRAM.............................................................C-76

C.11.8 Private Memory SRAM Timing....................................................................C-78

C.12 Power and Thermal Management (Chapter 10).................................................C-78

C.13 Performance Monitor (Chapter 11)....................................................................C-78

Contents xix

For More Information On This Product,

Go to: www.freescale.com

Page 20

Freescale Semiconductor, Inc.

Contents

..

.

nc

Paragraph

Number Title

Appendix D

User’s Manual Revision History

Index

Page

Number

Freescale Semiconductor, I

MPC750 RISC Microprocessor Family User’s Manual

For More Information On This Product,

Go to: www.freescale.com

Page 21

Freescale Semiconductor, Inc.

Figures

..

.

nc

Freescale Semiconductor, I

Figure

Number Title

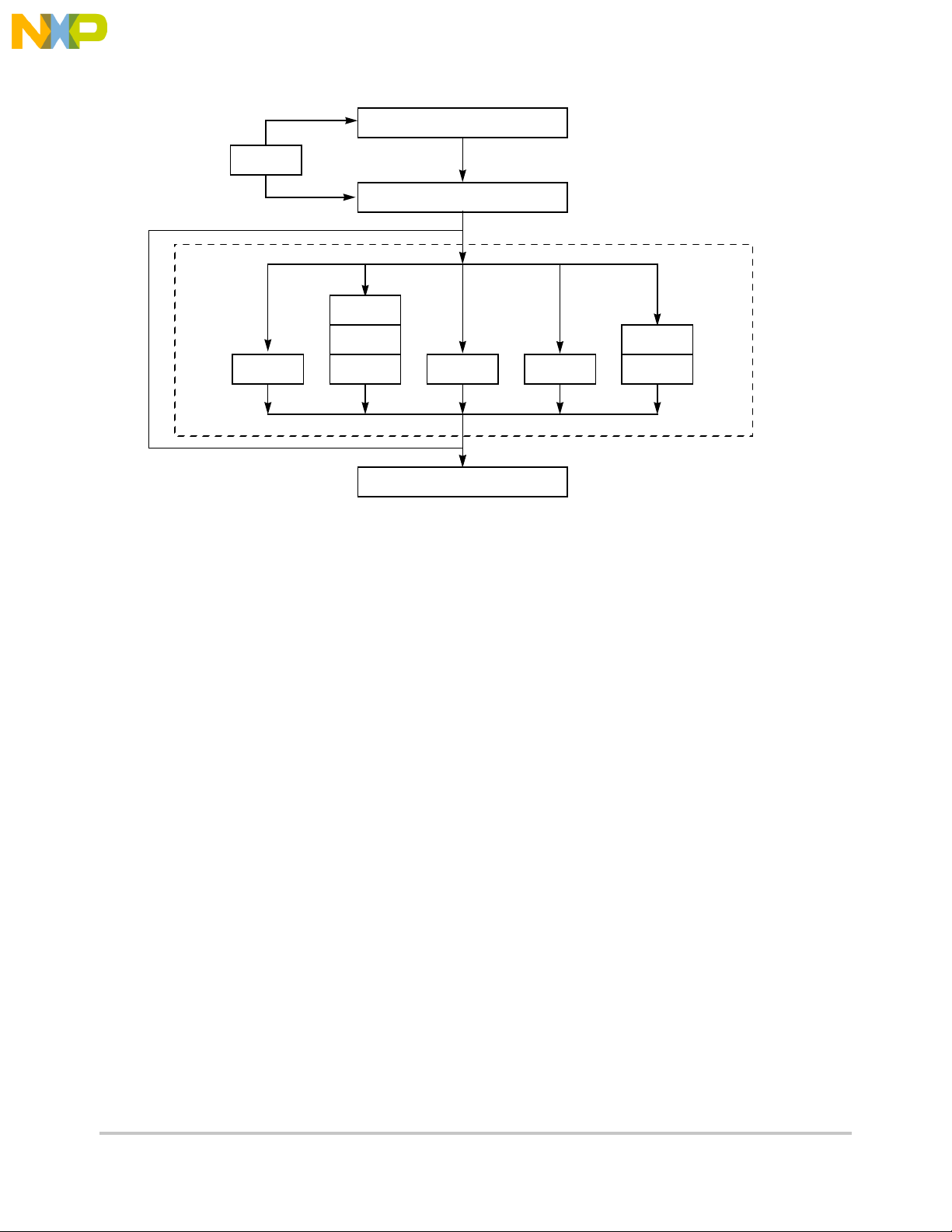

1-1 MPC750 Microprocessor Block Diagram ....................................................................1-3

1-2 Cache Organization..................................................................................................... 1-13

1-3 System Interface..........................................................................................................1-16

1-4 MPC750 Microprocessor Signal Groups....................................................................1-18

1-5 MPC750 Microprocessor Programming Model—Registers....................................... 1-22

1-6 Pipeline Diagram ........................................................................................................1-34

2-1 Programming Model—MPC750 Microprocessor Registers......................................... 2-3

2-2 Instruction Address Breakpoint Register......................................................................2-9

2-3 Hardware Implementation-Dependent Register 0 (HID0).......................................... 2-10

2-4 Hardware Implementation-Dependent Register 1 (HID1).......................................... 2-14

2-5 Monitor Mode Control Register 0 (MMCR0) ............................................................ 2-15

2-6 Monitor Mode Control Register 1 (MMCR1) ............................................................ 2-17

2-7 Performance Monitor Counter Registers (PMC1–PMC4).......................................... 2-17

2-8 Sampled instruction Address Registers (SIA) ............................................................ 2-21

2-9 Instruction Cache Throttling Control Register (ICTC)............................................... 2-22

2-10 Thermal Management Registers 1–2 (THRM1–THRM2) .........................................2-23

2-11 Thermal Management Register 3 (THRM3)...............................................................2-24

2-12 L2 Cache Control Register (L2CR)............................................................................ 2-25

3-1 Cache Integration..........................................................................................................3-2

3-2 Data Cache Organization.............................................................................................. 3-4

3-3 Instruction Cache Organization .................................................................................... 3-5

3-4 MEI Cache Coherency Protocol—State Diagram (WIM = 001).................................. 3-8

3-5 PLRU Replacement Algorithm...................................................................................3-19

3-6 Double-Word Address Ordering—Critical Double Word First..................................3-23

3-7 Bus Interface Address Buffers....................................................................................3-31

4-1 Machine Status Save/Restore Register 0 (SRR0)......................................................... 4-7

4-2 Machine Status Save/Restore Register 1 (SRR1)......................................................... 4-8

4-3 Machine State Register (MSR)..................................................................................... 4-8

5-1 MMU Conceptual Block Diagram—32-Bit Implementations...................................... 5-5

5-2 MPC750 Microprocessor IMMU Block Diagram........................................................ 5-6

5-3 MPC750 Microprocessor DMMU Block Diagram.......................................................5-7

5-4 Address Translation Types ...........................................................................................5-9

5-5 General Flow of Address Translation (Real Addressing Mode and Block)............... 5-12

5-6 General Flow of Page and Direct-Store Interface Address Translation .....................5-13

5-7 Segment Register and DTLB Organization................................................................ 5-24

Page

Number

Figures xxi

For More Information On This Product,

Go to: www.freescale.com

Page 22

Freescale Semiconductor, Inc.

Figures

..

.

nc

Freescale Semiconductor, I

Figure

Number Title

5-8 Page Address Translation Flow—TLB Hit.................................................................5-27

5-9 Primary Page Table Search.........................................................................................5-30

5-10 Secondary Page Table Search Flow............................................................................ 5-31

6-1 Pipelined Execution Unit.............................................................................................. 6-4

6-2 Superscalar/Pipeline Diagram....................................................................................... 6-5

6-3 MPC750 Microprocessor Pipeline Stages ....................................................................6-7

6-4 Instruction Flow Diagram...........................................................................................6-10

6-5 Instruction Timing—Cache Hit .................................................................................. 6-12

6-6 Instruction Timing—Cache Miss................................................................................ 6-15

6-7 Branch Folding............................................................................................................6-19

6-8 Removal of Fall-Through Branch Instruction.............................................................6-19

6-9 Branch Completion..................................................................................................... 6-20

6-10 Branch Instruction Timing..........................................................................................6-23

7-1 MPC750 Signal Groups................................................................................................ 7-3

8-1 MPC750 Microprocessor Block Diagram ....................................................................8-3

8-2 Timing Diagram Legend...............................................................................................8-5

8-3 Overlapping Tenures on the MPC750 Bus for a Single-Beat Transfer........................8-6

8-4 Address Bus Arbitration ............................................................................................. 8-10

8-5 Address Bus Arbitration Showing Bus Parking..........................................................8-11

8-6 Address Bus Transfer.................................................................................................. 8-13

8-7 Snooped Address Cycle with ARTRY

8-8 Data Bus Arbitration...................................................................................................8-20

8-9 Normal Single-Beat Read Termination ......................................................................8-23

8-10 Normal Single-Beat Write Termination......................................................................8-23