Page 1

MMC2107/D

REV 2

MMC2107

Technical Data

HCMOS

Micro cont ro ll er Unit

ORE M•CO

Page 2

Freescale Semiconductor, Inc.

blank

nc...

I

cale Semiconductor,

Frees

For More Information On This Product,

Go to: www.freescale.com

Page 3

Freescale Semiconductor, Inc.

MMC2107

Technical Data

nc...

I

cale Semiconductor,

Frees

Motorola reserves the right to make ch anges without further notice to any products

herein. Motorola makes no warranty, representation or guarantee regarding the

suitability of its products for any particular purpose, nor do es Motorola assume any

liability arisin g out of the app lication or u se of any pr oduct or ci rcuit, a nd sp ecifica lly

disclaims any and all liability, including without limitation consequ ential or incidental

damages. "Typical" parameters which may be provided in Motorola data sheets and/or

specifications can and do vary in different applications and actual performance may

vary over time. All operating parameters, including "Typicals" must be validated for

each customer application by customer’s technical experts. Motorola does not convey

any license under its patent rights nor the rights of others. Motorola products are not

designed, intended, or authorized for use as components in systems intended for

surgical implant into the body, or other applications intended to support or sustain life,

or for any other application in which the failure of the Motorola product could create a

situation where personal injury or death may occur. Should Buyer purchase or use

Motorola products for any such unintended or unauthorized application, Buyer shall

indemnify and hold Motorola and its officers, employees, subsidiaries, af filiates, and

distributors harmless against all claims, costs, damages, and expenses, and

reasonable attorney fees a rising out of, directly or indirectly, any claim of personal

injury or death associated with such unintended or unauthorized use, even if such claim

alleges that Motorola was negligent regarding t he design or manufacture of the part.

Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

Motorola and are registered trademarks of Motorola, Inc.

DigitalDNA is a trademark of Motorola, Inc. © Motorola, Inc., 2000

MMC2107 – Rev. 2.0 Technical Data

MOTOROLA 3

For More Information On This Product,

Go to: www.freescale.com

Page 4

Technical Data

nc...

I

Freescale Semiconductor, Inc.

cale Semiconductor,

Frees

Technical Data MMC2107 – Rev. 2.0

4 MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Page 5

Freescale Semiconductor, Inc.

Technical Data — MMC2107

List of Sections

Section 1. General Description . . . . . . . . . . . . . . . . . . . .43

Section 2. System Memory Map . . . . . . . . . . . . . . . . . . .51

Section 3. Chip Configuration Module (CCM) . . . . . . . .89

nc...

I

Section 4. Signal Description. . . . . . . . . . . . . . . . . . . . .107

cale Semiconductor,

Frees

Section 5. Reset Controller Module. . . . . . . . . . . . . . . .129

Section 6. M•CORE M210 Central Processor

Unit (CPU) . . . . . . . . . . . . . . . . . . . . . . . . . .143

Section 7. Interrupt Controller Module . . . . . . . . . . . . .153

Section 8. Static Random-Access Memory

(SRAM). . . . . . . . . . . . . . . . . . . . . . . . . . . . .175

Section 9. Non-Volatile Memory FLASH

(CMFR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . .179

Section 10. Clock Module. . . . . . . . . . . . . . . . . . . . . . . .221

Section 11. Ports Module . . . . . . . . . . . . . . . . . . . . . . . .247

Section 12. Edge Port Module (EPORT) . . . . . . . . . . . .261

Section 13. Watchdog Timer Module . . . . . . . . . . . . . .271

Section 14. Programmable Interrupt Timer

Modules (PIT1 and PIT2) . . . . . . . . . . . . . .281

Section 15. Timer Modules (TIM1 and TIM2). . . . . . . . .293

MMC2107 – Rev. 2.0 Technical Data

MOTOROLA List of Sections 5

For More Information On This Product,

Go to: www.freescale.com

Page 6

List of Sec ti o ns

nc...

I

Freescale Semiconductor, Inc.

Section 16. Serial Communications Interface

Modules (SCI1 and SCI2) . . . . . . . . . . . . . .329

Section 17. Serial Peripheral Interface

Module (SPI) . . . . . . . . . . . . . . . . . . . . . . . .371

Section 18. Queued Analog-to-Digital

Converter (QADC). . . . . . . . . . . . . . . . . . . .399

Section 19. External Bus Interface Module (EBI) . . . . .503

Section 20. Chip Select Module. . . . . . . . . . . . . . . . . . .521

Section 21. JTAG Test Access Port and OnCE . . . . . .533

cale Semiconductor,

Frees

Section 22. Electrical Specifications. . . . . . . . . . . . . . .585

Section 23. Mechanical Specifications . . . . . . . . . . . . .609

Section 24. Ordering Information . . . . . . . . . . . . . . . . .615

Technical Data MMC2107 – Rev. 2.0

6 List of Sections MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Page 7

Freescale Semiconductor, Inc.

Technical Data — MMC2107

1.1 Contents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .43

1.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .43

1.3 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .44

Table of Contents

Section 1. General Description

nc...

I

cale Semiconductor,

Frees

1.4 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4 8

Section 2. System Memory Map

2.1 Contents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .51

2.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .51

2.3 Address Map. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .52

2.4 Register Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .54

Section 3. Chip Configuration Module (CCM)

3.1 Contents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .89

3.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .90

3.3 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .90

3.4 Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .90

3.4.1 Master Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .91

3.4.2 Single-Chip Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9 1

3.4.3 Emulation Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .91

3.4.4 Factory Access Slave Test (FAST) Mode . . . . . . . . . . . . . .91

3.5 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9 2

3.6 Signal Descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .92

MMC2107 – Rev. 2.0 Technical Data

MOTOROLA Table of Contents 7

For More Information On This Product,

Go to: www.freescale.com

Page 8

Table of Contents

nc...

I

Freescale Semiconductor, Inc.

3.7 Memory Map and Registers . . . . . . . . . . . . . . . . . . . . . . . . . . .93

3.7.1 Programming Model. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .93

3.7.2 Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .94

3.7.3 Register Descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .94

3.7.3.1 Chip Configuration Register. . . . . . . . . . . . . . . . . . . . . . .94

3.7.3.2 Reset Configuration Register. . . . . . . . . . . . . . . . . . . . . .97

3.7.3.3 Chip Identification Register . . . . . . . . . . . . . . . . . . . . . . .99

3.7.3.4 Chip Test Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . .100

3.8 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .100

3.8.1 Reset Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .101

3.8.2 Chip Mode Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . .103

3.8.3 Boot Device Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . .103

3.8.4 Output Pad Strength Configuration . . . . . . . . . . . . . . . . . .105

3.8.5 Clock Mode Selection. . . . . . . . . . . . . . . . . . . . . . . . . . . . .105

3.8.6 Internal FLASH Configuration . . . . . . . . . . . . . . . . . . . . . .106

cale Semiconductor,

Frees

3.9 Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .106

3.10 Interrupts. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .106

Section 4. Signal Description

4.1 Contents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .107

4.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .109

4.3 Package Pinout Summary . . . . . . . . . . . . . . . . . . . . . . . . . . .110

4.4 MMC2107 Specific Implementation Signal Issues . . . . . . . . .120

4.4.1 RSTOUT Signal Functions. . . . . . . . . . . . . . . . . . . . . . . . . 120

4.4.2 INT Signal Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . .121

4.5 Signal Descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .121

4.5.1 Reset Signals. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .121

4.5.1.1 Reset In (RESET) . . . . . . . . . . . . . . . . . . . . . . . . . . . . .121

4.5.1.2 Reset Out (RSTOUT). . . . . . . . . . . . . . . . . . . . . . . . . . .121

4.5.2 Phase-Lock Loop (PLL) and Clock Signals . . . . . . . . . . . .122

4.5.2.1 External Clock In (EXTAL). . . . . . . . . . . . . . . . . . . . . . .122

4.5.2.2 Crystal (XTAL) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .122

4.5.2.3 Clock Out (CLKOUT). . . . . . . . . . . . . . . . . . . . . . . . . . .122

4.5.2.4 Synthesizer Power (V

DDSYN

and V

SSSYN

). . . . . . . . . . .122

Technical Data MMC2107 – Rev. 2.0

8 Table of Contents MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Page 9

nc...

I

cale Semiconductor,

Frees

Freescale Semiconductor, Inc.

4.5.3 External Memory Interface Signals . . . . . . . . . . . . . . . . . .122

4.5.3.1 Data Bus (D[31:0]). . . . . . . . . . . . . . . . . . . . . . . . . . . . .122

4.5.3.2 Show Cycle Strobe (SHS) . . . . . . . . . . . . . . . . . . . . . . .123

4.5.3.3 Transfer Acknowledge (TA). . . . . . . . . . . . . . . . . . . . . .123

4.5.3.4 Transfer Error Acknowledge (TEA) . . . . . . . . . . . . . . . .123

4.5.3.5 Emulation Mode Chip Selects (CSE[1:0]) . . . . . . . . . . .123

4.5.3.6 Transfer Code (TC[2:0]). . . . . . . . . . . . . . . . . . . . . . . . .123

4.5.3.7 Read/Write (R/W). . . . . . . . . . . . . . . . . . . . . . . . . . . . . .123

4.5.3.8 Address Bus (A[22:0]) . . . . . . . . . . . . . . . . . . . . . . . . . .124

4.5.3.9 Enable Byte (EB[3:0]) . . . . . . . . . . . . . . . . . . . . . . . . . .124

4.5.3.10 Chip Select (CS[3:0] ). . . . . . . . . . . . . . . . . . . . . . . . . . .124

4.5.3.11 Output Enable (OE

4.5.4 Edge Port Signals. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .124

4.5.4.1 External Interrupts (INT[7:6]) . . . . . . . . . . . . . . . . . . . . .124

4.5.4.2 External Interrupts (INT[5:2]) . . . . . . . . . . . . . . . . . . . . .124

4.5.4.3 External Interrupts (INT[1:0]

4.5.5 Serial Peripheral Interface Module Signals . . . . . . . . . . . .125

4.5.5.1 Master Out/Slave In (MOSI). . . . . . . . . . . . . . . . . . . . . .125

4.5.5.2 Master In/Slave Out (MISO). . . . . . . . . . . . . . . . . . . . . .125

4.5.5.3 Serial Clock (SCK). . . . . . . . . . . . . . . . . . . . . . . . . . . . .125

4.5.5.4 Slave Select (SS). . . . . . . . . . . . . . . . . . . . . . . . . . . . . .125

4.5.6 Serial Communications Interface Module Signals . . . . . . .125

4.5.6.1 Receive Data (RXD1 and RXD2). . . . . . . . . . . . . . . . . .125

4.5.6.2 Transmit Data (TXD1 and TXD2). . . . . . . . . . . . . . . . . .126

4.5.7 Timer Signals (ICOC1[3:0] and ICOC2[3:0]) . . . . . . . . . . .126

4.5.8 Analog-to-Digital Converter Signals. . . . . . . . . . . . . . . . . .126

4.5.8.1 Analog Inputs (PQA[4:3], PQA[1:0],

4.5.8.2 Analog Reference (V

4.5.8.3 Analog Supply (V

4.5.8.4 Positive Supply (V

4.5.9 Debug and Emulation Support Signals . . . . . . . . . . . . . . .127

4.5.9.1 Test Reset (TRST). . . . . . . . . . . . . . . . . . . . . . . . . . . . .127

4.5.9.2 Test Clock (TCLK) . . . . . . . . . . . . . . . . . . . . . . . . . . . . .127

4.5.9.3 Test Mode Select (TMS) . . . . . . . . . . . . . . . . . . . . . . . .127

4.5.9.4 Test Data Input (TDI). . . . . . . . . . . . . . . . . . . . . . . . . . .127

4.5.9.5 Test Data Output (TDO). . . . . . . . . . . . . . . . . . . . . . . . .127

4.5.9.6 Debug Event (DE) . . . . . . . . . . . . . . . . . . . . . . . . . . . . .127

Table of Contents

) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124

) . . . . . . . . . . . . . . . . . . . . .125

and PQB[3:0]). . . . . . . . . . . . . . . . . . . . . . . . . . . . . .126

and VRL) . . . . . . . . . . . . . . . . .126

RH

and V

DDA

) . . . . . . . . . . . . . . . . . . . . . . . . . 126

DDH

) . . . . . . . . . . . . . . . . . .126

SSA

MMC2107 – Rev. 2.0 Technical Data

MOTOROLA Table of Contents 9

For More Information On This Product,

Go to: www.freescale.com

Page 10

Table of Contents

Freescale Semiconductor, Inc.

4.5.10 Test Signal (TEST). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .128

4.5.11 Power and Ground Signals . . . . . . . . . . . . . . . . . . . . . . . .128

4.5.11.1 Power for FLASH Erase/Program (VPP) . . . . . . . . . . . .128

4.5.11.2 Power and Ground for FLASH Array

4.5.11.3 Standby Power (V

4.5.11.4 Positive Supply (VDD). . . . . . . . . . . . . . . . . . . . . . . . . . . 128

4.5.11.5 Ground (VSS) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .128

(V

DDF

and V

) . . . . . . . . . . . . . . . . . . . . . . . . . . . .128

SSF

) . . . . . . . . . . . . . . . . . . . . . . . . .128

STBY

Section 5. Reset Controller Module

5.1 Contents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .129

nc...

I

cale Semiconductor,

Frees

5.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .130

5.3 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .130

5.4 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .131

5.5 Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .131

5.6 Memory Map and Registers . . . . . . . . . . . . . . . . . . . . . . . . . .132

5.6.1 Reset Control Register. . . . . . . . . . . . . . . . . . . . . . . . . . . .133

5.6.2 Reset Status Register . . . . . . . . . . . . . . . . . . . . . . . . . . . .134

5.6.3 Reset Test Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .135

5.7 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .136

5.7.1 Reset Sources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .136

5.7.1.1 Power-On Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .137

5.7.1.2 External Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .137

5.7.1.3 Watchdog Timer Reset . . . . . . . . . . . . . . . . . . . . . . . . .137

5.7.1.4 Loss of Clock Reset. . . . . . . . . . . . . . . . . . . . . . . . . . . .137

5.7.1.5 Loss of Lock Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . .138

5.7.1.6 Software Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .138

5.7.2 Reset Control Flow. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .138

5.7.2.1 Synchronous Reset Requests . . . . . . . . . . . . . . . . . . . .138

5.7.2.2 Internal Reset Request . . . . . . . . . . . . . . . . . . . . . . . . .140

5.7.2.3 Power-On Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .140

5.7.3 Concurrent Resets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .140

5.7.3.1 Reset Flow. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .140

5.7.3.2 Reset Status Flags. . . . . . . . . . . . . . . . . . . . . . . . . . . . .141

5.8 Interrupts. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .141

Technical Data MMC2107 – Rev. 2.0

10 Table of Contents MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Page 11

Freescale Semiconductor, Inc.

Table of Contents

Section 6. M•CORE M210 Central

Processor Unit (CPU)

6.1 Contents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .143

6.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .143

6.3 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .144

6.4 Microarchitecture Summary . . . . . . . . . . . . . . . . . . . . . . . . . .145

6.5 Programming Model. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .147

6.6 Data Format Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .149

6.7 Operand Addressing Capabilities. . . . . . . . . . . . . . . . . . . . . .150

nc...

I

cale Semiconductor,

Frees

6.8 Instruction Set Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . .150

Section 7. Interrupt Controller Module

7.1 Contents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .153

7.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .154

7.3 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .154

7.4 Low-Power Mode Operation. . . . . . . . . . . . . . . . . . . . . . . . . . 154

7.5 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .155

7.6 External Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .155

7.7 Memory Map and Registers . . . . . . . . . . . . . . . . . . . . . . . . . .155

7.7.1 Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .156

7.7.2 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .157

7.7.2.1 Interrupt Control Register. . . . . . . . . . . . . . . . . . . . . . . .157

7.7.2.2 Interrupt Status Register . . . . . . . . . . . . . . . . . . . . . . . .159

7.7.2.3 Interrupt Force Registers . . . . . . . . . . . . . . . . . . . . . . . .160

7.7.2.4 Interrupt Pending Register. . . . . . . . . . . . . . . . . . . . . . .162

7.7.2.5 Normal Interrupt Enable Register. . . . . . . . . . . . . . . . . .163

7.7.2.6 Normal Interrupt Pending Register. . . . . . . . . . . . . . . . .164

7.7.2.7 Fast Interrupt Enable Register. . . . . . . . . . . . . . . . . . . .165

7.7.2.8 Fast Interrupt Pending Register. . . . . . . . . . . . . . . . . . .166

7.7.2.9 Priority Level Select Registers . . . . . . . . . . . . . . . . . . . .167

7.8 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .167

7.8.1 Interrupt Sources and Prioritization . . . . . . . . . . . . . . . . . .168

7.8.2 Fast and Normal Interrupt Requests . . . . . . . . . . . . . . . . .168

7.8.3 Autovectored and V e ctored Interrupt Requests. . . . . . . . .169

MMC2107 – Rev. 2.0 Technical Data

MOTOROLA Table of Contents 11

For More Information On This Product,

Go to: www.freescale.com

Page 12

Table of Contents

Freescale Semiconductor, Inc.

7.8.4 Interrupt Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . .171

7.8.4.1 M•CORE Processor Configuration. . . . . . . . . . . . . . . . .171

7.8.4.2 Interrupt Controller Configuration. . . . . . . . . . . . . . . . . .171

7.8.4.3 Interrupt Source Configuration. . . . . . . . . . . . . . . . . . . .172

7.8.5 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .172

Section 8. Static Random-Access Memory (SRAM)

8.1 Contents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .175

8.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .175

8.3 Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .175

nc...

I

cale Semiconductor,

Frees

8.4 Low-Power Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .176

8.5 Standby Power Supply Pin (V

8.6 Standby Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .176

8.7 Reset Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .177

8.8 Interrupts. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .177

) . . . . . . . . . . . . . . . . . . . .176

STBY

Section 9. Non-Volatile Memory FLASH (CMFR)

9.1 Contents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .179

9.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .180

9.3 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .181

9.4 Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .182

9.4.1 Stop Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .182

9.4.2 Disabled Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .182

9.5 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .183

9.6 Glossary of Terms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .185

9.7 Registers and Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . .186

9.7.1 Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .187

9.7.1.1 CMFR Module Configuration Register. . . . . . . . . . . . . . 188

9.7.1.2 CMFR Module Test Register . . . . . . . . . . . . . . . . . . . . .193

9.7.1.3 CMFR High-Voltage Control Register . . . . . . . . . . . . . .196

9.7.2 Array Addressing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .203

9.7.2.1 Read Page Buffers. . . . . . . . . . . . . . . . . . . . . . . . . . . . .203

9.7.2.2 Program Page Buffers . . . . . . . . . . . . . . . . . . . . . . . . . .204

Technical Data MMC2107 – Rev. 2.0

12 Table of Contents MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Page 13

Freescale Semiconductor, Inc.

9.8 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .205

9.8.1 Master Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .205

9.8.2 Register Read and Write Operation . . . . . . . . . . . . . . . . . .205

9.8.3 Array Read Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . .205

9.8.4 Programming . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .206

9.8.4.1 Program Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . .207

9.8.4.2 Program Margin Reads . . . . . . . . . . . . . . . . . . . . . . . . .211

9.8.4.3 Programming Shadow Information. . . . . . . . . . . . . . . . .212

9.8.4.4 Program Pulse-Width and Amplitude Modulation . . . . .213

9.8.4.5 Overprogramming . . . . . . . . . . . . . . . . . . . . . . . . . . . . .213

9.8.5 Erasing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .214

9.8.5.1 Erase Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 215

nc...

I

9.8.5.2 Erase Margin Reads . . . . . . . . . . . . . . . . . . . . . . . . . . .218

9.8.5.3 Erasing Shadow Information Words. . . . . . . . . . . . . . . .219

9.8.6 Erase Pulse Amplitude and Width Modulation. . . . . . . . . .219

9.8.7 Emulation Operation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .220

Table of Contents

cale Semiconductor,

Frees

9.9 Master Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .220

9.10 Interrupts. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .220

Section 10. Clock Module

10.1 Contents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .221

10.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 222

10.3 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .222

10.4 Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .223

10.4.1 Normal PLL Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .223

10.4.2 1:1 PLL Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .223

10.4.3 External Clock Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . .223

10.4.4 Low-Power Options . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .223

10.4.4.1 Wait and Doze Modes . . . . . . . . . . . . . . . . . . . . . . . . . .223

10.4.4.2 Stop Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .224

10.5 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .224

10.6 Signal Descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .225

10.6.1 EXTAL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .225

10.6.2 XTAL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .225

10.6.3 CLKOUT. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .225

MMC2107 – Rev. 2.0 Technical Data

MOTOROLA Table of Contents 13

For More Information On This Product,

Go to: www.freescale.com

Page 14

Table of Contents

Freescale Semiconductor, Inc.

10.6.4 V

10.6.5 RSTOUT. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .226

10.7 Memory Map and Registers . . . . . . . . . . . . . . . . . . . . . . . . . .226

10.7.1 Module Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . .226

10.7.2 Register Descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . .227

10.7.2.1 Synthesizer Control Register . . . . . . . . . . . . . . . . . . . . .227

10.7.2.2 Synthesizer Status Register. . . . . . . . . . . . . . . . . . . . . .230

10.7.2.3 Synthesizer Test Register . . . . . . . . . . . . . . . . . . . . . . .233

10.7.2.4 Synthesizer Test Register 2. . . . . . . . . . . . . . . . . . . . . .234

10.8 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .235

10.8.1 System Clock Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . .235

nc...

I

cale Semiconductor,

10.8.2 System Clocks Generation. . . . . . . . . . . . . . . . . . . . . . . . .236

10.8.3 PLL Lock Detection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .236

10.8.3.1 PLL Loss of Lock Conditions . . . . . . . . . . . . . . . . . . . . .238

10.8.3.2 PLL Loss of Lock Reset . . . . . . . . . . . . . . . . . . . . . . . . .238

10.8.4 Loss of Clock Detection . . . . . . . . . . . . . . . . . . . . . . . . . . .238

10.8.4.1 Alternate Clock Selection. . . . . . . . . . . . . . . . . . . . . . . .239

10.8.4.2 Loss-of-Clock Reset. . . . . . . . . . . . . . . . . . . . . . . . . . . .242

10.8.5 Clock Operation During Reset . . . . . . . . . . . . . . . . . . . . . .243

10.8.6 PLL Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .243

10.8.6.1 Phase and Frequency Detector (PFD). . . . . . . . . . . . . .245

10.8.6.2 Charge Pump/Loop Filter. . . . . . . . . . . . . . . . . . . . . . . .245

10.8.6.3 Voltage Control Output (VCO) . . . . . . . . . . . . . . . . . . . .246

10.8.6.4 Multiplication Factor Divider (MFD) . . . . . . . . . . . . . . . .246

10.9 Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .246

10.10 Interrupts. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .246

DDSYN

and V

SSSYN

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .225

Frees

11.1 Contents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .247

11.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 248

11.3 Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .249

11.4 Memory Map and Registers . . . . . . . . . . . . . . . . . . . . . . . . . .249

11.4.1 Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .250

11.4.2 Register Descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . .251

11.4.2.1 Port Output Data Registers . . . . . . . . . . . . . . . . . . . . . . 251

11.4.2.2 Port Data Direction Registers. . . . . . . . . . . . . . . . . . . . .252

Technical Data MMC2107 – Rev. 2.0

14 Table of Contents MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Section 11. Ports Module

Page 15

Freescale Semiconductor, Inc.

11.4.2.3 Port Pin Data/Set Data Registers . . . . . . . . . . . . . . . . .253

11.4.2.4 Port Clear Output Data Registers . . . . . . . . . . . . . . . . .254

11.4.2.5 Port C/D Pin Assignment Register. . . . . . . . . . . . . . . . . 255

11.4.2.6 Port E Pin Assignment Register. . . . . . . . . . . . . . . . . . .256

11.5 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .257

11.5.1 Pin Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .258

11.5.2 Port Digital I/O Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . .259

11.6 Interrupts. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .259

Table of Contents

Section 12. Edge Port Module (EPORT)

nc...

I

cale Semiconductor,

Frees

12.1 Contents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .261

12.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 261

12.3 Low-Power Mode Operation. . . . . . . . . . . . . . . . . . . . . . . . . .262

12.3.1 Wait and Doze Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . .262

12.3.2 Stop Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .263

12.4 Interrupt/General-Purpose I/O Pin Descriptions. . . . . . . . . . .263

12.5 Memory Map and Registers . . . . . . . . . . . . . . . . . . . . . . . . . .263

12.5.1 Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .263

12.5.2 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .264

12.5.2.1 EPORT Pin Assignment Register . . . . . . . . . . . . . . . . .264

12.5.2.2 EPORT Data Direction Register. . . . . . . . . . . . . . . . . . .266

12.5.2.3 Edge Port Interrupt Enable Register . . . . . . . . . . . . . . .267

12.5.2.4 Edge Port Data Register . . . . . . . . . . . . . . . . . . . . . . . .268

12.5.2.5 Edge Port Pin Data Register . . . . . . . . . . . . . . . . . . . . .268

12.5.2.6 Edge Port Flag Register. . . . . . . . . . . . . . . . . . . . . . . . .269

Section 13. Watchdog Timer Module

13.1 Contents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .271

13.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 271

13.3 Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .272

13.3.1 Wait Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .272

13.3.2 Doze Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .272

13.3.3 Stop Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .272

13.3.4 Debug Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .272

MMC2107 – Rev. 2.0 Technical Data

MOTOROLA Table of Contents 15

For More Information On This Product,

Go to: www.freescale.com

Page 16

Table of Contents

nc...

I

Freescale Semiconductor, Inc.

13.4 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .273

13.5 Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .273

13.6 Memory Map and Registers . . . . . . . . . . . . . . . . . . . . . . . . . .274

13.6.1 Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .274

13.6.2 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .274

13.6.2.1 Watchdog Control Register . . . . . . . . . . . . . . . . . . . . . .275

13.6.2.2 Watchdog Modulus Register . . . . . . . . . . . . . . . . . . . . .277

13.6.2.3 Watchdog Count Register . . . . . . . . . . . . . . . . . . . . . . .278

13.6.2.4 Watchdog Service Register . . . . . . . . . . . . . . . . . . . . . .279

Section 14. Programmable Interrupt Timer Modules

(PIT1 and PIT2)

14.1 Contents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .281

cale Semiconductor,

Frees

14.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 282

14.3 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .282

14.4 Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .283

14.4.1 Wait Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .283

14.4.2 Doze Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .283

14.4.3 Stop Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .283

14.4.4 Debug Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .283

14.5 Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .283

14.6 Memory Map and Registers . . . . . . . . . . . . . . . . . . . . . . . . . .284

14.6.1 Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .284

14.6.2 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .284

14.6.2.1 PIT Control and Status Register . . . . . . . . . . . . . . . . . .285

14.6.2.2 PIT Modulus Register . . . . . . . . . . . . . . . . . . . . . . . . . .288

14.6.2.3 PIT Count Register . . . . . . . . . . . . . . . . . . . . . . . . . . . .289

14.7 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .290

14.7.1 Set-and-Forget Timer Operation . . . . . . . . . . . . . . . . . . . .290

14.7.2 Free-Running Timer Operation . . . . . . . . . . . . . . . . . . . . .291

14.7.3 Timeout Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . .291

14.8 Interrupt Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .292

Technical Data MMC2107 – Rev. 2.0

16 Table of Contents MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Page 17

Freescale Semiconductor, Inc.

Table of Contents

Section 15. Timer Modules (TIM1 and TIM2)

15.1 Contents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .293

15.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 295

15.3 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .295

15.4 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .296

15.5 Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .297

15.5.1 Supervisor and User Modes. . . . . . . . . . . . . . . . . . . . . . . .297

15.5.2 Run Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .297

15.5.3 Stop Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .297

15.5.4 Wait, Doze, and Debug Modes . . . . . . . . . . . . . . . . . . . . .297

nc...

I

15.5.5 Test Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .297

15.6 Signal Description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .298

15.6.1 ICOC[2:0] . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .298

15.6.2 ICOC3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .298

cale Semiconductor,

Frees

15.7 Memory Map and Registers . . . . . . . . . . . . . . . . . . . . . . . . . .298

15.7.1 Timer Input Capture/Output Compare

Select Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .300

15.7.2 Timer Compare Force Register . . . . . . . . . . . . . . . . . . . . . 301

15.7.3 Timer Output Compare 3 Mask Register . . . . . . . . . . . . . .302

15.7.4 Timer Output Compare 3 Data Register . . . . . . . . . . . . . . .303

15.7.5 Timer Counter Registers . . . . . . . . . . . . . . . . . . . . . . . . . .304

15.7.6 Timer System Control Register 1. . . . . . . . . . . . . . . . . . . .305

15.7.7 Timer Toggle-On-Overflow Register . . . . . . . . . . . . . . . . .306

15.7.8 Timer Control Register 1 . . . . . . . . . . . . . . . . . . . . . . . . . .307

15.7.9 Timer Control Register 2 . . . . . . . . . . . . . . . . . . . . . . . . . .308

15.7.10 Timer Interrupt Enable Register. . . . . . . . . . . . . . . . . . . . .309

15.7.11 Timer System Control Register 2. . . . . . . . . . . . . . . . . . . .310

15.7.12 Timer Flag Register 1. . . . . . . . . . . . . . . . . . . . . . . . . . . . .312

15.7.13 Timer Flag Register 2. . . . . . . . . . . . . . . . . . . . . . . . . . . . .313

15.7.14 Timer Channel Registers . . . . . . . . . . . . . . . . . . . . . . . . . .314

15.7.15 Pulse Accumulator Control Register . . . . . . . . . . . . . . . . .315

15.7.16 Pulse Accumulator Flag Register. . . . . . . . . . . . . . . . . . . .317

15.7.17 Pulse Accumulator Counter Registers . . . . . . . . . . . . . . . .318

15.7.18 Timer Port Data Register . . . . . . . . . . . . . . . . . . . . . . . . . .319

15.7.19 Timer Port Data Direction Register . . . . . . . . . . . . . . . . . .320

15.7.20 Timer Test Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .321

MMC2107 – Rev. 2.0 Technical Data

MOTOROLA Table of Contents 17

For More Information On This Product,

Go to: www.freescale.com

Page 18

Table of Contents

nc...

I

Freescale Semiconductor, Inc.

15.8 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .321

15.8.1 Prescaler . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .321

15.8.2 Input Capture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .321

15.8.3 Output Compare. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .322

15.8.4 Pulse Accumulator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .323

15.8.4.1 Event Counter Mode . . . . . . . . . . . . . . . . . . . . . . . . . . .323

15.8.4.2 Gated Time Accumulation Mode . . . . . . . . . . . . . . . . . .324

15.8.5 General-Purpose I/O Ports. . . . . . . . . . . . . . . . . . . . . . . . .325

15.9 Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .326

15.10 Interrupts. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .326

15.10.1 Timer Channel Interrupts (CxF) . . . . . . . . . . . . . . . . . . . . .326

15.10.2 Pulse Accumulator Overflow (PAOVF). . . . . . . . . . . . . . . .327

15.10.3 Pulse Accumulator Input (PAIF). . . . . . . . . . . . . . . . . . . . .327

15.10.4 Timer Overflow (TOF) . . . . . . . . . . . . . . . . . . . . . . . . . . . .327

cale Semiconductor,

Frees

Section 16. Serial Communications Interface Modules

(SCI1 and SCI2)

16.1 Contents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .329

16.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 330

16.3 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .331

16.4 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .332

16.5 Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .333

16.5.1 Doze Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .333

16.5.2 Stop Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .333

16.6 Signal Description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .334

16.6.1 RXD . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .334

16.6.2 TXD . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .334

16.7 Memory Map and Registers . . . . . . . . . . . . . . . . . . . . . . . . . .334

16.7.1 SCI Baud Rate Registers . . . . . . . . . . . . . . . . . . . . . . . . . .336

16.7.2 SCI Control Register 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . 337

16.7.3 SCI Control Register 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . 340

16.7.4 SCI Status Register 1. . . . . . . . . . . . . . . . . . . . . . . . . . . . .342

16.7.5 SCI Status Register 2. . . . . . . . . . . . . . . . . . . . . . . . . . . . .344

16.7.6 SCI Data Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .345

16.7.7 SCI Pullup and Reduced Drive Register . . . . . . . . . . . . . .346

Technical Data MMC2107 – Rev. 2.0

18 Table of Contents MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Page 19

Freescale Semiconductor, Inc.

16.7.8 SCI Port Data Register. . . . . . . . . . . . . . . . . . . . . . . . . . . .347

16.7.9 SCI Data Direction Register. . . . . . . . . . . . . . . . . . . . . . . .348

16.8 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .349

16.9 Data Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .349

16.10 Baud Rate Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .350

16.11 Transmitter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .351

16.11.1 Frame Length. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .352

16.11.2 Transmitting a Frame. . . . . . . . . . . . . . . . . . . . . . . . . . . . .353

16.11.3 Break Frames. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .355

16.11.4 Idle Frames . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .355

Table of Contents

nc...

I

cale Semiconductor,

Frees

16.12 Receiver . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .356

16.12.1 Frame Length. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .356

16.12.2 Receiving a Frame. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .356

16.12.3 Data Sampling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .357

16.12.4 Framing Errors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .362

16.12.5 Baud Rate Tolerance . . . . . . . . . . . . . . . . . . . . . . . . . . . . .362

16.12.5.1 Slow Data Tolerance . . . . . . . . . . . . . . . . . . . . . . . . . . .363

16.12.5.2 Fast Data Tolerance . . . . . . . . . . . . . . . . . . . . . . . . . . .364

16.12.6 Receiver Wakeup. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .365

16.12.6.1 Idle Input Line Wakeup (WAKE = 0) . . . . . . . . . . . . . . .365

16.12.6.2 Address Mark Wakeup (WAKE = 1). . . . . . . . . . . . . . . .365

16.13 Single-Wire Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .366

16.14 Loop Operation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .367

16.15 I/O Ports . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .368

16.16 Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .369

16.17 Interrupts. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .369

16.17.1 Transmit Data Register Empty. . . . . . . . . . . . . . . . . . . . . .369

16.17.2 Transmission Complete . . . . . . . . . . . . . . . . . . . . . . . . . . .369

16.17.3 Receive Data Register Full. . . . . . . . . . . . . . . . . . . . . . . . .370

16.17.4 Idle Receiver Input. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .370

16.17.5 Overrun . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .370

MMC2107 – Rev. 2.0 Technical Data

MOTOROLA Table of Contents 19

For More Information On This Product,

Go to: www.freescale.com

Page 20

Table of Contents

nc...

I

cale Semiconductor,

Frees

Freescale Semiconductor, Inc.

Section 17. Serial Peripheral Interfac e Module ( SPI)

17.1 Contents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .371

17.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 372

17.3 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .372

17.4 Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .373

17.5 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .373

17.6 Signal Description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .374

17.6.1 MISO (Master In/Slave Out). . . . . . . . . . . . . . . . . . . . . . . .374

17.6.2 MOSI (Master Out/Slave In). . . . . . . . . . . . . . . . . . . . . . . .374

17.6.3 SCK (Serial Clock) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .375

17.6.4 SS (Slave Select). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .375

17.7 Memory Map and Registers . . . . . . . . . . . . . . . . . . . . . . . . . .375

17.7.1 SPI Control Register 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . .376

17.7.2 SPI Control Register 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . .378

17.7.3 SPI Baud Rate Register. . . . . . . . . . . . . . . . . . . . . . . . . . .379

17.7.4 SPI Status Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .381

17.7.5 SPI Data Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .382

17.7.6 SPI Pullup and Reduced Drive Register . . . . . . . . . . . . . .383

17.7.7 SPI Port Data Register. . . . . . . . . . . . . . . . . . . . . . . . . . . .384

17.7.8 SPI Port Data Direction Register . . . . . . . . . . . . . . . . . . . .385

17.8 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .386

17.8.1 Master Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .387

17.8.2 Slave Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .387

17.8.3 Transmission Formats . . . . . . . . . . . . . . . . . . . . . . . . . . . .388

17.8.3.1 Transfer Format When CPHA = 1 . . . . . . . . . . . . . . . . .388

17.8.3.2 Transfer Format When CPHA = 0 . . . . . . . . . . . . . . . . .390

17.8.4 SPI Baud Rate Generation. . . . . . . . . . . . . . . . . . . . . . . . .393

17.8.5 Slave-Select Output. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .393

17.8.6 Bidirectional Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .394

17.8.7 Error Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .395

17.8.7.1 Write Collision Error. . . . . . . . . . . . . . . . . . . . . . . . . . . . 395

17.8.7.2 Mode Fault Error . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .395

17.8.8 Low-Power Mode Options . . . . . . . . . . . . . . . . . . . . . . . . .396

17.8.8.1 Run Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .396

17.8.8.2 Doze Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .396

17.8.8.3 Stop Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .396

Technical Data MMC2107 – Rev. 2.0

20 Table of Contents MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Page 21

Freescale Semiconductor, Inc.

17.9 Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .397

17.10 Interrupts. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .397

17.10.1 SPI Interrupt Flag (SPIF) . . . . . . . . . . . . . . . . . . . . . . . . . .397

17.10.2 Mode Fault (MODF) Flag . . . . . . . . . . . . . . . . . . . . . . . . . .397

Table of Contents

Section 18. Queued Analog-to-Digital

Converter (QADC)

18.1 Contents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .399

18.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 401

18.3 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .402

nc...

I

cale Semiconductor,

Frees

18.4 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .403

18.5 Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .404

18.5.1 Debug Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .404

18.5.2 Stop Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .405

18.6 Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .405

18.6.1 Port QA Pin Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . .406

18.6.1.1 Port QA Analog Input Pins. . . . . . . . . . . . . . . . . . . . . . .406

18.6.1.2 Port QA Digital Input/Output Pins . . . . . . . . . . . . . . . . .407

18.6.2 Port QB Pin Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . .407

18.6.2.1 Port QB Analog Input Pins. . . . . . . . . . . . . . . . . . . . . . .407

18.6.2.2 Port QB Digital Input Pins . . . . . . . . . . . . . . . . . . . . . . .407

18.6.3 External Trigger Input Pins. . . . . . . . . . . . . . . . . . . . . . . . .408

18.6.4 Multiplexed Address Output Pins. . . . . . . . . . . . . . . . . . . .408

18.6.5 Multiplexed Analog Input Pins . . . . . . . . . . . . . . . . . . . . . .409

18.6.6 Voltage Reference Pins . . . . . . . . . . . . . . . . . . . . . . . . . . .409

18.6.7 Dedicated Analog Supply Pins. . . . . . . . . . . . . . . . . . . . . .409

18.7 Memory Map. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .409

18.8 Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .411

18.8.1 QADC Module Configuration Register . . . . . . . . . . . . . . . .411

18.8.2 QADC Test Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .412

18.8.3 Port Data Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .412

18.8.4 Port QA Data Direction Register . . . . . . . . . . . . . . . . . . . .414

MMC2107 – Rev. 2.0 Technical Data

MOTOROLA Table of Contents 21

For More Information On This Product,

Go to: www.freescale.com

Page 22

Table of Contents

nc...

I

cale Semiconductor,

Freescale Semiconductor, Inc.

18.8.5 Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .416

18.8.5.1 Control Register 0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . .416

18.8.5.2 Control Register 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . .419

18.8.5.3 QADC Control Register 2. . . . . . . . . . . . . . . . . . . . . . . .422

18.8.6 Status Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .427

18.8.6.1 QADC Status Register 0 . . . . . . . . . . . . . . . . . . . . . . . .427

18.8.6.2 QADC Status Register 1 . . . . . . . . . . . . . . . . . . . . . . . .436

18.8.7 Conversion Command Word Table . . . . . . . . . . . . . . . . . .437

18.8.8 Result Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 441

18.8.8.1 Right-Justified Unsigned Result Register. . . . . . . . . . . .441

18.8.8.2 Left-Justified Signed Result Register. . . . . . . . . . . . . . .442

18.8.8.3 Left-Justified Unsigned Result Register. . . . . . . . . . . . .442

18.9 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .443

18.9.1 QADC Bus Accessing . . . . . . . . . . . . . . . . . . . . . . . . . . . .443

18.9.2 External Multiplexing . . . . . . . . . . . . . . . . . . . . . . . . . . . . .443

18.9.2.1 External Multiplexing Operation. . . . . . . . . . . . . . . . . . .443

18.9.2.2 Module Version Options. . . . . . . . . . . . . . . . . . . . . . . . .444

18.9.2.3 External Multiplexed Address Configuration . . . . . . . . .446

18.9.3 Analog Subsystem . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .446

18.9.3.1 Analog-to-Digital Converter Operation. . . . . . . . . . . . . .446

18.9.3.2 Conversion Cycle Times . . . . . . . . . . . . . . . . . . . . . . . .446

18.9.3.3 Channel Decode and Multiplexer. . . . . . . . . . . . . . . . . .448

18.9.3.4 Sample Buffer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .448

18.9.3.5 Digital-to-Analog Converter (DAC) Array. . . . . . . . . . . .449

18.9.3.6 Comparator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .449

18.9.3.7 Bias . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .449

18.9.3.8 Successive-Approximation Register . . . . . . . . . . . . . . .449

18.9.3.9 State Machine . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .450

Frees

Technical Data MMC2107 – Rev. 2.0

22 Table of Contents MOTOROLA

18.10 Digital Control. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .450

18.10.1 Queue Priority Timing Examples. . . . . . . . . . . . . . . . . . . .450

18.10.1.1 Queue Priority . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .451

18.10.1.2 Queue Priority Schemes . . . . . . . . . . . . . . . . . . . . . . . .453

18.10.2 Boundary Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . .465

18.10.3 Scan Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .466

18.10.4 Disabled Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .467

18.10.5 Reserved Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .467

For More Information On This Product,

Go to: www.freescale.com

Page 23

Freescale Semiconductor, Inc.

18.10.6 Single-Scan Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .467

18.10.6.1 Software-Initiated Single-Scan Mode. . . . . . . . . . . . . . .468

18.10.6.2 External Trigger Single-Scan Mode . . . . . . . . . . . . . . . .469

18.10.6.3 External Gated Single-Scan Mode. . . . . . . . . . . . . . . . .470

18.10.6.4 Interval Timer Single-Scan Mode. . . . . . . . . . . . . . . . . .470

18.10.7 Continuous-Scan Modes . . . . . . . . . . . . . . . . . . . . . . . . . .472

18.10.7.1 Software-Initiated Continuous-Scan Mode. . . . . . . . . . .473

18.10.7.2 External Trigger Continuous-Scan Mode. . . . . . . . . . . . 474

18.10.7.3 External Gated Continuous-Scan Mode . . . . . . . . . . . .474

18.10.7.4 Periodic Timer Continuous-Scan Mode. . . . . . . . . . . . .475

18.10.8 QADC Clock (QCLK) Generation. . . . . . . . . . . . . . . . . . . .476

18.10.9 Periodic/Interval Timer . . . . . . . . . . . . . . . . . . . . . . . . . . . .480

nc...

I

18.10.10 Conversion Command Word Table . . . . . . . . . . . . . . . . . .481

18.10.11 Result Word Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .485

Table of Contents

cale Semiconductor,

Frees

18.11 Pin Connection Considerations . . . . . . . . . . . . . . . . . . . . . . .486

18.11.1 Analog Reference Pins. . . . . . . . . . . . . . . . . . . . . . . . . . . .486

18.11.2 Analog Power Pins. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .486

18.11.3 Conversion Timing Schemes . . . . . . . . . . . . . . . . . . . . . . .488

18.11.4 Analog Supply Filtering and Grounding . . . . . . . . . . . . . . .490

18.11.5 Accommodating Positive/Negative Stress Conditions . . . .494

18.11.6 Analog Input Considerations . . . . . . . . . . . . . . . . . . . . . . .495

18.11.7 Analog Input Pins. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .497

18.11.7.1 Settling Time for the External Circuit . . . . . . . . . . . . . . .498

18.11.7.2 Error Resulting from Leakage . . . . . . . . . . . . . . . . . . . .499

18.12 Interrupts. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .500

18.12.1 Interrupt Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .500

18.12.2 Interrupt Sources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .501

Section 19. External Bus Interface Module (EBI)

19.1 Contents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .503

19.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 504

19.3 Signal Descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .505

19.3.1 Data Bus (D[31:0]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .506

19.3.2 Show Cycle Strobe (SHS) . . . . . . . . . . . . . . . . . . . . . . . . .506

19.3.3 Transfer Acknowledge (TA) . . . . . . . . . . . . . . . . . . . . . . . .506

19.3.4 Transfer Error Acknowledge (TEA) . . . . . . . . . . . . . . . . . .506

MMC2107 – Rev. 2.0 Technical Data

MOTOROLA Table of Contents 23

For More Information On This Product,

Go to: www.freescale.com

Page 24

Table of Contents

Freescale Semiconductor, Inc.

19.3.5 Emulation Mode Chip Selects (CSE[1:0]) . . . . . . . . . . . . .506

19.3.6 Transfer Code (TC[2:0]). . . . . . . . . . . . . . . . . . . . . . . . . . .506

19.3.7 Read/Write (R/W). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .507

19.3.8 Address Bus (A[22:0]) . . . . . . . . . . . . . . . . . . . . . . . . . . . .507

19.3.9 Enable Byte (EB[3:0]). . . . . . . . . . . . . . . . . . . . . . . . . . . . .507

19.3.10 Chip Selects (CS[3:0]) . . . . . . . . . . . . . . . . . . . . . . . . . . . .507

19.3.11 Output Enable (OE) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .507

19.3.12 Transfer Size (TSIZ[1:0]) . . . . . . . . . . . . . . . . . . . . . . . . . .507

19.3.13 Processor Status (PSTAT[3:0]) . . . . . . . . . . . . . . . . . . . . .507

19.4 Memory Map and Registers . . . . . . . . . . . . . . . . . . . . . . . . . .508

19.5 Operand Transfer. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .508

nc...

I

cale Semiconductor,

Frees

19.6 Enable Byte Pins (EB[3:0]

19.7 Bus Master Cycles . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .510

19.7.1 Read Cycles. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 511

19.7.1.1 State 1 (X1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .512

19.7.1.2 Optional Wait States (X2W). . . . . . . . . . . . . . . . . . . . . .512

19.7.1.3 State 2 (X2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .512

19.7.2 Write Cycles. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .513

19.7.2.1 State 1 (X1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .514

19.7.2.2 Optional Wait States (X2W). . . . . . . . . . . . . . . . . . . . . .514

19.7.2.3 State 2 (X2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .514

19.8 Bus Exception Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . .516

19.8.1 Transfer Error Termination. . . . . . . . . . . . . . . . . . . . . . . . .516

19.8.2 Transfer Abort Termination . . . . . . . . . . . . . . . . . . . . . . . .516

19.9 Emulation Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .516

19.9.1 Emulation Chip-Selects (CSE[1:0]) . . . . . . . . . . . . . . . . . .516

19.9.2 Internal Data Transfer Display (Show Cycles) . . . . . . . . . .517

19.9.3 Show Strobe (SHS) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .518

19.10 Bus Monitor. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .519

). . . . . . . . . . . . . . . . . . . . . . . . . . .510

19.11 Interrupts. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .520

Section 20. Chip Select Module

20.1 Contents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .521

20.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 521

20.3 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .522

Technical Data MMC2107 – Rev. 2.0

24 Table of Contents MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Page 25

Freescale Semiconductor, Inc.

20.4 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .523

20.5 Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .524

20.6 Memory Map and Registers . . . . . . . . . . . . . . . . . . . . . . . . . .524

20.6.1 Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .524

20.6.2 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .525

20.7 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .530

20.8 Interrupts. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .531

Table of Contents

Section 21. JTAG Test Access Port and OnCE

21.1 Contents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .533

nc...

I

cale Semiconductor,

Frees

21.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 535

21.3 Top-Level Test Access Port (TAP). . . . . . . . . . . . . . . . . . . . .537

21.3.1 Test Clock (TCLK) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .538

21.3.2 Test Mode Select (TMS) . . . . . . . . . . . . . . . . . . . . . . . . . .538

21.3.3 Test Data Input (TDI) . . . . . . . . . . . . . . . . . . . . . . . . . . . . .538

21.3.4 Test Data Output (TDO). . . . . . . . . . . . . . . . . . . . . . . . . . .538

21.3.5 Test Reset (TRST). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .538

21.3.6 Debug Event (DE) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .538

21.4 Top-Level TAP Controller. . . . . . . . . . . . . . . . . . . . . . . . . . . .540

21.5 Instruction Shift Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . .541

21.5.1 EXTEST Instruction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .541

21.5.2 IDCODE Instruction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .542

21.5.3 SAMPLE/PRELOAD Instruction. . . . . . . . . . . . . . . . . . . . .543

21.5.4 ENABLE_MCU_ONCE Instruction. . . . . . . . . . . . . . . . . . .543

21.5.5 HIGHZ Instruction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .544

21.5.6 CLAMP Instruction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .544

21.5.7 BYPASS Instruction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .544

21.6 IDCODE Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .545

21.7 Bypass Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .546

21.8 Boundary SCAN Register. . . . . . . . . . . . . . . . . . . . . . . . . . . .546

21.9 Restrictions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .546

21.10 Non-Scan Chain Operation. . . . . . . . . . . . . . . . . . . . . . . . . . .547

21.11 Boundary Scan. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .547

21.12 Low-Level TAP (OnCE) Module. . . . . . . . . . . . . . . . . . . . . . .553

MMC2107 – Rev. 2.0 Technical Data

MOTOROLA Table of Contents 25

For More Information On This Product,

Go to: www.freescale.com

Page 26

Table of Contents

nc...

I

cale Semiconductor,

Frees

Freescale Semiconductor, Inc.

21.13 Signal Descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .555

21.13.1 Debug Serial Input (TDI) . . . . . . . . . . . . . . . . . . . . . . . . . .555

21.13.2 Debug Serial Clock (TCLK) . . . . . . . . . . . . . . . . . . . . . . . .555

21.13.3 Debug Serial Output (TDO) . . . . . . . . . . . . . . . . . . . . . . . .555

21.13.4 Debug Mode Select (TMS). . . . . . . . . . . . . . . . . . . . . . . . .556

21.13.5 Test Reset (TRST). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .556

21.13.6 Debug Event (DE) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .556

21.14 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .556

21.14.1 Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .557

21.14.2 OnCE Controller and Serial Interface. . . . . . . . . . . . . . . . .558

21.14.3 OnCE Interface Signals . . . . . . . . . . . . . . . . . . . . . . . . . . .559

21.14.3.1 Internal Debug Request Input (IDR) . . . . . . . . . . . . . . .559

21.14.3.2 CPU Debug Request (DBGRQ

21.14.3.3 CPU Debug Acknowledge (DBGACK). . . . . . . . . . . . . .560

21.14.3.4 CPU Breakpoint Request (BRKRQ

21.14.3.5 CPU Address, Attributes (ADDR, ATTR). . . . . . . . . . . .560

21.14.3.6 CPU Status (PSTAT) . . . . . . . . . . . . . . . . . . . . . . . . . . .560

21.14.3.7 OnCE Debug Output (DEBUG) . . . . . . . . . . . . . . . . . . .560

21.14.4 OnCE Controller Registers. . . . . . . . . . . . . . . . . . . . . . . . .561

21.14.4.1 OnCE Command Register. . . . . . . . . . . . . . . . . . . . . . .561

21.14.4.2 OnCE Control Register . . . . . . . . . . . . . . . . . . . . . . . . .564

21.14.4.3 OnCE Status Register . . . . . . . . . . . . . . . . . . . . . . . . . .568

21.14.5 OnCE Decoder (ODEC). . . . . . . . . . . . . . . . . . . . . . . . . . .570

21.14.6 Memory Breakpoint Logic. . . . . . . . . . . . . . . . . . . . . . . . . .570

21.14.6.1 Memory Address Latch (MAL). . . . . . . . . . . . . . . . . . . .571

21.14.6.2 Breakpoint Address Base Registers . . . . . . . . . . . . . . .571

21.14.7 Breakpoint Address Ma sk Registers . . . . . . . . . . . . . . . . .571

21.14.7.1 Breakpoint Address Comparators . . . . . . . . . . . . . . . . .572

21.14.7.2 Memory Breakpoint Counters . . . . . . . . . . . . . . . . . . . .572

21.14.8 OnCE Trace Logic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .572

21.14.8.1 OnCE Trace Counter. . . . . . . . . . . . . . . . . . . . . . . . . . .573

21.14.8.2 Trace Operation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .574

21.14.9 Methods of Entering Debug Mode . . . . . . . . . . . . . . . . . . .574

21.14.9.1 Debug Request During RESET

21.14.9.2 Debug Request During Normal Activity . . . . . . . . . . . . .575

21.14.9.3 Debug Request During Stop, Doze, or Wait Mode . . . .575

21.14.9.4 Software Request During Normal Activity . . . . . . . . . . .575

). . . . . . . . . . . . . . . . . . .560

). . . . . . . . . . . . . . . .560

. . . . . . . . . . . . . . . . . . .574

Technical Data MMC2107 – Rev. 2.0

26 Table of Contents MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Page 27

Freescale Semiconductor, Inc.

21.14.10 Enabling OnCE Trace Mode . . . . . . . . . . . . . . . . . . . . . . .575

21.14.11 Enabling OnCE Memory Breakpoints. . . . . . . . . . . . . . . . .576

21.14.12 Pipeline Information and Write-Back Bus Register . . . . . .576

21.14.12.1 Program Counter Register. . . . . . . . . . . . . . . . . . . . . . .577

21.14.12.2 Instruction Register . . . . . . . . . . . . . . . . . . . . . . . . . . . .577

21.14.12.3 Control State Register . . . . . . . . . . . . . . . . . . . . . . . . . . 577

21.14.12.4 Writeback Bus Register . . . . . . . . . . . . . . . . . . . . . . . . .579

21.14.12.5 Processor Status Register. . . . . . . . . . . . . . . . . . . . . . .579

21.14.13 Instruction Address FIFO Buffer (PC FIFO). . . . . . . . . . . .580

21.14.14 Reserved Test Control Registers. . . . . . . . . . . . . . . . . . . .581

21.14.15 Serial Protocol . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .581

21.14.16 OnCE Commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .582

nc...

I

21.14.17 Target Site Debug System Requirements . . . . . . . . . . . . .582

21.14.18 Interface Connector for JTAG/OnCE Serial Port . . . . . . . .582

Table of Contents

cale Semiconductor,

Frees

Section 22. Electrical Specifications

22.1 Contents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .585

22.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 585

22.3 Absolute Maximum Ratings . . . . . . . . . . . . . . . . . . . . . . . . . .586

22.4 Thermal Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . .587

22.5 Power Dissipation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .587

22.6 Electrostatic Discharge (ESD) Protection. . . . . . . . . . . . . . . .587

22.7 DC Electrical Specifications . . . . . . . . . . . . . . . . . . . . . . . . . .588

22.8 PLL Electrical Specifications. . . . . . . . . . . . . . . . . . . . . . . . . .590

22.9 QADC Electrical Characteristics. . . . . . . . . . . . . . . . . . . . . . .591

22.10 FLASH Memory Characteristics . . . . . . . . . . . . . . . . . . . . . . .594

22.11 External Interface Timing Characteristics. . . . . . . . . . . . . . . .596

22.12 Reset and Configuration Override Timing . . . . . . . . . . . . . . .601

22.13 SPI Timing Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . .602

22.14 OnCE, JTAG, and Boundary Scan Timing . . . . . . . . . . . . . . .605

MMC2107 – Rev. 2.0 Technical Data

MOTOROLA Table of Contents 27

For More Information On This Product,

Go to: www.freescale.com

Page 28

Table of Contents

Freescale Semiconductor, Inc.

Section 23. Mechan ical Specifications

23.1 Contents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .609

23.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 609

23.3 Bond Pins. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .610

23.4 Package Information for the 144-Pin LQFP . . . . . . . . . . . . . .611

23.5 Package Information for the 100-Pin LQFP . . . . . . . . . . . . . .611

23.6 144-Pin LQFP Mechanical Drawing . . . . . . . . . . . . . . . . . . . .612

23.7 100-Pin LQFP Mechanical Drawing . . . . . . . . . . . . . . . . . . . .613

nc...

I

cale Semiconductor,

Frees

Section 24. Ordering Information

24.1 Contents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .615

24.2 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 615

24.3 MC Order Numbers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .615

Technical Data MMC2107 – Rev. 2.0

28 Table of Contents MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Page 29

nc...

I

cale Semiconductor,

Frees

Freescale Semiconductor, Inc.

Technical Data — MMC2107

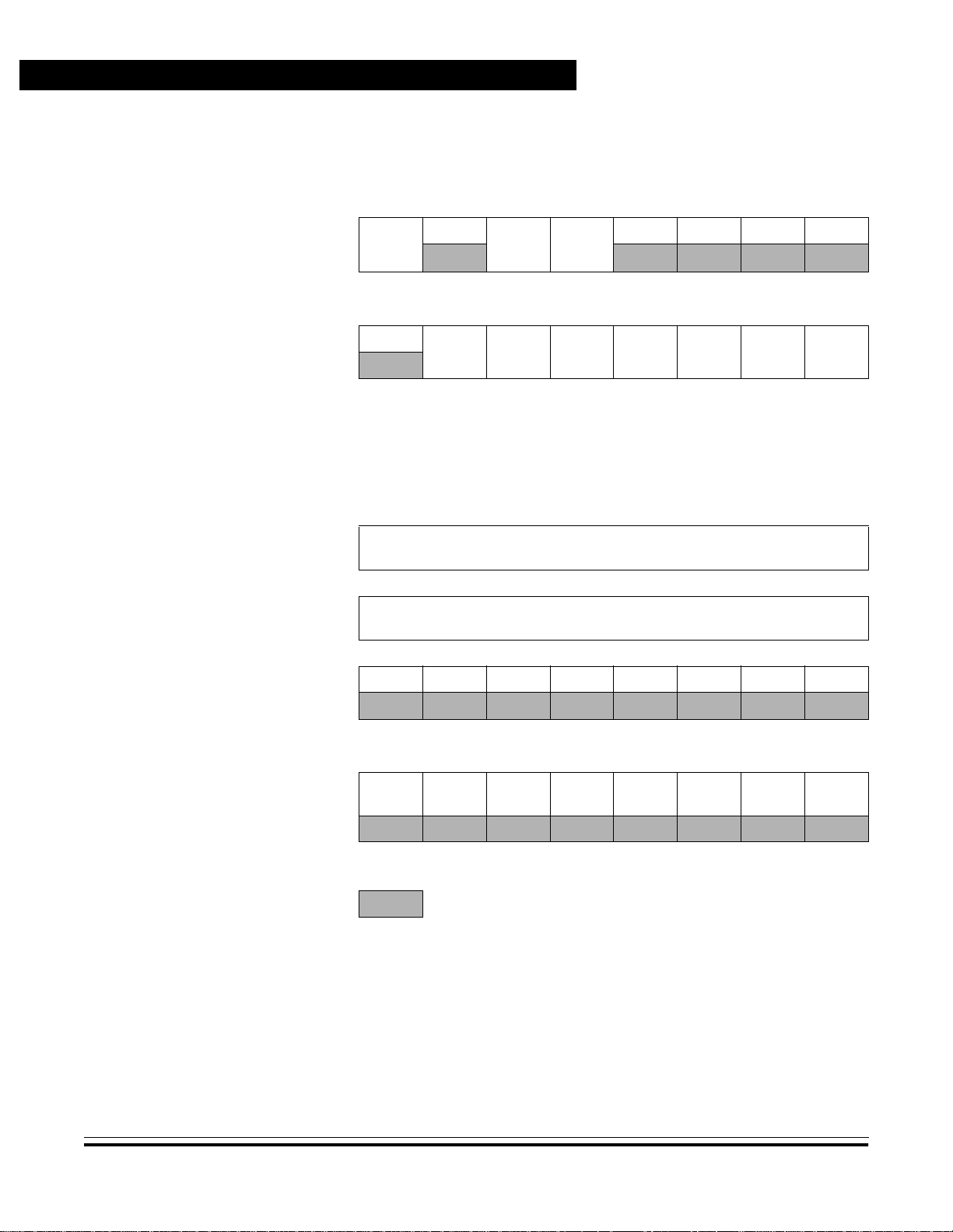

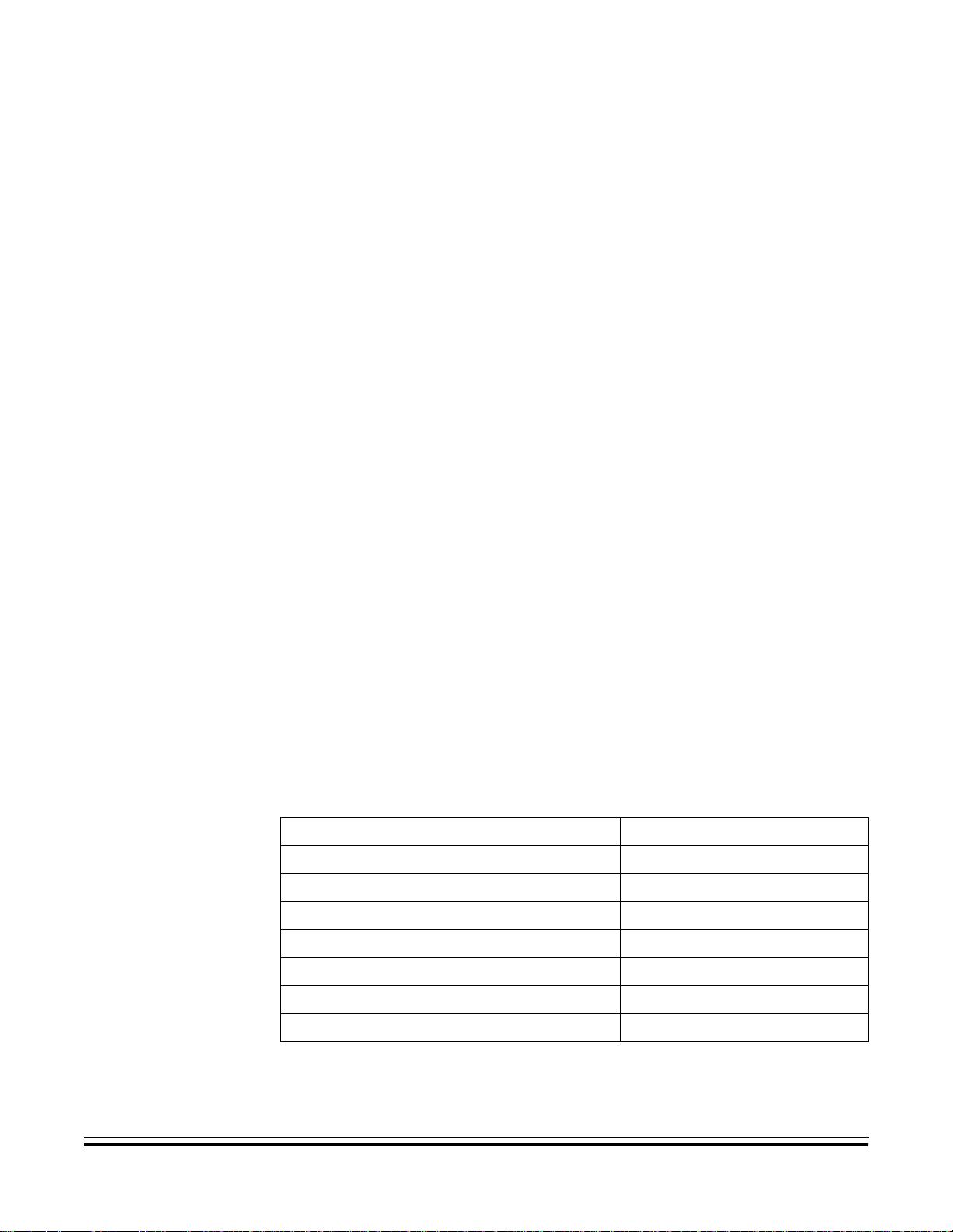

Figure Title P age

1-1 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .49

2-1 Address Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .52

2-2 Register Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .54

3-1 Chip Configuration Module Block Diagram . . . . . . . . . . . . .92

3-2 Chip Configuration Register (CCR) . . . . . . . . . . . . . . . . . . .94

3-3 Reset Configuration Register (RCON) . . . . . . . . . . . . . . . . .97

3-4 Chip Identification Register (CIR). . . . . . . . . . . . . . . . . . . . .99

3-5 Chip Test Register (CTR). . . . . . . . . . . . . . . . . . . . . . . . . .100

4-1 144-Pin LQFP Assignments. . . . . . . . . . . . . . . . . . . . . . . .115

4-2 100-Pin LQFP Assignments. . . . . . . . . . . . . . . . . . . . . . . .116

5-1 Reset Controller Block Diagram. . . . . . . . . . . . . . . . . . . . .131

5-2 Reset Control Register (RCR) . . . . . . . . . . . . . . . . . . . . . .133

5-3 Reset Status Register (RSR) . . . . . . . . . . . . . . . . . . . . . . .134

5-4 Reset Test Register (RTR). . . . . . . . . . . . . . . . . . . . . . . . .135

5-5 Reset Control Flow. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .139

6-1 M•CORE Processor Block Diagram . . . . . . . . . . . . . . . . . .145

6-2 Programming Model. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .147

6-3 Data Organization in Memory. . . . . . . . . . . . . . . . . . . . . . .149

6-4 Data Organization in Registers . . . . . . . . . . . . . . . . . . . . .149

List of Figures

7-1 Interrupt Controller Block Diagram. . . . . . . . . . . . . . . . . . .155

7-2 Interrupt Control Register (ICR) . . . . . . . . . . . . . . . . . . . . .157

7-3 Interrupt Status Register (ISR). . . . . . . . . . . . . . . . . . . . . .159

7-4 Interrupt Force Register High (IFRH) . . . . . . . . . . . . . . . . .160

7-5 Interrupt Force Register Low (IFRL). . . . . . . . . . . . . . . . . .161

MMC2107 – Rev. 2.0 Technical Data

MOTOROLA List of Figures 29

For More Information On This Product,

Go to: www.freescale.com

Page 30

List of Figu r e s

nc...

I

cale Semiconductor,

Freescale Semiconductor, Inc.

Figure Title P age

7-6 Interrupt Pending Register (IPR) . . . . . . . . . . . . . . . . . . . .162

7-7 Normal Interrupt Enable Register (NIER). . . . . . . . . . . . . .163

7-8 Normal Interrupt Pending Register (NIPR). . . . . . . . . . . . .164

7-9 Fast Interrupt Enable Register (FIER) . . . . . . . . . . . . . . . .165

7-10 Fast Interrupt Pending Register (FIPR ) . . . . . . . . . . . . . . .166

7-11 Priority Level Select Registers (PLSR0–PLSR39). . . . . . .167

9-1 CMFR 128-Kbyte Block Diagram . . . . . . . . . . . . . . . . . . . .183

9-2 CMFR Array and Control Register A ddressing . . . . . . . . .186

9-3 CMFR Module Configuration Register (CMFRMCR) . . . . .188

9-4 CMFR Module Test Register (CMFRMTR) . . . . . . . . . . . .193

9-5 CMFR High-Voltage Control Register (CMFRCTL) . . . . . .196