Page 1

MC9S12C Family

Data Sheet

Also covers

MC9S12GC Family

HCS12

Microcontrollers

MC9S12C Family

Rev. 1.15

7/2005

freescale.com

Page 2

Page 3

HCS12

Microcontrollers

MC9S12C Family

also covers

MC9S12GC Family

MC9S12C Family

Rev. 1.15

7/2005

freescale.com

Page 4

To provide the most up-to-date information, the revision of our documents on the World Wide Web will be

the most current. Your printed copy may be an earlier revision. To verify you have the latest information

available, refer to:

http://freescale.com/

A full list of family members and options is included in the appendices.

The following revision history table summarizes changes contained in this document.

This document contains information for all constituent modules, with the exception of the S12 CPU. For

S12 CPU information please refer to the CPU S12 Reference Manual.

Revision History

Date

June, 2005 01.14 New Book

July, 2005 01.15

Revision

Level

Removed 16MHz option for 128K, 96K and 64K versions

Minor corrections following review

Description

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc.

This product incorporates SuperFlash® technology licensed from SST.

© Freescale Semiconductor, Inc., 2005. All rights reserved.

MC9S12C128 Data Sheet, Rev. 1.15

4 Freescale Semiconductor

Page 5

Chapter 1 Device Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .19

Chapter 2 Port Integration Module (PIM9C32) . . . . . . . . . . . . . . . . . . . . .75

Chapter 3 Module Mapping Control (MMCV4) . . . . . . . . . . . . . . . . . . . .111

Chapter 4 Multiplexed External Bus Interface (MEBIV3) . . . . . . . . . . . .131

Chapter 5 Interrupt (INTV1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .161

Chapter 6 Background Debug Module (BDMV4) . . . . . . . . . . . . . . . . . .169

Chapter 7 Debug Module (DBGV1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . .195

Chapter 8 Analog-to-Digital Converter (ATD10B8CV2) . . . . . . . . . . . . .229

Chapter 9 Clocks and Reset Generator (CRGV4) . . . . . . . . . . . . . . . . . .255

Chapter 10 128 Kbyte Flash Module (S12FTS128K1V2). . . . . . . . . . . . . .291

Chapter 11 Freescale’s Scalable Controller Area Network (MSCANV2) 325

Chapter 12 Oscillator (OSCV2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .379

Chapter 13 Pulse-Width Modulator (PWM8B6CV1) . . . . . . . . . . . . . . . . .383

Chapter 14 Serial Communications Interface (S12SCIV2) . . . . . . . . . . . .419

Chapter 15 Serial Peripheral Interface (SPIV3) . . . . . . . . . . . . . . . . . . . . .449

Chapter 16 Timer Module (TIM16B8CV1) . . . . . . . . . . . . . . . . . . . . . . . . .471

Chapter 17 Dual Output Voltage Regulator (VREG3V3V2) . . . . . . . . . . .497

Appendix A Electrical Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . .505

Appendix B Emulation Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .537

Appendix C Package Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .539

Appendix D Derivative Differences . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .543

Appendix E Ordering Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .544

MC9S12C128 Data Sheet, Rev. 1.15

Freescale Semiconductor 5

Page 6

MC9S12C128 Data Sheet, Rev. 1.15

6 Freescale Semiconductor

Page 7

Chapter 1Device Overview

1.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

1.1.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

1.1.2 Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21

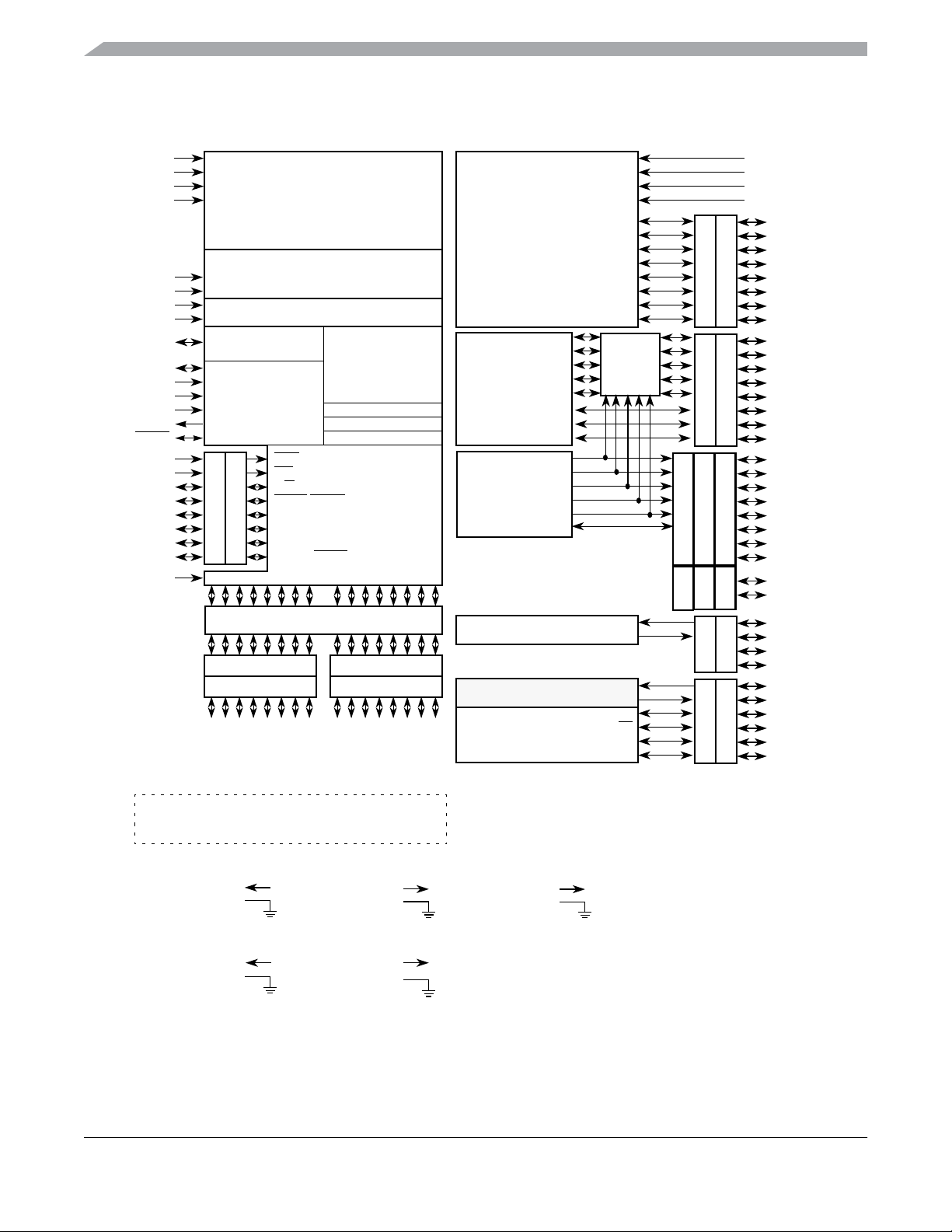

1.1.3 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

1.2 Memory Map and Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

1.2.1 Device Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

1.2.2 Detailed Register Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

1.2.3 Part ID Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .47

1.3 Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

1.3.1 Device Pinouts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

1.3.2 Signal Properties Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

1.3.3 Pin Initialization for 48- and 52-Pin LQFP Bond Out Versions . . . . . . . . . . . . . . . . . . . 52

1.3.4 Detailed Signal Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

1.3.5 Power Supply Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .58

1.4 System Clock Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

1.5 Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

1.5.1 Chip Configuration Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

1.5.2 Security . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

1.5.3 Low-Power Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

1.6 Resets and Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

1.6.1 Vectors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

1.6.2 Resets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

1.7 Device Specific Information and Module Dependencies . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

1.7.1 PPAGE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

1.7.2 BDM Alternate Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

1.7.3 Extended Address Range Emulation Implications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

1.7.4 VREGEN . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

1.7.5 V

DD1

, V

1.7.6 Clock Reset Generator And VREG Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

1.7.7 Analog-to-Digital Converter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

1.7.8 MODRR Register Port T And Port P Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

1.7.9 Port AD Dependency On PIM And ATD Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

1.8 Recommended Printed Circuit Board Layout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

DD2

, V

SS1

, V

SS2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

Chapter 2

Port Integration Module (PIM9C32) Block Description

2.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

2.1.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

2.1.2 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

MC9S12C128 Data Sheet, Rev. 1.15

Freescale Semiconductor 7

Page 8

2.2 Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

2.3 Memory Map and Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

2.3.1 Module Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

2.3.2 Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .81

2.4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

2.4.1 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

2.4.2 Port Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 106

2.4.3 Port A, B, E and BKGD Pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 108

2.4.4 External Pin Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 108

2.4.5 Low Power Options . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 108

2.5 Initialization Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 108

2.5.1 Reset Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 108

2.6 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109

2.6.1 Interrupt Sources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109

2.6.2 Recovery from STOP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109

2.7 Application Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109

Chapter 3

Module Mapping Control (MMCV4) Block Description

3.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

3.1.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 112

3.1.2 Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 112

3.2 External Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 112

3.3 Memory Map and Register Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 112

3.3.1 Module Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 112

3.3.2 Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 114

3.4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124

3.4.1 Bus Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124

3.4.2 Address Decoding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124

3.4.3 Memory Expansion . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 126

Chapter 4

Multiplexed External Bus Interface (MEBIV3)

Block Description

4.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 131

4.1.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 131

4.1.2 Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 133

4.2 External Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 133

4.3 Memory Map and Register Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 136

4.3.1 Module Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 136

4.3.2 Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 137

4.4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 153

4.4.1 Detecting Access Type from External Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 153

4.4.2 Stretched Bus Cycles . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 154

MC9S12C128 Data Sheet, Rev. 1.15

8 Freescale Semiconductor

Page 9

4.4.3 Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 154

4.4.4 Internal Visibility . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 159

4.4.5 Low-Power Options . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 159

Chapter 5

Interrupt (INTV1) Block Description

5.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 161

5.1.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 162

5.1.2 Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 162

5.2 External Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 163

5.3 Memory Map and Register Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 163

5.3.1 Module Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 163

5.3.2 Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 163

5.4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 165

5.4.1 Low-Power Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 166

5.5 Resets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 166

5.6 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 166

5.6.1 Interrupt Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 166

5.6.2 Highest Priority I-Bit Maskable Interrupt . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 166

5.6.3 Interrupt Priority Decoder . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 167

5.7 Exception Priority . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 167

Chapter 6

Background Debug Module (BDMV4) Block Description

6.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 169

6.1.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 169

6.1.2 Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 170

6.2 External Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 170

6.2.1 BKGD — Background Interface Pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 171

6.2.2

6.2.3

6.3 Memory Map and Register Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 172

6.3.1 Module Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 172

6.3.2 Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 173

6.4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 178

6.4.1 Security . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 178

6.4.2 Enabling and Activating BDM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 178

6.4.3 BDM Hardware Commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 179

6.4.4 Standard BDM Firmware Commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 180

6.4.5 BDM Command Structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 181

6.4.6 BDM Serial Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 183

6.4.7 Serial Interface Hardware Handshake Protocol . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 186

6.4.8 Hardware Handshake Abort Procedure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 188

6.4.9 SYNC — Request Timed Reference Pulse . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 191

TAGHI — High Byte Instruction Tagging Pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 171

TAGLO — Low Byte Instruction Tagging Pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 171

MC9S12C128 Data Sheet, Rev. 1.15

Freescale Semiconductor 9

Page 10

6.4.10 Instruction Tracing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 191

6.4.11 Instruction Tagging . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 192

6.4.12 Serial Communication Time-Out . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 192

6.4.13 Operation in Wait Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 193

6.4.14 Operation in Stop Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 193

Chapter 7

Debug Module (DBGV1) Block Description

7.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 195

7.1.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 195

7.1.2 Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 197

7.1.3 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 197

7.2 External Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 199

7.3 Memory Map and Register Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 200

7.3.1 Module Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 200

7.3.2 Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 200

7.4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 216

7.4.1 DBG Operating in BKP Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 216

7.4.2 DBG Operating in DBG Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 218

7.4.3 Breakpoints . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 225

7.5 Resets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 226

7.6 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 226

Chapter 8

Analog-to-Digital Converter (ATD10B8CV2)

Block Description

8.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 229

8.1.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 229

8.1.2 Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 229

8.1.3 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 230

8.2 Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 231

8.2.1 AN7 / ETRIG / PAD7 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 231

8.2.2 AN6 / PAD6 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 231

8.2.3 AN5 / PAD5 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 231

8.2.4 AN4 / PAD4 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 231

8.2.5 AN3 / PAD3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 231

8.2.6 AN2 / PAD2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 231

8.2.7 AN1 / PAD1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 231

8.2.8 AN0 / PAD0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 231

8.2.9 V

8.2.10 V

8.3 Memory Map and Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 232

8.3.1 Module Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 232

8.3.2 Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 236

, V

RH

RL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 231

, V

DDA

SSA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 231

MC9S12C128 Data Sheet, Rev. 1.15

10 Freescale Semiconductor

Page 11

8.4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 251

8.4.1 Analog Sub-block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 251

8.4.2 Digital Sub-block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 252

8.5 Resets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 253

8.6 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 253

Chapter 9

Clocks and Reset Generator (CRGV4) Block Description

9.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 255

9.1.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 255

9.1.2 Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 256

9.1.3 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 256

9.2 External Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 257

9.2.1 V

DDPLL

, V

SSPLL

9.2.2 XFC — PLL Loop Filter Pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 257

9.2.3

RESET — Reset Pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 258

9.3 Memory Map and Register Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 258

9.3.1 Module Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 258

9.3.2 Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 259

9.4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 270

9.4.1 Phase Locked Loop (PLL) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 270

9.4.2 System Clocks Generator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 273

9.4.3 Clock Monitor (CM) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 274

9.4.4 Clock Quality Checker . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 274

9.4.5 Computer Operating Properly Watchdog (COP) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 276

9.4.6 Real-Time Interrupt (RTI) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 276

9.4.7 Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 277

9.4.8 Low-Power Operation in Run Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 278

9.4.9 Low-Power Operation in Wait Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 278

9.4.10 Low-Power Operation in Stop Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 282

9.5 Resets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 286

9.5.1 Clock Monitor Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 288

9.5.2 Computer Operating Properly Watchdog (COP) Reset . . . . . . . . . . . . . . . . . . . . . . . . . 288

9.5.3 Power-On Reset, Low Voltage Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 289

9.6 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 290

9.6.1 Real-Time Interrupt . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 290

9.6.2 PLL Lock Interrupt . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 290

9.6.3 Self-Clock Mode Interrupt . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 290

— PLL Operating Voltage, PLL Ground . . . . . . . . . . . . . . . . . . . . . . 257

Chapter 10

128 Kbyte Flash Module (S12FTS128K1V2)

10.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 291

10.1.1 Glossary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 291

10.1.2 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 291

MC9S12C128 Data Sheet, Rev. 1.15

Freescale Semiconductor 11

Page 12

10.1.3 Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 292

10.1.4 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 292

10.2 External Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 292

10.3 Memory Map and Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 293

10.3.1 Module Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 293

10.3.2 Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 296

10.4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 308

10.4.1 Flash Command Operations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 308

10.4.2 Operating Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 322

10.4.3 Flash Module Security . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 322

10.4.4 Flash Reset Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 324

10.4.5 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 324

Chapter 11

Freescale’s Scalable Controller Area Network (MSCANV2) Block Description

11.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 325

11.1.1 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 326

11.1.2 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 326

11.1.3 Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 327

11.2 External Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 327

11.2.1 RXCAN — CAN Receiver Input Pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 327

11.2.2 TXCAN — CAN Transmitter Output Pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 327

11.2.3 CAN System . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 327

11.3 Memory Map and Register Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 328

11.3.1 Module Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 328

11.3.2 Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 330

11.3.3 Programmer’s Model of Message Storage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 351

11.4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 360

11.4.1 General . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 360

11.4.2 Message Storage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 361

11.4.3 Identifier Acceptance Filter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 364

11.4.4 Timer Link . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 370

11.4.5 Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 371

11.4.6 Low-Power Options . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 371

11.4.7 Reset Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 376

11.4.8 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 376

11.5 Initialization/Application Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 378

11.5.1 MSCAN initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 378

Chapter 12

Oscillator (OSCV2) Block Description

12.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 379

12.1.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 379

12.1.2 Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 379

MC9S12C128 Data Sheet, Rev. 1.15

12 Freescale Semiconductor

Page 13

12.2 External Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 380

12.2.1 V

DDPLL

and V

SSPLL

— PLL Operating Voltage, PLL Ground . . . . . . . . . . . . . . . . . . . 380

12.2.2 EXTAL and XTAL — Clock/Crystal Source Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 380

12.2.3 XCLKS — Colpitts/Pierce Oscillator Selection Signal . . . . . . . . . . . . . . . . . . . . . . . . . 381

12.3 Memory Map and Register Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 382

12.4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 382

12.4.1 Amplitude Limitation Control (ALC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 382

12.4.2 Clock Monitor (CM) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 382

12.5 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 382

Chapter 13

Pulse-Width Modulator (PWM8B6CV1) Block Description

13.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 383

13.1.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 383

13.1.2 Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 383

13.1.3 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 384

13.2 External Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 384

13.2.1 PWM5 — Pulse Width Modulator Channel 5 Pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 384

13.2.2 PWM4 — Pulse Width Modulator Channel 4 Pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 384

13.2.3 PWM3 — Pulse Width Modulator Channel 3 Pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 384

13.2.4 PWM2 — Pulse Width Modulator Channel 2 Pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 385

13.2.5 PWM1 — Pulse Width Modulator Channel 1 Pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 385

13.2.6 PWM0 — Pulse Width Modulator Channel 0 Pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 385

13.3 Memory Map and Register Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 385

13.3.1 Module Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 385

13.3.2 Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 387

13.4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 407

13.4.1 PWM Clock Select . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 407

13.4.2 PWM Channel Timers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 410

13.5 Resets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 417

13.6 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 417

Chapter 14

Serial Communications Interface (S12SCIV2)

Block Description

14.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 419

14.1.1 Glossary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 419

14.1.2 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 419

14.1.3 Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 420

14.1.4 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 421

14.2 External Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 421

14.2.1 TXD-SCI Transmit Pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 421

14.2.2 RXD-SCI Receive Pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 421

14.3 Memory Map and Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 422

MC9S12C128 Data Sheet, Rev. 1.15

Freescale Semiconductor 13

Page 14

14.3.1 Module Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 422

14.3.2 Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 422

14.4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 430

14.4.1 Data Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 431

14.4.2 Baud Rate Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 432

14.4.3 Transmitter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 433

14.4.4 Receiver . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 436

14.4.5 Single-Wire Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 445

14.4.6 Loop Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 445

14.5 Initialization Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 445

14.5.1 Reset Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 445

14.5.2 Interrupt Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 446

14.5.3 Recovery from Wait Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 447

Chapter 15

Serial Peripheral Interface (SPIV3) Block Description

15.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 449

15.1.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 449

15.1.2 Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 449

15.1.3 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 450

15.2 External Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 450

15.2.1 MOSI — Master Out/Slave In Pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 450

15.2.2 MISO — Master In/Slave Out Pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 451

15.2.3

15.2.4 SCK — Serial Clock Pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 451

15.3 Memory Map and Register Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 451

15.3.1 Module Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 451

15.3.2 Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 452

15.4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 459

15.4.1 Master Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 460

15.4.2 Slave Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 461

15.4.3 Transmission Formats . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 462

15.4.4 SPI Baud Rate Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 465

15.4.5 Special Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 466

15.4.6 Error Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 467

15.4.7 Operation in Run Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 468

15.4.8 Operation in Wait Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 468

15.4.9 Operation in Stop Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 468

15.5 Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 469

15.6 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 469

15.6.1 MODF . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 469

15.6.2 SPIF . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 469

15.6.3 SPTEF . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 469

SS — Slave Select Pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 451

MC9S12C128 Data Sheet, Rev. 1.15

14 Freescale Semiconductor

Page 15

Chapter 16

Timer Module (TIM16B8CV1) Block Description

16.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 471

16.1.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 471

16.1.2 Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 471

16.1.3 Block Diagrams . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 472

16.2 External Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 474

16.2.1 IOC7 — Input Capture and Output Compare Channel 7 Pin . . . . . . . . . . . . . . . . . . . . 474

16.2.2 IOC6 — Input Capture and Output Compare Channel 6 Pin . . . . . . . . . . . . . . . . . . . . 474

16.2.3 IOC5 — Input Capture and Output Compare Channel 5 Pin . . . . . . . . . . . . . . . . . . . . 474

16.2.4 IOC4 — Input Capture and Output Compare Channel 4 Pin . . . . . . . . . . . . . . . . . . . . 474

16.2.5 IOC3 — Input Capture and Output Compare Channel 3 Pin . . . . . . . . . . . . . . . . . . . . 474

16.2.6 IOC2 — Input Capture and Output Compare Channel 2 Pin . . . . . . . . . . . . . . . . . . . . 475

16.2.7 IOC1 — Input Capture and Output Compare Channel 1 Pin . . . . . . . . . . . . . . . . . . . . 475

16.2.8 IOC0 — Input Capture and Output Compare Channel 0 Pin . . . . . . . . . . . . . . . . . . . . 475

16.3 Memory Map and Register Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 475

16.3.1 Module Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 475

16.3.2 Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 477

16.4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 491

16.4.1 Prescaler . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 492

16.4.2 Input Capture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 493

16.4.3 Output Compare . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 493

16.4.4 Pulse Accumulator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 493

16.4.5 Event Counter Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 494

16.4.6 Gated Time Accumulation Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 494

16.5 Resets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 494

16.6 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 494

16.6.1 Channel [7:0] Interrupt (C[7:0]F) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 495

16.6.2 Pulse Accumulator Input Interrupt (PAOVI) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 495

16.6.3 Pulse Accumulator Overflow Interrupt (PAOVF) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 495

16.6.4 Timer Overflow Interrupt (TOF) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 495

Chapter 17

Dual Output Voltage Regulator (VREG3V3V2)

Block Description

17.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 497

17.1.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 497

17.1.2 Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 497

17.1.3 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 498

17.2 External Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 499

17.2.1 V

17.2.2 V

17.2.3 V

17.2.4 V

Freescale Semiconductor 15

, V

DDR

, V

DDA

, VSS — Regulator Output1 (Core Logic) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 500

DD

DDPLL

— Regulator Power Input . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 499

SSR

— Regulator Reference Supply . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 499

SSA

, V

— Regulator Output2 (PLL) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 500

SSPLL

MC9S12C128 Data Sheet, Rev. 1.15

Page 16

17.2.5 V

REGEN

— Optional Regulator Enable . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 500

17.3 Memory Map and Register Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 500

17.3.1 Module Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 500

17.3.2 Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 501

17.4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 501

17.4.1 REG — Regulator Core . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 502

17.4.2 Full-Performance Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 502

17.4.3 Reduced-Power Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 502

17.4.4 LVD — Low-Voltage Detect . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 502

17.4.5 POR — Power-On Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 502

17.4.6 LVR — Low-Voltage Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 502

17.4.7 CTRL — Regulator Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 502

17.5 Resets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 503

17.5.1 Power-On Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 503

17.5.2 Low-Voltage Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 503

17.6 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 503

17.6.1 LVI — Low-Voltage Interrupt . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 503

Appendix A

Electrical Characteristics

A.1 General . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 505

A.1.1 Parameter Classification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 505

A.1.2 Power Supply . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 505

A.1.3 Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 506

A.1.4 Current Injection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 506

A.1.5 Absolute Maximum Ratings. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 507

A.1.6 ESD Protection and Latch-up Immunity. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 508

A.1.7 Operating Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 509

A.1.8 Power Dissipation and Thermal Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 510

A.1.9 I/O Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 512

A.1.10 Supply Currents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 513

A.2 ATD Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 516

A.2.1 ATD Operating Characteristics In 5V Range. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 516

A.2.2 ATD Operating Characteristics In 3.3V Range . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 517

A.2.3 Factors Influencing Accuracy . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 517

A.2.4 ATD Accuracy (5V Range) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 518

A.2.5 ATD Accuracy (3.3V Range). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 519

A.3 MSCAN. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 521

A.4 Reset, Oscillator and PLL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 521

A.4.1 Startup. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 521

A.4.2 Oscillator. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 522

A.4.3 Phase Locked Loop. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 524

A.5 NVM, Flash, and EEPROM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 527

A.5.1 NVM Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 527

A.5.2 NVM Reliability . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 530

MC9S12C128 Data Sheet, Rev. 1.15

16 Freescale Semiconductor

Page 17

A.6 SPI. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 531

A.6.1 Master Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 531

A.6.2 Slave Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 533

A.7 Voltage Regulator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 535

A.7.1 Voltage Regulator Operating Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 535

A.7.2 Chip Power-up and LVI/LVR Graphical Explanation . . . . . . . . . . . . . . . . . . . . . . . . . . 535

A.7.3 Output Loads. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 536

Appendix B

Emulation Information

B.1 General . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 537

B.1.1 PK[2:0] / XADDR[16:14]. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 538

Appendix C

Package Information

C.1 General . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 539

C.1.1 80-Pin QFP Package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 540

C.1.2 52-Pin LQFP Package. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 541

C.1.3 48-Pin LQFP Package. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 542

Appendix D

Derivative Differences

Appendix E

Ordering Information

MC9S12C128 Data Sheet, Rev. 1.15

Freescale Semiconductor 17

Page 18

MC9S12C128 Data Sheet, Rev. 1.15

18 Freescale Semiconductor

Page 19

Chapter 1 Device Overview

1.1 Introduction

The MC9S12C-Family and the MC9S12GC Family are 48/52/80 pin Flash-based industrial/automotive

network control MCU families, which deliver the power and flexibility of the 16-bit core (CPU12) family

to a whole new range of cost and space sensitive, general purpose industrial and automotive network

applications. All MC9S12C-Family and MC9S12GC Family members are comprised of standard on-chip

peripherals including a 16-bit central processing unit (CPU12), up to 128K bytes of Flash EEPROM, up

to 4K bytes of RAM, an asynchronous serial communications interface (SCI), a serial peripheral interface

(SPI), an 8-channel 16-bit timer module (TIM), a 6-channel 8-bit pulse width modulator (PWM), an 8channel, 10-bit analog-to-digital converter (ADC). The MC9S12C-Family members also feature a CAN

2.0 A, B software compatible module (MSCAN12). All family members feature full 16-bit data paths

throughout. The inclusion of a PLL circuit allows power consumption and performance to be adjusted to

suit operational requirements. In addition to the I/O ports availablein each module, up to 10dedicated I/O

port bits are available with wake-up capability from stop or wait mode. The devices are available in 48-,

52-, and 80-pin QFP packages, with the 80-pin version pin compatible to the HCS12 A, B, and D Family

derivatives.

1.1.1 Features

• 16-bit HCS12 core:

— HCS12 CPU

– Upward compatible with M68HC11 instruction set

– Interrupt stacking and programmer’s model identical to M68HC11

– Instruction queue

– Enhanced indexed addressing

— MMC (memory map and interface)

— INT (interrupt control)

— BDM (background debug mode)

— DBG12 (enhanced debug12 module, including breakpoints and change-of-flow trace buffer)

— MEBI (multiplexed expansion bus interface) available only in 80-pin package version

• Wake-up interrupt inputs:

— Up to 12 port bits available for wake up interrupt function with digital filtering

MC9S12C128 Data Sheet, Rev. 1.15

Freescale Semiconductor 19

Page 20

Chapter 1 Device Overview

• Memory options:

— 16K or 32Kbyte Flash EEPROM (erasable in 512-byte sectors)

64K, 96K, or 128Kbyte Flash EEPROM (erasable in 1024-byte sectors)

— 1K, 2K, or 4K Byte RAM

• Analog-to-digital converters:

— One 8-channel module with 10-bit resolution

— External conversion trigger capability

• Available on MC9S12C Family:

— One 1M bit per second, CAN 2.0 A, B software compatible module

— Five receive and three transmit buffers

— Flexible identifier filter programmable as 2 x 32 bit, 4 x 16 bit, or 8 x 8 bit

— Four separate interrupt channels for Rx, Tx, error, and wake-up

— Low-pass filter wake-up function

— Loop-back for self test operation

• Timer module (TIM):

— 8-channel timer

— Each channel configurable as either input capture or output compare

— Simple PWM mode

— Modulo reset of timer counter

— 16-bit pulse accumulator

— External event counting

— Gated time accumulation

• PWM module:

— Programmable period and duty cycle

— 8-bit 6-channel or 16-bit 3-channel

— Separate control for each pulse width and duty cycle

— Center-aligned or left-aligned outputs

— Programmable clock select logic with a wide range of frequencies

— Fast emergency shutdown input

• Serial interfaces:

— One asynchronous serial communications interface (SCI)

— One synchronous serial peripheral interface (SPI)

• CRG (clock reset generator module)

— Windowed COP watchdog

— Real time interrupt

— Clock monitor

— Pierce or low current Colpitts oscillator

— Phase-locked loop clock frequency multiplier

— Limp home mode in absence of external clock

— Low power 0.5MHz to 16MHz crystal oscillator reference clock

MC9S12C128 Data Sheet, Rev. 1.15

20 Freescale Semiconductor

Page 21

• Operating frequency:

— 32MHz equivalent to 16MHz bus speed for single chip

— 32MHz equivalent to 16MHz bus speed in expanded bus modes

— Option of 9S12C Family: 50MHz equivalent to 25MHz bus speed

— All 9S12GC Family members allow a 50MHz operating frequency.

• Internal 2.5V regulator:

— Supports an input voltage range from 2.97V to 5.5V

— Low power mode capability

— Includes low voltage reset (LVR) circuitry

— Includes low voltage interrupt (LVI) circuitry

• 48-pin LQFP, 52-pin LQFP, or 80-pin QFP package:

— Up to 58 I/O lines with 5V input and drive capability (80-pin package)

— Up to 2 dedicated 5V input only lines (IRQ, XIRQ)

— 5V 8 A/D converter inputs and 5V I/O

• Development support:

— Single-wire background debug™ mode (BDM)

— On-chip hardware breakpoints

— Enhanced DBG12 debug features

Chapter 1 Device Overview

1.1.2 Modes of Operation

User modes (expanded modes are only available in the 80-pin package version).

• Normal and emulation operating modes:

— Normal single-chip mode

— Normal expanded wide mode

— Normal expanded narrow mode

— Emulation expanded wide mode

— Emulation expanded narrow mode

• Special operating modes:

— Special single-chip mode with active background debug mode

— Special test mode (Freescale use only)

— Special peripheral mode (Freescale use only)

• Low power modes:

— Stop mode

— Pseudo stop mode

— Wait mode

MC9S12C128 Data Sheet, Rev. 1.15

Freescale Semiconductor 21

Page 22

Chapter 1 Device Overview

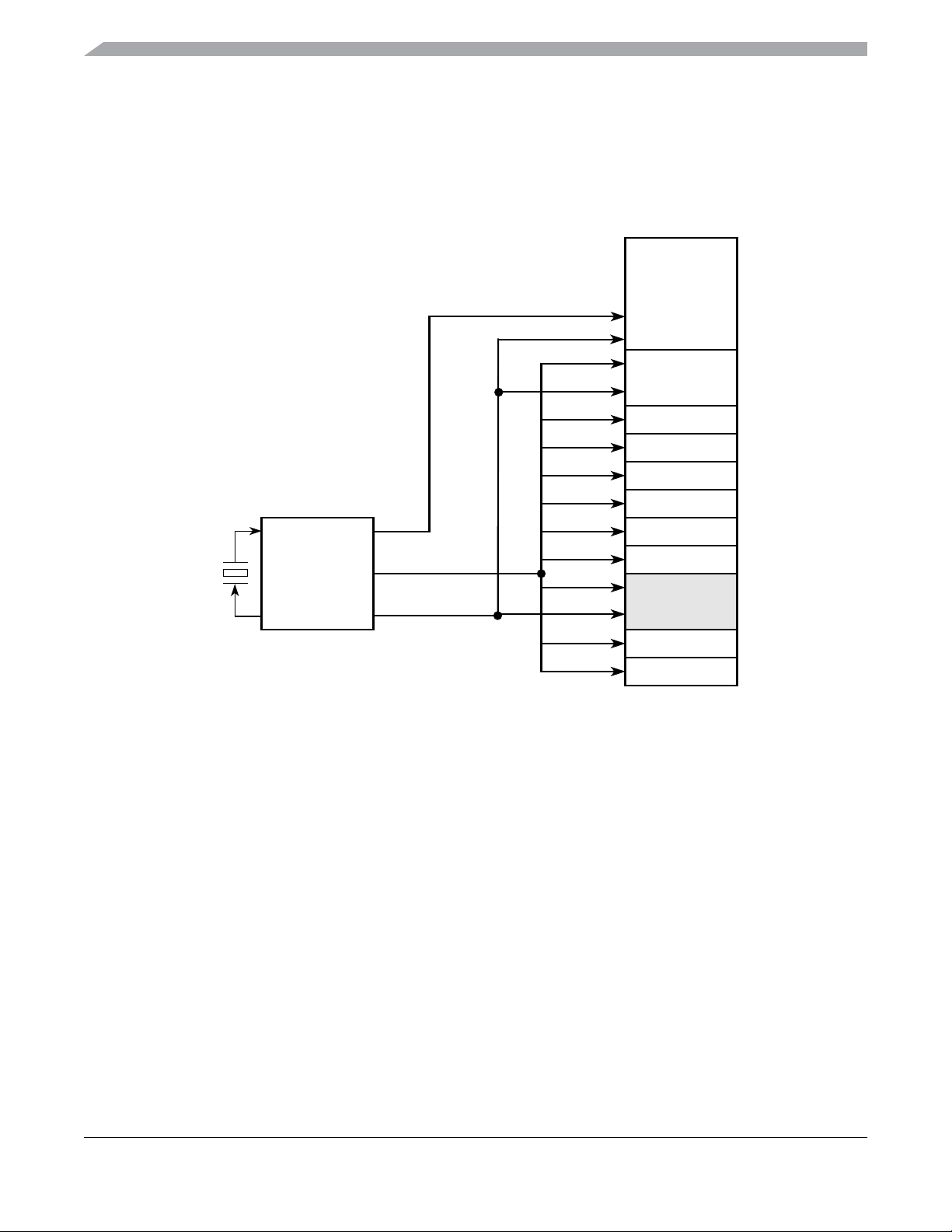

1.1.3 Block Diagram

V

V

V

BKGD

V

DDPLL

V

SSPLL

EXTAL

XTAL

RESET

TEST/V

V

V

V

V

V

XFC

PE0

PE1

PE2

PE3

PE4

PE5

PE6

PE7

SSR

DDR

DDX

SSX

DD2

SS2

DD1

SS1

V

DDA

V

SSA

V

RH

Voltage Regulator

V

RL

AN0

ATD

16K, 32K, 64K, 96K, 128K Byte Flash

AN1

AN2

AN3

AN4

AN5

AN6

AN7

MUX

MODC

PLL

PTE

1K, 2K, 4K Byte RAM

Background

Debug12 Module

Clock and

Reset

Generation

Module

XIRQ

IRQ

R/W

LSTRB/TAGLO

ECLK

DDRE

MODA/IPIPE0

HCS12

CPU

COP Watchdog

Clock Monitor

Periodic Interrupt

System

Integration

Module

(SIM)

Timer

Module

PWM

Module

IOC0

IOC1

IOC2

IOC3

IOC4

IOC5

IOC6

IOC7

PW0

PW1

PW2

PW3

PW4

PW5

MODB/IPIPE1

NOACC/XCLKS

PP

Keypad Interrupt

Key Int

Multiplexed Address/Data Bus

DDRA DDRB

PTA PTB

SCI

MSCAN is not available on the

9S12GC Family Members

MSCAN

RXD

TXD

RXCAN

TXCAN

MISO

PA4

PA3

PA 2

PA 1

PA7

PA6

PA5

PA 0

PB7

PB6

PB5

PB4

PB3

PB2

PB1

PB0

SPI

SS

MOSI

SCK

PTAD

DDRAD

PTT

DDRT

PTP

DDRP

PTJ

DDRJ

PTS

DDRS

PTM

DDRM

V

DDA

V

SSA

V

RH

V

RL

PAD0

PAD1

PAD2

PAD3

PAD4

PAD5

PAD6

PAD7

PT0

PT1

PT2

PT3

PT4

PT5

PT6

PT7

PP0

PP1

PP2

PP3

PP4

PP5

PP6

PP7

PJ6

PJ7

PS0

PS1

PS2

PS3

PM0

PM1

PM2

PM3

PM4

PM5

ADDR12

ADDR11

ADDR10

ADDR9

ADDR8

DATA11

DATA1 0

DATA9

DATA8

ADDR7

ADDR6

ADDR5

DATA4

DATA7

DATA6

DATA5

I/O Driver 5V

V

DDX

V

SSX

ADDR4

ADDR3

DATA3

ADDR2

ADDR1

DATA2

DATA1

ADDR0

Signals shown in Bold are not available on the 52 or 48 Pin Package

DATA0

Signals shown in Bold Italic are available in the 52, but not the 48 Pin Package

Voltage Regulator 5V & I/O

V

DDR

V

SSR

A/D Converter 5V

V

DDA

V

SSA

VRL is bonded internally to V

for 52- and 48-Pin packages

SSA

Multiplexed

Wide Bus

ADDR15

ADDR14

ADDR13

DATA12

DATA15

DATA14

DATA13

Internal Logic 2.5V

V

DD1,2

V

SS1,2

PLL 2.5V

V

DDPLL

V

SSPLL

Figure 1-1. MC9S12C-Family Block Diagram

MC9S12C128 Data Sheet, Rev. 1.15

22 Freescale Semiconductor

Page 23

Chapter 1 Device Overview

1.2 Memory Map and Registers

1.2.1 Device Memory Map

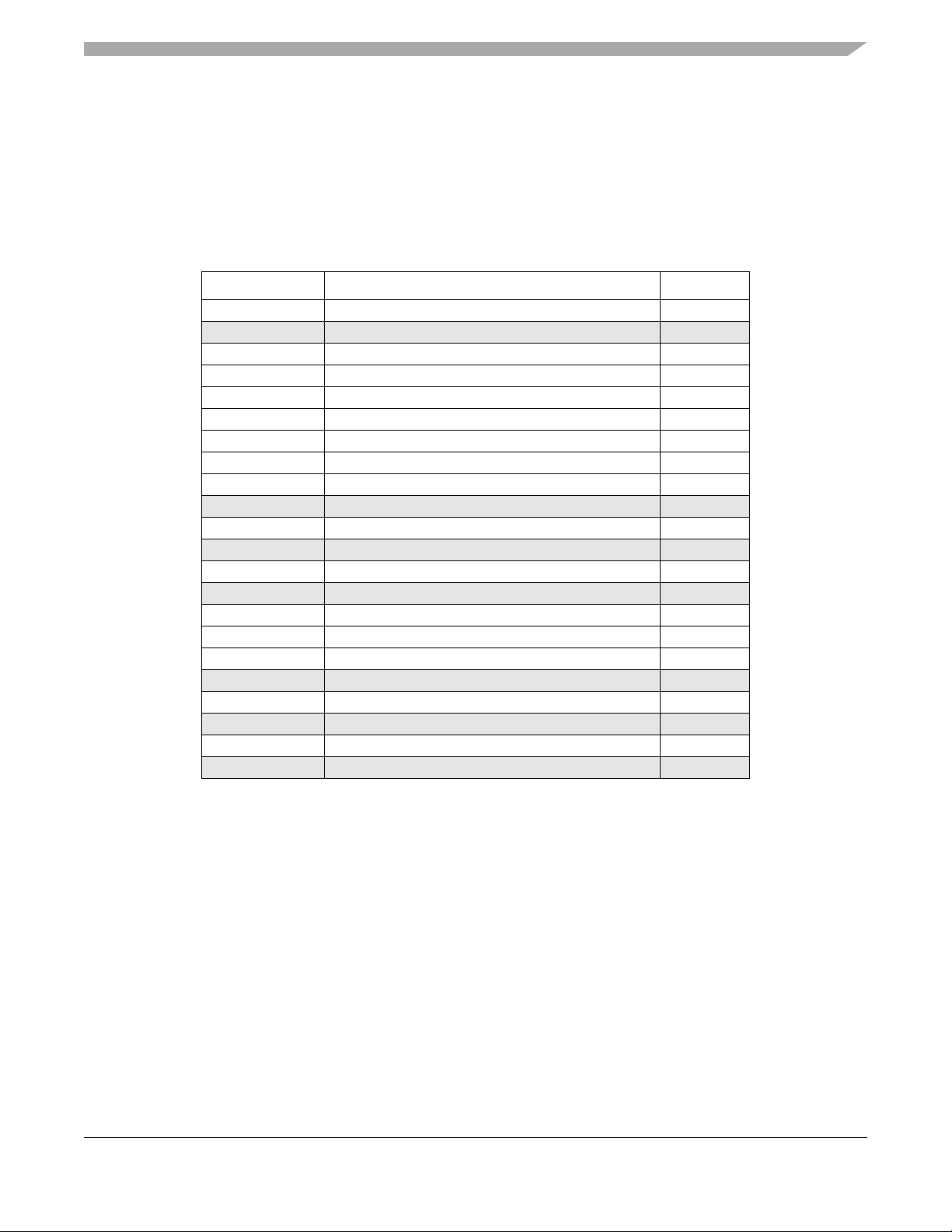

Table 1-1 shows the deviceregister map after reset. Figure 1-2through Figure 1-6 illustrate the full device

memory map.

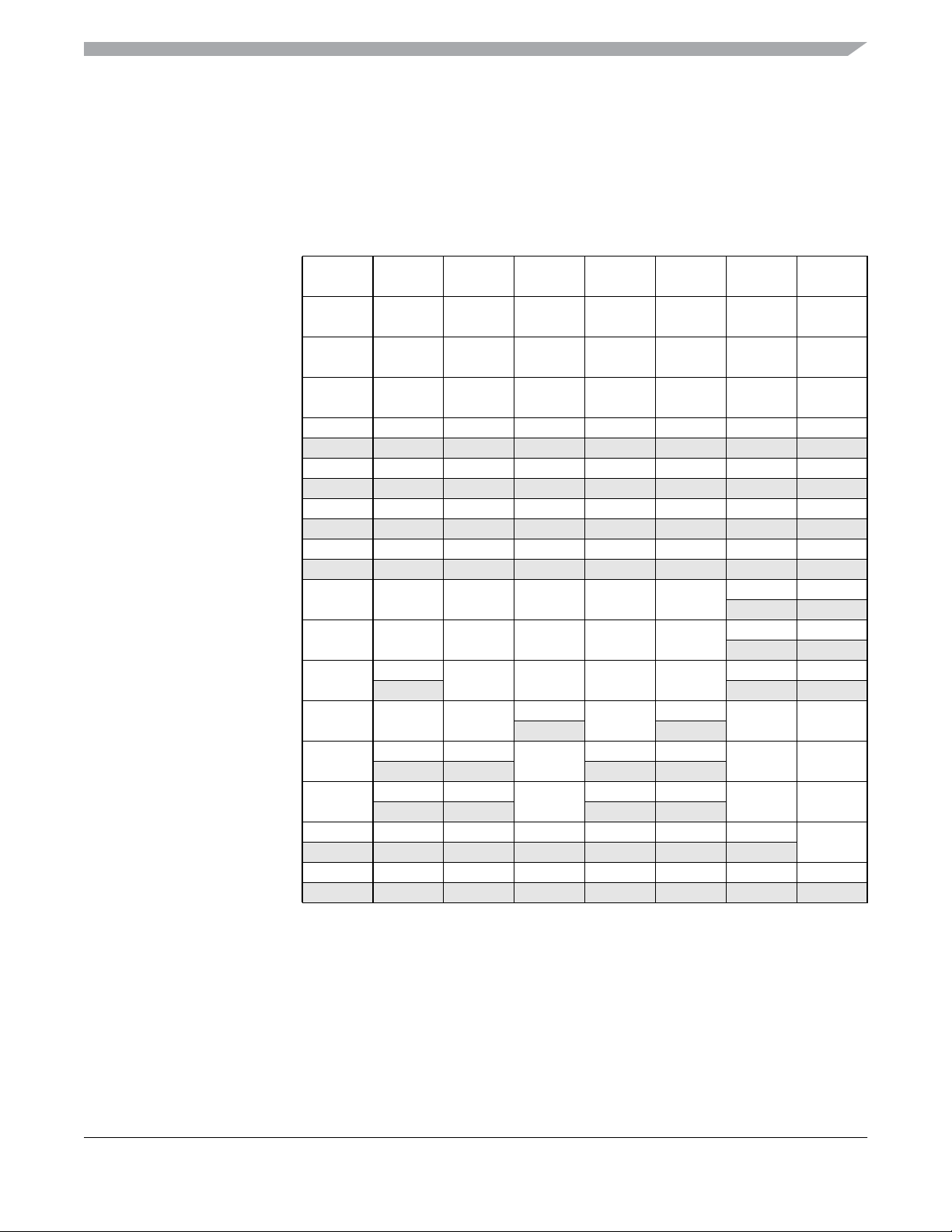

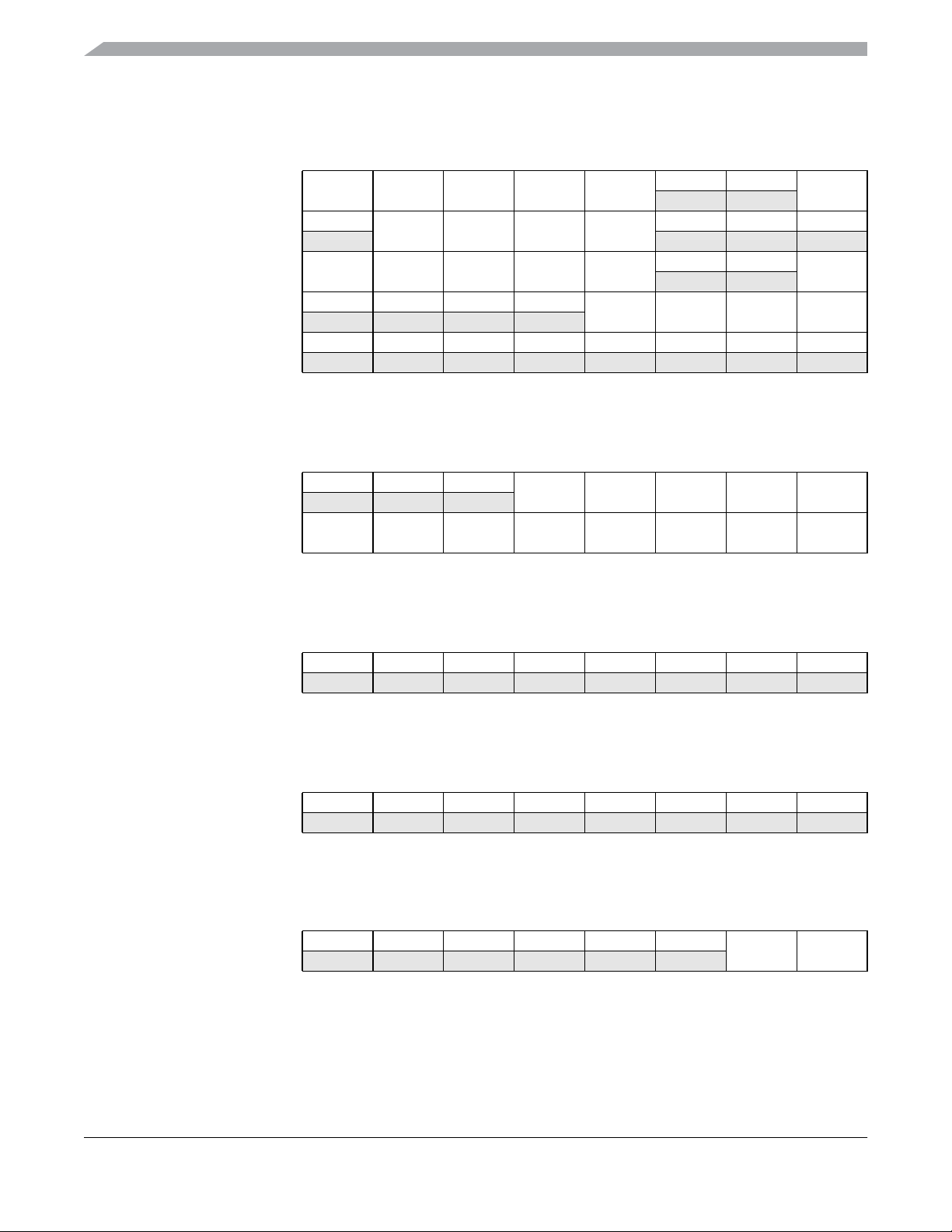

Table 1-1. Device Register Map Overview

Address Module Size

0x0000–0x0017 Core (ports A, B, E, modes, inits, test) 24

0x0018 Reserved 1

0x0019 Voltage regulator (VREG) 1

0x001A–0x001B Device ID register 2

0x001C–0x001F Core (MEMSIZ, IRQ, HPRIO) 4

0x0020–0x002F Core (DBG) 16

0x0030–0x0033 Core (PPAGE

0x0034–0x003F Clock and reset generator (CRG) 12

0x0040–0x006F Standard timer module (TIM) 48

0x0070–0x007F Reserved 16

0x0080–0x009F Analog-to-digital converter (ATD) 32

0x00A0–0x00C7 Reserved 40

0x00C8–0x00CF Serial communications interface (SCI) 8

0x00D0–0x00D7 Reserved 8

0x00D8–0x00DF Serial peripheral interface (SPI) 8

0x00E0–0x00FF Pulse width modulator (PWM) 32

0x0100–0x010F Flash control register 16

0x0110–0x013F Reserved 48

0x0140–0x017F Scalable controller area network (MSCAN)

0x0180–0x023F Reserved 192

0x0240–0x027F Port integration module (PIM) 64

0x0280–0x03FF Reserved 384

1. External memory paging is not supported on this device (Section 1.7.1, “PPAGE”).

2. Not available on MC9S12GC Family devices

(1)

)

(2)

4

64

MC9S12C128 Data Sheet, Rev. 1.15

Freescale Semiconductor 23

Page 24

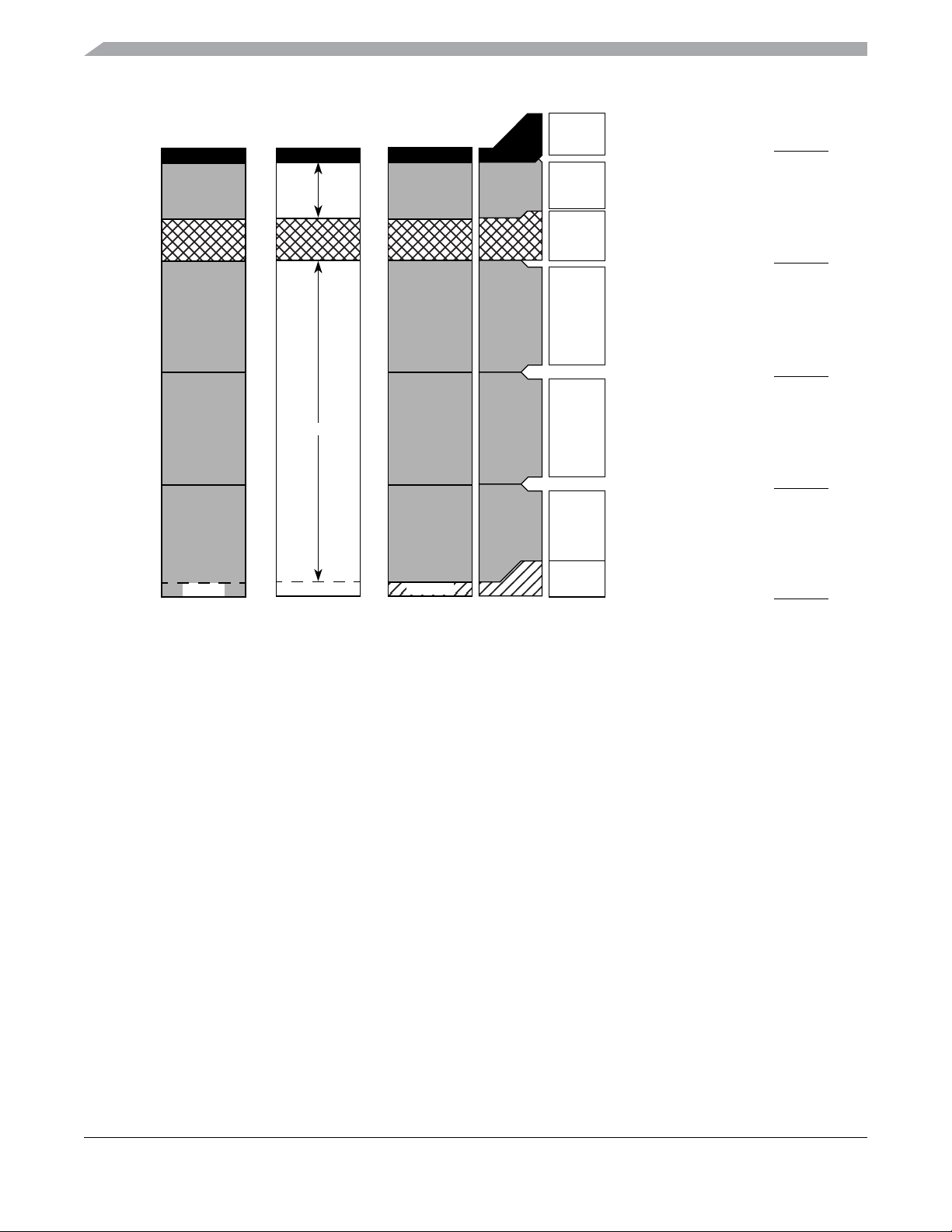

Chapter 1 Device Overview

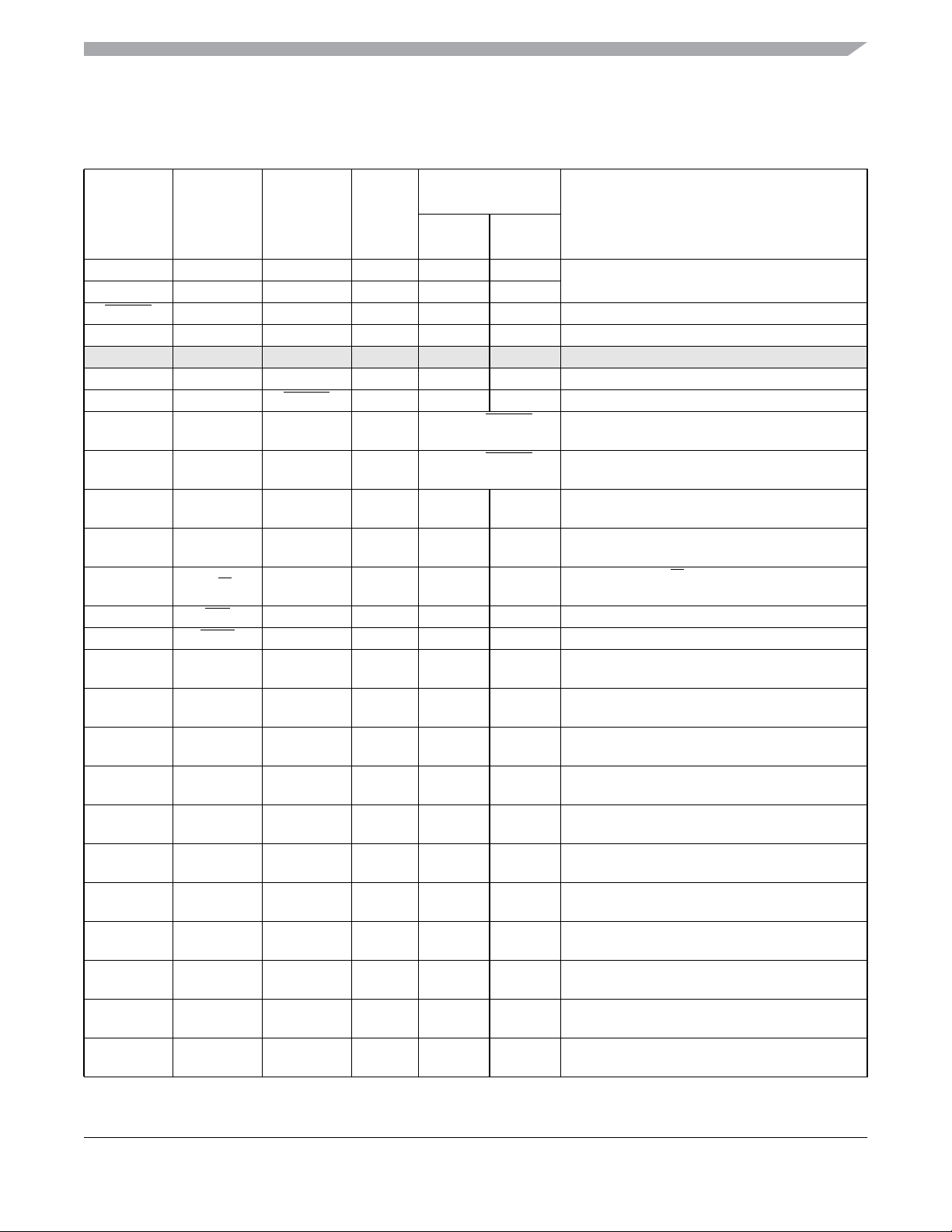

0x0000

0x0400

0x3000

0x4000

0x8000

EXT

0xC000

0xFF00

0xFFFF

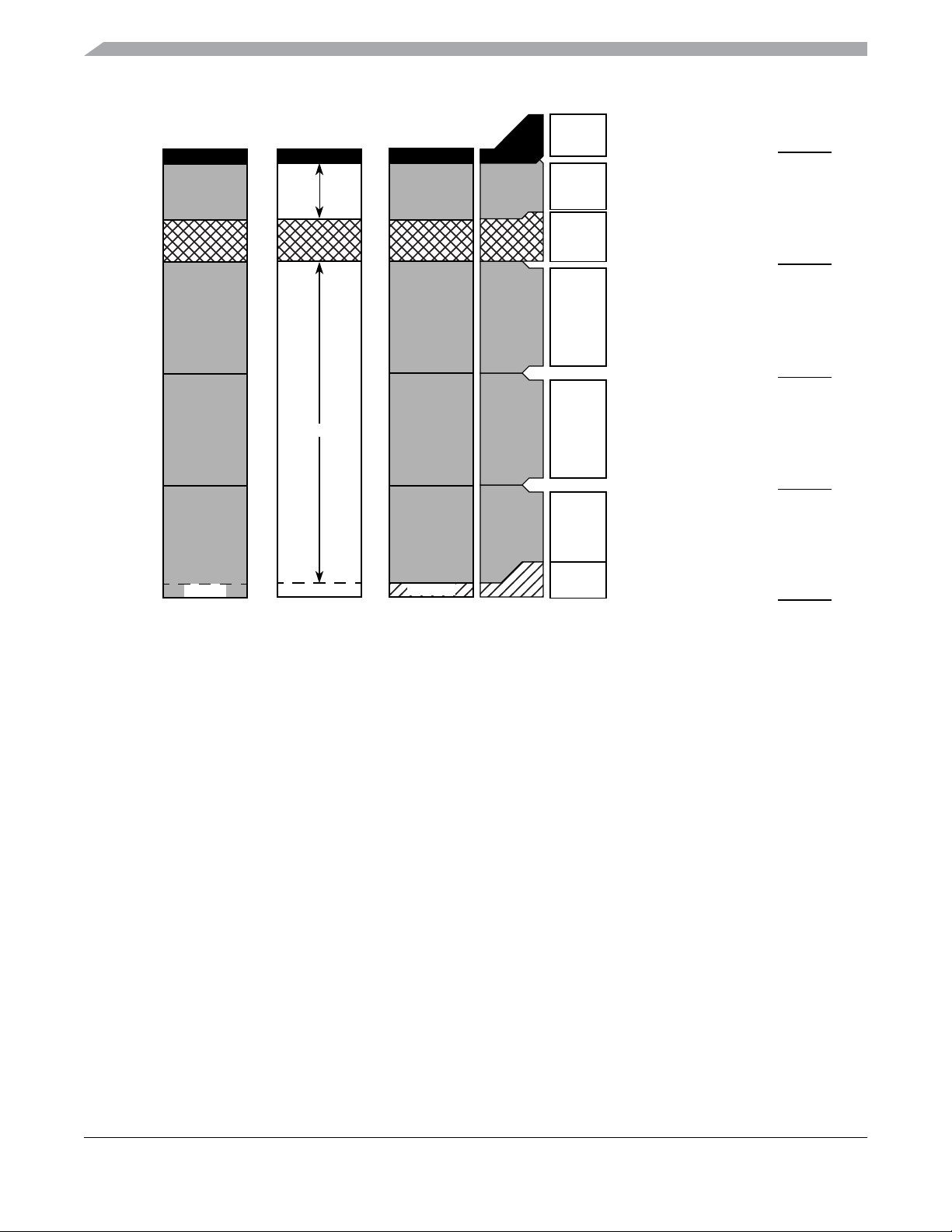

The figure shows a useful map, which is not the map out of reset. After reset the map is:

0x0000–0x03FF: Register Space

0x0000–0x0FFF: 4K RAM (only 3K visible 0x0400–0x0FFF)

Flash erase sector size is 1024 bytes

VECTORS

NORMAL

SINGLE CHIP

VECTORS

EXPANDED SPECIAL

VECTORS

SINGLE CHIP

Figure 1-2. MC9S12C128 and MC9S12GC128 User Configurable Memory Map

0x0000

0x03FF

0x0000

0x3FFF

0x3000

0x3FFF

0x4000

0x7FFF

0x8000

0xBFFF

0xC000

0xFFFF

0xFF00

0xFFFF

1K Register Space

Mappable to any 2K Boundary

16K Fixed Flash EEPROM

4K Bytes RAM

Mappable to any 4K Boundary

16K Fixed Flash EEPROM

16K Page Window

8 * 16K Flash EEPROM Pages

16K Fixed Flash EEPROM

BDM

(If Active)

PAGE MAP

0x003D

0x003E

PPAGE

0x003F

MC9S12C128 Data Sheet, Rev. 1.15

24 Freescale Semiconductor

Page 25

Chapter 1 Device Overview

0x0000

0x0400

0x3000

0x4000

0x8000

EXT

0xC000

0xFF00

0xFFFF

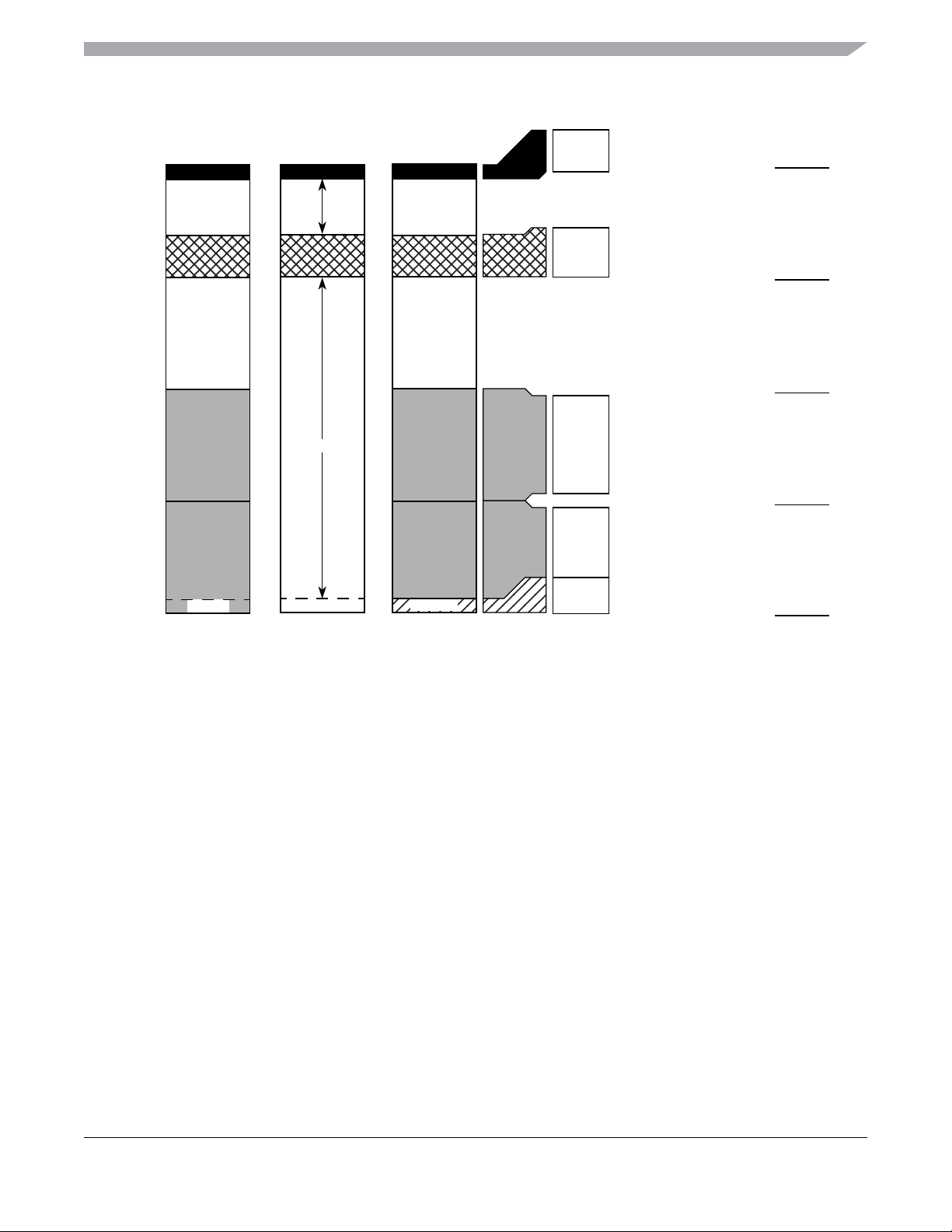

The figure shows a useful map, which is not the map out of reset. After reset the map is:

Flash erase sector size is 1024 bytes

VECTORS

NORMAL

SINGLE CHIP

0x0000–0x03FF: Register Space

0x0000–0x0FFF: 4K RAM (only 3K visible 0x0400–0x0FFF)

VECTORS

EXPANDED SPECIAL

VECTORS

SINGLE CHIP

Figure 1-3. MC9S12C96 and MC9S12GC96 User Configurable Memory Map

0x0000

0x03FF

0x0000

0x3FFF

0x3000

0x3FFF

0x4000

0x7FFF

0x8000

0xBFFF

0xC000

0xFFFF

0xFF00

0xFFFF

1K Register Space

Mappable to any 2K Boundary

16K Fixed Flash EEPROM

4K Bytes RAM

Mappable to any 4K Boundary

16K Fixed Flash EEPROM

16K Page Window

6 * 16K Flash EEPROM Pages

16K Fixed Flash EEPROM

BDM

(If Active)

PAGE MAP

0x003D

0x003E

PPAGE

0x003F

MC9S12C128 Data Sheet, Rev. 1.15

Freescale Semiconductor 25

Page 26

Chapter 1 Device Overview

0x0000

0x0400

0x3000

0x4000

0x8000

EXT

0xC000

0xFF00

0xFFFF

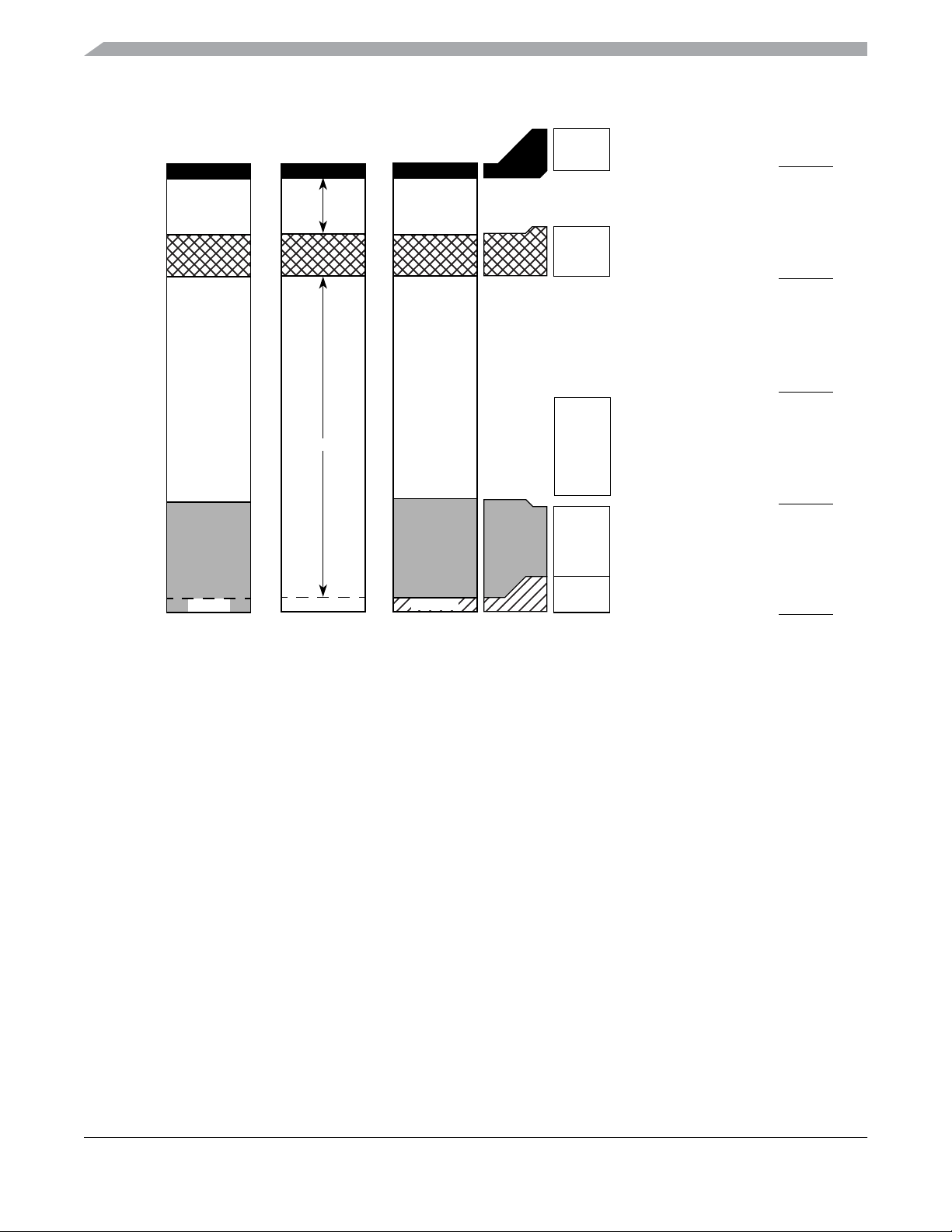

The figure shows a useful map, which is not the map out of reset. After reset the map is:

Flash erase sector size is 1024 Bytes

VECTORS

NORMAL

SINGLE CHIP

0x0000–0x03FF: Register space

0x0000–0x0FFF: 4K RAM (only 3K visible 0x0400–0x0FFF)

VECTORS

EXPANDED SPECIAL

VECTORS

SINGLE CHIP

0x0000

0x03FF

0x0000

0x3FFF

0x3000

0x3FFF

0x4000

0x7FFF

0x8000

0xBFFF

0xC000

0xFFFF

0xFF00

0xFFFF

1K Register Space

Mappable to any 2K Boundary

16K Fixed Flash EEPROM

4K Bytes RAM

Mappable to any 4K Boundary

16K Fixed Flash EEPROM

16K Page Window

4 * 16K Flash EEPROM Pages

16K Fixed Flash EEPROM

BDM

(If Active)

PAGE MAP

0x003D

0x003E

PPAGE

0x003F

Figure 1-4. MC9S12C64 and MC9S12GC64 User Configurable Memory Map

MC9S12C128 Data Sheet, Rev. 1.15

26 Freescale Semiconductor

Page 27

Chapter 1 Device Overview

0x0000

0x0400

0x3800

0x4000

0x8000

0xC000

0xFF00

0xFFFF

VECTORS

NORMAL

SINGLE CHIP

EXT

VECTORS

EXPANDED SPECIAL

VECTORS

SINGLE CHIP

0x0000

0x03FF

0x3800

0x3FFF

0x8000

0xBFFF

0xC000

0xFFFF

0xFF00

0xFFFF

1K Register Space

Mappable to any 2K Boundary

2K Bytes RAM

Mappable to any 2K Boundary

16K Page Window

2 * 16K Flash EEPROM Pages

16K Fixed Flash EEPROM

BDM

(If Active)

PAGE MAP

0x003E

PPAGE

0x003F

The figure shows a useful map, which is not the map out of reset. After reset the map is:

0x0000–0x03FF: Register space

0x0800–0x0FFF: 2K RAM

Flash erase sector size is 512 bytes

The flash page 0x003E is visible at 0x4000–0x7FFF in the memory map if ROMHM = 0.

In the figure ROMHM = 1 removing page 0x003E from 0x4000–0x7FFF.

Figure 1-5. MC9S12C32 and MC9S12GC32 User Configurable Memory Map

MC9S12C128 Data Sheet, Rev. 1.15

Freescale Semiconductor 27

Page 28

Chapter 1 Device Overview

0x0000

0x0400

0x3C00

0x4000

0x8000

EXT

0xC000

0xFF00

0xFFFF

The figure shows a useful map, which is not the map out of reset. After reset the map is:

VECTORS

NORMAL

SINGLE CHIP

0x0000–0x03FF: Register Space

0x0C00–0x0FFF: 1K RAM

VECTORS

EXPANDED SPECIAL

VECTORS

SINGLE CHIP

0x0000

0x03FF

0x3C00

0x3FFF

0x8000

0xBFFF

0xC000

0xFFFF

0xFF00

0xFFFF

1K Register Space

Mappable to any 2K Boundary

1K Bytes RAM

Mappable to any 2K Boundary

16K Page Window

16K Fixed Flash EEPROM

BDM

(If Active)

PAGE MAP

PPAGE

0x003F

The 16K flash array page 0x003F is also visible in the PPAGE window when PPAGE register contents are odd.

Flash Erase Sector Size is 512 Bytes

Figure 1-6. MC9S12GC16 User Configurable Memory Map

MC9S12C128 Data Sheet, Rev. 1.15

28 Freescale Semiconductor

Page 29

Chapter 1 Device Overview

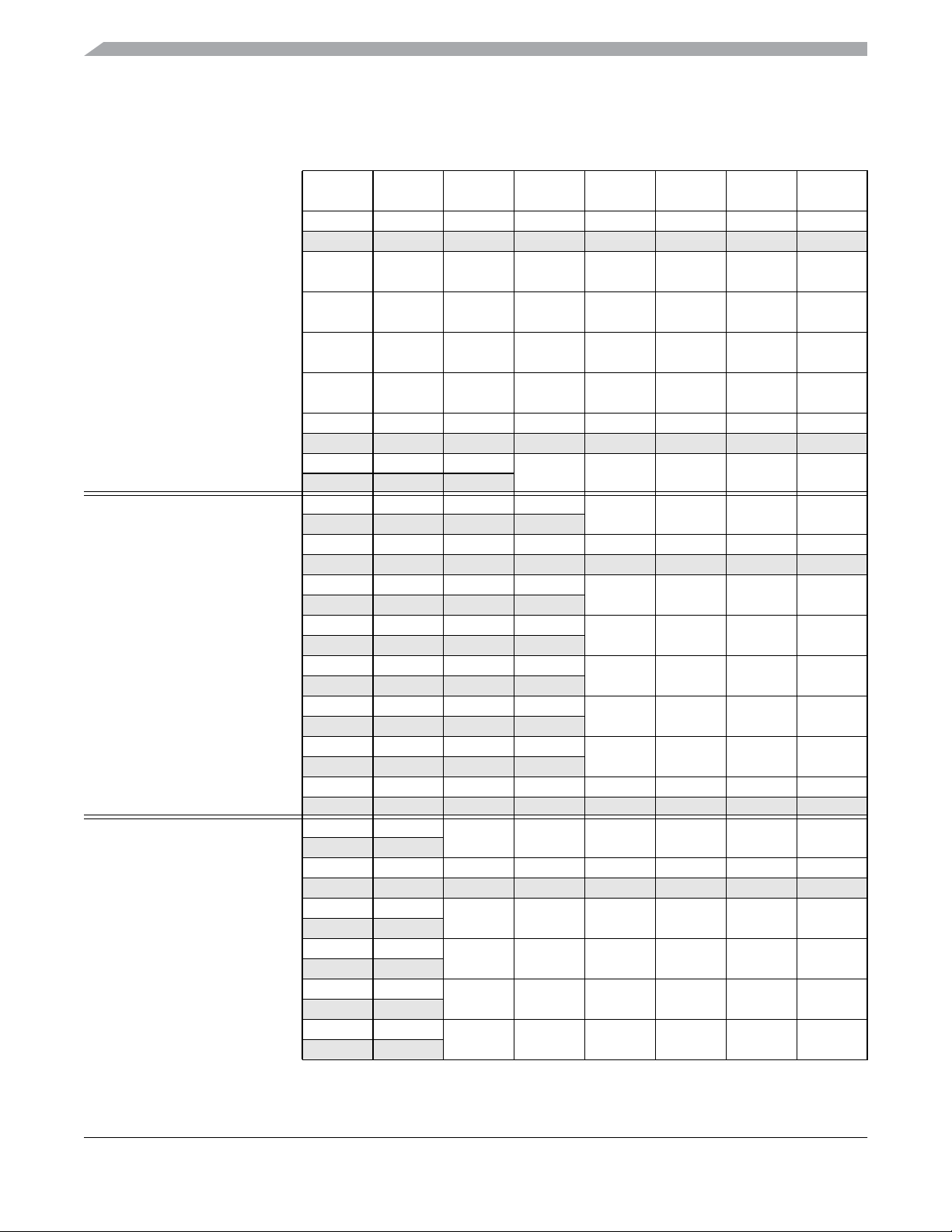

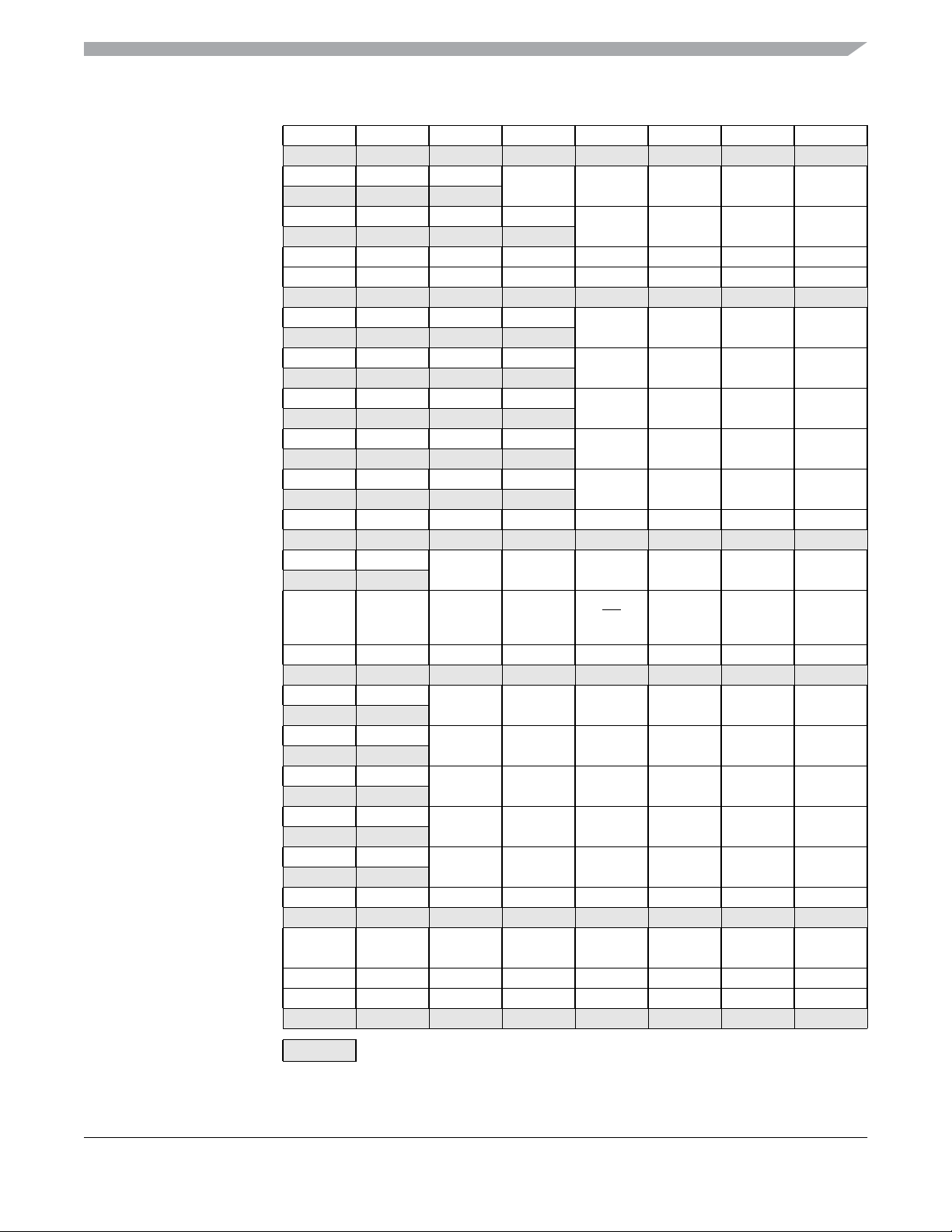

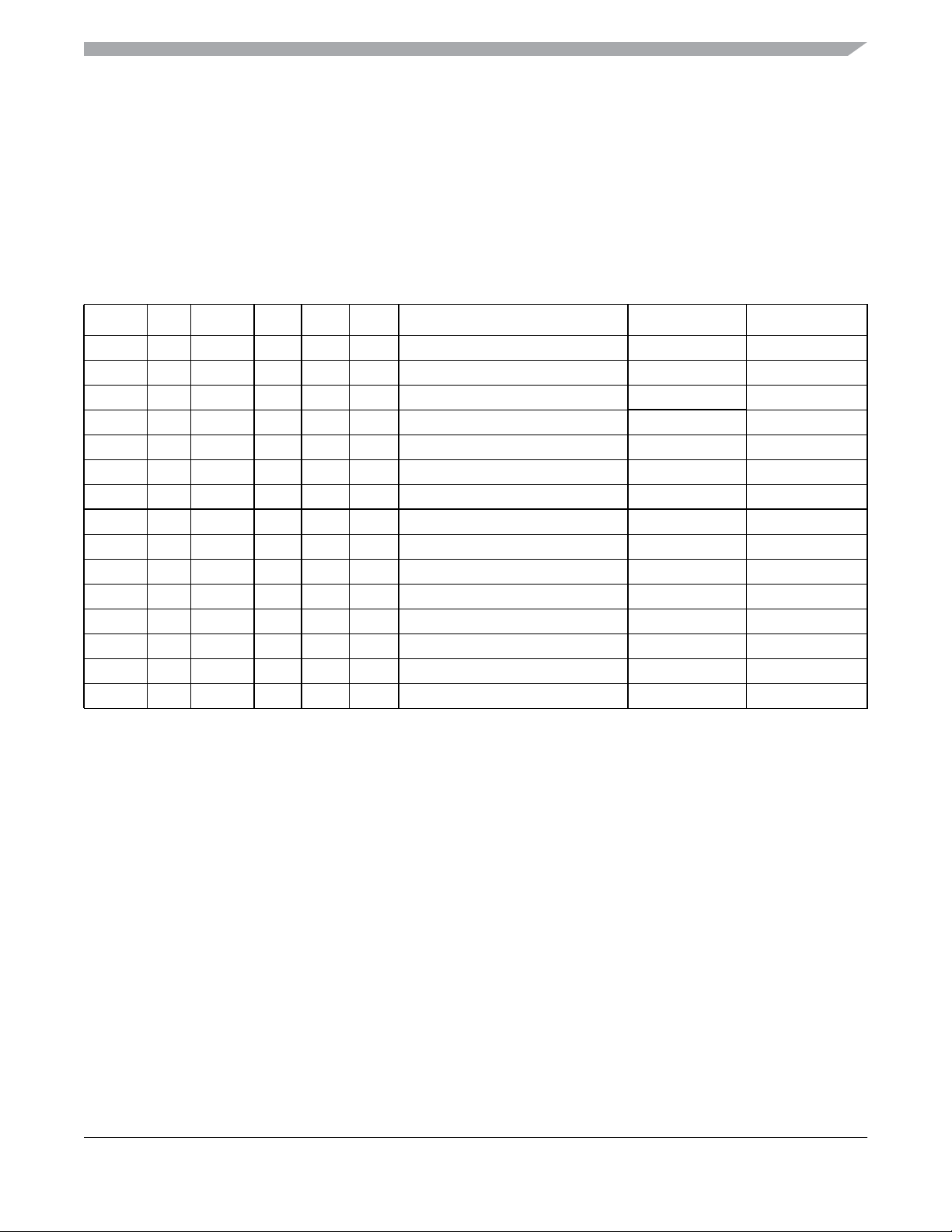

1.2.2 Detailed Register Map

The detailed register map of the MC9S12C Family

is listed in address order below.

0x0000–0x000F MEBI Map 1 of 3 (HCS12 Multiplexed External Bus Interface)

Address Name Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

0x0000 PORTA

0x0001 PORTB

0x0002 DDRA

0x0003 DDRB

0x0004 Reserved

0x0005 Reserved

0x0006 Reserved

0x0007 Reserved

0x0008 PORTE

0x0009 DDRE

0x000A PEAR

0x000B MODE

0x000C PUCR

0x000D RDRIV

0x000E EBICTL

0x000F Reserved

Read:

Write:

Read:

Write:

Read:

Write:

Read:

Write:

Read: 0 0 0 0 0 0 0 0

Write:

Read: 0 0 0 0 0 0 0 0

Write:

Read: 0 0 0 0 0 0 0 0

Write:

Read: 0 0 0 0 0 0 0 0

Write:

Read:

Write:

Read:

Write:

Read:

Write:

Read:

Write:

Read:

Write:

Read:

Write:

Read: 0 0 0 0 0 0 0

Write:

Read: 0 0 0 0 0 0 0 0

Write:

Bit 7 6 5 4 3 2 1 Bit 0

Bit 7 6 5 4 3 2 1 Bit 0

Bit 7 6 5 4 3 2 1 Bit 0

Bit 7 6 5 4 3 2 1 Bit 0