Page 1

MC9S12E128

MC9S12E64

MC9S12E32

Data Sheet

HCS12

Microcontrollers

MC9S12E128V1

Rev. 1.07

10/2005

freescale.com

Page 2

Page 3

MC9S12E128 Data Sheet

covers

MC9S12E64 & MC9S12E32

MC9S12E128V1

Rev. 1.07

10/2005

Page 4

To provide the most up-to-date information, the revision of our documents on the World Wide Web will be

the most current. Your printed copy may be an earlier revision. To verify you have the latest information

available, refer to:

http://freescale.com/

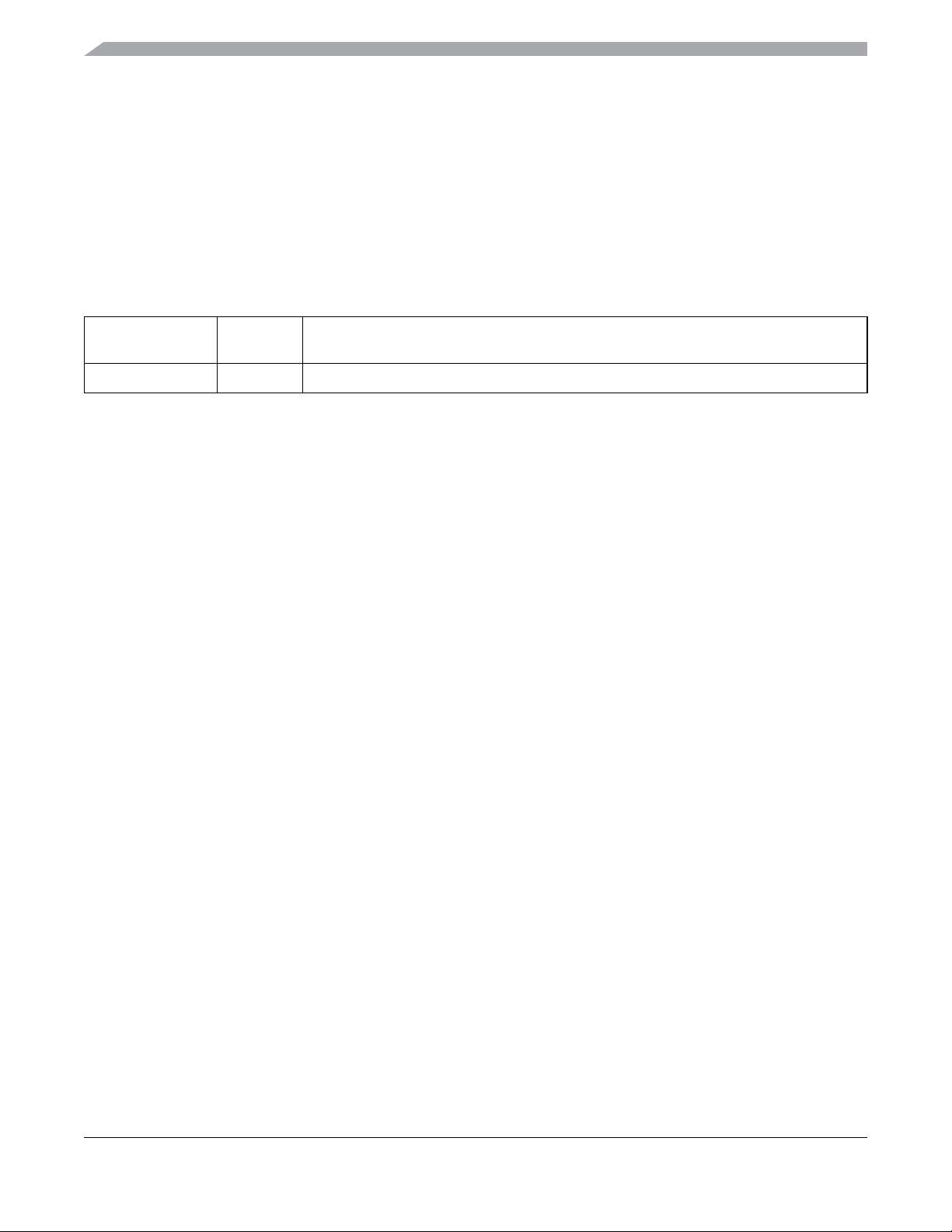

The following revision history table summarizes changes contained in this document.

Revision History

Date

October 10, 2005 01.07 New Data Sheet

Revision

Level

Description

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc.

This product incorporates SuperFlash® technology licensed from SST.

© Freescale Semiconductor, Inc., 2005. All rights reserved.

MC9S12E128 Data Sheet, Rev. 1.07

4 Freescale Semiconductor

Page 5

Chapter 1 MC9S12E128 Device Overview (MC9S12E128DGV1) . . . . . . .21

Chapter 2 128 Kbyte Flash Module (FTS128K1V1) . . . . . . . . . . . . . . . . . .85

Chapter 3 Port Integration Module (PIM9E128V1). . . . . . . . . . . . . . . . . .119

Chapter 4 Clocks and Reset Generator (CRGV4) . . . . . . . . . . . . . . . . . .165

Chapter 5 Oscillator (OSCV2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .201

Chapter 6 Analog-to-Digital Converter (ATD10B16CV2) . . . . . . . . . . . .205

Chapter 7 Digital-to-Analog Converter (DAC8B1CV1) . . . . . . . . . . . . . .237

Chapter 8 Serial Communication Interface (SCIV3) . . . . . . . . . . . . . . . .245

Chapter 9 Serial Peripheral Interface (SPIV3) . . . . . . . . . . . . . . . . . . . . .277

Chapter 10 Inter-Integrated Circuit (IICV2) . . . . . . . . . . . . . . . . . . . . . . . .299

Chapter 11 Pulse Width Modulator w/ Fault Protection (PMF15B6CV2).323

Chapter 12 Pulse-Width Modulator (PWM8B6CV1). . . . . . . . . . . . . . . . . .381

Chapter 13 Timer Module (TIM16B4CV1). . . . . . . . . . . . . . . . . . . . . . . . . .415

Chapter 14 Dual Output Voltage Regulator (VREG3V3V2). . . . . . . . . . . .439

Chapter 15 Background Debug Module (BDMV4). . . . . . . . . . . . . . . . . . .447

Chapter 16 Debug Module (DBGV1). . . . . . . . . . . . . . . . . . . . . . . . . . . . . .473

Chapter 17 Interrupt (INTV1). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .505

Chapter 18 Multiplexed External Bus Interface (MEBIV3) . . . . . . . . . . . .513

Chapter 19 Module Mapping Control (MMCV4). . . . . . . . . . . . . . . . . . . . .543

Appendix A Electrical Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . .563

Appendix B Package Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .599

Appendix C Ordering Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .602

MC9S12E128 Data Sheet, Rev. 1.07

Freescale Semiconductor 5

Page 6

MC9S12E128 Data Sheet, Rev. 1.07

6 Freescale Semiconductor

Page 7

Chapter 1

MC9S12E128 Device Overview (MC9S12E128DGV1)

1.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

1.1.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

1.1.2 Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .23

1.1.3 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

1.2 Device Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

1.2.1 Detailed Register Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

1.2.2 Part ID Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .58

1.3 Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

1.3.1 Device Pinout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

1.3.2 Signal Properties Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

1.4 Detailed Signal Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

1.4.1 EXTAL, XTAL — Oscillator Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

1.4.2 RESET — External Reset Pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

1.4.3 TEST — Test Pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .64

1.4.4 XFC — PLL Loop Filter Pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

1.4.5 BKGD / TAGHI / MODC — Background Debug, Tag High & Mode Pin . . . . . . . . . . . 64

1.4.6 PA[7:0] / ADDR[15:8] / DATA[15:8] — Port A I/O Pins . . . . . . . . . . . . . . . . . . . . . . . . 64

1.4.7 PB[7:0] / ADDR[7:0] / DATA[7:0] — Port B I/O Pins . . . . . . . . . . . . . . . . . . . . . . . . . . 64

1.4.8 PE7 / NOACC / XCLKS — Port E I/O Pin 7 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

1.4.9 PE6 / MODB / IPIPE1 — Port E I/O Pin 6 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

1.4.10 PE5 / MODA / IPIPE0 — Port E I/O Pin 5 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

1.4.11 PE4 / ECLK— Port E I/O Pin 4 / E-Clock Output . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

1.4.12 PE3 / LSTRB / TAGLO — Port E I/O Pin 3 / Low-Byte Strobe (LSTRB) . . . . . . . . . . . 66

1.4.13 PE2 / R/W — Port E I/O Pin 2 / Read/Write . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

1.4.14 PE1 / IRQ — Port E input Pin 1 / Maskable Interrupt Pin . . . . . . . . . . . . . . . . . . . . . . . 66

1.4.15 PE0 / XIRQ — Port E input Pin 0 / Non Maskable Interrupt Pin . . . . . . . . . . . . . . . . . . 67

1.4.16 PK7 / ECS / ROMCTL — Port K I/O Pin 7 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

1.4.17 PK6 / XCS — Port K I/O Pin 6 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

1.4.18 PK[5:0] / XADDR[19:14] — Port K I/O Pins [5:0] . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

1.4.19 PAD[15:0] / AN[15:0] / KWAD[15:0] — Port AD I/O Pins [15:0] . . . . . . . . . . . . . . . . 67

1.4.20 PM7 / SCL — Port M I/O Pin 7 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

1.4.21 PM6 / SDA — Port M I/O Pin 6 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

1.4.22 PM5 / TXD2 — Port M I/O Pin 5 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

1.4.23 PM4 / RXD2 — Port M I/O Pin 4 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

1.4.24 PM3 — Port M I/O Pin 3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

1.4.25 PM1 / DAO1 — Port M I/O Pin 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

1.4.26 PM0 / DAO2 — Port M I/O Pin 0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

1.4.27 PP[5:0] / PW0[5:0] — Port P I/O Pins [5:0] . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

MC9S12E128 Data Sheet, Rev. 1.07

Freescale Semiconductor 7

Page 8

1.4.28 PQ[6:4] / IS[2:0] — Port Q I/O Pins [6:4] . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

1.4.29 PQ[3:0] / FAULT[3:0] — Port Q I/O Pins [3:0] . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

1.4.30 PS7 / SS — Port S I/O Pin 7 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

1.4.31 PS6 / SCK — Port S I/O Pin 6 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

1.4.32 PS5 / MOSI — Port S I/O Pin 5 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

1.4.33 PS4 / MISO — Port S I/O Pin 4 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

1.4.34 PS3 / TXD1 — Port S I/O Pin 3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

1.4.35 PS2 / RXD1 — Port S I/O Pin 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

1.4.36 PS1 / TXD0 — Port S I/O Pin 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

1.4.37 PS0 / RXD0 — Port S I/O Pin 0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

1.4.38 PT[7:4] / IOC1[7:4]— Port T I/O Pins [7:4] . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

1.4.39 PT[3:0] / IOC0[7:4]— Port T I/O Pins [3:0] . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

1.4.40 PU[7:6] — Port U I/O Pins [7:6] . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

1.4.41 PU[5:4] / PW1[5:4] — Port U I/O Pins [5:4] . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

1.4.42 PU[3:0] / IOC2[7:4]/PW1[3:0] — Port U I/O Pins [3:0] . . . . . . . . . . . . . . . . . . . . . . . . 71

1.4.43 VDDX,VSSX — Power & Ground Pins for I/O Drivers . . . . . . . . . . . . . . . . . . . . . . . . . 72

1.4.44 VDDR, VSSR — Power Supply Pins for I/O Drivers & for Internal Voltage Regulator 72

1.4.45 VDD1, VDD2, VSS1, VSS2 — Power Supply Pins for Internal Logic . . . . . . . . . . . . . 72

1.4.46 VDDA, VSSA — Power Supply Pins for ATD and VREG . . . . . . . . . . . . . . . . . . . . . . 72

1.4.47 VRH, VRL — ATD Reference Voltage Input Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

1.4.48 VDDPLL, VSSPLL — Power Supply Pins for PLL . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

1.5 System Clock Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

1.6 Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

1.6.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

1.6.2 Chip Configuration Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

1.7 Security . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

1.7.1 Securing the Microcontroller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

1.7.2 Operation of the Secured Microcontroller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

1.7.3 Unsecuring the Microcontroller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

1.8 Low Power Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

1.8.1 Stop . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

1.8.2 Pseudo Stop . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

1.8.3 Wait . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

1.8.4 Run . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

1.9 Resets and Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

1.9.1 Vectors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

1.9.2 Resets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

1.10 Recommended Printed Circuit Board Layout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

MC9S12E128 Data Sheet, Rev. 1.07

8 Freescale Semiconductor

Page 9

Chapter 2

128 Kbyte Flash Module (FTS128K1V1)

2.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

2.1.1 Glossary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

2.1.2 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

2.1.3 Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .86

2.1.4 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86

2.2 External Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86

2.3 Memory Map and Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

2.3.1 Module Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

2.3.2 Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .90

2.4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

2.4.1 Flash Command Operations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

2.4.2 Operating Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 116

2.4.3 Flash Module Security . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 116

2.4.4 Flash Reset Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 118

2.4.5 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 118

Chapter 3

Port Integration Module (PIM9E128V1)

3.1 lntroduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 119

3.1.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 119

3.1.2 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 120

3.2 External Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 121

3.3 Memory Map and Register Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 127

3.3.1 Port AD . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 128

3.3.2 Port M . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 137

3.3.3 Port P . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 142

3.3.4 Port Q . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 145

3.3.5 Port S . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 148

3.3.6 Port T . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 152

3.3.7 Port U . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 155

3.4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 159

3.4.1 I/O Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 159

3.4.2 Input Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 159

3.4.3 Data Direction Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 159

3.4.4 Reduced Drive Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 160

3.4.5 Pull Device Enable Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 160

3.4.6 Polarity Select Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 161

3.4.7 Pin Configuration Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 161

3.5 Resets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 162

3.5.1 Reset Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 162

3.6 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 163

3.6.1 General . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 163

MC9S12E128 Data Sheet, Rev. 1.07

Freescale Semiconductor 9

Page 10

3.6.2 Interrupt Sources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 164

3.6.3 Operation in Stop Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 164

Chapter 4

Clocks and Reset Generator (CRGV4)

4.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 165

4.1.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 165

4.1.2 Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 166

4.1.3 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 166

4.2 External Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 167

4.2.1 V

DDPLL

, V

SSPLL

4.2.2 XFC — PLL Loop Filter Pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 167

4.2.3

RESET — Reset Pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 168

4.3 Memory Map and Register Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 168

4.3.1 Module Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 168

4.3.2 Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 169

4.4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 180

4.4.1 Phase Locked Loop (PLL) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 180

4.4.2 System Clocks Generator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 183

4.4.3 Clock Monitor (CM) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 184

4.4.4 Clock Quality Checker . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 184

4.4.5 Computer Operating Properly Watchdog (COP) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 186

4.4.6 Real-Time Interrupt (RTI) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 187

4.4.7 Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 187

4.4.8 Low-Power Operation in Run Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 188

4.4.9 Low-Power Operation in Wait Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 188

4.4.10 Low-Power Operation in Stop Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 192

4.5 Resets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 196

4.5.1 Clock Monitor Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 198

4.5.2 Computer Operating Properly Watchdog (COP) Reset . . . . . . . . . . . . . . . . . . . . . . . . . 198

4.5.3 Power-On Reset, Low Voltage Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 199

4.6 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 200

4.6.1 Real-Time Interrupt . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 200

4.6.2 PLL Lock Interrupt . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 200

4.6.3 Self-Clock Mode Interrupt . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 200

— PLL Operating Voltage, PLL Ground . . . . . . . . . . . . . . . . . . . . . . 167

MC9S12E128 Data Sheet, Rev. 1.07

10 Freescale Semiconductor

Page 11

Chapter 5

Oscillator (OSCV2)

5.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 201

5.1.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 201

5.1.2 Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 201

5.2 External Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 202

5.2.1 V

DDPLL

and V

SSPLL

— PLL Operating Voltage, PLL Ground . . . . . . . . . . . . . . . . . . . 202

5.2.2 EXTAL and XTAL — Clock/Crystal Source Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 202

5.2.3 XCLKS — Colpitts/Pierce Oscillator Selection Signal . . . . . . . . . . . . . . . . . . . . . . . . . 203

5.3 Memory Map and Register Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 204

5.4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 204

5.4.1 Amplitude Limitation Control (ALC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 204

5.4.2 Clock Monitor (CM) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 204

5.5 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 204

Chapter 6

Analog-to-Digital Converter (ATD10B16CV2)

6.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 205

6.1.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 205

6.1.2 Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 205

6.1.3 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 205

6.2 External Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 207

6.2.1 AN15/ETRIG — Analog Input Channel 15 / External trigger Pin . . . . . . . . . . . . . . . . 207

6.2.2 ANx (x = 14, 13, 12, 11, 10, 9, 8, 7, 6, 5, 4, 3, 2, 1, 0) — Analog Input Channel x Pins . .

207

6.2.3 V

6.2.4 V

6.3 Memory Map and Register Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 207

6.3.1 Module Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 207

6.3.2 Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 209

6.4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 230

6.4.1 Analog Sub-block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 230

6.4.2 Digital Sub-Block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 231

6.4.3 Operation in Low Power Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 232

6.5 Resets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 233

6.6 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 233

, VRL — High Reference Voltage Pin, Low Reference Voltage Pin . . . . . . . . . . . . 207

RH

DDA

, V

— Analog Circuitry Power Supply Pins . . . . . . . . . . . . . . . . . . . . . . . . . 207

SSA

MC9S12E128 Data Sheet, Rev. 1.07

Freescale Semiconductor 11

Page 12

Chapter 7

Digital-to-Analog Converter (DAC8B1CV1)

7.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 237

7.1.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 237

7.1.2 Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 237

7.1.3 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 237

7.2 External Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 238

7.2.1 DAO — DAC Channel Output . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 239

7.2.2 V

7.2.3 V

7.2.4 V

7.2.5 V

— DAC Power Supply . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 239

DDA

— DAC Ground Supply . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 239

SSA

— DAC Reference Supply . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 239

REF

— DAC Reference Ground Supply . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 239

RL

7.3 Memory Map and Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 239

7.3.1 Module Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 239

7.3.2 Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 240

7.4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 243

7.4.1 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 243

7.5 Resets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 244

7.5.1 General . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 244

Chapter 8

Serial Communication Interface (SCIV3)

8.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 245

8.1.1 Glossary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 245

8.1.2 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 245

8.1.3 Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 246

8.1.4 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 247

8.2 External Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 248

8.2.1 TXD — SCI Transmit Pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 248

8.2.2 RXD — SCI Receive Pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 248

8.3 Memory Map and Register Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 248

8.3.1 Module Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 248

8.3.2 Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 248

8.4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 258

8.4.1 Infrared Interface Submodule . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 259

8.4.2 Data Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 259

8.4.3 Baud Rate Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 261

8.4.4 Transmitter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 262

8.4.5 Receiver . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 265

8.4.6 Single-Wire Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 273

8.4.7 Loop Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 274

8.5 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 274

8.5.1 Description of Interrupt Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 274

8.5.2 Recovery from Wait Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 275

MC9S12E128 Data Sheet, Rev. 1.07

12 Freescale Semiconductor

Page 13

Chapter 9

Serial Peripheral Interface (SPIV3)

9.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 277

9.1.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 277

9.1.2 Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 277

9.1.3 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 278

9.2 External Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 278

9.2.1 MOSI — Master Out/Slave In Pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 278

9.2.2 MISO — Master In/Slave Out Pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 279

9.2.3

9.2.4 SCK — Serial Clock Pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 279

9.3 Memory Map and Register Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 279

9.3.1 Module Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 279

9.3.2 Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 280

9.4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 287

9.4.1 Master Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 288

9.4.2 Slave Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 289

9.4.3 Transmission Formats . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 290

9.4.4 SPI Baud Rate Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 293

9.4.5 Special Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 294

9.4.6 Error Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 295

9.4.7 Operation in Run Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 296

9.4.8 Operation in Wait Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 296

9.4.9 Operation in Stop Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 296

9.5 Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 297

9.6 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 297

9.6.1 MODF . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 297

9.6.2 SPIF . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 297

9.6.3 SPTEF . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 297

SS — Slave Select Pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 279

Chapter 10

Inter-Integrated Circuit (IICV2)

10.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 299

10.1.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 299

10.1.2 Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 300

10.1.3 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 300

10.2 External Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 301

10.2.1 IIC_SCL — Serial Clock Line Pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 301

10.2.2 IIC_SDA — Serial Data Line Pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 301

10.3 Memory Map and Register Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 301

10.3.1 Module Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 301

10.3.2 Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 302

10.4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 313

10.4.1 I-Bus Protocol . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 313

MC9S12E128 Data Sheet, Rev. 1.07

Freescale Semiconductor 13

Page 14

10.4.2 Operation in Run Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 316

10.4.3 Operation in Wait Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 316

10.4.4 Operation in Stop Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 316

10.5 Resets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 317

10.6 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 317

10.7 Initialization/Application Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 317

10.7.1 IIC Programming Examples . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 317

Chapter 11

Pulse Width Modulator with Fault Protection (PMF15B6CV2)

11.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 323

11.1.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 323

11.1.2 Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 324

11.1.3 Block Diagrams . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 324

11.2 External Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 326

11.2.1 PWM0–PWM5 Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 326

11.2.2 FAULT0–FAULT3 Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 326

11.2.3 IS0–IS2 Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 326

11.3 Memory Map and Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 327

11.3.1 Module Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 327

11.3.2 Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 330

11.4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 357

11.4.1 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 357

11.4.2 Prescaler . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 357

11.4.3 PWM Generator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 357

11.4.4 Independent or Complementary Channel Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . 361

11.4.5 Deadtime Generators . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 362

11.4.6 Software Output Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 370

11.4.7 PWM Generator Loading . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 373

11.4.8 Fault Protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 377

11.5 Resets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 379

11.6 Clocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 379

11.7 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 380

Chapter 12

Pulse-Width Modulator (PWM8B6CV1)

12.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 381

12.1.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 381

12.1.2 Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 381

12.1.3 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 382

12.2 External Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 382

12.2.1 PWM5 — Pulse Width Modulator Channel 5 Pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 382

12.2.2 PWM4 — Pulse Width Modulator Channel 4 Pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 382

12.2.3 PWM3 — Pulse Width Modulator Channel 3 Pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 382

MC9S12E128 Data Sheet, Rev. 1.07

14 Freescale Semiconductor

Page 15

12.2.4 PWM2 — Pulse Width Modulator Channel 2 Pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 383

12.2.5 PWM1 — Pulse Width Modulator Channel 1 Pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 383

12.2.6 PWM0 — Pulse Width Modulator Channel 0 Pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 383

12.3 Memory Map and Register Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 383

12.3.1 Module Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 383

12.3.2 Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 385

12.4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 403

12.4.1 PWM Clock Select . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 403

12.4.2 PWM Channel Timers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 406

12.5 Resets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 413

12.6 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 413

Chapter 13

Timer Module (TIM16B4CV1)

13.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 415

13.1.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 415

13.1.2 Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 415

13.1.3 Block Diagrams . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 416

13.2 External Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 418

13.2.1 IOC7 — Input Capture and Output Compare Channel 7 Pin . . . . . . . . . . . . . . . . . . . . 418

13.2.2 IOC6 — Input Capture and Output Compare Channel 6 Pin . . . . . . . . . . . . . . . . . . . . 418

13.2.3 IOC5 — Input Capture and Output Compare Channel 5 Pin . . . . . . . . . . . . . . . . . . . . 418

13.2.4 IOC4 — Input Capture and Output Compare Channel 4 Pin . . . . . . . . . . . . . . . . . . . . 418

13.3 Memory Map and Register Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 419

13.3.1 Module Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 419

13.3.2 Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 420

13.4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 435

13.4.1 Prescaler . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 436

13.4.2 Input Capture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 436

13.4.3 Output Compare . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 436

13.4.4 Pulse Accumulator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 436

13.4.5 Event Counter Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 437

13.4.6 Gated Time Accumulation Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 437

13.5 Resets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 437

13.6 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 438

13.6.1 Channel [7:4] Interrupt (C[7:4]F) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 438

13.6.2 Pulse Accumulator Input Interrupt (PAOVI) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 438

13.6.3 Pulse Accumulator Overflow Interrupt (PAOVF) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 438

13.6.4 Timer Overflow Interrupt (TOF) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 438

MC9S12E128 Data Sheet, Rev. 1.07

Freescale Semiconductor 15

Page 16

Chapter 14

Dual Output Voltage Regulator (VREG3V3V2)

14.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 439

14.1.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 439

14.1.2 Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 439

14.1.3 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 440

14.2 External Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 441

14.2.1 V

14.2.2 V

14.2.3 V

14.2.4 V

14.2.5 V

14.3 Memory Map and Register Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 442

14.3.1 Module Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 442

14.3.2 Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 443

14.4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 443

14.4.1 REG — Regulator Core . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 443

14.4.2 Full-Performance Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 444

14.4.3 Reduced-Power Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 444

14.4.4 LVD — Low-Voltage Detect . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 444

14.4.5 POR — Power-On Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 444

14.4.6 LVR — Low-Voltage Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 444

14.4.7 CTRL — Regulator Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 444

14.5 Resets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 445

14.5.1 Power-On Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 445

14.5.2 Low-Voltage Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 445

14.6 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 445

14.6.1 LVI — Low-Voltage Interrupt . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 445

— Regulator Power Input . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 441

DDR

, V

DDA

, VSS — Regulator Output1 (Core Logic) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 442

DD

DDPLL

REGEN

— Regulator Reference Supply . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 441

SSA

, V

— Regulator Output2 (PLL) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 442

SSPLL

— Optional Regulator Enable . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 442

Chapter 15

Background Debug Module (BDMV4)

15.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 447

15.1.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 447

15.1.2 Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 448

15.2 External Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 448

15.2.1 BKGD — Background Interface Pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 449

15.2.2

15.2.3

15.3 Memory Map and Register Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 450

15.3.1 Module Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 450

15.3.2 Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 451

15.4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 456

15.4.1 Security . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 456

15.4.2 Enabling and Activating BDM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 456

16 Freescale Semiconductor

TAGHI — High Byte Instruction Tagging Pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 449

TAGLO — Low Byte Instruction Tagging Pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 449

MC9S12E128 Data Sheet, Rev. 1.07

Page 17

15.4.3 BDM Hardware Commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 457

15.4.4 Standard BDM Firmware Commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 458

15.4.5 BDM Command Structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 459

15.4.6 BDM Serial Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 461

15.4.7 Serial Interface Hardware Handshake Protocol . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 464

15.4.8 Hardware Handshake Abort Procedure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 466

15.4.9 SYNC — Request Timed Reference Pulse . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 469

15.4.10Instruction Tracing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 469

15.4.11Instruction Tagging . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 470

15.4.12Serial Communication Time-Out . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 470

15.4.13Operation in Wait Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 471

15.4.14Operation in Stop Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 471

Chapter 16

Debug Module (DBGV1)

16.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 473

16.1.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 473

16.1.2 Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 475

16.1.3 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 475

16.2 External Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 477

16.3 Memory Map and Register Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 478

16.3.1 Module Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 478

16.3.2 Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 478

16.4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 493

16.4.1 DBG Operating in BKP Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 493

16.4.2 DBG Operating in DBG Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 495

16.4.3 Breakpoints . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 502

16.5 Resets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 503

16.6 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 503

Chapter 17

Interrupt (INTV1)

17.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 505

17.1.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 506

17.1.2 Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 506

17.2 External Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 507

17.3 Memory Map and Register Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 507

17.3.1 Module Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 507

17.3.2 Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 507

17.4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 509

17.4.1 Low-Power Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 509

17.5 Resets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 510

17.6 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 510

17.6.1 Interrupt Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 510

MC9S12E128 Data Sheet, Rev. 1.07

Freescale Semiconductor 17

Page 18

17.6.2 Highest Priority I-Bit Maskable Interrupt . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 510

17.6.3 Interrupt Priority Decoder . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 510

17.7 Exception Priority . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 511

Chapter 18

Multiplexed External Bus Interface (MEBIV3)

18.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 513

18.1.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 513

18.1.2 Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 515

18.2 External Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 516

18.3 Memory Map and Register Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 518

18.3.1 Module Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 518

18.3.2 Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 519

18.4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 536

18.4.1 Detecting Access Type from External Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 536

18.4.2 Stretched Bus Cycles . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 536

18.4.3 Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 537

18.4.4 Internal Visibility . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 541

18.4.5 Low-Power Options . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 542

Chapter 19

Module Mapping Control (MMCV4)

19.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 543

19.1.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 544

19.1.2 Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 544

19.2 External Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 544

19.3 Memory Map and Register Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 544

19.3.1 Module Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 544

19.3.2 Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 546

19.4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 555

19.4.1 Bus Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 555

19.4.2 Address Decoding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 556

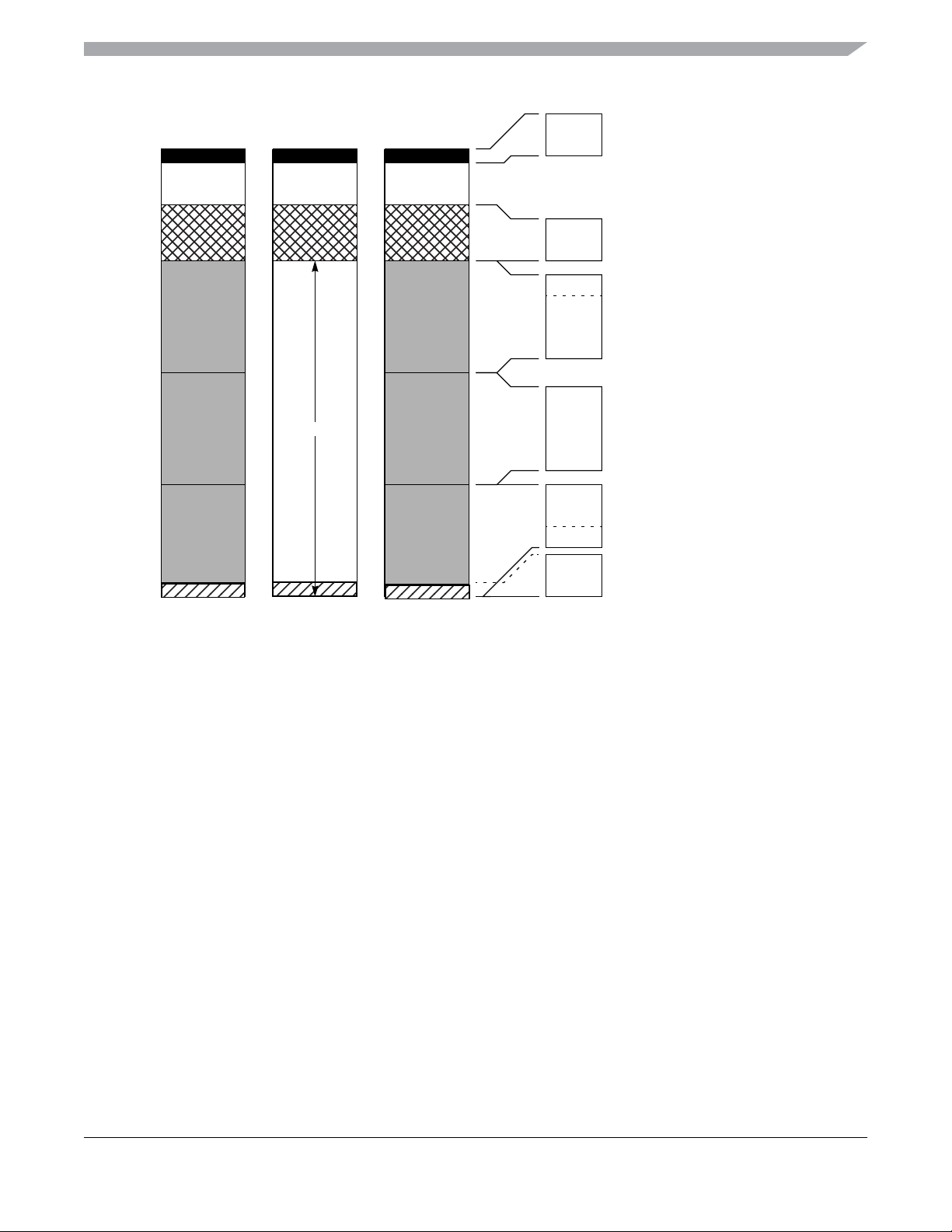

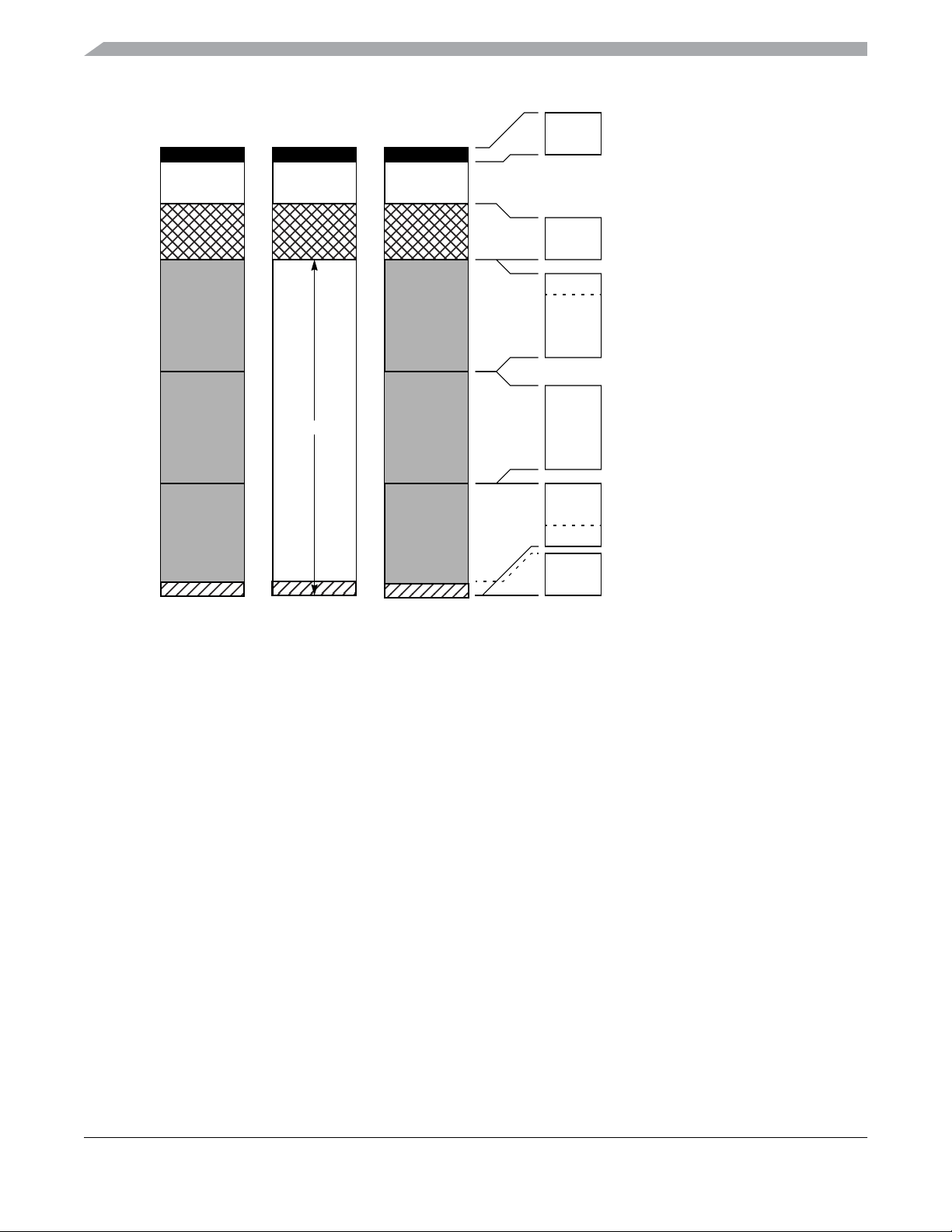

19.4.3 Memory Expansion . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 557

MC9S12E128 Data Sheet, Rev. 1.07

18 Freescale Semiconductor

Page 19

Appendix A

Electrical Characteristics

A.1 General . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 563

A.1.1 Parameter Classification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 563

A.1.2 Power Supply . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 563

A.1.3 Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 564

A.1.4 Current Injection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 564

A.1.5 Absolute Maximum Ratings. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 565

A.1.6 ESD Protection and Latch-up Immunity. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 566

A.1.7 Operating Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 567

A.1.8 Power Dissipation and Thermal Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 567

A.1.9 I/O Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 569

A.1.10 Supply Currents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 570

A.2 Voltage Regulator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 572

A.2.1 Chip Power-up and LVI/LVR Graphical Explanation . . . . . . . . . . . . . . . . . . . . . . . . . . 573

A.2.2 Output Loads. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 573

A.3 Startup, Oscillator and PLL. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 574

A.3.1 Startup. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 574

A.3.2 Oscillator. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 576

A.3.3 Phase Locked Loop. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 577

A.4 Flash NVM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 581

A.4.1 NVM Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 581

A.4.2 NVM Reliability . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 583

A.5 SPI Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 585

A.5.1 Master Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 585

A.5.2 Slave Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 587

A.6 ATD Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 589

A.6.1 ATD Operating Characteristics — 5V Range . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 589

A.6.2 ATD Operating Characteristics — 3.3V Range . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 590

A.6.3 Factors Influencing Accuracy . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 590

A.6.4 ATD Accuracy — 5V Range . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 592

A.6.5 ATD Accuracy — 3.3V Range. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 592

A.7 DAC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 595

A.7.1 DAC Operating Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 595

A.8 External Bus Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 595

Appendix B

Package Information

B.1 64-Pin QFN Package. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 599

B.2 80-Pin QFP Package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 600

B.3 112-Pin LQFP Package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 601

Appendix C

Ordering Information

MC9S12E128 Data Sheet, Rev. 1.07

Freescale Semiconductor 19

Page 20

MC9S12E128 Data Sheet, Rev. 1.07

20 Freescale Semiconductor

Page 21

Chapter 1 MC9S12E128 Device Overview (MC9S12E128DGV1)

1.1 Introduction

The MC9S12E128 is a 112/80/64 pin low cost general purpose MCU comprised of standard on-chip

peripherals including a 16-bit central processing unit (HCS12 CPU), up to 128K bytes of Flash EEPROM,

up to 8K bytes of RAM, three asynchronous serial communications interface modules (SCI), a serial

peripheral interface (SPI), an Inter-IC Bus (IIC), three 4-channel 16-bit timer modules (TIM), a 6-channel

15-bit Pulse Modulator with Fault protection module (PMF), a 6-channel 8-bit Pulse Width Modulator

(PWM), a 16-channel 10-bit analog-to-digital converter (ADC), and two 1-channel 8-bit digital-to-analog

converters (DAC). The MC9S12E128 has full 16-bit data paths throughout. The inclusion of a PLL circuit

allows power consumption and performance to be adjusted to suit operational requirements. In addition to

the I/O ports available on each module, 16 dedicated I/O port bits are available with Wake-Up capability

from STOP or WAIT mode. Furthermore, an on chip bandgap based voltage regulator (VREG) generates

the internal digital supply voltage of 2.5V (VDD) from a 3.135V to 5.5V external supply range.

1.1.1 Features

• 16-bit HCS12 CORE

— HCS12 CPU

– i. Upward compatible with M68HC11 instruction set

– ii. Interrupt stacking and programmer’s model identical to M68HC11

– iii. Instruction queue

– iv. Enhanced indexed addressing

— Module Mapping Control (MMC)

— Interrupt control (INT)

— Background Debug Module (BDM)

— Debugger (DBG12) including breakpoints and change-of-flow trace buffer

— Multiplexed External Bus Interface (MEBI)

• Wake-Up interrupt inputs

— Up to 16 port bits available for wake up interrupt function with digital filtering

• Memory Options

— 32K, 64K or 128K Byte Flash EEPROM

— 2K, 4K or 8K Byte RAM

MC9S12E128 Data Sheet, Rev. 1.07

Freescale Semiconductor 21

Page 22

Chapter 1 MC9S12E128 Device Overview (MC9S12E128DGV1)

• Two 1-channel Digital-to-Analog Converters (DAC)

— 8-bit resolution

• Analog-to-Digital Converter (ADC)

— 16-channel module with 10-bit resolution

— External conversion trigger capability

• Three 4-channel Timers (TIM)

— Programmable input capture or output compare channels

— Simple PWM mode

— Counter modulo reset

— External event counting

— Gated time accumulation

• 6 PWM channels (PWM)

— Programmable period and duty cycle

— 8-bit 6-channel or 16-bit 3-channel

— Separate control for each pulse width and duty cycle

— Center-aligned or left-aligned outputs

— Programmable clock select logic with a wide range of frequencies

— Fast emergency shutdown input

• 6-channel Pulse width Modulator with Fault protection (PMF)

— Three independent 15-bit counters with synchronous mode

— Complementary channel operation

— Edge and center aligned PWM signals

— Programmable dead time insertion

— Integral reload rates from 1 to 16

— Four fault protection shut down input pins

— Three current sense input pins

• Serial interfaces

— Three asynchronous serial communication interfaces (SCI)

— Synchronous serial peripheral interface (SPI)

— Inter-IC Bus (IIC)

• Clock and Reset Generator (CRG)

— Windowed COP watchdog

— Real Time interrupt

— Clock Monitor

— Pierce or low current Colpitts oscillator

— Phase-locked loop clock frequency multiplier

— Self Clock mode in absence of external clock

— Low power 0.5 to 16Mhz crystal oscillator reference clock

MC9S12E128 Data Sheet, Rev. 1.07

22 Freescale Semiconductor

Page 23

• Operating frequency

— 50MHz equivalent to 25MHz Bus Speed

• Internal 2.5V Regulator

— Input voltage range from 3.135V to 5.5V

— Low power mode capability

— Includes low voltage reset (LVR) circuitry

— Includes low voltage interrupt (LVI) circuitry

• 112-Pin LQFP or 80-Pin QFP or 64-Pin QFN package

— Up to 90 I/O lines with 5V input and drive capability (112 pin package)

— Up to two dedicated 5V input only lines (IRQ and XIRQ)

— Sixteen 3.3V/5V A/D converter inputs

• Development Support.

— Single-wire background debug

TM

mode

— On-chip hardware breakpoints

— Enhanced debug features

1.1.2 Modes of Operation

Chapter 1 MC9S12E128 Device Overview (MC9S12E128DGV1)

User modes (Expanded modes are only available in the 112-pin package version)

• Normal modes

— Normal Single-Chip Mode

— Normal Expanded Wide Mode

— Normal Expanded Narrow Mode

— Emulation Expanded Wide Mode

— Emulation Expanded Narrow Mode

• Special Operating Modes

— Special Single-Chip Mode with active Background Debug Mode

— Special Test Mode (Freescale use only)

— Special Peripheral Mode (Freescale use only)

• Low power modes

— Stop Mode

— Pseudo Stop Mode

— Wait Mode

MC9S12E128 Data Sheet, Rev. 1.07

Freescale Semiconductor 23

Page 24

Chapter 1 MC9S12E128 Device Overview (MC9S12E128DGV1)

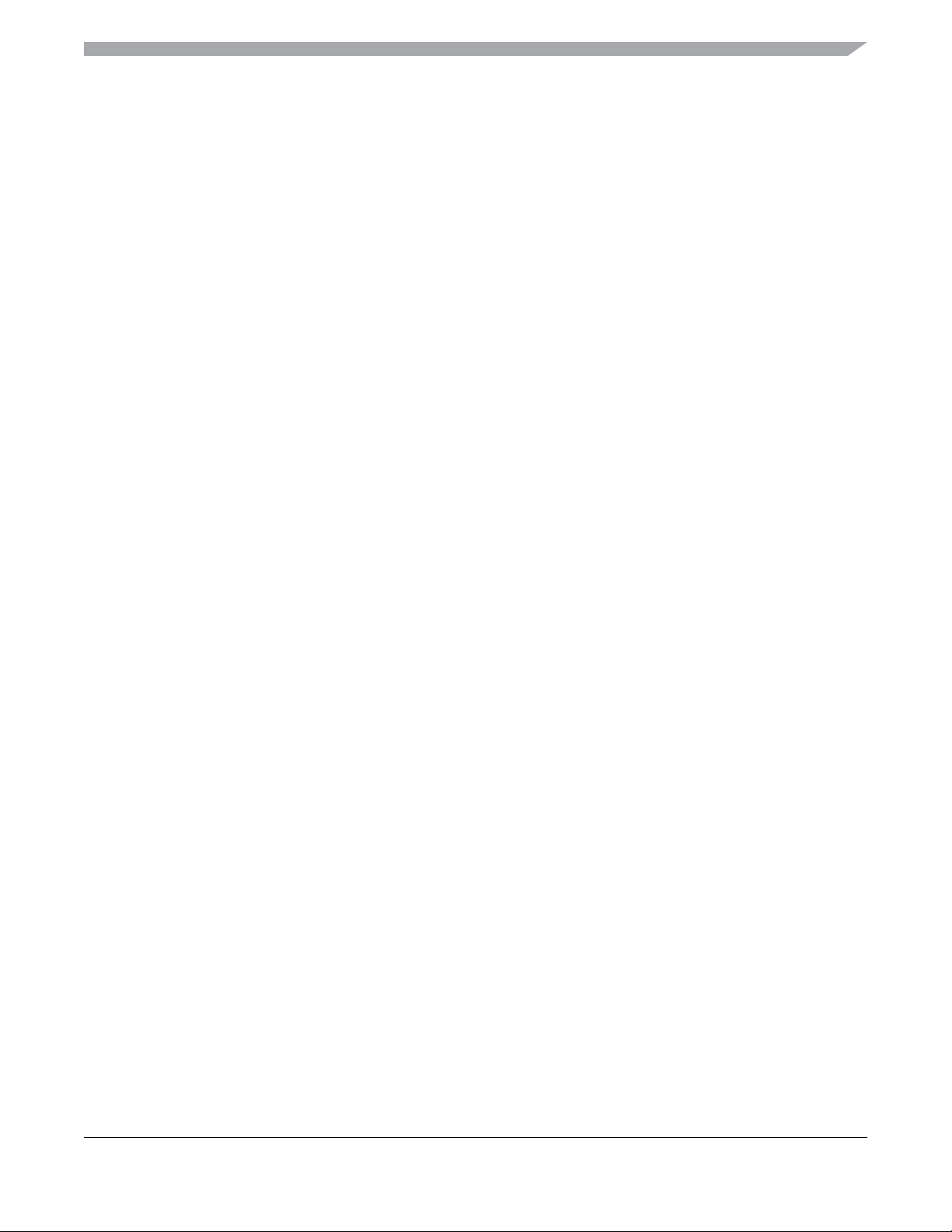

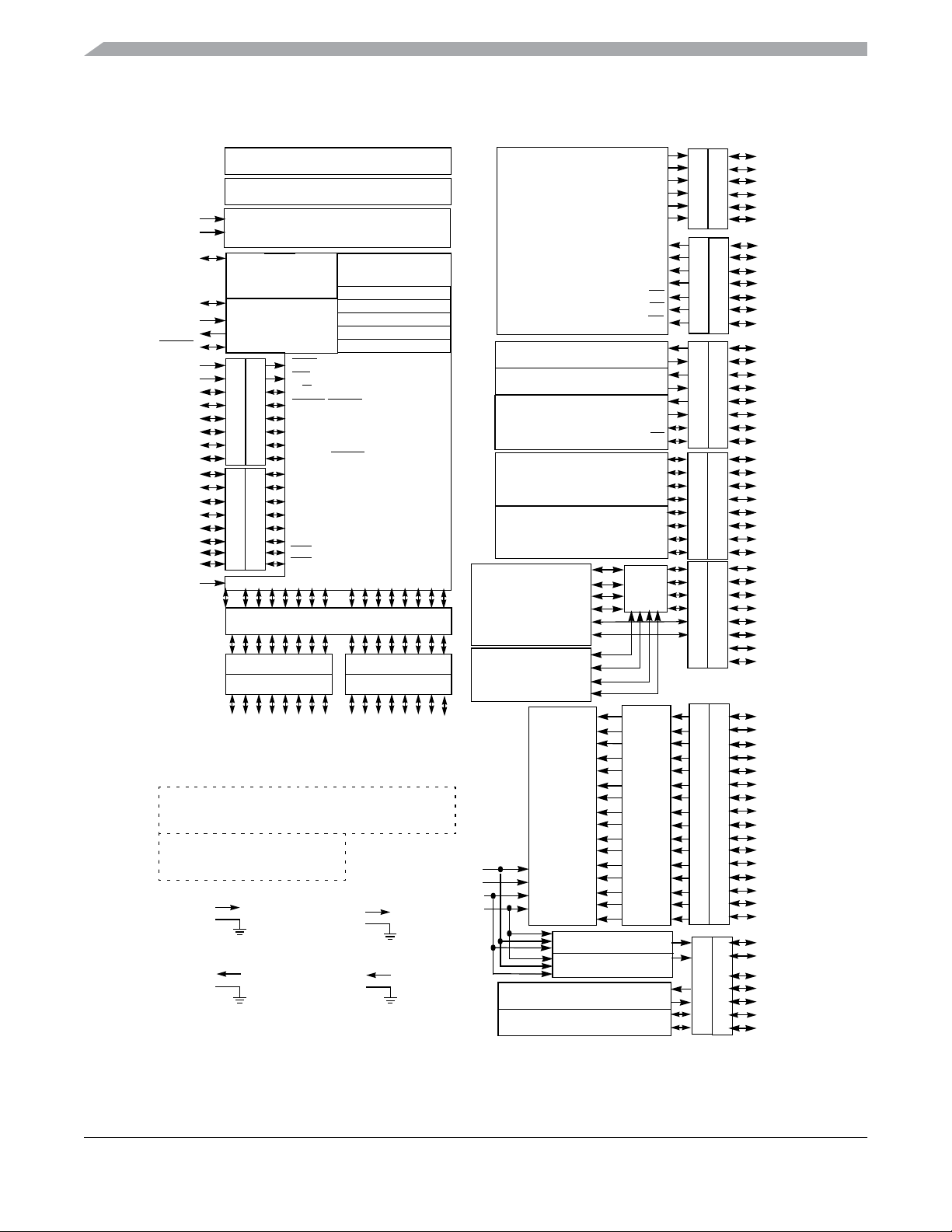

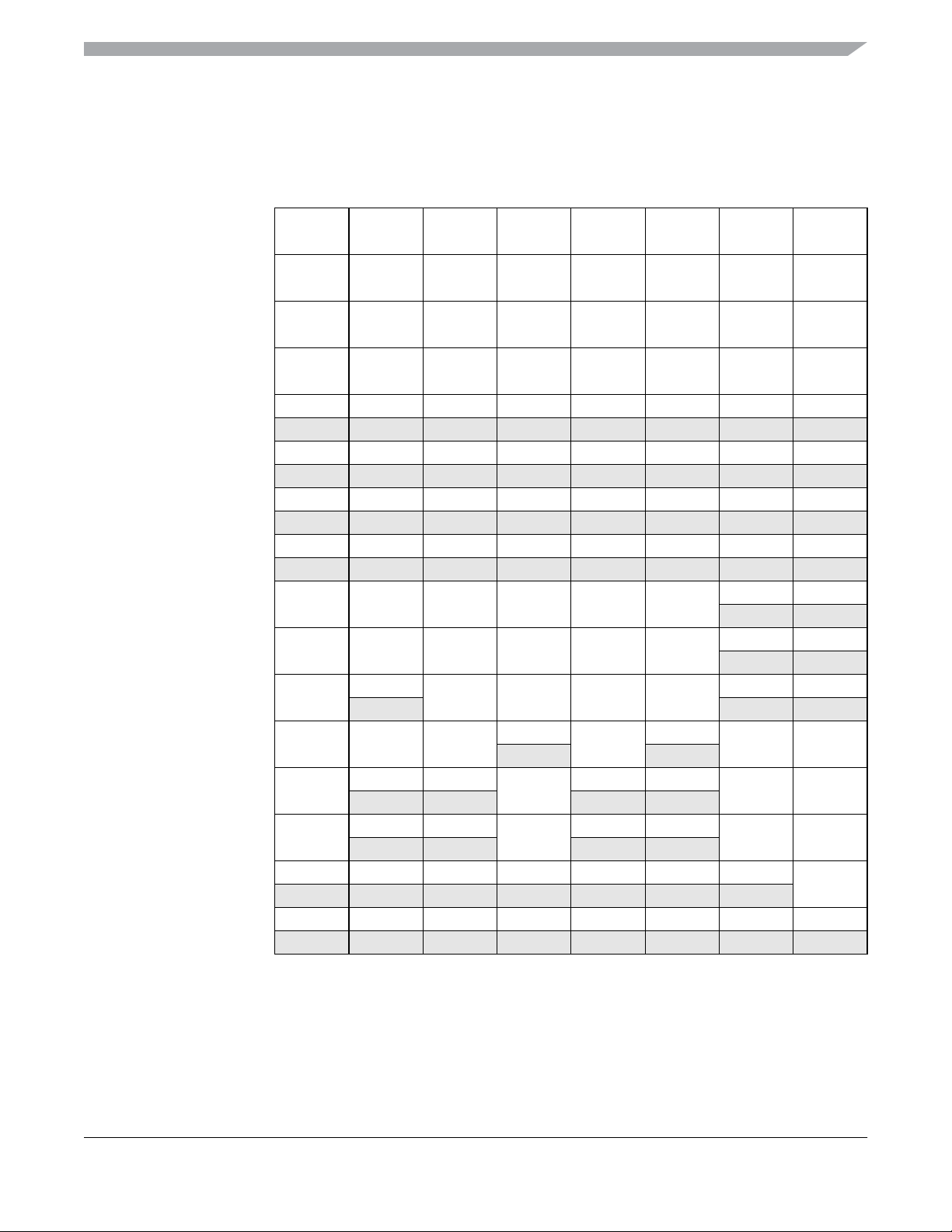

1.1.3 Block Diagram

32K / 64K / 128K Byte Flash EEPROM

2k / 4K / 8K Byte RAM

VDDR

VSSR

BKGD

XFC

EXTAL

XTAL

RESET

PE0

PE1

PE2

PE3

PE4

PE5

PE6

PE7

PK0

PK1

PK2

PK3

PK4

PK5

PK6

PK7

TEST

Multiplexed

Wide Bus

Multiplexed

Narrow Bus

Voltage Regulator 3.3V/5V

VDDR

VSSR

PLL 2.5V

VDDPLL

VSSPLL

Signals shown in Bold are not available on the 80 Pin Package

MODC/TAGHI

Single-wire Background

Debug Module

CRG

PTE

PTK

PA7

PA6

ADDR15

ADDR14

DATA15

DATA14

DATA7

DATA6

Voltage Regulator

CPU12

Periodic Interrupt

Clock and

Reset

Generation

XIRQ

IRQ

W

R/

LSTRB/TAGLO

ECLK

DDRE

MODA/IPIPE0

MODB/IPIPE1

NOACC/

XADDR14

XADDR15

XADDR16

XADDR17

XADDR18

DDRK

XADDR19

XCS

ECS

Multiplexed Address/Data Bus

DDRA DDRB

PTA PTB

PA4

PA3

PA2

PA5

ADDR12

ADDR11

ADDR10

ADDR13

DATA12

DATA11

DATA10

DATA13

DATA4

DATA3

DATA2

DATA5

Internal Logic 2.5V

COP Watchdog

Clock Monitor

Debugger(DBG12)

Breakpoints

System

Integration

Module

XCLKS

PA1

PA0

PB7

PB6

PB5

ADDR9

ADDR8

ADDR7

ADDR6

ADDR5

DATA9

DATA8

DATA7

DATA6

DATA5

DATA1

DATA0

I/O Driver 3.3V/5V

VDDX

VSSX

VDD1,2

VSS1,2

(SIM)

PB4

PB3

PB2

ADDR4

ADDR3

ADDR2

DATA4

DATA3

DATA2

ADC/DAC 3.3V/5V

Voltage Reference

Figure 1-1. MC9S12E128 Block Diagram

PB1

PB0

ADDR1

ADDR0

DATA1

DATA0

VDDA

VSSA

VRH

VRL

PWM

TIM2

PMF

SCI0

SCI1

SPI

SCI2

IIC

TIM0

TIM1

ADC

PW10

PW11

PW12

PW13

PW14

PW15

IOC24

IOC25

IOC26

IOC27

AN0

AN1

AN2

AN3

AN4

AN5

AN6

AN7

AN8

AN9

AN10

AN11

AN12

AN13

AN14

AN15

DAC0

DAC1

PW00

PW01

PW02

PW03

PW04

PW05

FAULT0

FAULT1

FAU LT2

FAULT3

IS0

IS1

IS2

RXD0

TXD0

RXD1

TXD1

MISO

MOSI

SCK

SS

IOC04

IOC05

IOC06

IOC07

IOC14

IOC15

IOC16

IOC17

MUX

KWAD0

KWAD1

KWAD2

KWAD3

KWAD4

KWAD5

KWAD6

KWAD7

KWAD8

KWAD9

KWAD10

KWAD11

KWAD12

KWAD13

KWAD14

KWAD15

DAO0

DAO1

RXD2

TXD2

SDA

SCL

PTP

DDRP

PTQ

DDRQ

PTS

DDRS

PTT

DDRT

PTU

DDRU

PAD

DDRAD

PTM

DDRM

PP0

PP1