Datasheet MC9S08RC8, MC9S08RC16, MC9S08RC32, MC9S08RC60, MC9S08RD8 Datasheet (Freescale)

...

查询MC9S08RC16供应商

MC9S08RC8/16/32/60

MC9S08RD8/16/32/60

MC9S08RE8/16/32/60

MC9S08RG32/60

Data Sheet

HCS08

Microcontrollers

MC9S08RG60/D

Rev 1.10

08/2004

freescale.com

MC9S08RG60 Data Sheet

Covers: MC9S08RC8/16/32/60

MC9S08RD8/16/32/60

MC9S08RE8/16/32/60

MC9S08RG32/60

MC9S08RG60/D

Rev 1.10

08/2004

Revision History

To provide the most up-to-date information, the revision of our documents on the World Wide Web will

be the most current. Your printed copy may be an earlier revision. To verify you have the latest information

available, refer to:

http://freescale.com

The following revision history table summarizes changes contained in this document.

Version

Number

1.07 2/4/2004 Initial external release.

1.08 4/22/2004 Changes to Table C-6 in electricals section.

1.09 7/7/2004

1.10 8/11/2004

Revision

Date

Description of Changes

Added Table C-4; changes to Table C-6; changed to Freescale

format

Removed BRK bit 13 and TXINV, which are not available on this

module version; fixed typo in Figure 13-2; corrected the SPTEF

description in section 12.3

This product contains SuperFlash® technology licensed from SST.

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc.

© Freescale Semiconductor, Inc., 2004. All rights reserved.

SoC Guide — MC9S08RG60/D Rev 1.10

List of Chapters

Chapter 1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15

Chapter 2 Pins and Connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .19

Chapter 3 Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .29

Chapter 4 Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .35

Chapter 5 Resets, Interrupts, and System Configuration . . . . . . . . . . . . . . .57

Chapter 6 Central Processor Unit (CPU) . . . . . . . . . . . . . . . . . . . . . . . . . . . . .73

Chapter 7 Carrier Modulator Timer (CMT) Module . . . . . . . . . . . . . . . . . . . . .93

Chapter 8 Parallel Input/Output . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

Chapter 9 Keyboard Interrupt (KBI) Module . . . . . . . . . . . . . . . . . . . . . . . . .121

Chapter 10 Timer/PWM Module (TPM) Module . . . . . . . . . . . . . . . . . . . . . . .127

Chapter 11 Serial Communications Interface (SCI) Module . . . . . . . . . . . .143

Chapter 12 Serial Peripheral Interface (SPI) Module . . . . . . . . . . . . . . . . . .161

Chapter 13 Analog Comparator (ACMP) Module . . . . . . . . . . . . . . . . . . . . .177

Chapter 14 Development Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 183

Appendix C Electrical Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 207

Appendix D Ordering Information and Mechanical Drawings . . . . . . . . . .223

Freescale Semiconductor

5MC9S08RC/RD/RE/RG

List of Chapters

MC9S08RC/RD/RE/RG6

Freescale Semiconductor

SoC Guide — MC9S08RG60/D Rev 1.10

Contents

Chapter 1 Introduction

1.1 Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

1.2 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

1.2.1 Standard Features of the HCS08 Family . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

1.2.2 Features of MC9S08RC/RD/RE/RG Series of MCUs . . . . . . . . . . . . . . . . . . . . . 15

1.2.3 Devices in the MC9S08RC/RD/RE/RG Series. . . . . . . . . . . . . . . . . . . . . . . . . . . 16

1.3 MCU Block Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

1.4 System Clock Distribution. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Chapter 2 Pins and Connections

2.1 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

2.2 Device Pin Assignment. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

2.3 Recommended System Connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

2.3.1 Power . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

2.3.2 Oscillator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

2.3.3 PTD1/RESET . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

2.3.4 Background/Mode Select (PTD0/BKGD/MS). . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

2.3.5 IRO Pin Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

2.3.6 General-Purpose I/O and Peripheral Ports . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

2.3.7 Signal Properties Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

Chapter 3 Modes of Operation

3.1 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

3.2 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

3.3 Run Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

3.4 Active Background Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

3.5 Wait Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

3.6 Stop Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

3.6.1 Stop1 Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

3.6.2 Stop2 Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

3.6.3 Stop3 Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

3.6.4 Active BDM Enabled in Stop Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

3.6.5 LVD Reset Enabled in Stop Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

3.6.6 On-Chip Peripheral Modules in Stop Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

Freescale Semiconductor

7MC9S08RC/RD/RE/RG

Contents

Chapter 4 Memory

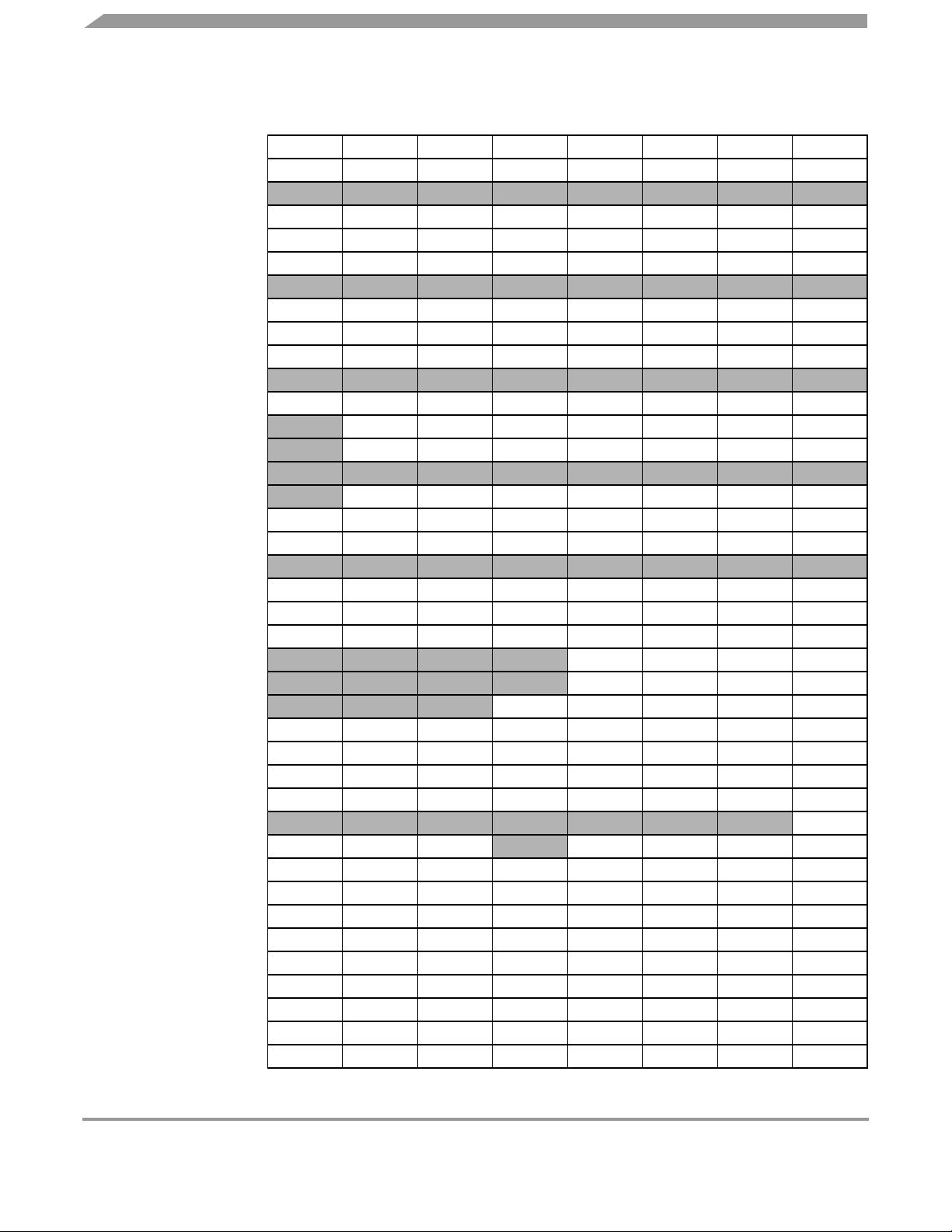

4.1 MC9S08RC/RD/RE/RG Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

4.1.1 Reset and Interrupt Vector Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

4.2 Register Addresses and Bit Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

4.3 RAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .41

4.4 FLASH . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

4.4.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

4.4.2 Program and Erase Times . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

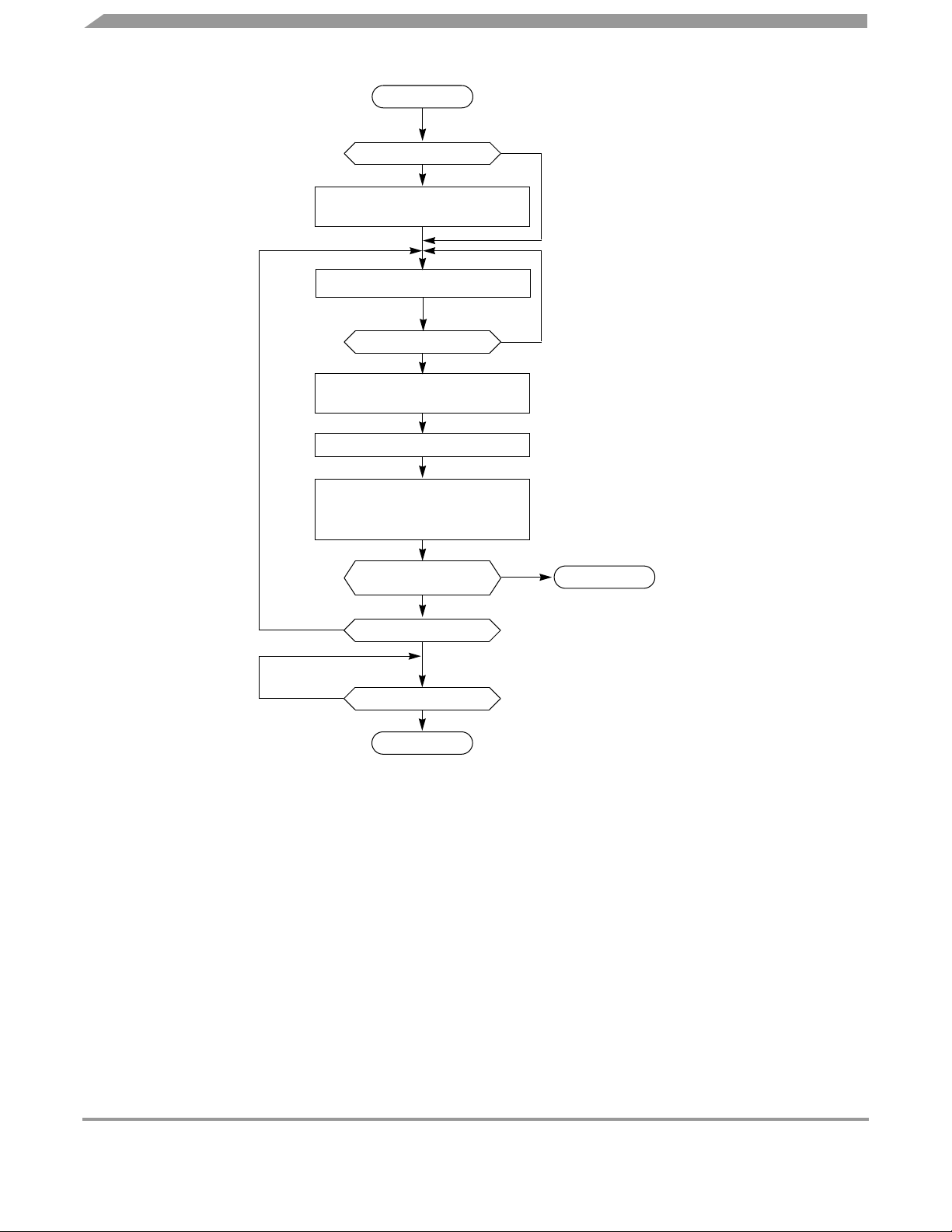

4.4.3 Program and Erase Command Execution . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

4.4.4 Burst Program Execution . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

4.4.5 Access Errors. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

4.4.6 FLASH Block Protection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

4.4.7 Vector Redirection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

4.5 Security. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .48

4.6 FLASH Registers and Control Bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

4.6.1 FLASH Clock Divider Register (FCDIV). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

4.6.2 FLASH Options Register (FOPT and NVOPT) . . . . . . . . . . . . . . . . . . . . . . . . . . 51

4.6.3 FLASH Configuration Register (FCNFG) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

4.6.4 FLASH Protection Register (FPROT and NVPROT) . . . . . . . . . . . . . . . . . . . . . . 52

4.6.5 FLASH Status Register (FSTAT) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

4.6.6 FLASH Command Register (FCMD) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

Chapter 5 Resets, Interrupts, and System Configuration

5.1 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

5.2 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

5.3 MCU Reset. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

5.4 Computer Operating Properly (COP) Watchdog . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

5.5 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

5.5.1 Interrupt Stack Frame . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

5.5.2 External Interrupt Request (IRQ) Pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

5.5.3 Interrupt Vectors, Sources, and Local Masks . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

5.6 Low-Voltage Detect (LVD) System. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

5.6.1 Power-On Reset Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

5.6.2 LVD Reset Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

5.6.3 LVD Interrupt and Safe State Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

5.6.4 Low-Voltage Warning (LVW) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

MC9S08RC/RD/RE/RG8

Freescale Semiconductor

SoC Guide — MC9S08RG60/D Rev 1.10

5.7 Real-Time Interrupt (RTI) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

5.8 Reset, Interrupt, and System Control Registers and Control Bits . . . . . . . . . . . . . . 64

5.8.1 Interrupt Pin Request Status and Control Register (IRQSC) . . . . . . . . . . . . . . . . 64

5.8.2 System Reset Status Register (SRS) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

5.8.3 System Background Debug Force Reset Register (SBDFR). . . . . . . . . . . . . . . . 67

5.8.4 System Options Register (SOPT) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

5.8.5 System Device Identification Register (SDIDH, SDIDL) . . . . . . . . . . . . . . . . . . . 69

5.8.6 System Real-Time Interrupt Status and Control Register (SRTISC) . . . . . . . . . . 69

5.8.7 System Power Management Status and Control 1 Register (SPMSC1) . . . . . . . 71

5.8.8 System Power Management Status and Control 2 Register (SPMSC2) . . . . . . . 72

Chapter 6 Central Processor Unit (CPU)

6.1 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

6.2 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

6.3 Programmer’s Model and CPU Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

6.3.1 Accumulator (A) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

6.3.2 Index Register (H:X). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

6.3.3 Stack Pointer (SP) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

6.3.4 Program Counter (PC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

6.3.5 Condition Code Register (CCR). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

6.4 Addressing Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

6.4.1 Inherent Addressing Mode (INH) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

6.4.2 Relative Addressing Mode (REL). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

6.4.3 Immediate Addressing Mode (IMM) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

6.4.4 Direct Addressing Mode (DIR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

6.4.5 Extended Addressing Mode (EXT). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

6.4.6 Indexed Addressing Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

6.5 Special Operations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

6.5.1 Reset Sequence. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

6.5.2 Interrupt Sequence. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

6.5.3 Wait Mode Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

6.5.4 Stop Mode Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

6.5.5 BGND Instruction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

6.6 HCS08 Instruction Set Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

Freescale Semiconductor

9MC9S08RC/RD/RE/RG

Contents

Chapter 7 Carrier Modulator Timer (CMT) Module

7.1 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

7.2 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

7.3 CMT Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

7.4 Pin Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

7.5 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

7.5.1 Carrier Generator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

7.5.2 Modulator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

7.5.3 Extended Space Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

7.5.4 Transmitter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

7.5.5 CMT Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103

7.5.6 Wait Mode Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103

7.5.7 Stop Mode Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103

7.5.8 Background Mode Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104

7.6 CMT Registers and Control Bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104

7.6.1 Carrier Generator Data Registers (CMTCGH1, CMTCGL1, CMTCGH2, and CMTCGL2)

104

7.6.2 CMT Output Control Register (CMTOC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 106

7.6.3 CMT Modulator Status and Control Register (CMTMSC) . . . . . . . . . . . . . . . . . 107

7.6.4 CMT Modulator Data Registers (CMTCMD1, CMTCMD2, CMTCMD3, and CMTCMD4)

109

Chapter 8 Parallel Input/Output

8.1 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

8.2 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

8.3 Pin Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

8.3.1 Port A . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 112

8.3.2 Port B . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 112

8.3.3 Port C . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

8.3.4 Port D . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

8.3.5 Port E . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 114

8.4 Parallel I/O Controls . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 114

8.4.1 Data Direction Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 114

8.4.2 Internal Pullup Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 115

8.5 Stop Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 115

8.6 Parallel I/O Registers and Control Bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 115

MC9S08RC/RD/RE/RG10

Freescale Semiconductor

SoC Guide — MC9S08RG60/D Rev 1.10

8.6.1 Port A Registers (PTAD, PTAPE, and PTADD) . . . . . . . . . . . . . . . . . . . . . . . . . 115

8.6.2 Port B Registers (PTBD, PTBPE, and PTBDD) . . . . . . . . . . . . . . . . . . . . . . . . . 117

8.6.3 Port C Registers (PTCD, PTCPE, and PTCDD) . . . . . . . . . . . . . . . . . . . . . . . . 118

8.6.4 Port D Registers (PTDD, PTDPE, and PTDDD) . . . . . . . . . . . . . . . . . . . . . . . . 119

8.6.5 Port E Registers (PTED, PTEPE, and PTEDD) . . . . . . . . . . . . . . . . . . . . . . . . . 120

Chapter 9 Keyboard Interrupt (KBI) Module

9.1 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 121

9.2 KBI Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123

9.3 Keyboard Interrupt (KBI) Module . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123

9.3.1 Pin Enables . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123

9.3.2 Edge and Level Sensitivity . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123

9.3.3 KBI Interrupt Controls. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124

9.4 KBI Registers and Control Bits. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124

9.4.1 KBI x Status and Control Register (KBIxSC) . . . . . . . . . . . . . . . . . . . . . . . . . . . 124

9.4.2 KBI x Pin Enable Register (KBIxPE) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 126

Chapter 10 Timer/PWM Module (TPM) Module

10.1 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 127

10.2 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 127

10.3 TPM Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 129

10.4 Pin Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 130

10.4.1 External TPM Clock Sources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 130

10.4.2 TPM1CHn — TPM1 Channel n I/O Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 130

10.5 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 130

10.5.1 Counter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 131

10.5.2 Channel Mode Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 132

10.5.3 Center-Aligned PWM Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 133

10.6 TPM Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 135

10.6.1 Clearing Timer Interrupt Flags . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 135

10.6.2 Timer Overflow Interrupt Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 135

10.6.3 Channel Event Interrupt Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 135

10.6.4 PWM End-of-Duty-Cycle Events . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 136

10.7 TPM Registers and Control Bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 136

10.7.1 Timer x Status and Control Register (TPM1SC) . . . . . . . . . . . . . . . . . . . . . . . . 136

10.7.2 Timer x Counter Registers (TPM1CNTH:TPM1CNTL) . . . . . . . . . . . . . . . . . . . 138

Freescale Semiconductor

11MC9S08RC/RD/RE/RG

Contents

10.7.3 Timer x Counter Modulo Registers (TPM1MODH:TPM1MODL) . . . . . . . . . . . . 139

10.7.4 Timer x Channel n Status and Control Register (TPM1CnSC) . . . . . . . . . . . . . 140

10.7.5 Timer x Channel Value Registers (TPM1CnVH:TPM1CnVL) . . . . . . . . . . . . . . 142

Chapter 11 Serial Communications Interface (SCI) Module

11.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 144

11.2 SCI System Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 144

11.3 Baud Rate Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 144

11.4 Transmitter Functional Description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 145

11.4.1 Transmitter Block Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 145

11.4.2 Send Break and Queued Idle. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 147

11.5 Receiver Functional Description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 147

11.5.1 Receiver Block Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 147

11.5.2 Data Sampling Technique . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 149

11.5.3 Receiver Wakeup Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 150

11.6 Interrupts and Status Flags . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 150

11.7 Additional SCI Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 151

11.7.1 8- and 9-Bit Data Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 151

11.8 Stop Mode Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 152

11.8.1 Loop Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 152

11.8.2 Single-Wire Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 152

11.9 SCI Registers and Control Bits. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 152

11.9.1 SCI Baud Rate Registers (SCI1BDH, SCI1BHL) . . . . . . . . . . . . . . . . . . . . . . . . 153

11.9.2 SCI Control Register 1 (SCI1C1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 153

11.9.3 SCI Control Register 2 (SCI1C2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 155

11.9.4 SCI Status Register 1 (SCI1S1). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 156

11.9.5 SCI Status Register 2 (SCI1S2). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 158

11.9.6 SCI Control Register 3 (SCI1C3) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 159

11.9.7 SCI Data Register (SCI1D) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 160

Chapter 12 Serial Peripheral Interface (SPI) Module

12.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 162

12.2 Block Diagrams . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 162

12.2.1 SPI System Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 162

12.2.2 SPI Module Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 163

12.2.3 SPI Baud Rate Generation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 165

MC9S08RC/RD/RE/RG12

Freescale Semiconductor

SoC Guide — MC9S08RG60/D Rev 1.10

12.3 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 165

12.3.1 SPI Clock Formats . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 166

12.3.2 SPI Pin Controls. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 168

12.3.3 SPI Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 169

12.3.4 Mode Fault Detection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 169

12.4 SPI Registers and Control Bits. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 170

12.4.1 SPI Control Register 1 (SPI1C1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 170

12.4.2 SPI Control Register 2 (SPI1C2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 172

12.4.3 SPI Baud Rate Register (SPI1BR). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 173

12.4.4 SPI Status Register (SPI1S) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 174

12.4.5 SPI Data Register (SPI1D). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 175

Chapter 13 Analog Comparator (ACMP) Module

13.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 178

13.2 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 178

13.3 Pin Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 178

13.4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 179

13.4.1 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 179

13.4.2 Wait Mode Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 179

13.4.3 Stop Mode Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 179

13.4.4 Background Mode Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 179

13.5 ACMP Status and Control Register (ACMP1SC) . . . . . . . . . . . . . . . . . . . . . . . . . . 180

Chapter 14 Development Support

14.1 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 183

14.2 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 184

14.3 Background Debug Controller (BDC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 185

14.3.1 BKGD Pin Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 185

14.3.2 Communication Details . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 186

14.3.3 BDC Commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 190

14.3.4 BDC Hardware Breakpoint. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 192

14.4 On-Chip Debug System (DBG) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 193

14.4.1 Comparators A and B. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 193

14.4.2 Bus Capture Information and FIFO Operation . . . . . . . . . . . . . . . . . . . . . . . . . . 194

14.4.3 Change-of-Flow Information. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 194

14.4.4 Tag vs. Force Breakpoints and Triggers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 195

Freescale Semiconductor

13MC9S08RC/RD/RE/RG

Contents

14.4.5 Trigger Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 195

14.4.6 Hardware Breakpoints . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 197

14.5 Registers and Control Bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 197

14.5.1 BDC Registers and Control Bits. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 197

14.5.2 System Background Debug Force Reset Register (SBDFR). . . . . . . . . . . . . . . 199

14.5.3 DBG Registers and Control Bits. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 200

Appendix C Electrical Characteristics

C.1 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 207

C.2 Absolute Maximum Ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 207

C.3 Thermal Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 208

C.4 Electrostatic Discharge (ESD) Protection Characteristics . . . . . . . . . . . . . . . . . . . 209

C.5 DC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 209

C.6 Supply Current Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 213

C.7 Analog Comparator (ACMP) Electricals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 214

C.8 Oscillator Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 214

C.9 AC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 215

C.9.1 Control Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 215

C.9.2 Timer/PWM (TPM) Module Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 216

C.9.3 SPI Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 217

C.10 FLASH Specifications. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 221

Appendix D Ordering Information and Mechanical Drawings

D.1 Ordering Information. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 223

D.2 Mechanical Drawings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 224

D.2.1 28-Pin SOIC Package Drawing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 225

D.2.2 28-Pin PDIP Package Drawing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 226

D.2.3 32-Pin LQFP Package Drawing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 227

D.2.4 44-Pin LQFP Package Drawing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 228

MC9S08RC/RD/RE/RG14

Freescale Semiconductor

SoC Guide — MC9S08RG60/D Rev 1.10

Chapter 1 Introduction

1.1 Overview

The MC9S08RC/RD/RE/RG are members of the low-cost, high-performance HCS08 Family of 8-bit

microcontroller units (MCUs). All MCUs in this family use the enhanced HCS08 core and are available

with a variety of modules, memory sizes, memory types, and package types.

1.2 Features

Features have been organized to reflect:

• Standard features of the HCS08 Family

• Additional features of the MC9S08RC/RD/RE/RG MCU

1.2.1 Standard Features of the HCS08 Family

• HCS08 CPU (central processor unit)

• HC08 instruction set with added BGND instruction

• Background debugging system (see also the Development Support section)

• Breakpoint capability to allow single breakpoint setting during in-circuit debugging (plus two more

breakpoints in on-chip debug module)

• Debug module containing two comparators and nine trigger modes. Eight deep FIFO for storing

change-of-flow addresses and event-only data. Debug module supports both tag and force

breakpoints.

• Support for up to 32 interrupt/reset sources

• Power-saving modes: wait plus three stops

• System protection features:

– Optional computer operating properly (COP) reset

– Low-voltage detection with reset or interrupt

– Illegal opcode detection with reset

– Illegal address detection with reset (some devices don’t have illegal addresses)

1.2.2 Features of MC9S08RC/RD/RE/RG Series of MCUs

• 8 MHz internal bus frequency

• On-chip in-circuit programmable FLASH memory with block protection and security option (see

Table 1-1 for device specific information)

• On-chip random-access memory (RAM) (see Table 1-1 for device specific information)

Freescale Semiconductor

15MC9S08RC/RD/RE/RG

Introduction

• Low power oscillator capable of operating from crystal or resonator from 1 to 16 MHz

• On-chip analog comparator with internal reference (ACMP1) see Table 1-1

– Full rail-to-rail supply operation

– Option to compare to a fixed internal bandgap reference voltage

• Serial communications interface module (SCI1) — see Table 1-1

• Serial peripheral interface module (SPI1) — see Table 1-1

• 2-channel, 16-bit timer/pulse-width modulator (TPM1) module with selectable input capture,

output compare, and edge-aligned or center-aligned PWM capability on each channel.

• Keyboard interrupt ports (KBI1, KBI2)

– Providing 12 keyboard interrupts

– Eight with falling-edge/low-level plus four with selectable polarity

• Carrier modulator timer (CMT) with dedicated infrared output (IRO) pin

– Drives IRO pin for remote control communications

– Can be disconnected from IRO pin and used as output compare timer

– IRO output pin has high-current sink capability

• Eight high-current pins (limited by maximum package dissipation)

• Software selectable pullups on ports when used as input. Selection is on an individual port bit basis.

During output mode, pullups are disengaged.

• 39 general-purpose input/output (I/O) pins, depending on package selection

• Four packages available

– 28-pin plastic dual in-line package (PDIP)

– 28-pin small outline integrated circuit (SOIC)

– 32-pin low-profile quad flat package (LQFP)

– 44-pin low-profile quad flat package (LQFP)

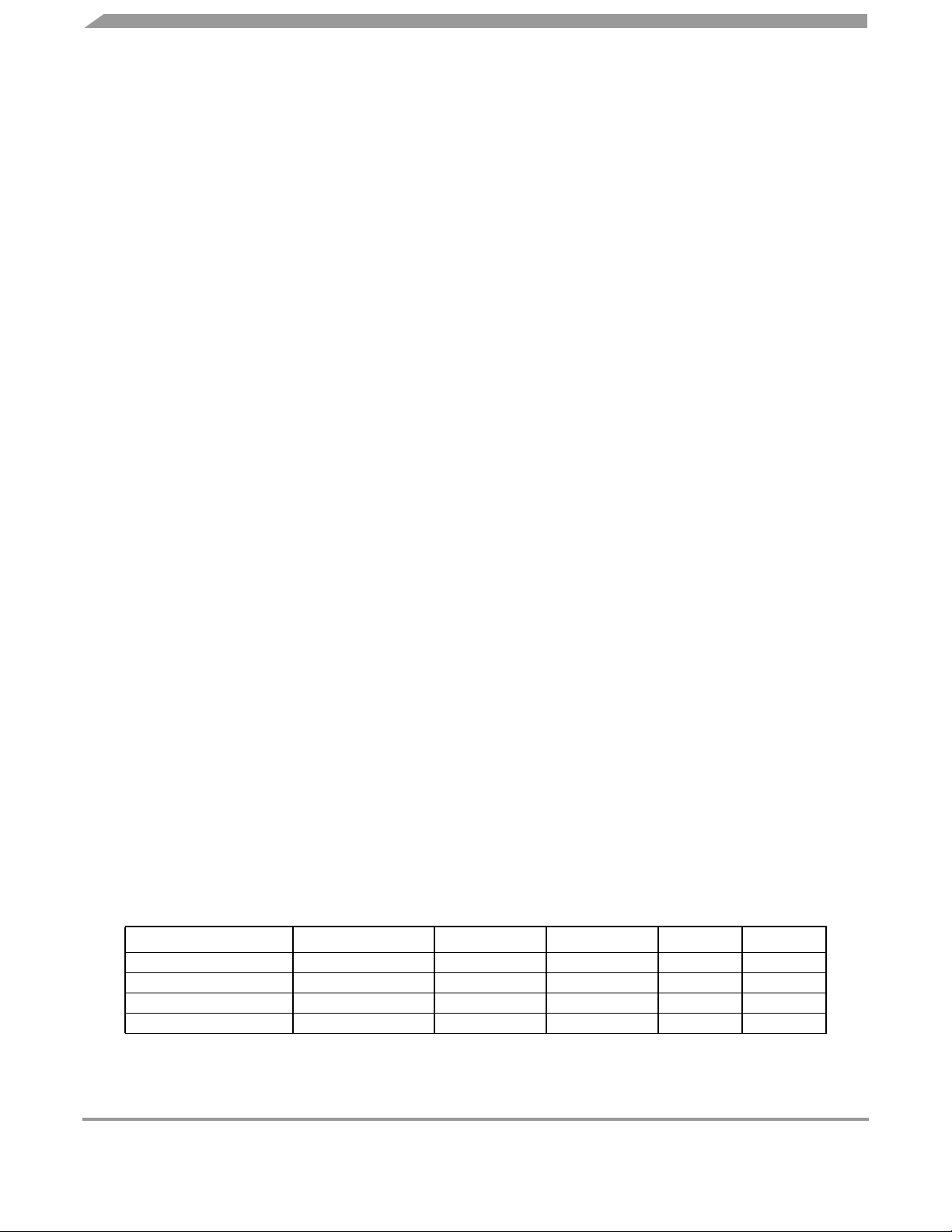

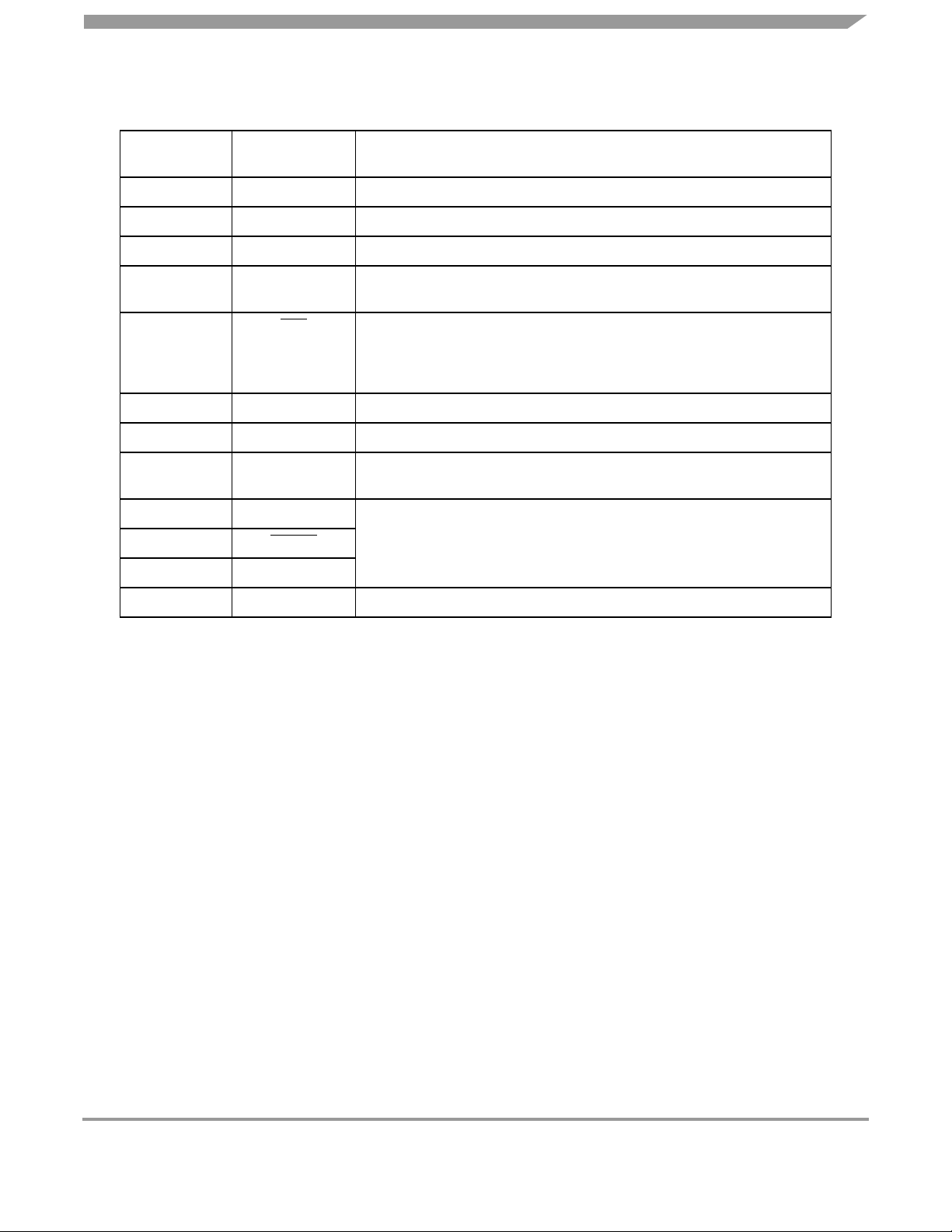

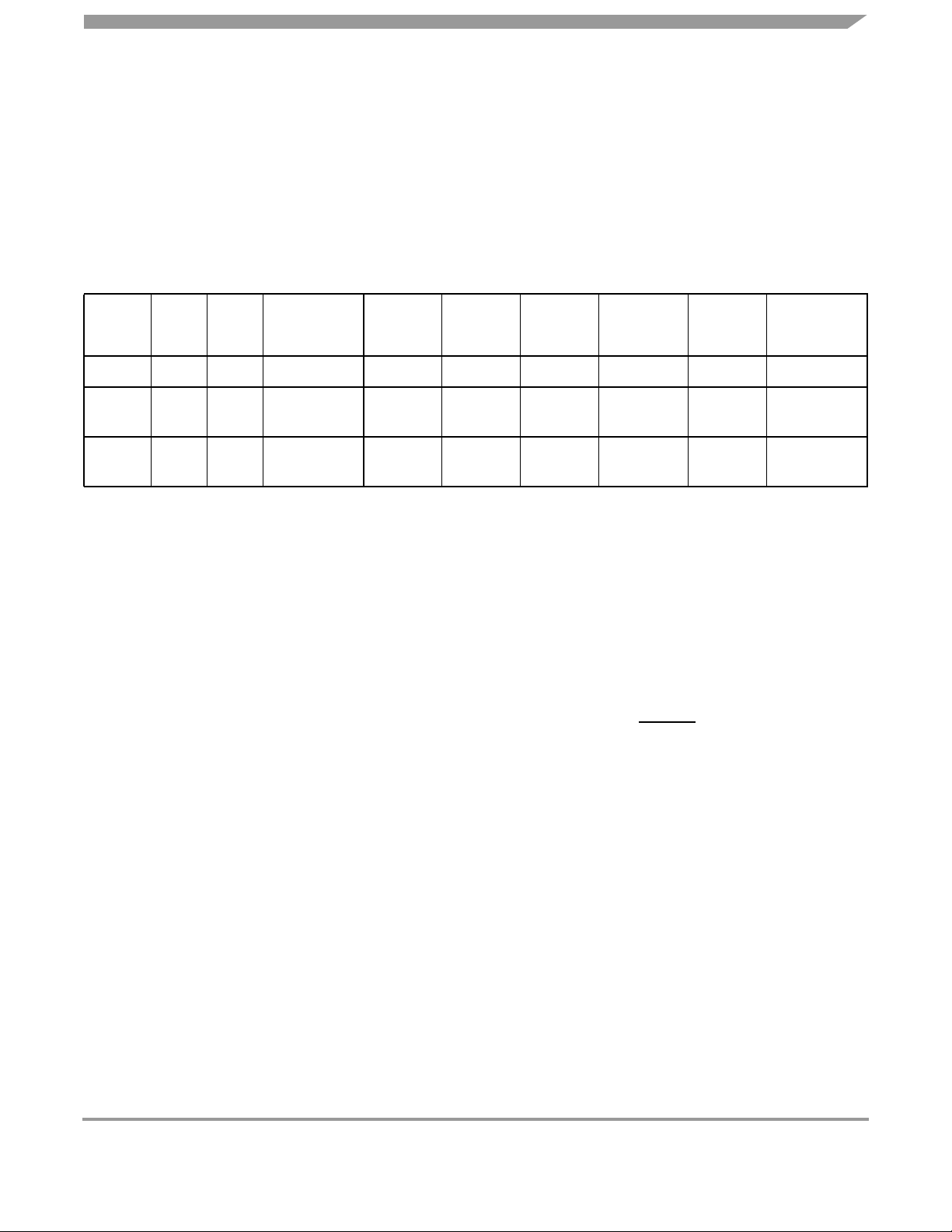

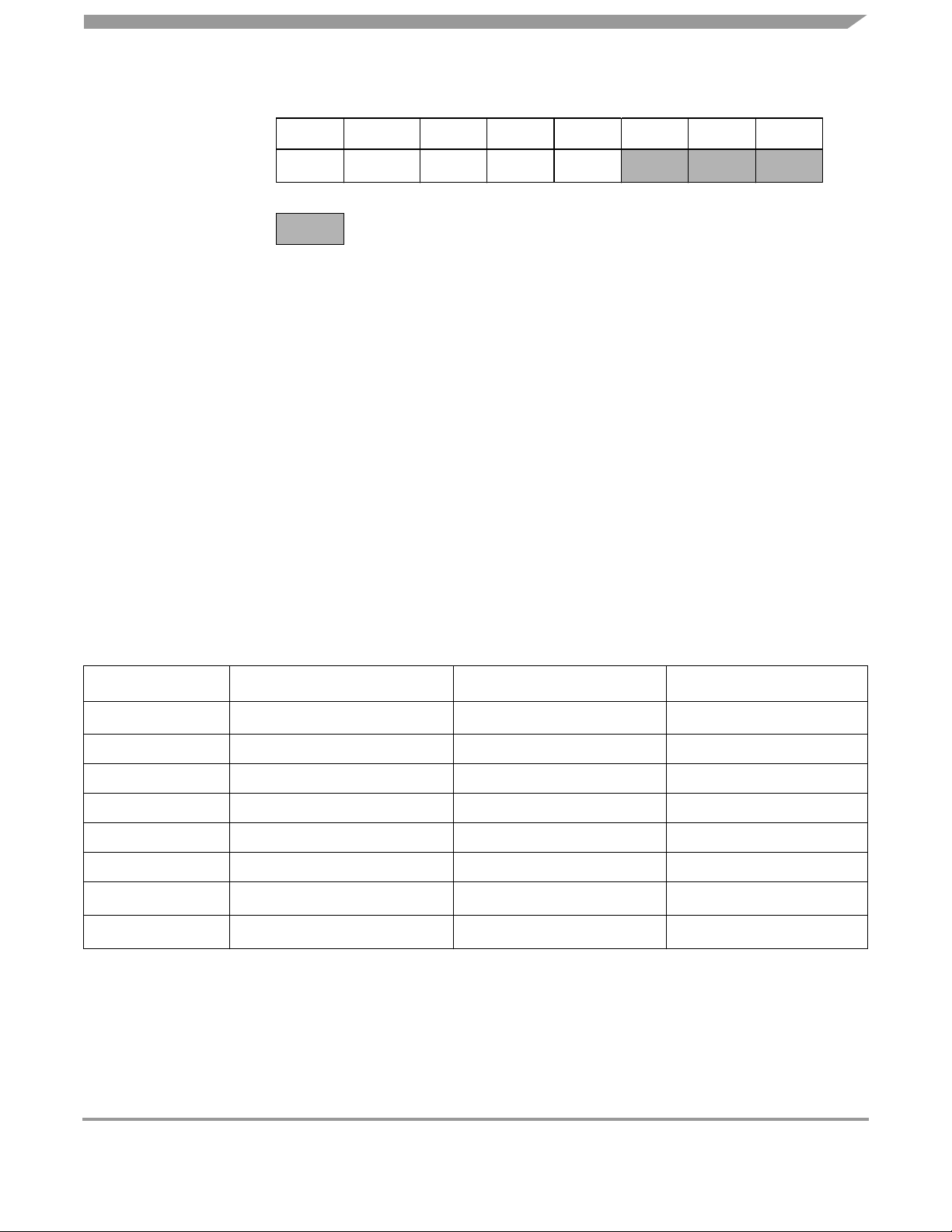

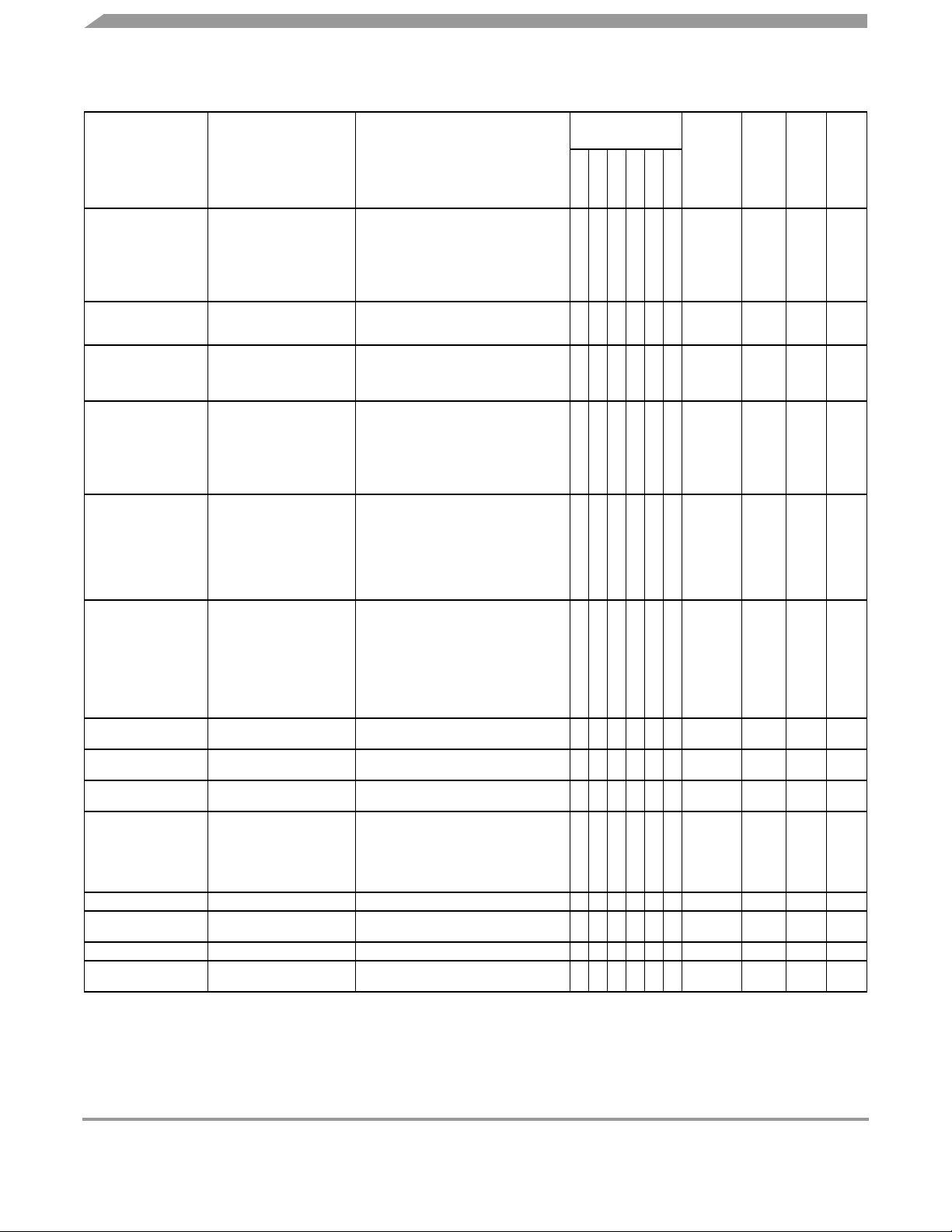

1.2.3 Devices in the MC9S08RC/RD/RE/RG Series

Table 1-1 below lists the devices available in the MC9S08RC/RD/RE/RG series and summarizes the

differences in functions and configuration between them.

Table 1-1 Devices in the MC9S08RC/RD/RE/RG Series

Device FLASH

9S08RG32/60 32K/60K 2K/2K Yes Yes Yes

9S08RE8/16/32/60 8/16K/32K/60K 1K/1K/2K/2K Yes Yes No

9S08RD8/16/32/60 8/16K/32K/60K 1K/1K/2K/2K No Yes No

9S08RC8/16/32/60 8/16K/32K/60K 1K/1K/2K/2K Yes No No

NOTES:

1. 3S08RC/RD/RE8/16 ROM MCU devices have 512 bytes RAM instead of 1K bytes.

2. Only available in 32- or 44-pin LQFP packages.

RAM

(1)

ACMP

(2)

SCI SPI

MC9S08RC/RD/RE/RG16

Freescale Semiconductor

SoC Guide — MC9S08RG60/D Rev 1.10

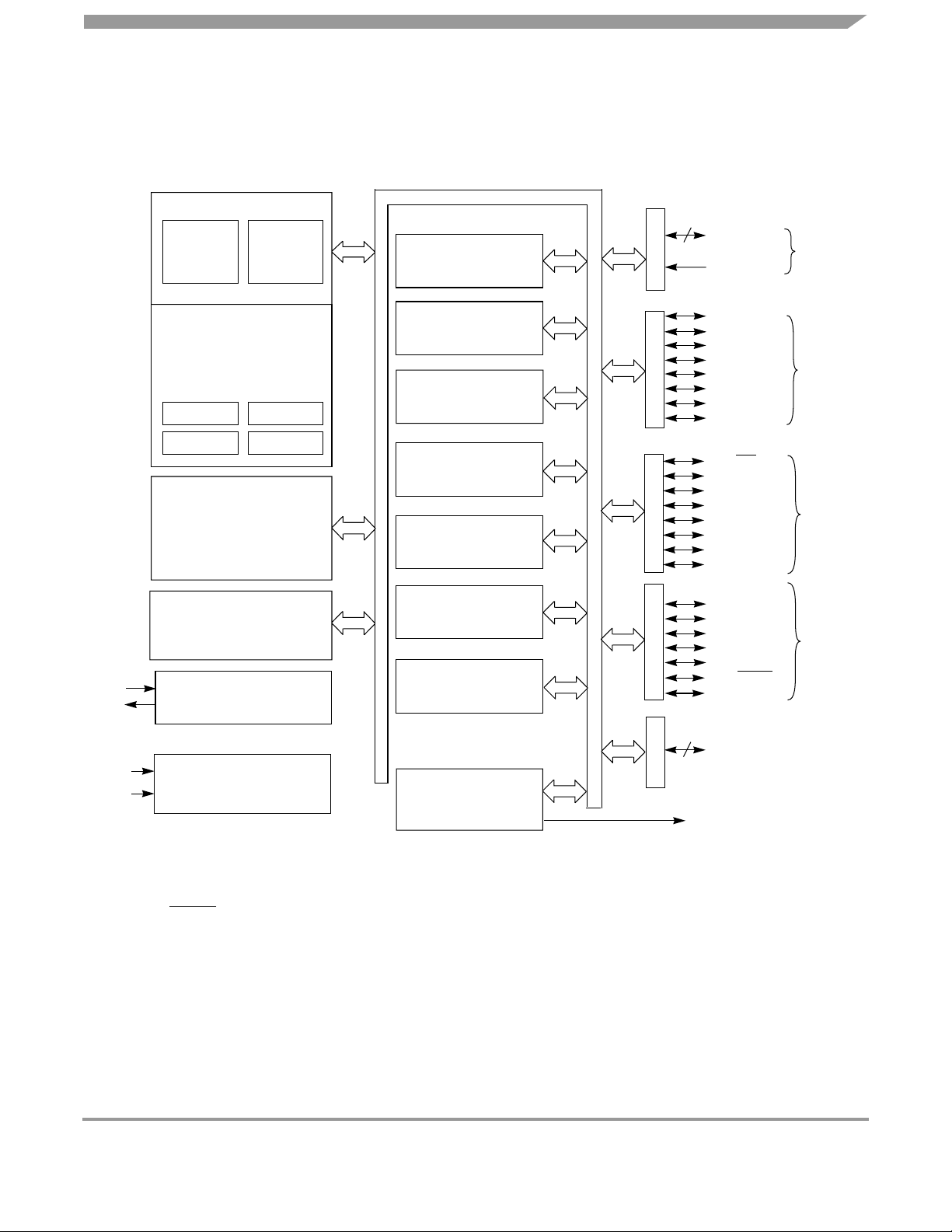

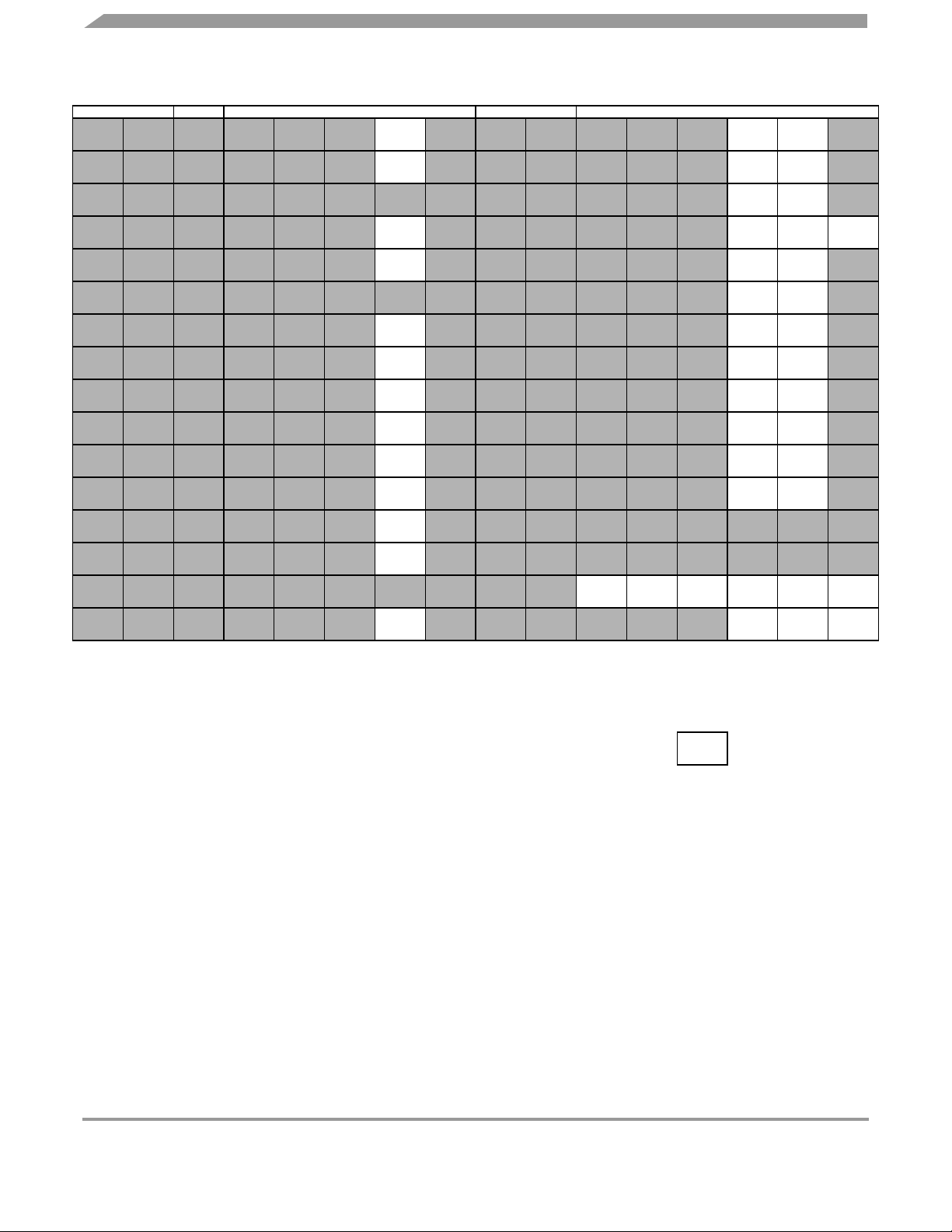

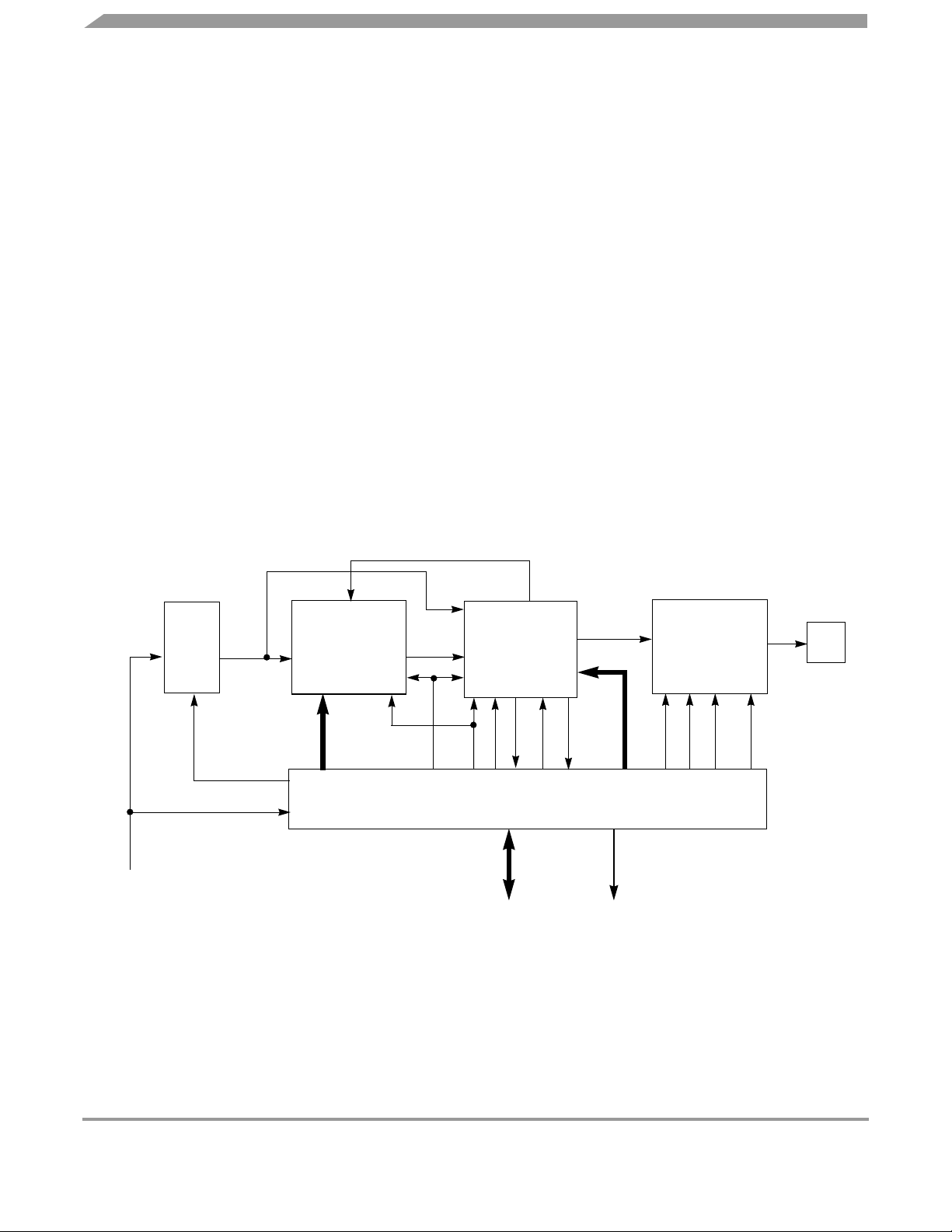

1.3 MCU Block Diagram

This block diagram shows the structure of the MC9S08RC/RD/RE/RG MCUs.

EXTAL

XTAL

HCS08 CORE

BDC

HCS08 SYSTEM CONTROL

RESETS AND INTERRUPTS

MODES OF OPERATION

POWER MANAGEMENT

RTI

IRQ LVD

USER FLASH

(RC/RD/RE/RG60 = 63,364 BYTES)

(RC/RD/RE/RG32 = 32,768 BYTES)

(RC/RD/RE16 = 16,384 BYTES)

(RC/RD/RE8 = 8192 BYTES)

USER RAM

(RC/RD/RE/RG32/60 = 2048 BYTES)

(RC/RD/RE8/16 = 1024 BYTES)

LOW-POWER OSCILLATOR

CPU

COP

INTERNAL BUS

DEBUG

MODULE (DBG)

8-BIT KEYBOARD

INTERRUPT MODULE (KBI1)

4-BIT KEYBOARD

INTERRUPT MODULE (KBI2)

SERIAL COMMUNICATIONS

INTERFACE MODULE (SCI1)

ANALOG COMPARATOR

MODULE (ACMP1)

2-CHANNEL TIMER/PWM

MODULE (TPM1)

SERIAL PERIPHERAL

INTERFACE MODULE (SPI1)

PORT A

PORT B

PORT C

PORT D

7

PTA7/KBI1P7–

PTA1/KBI1P1

PTA0/KBI1P0

PTB7/TPM1CH1

PTE6

PTB5

PTB4

PTB3

PTB2

PTB1/RxD1

PTB0/TxD1

PTC7/

PTC6/SPSCK1

PTC5/MISO1

PTC4/MOSI1

PTC3/KBI2P3

PTC2/KBI2P2

PTC1/KBI2P1

PTC0/KBI2P0

PTD6/TPM1CH0

PTD5/ACMP1+

PTD4/ACMP1–

PTD3

PTD2/IRQ

PTD1/

PTD0/BKGD/MS

NOTES1, 2, 6

NOTES 1, 5

SS1

NOTE 1

NOTES

1, 3, 4

RESET

8

V

DD

V

SS

VOLTAGE

REGULATOR

CARRIER MODULATOR

TIMER MODULE (CMT)

PORT E

PTE7–

IRO NOTE 5

NOTES:

1. Port pins are software configurable with pullup device if input port

2. PTA0 does not have a clamp diode to V

3. IRQ pin contains software configurable pullup/pulldown device if IRQ enabled (IRQPE = 1)

4. The

RESET pin contains integrated pullup device enabled if reset enabled (RSTPE = 1)

. PTA0 should not be driven above VDD.

DD

5. High current drive

6. Pins PTA[7:0] contain both pullup and pulldown devices. Pulldown available when KBI enabled (KBI1Pn = 1).

Figure 1-1 MC9S08RC/RD/RE/RG Block Diagram

Freescale Semiconductor

PTE0

NOTE 1

17MC9S08RC/RD/RE/RG

Introduction

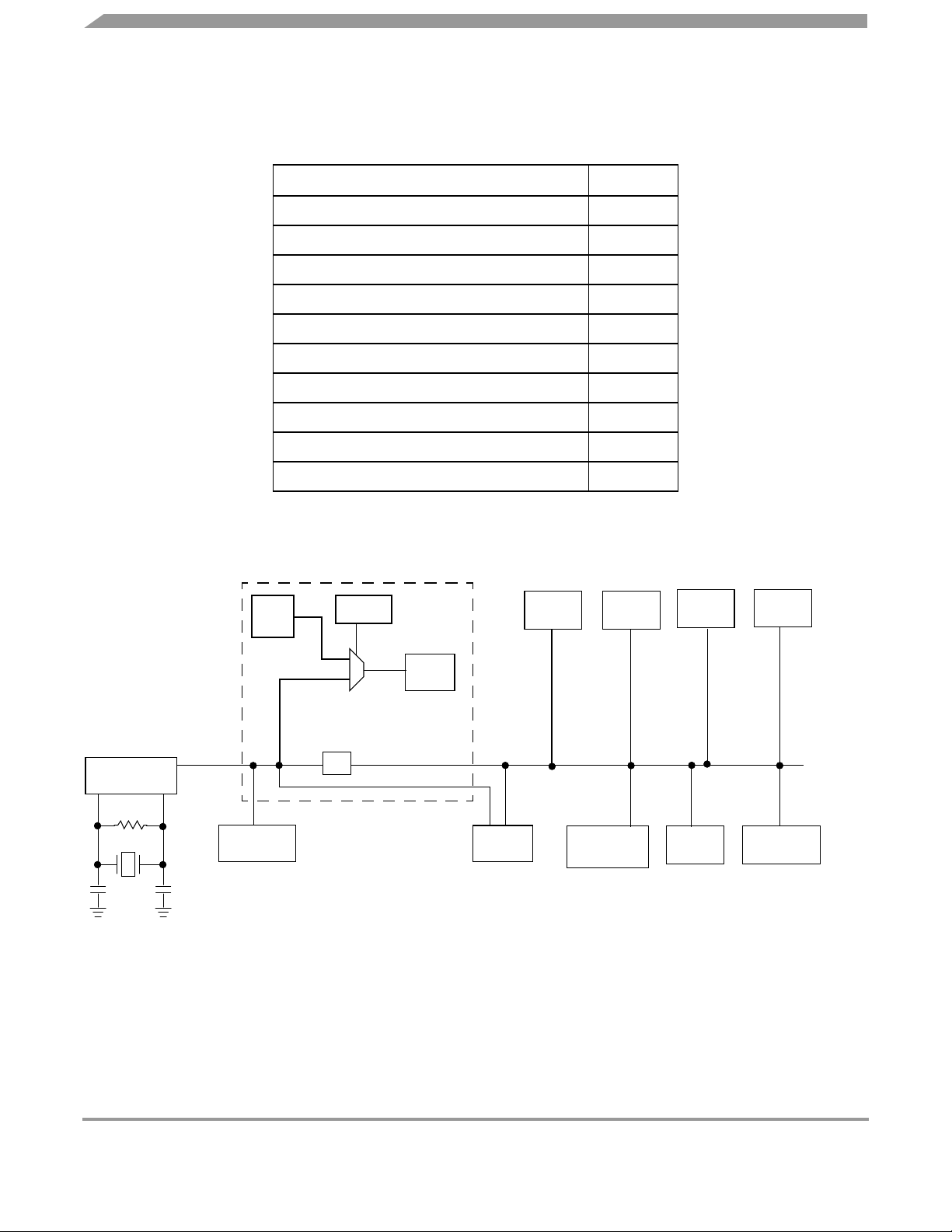

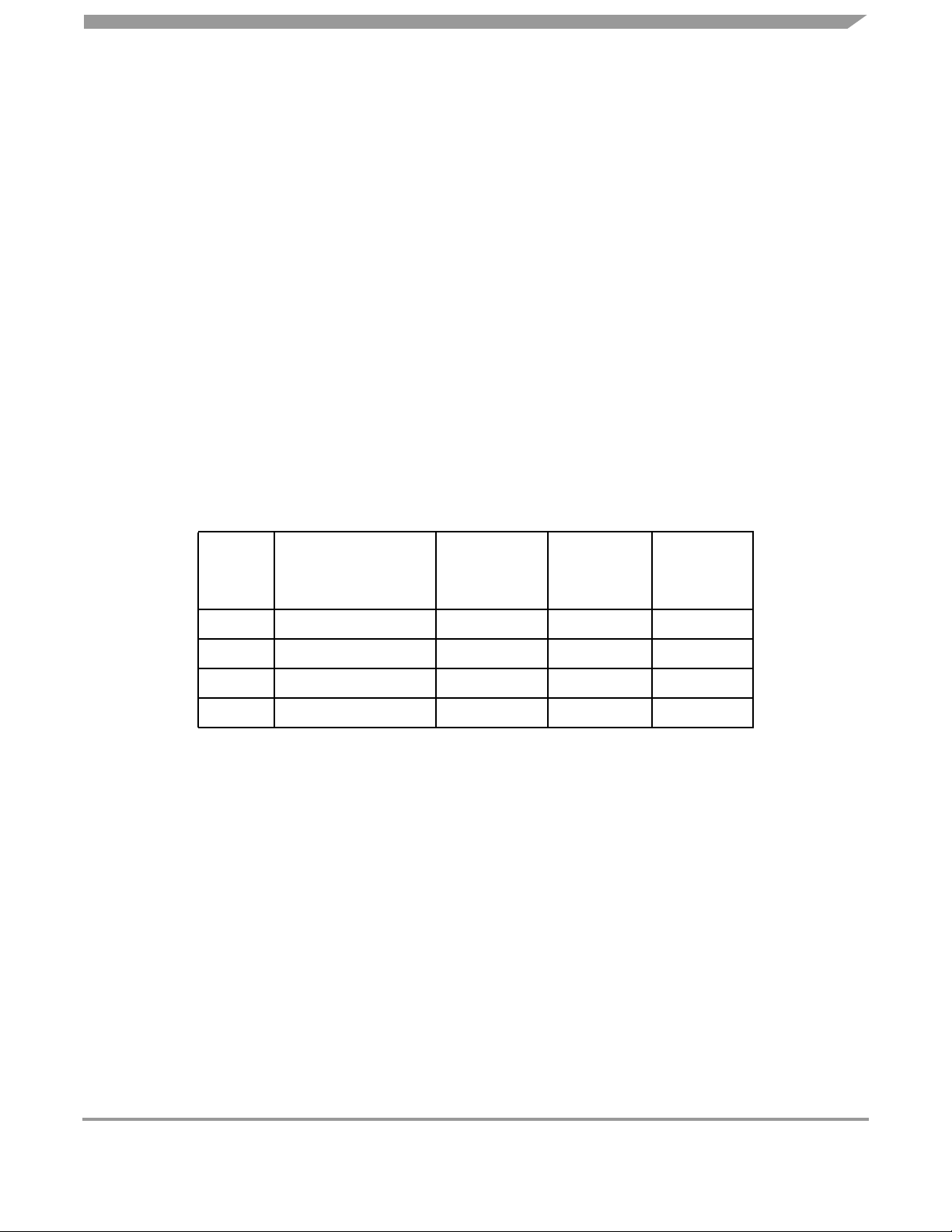

Table 1-2 lists the functional versions of the on-chip modules.

Table 1-2 Block Versions

Module Version

Analog Comparator (ACMP) 1

Carrier Modulator Transmitter (CMT) 1

Keyboard Interrupt (KBI) 1

Serial Communications Interface (SCI) 1

Serial Peripheral Interface (SPI) 3

Timer Pulse-Width Modulator (TPM) 1

Central Processing Unit (CPU) 2

Debug Module (DBG) 1

FLASH 1

System Control 2

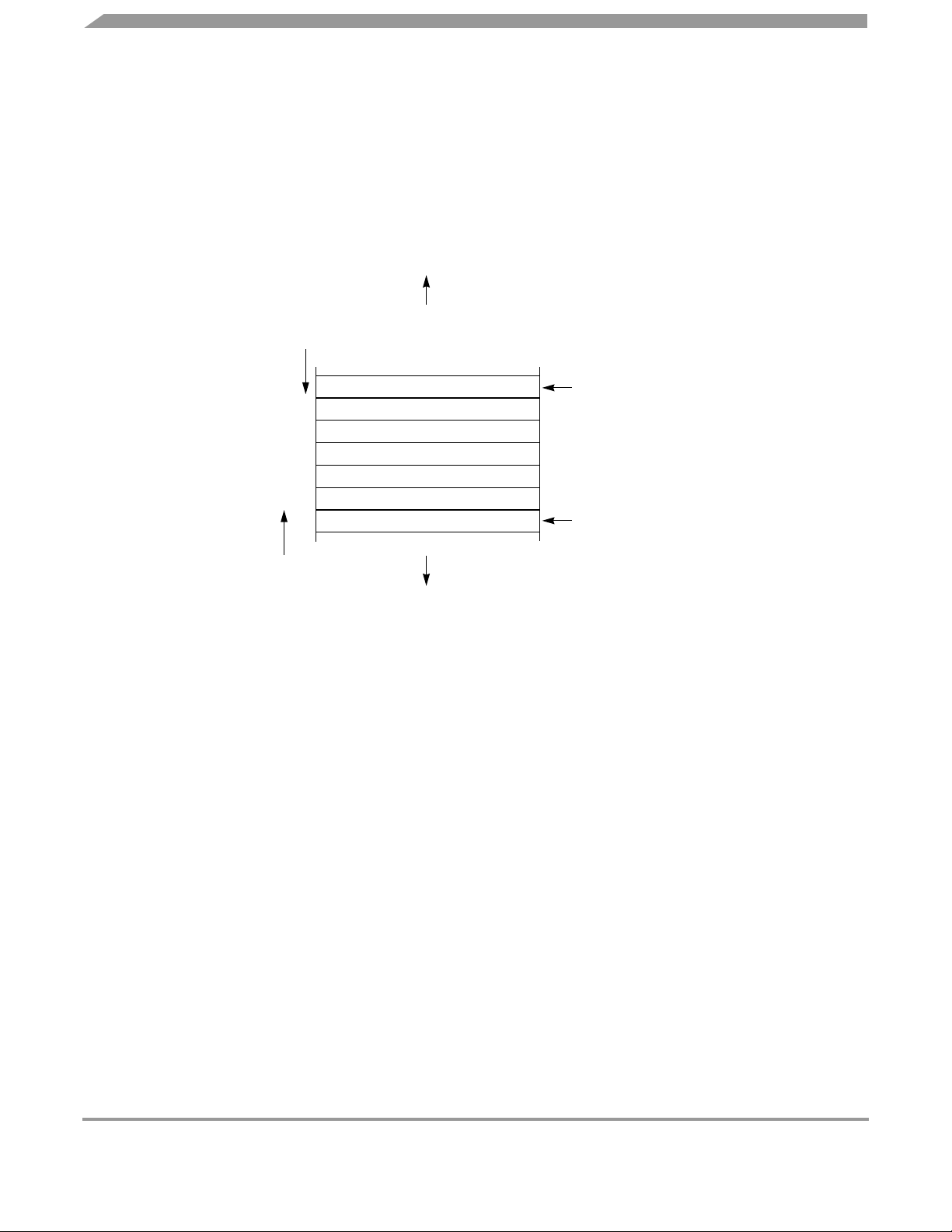

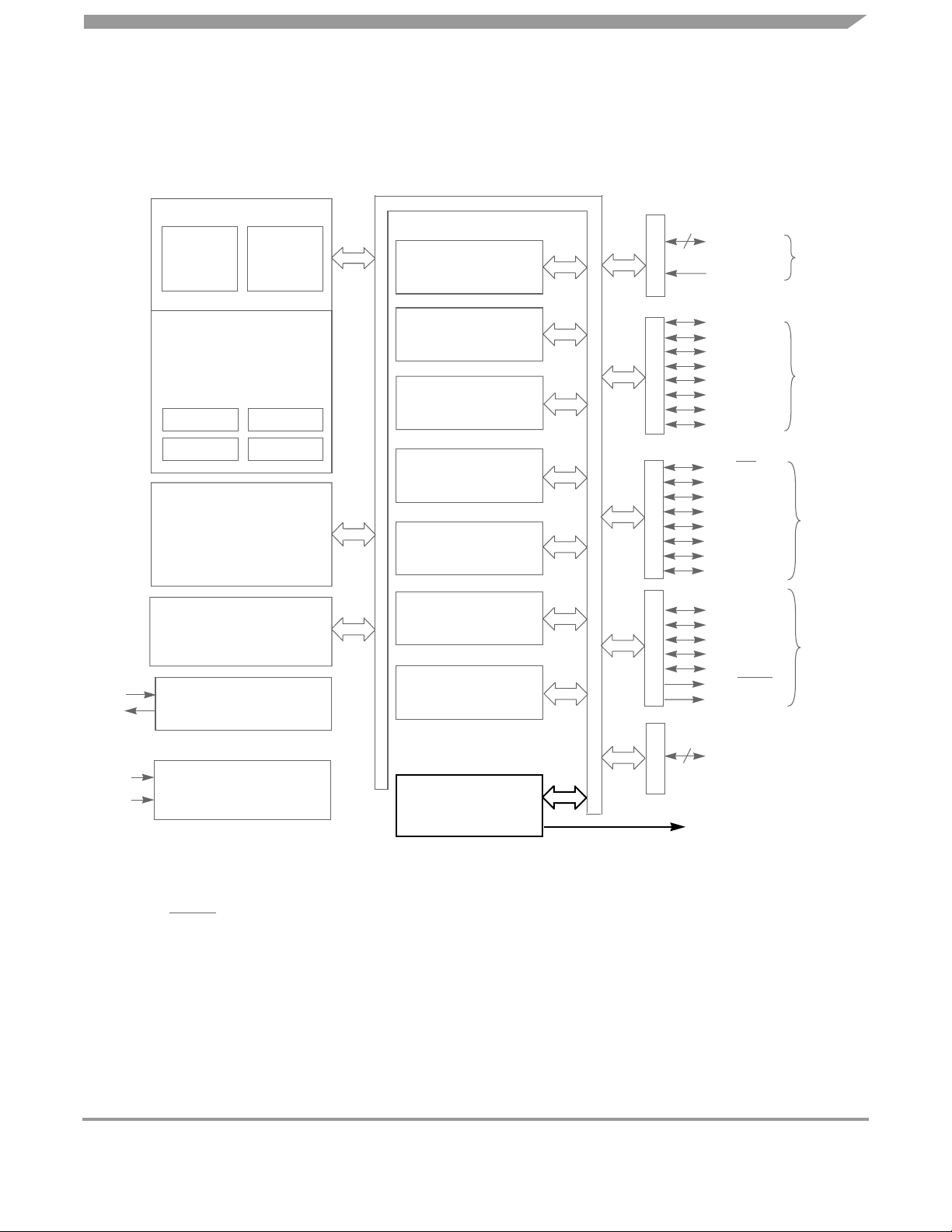

1.4 System Clock Distribution

SYSTEM

CONTROL

LOGIC

RTI

BUSCLK

OSC

RTI

OSC

OSCOUT*

CPU

* OSCOUT is the alternate BDC clock source for the MC9S08RC/RD/RE/RG.

RTICLKS

÷2

Figure 1-2 System Clock Distribution Diagram

BDC

TPM

ACMP

CMT

SCI

RAM FLASH

SPI

FLASH has frequency

requirements for program

and erase operation.

See Appendix A.

Figure 1-2 shows a simplified clock connection diagram for the MCU. The CPU operates at the input

frequency of the oscillator. The bus clock frequency is half of the oscillator frequency and is used by all

of the internal circuits with the exception of the CPU and RTI. The RTI can use either the oscillator input

or the internal RTI oscillator as its clock source.

MC9S08RC/RD/RE/RG18

Freescale Semiconductor

SoC Guide — MC9S08RG60/D Rev 1.10

Chapter 2 Pins and Connections

2.1 Introduction

This section describes signals that connect to package pins. It includes a pinout diagram, a table of signal

properties, and detailed discussion of signals.

2.2 Device Pin Assignment

PTA3/KBI1P3

PTE5

38

18

PTE4

37

19

36

20

PTA1/KBI1P1

PTA2/KBI1P2

34

35

32

31

30

29

28

27

26

25

24

21

22

PTA0/KBI1P0

33

PTD6/TPM1CH0

PTD5/ACMP1+

PTD4/ACMP1–

EXTAL

XTAL

PTD3

PTD2/IRQ

PTD1/RESET

PTD0/BKGD/MS

PTC7/SS1

23

PTB0/TxD1

PTB1/RxD1

PTB2

PTB3

PTB4

V

V

IRO

PTB5

PTB6

PTB7/TPM1CH1

PTA7/KBI1P7

PTA6/KBI1P6

PTA5/KBI1P5

44

43

1

2

3

4

5

6

DD

7

SS

8

9

10

11

12

42

13

14

PTE7

PTA4/KBI1P4

41

40

15

16

PTE6

39

17

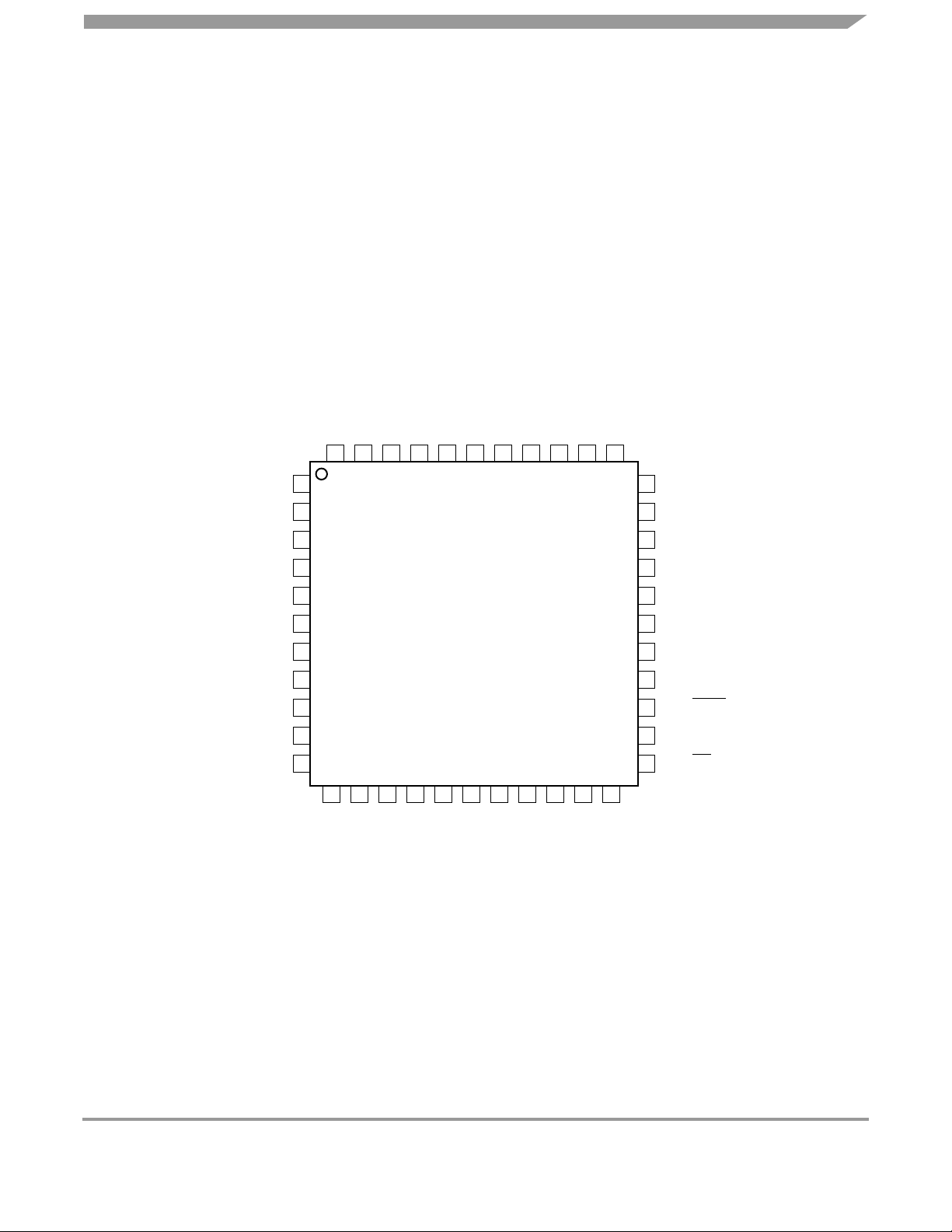

Figure 2-1 MC9S08RC/RD/RE/RG in 44-Pin LQFP Package

Freescale Semiconductor

PTC1/KBI2P1

PTC0/KBI2P0

PTC2/KBI2P2

PTC3/KBI2P3

PTE0

PTE1

PTE2

PTE3

PTC4/MOSI1

PTC5/MISO1

PTC6/SPSCK1

19MC9S08RC/RD/RE/RG

Pins and Connections

PTA0/KBI1P0

PTA1/KBI1P1

25

26

24

23

22

21

20

19

18

17

15

16

PTC7/SS1

PTC6/SPSCK1

PTD6/TPM1CH0

PTD5/ACMP1+

PTD4/ACMP1–

EXTAL

XTAL

PTD2/IRQ

PTD1/RESET

PTD0/BKGD/MS

PTB0/TxD1

PTB1/RxD1

PTB2

V

V

IRO

PTB6

PTB7/TPM1CH1

PTA7/KBI1P7

PTA6/KBI1P6

PTA5/KBI1P5

PTA4/KBI1P4

PTA3/KBI1P3

PTA2/KBI1P2

32

27

28

29

30

2

3

4

5

6

7

8

9

PTC0/KBI2P0

31

10

11

PTC1/KBI2P1

PTC2/KBI2P2

12

13

PTC4/MISO1

PTC3/KBI2P3

14

PTC5/MISO1

1

DD

SS

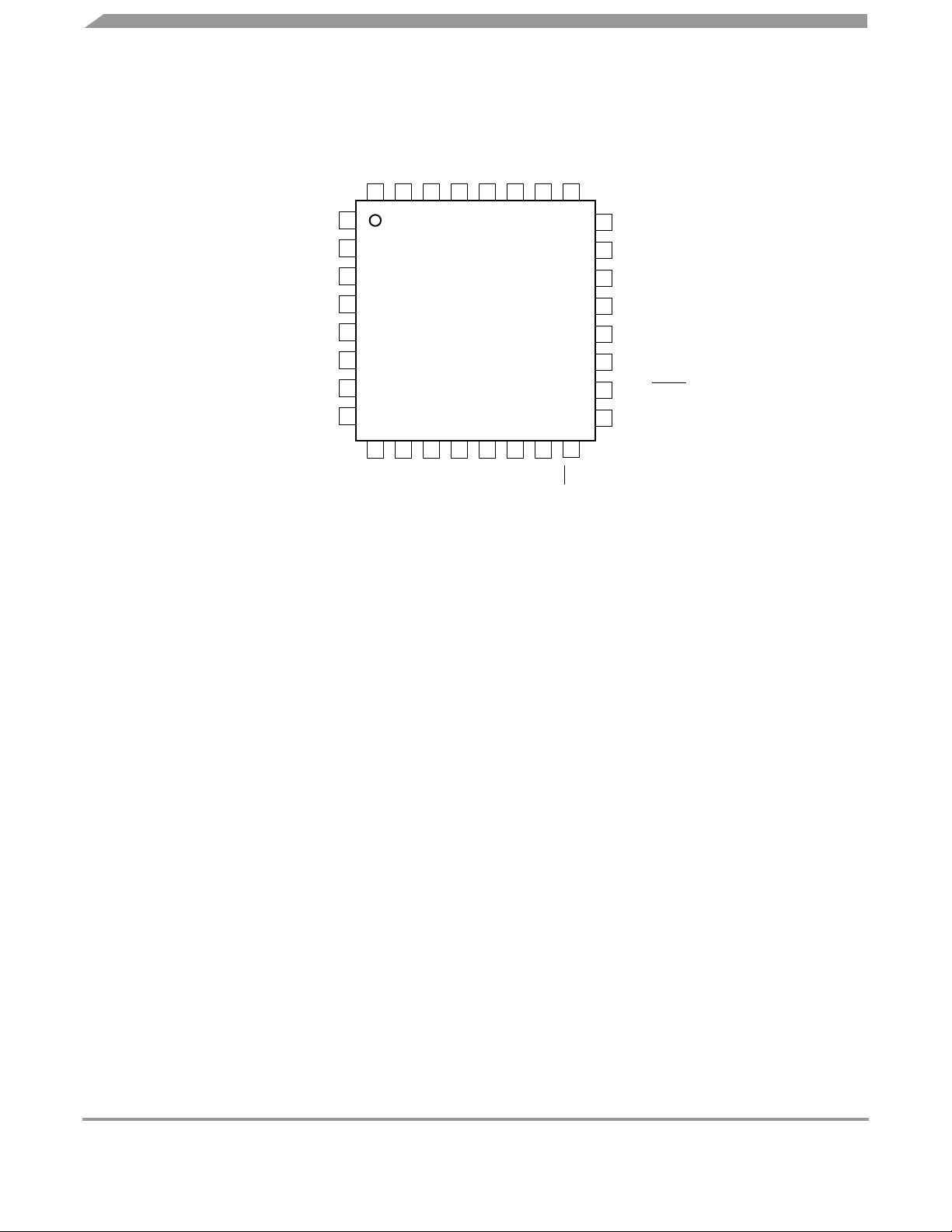

Figure 2-2 MC9S08RC/RD/RE/RG in 32-Pin LQFP Package

MC9S08RC/RD/RE/RG20

Freescale Semiconductor

SoC Guide — MC9S08RG60/D Rev 1.10

PTA5/KBI1P5

PTA6/KBI1P6

PTA7/KBI1P7

PTB0/TxD1

PTB1/RxD1

PTB2

V

V

IRO

PTB7/TPM1CH1

PTC0/KBI2P0

PTC1/KBI2P1

PTC2/KBI2P2

PTC3/KBI2P3

1

2

3

4

5

6

7

DD

8

SS

9

10

11

12

13

14

28

27

26

25

24

23

22

21

20

19

18

17

16

15

PTA4/KBI1P4

PTA3/KBI1P3

PTA2/KBI1P2

PTA1/KBI1P1

PTA0/KBI1P0

PTD6/TPM1CH0

EXTAL

XTAL

PTD1/RESET

PTD0/BKGD/MS

PTC7/SS1

PTC6/SPSCK1

PTC5/MISO1

PTC4/MOSI1

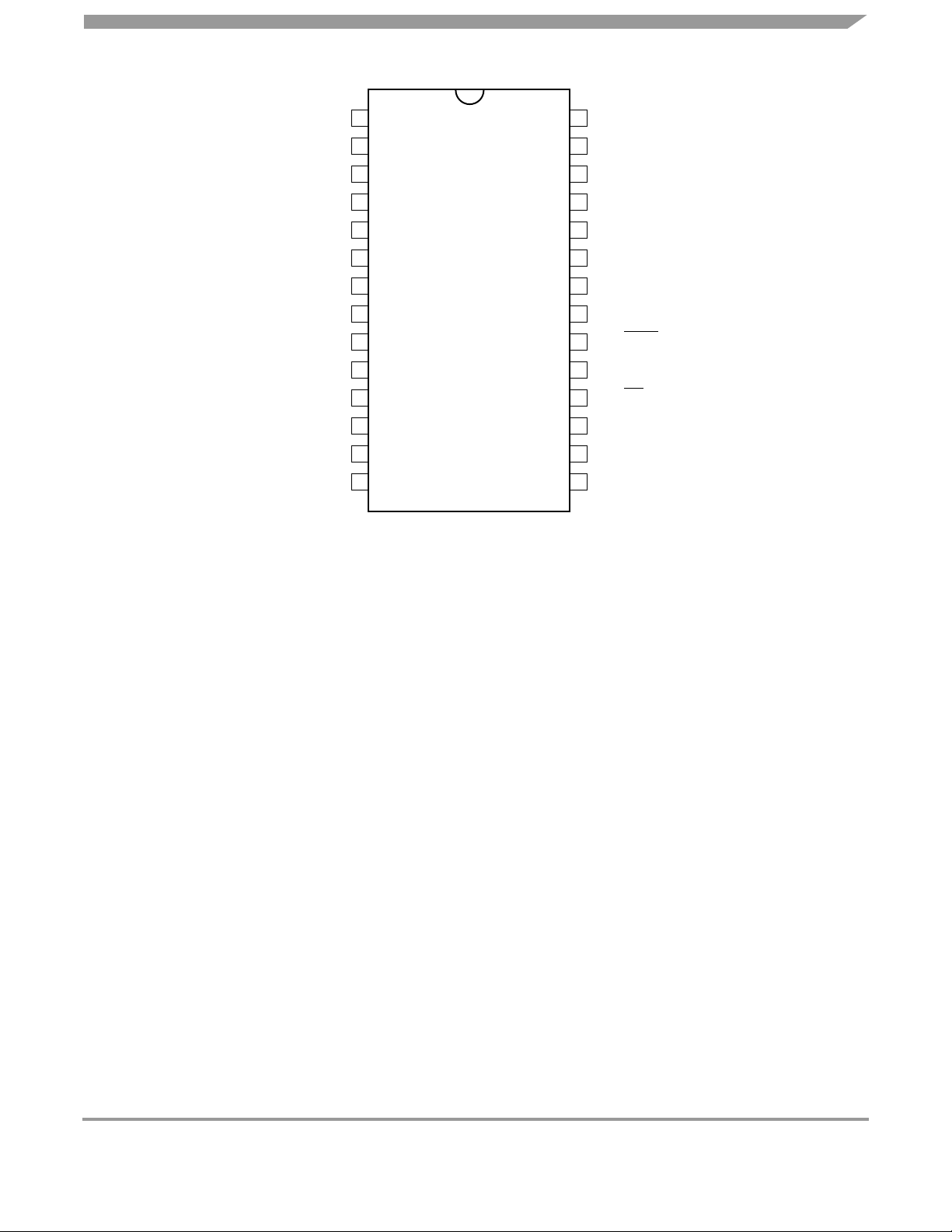

Figure 2-3 MC9S08RC/RD/RE/RG in 28-Pin SOIC Package and 28-Pin PDIP Package

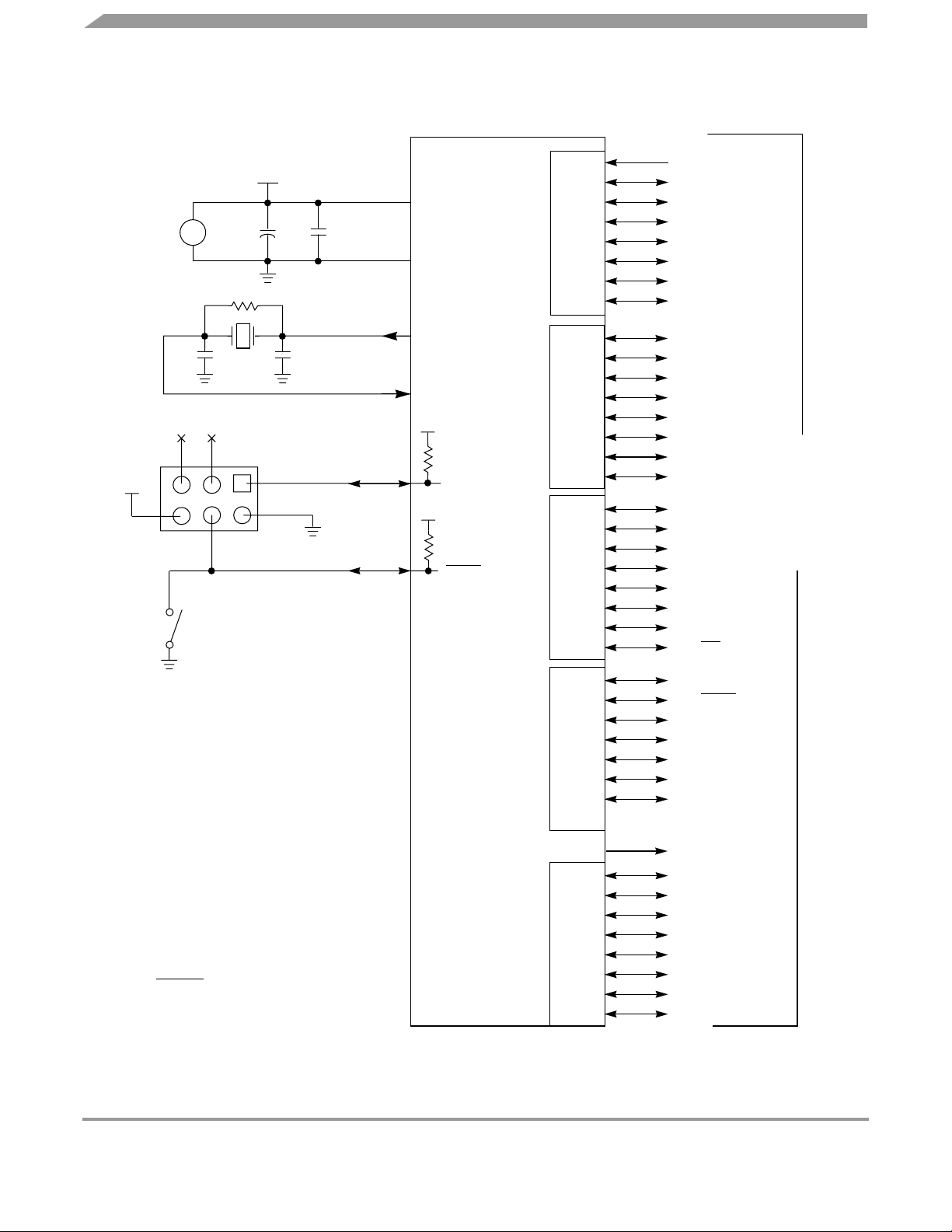

2.3 Recommended System Connections

Figure 2-4 shows pin connections that are common to almost all MC9S08RC/RD/RE/RG application

systems. A more detailed discussion of system connections follows.

Freescale Semiconductor

21MC9S08RC/RD/RE/RG

Pins and Connections

MC9S08RC/RD/RE/RG

SYSTEM

POWER

C2

BACKGROUND HEADER

V

DD

+

3 V

OPTIONAL

MANUAL

RESET

C

BLK

10 µF

X1

V

DD

V

DD

+

R

F

1

C1

C

BY

0.1 µF

V

SS

XTAL

EXTAL

BKGD/MS

NOTE 1

RESET

NOTE 2

PORT

A

PORT

B

PORT

C

PTA0/KBI1P0

PTA1/KBI1P1

PTA2/KBI1P2

PTA3/KBI1P3

PTA4/KBI1P4

PTA5/KBI1P5

PTA6/KBI1P6

PTA7/KBI1P7

PTB0/TxD1

PTB1/RxD1

PTB2

PTB3

PTB4

PTB5

PTB6

PTB7/TPM1CH1

PTC0/KBI2P0

PTC1/KBI2P1

PTC2/KBI2P2

PTC3/KBI2P3

PTC4/MOSI1

PTC5/MISO1

PTC6/SPSCK1

PTC7/SS1

I/O AND

PERIPHERAL

INTERFACE TO

APPLICATION

SYSTEM

NOTES:

1. BKGD/MS is the

same pin as PTD0.

2.

RESET is the

same pin as PTD1.

PORT

D

PORT

E

Figure 2-4 Basic System Connections

PTD0/BKGD/MS

PTD1/

RESET

PTD2/IRQ

PTD3

PTD4/ACMP1–

PTD5/ACMP1+

PTD6/TPM1CH0

IRO

PTE0

PTE1

PTE2

PTE3

PTE4

PTE5

PTE6

PTE7

MC9S08RC/RD/RE/RG22

Freescale Semiconductor

SoC Guide — MC9S08RG60/D Rev 1.10

2.3.1 Power

VDD and VSS are the primary power supply pins for the MCU. This voltage source supplies power to all

I/O buffer circuitry and to an internal voltage regulator. The internal voltage regulator provides a regulated

lower-voltage source to the CPU and other internal circuitry of the MCU.

Typically, application systems have two separate capacitors across the power pins. In this case, there

should be a bulk electrolytic capacitor, such as a 10-µF tantalum capacitor, to provide bulk charge storage

for the overall system and a 0.1-µF ceramic bypass capacitor located as near to the MCU power pins as

practical to suppress high-frequency noise.

2.3.2 Oscillator

The oscillator in the MC9S08RC/RD/RE/RG is a traditional Pierce oscillator that can accommodate a

crystal or ceramic resonator in the range of 1 MHz to 16 MHz.

Refer to Figure 2-4 for the following discussion. RFshould be a low-inductance resistor such as a carbon

composition resistor. Wire-wound resistors, and some metal film resistors, have too much inductance. C1

and C2 normally should be high-quality ceramic capacitors specifically designed for high-frequency

applications.

is used to provide a bias path to keep the EXTAL input in its linear range during crystal startup and its

R

F

value is not generally critical. Typical systems use 1 MΩ. Higher values are sensitive to humidity and

lower values reduce gain and (in extreme cases) could prevent startup.

C1 and C2 are typically in the 5-pF to 25-pF range and are chosen to match the requirements of a specific

crystal or resonator. Be sure to take into account printed circuit board (PCB) capacitance and MCU pin

capacitance when sizing C1 and C2. The crystal manufacturer typically specifies a load capacitance that

is the series combination of C1 and C2, which are usually the same size. As a first-order approximation,

use 5 pF as an estimate of combined pin and PCB capacitance for each oscillator pin (EXTAL and XTAL).

2.3.3 PTD1/RESET

The external pin reset function is shared with an output-only port function on the PTD1/RESET pin. The

reset function is enabled when RSTPE in SOPT is set. RSTPE is set following any reset of the MCU and

must be cleared in order to use this pin as an output-only port.

Whenever any reset is initiated (whether from an external signal or from an internal system), the reset pin

is driven low for about 34 cycles of f

Self_reset

later. If reset was caused by an internal source such as low-voltage reset or watchdog timeout, the circuitry

expects the reset pin sample to return a logic 1. If the pin is still low at this sample point, the reset is

assumed to be from an external source. The reset circuitry decodes the cause of reset and records it by

setting a corresponding bit in the system control reset status register (SRS).

, released, and sampled again about 38 cycles of f

Self_reset

Never connect any significant capacitance to the reset pin because that would interfere with the circuit and

sequence that detects the source of reset. If an external capacitance prevents the reset pin from rising to a

valid logic 1 before the reset sample point, all resets will appear to be external resets.

Freescale Semiconductor

23MC9S08RC/RD/RE/RG

Pins and Connections

2.3.4 Background/Mode Select (PTD0/BKGD/MS)

The background/mode select function is shared with an output-only port function on the PTD0/BKDG/MS

pin. While in reset, the pin functions as a mode select pin. Immediately after reset rises, the pin functions

as the background pin and can be used for background debug communication. While functioning as a

background/mode select pin, this pin has an internal pullup device enabled. To use as an output-only port,

BKGDPE in SOPT must be cleared.

If nothing is connected to this pin, the MCU will enter normal operating mode at the rising edge of reset.

If a debug system is connected to the 6-pin standard background debug header, it can hold BKGD/MS low

during the rising edge of reset, which forces the MCU to active background mode.

The BKGD pin is used primarily for background debug controller (BDC) communications using a custom

protocol that uses 16 clock cycles of the target MCU’s BDC clock per bit time. The target MCU’s BDC

clock could be as fast as the bus clock rate, so there should never be any significant capacitance connected

to the BKGD/MS pin that could interfere with background serial communications.

Although the BKGD pin is a pseudo open-drain pin, the background debug communication protocol

provides brief, actively driven, high speedup pulses to ensure fast rise times. Small capacitances from

cables and the absolute value of the internal pullup device play almost no role in determining rise and fall

times on the BKGD pin.

2.3.5 IRO Pin Description

The IRO pin is the output of the CMT. See Carrier Modulator Timer (CMT) Module for a detailed

description of this pin function.

2.3.6 General-Purpose I/O and Peripheral Ports

The remaining pins are shared among general-purpose I/O and on-chip peripheral functions such as timers

and serial I/O systems. (Not all pins are available in all packages. See Table 2-2.) Immediately after reset,

all 37 of these pins are configured as high-impedance general-purpose inputs with internal pullup devices

disabled.

NOTE: To avoid extra current drain from floating input pins, the reset initialization routine

in the application program should either enable on-chip pullup devices or change

the direction of unused pins to outputs so the pins do not float.

For information about controlling these pins as general-purpose I/O pins, see the Parallel Input/Output

section. For information about how and when on-chip peripheral systems use these pins, refer to the

appropriate section from Table 2-1.

MC9S08RC/RD/RE/RG24

Freescale Semiconductor

SoC Guide — MC9S08RG60/D Rev 1.10

Table 2-1 Pin Sharing References

Port Pins

PTA7–PTA0 KBI1P7–KBI1P0 Keyboard Interrupt (KBI) Module

PTB7 TPM1CH1 Timer/PWM Module (TPM) Module

PTB6–PTB2 — Parallel Input/Output

PTB1

PTB0

PTC7

PTC6

PTC5

PTC4

PTC3–PTC0 KBI2P3–KBI2P0 Keyboard Interrupt (KBI) Module

PTD6 TPM1CH0 Timer/PWM Module (TPM) Module

PTD5

PTD4

PTD2 IRQ

PTD0 BKGD/MS

Alternate

Function

RxD1

TxD1

SS1

SPSCK1

MISO1

MOSI1

ACMP1+

ACMP1–

RESET

Reference

Serial Communications Interface (SCI) Module

Serial Peripheral Interface (SPI) Module

Analog Comparator (ACMP) Module

Resets, Interrupts, and System ConfigurationPTD1

(1)

PTE7–PTE0 — Parallel Input/Output

NOTES:

1. See this section for information about modules that share these pins.

When an on-chip peripheral system is controlling a pin, data direction control bits still determine what is

read from port data registers even though the peripheral module controls the pin direction by controlling

the enable for the pin’s output buffer. See the Parallel Input/Output section for more details.

Pullup enable bits for each input pin control whether on-chip pullup devices are enabled whenever the pin

is acting as an input even if it is being controlled by an on-chip peripheral module. When the PTA7–PTA4

pins are controlled by the KBI module and are configured for rising-edge/high-level sensitivity, the pullup

enable control bits enable pulldown devices rather than pullup devices. Similarly, when PTD2 is

configured as the IRQ input and is set to detect rising edges, the pullup enable control bit enables a

pulldown device rather than a pullup device.

Freescale Semiconductor

25MC9S08RC/RD/RE/RG

Pins and Connections

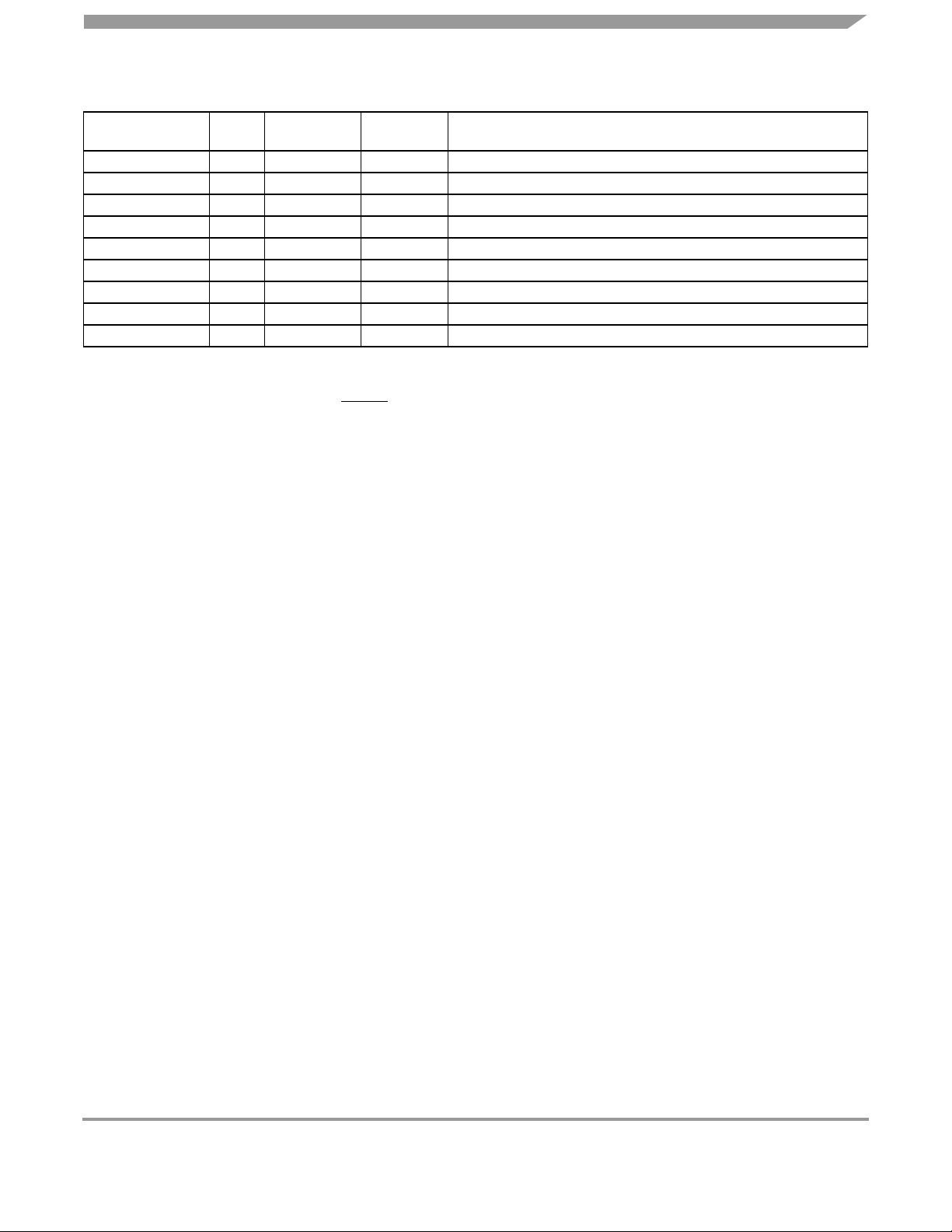

2.3.7 Signal Properties Summary

Table 2-2 summarizes I/O pin characteristics. These characteristics are determined by the way the

common pin interfaces are hardwired to internal circuits.

Table 2-2 Signal Properties

Pin

Name

V

DD

V

SS

XTAL O — — Crystal oscillator output

EXTAL I — — Crystal oscillator input

IRO O Y — Infrared output

PTA0/KBI1P0 I N SWC

PTA1/KBI1P1 I/O N SWC

PTA2/KBI1P2 I/O N SWC

PTA3/KBI1P3 I/O N SWC

PTA4/KBI1P4 I/O N SWC

PTA5/KBI1P5 I/O N SWC

PTA6/KBI1P6 I/O N SWC

PTA7/KBI1P7 I/O N SWC

PTB0/TxD1 I/O Y SWC

PTB1/RxD1 I/O Y SWC

PTB2 I/O Y SWC

PTB3 I/O Y SWC Available only in 44-LQFP package

PTB4 I/O Y SWC Available only in 44-LQFP package

PTB5 I/O Y SWC Available only in 44-LQFP package

PTB6 I/O Y SWC Available only in 32- or 44-LQFP packages

PTB7/TPM1CH1 I/O Y SWC

PTC0/KBI2P0 I/O N SWC

PTC1/KBI2P1 I/O N SWC

PTC2/KBI2P2 I/O N SWC

PTC3/KBI2P3 I/O N SWC

PTC4/MOSI1 I/O N SWC

PTC5/MISO1 I/O N SWC

PTC6/SPSCK1 I/O N SWC

SS1 I/O N SWC

PTC7/

PTD0/BKGD/MS I/O N

PTD1/

RESET I/O N

PTD2/IRQ I/O N

PTD3 I/O N SWC Available only in 44-LQFP package

PTD4/ACMP1– I/O N SWC Available only in 32- or 44-LQFP packages

PTD5/ACMP1+ I/O N SWC Available only in 32- or 44-LQFP packages

Dir

(1)

High

Current Pin

——

——

Pullup

SWC

SWC

SWC

(2)

PTA0 does not have a clamp diode to V

driven above V

(3)

Output-only when configured as PTD0 pin. Pullup enabled.

(3)

Output-only when configured as PTD1 pin.

(4)

Available only in 32- or 44-LQFP packages

DD

.

Comments

. PTA0 should not be

DD

MC9S08RC/RD/RE/RG26

Freescale Semiconductor

SoC Guide — MC9S08RG60/D Rev 1.10

Table 2-2 Signal Properties (Continued)

Pin

Name

PTD6/TPM1CH0 I/O N SWC

PTE0 I/O N SWC Available only in 44-LQFP package

PTE1 I/O N SWC Available only in 44-LQFP package

PTE2 I/O N SWC Available only in 44-LQFP package

PTE3 I/O N SWC Available only in 44-LQFP package

PTE4 I/O N SWC Available only in 44-LQFP package

PTE5 I/O N SWC Available only in 44-LQFP package

PTE6 I/O N SWC Available only in 44-LQFP package

PTE7 I/O N SWC Available only in 44-LQFP package

NOTES:

1. Unless otherwise indicated, all digital inputs have input hysteresis.

2. SWC is software-controlled pullup resistor, the register is associated with the respective port.

3. When these pins are configured as

4. When configured for the IRQ function, this pin will have a pullup device enabled when the IRQ is set for falling edge

detection and a pulldown device enabled when the IRQ is set for rising edge detection.

Dir

(1)

High

Current Pin

Pullup

RESET or BKGD/MS pullup device is enabled.

(2)

Comments

Freescale Semiconductor

27MC9S08RC/RD/RE/RG

Pins and Connections

MC9S08RC/RD/RE/RG28

Freescale Semiconductor

SoC Guide — MC9S08RG60/D Rev 1.10

Chapter 3 Modes of Operation

3.1 Introduction

The operating modes of the MC9S08RC/RD/RE/RG are described in this section. Entry into each mode,

exit from each mode, and functionality while in each of the modes are described.

3.2 Features

• Active background mode for code development

• Wait mode:

– CPU shuts down to conserve power

– System clocks running

– Full voltage regulation maintained

• Stop modes:

– System clocks stopped; voltage regulator in standby

– Stop1 — Full power down of internal circuits for maximum power savings

– Stop2 — Partial power down of internal circuits, RAM remains operational

– Stop3 — All internal circuits powered for fast recovery

3.3 Run Mode

This is the normal operating mode for the MC9S08RC/RD/RE/RG. This mode is selected when the

BKGD/MS pin is high at the rising edge of reset. In this mode, the CPU executes code from internal

memory with execution beginning at the address fetched from memory at $FFFE:$FFFF after reset.

3.4 Active Background Mode

The active background mode functions are managed through the background debug controller (BDC) in

the HCS08 core. The BDC, together with the on-chip debug module (DBG), provide the means for

analyzing MCU operation during software development.

Active background mode is entered in any of five ways:

• When the BKGD/MS pin is low at the rising edge of reset

• When a BACKGROUND command is received through the BKGD pin

• When a BGND instruction is executed

• When encountering a BDC breakpoint

• When encountering a DBG breakpoint

Freescale Semiconductor

29MC9S08RC/RD/RE/RG

Modes of Operation

After active background mode is entered, the CPU is held in a suspended state waiting for serial

background commands rather than executing instructions from the user’s application program.

Background commands are of two types:

• Non-intrusive commands, defined as commands that can be issued while the user program is

running. Non-intrusive commands can be issued through the BKGD pin while the MCU is in run

mode; non-intrusive commands can also be executed when the MCU is in the active background

mode. Non-intrusive commands include:

– Memory access commands

– Memory-access-with-status commands

– BDC register access commands

– BACKGROUND command

• Active background commands, which can only be executed while the MCU is in active background

mode, include commands to:

– Read or write CPU registers

– Trace one user program instruction at a time

– Leave active background mode to return to the user’s application program (GO)

The active background mode is used to program a bootloader or user application program into the FLASH

program memory before the MCU is operated in run mode for the first time. When the

MC9S08RC/RD/RE/RG is shipped from the Freescale Semiconductor factory, the FLASH program

memory is usually erased so there is no program that could be executed in run mode until the FLASH

memory is initially programmed. The active background mode can also be used to erase and reprogram

the FLASH memory after it has been previously programmed.

For additional information about the active background mode, refer to the Development Support section.

3.5 Wait Mode

Wait mode is entered by executing a WAIT instruction. Upon execution of the WAIT instruction, the CPU

enters a low-power state in which it is not clocked. The I bit in CCR is cleared when the CPU enters the

wait mode, enabling interrupts. When an interrupt request occurs, the CPU exits the wait mode and

resumes processing, beginning with the stacking operations leading to the interrupt service routine.

Only the BACKGROUND command and memory-access-with-status commands are available when the

MCU is in wait mode. The memory-access-with-status commands do not allow memory access, but they

report an error indicating that the MCU is in either stop or wait mode. The BACKGROUND command

can be used to wake the MCU from wait mode and enter active background mode.

MC9S08RC/RD/RE/RG30

Freescale Semiconductor

SoC Guide — MC9S08RG60/D Rev 1.10

3.6 Stop Modes

One of three stop modes is entered upon execution of a STOP instruction when the STOPE bit in the

system option register is set. In all stop modes, all internal clocks are halted. If the STOPE bit is not set

when the CPU executes a STOP instruction, the MCU will not enter any of the stop modes and an illegal

opcode reset is forced. The stop modes are selected by setting the appropriate bits in SPMSC2.

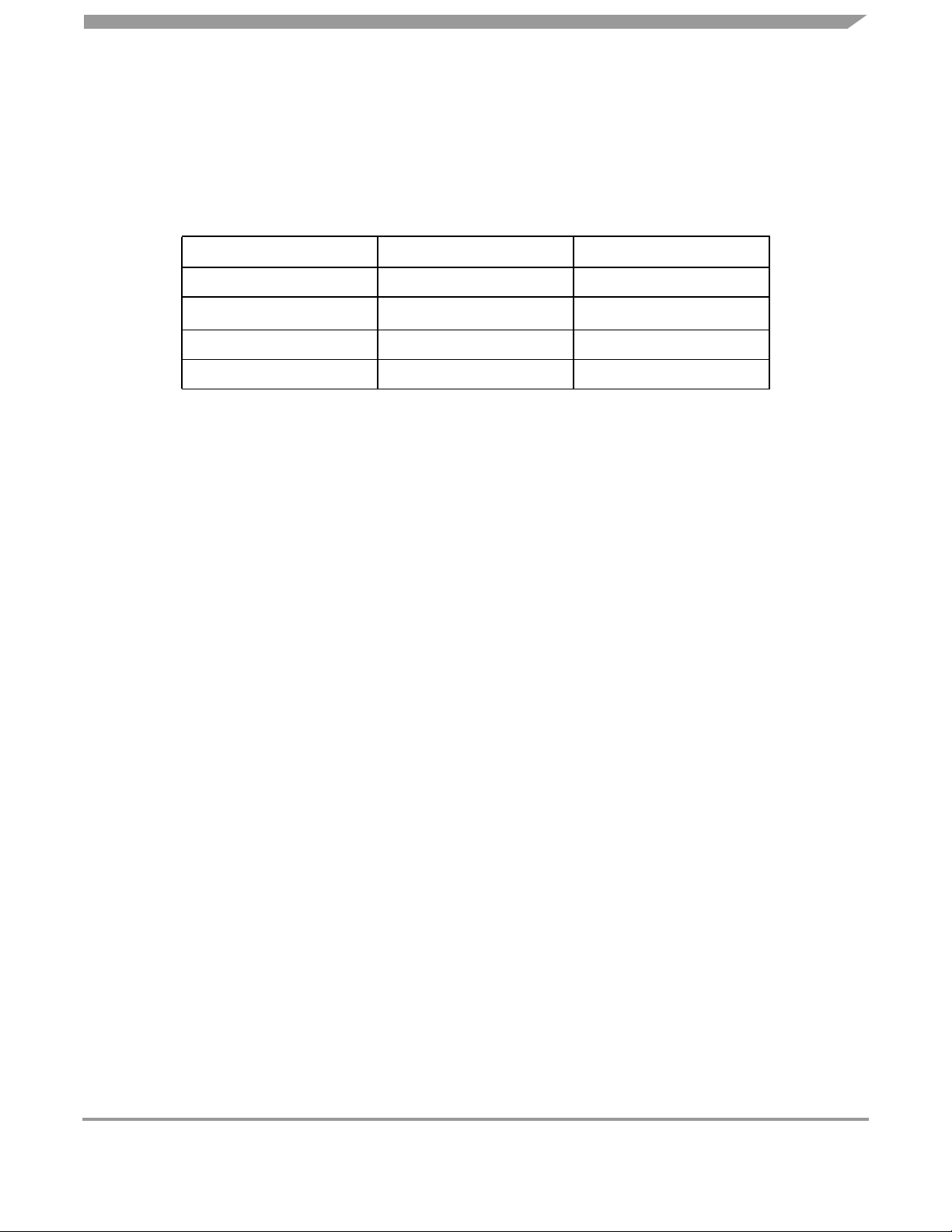

Table 3-1 summarizes the behavior of the MCU in each of the stop modes.

Table 3-1 Stop Mode Behavior

CPU, Digital

Mode PDC PPDC

Stop1 1 0 Off Off Off Standby Standby Reset Off

Peripherals,

FLASH

RAM OSC ACMP Regulator I/O Pins RTI

Stop2 1 1 Off Standby Off Standby Standby

Stop3 0

Don’t

care

Standby Standby Off Standby Standby

States

held

States

held

Optionally on

Optionally on

3.6.1 Stop1 Mode

Stop1 mode provides the lowest possible standby power consumption by causing the internal circuitry of

the MCU to be powered down. To enter stop1, the user must execute a STOP instruction with the PDC bit

in SPMSC2 set and the PPDC bit clear. Stop1 can be entered only if the LVD reset is disabled

(LVDRE = 0).

When the MCU is in stop1 mode, all internal circuits that are powered from the voltage regulator are

turned off. The voltage regulator is in a low-power standby state, as are the OSC and ACMP.

Exit from stop1 is done by asserting any of the wakeup pins on the MCU:

have been enabled. IRQ and KBI pins are always active-low when used as wakeup pins in stop1 regardless

of how they were configured before entering stop1.

Upon wakeup from stop1 mode, the MCU will start up as from a power-on reset (POR). The CPU will

take the reset vector.

RESET, IRQ, or KBI, which

3.6.2 Stop2 Mode

Stop2 mode provides very low standby power consumption and maintains the contents of RAM and the

current state of all of the I/O pins. To select entry into stop2 upon execution of a STOP instruction, the

user must execute a STOP instruction with the PPDC and PDC bits in SPMSC2 set. Stop2 can be entered

only if LVDRE = 0.

Before entering stop2 mode, the user must save the contents of the I/O port registers, as well as any other

memory-mapped registers that they want to restore after exit of stop2, to locations in RAM. Upon exit

from stop2, these values can be restored by user software.

Freescale Semiconductor

31MC9S08RC/RD/RE/RG

Modes of Operation

When the MCU is in stop2 mode, all internal circuits that are powered from the voltage regulator are

turned off, except for the RAM. The voltage regulator is in a low-power standby state, as is the ACMP.

Upon entry into stop2, the states of the I/O pins are latched. The states are held while in stop2 mode and

after exiting stop2 mode until a 1 is written to PPDACK in SPMSC2.

Exit from stop2 is done by asserting any of the wakeup pins:

RESET, IRQ, or KBI that have been enabled,

or through the real-time interrupt. IRQ and KBI pins are always active-low when used as wakeup pins in

stop2 regardless of how they were configured before entering stop2.

Upon wakeup from stop2 mode, the MCU will start up as from a power-on reset (POR) except pin states

remain latched. The CPU will take the reset vector. The system and all peripherals will be in their default

reset states and must be initialized.

After waking up from stop2, the PPDF bit in SPMSC2 is set. This flag may be used to direct user code to

go to a stop2 recovery routine. PPDF remains set and the I/O pin states remain latched until a 1 is written

to PPDACK in SPMSC2.

For pins that were configured as general-purpose I/O, the user must copy the contents of the I/O port

registers, which have been saved in RAM, back to the port registers before writing to the PPDACK bit. If

the port registers are not restored from RAM before writing to PPDACK, then the register bits will be in

their reset states when the I/O pin latches are opened and the I/O pins will switch to their reset states.

For pins that were configured as peripheral I/O, the user must reconfigure the peripheral module that

interfaces to the pin before writing to the PPDACK bit. If the peripheral module is not enabled before

writing to PPDACK, the pins will be controlled by their associated port control registers when the I/O

latches are opened.

3.6.3 Stop3 Mode

Upon entering stop3 mode, all of the clocks in the MCU, including the oscillator itself, are halted. The

OSC is turned off, the ACMP is disabled, and the voltage regulator is put in standby. The states of all of

the internal registers and logic, as well as the RAM content, are maintained. The I/O pin states are not

latched at the pin as in stop2. Instead they are maintained by virtue of the states of the internal logic driving

the pins being maintained.

Exit from stop3 is done by asserting

RESET, any asynchronous interrupt pin that has been enabled, or

through the real-time interrupt. The asynchronous interrupt pins are the IRQ or KBI pins.

If stop3 is exited by means of the RESET pin, then the MCU will be reset and operation will resume after

taking the reset vector. Exit by means of an asynchronous interrupt or the real-time interrupt will result in

the MCU taking the appropriate interrupt vector.

A separate self-clocked source (≈1 kHz) for the real-time interrupt allows a wakeup from stop2 or stop3

mode with no external components. When RTIS2:RTIS1:RTIS0 = 0:0:0, the real-time interrupt function

and this 1-kHz source are disabled. Power consumption is lower when the 1-kHz source is disabled, but

in that case the real-time interrupt cannot wake the MCU from stop.

MC9S08RC/RD/RE/RG32

Freescale Semiconductor

SoC Guide — MC9S08RG60/D Rev 1.10

3.6.4 Active BDM Enabled in Stop Mode

Entry into the active background mode from run mode is enabled if the ENBDM bit in BDCSCR is set.

This register is described in the Development Support section of this data sheet. If ENBDM is set when

the CPU executes a STOP instruction, the system clocks to the background debug logic remain active

when the MCU enters stop mode so background debug communication is still possible. In addition, the

voltage regulator does not enter its low-power standby state but maintains full internal regulation. The

MCU cannot enter either stop1 mode or stop2 mode if ENBDM is set.

Most background commands are not available in stop mode. The memory-access-with-status commands

do not allow memory access, but they report an error indicating that the MCU is in either stop or wait

mode. The BACKGROUND command can be used to wake the MCU from stop and enter active

background mode if the ENBDM bit is set. After active background mode is entered, all background

commands are available. Table 3-2 summarizes the behavior of the MCU in stop when entry into the active

background mode is enabled.

Table 3-2 BDM Enabled Stop Mode Behavior

CPU, Digital

Mode PDC PPDC

Peripherals,

FLASH

RAM OSC ACMP Regulator I/O Pins RTI

Stop3

Don’t

care

Don’t

care

Standby Standby On Standby On

States

held

Optionally on

3.6.5 LVD Reset Enabled in Stop Mode

The LVD system is capable of generating either an interrupt or a reset when the supply voltage drops

below the LVD voltage. If the LVD reset is enabled in stop by setting the LVDRE bit in SPMSC1 when

the CPU executes a STOP instruction, then the voltage regulator remains active during stop mode. If the

user attempts to enter either stop1 or stop2 with the LVD reset enabled (LVDRE = 1) the MCU will instead

enter stop3. Table 3-3 summarizes the behavior of the MCU in stop when LVD reset is enabled.

Table 3-3 LVD Enabled Stop Mode Behavior

CPU, Digital

Mode PDC PPDC

Stop3

Don’t

care

Don’t

care

Peripherals,

FLASH

Standby Standby On Standby On

RAM OSC ACMP Regulator I/O Pins RTI

States

held

Optionally on

3.6.6 On-Chip Peripheral Modules in Stop Mode

When the MCU enters any stop mode, system clocks to the internal peripheral modules are stopped. Even

in the exception case (ENBDM = 1), where clocks are kept alive to the background debug logic, clocks to

the peripheral systems are halted to reduce power consumption.

Freescale Semiconductor

33MC9S08RC/RD/RE/RG

Modes of Operation

I/O Pins

• All I/O pin states remain unchanged when the MCU enters stop3 mode.

• If the MCU is configured to go into stop2 mode, all I/O pin states are latched before entering stop.

Pin states remain latched until the PPDACK bit is written.

• If the MCU is configured to go into stop1 mode, all I/O pins are forced to their default reset state

upon entry into stop.

Memory

• All RAM and register contents are preserved while the MCU is in stop3 mode.

• All registers will be reset upon wakeup from stop2, but the contents of RAM are preserved. The

user may save any memory-mapped register data into RAM before entering stop2 and restore the

data upon exit from stop2.

• All registers will be reset upon wakeup from stop1 and the contents of RAM are not preserved. The

MCU must be initialized as upon reset. The contents of the FLASH memory are non-volatile and

are preserved in any of the stop modes.

OSC — In any of the stop modes, the OSC stops running.

TPM — When the MCU enters stop mode, the clock to the TPM module stops. The modules halt

operation. If the MCU is configured to go into stop2 or stop1 mode, the TPM module will be reset upon

wakeup from stop and must be reinitialized.

ACMP — When the MCU enters any stop mode, the ACMP will enter a low-power standby state

. No

compare operation will occur while in stop. If the MCU is configured to go into stop2 or stop1 mode, the

ACMP will be reset upon wakeup from stop and must be reinitialized.

KBI — During stop3, the KBI pins that are enabled continue to function as interrupt sources. During stop1

or stop2, enabled KBI pins function as wakeup inputs. When functioning as a wakeup, a KBI pin is always

active low regardless of how it was configured before entering stop1 or stop2.

SCI — When the MCU enters stop mode, the clock to the SCI module stops. The module halts operation.

If the MCU is configured to go into stop2 or stop1 mode, the SCI module will be reset upon wakeup from

stop and must be reinitialized.

SPI — When the MCU enters stop mode, the clock to the SPI module stops. The module halts operation.

If the MCU is configured to go into stop2 or stop1 mode, the SPI module will be reset upon wakeup from

stop and must be reinitialized.

CMT — When the MCU enters stop mode, the clock to the CMT module stops. The module halts

operation. If the MCU is configured to go into stop2 or stop1 mode, the CMT module will be reset upon

wakeup from stop and must be reinitialized.

Voltage Regulator — The voltage regulator enters a low-power standby state when the MCU enters any

of the stop modes unless the LVD reset function is enabled or BDM is enabled.

MC9S08RC/RD/RE/RG34

Freescale Semiconductor

SoC Guide — MC9S08RG60/D Rev 1.10

Chapter 4 Memory

4.1 MC9S08RC/RD/RE/RG Memory Map

As shown in Figure 4-1, on-chip memory in the MC9S08RC/RD/RE/RG series of MCUs consists of

RAM, FLASH program memory for nonvolatile data storage, and I/O and control/status registers. The

registers are divided into three groups:

• Direct-page registers ($0000 through $0045 for 32K and 60K parts, and $0000 through $003F for

16K and 8K parts)

• High-page registers ($1800 through $182B)

• Nonvolatile registers ($FFB0 through $FFBF)

$0000

DIRECT PAGE REGISTERS

$0045

$0046

$0845

$0846

$17FF

$1800

$182B

$182C

$FFFF

2048 BYTES

4026 BYTES

HIGH PAGE REGISTERS

59348 BYTES

MC9S08RC/RD/RE/RG60

RAM

FLASH

FLASH

DIRECT PAGE REGISTERS

RAM

2048 BYTES

UNIMPLEMENTED

4026 BYTES

HIGH PAGE REGISTERS

UNIMPLEMENTED

26580 BYTES

FLASH

32768 BYTES

MC9S08RC/RD/RE/RG32

$0000

$0045

$0046

$0845

$0846

$17FF

$1800

$182B

$182C

$8000

DIRECT PAGE REGISTERS

RAM

1024 BYTES

UNIMPLEMENTED

5056 BYTES

HIGH PAGE REGISTERS

UNIMPLEMENTED

42964 BYTES

FLASH

16384 BYTES

MC9S08RC/RD/RE16

(1)

$0000

$003F

$0040

$043F

$0440

$17FF

$1800

$182B

$182C

$BFFF

$C000

$FFFF

DIRECT PAGE REGISTERS

RAM

1024 BYTES

UNIMPLEMENTED

5056 BYTES

HIGH PAGE REGISTERS

UNIMPLEMENTED

51156 BYTES

FLASH

8192 BYTES

MC9S08RC/RD/RE8

(1)

$0000

$003F

$0040

$043F

$0440

$17FF

$1800

$182B

$182C

$DFFF

$E000

$FFFF

NOTE:

1. MC3S08RC/RD/RE16/8 ROM MCU devices have 512 bytes of RAM instead of 1K bytes.

Freescale Semiconductor

Figure 4-1 MC9S08RC/RD/RE/RG Memory Map

35MC9S08RC/RD/RE/RG

Memory

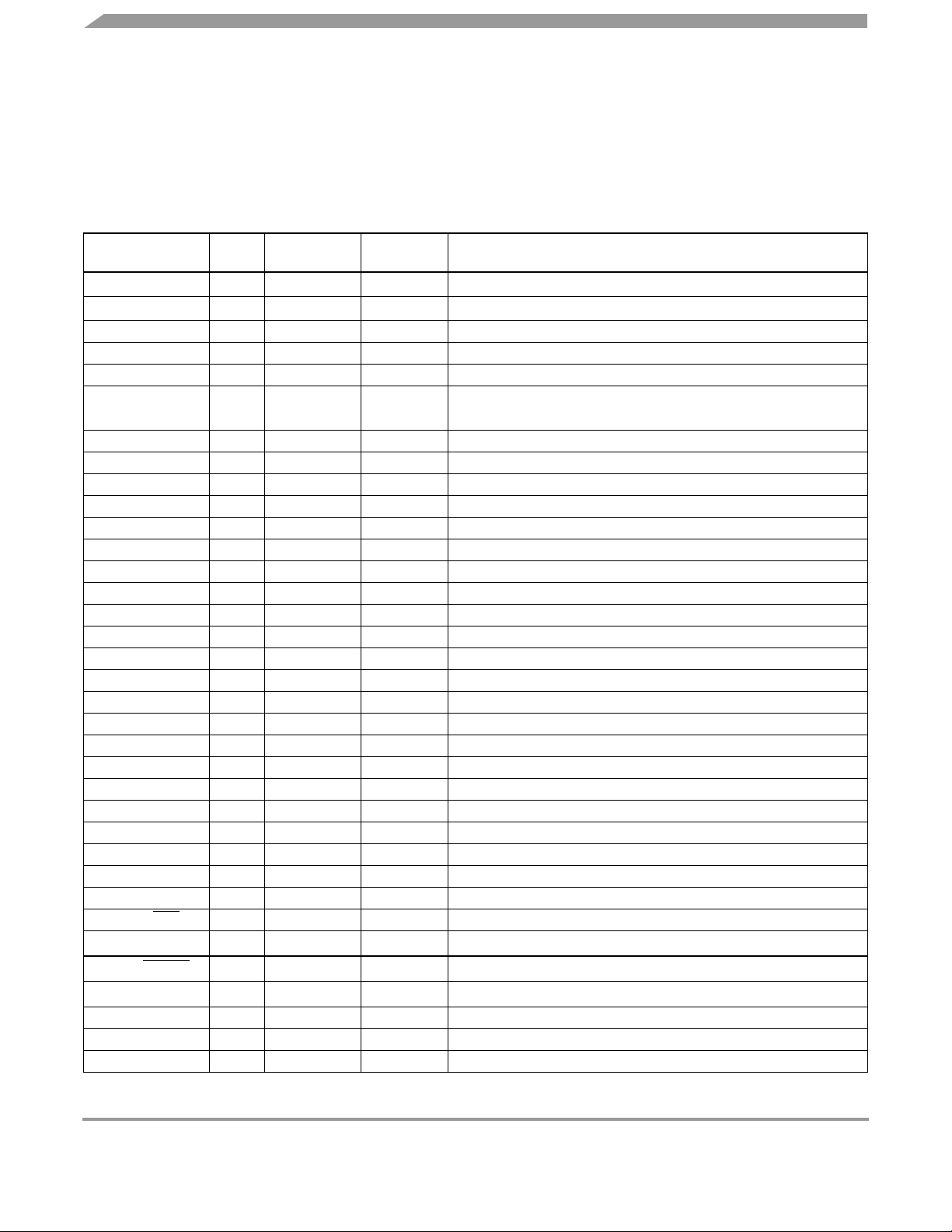

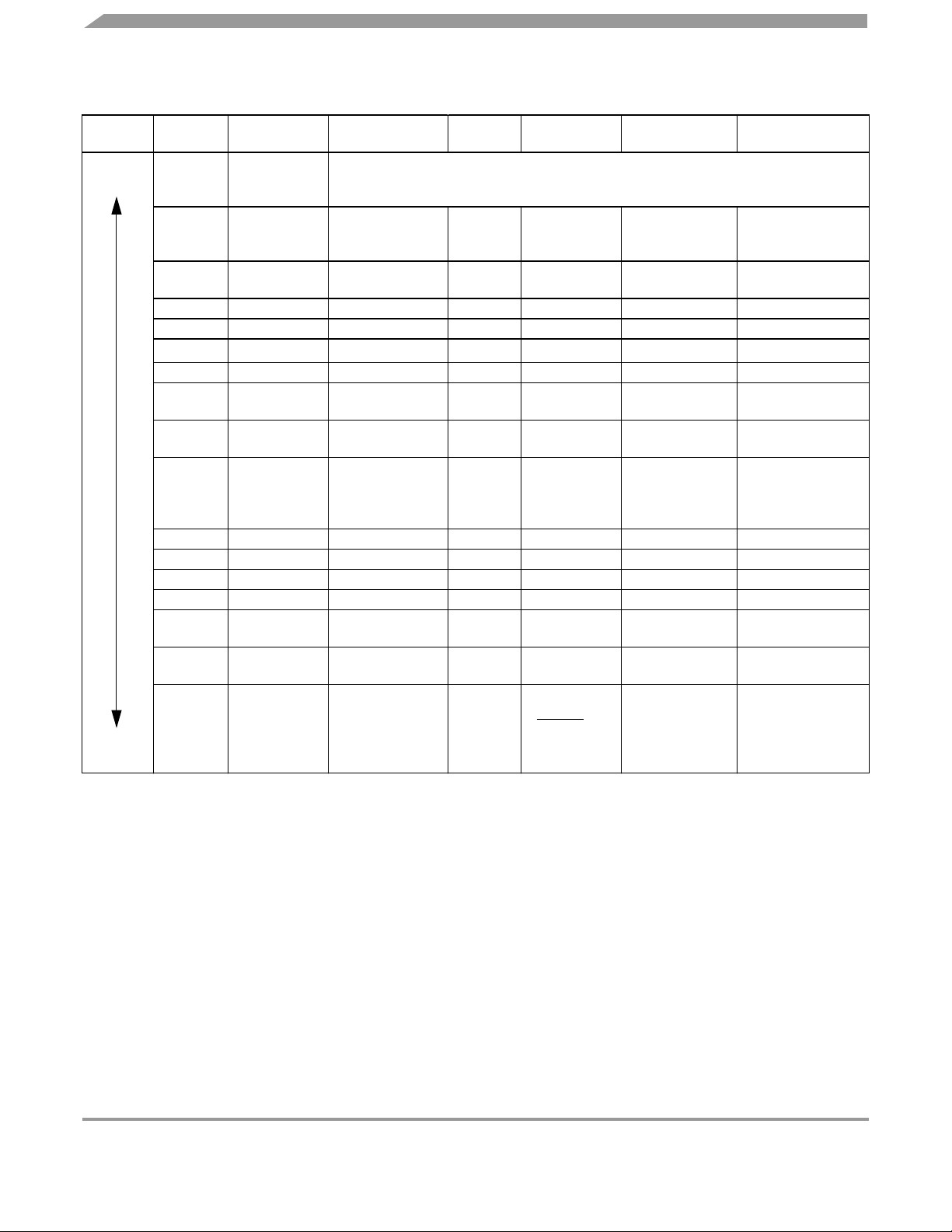

4.1.1 Reset and Interrupt Vector Assignments

Table 4-1 shows address assignments for reset and interrupt vectors. The vector names shown in this table

are the labels used in the Freescale-provided equate file for the MC9S08RC/RD/RE/RG. For more details

about resets, interrupts, interrupt priority, and local interrupt mask controls, refer to the Resets, Interrupts,

and System Configuration section.

Table 4-1 Reset and Interrupt Vectors

Vector

Numbe

r

16

through

31

15 $FFE0:FFE1

14 $FFE2:FFE3 RTI Vrti

13 $FFE4:FFE5 KBI2 Vkeyboard2

12 $FFE6:FFE7 KBI1 Vkeyboard1

11 $FFE8:FFE9

10 $FFEA:FFEB CMT Vcmt

9 $FFEC:FFED

8 $FFEE:FFEF

7 $FFF0:FFF1

6 $FFF2:FFF3 TPM Overflow Vtpm1ovf

5 $FFF4:FFF5 TPM Channel 1 Vtpm1ch1

4 $FFF6:FFF7 TPM Channel 0 Vtpm1ch0

3 $FFF8:FFF9 IRQ Virq

2 $FFFA:FFFB Low Voltage Detect Vlvd

1 $FFFC:FFFD SWI Vswi

0 $FFFE:FFFF Reset Vreset

NOTES:

1. The SPI module is not included on the MC9S08RC/RD/RE devices. This vector location is unused for those

devices.

2. The analog comparator (ACMP) module is not included on the MC9S08RD devices. This vector location is unused

for those devices.