MC9S08GB60

MC9S08GB32

MC9S08GT60

MC9S08GT32

MC9S08GT16

Data Sheet

HCS08

Microcontrollers

MC9S08GB60/D

Rev. 2.3

12/2004

freescale.com

MC9S08GB/GT Data Sheet

Covers: MC9S08GB60

MC9S08GB32

MC9S08GT60

MC9S08GT32

MC9S08GT16

MC9S08GB60

Rev. 2.3

12/2004

Revision History

To provide the most up-to-date information, the revision of our documents on the World Wide Web will

be the most current. Your printed copy may be an earlier revision. To verify you have the latest information

available, refer to:

http://freescale.com

The following revision history table summarizes changes contained in this document.

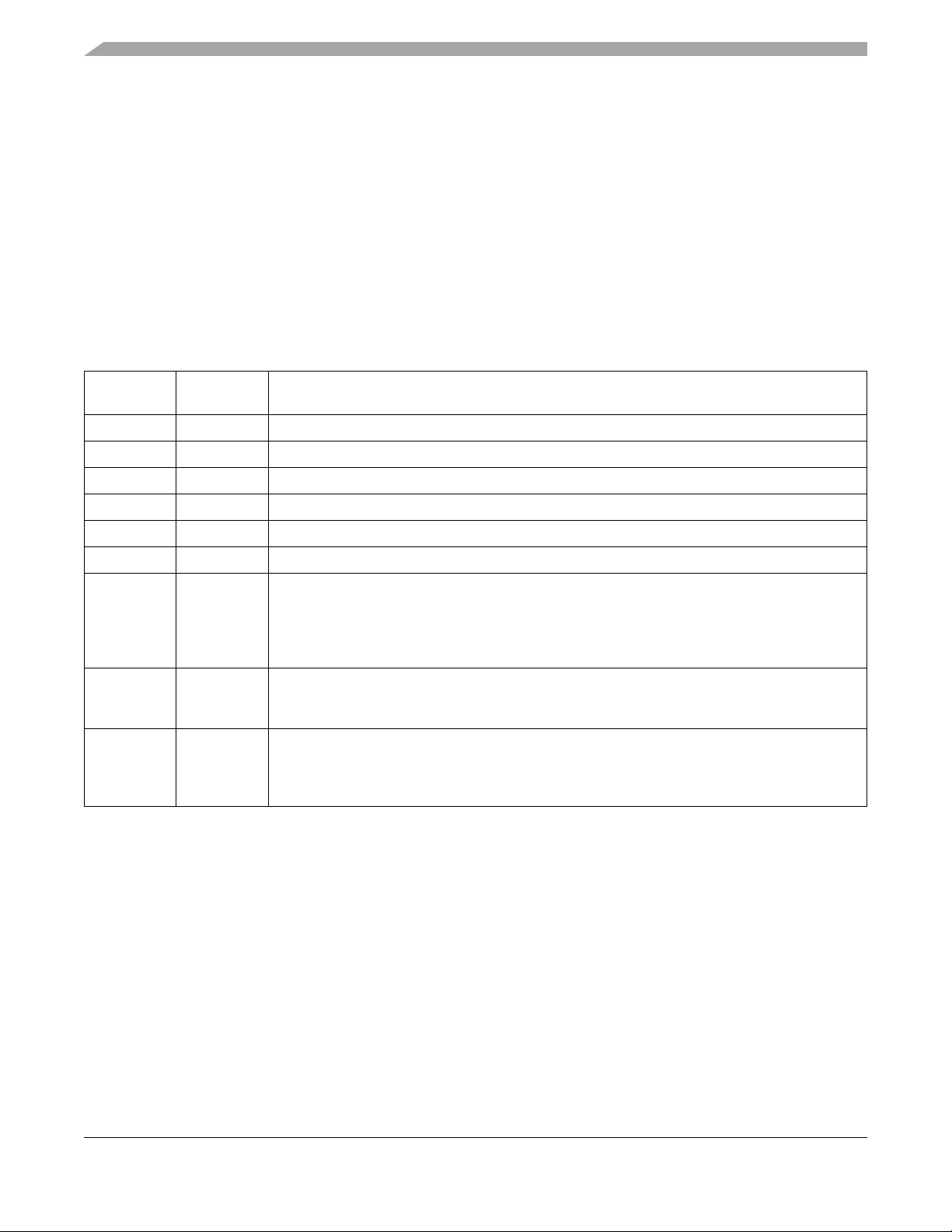

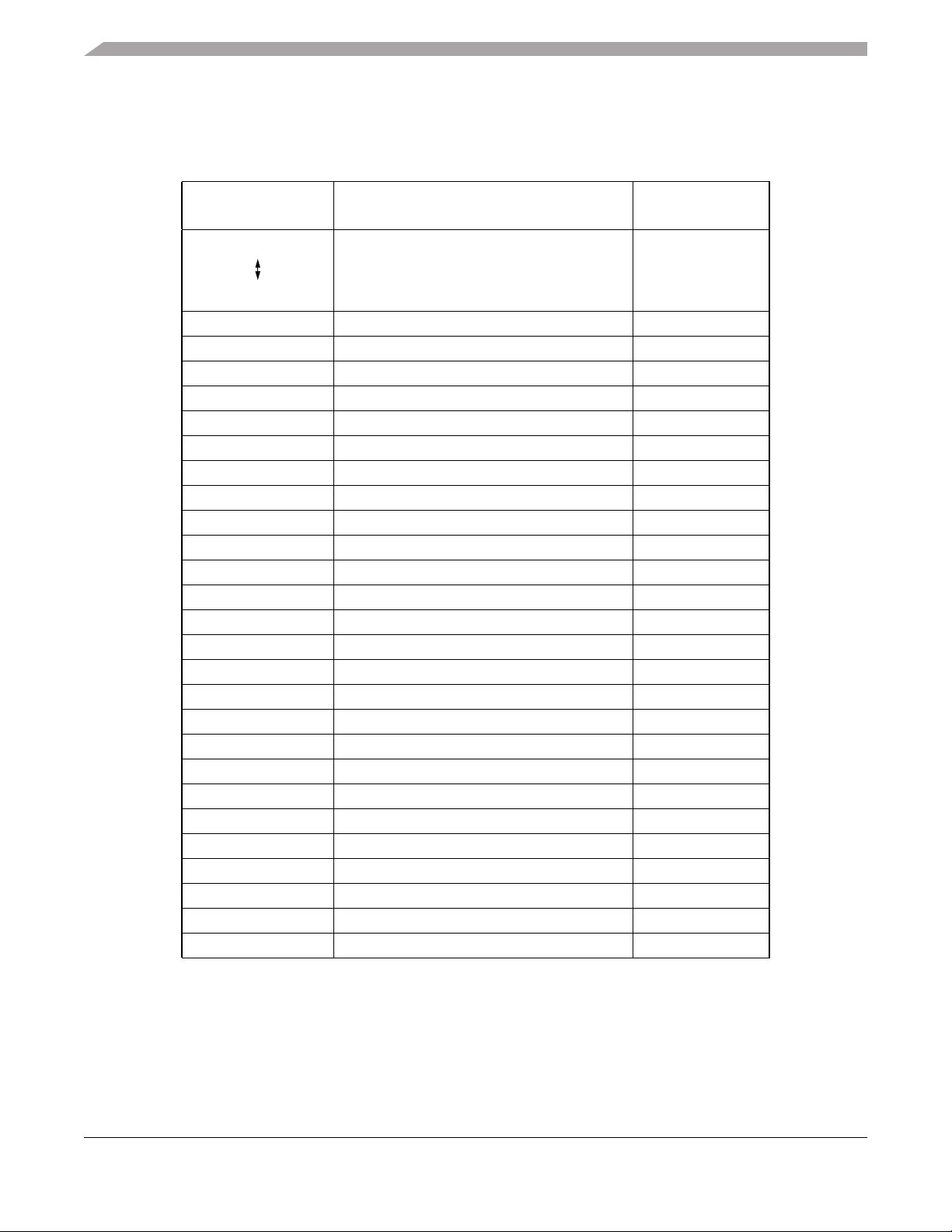

Revision

Number

1.0 4/25/2003 Initial release

1.1 Electricals change, appendix A only

1.2 Electricals change, appendix A only

1.3 10/2/2003 Added module version table; clarifications

1.4 10/29/2003 Fixed typos and made corrections and clarifications

1.5 11/12/2003 Added 1-MHz I

2 2/10/2004

2.2 9/2/2004

2.3 12/01/2004

Revision

Date

Description of Changes

values to Electricals, appendix A

DD

Changed format of register names to enable reuse of code (from SCIBD to SCI1BD, even when

only one instance of a module on a chip)

Added new device: MC9S08GT16 to book. Added new 48-pin QFN package to book. BKGDPE

description in Section 5 — changed PTD0 to PTG0. Changed typo in CPU section that listed

MOV instruction as being 6 cycles instead of 5 (Table 8-2).

Format to Freescale look-and-feel; Clarified RTI clock sources and other changes in Chapter 5;

updated ICG initialization examples; expanded descriptions of LOLS and LOCS bits in ICGS1;

updated ICG electricals Table A-9 and added a figure

Minor changes to Table 7-4, Table 7-5, Table A-9;

Clarifications in Section 11.10.6, “SCI x Control Register 3 (SCIxC3)”, Section 11.7, “Interrupts

and Status Flags”, Section 11.8.1, “8- and 9-Bit Data Modes”, PTG availability in 48-pin

package (see Table 2-2)

This product incorporates SuperFlash® technology licensed from SST.

Freescale‚ and the Freescale logo are trademarks of Freescale Semiconductor, Inc.

© Freescale Semiconductor, Inc., 2004. All rights reserved.

MC9S08GB/GT Data Sheet, Rev. 2.3

4 Freescale Semiconductor

List of Chapters

Chapter 1 Introduction.............................................................................. 17

Chapter 2 Pins and Connections.............................................................23

Chapter 3 Modes of Operation.................................................................33

Chapter 4 Memory.....................................................................................39

Chapter 5 Resets, Interrupts, and System Configuration .....................61

Chapter 6 Parallel Input/Output ............................................................... 77

Chapter 7 Internal Clock Generator (ICG) Module .................................97

Chapter 8 Central Processor Unit (CPU)............................................... 125

Chapter 9 Keyboard Interrupt (KBI) Module .........................................145

Chapter 10 Timer/PWM (TPM) Module..................................................... 151

Chapter 11 Serial Communications Interface (SCI) Module..................167

Chapter 12 Serial Peripheral Interface (SPI) Module.............................. 187

Chapter 13 Inter-Integrated Circuit (IIC) Module ....................................203

Chapter 14 Analog-to-Digital Converter (ATD) Module .........................219

Chapter 15 Development Support ...........................................................235

Appendix A Electrical Characteristics......................................................259

Appendix B Ordering Information and Mechanical Drawings................281

MC9S08GB/GT Data Sheet, Rev. 2.3

Freescale Semiconductor 5

Contents

Section Number Title Page

Chapter 1

Introduction

1.1 Overview .........................................................................................................................................17

1.2 Features ...........................................................................................................................................17

1.2.1 Standard Features of the HCS08 Family .........................................................................17

1.2.2 Features of MC9S08GB/GT Series of MCUs .................................................................17

1.2.3 Devices in the MC9S08GB/GT Series ............................................................................18

1.3 MCU Block Diagrams .....................................................................................................................19

1.4 System Clock Distribution ..............................................................................................................21

Chapter 2

Pins and Connections

2.1 Introduction .....................................................................................................................................23

2.2 Device Pin Assignment ...................................................................................................................23

2.3 Recommended System Connections ...............................................................................................26

2.3.1 Power ...............................................................................................................................28

2.3.2 Oscillator ..........................................................................................................................28

2.3.3 Reset ................................................................................................................................28

2.3.4 Background / Mode Select (PTG0/BKGD/MS) ..............................................................29

2.3.5 General-Purpose I/O and Peripheral Ports .......................................................................29

2.3.6 Signal Properties Summary .............................................................................................31

Chapter 3

Modes of Operation

3.1 Introduction .....................................................................................................................................33

3.2 Features ...........................................................................................................................................33

3.3 Run Mode ........................................................................................................................................33

3.4 Active Background Mode ................................................................................................................33

3.5 Wait Mode .......................................................................................................................................34

3.6 Stop Modes ......................................................................................................................................34

3.6.1 Stop1 Mode ......................................................................................................................35

3.6.2 Stop2 Mode ......................................................................................................................35

3.6.3 Stop3 Mode ......................................................................................................................36

3.6.4 Active BDM Enabled in Stop Mode ................................................................................36

3.6.5 LVD Enabled in Stop Mode .............................................................................................37

3.6.6 On-Chip Peripheral Modules in Stop Modes ...................................................................37

MC9S08GB/GT Data Sheet, Rev. 2.3

Freescale Semiconductor 7

Section Number Title Page

Chapter 4

Memory

4.1 MC9S08GB/GT Memory Map .......................................................................................................39

4.1.1 Reset and Interrupt Vector Assignments ..........................................................................39

4.2 Register Addresses and Bit Assignments ........................................................................................41

4.3 RAM ................................................................................................................................................46

4.4 FLASH ............................................................................................................................................46

4.4.1 Features ............................................................................................................................47

4.4.2 Program and Erase Times ................................................................................................47

4.4.3 Program and Erase Command Execution ........................................................................48

4.4.4 Burst Program Execution .................................................................................................49

4.4.5 Access Errors ...................................................................................................................50

4.4.6 FLASH Block Protection .................................................................................................51

4.4.7 Vector Redirection ...........................................................................................................52

4.5 Security ............................................................................................................................................52

4.6 FLASH Registers and Control Bits .................................................................................................53

4.6.1 FLASH Clock Divider Register (FCDIV) .......................................................................54

4.6.2 FLASH Options Register (FOPT and NVOPT) ..............................................................55

4.6.3 FLASH Configuration Register (FCNFG) .......................................................................56

4.6.4 FLASH Protection Register (FPROT and NVPROT) ......................................................56

4.6.5 FLASH Status Register (FSTAT) .....................................................................................58

4.6.6 FLASH Command Register (FCMD) ..............................................................................59

Chapter 5

Resets, Interrupts, and System Configuration

5.1 Introduction .....................................................................................................................................61

5.2 Features ...........................................................................................................................................61

5.3 MCU Reset ......................................................................................................................................61

5.4 Computer Operating Properly (COP) Watchdog .............................................................................62

5.5 Interrupts .........................................................................................................................................62

5.5.1 Interrupt Stack Frame ......................................................................................................63

5.5.2 External Interrupt Request (IRQ) Pin ..............................................................................64

5.5.2.1 Pin Configuration Options ..............................................................................64

5.5.2.2 Edge and Level Sensitivity ..............................................................................65

5.5.3 Interrupt Vectors, Sources, and Local Masks ..................................................................65

5.6 Low-Voltage Detect (LVD) System ................................................................................................67

5.6.1 Power-On Reset Operation ..............................................................................................67

5.6.2 LVD Reset Operation .......................................................................................................67

5.6.3 LVD Interrupt Operation .................................................................................................67

5.6.4 Low-Voltage Warning (LVW) ..........................................................................................67

5.7 Real-Time Interrupt (RTI) ...............................................................................................................67

MC9S08GB/GT Data Sheet, Rev. 2.3

8 Freescale Semiconductor

Section Number Title Page

5.8 Reset, Interrupt, and System Control Registers and Control Bits ...................................................68

5.8.1 Interrupt Pin Request Status and Control Register (IRQSC) ...........................................68

5.8.2 System Reset Status Register (SRS) ................................................................................69

5.8.3 System Background Debug Force Reset Register (SBDFR) ...........................................71

5.8.4 System Options Register (SOPT) ....................................................................................71

5.8.5 System Device Identification Register (SDIDH, SDIDL) ...............................................72

5.8.6 System Real-Time Interrupt Status and Control Register (SRTISC) ...............................73

5.8.7 System Power Management Status and Control 1 Register (SPMSC1) ..........................74

5.8.8 System Power Management Status and Control 2 Register (SPMSC2) ..........................75

Chapter 6

Parallel Input/Output

6.1 Introduction .....................................................................................................................................77

6.2 Features ...........................................................................................................................................79

6.3 Pin Descriptions ..............................................................................................................................79

6.3.1 Port A and Keyboard Interrupts .......................................................................................79

6.3.2 Port B and Analog to Digital Converter Inputs ...............................................................80

6.3.3 Port C and SCI2, IIC, and High-Current Drivers ............................................................80

6.3.4 Port D, TPM1 and TPM2 .................................................................................................81

6.3.5 Port E, SCI1, and SPI ......................................................................................................81

6.3.6 Port F and High-Current Drivers .....................................................................................82

6.3.7 Port G, BKGD/MS, and Oscillator ..................................................................................82

6.4 Parallel I/O Controls ........................................................................................................................82

6.4.1 Data Direction Control ....................................................................................................83

6.4.2 Internal Pullup Control ....................................................................................................83

6.4.3 Slew Rate Control ............................................................................................................83

6.5 Stop Modes ......................................................................................................................................84

6.6 Parallel I/O Registers and Control Bits ...........................................................................................84

6.6.1 Port A Registers (PTAD, PTAPE, PTASE, and PTADD) ................................................84

6.6.2 Port B Registers (PTBD, PTBPE, PTBSE, and PTBDD) ...............................................86

6.6.3 Port C Registers (PTCD, PTCPE, PTCSE, and PTCDD) ...............................................87

6.6.4 Port D Registers (PTDD, PTDPE, PTDSE, and PTDDD) ..............................................89

6.6.5 Port E Registers (PTED, PTEPE, PTESE, and PTEDD) ................................................90

6.6.6 Port F Registers (PTFD, PTFPE, PTFSE, and PTFDD) ..................................................92

6.6.7 Port G Registers (PTGD, PTGPE, PTGSE, and PTGDD) ..............................................93

MC9S08GB/GT Data Sheet, Rev. 2.3

Freescale Semiconductor 9

Section Number Title Page

Chapter 7

Internal Clock Generator (ICG) Module

7.1 Introduction .....................................................................................................................................99

7.1.1 Features ..........................................................................................................................100

7.1.2 Modes of Operation .......................................................................................................101

7.2 External Signal Description ..........................................................................................................101

7.2.1 Overview ........................................................................................................................101

7.2.2 Detailed Signal Descriptions .........................................................................................102

7.2.2.1 EXTAL— External Reference Clock / Oscillator Input ...............................102

7.2.2.2 XTAL— Oscillator Output ...........................................................................102

7.2.3 External Clock Connections ..........................................................................................102

7.2.4 External Crystal/Resonator Connections .......................................................................102

7.3 Functional Description ..................................................................................................................103

7.3.1 Off Mode (Off) ..............................................................................................................103

7.3.1.1 BDM Active .................................................................................................103

7.3.1.2 OSCSTEN Bit Set .........................................................................................103

7.3.1.3 Stop/Off Mode Recovery ..............................................................................104

7.3.2 Self-Clocked Mode (SCM) ............................................................................................104

7.3.3 FLL Engaged, Internal Clock (FEI) Mode ....................................................................105

7.3.3.1 FLL Engaged Internal Unlocked ..................................................................105

7.3.3.2 FLL Engaged Internal Locked ......................................................................106

7.3.4 FLL Bypassed, External Clock (FBE) Mode ................................................................106

7.3.5 FLL Engaged, External Clock (FEE) Mode ..................................................................106

7.3.5.1 FLL Engaged External Unlocked .................................................................106

7.3.5.2 FLL Engaged External Locked .....................................................................107

7.3.6 FLL Lock and Loss-of-Lock Detection .........................................................................107

7.3.7 FLL Loss-of-Clock Detection ........................................................................................107

7.3.8 Clock Mode Requirements ............................................................................................108

7.3.9 Fixed Frequency Clock ..................................................................................................109

7.4 Initialization/Application Information ..........................................................................................110

7.4.1 Introduction ....................................................................................................................110

7.4.2 Example #1: External Crystal = 32 kHz, Bus Frequency = 4.19 MHz .........................112

7.4.3 Example #2: External Crystal = 4 MHz, Bus Frequency = 20 MHz ............................113

7.4.4 Example #3: No External Crystal Connection, 5.4 MHz Bus Frequency .....................114

7.4.5 Example #4: Internal Clock Generator Trim .................................................................116

7.5 ICG Registers and Control Bits .....................................................................................................117

7.5.1 ICG Control Register 1 (ICGC1) ......................................................................118

7.5.2 ICG Control Register 2 (ICGC2) ......................................................................119

7.5.3 ICG Status Register 1 (ICGS1) .................................................................................120

7.5.4 ICG Status Register 2 (ICGS2) ........................................................................122

7.5.5 ICG Filter Registers (ICGFLTU, ICGFLTL) ....................................................... 122

7.5.6 ICG Trim Register (ICGTRM) ...........................................................................123

MC9S08GB/GT Data Sheet, Rev. 2.3

10 Freescale Semiconductor

Section Number Title Page

Chapter 8

Central Processor Unit (CPU)

8.1 Introduction ...................................................................................................................................125

8.2 Features .........................................................................................................................................126

8.3 Programmer’s Model and CPU Registers .....................................................................................126

8.3.1 Accumulator (A) ............................................................................................................127

8.3.2 Index Register (H:X) .....................................................................................................127

8.3.3 Stack Pointer (SP) ..........................................................................................................128

8.3.4 Program Counter (PC) ...................................................................................................128

8.3.5 Condition Code Register (CCR) ....................................................................................128

8.4 Addressing Modes .........................................................................................................................130

8.4.1 Inherent Addressing Mode (INH) ..................................................................................130

8.4.2 Relative Addressing Mode (REL) .................................................................................130

8.4.3 Immediate Addressing Mode (IMM) .............................................................................130

8.4.4 Direct Addressing Mode (DIR) .....................................................................................130

8.4.5 Extended Addressing Mode (EXT) ...............................................................................131

8.4.6 Indexed Addressing Mode .............................................................................................131

8.4.6.1 Indexed, No Offset (IX) ................................................................................131

8.4.6.2 Indexed, No Offset with Post Increment (IX+) .............................................131

8.4.6.3 Indexed, 8-Bit Offset (IX1) ...........................................................................131

8.4.6.4 Indexed, 8-Bit Offset with Post Increment (IX1+) .......................................131

8.4.6.5 Indexed, 16-Bit Offset (IX2) .........................................................................131

8.4.6.6 SP-Relative, 8-Bit Offset (SP1) ....................................................................131

8.4.6.7 SP-Relative, 16-Bit Offset (SP2) ..................................................................132

8.5 Special Operations .........................................................................................................................132

8.5.1 Reset Sequence ..............................................................................................................132

8.5.2 Interrupt Sequence .........................................................................................................132

8.5.3 Wait Mode Operation .....................................................................................................133

8.5.4 Stop Mode Operation .....................................................................................................133

8.5.5 BGND Instruction ..........................................................................................................134

8.6 HCS08 Instruction Set Summary ..................................................................................................134

Chapter 9

Keyboard Interrupt (KBI) Module

9.1 Introduction ...................................................................................................................................145

9.1.1 Port A and Keyboard Interrupt Pins ..............................................................................145

9.2 Features .........................................................................................................................................145

9.3 KBI Block Diagram ......................................................................................................................147

9.4 Keyboard Interrupt (KBI) Module ................................................................................................147

9.4.1 Pin Enables ....................................................................................................................147

9.4.2 Edge and Level Sensitivity ............................................................................................147

9.4.3 KBI Interrupt Controls ...................................................................................................148

9.5 KBI Registers and Control Bits .....................................................................................................148

9.5.1 KBI Status and Control Register (KBI1SC) ..................................................................148

9.5.2 KBI Pin Enable Register (KBI1PE) ..............................................................................150

MC9S08GB/GT Data Sheet, Rev. 2.3

Freescale Semiconductor 11

Section Number Title Page

Chapter 10

Timer/PWM (TPM) Module

10.1 Introduction ...................................................................................................................................151

10.2 Features .........................................................................................................................................151

10.3 TPM Block Diagram .....................................................................................................................153

10.4 Pin Descriptions ............................................................................................................................154

10.4.1 External TPM Clock Sources ........................................................................................154

10.4.2 TPMxCHn — TPMx Channel n I/O Pins ......................................................................154

10.5 Functional Description ..................................................................................................................154

10.5.1 Counter ..........................................................................................................................155

10.5.2 Channel Mode Selection ................................................................................................156

10.5.2.1 Input Capture Mode ......................................................................................156

10.5.2.2 Output Compare Mode .................................................................................156

10.5.2.3 Edge-Aligned PWM Mode ...........................................................................156

10.5.3 Center-Aligned PWM Mode ..........................................................................................157

10.6 TPM Interrupts ..............................................................................................................................159

10.6.1 Clearing Timer Interrupt Flags ......................................................................................159

10.6.2 Timer Overflow Interrupt Description ...........................................................................159

10.6.3 Channel Event Interrupt Description .............................................................................159

10.6.4 PWM End-of-Duty-Cycle Events ..................................................................................160

10.7 TPM Registers and Control Bits ...................................................................................................160

10.7.1 Timer x Status and Control Register (TPMxSC) ...........................................................160

10.7.2 Timer x Counter Registers (TPMxCNTH:TPMxCNTL) ..............................................162

10.7.3 Timer x Counter Modulo Registers (TPMxMODH:TPMxMODL) ..............................163

10.7.4 Timer x Channel n Status and Control Register (TPMxCnSC) .....................................163

10.7.5 Timer x Channel Value Registers (TPMxCnVH:TPMxCnVL) .....................................165

Chapter 11

Serial Communications Interface (SCI) Module

11.1 Introduction ...................................................................................................................................167

11.2 Features .........................................................................................................................................169

11.3 SCI System Description ................................................................................................................169

11.4 Baud Rate Generation ...................................................................................................................169

11.5 Transmitter Functional Description ...............................................................................................170

11.5.1 Transmitter Block Diagram ...........................................................................................170

11.5.2 Send Break and Queued Idle .........................................................................................172

11.6 Receiver Functional Description ...................................................................................................172

11.6.1 Receiver Block Diagram ................................................................................................172

11.6.2 Data Sampling Technique ..............................................................................................174

11.6.3 Receiver Wakeup Operation ..........................................................................................174

11.6.3.1 Idle-Line Wakeup ..........................................................................................175

11.6.3.2 Address-Mark Wakeup .................................................................................175

11.7 Interrupts and Status Flags ............................................................................................................175

MC9S08GB/GT Data Sheet, Rev. 2.3

12 Freescale Semiconductor

Section Number Title Page

11.8 Additional SCI Functions ..............................................................................................................176

11.8.1 8- and 9-Bit Data Modes ................................................................................................176

11.9 Stop Mode Operation ....................................................................................................................176

11.9.1 Loop Mode .....................................................................................................................177

11.9.2 Single-Wire Operation ...................................................................................................177

11.10 SCI Registers and Control Bits .....................................................................................................177

11.10.1 SCI x Baud Rate Registers (SCIxBDH, SCIxBDL) ......................................................177

11.10.2 SCI x Control Register 1 (SCIxC1) ...............................................................................178

11.10.3 SCI x Control Register 2 (SCIxC2) ...............................................................................180

11.10.4 SCI x Status Register 1 (SCIxS1) ..................................................................................181

11.10.5 SCI x Status Register 2 (SCIxS2) ..................................................................................183

11.10.6 SCI x Control Register 3 (SCIxC3) ...............................................................................184

11.10.7 SCI x Data Register (SCIxD) ........................................................................................185

Chapter 12

Serial Peripheral Interface (SPI) Module

12.1 Features .........................................................................................................................................189

12.2 Block Diagrams .............................................................................................................................189

12.2.1 SPI System Block Diagram ...........................................................................................189

12.2.2 SPI Module Block Diagram ...........................................................................................190

12.2.3 SPI Baud Rate Generation .............................................................................................192

12.3 Functional Description ..................................................................................................................192

12.3.1 SPI Clock Formats .........................................................................................................193

12.3.2 SPI Pin Controls ............................................................................................................195

12.3.2.1 SPSCK1 — SPI Serial Clock ........................................................................195

12.3.2.2 MOSI1 — Master Data Out, Slave Data In ..................................................195

12.3.2.3 MISO1 — Master Data In, Slave Data Out ..................................................195

12.3.2.4

12.3.3 SPI Interrupts .................................................................................................................196

12.3.4 Mode Fault Detection ....................................................................................................196

12.4 SPI Registers and Control Bits ......................................................................................................196

12.4.1 SPI Control Register 1 (SPI1C1) ...................................................................................197

12.4.2 SPI Control Register 2 (SPI1C2) ...................................................................................198

12.4.3 SPI Baud Rate Register (SPI1BR) .................................................................................199

12.4.4 SPI Status Register (SPI1S) ...........................................................................................201

12.4.5 SPI Data Register (SPI1D) ............................................................................................202

SS1 — Slave Select .......................................................................................195

MC9S08GB/GT Data Sheet, Rev. 2.3

Freescale Semiconductor 13

Section Number Title Page

Chapter 13

Inter-Integrated Circuit (IIC) Module

13.1 Introduction ...................................................................................................................................205

13.1.1 Features ..........................................................................................................................205

13.1.2 Modes of Operation .......................................................................................................205

13.1.3 Block Diagram ...............................................................................................................206

13.1.4 Detailed Signal Descriptions .........................................................................................206

13.1.4.1 SCL1 — Serial Clock Line ...........................................................................206

13.1.4.2 SDA1 — Serial Data Line ............................................................................206

13.2 Functional Description ..................................................................................................................207

13.2.1 IIC Protocol ...................................................................................................................207

13.2.1.1 START Signal ...............................................................................................208

13.2.1.2 Slave Address Transmission .........................................................................208

13.2.1.3 Data Transfer .................................................................................................208

13.2.1.4 STOP Signal ..................................................................................................209

13.2.1.5 Repeated START Signal ...............................................................................209

13.2.1.6 Arbitration Procedure ....................................................................................209

13.2.1.7 Clock Synchronization ..................................................................................209

13.2.1.8 Handshaking .................................................................................................210

13.2.1.9 Clock Stretching ............................................................................................210

13.3 Resets ............................................................................................................................................210

13.4 Interrupts .......................................................................................................................................211

13.4.1 Byte Transfer Interrupt ..................................................................................................211

13.4.2 Address Detect Interrupt ................................................................................................211

13.4.3 Arbitration Lost Interrupt ..............................................................................................211

13.5 IIC Registers and Control Bits ......................................................................................................212

13.5.1 IIC Address Register (IIC1A) ........................................................................................212

13.5.2 IIC Frequency Divider Register (IIC1F) ........................................................................212

13.5.3 IIC Control Register (IIC1C) .........................................................................................215

13.5.4 IIC Status Register (IIC1S) ............................................................................................216

13.5.5 IIC Data I/O Register (IIC1D) .......................................................................................217

Chapter 14

Analog-to-Digital Converter (ATD) Module

14.1 Introduction ...................................................................................................................................221

14.1.1 Features ..........................................................................................................................221

14.1.2 Modes of Operation .......................................................................................................221

14.1.2.1 Stop Mode .....................................................................................................221

14.1.2.2 Power Down Mode .......................................................................................221

14.1.3 Block Diagram ...............................................................................................................221

14.2 Signal Description .........................................................................................................................222

14.2.1 Overview ........................................................................................................................222

14.2.1.1 Channel Input Pins — AD1P7–AD1P0 ........................................................223

MC9S08GB/GT Data Sheet, Rev. 2.3

14 Freescale Semiconductor

Section Number Title Page

14.2.1.2 ATD Reference Pins — V

14.2.1.3 ATD Supply Pins — V

DDAD

REFH

, V

, V

SSAD

........................................................223

REFL

...........................................................223

14.3 Functional Description ..................................................................................................................223

14.3.1 Mode Control .................................................................................................................223

14.3.2 Sample and Hold ............................................................................................................224

14.3.3 Analog Input Multiplexer ..............................................................................................226

14.3.4 ATD Module Accuracy Definitions ...............................................................................226

14.4 Resets ............................................................................................................................................229

14.5 Interrupts .......................................................................................................................................229

14.6 ATD Registers and Control Bits ....................................................................................................229

14.6.1 ATD Control (ATDC) ....................................................................................................230

14.6.2 ATD Status and Control (ATD1SC) ..............................................................................232

14.6.3 ATD Result Data (ATD1RH, ATD1RL) ........................................................................234

14.6.4 ATD Pin Enable (ATD1PE) ...........................................................................................234

Chapter 15

Development Support

15.1 Introduction ...................................................................................................................................235

15.2 Features .........................................................................................................................................236

15.3 Background Debug Controller (BDC) ..........................................................................................237

15.3.1 BKGD Pin Description ..................................................................................................237

15.3.2 Communication Details .................................................................................................238

15.3.3 BDC Commands ............................................................................................................242

15.3.4 BDC Hardware Breakpoint ............................................................................................244

15.4 On-Chip Debug System (DBG) ....................................................................................................245

15.4.1 Comparators A and B ....................................................................................................245

15.4.2 Bus Capture Information and FIFO Operation ..............................................................245

15.4.3 Change-of-Flow Information .........................................................................................246

15.4.4 Tag vs. Force Breakpoints and Triggers ........................................................................246

15.4.5 Trigger Modes ................................................................................................................247

15.4.6 Hardware Breakpoints ...................................................................................................249

15.5 Registers and Control Bits .............................................................................................................249

15.5.1 BDC Registers and Control Bits ....................................................................................249

15.5.1.1 BDC Status and Control Register (BDCSCR) ..............................................250

15.5.1.2 BDC Breakpoint Match Register (BDCBKPT) ............................................251

15.5.2 System Background Debug Force Reset Register (SBDFR) .........................................251

15.5.3 DBG Registers and Control Bits ....................................................................................252

15.5.3.1 Debug Comparator A High Register (DBGCAH) ........................................252

15.5.3.2 Debug Comparator A Low Register (DBGCAL) .........................................252

15.5.3.3 Debug Comparator B High Register (DBGCBH) .........................................252

15.5.3.4 Debug Comparator B Low Register (DBGCBL) ..........................................252

MC9S08GB/GT Data Sheet, Rev. 2.3

Freescale Semiconductor 15

Section Number Title Page

15.5.3.5 Debug FIFO High Register (DBGFH) ..........................................................253

15.5.3.6 Debug FIFO Low Register (DBGFL) ...........................................................253

15.5.3.7 Debug Control Register (DBGC) ..................................................................254

15.5.3.8 Debug Trigger Register (DBGT) ..................................................................255

15.5.3.9 Debug Status Register (DBGS) .....................................................................256

Appendix A

Electrical Characteristics

A.1 Introduction ...................................................................................................................................259

A.2 Absolute Maximum Ratings ..........................................................................................................259

A.3 Thermal Characteristics .................................................................................................................260

A.4 Electrostatic Discharge (ESD) Protection Characteristics ............................................................261

A.5 DC Characteristics .........................................................................................................................261

A.6 Supply Current Characteristics ......................................................................................................265

A.7 ATD Characteristics ......................................................................................................................269

A.8 Internal Clock Generation Module Characteristics .......................................................................271

A.8.1 ICG Frequency Specifications ........................................................................................271

A.9 AC Characteristics .........................................................................................................................273

A.9.1 Control Timing ...............................................................................................................273

A.9.2 Timer/PWM (TPM) Module Timing ..............................................................................274

A.9.3 SPI Timing ......................................................................................................................275

A.10 FLASH Specifications ...................................................................................................................279

Appendix B

Ordering Information and Mechanical Drawings

B.1 Ordering Information ....................................................................................................................281

B.2 Mechanical Drawings ....................................................................................................................281

B.3 64-Pin LQFP Package Drawing ....................................................................................................282

B.4 48-Pin QFN Package Drawing ......................................................................................................283

B.5 44-Pin QFP Package Drawing .......................................................................................................284

B.6 42-Pin SDIP Package Drawing .....................................................................................................285

MC9S08GB/GT Data Sheet, Rev. 2.3

16 Freescale Semiconductor

Chapter 1 Introduction

1.1 Overview

The MC9S08GB/GT are members of the low-cost, high-performance HCS08 Family of 8-bit

microcontroller units (MCUs). All MCUs in the family use the enhanced HCS08 core and are available

with a variety of modules, memory sizes, memory types, and package types.

1.2 Features

Features have been organized to reflect:

• Standard features of the HCS08 Family

• Features of the MC9S08GB/GT MCU

1.2.1 Standard Features of the HCS08 Family

• 40-MHz HCS08 CPU (central processor unit)

• HC08 instruction set with added BGND instruction

• Background debugging system (see also Chapter 15, “Development Support”)

• Breakpoint capability to allow single breakpoint setting during in-circuit debugging (plus two more

breakpoints in on-chip debug module)

• Debug module containing two comparators and nine trigger modes. Eight deep FIFO for storing

change-of-flow addresses and event-only data. Debug module supports both tag and force

breakpoints.

• Support for up to 32 interrupt/reset sources

• Power-saving modes: wait plus three stops

• System protection features:

— Optional computer operating properly (COP) reset

— Low-voltage detection with reset or interrupt

— Illegal opcode detection with reset

— Illegal address detection with reset (some devices don’t have illegal addresses)

1.2.2 Features of MC9S08GB/GT Series of MCUs

• On-chip in-circuit programmable FLASH memory with block protection and security options (see

Table 1-1 for device specific information)

• On-chip random-access memory (RAM) (see Table 1-1 for device specific information)

• 8-channel, 10-bit analog-to-digital converter (ATD)

• Two serial communications interface modules (SCI)

• Serial peripheral interface module (SPI)

MC9S08GB/GT Data Sheet, Rev. 2.3

Freescale Semiconductor 17

Chapter 1 Introduction

• Multiple clock source options:

— Internally generated clock with ±0.2% trimming resolution and ±0.5% deviation across

voltage.

— Crystal

— Resonator, or

— External clock

• Inter-integrated circuit bus module to operate up to 100 kbps (IIC)

• One 3-channel and one 5-channel 16-bit timer/pulse width modulator (TPM) modules with

selectable input capture, output compare, and edge-aligned PWM capability on each channel. Each

timer module may be configured for buffered, centered PWM (CPWM) on all channels (TPMx).

• 8-pin keyboard interrupt module (KBI)

• 16 high-current pins (limited by package dissipation)

• Software selectable pullups on ports when used as input. Selection is on an individual port bit basis.

During output mode, pullups are disengaged.

• Internal pullup on

RESET and IRQ pin to reduce customer system cost

• Up to 56 general-purpose input/output (I/O) pins, depending on package selection

• 64-pin low-profile quad flat package (LQFP) — MC9S08GBxx

• 48-pin quad flat package, no lead (QFN) — MC9S08GTxx

• 44-pin quad flat package (QFP) — MC9S08GTxx

• 42-pin shrink dual in-line package (SDIP) — MC9S08GTxx

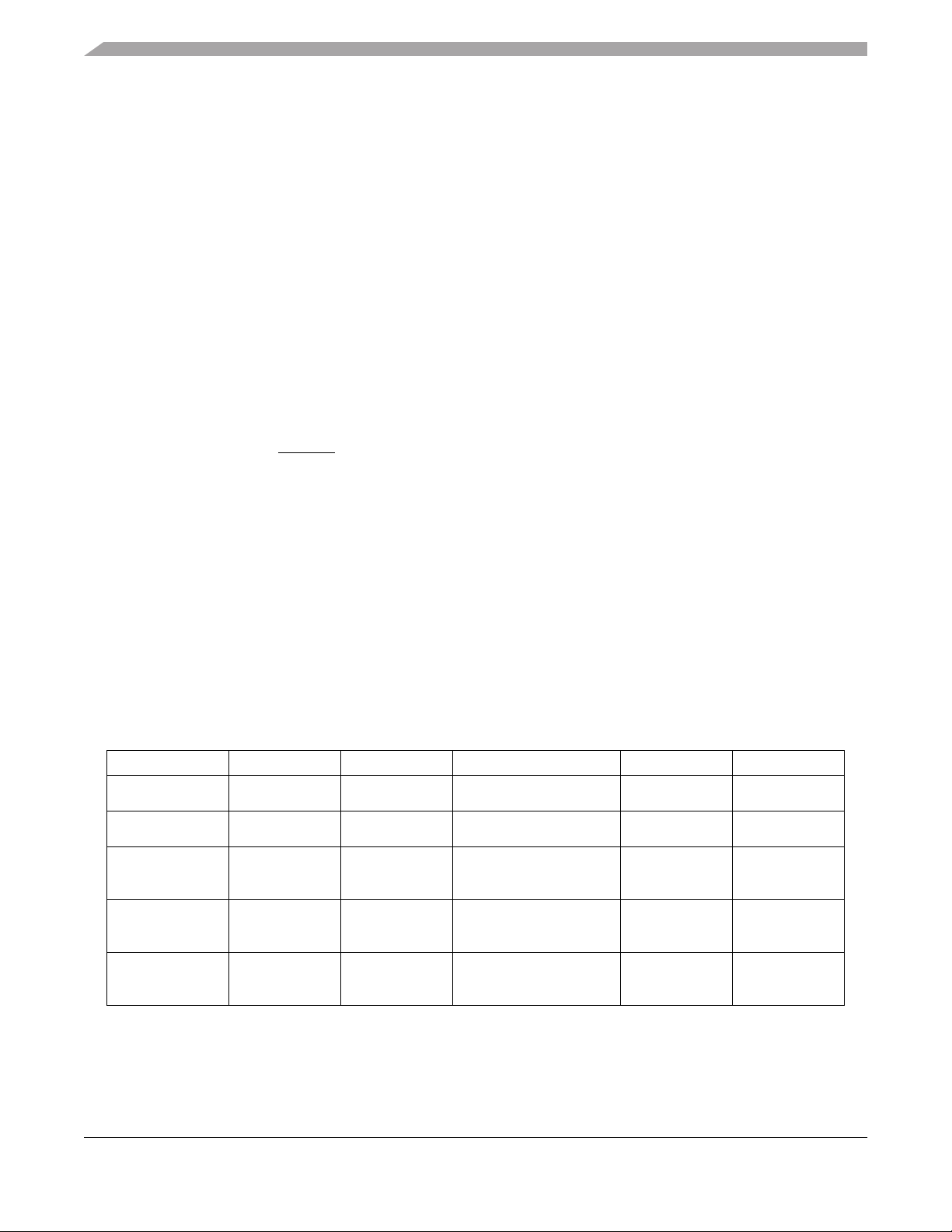

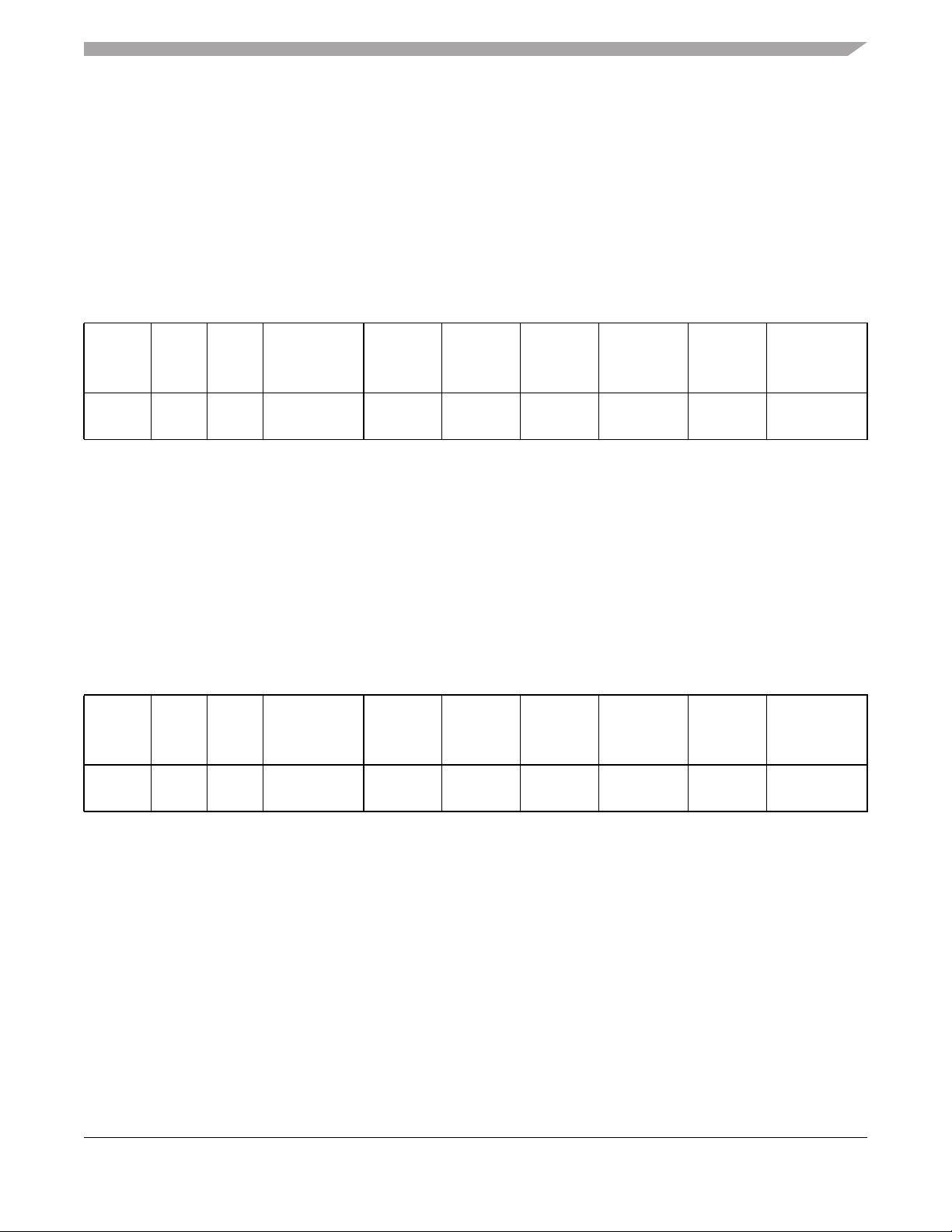

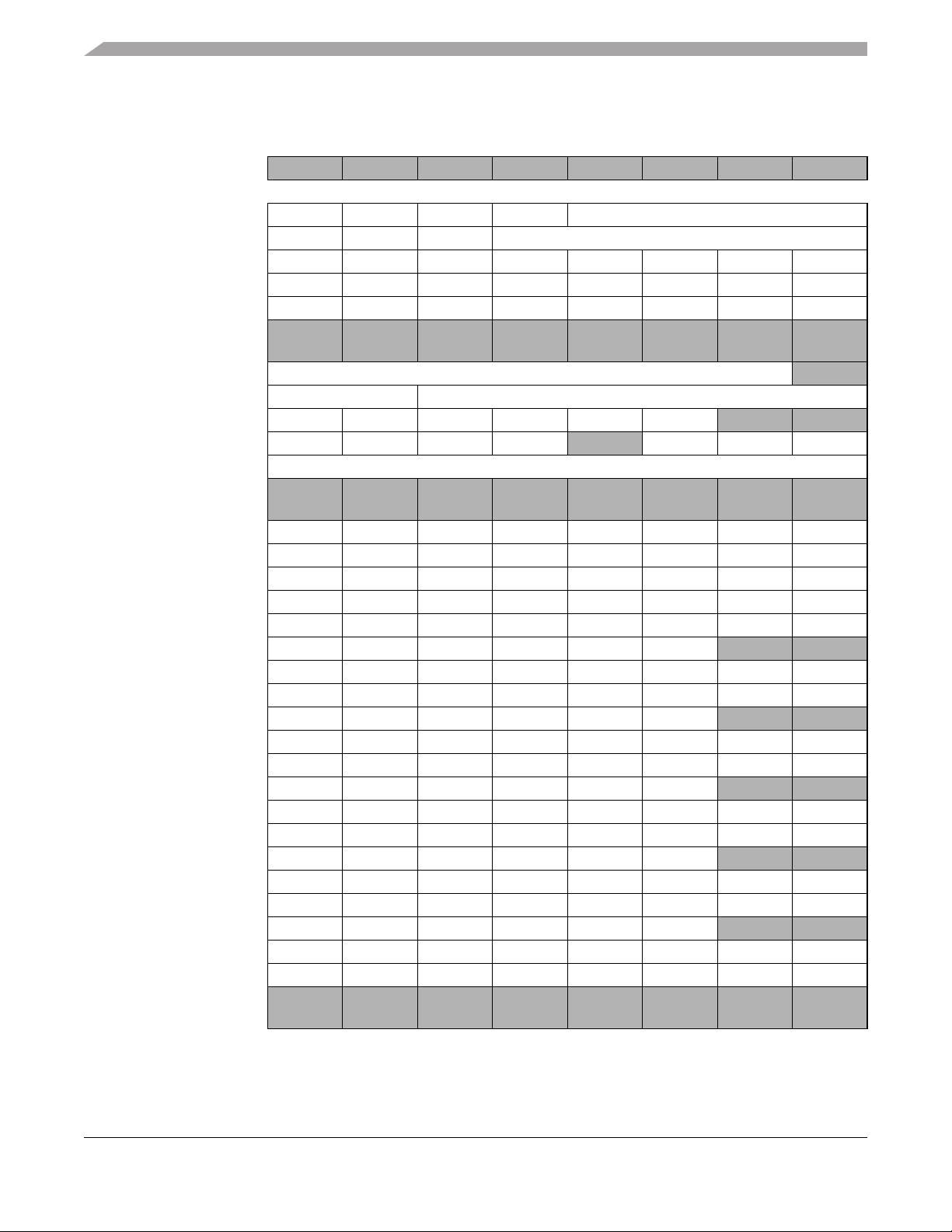

1.2.3 Devices in the MC9S08GB/GT Series

Table 1-1 lists the devices available in the MC9S08GB/GT series and summarizes the differences among

them.

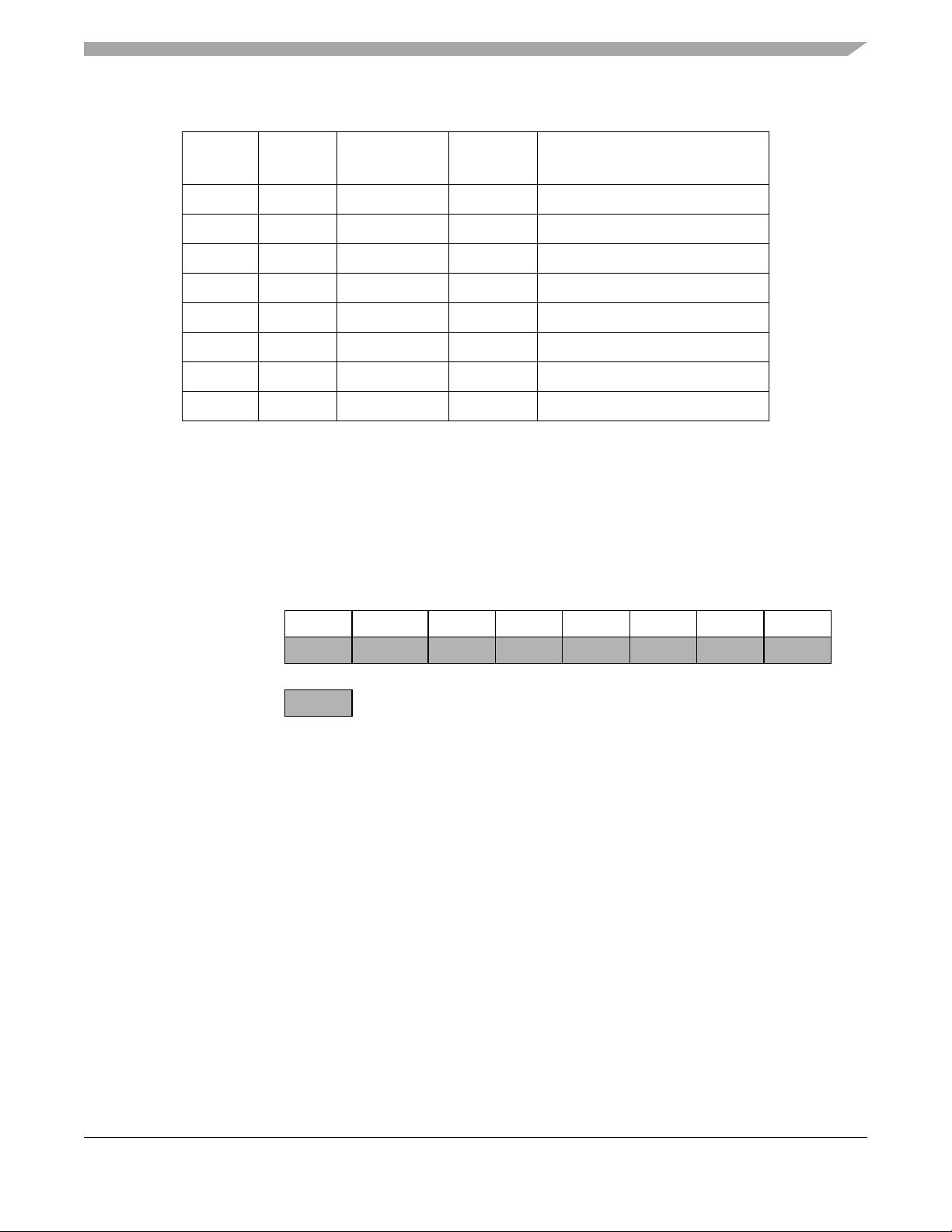

Table 1-1. Devices in the MC9S08GB/GT Series

Device FLASH RAM TPM I/O Packages

MC9S08GB60 60K 4K One 3-channel and one

5-channel, 16-bit timer

MC9S08GB32 32K 2K One 3-channel and one

5-channel, 16-bit timer

MC9S08GT60 60K 4K Two 2-channel,

16-bit timers

MC9S08GT32 32K 2K Two 2-channel,

16-bit timers

MC9S08GT16 16K 1K Two 2-channel,

16-bit timers

1

The 48-pin QFN package has one 3-channel and one 2-channel 16-bit TPM.

56 64 LQFP

56 64 LQFP

39

36

34

39

36

34

39

36

34

48 QFN

44 QFP

42 SDIP

48 QFN

44 QFP

42 SDIP

48 QFN

44 QFP

42 SDIP

1

(1)

(1)

MC9S08GB/GT Data Sheet, Rev. 2.3

18 Freescale Semiconductor

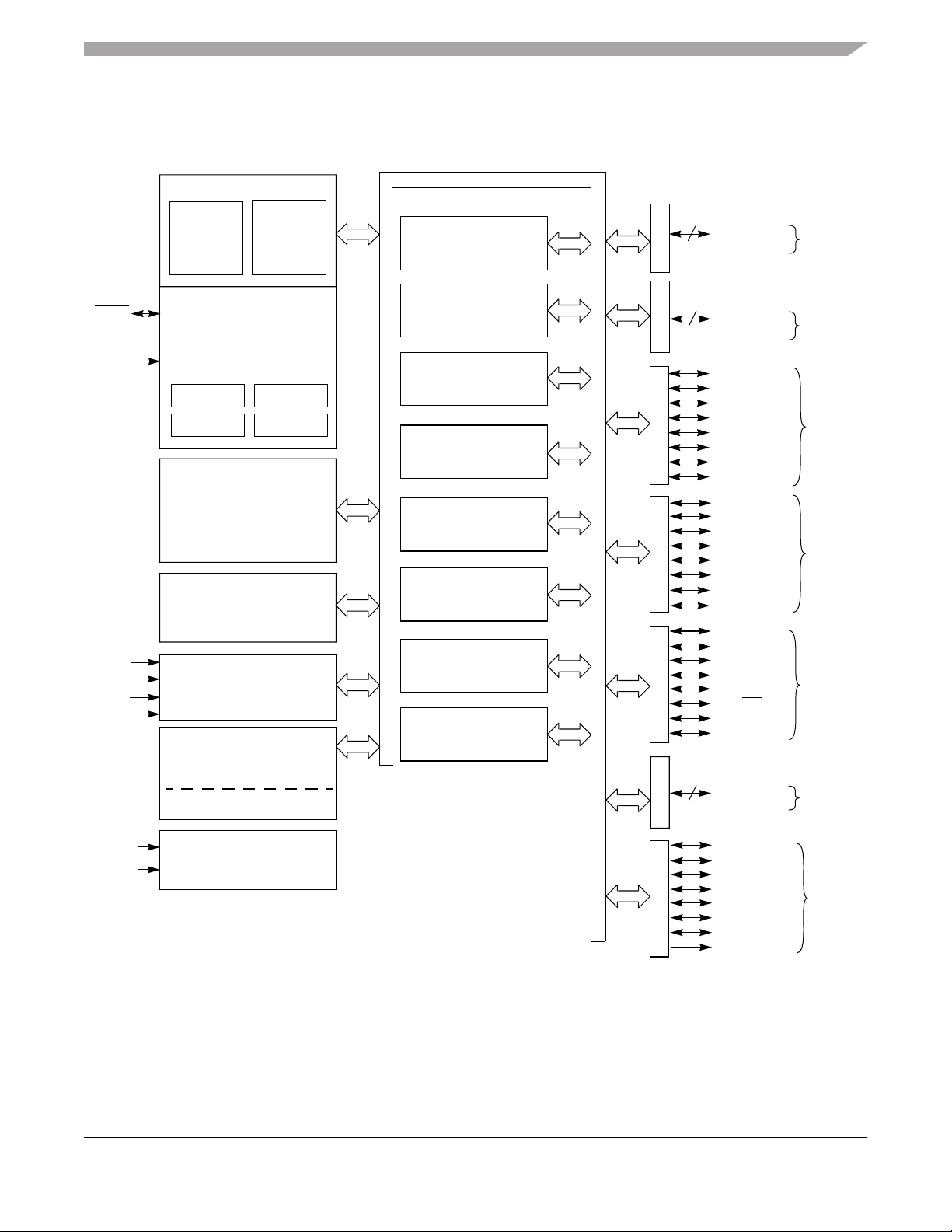

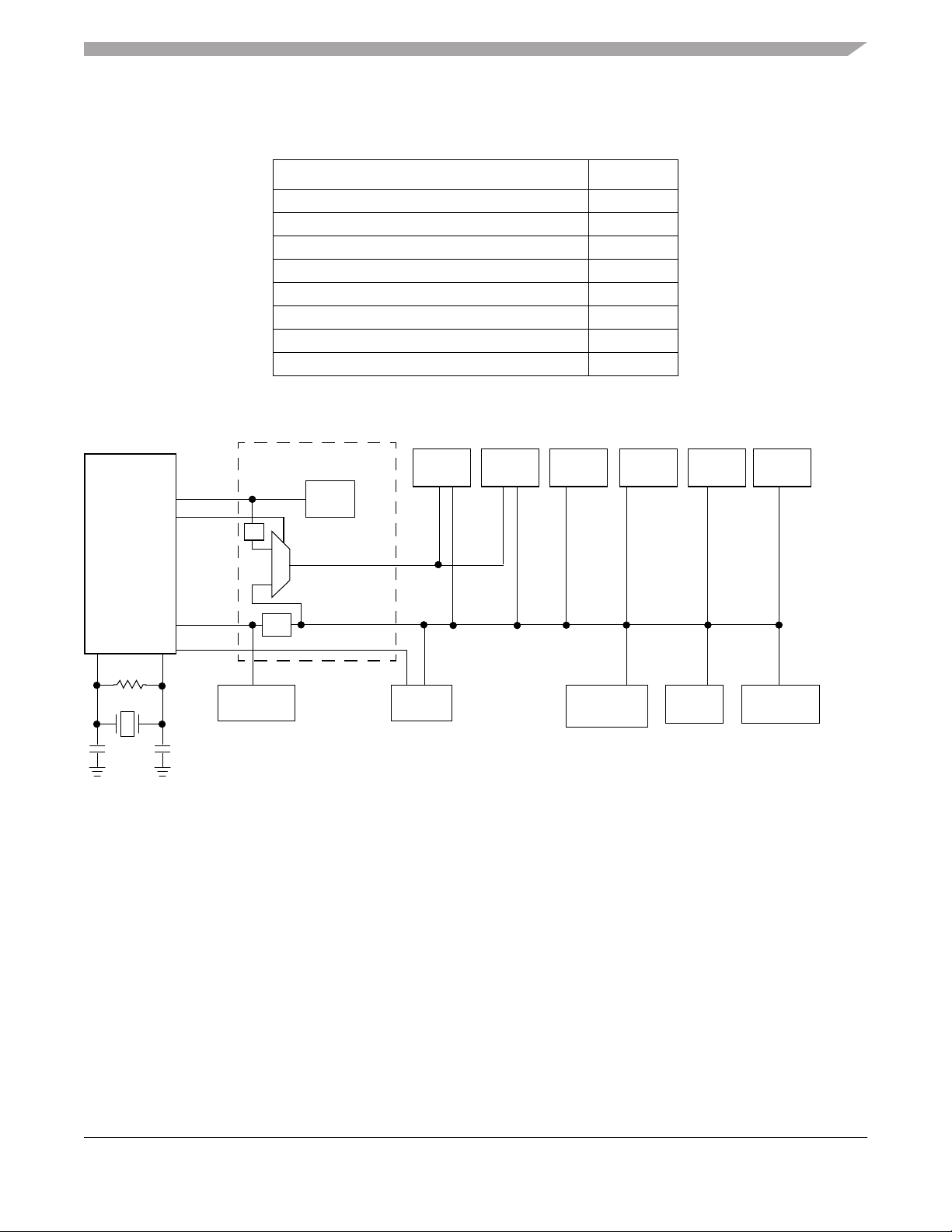

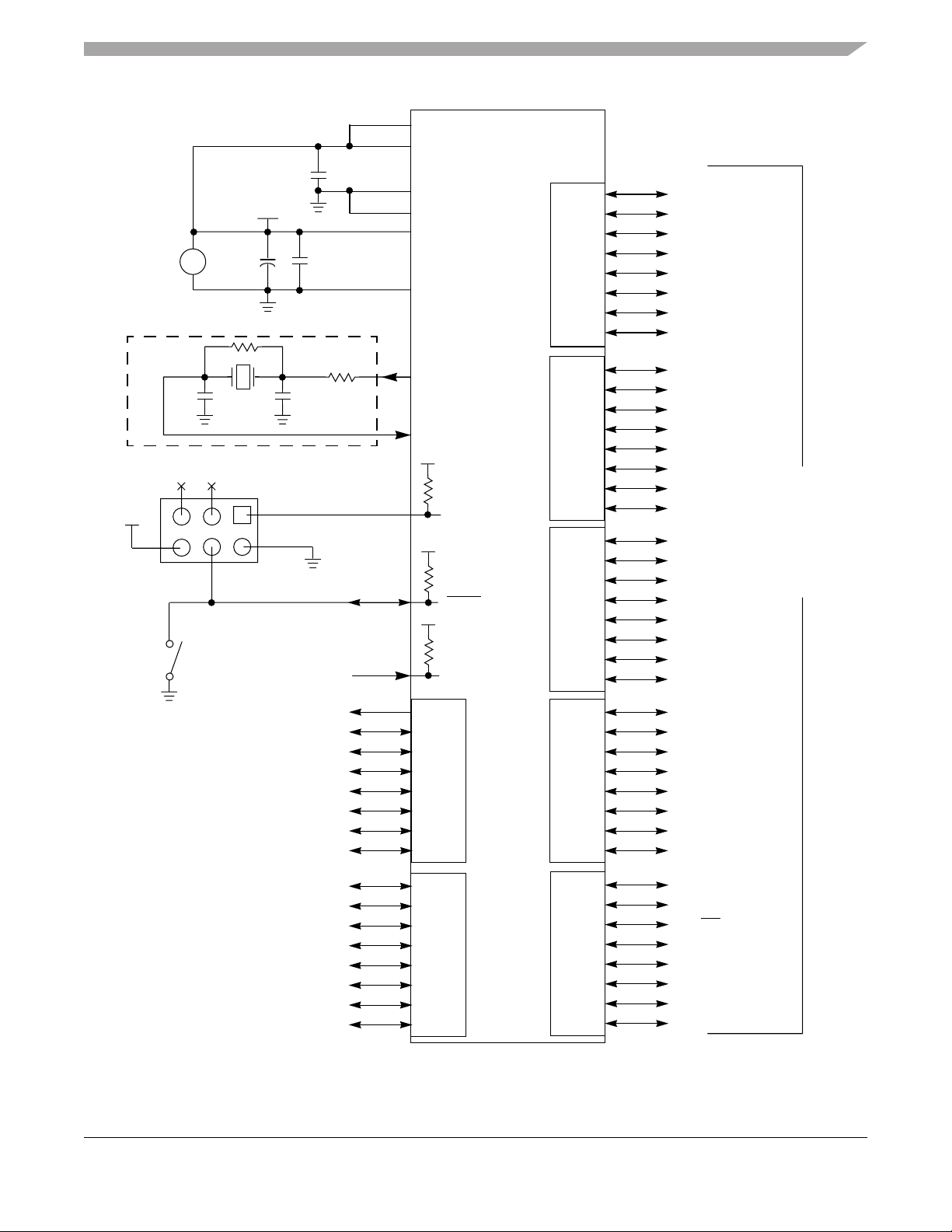

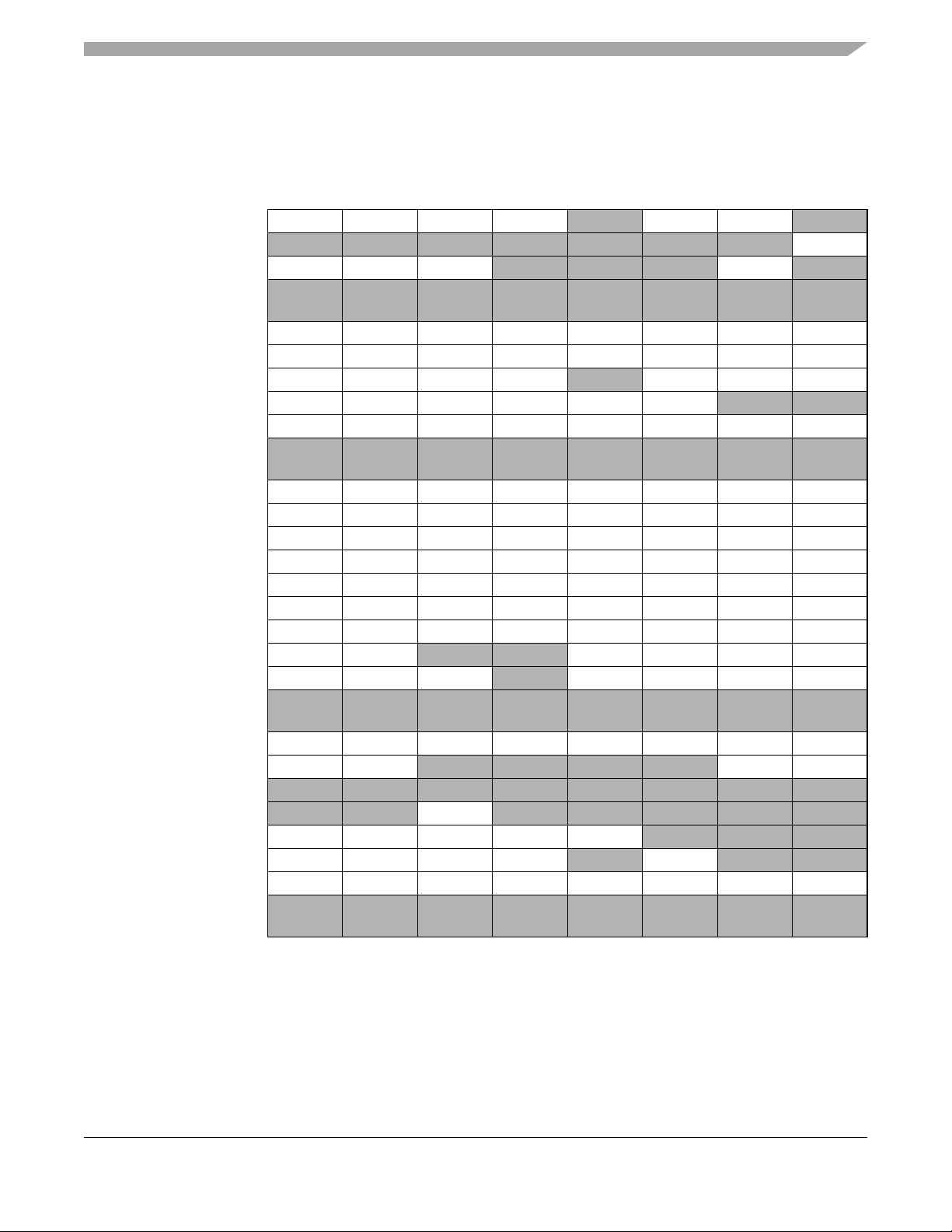

1.3 MCU Block Diagrams

These block diagrams show the structure of the MC9S08GB/GT MCUs.

MCU Block Diagrams

RESET

NOTE 4

IRQ

NOTES 2, 3

V

DDAD

V

SSAD

V

REFH

V

REFL

HCS08 CORE

BDC

HCS08 SYSTEM CONTROL

RESETS AND INTERRUPTS

MODES OF OPERATION

POWER MANAGEMENT

RTI

IRQ LVD

USER FLASH

(GB60 = 61,268 BYTES)

(GB32 = 32,768 BYTES)

USER RAM

(GB60 = 4096 BYTES)

(GB32 = 2048 BYTES)

ANALOG-TO-DIGITAL

CONVERTER (ATD1)

INTERNAL CLOCK

GENERATOR (ICG)

LOW-POWER OSCILLATOR

CPU

COP

10-BIT

INTERNAL BUS

DEBUG

MODULE (DBG)

8-BIT KEYBOARD

INTERRUPT MODULE (KBI1)

IIC MODULE (IIC1)

SERIAL COMMUNICATIONS

INTERFACE MODULE (SCI1)

SERIAL COMMUNICATIONS

INTERFACE MODULE (SCI2)

3-CHANNEL TIMER/PWM

MODULE (TPM1)

5-CHANNEL TIMER/PWM

MODULE (TPM2)

SERIAL PERIPHERAL

INTERFACE MODULE (SPI1)

PORT A

PORT B

PORT C

PORT D

PORT E

PORT F

8

PTA7/KBI1P7–

PTA0/KBI1P0

8

PTB7/AD1P7–

PTB0/AD1P0

PTC7

PTC6

PTC5

PTC4

PTC3/SCL1

PTC2/SDA1

PTC1/RxD2

PTC0/TxD2

PTD7/TPM2CH4

PTD6/TPM2CH3

PTD5/TPM2CH2

PTD4/TPM2CH1

PTD3/TPM2CH0

PTD2/TPM1CH2

PTD1/TPM1CH1

PTD0/TPM1CH0

PTE7

PTE6

PTE5/SPSCK1

PTE4/MOSI1

PTE3/MISO1

PTE2/SS1

PTE1/RxD1

PTE0/TxD1

8

PTF7–PTF0

NOTES 1, 6

NOTE 1

NOTES 1, 5

NOTE 1

NOTE 1

NOTES 1, 5

V

DD

V

SS

VOLTAGE

REGULATOR

NOTES:

1. Port pins are software configurable with pullup device if input port.

2. Pin contains software configurable pullup/pulldown device if IRQ

enabled (IRQPE = 1).

3. IRQ does not have a clamp diode to V

above V

4. Pin contains integrated pullup device.

DD

.

. IRQ should not be driven

DD

PORT G

PTG7

PTG6

PTG5

PTG4

PTG3

PTG2/EXTAL

PTG1/XTAL

PTG0/BKGD/MS

NOTE 1

5. High current drive

6. Pins PTA[7:4] contain both pullup and pulldown devices. Pulldown

available when KBI enabled (KBIPn = 1).

Figure 1-1. MC9S08GBxx Block Diagram

MC9S08GB/GT Data Sheet, Rev. 2.3

Freescale Semiconductor 19

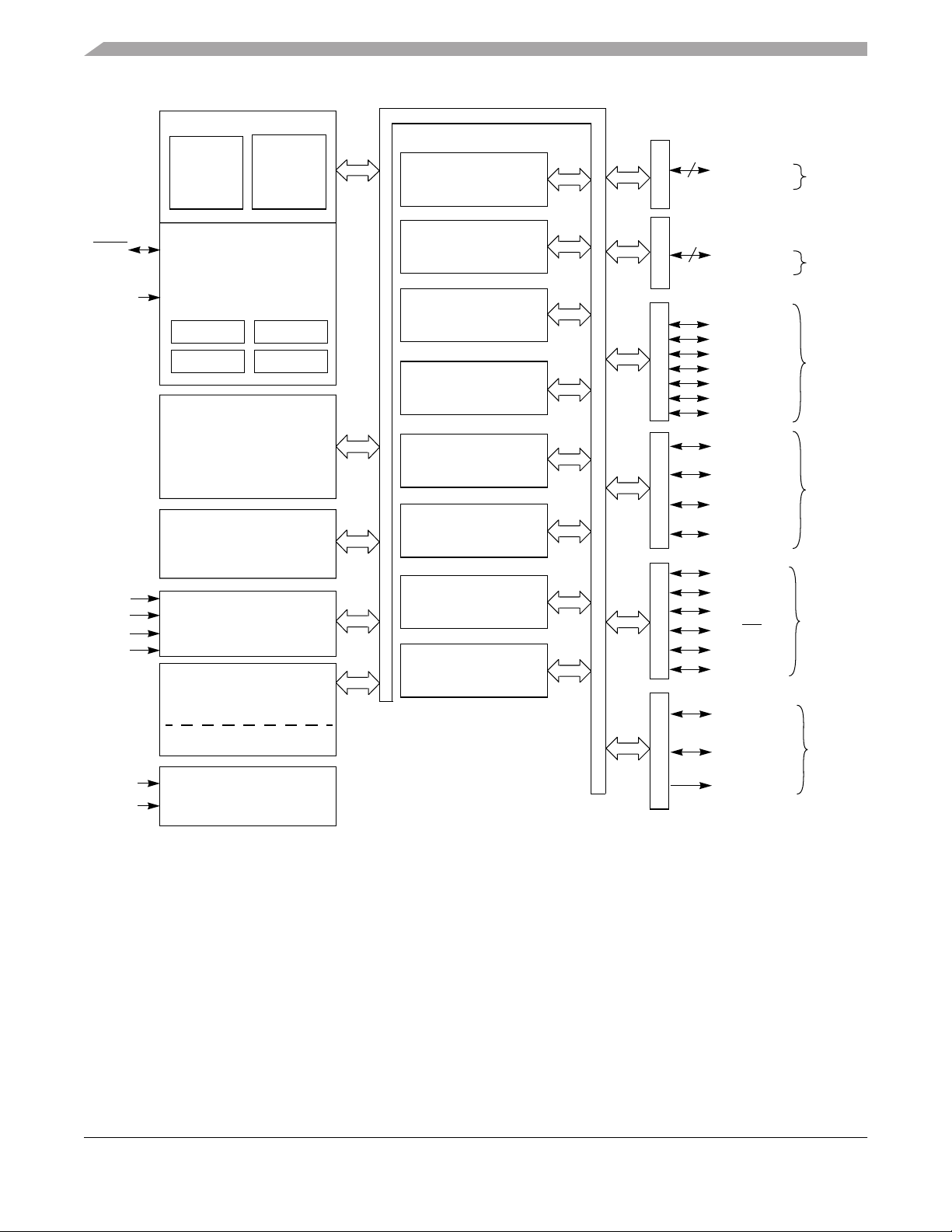

Chapter 1 Introduction

RESET

NOTE 4

IRQ

NOTES 2, 3

V

DDAD

V

SSAD

V

REFH

V

REFL

V

DD

V

SS

HCS08 CORE

BDC

HCS08 SYSTEM CONTROL

RESETS AND INTERRUPTS

MODES OF OPERATION

POWER MANAGEMENT

RTI

IRQ LVD

USER FLASH

(GT60 = 61,268 BYTES)

(GT32 = 32,768 BYTES)

(GT16 = 16,384 BYTES)

USER RAM

(GT60 = 4096 BYTES)

(GT32 = 2048 BYTES)

(GT16 = 1024 BYTES)

ANALOG-TO-DIGITAL

CONVERTER (ATD1)

INTERNAL CLOCK

GENERATOR (ICG)

LOW-POWER OSCILLATOR

VOLTAGE

REGULATOR

CPU

COP

10-BIT

INTERNAL BUS

DEBUG

MODULE (DBG)

8-BIT KEYBOARD

INTERRUPT MODULE (KBI1)

IIC MODULE (IIC1)

SERIAL COMMUNICATIONS

INTERFACE MODULE (SCI1)

SERIAL COMMUNICATIONS

INTERFACE MODULE (SCI2)

3-CHANNEL TIMER/PWM

MODULE (TPM1)

(NOTE 8)

5-CHANNEL TIMER/PWM

MODULE (TPM2)

(NOTE 8)

SERIAL PERIPHERAL

INTERFACE MODULE (SPI1)

PORT A

PORT B

PORT C

PORT D

PORT E

PORT G

8

PTA7/KBI1P7–

PTA0/KBI1P0

8

PTB7/AD1P7–

PTB0/AD1P0

PTC6 (NOTE 6)

PTC5 (NOTE 6)

PTC4

PTC3/SCL1

PTC2/SDA1

PTC1/RxD2

PTC0/TxD2

PTD4/TPM2CH1

PTD3/TPM2CH0

PTD1/TPM1CH1

PTD0/TPM1CH0

PTE5/SPSCK1

PTE4/MOSI1

PTE3/MISO1

PTE2/SS1

PTE1/RxD1

PTE0/TxD1

PTG2/EXTAL

PTG1/XTAL

PTG0/BKGD/MS

NOTES 1, 7

NOTE 1

NOTES 1, 5

NOTE 1

NOTE 1

NOTE 1

NOTES:

1. Port pins are software configurable with pullup device if input port.

2. Pin contains software configurable pullup/pulldown device if IRQ enabled (IRQPE = 1).

3. IRQ does not have a clamp diode to V

4. Pin contains integrated pullup device.

. IRQ should not be driven above VDD.

DD

5. High current drive

6. PTC[6:5] are not available on the 42-pin SDIP package.

7. Pins PTA[7:4] contain both pullup and pulldown devices. Pulldown available when KBI enabled (KBIPn = 1).

8. Only two timer channels per TPM are bonded out. All channels are available for use as software compare.

Figure 1-2. MC9S08GTxx Block Diagram

MC9S08GB/GT Data Sheet, Rev. 2.3

20 Freescale Semiconductor

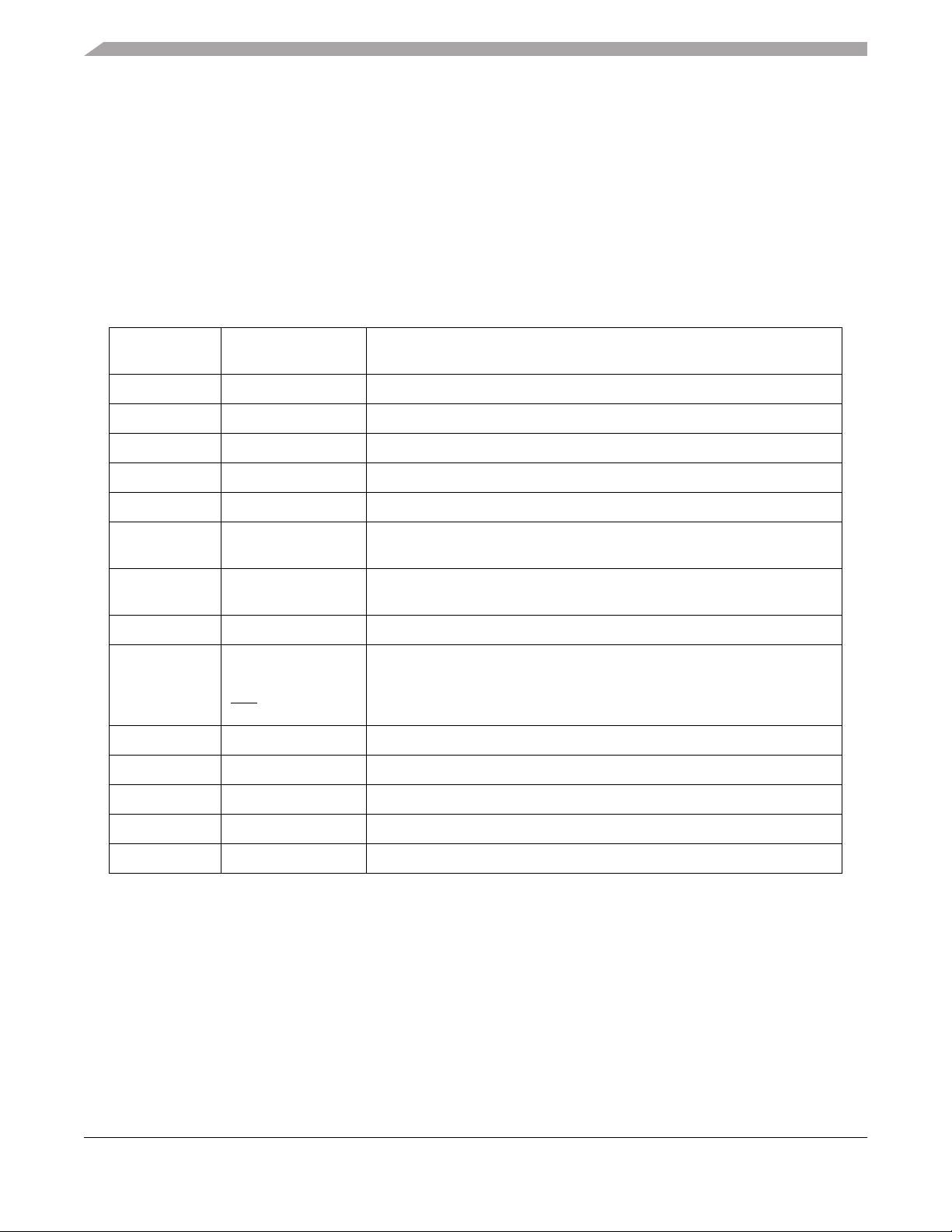

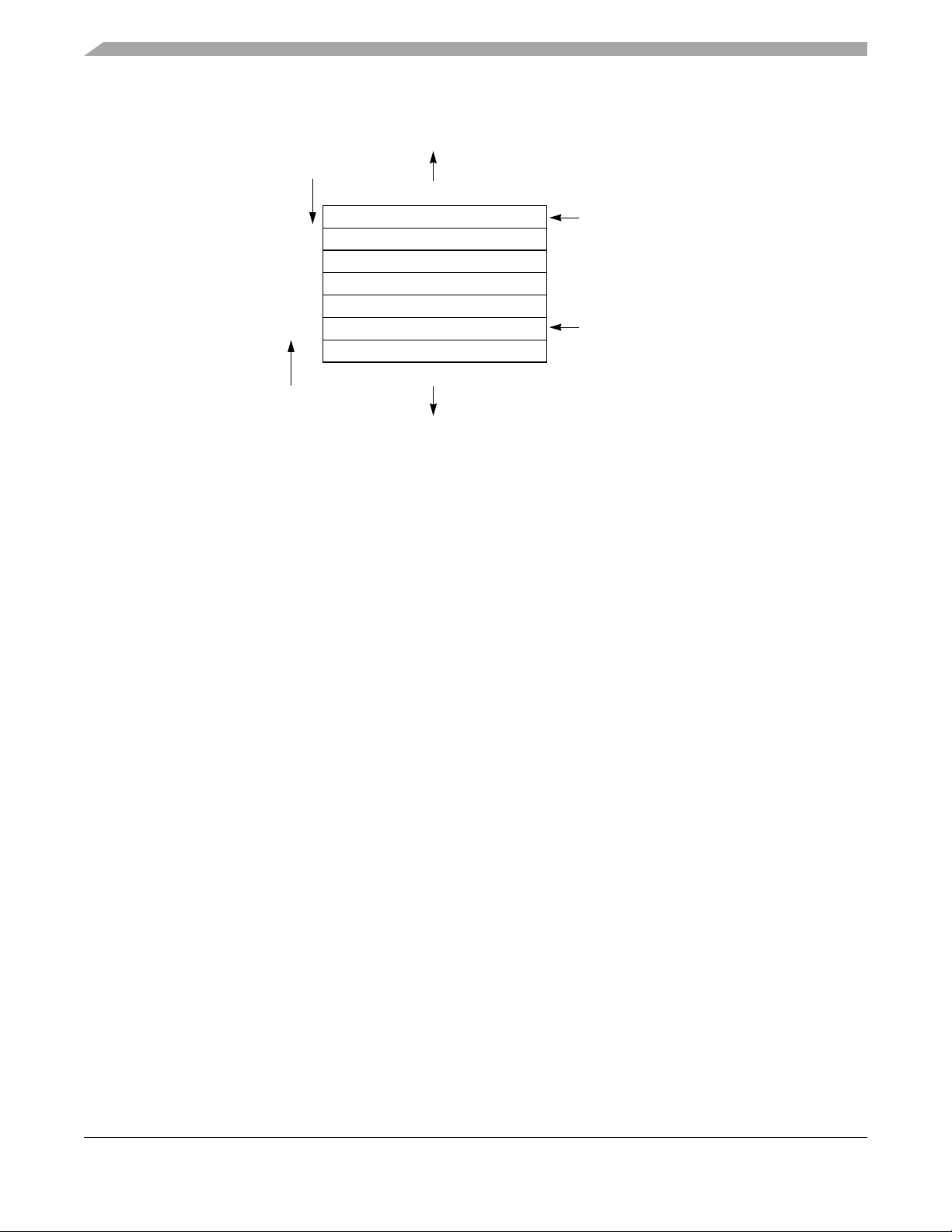

Table 1-2 lists the functional versions of the on-chip modules.

Table 1-2. Block Versions

Module Version

Analog-to-Digital Converter (ATD) 3

Internal Clock Generator (ICG) 2

Inter-Integrated Circuit (IIC) 1

Keyboard Interrupt (KBI) 1

Serial Communications Interface (SCI) 1

Serial Peripheral Interface (SPI) 3

Timer Pulse-Width Modulator (TPM) 1

Central Processing Unit (CPU) 2

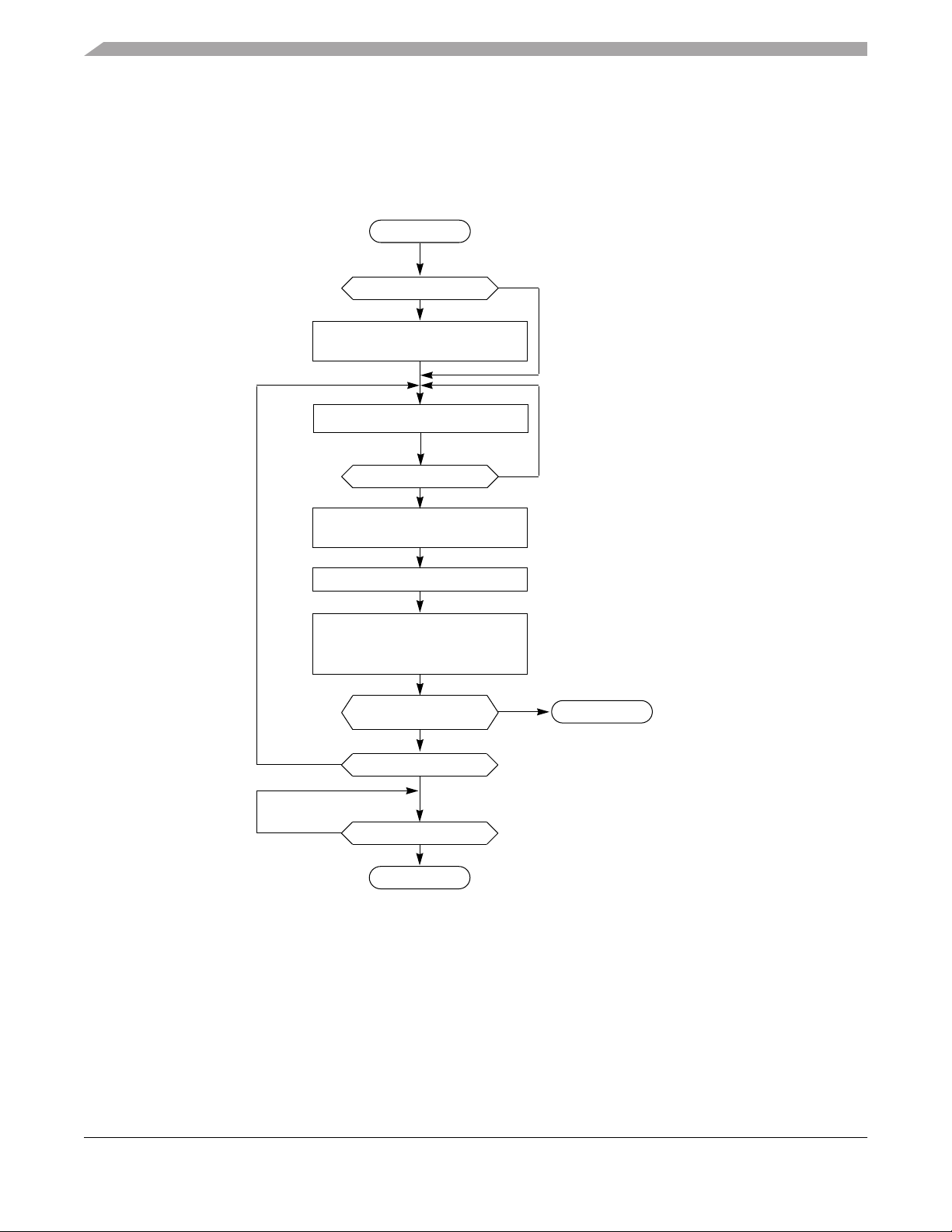

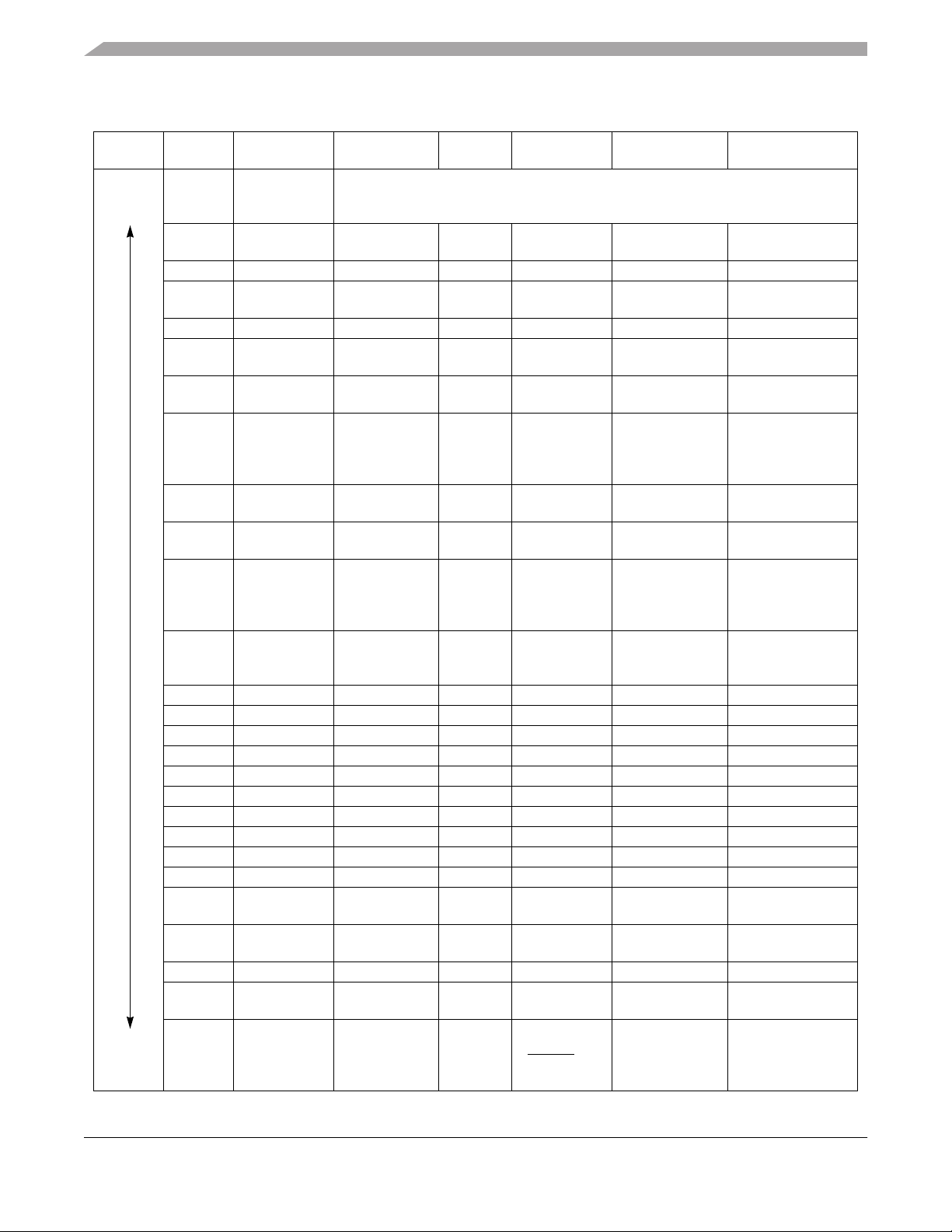

1.4 System Clock Distribution

System Clock Distribution

ICGERCLK

FFE

SYSTEM

CONTROL

LOGIC

RTI

TPM1 TPM2 IIC1 SCI1 SCI2 SPI1

÷2

ICG

ICGOUT

ICGLCLK*

CPU

* ICGLCLK is the alternate BDC clock source for the MC9S08GB/GT.

FIXED FREQ CLOCK (XCLK)

÷2

BUSCLK

BDC

ATD1

ATD has min and max

frequency requirements.

See Chapter 1, “Introduction”

and Appendix A, “Electrical

Characteristics.

RAM FLASH

FLASH has frequency

requirements for program

and erase operation.

See Appendix A, “Electrical

Characteristics.

Figure 1-3. System Clock Distribution Diagram

Some of the modules inside the MCU have clock source choices. Figure 1-3 shows a simplified clock

connection diagram. The ICG supplies the clock sources:

• ICGOUT is an output of the ICG module. It is one of the following:

— The external crystal oscillator

— An external clock source

— The output of the digitally-controlled oscillator (DCO) in the frequency-locked loop

sub-module

Control bits inside the ICG determine which source is connected.

MC9S08GB/GT Data Sheet, Rev. 2.3

Freescale Semiconductor 21

Chapter 1 Introduction

• FFE is a control signal generated inside the ICG. If the frequency of ICGOUT > 4 × the frequency

of ICGERCLK, this signal is a logic 1 and the fixed-frequency clock will be the ICGERCLK.

Otherwise the fixed-frequency clock will be BUSCLK.

• ICGLCLK — Development tools can select this internal self-clocked source (~ 8 MHz) to speed

up BDC communications in systems where the bus clock is slow.

• ICGERCLK — External reference clock can be selected as the real-time interrupt clock source.

MC9S08GB/GT Data Sheet, Rev. 2.3

22 Freescale Semiconductor

Chapter 2 Pins and Connections

2.1 Introduction

This section describes signals that connect to package pins. It includes a pinout diagram, a table of signal

properties, and detailed discussion of signals.

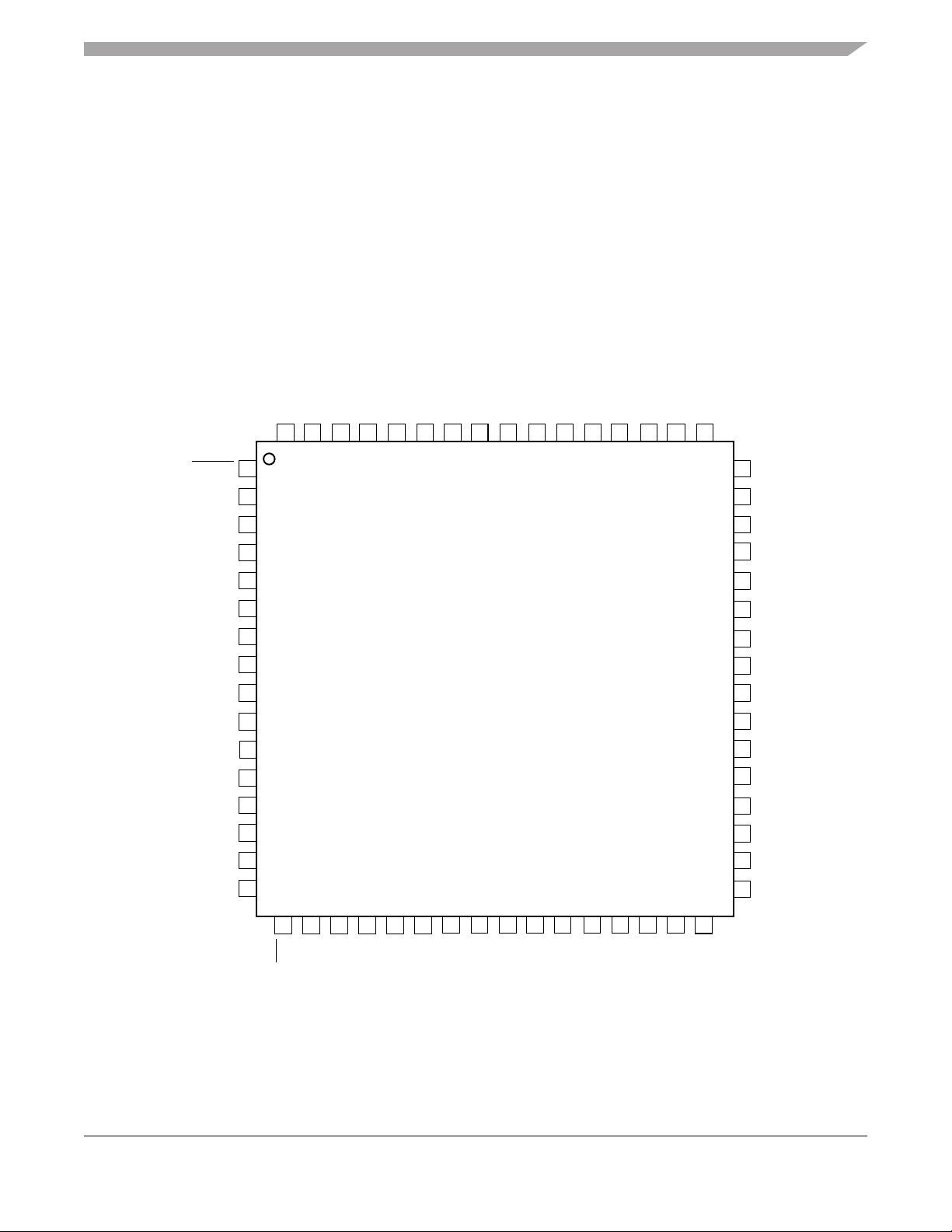

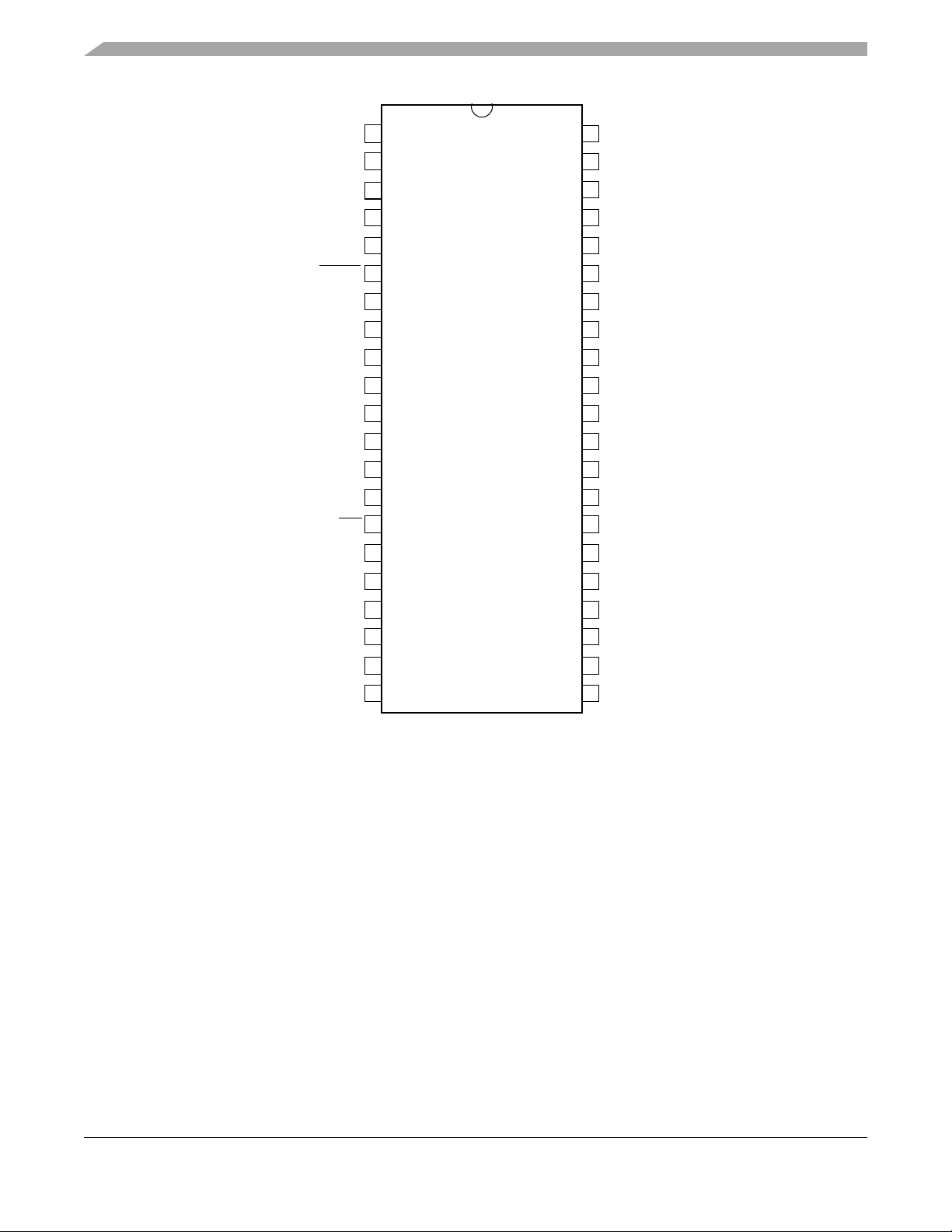

2.2 Device Pin Assignment

DDAD

SSAD

57

V

V

56

PTF1

PTF0

PTA7/KBI1P7

PTA5/KBI1P5

PTA6/KBI1P6

PTA4/KBI1P4

505152535455

PTA3/KBI1P3

49

48

47

46

45

44

43

42

41

40

PTA2/KBI1P2

PTA1/KBI1P1

PTA0/KBI1P0

PTF7

PTF6

PTF5

V

REFL

V

REFH

PTB7/AD1P7

RESET

PTG7

PTC0/TxD2

PTC1/RxD2

PTC2/SDA1

PTC3/SCL1

PTC4

PTC5

PTC6

PTG6

PTG5

PTG4

64

63 62 61

1

2

3

4

5

6

7

8

9

PTG2/EXTAL

PTG3

60

PTG0/BKGD/MS

PTG1/XTAL

58

59

PTC7

PTF2

PTF3

PTF4

PTE0/TxD1

PTE1/RxD1

IRQ

16

10

11

12

13

14

15

17

PTE2/SS1

19

18

PTE4/MOSI1

PTE3/MISO1

20 21 22

PTE6

PTE5/SPSCK1

23

PTE7

27

24

25

26

SS

DD

V

V

PTD0/TPM1CH0

28 29 30 31

PTD1/TPM1CH1

PTD2/TPM1CH2

PTD3/TPM2CH0

PTD5/TPM2CH2

PTD4/TPM2CH1

39

PTB6/AD1P6

38

PTB5/AD1P5

37

PTB4/AD1P4

PTB3/AD1P3

36

35

PTB2/AD1P2

34

PTB1/AD1P1

PTB0/AD1P0

33

32

PTD6/TPM2CH3

PTD7/TPM2CH4

Figure 2-1. MC9S08GBxx in 64-Pin LQFP Package

MC9S08GB/GT Data Sheet, Rev. 2.3

Freescale Semiconductor 23

Chapter 2 Pins and Connections

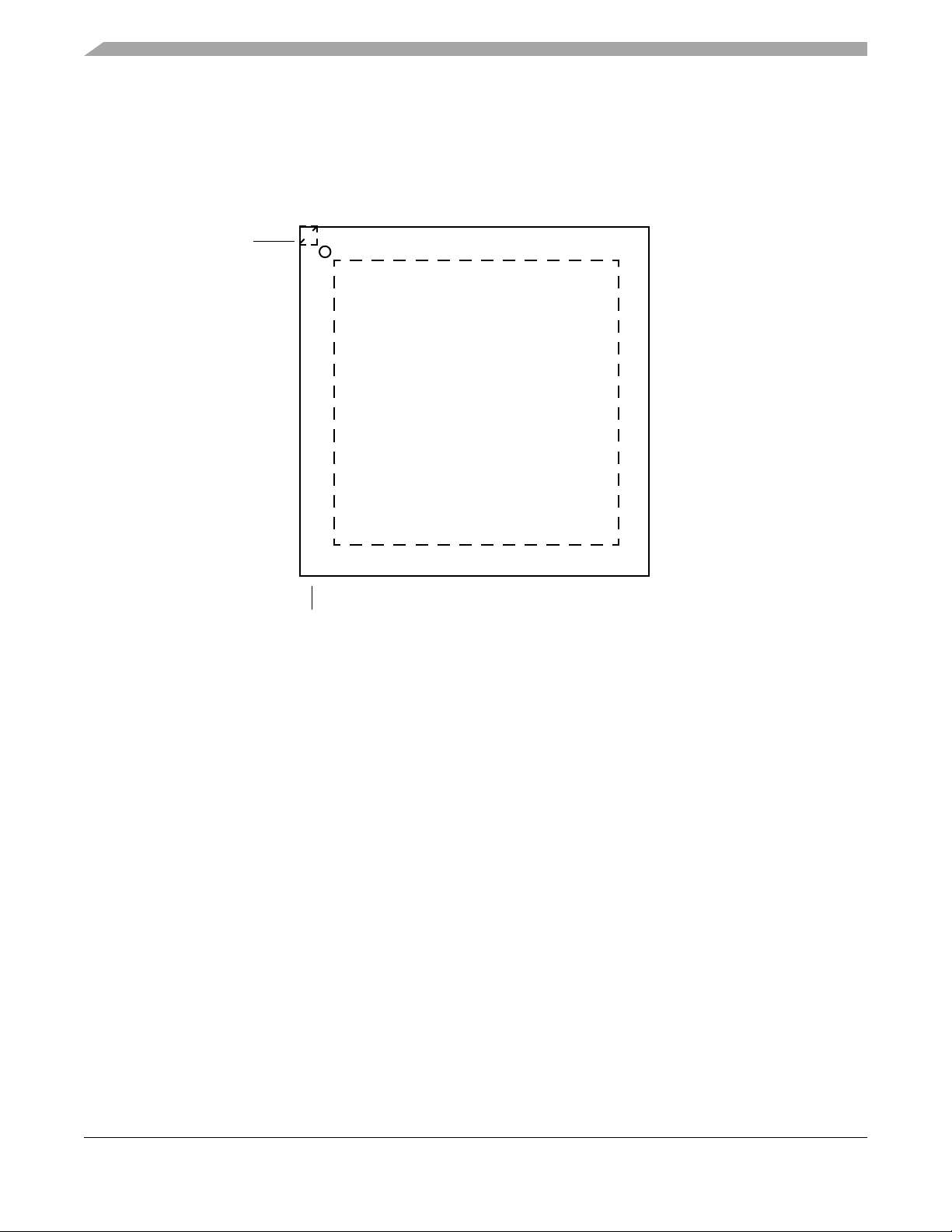

RESET

PTC0/TxD2

PTC1/RxD2

PTC2/SDA1

PTC3/SCL1

PTC4

PTC5

PTC6

PTE0/TxD1

PTE1/RxD1

PTC7

IRQ

DDAD

SSAD

PTG2/EXTAL

PTG1/XTAL

PTG3

47

48

1

PTG0/BKGD/MS

46

45

V

V

44

43

PTA6/KBI1P6

PTA7/KBI1P7

42

41

2

3

4

5

6

7

8

9

10

11

12

14

15

16

17

18

19

13

20

PTA4/KBI1P4

PTA5/KBI1P5

40

21

PTA3/KBI1P3

39

38

22

23

PTA2/KBI1P2

37

PTA1/KBI1P1

36

PTA0/KBI1P0

35

V

34

REFL

V

33

REFH

PTB7/AD1P7

32

PTB6/AD1P6

31

PTB5/AD1P5

30

PTB4/AD1P4

29

PTB3/AD1P3

28

PTB2/AD1P2

27

PTB1/AD1P1

26

PTB0/AD1P0

25

24

SS2

V

DD

V

SS1

V

PTE2/SS1

PTE3/MISO1

PTE5/SPSCK1

PTE4/MOSI1

PTD1/TPM1CH1

PTD0/TPM1CH0

PTD2/TPM1CH2

PTD3/TPM2CH0

PTD4/TPM2CH1

Figure 2-2. MC9S08GTxx in 48-Pin QFN Package

MC9S08GB/GT Data Sheet, Rev. 2.3

24 Freescale Semiconductor

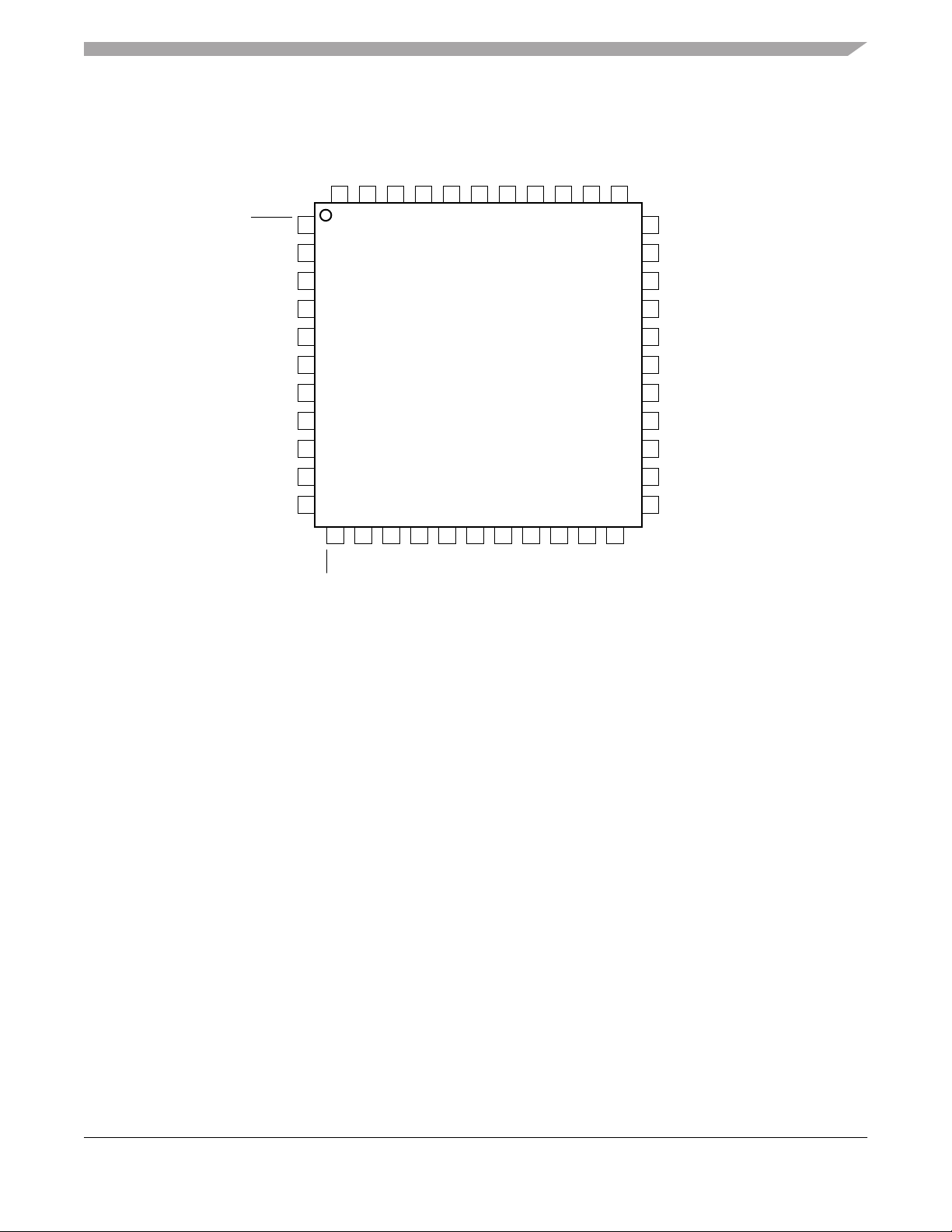

RESET

PTC0/TxD2

PTC1/RxD2

PTC2/SDA1

PTC3/SCL1

PTC4

PTC5

PTC6

PTE0/TxD1

PTE1/RxD1

IRQ

1

11

PTG2/EXTAL

44

2

3

4

5

6

7

8

9

10

12

PTG1/XTAL

PTG0/BKGD/MS

43

42

13

14

SSAD

V

41

15

DDAD

V

PTA7/KBI1P7

40

16

17

SS

DD

V

V

PTA6/KBI1P6

39

38

18

PTA4/KBI1P4

PTA5/KBI1P5

37

19

PTA3/KBI1P3

36

35

20

21

PTA2/KBI1P2

34

PTA1/KBI1P1

33

PTA0/KBI1P0

32

V

31

30

29

28

27

26

25

24

REFL

V

REFH

PTB7/AD1P7

PTB6/AD1P6

PTB5/AD1P5

PTB4/AD1P4

PTB3/AD1P3

PTB2/AD1P2

PTB1/AD1P1

23

22

Device Pin Assignment

PTE2/SS1

PTE3/MISO1

PTE4/MOSI1

PTE5/SPSCK1

PTD1/TPM1CH1

PTD0/TPM1CH0

PTD3/TPM2CH0

PTB0/AD1P0

PTD4/TPM2CH1

Figure 2-3. MC9S08GTxx in 44-Pin QFP Package

MC9S08GB/GT Data Sheet, Rev. 2.3

Freescale Semiconductor 25

Chapter 2 Pins and Connections

V

DDAD

V

SSAD

PTG0/BKGD/MS

PTG1/XTAL

PTG2/EXTAL

RESET

PTC0/TxD2

PTC1/RXD2

PTC2/SDA1

PTC3/SCL1

PTC4

PTE0/TxD1

PTE1/RxD1

IRQ

PTE2/

SS1

PTE3/MISO1

PTE4/MOSI1

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15 28

16 27

17 26

42

41

40

39

38

37

36

35

34

33

32

31

30

29

PTA7/KBI1P7

PTA6/KBI1P6

PTA5/KBI1P5

PTA4/KBI1P4

PTA3/KBI1P3

PTA2/KBI1P2

PTA1/KBI1P1

PTA0/KBI1P0

V

REFL

V

REFH

PTB7/AD1P7

PTB6/AD1P6

PTB5/AD1P5

PTB4/AD1P4

PTB3/AD1P3

PTB2/AD1P2

PTB1/AD1P1

PTE5/SPSCK1

V

SS

V

DD

PTD0/TPM1CH0

18 25

19 24

20 23

21 22

PTB0/AD1P0

PTD4/TPM2CH1

PTD3/TPM2CH0

PTD1/TPM1CH1

Figure 2-4. MC9S08GTxx in 42-Pin SDIP Package

2.3 Recommended System Connections

Figure 2-5 shows pin connections that are common to almost all MC9S08GB60 application systems.

MC9S08GTxx connections will be similar except for the number of I/O pins available. A more detailed

discussion of system connections follows.

MC9S08GB/GT Data Sheet, Rev. 2.3

26 Freescale Semiconductor

SYSTEM

POWER

NOTE 1

C1

BACKGROUND HEADER

V

DD

NOTES:

1. Not required if

using the internal

oscillator option.

2. These are the

same pins as

PTG1 and PTG2.

3. BKGD/MS is the

same pin as PTG0.

4. The 48-pin QFN

has 2 V

(V

SS1

both of which must

be connected to

GND.

+

3 V

10 µF

OPTIONAL

MANUAL

RESET

pins

SS

and V

V

DD

+

C

BLK

R

F

X1

ASYNCHRONOUS

PTG0/BKDG/MS

),

SS2

C

BY

0.1 µF

C2

INTERRUPT

INPUT

PTG1/XTAL

PTG2/EXTAL

PTG3

PTG4

PTG5

PTG6

PTG7

PTF0

PTF1

PTF2

PTF3

PTF4

PTF5

PTF6

PTF7

C

BYAD

0.1 µF

R

S

V

REFH

V

DDAD

V

SSAD

V

REFL

V

DD

V

SS

NOTE 4

XTAL

NOTE 2

EXTAL

NOTE 2

PORT

G

PORT

F

MC9S08GBxx

BKGD/MS

NOTE 3

RESET

IRQ

PORT

A

PORT

B

PORT

C

PORT

D

PORT

E

Recommended System Connections

PTA0/KBI1P0

PTA1/KBI1P1

PTA2/KBI1P2

PTA3/KBI1P3

PTA4/KBI1P4

PTA5/KBI1P5

PTA6/KBI1P6

PTA7/KBI1P7

PTB0/AD1P0

PTB1/AD1P1

PTB2/AD1P2

PTB3/AD1P3

PTB4/AD1P4

PTB5/AD1P5

PTB6/AD1P6

PTB7/AD1P7

PTC0/TxD2

PTC1/RxD2

PTC2/SDA1

PTC3/SCL1

I/O AND

PERIPHERAL

INTERFACE TO

APPLICATION

SYSTEM

PTC4

PTC5

PTC6

PTC7

PTD0/TPM1CH0

PTD1/TPM1CH1

PTD2/TPM1CH2

PTD3/TPM2CH0

PTD4/TPM2CH1

PTD5/TPM2CH2

PTD6/TPM2CH3

PTD7/TPM2CH4

PTE0/TxD1

PTE1/RxD1

SS1

PTE2/

PTE3/MISO1

PTE4/MOSI1

PTE5/SPSCK1

PTE6

PTE7

Figure 2-5. Basic System Connections

MC9S08GB/GT Data Sheet, Rev. 2.3

Freescale Semiconductor 27

Chapter 2 Pins and Connections

2.3.1 Power

VDD and VSS are the primary power supply pins for the MCU. This voltage source supplies power to all

I/O buffer circuitry and to an internal voltage regulator. The internal voltage regulator provides regulated

lower-voltage source to the CPU and other internal circuitry of the MCU.

Typically, application systems have two separate capacitors across the power pins. In this case, there

should be a bulk electrolytic capacitor, such as a 10-µF tantalum capacitor, to provide bulk charge storage

for the overall system and a 0.1-µF ceramic bypass capacitor located as close to the MCU power pins as

practical to suppress high-frequency noise.

V

DDAD

and V

are the analog power supply pins for the MCU. This voltage source supplies power to

SSAD

the ATD. A 0.1-µF ceramic bypass capacitor should be located as close to the MCU power pins as practical

to suppress high-frequency noise.

2.3.2 Oscillator

Out of reset, the MCU uses an internally generated clock (self-clocked mode — f

Self_reset

approximately equivalent to an 8-MHz crystal rate. This frequency source is used during reset startup and

can be enabled as the clock source for stop recovery to avoid the need for a long crystal startup delay. This

MCU also contains a trimmable internal clock generator (ICG) module that can be used to run the MCU.

For more information on the ICG, see Chapter 7, “Internal Clock Generator (ICG) Module.”

The oscillator in this MCU is a Pierce oscillator that can accommodate a crystal or ceramic resonator in

either of two frequency ranges selected by the RANGE bit in the ICGC1 register. Rather than a crystal or

ceramic resonator, an external oscillator can be connected to the EXTAL input pin, and the XTAL output

pin can be used as general I/O.

Refer to Figure 2-5 for the following discussion. R

(when used) and RF should be low-inductance

S

resistors such as carbon composition resistors. Wire-wound resistors, and some metal film resistors, have

too much inductance. C1 and C2 normally should be high-quality ceramic capacitors that are specifically

designed for high-frequency applications.

is used to provide a bias path to keep the EXTAL input in its linear range during crystal startup and its

R

F

value is not generally critical. Typical systems use 1 MΩ to 10 MΩ. Higher values are sensitive to humidity

and lower values reduce gain and (in extreme cases) could prevent startup.

) that is

C1 and C2 are typically in the 5-pF to 25-pF range and are chosen to match the requirements of a specific

crystal or resonator. Be sure to take into account printed circuit board (PCB) capacitance and MCU pin

capacitance when sizing C1 and C2. The crystal manufacturer typically specifies a load capacitance which

is the series combination of C1 and C2 which are usually the same size. As a first-order approximation,

use 10 pF as an estimate of combined pin and PCB capacitance for each oscillator pin (EXTAL and

XTAL).

2.3.3 Reset

RESET is a dedicated pin with a pullup device built in. It has input hysteresis, a high current output driver,

and no output slew rate control. Internal power-on reset and low-voltage reset circuitry typically make

external reset circuitry unnecessary. This pin is normally connected to the standard 6-pin background

MC9S08GB/GT Data Sheet, Rev. 2.3

28 Freescale Semiconductor

Recommended System Connections

debug connector so a development system can directly reset the MCU system. If desired, a manual external

reset can be added by supplying a simple switch to ground (pull reset pin low to force a reset).

Whenever any reset is initiated (whether from an external signal or from an internal system), the reset pin

is driven low for approximately 34 cycles of f

cycles of f

Self_reset

later. If reset was caused by an internal source such as low-voltage reset or watchdog

Self_reset

, released, and sampled again approximately 38

timeout, the circuitry expects the reset pin sample to return a logic 1. If the pin is still low at this sample

point, the reset is assumed to be from an external source. The reset circuitry decodes the cause of reset and

records it by setting a corresponding bit in the system control reset status register (SRS).

Never connect any significant capacitance to the reset pin because that would interfere with the circuit and

sequence that detects the source of reset. If an external capacitance prevents the reset pin from rising to a

valid logic 1 before the reset sample point, all resets will appear to be external resets.

2.3.4 Background / Mode Select (PTG0/BKGD/MS)

The background/mode select (BKGD/MS) shares its function with an I/O port pin. While in reset, the pin

functions as a mode select pin. Immediately after reset rises the pin functions as the background pin and

can be used for background debug communication. While functioning as a background/mode select pin,

the pin includes an internal pullup device, input hysteresis, a standard output driver, and no output slew

rate control. When used as an I/O port (PTG0) the pin is limited to output only.

If nothing is connected to this pin, the MCU will enter normal operating mode at the rising edge of reset.

If a debug system is connected to the 6-pin standard background debug header, it can hold BKGD/MS low

during the rising edge of reset which forces the MCU to active background mode.

The BKGD pin is used primarily for background debug controller (BDC) communications using a custom

protocol that uses 16 clock cycles of the target MCU’s BDC clock per bit time. The target MCU’s BDC

clock could be as fast as the bus clock rate, so there should never be any significant capacitance connected

to the BKGD/MS pin that could interfere with background serial communications.

Although the BKGD pin is a pseudo open-drain pin, the background debug communication protocol

provides brief, actively driven, high speedup pulses to ensure fast rise times. Small capacitances from

cables and the absolute value of the internal pullup device play almost no role in determining rise and fall