Page 1

HCS08

微控制器

freescale.com

MC9S08DZ60

MC9S08DZ48

MC9S08DZ32

MC9S08DZ16

产品介绍:详细信息

MC9S08DZ60

Rev. 3

10/2007

Page 2

MC9S08DZ60 系列产品的特性

8 位 HCS08 中央处理器 (CPU)

• 40-MHz HCS08 CPU (20-MHz 总线)

• HC08 指令集,带附加的 BGND 指令

• 支持最多 32 个中断 / 复位源

片内存储器

• 整个工作电压和温度范围内可读取 / 编程 / 擦除的

Flash 存储器

— MC9S08DZ60 = 60K

— MC9S08DZ48 = 48K

— MC9S08DZ32 = 32K

— MC9S08DZ16 = 16K

• 最大 2K 的 EEPROM 在线可编程内存; 支持 8 字

节单页或 4 字节双页擦除分区; 执行 Flash 程序的

同时可进行编程和擦除操作;支持擦除取消操作

• 最大 4K 的随机存取内存 (RAM)

省电模式

• 两种超低功耗停止模式

• 降低功耗的等待模式

• 超低功耗实时时钟中断,在运行、等待和停止模式

下均可操作

时钟源选项

• 振荡器 (XOSC) — 闭环控制的皮尔斯 (Pierce)

振荡器;支持范围 31.25 kHz 至 38.4 kHz 或 1

MHz 至 16MHz 之间的晶体或陶瓷谐振器

• 多功能时钟生成器 (MCG) — PLL 和 FLL 模式

(在使用内部温度补偿时 FLL 能够达到 1.5% 内的

偏差);带微调功能的内部参考时钟源;带可选择

晶体振荡器或陶瓷谐振器的外部参考时钟源

系统保护

外围设备

•ADC —24 通道, 12 位分辨率, 2.5uS 转换时间,

自动比较功能, 1.7 mV/?C 温度传感器,包含内部

能隙参考源通道

•ACMPx —两个模拟比较器,支持比较器输出的上

升、下降或任意边沿触发的中断;可选择与内部参

考电压源进行比较

• MSCAN —CAN 协议– V2.0 A 和 B ;支持标准和

扩展数据帧;支持远程帧; 5 个带有 FIFO 存储机

制的接收缓冲器;灵活的接收识别符过滤器,可编

程如下:2 x 32 位、 4 x 16 位或 8 x 8 位

•SCIx —两个 SCI,可支持 LIN 2.0 协议和 SAE

J2602 协议;全双工;主节点支持 break 信号生成

;从节点支持 break 信号检测;支持激活边沿唤醒

• SPI —全双工或单线双向;双重缓冲发射和接收;

主从模式选择;支持高位优先或低位优先的移位

•IIC —支持最高 100kbps 的总线波特率;多主节点

模式运行;可编程的从地址;通用呼叫地址;逐字

节数据传输驱动的中断

•TPMx — 一个 6 通道 (TPM1)和一个 2 通道

(TPM2);可支持输入捕捉,输出比较,或每个

通道带缓冲的边沿对齐 PWM 输出

•RTC —(实时时钟计数器)8 位模数计数器,带基

于二进制或十进制的预分频器;实时时钟功能,使

用外部晶体和 RTC 来确保精确时基、时间、日历

或任务调度功能;内带低功耗振荡器 (1 kHz),

用于周期唤醒而不需要外部器件

输入 / 输出

•53个通用输入 / 输出 (I/O)管脚和 1 个专用输入

管脚

•24个中断管脚,每个管脚带触发极性选择

• 所有输入管脚上带电压滞后和可配置的上下拉器件

• 所有输入管脚上可配置输出斜率和驱动强度

• 监视微控制器正常操作的看门狗 (COP)复位,

支持选择专用的后备 1-kHz 内部时钟源或总线时钟

运行

• 带复位和中断的低压检测电路;可选择的电压阀值

• 支持非法指令代码复位

• 支持非法操作地址复位

• 支持 Flash 块保护

• 支持时钟信号丢失保护

开发支持

• 单线背景调试接口

• 片上及在线仿真 (ICE),带总线实时捕获功能

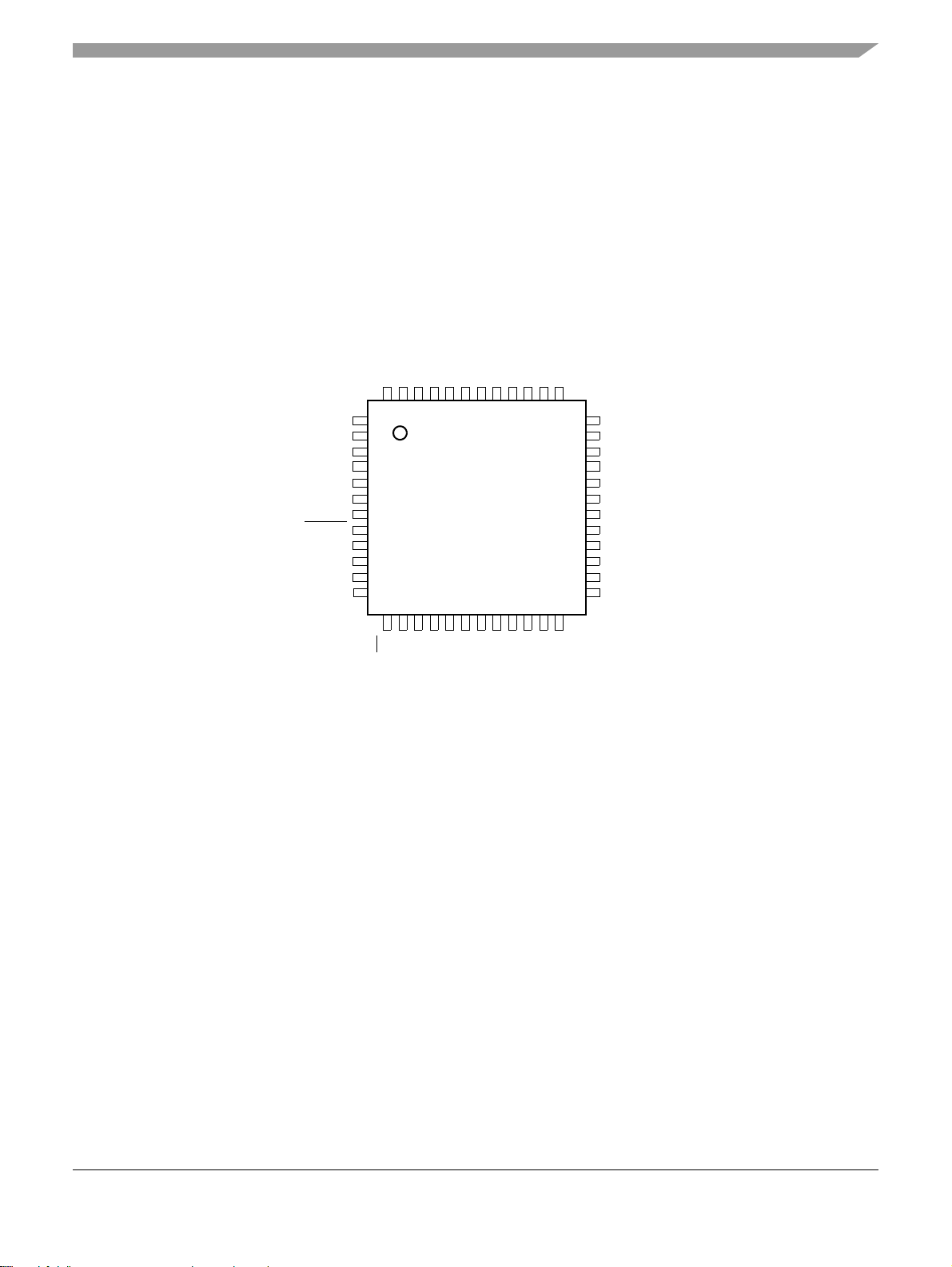

封装选项

•64管脚小尺寸四方扁平封装 (LQFP)—10x10

mm

•48管脚小尺寸四方扁平封装 (LQFP) — 7x7 mm

•32管脚小尺寸四方扁平封装 (LQFP) — 7x7 mm

Page 3

MC9S08DZ60 产品介绍

包括 MC9S08DZ60

MC9S08DZ48

MC9S08DZ32

MC9S08DZ16

MC9S08DZ60

第 3 版

2007 年 10 月

Freescale™ 和 Freescale 标识为飞思卡尔半导体公司的商标。

© 2007 年飞思卡尔半导体公司版权所有。保留所有权利。

Page 4

Running H/F 4

修订历史

为了向您提供最新的信息,我们在万维网上发布的文档将是最新版本的。您的打印版可能是较早的版本。

要确定你的信息是否是最新信息,请访问:

http://freescale.com/

以下修订历史表总结了对本文的修改历史。

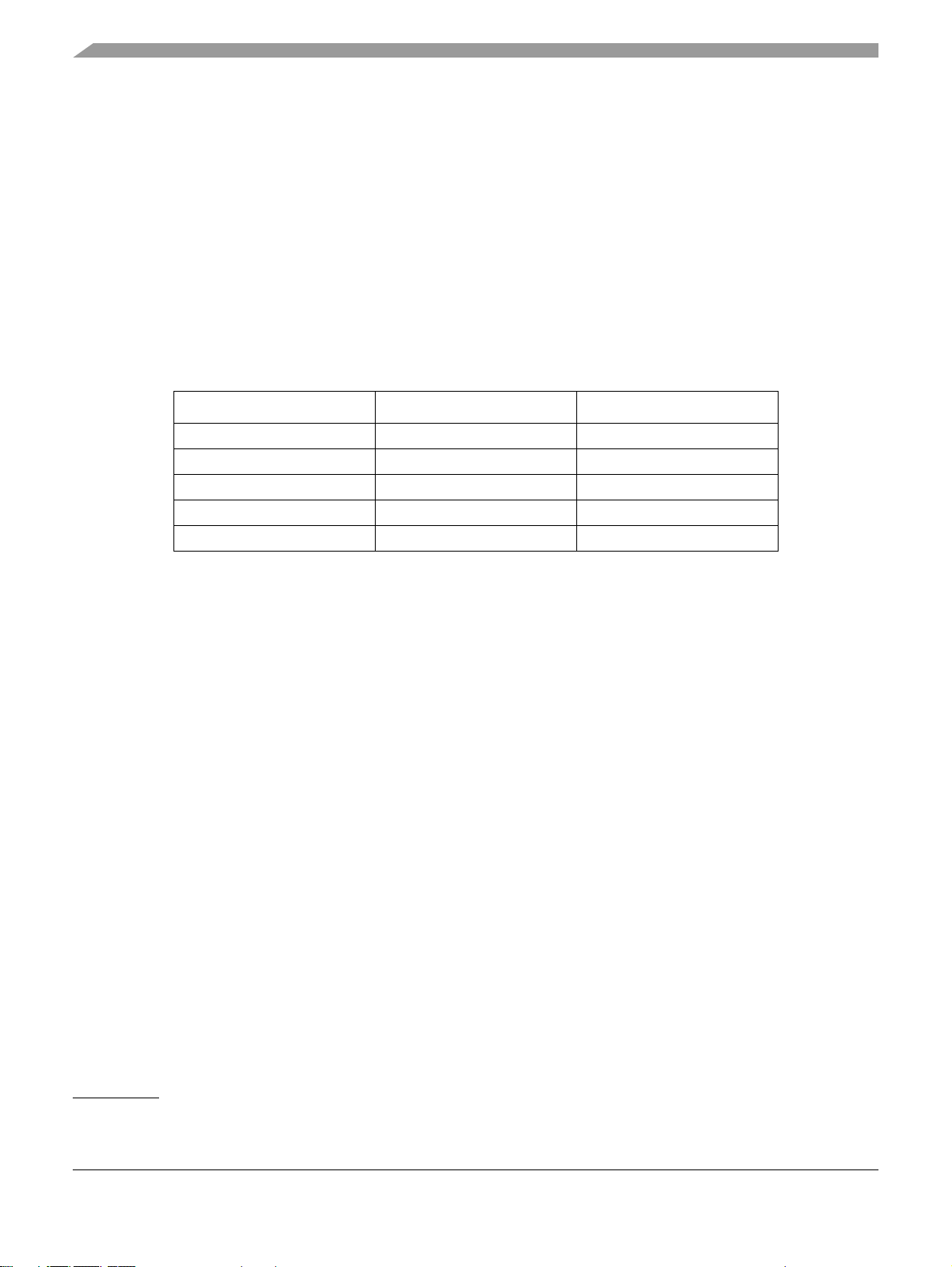

修订版本编

号

1

2

3

修订日期 修改内容描述

2006 年 6 月 面向早期样本用户的详细信息。

2007 年 9 月 产品发布。删除了 64 管脚 QFN 封装。寄存器总结部分中 MSCAN 寄存器从标准模式修改

为扩展模式。修正了 SCI 结构图。更新了最新的温度传感器信息。保留了 FTSTMOD。更

新了设备以使用 ADC 12 位模块。修改了 MCG 模块。更新

了 CPU 指令集表。将 TPM 组成模块更新为第 3 版。添加了 TPM 组成模块第 2 版作为使

用 3M05C (或更早版本的)掩码集的设备的附件。对 Electrical 附录进行了重大修改。

2007 年 10 月 删除了两个无意中添加到 MC9S08DZ6 说明书中的两个表格。

© 2007 年飞思卡尔半导体公司版权所有。保留所有权利。

本产品包含 SST 授权的 SuperFlash

# 飞思卡尔半导体公司

‚

技术。

MC9S08DZ60 系列 , 第 3 版

Page 5

第 1 章

器件概述

MC9S08DZ60 系列器件可以为那些希望将 CAN 网络和内嵌的 EEPROM 结合到应用程序中的

客户带来很高的价值。这一结合将可以降低成本,提高性能和质量。

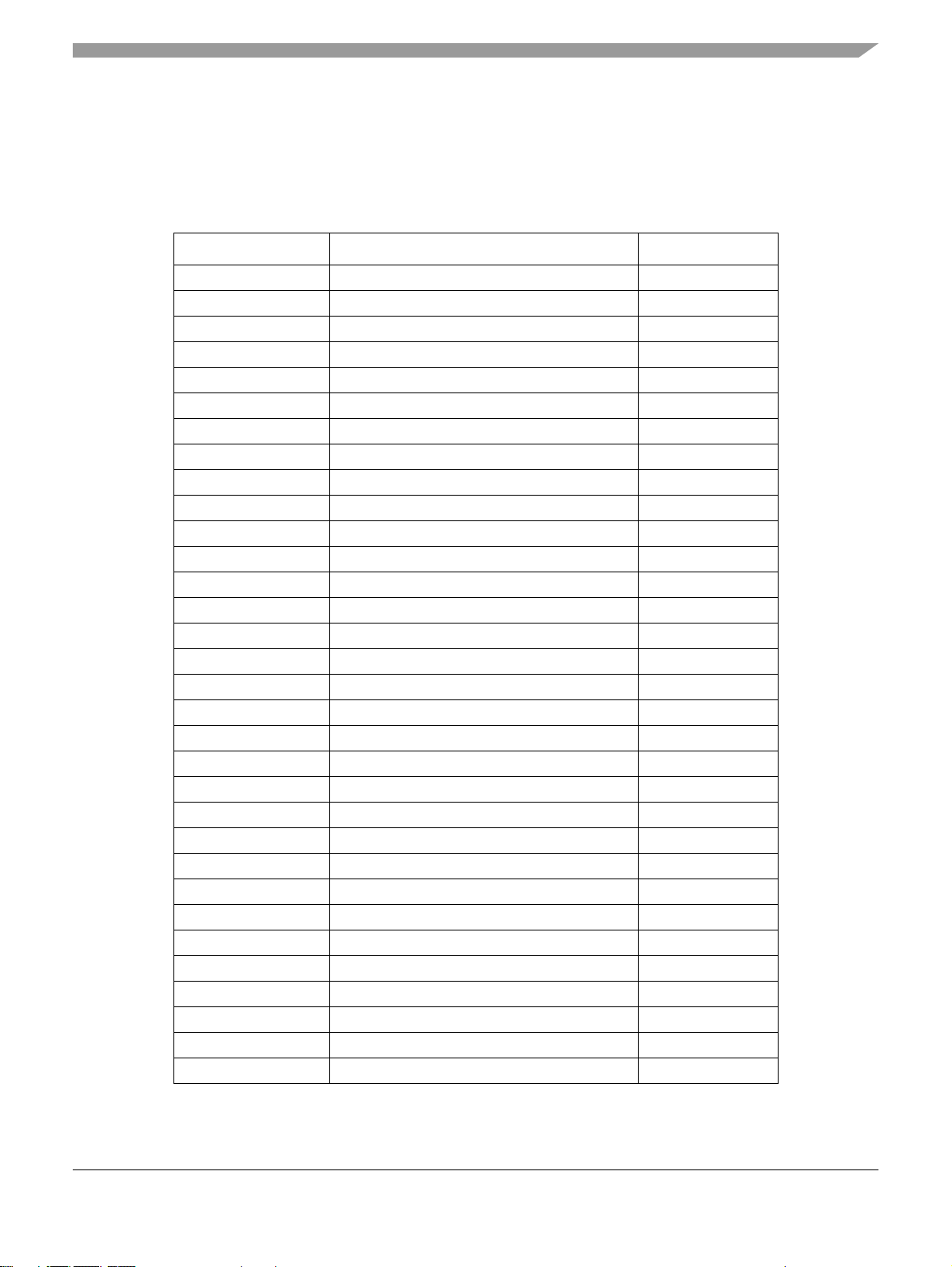

0.1 MC9S08DZ60 系列包含的器件

本产品介绍涵盖了 MC9S08DZ60 系列 MCU 产品的所有成员:

• MC9S08DZ60

• MC9S08DZ48

• MC9S08DZ32

• MC9S08DZ16

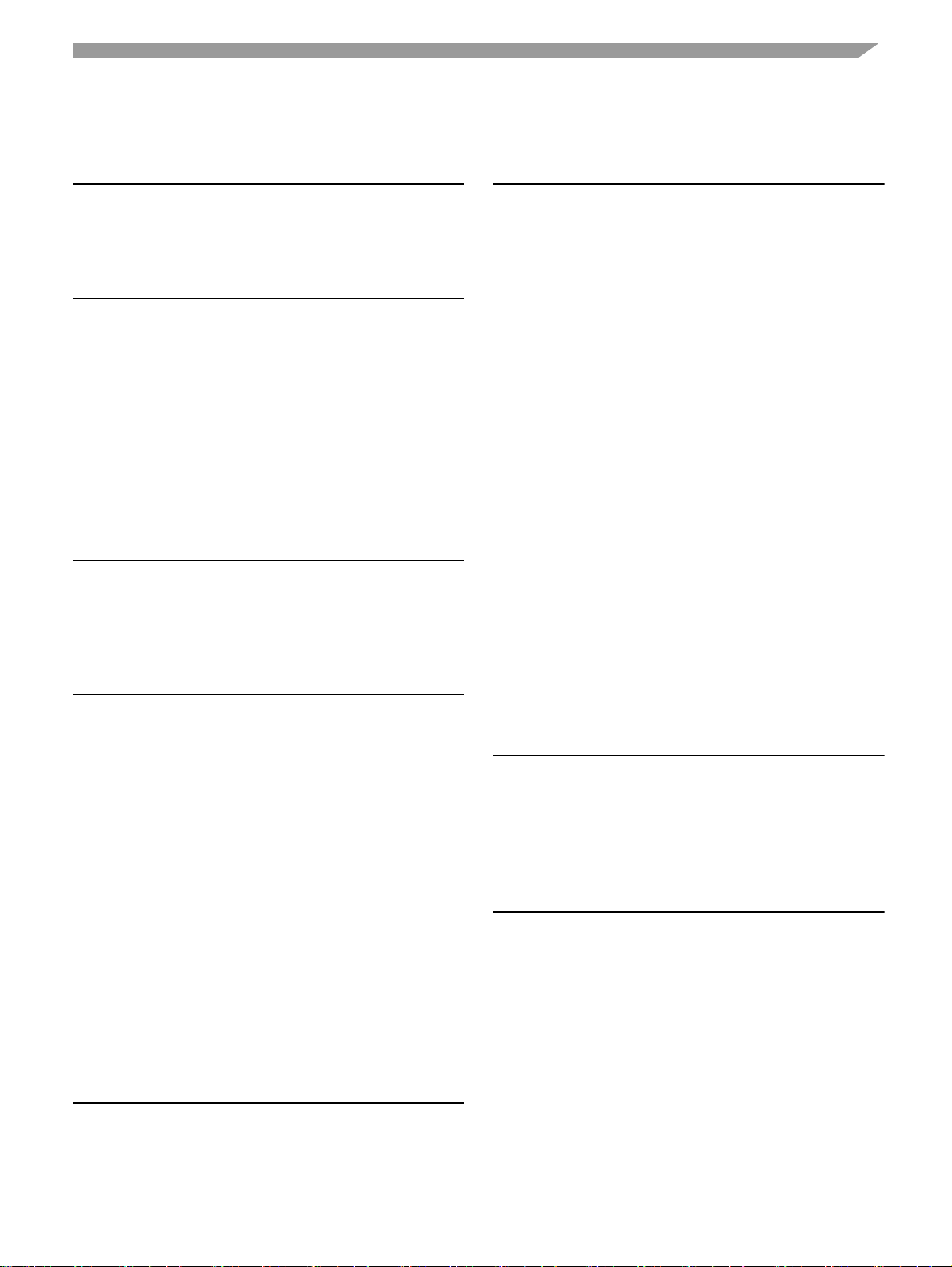

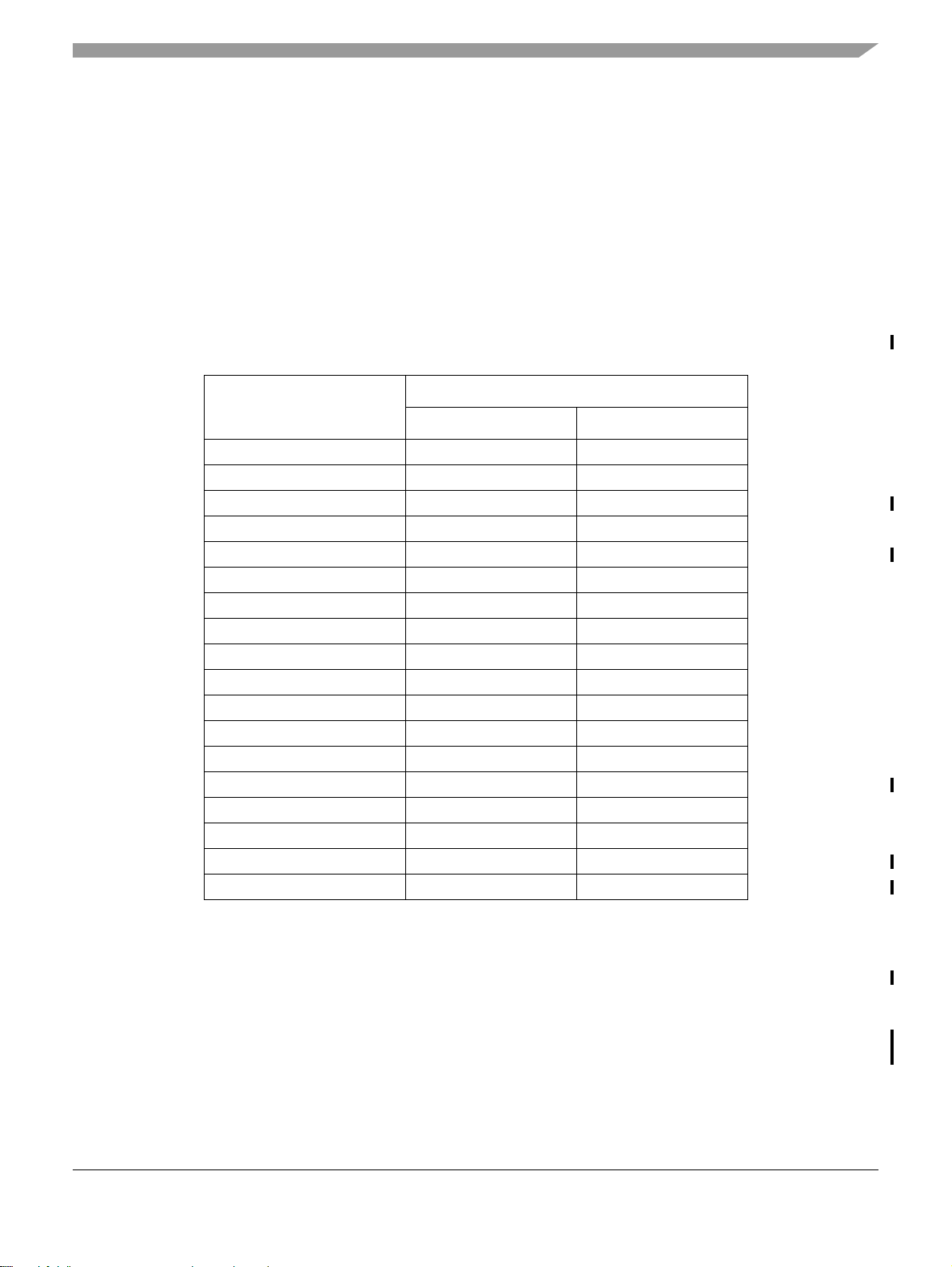

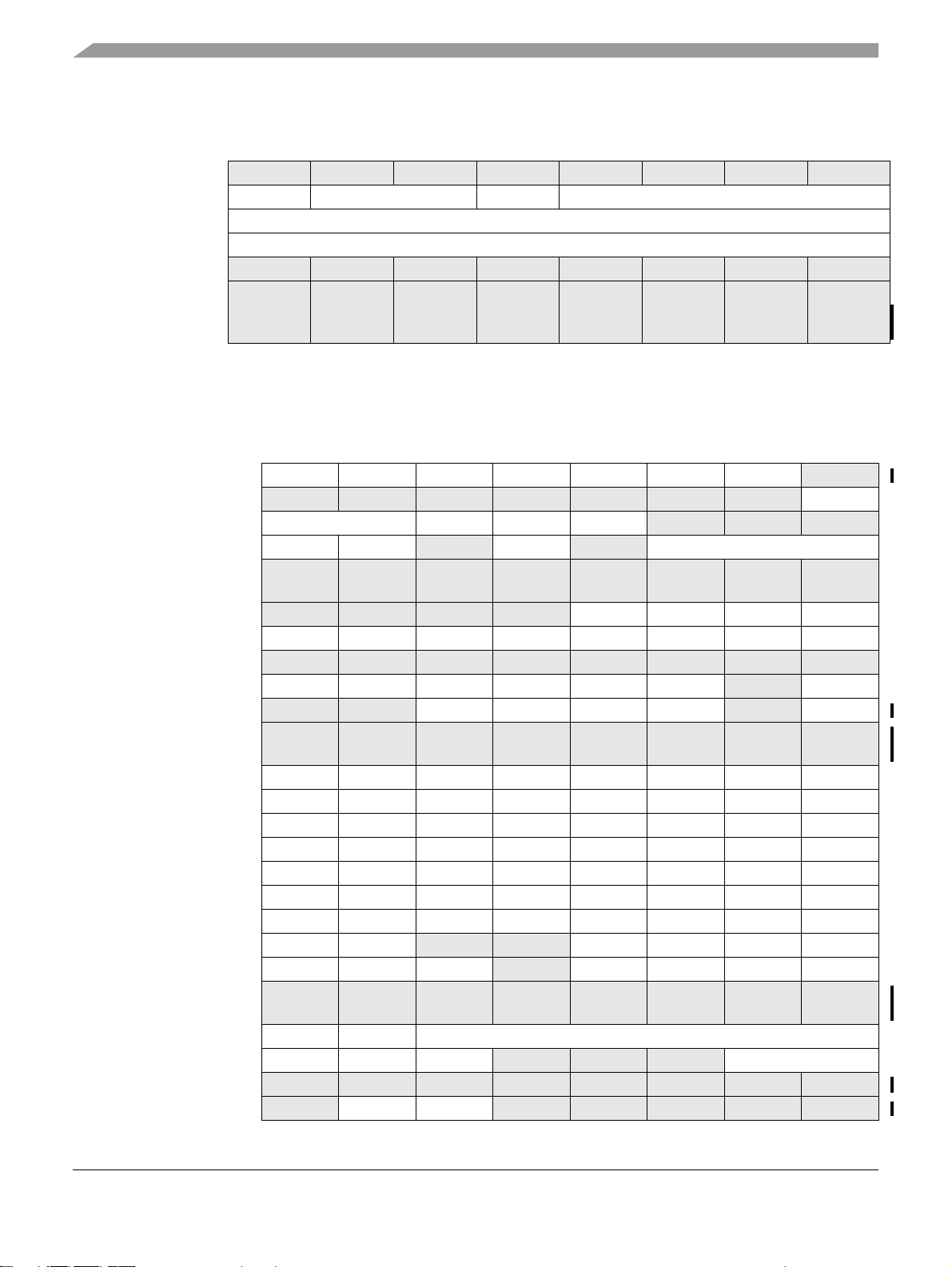

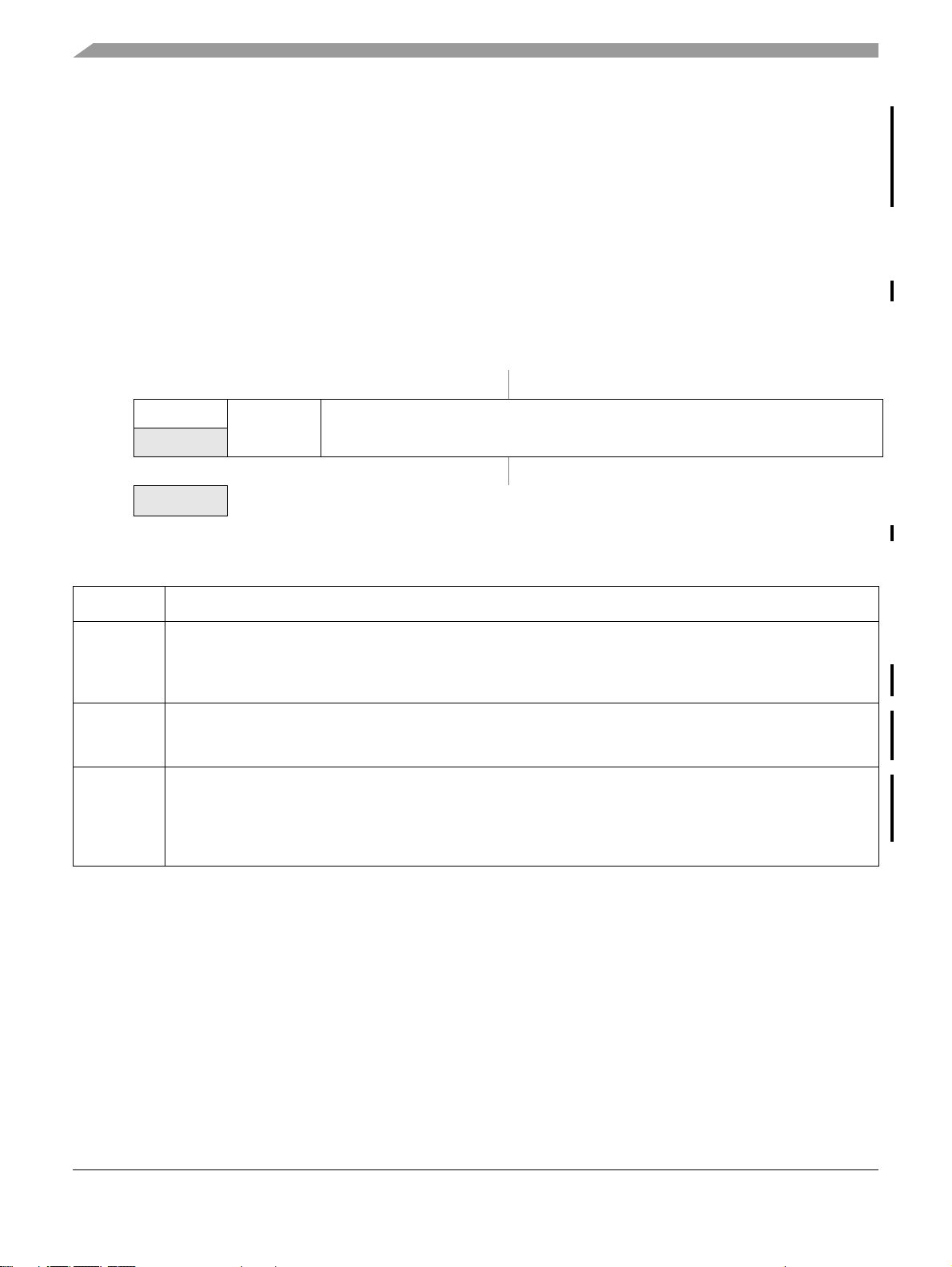

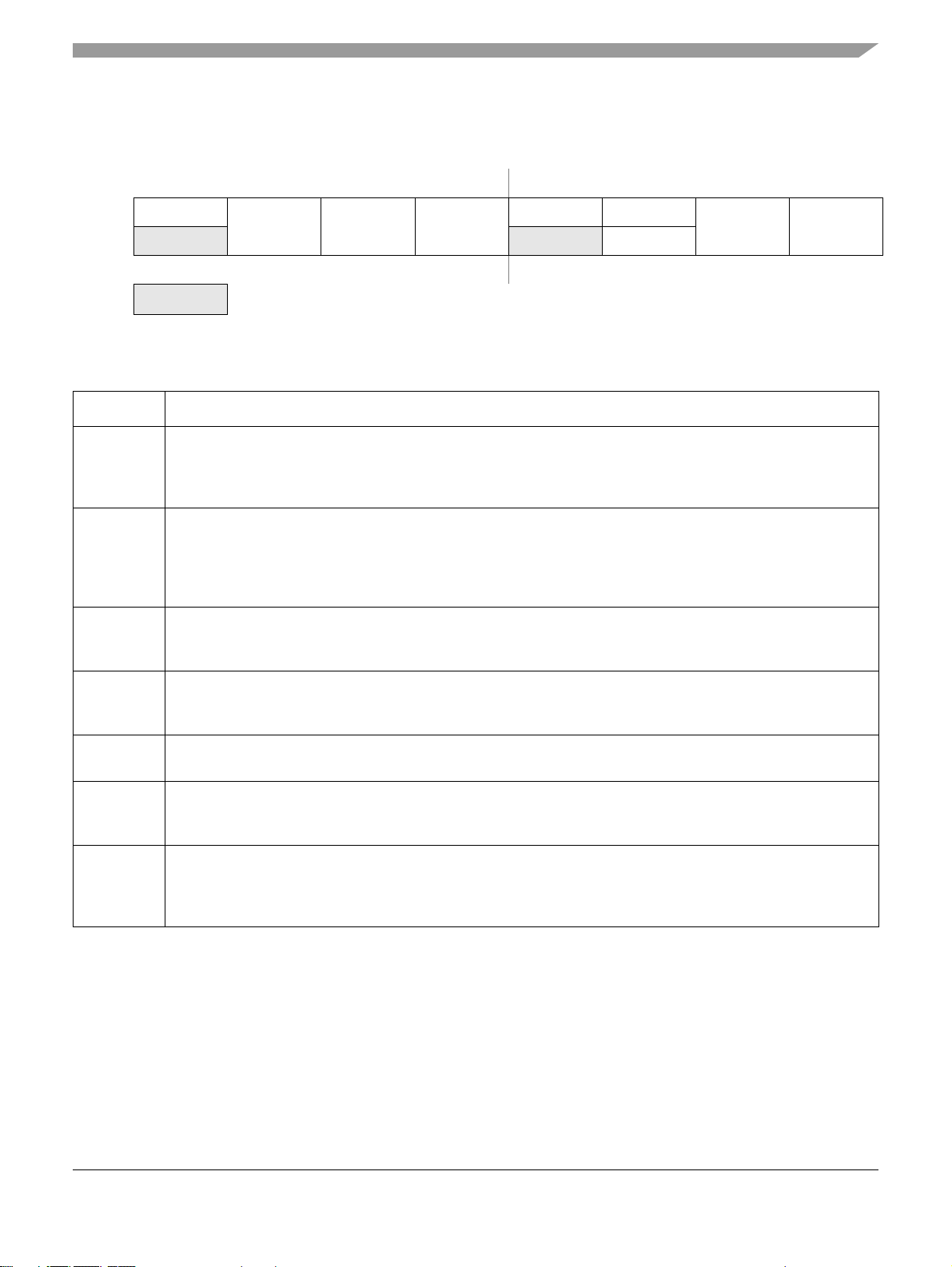

Tabl e 0-1 总结了 MC9S08DZ60 系列产品的各种特性。

MC9S08DZ60 系列 , 第 3 版

飞思卡尔半导体公司 21

Page 6

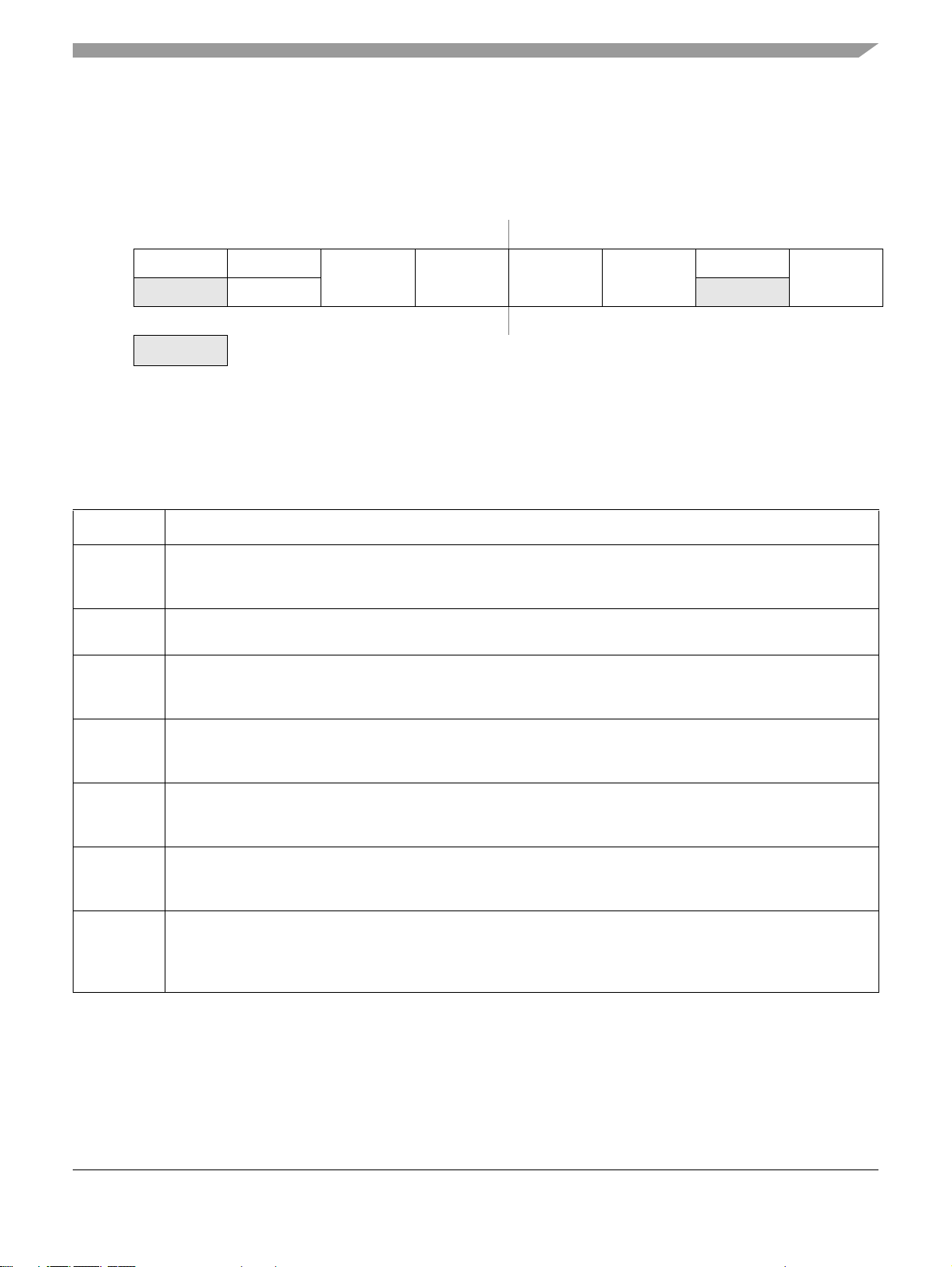

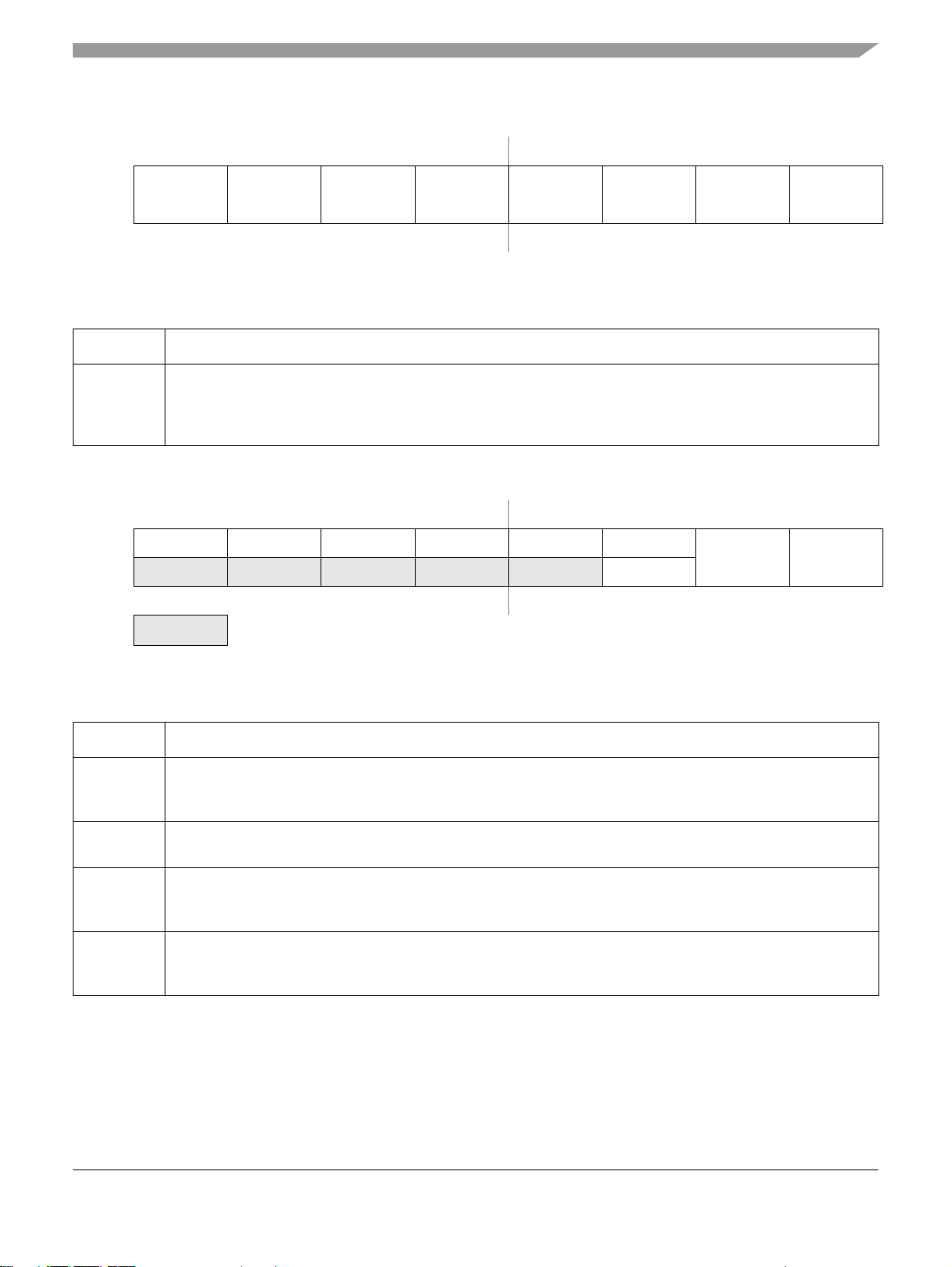

t

Table 0-1. MC9S08DZ60 系列产品的特性 (按 MCU 和管脚数量分)

特性

Flash 大小 (字

节)

RAM 大小 (字

节)

EEPROM 大小

(字节)

管脚数量

ACMP1

ACMP2

ADC 通道数

DBG

IIC

IRQ

MCG

MSCAN

RTC

SCI1

SCI2

SPI

TPM1 通道数

TPM2 通道数

XOSC

COP Watchdog

1

ACMP2O 不可用。

MC9S08DZ60 MC9S08DZ48 MC9S08DZ32 MC9S08DZ16

60032 49152 33792 16896

4096 3072 2048 1024

2048 1536 1024 512

64 48 32 64 48 32 64 48 32 48 32

是

是是

1

no

是是

1

no

是是

1

no

是

1

no

24 16 10 24 16 10 24 16 10 16 10

是

是

是

是

是

是

是

是

是

66466466464

2

是

是

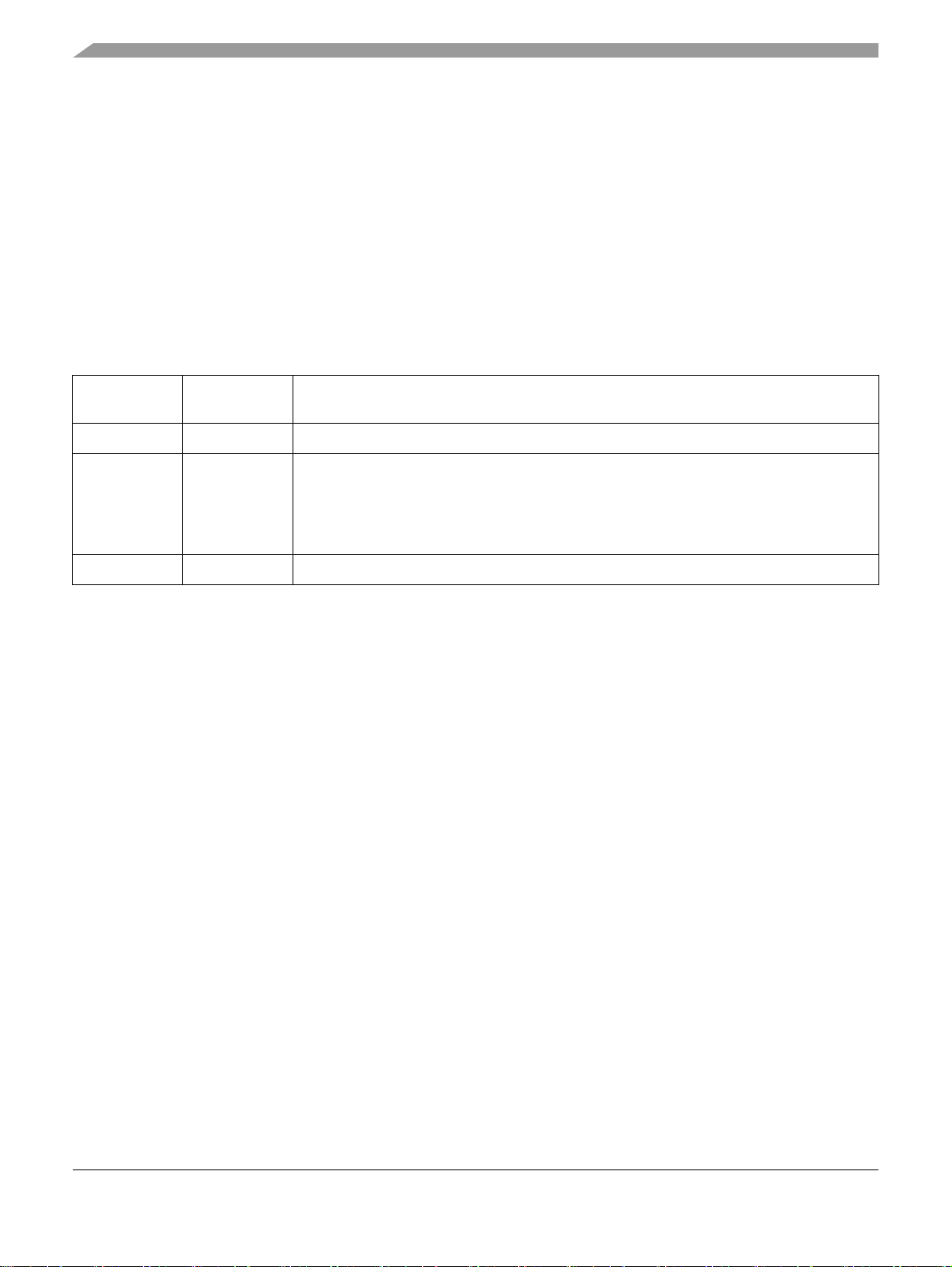

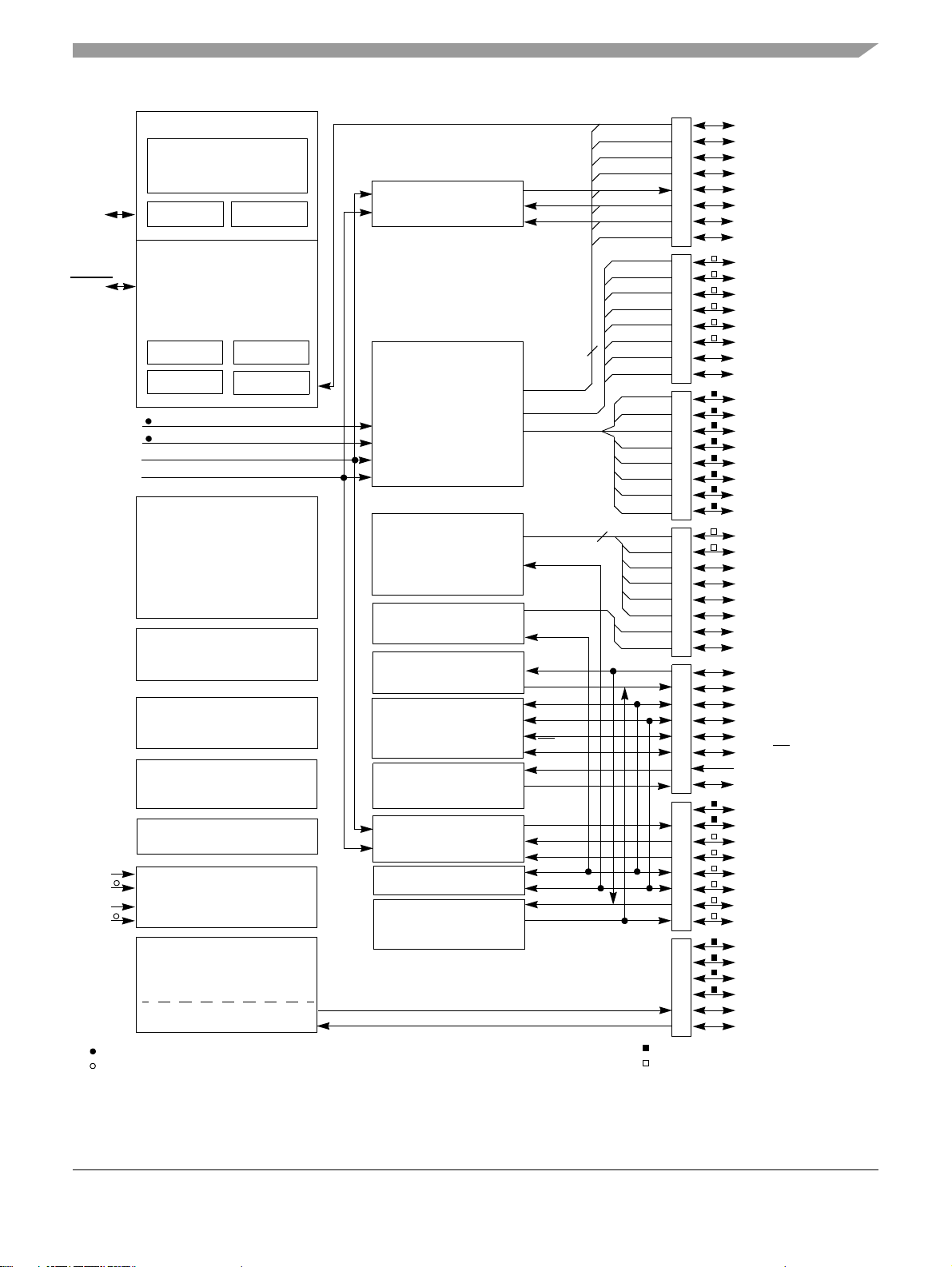

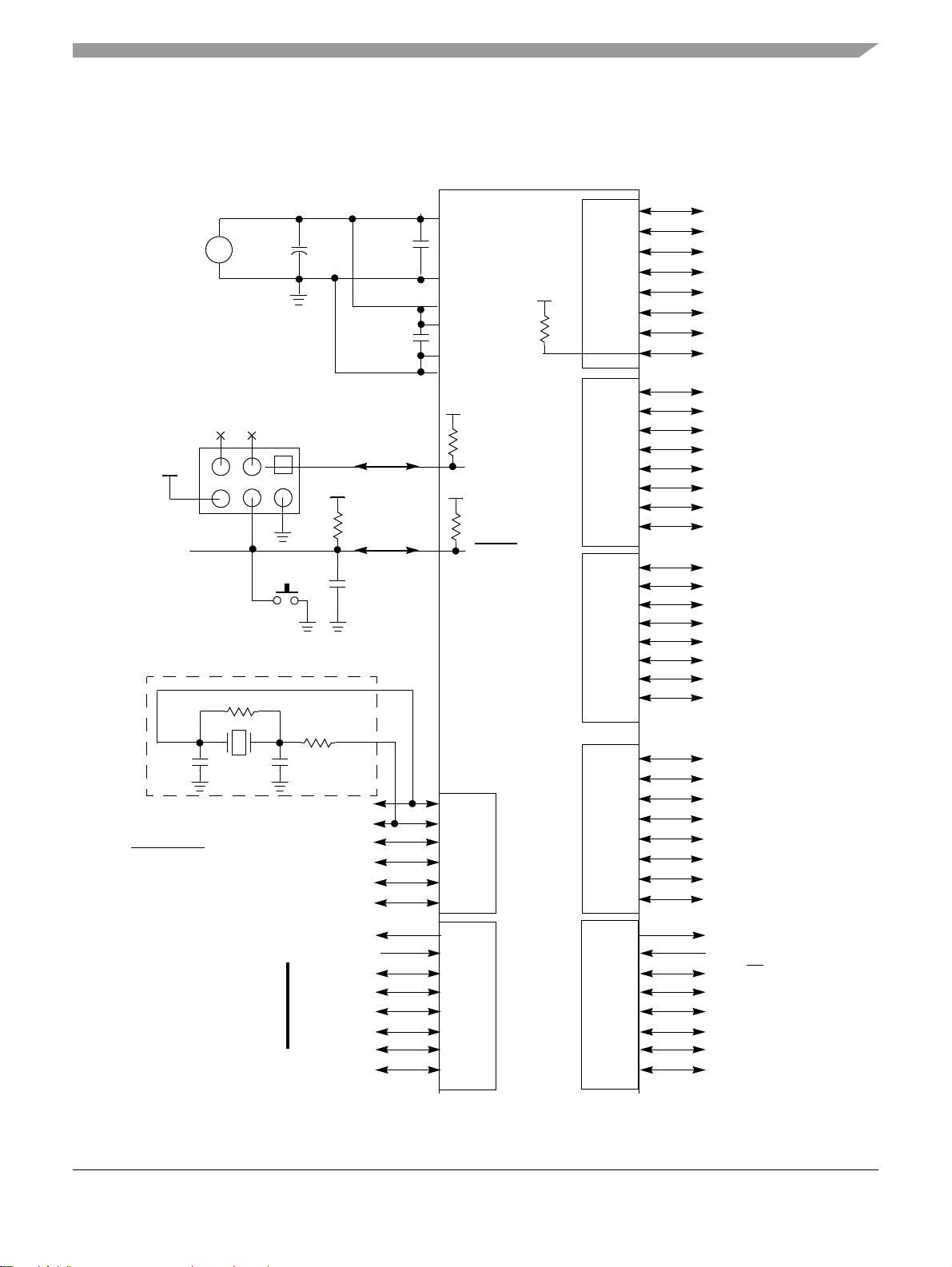

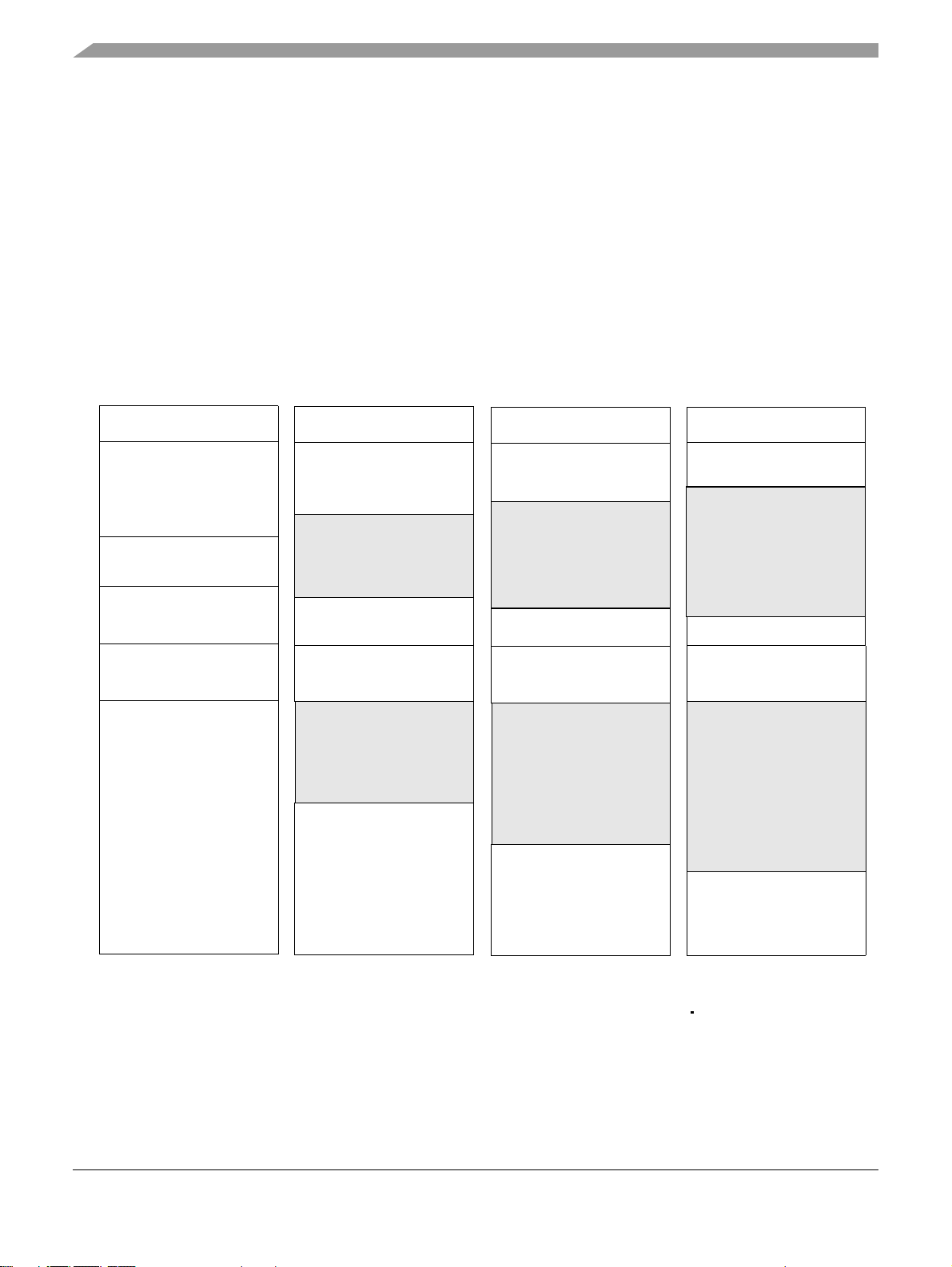

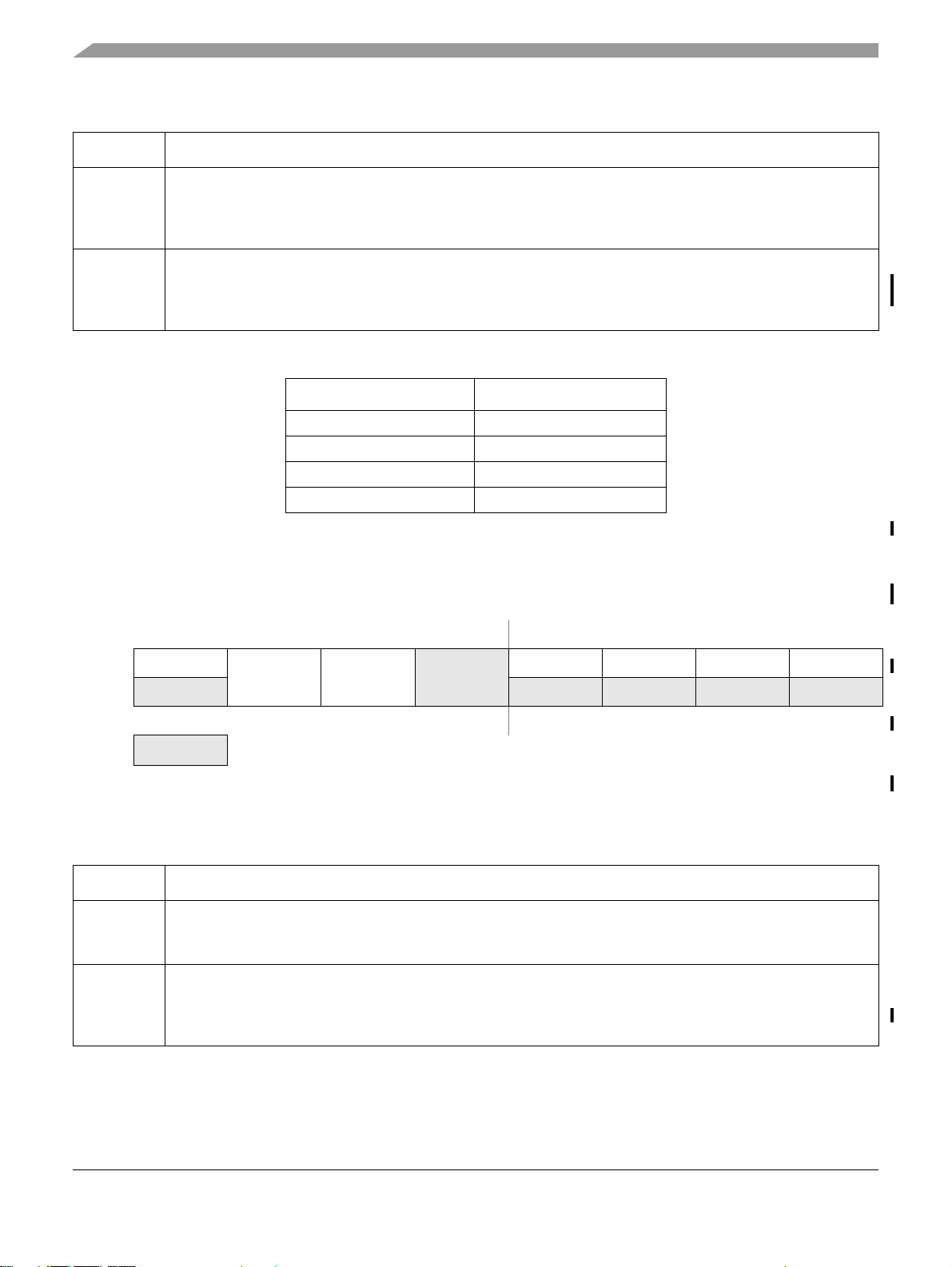

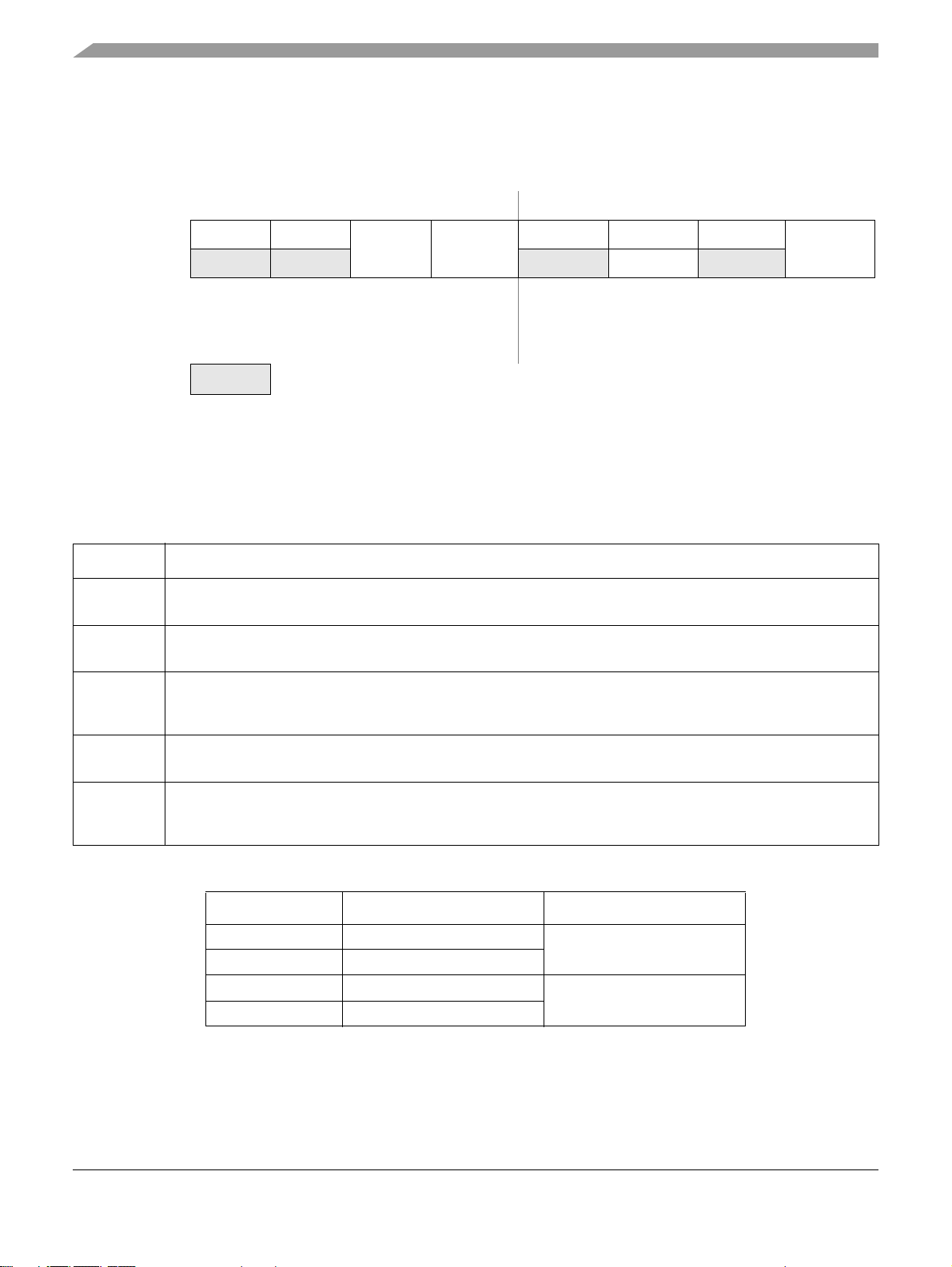

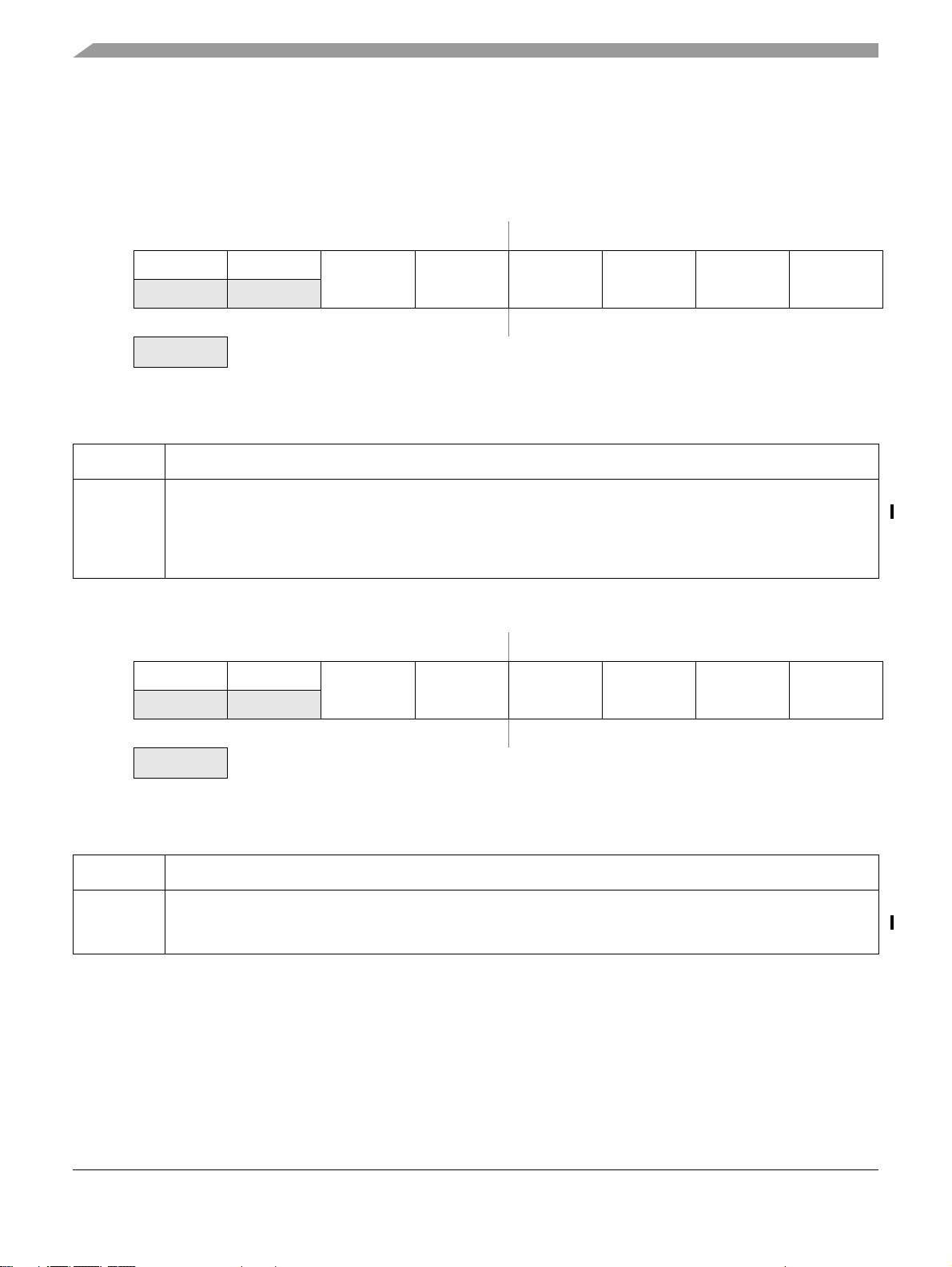

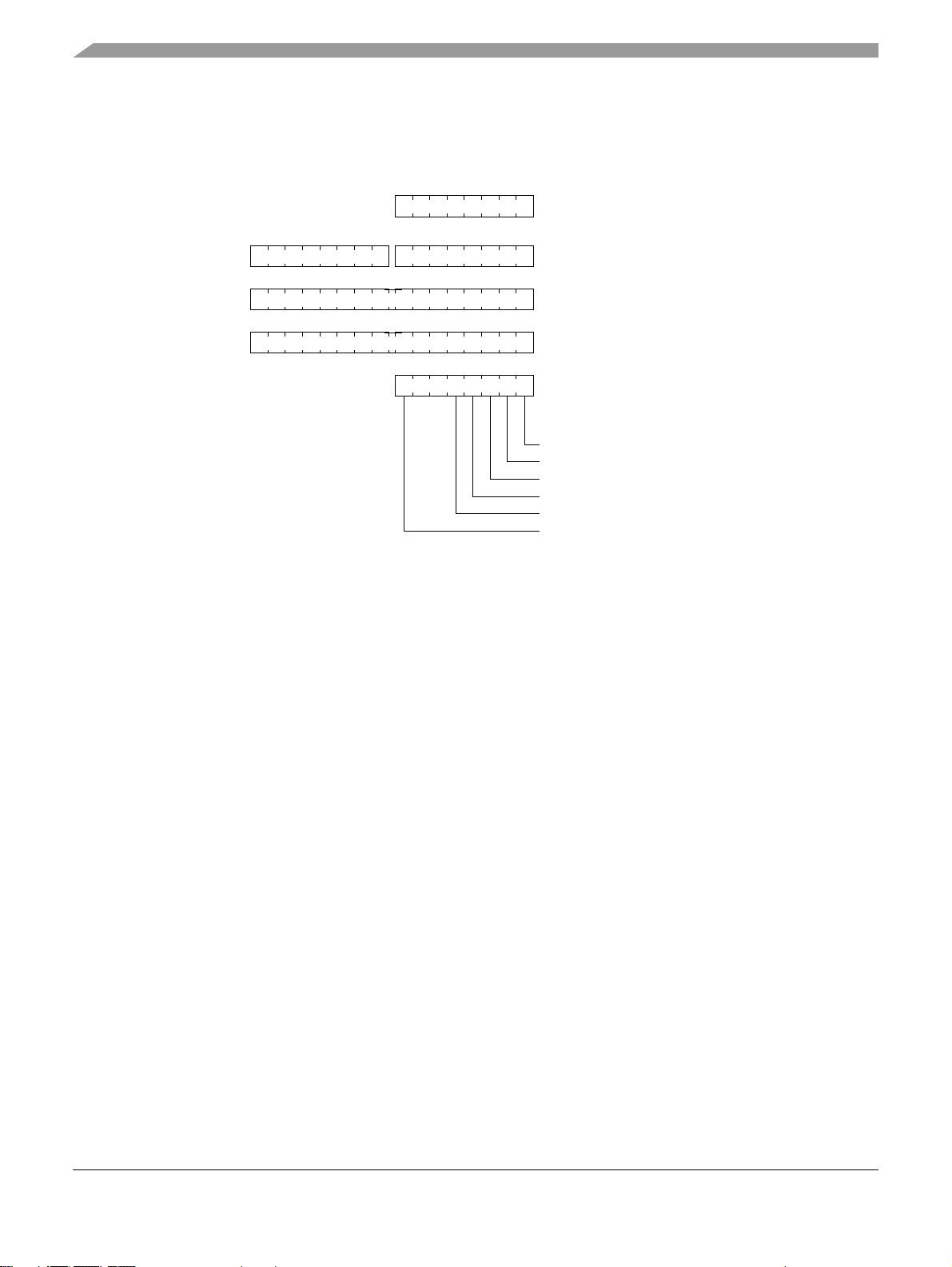

0.2 MCU 结构图

Figure 0-1 系列产品的系统级结构图。

MC9S08DZ60 系列 , 第 3 版

22 飞思卡尔半导体公司

Page 7

模拟比较器

(ACMP1)

ACMP1O

ACMP1ACMP1+

V

SS

V

DD

IIC 模块 (IIC)

串行外围设备

接口模块 (SPI)

用户闪存

用户 RAM

MC9S08DZ60 = 60K

HCS08 CORE

CPU

BDC

6 通定时器 /PWM

模块 (TPM1)

HCS08 系统控制

复位和中断

运行模式

电源管理

稳压器

COP

IRQ

LVD

OSCILLATOR (XOSC)

多功能

时钟管理器

RESET

V

REFL

V

REFH

数模

转换器 (ADC)

MC9S08DZ60 = 4K

24 通道,12 位

BKGD/MS

接口 (SCI1)

串行通信

SDA

SCL

MISO

SS

SPSCK

TxD1

RxD1

XTAL

EXTAL

8

(MCG)

2 通道定时器 /PWM

模块 (TPM2)

实时计数器 (RTC)

调试模块 (DBG)

IRQ

PTA3/PIA3/ADP3/ACMP1O

PTA4/PIA4/ADP4

PTA5/PIA5/ADP5

PTA2/PIA2/ADP2/ACMP1PTA1/PIA1/ADP1/ACMP1+

PTA0/PIA0/ADP0/MCLK

PORT A

PTA6/PIA6/ADP6

PTA7/PIA7/ADP7/IRQ

MOSI

PTB3/PIB3/ADP11

PTB4/PIB4/ADP12

PTB5/PIB5/ADP13

PTB2/PIB2/ADP10

PTB1/PIB1/ADP9

PTB0/PIB0/ADP8

PORT B

PTB6/PIB6/ADP14

PTB7/PIB7/ADP15

PTC3/ADP19

PTC4/ADP20

PTC5/ADP21

PTC2/ADP18

PTC1/ADP17

PTC0/ADP16

PORT C

PTC6/ADP22

PTC7/ADP23

PTD3/PID3/TPM1CH1

PTD4/PID4/TPM1CH2

PTD5/PID5/TPM1CH3

PTD2/PID2/TPM1CH0

PTD1/PID1/TPM2CH1

PTD0/PID0/TPM2CH0

PORT D

PTD6/PID6/TPM1CH4

PTD7/PID7/TPM1CH5

PTE3/SPSCK

PTE4/SCL/MOSI

PTE5/SDA/MISO

PTE2/SS

PTE1/RxD1

PTE0/TxD1

PORT E

PTE6/TxD2/TXCAN

PTE7/RxD2/RXCAN

PTF3/TPM2CLK/SDA

PTF4/ACMP2+

PTF5/ACMP2-

PTF2/TPM1CLK/SCL

PTF1/RxD2

PTF0/TxD2

PORT F

PTF6/ACMP2O

PTF7

PTG1/XTAL

PTG2

PTG3

PORT G

PTG4

PTG5

PTG0/EXTAL

V

SS

V

DD

V

SSA

V

DDA

BKP

INT

模拟比较器

(ACMP2)

ACMP2O

ACMP2-

ACMP2+

接口 (SCI2)

串行通信

TxD2

RxD2

(MSCAN)

控制器区域网络

TXCAN

RxCAN

用户 EEPROM

MC9S08DZ60 = 2K

ADP7-ADP0

ADP15-ADP8

ADP23-ADP16

6

TPM1CH5 -

TPM2CH1,

TPM2CH0

TPM2CLK

TPM1CLK

TPM1CH0

- 48 管脚和 32 管脚封装内管脚不连接

- 32 管脚封装内管脚连接

- 48 管脚和 32 管脚封装中,V

REFH/VREFL

和 V

DDA/VSSA

内部连接。

- V

DD

和 VSS 管脚是通过内部方式和 32 封装的 2 个管脚连接。

MC9S08DZ48 = 48K

MC9S08DZ32 = 32K

MC9S08DZ16 = 16K

飞思卡尔半导体公司 23

Figure 0-1. MC9S08DZ60 结构图

MC9S08DZ60 系列 , 第 3 版

Page 8

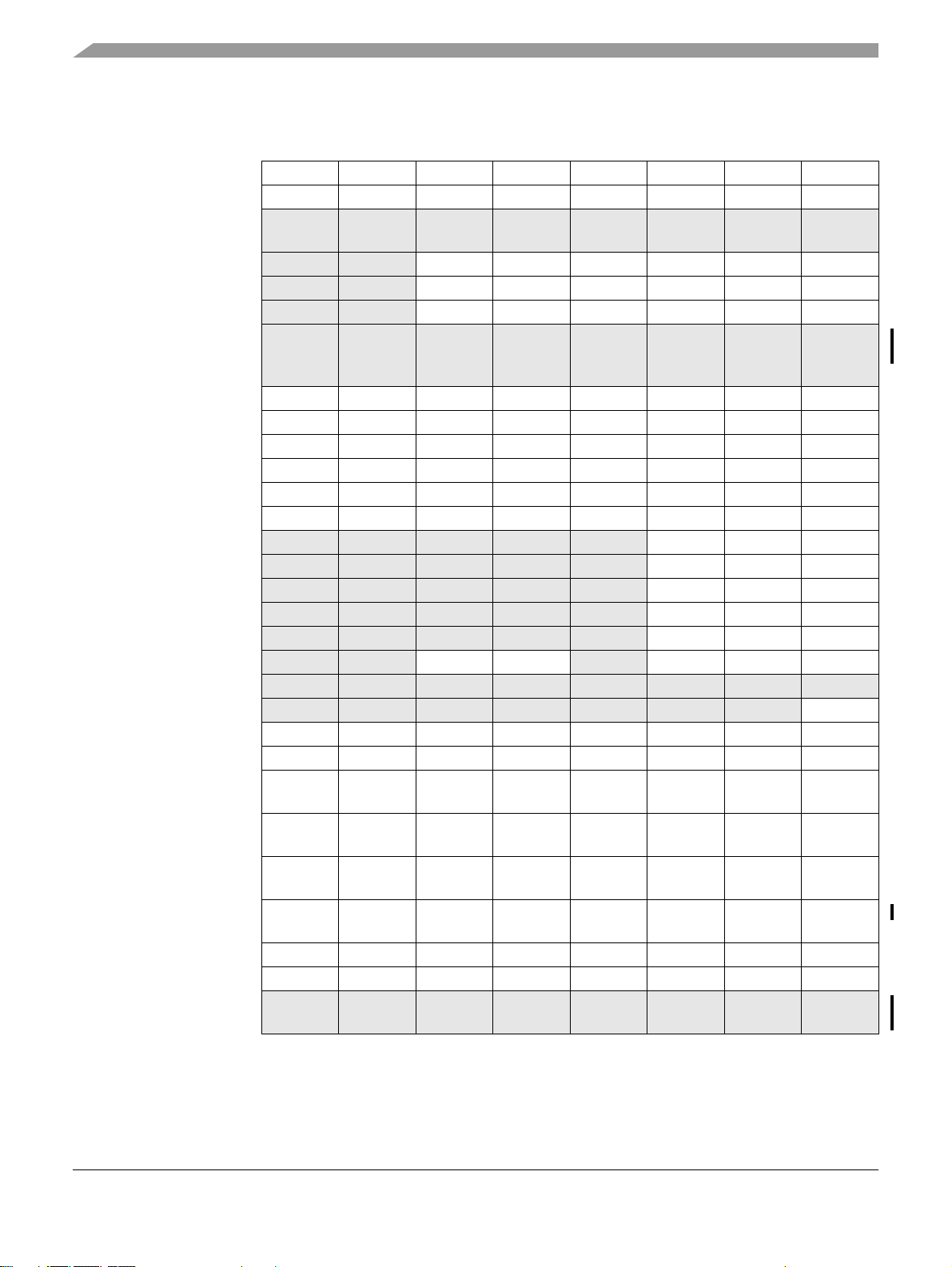

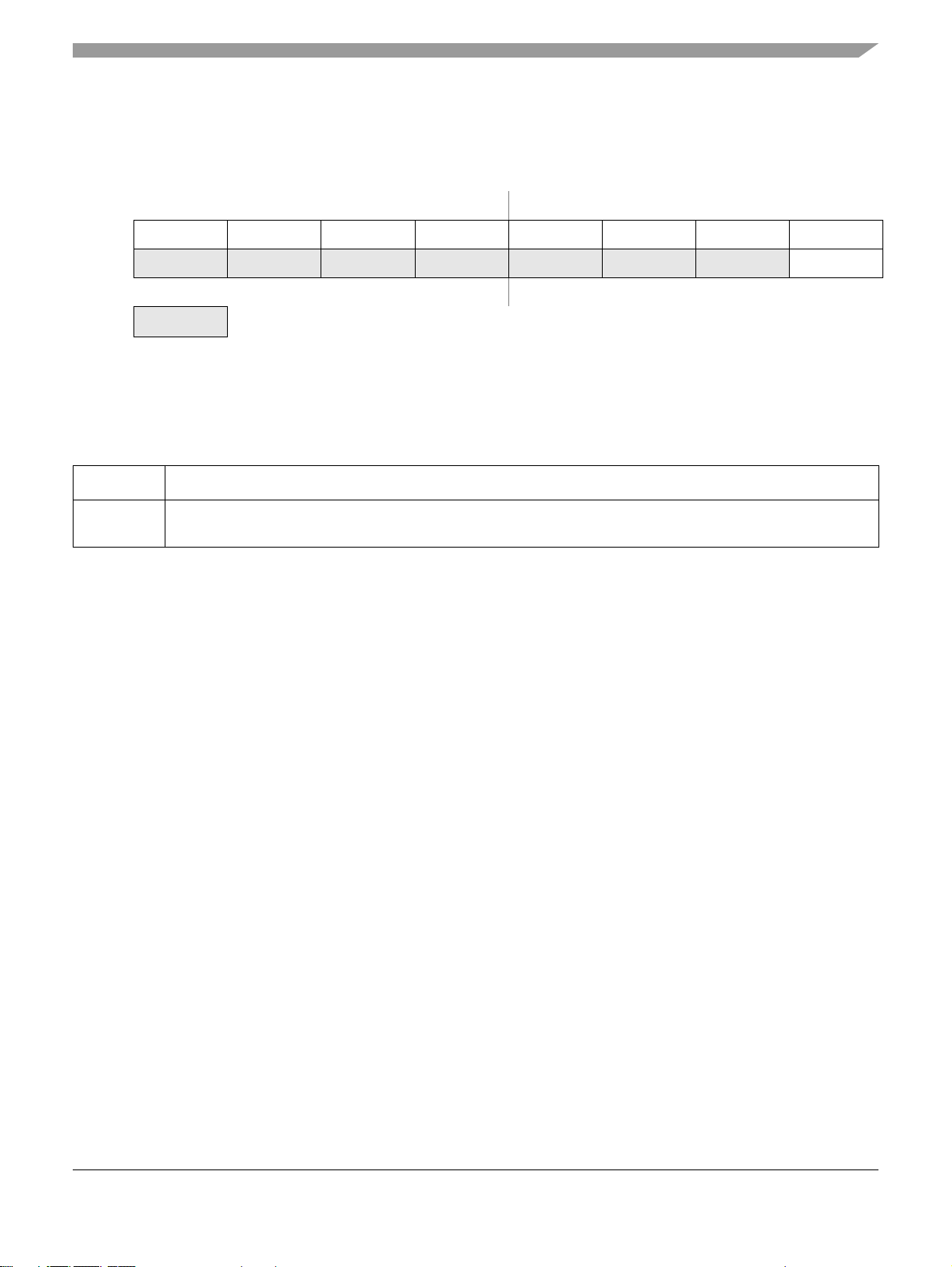

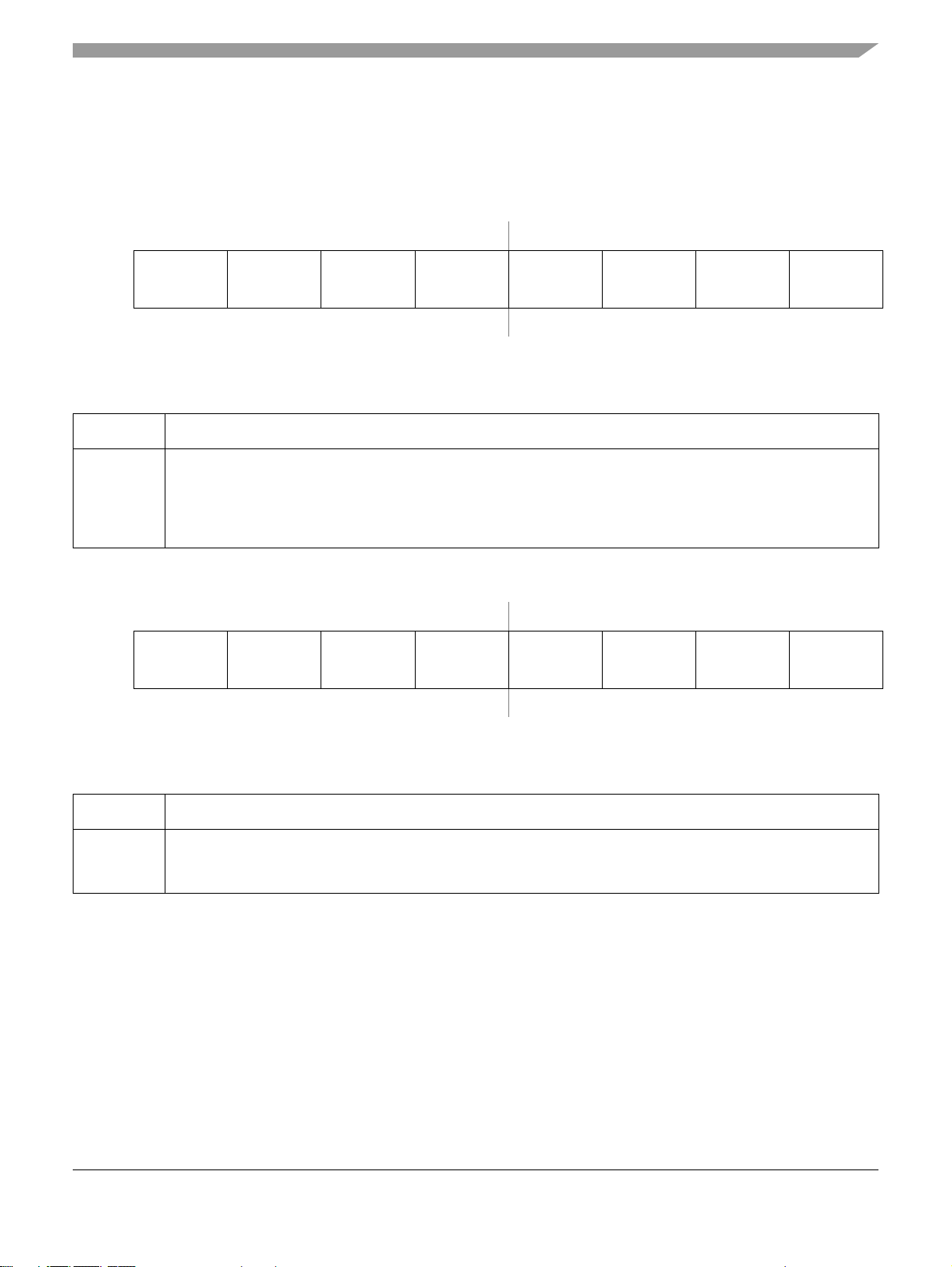

Tabl e 0-2 列出了片上模块的功能版本。

Table 0-2. 模块版本

模块 版本

中央处理器

多功能时钟生成器

模拟比较器

模数转换器

IIC 总线

飞思卡尔的 CANN

串行外围接口

串行通信接口

实时计数器

定时器脉宽调制器

调试模块

1

3M05C 和更早版本的掩码有 TPM 第 2 版。

(CPU) 3

(MCG) 1

(ACMP) 3

(ADC) 1

(IIC) 2

(MSCAN) 1

(SPI) 3

(SCI) 4

(RTC) 1

(TPM) 3

(DBG) 2

1

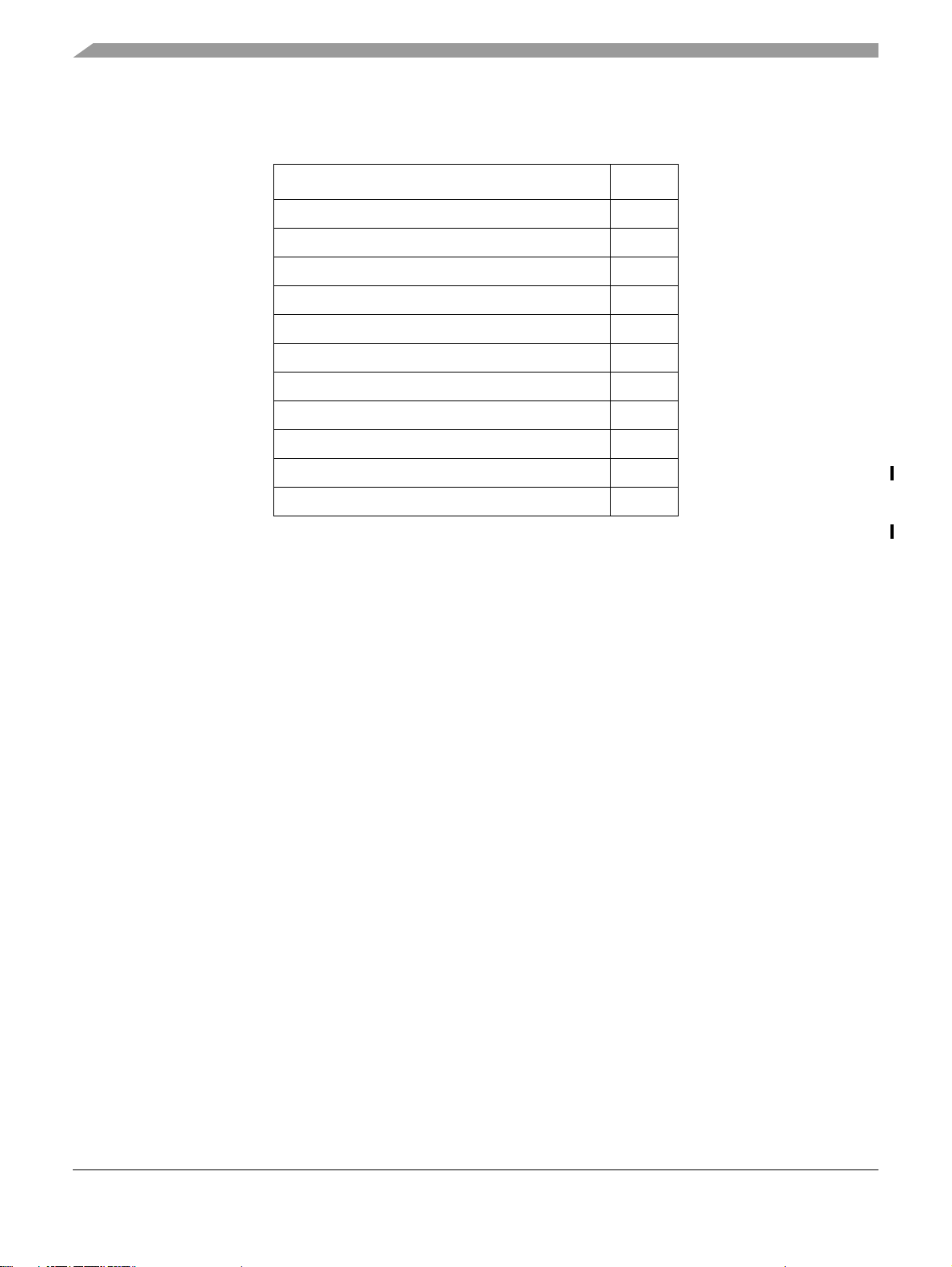

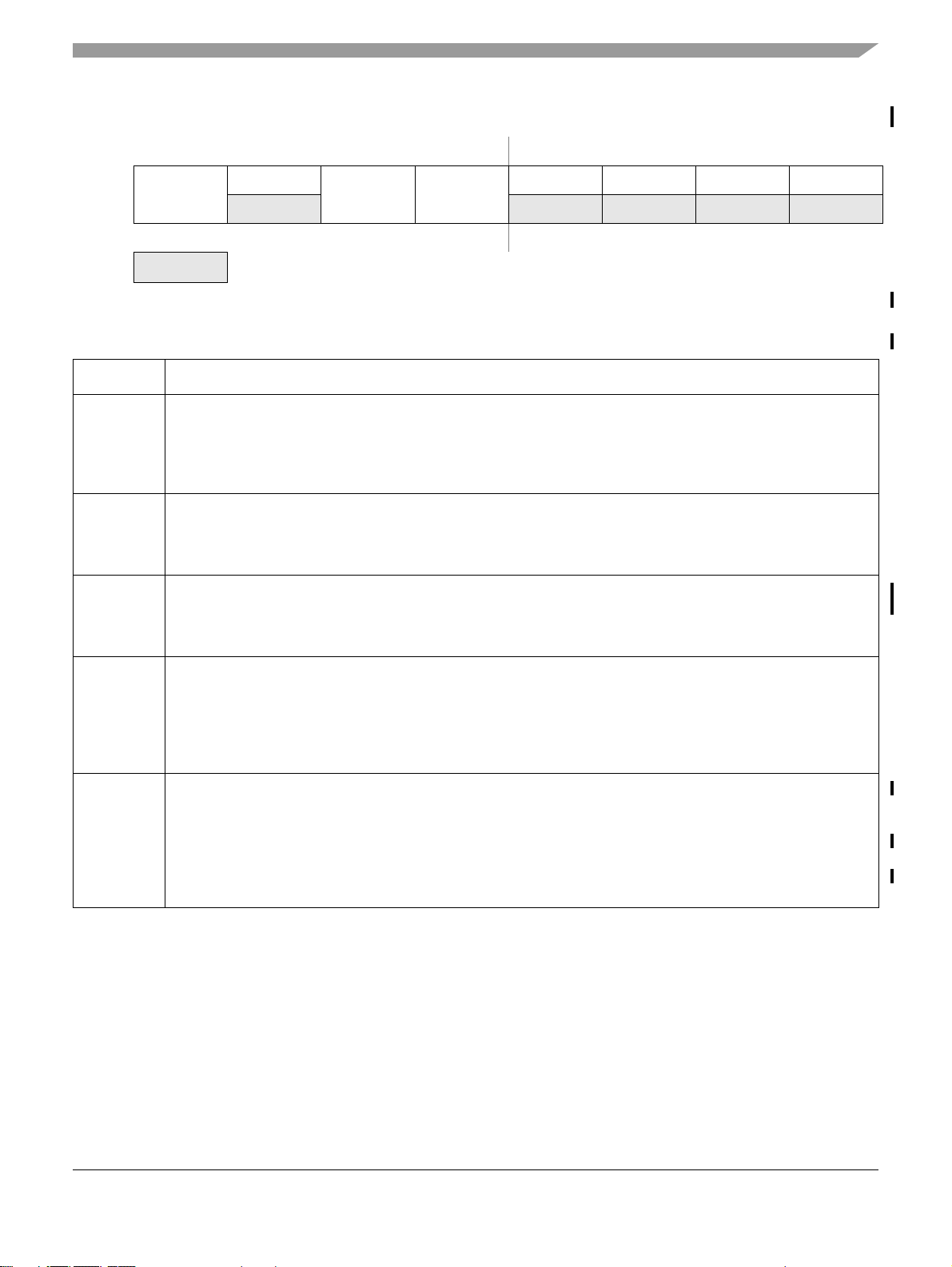

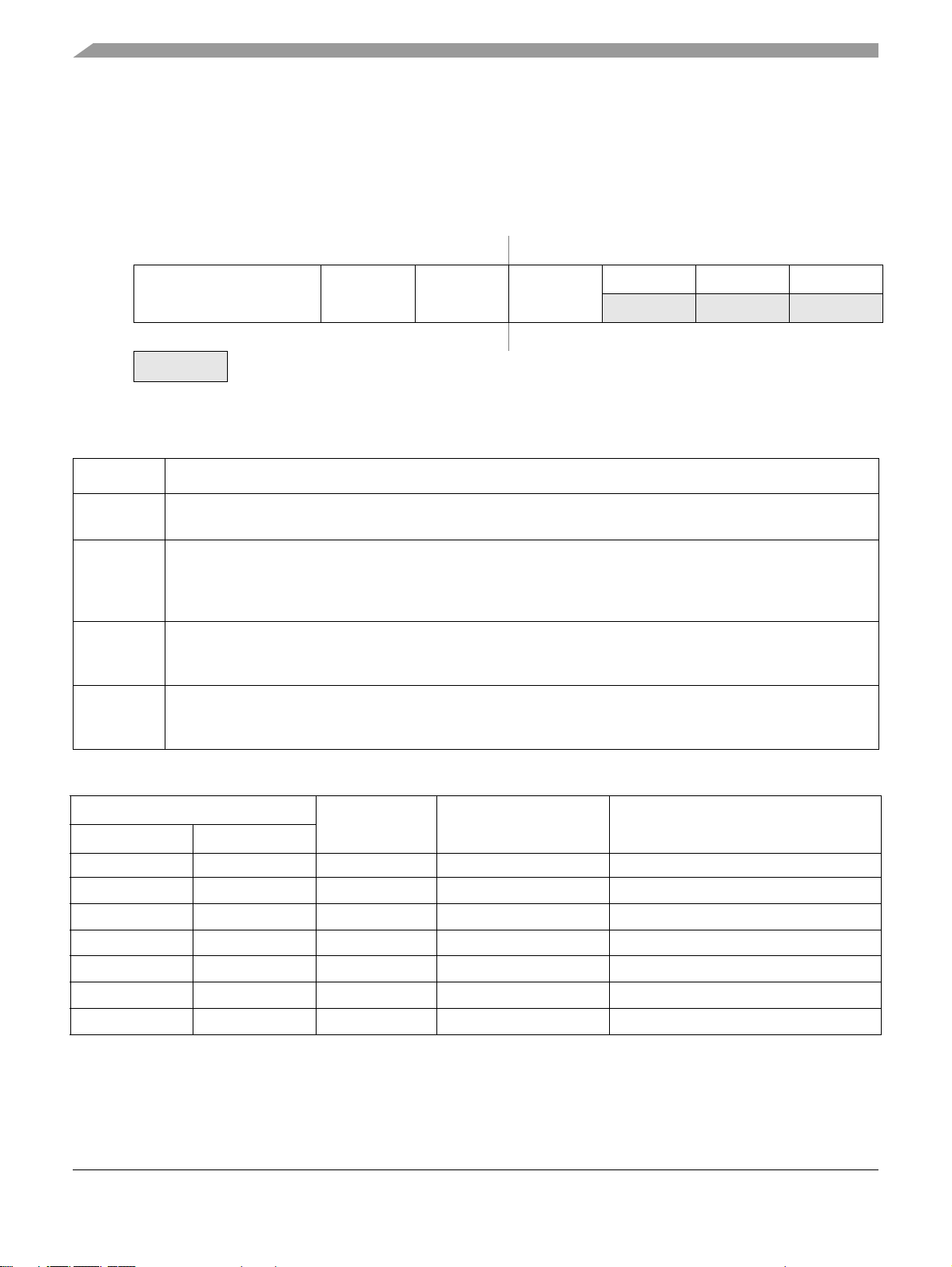

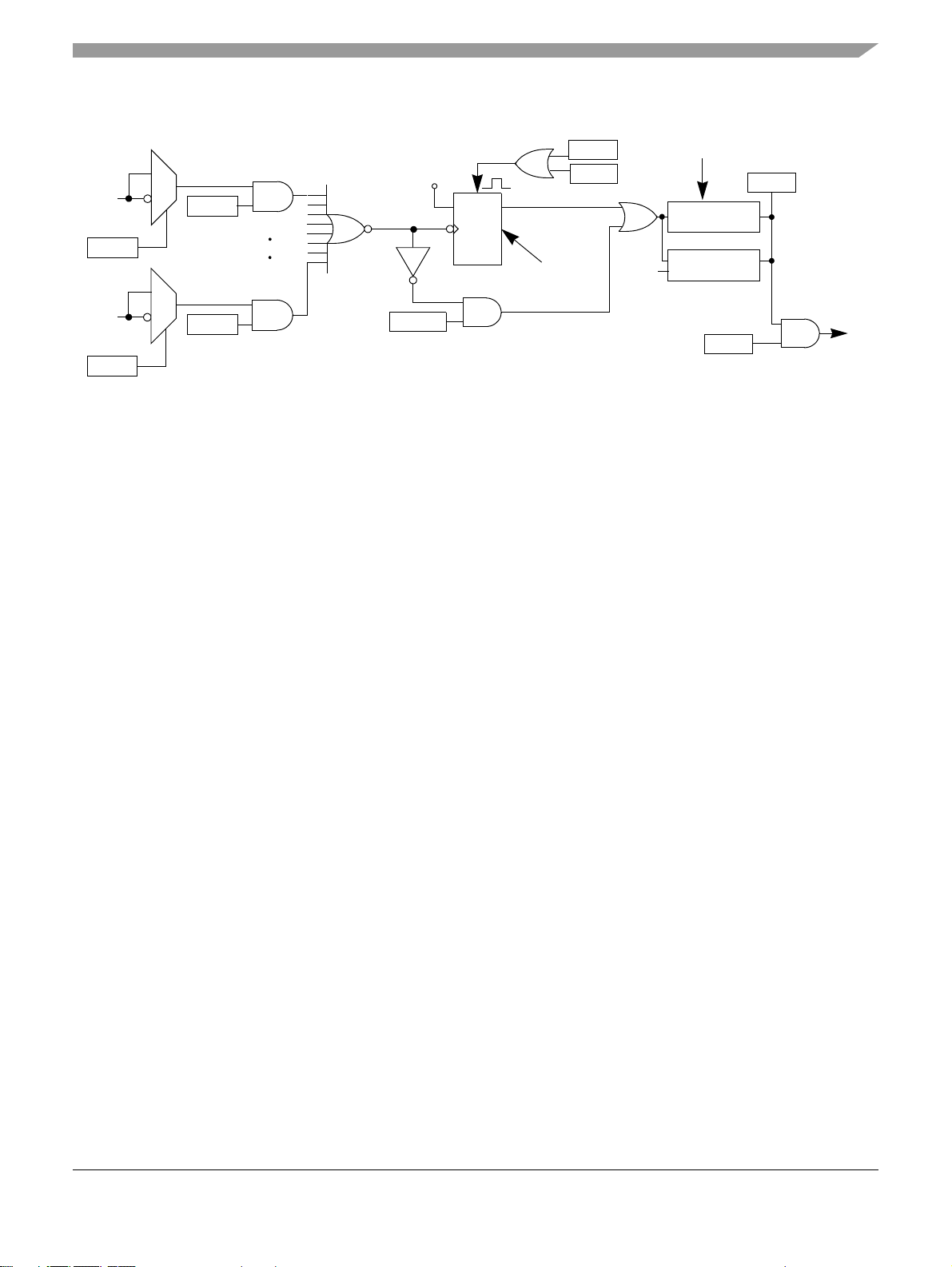

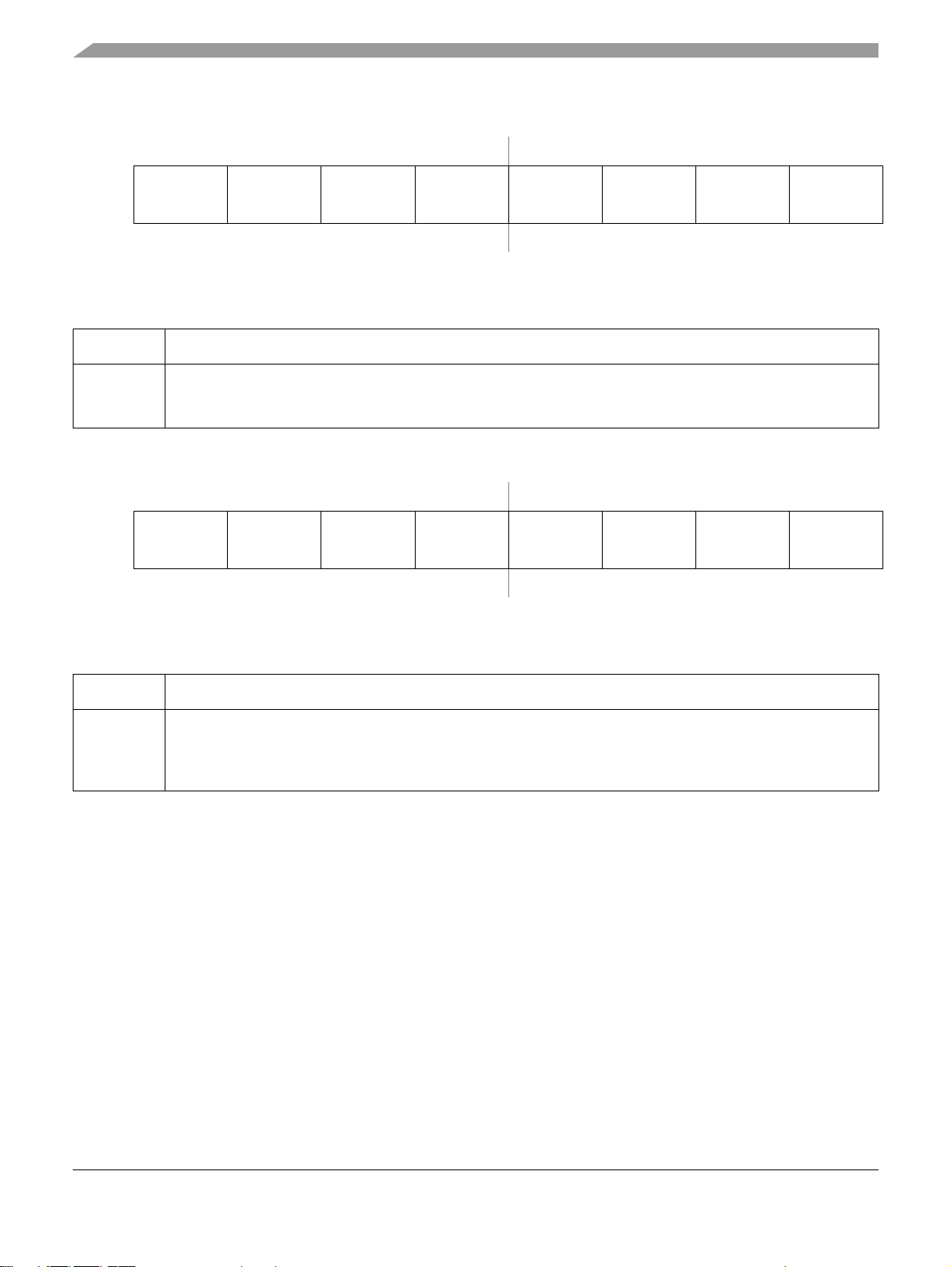

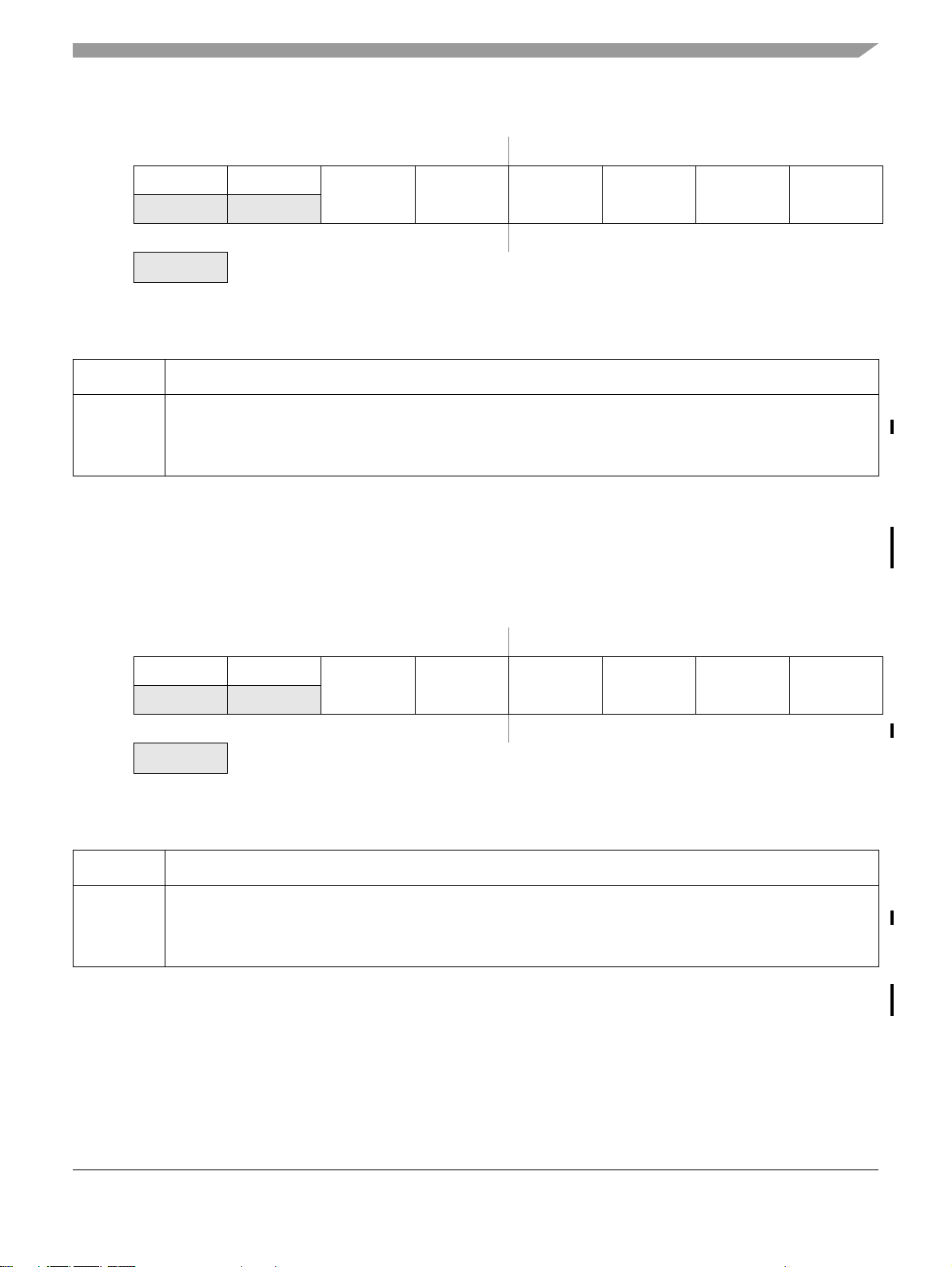

0.3 系统时钟分配

Figure 0-2 显示了一个简化的时钟连接结构图。MCU 中的某些模块具有可选择的时钟输入,如图

所示。到各模块的时钟输入显示用于驱动该模块的功能的时钟。

下面列出了本 MCU 中使用的时钟:

• BUSCLK — 总线频率始终为 MCGOUT 的一半。

•LPO — 独立的 1-kHz 时钟,可以选择作为 COP 和 RTC 模块的时钟源。

• MCGOUT — MCG 的主输出,为总线频率的两倍。

• MCGLCLK — 在 BUSCLK 被配置为以很低的频率运行的系统中,开发工具可以选择这一

时钟源来加快 BDC 通信。

• MCGERCLK — 外部参考时钟,可选择用作 RTC 时钟源。它还可以用作 ADC 和

MSCAN 的备用时钟。

• MCGIRCLK — 内部参考时钟,可选择用作 RTC 时钟源。

• MCGFFCLK — 固定频率时钟,可选择用作 TPM1 和 TPM2 的时钟源。

• TPM1CLK — TPM1 的外部输入时钟源。

• TPM2CLK — TPM2 的外部输入时钟源。

MC9S08DZ60 系列 , 第 3 版

24 飞思卡尔半导体公司

Page 9

Figure 0-2. MC9S08DZ60 系统时钟分配图

TPM1 TPM2 IIC SCI1 SCI2

BDC

CPU

ADC

MSCAN FLASH

MCG

MCGOUT

÷2

BUSCLK

MCGLCLK

MCGERCLK

COP

* 固定频率时钟 (FFCLK)在内部与总线时钟保

持同步,不能超过总线时钟频率的一半。

Flash 和 EEPROM 对编

程和擦除操作有频率要

求。详细信息请参见电气

规范附录。

ADC 有最低和最高频率

要求。详细信息请参见

ADC 一章和电气规范附

录。

XOSC

EXTAL XTAL

EEPROM

SPI

FFCLK*

MCGFFCLK

RTC

1 kHZ

LPO

TPM1CLK TPM2CLK

MCGIRCLK

÷2

第 2 章

管脚和连接

这一章描述连接到产品封装管脚的信号,内容包括管脚布局图、建议的系统连接和对信号的详细

讨论。

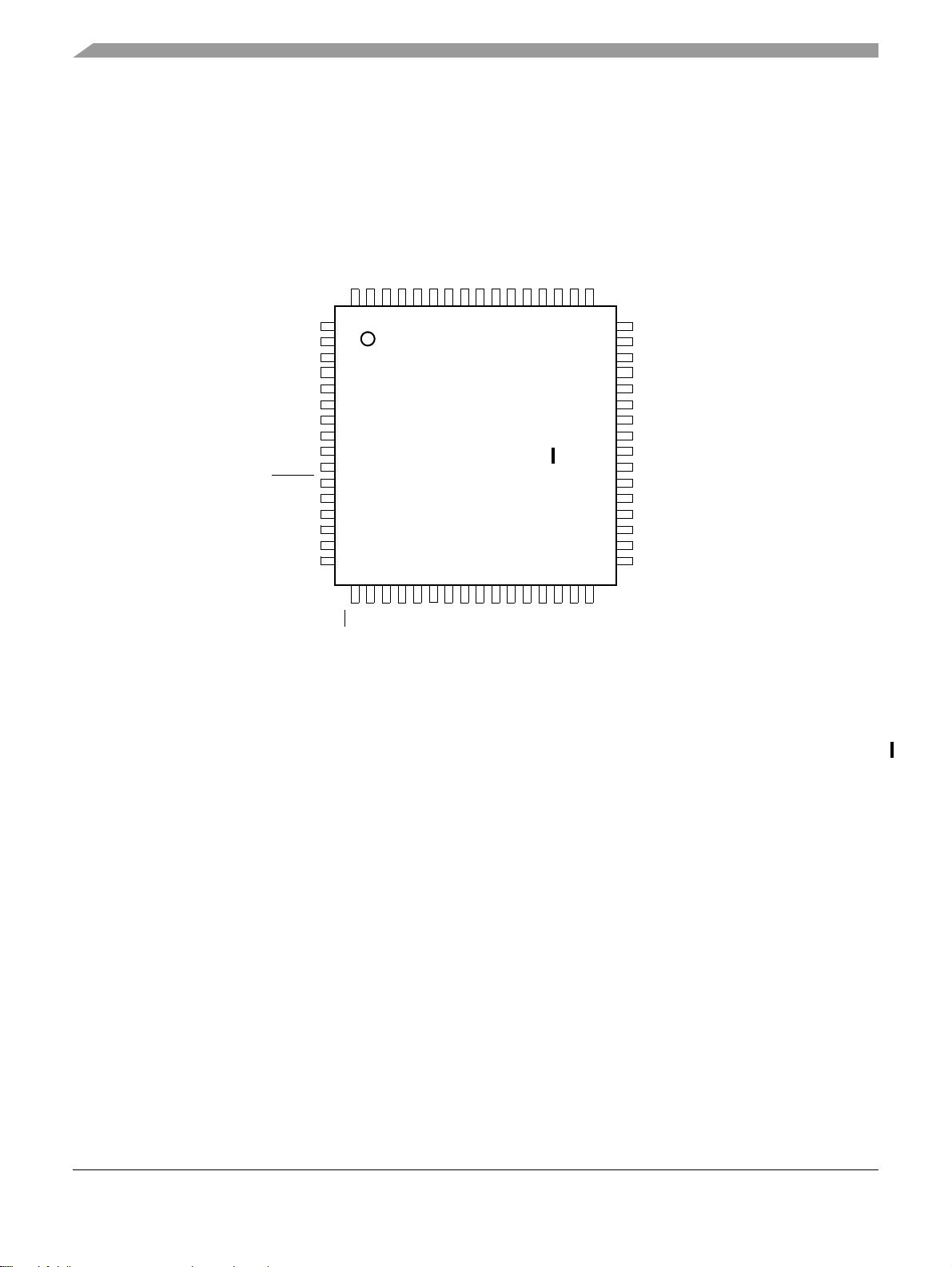

0.4 器件管脚分配

以下部分介绍了可用的 MC9S08DZ60 系列 MCU 封装中的管脚分配情况。

飞思卡尔半导体公司 25

MC9S08DZ60 系列 , 第 3 版

Page 10

1

2

3

4

5

6

7

8

9

10

11

12

13

14

64636261605958575655545352

51

17181920212223242526272829

30

4

8

4

7

4

6

4

5

4

4

4

3

4

2

4

64-Pin

LQFP

PTB1/PIB1/ADP9

PTB6/PIB6/ADP14

PTA6/PIA6/ADP6

PTE2/SS

PTC2/ADP18

PTC5/ADP21

PTA0/PIA0/ADP0/MCLK

PTA7/PIA7/ADP7/IRQ

PTC1/ADP17

PTC6/ADP22

PTB0/PIB0/ADP8

PTB7/PIB7/ADP15

PTC0/ADP16

PTC7/ADP23

BKGD/MS

V

DD

PTD7/PID7/TPM1CH5

V

SS

PTD6/PID6/TPM1CH4

PTG0/EXTAL

V

DDPTG1/XTAL

V

SSRESET

PTF7

PTF4/ACMP2+

PTD5/PID5/TPM1CH3

PTF5/ACMP2-

PTD4/PID4/TPM1CH2

PTF6/ACMP2O

PTD3/PID3/TPM1CH1

PTE0/TxD1

PTD2/PID2/TPM1CH0

PTE1/RxD1

PTB5/PIB5/ADP13

PTE3/SPSCK

PTA5/PIA5/ADP5

PTE4/SCL/MOSI

PTC4/ADP20

PTE5/SDA/MISO

PTB4/PIB4/ADP12

PTG2

PTA4/PIA4/ADP4

PTG3

V

DDA

PTF0/TxD2

V

REFH

PTF1/RxD2

V

REFL

PTF2/TPM1CLK/S

V

SSA

PTF3/TPM2CLK/S

PTA3/PIA3/ADP3/ACMP1O

PTG4

PTB3/PIB3/ADP11

PTG5

PTC3/ADP19

PTE6/TxD2/TXCAN

PTA2/PIA2/ADP2/ACMP1-

PTE7/RxD2/RXCAN

PTB2/PIB2/ADP10

PTD0/PID0/TPM2CH

PTA1/PIA1/ADP1/ACMP1+

PTD1/PID1/TPM2C

Figure 0-3. 64 管脚 LQFP

26 飞思卡尔半导体公司

MC9S08DZ60 系列 , 第 3 版

Page 11

PTB1/PIB1/ADP9

PTB6/PIB6/ADP14

PTA6/PIA6/ADP6

PTE2/SS

PTA0/PIA0/ADP0/MCLK

PTA7/PIA7/ADP7/IRQ

PTB0/PIB0/ADP8

PTB7/PIB7/ADP15

BKGD/MS

V

DD

PTD7/PID7/TPM1CH5

V

SS

PTD6/PID6/TPM1CH4

PTG0/EXTAL

V

DD

PTG1/XTAL

V

SS

RESET

PTF4/ACMP2+

PTD5/PID5/TPM1CH3

PTF5/ACMP2-

PTD4/PID4/TPM1CH2

PTD3/PID3/TPM1CH1

PTE0/TxD1

PTD2/PID2/TPM1CH0

PTE1/RxD1

PTB5/PIB5/ADP13

PTE3/SPSCK

PTA5/PIA5/ADP5

PTE4/SCL/M

PTE5/SDA/MI

PTB4/PIB4/ADP12

PTA4/PIA4/ADP4

V

DDA

/V

REFH

PTF0/TxD2

PTF1/RxD2

PTF2/TPM1CLK/S V

SSA

/V

REFL

PTF3/TPM2CLK/S

PTA3/PIA3/ADP3/ACMP1O

PTB3/PIB3/ADP11

PTE6/TxD2/TXCA

PTA2/PIA2/ADP2/ACMP1-

PTE7/RxD2/RXCA

PTB2/PIB2/ADP10

PTD0/PID0/TPM2C

PTA1/PIA1/ADP1/ACMP1+

PTD1/PID1/TPM2C

1

2

3

4

5

6

7

8

9

10

11

484746454443424140

39

1314151617181920212223

3

6

3

5

3

4

3

3

3

2

3

48-Pin LQFP

V

REFH

和 V

REFL

在内部分别连接到 V

DDA

和 V

SSA

。

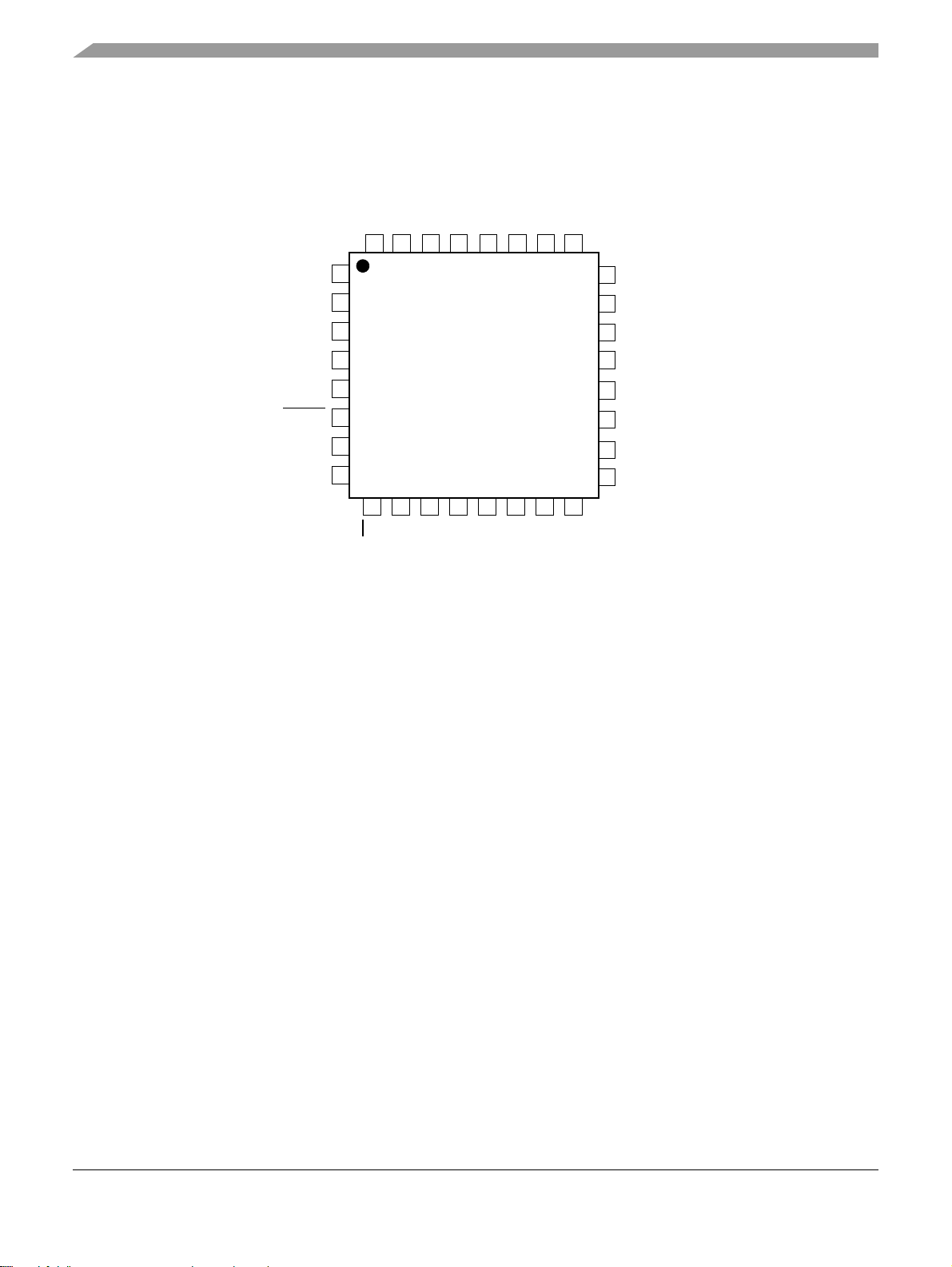

Figure 0-4. 48 管脚 LQFP

飞思卡尔半导体公司 27

MC9S08DZ60 系列 , 第 3 版

Page 12

RESET

1

2

3

4

5

6

7

8

V

SS

PTG0/EXTAL

PTD1/PID1/TPM2C

PTD0/PID0/TPM2C

PTE7/RxD2/RXCA

PTE6/TxD2/TXCA

PTE5/SDA/MI

PTE4/SCL/M

PTD3/PID3/TPM1C

PTD4/PID4/TPM1C

PTD5/PID5/TPM1C

BKGD/MS

PTA6/PIA6/ADP6

PTA1/ADP1/ACMP

PTB1/PIB1/ADP9

22

21

20

19

18

17

10

11

12 13 14

15

25

9

24

32

PTE0/TxD1

PTE1/RxD1

16

PTD2/PID2/TPM1C

PTA2/ADP2/ACMP

V

SSA

/V

REFL

26

V

DDA

/V

REFH

27

PTG1/XTAL

PTB0/PIB0/ADP8

23

PTA0/PIA0/ADP0/M

PTA5/PIA5/ADP5

31 30 29

PTA4/PIA4/ADP4

28

PTA7/PIA7/ADP7/I

V

DD

PTE2/SS

PTE3/SPSCK

32-Pin LQFP

PTA3/ADP3/ACMP

V

REFH

和 V

REFL

在内部分别连接到 V

DDA

和 V

SSA

。

Figure 0-5. 32 管脚 LQFP

MC9S08DZ60 系列 , 第 3 版

28 飞思卡尔半导体公司

Page 13

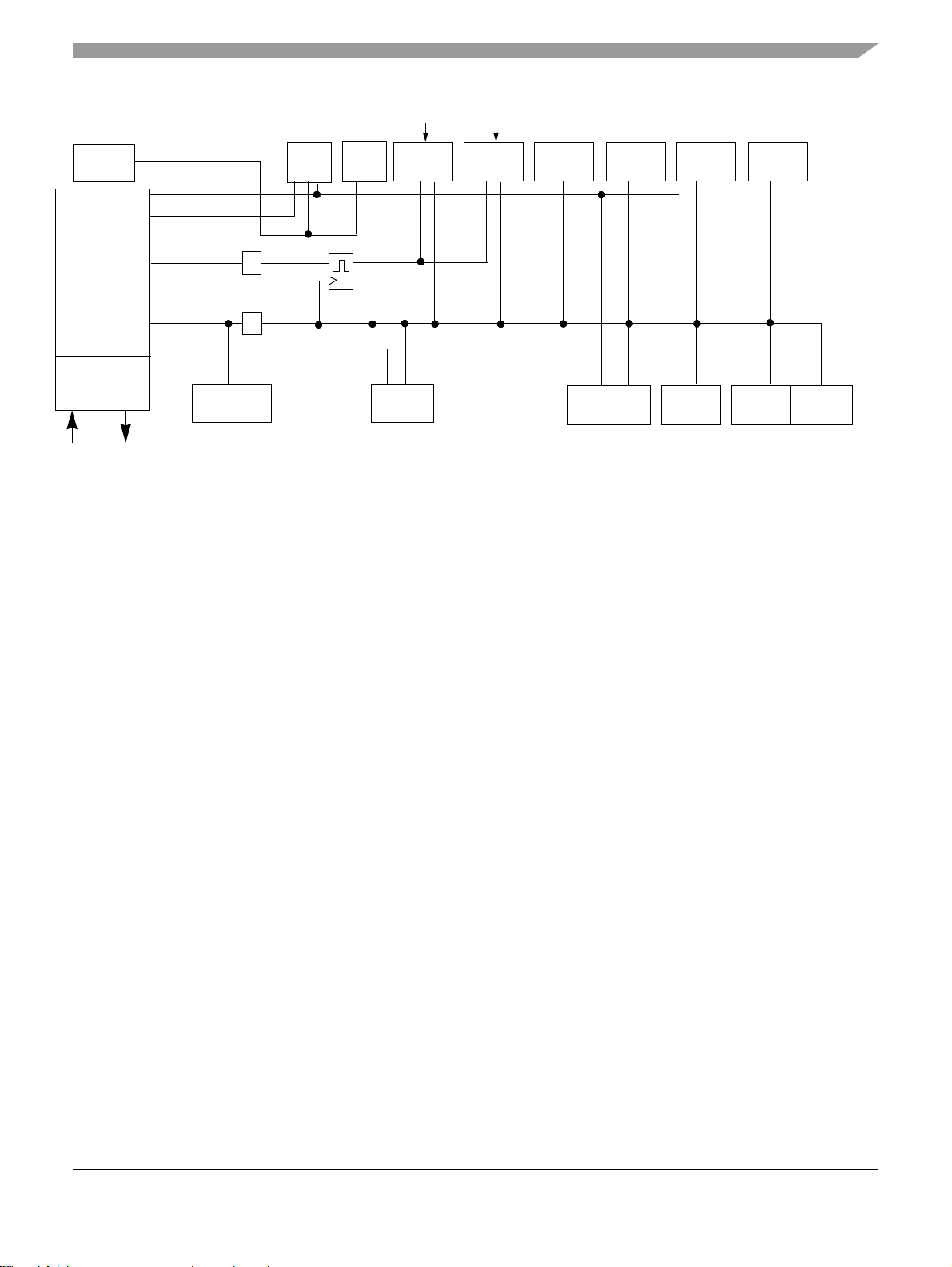

0.5 推荐的系统连接

NOTES:

1. 如果使用内部时钟选项 ,则

不需要外部晶体电路

。

2. RESRT管脚只能 用于复位到

用户模式 , 您不能使用

reset 管脚 进入背景调试模

式

。背景调式模式只能通

过以下方式进入 : 在 POR

期间 ,MS 保持低电平 , 并

同时把 SBDFR 中的 BDFR 设

为1

。

3. 建议在嘈杂的环境中在

RESET 管脚上使用 RC 过滤

器

。

4. 在32管脚和48管脚封装中:

V

DDA

和 V

SSA

通过两条线

路分别连接到 V

REFH

和

V

REFL

上。

PORT

A

C2

C1

X1

R

F

R

S

PTA0/PIA0/ADP0/MCLK

PTA1/PIA1/ADP1/ACMP1+

PTA2/PIA2/ADP2/ACMP1PTA3/PIA3/ADP3/ACMP1O

PTA4/PIA4/ADP4

PTA5/PIA5/ADP5

PTA6/PIA6/ADP6

PTA7/PIA7/ADP7/IRQ

PORT

B

PTB0/PIB0/ADP8

PTB1/PIB1/ADP9

PORT

C

PORT

D

PTD2/PID2/TPM1CH0

PTD3/PID3/TPM1CH1

PTD4/PID4/TPM1CH2

PTD5/PID5/TPM1CH3

PORT

E

PORT

G

PTG2

PTG3

PTG4

PTG5

PORT

F

IRQ

MC9S08DZ6

0

PTG0/EXTAL

PTG1/XTAL

PTF0/TxD2

PTF1/RxD2

PTF2/TPM1CLK/S

CL

PTF3/TPM2CLK/S

DA

PTF4/ACMP2+

PTF5/ACMP2–

PTE0/TxD1

PTE1/RxD1

PTE2/SS

PTE3/SPSCK

PTE4/SCL/MOSI

PTE5/SDA/MISO

PTE6/TxD2/TXCAN

PTE7/RxD2/RXCAN

PTD0/PID0/TPM2CH0

PTD1/PID1/TPM2CH1

PTB2/PIB2/ADP10

PTB3/PIB3/ADP11

PTB4/PIB4/ADP12

PTB5/PIB5/ADP13

PTB6/PIB6/ADP14

PTB7/PIB7/ADP15

PTC0/ADP16

PTC1/ADP17

PTC2/ADP18

PTC3/ADP19

PTC4/ADP20

PTC5/ADP21

PTC6/ADP22

PTC7/ADP23

PTD6/PID6/TPM1CH4

PTD7/PID7/TPM1CH5

C

BY

0.1 μF

V

REFH

V

REFL

V

SSA

V

DDA

V

DD

V

SS

C

BY

0.1 μF

C

BLK

10 μF

+

5 V

+

SYSTEM

POWER

BKGD/MS

RESET

OPTIONAL

MANUAL

RESET

V

DD

BACKGROUND HEADER

0.1 μF

V

DD

4.7 kΩ–10 k

Ω

Figure 0-6 显示了 MC9S08DZ60 系列应用系统通用的管脚连接。

飞思卡尔半导体公司 29

Figure 0-6. 基本系统连接 (显示的为 64 管脚封装)

MC9S08DZ60 系列 , 第 3 版

Page 14

0.5.1 电源

VDD 和 VSS 是 MCU 基本的电源管脚。该电源为所有 I/O 缓冲器电路和一个内部稳压器提供电

源。内部稳压器为 CPU 及 MCU 的其他内部电路提供经过稳压的低电压电源。

一般来说,应用系统在电源管脚上有两个独立的电容器。在这种情况下,我们应安装一个大容量

电解电容器 (如 10uF 钽电容器)来为整个系统提供大容量电荷存储,同时应在离 MCU 电源管

脚尽可能近的地方安装一个 0.1uF 陶瓷旁路电容器来抑制高频噪音。MC9S08DZ60 系列有两个

VDD管脚 (32 管脚封装除外)。每个管脚必须有一个旁路电容器以实现最有效的噪音抑制。

V

DDA

和 V

是 MCU 的模拟电源管脚。该电源为 ADC 模块提供电源。我们应在离 MCU 电源

SSA

管脚尽可能近的地方安装一个 0.1uF 陶瓷旁路电容器来抑制高频噪音。

0.5.2 振荡器

复位完成后, MCU 立即开始使用由多功能时钟生成器 (MCG)模块提供的内部生成的时钟。

若欲了解有关 MCG 的更详尽信息,请参见 Chapter 9, “Multi-Purpose Clock Generator

(S08MCGV1).”

该 MCU 中的振荡器 (XOSC)是一个皮尔斯 (Pierce)振荡器,可以支持晶体和陶瓷谐振器。

除了晶体或陶瓷谐振器外,我们还可以将一个外部振荡器连接到 EXTAL 输入管脚上。

请参见 Figure 0-6 来了解下面讨论的内容。 RS (如果使用了的话)和 RF 应该是低感电阻器,

如碳膜电阻器。线绕和一些金属薄膜电阻器的感应系数太高。 C1 和 C2 一般应该是专为高频应

用设计的高质量陶瓷电容器。

RF用来提供偏置路径为在晶体启动过程中将 EXTAL 输入保持在线性范围内。它的值并不是在

所有情况下都非常关键。一般的系统采用的值在 1M 到 10M 之间。更高的值对湿度太敏感,而

更低的值会减少增益并 (在一些极端情况下)使启动无法正常进行。

C1 和 C2 一般在 5pF 到 25pF 的范围内,选择的原则是匹配特定晶体或谐振器的要求。请注

意,在选择 C1 和 C2 时一定要考虑印刷电路板 (PCB)的电容和 MCU 管脚的电容。晶体生产

商一般都规定了一个负载电容——C1 和 C2 (二者的尺寸通常是相同的)的系列组合。按照一

次近似原则,我们应使用 10pF 作为每个振荡器管脚 (EXTAL 和 XTAL)的管脚和 PCB 总电容

的估计值。

0.5.3 RESET (复位)

RESET 是一个专用管脚,带有内置的上拉器件。它有输入电压迟滞、大电流输出驱动器但没有

输出斜率控制。内部加电复位和低压复位电路在一般情况使我们不必使用外部复位电路。该管脚

通常连接到标准的 6 脚背景调试接头上,以保证开发系统可以直接复位 MCU 系统。如果需要,

我们可以增加一个到地线的简单开关 (拉低复位管脚以强制进行复位)来实现手动外部复位。

在任何情况下启动复位时 (不管是从外部信号上还是从内部系统中), RESET 管脚都会下拉约

34 个总线周期。复位电路会解析复位原因并通过在系统复位状态寄存器 (SRS)中设置一个相

应的位来记录这一原因。

MC9S08DZ60 系列 , 第 3 版

30 飞思卡尔半导体公司

Page 15

0.5.4 背景调试和模式选择

在进行复位的过程中, BKGD/MS 管脚作为模式选择功能管脚。在复位信号上升沿后,该管脚立

即作为背景调试管脚,用于背景调试通信。当作为背景调试或模式选择功能管脚时,该管脚包括

一个内部上拉器件、输入电压滞后、标准的输出驱动器而没有输出斜率控制功能。

如果没有任何设备连接到该管脚上, MCU 将在复位的上升沿进入正常操作模式。如果有一个调

试系统连接到 6 脚标准背景调试头上,它将在复位的上升沿将 BKGD 保持在低位,从而强迫

MCU 进入活动背景调试模式。

BKGD/MS 管脚主要用于背景调试控制器 (BDC)通信。这一通信过程中使用一种定制的协议,

该协议在每个比特时间周期内使用目标 MCU 的 BDC 时钟的 16 个时钟周期。目标 MCU 的

BDC 时钟可以和总线时钟速率一样快,因此在任何情况下都不应将大电容器件连接到

BKGD/MS 管脚 (这样会干扰背景调试串行通信)。

虽然 BKGD/MS 管脚是一种准开漏管脚,但背景调试通信协议可以提供瞬间、主动驱动的高速

脉冲来确保快速上升沿。电缆上的小电容和内部上拉器件参数都不会影响 BKGD/MS 管脚上的

上升和下降沿时间时。

0.5.5 ADC 参考管脚 (V

V

REFH

和 V

管脚分别是 ADC 模块的电压参考高端和电压参考低端的输入管脚。

REFL

REFH

, V

REFL

)

0.5.6 通用 I/O 和外围设备端口

MC9S08DZ60 系列 MCU 最多可支持 53 个通用 I/O 管脚和 1 个专用输入管脚。这些管脚是和片

上外围设备 (定时器、串行 I/O、 ADC、 MSCAN 等)共享的。

当一个端口管脚被配置为通用输出或某外围设备使用该端口管脚作为输出时,软件可以选择两个

驱动强度之一并启用或禁用斜率控制。当一个端口管脚被配置为通用输入或某外围设备使用该端

口管脚作为输入时,软件可以选择一个上拉器件。复位完成后,所有这些管脚被立即配置为高阻

抗通用输入 (内部上拉器件被禁用)。

当一个片上外围系统控制管脚时,数据方向控制位仍决定从端口数据寄存器中读取的内容,即使

该外围模块通过控制该管脚的输出缓冲器的启用来控制管脚方向时也是如此。若欲了解有关如何

控制这些管脚作为通用 I/O 管脚方面的更详尽信息,请参见 Chapter 1, “Parallel Input/Output

Control.”

注意

为了避免浮空输入管脚消耗额外的电流,应用程序中的复位初始化程

序应该启用片内上拉器件或将未使用或未绑定的管脚的方向修改为输

出以确保他们不会浮空。

MC9S08DZ60 系列 , 第 3 版

飞思卡尔半导体公司 31

Page 16

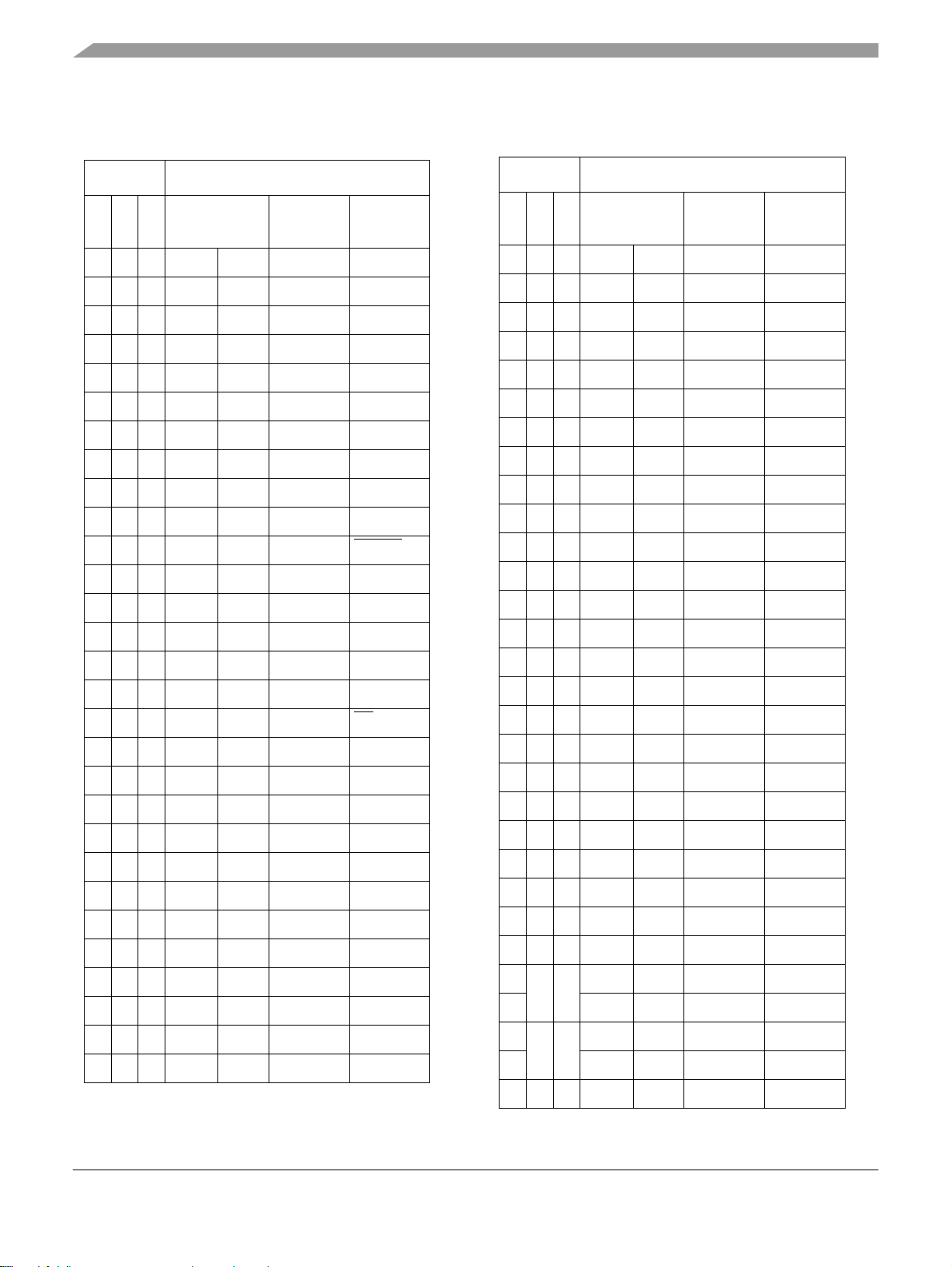

Table 2-1.

管脚编号 <-- 最低 优先级 --> 最高

64 48 32

端口管脚 / 中

断

Alt 1 Alt 2

11—PTB6PIB6ADP14

2——PTC5 ADP21

3 2 1 PTA7 PIA7 ADP7 IRQ

4——PTC6 ADP22

53—PTB7PIB7ADP15

6——PTC7 ADP23

742 V

DD

853 V

SS

9 6 4 PTG0 EXTAL

10 7 5 PTG1 XTAL

11 8 6 RESET

12 9 — PTF4 ACMP2+

13 10 — PTF5 ACMP2-

14 — — PTF6 ACMP2O

15 11 7 PTE0 TxD1

16 12 8 PTE1 RxD1

17 13 9 PTE2 SS

18 14 10 PTE3 SPSCK

19 15 11 PTE4 SCL

3

MOSI

20 16 12 PTE5 SDA

3

MISO

21 — — PTG2

22 — — PTG3

23 17 — PTF0 TxD2

4

24 18 — PTF1 RxD2

4

25 19 — PTF2 TPM1CLK SCL

3

26 20 — PTF3 TPM2CLK SDA

3

27 — — PTG4

28 — — PTG5

29 21 13 PTE6 TxD2

4

TXCAN

30 22 14 PTE7 RxD2

4

RxCAN

31 23 15 PTD0 PID0 TPM2CH0

32 24 16 PTD1 PID1 TPM2CH1

33 25 17 PTD2 PID2 TPM1CH0

34 26 18 PTD3 PID3 TPM1CH1

35 27 19 PTD4 PID4 TPM1CH2

36 28 20 PTD5 PID5 TPM1CH3

37 — — PTF7

38 29 — V

SS

39 30 — V

DD

40 31 — PTD6 PID6 TPM1CH4

41 32 — PTD7 PID7 TPM1CH5

42 33 21 BKGD MS

43 — — PTC0 ADP16

44 34 22 PTB0 PIB0 ADP8

45 — — PTC1 ADP17

46 35 23 PTA0 PIA0 ADP0 MCLK

47 — — PTC2 ADP18

48 36 24 PTB1 PIB1 ADP9

49 37 25 PTA1 PIA1 ADP1

1

ACMP1+

1

50 38 — PTB2 PIB2 ADP10

51 39 26 PTA2 PIA2 ADP2 ACMP1-

1

52 — — PTC3 ADP19

53 40 — PTB3 PIB3 ADP11

54 41 27 PTA3 PIA3 ADP3 ACMP1O

55

42 28

V

SSA

56 V

REFL

57

43 29

V

REFH

58 V

DDA

59 44 30 PTA4 PIA4 ADP4

Table 2-1.

管脚编号 <-- 最低 优先级 --> 最高

64 48 32

端口管脚 / 中

断

Alt 1 Alt 2

Table 0-3. 管脚可用性 (按封装管脚数)

32 飞思卡尔半导体公司

MC9S08DZ60 系列 , 第 3 版

Page 17

1. 如果这两个模拟模块都被启用,他们都将可以访问该管脚。

2. 管脚不包含到 V

V。连接到该管脚上的内部门被拉到 V

3. IIC 模块管脚可以通过 SOPT1 寄存器中的 IICPS 位进行重定位。缺省复位位置在 PTF2 和 PTF3 上。

4. SCI2 模块管脚可以通过 SOPT1 寄存器中的 SCI2PS 位进行重定位。缺省复位位置在 PTF0 和 PTF1 上。

的嵌位二极管,因此不应用在高于 VDD。 内部上拉器件被启用时在该管脚上测得的电压可能会低达 V

DD

DD

上。

DD

– 0.7

第 3 章

操作模式

0.6 简介

本章介绍 MC9S08DZ60 系列产品的操作模式,同时描述了如何进入每种模式、从每种模式中退

出及每种模式下可提供的功能。

0.7 特性

• 用于代码开发的活动后台模式

• 等待模式 — CPU 关闭以省电;系统时钟正常运行,内部稳压器正常工作

• 停止模式 — 系统时钟被关闭,内部稳压器处于待机状态

— Stop3 — 所有内部电路都接通电源以实现快速恢复

— Stop2 — 内部电路的部分电源被关闭; RAM 内容被保留

0.8 运行模式

这是 MC9S08DZ60 系列产品的正常操作模式。 BKGD/MS 管脚位于复位的上升边最高位置时选

择该模式。在这种模式下, CPU 从内部存储器中执行代码。代码执行在复位完成后从 0xFFFE

– 0xFFFF 上从内存中获取的地址上开始。

0.9 主动背景模式

主动背景模式功能通过 HCS08 内核中的背景调试控制器 (BDC)进行管理。 BDC 与片上调试

模块 (DBG)一同提供方法来在软件开发过程中分析 MCU 的运行情况。

主动背景模式可以通过以下 5 种方式中的任何一种进入:

• 当复位的上升边沿时, BKGD/MS 脚置于低电平;

• 通过 BKGD/MS 脚收到 BACKGROUND 命令时;

• 执行 BGND 指令时;

• 遇到 BDC 断点时;

• 遇到 DBG 断点时。

进入主动背景模式后, CPU 保持在挂起状态,等待串行后台命令而不是执行来自用户应用程序

的指令。

MC9S08DZ60 系列 , 第 3 版

飞思卡尔半导体公司 33

Page 18

后台命令有两种类型:

• 非中断型命令,被定义为可在用户程序运行时发出的命令。 非中断型命令可在 MCU 处于

运行模式时通过 BKGD/MS 管脚发出;非中断型命令也可以在 MCU 处于主动背景模式时

执行。非中断型命令包括:

— 内存访问命令

— 带状态内存访问命令

— BDC 寄存器访问命令

— 后台命令

• 主动背景命令只能在 MCU 处于主动背景模式时执行。主动背景命令包括执行以下操作的

命令:

— 读或写 CPU 寄存器

— 在特定时间跟踪一个用户程序指令

— 退出主动背景模式,返回到用户应用程序 (GO)

主动背景模式被用于在 MCU 第一次以运行模式运行前将 Bootloader 或用户应用程序写入到

Flash 程序存储器中。MC9S08DZ60 系列产品从飞思卡尔工厂运出时,Flash 程序存储器在缺省

情况下是被擦除的,除非特别说明,以确保在 Flash 最初被编程前不会有程序在运行模式下被执

行。主动背景模式可用于擦除或重新编程先前已编程的 Flash。

若欲了解有关主动背景模式的更详尽信息,请参见 Development Support 一章。

0.10 等待模式

等待模式通过执行 WAIT 指令进入。在执行 WAIT 指令后, CPU 进入无时钟的低功耗状态。

CPU 进入等待模式后,CCR 中的 I 位被清除,进而使能中断操作。发生中断请求后,CPU 退出

等待模式并执行恢复处理,先开始执行堆栈中的中断服务程序。

MCU 处于等待模式时,背景调试命令的使用要受一些限制。 MCU 处于等待模式时,只有后台

命令和带状态内存访问命令可用。带状态内存访问命令不允许内存访问,但它们会报告错误,指

出 MCU 处于停止或等待模式。后台命令可用于从等待模式中唤醒 MCU 并使之进入主动背景模

式。

MC9S08DZ60 系列 , 第 3 版

34 飞思卡尔半导体公司

Page 19

0.11 停止模式

在 SOPT1 寄存器中设置了 STOPE 位的情况下,执行 STOP 指令后会进入两种停止模式之一。

在两种停止模式下,所有内部时钟都被暂停。我们可对 MCG 模块进行适当配置以使参考时钟保

持运行。更详尽信息请参见 Chapter 9, “Multi-Purpose Clock Generator (S08MCGV1) .”。

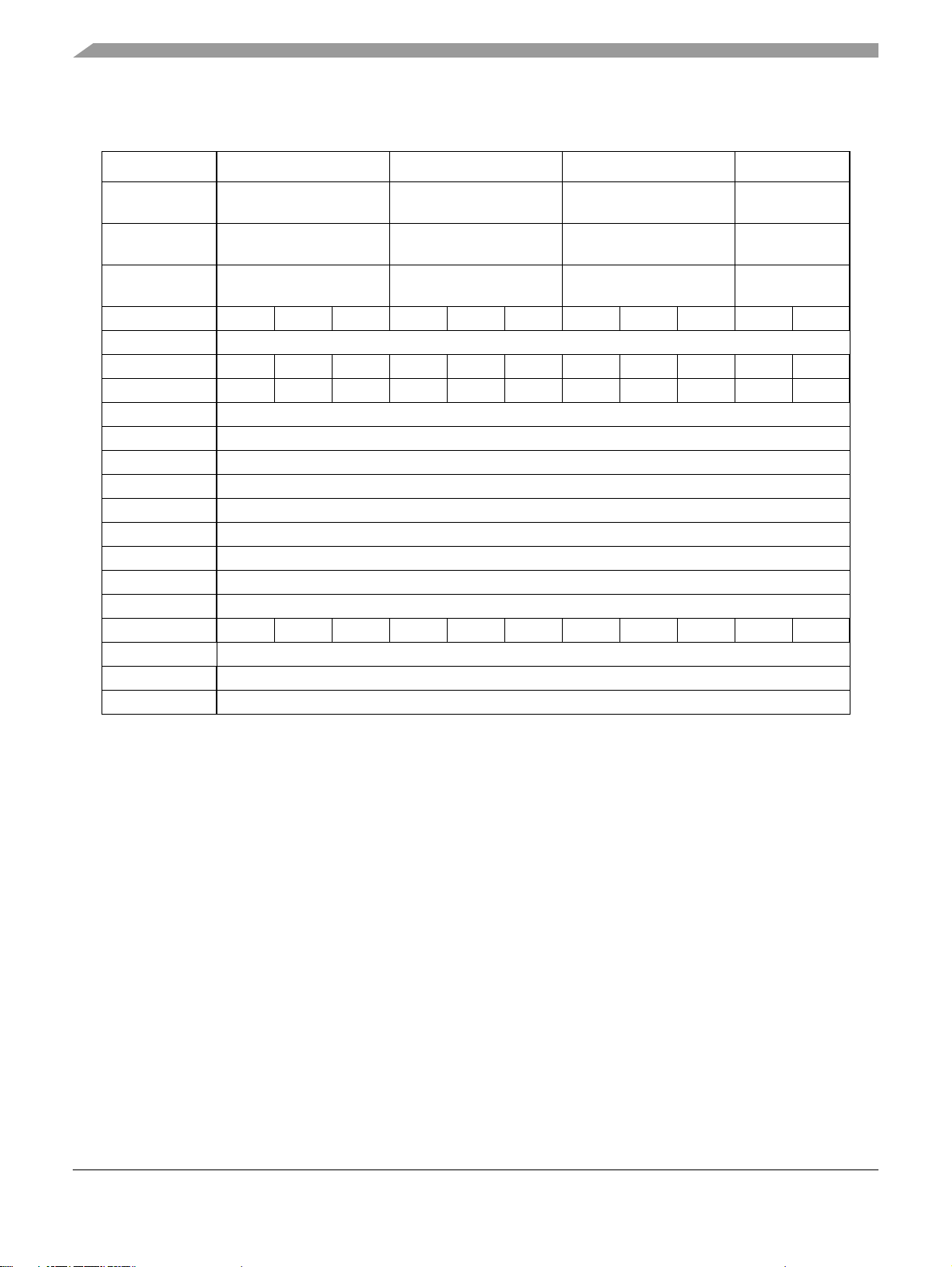

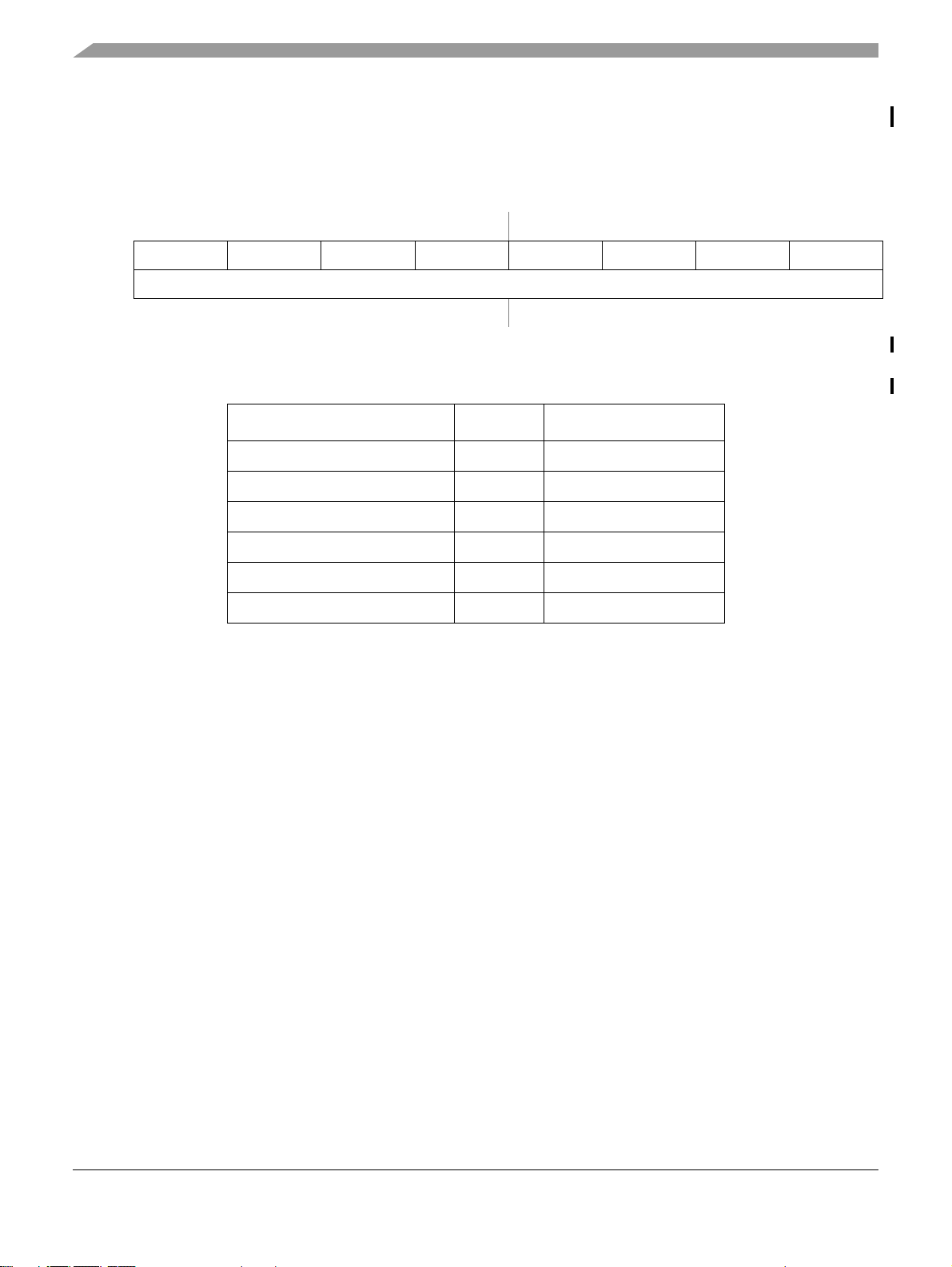

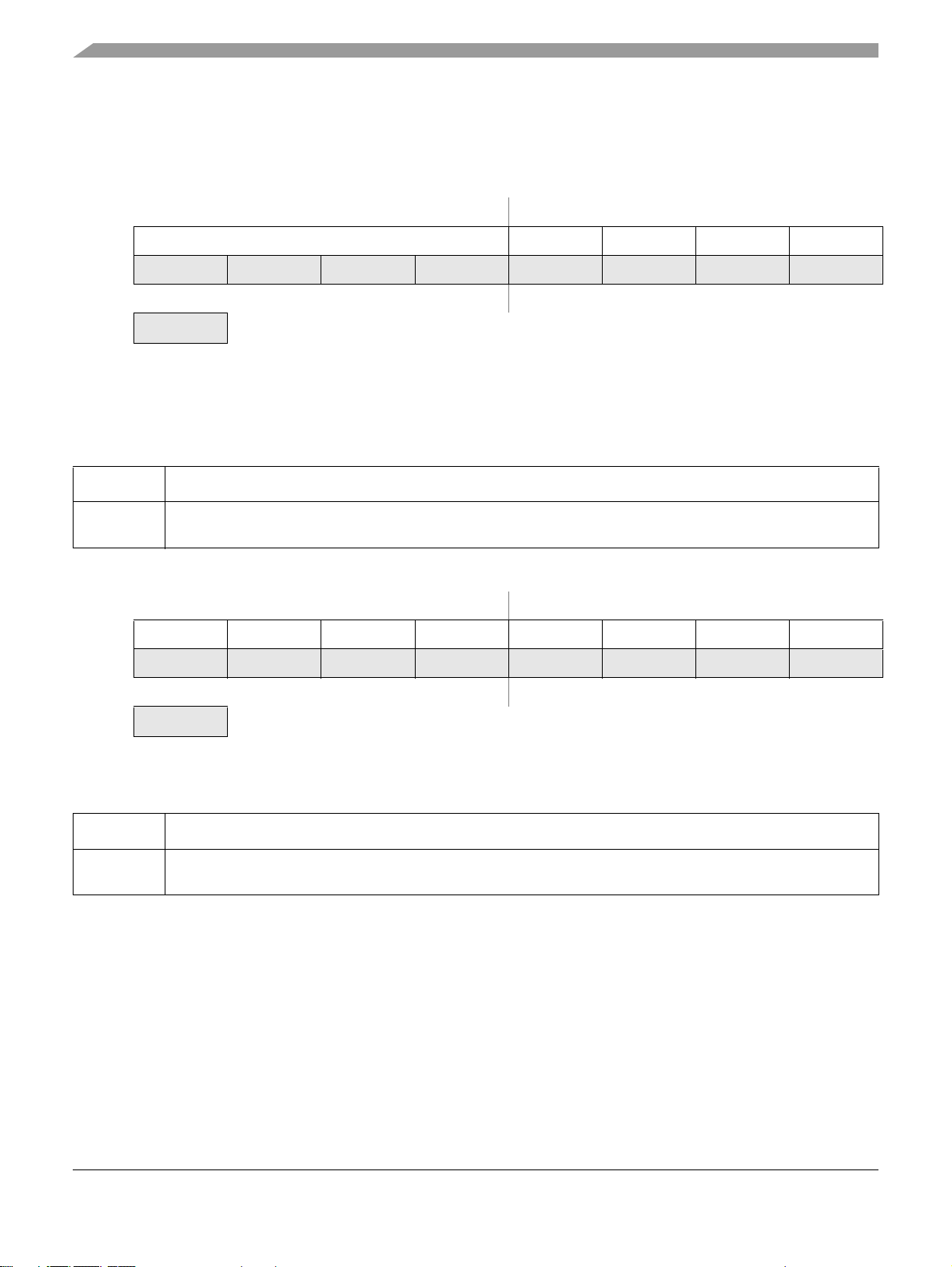

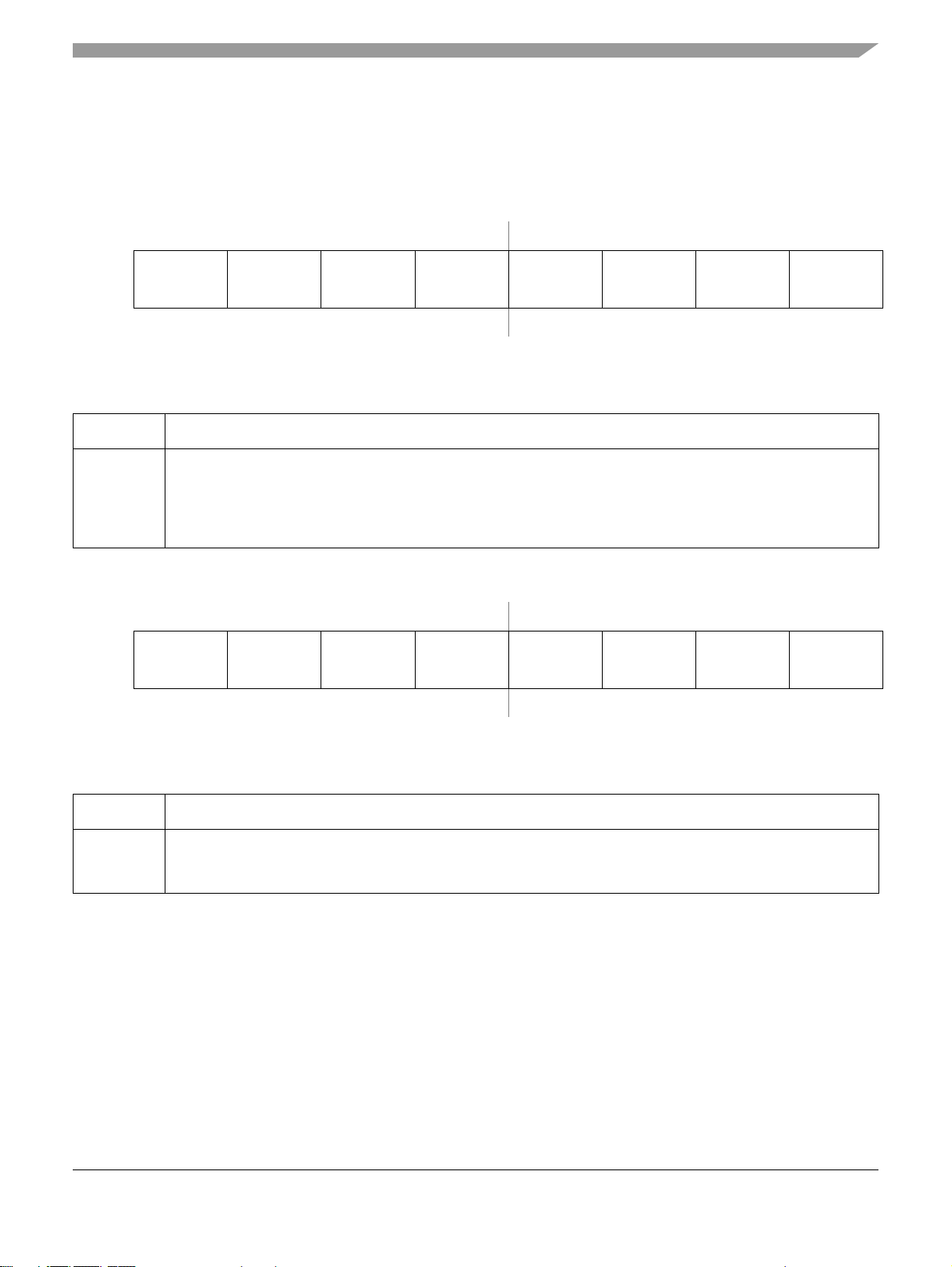

Table 0-4 显示了影响停止模式选择的所有控制位及各种条件下选择的模式。被选择的模式在执

行一个 STOP 指令后进入。

Table 0-4. 停止模式选择

STOPE ENBDM

0x x x

11 x x

10

10

10

1

ENBDM 位于 BDCSCR (只能通过 BDC 命令访问)中。详细信息请参见第 17.4.1.1 部分 “BDC 状态和控制寄存器

(BDCSCR)”。

2

处于 Stop3 模式而且 BDM 被启用时, SIDD 将接近 RIDD 水平,因为启用了内部时钟。

1

LVD E LVDSE PPDC

两个位都必须为 1

其中一个位为 0

其中一个位为 0

停止模式

停止模式被禁用; 如果执行了 STOP 指令,则进行非法 Opcode 代码复

位

Stop3 模式, BDM 被启用

x

Stop3 模式,电压调节器处于活动状态

0

Stop3 模式

1

Stop2 模式

2

0.11.1 Stop3 模式

Stop3 模式通过在 Table 0-4 所述条件下执行 STOP 指令进入。在这种情况下,所有内部寄存器

和逻辑、 RAM 内容和 I/O 管脚状态都被维持。

从 Stop3 模式中退出的操作通过 RESET 管脚或异步中断脚实现。这些异步中断脚包括 IRQ、

PIA0 – PIA7、 PIB0 – PIB7 和 PID0 – PID7。从 Stop3 模式中退出的操作也可以通过低压检

测(LVD)复位、低压警告 (LVW)中断、 ADC 转换完成中断、实时时钟 (RTC)中断、

MSCAN 唤醒中断或 SCI 接收器中断完成。

如果通过 RESET 脚的方式退出 Stop3 模式, MCU 将复位,操作将在获取复位向量后恢复。如

果通过中断的方式退出, MCU 将获取相应的中断向量。

0.11.1.1 在 Stop3 模式中启用 LVD

在电源电压下降到 LVD 电压以下时, LVD 系统可以生成一个中断或复位。在 CPU 执行 STOP

指令时,如果 LVD 在停止模式下被启用 (SPMSC1 中的 LVDE 和 LVDSE 位均被设置),那么

内部稳压器在停止模式下将继续保持活动状态。

要使 ADC 正常运行, LVD 必须在进入 Stop3 时处于启用状态。

MC9S08DZ60 系列 , 第 3 版

飞思卡尔半导体公司 35

Page 20

0.11.1.2 在 Stop3 模式中启用活动 BDM

如果 BDCSCR 中设置了 ENBDM,将启用从运行模式进入主动背景模式的操作。该寄存器在

Chapter 18, “开发支持.”中有详细描述。如果CPU执行STOP指令时设置了 ENBDM,连接到背景

调试逻辑的系统时钟将在 MCU 进入停止模式时继续保持活动状态。因此,这种情况下背景调试

通信仍可进行。此外,内部稳压器不会进入低功耗待机状态,而保持正常工作。

大多数后台命令不能在停止模式下使用。带状态内存访问命令不允许内存访问,但它们会报告错

误,支出 MCU 处于停止或等待模式。后台命令可用于从停止模式中唤醒 MCU 并使之进入主动

背景模式 (如果设置了 ENBDM 位的话)。进入背景调试模式后,所有后台命令都可以使用。

0.11.2 Stop2 模式

Stop2 模式通过在 Table 0-4 所示的情况下执行 STOP 指令进入。 MCU 的大部分内部电路在

Stop2 模式下是断电的, RAM 除外。在进入 Stop2 模式后,所有 I/O 管脚控制信号都被锁定,

以确保管脚可以在 Stop2 模式下保持原来的状态。

从 Stop2 模式中退出的操作通过输入有效 RESET 信号完成。只有在 3M05C 或更老的掩码集

中,您可以通过输入 PTA7/ADP7/IRQ 中断信号来退出 Stop2。

注意

只有在 3M05C 或更老的掩码集中, PTA7/ADP7/IRQ 是低电平唤

醒,因此在执行 STOP 指令前必须配置为输入,以避免从 Stop2 中

立即退出。如果 PTA7/ADP7/IRQ 被配置为高驱动输出,那么它可以

禁止唤醒功能。为了在 Stop2 模式下最大限度地降低功耗,该管脚

在被配置为输入时不应保持开路 (启用内部上拉器件;或连接外部

上拉 / 下拉器件;或将管脚设置为输出)。

此外,实时时钟计数器 (RTC)也可以从 Stop2 模式下唤醒 MCU (如果启用了的话)。

从 Stop2 模式中唤醒后, MCU 与加电复位 (POR)情况下一样启动:

• 所有模块控制和状态寄存器被复位

• LVD 复位功能被启用;如果 VDD低于 LVD 跳变点(由于 POR 选择的低跳变点),MCU 仍

处于复位状态

• CPU 读取复位向量

除了上面所述的以外,在从 Stop2 模式中唤醒后, SPMSC2 中的 PPDF 也会被设置。该标记用

于将用户代码引导到 Stop2 恢复程序中。 PPDF 仍保持有效且 I/O 管脚状态被锁定,直到 1 被写

入到 SPMSC2 中的 PPDACK 中。

为了在进入 Stop2 之前保持被配置为通用 I/O 的管脚的 I/O 状态,用户必须将 I/O 端口寄存器

(保存在 RAM 中)的内容恢复到端口寄存器中,然后再写入到 PPDACK 位中。如果端口寄存

器在写入到 PPDACK 中之前没有从 RAM 中恢复,那么在写入 PPDACK 时该管脚将切换到复位

状态。

MC9S08DZ60 系列 , 第 3 版

36 飞思卡尔半导体公司

Page 21

对于配置为外围 I/O 的管脚,用户在写入 PPDACK 位之前必须重新配置连接到该管脚的外围模

块。如果外围模块在写入 PPDACK 之前没有启用,那么该管脚在 I/O 锁定被打开时将由相关的

端口控制寄存器控制。

0.11.3 停止模式中的片上外围模块

当 MCU 进入任何停止模式时,连接到内部外围模块的系统时钟被停止。即使在异常情况下

(ENBDM = 1)(连接到背景调试逻辑的时钟继续运行),到外围系统的时钟也将被停止以降低

功耗。若欲了解有关停止模式下系统行为的详细信息,请参见 Section 0.11.2, “Stop2 Mode”

和 Section 0.11.1, “Stop3 Mode

外围设备

” 。

Table 0-5. 停止模式行为

模式

Stop2 Stop3

CPU

RAM

Flash/EEPROM

并行端口寄存器 关闭 待机

ACMP

ADC

IIC

MCG

MSCAN

RTC

SCI

SPI

TPM

电压调节器 关闭 可选择开启

XOSC

I/O 管脚 状态被保持 状态被保持

BDM

LVD/LVW

1

要求启用同步 ADC 时钟和 LVD,否则为待机。

2

MCGC1 中设置 IRCLKEN 和 IREFSTEN,否则为待机。

3

要求启用 RTC,否则为待机。

4

要求启用 LV D 或 BDC。

5

MCGC2 中设置 ERCLKEN 和 EREFSTEN,否则为待机。在高频率范围 (MCGC2

中设置 RANGE)还要求在 Stop3 中启用 LVD。

6

如果进入 Stop2 模式时设置了 ENBDM, MCU 实际上会进入 Stop3 模式。

7

如果进入 Stop2 模式时设置了 LVDSE, MCU 实际上会进入 Stop3 模式。

关闭 待机

待机 待机

关闭 待机

关闭 关闭

关闭 可选择开启

关闭 待机

关闭 可选择开启

关闭 待机

可选择开启

关闭

关闭

3

关闭 待机

关闭 待机

关闭 待机

关闭 可选择开启

6

7

可选择开启

可选择开启

可选择开启

1

2

3

4

5

MC9S08DZ60 系列 , 第 3 版

飞思卡尔半导体公司 37

Page 22

DIRECT PAGE REGISTERS

RAM

4096 BYTES

0x0000

0x007F

0x0080

0x107F

0x1800

0x17FF

0x18FF

0x1400

0xFFFF

0x1080

MC9S08DZ60

128 BYTES

EEPROM

1

2 x 1024 BYTES

HIGH PAGE REGISTERS

256 BYTES

FLASH

59136 BYTES

DIRECT PAGE REGISTERS

RAM

3072 BYTES

0x0000

0x007F

0x0080

0x0C7F

0x1800

0x17FF

0x18FF

0x1900

0xFFFF

0x1500

MC9S08DZ48

0x3FFF

0x4000

128 BYTES

HIGH PAGE REGISTERS

256 BYTES

FLASH

49152 BYTES

UNIMPLEMENTED

0x0C80

0x14FF

2176 BYTES

UNIMPLEMENTED

9984 BYTES

DIRECT PAGE REGISTERS

RAM

2048 BYTES

0x0000

0x007F

0x0080

0x087F

0x1800

0x17FF

0x18FF

0x1900

0xFFFF

0x1600

MC9S08DZ32

0x7BFF

0x7C00

128 BYTES

HIGH PAGE REGISTERS

256 BYTES

FLASH

33792 BYTES

UNIMPLEMENTED

0x0880

0x15FF

3456 BYTES

UNIMPLEMENTED

25,344 BYTES

DIRECT PAGE REGISTERS

RAM

1024 BYTES

0x0000

0x007F

0x0080

0x047F

0x1800

0x17FF

0x18FF

0x1900

0xFFFF

0x1700

MC9S08DZ16

0xBDFF

0xBE00

128 BYTES

HIGH PAGE REGISTERS

256 BYTES

FLASH

16896 BYTES

UNIMPLEMENTED

0x0480

0x16FF

4736 BYTES

UNIMPLEMENTED

42,240 BYTES

EEPROM

1

2 x 512 BYTES

EEPROM

1

2 x 256 BYTES

0x1900

FLASH

896 BYTES

0x13FF

EEPROM

1

2 x 768 BYTES

1

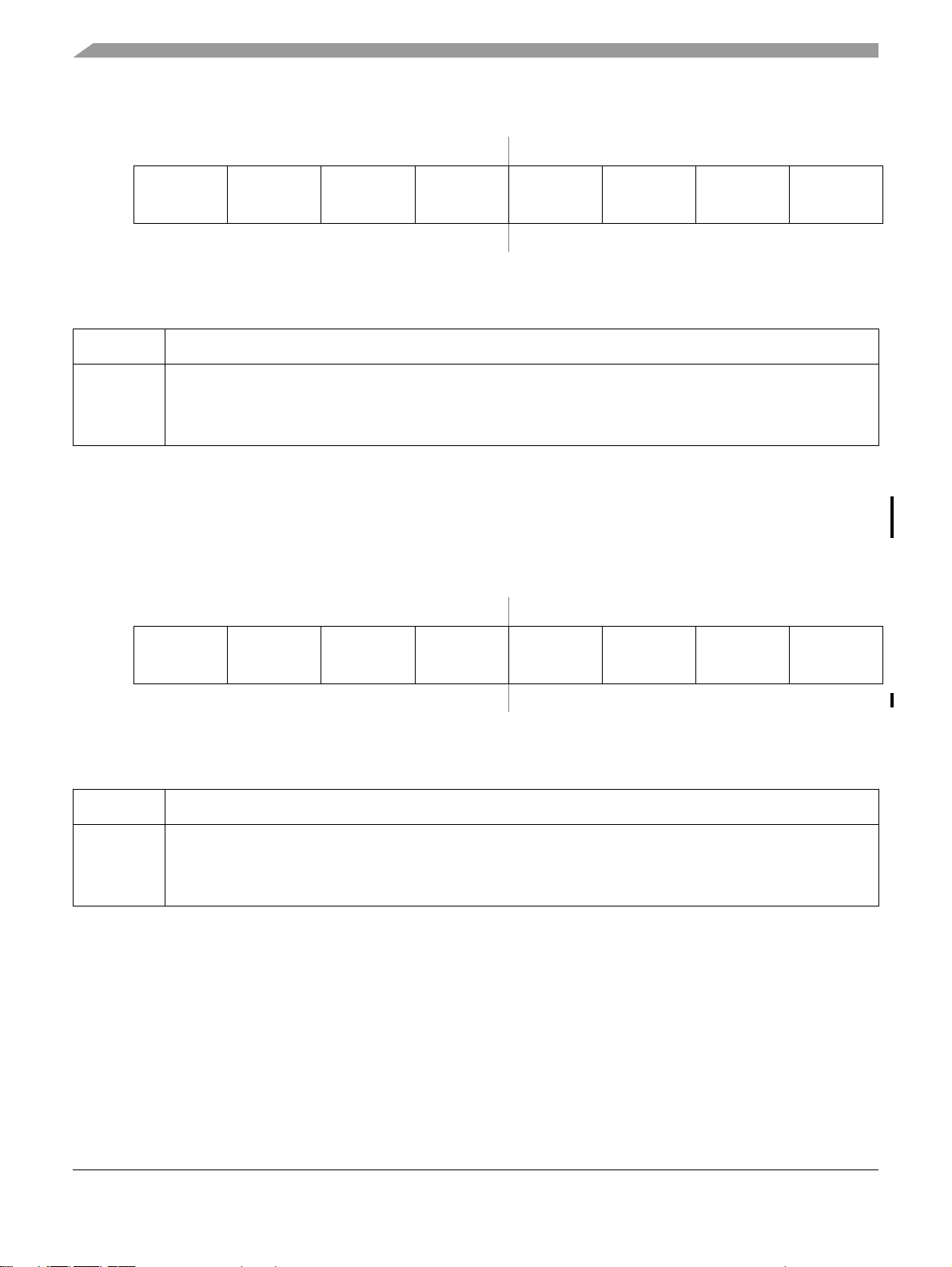

EEPROM 地址范围显示总 EEPROM 的一半。 详尽信息请参见 Section 0.16.10, “EEPROM 映射 ” 。

第 4 章

存储器

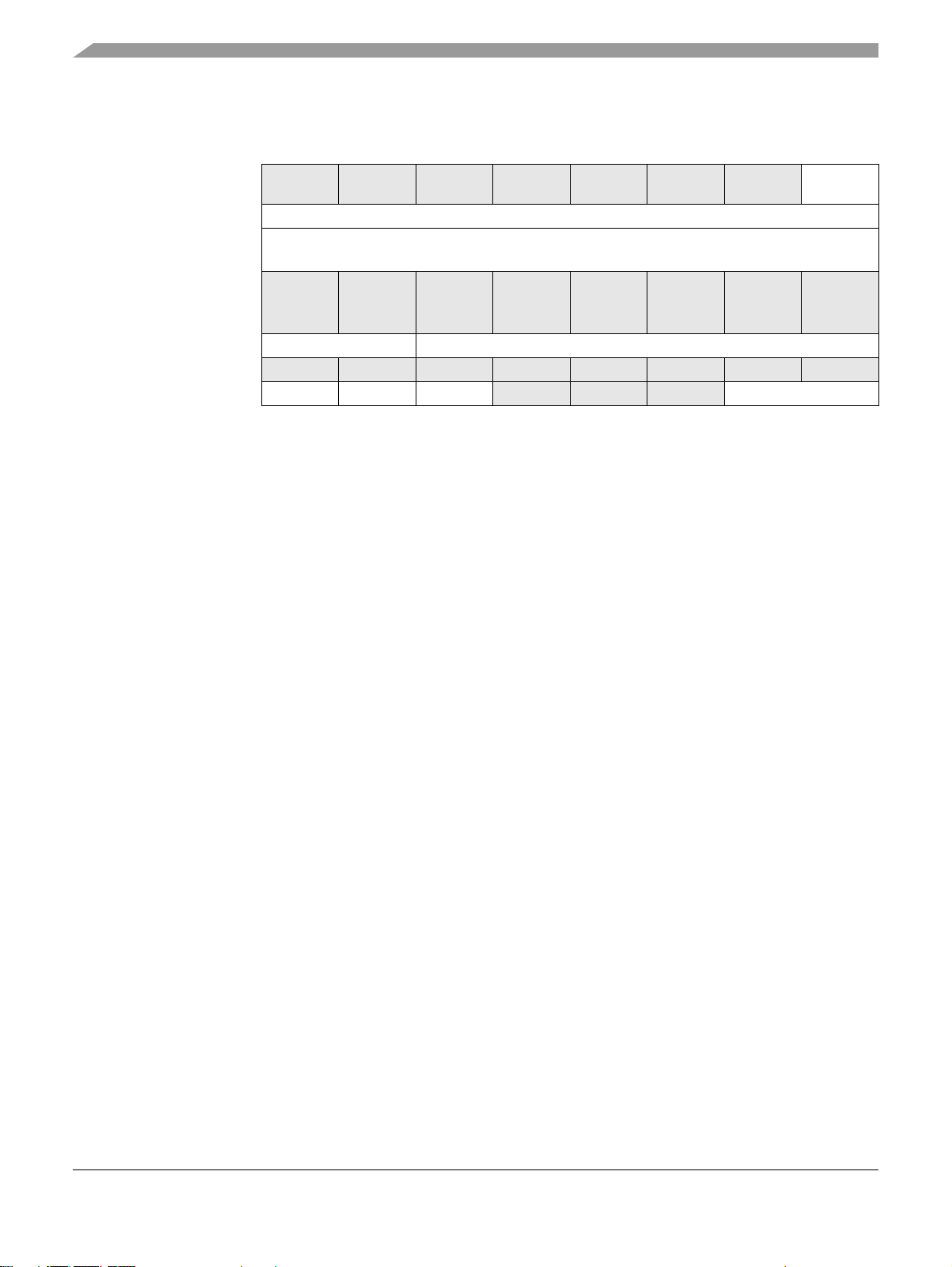

0.12 MC9S08DZ60 系列产品存储器映射

MC9S08DZ60 系列产品中的片上存储器包括 RAM、 EEPROM、用于非易失性数据存储的

Flash 程序存储器、 I/O 和控制 / 状态寄存器。这些寄存器可分为以下 3 组:

• 直接页面寄存器 (0x0000 through 0x007F)

• 高端页面 (High-page)寄存器 (0x1800 到 0x18FF)

• 非易失性寄存器 (0xFFB0 through 0xFFBF)

Figure 0-7. MC9S08DZ60 存储器图

MC9S08DZ60 系列 , 第 3 版

38 飞思卡尔半导体公司

Page 23

0.13 复位和中断向量分配

Table 0-6 显示了复位和中断向量的地址分配情况。该表中显示的向量名称为飞思卡尔半导体提

供的 MC9S08DZ60 系列通用文件中使用的标签。

Table 0-6. 复位和中断向量

地址 (高 / 低) 向量 向量名称

0xFFC0:0xFFC1 ACMP2 Vacmp2

0xFFC2:0xFFC3 ACMP1 Vacmp1

0xFFC4:0xFFC5 MSCAN Transmit Vcantx

0xFFC6:0xFFC7 MSCAN Receive Vcanrx

0xFFC8:0xFFC9 MSCAN errors Vcanerr

0xFFCA:0xFFCB MSCAN wake up Vcanwu

0xFFCC:0xFFCD RTC Vrtc

0xFFCE:0xFFCF IIC Viic

0xFFD0:0xFFD1 ADC Conversion Vadc

0xFFD2:0xFFD3 Port A, Port B, Port D Vport

0xFFD4:0xFFD5 SCI2 Transmit Vsci2tx

0xFFD6:0xFFD7 SCI2 Receive Vsci2rx

0xFFD8:0xFFD9 SCI2 Error Vsci2err

0xFFDA:0xFFDB SCI1 Transmit Vsci1tx

0xFFDC:0xFFDD SCI1 Receive Vsci1rx

0xFFDE:0xFFDF SCI1 Error Vsci1err

0xFFE0:0xFFE1 SPI Vspi

0xFFE2:0xFFE3 TPM2 Overflow Vtpm2ovf

0xFFE4:0xFFE5 TPM2 Channel 1 Vtpm2ch1

0xFFE6:0xFFE7 TPM2 Channel 0 Vtpm2ch0

0xFFE8:0xFFE9 TPM1 Overflow Vtpm1ovf

0xFFEA:0xFFEB TPM1 Channel 5 Vtpm1ch5

0xFFEC:0xFFED TPM1 Channel 4 Vtpm1ch4

0xFFEE:0xFFEF TPM1 Channel 3 Vtpm1ch3

0xFFF0:0xFFF1 TPM1 Channel 2 Vtpm1ch2

0xFFF2:0xFFF3 TPM1 Channel 1 Vtpm1ch1

0xFFF4:0xFFF5 TPM1 Channel 0 Vtpm1ch0

0xFFF6:0xFFF7 MCG Loss of lock Vlol

0xFFF8:0xFFF9 Low-Voltage Detect Vlvd

0xFFFA:0xFFFB IRQ Virq

0xFFFC:0xFFFD SWI Vswi

0xFFFE:0xFFFF Reset Vreset

MC9S08DZ60 系列 , 第 3 版

飞思卡尔半导体公司 39

Page 24

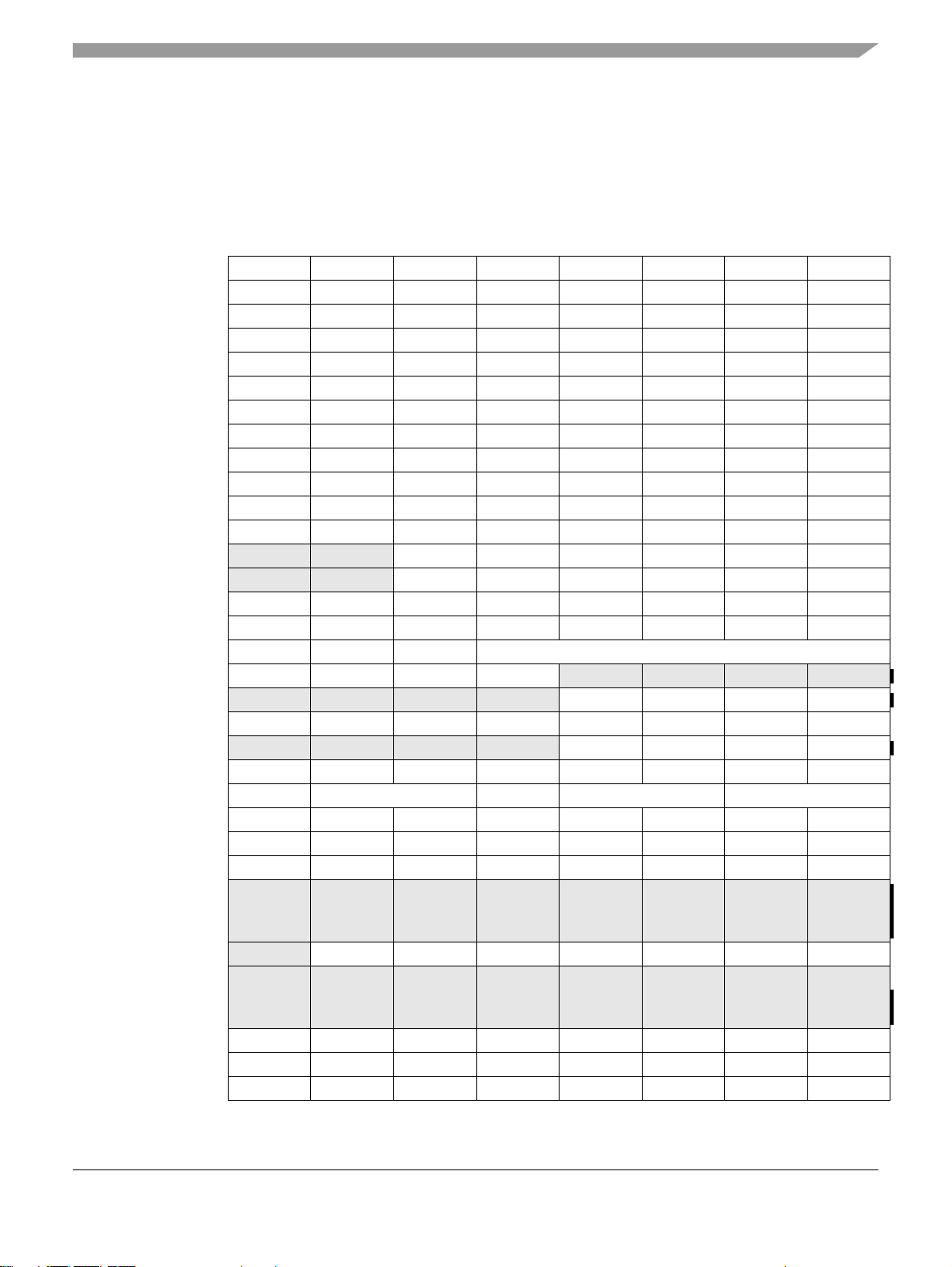

0.14 寄存器地址和位分配

MC9S08DZ60 系列产品中的寄存器可分为以下几组:

• 直接页面寄存器,位于存储器映象的前 128 个位置上。这些寄存器可以通过高效的直接寻

址模式指令访问。

• 高端页面 (High-page)寄存器,不经常使用,因此位于存储器映象中 0x1800 以上。这

样就在直接页面中为经常使用的寄存器和 RAM 留出了更多空间。

• 非易失性寄存器,由 Flash中0xFFB0–0xFFBF之间16个位置组成的位置段组成。 非易失

性寄存器位置包括:

— NVPROT 和 NVOPT 在复位时上载到工作的寄存器中。

— 一个 8 字节后门对比密钥,可选择为用户分配有控制的安全内存访问权限。

由于非易失性寄存器的位置是在 Flash 中,所以必须像其他位置 Flash 一样擦除和编程。

直接页面寄存器可以通过高效的直接寻址模式指令访问。位操作指令可用于访问任何直接页面寄

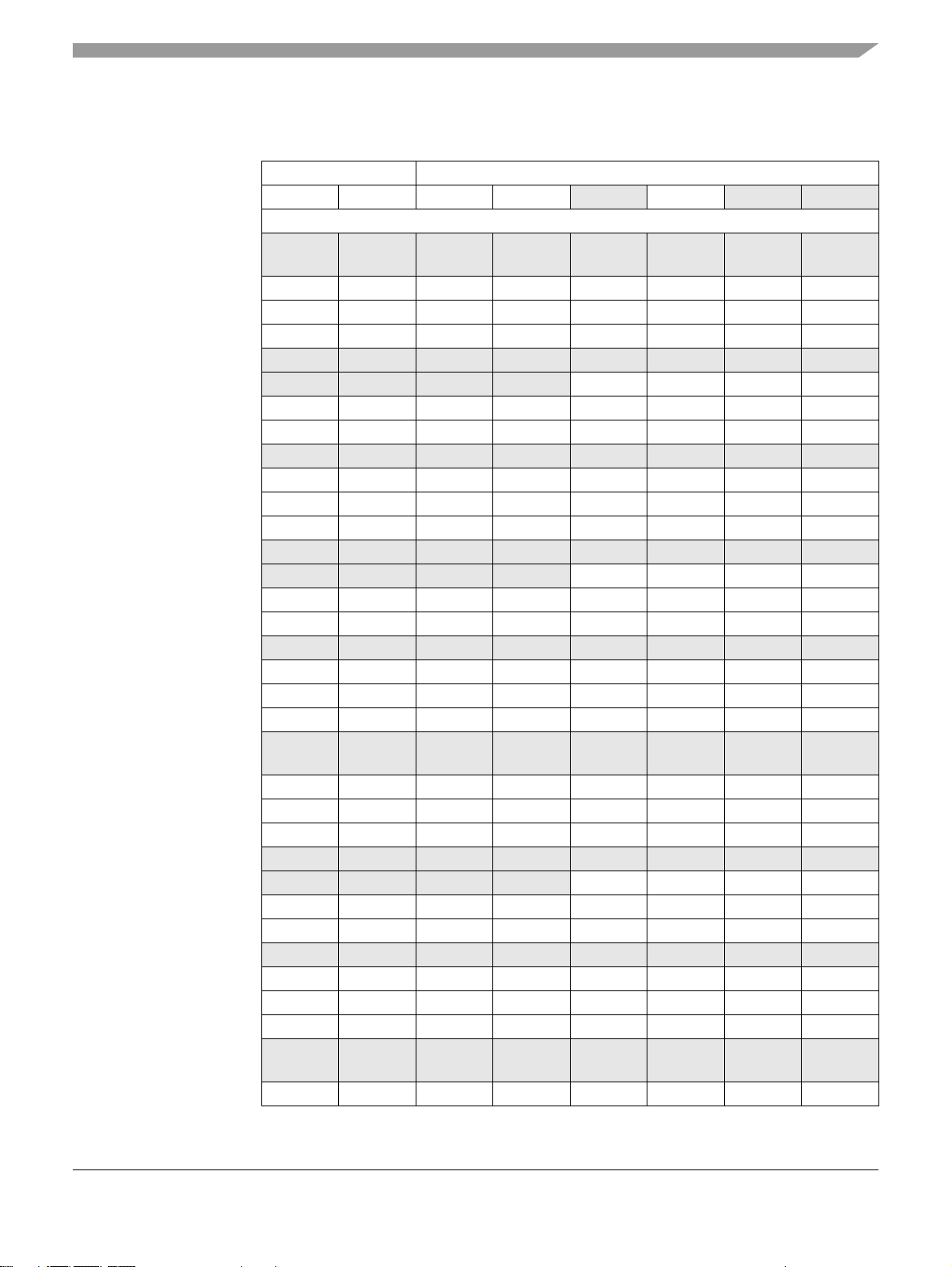

存器中的任何位。 Ta bl e 0 -7 总结了所有用户可访问的直接页面寄存器和控制位。

Table 0-7 所列的直接页面寄存器可以使用更高效的直接寻址模式 (这种模式只需要地址的较低

字节)。因此,第 1 栏中地址的较低字节用粗体显示。 在 Table 0-8 和 Table 0-10 中 , 第 1 栏中

的整个地址都用粗体显示。在 Ta ble 0 -7, Table 0-8, 和 Table 0-10 中 , 第 2 栏中的寄存器名称用

粗体显示以便与右侧的位名称区分开来。与所列出的位不相关的单元在阴影中显示。带有 0 的

阴影单元表示这个未使用的位始终应为 0。带有破折号的阴影单元表示未使用的或预留的位位

置,可以是 1 或 0。

MC9S08DZ60 系列 , 第 3 版

40 飞思卡尔半导体公司

Page 25

Table 0-7. 直接页面寄存器总结 (第 1 页,共 3 页)

地址 寄存器名称 位 7

0x0000 PTAD

0x0001 PTADD

0x0002 PTBD

0x0003 PTBDD

0x0004 PTCD

0x0005 PTCDD

0x0006 PTDD

0x0007 PTDDD

0x0008 PTED

0x0009 PTEDD

0x000A PTFD

0x000B PTFDD

0x000C PTGD

0x000D PTGDD

0x000E ACMP1SC

0x000F ACMP2SC

0x0010 ADCSC1

0x0011 ADCSC2

0x0012 ADCRH

0x0013 ADCRL

0x0014 ADCCVH

0x0015 ADCCVL

0x0016 ADCCFG

0x0017 APCTL1

0x0018 APCTL2

0x0019 APCTL3

0x001A

–

预留

0x001B

0x001C IRQSC

0x001D

–

预留

0x001F

0x0020 TPM1SC

0x0021 TPM1CNTH

0x0022 TPM1CNTL

654321

PTAD7 PTAD6 PTAD5 PTAD4 PTAD3 PTAD2 PTAD1 PTAD0

PTADD7 PTADD6 PTADD5 PTADD4 PTADD3 PTADD2 PTADD1 PTADD0

PTBD7 PTBD6 PTBD5 PTBD4 PTBD3 PTBD2 PTBD1 PTBD0

PTBDD7 PTBDD6 PTBDD5 PTBDD4 PTBDD3 PTBDD2 PTBDD1 PTBDD0

PTCD7 PTCD6 PTCD5 PTCD4 PTCD3 PTCD2 PTCD1 PTCD0

PTCDD7 PTCDD6 PTCDD5 PTCDD4 PTCDD3 PTCDD2 PTCDD1 PTCDD0

PTDD7 PTDD6 PTDD5 PTDD4 PTDD3 PTDD2 PTDD1 PTDD0

PTDDD7 PTDDD6 PTDDD5 PTDDD4 PTDDD3 PTDDD2 PTDDD1 PTDDD0

PTED7 PTED6 PTED5 PTED4 PTED3 PTED2 PTED1 PTED0

PTEDD7 PTEDD6 PTEDD5 PTEDD4 PTEDD3 PTEDD2 PTEDD1 PTEDD0

PTFD7 PTFD6 PTFD5 PTFD4 PTFD3 PTFD2 PTFD1 PTFD0

PTFDD7 PTFDD6 PTFDD5 PTFDD4 PTFDD3 PTFDD2 PTFDD1 PTFDD0

0 0 PTGD5 PTGD4 PTGD3 PTGD2 PTGD1 PTGD0

0 0 PTGDD5 PTGDD4 PTGDD3 PTGDD2 PTGDD1 PTGDD0

ACME ACBGS ACF ACIE ACO ACOPE ACMOD1 ACMOD0

ACME ACBGS ACF ACIE ACO ACOPE ACMOD1 ACMOD0

COCO AIEN ADCO ADCH

ADACT ADTRG ACFE ACFGT 0 0 — —

0 0 0 0 ADR11 ADR10 ADR9 ADR8

ADR7 ADR6 ADR5 ADR4 ADR3 ADR2 ADR1 ADR0

0 0 0 0 ADCV11 ADCV10 ADCV9 ADCV8

ADCV7 ADCV6 ADCV5 ADCV4 ADCV3 ADCV2 ADCV1 ADCV0

ADLPC ADIV ADLSMP MODE ADICLK

ADPC7 ADPC6 ADPC5 ADPC4 ADPC3 ADPC2 ADPC1 ADPC0

ADPC15 ADPC14 ADPC13 ADPC12 ADPC11 ADPC10 ADPC9 ADPC8

ADPC23 ADPC22 ADPC21 ADPC20 ADPC19 ADPC18 ADPC17 ADPC16

—

—

0 IRQPDD IRQEDG IRQPE IRQF IRQACK IRQIE IRQMOD

—

—

TOF TOIE CPWMS CLKSB CLKSA PS2 PS1 PS0

Bit 15 14 13 12 11 10 9 Bit 8

Bit 7654321Bit 0

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

位 0

—

—

—

—

MC9S08DZ60 系列 , 第 3 版

飞思卡尔半导体公司 41

Page 26

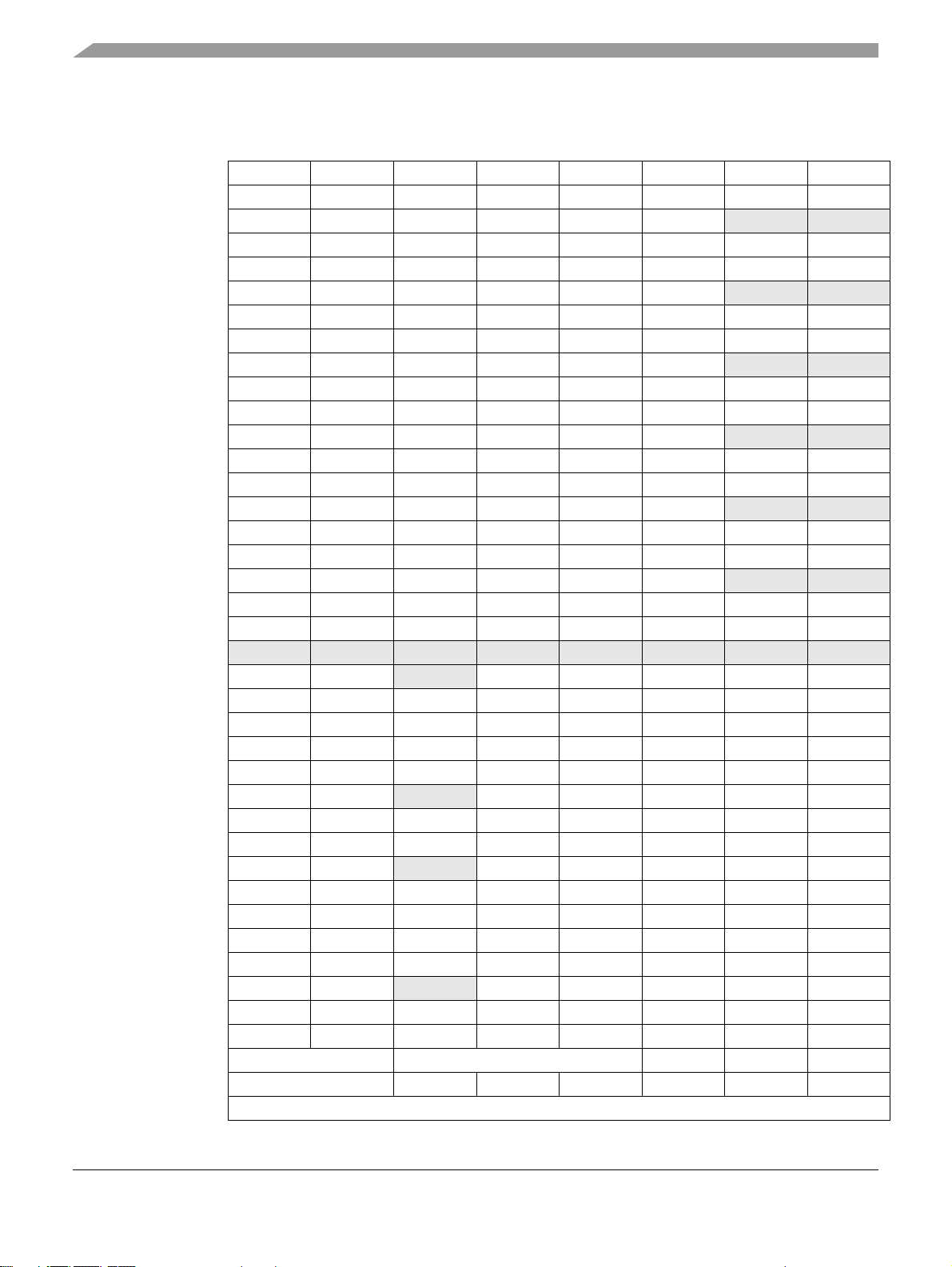

Table 0-7. 直接页面寄存器总结 (第 1 页,共 3 页)

地址 寄存器名称 位 7

0x0023 TPM1MODH

0x0024 TPM1MODL

0x0025 TPM1C0SC

0x0026 TPM1C0VH

0x0027 TPM1C0VL

0x0028 TPM1C1SC

0x0029 TPM1C1VH

0x002A TPM1C1VL

0x002B TPM1C2SC

0x002C TPM1C2VH

0x002D TPM1C2VL

0x002E TPM1C3SC

0x002F TPM1C3VH

0x0030 TPM1C3VL

0x0031 TPM1C4SC

0x0032 TPM1C4VH

0x0033 TPM1C4VL

0x0034 TPM1C5SC

0x0035 TPM1C5VH

0x0036 TPM1C5VL

0x0037

预留

0x0038 SCI1BDH

0x0039 SCI1BDL

0x003A SCI1C1

0x003B SCI1C2

0x003C SCI1S1

0x003D SCI1S2

0x003E SCI1C3

0x003F SCI1D

0x0040 SCI2BDH

0x0041 SCI2BDL

0x0042 SCI2C1

0x0043 SCI2C2

0x0044 SCI2S1

0x0045 SCI2S2

0x0046 SCI2C3

0x0047 SCI2D

0x0048 MCGC1

0x0049 MCGC2

0x004A MCGTRM

654321

Bit 15 14 13 12 11 10 9 Bit 8

Bit 7654321Bit 0

CH0F CH0IE MS0B MS0A ELS0B ELS0A 0 0

Bit 15 14 13 12 11 10 9 Bit 8

Bit 7654321Bit 0

CH1F CH1IE MS1B MS1A ELS1B ELS1A 0 0

Bit 15 14 13 12 11 10 9 Bit 8

Bit 7654321Bit 0

CH2F CH2IE MS2B MS2A ELS2B ELS2A 0 0

Bit 15 14 13 12 11 10 9 Bit 8

Bit 7654321Bit 0

CH3F CH3IE MS3B MS3A ELS3B ELS3A 0 0

Bit 15 14 13 12 11 10 9 Bit 8

Bit 7654321Bit 0

CH4F CH4IE MS4B MS4A ELS4B ELS4A 0 0

Bit 15 14 13 12 11 10 9 Bit 8

Bit 7654321Bit 0

CH5F CH5IE MS5B MS5A ELS5B ELS5A 0 0

Bit 15 14 13 12 11 10 9 Bit 8

Bit 7654321Bit 0

— — — — — — — —

LBKDIE RXEDGIE 0 SBR12 SBR11 SBR10 SBR9 SBR8

SBR7 SBR6 SBR5 SBR4 SBR3 SBR2 SBR1 SBR0

LOOPS SCISWAI RSRC M WAKE ILT PE PT

TIE TCIE RIE ILIE TE RE RWU SBK

TDRE TC RDRF IDLE OR NF FE PF

LBKDIF RXEDGIF 0 RXINV RWUID BRK13 LBKDE RAF

R8 T8 TXDIR TXINV ORIE NEIE FEIE PEIE

Bit 7654321Bit 0

LBKDIE RXEDGIE 0 SBR12 SBR11 SBR10 SBR9 SBR8

SBR7 SBR6 SBR5 SBR4 SBR3 SBR2 SBR1 SBR0

LOOPS SCISWAI RSRC M WAKE ILT PE PT

TIE TCIE RIE ILIE TE RE RWU SBK

TDRE TC RDRF IDLE OR NF FE PF

LBKDIF RXEDGIF 0 RXINV RWUID BRK13 LBKDE RAF

R8 T8 TXDIR TXINV ORIE NEIE FEIE PEIE

Bit 7654321Bit 0

CLKS RDIV IREFS IRCLKEN IREFSTEN

BDIV RANGE HGO LP EREFS ERCLKEN EREFSTEN

TRIM

位 0

MC9S08DZ60 系列 , 第 3 版

42 飞思卡尔半导体公司

Page 27

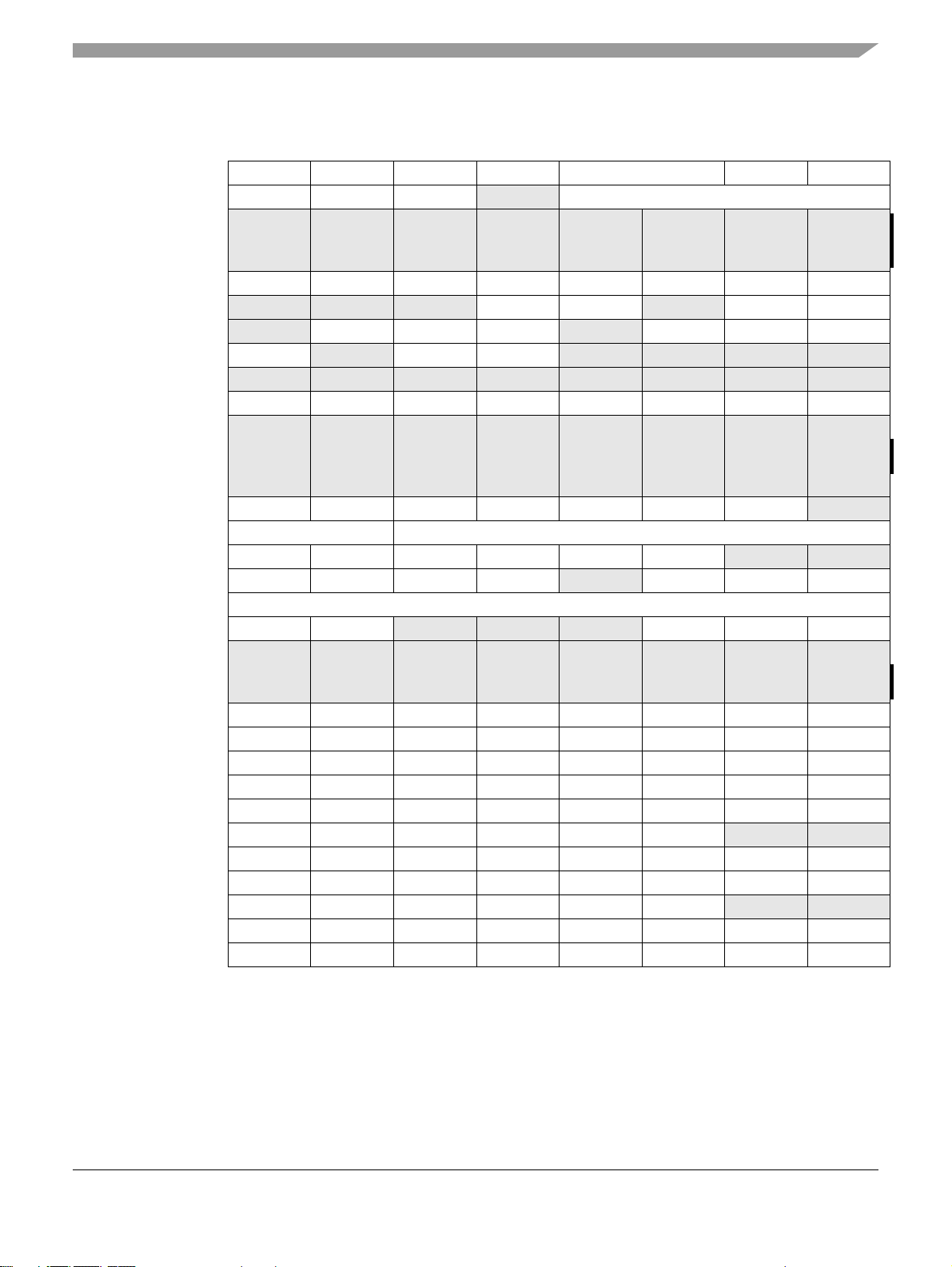

Table 0-7. 直接页面寄存器总结 (第 1 页,共 3 页)

地址 寄存器名称 位 7

0x004B MCGSC

0x004C MCGC3

0x004D

–

预留

0x004F

0x0050 SPIC1

0x0051 SPIC2

0x0052 SPIBR

0x0053 SPIS

0x0054

预留

0x0055 SPID

0x0056

–

0x0057

预留

0x0058 IICA

0x0059 IICF

0x005A IICC1

0x005B IICS

0x005C IICD

0x005D IICC2

0x005E

–

预留

0x005F

0x0060 TPM2SC

0x0061 TPM2CNTH

0x0062 TPM2CNTL

0x0063 TPM2MODH

0x0064 TPM2MODL

0x0065 TPM2C0SC

0x0066 TPM2C0VH

0x0067 TPM2C0VL

0x0068 TPM2C1SC

0x0069 TPM2C1VH

0x006A TPM2C1VL

654321

LOLS LOCK PLLST IREFST CLKST OSCINIT FTRIM

LOLIE PLLS CME 0VDIV

—

—

SPIE SPE SPTIE MSTR CPOL CPHA SSOE LSBFE

0 0 0 MODFEN BIDIROE 0 SPISWAI SPC0

0 SPPR2 SPPR1 SPPR0 0 SPR2 SPR1 SPR0

SPRF 0SPTEFMODF 0 0 0 0

0 0 0 0 0 0 0 0

Bit 7654321Bit 0

—

—

AD7 AD6 AD5 AD4 AD3 AD2 AD1 0

MULT ICR

IICEN IICIE MST TX TXAK RSTA 0 0

TCF IAAS BUSY ARBL 0 SRW IICIF RXAK

GCAEN ADEXT 0 0 0 AD10 AD9 AD8

—

—

TOF TOIE CPWMS CLKSB CLKSA PS2 PS1 PS0

Bit 15 14 13 12 11 10 9 Bit 8

Bit 7654321Bit 0

Bit 15 14 13 12 11 10 9 Bit 8

Bit 7654321Bit 0

CH0F CH0IE MS0B MS0A ELS0B ELS0A 0 0

Bit 15 14 13 12 11 10 9 Bit 8

Bit 7654321Bit 0

CH1F CH1IE MS1B MS1A ELS1B ELS1A 0 0

Bit 15 14 13 12 11 10 9 Bit 8

Bit 7654321Bit 0

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

DATA

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

位 0

—

—

—

—

—

—

MC9S08DZ60 系列 , 第 3 版

飞思卡尔半导体公司 43

Page 28

Table 0-7. 直接页面寄存器总结 (第 1 页,共 3 页)

地址 寄存器名称 位 7

0x006B

预留

0x006C RTCSC

0x006D RTCCNT

0x006E RTCMOD

0x006F

预留

0x0070

–

预留

0x007F

— — — — — — — —

RTIF RTCLKS RTIE RTCPS

— — — — — — — —

—

—

654321

RTCCNT

RTCMOD

—

—

—

—

—

—

—

—

—

—

—

—

Table 0-8 中显示的高端页面寄存器的访问频率与其它 I/O 和控制寄存器相比要低得多,因此存

放在可直接寻址的内存空间外,从 0x1800 开始。

Table 0-8. 高端页面寄存器总结 (第 1 页,共 3 页)

地址 寄存器名称 位 7

0x1800 SRS

0x1801 SBDFR

0x1802 SOPT1

0x1803 SOPT2

0x1804 –

0x1805

预留

0x1806 SDIDH

0x1807 SDIDL

0x1808

预留

0x1809 SPMSC1

0x180A SPMSC2

0x180B–

0x180F

预留

0x1810 DBGCAH

0x1811 DBGCAL

0x1812 DBGCBH

0x1813 DBGCBL

0x1814 DBGFH

0x1815 DBGFL

0x1816 DBGC

0x1817 DBGT

0x1818 DBGS

0x1819–

0x181F

预留

0x1820 FCDIV

0x1821 FOPT

0x1822

预留

0x1823 FCNFG

POR PIN COP ILOP ILAD LOCS LVD 0

0 0 0 0 0 0 0BDFR

COPT STOPE SCI2PS IICPS 0 0 0

COPCLKS COPW 0 ADHTS 0 MCSEL

—

—

— — — — ID11 ID10 ID9 ID8

ID7 ID6 ID5 ID4 ID3 ID2 ID1 ID0

— — — — — — — —

LVWF LVWACK LVWIE LVDRE LVDSE LVDE 0BGBE

0 0 LVDV LVWV PPDF PPDACK 0 PPDC

—

—

Bit 15 14 13 12 11 10 9 Bit 8

Bit 7654321Bit 0

Bit 15 14 13 12 11 10 9 Bit 8

Bit 7654321Bit 0

Bit 15 14 13 12 11 10 9 Bit 8

Bit 7654321Bit 0

DBGEN ARM TAG BRKEN RWA RWAEN RWB RWBEN

TRGSEL BEGIN 0 0 TRG3 TRG2 TRG1 TRG0

AF BF ARMF 0 CNT3 CNT2 CNT1 CNT0

—

—

DIVLD PRDIV8 DIV

KEYEN FNORED EPGMOD 0 0 0 SEC

— — — — — — — —

0 EPGSEL KEYACC Reserved

654321

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

1

0 0 0 1

—

—

—

—

—

—

—

—

—

—

—

—

位 0

—

—

—

—

—

—

位 0

—

—

MC9S08DZ60 系列 , 第 3 版

44 飞思卡尔半导体公司

Page 29

Table 0-8. 高端页面寄存器总结 (第 1 页,共 3 页)

地址 寄存器名称 位 7

0x1824 FPROT

0x1825 FSTAT

0x1826 FCMD

0x1827–

0x183F

预留

0x1840 PTAPE

0x1841 PTASE

0x1842 PTADS

0x1843

预留

0x1844 PTASC

0x1845 PTAPS

0x1846 PTAES

0x1847

预留

0x1848 PTBPE

0x1849 PTBSE

0x184A PTBDS

0x184B

预留

0x184C PTBSC

0x184D PTBPS

0x184E PTBES

0x184F

预留

0x1850 PTCPE

0x1851 PTCSE

0x1852 PTCDS

0x1853–

0x1857

预留

0x1858 PTDPE

0x1859 PTDSE

0x185A PTDDS

0x185B

预留

0x185C PTDSC

0x185D PTDPS

0x185E PTDES

0x185F

预留

0x1860 PTEPE

0x1861 PTESE

0x1862 PTEDS

0x1863–

0x1867

预留

0x1868 PTFPE

654321

EPS FPS

FCBEF FCCF FPVIOL FACCERR 0 FBLANK 0 0

FCMD

—

—

PTAPE7 PTAPE6 PTAPE5 PTAPE4 PTAPE3 PTAPE2 PTAPE1 PTAPE0

PTASE7 PTASE6 PTASE5 PTASE4 PTASE3 PTASE2 PTASE1 PTASE0

PTADS7 PTADS6 PTADS5 PTADS4 PTADS3 PTADS2 PTADS1 PTADS0

— — — — — — — —

0 0 0 0 PTAIF PTAACK PTAIE PTAMOD

PTAPS7 PTAPS6 PTAPS5 PTAPS4 PTAPS3 PTAPS2 PTAPS1 PTAPS0

PTAES7 PTAES6 PTAES5 PTAES4 PTAES3 PTAES2 PTAES1 PTAES0

— — — — — — — —

PTBPE7 PTBPE6 PTBPE5 PTBPE4 PTBPE3 PTBPE2 PTBPE1 PTBPE0

PTBSE7 PTBSE6 PTBSE5 PTBSE4 PTBSE3 PTBSE2 PTBSE1 PTBSE0

PTBDS7 PTBDS6 PTBDS5 PTBDS4 PTBDS3 PTBDS2 PTBDS1 PTBDS0

— — — — — — — —

0 0 0 0 PTBIF PTBACK PTBIE PTBMOD

PTBPS7 PTBPS6 PTBPS5 PTBPS4 PTBPS3 PTBPS2 PTBPS1 PTBPS0

PTBES7 PTBES6 PTBES5 PTBES4 PTBES3 PTBES2 PTBES1 PTBES0

— — — — — — — —

PTCPE7 PTCPE6 PTCPE5 PTCPE4 PTCPE3 PTCPE2 PTCPE1 PTCPE0

PTCSE7 PTCSE6 PTCSE5 PTCSE4 PTCSE3 PTCSE2 PTCSE1 PTCSE0

PTCDS7 PTCDS6 PTCDS5 PTCDS4 PTCDS3 PTCDS2 PTCDS1 PTCDS0

—

—

PTDPE7 PTDPE6 PTDPE5 PTDPE4 PTDPE3 PTDPE2 PTDPE1 PTDPE0

PTDSE7 PTDSE6 PTDSE5 PTDSE4 PTDSE3 PTDSE2 PTDSE1 PTDSE0

PTDDS7 PTDDS6 PTDDS5 PTDDS4 PTDDS3 PTDDS2 PTDDS1 PTDDS0

— — — — — — — —

0 0 0 0 PTDIF PTDACK PTDIE PTDMOD

PTDPS7 PTDPS6 PTDPS5 PTDPS4 PTDPS3 PTDPS2 PTDPS1 PTDPS0

PTDES7 PTDES6 PTDES5 PTDES4 PTDES3 PTDES2 PTDES1 PTDES0

— — — — — — — —

PTEPE7 PTEPE6 PTEPE5 PTEPE4 PTEPE3 PTEPE2 PTEPE1 PTEPE0

PTESE7 PTESE6 PTESE5 PTESE4 PTESE3 PTESE2 PTESE1 PTESE0

PTEDS7 PTEDS6 PTEDS5 PTEDS4 PTEDS3 PTEDS2 PTEDS1 PTEDS0

—

—

PTFPE7 PTFPE6 PTFPE5 PTFPE4 PTFPE3 PTFPE2 PTFPE1 PTFPE0

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

位 0

—

—

—

—

—

—

MC9S08DZ60 系列 , 第 3 版

飞思卡尔半导体公司 45

Page 30

Table 0-8. 高端页面寄存器总结 (第 1 页,共 3 页)

地址 寄存器名称 位 7

0x1869 PTFSE

0x186A PTFDS

0x186B–

0x186F

预留

0x1870 PTGPE

0x1871 PTGSE

0x1872 PTGDS

0x1873–

0x187F

预留

0x1880 CANCTL0

0x1881 CANCTL1

0x1882 CANBTR0

0x1883 CANBTR1

0x1884 CANRFLG

0x1885 CANRIER

0x1886 CANTFLG

0x1887 CANTIER

0x1888 CANTARQ

0x1889 CANTAAK

0x188A CANTBSEL

0x188B CANIDAC

0x188C

预留

0x188D CANMISC

0x188E CANRXERR

0x188F CANTXERR

0x1890 –

0x1893

0x1894 –

0x1897

0x1898 –

0x189B

0x189C–

0x189F

CANIDAR0 –

CANIDAR3

CANIDMR0 –

CANIDMR3

CANIDAR4 –

CANIDAR7

CANIDMR4 –

CANIDMR7

0x18BE CANTTSRH

0x18BF CANTTSRL

0x18C0–

0x18FF

1

该位被预留。用户必须在该位上写一个 1。如果不能这样做,可能会导致意外的行为。

预留

PTFSE7 PTFSE6 PTFSE5 PTFSE4 PTFSE3 PTFSE2 PTFSE1 PTFSE0

PTFDS7 PTFDS6 PTFDS5 PTFDS4 PTFDS3 PTFDS2 PTFDS1 PTFDS0

—

—

0 0 PTGPE5 PTGPE4 PTGPE3 PTGPE2 PTGPE1 PTGPE0

0 0 PTGSE5 PTGSE4 PTGSE3 PTGSE2 PTGSE1 PTGSE0

0 0 PTGDS5 PTGDS4 PTGDS3 PTGDS2 PTGDS1 PTGDS0

—

—

RXFRM RXACT CSWAI SYNCH TIME WUPE SLPRQ INITRQ

CANE CLKSRC LOOPB LISTEN BORM WUPM SLPAK INITAK

SJW1 SJW0 BRP5 BRP4 BRP3 BRP2 BRP1 BRP0

SAMP TSEG22 TSEG21 TSEG20 TSEG13 TSEG12 TSEG11 TSEG10

WUPIF CSCIF RSTAT1 RSTAT0 TSTAT1 TSTAT0 OVRIF RXF

WUPIE CSCIE RSTATE1 RSTATE0 TSTATE1 TSTATE0 OVRIE RXFIE

0 0 0 0 0 TXE2 TXE1 TXE0

0 0 0 0 0 TXEIE2 TXEIE1 TXEIE0

0 0 0 0 0 ABTRQ2 ABTRQ1 ABTRQ0

0 0 0 0 0 ABTAK2 ABTAK1 ABTAK0

0 0 0 0 0 TX2 TX1 TX0

0 0IDAM1IDAM00 IDHIT2 IDHIT1 IDHIT0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0BOHOLD

RXERR7 RXERR6 RXERR5 RXERR4 RXERR3 RXERR2 RXERR1 RXERR0

TXERR7 TXERR6 TXERR5 TXERR4 TXERR3 TXERR2 TXERR1 TXERR0

AC7 AC6 AC5 AC4 AC3 AC2 AC1 AC0

AM7 AM6 AM5 AM4 AM3 AM2 AM1 AM0

AC7 AC6 AC5 AC4 AC3 AC2 AC1 AC0

AM7 AM6 AM5 AM4 AM3 AM2 AM1 AM0

TSR15 TSR14 TSR13 TSR12 TSR11 TSR10 TSR9 TSR8

TSR7 TSR6 TSR5 TSR4 TSR3 TSR2 TSR1 TSR0

—

—

654321

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

位 0

—

—

—

—

—

—

MC9S08DZ60 系列 , 第 3 版

46 飞思卡尔半导体公司

Page 31

Figure 0-9 显示了接收到的及发送的缓冲器 (用于扩展的识别符映射)。这些寄存器各有不同,

具体取决于选择了标准映射还是扩展的映射。有关标准映射和扩展映射的更详尽信息请参见

Chapter 13, “Freescale Controller Area Network (S08MSCANV1)”。

Table 0-9. MSCAN 前台接收和发射缓冲器布局— 显示的为扩展映射

0x18A0 CANRIDR0

0x18A1 CANRIDR1

0x18A2 CANRIDR2

0x18A3 CANRIDR3

0x18A4

–

CANRDSR0 –

CANRDSR7

ID28 ID27 ID26 ID25 ID24 ID23 ID22 ID21

ID20 ID19 ID18 SRR

ID14 ID13 ID12 ID11 ID10 ID9 ID8 ID7

ID6 ID5 ID4 ID3 ID2 ID1 ID0 RTR

DB7DB6DB5DB4DB3DB2DB1DB0

0x18AB

0x18AC CANRDLR

0x18AD

预留

0x18AE CANRTSRH

0x18AF CANRTSRL

0x18B0 CANTIDR0

0x18B1 CANTIDR1

0x18B2 CANTIDR2

0x18B3 CANTIDR3

0x18B4

–

CANTDSR0 –

CANTDSR7

— — — — DLC3 DLC2 DLC1 DLC0

— — — — — — — —

TSR15 TSR14 TSR13 TSR12 TSR11 TSR10 TSR9 TSR8

TSR7 TSR6 TSR5 TSR4 TSR3 TSR2 TSR1 TSR0

ID10 ID9 ID8 ID7 ID6 ID5 ID4 ID3

ID2 ID1 ID0 RTR IDE — — —

— — — — — — — —

— — — — — — — —

DB7DB6DB5DB4DB3DB2DB1DB0

0x18BB

0x18BC CANTDLR

0x18BD CANTTBPR

1

SRR 和 IDE 均为 1s。

2

RTR 的位置在扩展识别符映射和标准识别符映射之间有不同。

— — — — DLC3 DLC2 DLC1 DLC0

PRIO7 PRIO6 PRIO5 PRIO4 PRIO3 PRIO2 PRIO1 PRIO0

(1 )

IDE

(1)

ID17 ID16 ID15

2

Table 0-10, 显示的非易失性 Flash 寄存器位于 Flash 中。这些寄存器包括 8 个字节的后门密钥

NVBACKKEY。该密钥可用于访问安全的内存资源。在复位事件中, Flash 中非易失性寄存器区

域的 NVPROT 和 NVOPT 内容会被转移到高端页面寄存器中相应的 FPROT 和 FOPT 工作寄存

器中,以控制安全性和块保护选项。

MC9S08DZ60 系列 , 第 3 版

飞思卡尔半导体公司 47

Page 32

Table 0-10. 非易失性寄存器总结

地址 寄存器名称 位 7

0xFFAE

0xFFAF

0xFFB0–

预留用于 FTRIM

的存储

预留用于存储

NVBACKKEY

0xFFB7

预留

0xFFB8–

0xFFBC

0xFFBD NVPROT

0xFFBE

预留

0xFFBF NVOPT

0 0 0 0 0 0 0FTRIM

—

—

EPS FPS

— — — — — — — —

KEYEN FNORED EPGMOD 0 0 0 SEC

654321

TRIM

8 字节对比密钥

—

—

—

—

—

—

—

—

—

—

—

—

位 0

—

—

如果密钥启用 (KEYEN)位为 1,那么 8 字节对比密钥可用于暂时脱离内存安全的限制。这种

密钥机制只能通过在安全内存中运行的用户代码访问。(安全密钥不能通过背景调试命令直接输

入。)这个安全密钥可通过将 KEYEN 位设为 0 来完全禁用。如果这个安全密钥被禁用,那么脱

离安全限制的唯一方式是在需要时整体擦除 Flash (通常通过背景调试接口)并确认 Flash 是空

的。为了避免在下一次复位后返回到安全模式,应该将安全位 (SEC)设置为非安全状态 (1:

0)。

MC9S08DZ60 系列 , 第 3 版

48 飞思卡尔半导体公司

Page 33

0.15 RAM

MC9S08DZ60 系列包括静态 RAM。 RAM 中 0x0100 以下的位置可以使用更高效的直接寻址模

式访问,而这一区域中的任何单一比特可以通过位操作指令 (BCLR、 BSET、 BRCLR 和

BRSET)访问。首选的方式是在查找 RAM 的这一区域中最经常被访问的程序变量。

在 MCU 处于低功耗等待、 Stop2 或 Stop3 模式时, RAM 会保留数据。加电启动时, RAM 中的

内容会未初始化。如果电源电压不会降低到 RAM 保留 (V

) 的最低值以下, RAM 数据就不会

RAM

受到复位的任何影响。

为了实现与 M68HC05 MCU 的兼容性, HCS08 会将栈指针复位为 0x00FF。在 MC9S08DZ60

系列中,最好的方法通常是将栈指针重新初始化到 RAM 顶部,以便使直接页面 RAM 可以用于

经常被访问的 RAM 变量和位可寻址程序变量。在您的复位初始化程序 (其中的 RamLast 等于

飞思卡尔半导体等同文件中 RAM 的最高地址)中包含以下两个指令序列。

LDHX #RamLast+1 ;point one past RAM

TXS ;SP<-(H:X-1)

在启用了安全性的情况下, RAM 被认为是一种安全的内存资源,不能通过 BDM 或从非安全内

存中执行代码来访问。若欲了解有关安全特性的更详尽描述, 请参见 Section 0.16.9, “Security。

0.16 Flash 和 EEPROM

MC9S08DZ60 系列器件包括 Flash 和 EEPROM 存储器。这些存储器主要设计用于保存程序和

数据。在线编程使正在运行的程序和数据可以在应用产品的最终组装完成后分别上载到 Flash 和

EEPROM 中。我们可以通过单线背景调试接口对阵列进行编程。由于擦除和编程操作不需要特

殊的电压,所以也可以通过其他软件控制的通信路径来实现应用内编程。若欲了解有关在线和应

用内编程的更详尽描述,请参见 “HCS08 系列参考手册,第 1 卷”( 飞思卡尔半导体文件编号

HCS08RMv1)。

0.16.1 特性

Flash 和 EEPROM 存储器的特性包括:

• 阵列大小 (具体阵列大小请参见 Ta bl e 0- 1 )

• Flash 分区大小:768 字节

• EEPROM 分区大小:可选择的 4 字节或 8 字节分区映射操作

• 单一电源程序和擦除

• 用于快速编程和擦除操作的命令接口

• 一般电压和温度下最多 100,000 个编程 / 擦除循环

• 灵活的块保护和向量重定向

• Flash、 EEPROM 和 RAM 的安全特性

• 突发编程功能

• 扇区擦除终止

MC9S08DZ60 系列 , 第 3 版

飞思卡尔半导体公司 49

Page 34

0.16.2 编程和擦除时间

在接受任何编程或擦除命令前,必须编写 Flash 和 EEPROM 时钟分频寄存器 (FCDIV)以将

Flash 和 EEPROM 模块的内部时钟设置为 150 kHz 到 200 kHz 之间的频率 (f

Section 0.16.11.1, “Flash 和 EEPROM 时钟分频寄存器 (FCDIV))。 这个寄存器只能写入一次,

因此这一写入操作通常是在复位初始化过程中执行的。用户必须确保在写入 FCDIV 寄存器之前

没有设置 FACCERR。命令处理器使用最终时钟 (1/f

) 的一个周期来对编程和擦除脉冲进行

FCLK

定时。命令处理器利用这些定时脉冲的一个整数来完成编程或擦除命令。

FCLK

) ( 请参见

Table 0-11 显示了编程和擦除时间。总线时钟频率和 FCDIV 决定着 FCLK 的频率 (f

FCLK 周期的时间长短为 t

(t

= 5s)。显示的编程和擦除时间包括命令状态机的开销及编程和擦除电压的启用及禁用。

FCLK

参数 FCLK 循环 FCLK = 200 kHz 时的时间

字节程序

突发程序

分区擦除

整体擦除

分区擦除终止

1

不包括开始 / 结束开销。

FCLK

= 1/f

。定时器显示为多个 FCLK 循环和一个绝对时间

FCLK

Table 0-11. 编程和擦除时间

945ms

420ms

4000 20 ms

20,000 100 ms

420ms

1

1

FCLK

)。一个

0.16.3 编程和擦除命令的执行

在开始命令执行之前, FCDIV 寄存器在任何复位和任何错误标记被清除后必须初始化。命令执

行步骤如下:

1. 将一个数据值写入到 Flash 或 EEPROM 阵列中的一个地址中。该地址和写入的数据信息

被锁定到 Flash 和 EEPROM 接口上。这一写入操作是任何命令序列中要求的第一步。对

于擦除和空白检查命令,这些数据的值并不重要。对于分区擦除命令,地址可以是将要擦

除的 Flash 或 EEPROM 分区中的任何地址。对于整体擦除和空白检查命令,地址可以是

Flash 或 EEPROM 内存中的任何地址。 Flash 和 EEPROM 擦除互相独立。

注意

在对 Flash 或 EEPROM 中的特定字节进行编程前,该字节所在的分

区必须通过整体或分区擦除操作擦除。如果对已经编程的字节中的位

进行重新编程而不首先进行擦除,可能会造成 Flash 或 EEPROM 内

存中保存的数据的错误。

2. 将想执行的命令的命令代码写入到 FCMD 中。 6 个有效的命令分别是空白检查 (空白检

查, 0x05)、字节编程 (byte program, 0x20)、突发编程 (burst program, 0x25)、

分区擦除 (分区擦除, 0x40)、整体擦除 1 (mass erase1 , 0x41)和分区擦除终止

(分区擦除 abort, 0x47)。命令代码被锁定到命令缓冲器中。

3. 将一个 1 写入到 FSTAT 中的 FCBEF 位上,以清除 FCBEF 并发起命令 (包括其地址和

数据信息)。

1. 整体擦除只能在 Flash 块完全不受保护的情况下进行。

MC9S08DZ60 系列 , 第 3 版

50 飞思卡尔半导体公司

Page 35

通过在写入到内存阵列中之后、写入会清除 FCBEF 并发起完整命令的 1 之前的任何时候

开始

将命令写到 FCMD 中

否

是

FPVIOL 还是

将 1 写到 FCBEF 中

发起命令

并清除 FCBEF

(2)

1

0

FCCF?

错误退出

完成

(2)

在检查 FCBEF 或 FCCF 之间

需要等待至少四个总线周期

0

FACCERR?

消除错误

FACCERR?

写入到 FCDIV

(1)

(1)

复位只需要一次

编程和擦除流程

写入 FLASH 或 EEPROM 中以缓

冲地址和数据

向 FCBEF 中写入一个 “0”,您可以以手工方式终止部分命令顺序。以这种方式终止一

个命令会设置 FACCERR 访问错误标记,而这个标记必须在开始一个新命令之前清除

掉。

您必须采用受到严格监控的流程,否则命令将不会被接受。这样就可以最大限度地降低无

意中修改内存内容的可能性。命令完整标记 (FCCF)显示一条命令是否完整。要启动命

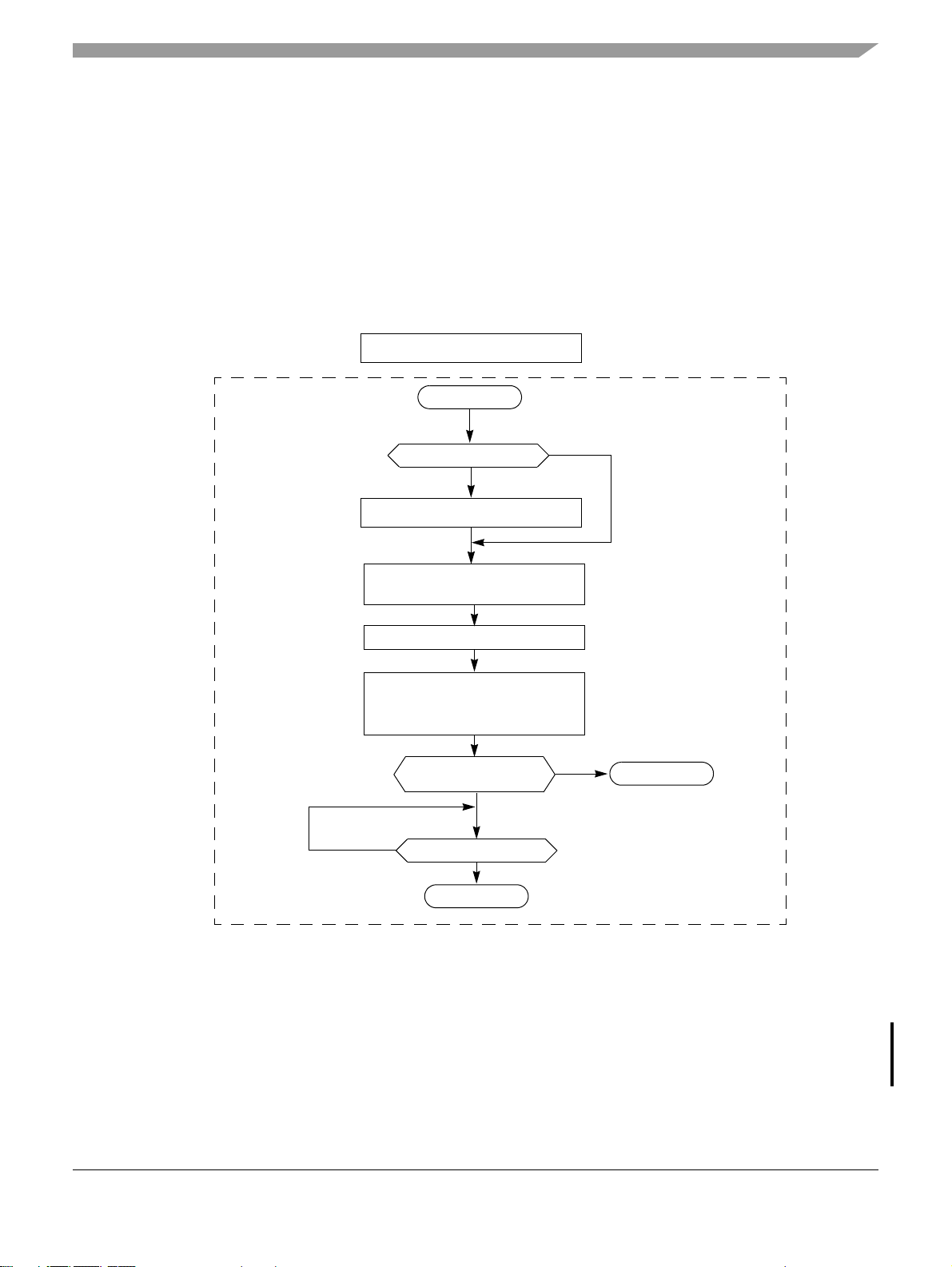

令,您必须通过清除 FCBEF 来是命令序列完整。 Figure 0-8 是一个显示如何执行除突发

编程和分区擦除终止以外的所有命令的流程图。

4. 等待 FSTAT 中的 FCCF 位被设置。只要 FCCF= 1,就说明操作成功完成。

Figure 0-8. 编程和擦除流程图

0.16.4 突发编程执行

突发编程命令用于在比标准编程命令更少的时间内对数据的连续字节进行编程。这是因为 Flash

阵列的高电压在编程操作之间不需要断开。通常情况下,在发出编程或擦除命令后,必须启用与

Flash 相关的一个内部电荷泵以便为阵列提供高电压。命令的执行完成后,该电荷泵会被关闭。

飞思卡尔半导体公司 51

MC9S08DZ60 系列 , 第 3 版

Page 36

发出突发编程命令后,电荷泵在以下两种条件下会被开启而且在突发编程操作完成后将保持开启

状态:

• 下一个突发编程命令序列在设置 FCCF 位之前已开始。

• 下一个顺序地址从所编程的当前字节所在的相同突发块中选择了一个字节。该 Flash 中的

突发块包括 32 个字节。新的突发块在每个 32 字节地址的边界开始。

突发模式下正进行编程的一系列连续字节的第一个字节将需要与标准模式下编程的字节相同的编

程时间。如果达到上述两个条件,后面的字节将在突发编程时间内编程。如果下一个顺序地址是

新的一行的开始,那么该字节的编程时间将是标准时间而不是突发时间。这是因为到阵列的高电

压必须断开然后重新开启。如果在当前的命令完成前队列中没有任何新的突发命令,那么电荷泵

将关闭,高电压将从阵列上断开。

Figure 0-9 显示了执行突发编程操作的一个流程图。

MC9S08DZ60 系列 , 第 3 版

52 飞思卡尔半导体公司

Page 37

1

0

FCBEF?

开始

写入 Flash 中

以缓冲地址和数据

将命令写到 FCMD 中

否

是

FPVIOL 还是

将 1 写到 FCBEF 中

以发起命令

并清除 FCBEF

(2)

NO

是

NEW BURST COMMAND?

1

0

FCCF?

错误退出

完成

(2)

在检查 FCBEF 或 FCCF 之间需

要等待至少 4 个总线周期

。

1

0

FACCERR?

清除错误

FACCERR?

写入到 FCDIV

(1)

(1)

复位后只需要一次。

突发编程

流程

Figure 0-9. 突发编程流程图

MC9S08DZ60 系列 , 第 3 版

飞思卡尔半导体公司 53

Page 38

开始

将 0x47 写入到 FCMD 中

将 1 写到 FCBEF 中

以发起命令

并清除 FCBEF

(2)

1

0

FCCF?

分区擦除终止

(2)

在检查 FCBEF 或 FCCF 之间需要

0

1

FCCF?

写入 Flash 中

以缓冲地址和数据

FACCERR?

0

1

分区擦除完成

等待至少 4 个总线周期。

分区擦除流程图

0.16.5 分区擦除终止

分区擦除终止操作将终止正在进行的分区擦除操作,以便使其他分区可用于读取和编程操作而不

需要等待分区擦除完成。

分区擦除终止命令写入顺序如下:

1. 写入任何 Flash 或 EEPROM 地址以开始分区擦除终止命令的命令写入顺序。写入的地址

和数据将被忽略。

2. 向 FCMD 寄存器中写入分区擦除终止命令 0x47。

3. 将一个 1 写入到 FCBEF 中来发起分区擦除终止命令以清除 FSTAT 寄存器中的 FCBEF 标

记。

如果分区擦除终止命令的发出导致了正在进行的分区擦除操作的提前终止, FACCERR 将在操

作完成 (由设置的 FCCF 标记显示)后马上设置。 设置 FACCERR 标记的目的是告诉用户

Flash 分区不能完全擦除,在这个分区内对任何位置进行编程前需要发出一个新的分区擦除命

令。

如果发出了分区擦除终止命令但正在进行的分区擦除操作正常完成了,那么在该操作完成 (由

设置的 FCCF 标记显示)后将不会设置 FACCERR 标记。因此,如果在分区擦除终止命令完成

后没有设置 FACCERR 标记,那么发出终止命令时正在擦除的分区将完全擦除。

Figure 0-10 显示了执行分区擦除终止操作的流程图。

54 飞思卡尔半导体公司

Figure 0-10. 分区擦除终止流程图

MC9S08DZ60 系列 , 第 3 版

Page 39

注意

FCBEF 标记在发出分区擦除终止命令后不会设置。如果在一个分区

擦除终止操作正在进行时开始一个新的命令写入顺序,那么 FSTAT

寄存器中将设置 FACCERR 标记 。 ACCERR 标记 (如果设置了的

话)被清除后,新的命令写入顺序可以开始。

注意

分区擦除终止命令应谨慎使用,因为终止的分区擦除操作会认为为一

个完整的编程或擦除周期。

0.16.6 访问错误

在命令执行协议被违反时就会出现访问错误。

下面所列的任何操作都会导致 FSTAT 中设置访问错误标记 (FACCERR)。 在处理任何命令前,

必须通过将一个 1 写入到 FSTAT 中的 FACCERR 来清除 FACCERR 。

• 在通过写入到 FCDIV 寄存器中设置内部 Flash 和 EEPROM 时钟频率前写入 Flash 地址。

• 在没有设置 FCBEF 的情况下写入 Flash 地址。(命令缓冲器清空之前新的命令不能开

始。)

• 发出前一个命令之前第 2 次写入 Flash 地址。(每个命令只能向 Flash 中写入一次。)

• 发出前一个命令之前第 2 次写入 FCMD。(每个命令只能向 FCMD 中写入一次。)

• 写入 Flash 地址之后写入 FCMD 以外的任何 Flash 控制寄存器。

• 向FCMD中写入6个允许的代码(0x05, 0x20, 0x25, 0x40, 0x41, or 0x47) 以外的任何命令代

码。

• 向FCMD中写入命令之后写入 FSTAT以外的任何Flash控制寄存器(以清除FCBEF并发出

命令)。

• MCU 在某个编程或擦除命令正在进行时进入停止模式。(命令被终止。)

• MCU 受到安全保护时通过背景调试命令写入字节编程、突发编程、分区擦除或分区擦除

终止命令代码 (0x20, 0x25, 0x40, or 0x47)。 背景调试控制器只能在 MCU 受到安全保护时

才能执行空白检查和整体擦除命令。)

• 将 0 写入到 FCBEF 中以取消部分命令。

MC9S08DZ60 系列 , 第 3 版

飞思卡尔半导体公司 55

Page 40

0.16.7 块保护

块保护特性可以防止 Flash 或 EEPROM 的受保护区域发生编程或擦除修改。块保护通过 Flash

and EEPROM 保护寄存器 (FPROT) 进行控制。 EPS 位决定 EEPROM 的受保护区域而 FPS 位

决定 Flash 的受保护区域。 详细说明请参见 Section 0.16.11.4, “Flash 和 EEPROM 保护寄存器

(FPROT and NVPROT).”

从复位操作中退出后, FPROT 中会上载 NVPROT 位置 (在 Flash 的非易失性寄存器块中)的

内容。 任何试图减少受保护区域大小的 FPROT 写入操作都会被忽略。 由于 NVPROT 在 Flash

的最后一个分区中,所以如果任何数量的内存受到保护, NVPROT 自身也会受到保护,不会受

到任何应用软件的影响 (不管是有意的还是无意的)。 FPROT 可通过背景调试命令写入,这为

擦除和重新编程受保护的 Flash 提供了一种有效的方法。

块保护的一个用途是为 bootloader 程序保护 Flash 中的一个区域。这个 bootloader 程序可以调

用 Flash 外的常用程序 (可用于分区擦除 Flash 的其余部分并进行重新编程)。 bootloader 可以

受到很好的保护,即使在擦除和编程操作中 MCU 电源中断。

0.16.8 向量重定向

在 Flash 受到块保护的同时,复位和中断向量也将受到有效保护。向量重定向使用户可以修改中

断向量信息而不必影响对 bootloader 和复位向量空间的保护。向量重定向通过在地址 0xFFBF

到 0 上的 NVOPT 寄存器中编程 FNORED 位来启用。要使重定向正常进行, Flash 中的至少一

些部分必须通过对地址 0xFFBD 上的 NVPROT 寄存器进行编程来进行块保护。所有中断向量

(内存位置为 0xFFC0–0xFFFD)都被重定向,虽然复位向量 (0xFFFE:0xFFFF)不是。

例如,如果 Flash 的 1536 个字节受到保护,那么受保护的地址区域为从 0xFA00 到 0xFFFF。

中断向量 (0xFFC0–0xFFFD) 被重定向到位置 0xF9C0–0xF9FD。如果启用了向量重定向并发生

了中断,那么位置 0xF9E0:0xF9E1 上的值被用于向量而不是位置 0xFFE0:0xFFE1 上的值。这

样,用户就可以利用新的程序代码对 Flash 的未保护部分进行重新编程,增加新的中断向量值,

同时保留受保护的区域 (这包括不发生任何变化的缺省向量)。

0.16.9 安全性

MC9S08DZ60 Series 包含有用于防止非法访问 Flash、 EEPROM 和 RAM 存储器的内容的电

路。启用了安全性之后, Flash、 EEPROM 和 RAM 被看作是安全的资源。直接页面寄存器、高

端页面寄存器和背景调试控制器被看作是不安全的资源。安全存储器中执行的程序可以正常访问

MCU 位置和资源。通过不安全存储器空间内运行的程序或通过背景调试接口访问安全存储器位

置的任何尝试都将被阻止 (写入操作被忽略,而读取操作则全部返回 0)。

安全性的启用和关闭根据 FOPT 寄存器中的两个寄存器位 (SEC[1:0]) 的状态决定。在复位过程

中,非易失性位置 NVOPT 的内容从 Flash 中拷贝到高端页面寄存器空间内的工作 FOPT 寄存器

上。用户可以通过编程 NVOPT 位置来启用安全性。这一操作可以在对 Flash 进行编程的同时进

行。 1:0 状态会关闭安全性;而另外 3 种组合会启用安全性。请注意,擦除状态 (1:1) 会使 MCU

处于安全状态。在开发过程中,不管 Flash 什么时候被擦除,立即将 NVOPT 中的 SEC0 设置为

0 以便使 SEC = 1:0 是一种有效的方法。这将使 MCU 在后来的复位完成后继续处于不安全状

态。

MC9S08DZ60 系列 , 第 3 版

56 飞思卡尔半导体公司

Page 41

MCU 处于安全状态时不能启用片上调试模块。您可以为后台存储器访问命令使用独立的背景调

试控制器,但 MCU 不能进入主动背景模式,除非您在复位的上升边将 BKGD 保持在较低位置。

用户可以选择通过一个 8 字节后门安全密钥来允许或不允许安全解锁机制。如果 NVOPT/FOPT

中的非易失性 KEYEN 位为 0,那么说明后门密钥被禁用,在没有完全擦除所有 Flash 位置的情

况下不能启用安全性。如果 KEYEN 为 1,那么安全的用户程序可以通过以下方式来暂时关闭安

全性:

1. 向 FCNFG 寄存器中的 KEYACC 写入 1。这将使 Flash 模块将后门对比密钥位置

(NVBACKKEY through NVBACKKEY+7) 的写入解释为将与密钥进行对比的值而不是

Flash 编程或擦除命令的第一步。

2. 将用户输入的密钥值写入到位置 NVBACKKEY 到 NVBACKKEY+7 上。这些写入操作必

须按顺序进行,以 NVBACKKEY 值开始,以 NVBACKKEY+7 值结束。这些写入操作中

必须使用 STHX,因为这些写入不能在相邻的总线循环上完成。用户软件一般通过通信接

口 (如串行 I/O)从 MCU 系统外部获取密钥代码。

3. 向 FCNFG 寄存器中的 KEYACC 写入 0。如果写入的 8 字节密钥与 Flash 位置上保存的

密钥相匹配,那么 SEC 位被自动修改为 1:0,同时安全性将关闭,直到下一个复位。

安全密钥只能从安全存储器 (RAM、 EEPROM 或 Flash)中写入,因此在没有安全的用户程序

协作的情况下不能通过后台命令输入。

后门对比密钥 (NVBACKKEY through NVBACKKEY+7) 保存在非易失性寄存器空间内的 Flash

位置上,因此用户可以准确地编程这些位置,就象编程任何其他 Flash 位置一样。非易失性寄存

器与复位和中断向量在 Flash 的同一个 768 字节块中,因此对这一空间进行块保护同时也可以

保护后门对比密钥。块保护不能从用户应用程序上修改,因此,如果向量空间受到块保护,后门

安全密钥机制就不能永久性地修改块保护、安全设置或后门密钥。

通过以下步骤,您可以通过背景调试接口始终关闭安全性:

1. 通过写入 FPROT 来禁用任何块保护。 FPROT 只能通过背景调试命令写入而不能从应用

软件上写入。

2. 在必要时整体擦除 Flash。

3. 对 Flash 进行空白检查。如果 Flash 内完全擦除,那么在下一复位前安全性一直是关闭

的。为了避免在下一次复位后返回到安全模式,对 NVOPT 进行编程以便使 SEC = 1:0。

0.16.10 EEPROM 映射

只有一半 EEPRO 在存储器映象中。 FCNFG 寄存器中的 EPGSEL 位选择阵列的哪一半可从前

台访问,而另一半不能从后台访问。有两种映射模式选项可选择用于配置 8 字节 EEPROM 分

区:4 字节模式和 8 字节模式。每种模式都通过 FOPT 寄存器中的 EPGMOD 位选择。

在 4 字节分区模式 (EPGMOD = 0) 中,每个 8 个字节分区被分成两部分,4 个字节在前台,4 个

在后台,但都在相同的地址上。 EPGSEL 位选择哪 4 个字节可以访问。在分区擦除过程中,整

个 8 字节分区 (前台的 4 个字节和后台的 4 个字节)都被擦除。

在 8 字节分区模式 (EPGMOD = 1) 中,每个 8 字节分区在一个页面上。 EPGSEL 位选择哪些分

区在后台。在分区擦除过程中,前台的整个 8 字节分区会被擦除。

MC9S08DZ60 系列 , 第 3 版

飞思卡尔半导体公司 57

Page 42

0.16.11 Flash 和 EEPROM 寄存器及控制位

Flash 和 EEPROM 模块在高端页面寄存器空间内有 7 个 8 位寄存器,在 Flash 的非易失性寄存

器空间内有 3 个位置。这些位置中的两个在复位时被拷贝到两个相应的高端页面控制寄存器中。

Flash 中还有一个 8 字节对比密钥。请参见 Tab le 0 -8 和 Table 0-10 来了解所有 Flash 和

EEPROM 寄存器的绝对地址分配情况。这一部分用名称指代寄存器和控制位。通常飞思卡尔半

导体提供将这些名称转换为相应的绝对地址的变量定义或头文件。

0.16.11.1 Flash 和 EEPROM 时钟分频寄存器 (FCDIV)

该寄存器的第 7 位是一个只读标记。 6:0 位可以在任何时候读取但只能写入一次。在开始任何擦

除或编程操作之前,写入该寄存器以将非易失性内存系统的时钟频率设置在可接受的限度内。

76543210

RDIVLD

W

Reset00000000

PRDIV8 DIV

= 未实现或被预留

Figure 0-11. Flash 和 EEPROM 时钟分频寄存器 (FCDIV)

Table 0-12. FCDIV 寄存器字段描述

字段 描述

7

DIVLD

6

PRDIV8

5:0

DIV

Divisor Loaded Status Flag — 当置 1 时,这个只读状态标记指出 FCDIV 寄存器自从复位后已有写入。复位会

清除该位而且第一次写入该寄存器的操作将导致该位被置 1,不管数据是不是已写入。

0FCDIV 自复位后没有写入; Flash 和 EEPROM 的擦除和编程操作被禁止。

1FCDIV自复位后已写入; Flash 和 EEPROM 的擦除和编程操作已开启。

预分频 (分频) Flash 和 EEPROM 时钟除以 8 (该位只设置一次。)

0 Flash 和 EEPROM 时钟分频器的时钟输入为总线速率时钟。

1 Flash 和 EEPROM 时钟分频器的时钟输入为总线速率时钟除以 8。

Divisor for Flash 和 EEPROM 时钟分频器 — 这些位只写入一次。 Flash 和 EEPROM 时钟分频器用 6 位 DIV 字

段中的值除总线速率时钟 (如果 PRDIV8 = 1,则用总线速率时钟除以 8)再加 1。最后的内部 Flash 和

EEPROM 时钟的频率必须在 200 kHz 到 150 kHz 的范围内,这样才能使 Flash 和 EEPROM 正常运行。 编程 /

擦除定时脉冲为这个内部 Flash 和 EEPROM 时钟的一个循环,这相当于 5ms 到 6.7 ms。 自动编程逻辑使用这

些脉冲的整数来完成擦除或编程操作。请参见等式 Equation 0-1 和 Equation 0-2

if PRDIV8 = 0 — f

if PRDIV8 = 1 — f

FCLK

FCLK

= f

= f

÷ (DIV + 1) Eqn. 0-1

Bus

÷ (8 × (DIV + 1)) Eqn. 0-2

Bus

Table 0-13 显示了选择的总线频率上 PRDIV8 和 DIV 的相应值。

。

MC9S08DZ60 系列 , 第 3 版

58 飞思卡尔半导体公司

Page 43

Table 0-13. Flash 和 EEPROM 时钟分频器设置

f

Bus

20 MHz 1 12 192.3 kHz 5.2 ms

10 MHz 0 49 200 kHz 5 ms

8 MHz 0 39 200 kHz 5 ms

4 MHz 0 19 200 kHz 5 ms

2 MHz 0 9 200 kHz 5 ms

1 MHz 0 4 200 kHz 5 ms

200 kHz 0 0 200 kHz 5 ms

150 kHz 0 0 150 kHz 6.7 ms

PRDIV8

( 二进制 )

DIV

( 十进制 )

f

FCLK

编程 / 擦除定时脉冲

( 最少 5 ms , 最多 6.7 ms )

0.16.11.2 Flash 和 EEPROM 选项寄存器 (FOPT 和 NVOPT)

在复位过程中,非易失性位置 NVOPT 上的内容从 Flash 中拷贝到 FOPT 中。若想修改这个寄存

器中的值,象平时一样对 Flash 中的 NVOPT 位置进行擦除和重新编程,然后发出新的 MCU 复

位命令。

76543210

R KEYEN FNORED EPGMOD 0 0 0 SEC

W

Reset F F F 0 0 0 F F

= 未实现或被预留 F = 在复位期间从非易失性位置 NVOPT 上上载

Figure 0-12. Flash 和 EEPROM 选项寄存器 (FOPT)

Table 0-14. FOPT 寄存器字段描述

字段 描述

7

KEYEN

6

FNORED

后门密钥机制启动 — 该位设置为 0 时,后门密钥机制不能用于关闭安全性。后门密钥机制只能从用户 (受保

护)固件上访问。 BDM 命令不能用于写入可能会解锁后门密钥的密钥对比值。若欲了解有关后门密钥机制的更

详尽信息,请参见 Section 0.16.9, “Security ”。

0 不允许后门密钥访问。

1 如果用户固件写入一个与非易失性后门密钥 (按顺序为 NVBACKKEY 到 NVBACKKEY+7)相匹配的 8 字节

值,安全性会暂时关闭,直到下一次 MCU 复位。

向量重定向禁用 — 该位为 1 时向量重定向被禁用。

0 向量重定向启用。

1 向量重定向禁用。

MC9S08DZ60 系列 , 第 3 版

飞思卡尔半导体公司 59

Page 44

Table 0-14. FOPT 寄存器字段描述

字段 描述

5

EPGMOD

EEPROM 分区模式 — 该位为 0 时,每个分区分为两个页面 (4 字节模式)。该位为 1 时,每个分区在一个页面

中(8 字节模式)。

0 每个 EEPROM 分区的一半在页面 0 中而另一半在页面 1 中。

1 每个分区在一个页面中。

1:0

SEC

安全状态代码 — 这个 2 位字段决定 MCU 的安全状态 MCU,如 Ta ble 0 -1 5 所示。 MCU 处于安全状态时,

RAM、 EEPROM 和 Flash 中的内容不能通过指令从不安全的源 (包括背景调试接口)上访问。后门密钥被成功

输入或对 Flash 进行了成功的空白检查后, SEC 将变为 1:0 。若欲了解有关安全性的更详尽信息,请参见

Section 0.16.9, “Security ”。

Table 0-15. Security States

SEC[1:0]

0:0

0:1

1:0

1:1

1

后门密钥被成功输入或对Flash进行了成功的空白检查后,

1

描述

安全

安全

不安全

安全

SEC 将变为 1:0。

0.16.11.3 Flash 和 EEPROM 配置寄存器 (FCNFG)

76543210

R0

W

EPGSEL KEYACC Reserved

1

0001

Reset00010001

= 未实现或被预留

Figure 0-13. Flash Configuration Register (FCNFG)

1

用户必须在该位上写入一个 1。如果不这样,可能会导致意外的行为。

Table 0-16. FCNFG 寄存器字段描述

字段 描述

6

EPGSEL

5

KEYACC

60 飞思卡尔半导体公司

页面选择 — 该位选择存储器映象中的哪个 EEPROM 页面可以访问。

0 页面 0 在存储器映象的前台。页面 1 在后台,而且不能访问。

1 页面 1 在存储器映象的前台。页面 0 在后台,而且不能访问。

启用访问密钥的写入 — 该位启用后门对比密钥的写入。若欲了解有关后门密钥机制的更详尽信息,请参见

Section 0.16.9, “Security ” 。

0 写入 0xFFB0–0xFFB7 被解释为 Flash 编程或擦除命令的开始。

1 写入 NVBACKKEY (0xFFB0–0xFFB7) 解释为对比密钥写入。

MC9S08DZ60 系列 , 第 3 版

Page 45

0.16.11.4 Flash 和 EEPROM 保护寄存器 (FPROT and NVPROT)

FPROT 寄存器定义哪些 Flash 和 EEPROM 分区不受编程和擦除操作的影响。

在复位顺序中, FPROT 寄存器从非易失性位置 NVPROT 中上载。若想改变复位序列中将上载

的保护,包含 NVPROT 的分区必须不受保护并被擦除,然后才可以对 NVPROT 进行重新编程。

FPROT 位任何时候都可以读取,但只能在受保护区域的范围增加时才可以写入。任何企图缩小

受保护内存的 FPROT 写入操作都会被忽略。

尝试修改任何受保护区域的数据将导致保护违反错误, FSTAT 寄存器中将设置 FPVIOL 标记。

如果有任何一个分区被保护, 就不能进行整体擦除。

76543210

R

W

EPS

1

FPS

1

Reset

1

后台命令可用于修改 FPROT 中的这些位的内容。

本寄存器在复位过程中从非易失性位置 NVPROT 中上载。

Figure 0-14. Flash 和 EEPROM 保护寄存器 (FPROT)

Table 0-17. FPROT 寄存器字段描述

字段 描述

7:6

EPS

5:0

FPS

EEPROM 保护选择位 — 这个 2 位字段决定不能被擦除或编程的受保护 EEPROM 位置。参见 Ta ble 0 -1 8 .

Flash 保护选择位 — 这个 6 位字段决定不能被擦除或编程的受保护 Flash 位置。参见 Ta bl e 0 -19 .

Table 0-18. EEPROM 块保护

EPS

0x3 N/A 0 0

0x2 0x17F0 - 0x17FF 32 4

0x1 0x17E0 - 0x17FF 64 8

0x0 0x17C0–0x17FF 128 16

受保护的地址域 受保护的内存大小 (字节) 受保护的扇区数量

Table 0-19. Flash 块保护

FPS

0x3F N/A 0 0

0x3E 0xFA00–0xFFFF 1.5K 2

0x3D 0xF400–0xFFFF 3K 4

0x3C 0xEE00–0xFFFF 4.5K 6

0x3B 0xE800–0xFFFF 6K 8

... ... ... ...

飞思卡尔半导体公司 61

受保护的地址域 受保护的内存大小 (字节) 受保护的扇区数量

MC9S08DZ60 系列 , 第 3 版

Page 46

Table 0-19. Flash 块保护 (continued)

FPS

受保护的地址域 受保护的内存大小 (字节) 受保护的扇区数量

0x37 0xD000–0xFFFF 12K 16

0x36 0xCA00–0xFFFF 13.5K 18

0x35 0xC400–0xFFFF 15K 20

0x34 0xBE00–0xFFFF 16.5K 22

... ... ... ...

0x2C 0x8E00–0xFFFF 28.5K 38

0x2B 0x8800–0xFFFF 30K 40

0x2A 0x8200–0xFFFF 31.5K 42

0x29 0x7C00–0xFFFF 33K 44

... ... ... ...

0x22 0x5200–0xFFFF 43.5K 58

0x21 0x4C00–0xFFFF 45K 60

0x20 0x4600–0xFFFF 46.5K 62

0x19 0x4000–0xFFFF 48K 64

... ... ... ...

0x1B 0x2800–0xFFFF 54K 72

0x1A 0x2200–0xFFFF 55.5K 74

0x19 0x1C00–0xFFFF 57K 76

0x18–0x00 0x0000–0xFFFF 64K 86

MC9S08DZ60 系列 , 第 3 版

62 飞思卡尔半导体公司

Page 47

0.16.11.5 Flash 和 EEPROM 状态寄存器 (FSTAT)

76543210

R

FCBEF

W

FCCF

FPVIOL FACCERR

0FBLANK0 0

复位

11000000

= 未实现或被预留

Figure 0-15. Flash 和 EEPROM 状态寄存器 (FSTAT)

Table 0-20. FSTAT 寄存器字段描述

字段 描述

7

FCBEF

6

FCCF

5

FPVIOL

4

FACCERR

2

FBLANK

命令缓冲器空标记 — FCBEF 位用于发出命令。它还指示命令缓冲器是空的,因此可以在执行突发编程时执行新

的命令顺序。 FCBEF 位通过在其中写入 1 或一个突发编程命令被发送到阵列中以进行编程时清除。只有突发编

程命令可以被缓冲。

0 命令缓冲器满 (没有准备好缓冲额外的命令)。

1 新的突发编程命令可以写入到命令缓冲器中。

命令完成标记 — FCCF 在命令缓冲器变空而且没有处理任何命令时自动设置。 FCCF 在开始执行一个新命令时

自动清除 (通过将 1 写到 FCBEF 中以登记一个命令)。 向 FCCF 写入内容没有任何意义或效果。

0 命令正在执行过程中。

1 所有命令都已完成。

保护规则违反标记 — FPVIOL 在发出试图擦除或编程受保护块中的一个位置的命令后自动设置 (错误的命令会

被忽略)。 FPVIOL 通过向 FPVIOL 中写入 1 来清除。

0 无保护规则违反。

1 有人尝试擦除或编程一个受保护的位置。

访问错误标记 — FACCERR 在以下情况下自动设置:正确的命令顺序没有严格遵守 (错误的命令将被忽略),

FCDIV 寄存器初始化之前尝试进行编程或擦除操作,或在命令正在执行时 MCU 进入停止模式。若欲了解会被

认为是访问错误的具体操作的更详尽信息,请参见 Section 0.16.6, “Access Errors.” FACCERR 通过向

FACCERR 中写入一个 1 来清除。向 FACCERR 中写入 0没有任何意义或效果。

0 没有访问错误。

1 发生了访问错误。

验证为全空 (被擦除)标记 — FBLANK 在空白检查命令完成后自动设置 (如果整个 Flash 或 EEPROM 阵列被

确认已擦除)。 FBLANK 通过清除 FCBEF 以写入新的有效命令来清除。向 FBLANK 中写入没有任何意义或效

果。

0 在空白检查命令执行完成而且 FCCF = 1 的情况下,

除。

1 在空白检查命令执行完成而且 FCCF = 1 的情况下, FBLANK = 1 表示 Flash 或 EEPROM 阵列已完全擦除

(全部为 0xFFFF)。

FBLANK = 0 表示 Flash 或 EEPROM 阵列未被完全擦

MC9S08DZ60 系列 , 第 3 版

飞思卡尔半导体公司 63

Page 48

0.16.11.6 Flash 和 EEPROM 命令寄存器 (FCMD)

如 Table 0-21 所示,正常用户模式下只能识别 6 种命令代码。所有其他命令代码都是非法的,

会生成访问错误。 请参见 Section 0.16.3, “ 编程和擦除命令的执行 ,” 来了解对 Flash 和 EEPROM

编程及擦除操作的详细描述。

76543210

R00000000

WFCMD

Reset00000000

Figure 0-16. Flash 和 EEPROM 命令寄存器 (FCMD)

Table 0-21. Flash 和 EEPROM 命令

命令

空白检查

字节编程

突发编程

分区擦除

整体擦除

分区擦除终止

FCMD

0x05 mBlank

0x20 mByteProg

0x25 mBurstProg

0x40 mSectorErase

0x41 mMassErase

0x47 mEraseAbort

等同文件标签

进行整体擦除操作后没有必要再执行空白检查命令。空白检查只是安全解锁机制的一部分。

第五章

复位、中断和系统总控制

0.17 介绍

本小节详细介绍了 MC9S08DZ60 Series 的基本复位和中断机制,以及它们的各种源。外围模块

的有些中断源在本产品说明的其他章节中进行了更详细地讨论。本节收集了所有复位和中断源的

基本报文,以便参考。而有些复位和中断源,包括计算机正常操作 (COP)的看门狗,并不是

有其各自章节的片上外围系统的一部分。

0.18 特性

复位和中断功能包括:

• 多源复位,实现灵活的系统配置和可靠操作;

• 复位状态寄存器 (SRS) ,显示最新的复位源;

• 各个模块的单独中断向量 (减少轮询开销),参见 Table 0-22 ;

MC9S08DZ60 系列 , 第 3 版

64 飞思卡尔半导体公司

Page 49

0.19 MCU 复位

复位 MCU 提供了一条从已知初始条件启动处理的途径。复位期间,大部分控制和状态寄存器被

迫使用初始值,并从复位向量 (0xFFFE:0xFFFF) 上载程序计数器。片上外围模块被禁止, I/O 管

脚初始配置为上拉器件被禁止的通用高阻抗输入。条件码寄存器 (CCR) 中的 I 位被设置用来拦

截可隐藏中断,以便用户程序有机会对堆栈指针 (SP) 和系统控制设置进行初始化 (如需了解中

断 (I) 位的相关信息,请参见 CPU 章节)。 SP 在复位时强制设为 0x00FF。

MC9S08DZ60 Series 系列有 8 个用于复位的源:

• 加电复位 (POR)

• 外部管脚复位 (PIN)

• 计算机正常操作 (COP) 定时器

• 非法操作码检测 (ILOP)

• 非法地址检测 (ILAD)

• 低电压检测 (LVD)

• 时钟丢失 (LOC)

• 背景调试强制复位 (BDFR)

上述复位源 (背景调试强制复位除外)在系统复位状态寄存器 (SRS) 中都有一个相关位。

0.20 计算机正常操作 (COP) 看门狗

当系统软件不能预期实施时, COP 看门狗用来强制进行系统复位。为了防止从 COP 定时器

(当 COP 定时器被使能时)进行系统复位,应用软件必须定期复位应用程序。如果应用在到期

前未能复位 COP 计数器,这时会生成一个系统复位,强迫系统回到已知起点。

每次复位后, COP 看门狗都会被使能 (更多信息请参见 Section 0.24.4, “ 系统选项寄存器 1

(SOPT1),” )。如果应用中没有使用 COP 门狗,可以通过清除 SOPT1 的 COPT 位进行禁止。

COP 在选定的超时期间,通过把 0x55 and 0xAA (按此顺序)写入 SRS 地址复位 COP 计数

器。写入不会对只读 SRS 中的数据造成影响。一旦写入顺序确定, COP 超时时段就会重启。如

果程序在超时时段内未能完成该操作, MCU 将复位。此外,如果向 SRS 写入了非 0x55 或

0xAA 外的其他值, MCU 也会被立即复位。

SOPT2 中的 COPCLKS 位 (更多信息请参见 Section 0.24.5, “ 系统选项寄存器 2 (SOPT2),” 选

择供 COP 定时器使用的时钟源。 时钟源选项可以是总线时钟或 1-kHz 内部时钟源。对任意一个

时钟源来说,都有 3 个由 SOPT1 中的 COPT 控制的相关超时。 Table 0-27 概括地介绍了

COPCLKS 和 COPT 位的控制功能。 COP 看门狗默认为 1-kHz 时钟源和最长超时 (210周期)

的操作。

当选定了总线时钟源后,在 SOPT2 寄存器中设置 COPW 可以实现窗口化 COP 操作。在该模

式中,写入 SRS 寄存器来清除 COP 定时器必须发生在所选超时时段的后 25% 的时间内。提前

写入会立即复位 MCU。当选择 1-kHz 时钟源时,窗口化 COP 操作不可用。

首次写入 SOPT1 和 SOPT2 寄存器及任意一次系统复位后, COP 计数器被初始化。 SOPT1 和

SOPT2 的后续写入则不会对 COP 操作产生影响。即使应用使用 COPT、 COPCLKS 和 COPW

MC9S08DZ60 系列 , 第 3 版

飞思卡尔半导体公司 65

Page 50

位的默认复位设置,用户也应该在复位初始化过程中写入 write-once (一次写入) SOPT1 和

SOPT2 寄存器上,以便在该设置中锁定。如果应用丢失,这样可以防止意外修改。

向服务 (清除) COP 计数器的 SRS 写入不能在中断服务程序 (ISR)中进行,因为即使是在

主应用失败的情况下,仍然可以定期实施 ISR。

如果选择了总线时钟源,当 MCU 处于背景调试模式或者系统处于停止模式时, COP 计数器不

会增量。当 MCU 退出背景调试模式或停止模式时, COP 计数器会重新开始计数。

如果选择 1-kHz 时钟源,那么一旦进入背景调试模式或停止模式时, COP 计数器就会被重新初

始化为 0,并在退出背景调试模式或停止模式时会从 0 开始计数。

0.21 中断

中断提供了一个保存当前 CPU 状态和寄存器、实施中断服务程序 (ISR),然后恢复 CPU 状态的

方法,这样处理可以从中断前的位置重新开始。与软件中断 (SWI)不同 (SWI 是程序指令)

的是,中断是由诸如 IRQ 管脚上的边沿或定时器溢出事件这样的硬件事件造成的。调试模块也

可以在特定环境下生成 SWI。

如果事件发生在使能中断源内,将会设置相关的只读状态标记。但 CPU 不会响应,除非使能中

断的本地中断使能是 1 ; CCR 中的 I 位是 0,允许中断。 CCR 中的全球中断屏蔽 (I 位)在复

位后首次设置,有可能阻止所有屏蔽中断源。在清除 I 位之前,用户程序初始化堆栈指针,实施

其他系统设置,以便允许 CPU 响应中断。

当 CPU 接收到符合条件的中断请求时,它会在响应中断前先完成当前指令。中断顺序与 SWI 指

令的逐周期顺序相同,这个顺序是:

• 在堆栈上保存 CPU 寄存器;

• 在 CCR 中设置 I 位,禁止中断;

• 为当前悬而未决的最高优先级中断获取中断向量;

• 用程序报文的前 3 个字节填写指令队列,程序报文从在中断向量位置上获取的地址开始;

当 CPU 响应中断时,会自动设置 I 位以避免出现中断 ISR 自身的另外一个中断 (这也叫做中断

嵌套)。在正常情况下,当 CCR 从 ISR 入口处堆栈的值进行恢复时, I 位就恢复为 0。在极个别

情况中, I 位可以在 ISR 内部清除 (在清除生成中断的状态标志后),所以无需等待第一个服务

程序完成,就可以服务另一个中断。如果您还不是一个有着丰富经验的程序员,建议不要使用该

操作,因为它可能导致细微的程序错误,很难进行调试。

中断服务程序以从中断中恢复 (RTI)指令作为结尾。 RTI 指令从堆栈中读取先前保存的报文,

将 CCR、 A、 X 和 PC 寄存器恢复为中断前的值。

注意

为了实现与 M68HC08 器件的兼容, H 寄存器不能自动保存和恢复。

一种不错的编程方法是在中断服务日程 (ISR)开始时就将 H 推到

堆栈上,并在 RTI (用来从 ISR 中恢复)前立即恢复它。

当 I 位被清除时有不止一个中断未决,应首先服务优先级最高的源 (参见 Table 0-22)。

MC9S08DZ60 系列 , 第 3 版

66 飞思卡尔半导体公司

Page 51

0.21.1 中断堆栈帧

条件编码寄存器

累加器

索引寄存器 ( 低阶字节 X)

程序计数器高

* 索引寄存器的高阶字节 (H) 没有自动进行堆栈

*

程序计数器低

²

²

²

²

70

未堆栈顺序

堆栈顺序

5

4

3

2

1

1

2

3

4

5

指向更低阶地址

指向更高阶地址

中断堆栈后的 SP

中断堆栈后的 SP

Figure 0-17 显示了堆栈帧的内容和结构。在中断前,堆栈指针 (SP)指向堆栈的下一个可用字

节。 CPU 寄存器的当前值保存在堆栈中,以程序计数器 (PCL)的低阶字节开始,以 CCR 结

束。堆栈后, SP 指向堆栈的下一个可用位置,该堆栈是比保存 CCR 的地址小一的地址。 被堆

栈的 PC 值是主程序的指令地址,如果中断没有发生,那么将在下一次中断中实施主程序。

Figure 0-17. 中断堆栈帧

实施 RTI 指令时,这些值以相反顺序从堆栈中恢复。作为 RTI 顺序的一部分, CPU 通过读取程

序报文的 3 个字节 (从堆栈中恢复的 PC 地址开始)来填写指令。

在从 ISR 返回前,必须确认 (清除)与中断源对应的状态标记。通常,该标记在 ISR 开始时被

清除,这样如果同一源生成另外一个中断,它就被注册,从而在当前 ISR 完成后为其提供服务。

0.21.2 外部中断请求 (IRQ)管脚

外部中断由 IRQ 状态和控制寄存器 (IRQSC)管理。当 IRQ 功能使能时,同步逻辑监控管脚的

边沿或边沿加电平的触发事件。当 MCU 处于停止模式且系统时钟关闭时,将使用单独的异步路

径,这样 IRQ (如果支持的话)就可以唤醒 MCU。

0.21.2.1 管脚配置选项

IRQSC 中的 IRQ 管脚使能 (IRQPE)控制位必须为 1,这样 IRQ 管脚才能作为中断请求

(IRQ)输入。作为 IRQ 输入,用户可以选择检测边沿或电平 (IRQEDG)的极性,无论管脚检

测到只边沿还是边沿和电平 (IRQMOD),也无论事件造成了中断还是只设置了软件可以轮询

的 IRQF 标记。

IRQ 管脚使能时,默认使用内部上拉器件 (IRQPDD = 0),器件究竟是上拉还是下拉取决于所

选的极性。如果用户希望使用外部上拉或下拉,可以在 IRQPDD 中写入 1,以关闭内部器件。

当把 IRQ 管脚配置为 IRQ 输入时,可以使用 BIH 和 BIL 指令来检测 IRQ 管脚上的电平。

飞思卡尔半导体公司 67

MC9S08DZ60 系列 , 第 3 版

Page 52

注意

这个管脚不包括 VDD的钳位二极管,并且在高于 VDD时不应驱动。

内部上拉 IRQ 管脚上测量到的电压可能只有 VDD – 0.7 V。与该管脚

相连的内门一直拉到 VDD。

0.21.2.2 边沿和电平敏感度

IRQMOD 控制位重新配置检测逻辑,这样它就能检测边沿事件和管脚电平。在边沿和电平检测

模式中,当检测到边沿时 (IRQ 管脚从未断言级更改为断言级), IRQF 状态标记就被设置,但

只要 IRQ 管脚处于断言级,就会连续设置该标记 (并且不能清除)。

0.21.3 中断向量、源和本地掩码

Table 0-22 概括地说明了一下所有中断源。较高优先级的源位于表格下方。中断服务程序地址的

高阶字节位于向量地址栏的第一个地址,中断服务程序地址的低阶字节位于下一个较高阶地址

中。

当出现中断条件时,设置相关标记位。如果相关的本地中断使能是 1,中断请求会发送到 CPU。

在 CPU 中,如果全球中断屏蔽 (CCR 中的 1 位)是 0, CPU 将完成当前指令;堆栈 PCL、

PCH、 X、 A 和 CCR CPU 寄存器;设置 I 位;然后为最高优先级未决中断获取中断向量。处理

然后在中断服务程序中继续。

MC9S08DZ60 系列 , 第 3 版

68 飞思卡尔半导体公司

Page 53

Table 0-22. 向量摘要

向量编号

31 0xFFC0/0xFFC1 Vacmp2 ACMP2 ACF ACIE

30 0xFFC2/0xFFC3 Vacmp1 ACMP1 ACF ACIE

地址

(高 / 低)

向量名称 模块 源 使能 描述

1

模拟比较器 2

模拟比较器 1

29 0xFFC4/0xFFC5 Vcantx MSCAN TXE[2:0] TXEIE[2:0]

28 0xFFC6/0xFFC7 Vcanrx MSCAN RXF RXFIE

27 0xFFC8/0xFFC9 Vcanerr MSCAN CSCIF, OVRIF CSCIE, OVRIE

26 0xFFCA/0xFFCB Vcanwu MSCAN WUPIF WUPIE

25 0xFFCC/0xFFCD Vrtc RTC RTIF RTIE

24 0xFFCE/0xFFCF Viic IIC IICIS IICIE

23 0xFFD0/0xFFD1 Vadc ADC COCO AIEN ADC

22 0xFFD2/0xFFD3 Vport

端口 A,B,D

PTAIF, PTBIF,

PTAIE, PTBIE, PTDIE

PTDIF

21 0xFFD4/0xFFD5 Vsci2tx SCI2 TDRE, TC TIE, TCIE

20 0xFFD6/0xFFD7 Vsci2rx SCI2 IDLE, LBKDIF,

RDRF,

ILIE, LBKDIE, RIE,

RXEDGIE

RXEDGIF

19 0xFFD8/0xFFD9 Vsci2err SCI2 OR, NF

FE, PF

ORIE, NFIE,

FEIE, PFIE

18 0xFFDA/0xFFDB Vsci1tx SCI1 TDRE, TC TIE, TCIE

17 0xFFDC/0xFFDD Vsci1rx SCI1 IDLE, LBKDIF,

RDRF,

ILIE, LBKDIE, RIE,

RXEDGIE

RXEDGIF

16 0xFFDE/0xFFDF Vsci1err SCI1 OR, NF,

FE, PF

15 0xFFE0/0xFFE1 Vspi SPI SPIF, MODF,

ORIE, NFIE,

FEIE, PFIE

SPIE, SPIE, SPTIE SPI

SPTEF

14 0xFFE2/0xFFE3 Vtpm2ovf TPM2 TOF TOIE

13 0xFFE4/0xFFE5 Vtpm2ch1 TPM2 CH1F CH1IE

12 0xFFE6/0xFFE7 Vtpm2ch0 TPM2 CH0F CH0IE

TPM2 通道 1

TPM2 通道 0

11 0xFFE8/0xFFE9 Vtpm1ovf TPM1 TOF TOIE

10 0xFFEA/0xFFEB Vtpm1ch5 TPM1 CH5F CH5IE

9 0xFFEC/0xFFED Vtpm1ch4 TPM1 CH4F CH4IE

8 0xFFEE/0xFFEF Vtpm1ch3 TPM1 CH3F CH3IE

7 0xFFF0/0xFFF1 Vtpm1ch2 TPM1 CH2F CH2IE

6 0xFFF2/0xFFF3 Vtpm1ch1 TPM1 CH1F CH1IE

5 0xFFF4/0xFFF5 Vtpm1ch0 TPM1 CH0F CH0IE

TPM1 通道 5

TPM1 通道 4

TPM1 通道 3

TPM1 通道 2

TPM1 通道 1

TPM1 通道 0

4 0xFFF6/0xFFF7 Vlol MCG LOLS LOLIE

3 0xFFF8/0xFFF9 Vlvd

系统控制

LVWF LVWIE

2 0xFFFA/0xFFFB Virq IRQ IRQF IRQIE IRQ pin

1 0xFFFC/0xFFFD Vswi

0 0xFFFE/0xFFFF Vreset

内核 SWI 指令

系统控制

COP,

LOC,

LVD ,

RESET

ILOP,

ILAD,

POR,

BDFR

,

—

COPE

CME

LVDRE

—

—

—

—

—

看门狗定时器

非法 opcode

BDM- 强制复位

CAN 发送

CAN 接收

CAN 错误

CAN 唤醒

实时中断

IIC 控制

端口管脚

SCI2 发送

SCI2 接收

SCI2 错误

SCI1 发送

SCI1 接收

SCI1 错误

TPM2 溢出

TPM1 溢出

锁定丢失

低压警告

软件中断

时钟丢失

低压检测

外部管脚

非法地址

加电复位

MC9S08DZ60 系列 , 第 3 版

70 飞思卡尔半导体公司

Page 54

1

向量优先级采用从低到高 (最后一栏)的顺序表示。例如, Vreset 是最高优先级向量。

0.22 低压检测 (LVD) 系统

MC9S08DZ60 Series 包括一个防止低压状况的系统,以便在电源电压不稳时保护存储器内容、

控制 MCU 系统状态。该系统由加电复位 (POR)电路和带脱扣电压的 LVD 电路组成,用于警

告和检测。当 SPMSC1 中的 LVDE 设置为 1 时, LVD 电路使能。当进入停止模式时, LVD 禁

止,除非 SPMSC1 中设置了 LVDSE。如果同时设置了 LVDSE 和 LVDE,那么 MCU 不能进入

stop2 (相反会进入 stop3),使能 LVD 的 stop3 模式电流消耗更高。

0.22.1 加电复位操作